### DRAGON VIDEO SYSTEM HARDWARE SPECIFICATION

and the second

$\mathbb{V}_{2}$

June 25, 1985 Revision 4.2 This page intentionally left blank.

۲:

### DRAGON VIDEO SYSTEM HARDWARE SPECIFICATION

and the second sec

June 25, 1985 Revision 4.2

#### COMPANY CONFIDENTIAL

#### RESTRICTED DISTRIBUTION - DO NOT REPRODUCE

The specifications contained in this document are subject to change without notice. For further information or to obtain additional copies contact:

| Bob Rose      | HL02-1/J12 | 225-6136 | SEAMOS::ROSE              |

|---------------|------------|----------|---------------------------|

| Ned Forrester | PKO3-1/K90 | 223-7015 | <b>REGINA::</b> FORRESTER |

## DRAGON VIDEO SYSTEM HARDWARE COMPANY CONFIDENTIAL page 2

**i**

# CONTENTS

4

| 1<br>1.1<br>1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | INTRODUCTION                   | 5<br>5<br>6                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------|

| 2<br>2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.2<br>2.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SYSTEM OVERVIEW                | 9<br>10<br>12                           |

| 3<br>3.1<br>3.2<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.4<br>3.4.1<br>3.4.1<br>3.4.1<br>3.4.1<br>3.4.1<br>3.5.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.1<br>3.5.1.2<br>3.5.2.2<br>3.5.2.3<br>3.5.2.1<br>3.5.2.1<br>3.5.2.1<br>3.5.2.1<br>3.5.2.1<br>3.5.2.2<br>3.5.2.3<br>3.5.2.1<br>3.5.2.1<br>3.5.2.1<br>3.5.2.2<br>3.5.2.1<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.2.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.2<br>3.5.5.5.2<br>3.5.5.5.2<br>3.5.5.5.2<br>3.5.5.5.2<br>3.5.5.5.5.2<br>3.5.5.5.5.5.5.5.5.5.5.5.5.5 | .2 Bresenham Error Computation | 111122222222233333334444444444444444444 |

| 3.7.1<br>3.7.2<br>3.7.3<br>3.7.3.1<br>3.7.3.2<br>3.7.4<br>3.7.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Support                        | 54<br>57<br>60<br>62<br>62              |

# DRAGON VIDEO SYSTEM HARDWARE COMPANY CONFIDENTIAL page 3

-0

,

| 4 DRAGO            | N CHIP REGI                                  | CUBDC > | ND CO  |          | •       |      |       |     |      | £ E        |

|--------------------|----------------------------------------------|---------|--------|----------|---------|------|-------|-----|------|------------|

| 4.1 Add            | ler Chip Reg                                 | ictore  |        |          | )<br>1e | • •  | • •   | •   | • •  | . 05       |

| 4.1.1 A            | dder Chin B                                  | anietar |        | Juniaric | 43 •    | • •  | • •   | •   | • •  | . 05       |

| 4.1.1.1            | dder Chip Ř<br>Interface (                   | Control | Reci   | etore    | • • •   | • •  | • •   | •   | • •  | - 03<br>66 |

| 4.1.1.2            | Scroll Reg                                   | isters  |        |          | • •     | • •  | •••   | •   | • •  | . 72       |

| 4.1.1.3            | Scroll Reg<br>Update Con                     | trol Re | aister |          | • • •   | • •  | • •   | •   | • •  | 74         |

| 4.1.1.4            | Rasterop Co                                  | ontrol  | Regist | ters     | •••     | •••  | •••   | •   | •••  | . 76       |

| 4.1.1.5            | Screen For                                   | nat Con | troll  | Reaist   | ers     | •••  | •••   | •   | •••  | . 78       |

| 4.1.2 A            | dder Chip Co                                 | ommands |        |          |         | •••  | •••   | •   | •••  | . 85       |

| 4.1.2.1            | Register Lo                                  | oading  | •••    |          | •••     | •••  | •••   |     | •••  | . 86       |

| 4.1.2.2            | Rasterop Co                                  | ommand  |        |          |         | •••  | •••   | •   |      | . 88       |

|                    | Processor/1                                  | Bitmap  | Trans  | fers .   | •••     | •••  | •••   | •   |      | . 89       |

| 4.1.2.3.1          | X Mode Pl                                    | BT      |        |          |         |      | •••   | •   | •    | . 89       |

| 4.1.2.3.2          | Z Mode Pl                                    | вт      |        |          |         | •••  |       |     |      | . 91       |

| 4.1.2.4            | Cancel Com                                   | mand .  |        |          |         | •••  | •••   | •   | •••  | . 92       |

| 4.2 Vir            | Cancel Com<br>Der Chip (1/1<br>Viper Chip R  | D Bus)  | Comma  | nds .    |         |      |       |     |      | . 93       |

| 4.2.1 v            | liper Chip R                                 | egister | s      |          |         |      |       |     |      | . 93       |

| 4.2.2 I            | Instruction/                                 | Data Bu | s Ins  | tructi   | ons     |      |       |     |      | 101        |

| 4.2.2.1            | Local Proc                                   | essor I | /D In: | struct   | ions    |      |       | •   |      | 101        |

| 4.2.2.2            | Adder Chip                                   | I/D In  | struc  | tions    |         |      |       |     |      | 102        |

|                    |                                              | -,      |        |          | • •     | •••  | •••   | •   |      |            |

| 5 PHYSI            | CAL CONFIGU                                  | RATION  |        |          |         |      |       |     |      | 105        |

| 5.1 Add            | ler Chip Pin                                 | s       |        |          |         |      |       |     |      | 105        |

| 5.1.1 F            | Processor In                                 | terface |        |          |         |      |       |     |      | 105        |

| 5.1.2 M            | lemory Addre                                 | ss And  | VIPER  | Chip     | Inte    | rfac | e.    |     |      | 106        |

| 5.1.3 1            | /D Bus                                       |         |        |          |         |      |       | •   | • •  | 107        |

| 5.1.4 M            | fonitor Timi                                 | na      |        |          |         |      |       | •   |      | 108        |

| 5.1.5 0            | clocks                                       |         |        |          |         |      |       |     |      | 108        |

| 5.1.6 F            | Power                                        |         |        |          |         |      |       |     |      | 108        |

|                    | per Chip Pin                                 |         |        |          |         |      |       |     |      |            |

| 5.2.1 E            | Bitmap Memor                                 | y       |        |          |         |      |       |     | • •  | 109        |

|                    | /D Bus                                       |         |        |          |         |      |       |     |      |            |

| 5.2.3 V            | Video Output                                 |         |        | • •      |         |      |       | •   | • •  | 110        |

| 5.2.4 0            | locks                                        |         |        |          |         |      |       |     |      | 110        |

|                    | Power                                        |         |        |          |         |      |       |     |      |            |

| 5.3 Hic            | h Speed Tim                                  | ing .   |        | • •      |         | • •  |       | •   | • •  | 111        |

|                    | Lock Genera                                  |         |        |          |         |      |       |     |      |            |

| 5.3.2 \$           | System Sync                                  |         |        | • •      |         |      |       | •   |      | 112        |

| 5.4 I/I            | Bus                                          |         |        |          |         |      |       | •   |      | 113        |

| 5.4.1 H            | External I/D                                 | Bus De  | vices  | • •      |         |      |       | •   | • •  | 114        |

| 5.5 Chi            | ip Selects .<br>nory Address<br>Memory Addre |         |        | • •      |         |      | • •   | •   | • •  | 114        |

| 5.6 Men            | nory Address                                 | Bus .   |        | • •      |         | • •  | • •   | •   | • •  | 115        |

| 5.6.1 N            | lemory Addre                                 | ss Bit  | Assig  | nment    | 5       | • •  | • •   | •   | • •  | 117        |

| 5.6.2 N            | Aemory Refre                                 | sh      |        |          |         |      | • •   | •   | • •  | . 118      |

| 5.6.3 N            | Memory Selec                                 | tion An | ıd Con | figura   | ation   | • •  | • •   | •   | • •  | . 119      |

| 5.7 Mer            | nory Data Bu                                 | s       |        |          |         | • •  | • •   | •   |      | , 120      |

| 5.7.1 V            | Write Enable                                 | Circui  | .ts .  |          |         |      | • •   |     | • •  | . 121      |

| 5.7.1.1            | Single Pix                                   | el Clip | ping   | And So   | croll   | ing  | Bour  | ıda | ries | s 122      |

| 5.8 Vid            | leo Bus And                                  | Video C | Dutput | Circ     | uits    | • •  | • •   | •   | • •  | . 123      |

| 5.9 Pro            | ocessor Bus                                  |         |        | • •      |         | • •  | • •   | •   | • •  | . 124      |

|                    |                                              |         |        |          |         |      |       |     |      |            |

| A DRAGO            | ON CHIP BUGS                                 | AND CH  | IANGES | •        |         | • •  | • •   | • • | •    | . 125      |

| A.1 Pas            | ss 2 Chips .                                 | • • •   | • • •  | • •      | • • •   | • •  | • •   | • • | •    | . 125      |

| A.1 Pas<br>A.1.1 A | Adder Chip -                                 | Pass 2  | ?      | • •      |         | • •  | •     | • • | •    | . 125      |

| A.1.1.1            | Bugs In Th                                   | e Pass  | 2 Add  | er.      | • • •   | • •  | • . • | • • | •    | . 125      |

|                    |                                              |         |        |          |         |      |       |     |      |            |

# DRAGON VIDEO SYSTEM HARDWARE COMPANY CONFIDENTIAL page 4

| A.1.1.2 | Features Not In The Pass   | 2 | Adder         | • |   |   |   |   |   |   | 125 |

|---------|----------------------------|---|---------------|---|---|---|---|---|---|---|-----|

| A.1.2   | Viper Chip - Pass 2        | • |               |   |   |   | • |   |   |   | 125 |

| A.1.2.1 | Bugs In The Pass 2 Viper   | • |               |   |   |   |   |   | Ì |   | 125 |

| A.1.2.2 | Features Not In The Pass   | 2 | Viper         |   | - |   | Ţ |   |   | • | 126 |

| A.2     | Pass 1 Chips               |   |               | • | • | • | • | e | • | • | 126 |

| A.2.1   | Adder Chip - Pass 1        | • | •••           | • | • | • | • | • | • | • | 120 |

| A.2.1.1 | Bugs In The Pass 1 Adder   | ٠ | • • •         | ۰ | • | • | ٠ | ٠ | • | ٠ | 196 |

|         | Dugs III IIIE FASS I AUUEI | : | • • •         | ٠ | ٠ | ٠ | ٠ | ٠ | 9 | • | 120 |

| A.2.1.2 | Features Not In The Pass   | 1 | Adder         |   | • | e |   | • | ٠ | • | 127 |

| A.2.2   | Viper Chip - Pass 1        |   | • • •         | • |   | 0 | • | 0 |   | • | 128 |

| A.2.2.1 | Bugs In The Pass 1 Viper   |   |               | 0 |   |   |   |   |   |   | 128 |

| A.2.2.2 | Features Not In The Pass   | 1 | Viner         |   |   | Ţ | · | • | • | • | 128 |

|         |                            |   | · · · · · · · | • | • | ¢ | 0 | 9 | e | ٥ |     |

|         |                            |   |               |   |   |   |   |   |   |   |     |

|         |                            |   |               |   |   |   |   |   |   |   |     |

INDEX 131

page 5

#### 1 INTRODUCTION

This document describes the hardware of the Dragon Video System that will be used in many future terminals and display systems. These video terminals may support virtual terminals for the control of several different processes by one user, making them DEC's next generation replacement for the VT100 and VT200 series. New display features may include larger screen sizes, variable pitch fonts, rectangular screen regions, and bitmap graphics.

In this specification, the Dragon system is described in its most general form without regard to which features or screen formats will actually be used in any products. Some features may be reserved for future extensions and not be implemented in the initial product offering.

This specification is the complete description of the Dragon system. The second pass Adder chip (DC323B) and Viper chip (DC322B) have some new features, not in the first pass chips. The specification describes only features of the second pass chips; first pass bugs and differences are listed in the appendix. No product design should use the first pass chips.

Under no circumstances should this document be construed as a commitment by Terminals Engineering to produce any terminal related to the enclosed specification. This specification should only be used for training personnel and designing Dragon based products. Due to the confidential and variable nature of the enclosed information, please do not copy this document or allow uncontrolled circulation. Extra copies may be obtained from the authors.

#### 1.1 Definitions

Throughout this document, the terms "Z axis", "Z dimension" or "color" refer to variations in intensity, color or blink as provided by multiple bitmap planes and does not refer to the third spatial dimension. "X" and "Y" do refer to the horizontal DRAGON VIDEO SYSTEM HARDWARE COMPANY CONFIDENTIAL INTRODUCTION

and vertical spatial dimensions respectively.

The term "local processor" refers to the processor that controls the Dragon system. This processor may have non-video tasks such as providing the communications interface of the product to the outside world, or even running the user's application.

"Dragon" or "Dragon system" refers to the entire video system (with or without a local processor). "Chips" or "Dragon chips" refers only to the Adder and Viper chips. "Hardware" refers to all of the Dragon system EXCEPT the local processor and its firmware.

A "viewport" is the place on the screen to which an image is mapped from a "window" in the users data. The term "region", refers to the implementation of viewports in the hardware. 7 × .

Differences between this specification and revision 3.4 are highlighted by change bars in the left margin.

A "<" symbol at the start of a paragraph indicates detailed information that readers may wish to skip during their first reading.

#### 1.2 Related Documents

This specification provides general coverage of the hardware and software concepts of the Dragon system. The following documents provide additional detail of interest to product implementers:

- 1. Dragon Video System Hardware Summary Specification - A 17 page summary of this specification.

- 2. Dragon Firmware Programmers Guide - A tutorial in Dragon programming. Seriously out of date, but still potentially useful.

- DC323 Adder Chip Specification Functional and 3. parametric specification of the Adder chip.

- Functional Description of the DC322 Functional 4. specification of the Viper chip.

- 5. DC322B Video Processor (Viper) Chip Specification - DC and AC parametric specifications of the Viper chip.

The following documents provide implementation examples:

DRAGON VIDEO SYSTEM HARDWARE INTRODUCTION

- DRAGONLIB.C A library of drawing routines written in the C language. Along with associated calling programs, the library provides a set of examples for using most Dragon functions.

- Pegasus Viper and Adder Board These schematics show an implementation of a four plane Dragon system that is programmable to run any memory bus width mode and any resolution mode.

- Pegasus etch board schematics Simplified half page Dragon system.

- QDSS Base Subsystem and Memory Upgrade Modules A full page, 8 plane system with capability to DMA Dragon commands from a Qbus.

COMPANY CONFIDENTIAL

page 8

#### 2 SYSTEM OVERVIEW

The Dragon Video System displays on a raster scanned cathode ray tube driven by a bitmap to facilitate flexible formatting of text and to provide graphics capability in all video terminals. Appropriate modularity allows a range of display and memory sizes to be produced, including full page or traditional partial page displays and with one or more planes of display memory. Monochrome and color displays are available. Display regions are' implemented to facilitate the use of different portions of the screen by different processes. The system allows high speed text (or graphics) update of the bitmap by the local processor to support editing.

#### 2.1 Principal Features

I

1

- A bitmap display provides many well known advantages over a cell display like the VT100. Examples include: variable character size or positioning and inherent graphics capability.

- The full page version of the display provides about 850 thousand pixels refreshed on the screen at 60 Hertz, avoiding the flicker and smear of an interlaced display. (Faster systems may also be possible.)

- 3. The display format is programmable to allow different height, width and refresh rate combinations.

- 4. Arbitrary rectangular regions support multiple viewports on the screen. Each region can be smooth scrolled both vertically and horizontally at various speeds. Incoming data is clipped to the region boundaries. New data can be added to a region even though scrolling is in progress.

- 5. Return of clipping results can be used by the local processor to assist editing, windowing and picking algorithms.

- 6. The interface with the local processor supports either direct local processor access to the video system, or passing of commands through a DMA controller.

- 7. Multiple bitmap planes (up to 24) support applications requiring gray scale, color or control planes. All planes can be manipulated simultaneously.

- Any of the planes can be subdivided into two half resolution or four quarter resolution planes. This allows Z depth (color) to be traded for X resolution.

1

1

L

- 9. Z axis addressing allows an alternate form of memory access that transfers the bits from each plane (or sub-plane) that correspond to one pixel, instead of adjacent X bits from one plane. This can also be used to easily program all planes for a color to be written.

- 10. The basic bit manipulation hardware provides a fast character writing rate of 20 thousand characters/second, if fully supported by the local processor (about 200 msec to fill an average page).

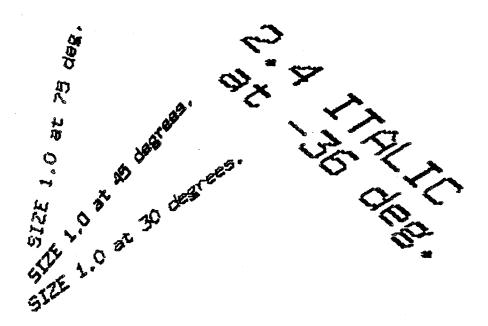

- 11. Text attributes may be extended beyond the VT100 with additions like: arbitrary character size, arbitrary angle, italics, sub/superscript and variable pitch fonts.

- 12. Rasterops are provided that transform a rectangular source to a parallelogram destination of any size or orientation. Halftone tiles or another image may be combined with any destination. Scaled or rotated rasterops (single source) operate at about 0.5 million pixels/sec; normal rasterops operate at about 8 million pixels/sec.

- 13. A rasterop mode allows creation of two-dimensional linear patterns of any cell size. Linear patterns orient to follow the drawing path.

- 14. Another mode of rasterop allows the area between a series of vector pairs to be filled with a solid color, tile pattern or an image at about 8 million pixels/sec.

- 15. The use of 64Kx1 or 64Kx4 RAMs and custom VLSI control circuits will lower the cost of the system to achieve a good cost/performance ratio.

#### 2.2 Hardware

A brief overview of the hardware will aid understanding of the functions presented in sections 3 and 4. Basic timing information is also provided to enable calculation of performance. Additional hardware is introduced in section 3 as it is required. Additional information about the Adder and Viper chips and other Dragon hardware components is contained in section 5; the complete internal specification of these chips is covered by separate documents, see section 1.2.

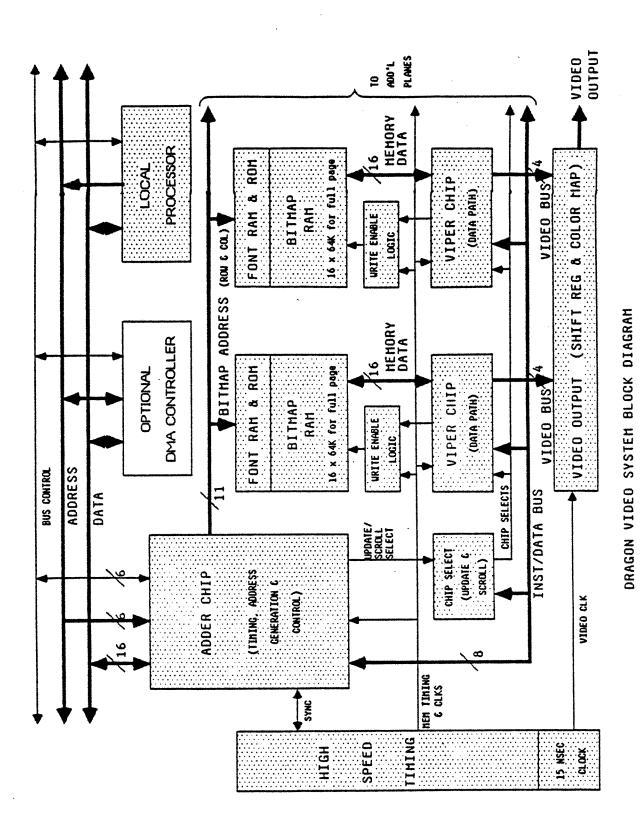

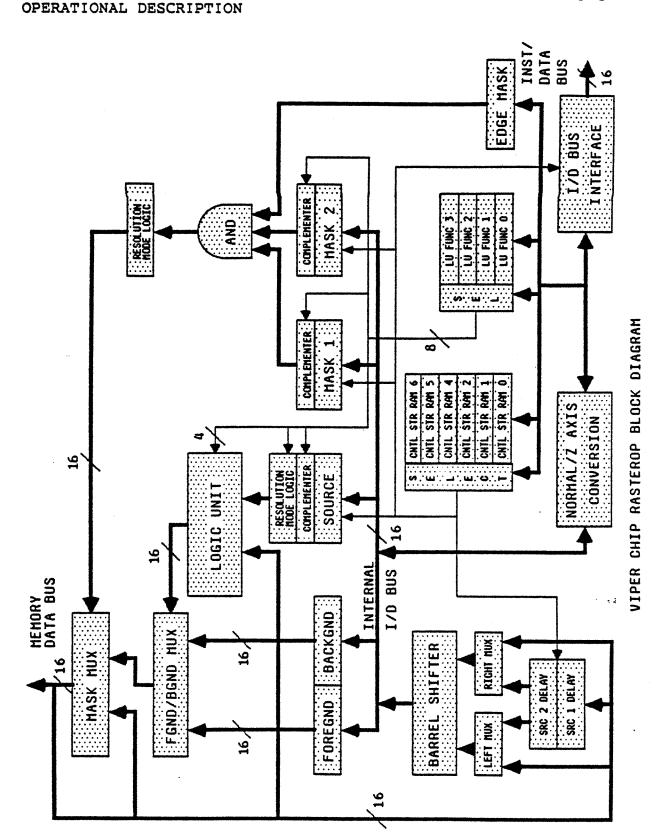

Figure 1 shows the Dragon system hardware. The design uses two, custom, VLSI chips to reduce the cost and size, and increase the speed of the system. The system comprises six logical components: the local processor (optionally, with a DMA

controller), the Adder (address processor) chip (3 micron, ZMOS), the bitmap memory planes, the Viper (video processor) chips (4 micron, HMOS), the color map and shift register circuits, and the high speed timing logic. The Adder chip (DC323, formerly upper chip) is responsible for functions that are common to all planes, such as: local processor interaction, all rasterop computations, bitmap address generation, clipping, screen refresh, scroll control and monitor sync generation. The Viper chip (DC322, formerly lower chip) provides the data path and control elements that are unique to each plane, such as: data FIFOs for refresh and scrolling, a barrel shifter for bit alignment, a logic unit with data and mask registers for memory modification, Z axis address logic, and a control store RAM to define Viper chip operations during rasterops.

< It is possible to synchronize the screen displays of multiple Dragon systems that are running from the same clock generator; no buses may be shared by separate Dragon systems except the local processor bus. Generally, up to 24 Viper chips may be used with each Adder chip; however, if the loading limitations for the I/D bus specified in section 5.4 are not exceeded, up to 32 Viper chips may be used.

#### 2.2.1 Buses

The Adder chip communicates on three buses:

- The local processor bus is controlled by six control and six address lines and has 16 bi-directional data lines that transfer data to/from internal registers in the Adder chip. These registers may be addressed in two ways:

- a. the six address lines are provided for direct access by the local processor through its normal memory or I/O addressing modes;

- b. an address counter in the Adder chip allows a DMA controller to pass data and control words to sequential Adder chip registers via a single bus address.

- 2. The bitmap address bus uses 11 bits each of multiplexed row and column address to the bitmap RAM. This allows an area of up to 8K by 8K pixels to be addressed for update when a 16 bit memory data bus is used (limitations on the displayable portion of this are outlined in sections 2.2.2, 2.2.3, 3.1, 4.1.1.5 and 5.6). All addresses for screen refresh, scroll write back, and bitmap read and update are provided on this bus.

# DRAGON VIDEO SYSTEM HARDWARE COMPANY CONFIDENTIAL

SYSTEM OVERVIEW

Figure 1

COMPANY CONFIDENTIAL

DRAGON VIDEO SYSTEM HARDWARE SYSTEM OVERVIEW

> 3. Finally, the instruction/data (I/D) bus controls the Viper chips and provides for all data flow to and between Viper chips and to/from the local processor (via the Adder chip). Each cycle of the 8 bit I/D bus has four states that provide a 16 bit instruction from the Adder chip to the Viper chips and 16 bits of data from one I/D bus device to the others. These cycles are used to configure the Viper chip registers, to regulate data transfers during rasterops, and to load any external device on the I/D bus, such as a color map. A chip select mechanism, external to the Viper chips (and possibly controlled by the I/D bus) is provided to allow one or more Viper chips to be involved in a transfer.

The Viper chips use three buses:

- 1. The I/D bus described above.

- 2. The memory data bus is used in the transfer of all data into or out of the memories during screen refresh, scroll write back and for memory update. This bus is either 16, 8 or 4 bits per Viper chip, depending on the screen size required.

- 3. The video output bus supplies the bit stream for each plane as successive 4 bit nibbles. These nibbles are externally processed by the color map, video shift registers and D/As to provide the video signal to the monitor.

Readers primarily interested in Dragon programming rather than hardware can skip to section 3.

#### 2.2.2 Bitmap Memory

1

I

The bitmap memory is configurable to three sizes to allow a reduced cost for displays with fewer pixels. This is accomplished by selecting the appropriate bus width mode for the system and then using a minimum of 16, 8, or 4 64Kxl memories per plane for full page, half page and quarter page displays respectively. Up to four memory chips may be attached to each Viper chip data pin (limited by capacitive loading) to increase the memory of a full page plane from 1 Mbit to 4 Mbit (for off screen memory) and still operate at the full specified speed; more memories can be added if the speed is appropriately derated.

The following table lists some data about the three modes. Instantaneous pixel time is the fastest that the memory and Viper chip can operate; average pixel time allows 25% of time for the monitor to be in horizontal or vertical retrace. Approximate

number of displayable pixels is given for two popular frame rates; these numbers could vary by +/- 10% depending on the exact numbers of pixels per scan and scans per frame.

|       | Width | of 64K | Num. of<br>Pix. in<br>Memory | Pixel | Pixel | Pixels | Pixels |

|-------|-------|--------|------------------------------|-------|-------|--------|--------|

|       |       |        |                              |       |       |        |        |

|       |       |        | 1024 K                       |       |       |        |        |

| Half  | · 8   | 8      | 512 K                        | 30 ns | 40 ns | 420 K  | 310 K  |

| Quar. |       |        | 256 K                        |       |       |        |        |

#### NOTE

< The Dragon system is designed to use 64Kxl RAMs that have half the normal page mode access time; this speed is provided by fast static column address circuitry on the RAM. Other approaches to obtain the required speed from 64K density parts might be: 8Kx8 RAMs, 16Kx4 RAMs, and 64Kxl RAMs with other forms of fast page mode output. Some of these options are discussed in section 5.6.3.

#### 2.2.3 Timing

I

1

All timing specified in this document is referred to a standard full page pixel period of 15 nsec. This time represents approximately the fastest system speed allowed by the design (the actual specification is 14.25 nsec). Slower speeds are allowed within the limitations of dynamic storage in the Adder and Viper chips and the memories; it will be possible to operate the hardware at half of this speed (assuming a screen format that provides for bitmap memory refresh).

#### NOTE

< It is likely that some of the process distribution of the chips will be able to operate at greater than specified speed, but this will have to be determined when the parts are characterized. If such chips can be selected, it will be possible to build some systems that have the 60 Hz screen sizes listed above but that operate at 80 Hz, or larger screen formats at 60 Hz; of course, it will be necessary to have memories, monitors and other system components that also operate at the increased speed.

1

COMPANY CONFIDENTIAL

All bus timing, with the exception of the video output bus, is independent of the bus width mode (screen size) and is based on multiples of a 30 nsec clock. The video bus operates at 60, 120 or 240 nsec in a 16, 8 or 4 bit system, respectively; the video bus is always 4 bits wide.

The local processor bus on the Adder chip is asynchronous to the rest of the hardware because its timing is controlled by the local processor (or DMA controller, if present). Internal propagation delays in the Adder chip may require wait states to be added to Adder chip access cycles when used with some processors.

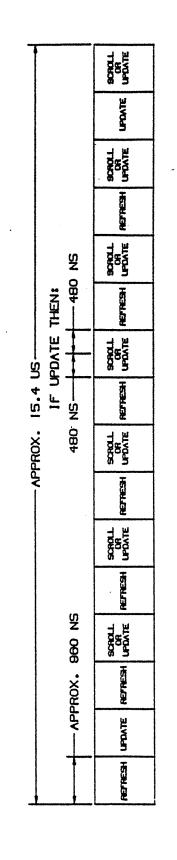

There are two kinds of bitmap memory cycles. A major cycle (960 nsec nominal) is used to read or write 8 words (128 bits in a 16 bit system) to or from the Viper chip for screen refresh or scrolling. Any unused major cycle is subdivided into two minor cycles (also called update cycles, 480 nsec nominal) during any of which either a read or a read-modify-write of a word may occur to accomplish bitmap update. Refresh of the dynamic bitmap memory is accomplished roughly (dependent on screen size parameters) every 0.5 msec (except during vertical retrace, which is less than 1.5 msec) by the screen refresh reads.

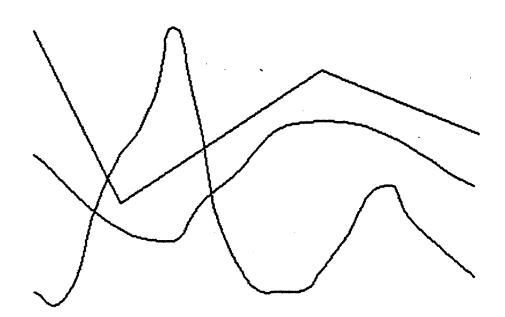

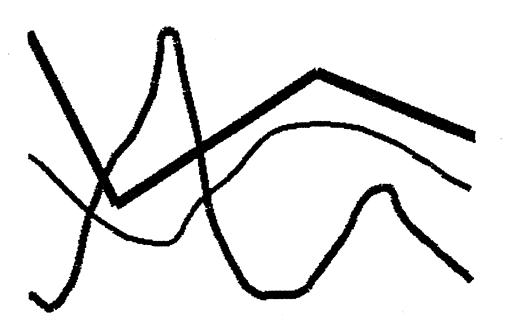

Figure 2 shows an example of a scan which has been divided into 16 major cycles, 7 of which are used for screen refresh, 7 may be used for scroll writeback if any of their words are contained in a scrolling region, and the remaining 2, plus any unused scroll cycles, are divided into minor cycles for updates or NOPs. The address bus provides one row and eight column addresses during a major cycle, and one row and one column address during a minor cycle. The data bus to the Viper chips operates concurrently to transfer 8 words (128, 64 or 32 bits) during a major cycle, and to read and return a modified word during a minor cycle.

Each scan can be programmed to last an integer number of major cycles (N  $\geq$  2R+2, where N is the number of major cycles/scan and R is the number of major cycles used to read the data that is refreshed on the screen). Enough screen refresh memory reads must be executed on each scan to display 512 pixels horizontally, regardless of the bus width, to guarantee dynamic memory refresh (not all of these pixels need to be displayed, but they must be read). No more than 2048 pixels may be contained in one scan (including horizontal retrace time); no more than 1024 pixels can be displayed unless extra memory is added to each plane beyond the minimum requirement. The positioning and width of horizontal blank and sync are programmable with respect to memory cycles. Any number of scans per frame may be programmed, up to 2048 (including vertical retrace time); the number of displayable scans is limited by the amount of memory used (for a minimum full page, 992 scans could be displayed; this is the memory height of 1024, less 32 for down scrolling; see section 3.3.1). The position and width of vertical blank and sync are

MEMORY CYCLES DURING ONE SCAN

## DRAGON VIDEO SYSTEM HARDWARE SYSTEM OVERVIEW

COMPANY CONFIDENTIAL

page 15

Figure 2

COMPANY CONFIDENTIAL

DRAGON VIDEO SYSTEM HARDWARE SYSTEM OVERVIEW

programmable.

The I/D bus operates continually at the minor cycle rate (480 nsec nominal), whether major or minor cycles are in progress and in sync with the memory cycles, during which it transfers two instruction bytes and two data bytes.

The computation cycle of the Adder chip is two major cycles (1920 nsec, nominal). In this time, all source and destination address computations occur for one step of a rasterop. This step may be either one pixel or, if the rasterop is progressing parallel to the X axis and is not scaling the source, a whole bitmap bus word (see additional conditions in section 3.5.1.3). Four additional compute cycles are required to initialize a rasterop. Computation can occur with or without available update cycles and there is a small amount of buffering of results (6 addresses, eg. 3 sources and 3 destinations, 6 destinations, This allows optimum use of update cycles. No source and etc.). one source operations are compute bound when no scrolling is in progress; any other operations may be memory cycle bound. In general, the time to load data and start the next rasterop is in addition to the rasterop execution time, although the rasterop origins may be loaded during rasterop execution so that sequential text characters may be written to the bitmap without wasting time between characters.

All performance data in the remainder of this document will be for a full page (16 bit) system only. The performance of the smaller systems can be calculated from the above data.

#### COMPANY CONFIDENTIAL

page 17

#### 3 OPERATIONAL DESCRIPTION

This section describes the overall capabilities, functions and performance of the Dragon video hardware in general terms; most of the description covers the Dragon chips with reference to support expected from the local processor. Section 4 will present the interface and registers of the Adder and Viper chips in detail.

#### 3.1 Memory Organization

The design of the Adder chip provides one large rectangular bitmap memory of fixed dimensions for the storage of data. Any address to this memory consists of an X and a Y component. All bit map space must be allocated two dimensionally.

The bitmap memory is not directly accessible to the local processor, and the Adder chip does not perform rasterop manipulations in the local processor's memory; but, requests may be made for data exchange between processor memory and the bitmap.

The memory is divided into an on screen and an off screen portion. The on screen memory is a rectangle starting at the address [0,0] to (but not including) the address [X limit, Y limit] (these limits are programmable in the Adder chip; this includes all memory that is read (but not necessarily displayed) by the screen refresh process. The memory in the rectangle from address [0, height of displayed screen (scans)] to (but not including) the address [X limit, Y limit] is not usable for any purpose. The off screen memory is all the rest of the memory; it is "L" shaped in the general case. (See the description of the X limit and Y limit registers in section 4.1.1.5 for more information.)

The dimensions of the bitmap memory are implementation dependent. Generally, the height and width are powers of two; for minimum 16, 8, and 4 bit bus widths the height is 1024, 512 and 256 respectively, while the width is 1024 in each case. When additional memory is used, rectangles of these sizes can be added in either the X or Y direction out to a limit of 8Kx8K pixels. It is possible to use hardware external to the Adder chip to alter the power of two restriction.

#### 3.2 Dragon System Control

The hardware is controlled by the local processor through the loading of command and data registers in the Adder chip. Registers control the configuration of the Adder and Viper chips for: screen format, video sync, scrolling and rasterops.

The processor can load any of the writable registers directly. Several status bits can be read by the processor to know if the Adder chip is ready to accept (or provide) data; these include: rasterop initialization complete, rasterop computation complete, address buffer empty, pause complete (programmable frame sync), scroll service required and vertical blank (fixed frame syncs), ID bus data ready, and various clipping occurrences (the use of each bit is described in section 4.1.1.1). Any of these status bits may be enabled to assert an interrupt request pin on the Adder chip.

If the local processor is not dedicated to video service or is providing complex video services, it may not wish to wait for the appropriate Adder chip status before proceeding with its next request. To allow decoupling of local processor computations from Adder chip execution, an interface for a DMA controller has been provided. A request pin may be programmed to assert on any of the same conditions that are available as flags or interrupts to the local processor; this request will fetch the next data word from the DMA controller. When loading data and command registers, the DMA controller writes to a special address in the Adder chip that is associated with an internal address counter. If the MSB of the data word is clear, the counter addresses the Adder chip register to which data is to be transferred; the counter is incremented after each word is transferred. If the MSB of the data word is set, the address counter is loaded with the low six bits of the data word. Only the ID bus data registers contain 16 significant bits of data; to allow arbitrary data to be loaded to these addresses, the MSB does not cause the address counter to be loaded if it is pointing to either of the ID data registers (the addresses of these registers are preceded by reserved register addresses so that no register load will cause the address counter to be inadvertently left pointing to an ID data register). The register addresses are assigned such that common repetitive functions only need access one group of consecutive registers, in addition to the command register.

#### 3.3 Viewport Support

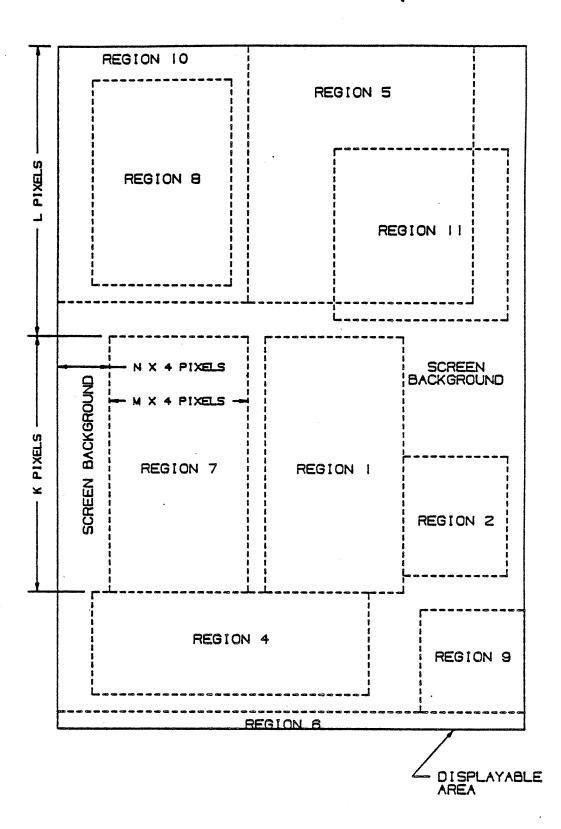

To assist the implementation of multiple viewports on the screen, the Dragon chips provide clipping to and scrolling or dragging of rectangular regions (the term "region", as used in this document, refers to the implementation of viewports in the hardware). The top and bottom of a region may be set to any pixel, the left and right edges must lie on a multiple of 4 pixels from the left side of the screen. Figure 3 shows examples of possible region configurations. There is one clipping (update) region and one scrolling region at any instant, but the two are independent of each other so that writing and scrolling may be active in different regions at the same time. Any part of the screen not currently contained in either the clipping or scrolling region cannot be modified and will continue to contain

I

any data placed in it when it was previously contained in a region. The whole update region may be either scrolling or not, but a region should not be updated if only part of it is scrolling (eg. region 11 should not be updated if region.5 is being scrolled).

#### NOTE

< It is possible to have the left and right edges of a region specified to single pixels, but this requires many chips external to the Adder chip. Also, clipping status would not correspond to these edges; and, it would be impossible to use memories that are organized by four bits (because these will have only one write enable for all bits). For more information, see section 5.7.1.1.

When updating a region, clipping allows the image outside of the region to still be computed but with writing disabled. The Adder chip provides status to the local processor to indicate if any rasterop was completely or partially clipped while writing or whether any rasterop was not completely clipped (to aid a picking algorithm). These clipping status bits are accumulated as rasterops progress, and may be read or cleared at any time, but the results are only predictable if they are read or cleared between rasterops.

To the greatest extent possible, the regions are allowed to be independent. In some ways, this is not possible. The scrolling resource must be allocated to only one region per frame time (and an additional frame time is normally required to change regions). Unless large amounts of color map and a controller are provided, all regions must share one color map and agree on the resolution mode settings. Unless large amounts of extra bitmap are provided, regions probably share the off screen areas used for symbol storage. Obviously, overlapping regions cannot be independent of each other.

#### 3.3.1 Scrolling

Scrolling movement can be up, down, left or right (not diagonally) at a rate from 0 to 15 pixels/frame (or faster for vertical scrolls). The part of the region vacated by the moving image is simultaneously filled with any solid color. Scrolling uses part of the memory time that would otherwise be available for writing; but, even when the whole screen is in motion, about 30-40% of the non-scrolling update time is still available for source/destination operations, depending on screen format (50-80% of non-scrolling time is available for destination only or source only operations because these operations are primarily compute

page 20

REGION EXAMPLE

Figure 3

COMPANY CONFIDENTIAL

#### page 21

bound when not scrolling).

#### NOTE

< Actually, the distance that may be moved during an upward scroll is limited only by the number of scan times allowed for vertical retrace, as this time is used to write the fill color back into the vacated memory (if the region extended to the bottom of the screen). The distance of a downward scroll is subject to the memory limitation described below.

Scrolling is accomplished by moving all of the scrolling data from its old position in memory to a new position. The normal screen refresh process reads and displays the existing memory data; and additional memory write cycles are used where necessary to return scrolling data to new locations. This is the only technique that allows any size region, including the whole screen, to be scrolled in one frame time; but there are two unpleasant side effects. First, only one region can be in motion during a frame time, because two regions might want to write portions of the same word to more than one memory location. Second, down scrolling cannot be accomplished in the obvious way because this would require writing data into memory locations not yet read by the refresh/scrolling process, thereby destroying screen data.

< Instead, down scrolling moves all of the data outside the scrolling region up, and then offsets the memory address at which screen refresh starts reading the bitmap, thereby creating the illusion that the scroll region moved down. (Proper synchronism is maintained so that the data outside the region does not move.) This creates four bad effects:

- Some scans of memory must be reserved (and not displayed) to prevent data at the bottom of the screen from being overwritten by data from the top. The number of scans required is equal to the maximum distance, in pixels, to be down scrolled in one frame time.

- The consumption of writing time is as if the whole screen were up scrolling. Scroll writing must occur throughout the frame so that all data can be moved up in planes where scrolling is "disabled".

- Diagonal scrolling is not possible because different data must be moved for the downward and sideways motion of a region.

- 4. Management of the Y Offset adds extra work for the local processor.

To synchronize scrolling commands with screen refresh, most of the scroll related registers in both the Adder and Viper chips are double buffered. In the Adder chip, the index registers are only buffered to the extent required for the continuation of scrolling in one region (see note below). The pending half (top level) of any of the buffered registers is addressable by the local processor and is loaded at any time during a frame; between frames, the Adder chip transfers the data from all pending registers to the active registers and then sets the flag that requests more scroll data.

To prevent interference between the loading of Viper chip registers for scrolling and for update, a separate ID command and data path (including chip select control for the Viper chips) is provided for scrolling; this allows a scroll service routine to act without regard to the state of update service. The scroll and update services must avoid using each other's registers. The use and control of the index registers is somewhat more complicated and is described in section 3.3.4.1.

#### NOTE

To conserve die area in the Adder chip, < scroll registers are only buffered to the extent required to sustain scrolling or dragging of a single region. Extra buffering of the index registers would be needed to scroll different regions in successive frames. This function is not considered important because its only use would be in trying to simulate simultaneous scrolling of two separate regions; however, a smooth effect cannot be achieved by this technique, anyway, so it should not matter if the abruptness of jump scrolling of the two regions is increased. If the local processor can service an interrupt request to load four registers in 200-500 usec (depending on screen format), then it will be possible to scroll different regions in successive frames without the extra buffering of the index registers. (Normally, the local processor may take an entire frame time to load any buffered register.)

#### 3.3.2 Dragging

The scroll function can be used to smoothly drag a region to a different place on the screen. For each increment of motion, the scroll boundary registers are set for the current region location, but with the region size increased in the direction of motion by the distance to be moved; this allows the whole region

to be moved, without the normal truncation, and leaves the fill color in the "wake" of the region. Because the region boundaries can only be defined on four pixel increments in the horizontal direction, horizontal dragging must stop on four pixel boundaries; however, it is possible to move the region at any valid scroll speed during the drag. If desired, the area to be covered by the moving region may be saved prior to each movement; and the area vacated may be restored following each movement. A region cannot be updated while it is scrolling because there is no way to synchronously change the clipping boundaries; the clipping boundaries are NOT double buffered like the scroll boundaries.

#### 3.3.3 Clearing A Region

The Adder chip has a provision to allow a region to be cleared to the fill color in one frame time, using the bulk scrolling hardware. This action will be linked to one frame time in the same way that scrolling is. While small regions (less than one sixth of the screen) can be cleared more quickly with a rasterop and without waiting for the next frame time, use of the erase mechanism will provide a very clean appearance because it is synchronized to occur between two display frames.

#### 3.3.4 Drawing In The Scrolling Region

The blank space that is created by scrolling needs to be filled with new data. It is desirable to draw while scrolling continues so that the smooth effect of the scroll is not disturbed. The indexing mechanism of the Adder chip allows data to be drawn to the correct screen location without regard to how scrolling is moving the screen. Typically, the update process draws the display list (or selected portions of it) repeatedly to keep filling in the scroll region as more blank space is created.

The clipping region stands still during scrolling to prevent data from being written outside the region. However, this means that the clipping region cannot be used as a "drawing function" to control the shape or extent of objects being drawn into a moving region, because the clipping region does not move with the objects as they are drawn. Also, clipping cannot be used to prevent multiple writes of data when the same display list segments are repeated during scrolling; this would require the clipping region to follow a particular set of blank pixels as they move on the screen. Multiple writes will create problems for display lists that contain segments drawn in complement mode or drawn with the painter's algorithm (in which successive elements replace previous elements).

COMPANY CONFIDENTIAL

page 24

To enable synchronizing the update process with scroll commands, (to fill the blank areas created by scrolling), the pause register and the interrupt or request enable bits can be set to interrupt the local processor or request further data from a DMA controller when a specific point on the screen has been passed by screen refresh. Normally, the pause would be set, by the scroll service routine to allow the update process to continue after the top or bottom of the scroll region has been displayed; this allows a full frame time to fill the top or bottom edge of a region that is up or down scrolling, before the blank space would become visible.

#### 3.3.4.1 Indexing

To allow updating from the local processor or DMA controller into a region that is scrolling (or has scrolled) without requiring the local processor to change the coordinate values in its display list, there are index registers in the Adder chip that are added to the first source and destination coordinates to match the new position of data that has been moved in the memory by scrolling. There are six index registers: old X and Y, new X and Y, and pending X and Y. The old values are the indexes that apply to data that has not yet moved during the current frame; the new values are the indexes that apply to data that has already been moved; the pending values will become the new values at the start of the next frame. Between frames, the Adder chip transfers the value stored in the new register to the old register, and from the pending register to the new register, thus starting the new frame with the correct indexes. The index values apply to the region that is being updated. Ordinarily if the update region is also being scrolled, the new and old indexes will differ by the scroll constant (X or Y) for the current frame (loaded in the previous frame); and if the update region is not being scrolled the new and old values are the same.

The index values must be changed by the update process between updates to different regions. Also, if the update region is being scrolled, the scroll process must update the index values between frames so that updates will stay locked to the scroll movement when they extend beyond the end of one frame time. Because both the update and scroll processes modify the index registers and the update process must use the most recent values provided by the scroll process, a very tight interlock must be maintained between these two processes.

This interlock is maintained by the local processor thus, in general, if the update process is driven by a DMA controller, the update process may not change the update region to one that is scrolling because a frame may end between the time that the local processor places index values in the data list for the DMA controller and the time that these values are loaded into the Adder chip. Thus it is best not to send region changes through a

COMPANY CONFIDENTIAL

page 25

DMA controller.

I

I

< When the local processor changes the update region, the following interlock with the scroll process is recommended:

- The local processor always executes the scroll process and the part of the update process that changes regions (no DMA controller).

- 2. The update process must be interruptable by the scroll process when the update process is changing regions (note exception below), unless the latency caused by disabling interrupts during index loading is acceptable to the system.

- During a region change, the update process loads a memory location that tells the scroll process what region is now being updated.

- 4. The update process copies the correct index values for that region from a table maintained by the scroll process to the Adder chip registers. The index registers must be loaded in the order: pending, new and then old. If the instruction(s) that is used to move each index value to the Adder chip is interruptable, it is necessary to disable interrupts (at least for the priority of the scroll service interrupt) while each index value is copied.

- 5. If a new frame is started, the scroll process will be awakened by the scroll service interrupt from the Adder chip. The scroll process must run to completion before returning to the update process. The scroll process updates the index table entries for the region being SCROLLED so that new values will be available to the update process.

- 6. The scroll process should load all six index registers in the Adder chip with the new values for the region being UPDATED. If the update region is NOT the same as the scroll region, the registers need not be loaded. If the scroll process is certain that the index values in the Adder chip corresponded to the region being scrolled BEFORE the end of the frame that caused the scroll interrupt (perhaps there is only one region on the screen or only the scroll region has been updated since the last scroll), then only the pending index registers need to be loaded.

- 7. Update processing may now continue.

#### COMPANY CONFIDENTIAL

#### DRAGON VIDEO SYSTEM HARDWARE OPERATIONAL DESCRIPTION

#### 3.4 Multiplane Support

The use of multiple Viper chips (data path chips) allows the simultaneous manipulation of data in many planes of memory. The Viper chips are controlled by and exchange data on the I/D bus as described above. The registers for data transfers and the logic functions to be performed may be independently programmed for each Viper chip in a system.

The number of planes is limited, by the fanout of the I/D and address buses, to 24 Viper chips (buffering of the address bus is required; the 400 pf maximum load on the I/D bus may permit 32 Vipers if a close layout is maintained). Z axis operations are limited to addressing 4, 16 bit words of Z data which allows a maximum of 64 planes or subplanes; this corresponds to half the maximum number of subplanes that would otherwise be possible from 32 Viper chips.

#### 3.4.1 Resolution Mode

The resolution of any or all planes may be set to 1, 2 or 4 bits/pixel. In one bit mode, each of the four bits appearing on the video bus of a Viper chip defines two possible states for each of four pixels on the screen; in two bit mode, each of the two pairs of bits defines four possible states for each of two pairs of horizontally adjacent pixels on the screen; and, in four bit mode, each output to the video bus defines 16 possible states for four horizontally adjacent pixels. One of the two or four divisions of a low resolution plane is referred to as a subplane.

The actual interpretation of the video bus data as multiple states for adjacent pixels must be provided in the color map; but, the Viper chip provides modifications to the use of data and masks, the interpretation of barrel shift values, and the effects of Z axis addressing that aid the manipulation of low resolution planes (see section 4.2.1 for an complete description of the effects of resolution mode). Resolution mode in the Viper chips affects only the writing of new data so that different regions can have different resolution settings; however, additional external hardware would be required to actually provide different color map interpretations to different regions.

< Resolution mode has the limited application of allowing a tradeoff between Z depth and X resolution in one or more planes; it is not intended to provide more general purpose planes than there are Viper chips. Note that subplanes are NOT independent of each other as are planes implemented with separate Viper chips. Some of the restrictions on subplanes are:

1. Subplanes share update settings for the logic function and control store ram in the viper chip.

- 2. Complement mode writing will not work in general because each of the bits in a low resolution pixel will be addressed separately, but both bits will be written during each access. Some but not all of the problems with complement writing can be avoided by programming a mask register in the Viper chip to permit writing to only one bit within a low resolution pixel.

- 3. Writing speed per low resolution pixel will be proportionately reduced because The Adder chip still addresses the memory as if it were full resolution, accessing each bit within a low resolution pixel. Of course, there are fewer low resolution pixels on the screen, so the time to draw a given fraction of the screen is the same as for full resolution.

- 4. Fonts and patterns loaded off screen may have to be scaled up horizontally, depending on the intended use.

- 5. Subplanes cannot be scrolled independently. When horizontally scrolling a region that contains subplanes, the region should only be moved by multiples of the lowest resolution subplane to preserve the phase of low resolution data. The maximum horizontal scroll speed (pixels/frame time) would be proportionately reduced in low resolution planes because the pixels are larger.

- 6. When subplanes are enabled in a Viper chip, the low resolution pixels are of longer duration; enabling subplanes does not increase the data rate through a Viper chip.

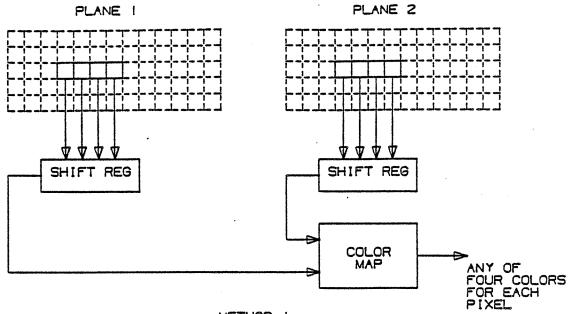

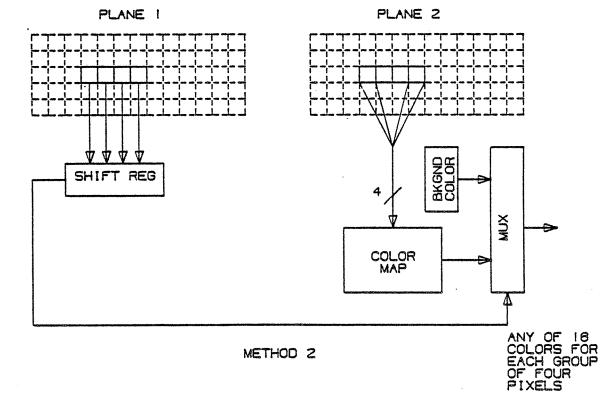

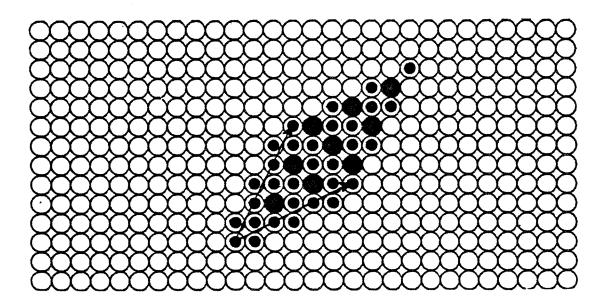

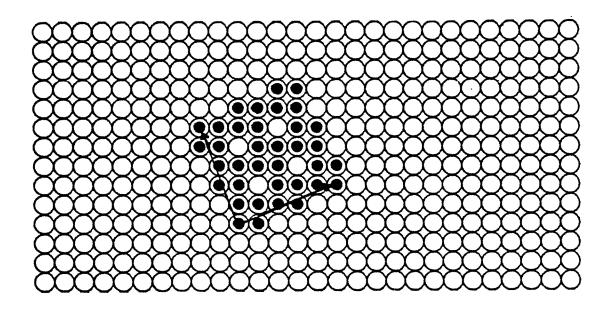

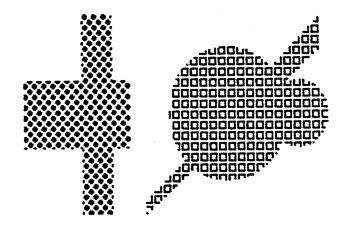

Figure 4 shows two examples of the use of resolution mode. In the upper example, two planes are used, both in 1 bit mode, whose video output buses are serialized by shift registers to form a two bit code that accesses one of four values from a color map to determine the color of each pixel. In the lower example, one plane is used in 4 bit mode to choose one of sixteen foreground colors for four adjacent pixels while the 1 bit mode plane makes an independent choice of this foreground color or a screen-wide background color for each pixel in the group of four.

#### 3.4.2 Z Axis Addressing

Z axis operations allow the exchange of data between the Adder and Viper chips on the I/D bus by using the 16 bits of a data word to transfer one bit to/from each of 16 planes or subplanes. This can be used for both the exchange of data between the local processor memory and the bitmap, and the loading of appropriate Viper chip data registers.

#### DRAGON VIDEO SYSTEM HARDWARE COMPANY CONFIDENTIAL OPERATIONAL DESCRIPTION

#### page 28

METHOD I

ALTERNATE USE OF MEMORY PLANES FOR COLOR

Figure 4

COMPANY CONFIDENTIAL

< Each Viper chip can be programmed with a six bit plane address; the lower four bits specify the bit within an I/D bus data word to which a Viper chip will respond during a Z axis operation; and the upper two bits specify the Z block (separate I/D bus transaction) if more than 16 planes or subplanes need to be transferred. Alternatively, chips selects may be used to enable groups of viper chips to form Z blocks.

A 1 bit resolution plane may have any plane address, and transfers the addressed bit on the I/D bus; a 2 bit resolution plane must have an even address, and transfers the addressed bit and the next higher bit; and a 4 bit resolution plane must have an address that starts on a nibble boundary, and transfers the whole nibble whose lowest bit corresponds to the plane address. No two planes may have the same address; and no other plane may have a plane address equal to the addresses of any of the two or four bits accessed by a low resolution plane (this must be ensured by the local processor).

During local processor/bitmap data exchanges, data in a normal rectangle from the bitmap is transferred to/from a DMA controller or the local processor. If Z mode transfers are requested, each word transferred will be the color of one pixel. For more information see sections 3.5.3 and 4.1.2.3.2.

A Z axis I/D bus cycle can be commanded directly, with an I/D command, to load either the source, foreground, background or scroll fill data registers in the Viper chips. The source register is one input to the logic units in the Viper chip, the foreground and background registers are selected on a bit-for-bit basis by the output of the logic unit and loading them with a Z axis command can program the Viper chips for the colors with which subsequent elements will be drawn. The fill registers in the Viper chips define the color that will be written into the new areas of scrolled regions.

3.5 Basic Address Calculation And Data Path Hardware

The Adder and Viper chips contain bitmap manipulation hardware to execute the commands provided by the local processor. All manipulations are based on rasterops, which can select pixels from an area of the screen (a source) and combine them with pixels selected from another area (a destination). The Adder chip handles all word and bit addressing, clipping, and control. The Viper chip provides bit alignment, data exchange and logical combinations. There are three rasterop modes: normal, linear pattern, and fill. This section will describe the normal mode; the linear pattern and fill modes will be described in section 3.7.

The contents of the Adder and Viper chip rasterop parameter registers are NOT modified or destroyed by any operation of the

system. Only those registers whose values are to be changed need to be loaded between operations. Of course, the content of data registers may be changed by rasterops.

#### 3.5.1 Adder Chip - Addressing

L

1

Every rasterop has a destination and may have zero one or two sources; a zero source implies a constant source. The destination generator selects pixels to be modified and the source generators select pixels being combined with the destination. No curve algorithms are implemented because all of the useful ones require multiplications and there is no "best" algorithm for all applications; curves may be handled by passing a series of straight vectors to the Adder chip.

The destination is a parallelogram and may be a different size or orientation than the first source rectangle with the data scaled or rotated to fit the destination. Rotation and scaling are used more for transforming picture elements such as characters and patterns than for transforming whole pictures. However, scaling can be used to "zoom" an image to an area of the screen by a scaled copy from another area, possibly off screen. The parallelogram (as opposed to simple rectangle) form of the destination is largely a fallout of its implementation as two independent vectors, but is useful for forming italic characters and performing operations on screens with non-square pixels. As discussed below, rotation and scaling may not be suitable during complement mode drawing operations.

The sequence of source/destination operations is controlled by the Adder chip command register; three bits select one of the eight possible combinations of sources and a destination (sources: none, first, second and both, destination: on, off; not all of these combinations are useful); the source and destination addresses are always computed, but these three bits determine whether they are used. The effect of the source data is determined by the programming of the Viper chips.

The origins for the first source and the destination areas may be offset by the addition of an X and a Y index. Index mode may be invoked for either the first source or the destination independently but the X and Y index values are the same for both. This mode allows the command data to remain unmodified when a region has been scrolled or is being scrolled (only the index values need to be updated), and/or the origin of a region may be 0,0 to the update process regardless of its actual location in the bitmap.

All address computations in the Adder chip use 14 bit, two's complement numbers for each of X and Y. Beyond the 14 bit limit, calculations will wrap from plus to minus in the normal fashion. The usable range of values for any of the DX or DY registers is

COMPANY CONFIDENTIAL

page 31

+/- 12 bits (+/- 4095) because these values are multiplied by two in some internal calculations; however they are still specified as 14 bit, two's complement numbers. 13 bits of the X address (including specification of the pixel within a word) and 13 bits of the Y address are available at the output of the chip (in 16 bit bus width mode). The large address output of the Adder chip is provided to allow bitmap writing for a laser printer, which will require about four times the resolution in both X and Y as will a video display.

A six deep FIFO is provided to store the computed addresses before they are used in memory cycles; this allows better use of available memory cycles during scrolling. If only one destination or source is required, six operations can be stored (and two more can usually be computed while these are being used, so that at least 8 operations can be performed during each scan of scrolling if the screen format allows); and, if source/destination operations are required, then three (or two for double source) operations can be stored.

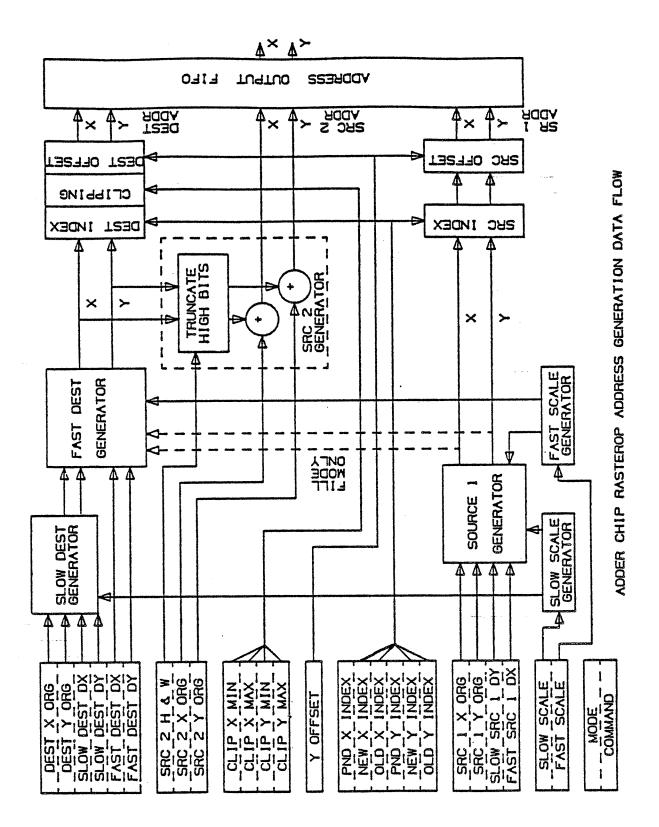

In the following discussion of Adder chip computation functions, it may be helpful to refer to the Adder chip computation address path diagram, shown in Figure 5.

#### 3.5.1.1 Destination - Rotation

1

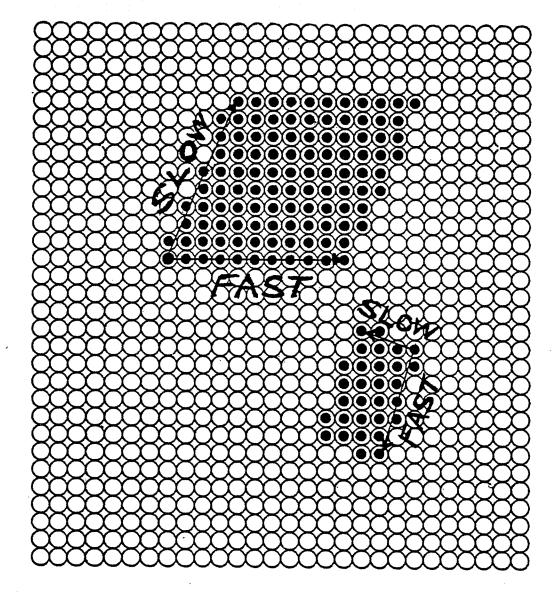

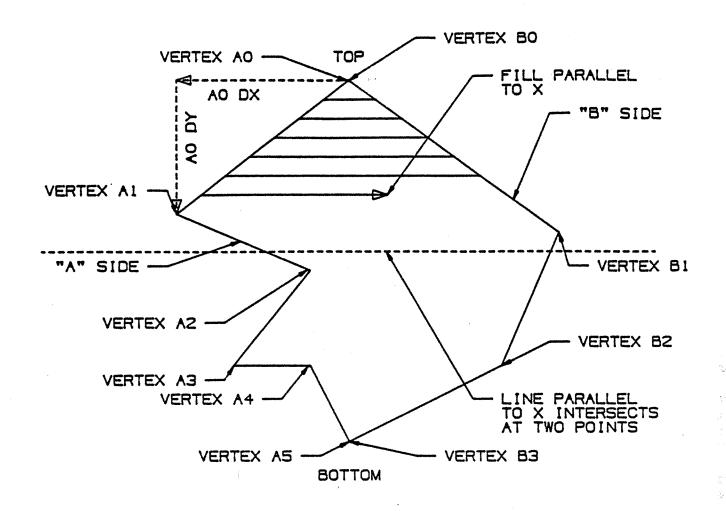

The destination is a parallelogram defined by two vectors and an origin (see Figure 6). Each vector is defined by two signed integers representing a horizontal delta (DX) and a vertical delta (DY) and both vectors start at the same origin. The area is scanned by addressing pixels along the path of one vector (the fast vector), starting from the destination origin (after indexing, if selected), until it is exhausted; and then, using the next pixel on the path of the other vector (the slow vector) as a new origin for another fast vector with its same DX and DY; fast vectors are scanned until all of the pixels on the slow vector have been addressed. Thus parallelograms of any size or rotation can be scanned. Parallelograms can be used to scan rectangles on screens having non-square pixels.

The pixels on the path of the vectors are computed by Bresenham's Algorithm. Of the two components (DX and DY) of a fast or slow vector, one component is generally longer than the other and is called the "major axis"; the shorter component is called the "minor axis". According to Bresenham's Algorithm, the number of pixels selected along the path of a vector is equal to the length of the major axis. The origin and all points up to but not including the last point on any vector (the point at "origin+delta") are selected. The last point is not included because then the length of a vector would be one pixel too long, and an adjoining rasterop should not select the last point (its first point) a second time because this would restore a pixel to

Figure 5

page 33

its original state during complement writing. Because the destination can be indexed and is corrected for the effects of Y offset used in down scrolling, it can address any portion of the bitmap memory.

### Example Destination Rasters

Figure 6

3.5.1.1.1 Holes And Duplications

Survey of this scanning technique for the destination, some fast and slow vector combinations will cause some pixels within the parallelogram to be addressed more than once, some vector combinations will cause some pixels to be missed, and some vector combinations will cause both effects or neither effect within the parallelogram. The following combinations of fast and slow vectors will create duplications (Figure 7 shows an example that creates duplication):