# **DYS50**

## **Technical Manual**

Prepared by Educational Services of Digital Equipment Corporation Copyright © 1983 by Digital Equipment Corporation

## All Rights Reserved

The reproduction of this material, in part or whole, is strictly prohibited. For copy information, contact the Educational Services Department, Digital Equipment Corporation, Maynard, Massachusetts Ø1754.

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

Printed in U.S.A.

Mate-N-Lok is a trademark of AMP, Inc.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts.

| digital      | DECwriter    | RSTS           |

|--------------|--------------|----------------|

| DECdataway   | DIBOL        | RSX            |

| DECsystem-10 | MASSBUS      | UNIBUS         |

| DECSYSTEM-20 | PDP          | VAX            |

| DECUS        | P/OS         | VMS            |

| DECmate      | Professional | VT             |

| DECnet       | Rainbow      | Work Processor |

|              |              |                |

## CONTENTS

## PREFACE

| CHAPTER 1                                                                                                                                                                    | INTRODUCTION                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

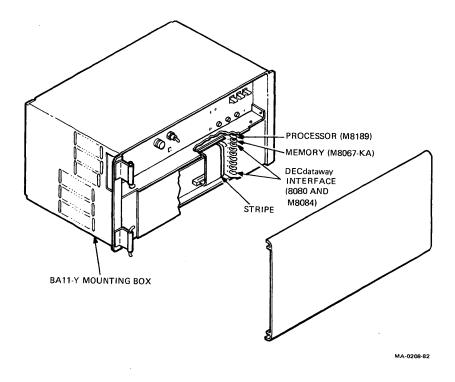

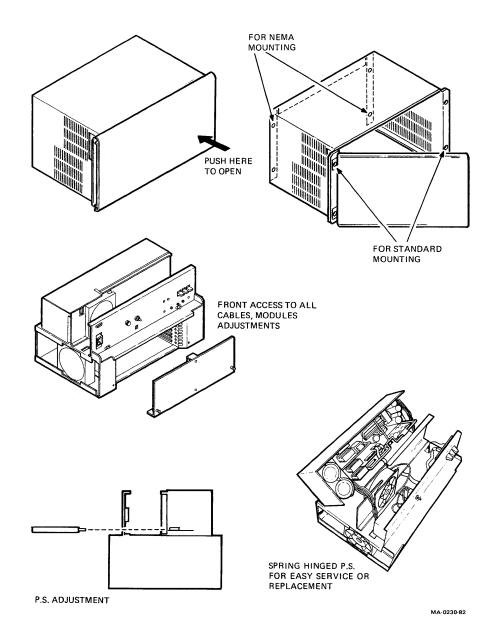

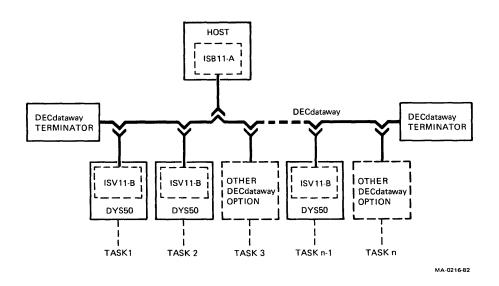

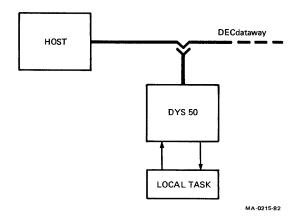

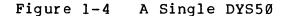

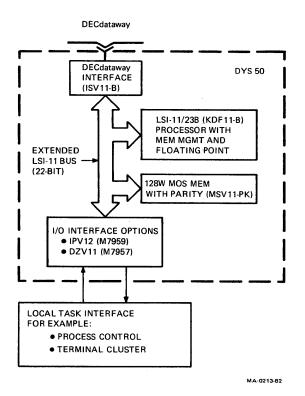

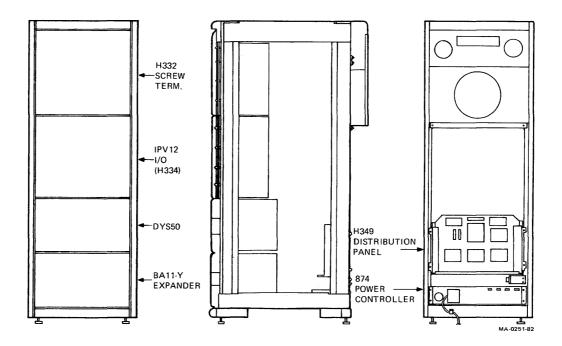

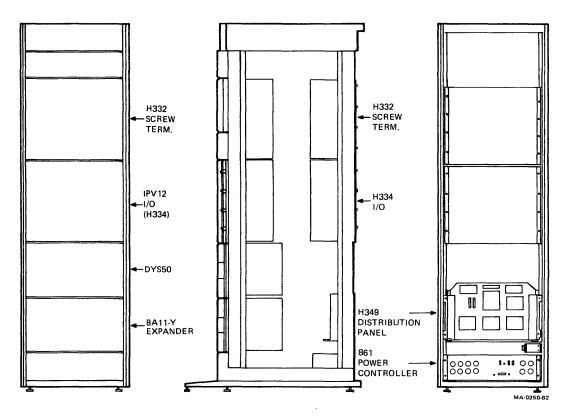

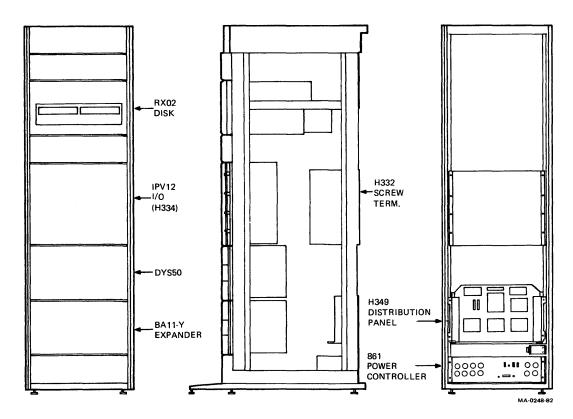

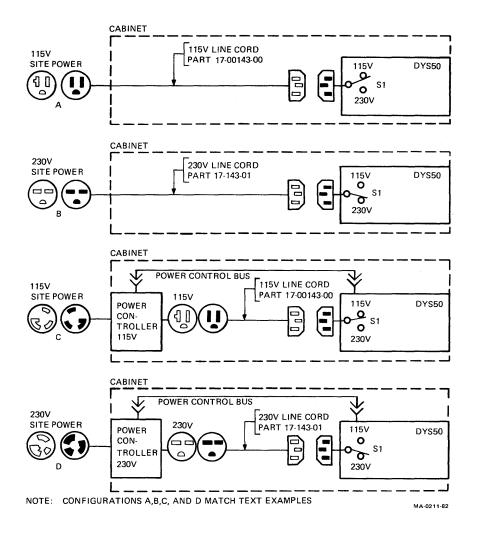

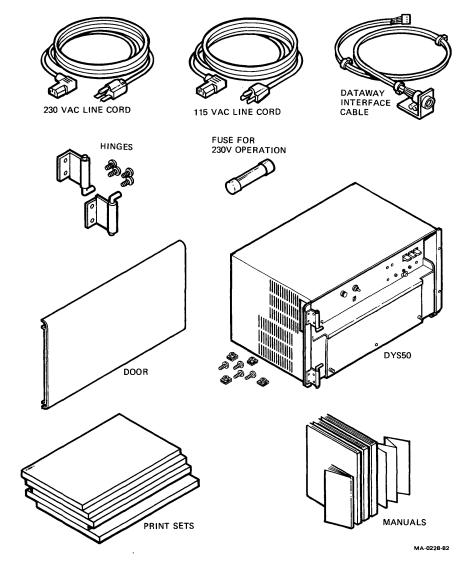

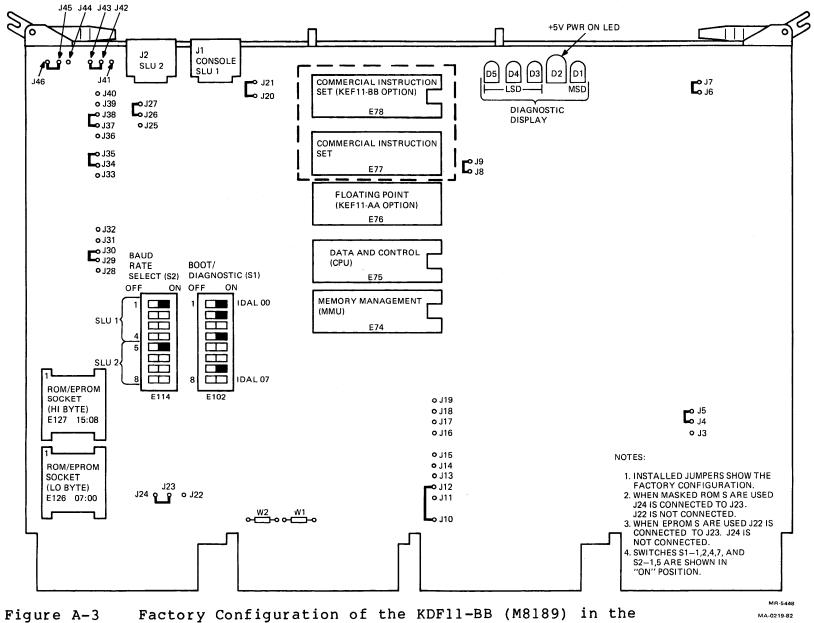

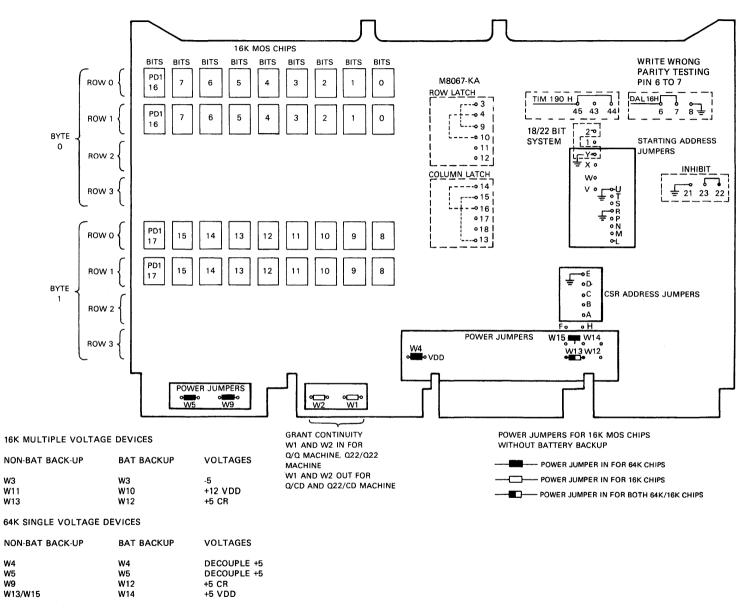

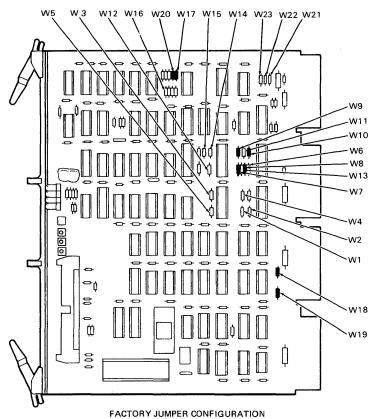

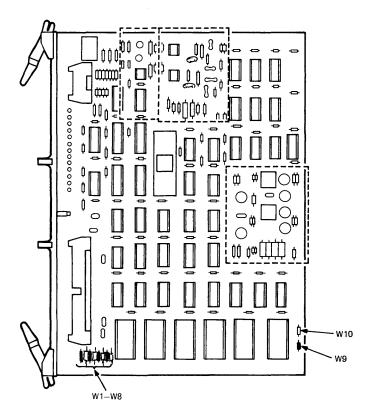

| 1.1<br>1.2<br>1.3<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.4<br>1.4<br>1.4.1<br>1.4.2<br>1.5<br>1.6<br>1.7                                                                          | Definition and Scope<br>Introduction<br>Features<br>KDF11-BB Processor (M8189)<br>MSV11-PK Memory (M8067-KA)<br>ISV11-B DECdataway Interface<br>BA11-Y Mounting Box<br>General Description<br>DY Systems<br>DYS50 Functional Description<br>Typical DYS50 Cabinet Configurations<br>Related Documents<br>Specifications | 1-1<br>1-2<br>1-3<br>1-3<br>1-3<br>1-3<br>1-3<br>1-3<br>1-3<br>1-3<br>1-6<br>1-7<br>1-10<br>1-11                                                                   |

| CHAPTER 2                                                                                                                                                                    | INSTALLATION                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                    |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.3<br>2.3.1<br>2.3.1.1<br>2.3.1.1<br>2.3.1.2<br>2.3.2<br>2.4<br>2.5<br>2.6<br>2.6.1<br>2.6.2<br>2.7<br>2.8<br>2.8.1<br>2.8.2<br>2.9<br>2.10 |                                                                                                                                                                                                                                                                                                                         | $\begin{array}{c} 2-1\\ 2-1\\ 2-3\\ 2-3\\ 2-3\\ 2-3\\ 2-4\\ 2-5\\ 2-9\\ 2-12\\ 2-14\\ 2-14\\ 2-14\\ 2-18\\ 2-18\\ 2-18\\ 2-18\\ 2-19\\ 2-19\\ 2-20\\ 2\end{array}$ |

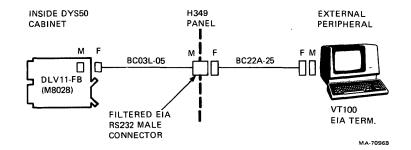

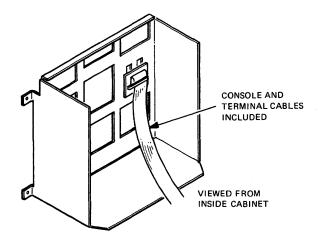

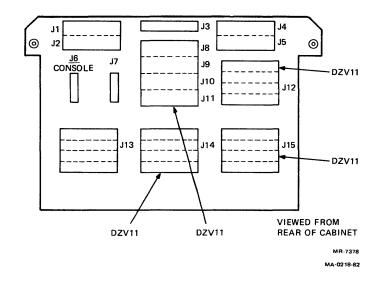

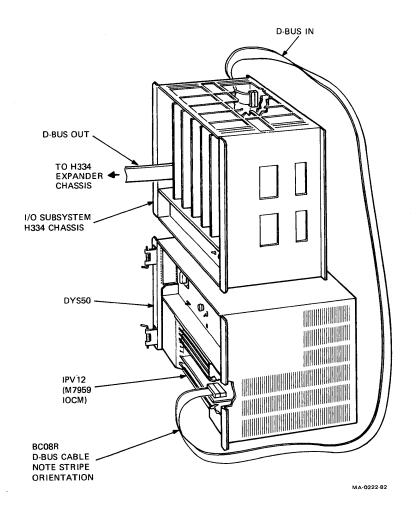

| 2.11<br>2.12<br>2.12.1<br>2.12.2<br>2.12.3<br>2.12.4<br>2.13<br>2.13.1<br>2.13.1<br>2.13.2<br>2.14                                                                           | On-Dataway Operation<br>DYS50 Peripheral Interfaces<br>Standard Interfaces<br>Filtered Interfaces<br>H349 Distribution Panel<br>DYS50 to I/O Subsystem Interface<br>Expanding an Existing System<br>Adding New Modules<br>Adding an Expansion Chassis<br>Performance Verification                                       | 2-24                                                                                                                                                               |

## CHAPTER 3 MAINTENANCE

| 3.1                                                                                                                                                                                               | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2                                                                                                                                                                                               | Troubleshooting Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2.1                                                                                                                                                                                             | Maintenance Software (Diagnostics)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2.1.1                                                                                                                                                                                           | System Level Diagnostics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2.1.2                                                                                                                                                                                           | Standalone Diagnostics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2.2                                                                                                                                                                                             | Hardware Troubleshooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2.3                                                                                                                                                                                             | Built-in Diagnostics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

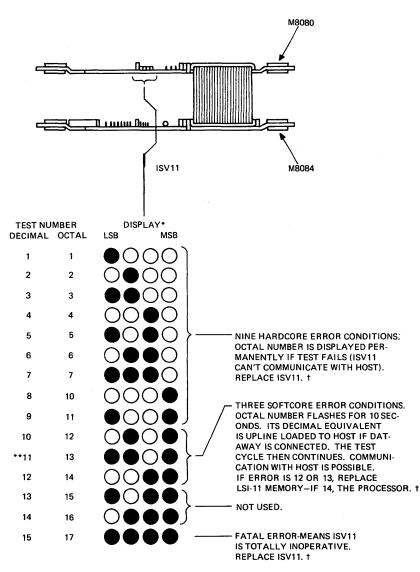

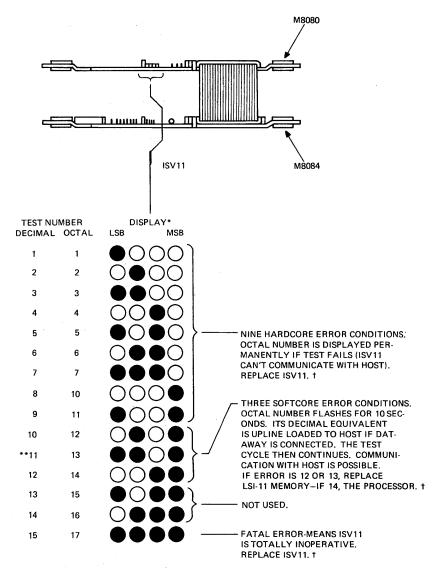

| 3.2.3.1                                                                                                                                                                                           | Hardcore Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2.3.2                                                                                                                                                                                           | Softcore Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

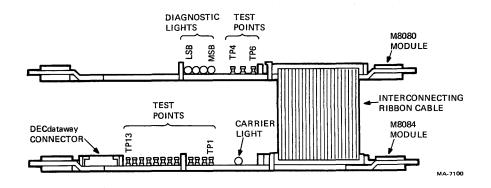

| 3.2.4                                                                                                                                                                                             | ISV11 Indicators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

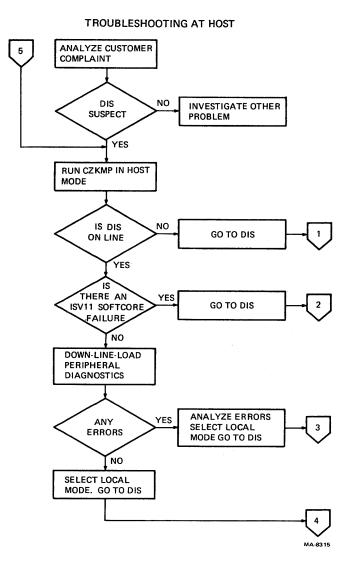

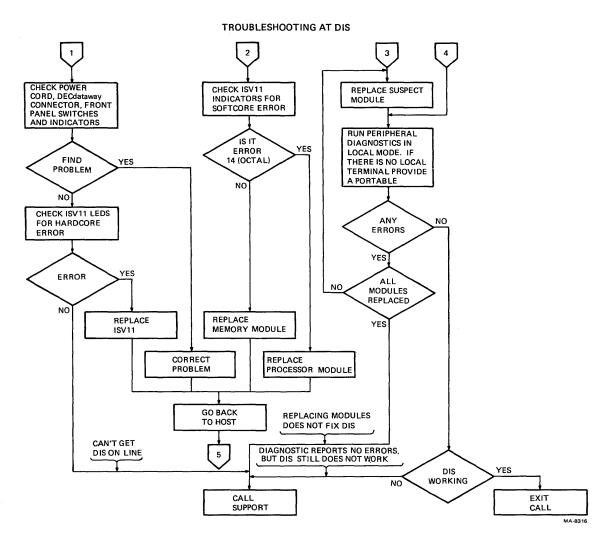

| 3.2.5                                                                                                                                                                                             | DYS50 Troubleshooting Flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

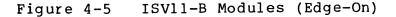

| 3.3                                                                                                                                                                                               | ISV11-B Troubleshooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.4                                                                                                                                                                                               | Routine Maintenance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5                                                                                                                                                                                               | Unit Removal and Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5.1                                                                                                                                                                                             | Replacement of the BAll-Y Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

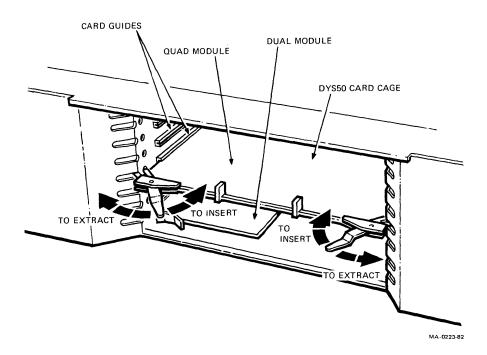

| 3.5.2                                                                                                                                                                                             | Module Insertion and Removal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

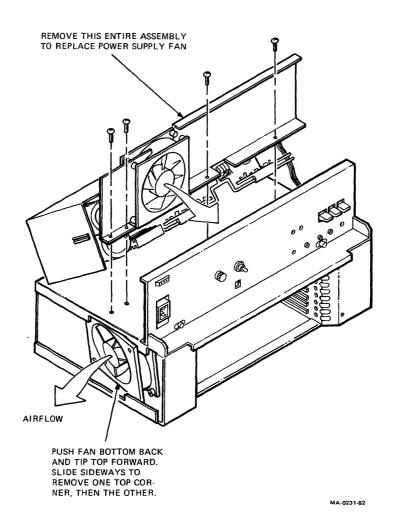

| 3.5.3                                                                                                                                                                                             | Fan Removal and Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

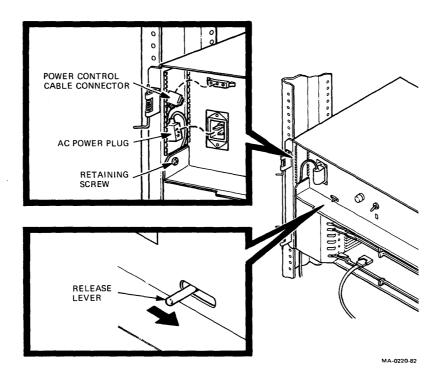

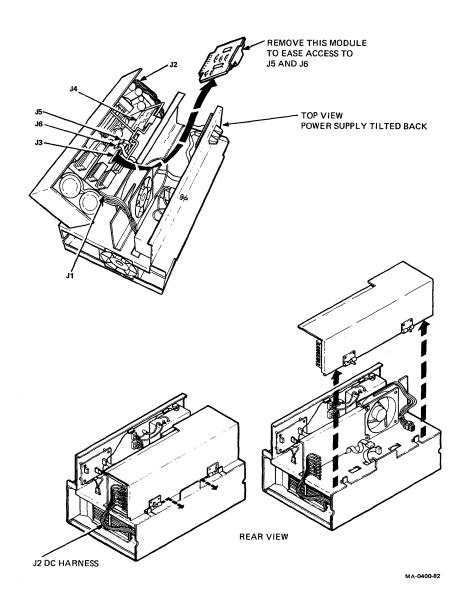

| 3.5.4                                                                                                                                                                                             | Power Supply Removal and Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.5.5                                                                                                                                                                                             | Control Module Replacement (Bezel)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

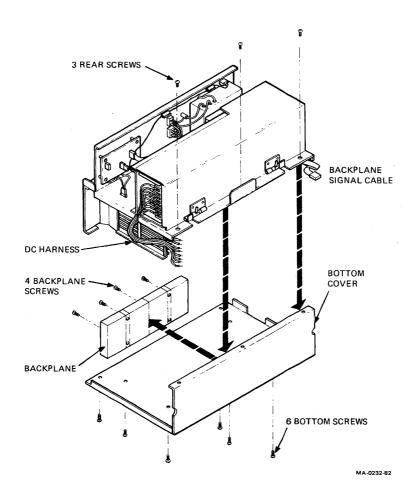

| 3.5.6                                                                                                                                                                                             | Backplane Replacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

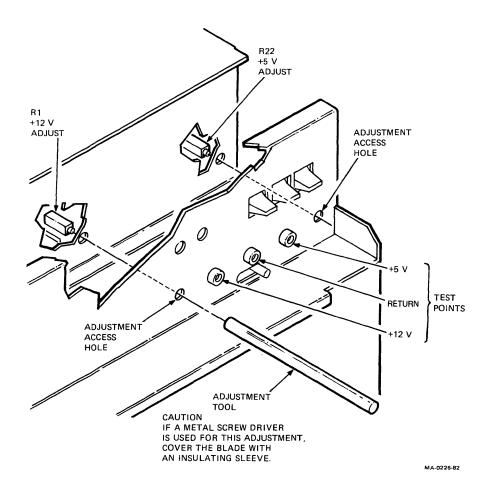

| 3.6                                                                                                                                                                                               | DC Voltage Measurement and Adjustment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.6.1                                                                                                                                                                                             | Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |