# DELQA-PLUS

### Addendum to DELQA User's Guide

September 1989

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may only be used or copied in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright © 1989 by Digital Equipment Corporation

All Rights Reserved Printed in U.S.A.

The postpaid READER'S COMMENTS form on the last page of this document requests the user's critical evaluation to assist in preparing future documentation.

The following are trademarks of Digital Equipment Corporation:

| DEC          | DIBOL     | RSX        |

|--------------|-----------|------------|

| DEC/CMS      | digital"  | UNIBUS     |

| DEC/MMS      | EduSystem | VAX        |

| DECnet       | IAS       | VAXcluster |

| DECsystem-10 | MASS      | VMS        |

| DECSYSTEM-20 | PDP       | VT         |

| DECUS        | PDT       |            |

| DECwriter    | RSTS      |            |

This manual was produced by Networks and Communications Publications.

# Contents

### Preface

Introduction to Addendum

### 5 DELQA-PLUS Installation

| 5.1   | Introduction                                           | 5 - 1 |

|-------|--------------------------------------------------------|-------|

| 5.2   | Setting Switches On The DELQA-T Board                  | 5 - 2 |

| 5.2.1 | Switch S1 Identifies the Device                        | 5-4   |

| 5.2.2 | Switches S3 and S5 Select the DELQA-PLUS Board's Mode  | 5-4   |

| 5.2.3 | Switch S4 Sets Both HIT And Reboot Features            | 5-5   |

| 5.3   | Running Two DELQA-PLUS Boards on the Same Q-bus System | 5–5   |

.

### 6 DELQA-PLUS Programming

| 6.1   | Introduction                     | 6–1 |

|-------|----------------------------------|-----|

| 6.1.1 | Terminology                      | 6–1 |

| 6.1.2 | Overview of DELQA-PLUS Functions | 6–2 |

| 6.1.3 | What Does the Device Driver Do?  | 6–3 |

| 6.1.4 | Summary of Driver's Major Tasks  | 6–3 |

| 6.1.5 | The DELQA-T Board's Address      | 6–5 |

| 6.1.6 | Summary of Data Structures       | 6–5 |

| 6.1.7 | Summary of DELQA-T Registers     | 6–5 |

| 6.2   | Select DELQA-T Mode              | 68  |

| 6.2.1 | Select DELQA-T Mode—Description  | 6–8 |

| 6.2.2 | Select DELQA-T Mode—Steps        | 6–8 |

| 6.2.3   | The Host Inactivity Timer (HIT)                    | 6-10   |

|---------|----------------------------------------------------|--------|

| 6.2.3.1 | Setting the Host Inactivity Timer (HIT)            | . 6–11 |

| 6.2.3.2 | The HIT Timeout Value                              | . 6–11 |

| 6.2.3.3 | How the HIT Timer Works                            | . 6–11 |

| 6.3     | Start the DELQA-T Board                            | 6–12   |

| 6.3.1   | Start the DELQA-T Board—Description                | 6–12   |

| 6.3.2   | Start The DELQA-T Board—Steps                      | 6–12   |

| 6.4     | Transmit                                           | 6–15   |

| 6.4.1   | Transmit—Description                               | 6–15   |

| 6.4.2   | How the DELQA-T Board Transmits                    | 6–15   |

| 6.4.3   | Transmit—Steps                                     | 6-17   |

| 6.4.4   | Chaining Buffers                                   | 6–18   |

| 6.5     | Receive                                            | 6–21   |

| 6.5.1   | Receive—Description                                | 6-21   |

| 6.5.2   | Receive—Steps                                      | 6-21   |

| 6.5.3   | Size Restrictions—Received Data                    | 6–22   |

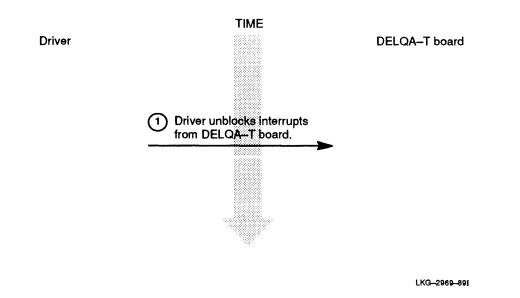

| 6.6     | Stop the DELQA-T Board                             | 6–25   |

| 6.6.1   | Stop The DELQA-T Board—Description                 | 6–25   |

| 6.6.2   | Stop the DELQA-T Board—Steps                       | 6–25   |

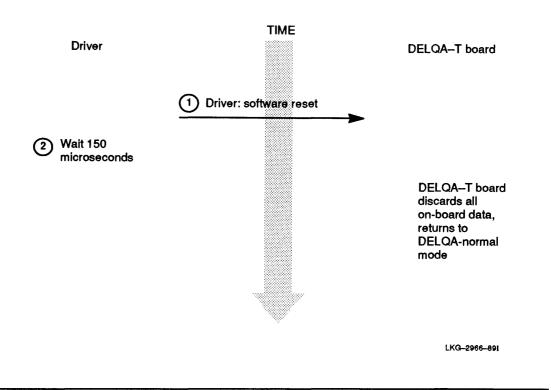

| 6.7     | Software Reset of the DELQA-PLUS Board             | 6–28   |

| 6.7.1   | Software Reset of the DELQA-PLUS Board-Description | 6–28   |

| 6.7.2   | Software Reset—Steps                               | 6–28   |

| 6.8     | Changing DELQA-T Operating Parameters              | 6-30   |

| 6.8.1   | Changing DELQA-T Operating Parameters—Description  | 6-30   |

| 6.8.2   | Changing DELQA-T Operating Parameters—Steps        | 630    |

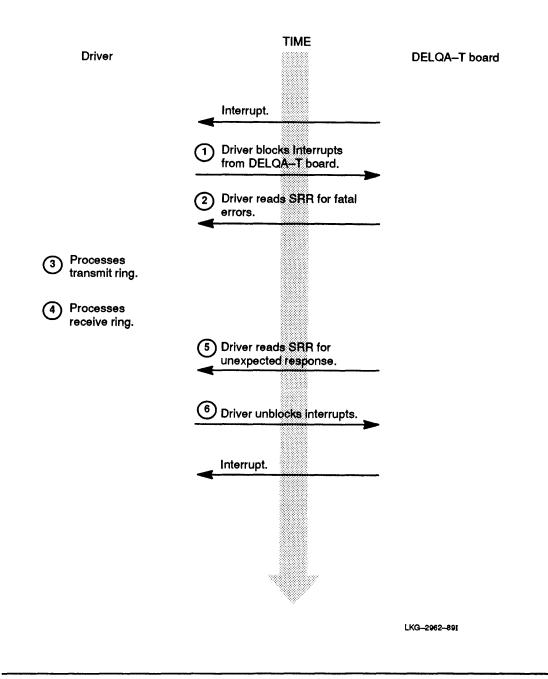

| 6.9     | Interrupts                                         | 6–32   |

| 6.9.1   | Interrupts—Description                             | 6–32   |

| 6.9.2   | Blocking And Unblocking Interrupts                 | 6-32   |

| 6.9.3   | Value of Blocking and Unblocking Interrupts        | 6–33   |

| 6.9.4   | Interrupt Defaults At DELQA-T Startup              | 6–33   |

| 6.9.5   | When Do Interrupts Occur?                          | 6-33   |

| 6.9.6   | Basic Interrupt Service Routine                    | 6–34   |

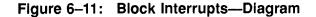

| 6.10    | Block Interrupts                                   | 6-36   |

| 6.10.1  | Block Interrupts—Description                       | 6–36   |

| 6.10.2  | Block Interrupts—Steps                             | 6–36   |

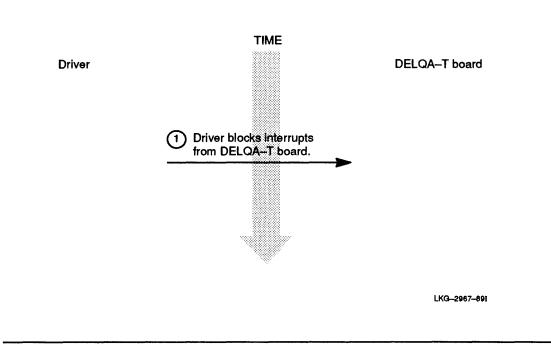

| 6.11    | Unblock Interrupts                                 | 6-37   |

| 6.11.1  | Unblock Interrupts—Description                     | 6-37   |

| 6.11.2  | Unblock Interrupts—Steps                           | 638    |

| 6.12    | Return to DELQA-normal Mode                        | 6–39   |

| 6.12.1  | Return to DELQA-normal Mode—Description            | 6–39   |

| 6.12.2  | Return to DELQA-normal Mode—Steps                  | 6–39   |

| 6.13    | Registers on the DELQA-T Board                     | 6-41   |

| 6.13.1  | Reserved Fields                                    | 6–41   |

| The Status And Response Register (SRR)   | 642                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Station Address ROM (SA ROM) Locations   | 6–45                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Synchronous Request Register (SRQR)      | 6-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Asynchronous Request Register (ARQR)     | 6-47                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

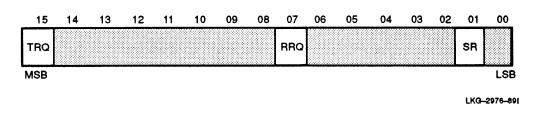

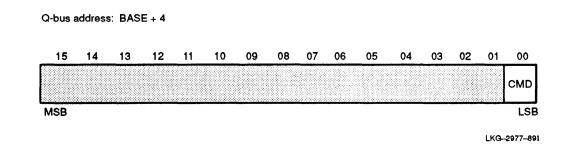

| Interrupt Control Register (ICR)         | 6-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Init Block Registers (IBAH and IBAL)     | 6–50                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

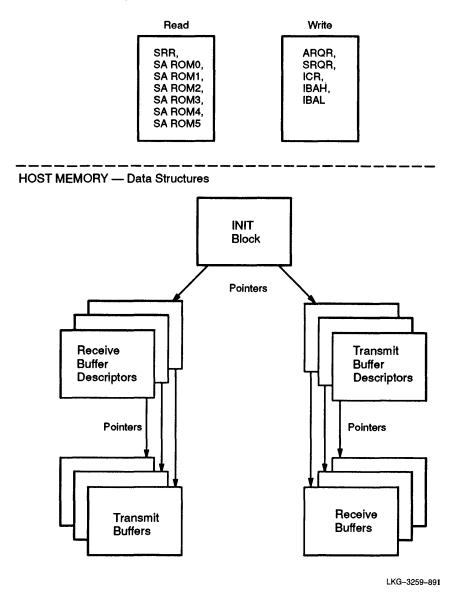

| Data Structures In Host Memory           | 6–52                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Reserved Fields                          | 6 - 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Data Structures On the DELQA-T Board     | 6–52                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

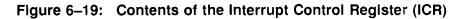

| The Init Block                           | 6-53                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| The Transmit And Receive Rings           | 6-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

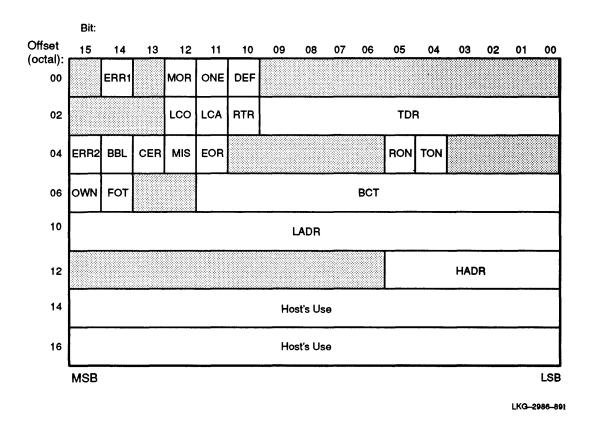

| Transmit Buffer Descriptor               | 6-62                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Fields in the Transmit Buffer Descriptor | 6-63                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Transmit Data Buffers                    | 666                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

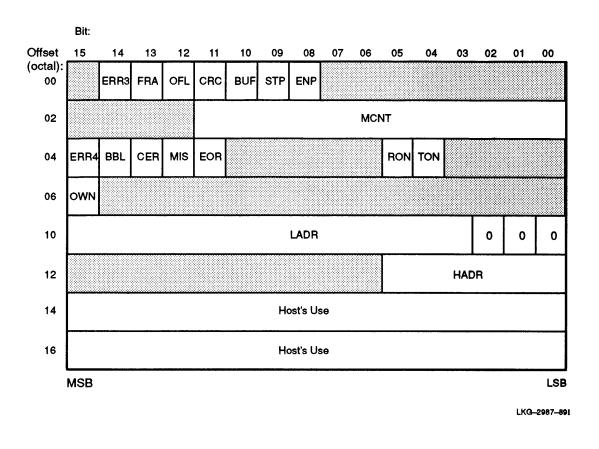

| Receive Buffer Descriptor                | 6-66                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Fields in the Receive Buffer Descriptor  | 6-67                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Receive Data Buffers                     | 6-70                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                          | Station Address ROM (SA ROM) LocationsSynchronous Request Register (SRQR)Asynchronous Request Register (ARQR)Interrupt Control Register (ICR)Init Block Registers (IBAH and IBAL)Data Structures In Host MemoryReserved FieldsData Structures On the DELQA-T BoardThe Init BlockThe Transmit And Receive RingsTransmit Buffer DescriptorFields in the Transmit Buffer DescriptorTransmit Data BuffersReceive Buffer DescriptorFields in the Receive Buffer Descriptor |

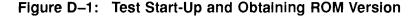

## D Reading The DELQA-PLUS Board's ROM Version

| D.1   | Introduction                                      | <b>D–1</b> |

|-------|---------------------------------------------------|------------|

| D.2   | Test Startup—Steps                                | D–2        |

| D.3   | Request/Read DELQA-PLUS Board's ROM Version-Steps | D-3        |

| D.3.1 | The Extended Setup Packet                         | D–4        |

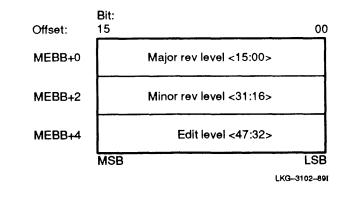

| D.3.2 | MOP Element Block Type 10                         | <b>D-4</b> |

| D.3.3 | The MOP Element Block (MEB) Type 10's Buffer      | D–5        |

| D.3.4 | ROM Version 0.10.37                               | <b>D6</b>  |

### Glossary of Acronyms

Index

Figures

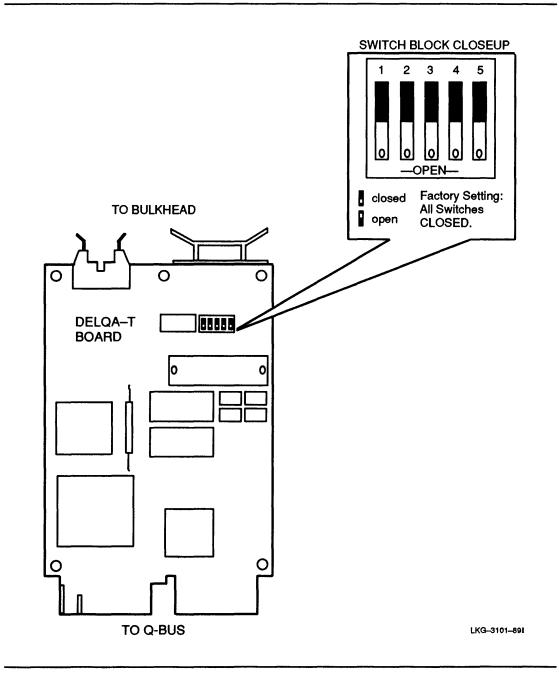

| 5–1 | Switches on the DELQA-T board                     | 5–3  |

|-----|---------------------------------------------------|------|

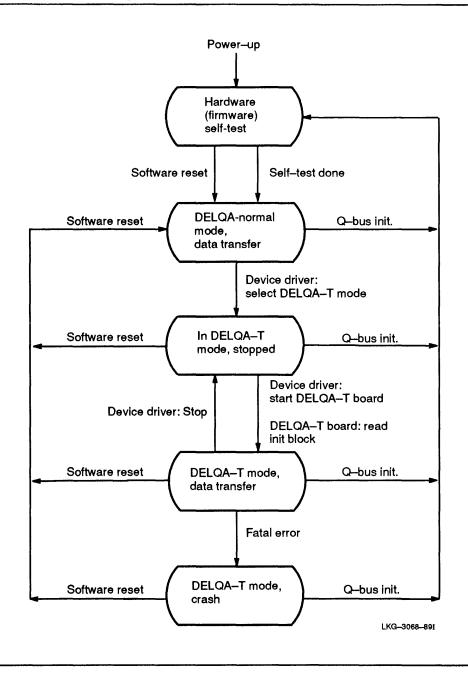

| 6–1 | State Diagram of DELQA-PLUS Board                 | 6-6  |

| 6–2 | DELQA-T Registers and Host Memory Data Structures | 6-7  |

| 6–3 | Select DELQA-T Mode—Diagram                       | 6-10 |

| 6-4 | Start-Up—Diagram                                  |      |

| Transmit—Diagram                                     | 6–19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive—Diagram                                      | 6–23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Stop—Diagram                                         | 6-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Software Reset—Diagram                               | 6–29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Changing DEQLA-T Operating Parameters-Diagram        | 6–31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Interrupt Service Routine—Diagram                    | 6–35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Block Interrupts—Diagram                             | 6-37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Unblock Interrupts—Diagram                           | 6–38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Return to DELQA-normal Mode—Diagram                  | 6-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Registers on the DELQA-T board                       | 6-42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Contents of the Status and Response Register (SRR)   | 6–43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| The Station Address ROM Locations                    | 6-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Contents of the Synchronous Request Register (SRQR)  | 6-47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Contents of the Asynchronous Request Register (ARQR) | 6–48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Contents of the Interrupt Control Register (ICR)     | 6–50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

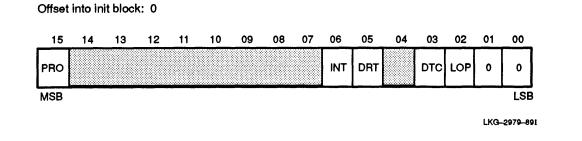

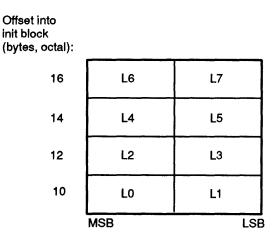

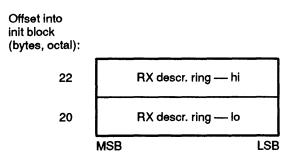

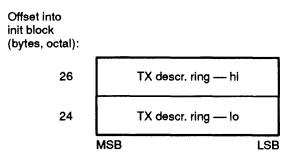

| Contents of the Init Block                           | 6–54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Contents of the MODE Field                           | 6–55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Contents of the OPTIONS Field                        | 6–59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

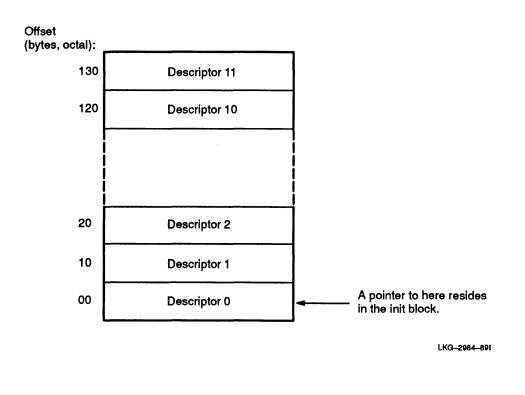

| Transmit Descriptor Ring                             | 6-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

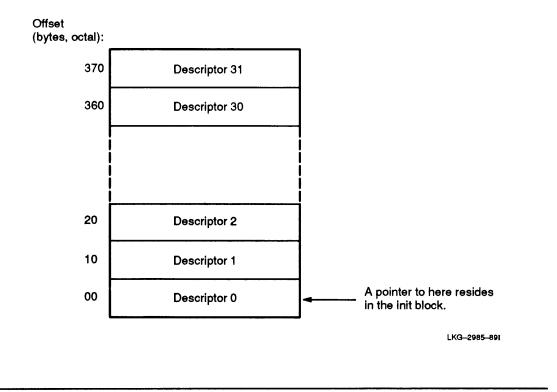

| Receive Descriptor Ring                              | 6-62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

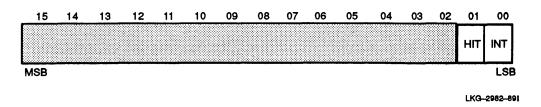

| Contents of a Transmit Buffer Descriptor             | 6–63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Contents of a Receive Buffer Descriptor              | 6–67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Test Start-Up and Obtaining ROM Version              | . D–3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

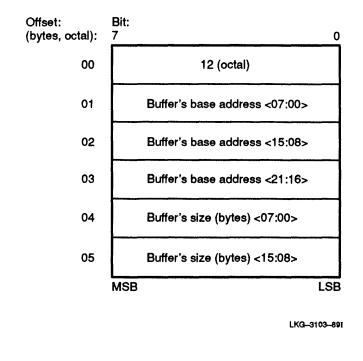

| MOP Element Block Type 10                            | . D5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MEB Type 10's Buffer                                 | . D–6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      | Receive—Diagram         Stop—Diagram         Software Reset—Diagram         Changing DEQLA-T Operating Parameters—Diagram         Interrupt Service Routine—Diagram         Block Interrupts—Diagram         Unblock Interrupts—Diagram         Return to DELQA-normal Mode—Diagram         Registers on the DELQA-T board         Contents of the Status and Response Register (SRR)         The Station Address ROM Locations         Contents of the Synchronous Request Register (SRQR)         Contents of the Asynchronous Request Register (ARQR)         Contents of the Interrupt Control Register (ICR)         Contents of the Init Block         Contents of the OPTIONS Field         Transmit Descriptor Ring         Receive Descriptor Ring         Contents of a Transmit Buffer Descriptor         Contents of a Receive Buffer Descriptor         Test Start-Up and Obtaining ROM Version         MOP Element Block Type 10 |

## Tables

| 5–1 | Switches In DELQA-T Mode                  | 5-4  |

|-----|-------------------------------------------|------|

| 6–1 | Size Restrictions For Transmitted Buffers | 6–17 |

| 6–2 | Fields in the SRR Register                | 6-43 |

| 6–3 | Fields in the SRQR Register               | 6-47 |

| 6-4 | Fields in the ARQR Register               | 6–49 |

| 6-5 | Fields in the ICR Register                | 6–50 |

| 6–6 | Bits in the MODE field                    | 6-55 |

| 6–7 | Bits in the OPTION field                  | 6–59 |

| 6-8 | Fields in the Transmit Buffer Descriptor  | 6-63 |

| 6–9 | Fields in the Receive Buffer Descriptor   | 6-68 |

| D-1 | Current ROM Version Levels                | D6   |

## Preface

#### Introduction to Addendum

This addendum contains instructions for using the DELQA-PLUS board, which is a new version of the DELQA Ethernet/IEEE 802.3 LAN-to-Q-bus board. Include this addendum with the manual as a means of maintaining an up-todate record of changes to the manual.

This addendum has four parts:

- An additional chapter, Chapter 5, which contains specific installation instructions for the DELQA-PLUS board. For basic installation instructions for all DELQA boards, see the *DELQA User's Guide*.

- An additional chapter, Chapter 6, which contains programming instructions for the DELQA-PLUS board.

- An additional appendix, Appendix D, which contains instructions for reading the ROM version from the DELQA-PLUS board.

- A glossary of terms that relate to the DELQA-PLUS board.

To use this addendum, first determine whether you will be using software supplied by Digital Equipment Corporation to operate the DELQA-PLUS board or will be building your own software to operate the board.

• If you will be using Digital-supplied software, follow the installation instructions in Chapter 5 in this Addendum to DELQA User's Guide, then follow the instructions for the software. • If you will be building software, follow the programming instructions in the new Chapter 6. Then, when you have created the software for the DELQA-PLUS board, follow the installation instructions in Chapter 5 in this Addendum to DELQA User's Guide.

# **DELQA-PLUS** Installation

This chapter contains installation instructions for the DELQA-PLUS board.

These instructions supplement the basic installation instructions in the DELQA User's Guide, which apply to all DELQA boards.

#### NOTE

There can be more than one DELQA-PLUS board on the same Q-bus. For convenience, this chapter always refers to the first DELQA-PLUS board on a two-DELQA-PLUSboard Q-bus system (unless otherwise noted). For more information about running more than one DELQA-PLUS board on a Q-bus, see Section 5.3.

#### 5.1 Introduction

The DELQA-PLUS board can operate in two modes, DELQA-normal mode and DELQA-T mode. For more information on the differences between DELQA-normal and DELQA-T modes, see Chapter 6 in this Addendum to DELQA User's Guide.

This chapter describes how to install the DELQA-PLUS board when it will be used in DELQA-T mode. For information on using the DELQA-PLUS board as a DELQA-normal board, see to the DELQA User's Guide.

The basic steps to install a DELQA-PLUS board when it will be used as a DELQA-T board are:

Setting switches—Make sure the on-board switches are set correctly for DELQA-T mode operation.

- Make sure each DELQA-PLUS board is properly installed in the host chassis and is powered up and running.

- Running more than one DELQA-PLUS board—If there is more than one DELQA-PLUS board on the same system, follow the procedures in Section 5.3 in order to distinguish the two boards.

After you have performed these steps, the DELQA-PLUS board will be ready to operate as a DELQA-T board. To verify that the DELQA-PLUS board is running the proper ROM version for DELQA-T mode operation, see Appendix D.

For instructions on how to program the DELQA-PLUS board, see Chapter 6 in this Addendum to DELQA User's Guide.

#### 5.2 Setting Switches On The DELQA-T Board

These are the same switches that are on the DELQA-normal board; the only differences are that they mean different things in DELQA-T mode than in DELQAnormal mode. The meanings of the switches in DELQA-T mode are described in Table 5-1.

Figure 5-1 shows the location of the five switches on the DELQA-T board.

Make sure the five switches on the DELQA-T board are in the CLOSED position (which is the factory default).

#### CAUTION

Do not set the switches while the board is powered ON.

Table 5–1: Switches In DELQA-T Mode

| Switch | Setting | Meaning                                                                                          |

|--------|---------|--------------------------------------------------------------------------------------------------|

| S1     | CLOSED  | This is the first DELQA-PLUS device; this device resides at Q-<br>bus address 1777 4440 (octal). |

|        | OPEN    | This is the second DELQA-PLUS device; this device resides at Q-bus address 1777 4460 (octal).    |

| S2     |         | (Reserved.)                                                                                      |

| S3     | CLOSED  | Selects DELQA-normal mode                                                                        |

|        | OPEN    | Selects DEQNA-lock mode (Board can operate in DEQNA mode only, not in DELQA modes.)              |

| S4     | CLOSED  | HIT (host inactivity timer) initially disabled                                                   |

|        | OPEN    | HIT timer initially enabled                                                                      |

| S5     | CLOSED  | T-mode enabled (Board can operate as DELQA-normal board or DELQA-T board.)                       |

|        | OPEN    | T-mode disabled (Board can operate only as a DELQA-normal board or DEQNA board.)                 |

#### 5.2.1 Switch S1 Identifies the Device

Switch S1 establishes the DELQA-PLUS board's Q-bus address and also allows you to distinguish two DELQA-PLUS boards that are on the same Q-bus:

- On the first DELQA-PLUS board, set switch S1 to CLOSED.

- On the second DELQA-PLUS board, set switch S1 to OPEN.

See also Table 5-1.

#### 5.2.2 Switches S3 and S5 Select the DELQA-PLUS Board's Mode

Switches S3 and S5 let you restrict the DELQA-PLUS board's operating mode to DELQA-only (switch S3) or DEQNA-only (switch S5).

To make sure the DELQA-PLUS board can run in DELQA-T mode, make sure both switches S3 and S5 are CLOSED.

#### 5.2.3 Switch S4 Sets Both HIT And Reboot Features

Switch S4 OPEN means "HIT initially enabled" in DELQA-T mode and "rebooting enabled" in DELQA-normal mode; in other words, switch S4 enables these two features together.

#### 5.3 Running Two DELQA-PLUS Boards on the Same Q-bus System

There can be either one or two DELQA-PLUS boards on the same Q-bus system.

If there are two DELQA-PLUS boards on the same system, configure the two DELQA-PLUS boards as follows:

1. The first DELQA-PLUS must have switch S1 CLOSED.

This sets the first DELQA-PLUS board's Q-bus address to 1777 4440 (octal).

2. The second DELQA-PLUS must have switch S1 OPEN.

This sets the second DELQA-PLUS board's Q-bus address to 1777 4460 (octal).

Make sure the driver(s) uses these two different addresses to contact the two DELQA-PLUS boards correctly.

# **DELQA-PLUS** Programming

This chapter gives basic information about programming the DELQA-PLUS board.

#### 6.1 Introduction

The DELQA-PLUS hardware consists of a DELQA board with ROM (read-only memory) firmware of revision at least 2.0.0. This firmware allows the DELQA-PLUS board to operate in both a DELQA-normal mode and a new mode, called Turbo mode or DELQA-T mode.

The firmware resides in ROMs that reside on the DELQA-PLUS board. To determine your DELQA-PLUS board's ROM firmware version, follow the instructions in Appendix D of this Addendum to DELQA User's Guide.

#### 6.1.1 Terminology

**DELQA-T mode and DELQA-normal mode** — For convenience, we have described the two modes in which the DELQA-PLUS board can operate as two different boards. When the DELQA-PLUS board is operating in Turbo mode, we call it a DELQA-T board or say that it is operating in DELQA-T mode. When the DELQA-PLUS board is not operating in Turbo mode, we call it a DELQA-normal board or say that it is operating in DELQA-normal mode.

**Device driver software** — Although it is possible to operate individual features of the DELQA-PLUS board from any software that has access to the Q-bus on which the DELQA-PLUS board resides, this chapter describes programming the DELQA-PLUS board in terms of a how a single device driver would operate the DELQA-PLUS board in an orderly way when the DELQA-PLUS board is in DELQA-T mode. **Multiple DELQA-PLUS boards on a system** — There can be more than one DELQA-PLUS board on the same Q-bus. For convenience, this chapter always refers to the first DELQA-PLUS board on a two-DELQA-PLUS-board Q-bus system (unless otherwise noted). For more information about running more than one DELQA-PLUS board on a Q-bus, see Section 5.3 in this Addendum to DELQA User's Guide.

#### 6.1.2 Overview of DELQA-PLUS Functions

The DELQA-PLUS board when in DELQA-T mode performs the same data transfer functions as the original DELQA board (called the DELQA-normal board)—it transfers network message data between the host's memory and the network to which the board is connected. The DELQA-PLUS board in DELQA-T mode also provides added functionality to that of the DELQA-normal board. You can still use all the DELQA-normal board features; in fact, you must use them in order to cause the DELQA-PLUS board to run in DELQA-T mode.

The differences between the DELQA-normal and the DELQA-PLUS boards are:

- The DELQA-PLUS board offers a superset of the functionality of the original DELQA board.

- In DELQA-T mode, the DELQA-PLUS board has a higher throughput rate than in DELQA-normal mode.

- The programming interface to the DELQA-T board is simpler than that of the DELQA-normal board—ownership of the transmitted and received data is unambiguous.

- In DELQA-T mode, the DELQA-PLUS board does not run the DECnet Maintenance Operations Protocol (MOP) on-board; it does support MOP in DELQA-normal mode.

In addition, ROM version 2.0.0 adds the following functionality to the DELQA-PLUS board's DELQA-normal mode:

- In DELQA-normal mode, the DELQA-PLUS board will transmit on the network a DECnet system ID message that contains the correct device ID for DELQA-T boards. (This device ID is 75 (decimal).)

- There are two new on-board registers, XCR0 and XCR1, which allow host software to cause the DELQA-PLUS board to go into DELQA-T mode.

Setting the boot password to the value zero allows only passwords of value zero (0) to cause the DELQA-PLUS board to reboot its host, not all passwords to reboot it.

The information in the *DELQA User's Guide* applies to the DELQA-PLUS board when it is in DELQA-normal mode; Chapter 3 of the *DELQA User's Guide* describes how to program a DELQA-normal board.

#### 6.1.3 What Does the Device Driver Do?

The device driver for the DELQA-T board resides in host memory. It communicates with the DELQA-T board through a series of registers that reside on the DELQA-T board.

Briefly, to operate the DELQA-T board, the driver must provide a set of transmit and receive buffers, then order the board through one of the registers to read or write data to and from these buffers. (The buffers reside in host memory, and the registers reside on the board; the registers appear in Q-bus memory space.) The driver also performs other operations, such as starting and stopping the DELQA-T board, as needed.

In more detail, the normal sequence of events that a device driver follows in using the DELQA-T board is:

- 1. Orderly start-up— Verify ROM version, select DELQA-T mode, and start the board running.

- 2. Perform transmit and receive operations as required and modify operating parameters as needed.

- 3. Orderly shutdown-Stop board and return to DELQA-normal mode.

This sequence of events can be broken down into essential tasks; these tasks are listed in the next section.

#### 6.1.4 Summary of Driver's Major Tasks

The major tasks that a device driver for the DELQA-T board can perform are:

- Select DELQA-T mode—Prepares the DELQA-PLUS board to function as a DELQA-T board rather than a DELQA-normal board.

- Start the DELQA-T board—Enables the DELQA-T board to perform data transfer operations on the network.

- Transmit—The transmit operation involves three main steps: 1) setting up the data to be transferred, 2) notifying the DELQA-T board that the data is ready (the DELQA-T board then performs the transfer), and 3) checking status information afterwards.

- Receive—Like the transmit operation, the receive operation involves three main steps: 1) providing buffers for the DELQA-T board to write received data, 2) notifying the the DELQA-T board that the buffers are ready (the DELQA-T board then performs the receive), and 3) checking status information afterwards.

- Stop the DELQA-T board—Disables the DELQA-T board from performing data transfer operations.

- Software reset of the DELQA-PLUS board—Moves the DELQA-T board to DELQA-normal mode.

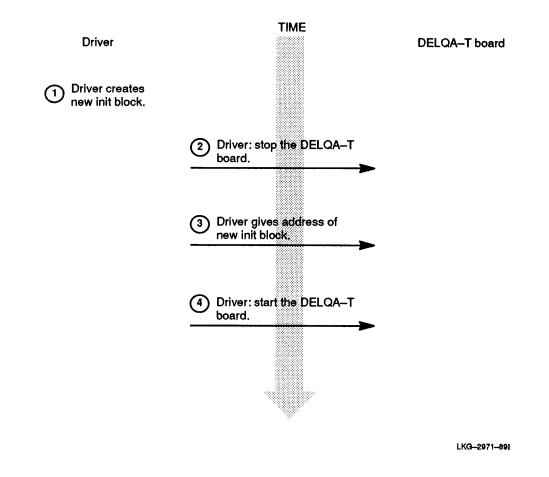

- Change the DELQA-T board's operating parameters—Allows the driver to substitute a new init block to the DELQA-T board; requires the driver to stop and the restart the DELQA-T board.

- Interrupts—The DELQA-T board can notify the driver by means of an interrupt that an operation is complete.

- Block interrupts from the DELQA-T board—Causes the DELQA-T board to save interrupts but not send them to the driver until the driver issues an unblock request.

- Unblock interrupts from the DELQA-T board—Allows the DELQA-T board to resume sending interrupts to the driver.

- Return to DELQA-normal mode—Moves the DELQA-T board to DELQAnormal mode in an orderly fashion.

These tasks can be arranged into a state diagram, as shown in Figure 6-1.

The following sections explain in detail how the driver performs each of the above-mentioned tasks. Each section describes the task briefly, then lists the steps the driver must perform to accomplish the task, then shows the steps in the form of a time-sequence diagram.

#### 6.1.5 The DELQA-T Board's Address

The DELQA-T board resides in Q-bus memory space. Q-bus addresses are 22 bits long. (The software that operates the DELQA-T board may be required to address the DELQA-T board differently depending on the mapping hardware of the host machine.)

In this addendum, we refer to the address of each DELQA-T board as BASE, whether it is the first or the second board on the system. To find out the BASE address of your DELQA-T board, see the setting of switch S1 on the board and read the address listed in Table 5–1.

#### 6.1.6 Summary of Data Structures

To perform the tasks listed in Section 6.1.4, the device driver uses a number of important data structures. The data structures are the:

- Init block

- Transmit descriptor ring

- Transmit buffers

- Receive descriptor ring

- Receive buffers

These structures are shown in Figure 6-2 and are described in detail in Section 6.14.

#### 6.1.7 Summary of DELQA-T Registers

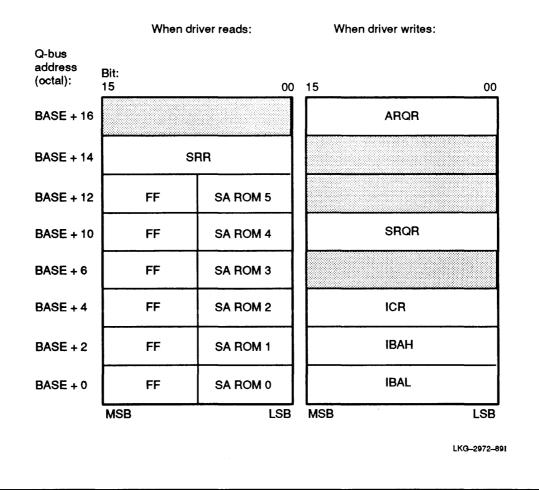

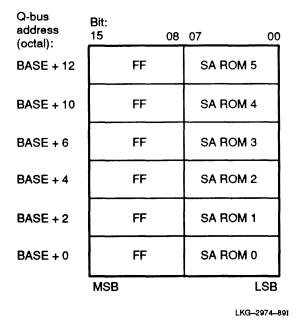

The driver also uses the DELQA-T board's on-board registers to perform the tasks listed in Section 6.1.4. These registers are:

- The ARQR, SRQR, ICR, IBAH, and IBAL which the driver uses to talk to the board, and

- The SRR, which the board uses to talk to the driver.

These registers are shown in Figure 6-2 and are described in detail in Section 6.13.

#### 6.2 Select DELQA-T Mode

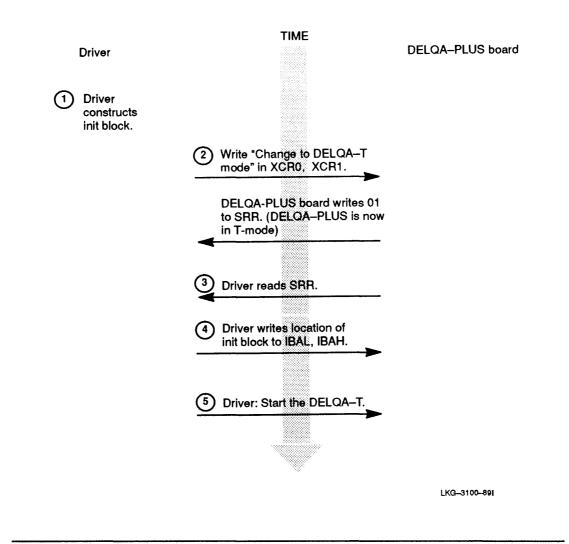

This section describes the driver's task of selecting DELQA-T mode.

#### 6.2.1 Select DELQA-T Mode—Description

This operation consists of moving the DELQA-PLUS board from DELQA-normal mode to DELQA-T mode.

Beforehand, you must perform the basic installation tasks that are described in Chapter 5 of this Addendum to DELQA User's Guide.

After you have installed the DELQA-PLUS board, follow the steps listed below. Figure 6–3 shows these steps in diagram form.

#### 6.2.2 Select DELQA-T Mode—Steps

To move an installed DELQA-PLUS board from DELQA-normal mode to DELQA-T mode, the device driver follows these steps:

1. The driver constructs a block of initialization data (called the init block) in host memory.

For complete information on the structure and contents of init blocks, see Section 6.14.3.

Remember, the DELQA-T board will not actually read the init block until after the driver issues a start request.

- 2. The driver gives the DELQA-PLUS board the order to change from DELQAnormal mode to DELQA-T mode by writing the following:

- a. 0BAF (hexadecimal) to the XCR0 register.

- b. Then FF00 (hexadecimal) to the XCR1 register.

The XCR0 and XCR1 registers reside on the DELQA-normal board at Q-bus addresses BASE + 0 and BASE + 2, respectively, where BASE is the Q-bus address of the DELQA-PLUS board.

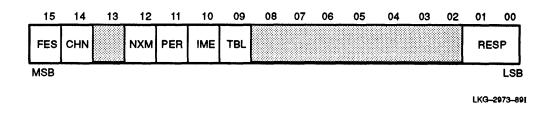

3. The driver reads the response field (bits 01 and 00) in the SRR (status and response register) for the value 01 (binary). The value 01 (binary) means the DELQA-PLUS board has moved from DELQA-normal mode to DELQA-T mode. (The SRR register resides at the same address on the DELQA-T board as the VAR register does on the DELQA-normal board, which is Q-bus address BASE + 14 (octal). The driver may read the SRR as often as desired.)

If the RESP field (bits 01-00) in the SRR register does not contain the value 01 (binary) within 1 second, then the DELQA-PLUS board has failed to go into DELQA-T mode. Check the previous steps in this list, especially the settings of the on-board switches.

4. The driver informs the board of the location of the init block by writing the host memory address of the init block to the IBAL and IBAH registers. The IBAL and IBAH registers reside on the DELQA-T board; their Q-bus addresses are also BASE + 0 and BASE + 2, respectively.

Remember, the DELQA-T board has a different Q-bus address depending on whether it is the first or second board on the Q-bus system. For information on the DELQA-T board's two Q-bus addresses, see Chapter 5 of this Addendum to DELQA User's Guide.

5. Since the DELQA-T board comes up in stopped mode, the driver must start the DELQA-T board running. To do so, the driver follows the steps in Section 6.3.

Note that the DELQA-T board does not actually read the init block until this point.

After a successful start, the DELQA-T board is ready to transmit and receive network message data.

For information on how the driver conducts transmit and receive operations with the DELQA-T board, see Section 6.4 and Section 6.5.

#### NOTE

After the DELQA-T board is up and running, you should enable the host inactivity timer (HIT). (The DELQA/DELQA-T board is shipped with the timer initially disabled.)

To enable the HIT, follow the directions in Section 6.2.3.

#### 6.2.3 The Host Inactivity Timer (HIT)

The purpose of the HIT is to put the DELQA-T board back into DELQA-normal mode when the driver has not communicated with the DELQA-T board for a certain amount of time. When the driver does not communicate with the DELQA-T board, the DELQA-T board assumes the host has crashed and cannot reboot itself. By going back to DELQA-normal mode, the DELQA-PLUS board can now respond to DECnet Maintenance Operations Protocol (MOP), which means the DELQA-PLUS board can respond to a request from a remote user to reboot the host machine.

For more information on rebooting, see the DELQA User's Guide.

#### 6.2.3.1 Setting the Host Inactivity Timer (HIT)

You enable and set the HIT differently, depending on when you do it, either before or after the DELQA-PLUS board has begun to operate in DELQA-T mode.

- Before the DELQA-PLUS board powers up, you must make sure that switch S4 (Enable/Disable HIT) on the DELQA-PLUS board is OPEN.

- After the DELQA-PLUS board powers up but before it has begun to operate in DELQA-T mode, the driver must:

- 1. Set the HIT field (bit 01) in the OPTION field (BASE + 22 (octal)) in the init block.

- 2. Set the time interval after which the HIT should go off by setting the HIT timeout value (BASE + 34 (octal)) in the init block to the desired time interval, in seconds.

Remember, after the DELQA-T board is running, set the HIT timer by having the driver enable it in the init block. Do not set it by throwing switch S4 on the board. To throw switches at that point, you must power down the board, which will erase the configuration of the DELQA-T board you've done so far.

#### 6.2.3.2 The HIT Timeout Value

Before the driver begins to operate the DELQA-PLUS board as a DELQA-T board (and assuming switch S4 is OPEN), the HIT timeout value will be 3 minutes by default.

After the driver gives the DELQA-PLUS board the command to start running in DELQA-T mode, the HIT timeout value will be the timeout value in the init block.

#### 6.2.3.3 How the HIT Timer Works

The HIT timer will expire if the driver does not write to either the DELQA-T-resident Synchronous Request Register (SRQR) or Asynchronous Request Register (ARQR) for the time limit specified in the HIT timeout value field in the init block. (The SRQR is for start and stop commands; the ARQR is for transmit and receive commands.)

When the HIT expires, the DELQA-PLUS board returns to DELQA-normal mode. The DELQA-normal board does not interrupt the host to announce it has completed this transition.

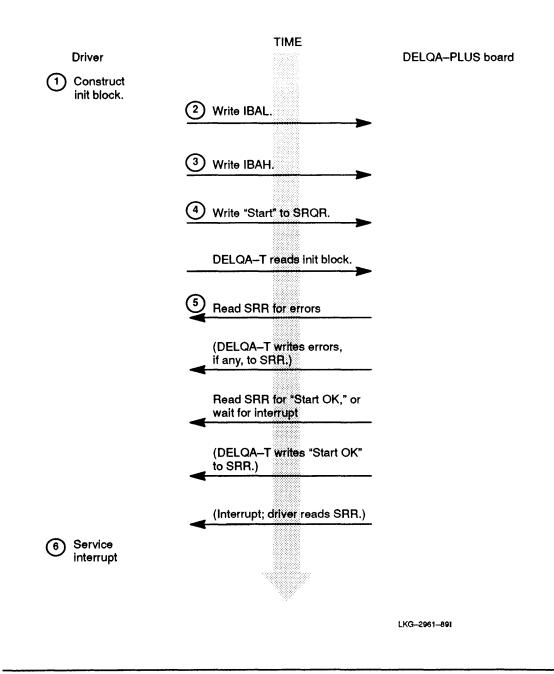

#### 6.3 Start the DELQA-T Board

This section describes the driver's task of starting to operate the DELQA-PLUS board in DELQA-T mode.

#### 6.3.1 Start the DELQA-T Board—Description

This operation involves the driver supplying a block of initialization data, then notifying the board of the block's location, then issuing the start request, then verifying that the board has read the block.

The DELQA-T board starts running with the following defaults:

- Starts processing at the beginning of the rings of transmit and receive buffer descriptors, regardless of where it may have stopped. (The beginnings of these rings are noted in the init block.)

- Interrupts are unblocked.

At this time (start-up) the driver can help the DELQA-T board operate more efficiently by giving the board as many receive buffers as possible (that is, by setting the ownership in each buffer's descriptor to "DELQA-T").

#### 6.3.2 Start The DELQA-T Board—Steps

Figure 6-4 shows these steps in diagram form.

- 1. The driver constructs an init block for the DELQA-T board; the init block resides in host memory. For complete information on the structure and contents of init blocks, see Section 6.14.3.

- 2. The driver writes the most significant bits of the init block's host memory address to the IBAH (init block address, high-order) register.

- 3. The driver writes the least significant bits of the init block's host memory address to the IBAL (init block address, low-order) register.

The IBAL and IBAH registers reside on the DELQA-T board. Their Q-bus addresses are BASE + 0 and BASE + 2, respectively.

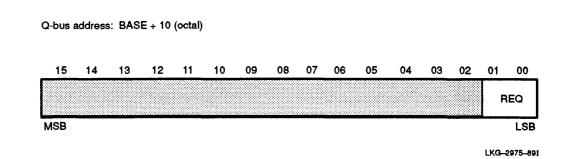

4. The driver writes the start request (value = 10 (binary)) to the REQ field (bits 01 and 00) of the SRQR register. The SRQR register resides on the DELQA-T board at Q-bus address BASE + 12 (octal).

5. The driver reads the SRR. If there are errors, the driver handles the errors; if there are no errors, the driver responds to the status information; if there are no errors or status information, and none appear for one second, the driver times out.

Successful status information is: the RESP field (bits 01 and 00) in the SRR has value 10 (binary) and the FES field (bit 15) has value 0.

If the driver times out before obtaining errors or status from the SRR, the driver may then receive an interrupt from the DELQA-T board (if interrupts are enabled; see bit 00 in the OPTIONS field in the init block).

6. After receiving an interrupt, the driver reads the SRR. If there are errors, the driver handles the errors; if there are no errors, the driver responds to the status information.

After these steps, the DELQA-T board is running and is ready to transmit and receive network message data.

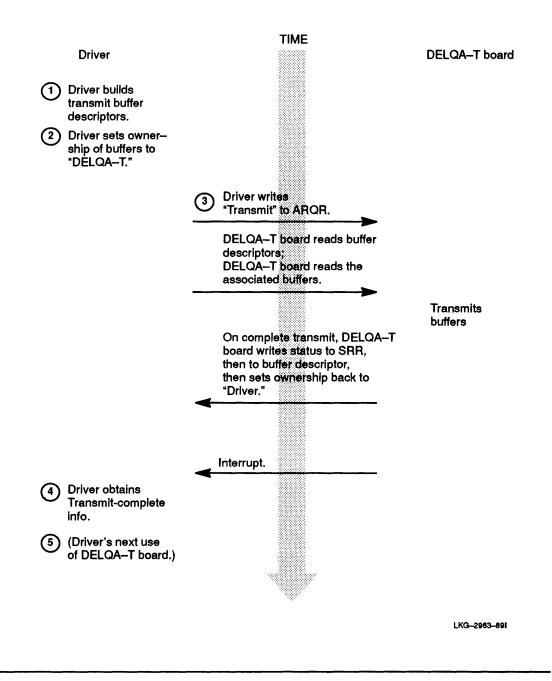

#### 6.4 Transmit

This section describes how the DELQA-T device driver causes the DELQA-T board to transfer network message data from host memory to the DELQA-T board's internal buffer memory and from there onto the network.

#### 6.4.1 Transmit—Description

Briefly, the driver gives the initial request to transmit some data by first setting the ownership of a transmit buffer descriptor to "DELQA-T" (setting bit 15 in word 3 to 0 (zero)), then writing the ARQR to notify the DELQA-T board to perform the transfer. The DELQA-T board then copies the data out of the transmit buffers and transmits it on the network.

On completion of the transmission, the DELQA-T provides a response to the driver. The driver gives this response by writing fields in the transmit buffer descriptors. If interrupts are not blocked, the DELQA-T board will also issue an interrupt after every transmitted buffer (or buffer pair—see Section 6.4.4).

#### 6.4.2 How the DELQA-T Board Transmits

Whenever the driver writes the transmit request (value = 8000 (hex)) to the ARQR, the DELQA-T board will start reading the next transmit buffer descriptor in the transmit buffer descriptor ring. (The location of the transmit buffer ring is given by pointers in the init block).

Note that the next buffer may be the first buffer in the ring under the following conditions:

- This is the first transmit operation after a board startup, or

- The board has worked its way around the ring.

The DELQA-T board proceeds through the ring sequentially, reading descriptors and transmitting buffers, until it encounters a descriptor whose owner is not "DELQA-T." This could be because the DELQA-T board has come all the way around the ring and encountered the first buffer it transmitted again, or it could be that the ring had less than 12 entries to transmit in the first place.

#### NOTE

In this discussion, "buffer ring" means the buffers as pointed to by the ring of descriptors. The buffers themselves may or may not be in a ring. The DELQA-T board then stops examining the ring, transmits the last buffer, if any, it has obtained because that buffer had its ownership set to "DELQA-T", posts status in that buffer's descriptor, and also attempts to give an interrupt.

The DELQA-T board transmits buffers that have their ownership set to "DELQA-T" (bit 15 word 3 of the buffer's descriptor), setting the ownership back to "Driver" after transmitting each buffer.

Meanwhile, the driver can be servicing the ring, reloading buffers, and setting the ownership in the buffer descriptors back to "DELQA-T" so that the DELQA-T board may never have to stop transmitting.

When the DELQA-T board encounters a pair of buffers that are chained together (see Section 6.4.4), it will transmit both buffers as one packet and give only one interrupt on completion of the transmit. (In addition to the interrupt, the DELQA-T board will also write status and ownership information for both buffers.)

#### Size Restrictions—Transmitted Data

The driver must make sure the packets it transmits on the network comply with the Ethernet/IEEE 802.3 size restriction, which is that the packet must be between 64 and 1518 (decimal) bytes inclusive, including CRC.

The driver must also make sure to comply with following size restrictions for buffers:

• The driver must not transmit a buffer whose size field contains a value larger than the maximum or smaller than the minimum legal size (see Table 6-1). The DELQA-T board is not guaranteed to perform the transmit correctly if the size field (and/or the buffer) is too large or too small.

Table 6–1 summarizes the size restrictions for all buffers that the driver can transmit via the DELQA-T board. Note that the size restrictions are complex and have effects on each other.

- When chaining buffers during transmit operations:

- 1. The first buffer must be at least 100 (decimal) bytes long, and

- 2. The second buffer must be at least 1 byte long but not more than 1418 (decimal) bytes long.

- The driver must never send buffers of 0 bytes in length or larger than 1518 (decimal) bytes in length.

The driver notes the size of each buffer to be transmitted in the BCT in that transmit buffer's descriptor.

| If these fields are set as follows: |     |     | The minimum and<br>maximum sizes,<br>in bytes, are: |                      |                      |

|-------------------------------------|-----|-----|-----------------------------------------------------|----------------------|----------------------|

| LOP                                 | DTC | FOT | FOT in previous de-<br>scriptor                     | Minimum<br>(decimal) | Maximum<br>(decimal) |

| 0                                   | 0   | 0   | 0                                                   | 60                   | 1514                 |

| 0                                   | 0   | 1   | 0                                                   | 100                  | 1513                 |

| 0                                   | 0   | 0   | 1                                                   | 1                    | 1414                 |

| 0                                   | 1   | 0   | 0                                                   | 64                   | 1518                 |

| 0                                   | 1   | 1   | 0                                                   | 100                  | 1517                 |

| 0                                   | 1   | 0   | 1                                                   | 1                    | 1418                 |

| 1                                   | х   | 0   | 0                                                   | 32                   | 32                   |

Table 6–1: Size Restrictions For Transmitted Buffers

Key:

LOP—Loopback mode; resides in init block DTC—Disable CRC on transmit; resides in init block FOT—First-of-two buffers; resides in transmit descriptor

#### 6.4.3 Transmit—Steps

Figure 6-5 shows these steps in diagram form.

- 1. The driver builds a descriptor; the descriptor points to a buffer that is ready to be transmitted.

- 2. The driver sets the ownership to "DELQA-T" (sets bit 15 of word 3 in the buffer descriptor is set to 0 (zero)).

- 3. The driver notifies the DELQA-T board to begin transmitting by writing a transmit request (value = 8000 (hex)) to the ARQR.

The DELQA-T board will then begin:

- a. Sequentially reading transmit buffer descriptors,

- b. Reading each descriptor's associated buffer, and

c. Transmitting each buffer.

On completing the transmission of each buffer (or buffer pair if the buffers are chained), the DELQA-T board will:

- a. Write status information to the SRR.

- b. Write status information into the buffer descriptor.

- c. Set the ownership in the buffer descriptor back to "Driver."

- d. If the DELQA-T board's interrupts are currently unblocked, interrupt the driver.

- 4. The driver must now obtain the transmit-complete information from the board, which exists in the above-mentioned forms. The suggested procedure is:

- a. The driver reads the SRR.

If there are errors, the driver handles the errors.

- b. If there are no errors, the driver checks the appropriate buffer descriptors for the following information:

- Ownership is set back to "Driver."

- Status information about the transfer.

- 5. The driver can now re-use the descriptor for subsequent transmits.

#### 6.4.4 Chaining Buffers

Chaining is useful for allowing higher-level software to pass the driver a packet as two buffers; for example, the packet header travels in one buffer and the packet data travels in the other. Chaining allows this packet to be reunited and transmitted as a unit.

To chain two transmit buffers together, the driver must

1. Set the FOT (first-of-two) field (bit 14 in word 3) in the first transmit buffer's descriptor to 1.

- 2. Make sure the FOT field in the second (that is, the next) transmit buffer's descriptor to 0.

- 3. Give the buffers to the board in reverse order, chronologically. ("Give" here means set the ownership.)

This guarantees that the DELQA-T board will own both buffers by the time it must transmit them rather than possibly having to wait for the second buffer. If the driver does not follow this procedure, the DELQA-T board is not guaranteed to transmit chained buffers correctly.

This will cause the DELQA-T board to transmit both buffers as one packet before reporting completion. The DELQA-T board will transmit the buffers in correct order, that is, the first buffer at the beginning of the packet and the second buffer at the end of the packet.

#### NOTE

When chaining, it is the driver's responsibility to make sure the DELQA-T board does not transmit oversize packets on the network.

#### 6.5 Receive

This section describes the driver's task of receiving data using the DELQA-T board.

#### 6.5.1 Receive—Description

Receiving a packet involves transferring the packet from the network to the DELQA-T board's internal buffer memory and from there to host memory.

Even if the driver doesn't ask the DELQA-T board to receive, the DELQA-T board will begin collecting packets from the network that are addressed to the local node as soon as the the DELQA-T board completes startup and starts running.

The DELQA-T board will buffer up to to 16 (decimal) maximum-size Ethernet/IEEE 802.3 packets before it begins discarding further incoming packets.

The DELQA-T board will operate more efficiently if the driver gives the DELQA-T board as many receive buffers as possible.

#### NOTE

It is not necessary for the driver to get a receive response from DELQA-T board before the driver issues further receive requests. The driver can have multiple unacknowledged receive requests ready on the receive ring.

#### 6.5.2 Receive—Steps

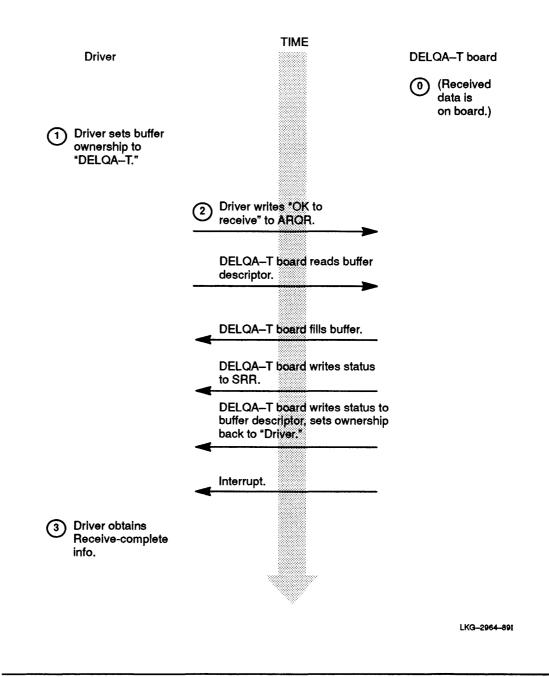

To receive a buffer of data from the DELQA-T board, the driver follows these steps. Figure 6–6 shows these steps in diagram form. (The steps assume the DELQA-T board has data that it has received from the network.)

- 1. The driver sets the ownership in the buffer descriptor to "DELQA-T."

- 2. The driver notifies the DELQA-T board to begin receiving, that is, begin writing received data into the receive buffers. To do this, the driver writes the receive request (value = 8000 (hex)) to the ARQR register.

The DELQA-T board will then begin:

- a. Reading buffer descriptors, and

- b. Filling each descriptor's associated buffer with received data.

On filling each buffer, the DELQA-T board will

- Write status information to the SRR.

- Write status information into the buffer descriptor.

- Set the ownership in the descriptor to "driver" (DELQA-T board sets bit 15 of word 3 of the receive buffer descriptor to 1).

- If interrupts are unblocked, it will then interrupt the driver.