INSTRUCTION MANUAL

## TCO2 DECTAPE TRANSPORT CONTROL

DIGITAL EQUIPMENT CORPORATION . MAYNARD, MASSACHUSETTS

# TCO2

## DECTAPE TRANSPORT CONTROL

## INSTRUCTION MANUAL

March 1968

DIGITAL EQUIPMENT CORPORATION • MAYNARD, MASSACHUSETTS

Copyright 1968 by Digital Equipment Corporation

## TABLE OF CONTENTS

•

## CHAPTER 1 INTRODUCTION AND DESCRIPTION

| 1.1   | PURPOSE AND SCOPE        | 1-1 |

|-------|--------------------------|-----|

| 1.2   | EQUIPMENT DESCRIPTION    | 1-2 |

| 1.2.1 | Physical Characteristics | 1-2 |

| 1.3   | SYSTEM DESCRIPTION       | 1-3 |

| 1.4   | REFERENCED DOCUMENTS     | 1-4 |

#### CHAPTER 2 OPERATION AND PROGRAMMING

| 2.1   | DECTAPE SYSTEM               | 2-1  |

|-------|------------------------------|------|

| 2.2   | DECTAPE CONTROL TC02         | 2-2  |

| 2.3   | DECTAPE FORMAT               | 2-2  |

| 2.3.1 | Mark – Track Format          | 2-4  |

| 2.4   | DECTAPE INSTRUCTIONS         | 2-7  |

| 2.5   | STATUS A AND B REGISTERS     | 2-8  |

| 2.5.1 | Status A Register Functions  | 2-8  |

| 2.5.2 | Status B Register Functions  | 2-10 |

| 2.6   | CONTROL MODES AND FUNCTIONS  | 2-11 |

| 2.7   | CONTROL FUNCTIONS            | 2-11 |

| 2.7.1 | Move                         | 2-12 |

| 2.7.2 | Search                       | 2-12 |

| 2.7.3 | Read Data                    | 2-13 |

| 2.7.4 | Read All                     | 2-13 |

| 2.7.5 | Write Data                   | 2-14 |

| 2.7.6 | Write All                    | 2-14 |

| 2.7.7 | Write Timing and Mark Tracks | 2-14 |

| 2.7.8 | Enable and Interrupt Feature | 2-15 |

| 2.7.9 | Error Conditions             | 2-15 |

| 2.8   | PROGRAMMED OPERATION         | 2-15 |

|       |                              |      |

## CONTENTS (cont.)

## CHAPTER 3 PRINCIPLES OF OPERATION

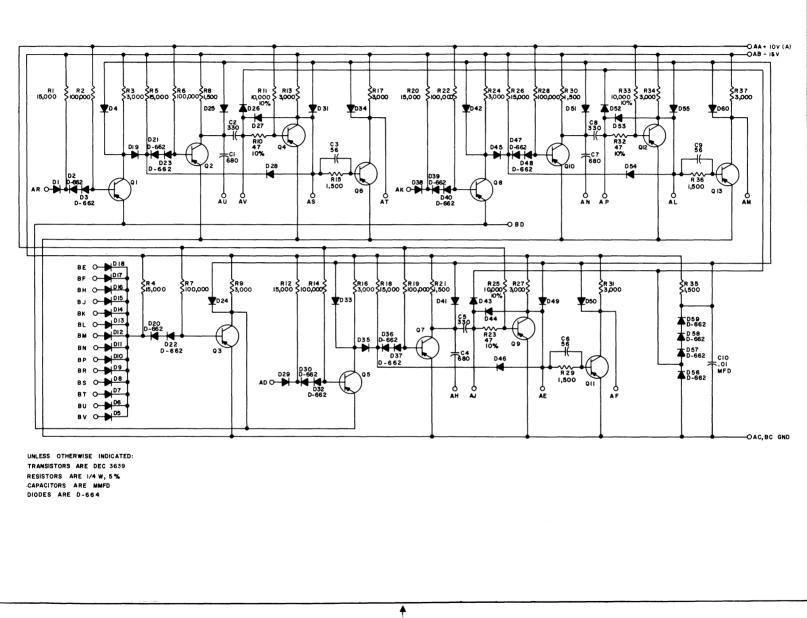

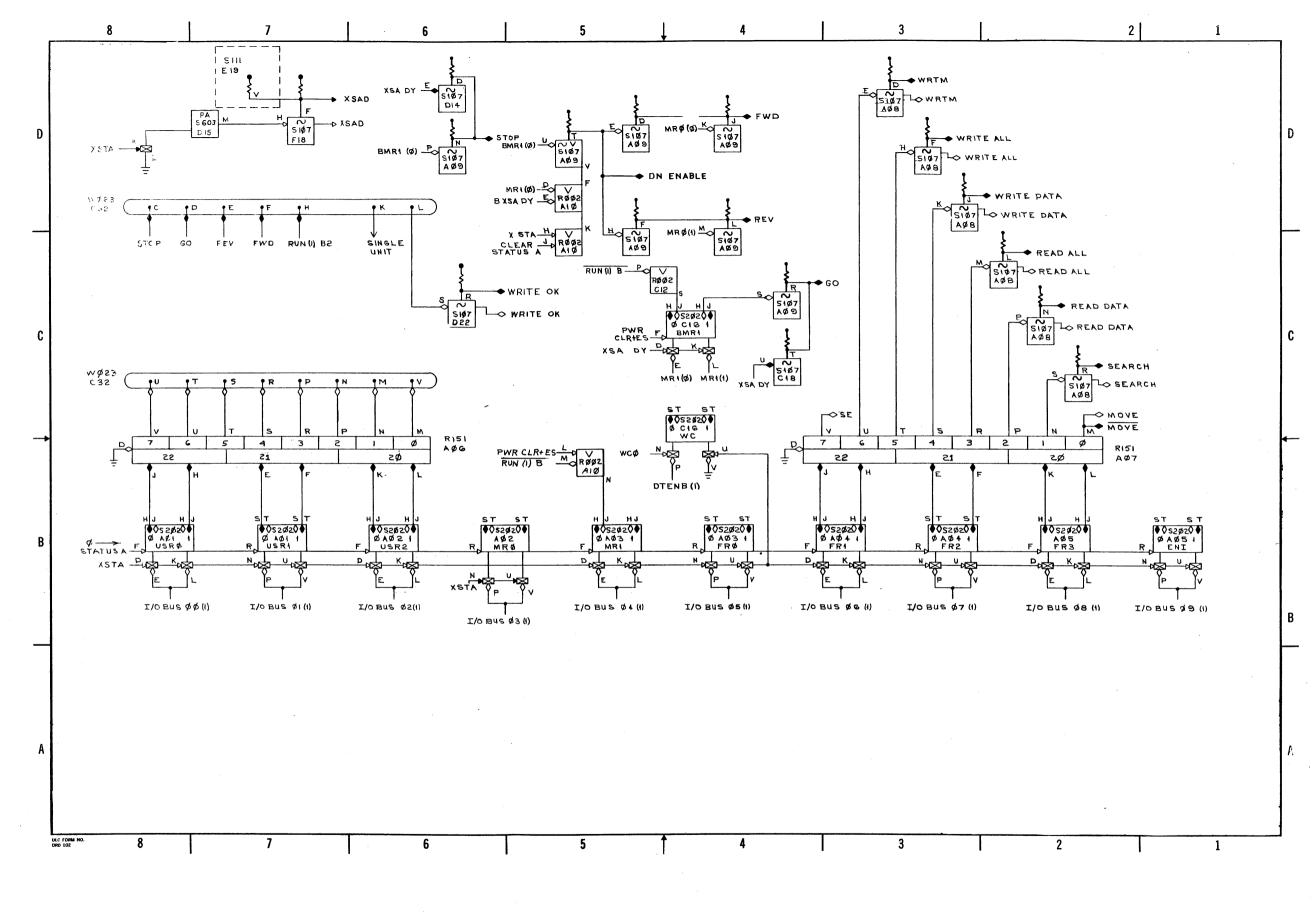

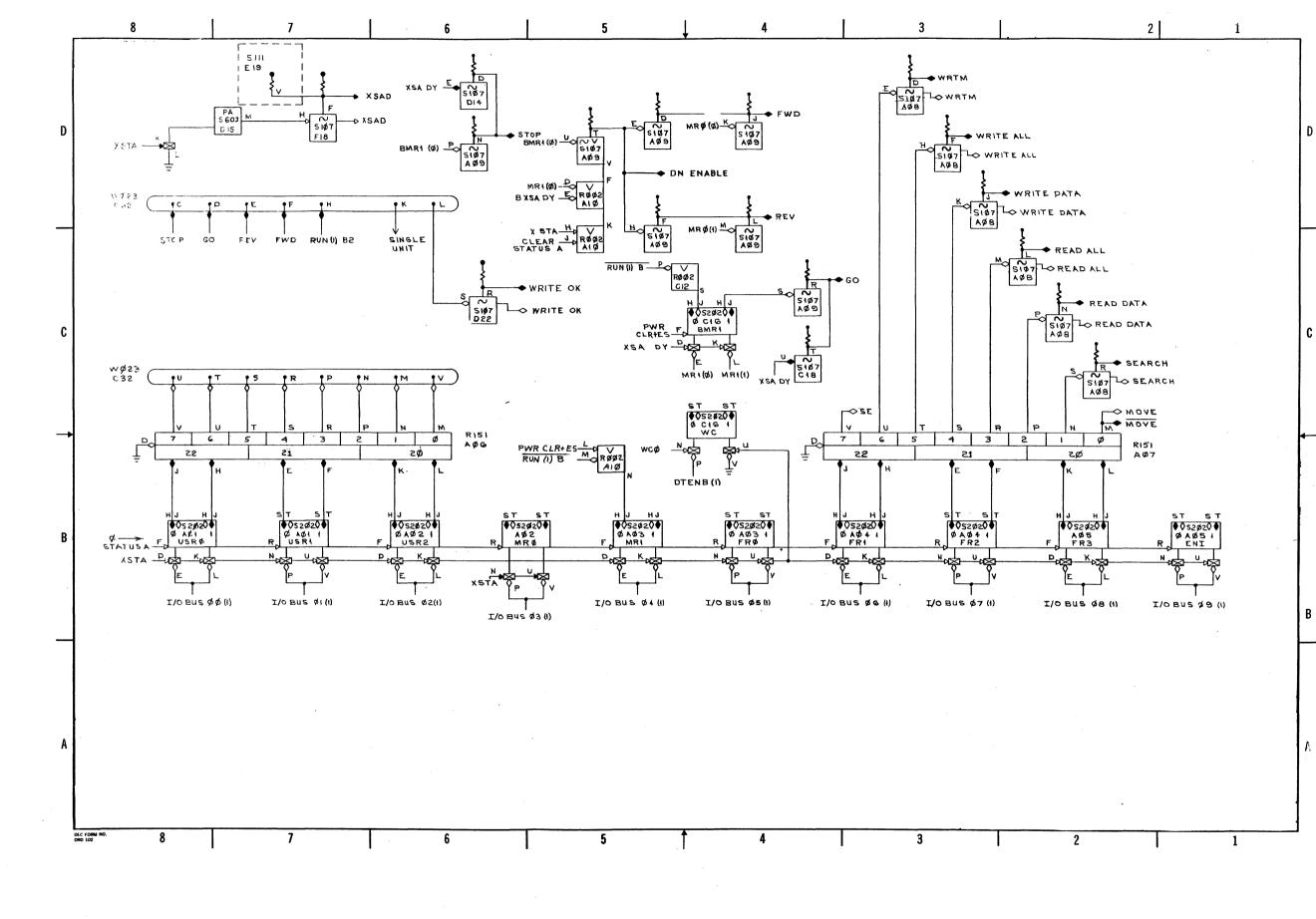

| 3.1      | FUNCTIONAL DESCRIPTION                  | 3-1  |

|----------|-----------------------------------------|------|

| 3.1.1    | Information Flow                        | 3-1  |

| 3.1.2    | Command Flow Registers                  | 3–5  |

| 3.2      | SYMBOLS AND ABBREVIATIONS               | 3-6  |

| 3.3      | DETAILED DESCRIPTIONS                   | 3-11 |

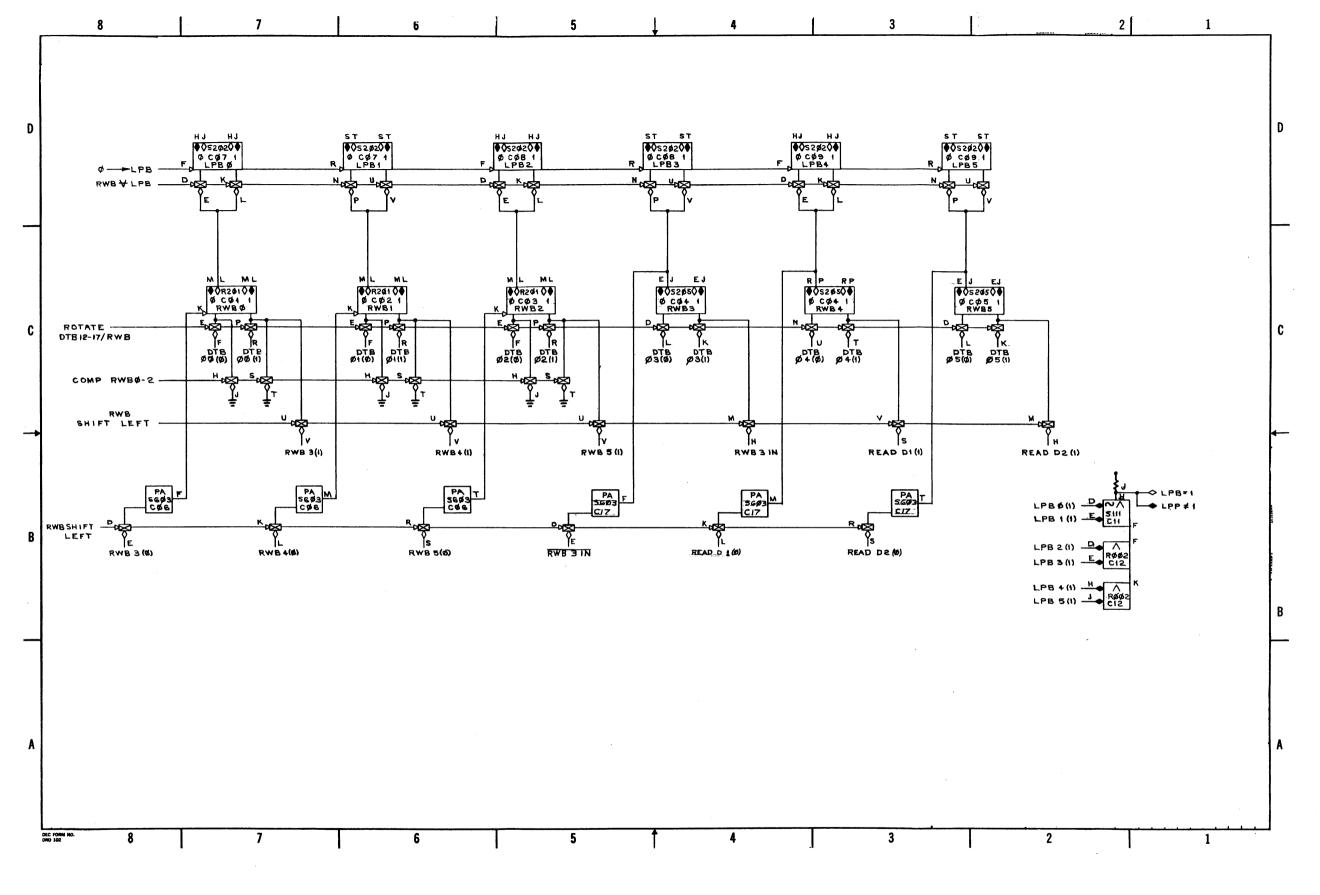

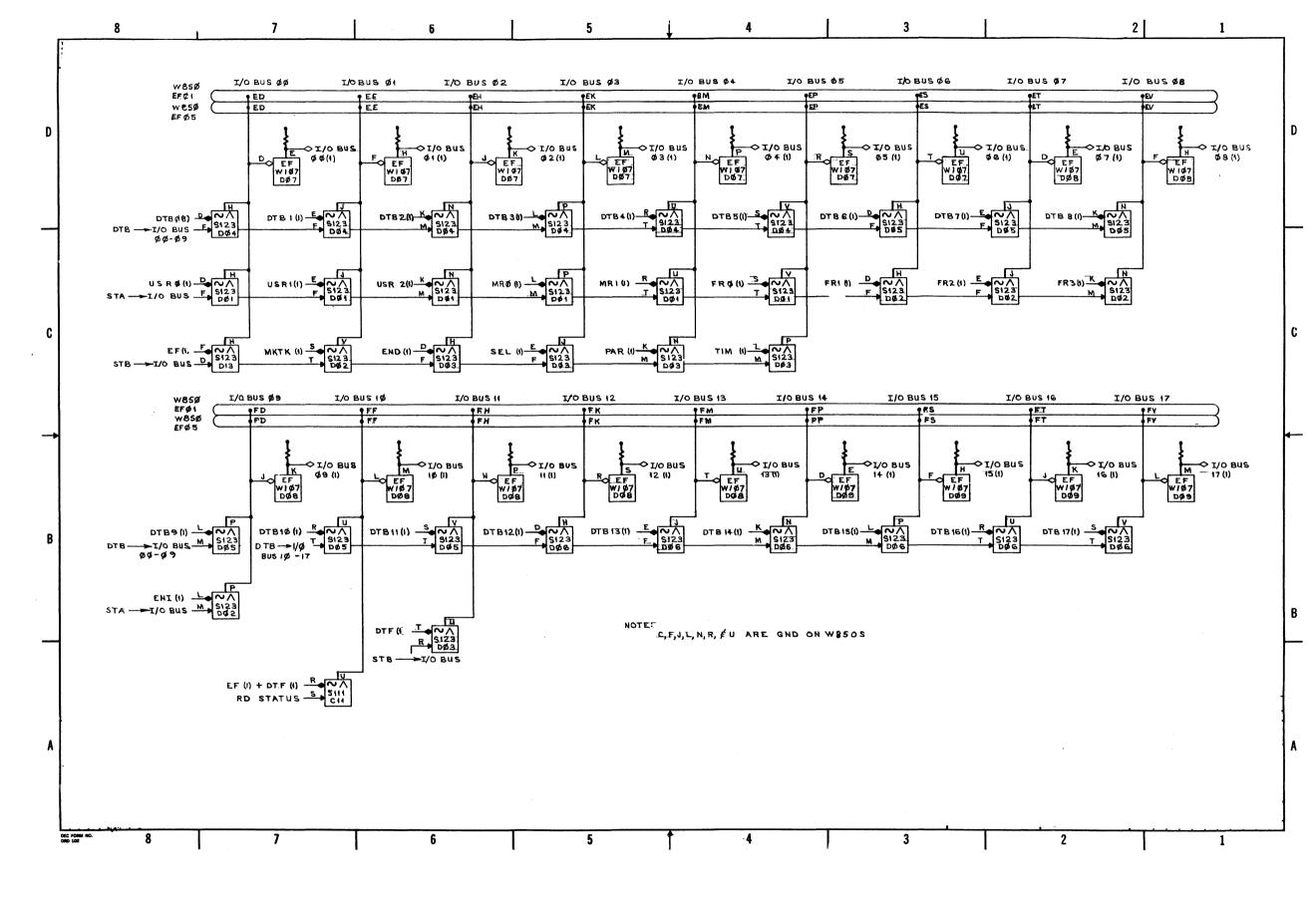

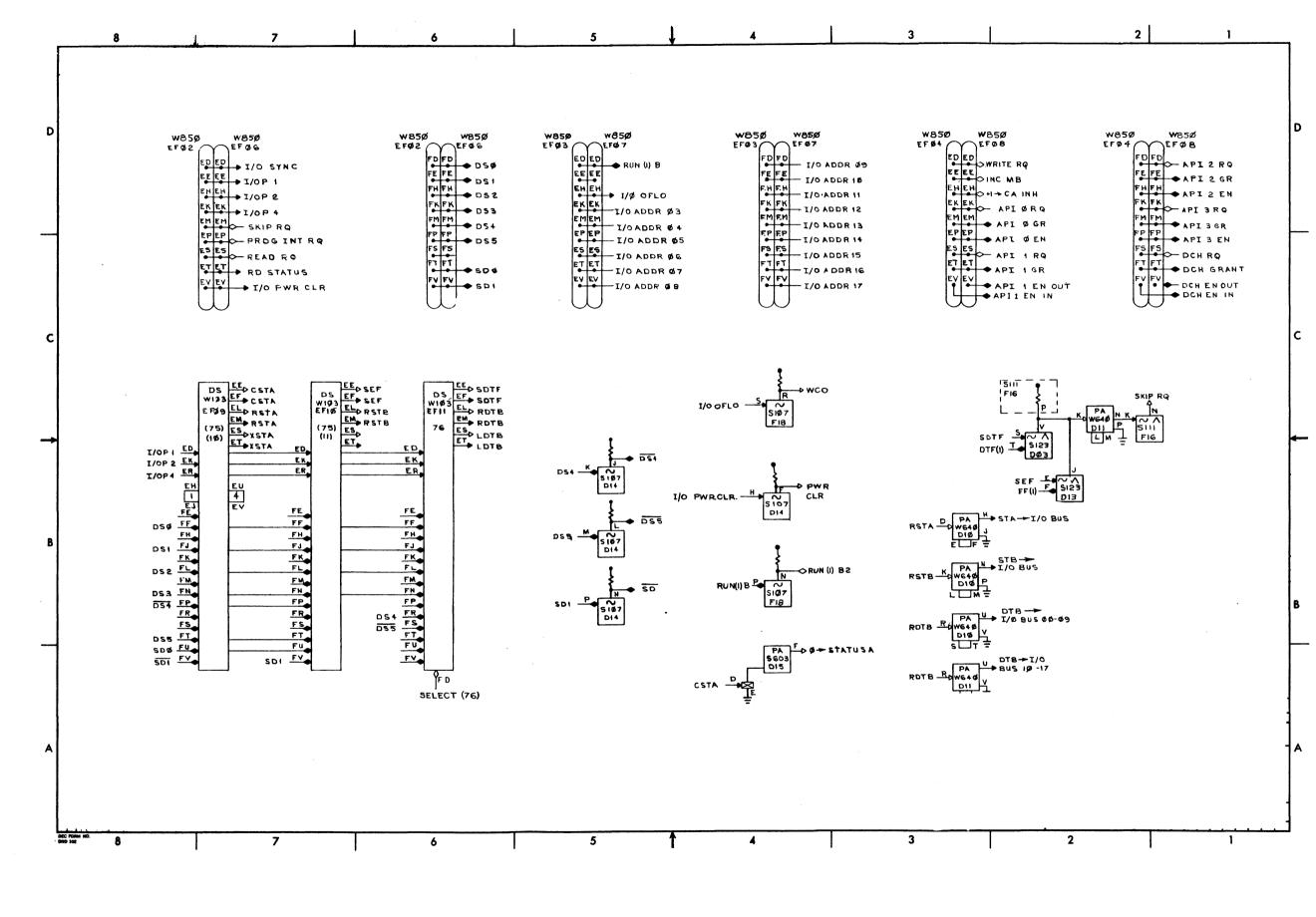

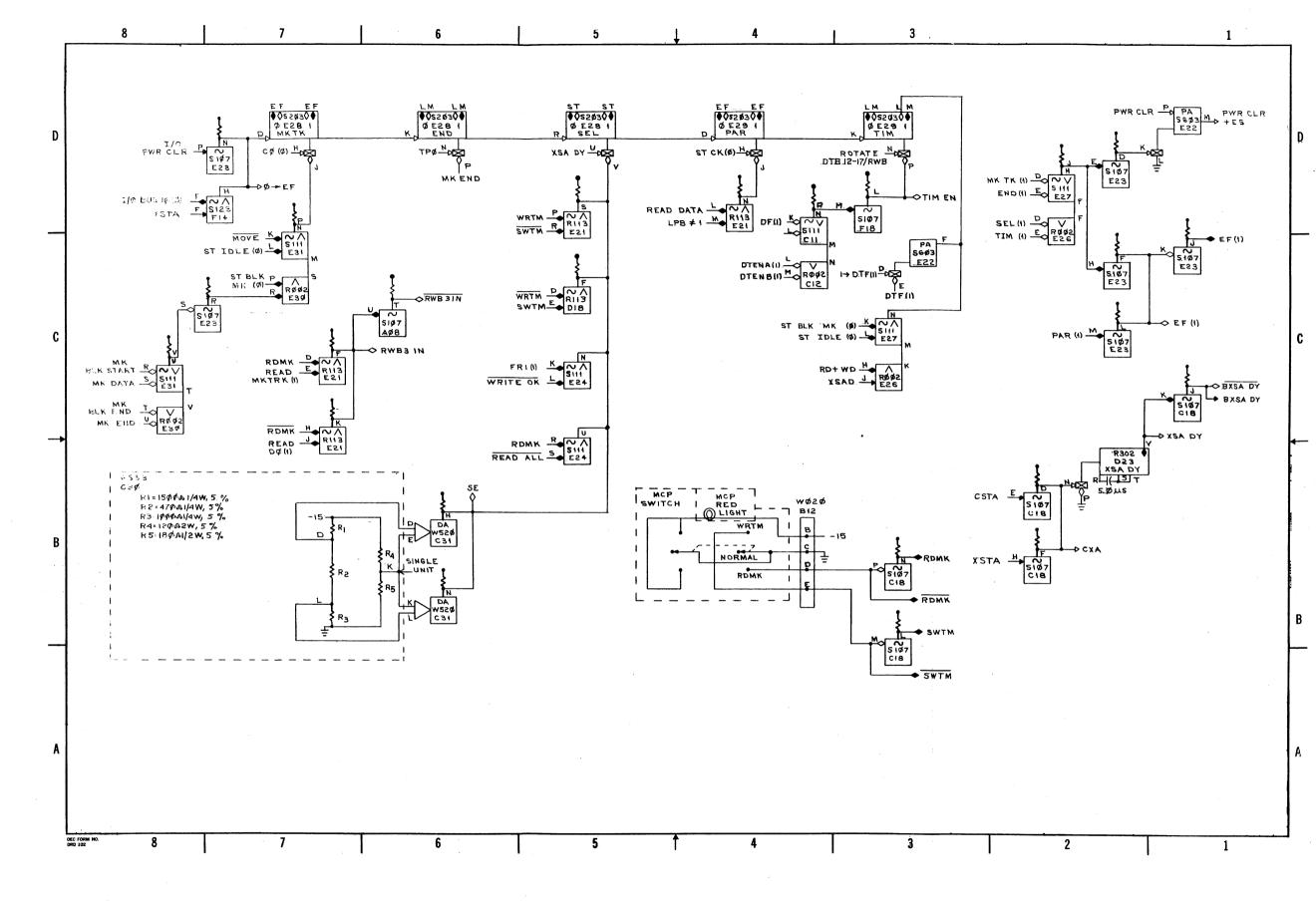

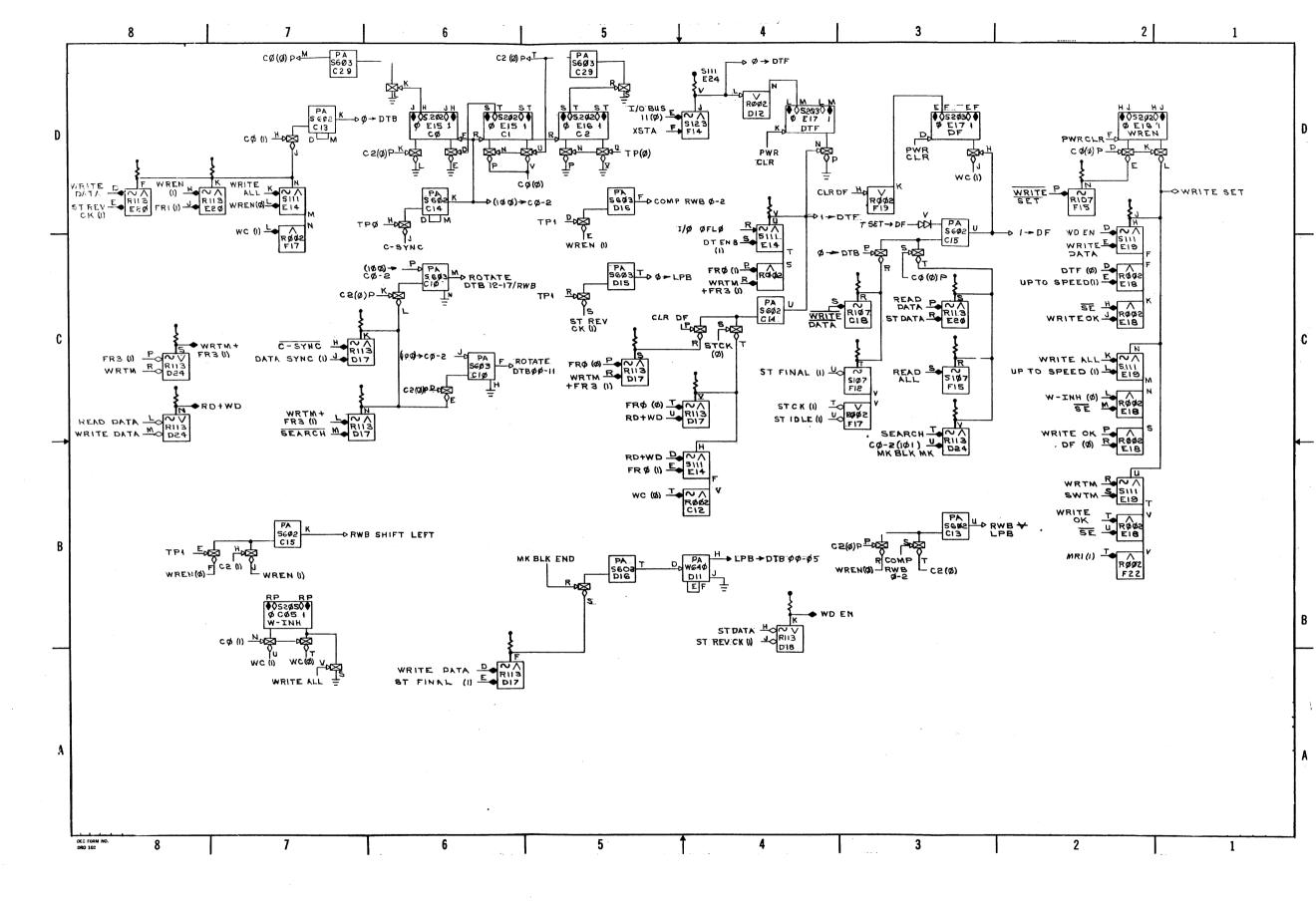

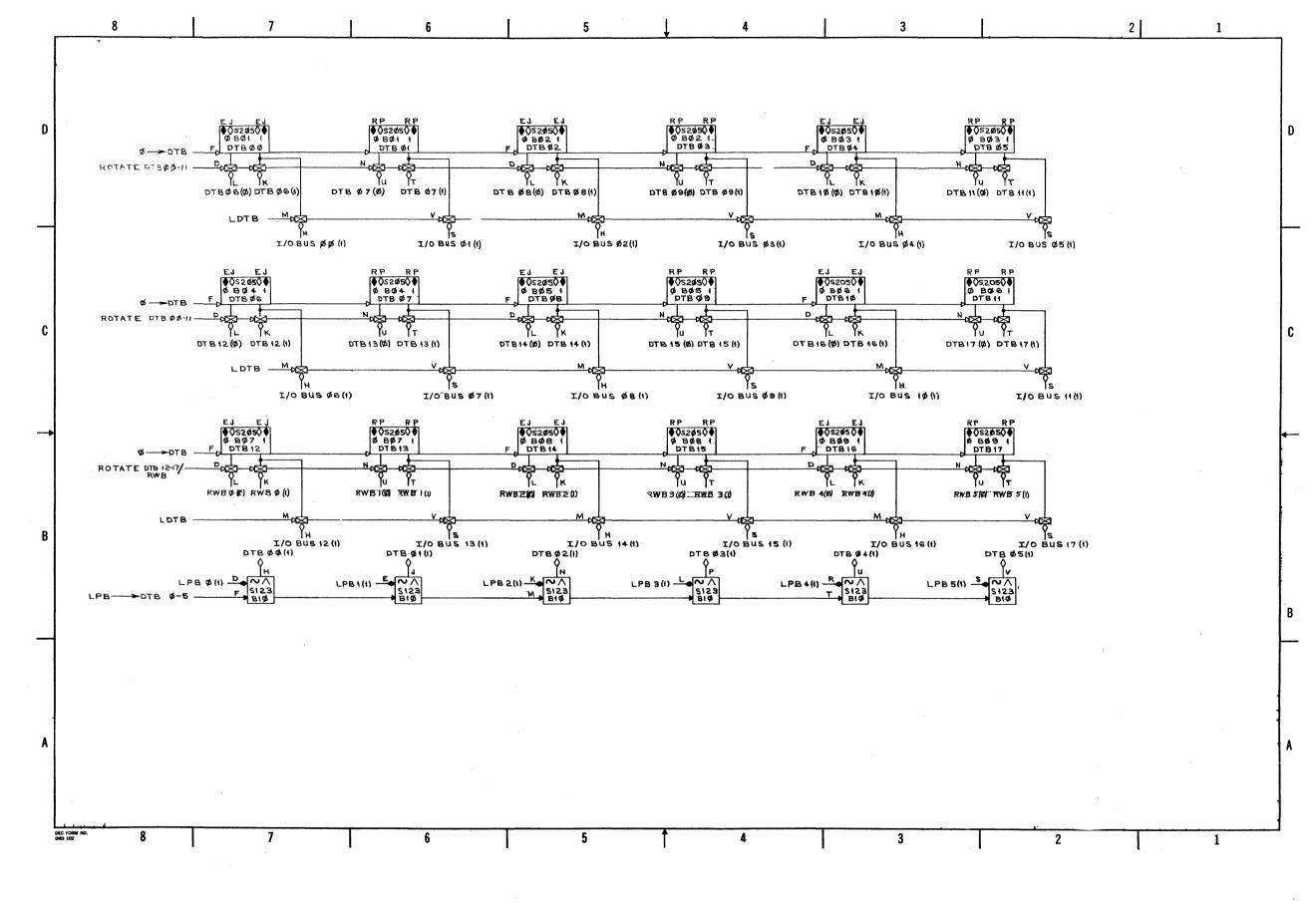

| 3.3.1    | Basic Read/Write Logic                  | 3-11 |

| 3.3.2    | Initialization Operations               | 3-13 |

| 3.3.2.1  | I/O Bus Interface                       | 3-13 |

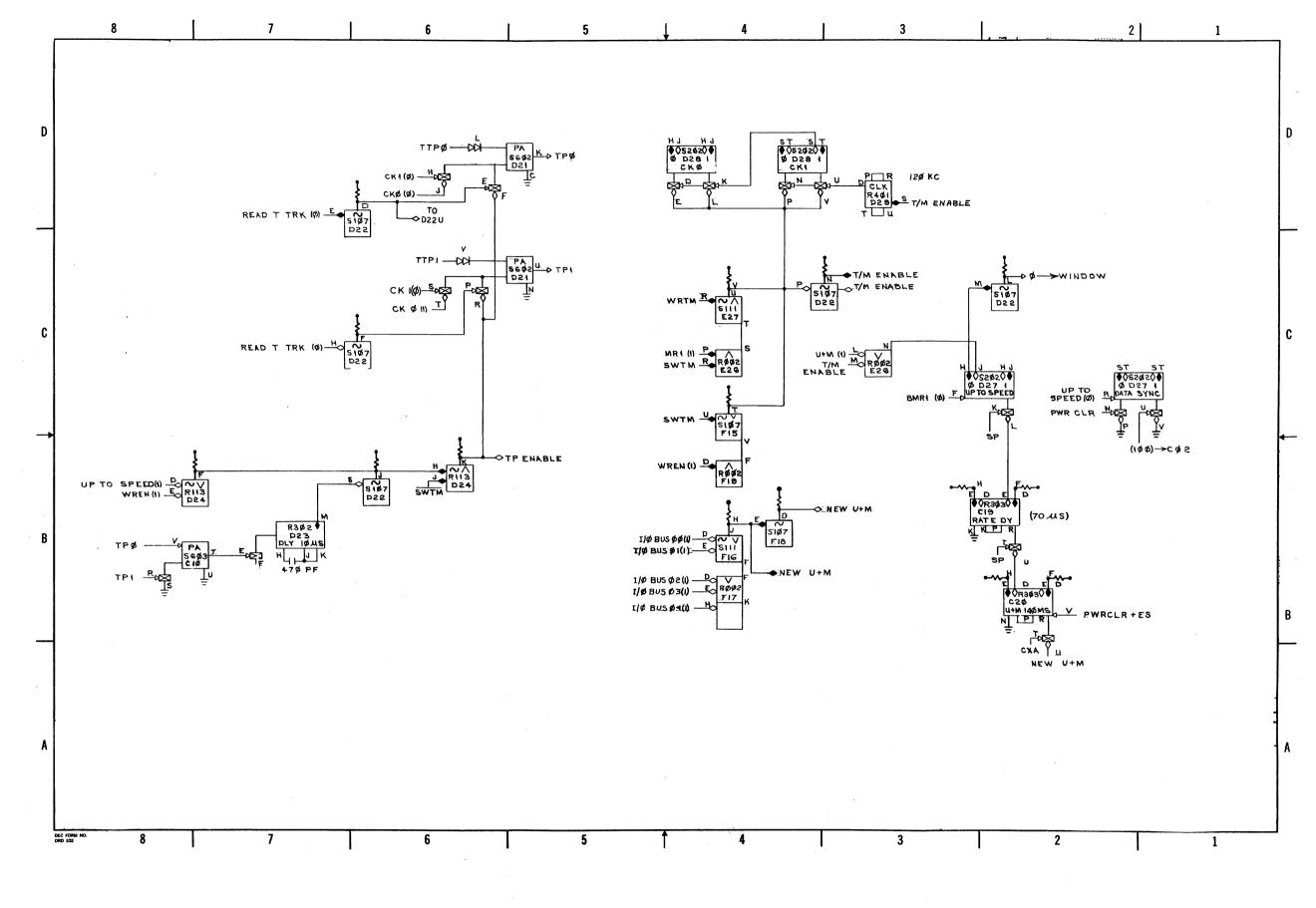

| 3.3.2.2  | Timing Pulse Generation                 | 3-14 |

| 3.3.2.3  | Tape Unit Selection                     | 3-14 |

| 3.3.2.4  | Tape Motion Selection                   | 3-15 |

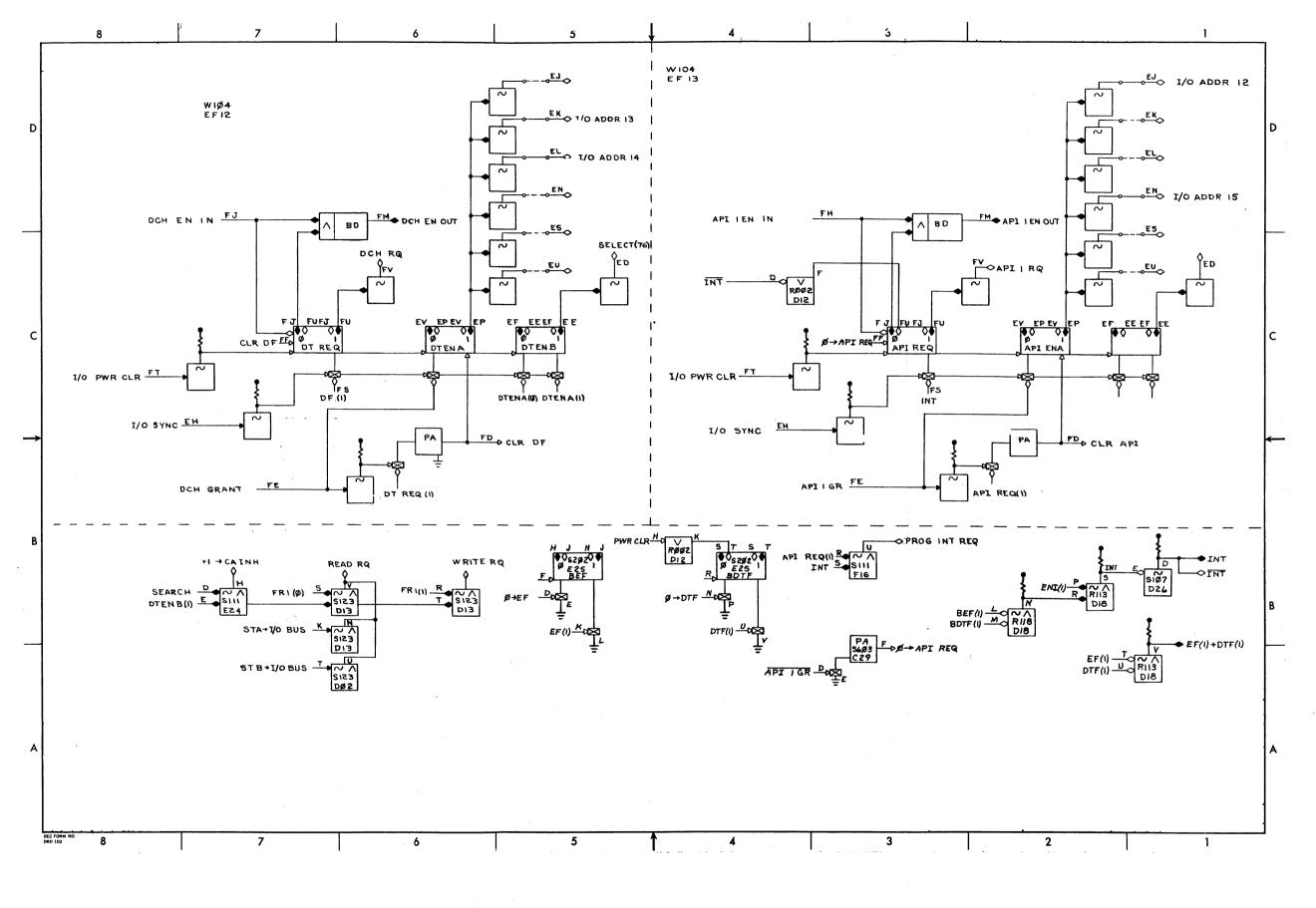

| 3.3.3    | Device Selection Logic                  | 3-15 |

| 3.3.4    | Status B Register and Skip Instructions | 3-16 |

| 3.3.5    | Interrupt Enable                        | 3-16 |

| 3.3.6    | New Unit/Motion Select                  | 3-16 |

| 3.3.7    | Counter Register                        | 3-17 |

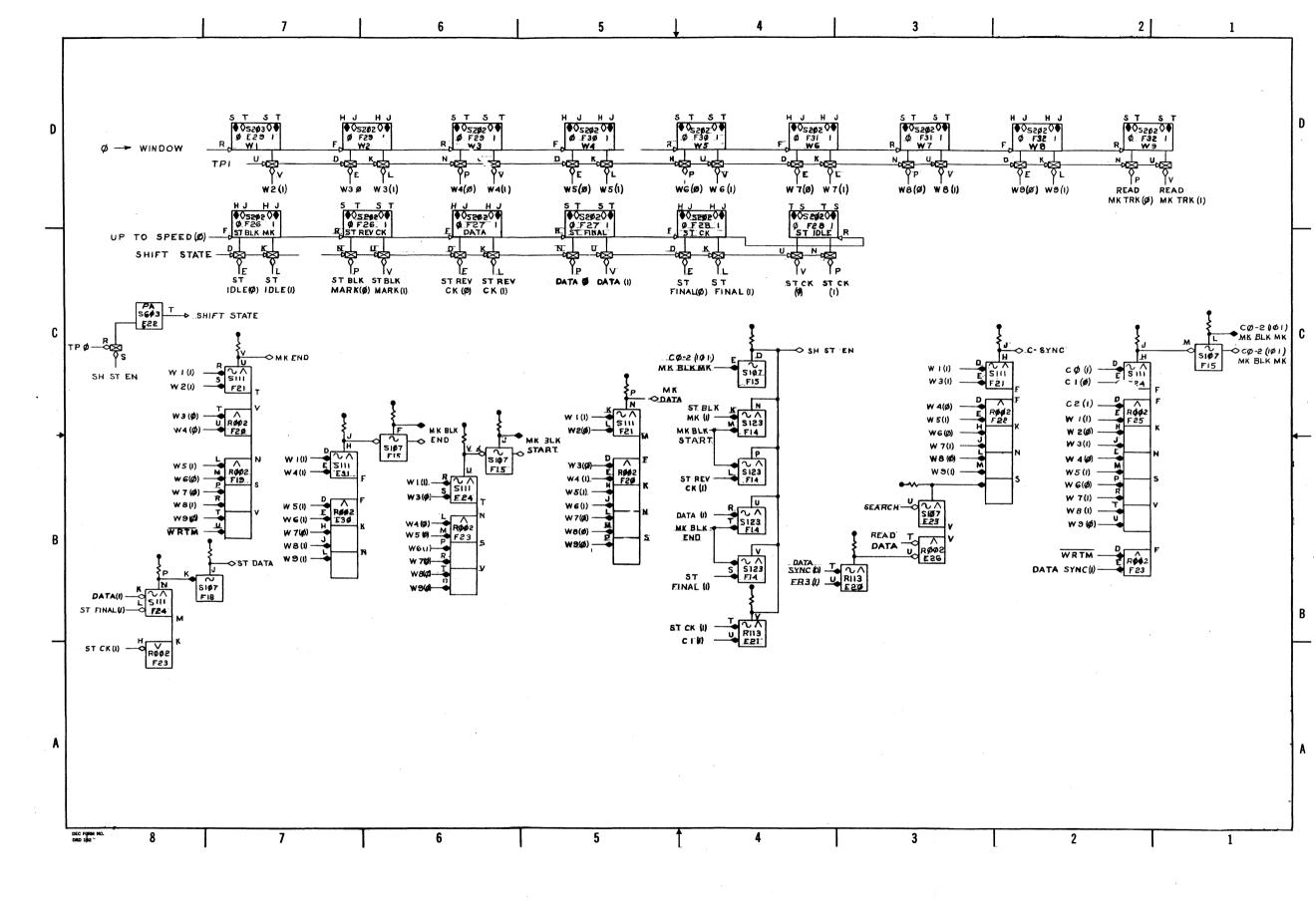

| 3.3.8    | Window Register                         | 3-18 |

| 3.3.8.1  | Counter Sync Level (C-SYNC)             | 3-18 |

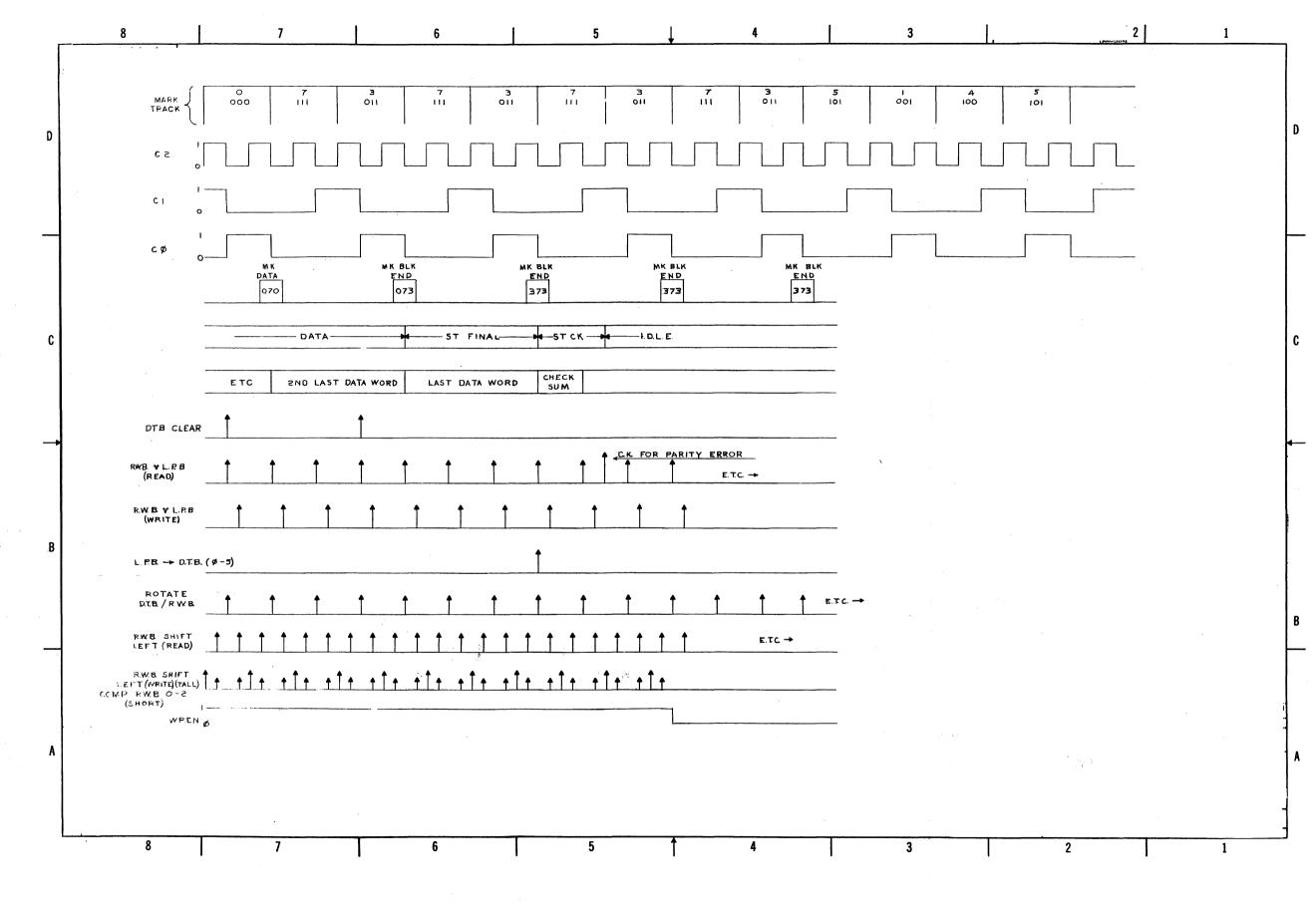

| 3.3.8.2  | Start Block Mark (MK BLK MK)            | 3-19 |

| 3.3.8.3  | Data Marks                              | 3-21 |

| 3.3.9    | State Register                          | 3-22 |

| 3.3.10   | Function Selection                      | 3-22 |

| 3.3.10.1 | Move Tape (000)                         | 3-23 |

| 3.3.10.2 | Search (001)                            | 3-23 |

| 3.3.10.3 | Read Data (010)                         | 3-24 |

| 3.3.10.4 | Read All Functions (011)                | 3-24 |

| 3.3.10.5 | Write Data Function (100)               | 3-25 |

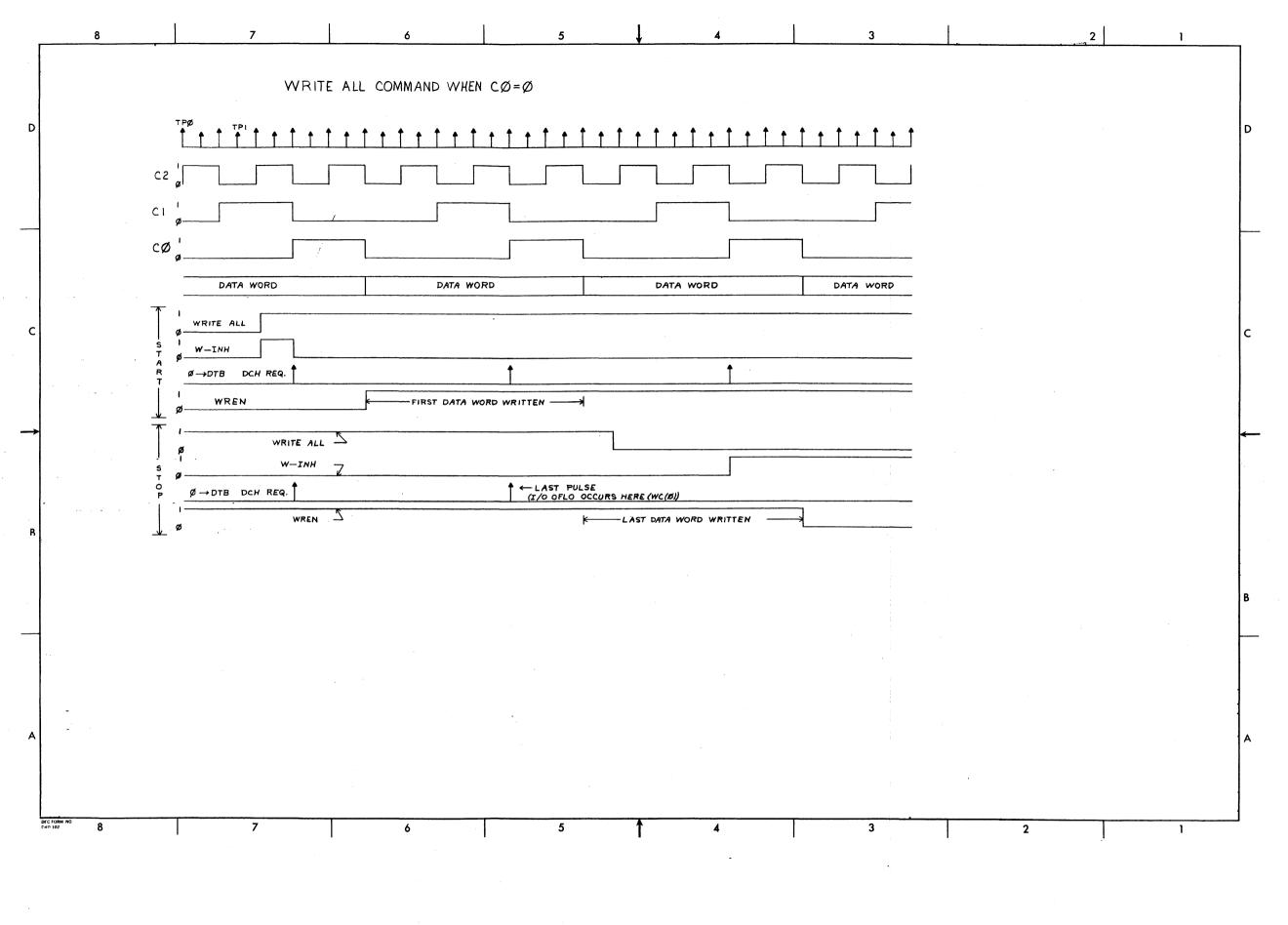

| 3.3.10.6 | Write All Function (101)                | 3-26 |

| 3.3.10.7 | Write Timing and Mark Track (110)       | 3-26 |

| 3.3.11   | Read and Write Sequences                | 3-27 |

| 3.3.12   | Longitudinal Parity Buffer Operation    | 3-32 |

## CONTENTS (cont.)

| 3.3.13   | Power Clear and Error Stop Logic | 3-33 |

|----------|----------------------------------|------|

| 3.3.14   | Increment CA Inhibit (+1←CA INH) | 3-33 |

| 3.3.15   | Interrupt Request                | 3-33 |

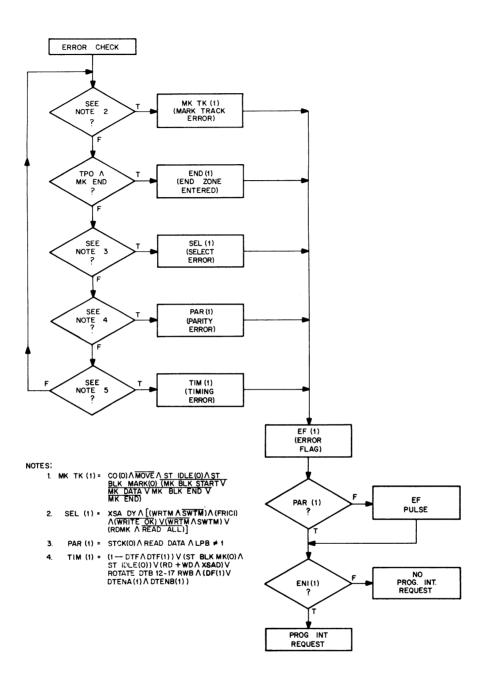

| 3.3.16   | Error Flags (EF)                 | 3-33 |

| 3.3.16.1 | Mark – Track Error (MK TRK)      | 3-34 |

| 3.3.16.2 | Select Error (SEL)               | 3-34 |

| 3.3.16.3 | Parity Error (PAR)               | 3-36 |

| 3.3.16.4 | Timing Error (TIM)               | 3-36 |

| 3.3.16.5 | End Error (END)                  | 3-37 |

| 3.3.17   | DECtape Flag (DTF)               | 3-37 |

## CHAPTER 4

| 4.1   | INSTALLATION PROCEDURES      | 4-1 |

|-------|------------------------------|-----|

| 4.1.1 | Site Preparation             | 4-1 |

| 4.1.2 | Environmental Conditions     | 4-2 |

| 4.1.3 | Power and Cable Requirements | 4-2 |

| 4.1.4 | DECtape Signal Connectors    | 4-2 |

## CHAPTER 5 MAINTENANCE

| 5.1   | MAINTENANCE EQUIPMENT           | 5-1  |

|-------|---------------------------------|------|

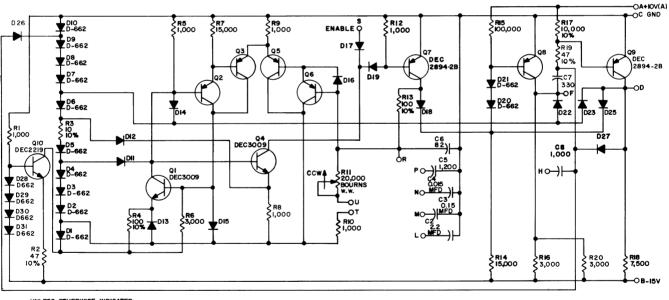

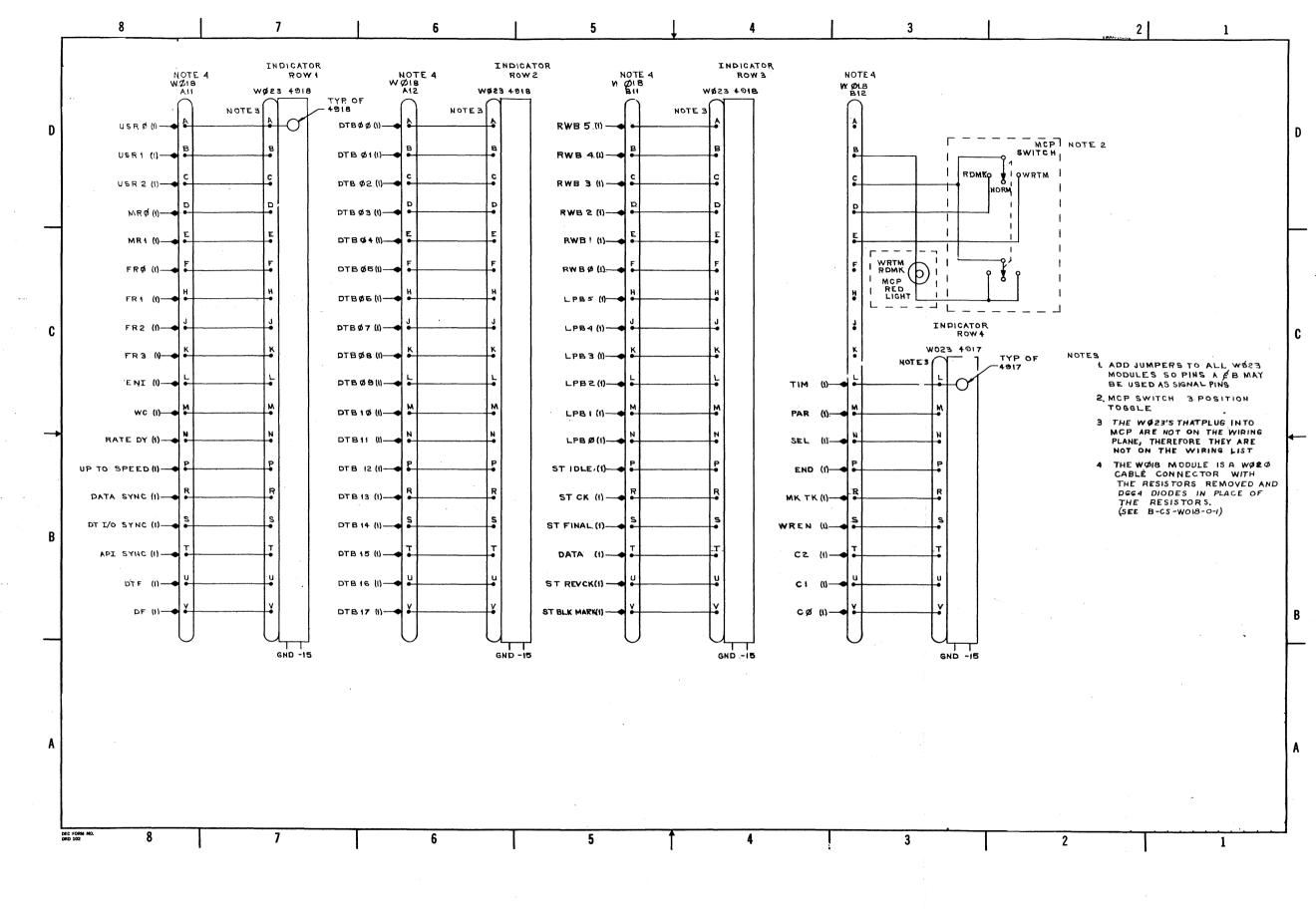

| 5.2   | MAINTENANCE CONTROL PANEL       | 5-1  |

| 5.3   | DEC MODULES                     | 5-4  |

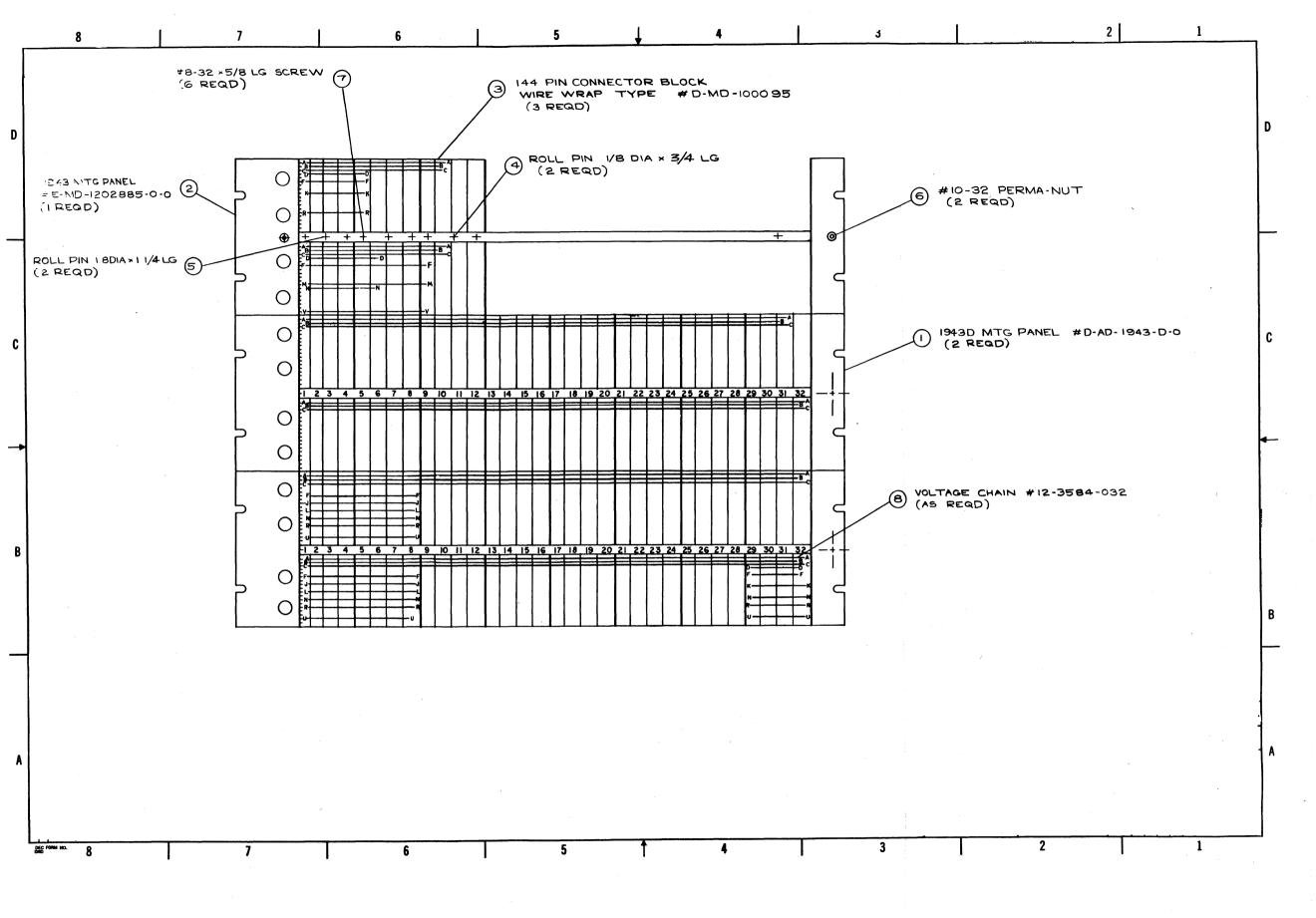

| 5.3.1 | Module Locations and Complement | 5-4  |

| 5.3.2 | Circuit Description             | 5-5  |

| 5.3.3 | Module Replacement Procedure    | 5-5  |

| 5.4   | POWER SUPPLY 779                | 5-21 |

| 5.4.1 | Mechanical Characteristics      | 5-22 |

| 5.4.2 | Power Supply Checks             | 5-22 |

| 5.4.3 | Marginal Checks                 | 5-22 |

| 5.5   | POWER CONTROL PANEL (Type 832F) | 5-23 |

| 5.6   | PREVENTIVE MAINTENANCE          | 5-24 |

| 5.6.1 | Mechanical Checks               | 5-24 |

## CONTENTS (cont.)

## CHAPTER 6 ENGINEERING DRAWINGS

| 6.1 | SYMBOLS AND DESIGNATIONS | 6-1 |

|-----|--------------------------|-----|

| 6.2 | DRAWING LIST             | 6-1 |

## TABLES

| 1-1 | DEC Documents                                      | 1-4  |

|-----|----------------------------------------------------|------|

| 2-1 | Mark Track Coding                                  | 2-6  |

| 2-2 | TC02 DECtape Instruction List                      | 2-8  |

| 2-3 | Status A Bit Assignments                           | 2-9  |

| 2-4 | Status B, Bit Assignment                           | 2-10 |

| 3-1 | Engineering Drawing Identification                 | 3-6  |

| 3-2 | Symbols and Abbreviations                          | 3-7  |

| 3-3 | Counter Register Sequence                          | 3-17 |

| 3-4 | Sequence of Block Marks and Control States         | 3-19 |

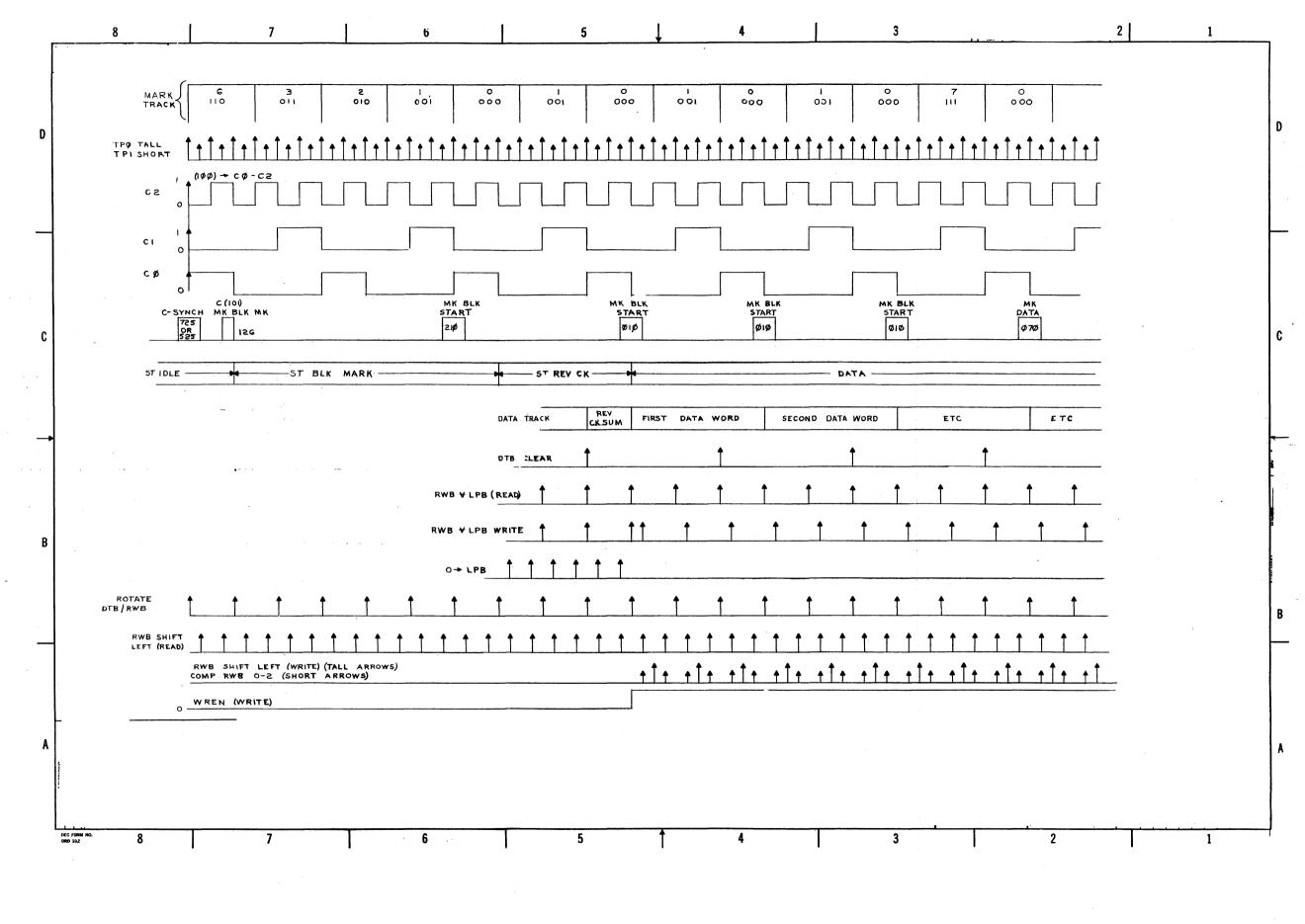

| 3-5 | Sequence of Events During Read Operation           | 3-28 |

| 3-6 | Sequence of Events During Write Operation          | 3-30 |

| 5-1 | Maintenance Equipment                              | 5-1  |

| 5-2 | Maintenance Control Panels (Switch and Indicators) | 5-2  |

| 5-3 | TC02 Module Complement                             | 5-4  |

| 6-1 | Engineering Drawing List                           | 6-1  |

## ILLUSTRATIONS

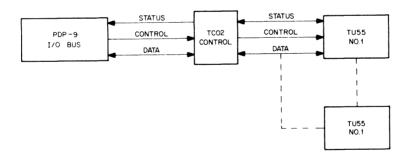

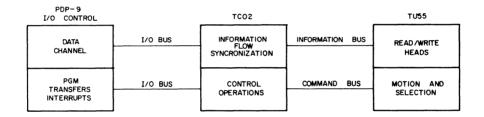

| 1-1 | System Configuration                               | 1-1  |

|-----|----------------------------------------------------|------|

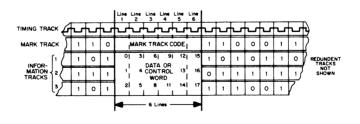

| 2-1 | Basic Six Line Tape Unit                           | 2-1  |

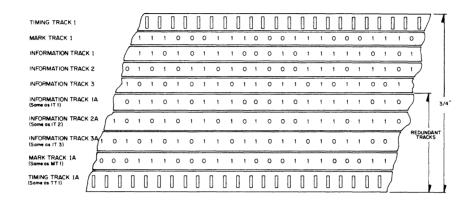

| 2-2 | Track Allocation Showing Redundantly Paired Tracks | 2-3  |

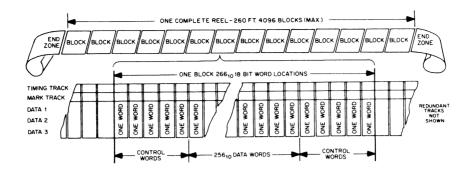

| 2-3 | Control and Data Word Assignments                  | 2-4  |

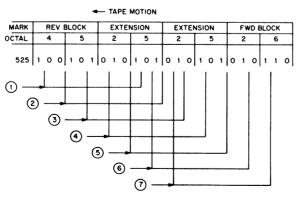

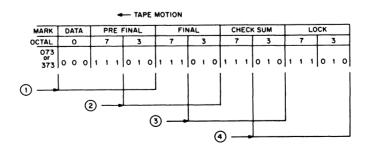

| 2-4 | Mark – Track Format                                | 2-5  |

| 2-5 | Status A Register, Format                          | 2-9  |

| 2-6 | Status B Register, Format                          | 2-10 |

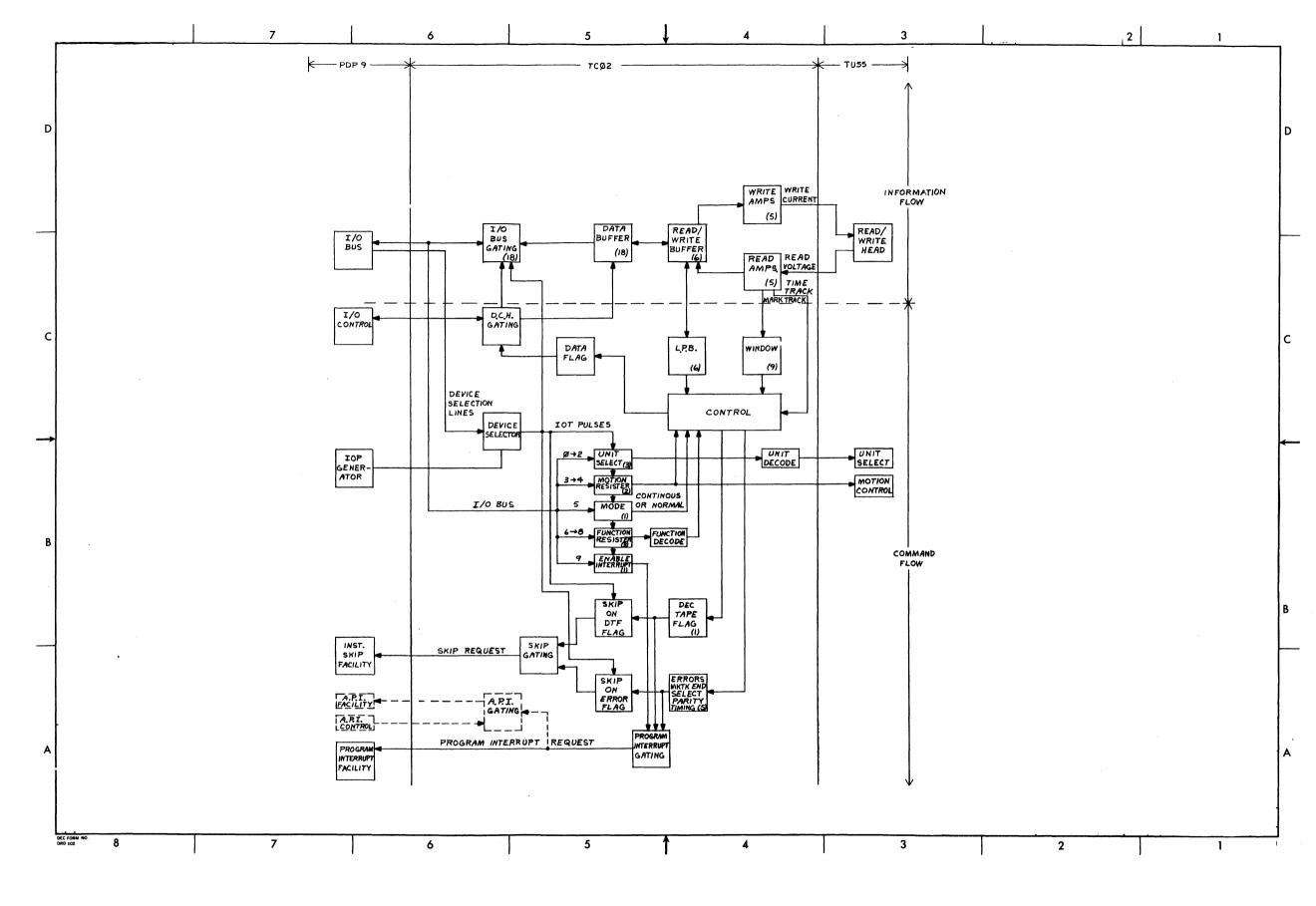

| 3-1 | Information and Command Flow                       | 3-1  |

| 3-2 | Type TC01 DECtape Control Functional Block Diagram | 3-3  |

## ILLUSTRATIONS (cont.)

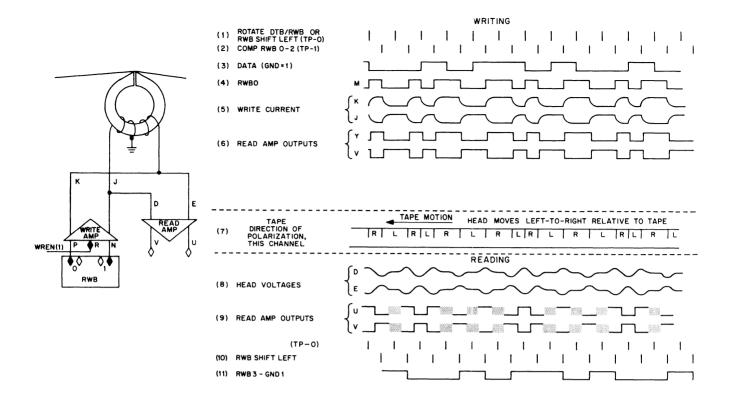

| 3-3           | Read/Write Logic and Waveforms                     | 3-12 |

|---------------|----------------------------------------------------|------|

| 3-4           | Mark – Track Decoding (C-SYNC)                     | 3-18 |

| 3-5           | Mark – Track Decoding (MK BLK MK)                  | 3-20 |

| 3-6           | Mark – Track Decoding (MK BLK START –210)          | 3-20 |

| 3-7           | Mark – Track Decoding (MK BLK START –010)          | 3-21 |

| 3-8           | Mark – Track Decoding (MK DATA 070)                | 3-21 |

| 3-9           | Mark – Track Decoding (MK BLK END)                 | 3-21 |

| 3-10          | Error Check Flow Diagram                           | 3-35 |

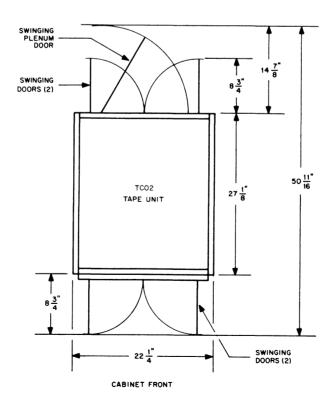

| 4-1           | TC02 Unit Single Cabinet Installation Dimensions   | 4-1  |

| 4-2           | TC02 Control, Cable Diagram                        | 4-3  |

| 5-1           | Maintenance Control Panels (Switch and Indicators) | 5-2  |

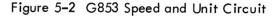

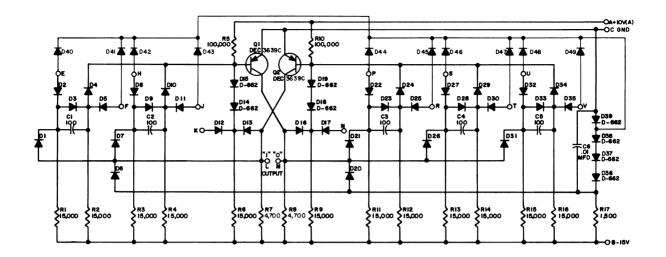

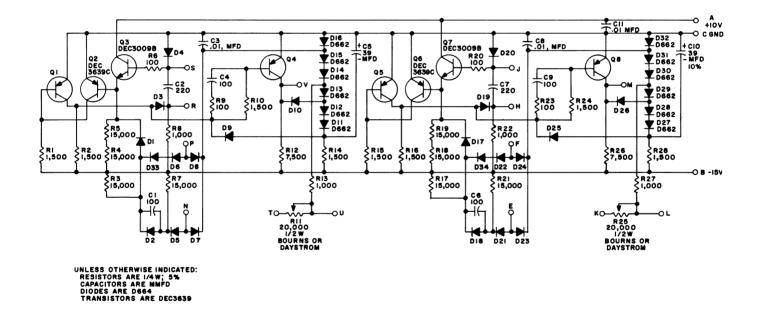

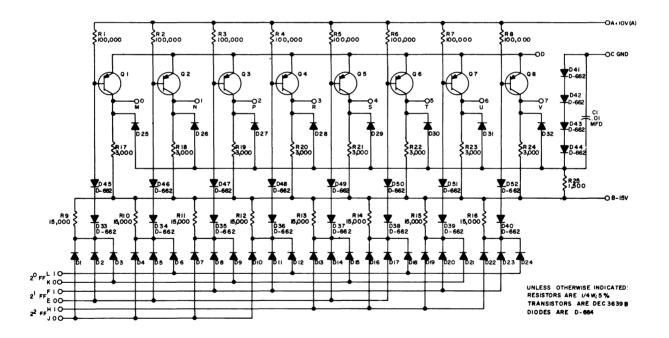

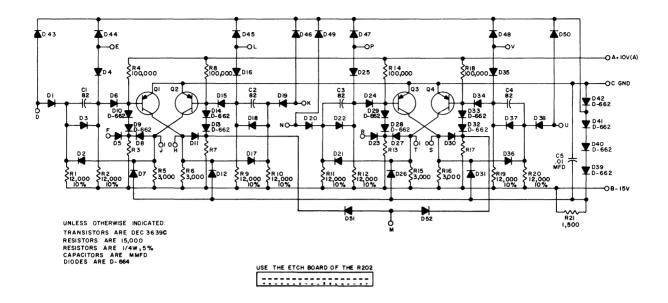

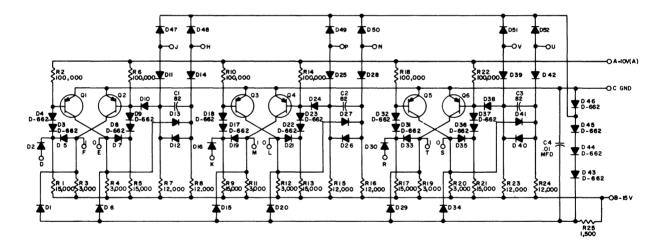

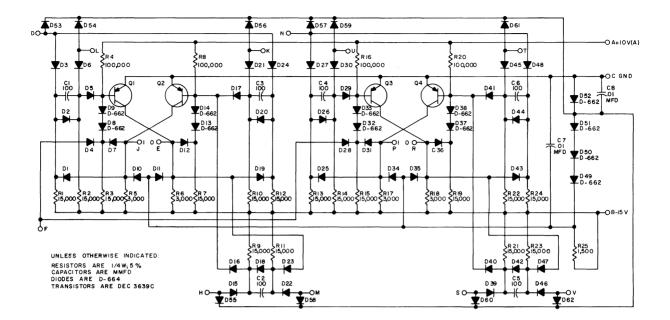

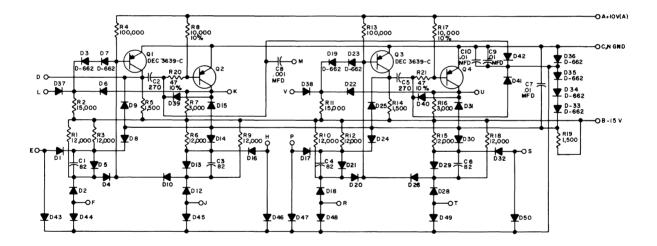

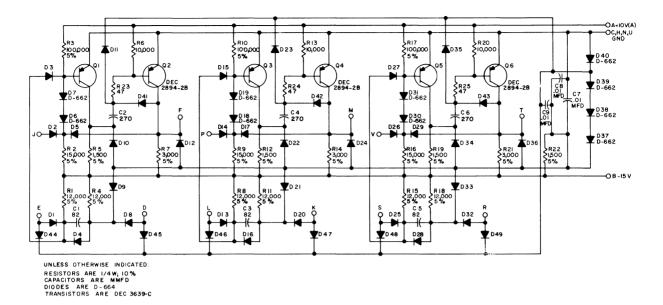

| 5-2           | G853 Speed and Unit Circuit                        | 5-6  |

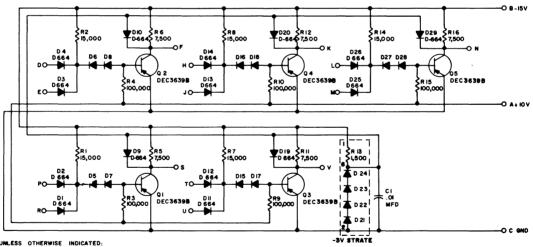

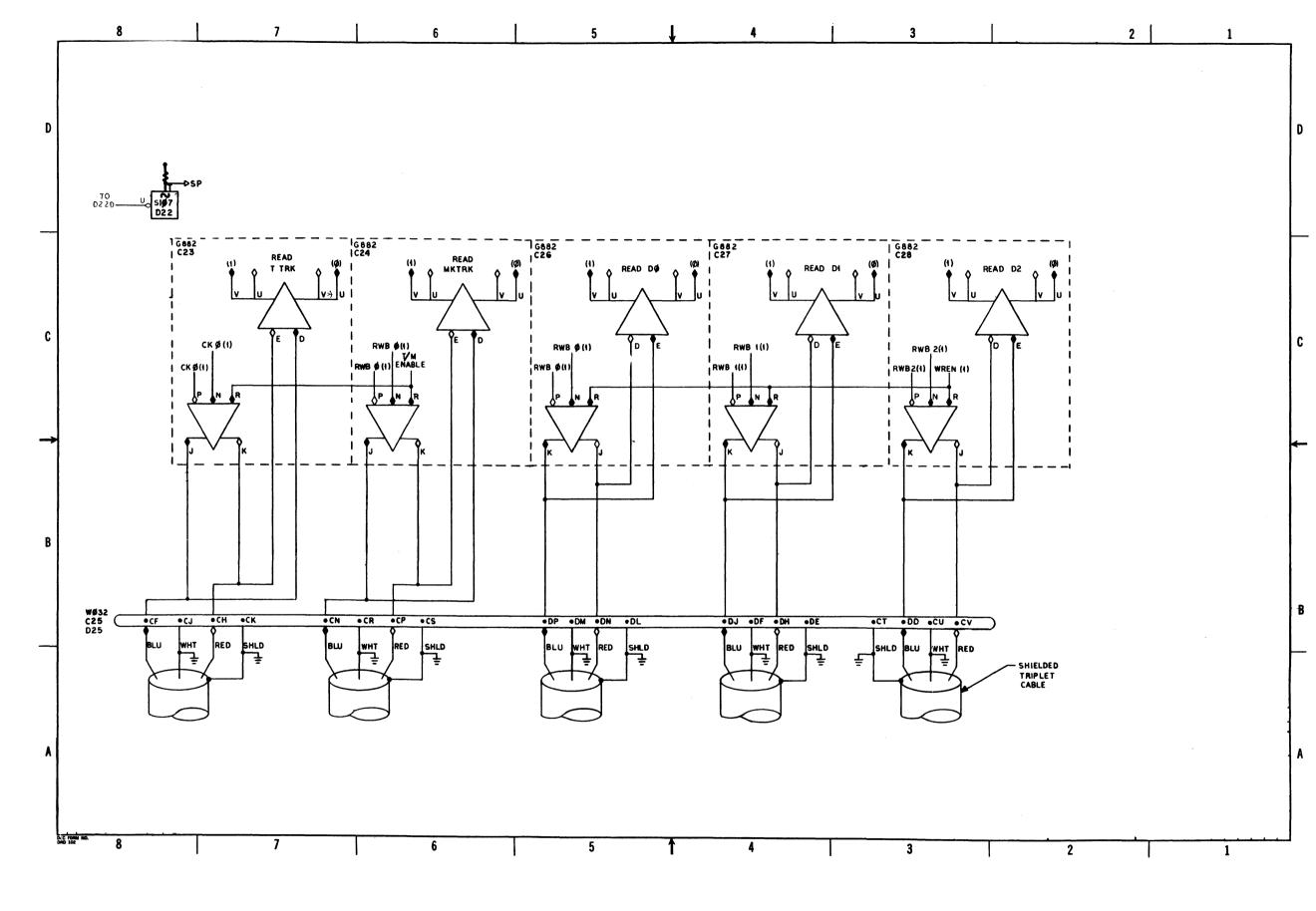

| 5-3           | G882 Manchester Read/Write Amplifier               | 5-7  |

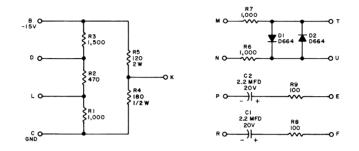

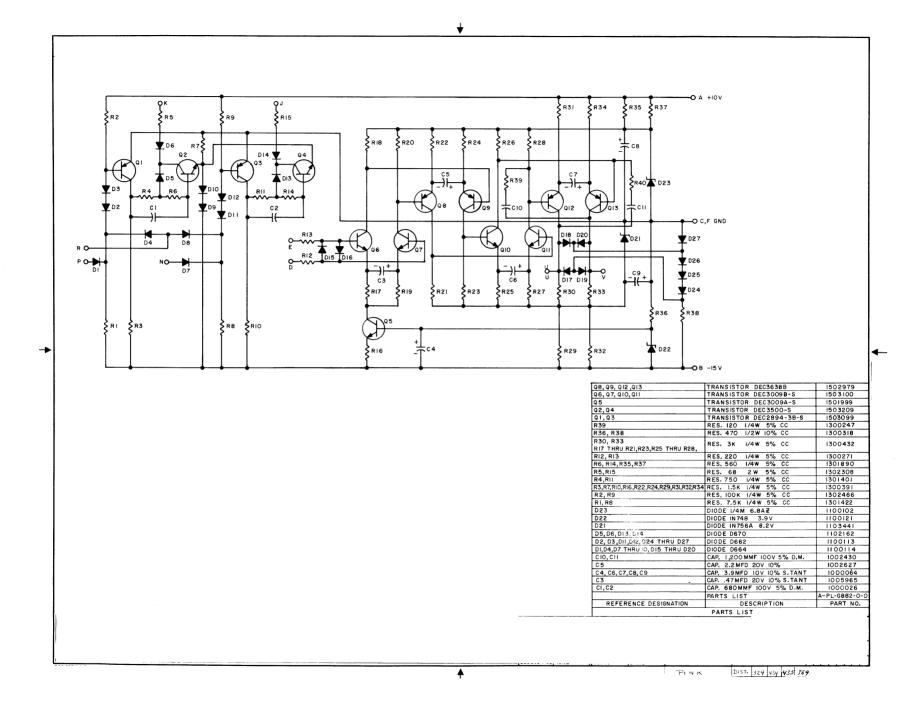

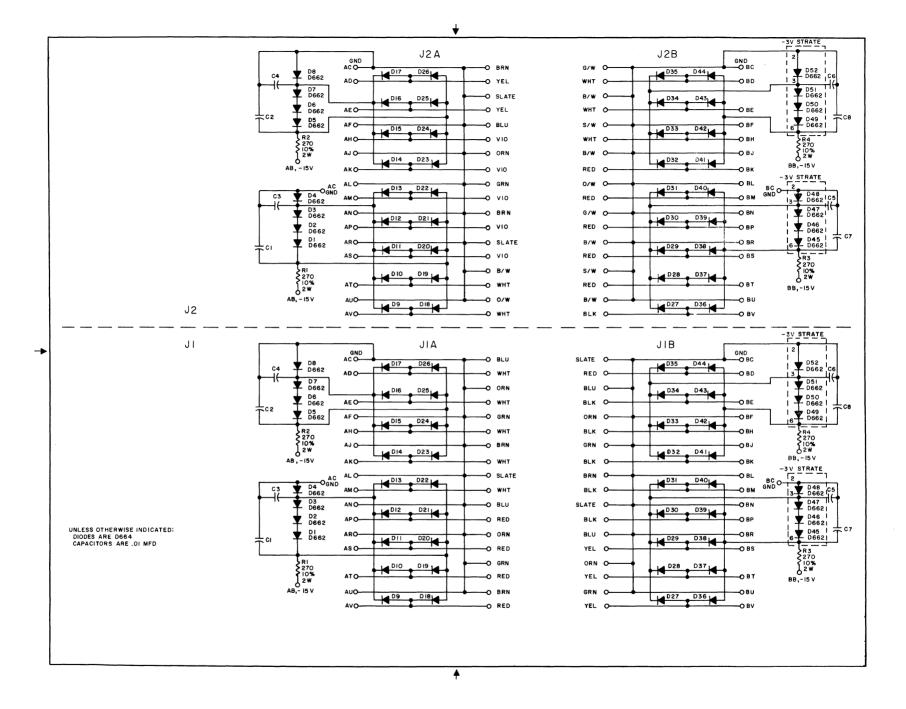

| 5-4           | R002 Diode Network                                 | 5-8  |

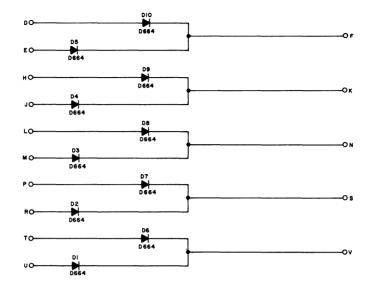

| 5-5           | R113 Diode Gate                                    | 5-8  |

| 5-6           | R201 Flip-Flop                                     | 5-9  |

| 5 <b>-</b> 7  | R302 Delay (One-Shot)                              | 5-9  |

| 5-8           | R303 Integrating One-Shot                          | 5-10 |

| 5-9           | R401 Variable Clock                                | 5-10 |

| 5-10          | S107 Inverter                                      | 5-11 |

| 5-11          | S111 Diode Gate                                    | 5-11 |

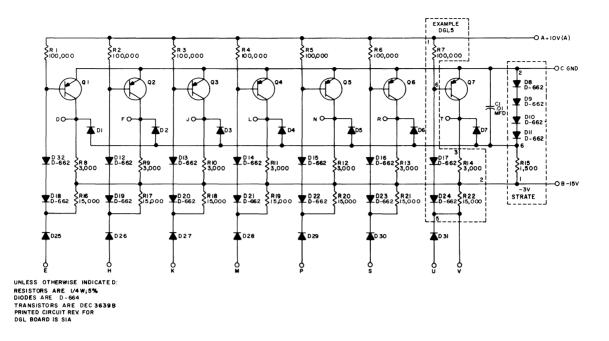

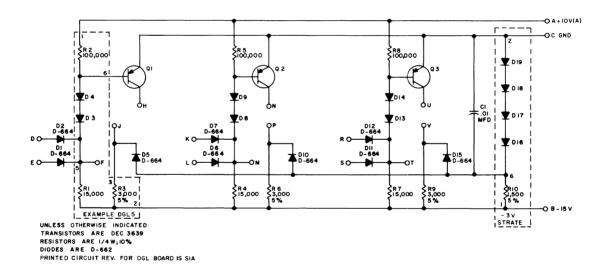

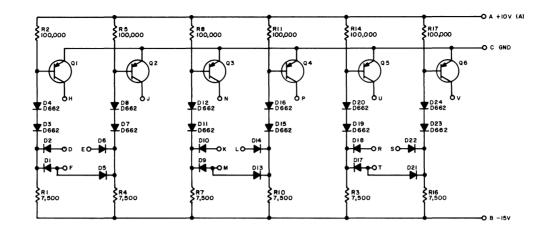

| 5-12          | S123 Diode Gate                                    | 5-12 |

| 5-13          | S151 Binary-to-Octal Decoder                       | 5-12 |

| 5-14          | S202 Dual Flip-Flop                                | 5-13 |

| 5 <b>-</b> 15 | S203 Triple Flip-Flop                              | 5-13 |

| 5-16          | S205 Dual Flip-Flop                                | 5-14 |

| 5-17          | S602 Pulse Amplifier                               | 5-14 |

| 5-18          | S603 Pulse Amplifier                               | 5-15 |

| 5-19          | W018 Connector Board                               | 5-15 |

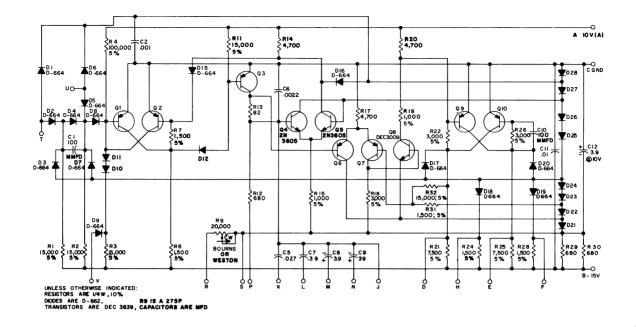

| 5-20          | W103 PDP-9 Device Selector                         | 5-16 |

| 5-21          | W104 PDP-9 I/O Bus Module                          | 5-17 |

## ILLUSTRATIONS (cont.)

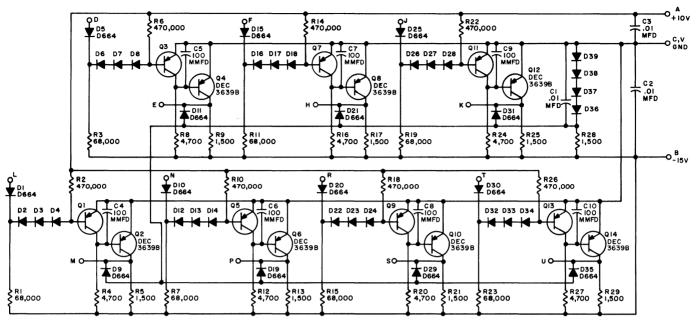

| 5-22 | W107 High Impedance Follower             | 5-19 |

|------|------------------------------------------|------|

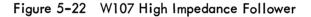

| 5-23 | W520 Comparator                          | 5-19 |

| 5-24 | W850 I/O Cable Connectors                | 5-20 |

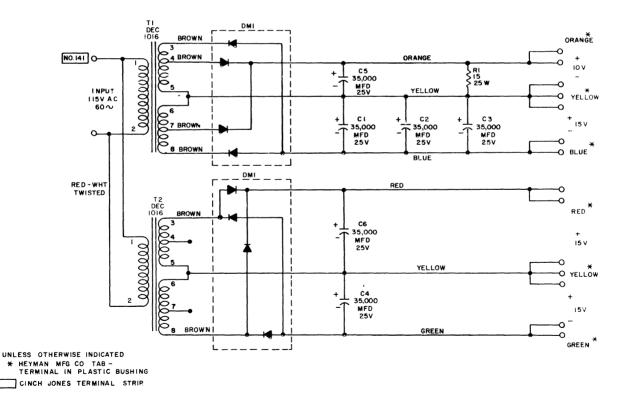

| 5-25 | Power Supply Type 779, Schematic Diagram | 5-21 |

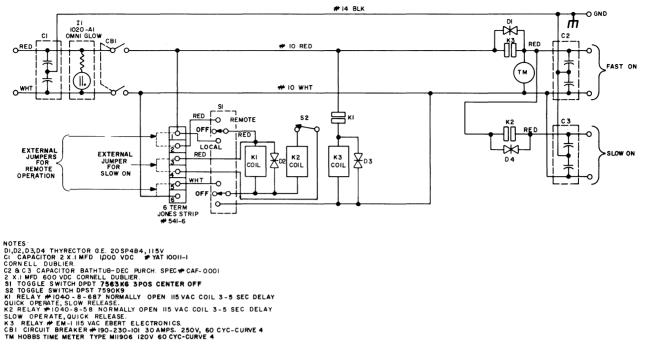

| 5-26 | Power Control Panel Type 832F            | 5-24 |

#### CHAPTER 1 INTRODUCTION AND DESCRIPTION

The Type TCO2 DECtape Control, manufactured by Digital Equipment Corporation, is a synchronizing and controlling unit used for transfer of information between Programmed Data Processor PDP-9\* and the TU55 DECtape Transport.

The DECtape system, consisting of the TC02 control and up to eight TU55 transports, is a magnetic tape storage facility that stores information at fixed positions on magnetic tape, as in magnetic disc or drum storage devices; rather than at unknown or variable positions, as in conventional magnetic tape systems. This feature allows the replacement of blocks of data on tape in an ordered fashion without disturbing previously recorded information. In particular, during the writing of information on tape, the system reads format (mark) and timing information from the tape and uses this information to determine the exact position at which to record the information to be written. Similarly, in reading, the same mark and timing information is used to locate data to be played back from the tape.

A typical system (Figure 1–1) consists of a PDP-9, one TC02, and up to eight TU55 transports (only one transport can be selected at a time).

The levels of discussion in this manual assumes that the reader has previous knowledge of both the PDP-9 processor and the TU55 DECtape Transport. This manual includes references to the support – ing documents listed in Table 1–1.

Figure 1-1 System Configuration

#### 1.1 PURPOSE AND SCOPE

This manual describes the DECtape Transport Control TC02, includes maintenance information in a form for easy use and quick reference, and is the major reference covering the TC02 control. Detailed explanations of standard products, such as modules, PDP-9 processor, and TU55 are contained in the standard documents for these products.

<sup>\*</sup> PDP is the registered trade mark for the programmed data processors manufactured by Digital Equipment Corporation, Maynard, Massachusetts.

#### 1.2 EQUIPMENT DESCRIPTION

The TCO2 DECtape control logic occupies three Flip-Chip mounting panels. A maintenance control panel (Figure 5-1) occupies the right-hand half of the upper mounting panel. This panel is covered during normal programmed operations.

The TCO2 is mounted one mounting panel space up from the bottom of the cabinet, and a maximum of four TU55 transport units can be mounted above the TCO2 in the same cabinet. (Additional units must be mounted in another cabinet.)

The standard DEC computer has double doors on front and rear. Power supplies and power controls are mounted inside the rear double doors on a full-width plenum door latched by a spring loaded pin at the top. Module mounting panels are mounted behind the double door in front with the wiring side facing outward. Fans at the bottom of the cabinet provide filtered cooling air. The rear plenum door has blank panels in space not occupied by components. The TCO2 and associated DECtape TU55 Transports receive power from the Type 779 Power Supply and the Type 832F Power Control.

#### 1.2.1 Physical Characteristics

| Dimensions                   |                                                                                                                                                     |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TC02 Control:                | 15-3/4 in. high, 19 in. wide                                                                                                                        |  |  |

| TU55 Transport:              | 10-1/2 in. high, 19-1/2 in. wide, 9-3/4 in. deep                                                                                                    |  |  |

| Cabinet:                     | 69-1/8 in. high, 22-1/4 in. wide, 27-1/6 in. deep                                                                                                   |  |  |

| Weight                       |                                                                                                                                                     |  |  |

| TC02:                        | 30 lb                                                                                                                                               |  |  |

| TU55:                        | 65 lb (rack mounted)                                                                                                                                |  |  |

| Cabinet:                     | 620 lb (with maximum equipment mounted)                                                                                                             |  |  |

| Power Requirement            |                                                                                                                                                     |  |  |

| TC02:                        | 115V, 60 cps, 4A. A Type 832F Power Control and a<br>Type 779 Power Supply are included with the TC02<br>Control (N9M transformer used for 50 cps). |  |  |

| TU55 Transport:              | 115V ±10%, 60 cps, 2A maximum, 1.5A idle                                                                                                            |  |  |

| Cabinet:                     | 115V, 60 cps cource capable of delivering 20A                                                                                                       |  |  |

| Tape Characteristics         |                                                                                                                                                     |  |  |

| Reel capacity:               | 260 ft of 0.75 in., 1 mil thick Mylar tape (empty reel:<br>2-3/4 in. diameter; loaded reel: 3-3/4 in. diameter)                                     |  |  |

| Density:                     | $350 \pm 55$ lines per in.                                                                                                                          |  |  |

| Motion:                      | Bidirectional                                                                                                                                       |  |  |

| Addressable blocks per reel: | 1100 <sub>8</sub> (576 <sub>10</sub> )18-bit words in blocks of 256 <sub>10</sub> words                                                             |  |  |

#### Word Transfer Rate

One tape line is read or written every 33-1/3 µs. An 18-bit word is read and assembled or disassembled and written in 200 µs. In reverse direction, the transfer rate varies by 30% as the effective reel diameter changes.

#### Addressing

Mark and timing tracks allow searching for a particular block.

| Start time:       | 375 ms approximate |

|-------------------|--------------------|

| Stop time:        | 375 ms approximate |

| Turn around time: | 375 ms             |

Input Signals to Transport from Control

| Commands:    | FORWARD, REVERSE, GO, STOP, ALL HALT       |

|--------------|--------------------------------------------|

| Unit select: | Select unit 1 through 8                    |

| Information: | Analog write signals to the recording head |

Output Signal from Transport to Control

| Control:     | WRITE ENABLE                            |

|--------------|-----------------------------------------|

| Information: | Analog read signals from recording head |

Environmental Conditions

| Thermal Dissipation:   | 2000W                        |

|------------------------|------------------------------|

| Operating Temperature: | 50° to 90°F ambient          |

| Humidity:              | 10% – 90% relative humidity* |

#### 1.3 SYSTEM DESCRIPTION

The TC02 consists of tape control logic, which under direction of the PDP-9, controls the operation of up to eight TU55 DECtape Transports. The TC02 transfers data between the PDP-9 core memory and the selected tape transport. To transfer data, the TC02 uses the data channel facility of the PDP-9; the WC (word count) register specifies the record length, the CA (current address) register specifies the core memory address of the data transfer.

During both input and output operations, the TC02 receives data and control information from the processor and generates the appropriate signals for the selected transport to execute the programmed commands. Binary information is transferred between the tape transport and the computer as one 18-bit

<sup>\*</sup> Tape manufacturer recommends 60°F - 80°F and 40% - 60% relative humidity for best tape performance.

computer word every 200 µs. In writing the TC02 disassembles the 18-bit computer word into six successive 3-bit words to be written on tape. During reading, the TC02 assembles six successive 3-bit words into an 18-bit computer word. Transfer of an 18-bit word always occurs in parallel. As the start and end of each block are detected, the TC02 generates a DECtape control flag signal (DTCF) to cause a program interrupt in the computer.

The program interrupt is used by the computer program to determine the block number. When it determines that the next block is the one selected for transfer, it selects the read or write control function. Each time a word is assembled, or DECtape is ready to receive a word from the computer, the control produces a data flag (DF) to request a data break. Therefore, when each 18-bit computer word is assembled the data break initiates a transfer. By using the mark-track decoding circuits and the data break facility, the main computer program can continue during tape operation.

#### 1.4 REFERENCED DOCUMENTS

The DEC documents listed in Table 1-1 contain material which supplements the information in this manual. These documents may be obtained from DEC field offices or from the main office in Maynard, Massachusetts.

| Document<br>No. | Title                    | Description                                                                                                |

|-----------------|--------------------------|------------------------------------------------------------------------------------------------------------|

| C105            | Digital Logic Handbook   | Specifications and descriptions of the FLIP-<br>CHIP modules.                                              |

| C100            | System Modules           | Specifications and descriptions of basic system modules and power supplies.                                |

| F95             | PDP-9 Users Handbook     | Programming and operating information for<br>the computer including brief instructions on<br>TC02 control. |

| F97             | PDP-9 Maintenance Manual | Complete information on the internal opera-<br>tion of PDP-9 logic, memory, basic in/out,<br>and options.  |

| H- TU55         | TU55 Maintenance Manual  | Transport drive logic and internal operations.                                                             |

Table 1–1 DEC Documents

In addition to the documents listed in Table 1-1, a complete set of library programs are available.

#### CHAPTER 2 OPERATION AND PROGRAMMING

This chapter contains information required for operation and programming of the TC02. Included are a description of the format of information on the DECtape magnetic tape, and the modes of operation used in programming TC02 operations. General operating information for TU55 transport is contained in the TU55 Maintenance Manual.

#### 2.1 DECTAPE SYSTEM

DECtape uses a 10-track read/write head. Tracks are arranged in five nonadjacent redundant channels: a timing channel, a mark channel, and three information channels. Redundant recording of each character bit on nonadjacent tracks materially reduces bit dropout and minimizes the effect of skew. Series connection of corresponding track heads within a channel and the use of Manchester phase recording techniques, rather than amplitude sensing techniques, virtually eliminate dropouts.

The timing and mark channels control the timing of operations within the TC02 control unit and establish the format of data contained on the information channels. The timing and mark channels are recorded prior to all normal data reading and writing on the information channels. The timing of operations performed by the tape drive and some control functions are determined by the information on the timing channel. Therefore, wide variations in the speed of tape motion do not affect system performance. Information read from the mark channel is used during reading and writing data, to indicate the beginning and end of data blocks and to determine the functions performed by the system in each control function.

During normal data reading, the TC02 control assembles 18-bit computer length words from six successive lines read from the information channels of the tape (Figure 2-1). During normal data writing, the control disassembles 18-bit words and distributes the bits so they are recorded on six successive lines on the information channels. A mark channel error check circuit assures that one of the permissible marks is read in every six lines on the tape.

Figure 2-1 Basic Six Line Tape Unit

A tape contains a series of data blocks that can be of any length which is an even number of 18-bit words. Block length is determined by information on the mark channel. Usually a uniform block

length (256<sub>10</sub> for the PDP-9) is established over the entire length of a reel of tape by a program which writes mark and timing information at specific locations. The ability to write variable-length blocks is useful for certain data formats. For example, small blocks containing index or tag information can be alternated with large blocks of data. The maximum number of blocks addressable is 4096.

Between the blocks of data are areas called interblock zones. The interblock zones consist of 30 lines on tape before and after a block of data. Each of these 30 lines is divided into five 6-line control words.

Block numbers normally occur in sequence from 1 to N. There is one block numbered 0 and one block N + 1. The total length of the tape is equivalent to 849,036 lines which can be divided into any number of blocks up to 4096 by prerecording of the mark track. Normally,  $576_{10}$  blocks of  $256_{10}$  words each are prerecorded for PDP-9 DECtape.

#### 2.2 DECTAPE CONTROL TC02

A maximum of eight TU55 transports can be connected to a TC02. Of the PDP-9 data channels available, DECtape is assigned to channel 0 (core memory locations 30 and 31).

> C(30) = Word Count (in 2s complement form)-WC C(31) = Current Address Register - CA

Data transfers can take place to or from only one transport at a time at a rate of one word every 200  $\mu$ s (1 block of 256<sub>10</sub> words every 53 ms), after the desired block has been found. Since the CA is incremented before the data transfer (except in search where the CA is not incremented), the initial contents should be set to the desired initial address minus one. The WC is also incremented before each transfer and must be set to the 2s complement of the desired number of data transfers. In this way, the word transfer which causes the word count overflow is the last transfer to take place.

The number of IOTs (input/output transfer commands) required for the TC02 is minimized by transferring all required control data (unit, function, mode, direction, etc.) from the accumulator (AC) to the control using one set of IOTs, and similarly, transferring all status information (the above plus status bits, error flags, etc.) into the AC from the control by a second set of IOTs.

To provide for automatic parity checking during the READ DATA function, a 6-bit parity check character is computed and recorded by the DECtape control for every block recorded during the Write Data function. The 6-bit parity check character is computed by the complement of the exclusive OR (logical equivalence) of the reverse parity check character and every six bits of every data word.

#### 2.3 DECTAPE FORMAT

The format of the DECtape is shown in Figure 2–2 and provides 10 tracks, 5 tracks redundantly recorded; i.e., three pair of tracks for data and two pair for timing and mark information. A 10-track recording head reads and writes the five duplexed channels.

The prerecorded timing track synchronizes read/write operations. The location of the timing tracks along the edges of the tape permits strobing on the analog sum of the timing track signals

(minimizing tape skew effect) and thus reading the data tracks when they are in the most favorable position. The location of the data tracks in the middle of the tape also minimizes skew effect.

Figure 2-2 Track Allocation Showing Redundantly Paired Tracks

Data is recorded by the Manchester method in which a prerecorded timing track synchronizes read/write operations. When writing on the tape, the write amplifiers supply the maximum current in either one direction or the other (non-return to zero, NRZ). To write a pulse, the polarity of the write current is reversed, and the polarity of the pulse that is produced depends on whether the write current underwent a positive or negative transition. The timing track is prerecorded with alternate positive and negative transitions at fixed time intervals. The negative transition is used only during writing and is a signal to load the write buffer. The positive transition is used during both reading and writing. During writing, this transition is a signal to switch the polarity of the write current in all write heads. If a ZERO is being written, the current, which starts out positive for writing ZEROs, is switched to negative transition when switched to positive. During reading, the positive transition of the timing track is a signal to strobe the data and mark track read-amplifier outputs into the read buffer. If a positive transition is sensed at strobe time, a ONE is placed in the buffer; otherwise a ZERO is strobed in.

Because the strobe is a relatively narrow pulse, the system is not affected by noise outside the strobe time. At strobe time, all data signals are negative pulses representing ZEROs or positive pulses representing ONEs. These pulses are all at their peaks. To have any effect, a noise pulse must be large enough to reverse the polarity of a data pulse. Data can be written immediately adjacent to previously written data because the timing is controlled by the timing track that is written on the tape.

Information is stored on the tape in block form (Figure 2-3). Block length is flexible and determined by information on the mark-track. A complete reel of tape (849,036 lines) can be divided into any number of blocks up to 4096. As stated earlier, a uniform block length is established over the entire length of a reel of tape by a program which writes mark and timing information at specific locations. The ability to write variable-length blocks, however, is useful for certain formats, for example, where small blocks containing index or tag information need to be alternated with the large blocks of data.

Figure 2-3 Control and Data Word Assignments

Each block contains data and control words as shown in Figure 2-3. These of course are assembled by the TCO2. Control words separate the data portions of adjacent blocks and record address and checking information. Each control or data word occupies six lines on tape, i.e., 18 bits (see Figure 2-1).

#### 2.3.1 Mark – Track Format

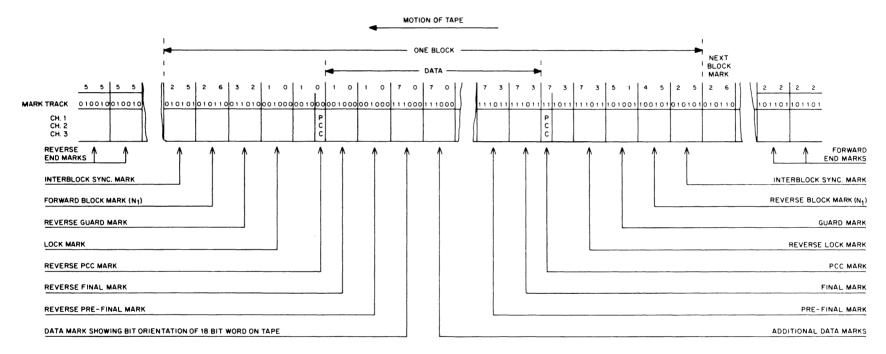

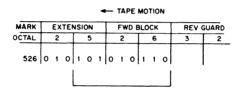

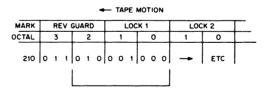

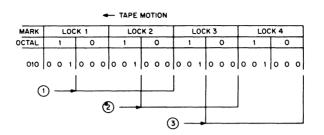

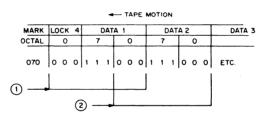

One of the five DECtape channels is reserved for control information exclusively. The control codes are stored serially, six bits per code. The mark track contains these 6-bit codes (see Figure 2-1), which initiate controls to raise flags in the program, request data breaks, detect block mark numbering and block ends, and protect control portions of tape (see Figure 2-4). The TCO2 automatically identifies these codes to control transmission of data. The mark track also provides for automatic bidirectional compatibility, variable block formatting, and end-of-tape sensing.

During all tape processing functions except recording of the timing and mark track, a single mark-track bit is read from each line of tape, regardless of whether the information is being read from or written onto the data tracks; and each tape line in both the information and mark tracks is positioned at the center of the right polarization in the timing track, as shown in Figure 2-1. The six lines on the tape that contain the mark code in the mark track are designated as a mark frame.

A given change of polarization on tape read in one direction produces a pulse opposite in polarity to that produced by the same change when tape is read in the opposite direction. Consequently, a mark code read in reverse of the direction in which it was recorded has the order of bits reversed and the bits complemented. For example, a mark code read forward as 100101 is read as 010110 in reverse. This correspondence is termed the complement obverse or the complement image. Every 6-bit code has one and only one complement obverse which is constructed by complementing all bits and reversing their order. Therefore, the complement obverse of the complement obverse is the original code itself. In octal notation, the complement obverse of any pair of digits is constructed by reversing the order of digits, then performing the following transformation on each:

0 - 7 1 - 3 2 - 5 3 - 1 4 - 6 5 - 2 6 - 4 7 - 0

PCC = 6 BIT PARITY CHECK CHARACTER (HARDWARE COMPUTED)

.

The transformations indicate that there are eight octal codes which are their own complement obverses: 07, 13, 25, 31, 46, 52, 64, and 70. All other possible combinations of two octal digits (there are 56) are different from their complement obverses. As shown in Table 2-1, the complement obverse of any mark is designated by the minus sign (e.g., mark G = 51 has the complement obverse -G = 32).

Since the DECtape system allows reading and writing in both directions of tape motion, the mark track must be coded to present the same information when entering a block from either direction. The marks at the end of a block are the complement obverses of the marks at the beginning, in reverse order. For example, if the control reads the marks E, M, -G as the first three marks beginning a block in forward motion, then it will read G, -M, -E, in that order, as the last three marks of the same block. In reverse motion, however, the control sees the complement obverse of the contents of the mark track; thus the first information, when reading the block in reverse, is -(-E), -(-M), -(G), which is identical to E, M, -G.

All marks used in the standard DECtape format are listed in Table 2-1. Only 10 valid codes exist even though a given code may have different designations. Some of these marks are not required for the operation of the Type TC02 DECtape control.

| Mark               | Octal Code | Function                                                                                                                                                                                                                              |

|--------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C (Check)          | 73         | Signifies the end of a mark frame whose first two lines were the forward parity check group.                                                                                                                                          |

| -C (Reverse Check) | 10         | Signifies that the 6-bit reverse longitudinal parity<br>check group is contained in the control unit read/<br>write buffer and that the beginning of the data por-<br>tion of a block is in the forward direction.                    |

| E, -D (Data)       | 70         | In both forward and reverse tape motion, the data<br>mark occupies all mark frames in the data portion of<br>the block except for the final and prefinal marks.<br>The number of data marks is limited only by the<br>length of tape. |

| E, (Interblock)    | 25         | The first and last mark of every block (no-op mark).                                                                                                                                                                                  |

| End (Forward End)  | 55         | Indicates the end zone of tape in forward direction.<br>The forward end mark is positioned approximately<br>10 ft from actual tape end.                                                                                               |

| -END (Reverse End) | 22         | Indicates the end zone of tape in reverse direction.<br>The reverse end mark is positioned approximately<br>10 ft from end of tape.                                                                                                   |

| F (Final)          | 73         | Signifies that the last word read from the data portion<br>of the block is in the read/write buffer and data<br>buffer. Signals that the next frame begins with the<br>6-bit forward longitudinal parity check group.                 |

| -F (Reverse Final) | 10         | Signifies that the last word read from the block, in the reverse direction, is in the read/write buffer and data buffer.                                                                                                              |

Table 2 – 1 Mark Track Coding

| Mark                  | Octal Code | Function                                                                                                                                                           |

|-----------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G (Guard)             | 51         | Performs same function as -L (reverse lock).                                                                                                                       |

| -G (Reverse Guard)    | 32         |                                                                                                                                                                    |

| L (Lock)              | 10         | Indicates the first of four octal 10 marks.                                                                                                                        |

| -L (Reverse Lock)     | 73         | Protects subsequent records in the event of mark-track errors.                                                                                                     |

| M (Forward Block)     | 26         | Signifies the start of a block and indicates that the block number is contained in the TC02 control.                                                               |

| -M (Reverse Block)    | 45         |                                                                                                                                                                    |

| P (Prefinal)          | 73         | In the forward tape direction, the prefinal mark is the<br>next to last mark in the data portion of a block. It<br>is the first of four marks using octal code 73. |

| -P (Reverse Prefinal) | 10         | In the reverse tape direction, signifies the next to last mark in the data portion of a block.                                                                     |

Table 2–1 (Cont) Mark Track Coding

The standard mark track uses the serial code of 6-bit characters to divide the tape into words. Codes are written on the mark track opposite word locations to identify the type of information stored at that location on tape. Block addresses are written for both forward and reverse directions and identified by two types of mark codes (the second is the complement obverse of the first). A checksum is written at each end of the block. The hardware computed checksum is the 6-bit logical equivalent (i.e., the complement of the exclusive OR) of each six bits written on tape plus the reverse checksum previously recorded. By including the reverse checksum in the computation, the block may be read in either direction at a later time without an error. The control uses the final marks to establish synchronism and raise block-end flags. Data marks locate data words.

## 2.4 DECTAPE INSTRUCTIONS

The seven basic IOT instructions used in the programming of the PDP-9 for TC02 operations are listed in Table 2-2, with octal code assignments and a description of the instruction operation. These instructions apply to two functional groups within the TC02, designated as status A and status B, and are used to clear, read, and load the status A and B registers. These two registers are used to govern tape operations and provide status information to the computer programs.

| Mnemonic | Octal Code | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTCA     | 707541     | Clear status A register. The DECtape control and error flags are undisturbed (DTF and EF).                                                                                                                                                                                                                                                                                                                                                |

| DTRA     | 707552     | Read status A register. The AC is cleared and the content of status A register is ORed into the accumulator.                                                                                                                                                                                                                                                                                                                              |

| DTXA     | 707544     | XOR status A register. The exclusive OR of the content of<br>bits 0 through 9 of the accumulator and status A is loaded<br>into status A register, and bits 10 and 11 of the accumulator<br>are sampled to control clearing of the error and DECtape<br>flags, respectively. Any time this command is given with<br>AC bits 0 through 4 set to 1, the select delay of 120 ms will<br>be incurred, while the new mechanical motion begins. |

| DTLA     | 707545     | Load status A register. Combines action of DTCA and DTXA<br>to load AC0 through 9 into status A register. Bits 10 and 11<br>control clearing of error and DECtape flags, respectively.                                                                                                                                                                                                                                                    |

| DTEF     | 707561     | Skip on error flag. The state of the error flag (EF) is sampled<br>If it is set to 1 the content of the PC is incremented by one<br>to skip the next sequential instruction.                                                                                                                                                                                                                                                              |

| DTRB     | 707572     | Read status B. The AC is cleared and the content of status B is ORed into the accumulator.                                                                                                                                                                                                                                                                                                                                                |

| DTDF     | 707601     | Skip on DECtape flag. The state of the DECtape flag (DTF)<br>is sampled. If it is set to a 1, the content of the PC is<br>incremented by one to skip the next sequential <u>instruction</u> .                                                                                                                                                                                                                                             |

Table 2–2 TC02 DECtape Instruction List

#### 2.5 STATUS A AND B REGISTERS

All 10 command bits (0 through 9) of status A register may be sensed, set, or changed via IOTs. Bits 10 and 11 of the AC are not retained by status A but enable or disable the clearing of the DECtape and ERROR flags. The bits in status B register may be sensed and cleared by IOTs.

To issue a DECtape command, the command bits 0 through 9 of status A register are set as desired by bits 0 through 9 of the AC with bits 10 and 11 set to 0. Bit 11 of B register is set when a DTF occurs and must be cleared before the next DTF to avoid a timing error. When any error occurs, bit 0 of B register and the corresponding bits 1 through 5 will be set depending on the error. This bit must be cleared to avoid further interrupts on the same condition. All error flags (status B register) are cleared by issuing a DTXA instruction with AC bit 10 set to 0.

#### 2.5.1 Status A Register Functions

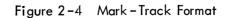

Figure 2-5 is the format for the status A register. This register contains three unit select bits, two motion bits, one mode bit, three function bits and three bits which control the flags. The bit assignments for the status A register are provided in Table 2-3.

Figure 2-5 Status A Register, Format

.

| Function              | AC Bit | Conditions                                                                                                                                                                                                              |

|-----------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transport Unit Select | 0-2    | Octal Code         Unit           000         8           001         1           010         2           011         3           100         4           101         5           110         6           111         7 |

| Motion                | 3      | 0 = Forward (FWD)<br>1 = Reverse (REV)                                                                                                                                                                                  |

|                       | 4      | 0 = Stop motion (STOP)<br>1 = Start motion (GO)                                                                                                                                                                         |

| Mode                  | 5      | 0 = Normal mode (NM)<br>1 = Continuous mode (CM)                                                                                                                                                                        |

| Function              | 6,7,8  | Octal CodeOperation000Move001Search010Read data011Read all100Write data101Write all110Write timing and mark track111Unused (causes select error)                                                                        |

| Enable the interrupt  | 9      | 1 = Enable DECtape control flag DTF and<br>EF to cause program interrupt                                                                                                                                                |

| Error flag            | 10     | 0 = Clear all error flags<br>1 = Error flags undisturbed                                                                                                                                                                |

| DECtape flag          | 11     | 0 = Clear DECtape flag<br>1 = DECtape flag undisturbed                                                                                                                                                                  |

Table 2–3 Status A Bit Assignments

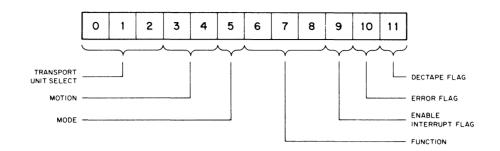

## 2.5.2 Status B Register Functions

Figure 2-6 shows the format of the information in the status B register. This register contains 6 bits of error status information, and the DECtape flag bit. Table 2-4 lists the function of the bit assignments.

Figure 2-6 Status B Register, Format

|        | Ta | ble | 2-4        |

|--------|----|-----|------------|

| Status | Β, | Bit | Assignment |

| Function                      | ÁC Bit | Conditions                                                                                                                                                                                                                                   |  |

|-------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Error Flag (EF)               | 0      | <ul> <li>1 = Detection of any nonoperative condition by the<br/>control as listed in the error functions described in AC<br/>bits 1 through 5 of this table. These conditions stop<br/>transport motion except for parity errors.</li> </ul> |  |

| Mark – Track Error<br>(MKTRK) | 1      | I = Information read from mark track is erroneously<br>decoded.                                                                                                                                                                              |  |

| End of Tape Error<br>(END)    | 2      | 1 = the end zone on either end of tape is over the read head.                                                                                                                                                                                |  |

| Select Error (SE)             | 3      | This error occurs 5 µs after loading status A register to indicate one or more of the following conditions.                                                                                                                                  |  |

|                               |        | <ul> <li>(a) The unit select code specified does not correspond<br/>to any transport select number or is set to more than<br/>one transport.</li> </ul>                                                                                      |  |

|                               |        | (b) Specifies a write function when the WRITE ENABLE/<br>WRITE LOCK switch is in the WRITE LOCK position.                                                                                                                                    |  |

|                               |        | <ul><li>(c) Specifies an unused function code (111) bits 6 through<br/>8 of the status A register.</li></ul>                                                                                                                                 |  |

|                               |        | (d) Specifies any function except Read All with the<br>maintenance control panel RDMK/WRTM/NORMAL<br>switch in the RDMK position.                                                                                                            |  |

|                               |        | (e) Specifies any function except Write Timing and<br>Mark Track with the RDMK/WRTM/NORMAL switch<br>in the WRTM position.                                                                                                                   |  |

|                               |        | (f) Specifies the Write Timing and Mark-Track function<br>with the RDMK/WRTM/NORMAL switch in a position<br>other than WRTM.                                                                                                                 |  |

| Tab      | le 2-4   | (Cont)    |

|----------|----------|-----------|

| Status E | 3, Bit A | ssignment |

| Function           | AC Bit         | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parity Error (PAR) | 4              | 1 = Error occurs during a Read Data function if the<br>longitudinal parity over entire data block including<br>reverse checksum and checksum, is not equal to 1.<br>If a parity error is to be set at the end of a block,<br>it will be set at the same time the DTF is set. During<br>CM if a word count overflow does not occur at the<br>end of a block, the parity error is set at the end of<br>the block in which the parity error occurs. The parity<br>error cannot be set after the DTF is set. |

| Timing Error (TIM) | 5              | <ol> <li>Program fault caused by one of the following condi-<br/>tions:</li> <li>(a) A data break request is not answered within 66 μs<br/>±30% of the data break request.</li> </ol>                                                                                                                                                                                                                                                                                                                    |

|                    |                | <ul> <li>(b) The DTF was not cleared by the program before the control attempted to set it.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    |                | (c) The read data or write data function was specified<br>after the current data block has been entered to<br>prevent incomplete data block transfers.                                                                                                                                                                                                                                                                                                                                                   |

|                    | 6,7,8,9,<br>10 | Unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DECtape Flag (DTF) | 11             | 1 = DECtape operation complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## 2.6 CONTROL MODES AND FUNCTIONS

The TCO2 control unit operates in either the normal mode (NM) or continuous mode (CM) as determined by the mode bit (5) in the status A register. In the normal mode, the data transfer and flag indications are controlled by the format of the information on tape. In the continuous mode, data transfer and flag indications are controlled by a word count (WC) read from core memory and by the tape format.

The normal mode differs from the continuous mode primarily in the time at which the DECtape flag (DTF) is set. The DECtape flags which occur in the normal mode are inhibited in the continuous mode until a word count overflow has occurred. In both modes, data break requests occur only when a word count overflow has not occurred during the currently specified function.

## 2.7 CONTROL FUNCTIONS

The seven functions available with the TC02 and their octal numbers, as specified by the bits 6 through 8 of the AC are as follows.

| Function                                  | Octal No. |

|-------------------------------------------|-----------|

| Move                                      | 0         |

| Search                                    | 1         |

| Read Data                                 | 2         |

| Read All                                  | 3         |

| Write Data                                | 4         |

| Write All                                 | 5         |

| Write Timing and Mark Track               | 6         |

| Unused at present (select error if given) | 7         |

All functions take place in either direction and in either normal mode (NM) or continuous mode (CM). NM differs from CM only in the fact that the DECtape flag (DTF) occurs at more frequent intervals in NM. The DTF settings which occur in NM are eliminated in the CM until word count overflow (WC) has occurred.

## 2.7.1 Move

The Move function simply sets the selected unit in motion (forward/reverse). NM and CM have no meaning and are ignored in this function alone. When the tape enters either end zone\* (i.e., beginning of tape (BOT) and end of tape (EOT)), and the unit in question is selected:

- a. The error flag (EF) is set.

- b. The EOT bit (bit 2 of status B register) is set.

- c. An interrupt occurs. \*\*

A program check on the forward/reverse motion bit (AC bit 3) of the status register will determine whether EOT or BOT occurred. If the unit is deselected, however, the tape runs off the reel with no flags raised and no interrupt. In order to stop a selected unit at any time, the GO bit (AC bit 4) must be set to 0.\* Once a unit is deselected, status information pertaining to that unit is no longer accessible unless it was saved by the program prior to deselection.

## 2.7.2 Search

The Search function provides the capability of random access of data blocks on DECtape. This function is used to locate the number of the block to or from which data transfer will occur. In normal mode at each block mark until EOT occurs, the DTF is raised and an interrupt occurs. The block number is automatically transferred by the hardware into the memory location specified by the

<sup>\*</sup> If either end zone is entered during turn around or during stopping of tape, the EOT bit is not set and no interrupt occurs.

<sup>\*\*</sup>All references to the occurrence of interrupts assume both that the program interrupt is on, and the DTF and EF have been enabled to the program interrupt or API (i.e., bit 9 of status A register is set to a 1). If either of these is not true, flags are raised and status bits are set (and may be sensed and/or cleared), but no interrupt occurs.

CA (current address). The CA must have been set previously by the program, but the contents are not incremented. The WC is incremented at each DTF, and the program must clear the DTF bit in the status register and check the block number until the desired one is found.

In continuous mode, the WC is set to the 2s complement of the number of blocks to skip. At each block mark, the block number is read into the memory location specified by the CA which is not incremented. The DTF is raised only at the block mark at which the WC overflows. At that time, an interrupt occurs. Continuous mode provides a virtually automatic DECtape search.

#### 2.7.3 Read Data

The Read Data function is used to transfer blocks of data into core memory with the transfer controlled by the standard tape format. The standard block length is 256 18-bit words. For this and all following functions, the CA register initially must be set to the transfer memory location - 1 be - cause the CA register is incremented just before each word transfer. The WC register is also incre- mented prior to each word transfer so must be set to the 2s complement of the number of words to be transferred prior to the transfer. Data may be transferred in forward or reverse but it is transferred into (from) ascending addresses in memory.

Any number of words equal to or less than 1 block may be transferred in NM. The DTF is raised and an interrupt occurs at the end of each block. The DTF must be cleared before the beginning of the next block (i.e., 1.7 ms) to avoid an erroneous timing error. When partial blocks are trans-ferred, data transmission ends with WC overflow (i.e., the word which causes the WC overflow is the last one transferred). The remainder of the block is read and parity checked, however, before the DTF and interrupt occur. Tape motion continues until the GO bit is reset to 0 by the program. If the GO bit is not reset to a 0 or a new function specified before the end of the next block, a timing error will occur. READ DATA in NM is intended primarily for single, 256-word, block transfers. If any other number of words is to be transferred, it is advantageous to use CM. If the programmer chooses to use NM for any other number of words, however, the program must check for WC overflow of each interrupt since there is no other way to determine when to stop the tape or change to another function. When the WC overflow occurs, it is essential that the function be changed or the GO bit set to 0. Otherwise transfer begins again (the IOT to clear the DTF implicitly specifies the same function again) at the next block (or next word for the ALL BITS functions) since WC = 000000<sub>R</sub> is valid.

Any number of words may be transferred in CM. However, the DTF and an interrupt occur only once after a WC overflow and an end of block. The comments concerning tape continuation apply in CM as well as NM.

#### 2.7.4 Read All

The Read All function allows information to be read from an unusually formatted tape essentially reading all data channels recorded on DECtape regardless of the mark-track value. During the Read All function the DECtape control does not distinguish between different marks recorded on the mark track-- except to check for mark-track errors (MKTK) and end of tape (END). In normal mode (NM), the DTF is raised and causes an interrupt at the end of each 18-bit word transfer. Data transfer stops after WC overflow, but tape motion continues until the GO bit is set to 0 or a new function is specified (in both NM and CM). If the DTF is not cleared after each word transfer, a timing error occurs at the end of the next word (i.e., 200 µs later).

For continuous mode, the DTF is raised and causes an interrupt at WC overflow only. If this interrupt is ignored no more data transfers occur but tape motion continues to EOT.

#### 2.7.5 Write Data

The WRITE ENABLE switch on the TU55 must be in WRITE ENABLE position for all Write functions. All the details of the Read Data function description apply with the following exceptions.

In normal mode, the DTF is set to a 1 at the end of each block. If WC0 did not occur in the block just ended and a new function is specified, the next block will be written (provided the DTF has been cleared). If WC overflow did occur in the block just ended and no new function is specified, the tape continues to move but the writers are disabled. In both CM and NM, when partial blocks are written, data transfer from core to DECtape stops at WC overflow. The 000000s are written in the re-maining data words of the block and the parity check character is computed over the entire block and recorded.

In continuous mode, the DTF is set at the end of the block in which WC overflow occurred. Therefore, if no new function is specified, the tape continues to move but the writers are disabled.

#### 2.7.6 Write All

All the details of the Read All function description apply. The Write All function is used to write an unusual format (such as block numbers on DECtape after timing and mark tracks have been recorded). The word which causes WC overflow is the last one written in NM or CM. The tape continues to move but the writers are disabled.

#### NOTE

Change of function must be delayed for 90  $\mu$ s to insure recording of last word. Alternative method: set WC to 1 greater than desired number of word transfers and change function within 40  $\mu$ s after WC0.

#### 2.7.7 Write Timing and Mark Tracks

This function and only this function may be performed with the selector switch on write timing and mark track (WRTM) on the maintenance control panel. Whereas the timing track is actually hardware recorded during execution of this function, the mark track is generated and recorded by program. The value written in the mark track is determined by bits 0, 3, 6, 9, 12, and 15 of the 18-bit word being written (i.e., the same bits assigned to channel 1).

CM may be conveniently used for this function since the hardware WC provides an automatic counter and interrupt at WC overflow only; in NM, the DTF and interrupt occur at every word until

WC overflow. In NM, after WC overflow, if the GO bit or DECtape flag are not cleared, a timing error occurs and no more data is recorded. After WC overflow in CM, if the GO bit is not set to 0, zeros are written on down tape.

#### 2.7.8 Enable and Interrupt Feature

The enable-to-the-interrupt feature allows the program to remove DECtape from the program interrupt line (even if the interrupt is ON). This is primarily of value in the automatic priority interrupt system.

When command bit 9 in the status register is set to a 1, the TC02 is connected to the interrupt system. If this bit is 0, the DTF in the TC02 cannot cause an interrupt even if the interrupt facility in the PDP-9 is ON. Similarly, any of the five error conditions will cause an interrupt if bit 9 is set to 1 in the status register, but cannot cause a program interrupt if bit 9 is a 0.

Whether this bit is set or not does not influence the setting of status bits 0 through 5 of the status B register upon receipt of an error flag (EF) or DTF. Similarly, the result of the I/O skip in - struction is independent of the condition of this bit.

#### 2.7.9 Error Conditions

Five types of errors can be detected in using DECtape: timing, parity, selection, end-oftape, and mark-track errors.

For all errors the EF is raised, a bit is set in the status register, and an interrupt occurs (if the enable-to-interrupt bit has been set). The DTEF instruction skips on the inclusive OR of those error bits; hence, each status bit must be checked to determine the kind of error. For all but the parity error, the selected transport is stopped and the EF is raised at the time of error detection. No DTF occurs. For a parity error, the GO bit remains 1 (i.e., motion continues) and the EF is raised simul-taneously with the DTF in NM. Only 1 interrupt occurs, hence the program must check the EF.

A parity error in CM raises the EF at the end of the block in which the parity occurs, causing an interrupt (if enabled). If no program action is taken, for example, stop transport or reverse and reread, data transfer continues and the DTF is raised and causes an interrupt at WC overflow and end of final block read.

#### 2.8 PROGRAMMED OPERATION

Before using DECtape tape for data storage, the reel of tape is prerecorded in two passes. In the first pass, the timing and mark tracks are placed on the tape. During the second pass, the forward and reverse block numbers are written. Prerecording uses the WRTM control function and the manual switch on the maintenance control panel of the type TC02 control to (1) write on the timing and mark tracks, (2) to activate a clock which produces the timing track recording pattern, and (3) to enable flags for program control. Unless the WRTM control function and the switch are used simultaneously, writing on the mark and timing channels is inhibited. A red indicator lights on the maintenance control panel when the manual switch is in the WRTM position.

The seven basic IOT instructions are generated, as required, by the PDP-9 program to clear, read, and load the Status A and Status B elements. The IOT skip instruction is available to test the status of the TC02 control. Since all data transfers between the TC02 and the PDP-9 memory are controlled from the computer, the program sets the word count (WC) and current address (CA) registers using the memory reference instruction in the process of initializing a block transfer. Before and after a DECtape operation, the program can check for error conditions.

The DECtape system is started with the search function to locate the block number selected for transfer. When the correct block is found, the transfer is accomplished by setting the WC, CA, and the status A and status B registers. When searching, the DECtape control reads only block numbers. These are used by the operating program to locate the correct block number. In NM, the DTF is raised at each block number. In CM, the DTF is raised only after the WC reaches zero. The CA is not in – cremented during searching, and the block number is placed in core memory at the location specified by the contents of the CA. Data is transferred to or from PDP-9 memory from locations specified by the CA which is incremented before each transfer.

When the start of the data position of the block is detected, DF is raised to initiate a data break request to the computer each time the DECtape system is ready to transfer an 18-bit word. Transfers occur between the DECtape and successive core memory locations specified by the CA. The initial transfer address-1 is stored in the CA by an initializing routine. The number of words that are transferred is determined by the tape format in NM or by the tape format and WC in CM. At the conclusion of the data block transfer, the DTF is raised and a program interrupt occurs. The interrupt subroutine checks the DECtape error bits to determine the validity of the transfer and either initiates a search for the next information to be transferred or returns to the main program.

During all normal writing transfers, a checksum (the 6-bit logical equivalent of the words in data block) is computed automatically by the control and is automatically recorded as one of the control words immediately following the data portion of the block. The same checksum is used during reading to determine that the data playback and recognition takes place without error.

Any one of the eight tape transports may be selected for use by the program. After using a particular transport, the program can stop the drive currently being used and select a new drive, or can select another transport while permitting the original selection to continue running. This allows rapid searching, since several transports may be used simultaneously. Caution must be exercised because, although the original transport continues to run, no tape-end detection or other sensing take place. All functions provide for automatic and sensing, but this feature stops tape in the selected tape drive only.

For programming examples that illustrate possible ways to code DECtape functions on the PDP-9, see the PDP-9 Users Handbook, Chapter 5, page 5–13.

#### CHAPTER 3 PRINCIPLES OF OPERATION

This chapter provides a description of the basic functional elements of the DECtape Control Type TC02, descriptions of data and control information transfers, and detailed descriptions of TC02 control operations. For information on the PDP-9 and TU55 transport, refer to the documents listed in Table 1-1.

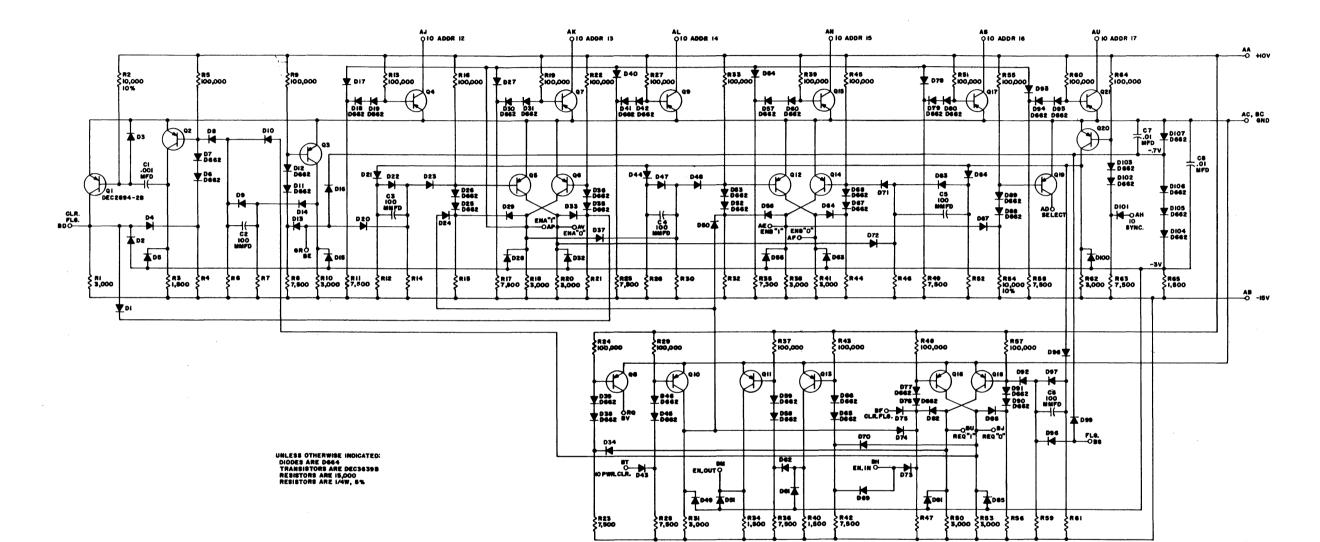

#### 3.1 FUNCTIONAL DESCRIPTION

The I/O bus interface shown in Figure 3-1 is completely described in paragraph 3.3.2.1. When operations are initiated, and the device number, to which the command in the I/O bus is addressed, is sent, the major registers are cleared. Information then is transferred into the TC02 registers from the computer or read from the DECtape into the TC02 registers for assembly of a computer word.

Figure 3-1 Information and Command Flow

Once the tape unit is selected, the read or write operation is established, and proper motion is determined.

The basic functional elements of the PDP-9 processor, TC02 control, and TU55 transport interface blocks are shown in Figure 3-2. Numerals in the lower right-hand corner of the blocks indicate the bit capacity of the element. Numerical subscripts on the signal flow lines indicate the bit assignments of the signals. Numerals in the lower left-hand corner indicate the engineering drawing that shows the detailed elements of the function. Blocks that represent the Status A and Status B functions are indicated by A and B, respectively, at the top right-hand corner of the block.

#### 3.1.1 Information Flow

Information flow for write operation, indicated on Figure 3-2, involves transfer from the I/O bus through gating, a data buffer, read/write buffer, and write amplifiers to the write heads. For reading, data is transferred through the read amplifiers and back through the same elements. The following list defines the characteristics and functions of each of these elements.

Figure 3–2 Type TC01 DECtape Control Functional Block Diagram

3-3

a. <u>Data Buffer (DB)</u>. - The data buffer is an 18-bit register used as a storage buffer to synchronize data transfers as a function of tape timing between the memory buffer register of the computer and the read/write buffer.

b. <u>Read/Write Buffer (RWB)</u>. - The read/write buffer is a 6-bit register consisting of two 3-bit registers which transmit data between the data control and the read/write heads. During read operations, one bit from each of the three data channels on tape is read into the read/write buffer and shifted left.

c. <u>Write Amplifiers</u>. - The five write amplifiers receive timing signals, mark-track, and data information from the read/write buffer and provide the necessary current to the tape heads to write the data on tape.

d. <u>Read Amplifiers</u>. - The five read amplifiers transfer information from the tape heads to the read/write buffer, and mark track to the window register, and timing signals to control.

#### 3.1.2 Command Flow Registers

The registers and signals which control the transport operations and the data flow are described as follows.

a. <u>Longitudinal Parity Buffer (LPB)</u>. - The longitudinal parity buffer is a 6-bit register used to perform a parity check on the three information channels. The operation is performed by setting the 6-bits of information read from two consecutive lines on tape into the RWB and complementing each stage of the LPB if the corresponding bit of the RWB contains a zero.

b. <u>Window (W)</u>. - The window is a 9-bit shift register through which mark-track information is serially shifted to generate control signals for the DECtape system. Because the mark-track window is three bits longer than is required to contain one mark, additional redundance is provided to check that marks follow one another in the proper order. The bits of the mark-track window are continuously decoded to detect when any of the legal marks appear.

c. <u>Data Flag (DF)</u>. - The data flag flip-flop through DCH gating, requests a data break from the processor when a word is ready to be transferred to or from the TC02.

d. <u>Control</u>. - The control logic generates the timing and synchronizing pulses to perform the functions specified in the function register and to coordinate the operations between the PDP-9 processor and TU55 transport.

e. <u>Device Selector</u>. - The device selector decodes the IOT instructions for the DECtape and generates the necessary pulses to load status registers, and generate SKIP pulses.

f. <u>Unit Select Register.</u> - The unit select register is a 3-bit register which is loaded under program control from the accumulator bits 0 through 2, and specifies a particular TU55 transport.

g. <u>Motion Register</u> - The motion register is a 2-bit register loaded from the accumulator bits 3 and 4, with the appropriate command of GO or STOP (bit 4), FORWARD or REVERSE (bit 3).

h. <u>Mode Register.</u> - The mode register is a 1-bit register that selects either normal or continuous mode.

i. <u>Function Register</u>. - This is a 3-bit register that specifies one of seven possible operations to be performed by the DECtape.

i. <u>Function Decoder</u>. - This decodes the content of the function register bits 1 through 3, and transfers the decoded information to the control.

k. <u>Enable to the Interrupt</u>. - This 1-bit register is loaded from the accumulator, bit 9, to enable or disable the DECtape from the program interrupt.

I. <u>Error Register.</u> - A 5-bit register in which any section can be set by the TC02 control to indicate one of five error conditions.

m. Error Flag (EF). - The error flag is set by one or more errors indicated by the error register.

n. <u>DECtape Flag (DTF)</u>. - The DECtape flag is set at the completion of the currently specified operation.

o. <u>Skip Gating</u>. - Skip gating logic generates a pulse from the DTF flag and SKIP IOT to request a skip from the PDP-9. This gating is not affected by the enable to the interrupt.