#### EK-DCT11-UG-003

$\frac{1}{1}$

# USER'S GUIDE

## Copyright © 1982 by Digital Equipment Corporation All Rights Reserved

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

#### Printed in U.S.A.

The manuscript for this book was created on a DIGITAL Word Processing System and, via a translation program, was automatically typeset on DIGITAL's DECset-8000 Typesetting System. Book production was done by Educational Services Development and Publishing in Marlboro, MA.

The following are trademarks of Digital Equipment Corporation:

| DEC          | EduSystem | RSTS    |

|--------------|-----------|---------|

| DECnet       | IAS       | RSX     |

| DECUS        | MASSBUS   | TOPS-10 |

| DECsystem-10 | MINC-11   | TOPS-20 |

| DECSYSTEM-20 | OMNIBUS   | UNIBUS  |

| DECwriter    | OS/8      | VAX     |

| DIBOL        | PDP       | VMS     |

| digital      | PDT       | VT      |

# CONTENTS

٤.

## CHAPTER 1 ARCHITECTURE

| 1.1     | INTRODUCTION                                       | 1-1 |

|---------|----------------------------------------------------|-----|

| 1.2     | REGISTERS                                          | 1-1 |

| 1.2.1   | General-Purpose Registers                          | 1-1 |

| 1.2.2   | General-Purpose Registers<br>Status Register       | 1-3 |

| 1.2.3   | Mode Register                                      | 1-4 |

| 1.3     | ARITHMETIC LOGIC UNIT (ALU)                        | 1-4 |

| 1.4     | DCT11-A HARDWARE STACK                             | 1-4 |

| 1.5     | INTERRUPTS                                         | 1-5 |

| 1.5.1   | Interrupt Mechanism                                | 1-5 |

| 1.5.2   | Interrupt Posting                                  | 1-5 |

| 1.5.3   | Interrupt Request (IRQ)                            | 1-5 |

| 1.5.4   | Vectors                                            | 1-6 |

| 1.5.4.1 | Internal Vector Address                            | 1-7 |

| 1.5.4.2 | Internal Vector Address<br>External Vector Address | 1-7 |

| 1.5.5   | Priority                                           | 1-7 |

| 1.5.5.1 | Maskable Interrupts                                | 1-7 |

| 1.5.5.2 |                                                    | 1-8 |

| 1.6     |                                                    | 1-8 |

1

## CHAPTER 2 BUS TRANSACTIONS

| 2.1     | INTRODUCTION                                                                               | 2-1 |

|---------|--------------------------------------------------------------------------------------------|-----|

| 2.2     | BUS TRANSACTION                                                                            | 2-1 |

| 2.2.1   | Transaction                                                                                | 2-2 |

| 2.2.2   | Microcycle<br>Clock Phase                                                                  | 2-2 |

| 2.2.3   | Clock Phase                                                                                | 2-2 |

| 2.3     | 16-BIT STATIC READ TRANSACTION                                                             | 2-2 |

| 2.3.1   | Output of Address                                                                          | 2-2 |

| 2.3.2   | 16-BIT STATIC READ TRANSACTION.<br>Output of Address<br>Input of Data<br>Instruction Fetch | 2-2 |

| 2.3.3   | Instruction Fetch                                                                          | 2-4 |

| 2.4     |                                                                                            | 2-4 |

| 2.4.1   | Output of Address                                                                          | 2-4 |

| 2.4.2   | Output of Data                                                                             | 2-4 |

| 2.5     | 16-BIT DYNAMIC READ TRANSACTION                                                            | 2-6 |

| 2.5.1   | Output of Address                                                                          | 2-6 |

| 2.5.1.1 | Dynamic Address                                                                            | 2-6 |

| 2.5.1.2 | Static Address                                                                             | 2-6 |

| 2.5.1.3 | Address Control                                                                            | 2-6 |

| 2.5.2   | Input of Data                                                                              | 2-6 |

## Page

3

| 2.5.3    | Instruction Fetch                                    | 2-9    |

|----------|------------------------------------------------------|--------|

| 2.5.3.1  | 4K/16K Mode                                          |        |

| 2.5.3.2  | 64K Mode                                             | 2-9    |

| 2.6      | 16-BIT DYNAMIC WRITE TRANSACTION                     |        |

| 2.6.1    | Output of Address                                    |        |

| 2.6.1.1  | Dynamic Address                                      |        |

| 2.6.1.2  | Static Address                                       |        |

| 2.6.1.3  | Address Control                                      |        |

| 2.6.2    | Output of Data                                       |        |

| 2.7      | 8-BIT STATIC READ TRANSACTION                        | 2 - 12 |

| 2.7.1    |                                                      |        |

| 2.7.2    | Output of Address                                    | 2-13   |

| 2.7.3    | Input of Data                                        | 2-13   |

|          | Instruction Fetch                                    | 2-14   |

| 2.8      | 8-BIT STATIC WRITE TRANSACTION                       |        |

| 2.8.1    | Output of Address                                    | 2-16   |

| 2.8.2    | Output of Data                                       | 2-16   |

| 2.9      | 8-BIT DYNAMIC READ TRANSACTION                       |        |

| 2.9.1    | Output of Address                                    |        |

| 2.9.1.1  | Dynamic Address                                      |        |

| 2.9.1.2  | Static Address                                       |        |

| 2.9.1.3  | Address Control                                      |        |

| 2.9.2    | Input of Data                                        |        |

| 2.9.3    | Instruction Fetch                                    | 2-21   |

| 2.9.3.1  | 4K/16K Mode                                          | 2-21   |

| 2.9.3.2  | 64K Mode                                             | 2-21   |

| 2.10     | 8-BIT DYNAMIC WRITE TRANSACTION                      | 2-21   |

| 2.10.1   | Output of Address                                    |        |

| 2.10.1.1 | Dynamic Address                                      |        |

| 2.10.1.2 | Static Address                                       |        |

| 2.10.1.3 | Address Control                                      |        |

| 2.10.2   | Output of Data                                       |        |

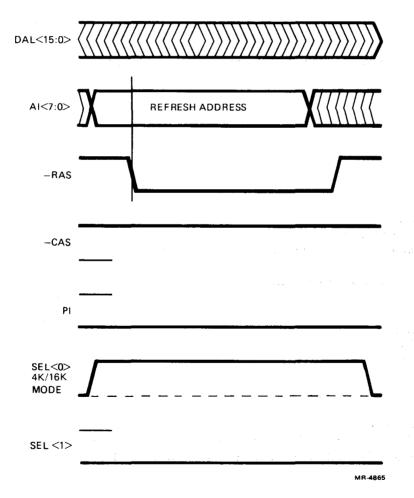

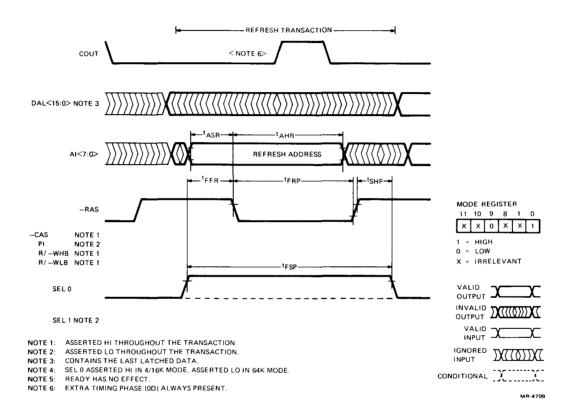

| 2.11     | REFRESH TRANSACTION                                  |        |

| 2.11.1   | Output of Refresh Address                            |        |

| 2.11.2   | Address Control                                      |        |

| 2.11.3   | Output of SEL<0> and SEL<1>                          |        |

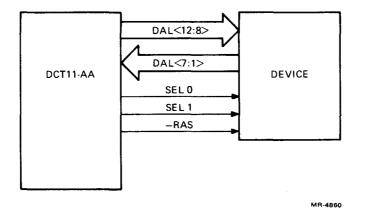

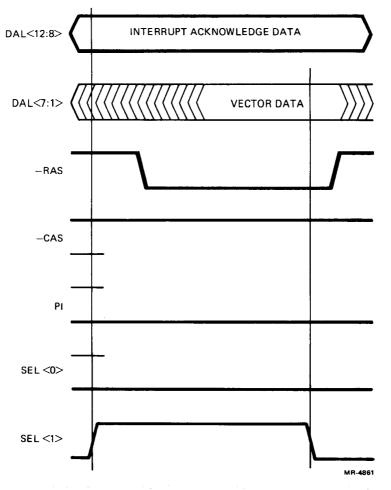

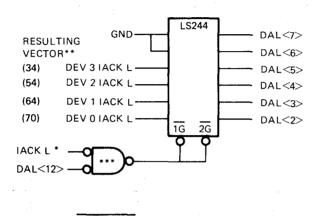

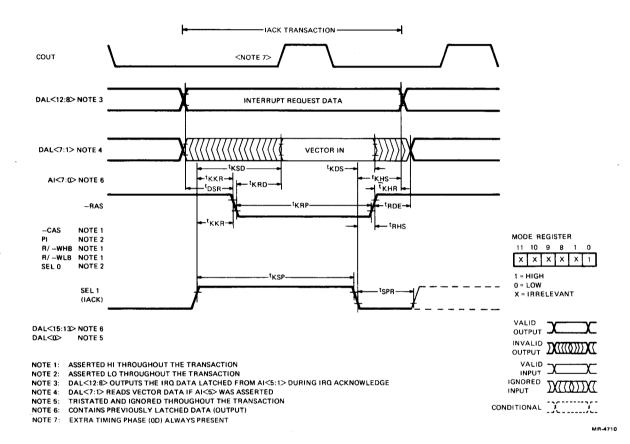

| 2.12     | IACK (INTERRUPT ACKNOWLEDGE) TRANSACTION             | 2-27   |

| 2.12.1   | Output of Interrupt Acknowledge Data                 |        |

| 2.12.2   | Input of Vector Address                              | 2-28   |

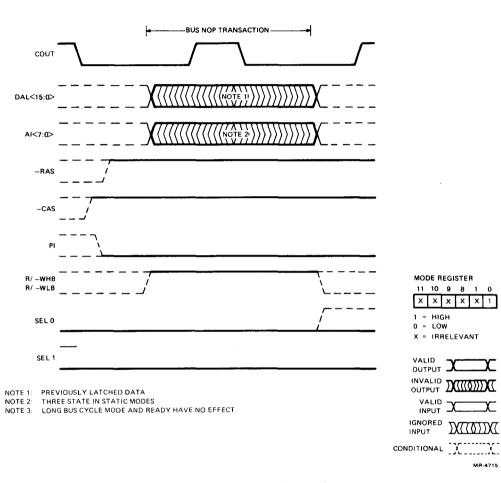

| 2.13     | BUSNOP (NO OPERATION) TRANSACTION                    |        |

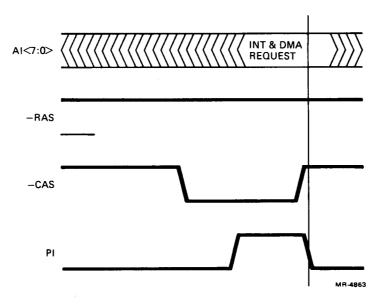

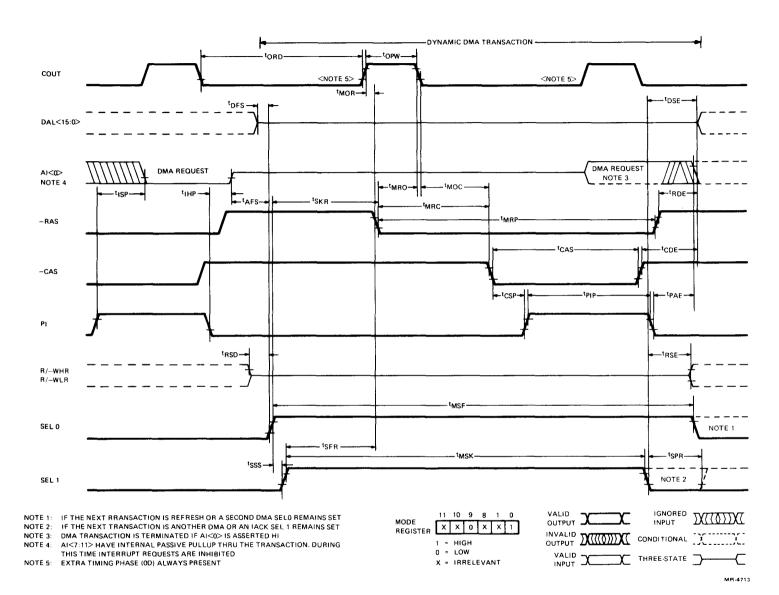

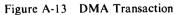

| 2.14     | DMA (DIRECT MEMORY ACCESS) TRANSACTION               |        |

| 2.14.1   | Three-State of DAL<15:0>                             |        |

| 2.14.2   | Output of $-RAS$ , $-CAS$ , and PI                   |        |

| 2.14.2   | Output of Direct Memory Grant (DMG)                  |        |

| 2.14.3   |                                                      |        |

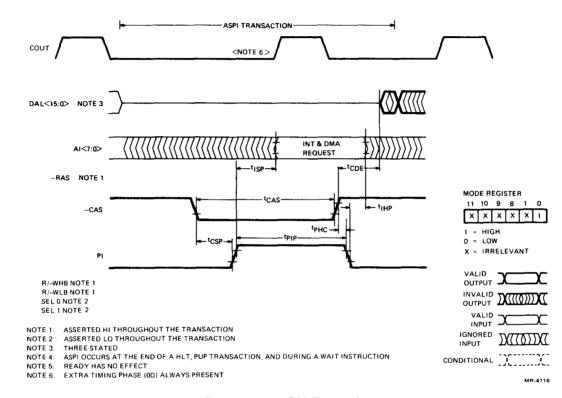

|          | READY Input<br>ASPI (ASSERT PRIORITY IN) TRANSACTION | 2-31   |

| 2.15     | ASTI (ASSEKI PRIORII I IN) IRANSACIION               | 2-31   |

## CHAPTER 3 PIN DESCRIPTIONS

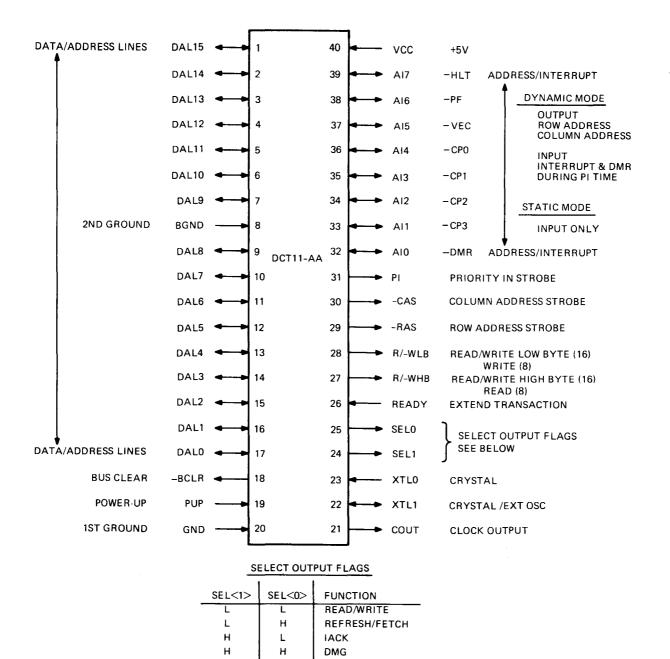

| 3.1     | INTRODUCTION                                                           | 3-1  |

|---------|------------------------------------------------------------------------|------|

| 3.2     | DATA ADDRESS LINES (DAL<15:0>)                                         |      |

| 3.2.1   | 16-Bit Mode – DAL < 15:0>                                              |      |

| 3.2.2   | 8-Bit Mode – DAL<15:8>                                                 |      |

| 3.2.3   | 8-Bit Mode – DAL < 7:0>                                                | 3-6  |

| 3.3     | ADDRESS INTERRUPT (AI<7:0>)                                            |      |

| 3.3.1   | AI < 7:0 > at - RAS and $- CAS$ Time (Static Mode)                     |      |

| 3.3.2   | AI<7:0> at -RAS and -CAS Time (Dynamic Mode)                           |      |

| 3.3.3   | AI<7:0> at Priority In (PI) Time                                       |      |

|         | (Dynamic and Static Modes)                                             | 3-8  |

| 3.4     | CONTROL LINES                                                          |      |

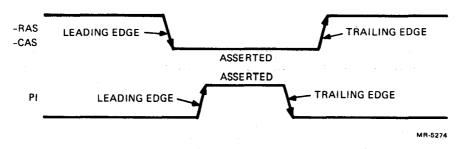

| 3.4.1   | -RAS (Row Address Strobe)                                              | 3-10 |

| 3.4.2   | -CAS (Column Address Strobe)                                           | 3-10 |

| 3.4.3   | PI (Priority In)                                                       |      |

| 3.4.4   | R/-WHB and $R/-WLB$                                                    | 3-11 |

| 3.4.4.1 | R/-WHB and $R/-WLB$ (16-Bit Mode)                                      | 3-11 |

| 3.4.4.2 | $\mathbf{R}'$ – WHB (– RD) and $\mathbf{R}'$ – WLB (– WT) (8-Bit Mode) | 3-11 |

| 3.4.5   | SEL $<1>$ and SEL $<0>$                                                | 3-11 |

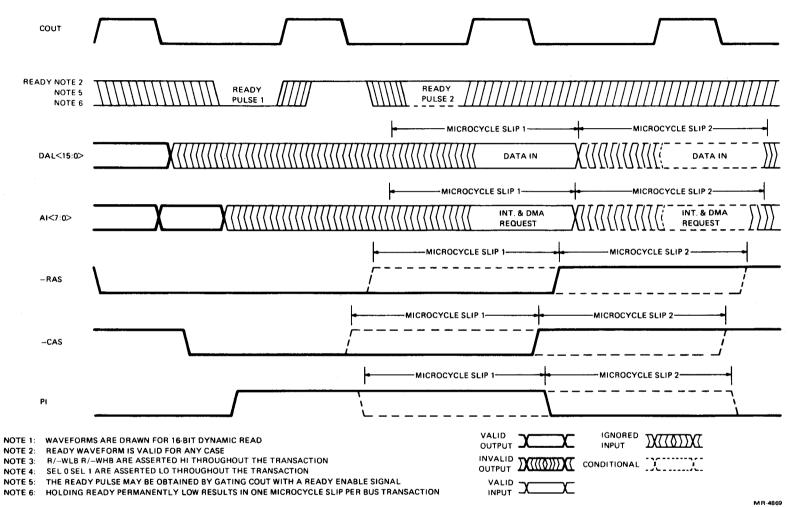

| 3.4.6   | READY                                                                  | 3-11 |

| 3.5     | MISCELLANEOUS SIGNALS                                                  | 3-13 |

| 3.5.1   | - BCLR (Bus Clear)                                                     | 3-13 |

| 3.5.2   | PUP (Power-Up)                                                         | 3-13 |

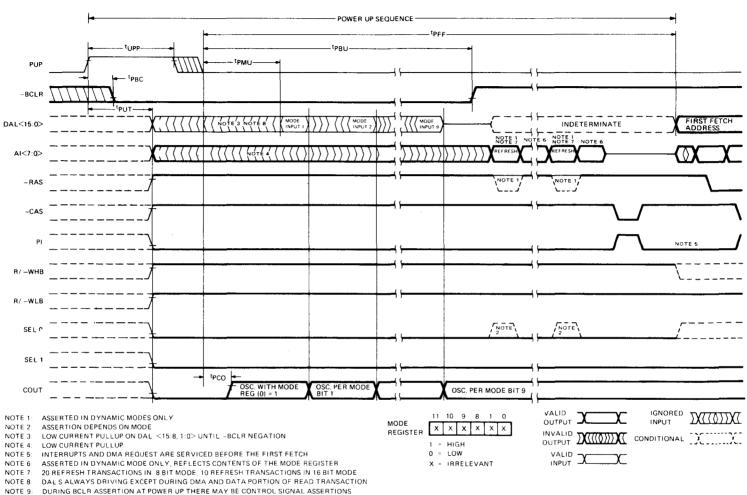

| 3.5.2.1 | Power-Up (PUP) Input                                                   |      |

| 3.5.2.2 | Bus Clear (-BCLR)                                                      |      |

| 3.5.2.3 | Mode Register Load                                                     | 3-14 |

| 3.5.2.4 | Refresh or Busnop Transaction                                          | 3-14 |

| 3.5.2.5 | Loading the SP, PC, and PSW                                            | 3-14 |

| 3.5.2.6 | ASPI Transaction                                                       |      |

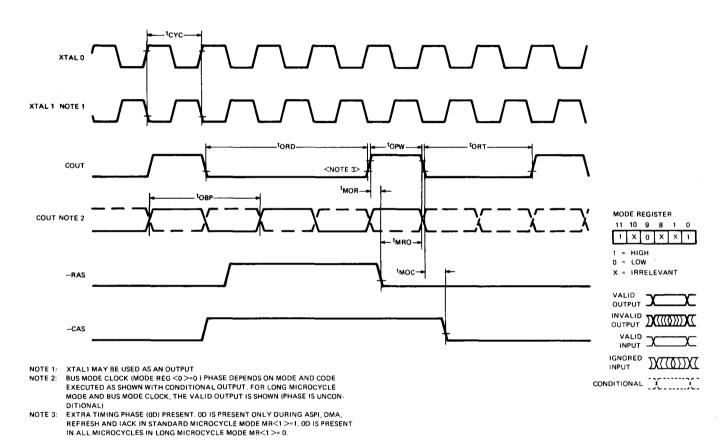

| 3.5.3   | COUT (Clock Output)                                                    | 3-15 |

| 3.5.4   | XTL1 and XTL0 (Crystal Inputs)                                         | 3-15 |

| 3.6     | POWER PINS                                                             |      |

| 3.6.1   | GND and BGND                                                           |      |

| 3.6.2   | V <sub>CC</sub>                                                        | 3-16 |

## CHAPTER 4 MODE SELECTION

| 4.1     | INTRODUCTION                   | 4-1 |

|---------|--------------------------------|-----|

| 4.2     | MODES RELATED TO FUNCTION      | 4-1 |

| 4.2.1   | 16-Bit or 8-Bit Mode (MR<11>)  | 4-1 |

| 4.2.1.1 | 16-Bit Mode                    | 4-1 |

| 4.2.1.2 | 8-Bit Mode                     | 4-2 |

| 4.2.2   | Dynamic or Static Mode (MR<9>) | 4-3 |

| 4.2.2.1 | Dynamic Mode                   | 4-3 |

| 4.2.2.2 | Static Mode                    | 4-3 |

## Page

| 4.2.3   | 64K or 4K/16K Mode (MR<10>)           | 4-3 |

|---------|---------------------------------------|-----|

| 4.2.4   | Tester or User Mode (MR<12>)          | 4-3 |

| 4.2.5   | Start and Restart Address (MR<15:13>) | 4-4 |

| 4.3     | MODES RELATED TO TIMING               | 4-4 |

| 4.3.1   | Constant or Processor Clock (MR<0>)   | 4-4 |

| 4.3.2   | Long or Standard Microcycle (MR<1>)   | 4-4 |

| 4.3.3   | Normal or Delayed Read/Write (MR<8>)  | 4-4 |

| 4.4     | MODE REGISTER BIT SETTING             | 4-4 |

| 4.5     | MODE REGISTER SELECTION GUIDELINES    | 4-5 |

| 4.5.1   | Minimum Cost                          | 4-5 |

| 4.5.1.1 | 8-Bit Mode                            | 4-5 |

| 4.5.1.2 | Dynamic Mode                          | 4-5 |

| 4.5.1.3 | Long Microcycle Mode                  | 4-5 |

| 4.5.2   | Maximum Speed                         | 4-5 |

| 4.5.2.1 | 16-Bit Mode                           | 4-5 |

| 4.5.2.2 | Static Mode                           | 4-5 |

| 4.5.2.3 | Standard Microcycle                   | 4-5 |

| 4.5.3   | Minimum Size (Chip Count)             | 4-5 |

| 4.5.3.1 | 8-Bit Mode                            | 4-6 |

| 4.5.3.2 | Static Mode                           | 4-6 |

| 4.5.4   | Minimum Development Time              | 4-6 |

| 4.5.4.1 | 16-Bit Mode                           | 4-6 |

| 4.5.4.2 | Static Mode                           | 4-6 |

|         |                                       |     |

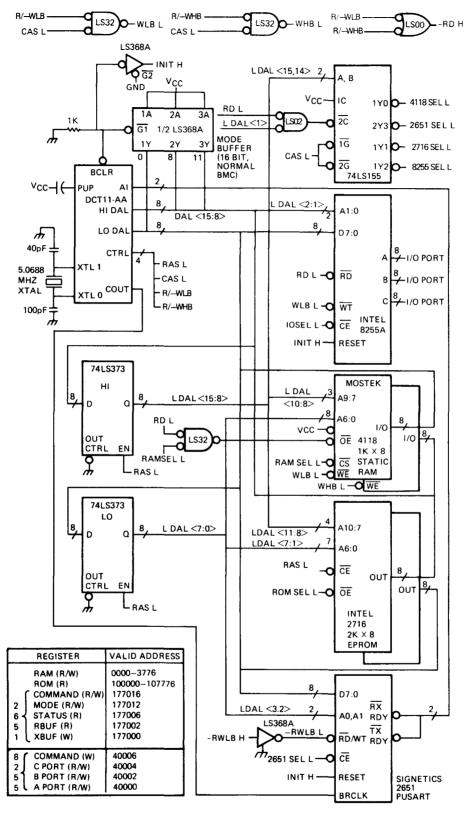

## CHAPTER 5 INTERFACING

.

| 5.1     | INTRODUCTION                                |      |

|---------|---------------------------------------------|------|

| 5.2     | POWER-UP                                    |      |

| 5.3     | LOADING THE MODE REGISTER                   | 5-1  |

| 5.4     | CLOCK                                       |      |

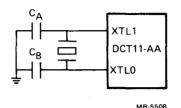

| 5.4.1   | Crystal-Based Clock                         |      |

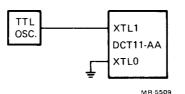

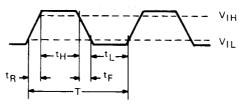

| 5.4.2   | TTL Oscillator-Based Clock                  |      |

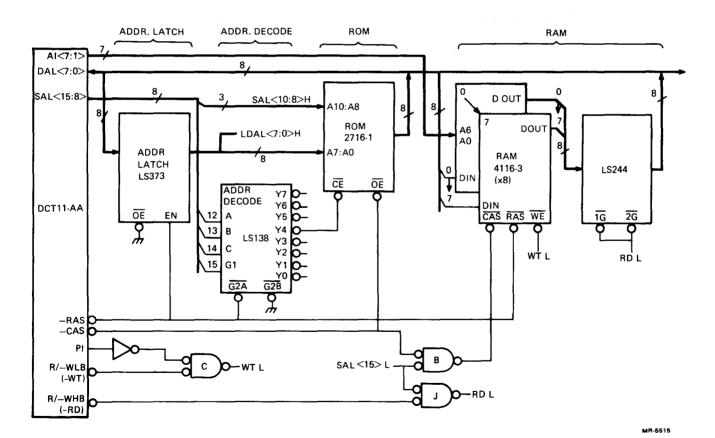

| 5.5     | ADDRESS LATCH AND DECODE                    | 5-4  |

| 5.6     | MEMORY SUBSYSTEMS                           |      |

| 5.6.1   | 16-Bit Mode Memory System                   |      |

| 5.6.2   | 8-Bit Mode Memory System                    |      |

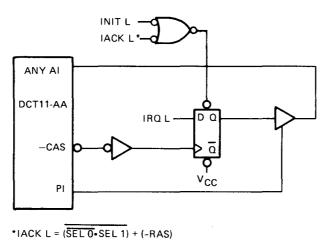

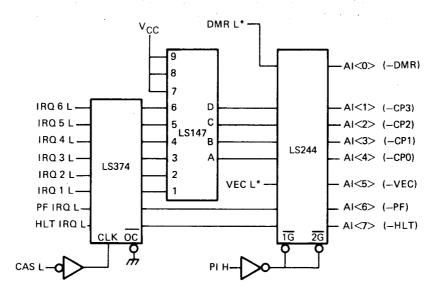

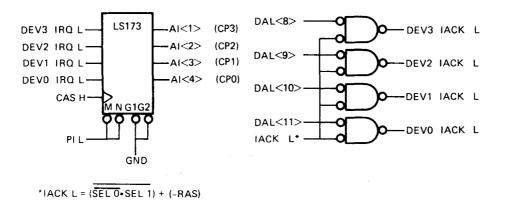

| 5.7     | INTERRUPTS                                  |      |

| 5.7.1   | Posting Interrupts                          |      |

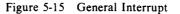

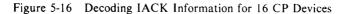

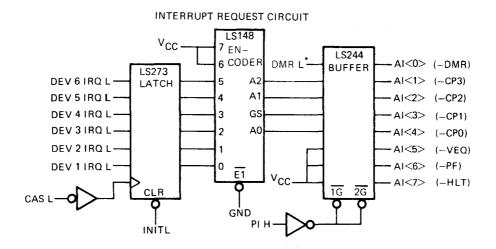

| 5.7.2   | Decoding IACK Information                   |      |

| 5.7.3   | External Vectors                            |      |

| 5.7.4   | Using a Priority Encoder Chip               |      |

| 5.7.5   | Direct CP Encoding                          |      |

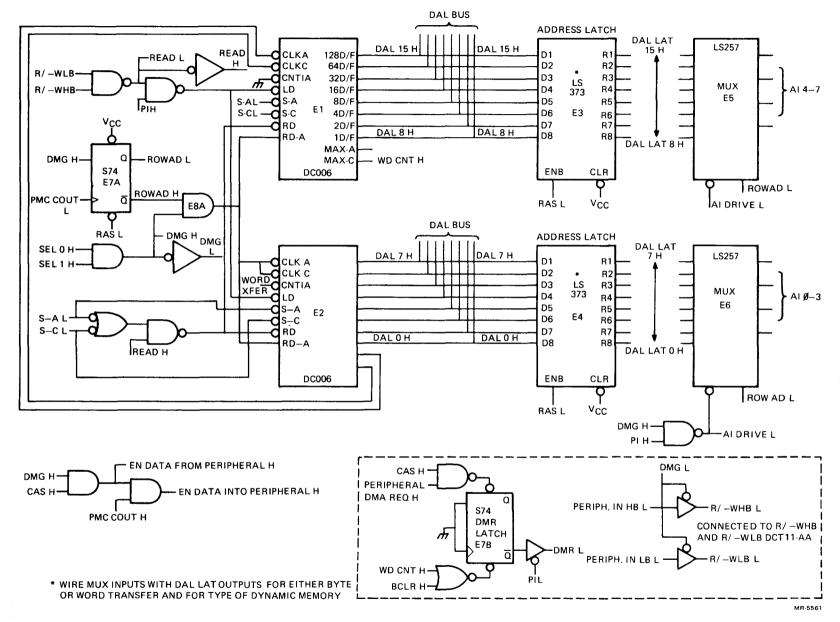

| 5.8     | DMA                                         |      |

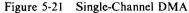

| 5.8.1   | Single-Channel DMA Controller (16-Bit Mode) | 5-17 |

| 5.8.1.1 | Address Latches                             |      |

|         | (Single-Channel DMA Controller)             | 5-17 |

| 5.8.1.2 | Pulse Mode Clock                            |      |

|         | (Single-Channel DMA Controller)             | 5-17 |

## Page

| 5.8.1.3          | Address Decode Structures                                                | 5-17 |

|------------------|--------------------------------------------------------------------------|------|

| 5.8.1.4          | Operation Sequence                                                       |      |

|                  | (Single-Channel DMA Controller)                                          | 5-17 |

| 5.8.2            | Software DMA Requests                                                    | 5-19 |

| 5.9              | WORKING WITH PERIPHERAL CHIPS                                            | 5-20 |

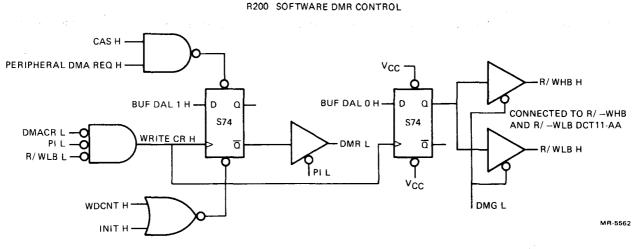

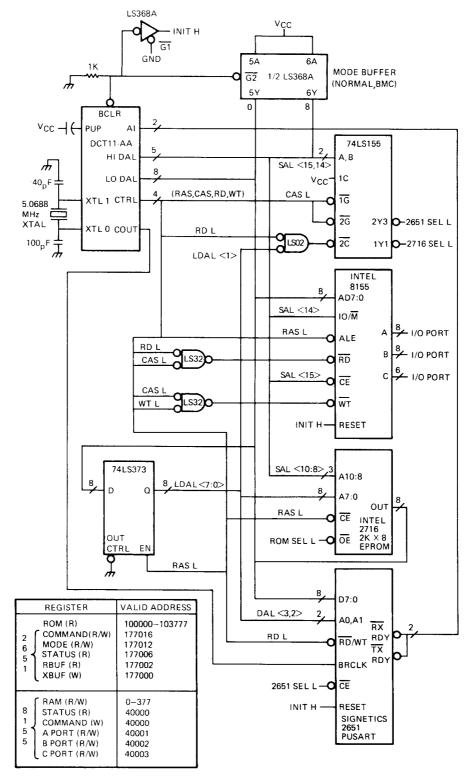

| 5.9.1            | 8155 – RAM, Three Ports, and Timer                                       | 5-20 |

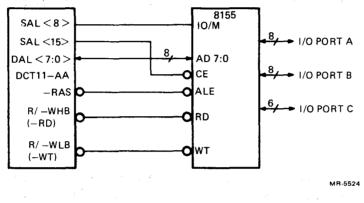

| 5.9.2            | 2651 – PUSART                                                            | 5-20 |

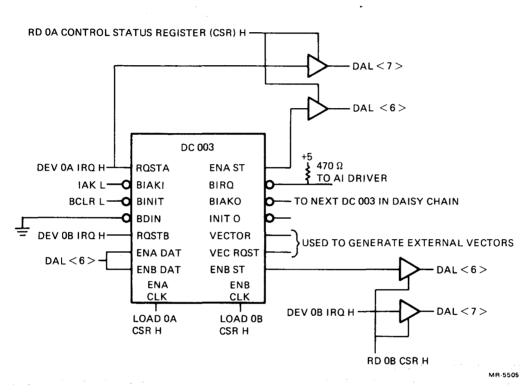

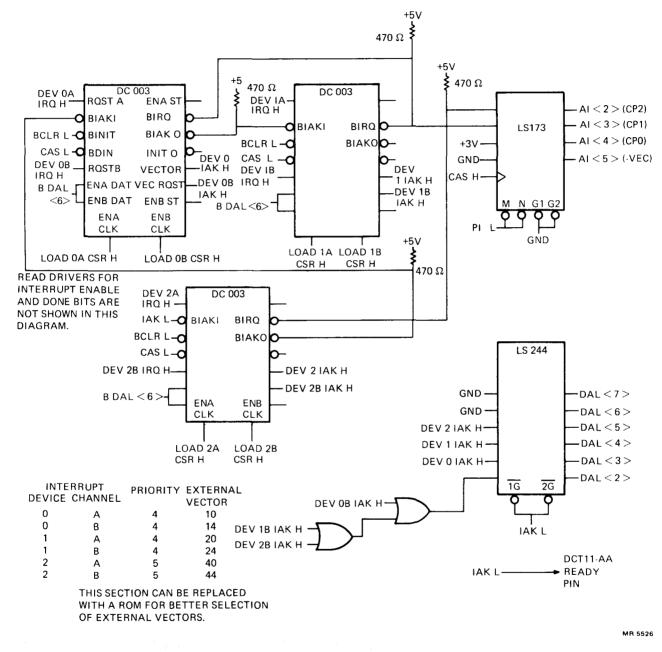

| 5.9.3            | DC003 – Interrupt Logic                                                  |      |

|                  |                                                                          |      |

|                  |                                                                          |      |

| CHAPTER 6        | ADDRESSING MODES AND INSTRUCTION SET                                     | ,    |

| 6.1              | INTRODUCTION                                                             | 6-1  |

| 6.2              | ADDRESSING MODES.                                                        |      |

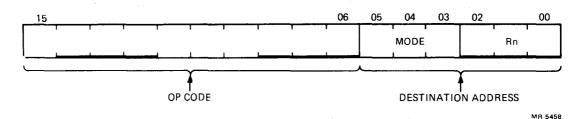

| 6.2.1            | Single-Operand Addressing                                                |      |

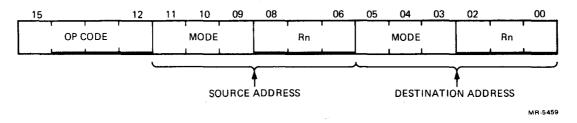

| 6.2.2            | Double-Operand Addressing                                                |      |

| 6.2.3            | Direct Addressing                                                        |      |

| 6.2.3.1          | Register Mode                                                            |      |

| 6.2.3.2          | Autoincrement Mode [OPR (Rn)+]                                           |      |

| 6.2.3.3          | Autodecrement Mode $[OPR - (Rn)]$ .                                      |      |

| 6.2.3.4          | Index Mode [OPR X(Rn)]                                                   |      |

| 6.2.4            | Deferred (Indirect) Addressing                                           |      |

| 6.2.5            | Use of the PC as a General-Purpose Register                              |      |

| 6.2.5.1          | Immediate Mode [OPR #n,DD]                                               | 0-10 |

| 6.2.5.2          | Absolute Addressing [OPR @#A]                                            | 0-10 |

| 6.2.5.3          | Relative Addressing [OPR A or OPR X(PC)]                                 |      |

| 6.2.5.4          | Relative Addressing [OFR A of OFR A(FC)]<br>Relative-Deferred Addressing | 0-10 |

| 0.2.3.4          | [OPR @A or OPR @X(PC)]                                                   | 6 10 |

| 6.2.6            |                                                                          |      |

| 0.2.0            | Use of the Stack Pointer as a<br>General-Purpose Register                | 6 20 |

| 6.3              | INSTRUCTION SET                                                          | 0-20 |

| 6.3.1            | Instruction Formats                                                      |      |

| 6.3.2            | List of Instructions                                                     |      |

| 6.3.3            | Single-Operand Instructions                                              |      |

| 6.3.3.1          | General                                                                  |      |

| 6.3.3.2          |                                                                          |      |

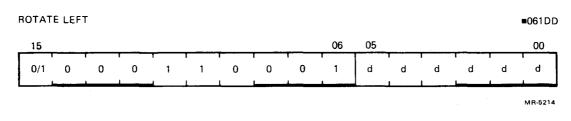

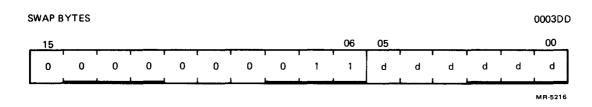

| 6.3.3.3          | Shifts and Rotates                                                       |      |

|                  | Multiple-Precision                                                       |      |

| 6.3.3.4          | PS Word Operators                                                        |      |

| 6.3.4<br>6.3.4.1 | Double-Operand Instructions                                              |      |

|                  | General                                                                  |      |

| 6.3.4.2          | Logical                                                                  |      |

| 6.3.5            | Program Control Instructions                                             |      |

| 6.3.5.1          | Branches                                                                 |      |

| 6.3.5.2          | Signed Conditional Branches                                              |      |

| 6.3.5.3          | Unsigned Conditional Branches                                            |      |

| 6.3.5.4          | Jump and Subroutine Instructions                                         |      |

| 6.3.5.5          | Traps                                                                    |      |

| 6.3.5.6          | Reserved Instruction Traps                                               | 6-61 |

## Page

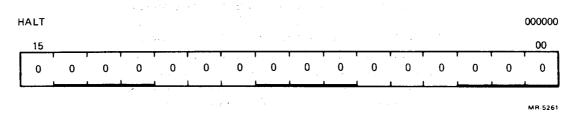

| 6.3.5.7  | Halt Interrupt             | 6-61 |

|----------|----------------------------|------|

| 6.3.5.8  | Trace Trap                 |      |

| 6.3.5.9  | Power Failure Interrupt    | 6-61 |

| 6.3.5.10 | CP<3:0> Interrupts         | 6-61 |

| 6.3.5.11 | Special Cases of the T Bit | 6-61 |

| 6.3.6    | Miscellaneous Instructions |      |

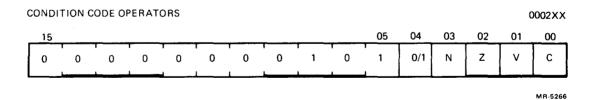

| 6.3.7    | Condition Code Operators   | 6-63 |

## APPENDIX A TABLES AND TIMING DIAGRAMS

## APPENDIX B SOFTWARE DIFFERENCES

| B.1             | INTRODUCTION                                 | <b>B-</b> 1 |

|-----------------|----------------------------------------------|-------------|

| B.2             | ADDRESSING MODES                             |             |

| B.2.1           | Modes 2 and 4                                |             |

| B.2.2           | Modes 3 and 5                                | B-2         |

| B.2.3           | Using the PC Contents as the Source Operand  | B-2         |

| B.2.4           | Jump (JMP) and Jump to Subroutine (JSR)      |             |

|                 | Instructions                                 | B-3         |

| B.3             | Instructions<br>PDP-11 INSTRUCTION SET       | B-3         |

| B.3.1           | Instructions Not Common to All PDP-11s       |             |

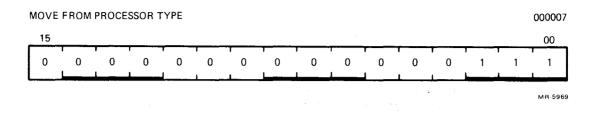

| <b>B</b> .3.1.1 | MFPT Instruction                             | <b>B-4</b>  |

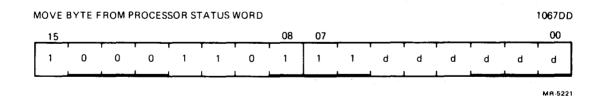

| <b>B</b> .3.1.2 | MFPS Instruction                             | B-4         |

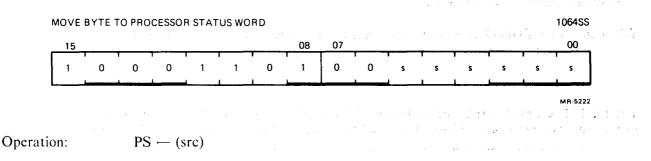

| B.3.1.3         | MTPS Instruction                             |             |

| B.3.2           | Basic Instruction Execution                  | <b>B-</b> 5 |

| B.3.2.1         | Halt Instruction                             | <b>B-</b> 6 |

| <b>B</b> .3.2.2 | Reset Instruction                            | <b>B-</b> 6 |

| <b>B</b> .3.3   | Instructions Not Executed                    | <b>B-7</b>  |

| <b>B</b> .3.4   | Effect of the T Bit (Instruction Trace Trap) |             |

| B.4             | DCT11-AA INSTRUCTION EXECUTION SEQUENCE      |             |

|                 | ON THE DATA BUS                              | B-8         |

| B.5             | EXCEPTIONS AND INTERRUPTS                    |             |

| B.5.1           | Bus Errors                                   |             |

| B.5.2           | Internal Register Access                     |             |

| B.6             | POWER-UP                                     |             |

## **FIGURES**

## Figure No.

## Title

## Page

Sz.

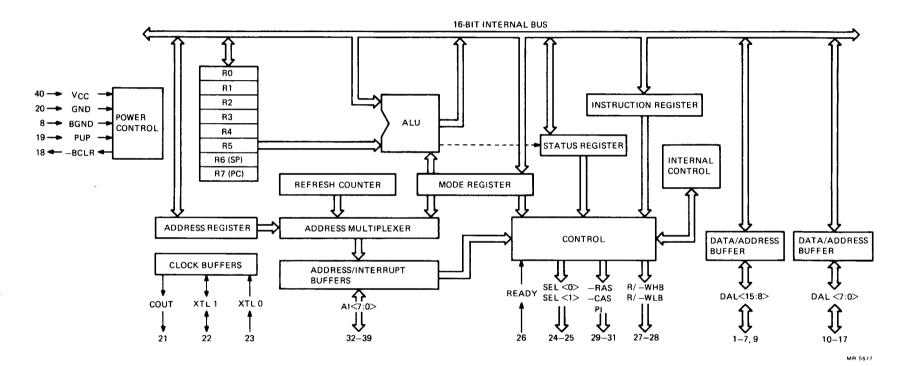

| 1-1 | DCT11-AA, Block Diagram   | 1-2 |

|-----|---------------------------|-----|

| 1-2 | General-Purpose Registers |     |

| 1-3 | Processor Status Word     | 1-3 |

| ]-4 | Mode Register             | 1-4 |

| 1-5 | Interrupt Request         | 1-5 |

| 1-6 | Interrupt Timing          | 1-6 |

# FIGURES (Cont)

## Figure No.

-

đ

٤

## Page

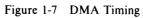

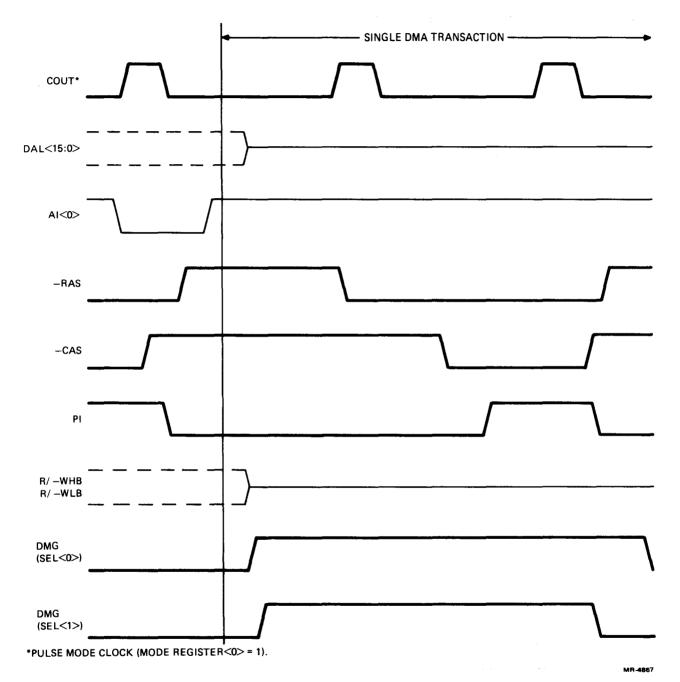

| 1-7  | DMA Timing                                      | 1-9     |

|------|-------------------------------------------------|---------|

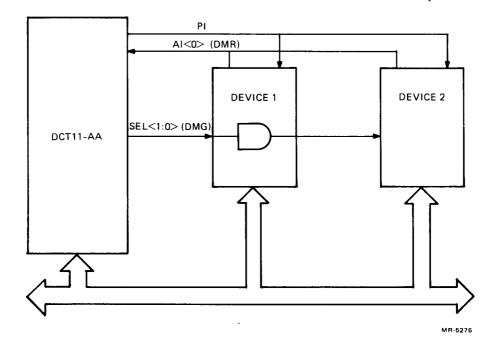

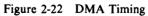

| 1-8  | DMA, Block Diagram                              | 1-9     |

| 2-1  | Parts of a Transaction                          |         |

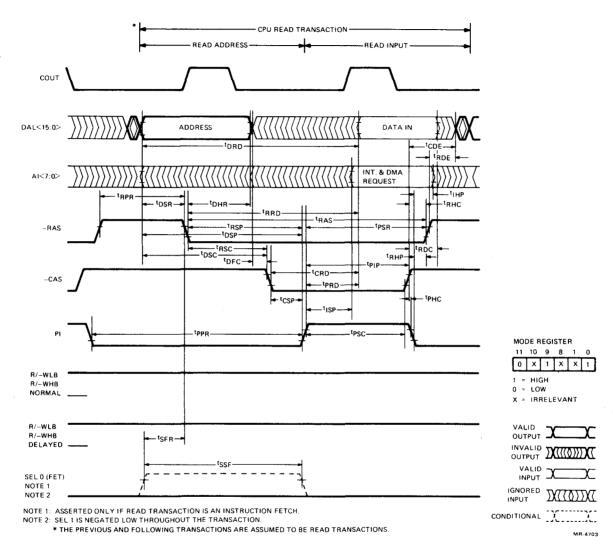

| 2-2  | 16-Bit Static Read, Block Diagram               |         |

| 2-3  | 16-Bit Static Read Timing                       |         |

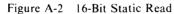

| 2-4  | 16-Bit Static Write, Block Diagram              | 2-5     |

| 2-5  | 16-Bit Static Write Timing                      | 2-5     |

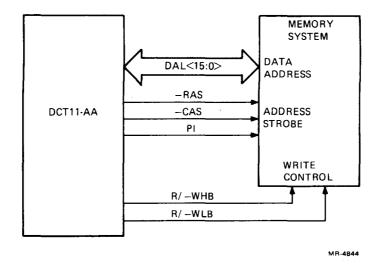

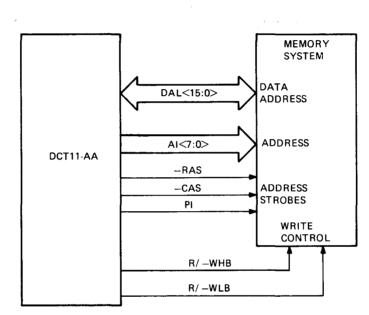

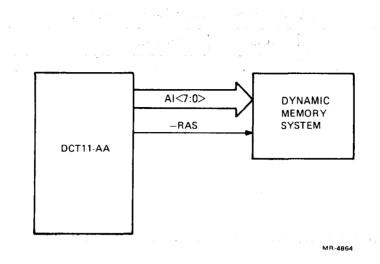

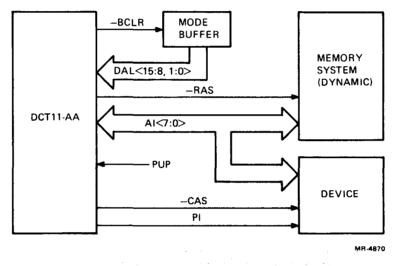

| 2-6  | 16-Bit Dynamic Read, Block Diagram              | 2-7     |

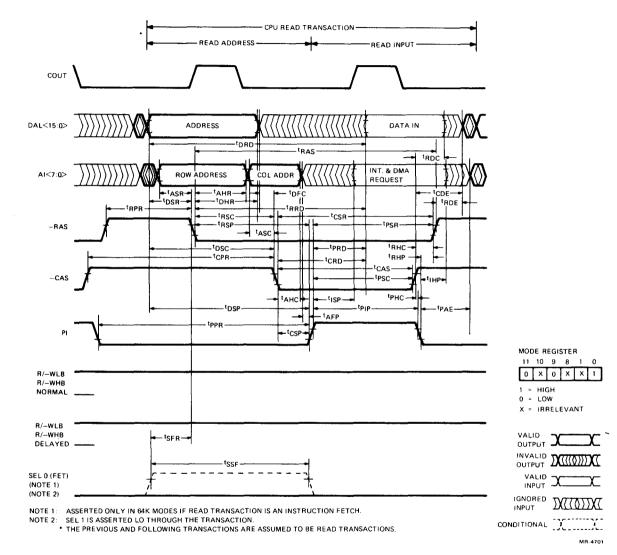

| 2-7  | 16-Bit Dynamic Read Timing                      | 2-8     |

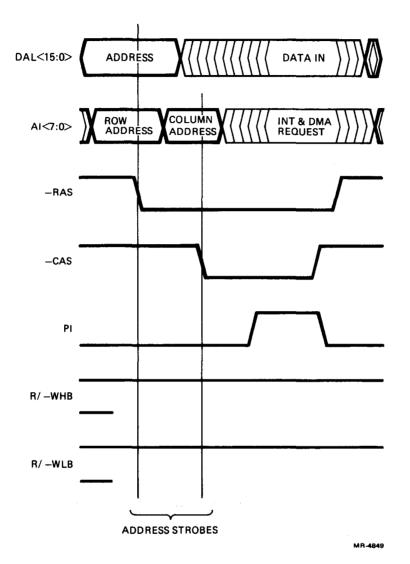

| 2-8  | 16-Bit Dynamic Write, Block Diagram             | 2-10    |

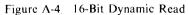

| 2-9  | 16-Bit Dynamic Write Timing                     |         |

| 2-10 | 8-Bit Static Read, Block Diagram                | 2-14    |

| 2-11 | 8-Bit Static Read Timing                        |         |

| 2-12 | 8-Bit Static Write, Block Diagram               | 2-16    |

| 2-13 | 8-Bit Static Write Timing                       |         |

| 2-14 | 8-Bit Dynamic Read, Block Diagram               |         |

| 2-15 | 8-Bit Dynamic Read Timing                       |         |

| 2-16 | 8-Bit Dynamic Write, Block Diagram              |         |

| 2-17 | 8-Bit Dynamic Write Timing                      |         |

| 2-18 | Refresh Transaction, Block Diagram              | 2-26    |

| 2-19 | Refresh Transaction Timing                      |         |

| 2-20 | IACK Transaction, Block Diagram                 | 2-20    |

| 2-21 | IACK Transaction Timing                         |         |

| 2-22 | DMA Timing                                      |         |

| 2-23 | ASPI Transaction, Block Diagram                 |         |

| 2-23 | ASPI Transaction Timing                         |         |

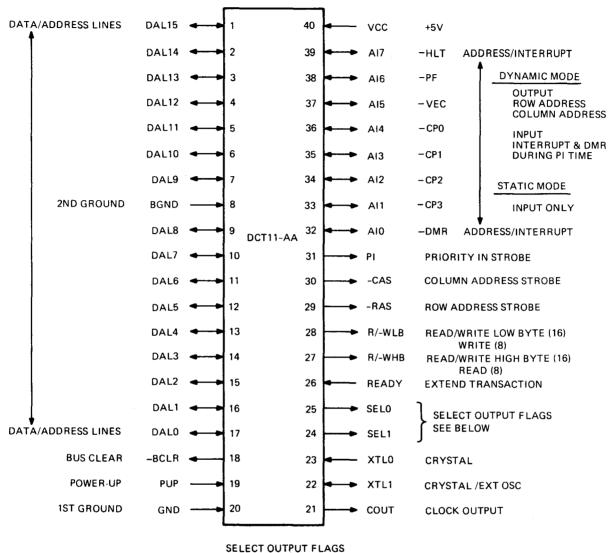

| 3-1  | DCT11-AA Pin Layout                             |         |

| 3-2  | Leading and Trailing Edge                       | 3-10    |

| 3-3  | READY Timing                                    |         |

| 3-4  | Power-Up Sequence, Block Diagram                |         |

| 3-5  | Power-Up Sequence Timing                        |         |

| 3-6  | COUT Timing                                     |         |

| 4-1  | Mode Register                                   |         |

| 5-1  | Power-Up Circuit                                |         |

| 5-2  | Mode Register Loading                           |         |

| 5-3  | Crystal Oscillator Clock                        | 5-3     |

| 5-4  | TTL Oscillator Clock                            |         |

| 5-5  | TTL Oscillator Waveform                         | 5-4     |

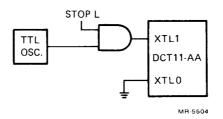

| 5-6  | Gating XTL1                                     | 5-4     |

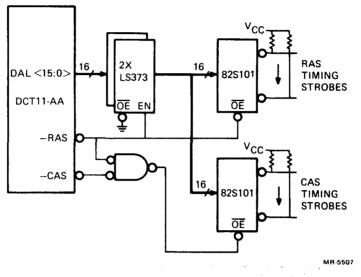

| 5-7  | 16-Bit Address Latch and Decode                 |         |

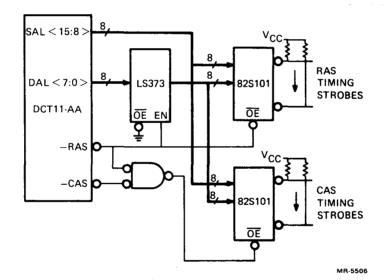

| 5-8  | 8-Bit Address Latch and Decode                  |         |

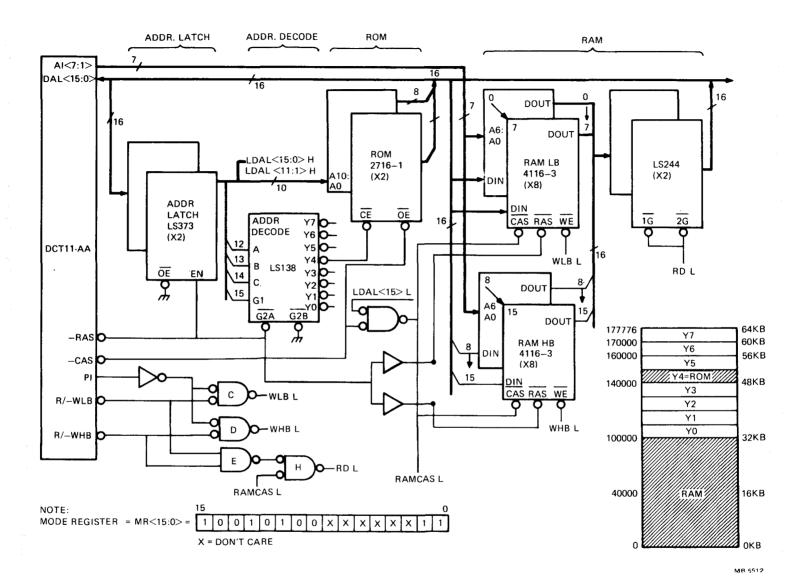

| 5-9  | 16-Bit ROM (4K) and Dynamic RAM (32K) Subsystem |         |

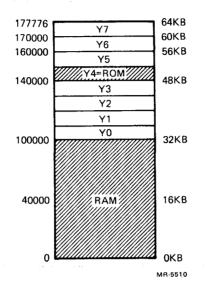

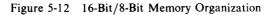

| 5-10 | 16-Bit System Memory Map.                       |         |

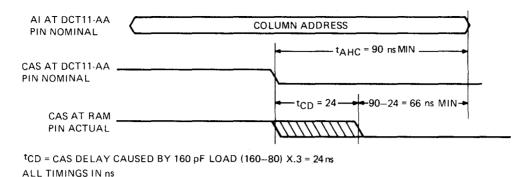

| 5-11 | Column Address Setup and Hold-Time Calculations |         |

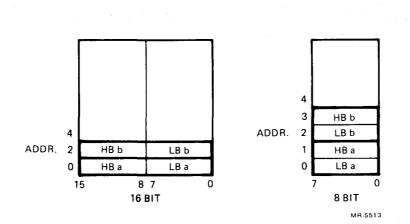

| 5-12 | 16-Bit/8-Bit Memory Organization                |         |

| 5-12 | 8-Bit System Memory Map                         |         |

| 5-14 | 8-Bit ROM (2K) and Dynamic RAM (16K) Subsystem  |         |

| 5-15 | General Interrupt                               |         |

|      | Several Interior                                | <i></i> |

# FIGURES (Cont)

# Figure No.

## Title

## Page

÷

.

| 5-16 | Decoding IACK Information for 16 CP Devices  |      |

|------|----------------------------------------------|------|

| 5-17 | Interrupt System                             | 5-13 |

| 5-18 | Driving an External Vector During IACK       | 5-14 |

| 5-19 | Interrupt Request Circuit (Priority Encoder) | 5-15 |

| 5-20 | Direct CP Encoding Interrupt System          |      |

| 5-21 | Single-Channel DMA                           | 5-18 |

| 5-22 | Software DMR Control                         |      |

| 5-23 | 8155 RAM                                     | 5-20 |

| 5-24 | 2651 PUSART                                  |      |

| 5-25 | DC003 Interrupt Logic                        |      |

| 5-26 | DC003 at Different Priority Levels           |      |

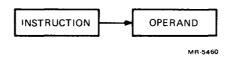

| 6-1  | Single-Operand Addressing                    |      |

| 6-2  | Double-Operand Addressing                    |      |

| 6-3  | Mode 0 Register                              |      |

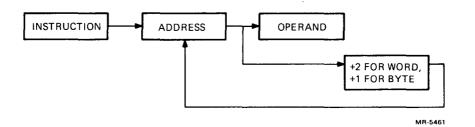

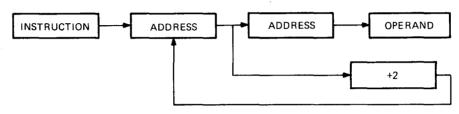

| 6-4  | Mode 2 Autoincrement                         |      |

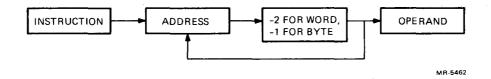

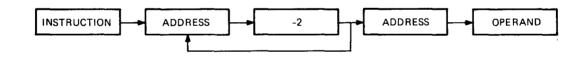

| 6-5  | Mode 4 Autodecrement                         |      |

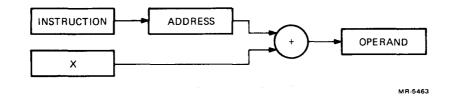

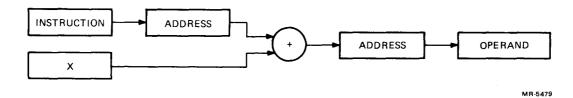

| 6-6  | Mode 6 Index                                 |      |

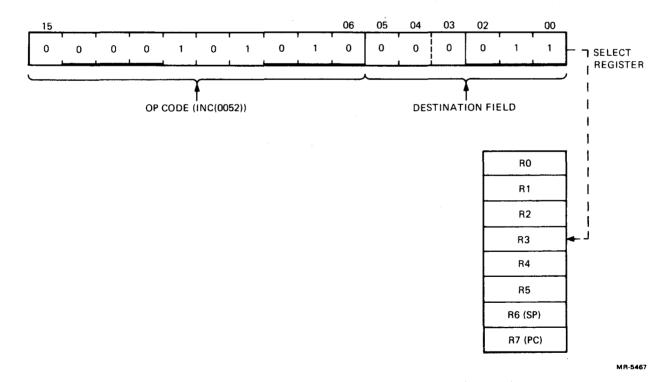

| 6-7  | INC R3 Increment                             |      |

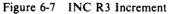

| 6-8  | ADD R2, R4 Add                               |      |

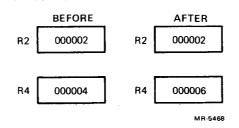

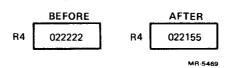

| 6-9  | COMB R4 Complement Byte                      |      |

| 6-10 |                                              |      |

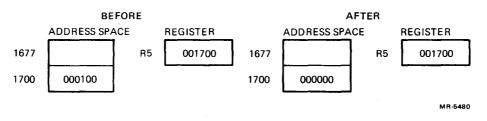

| 6-11 | CLR(R5) + Clear                              |      |

|      | CLRB(R5) + Clear Byte                        |      |

| 6-12 | ADD(R2) + R4 Add                             |      |

| 6-13 | INC –(R0) Increment                          | 6-9  |

| 6-14 | INCB – (R0) Increment Byte                   |      |

| 6-15 | ADD - (R3), R0 Add                           |      |

| 6-16 | CLR 200 (R4) Clear                           |      |

| 6-17 | COMB 200 (R1) Complement Byte                |      |

| 6-18 | ADD 30 (R2), 20 (R5) Add                     |      |

| 6-19 | Mode 1 Register-Deferred                     | 6-12 |

| 6-20 | Mode 3 Autoincrement-Deferred.               | 6-13 |

| 6-21 | Mode 5 Autodecrement-Deferred                |      |

| 6-22 | Mode 7 Index-Deferred                        |      |

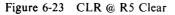

| 6-23 | CLR @ R5 Clear                               |      |

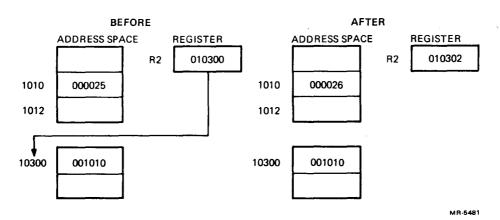

| 6-24 | INC @ (R2) + Increment                       | 6-14 |

| 6-25 | COM @ (R0) Complement                        |      |

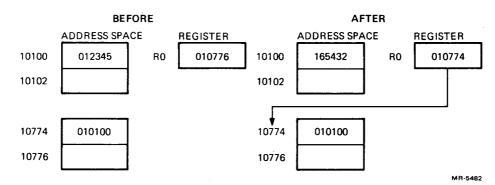

| 6-26 | ADD @ 1000 (R2), R1 Add                      | 6-15 |

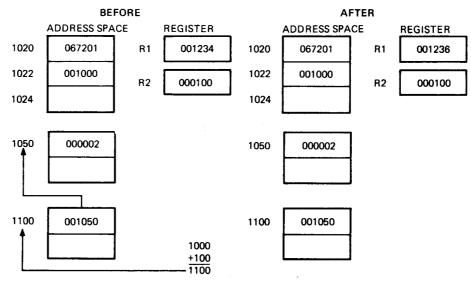

| 6-27 | ADD # 10, R0 Add                             | 6-17 |

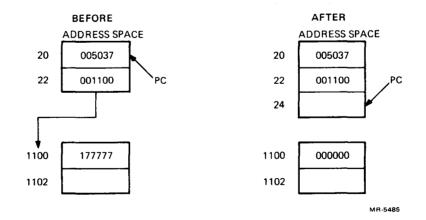

| 6-28 | CLR @ # 1100 Clear                           | 6-17 |

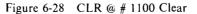

| 6-29 | ADD @ # 2000 Add                             | 6-18 |

| 6-30 | INC A Increment                              | 6-19 |

| 6-31 | CLR @ A Clear                                | 6-19 |

| 6-32 | Single-Operand Group                         |      |

| 6-33 | Double-Operand Group                         |      |

| 6-34 | Program Control Group Branch                 |      |

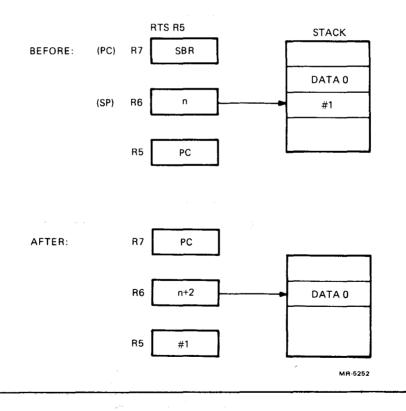

| 6-35 | Program Control Group JSR                    | 6-21 |

| 6-36 | Program Control Group RTS                    |      |

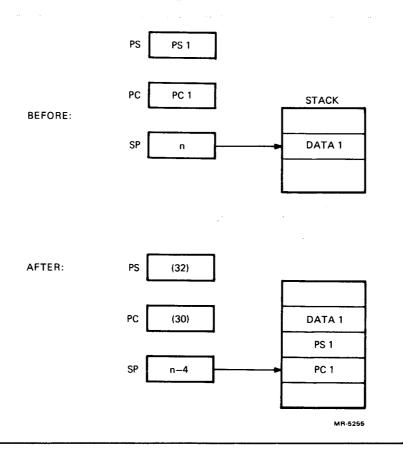

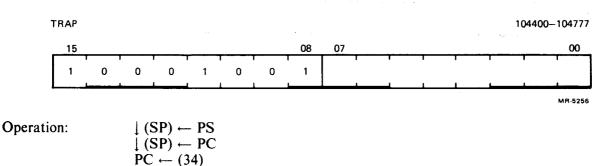

| 6-37 | Program Control Group Traps                  |      |

|      |                                              |      |

# FIGURES (Cont)

# Figure No.

حيسهم

.

# Title

Page

| ( )  |                                |      |

|------|--------------------------------|------|

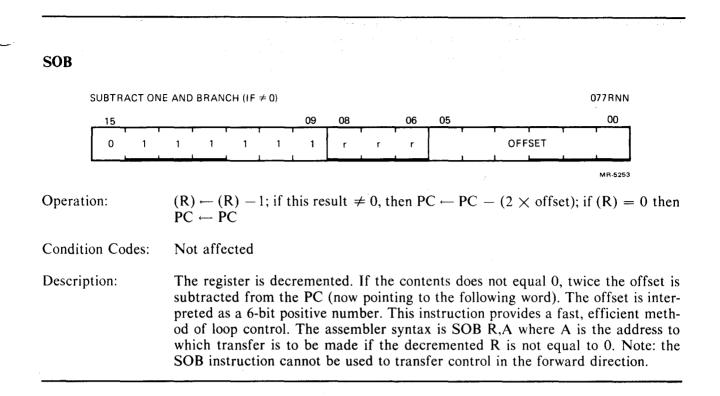

| 6-38 | Program Control Group Subtract |      |

| 6-39 | Operate Group                  |      |

| 6-40 | Condition Group                |      |

| 6-41 | Byte Instructions              | 6-23 |

| A-1  | DCT11-AA, Block Diagram        | A-23 |

| A-2  | 16-Bit Static Read             | A-24 |

| A-3  | 16-Bit Static Write            |      |

| A-4  | 16-Bit Dynamic Read            |      |

| A-5  | 16-Bit Dynamic Write           |      |

| A-6  | 8-Bit Static Read              |      |

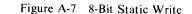

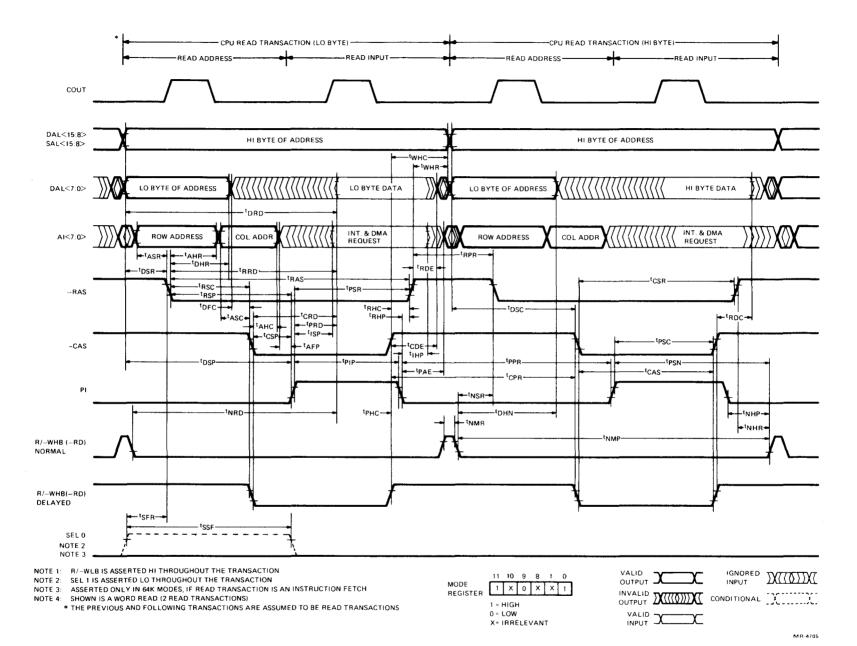

| A-7  | 8-Bit Static Write             |      |

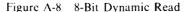

| A-8  | 8-Bit Dynamic Read             |      |

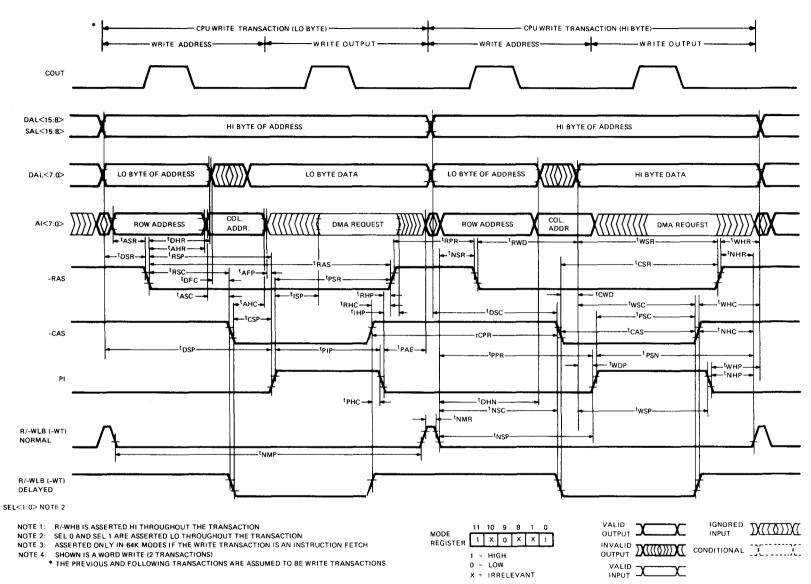

| A-9  | 8-Bit Dynamic Write            |      |

| A-10 | Refresh                        |      |

| A-11 | IACK Transaction               |      |

| A-12 | Busnop Transaction             |      |

| A-13 | DMA Transaction                |      |

| A-14 | ASPI Transaction               |      |

| A-15 | Ready                          |      |

| A-16 | Power-Up                       |      |

| A-17 | XTAL and COUT                  |      |

| A-18 | DCT11-AA Pin Layout            |      |

| A-19 | Mode Register                  |      |

| A-20 | Processor Status Word          |      |

| A-21 | 16-Bit Application             |      |

| A-22 | 8-Bit Application              |      |

|      |                                |      |

# **TABLES**

## Table No.

.

## Title

# Page

| 1-1  | Interrupt Signals                      |      |

|------|----------------------------------------|------|

| 1-2  | Interrupt Decode                       |      |

| 2-1  | 16-Bit Static Write Conditions         |      |

| 2-2  | 16-Bit Static Write Data Strobes       | 2-6  |

| 2-3  | 16-Bit Dynamic Read Addressing Scheme  | 2-8  |

| 2-4  | 16-Bit Dynamic Read AI Addressing      | 2-9  |

| 2-5  | 16-Bit Dynamic Read Address Strobes    | 2-9  |

| 2-6  | 16-Bit Dynamic Write Addressing Scheme |      |

| 2-7  | 16-Bit Dynamic Write AI Addressing     | 2-12 |

| 2-8  | 16-Bit Dynamic Write Address Strobes   | 2-12 |

| 2-9  | 16-Bit Dynamic Write Data Strobes      | 2-12 |

| 2-10 | 16-Bit Dynamic Write Conditions        |      |

| 2-11 | 16-Bit Dynamic Write Control Timing    | 2-13 |

| 2-12 | 8-Bit Static Read Control Timing       |      |

| 2-13 | 8-Bit Static Read Data Strobes         |      |

|      |                                        |      |

# TABLES (Cont)

## Table No.

## Title

## Page

| <b>•</b> • • |                                               | • • •         |

|--------------|-----------------------------------------------|---------------|

| 2-14         | 8-Bit Static Write Control Timing             |               |

| 2-15         | 8-Bit Dynamic Read Addressing Scheme          |               |

| 2-16         | 8-Bit Dynamic AI Addressing                   |               |

| 2-17         | 8-Bit Dynamic Read Address Strobes            |               |

| 2-18         | 8-Bit Dynamic Read Control Timing             | 2-20          |

| 2-19         | 8-Bit Dynamic Write Addressing Scheme         | 2-24          |

| 2-20         | 8-Bit Dynamic Write AI Addressing             | 2-24          |

| 2-21         | 8-Bit Dynamic Write Address Strobes           | 2-24          |

| 2-22         | 8-Bit Dynamic Write Data Strobes              | 2-24          |

| 2-23         | 8-Bit Dynamic Write Control Timing            | 2-25          |

| 2-24         | Interrupt Acknowledge Data                    |               |

| 3-1          | Mapping of AI onto DAL in an IACK Transaction | 3-1           |

| 3-2          | Signal and Pin Utilization, 16-Bit Mode       |               |

| 3-3          | Signal and Pin Utilization, 8-Bit Mode        |               |

| 3-4          | SEL<1:0> Functions in Static Mode             |               |

|              | or Dynamic 64K Mode                           | 3-5           |

| 3-5          | SEL<1:0> Functions in Dynamic 4K/16K Mode     |               |

| 3-6          | AI Functions                                  |               |

| 3-7          | Control Signal Usage                          |               |

| 3-8          | Refresh and Busnop                            |               |

| 4-1          | Mode Register Bit Settings                    | 4-2           |

| 4-2          | DCT11-AA Modes                                |               |

| 5-1          | Control Signals for Each Transaction          |               |

| 5-2          | Data Bus for Each Transaction                 |               |

| A-1          | Interrupt Decode.                             |               |

| A-2          | DC Characteristics                            |               |

| A-3          | Sequences of Transactions                     |               |

| A-4          | Signal and Pin Utilization, 16-Bit Mode       | A-5           |

| A-5          | Signal and Pin Utilization, 8-Bit Mode        |               |

| A-6          | 16-Bit Dynamic Write Addressing Scheme        |               |

| A-7          | SEL<1:0> Functions in Static Mode             | 2 <b>x</b> -7 |

| 1 1-1        | or Dynamic 64K Mode                           | Δ_7           |

| A-8          | SEL<1:0> Functions in Dynamic 4K/16K Mode     |               |

| A-9          | AI Functions                                  |               |

| A-10         | Control Signals for Each Transaction          |               |

| A-11         | Data Bus for Each Transaction                 |               |

| A-12         | Summary of DCT11-AA Instructions              |               |

| A-13         | Numerical Op Code List                        |               |

| A-14         | Reserved Trap and Interrupt Vectors           |               |

| A-14<br>A-15 | 7-Bit ASCII Code                              |               |

| A-16         | Octal, Hex, Decimal Memory Addresses          |               |

| A-17         | XOR and Single-Operand Instructions           |               |

| A-18         | Double-Operand Instructions.                  |               |

| A-19         | Jump and Subroutine Instructions              |               |

| A-20         | Branch, Trap, and Interrupt Instructions      | A-18          |

| A-20<br>A-21 | Miscellaneous and Condition Code Instructions |               |

| A-21<br>A-22 | Maximum Latencies                             |               |

|              |                                               |               |

# TABLES (Cont)

## Table No.

# Title

| B-1        | Processor Codes                                  | B-4          |

|------------|--------------------------------------------------|--------------|

| <b>B-2</b> | PDP-11 Instructions Not Executed by the DCT11-AA | <b>B-</b> 7  |

| B-3        | Interrupt Priority Codes                         | B-10         |

| B-4        | Start/Restart Addresses                          |              |

| B-5        | Software Differences and Compatibilities         | B-12         |

| <b>B-6</b> | Hardware Differences – Traps                     |              |

|            | (Transparent to Software)                        | <b>B-2</b> 1 |

## PREFACE

This user's guide is designed for engineers familiar with PDP-11 architecture. Chapters 1 through 6 offer a tutorial on DCT11-AA architecture and operation. (Chapter 5 includes some design examples.) Appendix A contains reference material (instruction set tables and timing diagrams). Appendix B briefly describes the software differences and compatibilities among the DCT11-AA and other members of the PDP-11 family.

This guide can be used by both hardware and software specialists. The hardware specialist should especially become familiar with Chapters 1 through 5, whereas the software specialist should become familiar with Chapters 1, 4, and 6.

One of the characteristics of the DCT11-AA is that it can be user-programmed to operate in a variety of modes, which affect both its functionality and timing. Chapter 2 (Bus Transactions) and Chapter 3 (Pin Descriptions) are arranged by mode. This allows the user to find, in one place, all the information relevant to a selected mode. A user not knowing which mode to use for a given application should first read Chapter 4 (Mode Selection).

## CHAPTER 1 ARCHITECTURE

#### **1.1 INTRODUCTION**

This chapter describes the internal architecture of the DCT11-AA microprocessor. The chapter is divided into five sections covering all aspects of the architecture:

- Registers

- Arithmetic and logic unit (ALU)

- DCT11-AA hardware stack

- Interrupts

- DMA mechanism

#### **1.2 REGISTERS**

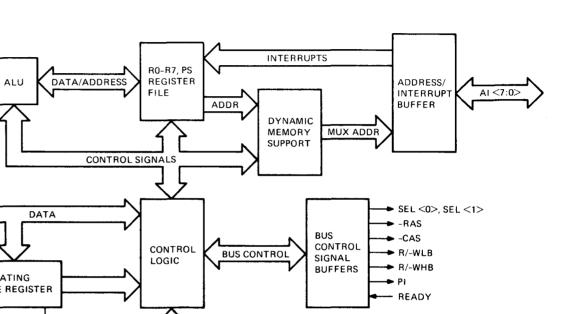

The DCT11-AA contains a number of internal registers used for various purposes (refer to Figure 1-1). The registers are divided into three groups:

- General-Purpose

- Status

- Mode

#### **1.2.1 General-Purpose Registers**

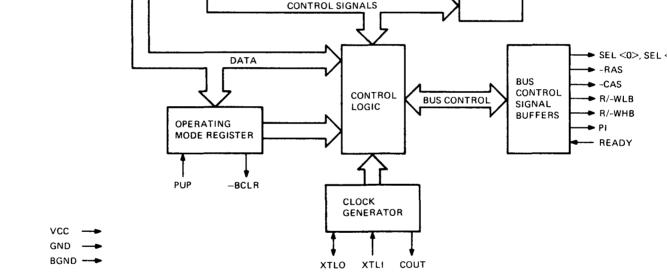

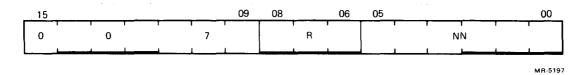

The DCT11-AA microprocessor contains eight 16-bit general-purpose registers that can perform a variety of functions. These registers can serve as accumulators, index registers, autoincrement registers, autodecrement registers, or stack pointers for temporary storage of data. Arithmetic operations can be performed between one general-purpose register and another, one memory location or device register and another, between memory locations, or between a device register and a general register. The eight 16-bit general-purpose registers (R0–R7) are identified in Figure 1-2.

Figure 1-1 DCT11-AA, Block Diagram

í

DAL <15:8>

DAL <7:0>

DATA/ ADDRESS BUFFER (IN/OUT)

DATA/ADDRESS

PRELIMINARY

MR 5759

Registers R6 and R7 in the DCT11-AA are dedicated. R6 serves as the stack pointer (SP) and contains the location (address) of the last entry in the stack. Register R7 serves as the processor program counter (PC) and contains the address of the next instruction to be executed. The PC is normally used for addressing purposes only and not as an accumulator.

#### 1.2.2 Status Register

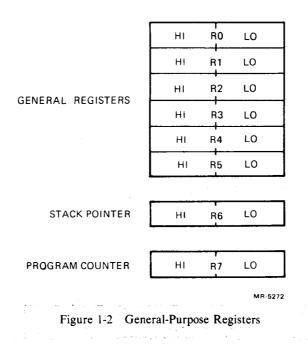

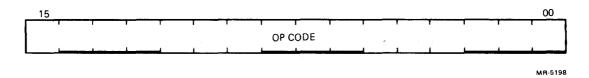

The processor status word (PSW) contains information on the current processor status. This information includes the current processor priority, the condition codes describing the arithmetic or logic results of the last instruction, and an indicator for detecting the execution of an instruction to be trapped during program debugging. This indicator (the T bit) cannot be directly set or cleared. The T bit can only be set or cleared when entering or exiting an interrupt routine.

The PSW format is shown in Figure 1-3. Certain instructions allow programmed manipulation of condition code bits and loading and storing (moving) the processor status.

1-3

#### 1.2.3 Mode Register

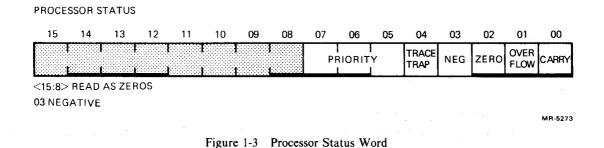

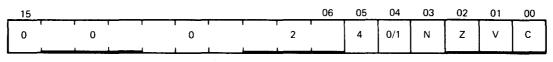

The DCT11-AA incorporates a user-loadable mode register (refer to Figure 1-4). The mode register is loaded at power-up or when a reset instruction is issued. Access to the mode register is not possible at any other time. The user has the option of selecting any combination of the following modes.

- 16-bit or 8-bit data bus

- Dynamic or static memory support

- 64K or 4K/16K dynamic memory support

- Constant or processor clock

- Long or standard microcycle

- Normal or delayed read/write timing

- Tester or user operation

- One of eight start/restart address pairs

A complete discussion of the mode register is contained in Chapter 4.

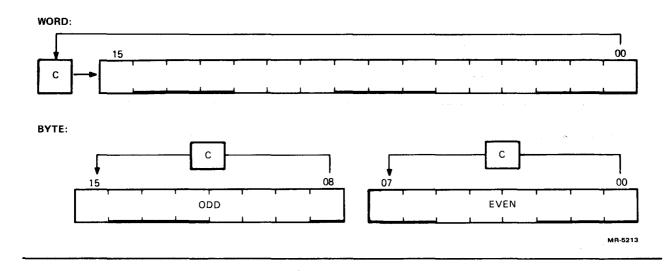

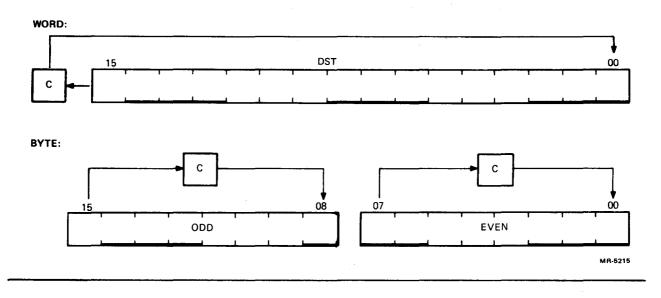

| 15     | 14          | 13              | 12     | 11              | 10            | 09          | 08            | 07    | 06    | 05     | 04     | 03     | 02     | 01          | 00              |

|--------|-------------|-----------------|--------|-----------------|---------------|-------------|---------------|-------|-------|--------|--------|--------|--------|-------------|-----------------|

| STAI   | I<br>RT/RES | I<br>START<br>L |        | 16-BIT<br>8-BIT | 64K<br>4K/16K | DYN<br>STAT | NORM<br>DELAY |       |       |        |        | I<br>I |        | LONC<br>STD | G CONST<br>PROC |

| <15:13 | > st        | ART/R           | ESTAR  | T ADD           | RESS          |             |               |       |       |        |        |        | -      |             |                 |

| 12     | TE          | STER/           | USER N | IODE            |               |             | 08            | NO    | RMA   | L/DELA | YED R/ | w      |        |             |                 |

| 11     | 16          | BIT/8-          | BIT BU | s               |               |             | <7:2>         | RE    | SERV  | ED     |        |        |        |             |                 |

| 10     | 64          | K/4K 0          | R 16K  | мемо            | RY            |             | 01            | LC    | NG/ST | TANDA  | RD MIC | ROCYC  | CLE    |             |                 |

| 09     | DI          | YNAMI           | C/STAT | IC MEN          | NORY          |             | 00            | CC    | NSTA  | NT/PRC | CESSO  | r mod  | E CLOC | к           |                 |

|        |             |                 |        |                 |               |             |               |       |       |        |        |        |        |             |                 |

| ADDR   | ESS BIT     | S               | START  |                 |               |             | RESTAR        | ят    |       |        |        |        |        |             |                 |

| <15    | 5:13>       |                 | ADDR   | ESS             |               |             | ADDRE         | SS    |       |        |        |        |        |             |                 |

|        |             |                 |        |                 |               |             |               |       |       |        |        |        |        |             | -               |

|        | 7           |                 | 172000 | )               |               |             | 172004        |       |       |        |        |        |        |             |                 |

|        | 6           |                 | 173000 | )               |               |             | 173004        |       |       |        |        |        |        |             |                 |

|        | 5           |                 | 000000 | )               |               |             | 000004        |       |       |        |        |        | •      |             |                 |

|        | 4           |                 | 010000 | )               |               |             | 010004        |       |       |        |        |        |        |             |                 |

|        | 3           |                 | 020000 | )               |               |             | 020004        |       |       |        |        |        |        |             |                 |

|        | 2           |                 | 040000 | )               |               |             | 040004        |       |       |        |        |        |        |             |                 |

|        | 1           |                 | 100000 | )               |               |             | 100004        |       |       |        |        |        |        |             |                 |

|        | 0           |                 | 140000 | )               |               |             | 140004        |       |       |        |        |        |        |             |                 |

|        |             |                 |        |                 |               |             | **            | - · · |       |        |        |        |        |             |                 |

Figure 1-4 Mode Register

MR 4843

÷

#### **1.3 ARITHMETIC LOGIC UNIT (ALU)**

Arithmetic and logical instructions of the 16-bit CPU are executed in the ALU. The ALU internally communicates with registers and buffers in order to execute instructions.

#### 1.4 DCT11-AA HARDWARE STACK

The hardware stack is part of the basic design architecture of the DCT11-AA. It is an area of memory set aside by the programmer or by the operating system for temporary storage and linkage. It is handled on a LIFO (last in/first out) basis, where items are retrieved in the reverse of the order in which they were stored. On the DCT11-AA the stack starts at the highest location reserved for it ( $376_8$  at power-up) and expands linearly downward to a lower address as items are added to the stack. There is no stack overflow warning.

It is not necessary to keep track of the actual locations into which data is being stacked. This is done automatically through the use of the stack pointer (SP). Register six (R6) always contains the memory

address of the last item stored in the stack. Instructions associated with subroutine linkage and interrupt service automatically use register six as the hardware stack pointer. For this reason, R6 is frequently referred to as the system SP. The hardware stack is organized in full-word units only.

#### **1.5 INTERRUPTS**

Interrupts are requests (made by peripheral devices) that cause the processor to temporarily suspend its present program execution to service the requesting device. A device can interrupt the processor only when its priority is higher than the processor priority indicated by PSW < 7:5 > .

The DCT11-AA supports a vectored interrupt structure (with optional internally generated vector addresses) with priority on four levels encoded on four lines. In addition, on separate pins it supports two nonmaskable interrupts, power fail (-PF) and -HALT.

#### 1.5.1 Interrupt Mechanism

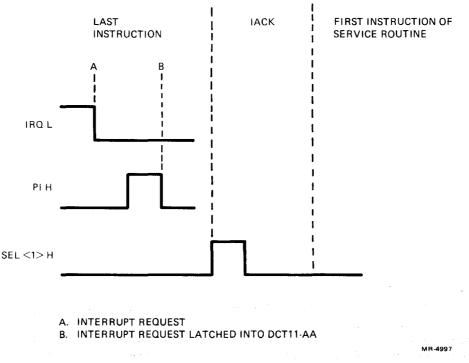

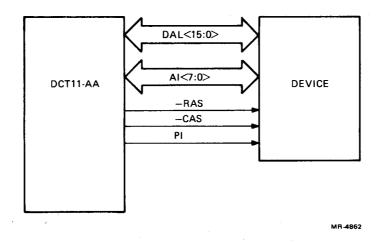

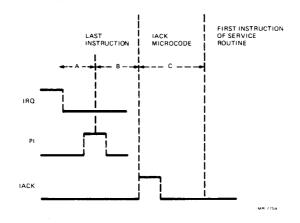

When the DCT11-AA receives an interrupt, no action is taken until the end of the current instruction (refer to Figure 1-5). Interrupts are only read during a read transaction or assert priority in (ASPI) transaction. Before fetching the next instruction, the DCT11-AA arbitrates the interrupt priority. If the interrupt request has a higher priority than the processor's, it initiates an interrupt acknowledge (IACK) transaction (refer to Paragraph 2.12). Following the IACK transaction, the current PC and PSW are saved on the stack and the new PC and PSW are loaded from the vector address.

#### **1.5.2** Interrupt Posting

With the assertion of the priority in (PI) signal, interrupts are read into the DCT11-AA during any read transaction and ASPI transaction. Interrupts are read in only at the occurrence of PI.

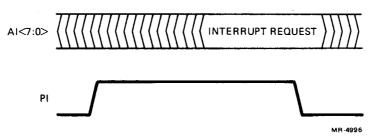

#### 1.5.3 Interrupt Request (IRQ)

During the assertion of PI the interrupt request is read by the DCT11-AA (refer to Figures 1-5 and 1-6). Refer to Table 1-1 for signal names. Interrupt requests are implemented from the following seven different signals.

Figure 1-5 Interrupt Request

Maskable interrupts:

• -CP < 3:0> (coded priority)

Nonmaskable interrupt:

-PF (power fail)

-HALT (halt)

Control (internal or external) vector:

• - VEC (vector)

| Interrupt | Pin   | Pin    |

|-----------|-------|--------|

| Signals   | Name  | Number |

| -CP<3>    | AI<1> | 33     |

| -CP<2>    | AI<2> | 34     |

| -CP<1>    | AI<3> | 35     |

| -CP<0>    | AI<4> | 36     |

| -VEC      | AI<5> | 37     |

| -PF       | AI<6> | 38     |

| -HALT     | AI<7> | 39     |

Table 1-1

Interrupt Signals

The DCT11-AA detects an interrupt request if during the assertion of PI at least one of the following signals is asserted low.

- -CP<3> (AI<1>)

- -CP < 2> (AI < 2>)

- -CP<1> (AI<3>) • -CP<0> (AI<4>)

- -PF (AI<6>)

- -HALT (AI<7>)

#### 1.5.4 Vectors

Every interrupt except -HALT is associated with an interrupt vector. An interrupt vector consists of two words: the next PC and next PSW. The PC is the address of the routine to service an interrupt device. The PSW has new information to load into the processor status register. After the IACK transaction, the current PC and PSW are saved on the stack and the new PC and PSW are loaded from the vector address.

Up to 64 vectors may reside in the first 256 memory locations ( $374_8$  is the highest vector location). The vector address is provided by the interrupting device (external vector address) or by a fixed table stored in the DCT11-AA (internal vector address).

#### NOTE

The power fail (-PF) interrupt uses interrupt vector address 24 and is not acknowledged with an IACK transaction. (Refer to Paragraph 2.12.) The -HALT interrupt is not associated with a vector; it pushes the PC and PSW onto the stack and immediately goes to the restart address with PSW (340<sub>8</sub>). -HALT is not acknowledged.

**1.5.4.1** Internal Vector Address – If -VEC (AI<5>) is not asserted (high) during the assertion of PI, the DCT11-AA gets the vector address from an internal fixed table by decoding the inputs -HALT, -PF, and -CP<3:0>. Refer to Table 1-2.

|        |                   | Table             |                   |                   |                   |                   |

|--------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

|        | -CP<3><br>(Al<1>) | -CP<2><br>(AI<2>) | -CP<1><br>(AI<3>) | -CP<0><br>(AI<4>) | Priority<br>Level | Vector<br>Address |

| -HALT* | x                 | x                 | х                 | x                 | 8                 | -                 |

| – PF   | X                 | X                 | X                 | X                 | 8                 | 24                |

|        | L                 | L                 | L                 | L                 | 7                 | 140               |

|        | L                 | L                 | L                 | Н                 | 7                 | 144               |

|        | L                 | L                 | Н                 | L                 | 7                 | 150               |

|        | L                 | L                 | н                 | Н                 | 7                 | 154               |

|        | L                 | Н                 | L                 | L                 | 6                 | 100               |

|        | L                 | н                 | L                 | Н                 | 6                 | 104               |

|        | L                 | Н                 | Н                 | L                 | 6                 | 110               |

|        | L                 | Н                 | Н                 | Н                 | 6                 | 114               |

|        | Н                 | L                 | L                 | L                 | 5                 | 120               |

|        | н                 | L                 | L                 | Н                 | 5                 | 124               |

|        | Н                 | L                 | Н                 | L                 | 5                 | 130               |

|        | Н                 | L                 | Н                 | Н                 | 5                 | 134               |

|        | н                 | Н                 | L                 | L                 | 4                 | 60                |

|        | Н                 | н                 | L                 | н                 | 4                 | 64                |

|        | Н                 | Н                 | Н                 | L                 | 4                 | 70                |

|        | н                 | н                 | Н                 | н                 | No action         |                   |

|        |                   |                   |                   |                   |                   |                   |

\*PC is loaded with the restart address; PSW = 340.

**1.5.4.2** External Vector Address – If during the assertion of PI (-PF or -HALT not asserted) -VEC (AI<5>) is asserted (low), the DCT11-AA obtains the vector from the external device during an IACK transaction. Asserting READY causes the DCT11-AA to wait for the vector.

#### 1.5.5 Priority

Each interrupt is assigned a priority level (refer to Table 1-2). The DCT11-AA divides interrupts into two groups:

- Maskable

- Nonmaskable

**1.5.5.1** Maskable Interrupts – Interrupts on -CP < 3:0> are maskable. The interrupts are serviced according to their priority level (refer to Table 1-2).

#### NOTE

As in any multilevel priority structure, the PSW of the service routine must contain a priority level as high or higher than that of the interrupt request. Otherwise, the interrupt request continues to cause IACK transactions until the stack is full. (Refer to Paragraph 2.12.)

**1.5.5.2** Nonmaskable Interrupts – The -HALT interrupt has the highest priority; it interrupts the processor whatever the processor's status.

#### NOTE

The -HALT interrupt or execution of the -HALT instruction results in an interrupt, not in a stopping of the processor.

#### 1.6 DIRECT MEMORY ACCESS (DMA) MECHANISM

During a DMA transaction the only lines that are three-stated are DAL<15:0>. Low current pull-ups are placed on:

- AI < 7:0 >

- R/-WHB

- $\mathbf{R}' \mathbf{WLB}$

The processor maintains control of -RAS, -CAS, and PI.

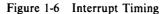

A device requests control of the DMA bus (DAL<15:0>, AI<7:0>, R/-WHB, and R/-WLB) by asserting direct memory request [(DMR (AI<0>)] during the assertion of PI (refer to Figure 1-7). DMR is read during any assertion of PI, unlike interrupts that are read only during a read or ASPI transaction. The processor waits for the end of the current transaction (read, write, DMG, or ASPI) and then releases the DMA bus. The requesting device is signaled (by the processor) when it asserts the two signals:

- SEL<0> (high)

- SEL < l > (high)

SEL < 0 > and SEL < 1 > indicate a direct memory grant (DMG).

The requesting device, having received DMG, performs the DMA by controlling the DMA bus. The processor continues to output PI in order to allow the negation of DMR. The device holds control of the DMA bus until DMR is negated during PI. Multiple DMA devices can be implemented using a daisy-chain structure, as shown in Figure 1-8.

1-9

7

# CHAPTER 2 BUS TRANSACTIONS

#### 2.1 INTRODUCTION

This chapter provides a basic discussion of each bus transaction. Paragraphs 2.3 through 2.10 pertain to the read and write transactions. The details of the read and write transactions change considerably in each of the following modes.

- 8-bit static

- 8-bit dynamic

- 16-bit static

- 16-bit dynamic

Therefore, a separate discussion of each read and write transaction is presented. All other transactions are described as they apply to the DCT11-AA bus.

#### 2.2 BUS TRANSACTION

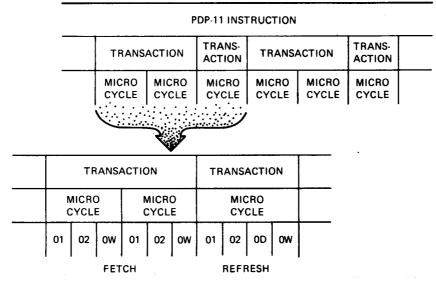

Refer to Figure 2-1. Each PDP-11 instruction is composed of a number of transactions.

MR-4842

Figure 2-1 Parts of a Transaction

#### 2.2.1 Transaction

A transaction is defined as an activity that takes place on the DCT11-AA bus in order to perform a function such as:

- Read

- Write

- Refresh

- IACK (interrupt acknowledge)

- DMA (direct memory access)

- ASPI (assert priority in)

- NOP (no operation)

#### 2.2.2 Microcycle

Each transaction is made up of either one or two microcycles. A microcycle is defined as the activity required for one microinstruction to be executed. The microcycle performs the functions necessary to transfer information to and from the DCT11-AA bus, move data internally, and calculate values.

#### 2.2.3 Clock Phase

The basic building block of the DCT11-AA timing is the clock phase. Each microcycle is normally constructed of three clock phases:  $\phi_1$ ,  $\phi_2$ , and  $\phi_W$ . During an ASPI transaction, IACK transaction, DMA transaction, or when operating in long microcycle mode, it is necessary to add a fourth phase, phase D ( $\phi$ D), between  $\phi_2$  and  $\phi_W$ . All clock phases have the same duration between assertions.

#### 2.3 16-BIT STATIC READ TRANSACTION

A read transaction consists of three distinct processes:

- Output of address

- Input of data

- Input of interrupt and DMA request (refer to Paragraphs 1.5 and 2.14)

Detailed timing of a 16-bit static read transaction is found in Figure A-2 in Appendix A.

#### NOTE All references to input or output are to the processor.

#### 2.3.1 Output of Address

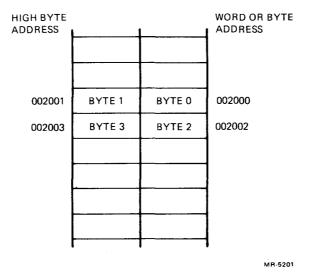

Refer to Figures 2-2 and 2-3. The address is output on the data address lines (DALs) 15-0 (<15:0>). The condition of DAL<0> indicates the address of a word, high byte, or low byte. Data address lines are time multiplexed and are used for both address and data.

Address Control – Refer to Figures 2-2 and 2-3. Address strobe, which is used to latch the address into the memory system or register, is accomplished by means of row address strobe (-RAS). The address is latched upon the assertion (leading edge) of -RAS.

#### 2.3.2 Input of Data

The input data should be valid on DAL<15:0> during the period that priority in (PI) is asserted (refer to Figure 2-3).

Figure 2-2 16-Bit Static Read, Block Diagram

MR-4845

Figure 2-3 16-Bit Static Read Timing

**Data Control** – The data strobe, which the processor uses to latch the input data, is accomplished by means of column address strobe (-CAS). The data is latched upon the negation (trailing edge) of -CAS. Read/write control is accomplished through the use of two signals:

- Read/-Write High Byte (R/-WHB)

- Read/-Write Low Byte (R/-WLB)

Both these signals remain high during a read transaction.

#### 2.3.3 Instruction Fetch

An instruction fetch is indicated by two signals:

• SEL<0> high

• SEL < 1 > low

Refer to Figure A-2 in Appendix A.

#### 2.4 16-BIT STATIC WRITE TRANSACTION

A write transaction is composed of three distinct processes:

- Output of address

- Output of data

- Input of DMA request (refer to Paragraph 2.14)

Detailed timing of a 16-bit static write transaction is found in Figure A-3 of Appendix A.

#### NOTE

All references to input or output are to the processor.

#### A write transaction is always preceded by a read transaction (the two are indivisible) except when writing the stack during an interrupt or trap.

#### 2.4.1 Output of Address

Refer to Figures 2-4 and 2-5. The address is output on DAL<15:0>. The condition of DAL<0> indicates the addressing of a word, high byte, or low byte. Refer to Table 2-1. DAL<15:0> are time multiplexed and used for both address and data.

Address Control – Address strobe, which is used to latch the address into the memory system or register, is accomplished by means of -RAS. The address is latched upon the assertion (leading edge) of -RAS.

#### 2.4.2 Output of Data

Refer to Figure 2-5. The data is output on DAL<15:0> before the assertion (leading edge) of PI.

**Data Control** – The signal used to latch the data into the memory system or register and the edge required is found in Table 2-2. Write control is accomplished through the use of two signals:

- R/-WHB

- $\mathbf{R}' \mathbf{W} \mathbf{L} \mathbf{B}$

Table 2-1 indicates the conditions necessary to address and write a memory.

Figure 2-4 16-Bit Static Write, Block Diagram

Figure 2-5 16-Bit Static Write Timing

| Addressed Memory | Address                | R/-WHB | R/-WLB |

|------------------|------------------------|--------|--------|

| Word             | Even (DAL $<0>=0$ )    | 0      | 0      |

| Low byte         | Even $(DAL < 0 > = 0)$ | 1      | 0      |

| High byte        | Odd (DAL < 0 > = 1)    | 0      | 1      |

#### Table 2-2 16-Bit Static Write Data Strobes

| Signal | Edge                |

|--------|---------------------|

| – RAS  | Negation (trailing) |

| – CAS  | Negation (trailing) |

| PI     | Assertion (leading) |

| PI     | Negation (trailing) |

#### 2.5 16-BIT DYNAMIC READ TRANSACTION

A read transaction consists of three distinct processes:

- Output of address

- Input of data

- Input of interrupt and DMA request (refer to Paragraphs 1.5 and 2.14)

Detailed timing of a 16-bit dynamic read transaction is found in Figure A-4 in Appendix A.

#### NOTE

#### All references to input or output are to the processor.

#### 2.5.1 Output of Address

Both static and dynamic addresses are output concurrently while in dynamic mode.

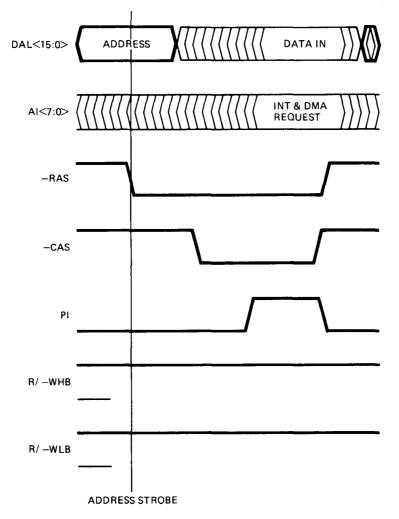

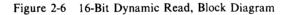

**2.5.1.1** Dynamic Address – Refer to Figures 2-6 and 2-7. The address is output on the address interrupt (AI) lines 7-0 (<7:0>). The AI lines output the row address first and the column address second. Table 2-3 lists the address bits required in 4K/16K mode and 64K mode.

#### NOTE

#### The AI lines are not in order. Refer to Table 2-4.

**2.5.1.2** Static Address – The addressing of a static ROM, RAM, or register in a system supporting dynamic devices is accomplished by outputs concurrent with the AI<7:0>. The concurrent address is output on DAL<15:0>.

**2.5.1.3** Address Control – Table 2-5 indicates the signals and edges required to latch each portion of the address into the memory system or register.

#### 2.5.2 Input of Data

Refer to Figure 2-7. The input data should be valid on DAL<15:0> during the period of time that PI is asserted. The negation of -CAS strobes the data into the DCT11-AA.

MR-4848

,

2-7

Figure 2-7 16-Bit Dynamic Read Timing

| Table 2-3 | 16-Bit | Dynamic | Read | Addressing | Scheme |

|-----------|--------|---------|------|------------|--------|

|-----------|--------|---------|------|------------|--------|

| Mode          | Memory Chip               | Address          | AI Used        |

|---------------|---------------------------|------------------|----------------|

| 4K/16K        | <b>4K</b> × 1             | A1-A12           | <6:1>          |

| 4K/16K<br>64K | $16K \times 1$<br>64K × 1 | A1-A14<br>A1-A15 | <7:1><br><7:0> |

|                                                      | Address         |      |         |      |  |  |

|------------------------------------------------------|-----------------|------|---------|------|--|--|

| AI                                                   | 4K/16K<br>- RAS | -CAS | 64K<br> | -CAS |  |  |

| <0>                                                  | FET             | A14  | A15     | A14  |  |  |

| <1>                                                  | A1              | A2   | A1      | A2   |  |  |

| <2>                                                  | A3              | A4   | A3      | A4   |  |  |

| <3>                                                  | A5              | A6   | A5      | A6   |  |  |

| <4>                                                  | A7              | A8   | A7      | A8   |  |  |

| <5>                                                  | A9              | A10  | A9      | A10  |  |  |

| <6>                                                  | A11             | A12  | A11     | A12  |  |  |

| <0><br><1><br><2><br><3><br><4><br><5><br><6><br><7> | A13             | A14  | A13     | A12  |  |  |

Table 2-4 16-Bit Dynamic Read AI Addressing

Table 2-5

16-Bit Dynamic Read Address Strobes

| Address | Signal | Edge                | Device            | R/-WHB | R/-WLB |

|---------|--------|---------------------|-------------------|--------|--------|

| Row     | -RAS   | Assertion (leading) | Dynamic           | 1      | 1      |

| Column  | -CAS   | Assertion (leading) | Dynamic           | 1      | 1      |

| DAL     | -RAS   | Assertion (leading) | Dynamic or static | 1      | 1      |

**Data Control** – The data strobe, which the processor uses to latch the input data, is accomplished by means of -CAS. The data is latched upon the negation (trailing edge) of -CAS. Write control is accomplished through the use of two signals:

• R/-WHB

• R' - WLB

Both these signals remain high during a read transaction.

#### 2.5.3 Instruction Fetch

An instruction fetch is indicated by different signals, depending on the mode. Refer to Tables A-4, A-7, and Figure A-4 in Appendix A.

**2.5.3.1** 4K/16K Mode – In 4K/16K 16-bit dynamic mode, AI < 0> is asserted at the leading edge of –RAS to indicate a fetch operation. AI < 0> is three-stated before the leading edge of PI. Fetch is indicated by AI < 0> high during –RAS.

#### NOTE

# During refresh the AI lines have the refresh counter address on them.

**2.5.3.2** 64K Mode – Static modes and 64K use SEL<0> high and SEL<1> low to indicate a fetch condition. When SEL<0> signifies a fetch, it is asserted only during the read cycle. Fetch is indicated by SEL<0> high and SEL<1> low.

#### 2.6 16-BIT DYNAMIC WRITE TRANSACTION

A write transaction consists of three distinct processes:

- Output of address

- Output of data

- Input of DMA request (refer to Paragraph 2.14)

Detailed timing of a 16-bit dynamic write transaction is found in Figure A-5 of Appendix A.

#### NOTE

#### All references to input or output are to the processor.

#### A write transaction is always preceded by a read transaction (the two are indivisible) except when writing the stack during an interrupt or trap.

#### 2.6.1 Output of Address

Both static and dynamic addresses are output concurrently while in dynamic mode.

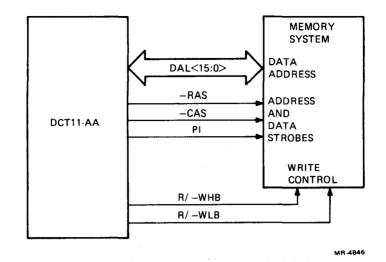

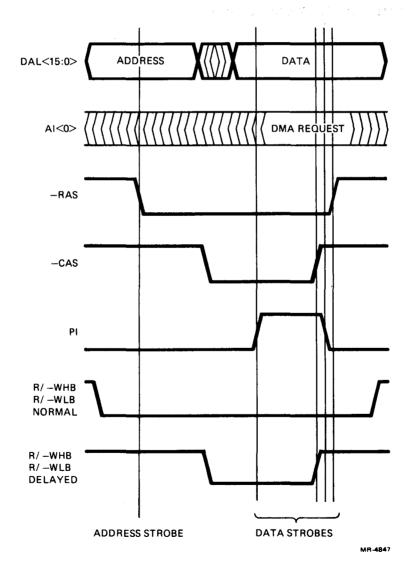

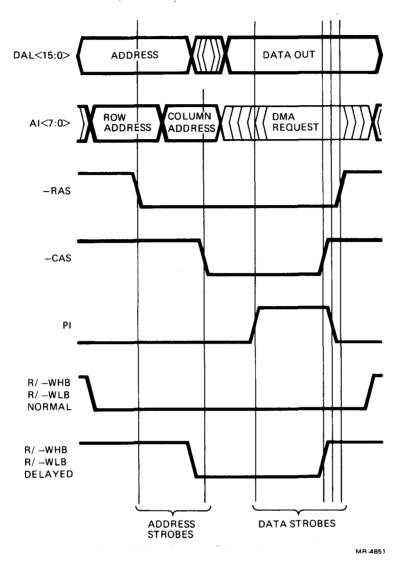

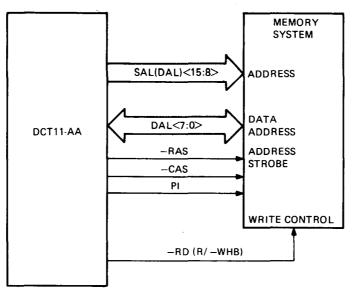

**2.6.1.1** Dynamic Address – Refer to Figures 2-8 and 2-9. The address is output on AI < 7:0>. The AI lines output the row address first and the column address second. Table 2-6 indicates the address bits required by memories in 4K/16K mode and 64K mode.

#### NOTE The AI lines are not in order. Refer to Table 2-7.

**2.6.1.2** Static Address – The addressing of a static ROM, RAM, or register in a system supporting dynamic devices is accomplished by outputs concurrent with the AI<7:0>. The concurrent address is output on DAL<15:0>.

Figure 2-8 16-Bit Dynamic Write, Block Diagram

Figure 2-9 16-Bit Dynamic Write Timing

| Table 2-6 | 16-Bit Dynamic | Write Addressing Scheme |

|-----------|----------------|-------------------------|

|-----------|----------------|-------------------------|

| Mode   | Memory Chip   | Address* | AI Used |

|--------|---------------|----------|---------|

| 4K/16K | $4K \times 1$ | A1-A12   | <6:1>   |

| 4K/16K | 16K × 1       | A1-A14   | <7:1>   |

| 64K    | 64K × 1       | A1-A15   | <7:0>   |

\*Address lines necessary to address all bits in each chip.

4

|            | Address       |      |              |      |  |

|------------|---------------|------|--------------|------|--|

| AI         | 4K/16K<br>RAS | -CAS | 64K<br>— RAS | -CAS |  |

| <0>        | FET           | A14  | A15          | A14  |  |

| <0><br><1> | A1            | A2   | A1           | A2   |  |

| <2>        | A3            | A4   | A3           | A4   |  |

| <3><br><4> | A5            | A6   | A5           | A6   |  |

| <4>        | <b>A</b> 7    | A8   | A7           | A8   |  |

| <5>        | A9            | A10  | A9           | A10  |  |

| <6><br><7> | A11           | A12  | A11          | A12  |  |

| <7>        | A13           | A14  | A13          | A12  |  |

Table 2-7 16-Bit Dynamic Write AI Addressing

**2.6.1.3** Address Control – Table 2-8 indicates the signals and edges required to latch each portion of the address into the memory system or register.

#### 2.6.2 Output of Data

Refer to Figure 2-9. The data is output on DAL<15:0>.

Data Control - The signals used to latch the data into the memory system or register and the edges required are found in Table 2-9. Write control is accomplished through the use of two signals:

- •

- R/-WHB R/-WLB •

Table 2-10 indicates the conditions necessary to address and write a memory system or register. The timing of R/-WHB and R/-WLB is found in Table 2-11.

| al Edge                | Device                                  |

|------------------------|-----------------------------------------|

| AS Assertion (leading) | Dynamic<br>Dynamic<br>Dynamic or static |

| 2                      | × 0,                                    |

Table 2-8 16-Bit Dynamic Write Address Strobes

Table 2-9 16-Bit Dynamic Write Data Strobes

| Signal | Edge                |

|--------|---------------------|

| -RAS   | Negation (trailing) |

| -CAS   | Negation (trailing) |

| PI     | Assertion (leading) |

| PI     | Negation (trailing) |

| Addressed Memory | Address                | R/-WHB | R/-WLB |  |

|------------------|------------------------|--------|--------|--|

| Word             | Even $(DAL < 0 > = 0)$ | 0      | 0      |  |

| Low byte         | Even $(DAL < 0 > = 0)$ | 1      | 0      |  |

| High byte        | Odd (DAL < 0 > = 1)    | 0      | 1      |  |

| Table 2-10 | 16-Bit | Dynamic | Write | Conditions |

|------------|--------|---------|-------|------------|

|------------|--------|---------|-------|------------|

Table 2-11

16-Bit Dynamic Write Control Timing

| Signal                                           | Mode    | Parameter                                |

|--------------------------------------------------|---------|------------------------------------------|

| R/-WHB                                           | Normal  | Write control before – CAS assertion     |

| R/-WLB                                           | Normal  | Write control before - CAS assertion     |

| R/-WHB                                           | Delayed | Write control at or after -CAS assertion |

| $\mathbf{R}' - \mathbf{W} \mathbf{L} \mathbf{B}$ | Delayed | Write control at or after -CAS assertion |

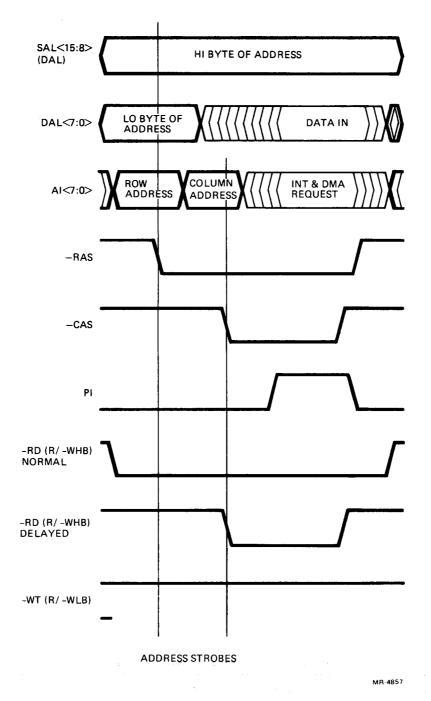

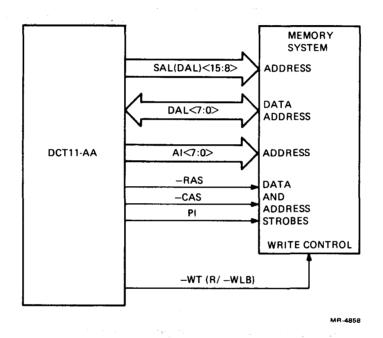

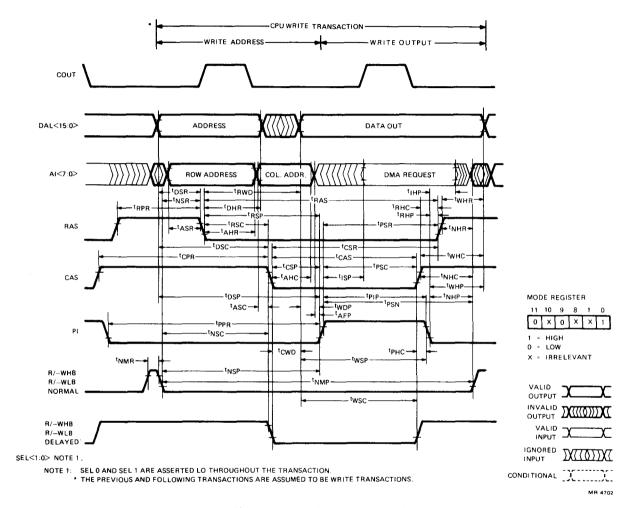

#### 2.7 8-BIT STATIC READ TRANSACTION

A read transaction consists of three distinct processes:

- Output of address

- Input of data

- Input of interrupt and DMA request (refer to Paragraphs 1.5 and 2.14)

Detailed timing of an 8-bit static read transaction is found in Figure A-6 of Appendix A.

When a word read or a word write is being executed, the transaction is repeated twice and the two transactions are indivisible. For example, the MOV (move word) instruction first does a read transaction and addresses the low-byte data. The address is then incremented by one and the second read transaction addresses the high byte data. In the case of the MOVB (move byte) instruction, the transaction occurs only once.

#### NOTE

#### All references to input or output are to the processor.

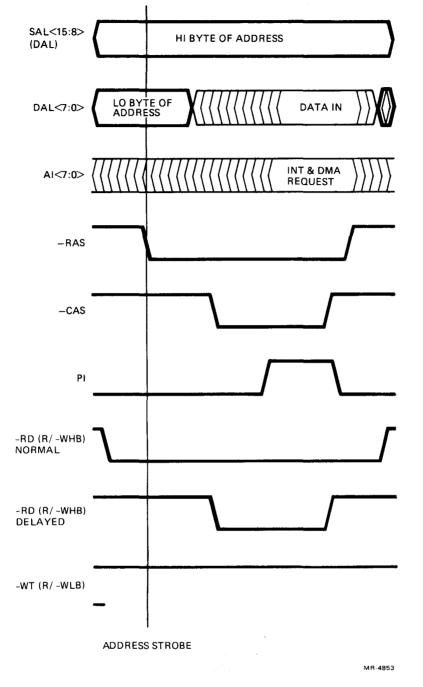

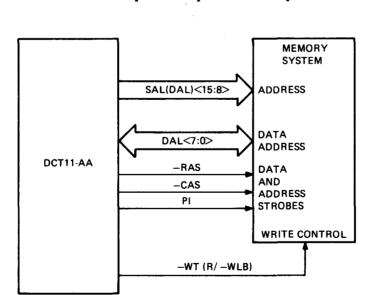

#### 2.7.1 Output of Address

Refer to Figures 2-10 and 2-11. The high byte address is output on the static address lines (SALs) 15-8 (<15:8>). The low byte of the address is output on DAL<7:0>. Data address lines are time multiplexed and used for both address and data.

Address Control – Address strobe, which is used to latch the address into the memory system or register, is accomplished by means of -RAS. The address is latched upon the assertion (leading edge) of -RAS.

#### 2.7.2 Input of Data

Refer to Figure 2-11. The input data should be valid on DAL < 7:0 > during the period PI is asserted.

**Data Control** – The data strobe, which the processor uses to latch the input data, is accomplished by means of -CAS. The data is latched upon the negation (trailing edge) of -CAS. Read control is accomplished through the use of the signal -Read (R/-WHB). The timing of -Read is found in Table 2-12.

MR-4852

Figure 2-10 8-Bit Static Read, Block Diagram

#### 2.7.3 Instruction Fetch

An instruction fetch is indicated by two signals:

- SEL<0> high

- SEL < 1 > low

Refer to Figure A-6 in Appendix A.

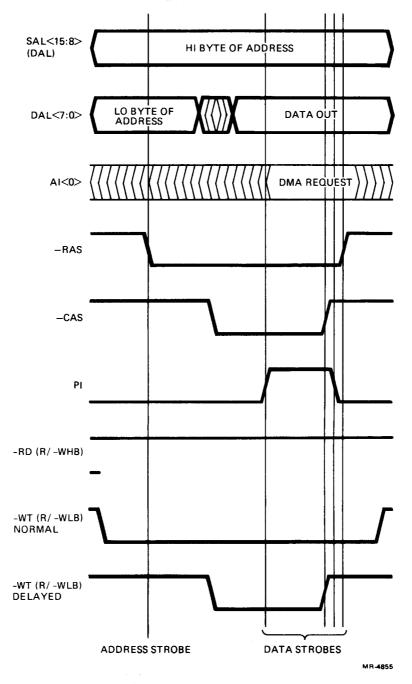

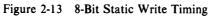

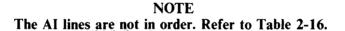

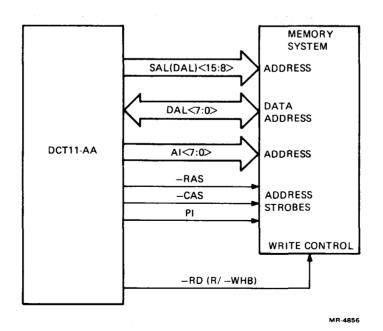

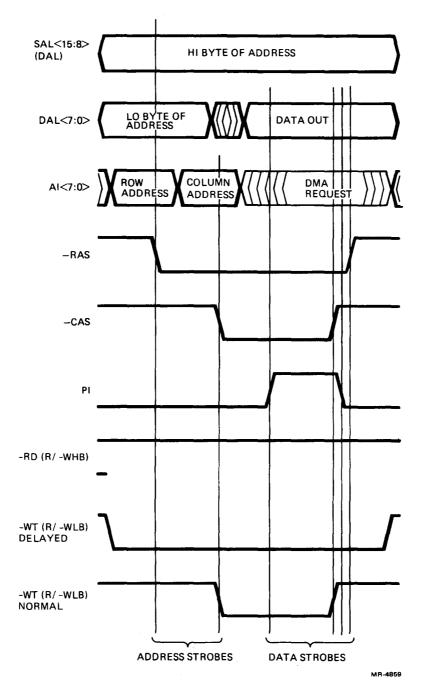

#### 2.8 8-BIT STATIC WRITE TRANSACTION

A write transaction consists of three distinct processes:

- Output of address

- Output of data

- Input of DMA request (refer to Paragraph 2.14)

Detailed timing of an 8-bit static write transaction is found in Figure A-7 in Appendix A.

When a word read or a word write is being executed, the transaction is repeated twice and the two transactions are indivisible. For example, the MOV (move word) instruction first does a read transaction and addresses the low byte data. The address is then incremented by one and the second read transaction addresses the high byte data. In the case of the MOVB (move byte) instruction, the transaction occurs only once.

#### NOTE

All references to input or output are to the processor.

A write transaction is always preceded by a read transaction (the two are indivisible) except when writing the stack during an interrupt or trap.

Figure 2-11 8-Bit Static Read Timing

۰.

Table 2-12 8-Bit Static Read Control Timing

| Signal                    | Mode              | Parameter                                                                     |

|---------------------------|-------------------|-------------------------------------------------------------------------------|

| -RD (R/-WHB) -RD (R/-WHB) | Normal<br>Delayed | Read control before -CAS assertion<br>Read control at or after -CAS assertion |

#### 2.8.1 Output of Address

Refer to Figures 2-12 and 2-13. The high byte address is output on the static address lines (SALs) 15-8 (<15:8>). The low byte of the address is output on DAL<7:0>. Data address lines are time multiplexed and used for both address and data.

Address Control – Address strobe, which is used to latch the address into the memory system or register, is accomplished by means of -RAS. The address is latched upon the assertion (leading edge) of -RAS.

#### 2.8.2 Output of Data

Refer to Figure 2-13. The data is output on DAL<7:0> before the assertion (leading edge) of PI.

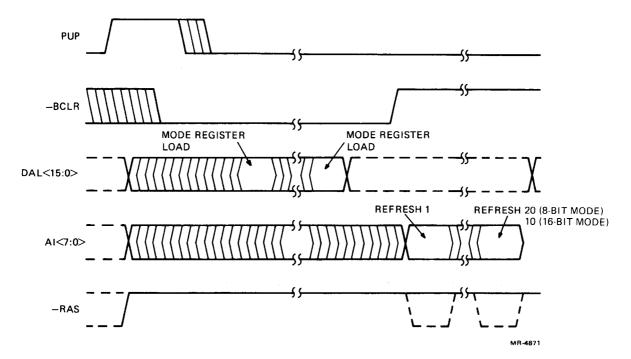

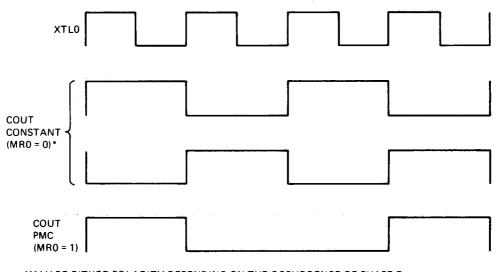

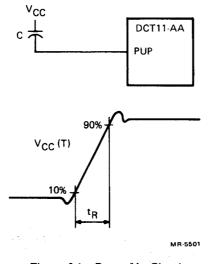

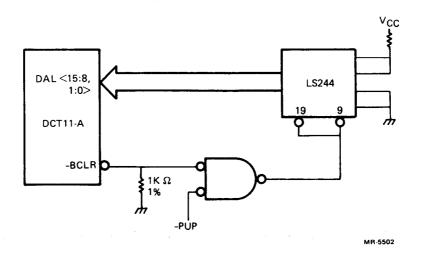

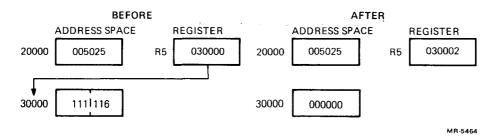

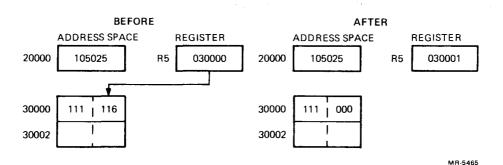

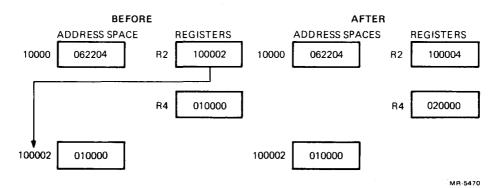

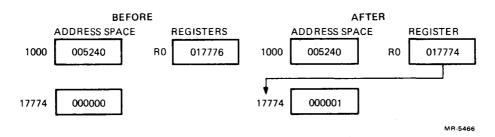

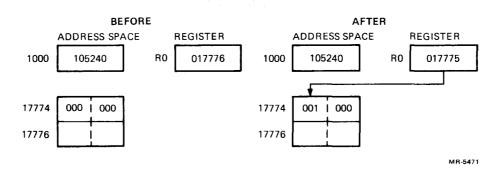

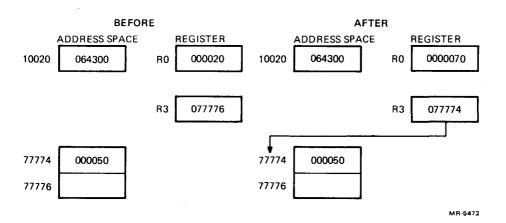

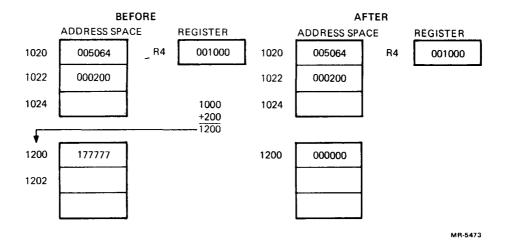

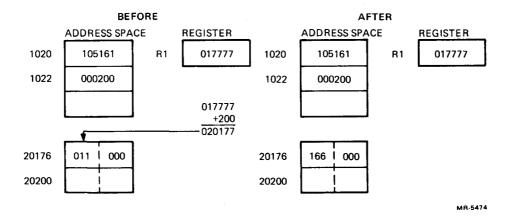

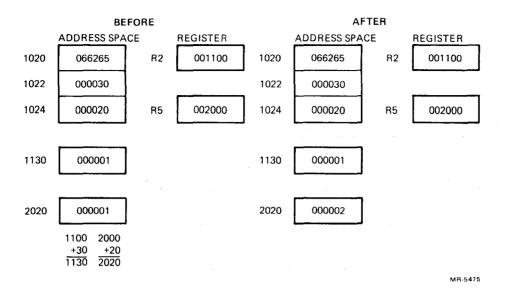

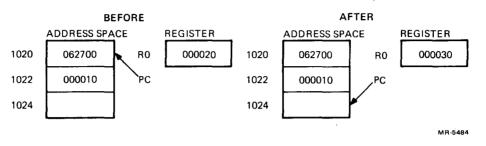

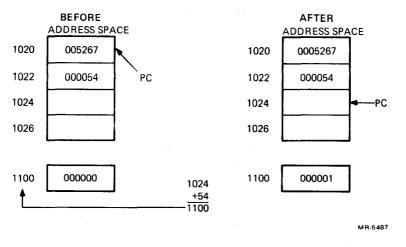

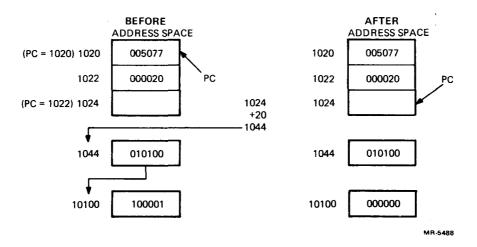

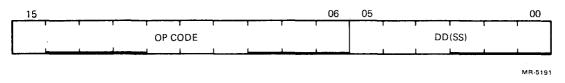

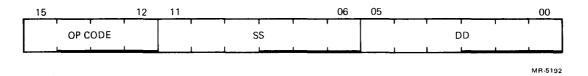

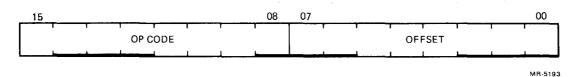

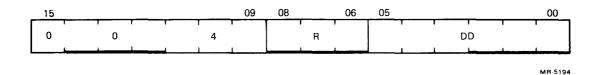

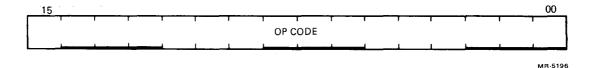

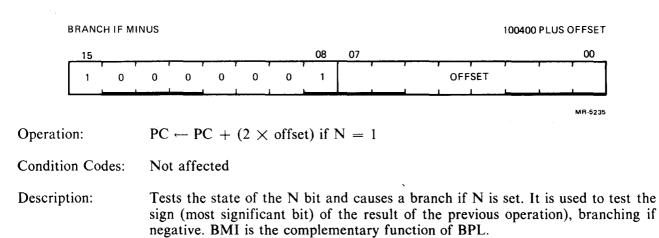

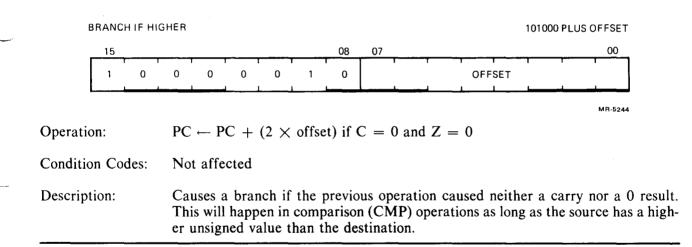

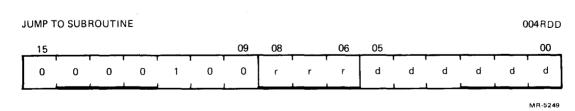

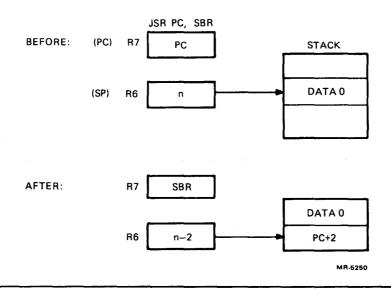

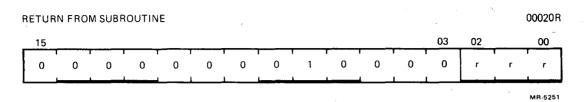

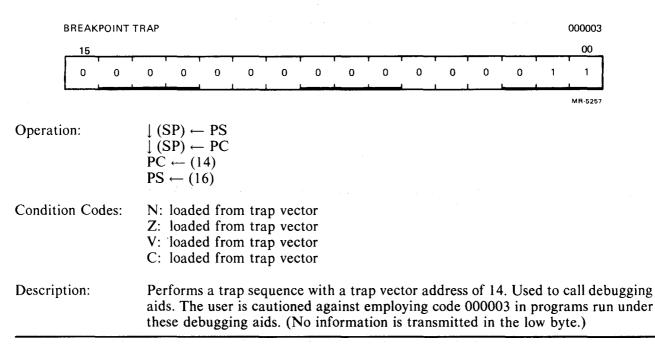

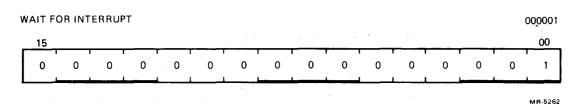

**Data Control** – The signals used to latch the data into the memory system or register and the edges required are found in Table 2-13. Write control is accomplished through the use of the signal – Write (R/-WLB). The timing of – Write is found in Table 2-14.