# PDT-11/150 USER GUIDE

digital equipment corporation • marlboro, massachusetts

#### Copyright © 1979, 1980 by Digital Equipment Corporation

#### All Rights Reserved

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS      |

|---------|--------------|--------------|

| DEC     | DECSYSTEM-20 | OMNIBUS      |

| PDP     | DIBOL        | <b>OS</b> /8 |

| DECUS   | EduSystem    | RSTS         |

| UNIBUS  | VAX          | RSX          |

| DECLAB  | VMS          | IAS          |

|         |              | MINC-11      |

### CONTENTS

,

### CHAPTER 1 INTRODUCTION

| 1.1<br>1.1.1                                                                                                                                        | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1.2                                                                                                                                               | PDT-11/150 Equipment Specifications1-4                                                                                                                                                                                                                                                                                                                                                   |

| 1.1.3                                                                                                                                               | Media Specifications1-5                                                                                                                                                                                                                                                                                                                                                                  |

| 1.2                                                                                                                                                 | REFERENCE DOCUMENTS                                                                                                                                                                                                                                                                                                                                                                      |

| 1.3                                                                                                                                                 | SUPPLIES AND ACCESSORIES1-7                                                                                                                                                                                                                                                                                                                                                              |

| CHAPTER 2                                                                                                                                           | UNPACKING/INSTALLATION                                                                                                                                                                                                                                                                                                                                                                   |

| 2.1                                                                                                                                                 | UNPACKING AND INSPECTION                                                                                                                                                                                                                                                                                                                                                                 |

| 2.2                                                                                                                                                 | SITE PREPARATION AND CONNECTIONS                                                                                                                                                                                                                                                                                                                                                         |

| 2.2.1                                                                                                                                               | ac Power Requirements2-3                                                                                                                                                                                                                                                                                                                                                                 |

| 2.2.2                                                                                                                                               | Serial Line Cable Connectors2-3                                                                                                                                                                                                                                                                                                                                                          |

| 2.2.2.1                                                                                                                                             | EIA Connector Pin Assignments2-6                                                                                                                                                                                                                                                                                                                                                         |

| 2.2.2.2                                                                                                                                             | Serial Line Cable Length                                                                                                                                                                                                                                                                                                                                                                 |

| 2.3                                                                                                                                                 | SERIAL LINE DATA CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                         |

| CHAPTER 3                                                                                                                                           | OPERATING PROCEDURES                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.1                                                                                                                                                 | SWITCHES AND INDICATORS                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.1                                                                                                                                                 | SWITCHES AND INDICATORS                                                                                                                                                                                                                                                                                                                                                                  |

| 3.1<br>3.1.1                                                                                                                                        | SWITCHES AND INDICATORS                                                                                                                                                                                                                                                                                                                                                                  |

| 3.1<br>3.1.1<br>3.1.2                                                                                                                               | SWITCHES AND INDICATORS3-1Front Panel Indicators3-1Rear Panel Switches and Components3-2Function Control Switch3-2DISK HANDLING AND STORAGE3-3                                                                                                                                                                                                                                           |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3                                                                                                                      | SWITCHES AND INDICATORS3-1Front Panel Indicators3-1Rear Panel Switches and Components3-2Function Control Switch3-2                                                                                                                                                                                                                                                                       |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2                                                                                                               | SWITCHES AND INDICATORS3-1Front Panel Indicators3-1Rear Panel Switches and Components3-2Function Control Switch3-2DISK HANDLING AND STORAGE3-3                                                                                                                                                                                                                                           |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2<br>3.2.1                                                                                                      | SWITCHES AND INDICATORS3-1Front Panel Indicators3-1Rear Panel Switches and Components3-2Function Control Switch3-2DISK HANDLING AND STORAGE3-3Insertion and Removal of a Disk3-4                                                                                                                                                                                                         |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2<br>3.2.1<br>3.3                                                                                               | SWITCHES AND INDICATORS3-1Front Panel Indicators3-1Rear Panel Switches and Components3-2Function Control Switch3-2DISK HANDLING AND STORAGE3-3Insertion and Removal of a Disk3-4TEST PROCEDURES3-6                                                                                                                                                                                       |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2<br>3.2.1<br>3.3<br>3.3.1                                                                                      | SWITCHES AND INDICATORS3-1Front Panel Indicators3-1Rear Panel Switches and Components3-2Function Control Switch3-2DISK HANDLING AND STORAGE3-3Insertion and Removal of a Disk3-4TEST PROCEDURES3-6Preliminary Set-Up3-6Optional Loopback Connector3-7                                                                                                                                    |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2<br>3.2.1<br>3.3<br>3.3.1<br>3.3.2<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4                                         | SWITCHES AND INDICATORS3-1Front Panel Indicators3-1Rear Panel Switches and Components3-2Function Control Switch3-2DISK HANDLING AND STORAGE3-3Insertion and Removal of a Disk3-4TEST PROCEDURES3-6Preliminary Set-Up3-6Optional Loopback Connector3-6Self-Test Procedures3-7Loading the System Exerciser Program3-9                                                                      |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2<br>3.2.1<br>3.3<br>3.3.1<br>3.3.2<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.4                                | SWITCHES AND INDICATORS3-1Front Panel Indicators3-1Rear Panel Switches and Components3-2Function Control Switch3-2DISK HANDLING AND STORAGE3-3Insertion and Removal of a Disk3-4TEST PROCEDURES3-6Preliminary Set-Up3-6Optional Loopback Connector3-6Self-Test Procedures3-7Loading the System Exerciser Program3-9Exerciser Compatability Test3-13                                      |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2<br>3.2.1<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.4.1<br>3.3.4.2          | SWITCHES AND INDICATORS3-1Front Panel Indicators3-1Rear Panel Switches and Components3-2Function Control Switch3-2DISK HANDLING AND STORAGE3-3Insertion and Removal of a Disk3-4TEST PROCEDURES3-6Preliminary Set-Up3-6Optional Loopback Connector3-6Self-Test Procedures3-7Loading the System Exerciser Program3-9Exerciser Compatability Test3-13Copying the System Exerciser Disk3-13 |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2<br>3.2.1<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.4.1<br>3.3.4.2<br>3.3.5 | SWITCHES AND INDICATORS3-1Front Panel Indicators3-1Rear Panel Switches and Components3-2Function Control Switch3-2DISK HANDLING AND STORAGE3-3Insertion and Removal of a Disk3-4TEST PROCEDURES3-6Preliminary Set-Up3-6Optional Loopback Connector3-6Self-Test Procedures3-7Loading the System Exerciser Program3-13Copying the System Exerciser Disk3-13Loading a System Program3-14    |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2<br>3.2.1<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.4.1<br>3.3.4.2          | SWITCHES AND INDICATORS3-1Front Panel Indicators3-1Rear Panel Switches and Components3-2Function Control Switch3-2DISK HANDLING AND STORAGE3-3Insertion and Removal of a Disk3-4TEST PROCEDURES3-6Preliminary Set-Up3-6Optional Loopback Connector3-6Self-Test Procedures3-7Loading the System Exerciser Program3-9Exerciser Compatability Test3-13Copying the System Exerciser Disk3-13 |

| 4-5  |

|------|

| 4-7  |

|      |

| 4-14 |

| •    |

### **CONTENTS** (Cont)

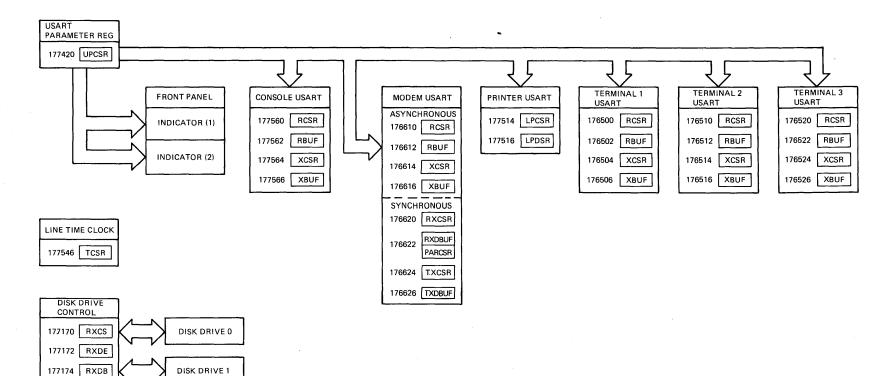

#### CHAPTER 5 PROGRAMMING INFORMATION

| 5.1     | SYSTEM CHARACTERISTICS                                   | 5-1  |

|---------|----------------------------------------------------------|------|

| 5.2     | PERIPHERAL DEVICE COMMUNICATION                          | 5-2  |

| 5.2.1   | Console Device                                           |      |

| 5.2.2   | Communications Modem                                     |      |

| 5.2.3   | Line Printer Terminal                                    |      |

| 5.2.4   | Cluster Option Terminals                                 |      |

| 5.2.5   | Power Up and Manual Reset Conditions                     | 5-3  |

| 5.2.6   | Programmed Reset Instruction (Initialize)                | 5-4  |

| 5.3     | DEVICE AND INTERRUPT VECTOR ADDRESS ASSIGNMENTS          |      |

| 5.3.1   | USART Parameter Control Register Address                 |      |

| 5.3.2   | Standard Terminal Addresses                              |      |

| 5.3.3   | Optional (Cluster) Terminal Addresses                    |      |

| 5.3.4   | Disk Drive Addresses                                     |      |

| 5.3.5   | Line Time Clock Addresses                                |      |

| 5.4     | STANDARD TERMINAL REGISTER FORMATS                       |      |

| 5.4.1   | USART Parameter Register                                 |      |

| 5.4.2   | Console Device Interface                                 |      |

| 5.4.2.1 | Receiver Control/Status Register (RCSR)                  | 5-12 |

| 5.4.2.2 | Receiver Data Buffer (RBUF)                              |      |

| 5.4.2.3 | Transmitter Control/Status Register (XCSR)               | 5-13 |

| 5.4.2.4 | Transmitter Data Buffer (XBUF)                           | 5-13 |

| 5.4.3   | Communications Interface (Modem)                         | 5-14 |

| 5.4.4   | Asynchronous Modem Interface                             | 5-15 |

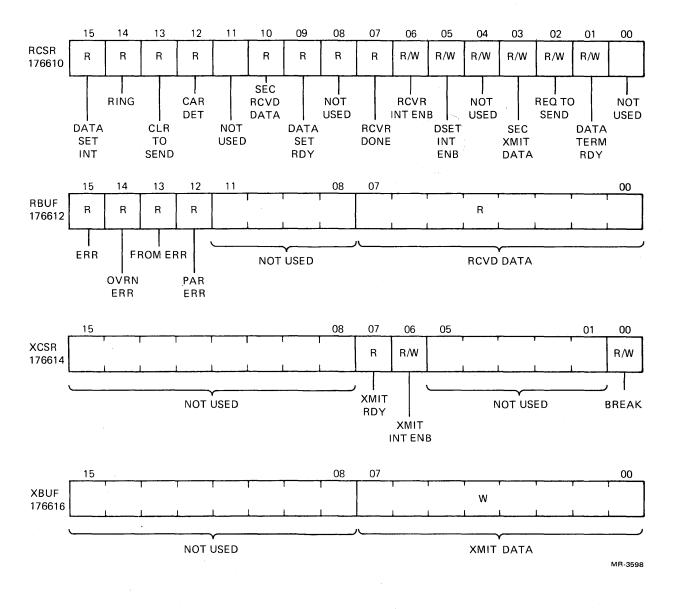

| 5.4.4.1 | Asychronous Receiver Control/Status Register (RCSR)      | 5-15 |

| 5.4.4.2 | Asynchronous Receiver Data Buffer (RBUF)                 | 5-17 |

| 5.4.4.3 | Asychronous Transmitter Control/Status Register (XCSR)   | 5-18 |

| 5.4.4.4 | Asychronous Transmitter Data Buffer (XBUF)               | 5-19 |

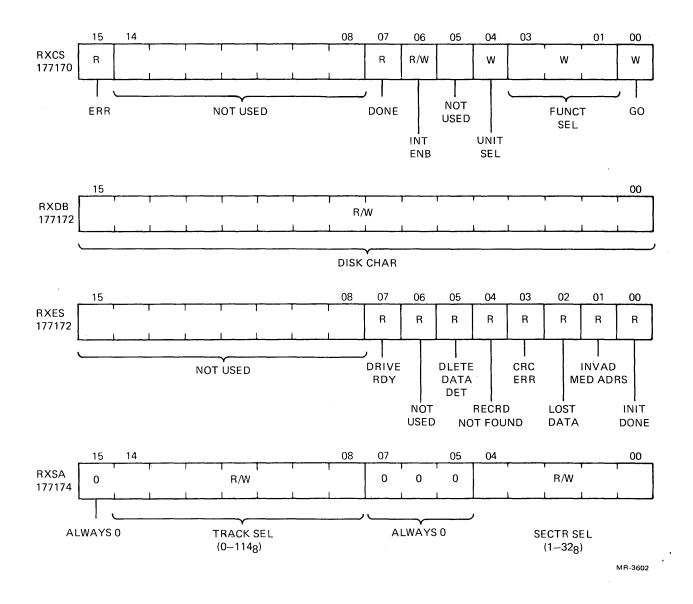

| 5.4.5   | Synchronous Modem Interface                              | 5-19 |

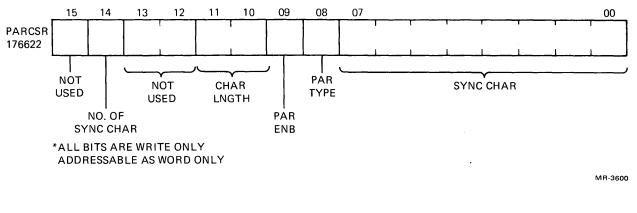

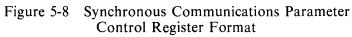

| 5.4.5.1 | Parameter Control Register (PARCSR)                      | 5-20 |

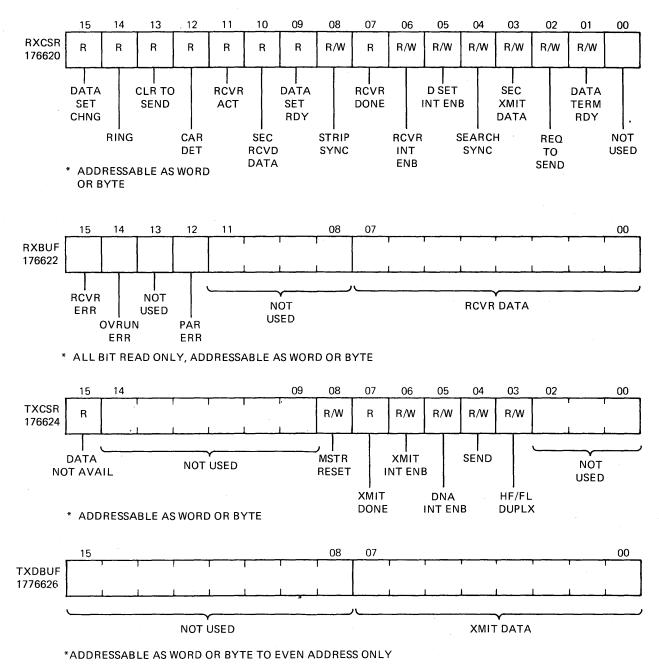

| 5.4.5.2 | Synchronous Receiver Control/Status Register (RXCSR)     | 5-22 |

| 5.4.5.3 | Synchronous Receiver Data Buffer (RXDBUF)                | 5-24 |

| 5.4.5.4 | Synchronous Transmit Control and Status Register (TXCSR) | 5-25 |

| 5.4.5.5 | Synchronous Transmit Data Buffer (TXDBUF)                | 5-27 |

| 5.4.6   | Printer Terminal Interface                               | 5-27 |

| 5.4.6.1 | Printer Control/Status Register (LPCSR)                  | 5-28 |

| 5.4.6.2 | Printer Data Buffer (LPDSR)                              | 5-28 |

| 5.5     | OPTIONAL TERMINAL REGISTER WORD FORMATS                  | 5-28 |

| 5.6     | DISK DRIVE REGISTER FORMATS                              |      |

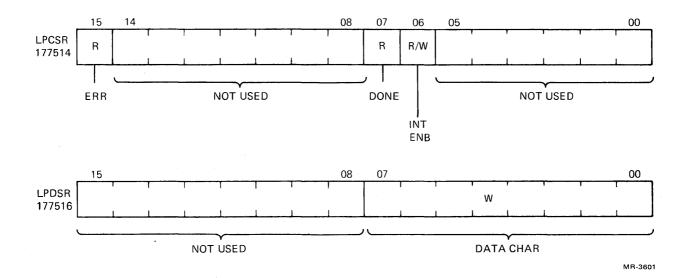

| 5.6.1   | Drive Control/Status Register (RXCS)                     |      |

| 5.6.2   | Disk Controller Data Buffer Register (RXDB)              |      |

| 5.6.3   | Disk Controller Track and Sector Register (RXSA)         | 5-34 |

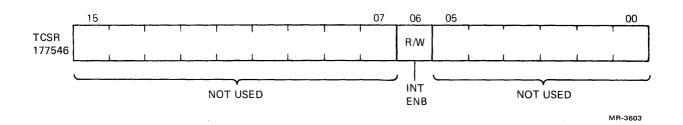

| 5.7     | LINE TIME CLOCK (LTC)                                    |      |

| 5.8     | FUNCTION CONTROL SWITCH SELECTIONS                       | 5-36 |

|         |                                                          |      |

### **FIGURES**

| Figure No. | Title                                                        | Page |

|------------|--------------------------------------------------------------|------|

| 1-1        | Typical PDT-11/150 Flexible Disk Operating System            |      |

| 1-2        | PDT-11/150 Model Designations                                |      |

| 2-1        | PDT-11/150 Unpacking Procedure Diagram                       |      |

| 2-2        | PDT-11/150 Single and Dual Disk Unit Dimensions              | 2-4  |

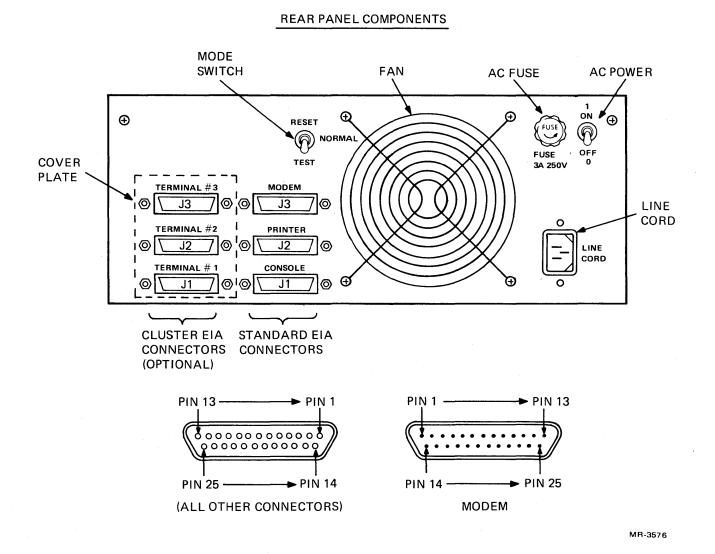

| 2-3        | Rear Panel Components and Connector Pin Assignments          |      |

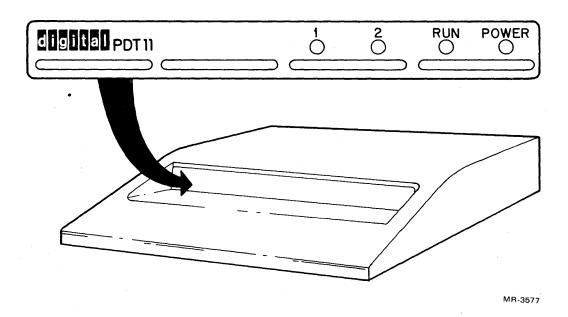

| 3-1        | Front Panel Indicators                                       | 3-1  |

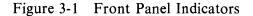

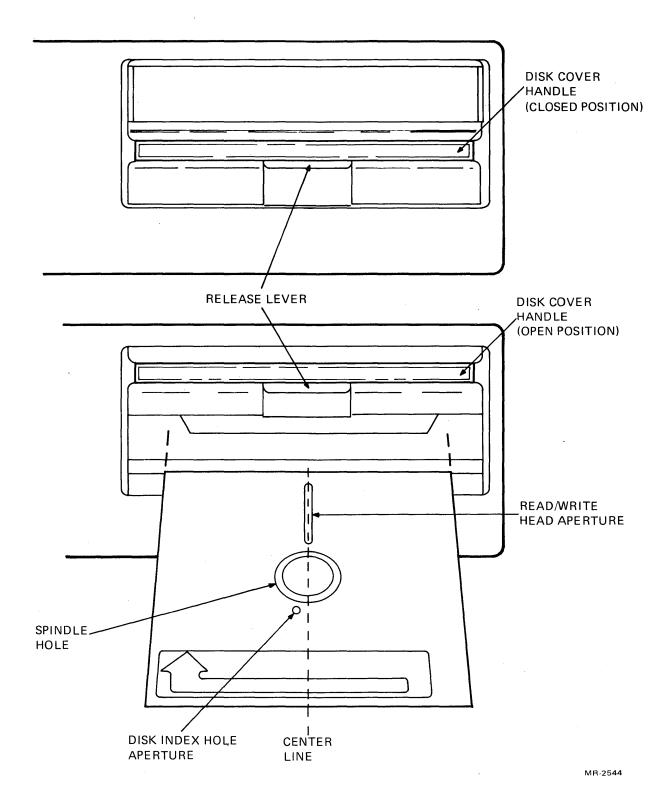

| 3-2        | Flexible Disk                                                | 3-4  |

| 3-3        | Loading the Disk into the Drive                              | 3-5  |

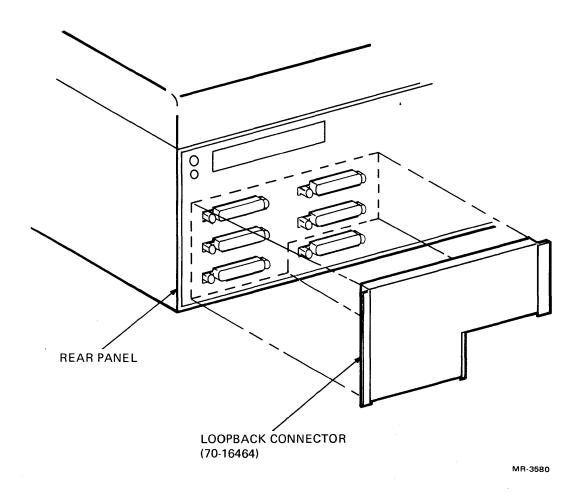

| 3-4        | Loopback Connector Installation                              | 3-7  |

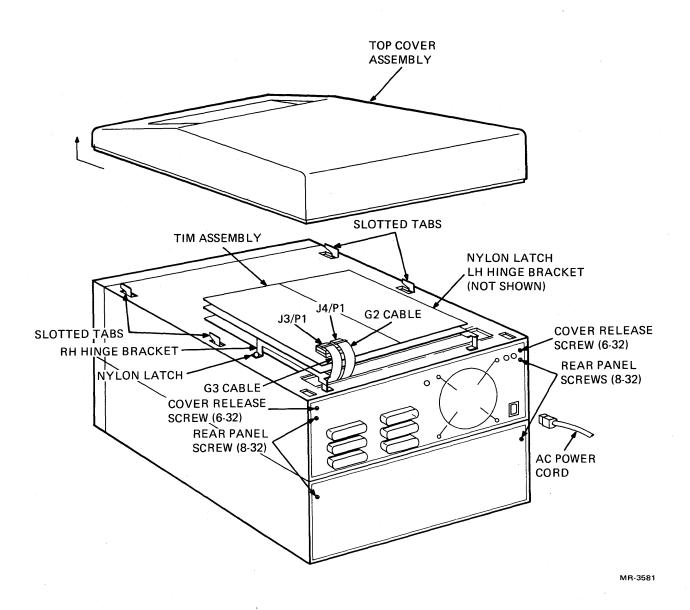

| 4-1        | Top Cover and TIM Assembly Removal and Replacement           | 4-2  |

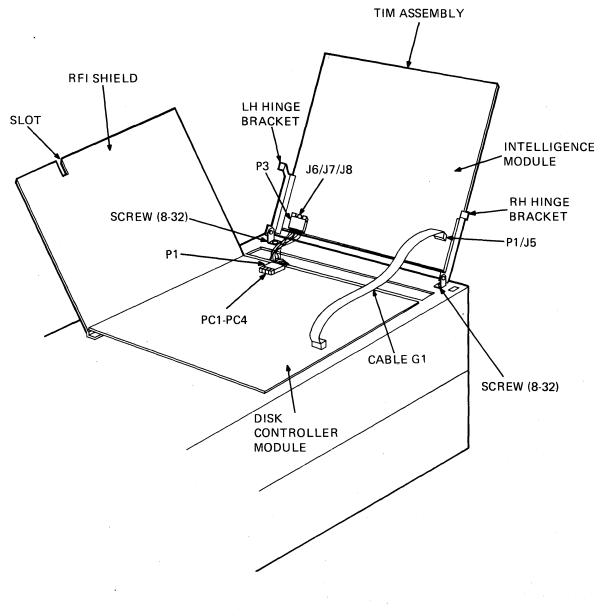

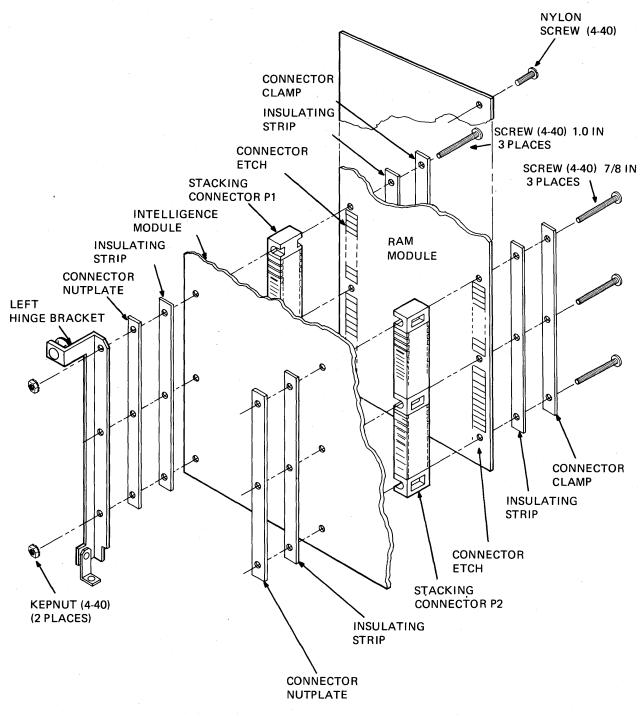

| 4-2        | TIM Assembly Connections                                     | 4-3  |

| 4-3        | TIM Group, Assembly and Disassembly                          | 4-4  |

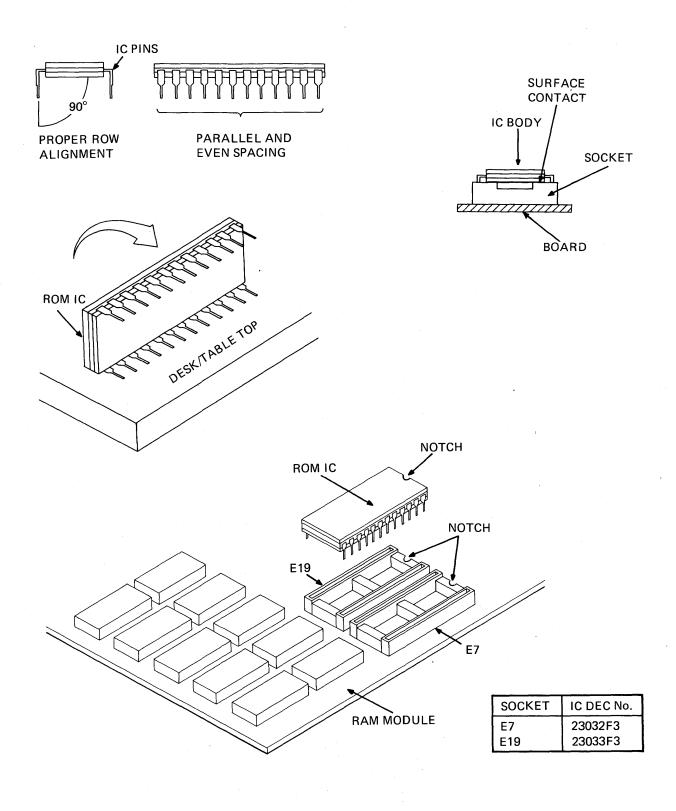

| 4-4        | RAM Module, PROM Installation                                |      |

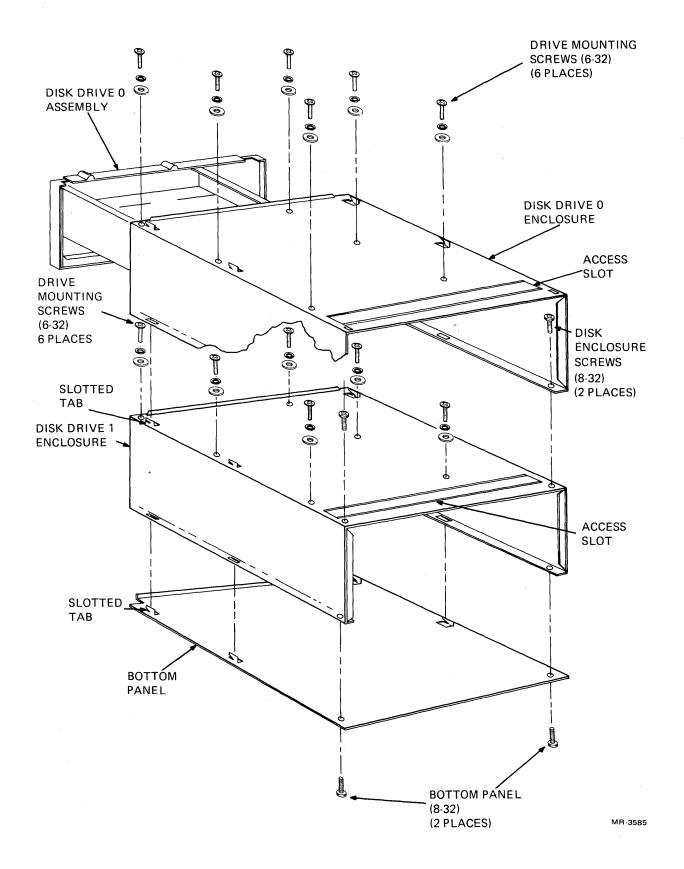

| 4-5        | Disk Drive 1 Enclosure Mounting                              | 4-9  |

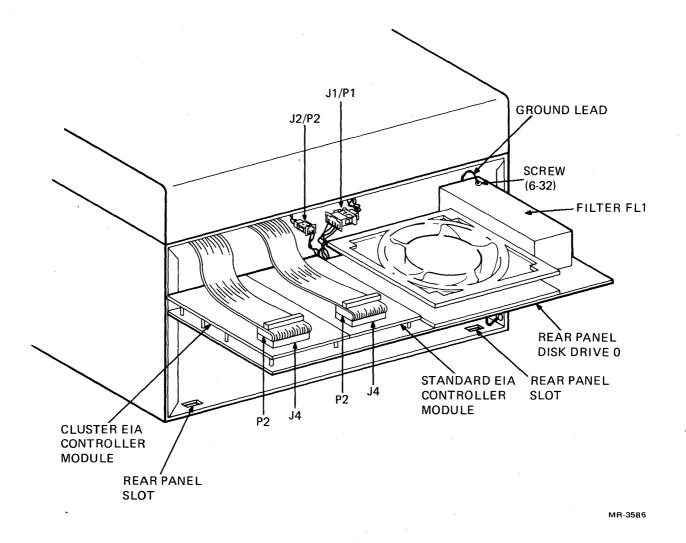

| 4-6        | Rear Panel Removal, Disk Drive 0 Enclosure                   | 4-10 |

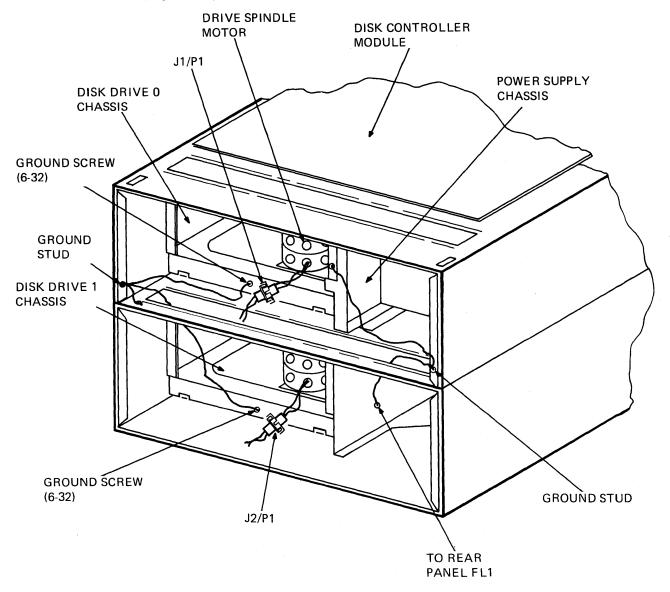

| 4-7        | Ground Leads and ac Cable Routing                            |      |

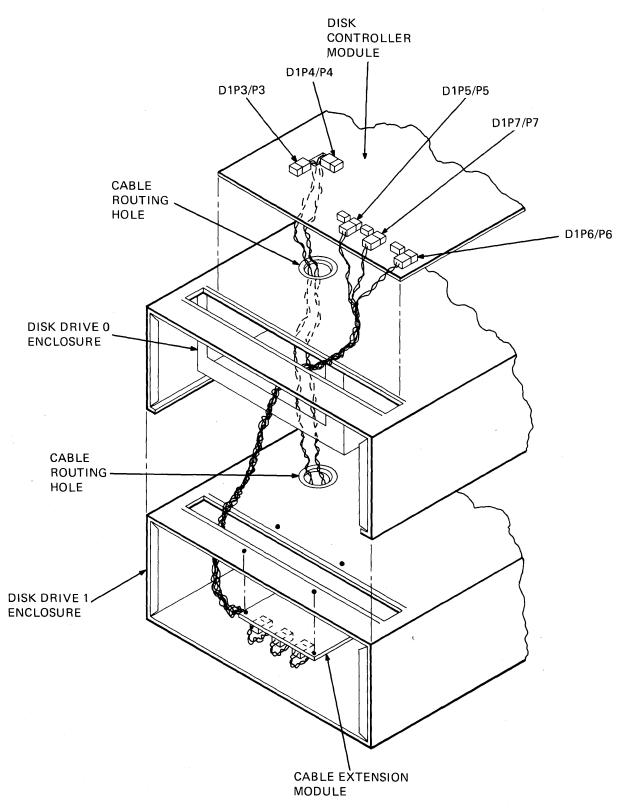

| 4-8        | Disk Drive 1 Assembly, Cable Routing                         |      |

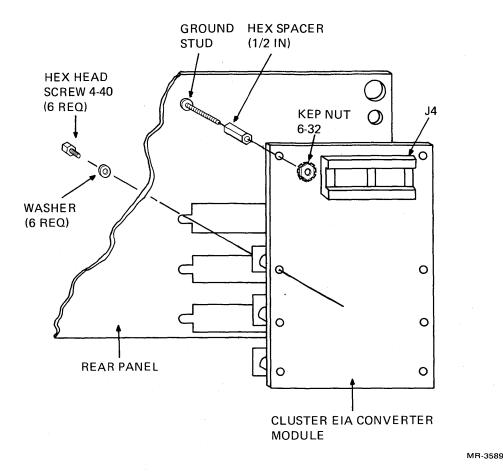

| 4-9        | Cluster EIA Converter Module Mounting                        | 4-14 |

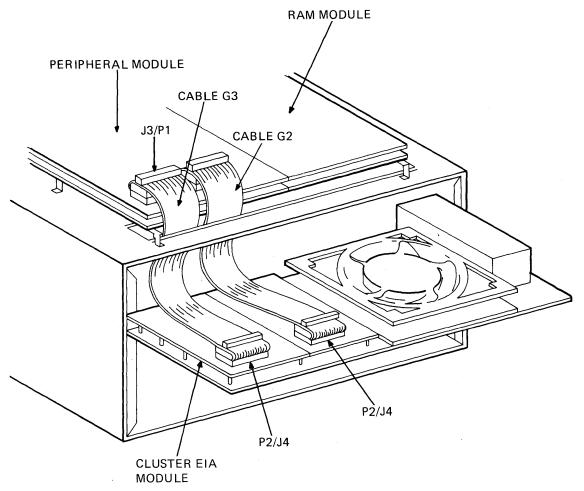

| 4-10       | Cluster EIA Converter, Cable Routing                         | 4-15 |

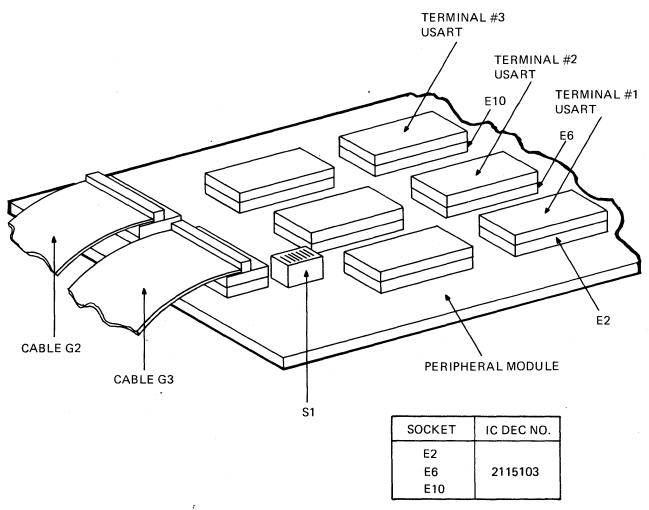

| 4-11       | Cluster EIA Module, USART Installation                       | 4-16 |

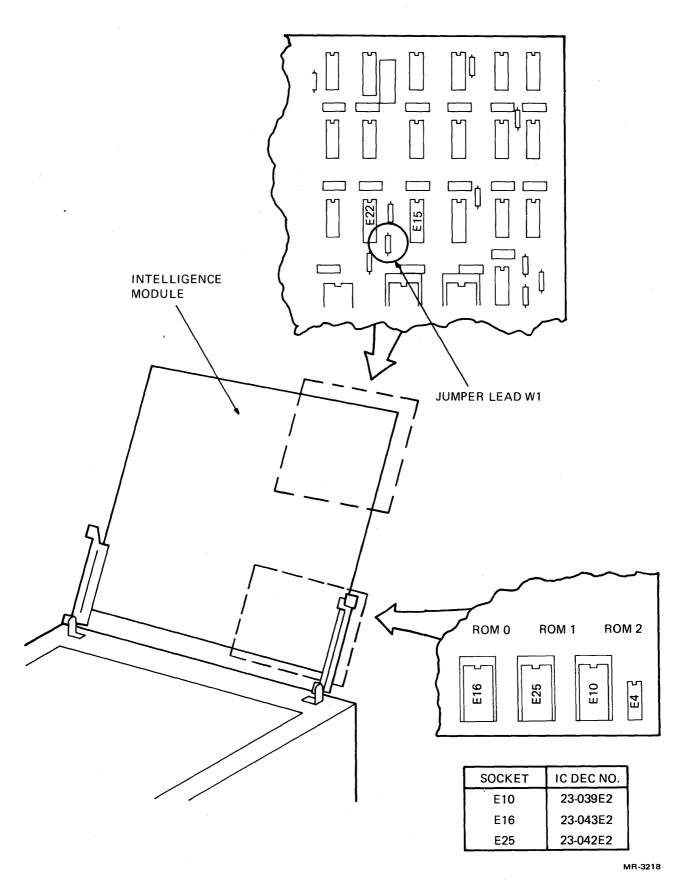

| 4-12       | Intelligence Module, W1 Jumper Lead Location                 | 4-18 |

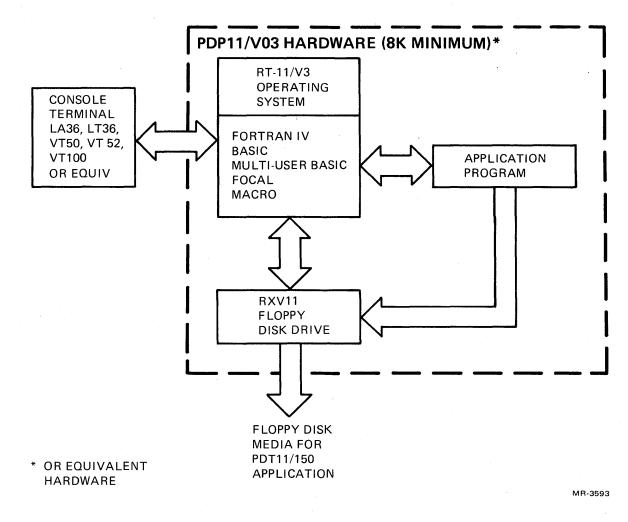

| 5-1        | PDT-11/150 Program Development System                        | 5-2  |

| 5-2        | PDT-11/150 Control and Address Register, Buffer Assignment   | 5-5  |

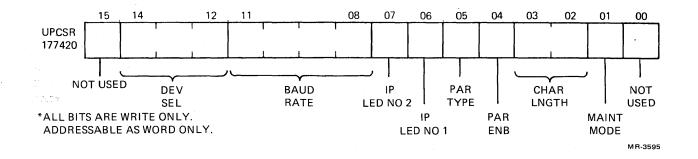

| 5-3        | USART Parameter Control Register UPCSR Format                | 5-9  |

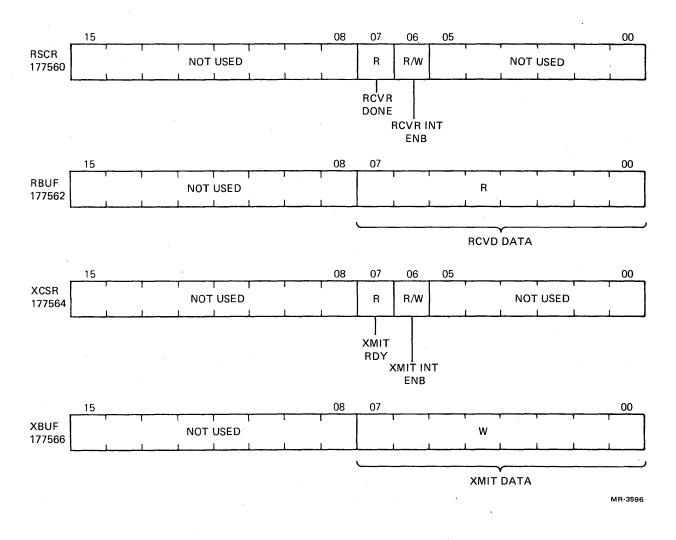

| 5-4        | Console Terminal Interface Register Formats                  | 5-12 |

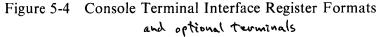

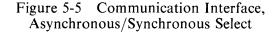

| 5-5        | Communication Interface, Asynchronous/Synchronous Select     | 5-14 |

| 5-6        | Asynchronous Communications Interface Register Formats       | 5-15 |

| 5-7        | Synchronous Communications Interface Register Format         | 5-20 |

| 5-8        | Synchronous Communications Parameter Control Register Format | 5-21 |

| 5-9        | Printer Terminal Interface, Register Formats                 | 5-27 |

| 5-10       | Disk Drive Interface, Register Formats                       | 5-29 |

| 5-11       | Line Time Clock (TCSR) Format                                | 5-35 |

### TABLES

¢,

| Table No. | Title                                                     | Page |

|-----------|-----------------------------------------------------------|------|

| 1-1       | PDT-11/150 Options                                        | 1-3  |

| 1-2       | PDT-11/150 Specifications                                 | 1-4  |

| 1-3       | Flexible Disk Specifications                              |      |

| 1-4       | PDT-11/150 Related Publications                           |      |

| 2-1       | ac Power Requirements                                     |      |

| 2-2       | Rear Panel, Device Connector Assignments                  |      |

| 2-3       | Available Device Cable Assemblies                         |      |

| 2-4       | Standard EIA Connector Signals                            |      |

| 2-5       | Cluster Option EIA Connector Signals                      |      |

| 3-1       | Front Panel Indicators                                    |      |

| 3-2       | Rear Panel Switches and Fuse                              |      |

| 3-3       | Function Control Switch Positions                         |      |

| 3-4       | Device Map Options (DEVM)                                 |      |

| 5-1       | Standard Device and Vector Addresses                      |      |

| 5-2       | Optional (Cluster) Terminals, Device and Vector Addresses |      |

| 5-3       | Disk Drive, Device and Vector Addresses                   |      |

| 5-4       | Line Time Clock, Device and Vector Address                |      |

| 5-5       | USART Parameter Register, Bit Descriptions                |      |

| 5-6       | Console Interface, Receiver Register Bit Descriptions     |      |

| 5-7       | Console Interface, Transmitter Register Bit Descriptions  |      |

| 5-8       | Asynchronous Communications, RCSR Bit Descriptions        |      |

| 5-9       | Asynchronous Communications, RBUF Bit Descriptions        |      |

| 5-10      | Asynchronous Communications, XCSR Bit Descriptions        |      |

| 5-11      | Asynchronous Communications, XBUF Bit Descriptions        |      |

| 5-12      | Parameter Control Register PARCSR, Bit Descriptions       |      |

| 5-13      | Synchronous Communications, RXCSR Bit Descriptions        |      |

| 5-14      | Synchronous Communications RXDBUF Bit Descriptions        |      |

| 5-15      | Synchronous Communications, TXCSR Bit Descriptions        |      |

| 5-16      | Synchronous Communications TXCBUF Bit Descriptions        |      |

| 5-17      | Printer Interface PCSR Bit Descriptions                   |      |

| 5-18      | Printer Interface PDBUF Bit Descriptions                  |      |

| 5-19      | Disk Controller RXCS Bit Descriptions                     |      |

| 5-20      | Disk Controller RXDB Bit Descriptions                     |      |

| 5-21      | Disk Controller RXES Bit Descriptions                     |      |

| 5-22      | Disk Controller RXSA Bit Descriptions                     |      |

| 5-23      | Line Time Clock Control/Status Register (TCSR)            |      |

| 5-24      | Function Control Switch Pack Selections                   |      |

### CHAPTER 1 INTRODUCTION

This guide contains the information required to unpack, inspect, install and verify the proper operation of the Programmable Data Terminal PDT-11/150. Also included is programming information necessary to develop the application software. The PDT-11/150 is a user-programmable disk storage system available as either a single flexible (floppy) disk drive unit or dual flexible disk drive unit. Input to and output from the system is through serial line terminals (consoles, printers, etc.) which conform to EIA standard RS-232C.

Chapter 1 provides a general introduction to the PDT-11/150 operating system and includes the specifications for the single and dual disk drive units. Also included is a list of the supporting publications.

Chapter 2 contains detailed procedures for unpacking the PDT-11/150, inspecting the unit and related contents, and connecting the unit to ac power and associated terminals.

Chapter 3 defines the switches and indicators and provides detailed procedures to verify the proper operation of the PDT-11/150.

Chapter 4 includes installation information required to incorporate the various options available into an existing PDT-11/150 unit.

Chapter 5 provides programming information and considerations for the development of application software.

#### **1.1 GENERAL DESCRIPTION**

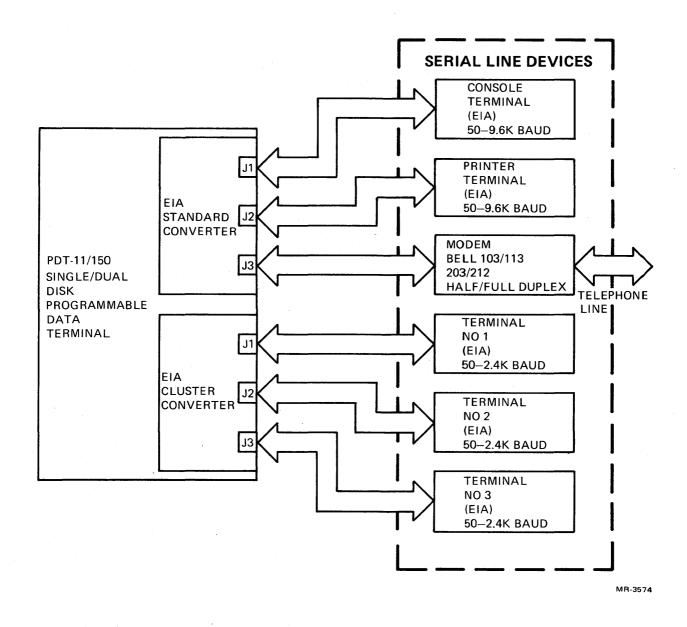

Figure 1-1 is a typical operating system configuration which includes the maximum number of terminals. Three serial devices connect to the standard EIA-level converter, and three serial terminals connect to the cluster EIA-level converter (optional).

The standard EIA-level converter allows full or half duplex operation with a console terminal, printer terminal or communications device (modem). The cluster converter expands the capability of the unit to include three additional serial line terminals; however, only one console, one line printer, and one modem device are allowable for each system.

The data transfer rates to and from the devices and terminals are dependent on the applications program or operating system and the number and types of peripheral units connected to the PDT-11/150. Refer to Paragraph 5.2 for detailed data transfer rate information.

The PDT-11/150 is controlled by a DIGITAL LSI-11 microprocessor and application programs can be developed on PDP-11/V03 systems or equivalent using RT-11V3 (or later versions) operating systems available for the LSI-11 microprocessor.

Figure 1-1 Typical PDT-11/150 Flexible Disk Operating System

#### **1.1.1** System Configurations and Options

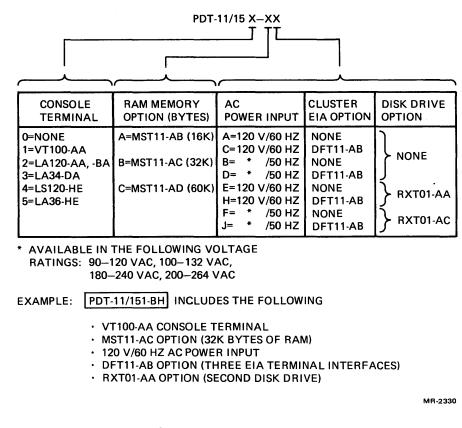

Figure 1-2 lists the model designations assigned to each of the PDT-11/150 units. The units are available with a single disk drive or dual disk drive. They operate with either 120 V/60 Hz input ac power or several voltage ranges for the 50 Hz power.

Table 1-1 lists and describes the options associated with the PDT-11/150. The RXT01-AA or -AC option is always included with a dual disk drive unit.

Figure 1-2 PDT-11/150 Model Designations

Table 1-1PDT-11/150 Options

| Option No.                             | Description *                                                                                                                             |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RXT01-AA                               | 60 Hz disk drive assembly includes enclosure and front bezel                                                                              |

| RXT01-AC                               | 50 Hz disk drive assembly includes enclosure and front panel                                                                              |

| DFT11-AA*                              | Standard EIA converter module (includes cable and USARTs)                                                                                 |

| DFT11-AB                               | Cluster EIA converter module (includes cable and USARTs)                                                                                  |

| MST11-AB †<br>MST11-AC †<br>MST11-AD † | RAM module/16K bytes<br>RAM module/32K bytes<br>RAM module/60K bytes<br>(The MST11 modules include diagnostic ROM with bootstrap loader.) |

| KDT11-AA*                              | Intelligence module with ROM program                                                                                                      |

| DLT11*                                 | Peripheral module with USARTs for standard EIA terminals                                                                                  |

| RXT11*                                 | Disk controller module with ROM program                                                                                                   |

\*Included with all PDT-11/150 models.

†These options are factory installable only.

**1.1.2 PDT-11/150 Equipment Specifications** Table 1-2 describes the mechanical, environmental and electrical characteristics of the PDT-11/150 units.

| Characteristic                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mechanical                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Overall Dimensions<br>Single Disk Unit | 51.0 cm (20.08 in) length $\times$ 33.02 cm (13.0 in) width $\times$ 20.9 cm (8.23 in) height                                                                                                                                                                                                                                                                                                                                                                 |

| Dual Disk Unit                         | 51.0 cm (20.08 in) length $\times$ 33.02 cm (13.0 in) width $\times$ 34.8 cm (13.42 in) height                                                                                                                                                                                                                                                                                                                                                                |

| Weight<br>Unpackaged                   | Single disk unit: 33 lb<br>Dual disk unit: 46 lb                                                                                                                                                                                                                                                                                                                                                                                                              |

| Packaged                               | Single disk unit: 40 lb<br>Dual disk unit: 55 lb                                                                                                                                                                                                                                                                                                                                                                                                              |

| Environmental                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Temperature<br>Operating               | 15° C to 32° C (59° to 90° F) ambient (Temperature is derated 1.8° C/1000 m or 1° F/1000 ft for altitude.)                                                                                                                                                                                                                                                                                                                                                    |

| Maximum gradient                       | 11° C/hr (20° F/hr)                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Nonoperating                           | -35° C to +60° C (-30° F to 140° F)                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Humidity<br>Operating                  | Maximum wet bulb: 25° C (77° F)<br>Minimum dew point: 2° C (36° F)<br>Relative humidity: 20% to 80%                                                                                                                                                                                                                                                                                                                                                           |

| Nonoperating                           | 5% to 95% relative humidity (noncondensing)                                                                                                                                                                                                                                                                                                                                                                                                                   |

| System Reliability                     | Disk Life: 3 million revolutions per track with head loaded. The head contacts 5 tracks when loaded.                                                                                                                                                                                                                                                                                                                                                          |

|                                        | Seek error rate:1 in $10^6$ seeksSoft read error rate:1 in $10^9$ bits readHard read error rate:1 in $10^{12}$ bits read                                                                                                                                                                                                                                                                                                                                      |

|                                        | NOTE<br>The above error rates only apply to media that is properly cared<br>for. Seek error and soft read errors are usually attributable to<br>random effects in the head/media interface, such as electrical<br>noise, dirt, or dust. Both are defined as "soft" errors if the error is<br>recoverable in ten additional tries or less. "Hard" errors cannot be<br>recovered. Seek error retries should be preceded by an initialize or<br>restore command. |

Table 1-2 PDT-11/150 Specifications

| Characteristic                                                | Description                                                                                                                                                                                                                                                           |  |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                               | NOTE                                                                                                                                                                                                                                                                  |  |

|                                                               | To ensure the integrity of the information stored on the disk, the<br>disks should not be in the disk drives when the ac power is initially<br>applied to the unit. The disks should be removed from the disk<br>drives before the ac power is removed from the unit. |  |

| Drive Performance<br>Data transfer rate<br>disk to RAM module | 32 $\mu$ s/16-bit word (nominal)                                                                                                                                                                                                                                      |  |

| Track-to-track-move                                           | 10 ms/track max                                                                                                                                                                                                                                                       |  |

| Head settle time                                              | 20 ms max                                                                                                                                                                                                                                                             |  |

| Rotational speed                                              | $360 \text{ r/min} \pm 2.5\%$ ; 166 ms/rev nominal                                                                                                                                                                                                                    |  |

| Recording surfaces per disk                                   | 1                                                                                                                                                                                                                                                                     |  |

| Tracks per disk                                               | 77 (0–76) or (0–114 <sub>8</sub> )                                                                                                                                                                                                                                    |  |

| Sectors per track                                             | 26 (1–26) or (1–32 <sub>8</sub> )                                                                                                                                                                                                                                     |  |

| Recording technique                                           | Double frequency                                                                                                                                                                                                                                                      |  |

| Bit density                                                   | 3200 bits/in at inner track                                                                                                                                                                                                                                           |  |

| Track density                                                 | 48 tracks/in                                                                                                                                                                                                                                                          |  |

| Average access*                                               | 488 ms                                                                                                                                                                                                                                                                |  |

| ac Power Requirements<br>115 V/60 Hz Input                    | Single disk drive: 2.5 A<br>Dual disk drive: 3.0 A                                                                                                                                                                                                                    |  |

| 90-130 V/50 Hz Input                                          | Single disk drive: 2.5 A<br>Dual disk drive: 3.0 A                                                                                                                                                                                                                    |  |

| 180–264 V/50 Hz                                               | Single disk drive: 1.5 A<br>Dual disk drive: 2.0 A                                                                                                                                                                                                                    |  |

| Device Signals                                                | All device signals are serial line and compatible with EIA stand<br>ard RS-232-C. (Refer to Tables 2-4 and 2-5 for signal require<br>ments.)                                                                                                                          |  |

| Table 1-2 | PDT-11/150 | Specifications (Cont) |

|-----------|------------|-----------------------|

|-----------|------------|-----------------------|

$(77 \text{ tks}/2) \times 10 \text{ ms}$

**1.1.3 Media Specifications** Table 1-3 describes the physical and electrical characteristics of the flexible disk media used with the PDT-11/150.

(166 ms/2)

20 ms

+

+

= 488 ms

| Specifications                    | Description                                                                                          |

|-----------------------------------|------------------------------------------------------------------------------------------------------|

| Description                       | Mylar based, oxide-coated disk                                                                       |

| Dimensions<br>Disk<br>Jacket      | 19.8 cm (7.8 in) diameter<br>20.26 cm (7.94 in) square                                               |

| Recording Format                  | Single-side, industry-compatible according to IBM 3740 floppy disk format, 77 data/address tracks    |

| Operating<br>Temperature/Humidity | Media temperature must be within PDT-11/150 operating tem-<br>perature and humidity range before use |

| Storage<br>Temperature            | -34° C (-30° F) to 52° C (125° F)                                                                    |

| Relative Humidity                 | 10% to 80% (noncondensing)                                                                           |

| Magnetic field                    | Exposure to magnetic field strength of 50 oersteds or greater may result in loss of data.            |

#### Table 1-3 Flexible Disk Specifications

#### **1.2 REFERENCE DOCUMENTS**

Table 1-4 lists the related publications that are available for the PDT-11/150 system. These publications provide detailed operator and maintenance information.

| Document No. | Title                                         | Medium*                |

|--------------|-----------------------------------------------|------------------------|

| EK-PT150-IN  | PDT-11/150 Installation Guide                 | Printed                |

| EK-PT150-J1  | PDT-11/150 Mini Maintenance Hardware<br>Guide | Printed                |

| EK-PT150-TM  | PDT-11/150 Technical Manual                   | Printed/<br>Microfiche |

\*Purchase orders for publications should be forwarded to:

Digital Equipment Corporation Accessories and Supplies Group Cotton Road Nashua, New Hampshire 03060

Contact your local sales office or call toll-free 800-258-1710 from 8:30 a.m. to 5:00 p.m. eastern standard time (U.S. customers only). New Hampshire, Alaska, and Hawaii customers should dial (603)-884-6660. Terms and conditions include net 30 days and F.O.B. DIGITAL plant. Freight charges will be prepaid by DIGITAL and added to the invoice. Minimum order is \$35.00. Minimum does not apply when full payment is submitted with an order. Checks and money orders should be made out to Digital Equipment Corporation.

#### **1.3 SUPPLIES AND ACCESSORIES**

DIGITAL's Direct Sales Catalog includes a complete line of computer and terminal supplies and accessories specifically designed for use with DIGITAL systems. These products enable reliable and efficient operation of your equipment. These products include:

- Preformatted flexible disks

- Power and terminal cables

- Printer and video terminals

- Storage cabinets and tables

A copy of the catalog may be obtained by calling toll free:

800-258-1710 (8:30 am 5:00 pm EST) 603-884-6660 (New Hampshire, Alaska, and Hawaii)

#### CHAPTER 2 UNPACKING/INSTALLATION

The PDT-11/150 programmable data terminal is a free-standing, self-enclosed unit that can be placed on a desk or table. The console device, modem, printer, and terminals which operate with the unit are attached by cables to the rear panel. The devices can be located adjacent to the unit or at a remote location.

The PDT-11/150 units are packaged in reinforced cartons and protected by side cushions and a protective cover. The *PDT-11/150 Installation Guide*, EK-PT150-IN, is included with the unit. All remaining publications, when ordered, are supplied in a separate container.

This chapter provides the information necessary to unpack PDT-11/150 and supporting documents; and to inspect the contents and connect the units with the associated devices.

#### 2.1 UNPACKING AND INSPECTION

Figure 2-1 shows the method used to unpack a dual drive unit. The single drive unit is packaged in a similar manner.

- 1. Remove the unpacking procedure diagram attached to the outside of the PDT-11/150 container.

- 2. Remove the PDT-11/150 unit according to the procedures on the diagram.

#### CAUTION

#### Do not lift the unit by grasping the front door handles of the disk drive assembly.

3. Visually inspect the unit for any physical damage.

#### NOTE

## If physical damage is evident, notify a local DIGITAL sales office.

- 4. Open and remove the contents of any other cartons supplied.

- 5. Using the packing lists attached to each carton, inspect the contents of each to ensure that all items listed are supplied.

Figure 2-1 PDT-11/150 Unpacking Procedure Diagram

6. Connect the female end of the ac power cord to the recessed male connector on the rear panel of the unit.

#### CAUTION

The PDT-11/150 units are available to operate with several variations of the ac input power. Check the metallic label on the rear panel of the unit to ensure that the power supplied at the site is compatible with the unit requirements.

#### **2.2 SITE PREPARATION AND CONNECTIONS**

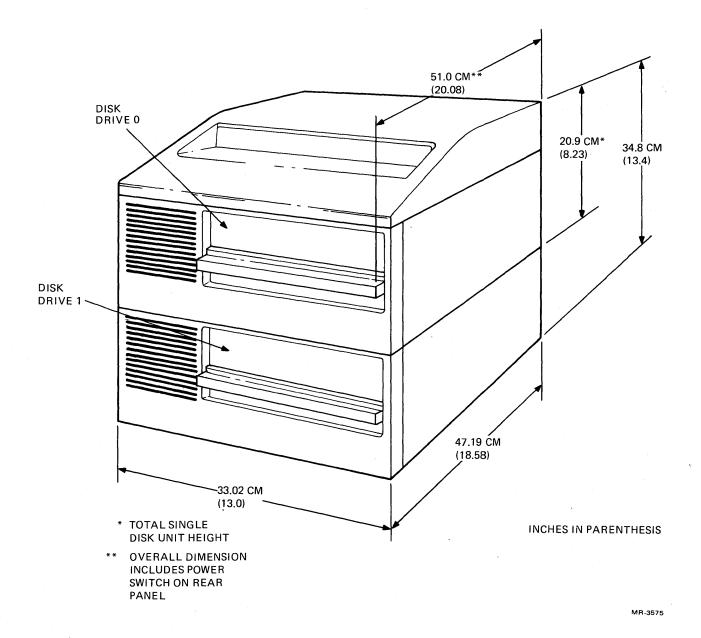

Figure 2-2 shows the overall dimensions of the single and dual drive units. Adequate clearance is required at the front of the unit for monitoring the indicators on the front panel and to allow the insertion and removal of the disk. Adequate area should be allowed at the rear of the unit for operation of the ac power switch and mode switch and to permit the free circulation of air through the fan also located on the rear panel. The signal and power cables that attach to the connectors on the rear panel should be free from obstructions and sharp bends.

#### NOTE

To prevent the accumlation of film and foreign matter on the disk and disk drive components, the PDT-11/150 should not be operated in locations having high levels of dust or industrial contaminants.

#### **2.2.1** ac Power Requirements

Table 2-1 lists the voltage, frequency and current ratings of the PDT-11/150 models. Each unit is shipped with the appropriate ac power cable also listed. Additional cable lengths are also available on request. A separate ac power outlet is required for connecting the PDT-11/150 power cord and console terminal power cord. The main ac line to the outlet can be fused at 10 A or greater.

#### NOTE

# Do not connect appliances or office equipment to the same ac circuits that supply power to the PDT-11/150 unit or associated console and terminals.

To connect the ac power, perform the following procedures:

- 1. Set the ac power switch on the rear panel to the OFF (0) position.

- 2. Connect the male end of the line cord to the ac outlet.

- 3. Connect the female end of the line cord to the rear panel of the PDT-11/150 unit.

#### 2.2.2 Serial Line Cable Connectors

Three 25-pin serial line connectors are mounted on the rear panel of the PDT-11/150 and an additional three 25-pin connectors are optional as shown in Figure 2-3. All cables from the devices operating with the disk unit attach to these connectors through compatible 25-pin RS232-type plugs. Table 2-2 lists the type of devices that can be attached to each connector. The connector type used on the other end of the cable is dependent on the device. Cable assemblies are normally included with the terminals; however, additional cables of various lengths are available from DIGITAL.

Some of the typical cable assembly types are listed in Table 2-3 and can be ordered by contacting a local DIGITAL sales office.

Figure 2-2 PDT-11/150 Single and Dual Disk Unit Dimensions

| Model No.                                                        | Voltage (ac)/<br>Frequency         | A/Unit | Cable No.                          |

|------------------------------------------------------------------|------------------------------------|--------|------------------------------------|

| PDT-11/150-AA, -AC,<br>-BA, -BC, -CA, CC<br>(single disk drive)  | 100–125 V/60 Hz                    | 2.5 A  |                                    |

| PDT-11/150-AE, -AH,<br>-BE, -BH, -CE, -CH<br>(dual disk drives)  | 100–125 V/60 Hz                    | 3.0 A  | 1700083-09*                        |

| PDT-11/150-AB, -AD,<br>-BB, -BD, -CB, -CD<br>(single disk drive) | 90–130 V/50 Hz<br>100–130 V/50 Hz  | 2.5 A  |                                    |

|                                                                  | 180–240 V/50 Hz<br>200–264 V/50 Hz | 1.5 A  | 1700083-10*                        |

| PDT-11/150-AF, -AJ,<br>-BF, -BJ, -CF, -CJ<br>(dual disk drive)   | 90–130 V/50 Hz<br>100–130 V/50 Hz  | 3.0 A  | (Europe)<br>1700083-09*<br>(Japan) |

| *Culli landia - 100 - // 25                                      | 180–240 V/50 Hz<br>200–264 V/50 Hz | 1.5A   |                                    |

Table 2-1

ac Power Requirements

\*Cable lengths are 1.90 m (6.25 ft).

| Table 2-2 | Rear Panel, | Device | Connector | Assignments |

|-----------|-------------|--------|-----------|-------------|

|-----------|-------------|--------|-----------|-------------|

| EIA Connections                            |                                                       |  |

|--------------------------------------------|-------------------------------------------------------|--|

| Standard                                   | Cluster                                               |  |

| Modem (J3)<br>Printer (J2)<br>Console (J1) | Terminal 3 (J3)<br>Terminal 2 (J2)<br>Terminal 1 (J1) |  |

Table 2-3

Available Device Cable Assemblies

| Cable No. | Cable Length | Connector    | Cable Type       | Connector      |

|-----------|--------------|--------------|------------------|----------------|

| BC05C-25  | 25 ft        | H856*        | Round            | RS232 (male)   |

| BC05C-50  | 50 ft        | H856*        | 25-<br>conductor | RS232 (male)   |

| BC05D-10  | 10 ft        | RS232 (male) |                  | RS232 (female) |

| BC05D-25  | 25 ft        | RS232 (male) |                  | RS232 (female) |

\*H856 40-contact female connector

-

**2.2.2.1** EIA Connector Pin Assignments – Figure 2-3 shows the contact numbering of the rear panel EIA connectors. Connector J3 of the standard EIA connectors is male and all other connectors on both the standard EIA and cluster EIA option are female. The signal/pin assignments for the standard connectors are listed in Table 2-4 and those for the cluster connectors are listed in Table 2-5. These signals are pin-compatible with equipment conforming to RS-232-C specifications, but not all the signals defined by RS-232-C are required by the PDT-11/150.

Figure 2-3 Rear Panel Components and Connector Pin Assignments

| Connector                           | Signal Designation                                                                                                     | Device                                                                                                                        |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| J1 (female)<br>pin                  |                                                                                                                        | Console Terminal<br>DIGITAL-type:                                                                                             |

| 2<br>3<br>20                        | Term Xmit Data<br>Term RCV Data<br>Term RDY                                                                            | LA34 DECwriter IV<br>LA36 DECwriter II<br>VT50 DECscope                                                                       |

| 1<br>7                              | Chassis GND<br>Signal GND                                                                                              | VT100 video terminal<br>LA120 DECwriter III<br>LS120 DECwriter III<br>VT52 DECscope                                           |

| J2 (female) -<br>pin                |                                                                                                                        | Printer Terminal<br>DIGITAL-type:                                                                                             |

| 2<br>3<br>20<br>1<br>7              | LP Xmit Data<br>LP RCV Data<br>LP RDY<br>Chassis GND<br>Signal GND                                                     | LA35 DECwriter II<br>LA36 DECwriter II<br>LA180 DECprinter<br>LA34 DECwriter II<br>LA120 DECwriter III<br>LS120 DECwriter III |

| J3 (male)<br>pin                    |                                                                                                                        | <i>Modem</i><br>Bell System type:                                                                                             |

| 2<br>3<br>12<br>5<br>22<br>8<br>6   | Modem RCV Data<br>Modem Xmit Data<br>SEC Carrier Detect<br>PRI CTS<br>Ring Indicator<br>Carrier Detect<br>Data Set RDY | 103, 113, 202, 212,<br>or equivalent                                                                                          |

| 11<br>4<br>20<br>17<br>15<br>1<br>7 | SEC RTS<br>PRI RTS<br>DTR<br>SYN CLK R<br>SYN CLK T<br>Chassis GND<br>Signal GND                                       |                                                                                                                               |

Table 2-4

Standard EIA Connector Signals

| Connector              | Signal Designation                                                                       | Device                                                                                                                          |

|------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| J1 (female)<br>pin     |                                                                                          | Printer/Video Terminal<br>DIGITAL type:                                                                                         |

| 2<br>3<br>20<br>7<br>1 | Term 1 Xmit Data<br>Term 1 RCV Data<br>Term 1 RDY<br>Signal IN (GND)<br>Chassis IN (GND) | LA36 DECwriter II<br>VT50 DECscope<br>VT52 DECscope<br>LA34 DECwriter IV<br>VT100<br>LA120 DECwriter III<br>LS120 DECwriter III |

| J2 (female)<br>pin     |                                                                                          |                                                                                                                                 |

| 2<br>3<br>20<br>7<br>1 | Term 2 Xmit Data<br>Term 2 RCV Data<br>Term 2 RDY<br>Signal IN (GND)<br>Chassis IN (GND) | Same as J1 terminal                                                                                                             |

| J3 (female)<br>pin     |                                                                                          |                                                                                                                                 |

| 2<br>3<br>20<br>7<br>1 | Term 3 Xmit Data<br>Term 3 RCV Data<br>Term 3 RDY<br>Signal IN (GND)<br>Chassis IN (GND) | Same as J1 terminal                                                                                                             |

Table 2-5

Cluster Option EIA Connector Signals

**2.2.2.2** Serial Line Cable Length – The maximum length of the serial line cables that connect from the PDT-11/150 to the terminals is 15.24 meters (50 feet).

#### 2.3 SERIAL LINE DATA CHARACTERISTICS

The baud rate and character parameters of the serial line data transferred between the devices and terminals and the PDT-11/150 must be compatible. Refer to Chapter 5 for the initial data conditions and for the data parameter programming information.

### CHAPTER 3 OPERATING PROCEDURES

The PDT-11/150 contains a series of diagnostic test programs stored in ROM and used to exercise the disk drives, the LSI-11 microprocessor and associated RAM module, and the peripheral ports which communicate with the serial line terminals. This chapter provides the information required to initiate the self-test functions and to monitor the results.

#### 3.1 SWITCHES AND INDICATORS

The front panel indicators and the switches on the rear panel provide the controls used during the selftest programs. The console terminal display and keyboard are also used in conjunction with the controls and indicators.

#### **3.1.1 Front Panel Indicators**

The front panel is located at the front of the unit on the top cover. Figure 3-1 shows the four indicators and Table 3-1 lists and describes the function of each indicator.

| Designation | Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | Lights to indicate a system error when in the self-test mode. During programmed operation, can be controlled by the user.                                                                                                                                                                                                                                                                                                                      |

| 2           | Lights to indicate that the system is waiting for an autobaud response from the con-<br>sole terminal. Occurs when ac power is applied to the unit or when the mode switch is<br>momentarily set to the RESET position and released during program operation<br>(NORMAL) or self-test mode. The autobaud function can be disabled by switch S1-1<br>(Table 5-24). During programmed operation, it can also be controlled by user pro-<br>gram. |

| RUN         | Lights to indicate that the LSI-11 microprocessor is executing instructions.                                                                                                                                                                                                                                                                                                                                                                   |

| POWER       | Lights to indicate that the +5 Vdc is present in the unit.                                                                                                                                                                                                                                                                                                                                                                                     |

#### 3.1.2 Rear Panel Switches and Components

The panel, mounted at the rear of disk drive 0, contains the ac power switch, fuse, and receptacle, a fan, the mode switch and the EIA 25-pin connectors. Figure 2-3 shows the location of the switches and components and Table 3-2 lists their functions. Refer to Paragraph 2.2.2 for a description of the 25-pin connectors and the associated devices.

#### 3.1.3 Function Control Switch

The PDT-11/150 contains an internal 5-switch DIP pack (S1) used to select specific conditions during program operations and during test functions. The switch pack is mounted on the peripheral module and can only be accessed by removal of the top cover of the unit. When the unit is shipped, the switches are set to the positions shown in Table 3-3 (refer to Figure 4-11).

| Item                   | Function                                                                                                                                                    |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ac power toggle switch | Up position (ON) – applies ac power to the PDT- $11/150$ .                                                                                                  |

| Fuse (3 A, 250 V)      | ac power fuse                                                                                                                                               |

| Mode (toggle switch)   | Three positions:                                                                                                                                            |

| RESET                  | Up position (momentary) – Initializes the PDT-11/150 system by clearing registers and logic.                                                                |

| NORMAL                 | Center position (latch) – Allows normal operation of the PDT- $11/150$ .                                                                                    |

| TEST                   | Down position (latch) – Initiates diagnostic testing of the PDT-<br>11/150 system and allows the BREAK key detection from the<br>console terminal keyboard. |

Table 3-2

Rear Panel Switches and Fuse

| Switch<br>No. S1 | Position | Function                                  |

|------------------|----------|-------------------------------------------|

| 1                | OFF      | Console terminal autobaud enabled         |

| 2                | ON       | Line time clock interrupt disabled        |

| 3                | OFF      | Dynamic RAM refresh enabled               |

| 4                | ON       | Self-test function of mode switch enabled |

| 5                | OFF      | Manufacture mode disabled                 |

#### Table 3-3 Function Control Switch Positions

#### **3.2 DISK HANDLING AND STORAGE**

The flexible disk used to store data and programs in the PDT-11/150 is shown in Figure 3-2. The oxide-coated disk is enclosed within a square plastic envelope. Precautions must be taken when handling and storing the disks to prevent loss of data or erroneous data and to ensure maximum operating life. The following practices are recommended.

- 1. To avoid touching the oxide surface of the disk, handle the disk by the envelope.

- 2. All disk identification should be written on a label prior to affixing on the disk. Do not write directly on envelope or apply a label over another label.

- 3. Solutions or chemicals should not be applied to the disk surface or to the envelope.

- 4. Clips or rubber bands should not be attached to the disk envelopes.

- 5. Heavy objects should not be placed on the disk.

- 6. Disks should not be subjected to sharp objects or magnetic fields.

- 7. Disks that are bent or mutilated should not be used.

- 8. The oxide-coated disk must not be removed from envelope.

- 9. Store disks in a box or contaminant-free enclosure.

- 10. Disks should not be exposed to direct sunlight or excessive heat.

3-3

Figure 3-2 Flexible Disk

#### 3.2.1 Insertion and Removal of a Disk

Perform the following procedures to load and remove a disk from the disk drive. Refer to Figure 3-3.

#### CAUTION

Remove all disks from the disk drives before applying ac power to the unit or removing the ac power from the unit. Do not install or remove a disk when the disk drive is performing read or write operations.

- 1. With the disk drive cover closed, grasp the center of the disk cover handle and press the release lever. The cover is spring-activated and will rise to the open position when the latch is released.

- 2. Hold the disk in the position shown with the read/write head aperture closest to the disk drive opening.

#### NOTE

The index hole aperture must be located on the left side of the disk center line as shown. If the hole is on the opposite side, turn the diskette over.

- 3. Insert the disk fully into the disk drive opening.

- 4. Press down on the top of the cover handle until the cover closes and remains in the latched position.

Figure 3-3 Loading the Disk into the Drive

5. To remove a disk, perform step 1, slide the disk gently from the drive unit and close the cover as described in step 4.

#### **3.3 TEST PROCEDURES**

The following procedures initiate the self-test diagnostic programs stored within ROM memory of the PDT-11/150. These procedures verify the correct operation of the disk drive and logical components within the unit. When the diagnostic tests have been successfully completed, the PDT-11/150 system exerciser program (CVKDAB0), contained on disk, may be initiated to further evaluate the performance of the unit.

#### NOTE

The PDT-11/150 system exerciser disk (CVKDAB0) can be ordered through your local DIGITAL sales office. The ordering designations are as follows:

Flexible Disk and Listing – ZJV03-RY Flexible Disk only – ZJV03-PY Listing only – ZJV03-RZ

#### 3.3.1 Preliminary Set-Up

Prior to initiating the self-test procedure, ensure that the following conditions exist.

- 1. The ac power is properly applied.

- 2. The console device and terminals are properly connected to the PDT-11/150 (Paragraph 2.2.2) and to the ac power.

- 3. The function control switches (Table 3-3) are set to the positions indicated.

- 4. The ac power switch (Figure 2-3) on the rear panel of the unit is in the OFF (0) position.

- 5. The mode switch (Figure 2-3) on the rear panel is in the TEST position (down).

- 6. No blank or programmed disks are installed in the drive(s).

#### **3.3.2** Optional Loopback Connector

The self-test procedures and system exerciser program include the facility for testing serial data transfers through the standard EIA connectors (except the console) and the Cluster EIA connectors. The loopback connector assembly is available as an option (DEC No. 70-16464) and must be attached to the connectors on the rear panel as shown in Figure 3-4. Remove all terminal cable connectors on the rear panel except the console terminal.

Figure 3-4 Loopback Connector Installation

#### 3.3.3 Self-Test Procedures

Perform the following procedures in the sequence indicated. If a failure is detected during the performance of this test, one or more of the following events will take place.

- 1. The error indicators (1) on the front panel will light.

- 2. An improper response to the test procedure will occur.

- 3. No response will occur when a response is indicated by the test procedure.

If the self-test diagnostic does not run successfully, repeat the procedure for a minimum of three times. The function control switches must be set to the positions indicated in Table 3-3.

1. Set the ac power switch to the ON (1) position.

#### NOTE

All indicators on the front panel, except the RUN indicator, will light initially when the ac power is applied. This confirms that the indicators are operative.

2. The power indicator on the front panel will remain lighted.

3. When the (2) indicator on the front panel remains lighted, press the @ symbol key twice on the console terminal keyboard.

#### NOTE

Some terminal keyboards may require that the SHIFT key be pressed when typing the two @ symbols.

4. The (2) indicator will be extinguished. This procedure establishes the baud rate of the PDT-11/150 to be compatible with the console terminal. The console terminal will respond by displaying the following message:

#### SCRATCH FLOPPY INSTALLED?

5. Open the front cover of the disk drive and insert a scratch disk. Refer to Paragraph 3.2.1 for disk insertion. In a dual drive unit, insert a scratch disk in each drive.

#### NOTE

## Scratch disks are preformatted blank disks without recorded data or disks with data no longer required.

6. Type Y on the console terminal when the disks are properly installed. This indicates a yes to the question in step 4.

#### NOTE

This initiates the read/write test of the disk. The disk controller module will write and read information from selected tracks. In a dual disk drive unit, disk 0 will be exercised first followed by disk 1. Allow approximately 2 minutes for the complete disk test.

7. If N is typed to indicate no, the disk drive exercise part of the self-test will not be performed. The console terminal will respond by displaying the following message:

#### EIA LOOPBACK TEST?

- 8. To run the EIA loopback test, the loopback connector assembly must be installed on the rear panel (Paragraph 3.3.2). Disconnect all terminal cable connectors from the rear panel except for the console terminal and attach the loopback connector. Type Y indicating yes on the console keyboard after the connector is attached. Type N indicating no if the loopback test is not desired.

- 9. After successful completion of this test, the console terminal will respond by displaying the following message:

XXXXXX (the six digits can be of any value) @

10. To initiate the LSI-11 microprocessor test and RAM module test, set the mode switch to the RESET position and release to the NORMAL position.

11. When the (2) indicator on the front panel remains lighted, press the @ symbol key twice on the console terminal.

#### NOTE

### Some terminal keyboards may require that the SHIFT key be pressed when typing the @ symbols.

12. The (2) light will be extinguished and the RUN indicator will light. After a short delay, the following message will be displayed on the console terminal.

#### NO BOOT ON VOLUME TYPE START UNIT NUMBER (0 OR 1):

13. The PDT-11/150 has successfully completed the self-test diagnostic. If it is desired to load a program disk or system exerciser disk, remove the scratch disk and insert the appropriate programmed disk into drive 0 or 1.

#### NOTE