# IAS Guide to Writing a Device Handler Task

Order Number: AA--H278C--TC

This document contains instructions for writing a device handler task for a peripheral device that is not part of the standard hardware configuration.

**Operating System Version:** IAS Version 3.4

#### May 1990

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

Restricted Rights: Use, duplication, or disclosure by the U.S. Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright ©1990 by Digital Equipment Corporation

All Rights Reserved. Printed in U.S.A.

\_ \_ \_

The postpaid READER'S COMMENTS form on the last page of this document requests the user's critical evaluation to assist in preparing future documentation.

The following are trademarks of Digital Equipment Corporation:

| DDIF       | IAS     | VAX C      |

|------------|---------|------------|

| DEC        | MASSBUS | VAXcluster |

| DEC/CMS    | PDP     | VAXstation |

| DEC/MMS    | PDT     | VMS        |

| DECnet     | RSTS    | VR150/160  |

| DECUS      | RSX     | VT         |

| DECwindows | ULTRIX  |            |

| DECwrite   | UNIBUS  |            |

| DIBOL      | VAX     | digital    |

|            |         |            |

This document was prepared using VAX DOCUMENT, Version 1.2

| PRE     | FACE                                                                                                                | xi             |

|---------|---------------------------------------------------------------------------------------------------------------------|----------------|

| CHAPTER | 1 DEVICE HANDLER TASK FUNCTIONS                                                                                     | 1–1            |

| 1.1     | EXECUTIVE PRIVILEGED TASKS                                                                                          | 1–2            |

| 1.2     | QUEUE I/O DIRECTIVE                                                                                                 | 1–3            |

| 1.3     | I/O INTERRUPTS                                                                                                      | 1–4            |

| 1.4     | SYSTEM SUBROUTINES                                                                                                  | 1-4            |

| 1.5     | PROCESSOR PRIORITIES                                                                                                | 1–4            |

| 1.6     | SYSTEM DATA STRUCTURES1.6.1Physical Unit Directory (PUD)1.6.2System Task Directory (STD)1.6.3Active Task List (ATL) | 1–5<br>1–6     |

| 1.7     | 1.6.4 I/O Request Node<br>MULTIUSER DEVICE HANDLERS                                                                 | 1–6<br><br>1–6 |

| 1.8     | USE OF ANCILLARY CONTROL PROCESSORS                                                                                 | 1–6            |

| CHAPTER | 2 DEVICE HANDLER TABLES                                                                                             | 2–1            |

| 2.1     | UNIT IDENTIFICATION TABLE                                                                                           | 2–1            |

| 2.2     | DISPATCH TABLE                                                                                                      | 2–2            |

| CHAP  | FER 3 | INITIALIZATION CODE                                                                                                                                                                                                                                                                | 3–1                             |

|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|       | 3.1   | 3.1 DECLARING THE HANDLER TASK RESIDENT (DSUT/DSMU)                                                                                                                                                                                                                                |                                 |

|       | 3.2   | CONNECTING TO A VECTOR (CINT)                                                                                                                                                                                                                                                      | 3–2                             |

|       | 3.3   | DEVICE-SPECIFIC INITIALIZATION                                                                                                                                                                                                                                                     | 3–3                             |

|       | 3.4   | SETTING UP THE POWER FAILURE AST                                                                                                                                                                                                                                                   | 3–3                             |

| СНАРТ | FER 4 | HANDLER TASK MAIN CODE                                                                                                                                                                                                                                                             | 4–1                             |

|       | 4.1   | WAITING FOR I/O COMPLETION OR A REQUEST                                                                                                                                                                                                                                            | 4–1                             |

|       | 4.2   | PERFORMING I/O COMPLETION (IODN)                                                                                                                                                                                                                                                   | 4–2                             |

|       | 4.3   | DEQUEUING A REQUEST (DQRN ANDDQRE)                                                                                                                                                                                                                                                 | 4–3                             |

|       | 4.4   | VALIDATING A REQUEST (VACC)                                                                                                                                                                                                                                                        | 4–4                             |

|       | 4.5   | DISPATCHING THE REQUEST (DISP)                                                                                                                                                                                                                                                     | 4–4                             |

|       | 4.6   | PROCESSING THE I/O FUNCTIONS         4.6.1       Special Functions Processor         4.6.1.1       KILL ALL REQUESTS and I/O RUNDOWN • 4–6         4.6.1.2       UNLOAD HANDLER • 4–7         4.6.3       Attach and Detach Processors         4.6.4       NOP and Error Processor | 4–5<br>4–5<br>4–7<br>4–8<br>4–8 |

|       | 4.7   | RECOVERING FROM POWER FAILURE                                                                                                                                                                                                                                                      | 4–9                             |

|       | 4.8   | SWAPPING CONSIDERATIONS<br>4.8.1 Free a Task for Swapping (FRSW)<br>4.8.2 Get Task Back in Memory (TKBK)                                                                                                                                                                           | 4–9<br>4–10<br>4–10             |

|           | 4.8.3   | Locking a Handler Task in Memory  | 4–10 |

|-----------|---------|-----------------------------------|------|

| 4.9       | EXITIN  | IG FROM THE SYSTEM                | 4–10 |

|           | 4.9.1   | Device-Specific Exit Processing   | 4–11 |

|           | 4.9.2   | Disconnecting from Interrupts     | 4–11 |

|           | 4.9.3   | Declaring Nonresidency            | 4–11 |

|           | 4.9.4   | Handler Task Exiting              |      |

| CHAPTER 5 | 5 INTER | RUPT SERVICE ROUTINE              | 5–1  |

| CHAPTER 6 | 5 SYSTI | EM GENERATION AND TASK BUILDING   | 6–1  |

| 6.1       | SYSTE   | EM GENERATION REQUIREMENTS        | 6–1  |

| 6.2       | LINKIN  | NG                                | 6–2  |

|           | 6.2.1   | Examples of Build Files           | 6–3  |

| CHAPTER 7 | 7 ERRO  | RLOGGING                          | 7–1  |

| 7.1       | INTRO   | DUCTION                           | 7–1  |

| 7.2       | ERRO    | R LOG SUPPORT FOR DEVICE HANDLERS | 7–1  |

| 7.3       | ERRO    | R LOGGING INTERFACE               | 7–1  |

|           | 7.3.1   | Handler Initialization            | 7–2  |

|           | 7.3.2   | Loading the Function Register     | 7–2  |

|           | 7.3.3   | Interrupt Service Routine         | 7–2  |

|           | 7.3.4   | MOUNT Command                     | 7–3  |

|           | 7.3.5   | Handler Exit                      |      |

| 7.4       | ERRL    | OG TASK RESPONSIBILITY            | 7–3  |

|           | 7.4.1   | ERRLOG Task Initialization        |      |

|           | 7.4.2   | ERRLOG Task Processing            | 7–3  |

| TER 8 | 8 SPECIAL CONSIDERATIONS FOR DMA DEVICES |                                                                            | 8–   |

|-------|------------------------------------------|----------------------------------------------------------------------------|------|

| 8.1   | INTRO                                    | DUCTION TO UMRS                                                            | -8   |

|       | 8.1.1                                    | Summary of Introduction                                                    | . 8- |

| 8.2   | UMR S                                    | SUPPORT DATABASE                                                           | -8   |

|       | 8.2.1                                    | Allocation Bitmap (.UMRBM)                                                 | - 8- |

|       | 8.2.2                                    | Free UMRs                                                                  | - 8- |

|       | 8.2.3                                    | Machine Indicator Word (.UMR22)                                            | - 8- |

| 8.3   | HAND                                     | LER LIBRARY ROUTINES FOR UMR SUPPORT                                       | -8-  |

|       | 8.3.1                                    | UMR Allocation Routines                                                    | _ 8- |

|       |                                          | 8.3.1.1URAL (UMR Allocator) • 8–4                                          |      |

|       |                                          | 8.3.1.2ALMR (UMR Allocator) • 8-4                                          |      |

|       | 8.3.2                                    | UMR Deallocation Routines                                                  | - 8  |

|       |                                          | 8.3.2.1URDA (UMR Deallocator) • 8–5<br>8.3.2.2DEMR (UMR Deallocator) • 8–5 |      |

|       | 8.3.3                                    | URFL (Provides 22-Bit Address for Transfer)                                | _ 8- |

|       | 8.3.4                                    | URF2 (Provides 22-Bit Address for Transfer)                                |      |

|       | 8.3.5                                    | URFR (Frees UMRs)                                                          |      |

|       | 8.3.6                                    | URAD (Converts Slot/Length To 18-Bit Address)                              |      |

|       | 8.3.7                                    |                                                                            |      |

|       | 8.3.8                                    | REAL (Calculates Real Address)                                             |      |

| 8.4   | SCOM                                     | BUFFERS AND UMR TRANSFERS                                                  | 8-   |

| 8.5   | VERIF                                    | Y TRANSFER (VXFR ANDVXUR)                                                  | 8    |

| 8.6   | FIXED                                    | AND DYNAMIC UMR HANDLING                                                   | 8    |

|       | 8.6.1                                    | Fixed UMR Handling                                                         | . 8- |

|       | 8.6.2                                    | Dynamic UMR Handling                                                       | _ 8  |

|       |                                          | 8.6.2.1 Semi-dynamic Handling • 8–9                                        |      |

|       |                                          | 8.6.2.2 Totally Dynamic UMR Handling • 8–9                                 |      |

### APPENDIX A SYSTEM SUBROUTINES

A–1

| <b>A</b> .1 | INTERRUPT HANDLING |      | A–2 |     |

|-------------|--------------------|------|-----|-----|

|             | A.1.1              | CINT |     | A–2 |

|         | A.1.2   | DINT                        | A2   |

|---------|---------|-----------------------------|------|

| A.2     | DECLA   | RING RESIDENCY/NONRESIDENCY | A_2  |

|         | A.2.1   | DSUT                        | A_3  |

|         | A.2.2   | DSMU                        |      |

|         | A.2.3   | DNRC                        | A-3  |

| A.3     |         | MPLETION                    | A-4  |

|         | A.3.1   | IODN                        | A-4  |

| A.4     | I/O REC | QUEST HANDLING              | A4   |

|         | A.4.1   | DQRE                        | A-4  |

|         | A.4.2   | DQRN                        | A5   |

|         | A.4.3   | DISP                        | A–5  |

|         | A.4.4   | VACC                        | A–6  |

| A.5     | NODE I  | HANDLING                    | A6   |

|         | A.5.1   | PENP                        | A6   |

|         | A.5.2   | PICK                        | A-7  |

|         | A.5.3   | NADD                        | A7   |

|         | A.5.4   | NDEL                        | A7   |

|         | A.5.5   | IPRI                        | A7   |

|         | A.5.6   | RNTP                        | A8   |

|         | A.5.7   | PENV                        | A8   |

|         | A.5.8   | PICV                        | A-8  |

|         | A.5.9   | RNTV                        |      |

|         | A.5.10  | NADV                        | A9   |

| A.6     | SETTIN  | G/CLEARING EVENT FLAGS      | A-9  |

|         | A.6.1   | SEFN                        | A-9  |

|         | A.6.2   | CEFN                        | A-9  |

|         | A.6.3   | STEF                        | A–10 |

|         | A.6.4   | CLEF                        | A-10 |

| A.7     | ATTAC   | HING/DETACHING A UNIT       | A-10 |

|         | A.7.1   | ATUN                        | A–10 |

|         | A.7.2   | DTUN                        | A–11 |

| <br>A.8 | I/O RUN | NDOWN AND KILL ALL REQUESTS | A11  |

|         | A.8.1FLSH<br>A.8.2FIFL        |      |

|---------|-------------------------------|------|

| A.9     |                               | A–11 |

|         | A.9.1VXFR                     | A–11 |

|         | A.9.2BLXO andBLXI             |      |

| A.10    | SWAPPING PAGE DESCRIPTORS     | A-12 |

|         | A.10.1SPD3                    |      |

|         | A.10.2SPD4                    | A–13 |

|         | A.10.3SPD5                    | A–13 |

| A.11    | TASK SWITCHING                | A–13 |

|         | A.11.1ENB0                    | A–13 |

| A.12    | ERROR LOGGING                 | A-13 |

|         | A.12.1ERLI                    | A–13 |

|         | A.12.2ERLD                    | A–14 |

| A.13    | IAS TASK SWAPPING             | A-14 |

|         | A.13.1FRSW                    | A-14 |

|         | А.13.2ТКВК                    | A–15 |

| A.14    | UMR HANDLING                  | A–15 |

| A.15    | POWER FAIL RECOVERY           | A–15 |

|         | A.15.1PWUP                    | A–15 |

| ENDIX B | SYMBOLIC DEFINITIONS          | B–1  |

| B.1     | PHYSICAL UNIT DIRECTORY (PUD) | B–1  |

| B.2     | SYSTEM TASK DIRECTORY (STD)   | B–5  |

| B.3     | ACTIVE TASK LIST (ATL)        | B–7  |

ı

| B.4        | I/O REQUEST NODE                                         | B–11  |

|------------|----------------------------------------------------------|-------|

| B.5        | INTERRUPT SERVICE ROUTINE NODE                           | B–12  |

| APPENDIX C | I/O STATUS BLOCK                                         | C–1   |

| APPENDIX D | SAMPLE DEVICE HANDLERS                                   | D1    |

| INDEX      |                                                          |       |

| FIGURES    |                                                          |       |

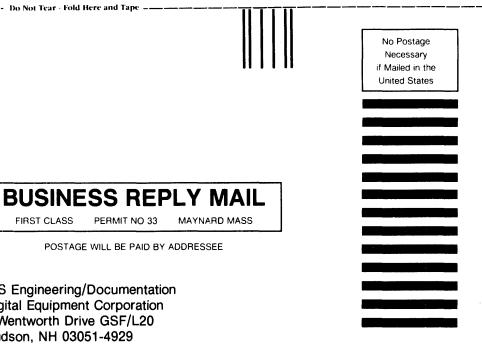

| 1–1        | Executive and Typical Handler Task Memory Maps           |       |

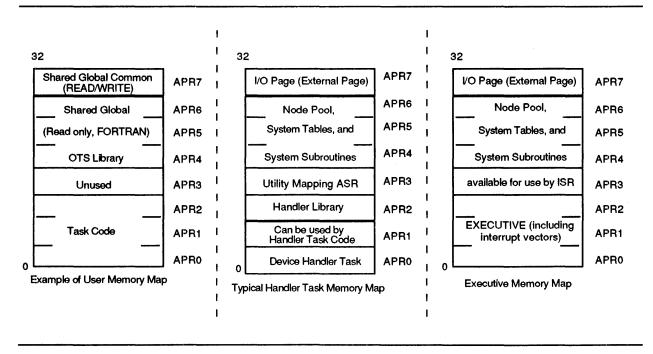

| 1–2        | Interface Between QIO and Device Handler Task            |       |

| C-1        | I/O Status Block                                         | C–1   |

| TABLES     |                                                          |       |

| 2–1        | Unit Identification Table Contents                       | . 2–2 |

| 2–2        | Dispatch Table Content and Layout                        |       |

| 6–1        | Device Directive Unit Type Characteristics Words         | . 6–1 |

| 7–1        | Record Format* of ERR.TMP and ERROR.TMP Files for Device |       |

|     | Errors                | 7–4 |

|-----|-----------------------|-----|

| 7–2 | Unit Descriptor Words | 7–5 |

## Preface

### **Purpose of the Manual**

The intent of this manual is to provide the information necessary to enable system managers and programmers of IAS operating systems to create a device handler task for a peripheral I/O device that is not part of the standard system hardware configuration.

To use this manual efffectively, you should:

- Be familiar with the PDP-11 computer and its peripheral devices.

- Have a thorough understanding of the operation of the IAS system.

- Be able to write programs using the MACRO-11 assembly language.

- Be able to use the task builder program.

#### Structure of the Document

This manual consists of eight chapters and four appendixes.

- Chapter 1 introduces the general functional requirements for a device handler task.

- Chapter 2 describes the task's internal communication tables.

- Chapter 3 discusses the various functions that must be performed during task initialization.

- Chapter 4 describes the details of a task's main functions.

- Chapter 5 describes the interrupt service routine portion of a task.

- Chapter 6 contains generation and linking procedures necessary to incorporate the task into the host operating system.

- Chaper 7 discusses the system's error logging facility and how to interface the task to this facility.

- Chapter 8 discribes UMR handling for handler tasks that are to service DMA devices attached to the UNIBUS of a PDP-11/70 or an 11/44.

- Appendix A describes the IAS system subroutines that a task can use.

- Appendix B shows the format, content, and offsets for various system tables and lists.

- Appendix C shows the structure of the task's I/O status block.

- Appendix D directs the programmer to various device handler source programs which can be used as examples

#### **Associated Documents**

Documents that provide information related to the creation, installation, and use of device handler tasks are listed in the IAS Master Index and Documentation Directory.

# **Device Handler Task Functions**

IAS provides a flexible, device-and-function-independent I/O capability that can support standard PDP-11 peripherals and special purpose devices. Peripheral device support is not an integral part of the Executive. It is provided by privileged tasks called device handlers.

I/O requests are issued by user tasks to logical units. The Executive maps the requests into physical device references using a set of device assignments. Each task has its own set of assignments that can be changed from the user's terminal or by the task during execution.

An I/O request is made by issuing a system directive, Queue I/O (QIO), to queue a request for a specified logical unit number (LUN). If the LUN is assigned to a physical unit and if the handler task that supports that unit is in memory and loaded or running, the request information is put into a request node buffer that is queued by priority in a request list for the specified physical unit.

The Executive does not attempt to interpret or validate the request; it only passes the request to a device handler task indicated by the LUN assignment. Interpretation and execution of the request are functions of the device handler task.

When an I/O request is issued by a user task, control is returned immediately to the task (contingent only upon the task priority). The user task has the option to suspend execution until I/O completion or to operate asynchronously.

The handler task can notify the user task of I/O completion by calling a system subroutine. You can use the subroutine to perform the notification in any of the following ways:

- Declaring a significant event and setting a specified event flag.

- Setting indicators in an I/O status block within the requesting task.

- Causing an asynchronous system trap for the requesting task.

Each I/O request contains an I/O function code that describes the operation to be performed. Device handler tasks must be able to interpret a set of standard I/O function codes in a manner that is appropriate to the indicated device.

Because most devices have device-dependent characteristics, it is not practical to implement all functions for all devices (for example, a read function is not implemented for a line printer). If an I/O request is issued that contains an illegal function code for a specified device, the handler task returns an error code indicating that the function is not implemented.

Device handler tasks also return a standard set of error conditions to the I/O status block. Appendix C describes the I/O status block.

The IAS system provides device handler tasks for standard Digital hardware (for example, DECtape, magnetic tape, line printers, A/D converters); however, when a nonstandard device is to be supported, the user must write the requisite device handler task. The user can write device handler tasks to control I/O for both single-unit and multiple-unit devices. Multiple-unit devices require more complex handlers than single-unit devices.

Device handler tasks contain five basic sections:

1 A table area to facilitate communication with system subroutines,

- 2 Initialization code to execute once the task is loaded,

- 3 Code to dequeue and service I/O requests,

- 4 An interrupt service routine (ISR), and

- 5 A power failure recovery section.

In some cases, for example pseudo device handlers, power failure recovery and/or an ISR is not required.

#### **1.1 Executive Privileged Tasks**

Because device handler tasks are executive privileged tasks, they have access to some Executive portions of memory. Portions of the handler task are commonly mapped with the Executive, thus enabling access to common areas of code. Figure 1–1 illustrates a typical memory map for a device handler task.

Note that APR3 is used by several Handler Library (HNDLIB) and System Communications area (SCOM) routines as a *scratch* mapping area. APR3 should not contain handler code. If the handler also uses APR3 as a scratch area, care should be taken that the data currently mapped by the APR is not required by any of the system routines. See also Section 6.2.

Handler tasks, like all other tasks, execute in User Mode, with the exception of the interrupt service routine, which executes in Kernel Mode.

#### Figure 1–1 Executive and Typical Handler Task Memory Maps

#### 1.2 Queue I/O Directive

The Queue I/O (QIO) is the lowest level of task I/O. When a task issues a QIO directive, the directive parameter block (DPB) contains the information that the Executive requires to place the I/O request in the queue of the desired device handler. The DPB provides the following information:

- An I/O function code,

- A logical unit number (LUN),

- An event flag number,

- A request priority,

- The address of the I/O status block, (optional),

- The address of the I/O done asynchronous trap (AST) entry point (optional), and

- A list of up to six parameters specific to the I/O function.

The IAS System Directives Reference Manual contains a detailed description of the QIO directive.

The Executive uses the LUN to determine the device handler task for which a request is intended, takes a node from the pool, and fills the node with I/O request parameters from the QIO DPB. A node containing I/O request parameters is called an I/O request node. The Executive places this node in the device handler task's queue. I/O requests are queued according to priority (normally that of the requesting task) so that higher priority requests receive faster service than lower priority requests. Requests of the same priority are queued in the order issued.

After queuing a request, the Executive sets an event flag to signal the handler task that an I/O request for the task has been queued. Figure 1-2 illustrates the flow of an I/O request.

Figure 1–2 Interface Between QIO and Device Handler Task

#### 1.3 I/O Interrupts

When an I/O interrupt occurs, the handler task's interrupt service routine (ISR) must process the interrupt. Because the rapid processing of interrupts is essential, the Executive maps the ISR into Kernel address space 60000 through 77777 (APR3) and jumps (JMP) to it for execution whenever an interrupt occurs. Processing the interrupt in this fashion eliminates the need to switch from Kernel Mode to User Mode before processing the interrupt. It also eliminates the need to save and restore the user APRs. See Figure 1-1 for an illustration of the Executive memory map.

The initialization portion of the device handler task contains a call to a system subroutine (...CINT) to connect an interrupt service routine to a unique vector address. For multiple-unit handlers, this subroutine is called once for each vector. The subroutine creates a code sequence (contained in a node) that executes in Kernel Mode. The code sequence performs the following functions when an interrupt occurs:

- 1 Saves the current Kernel APR3 on the stack,

- 2 Sets Kernel APR3 to the address of the handler task's ISR,

- 3 Clears the corresponding bus activity bit in the I/O bit map used in error logging,

- 4 Sets specified condition codes for the unit in the Processor Status Word (condition code settings are frequently used to pass unit numbers when a common ISR is used for multiple units), and

- 5 Jumps to the ISR of the handler task.

#### 1.4 System Subroutines

The IAS system provides subroutines that device handler tasks can call to perform standard functions. Some of the subroutines are contained in the system communications area (SCOM) and are available to any privileged task. Others are contained within the handler library routines (HNDLIB). Access the handler library routines either by mapping onto a shareable global area or extracting them from an object module library at task build time. Use of the Handler Library is described in Section 6.2 and Appendix A. Appendix A also describes the functions of the system subroutines.

System subroutine names have the format ..xxxx. The designation xxxx is a unique 4-character name (for example, ..CINT). Device handler tasks call the subroutines with the CALL macro, which generates a JSR to the subroutine using the program counter (JSR PC). The only exception is ..DISP, which is jumped to (JMP) rather than called.

Communicate with system subroutines through general registers and the program stack. An error return from a system subroutine causes the C condition code in the processor status word to be set. Routines such as ..IODN that do not detect errors can return with the C condition code either set or clear.

#### **1.5 Processor Priorities**

When a device handler task is running, it is often necessary to disable the host operating system's task switching function as well as the processor's interrupt facility while critical sections of handler code are being executed. Task switching is disabled by raising the processor priority level to 3. Interrupts and task switching are inhibited by raising the processor priority level to 7. The following macros are commonly used to disable and reenable task switching and interrupts. These macros are contained in the file RSXMAC.SML. The macros .INH0 and .ENB0 should be used as a matched pair, and so should .INH and .ENB.

Inhibit Task Switching:

;PROCESSOR STATUS WORD ADDRESS .MACRO .INHO ;INHIBIT TASK SWITCHING MOV PS.EXP,-(SP) ;SAVE THE CURRENT PROGRAM ;STATUS BIS #140,PS.EXP ;SET PRIORITY TO 3 .ENDM .INHO

Allow Task Switching:

;PROCESSOR STATUS WORD ADDRESS .MACRO .ENBO ;ALLOW TASK SWITCHING CALL ..ENBO ;CALL THIS SYSTEM ROUTINE WITH ;THE PROGRAM STATUS ON THE ;TOP OF THE STACK .ENDM .ENBO

Inhibit Interrupts and Task Switching:

; PROCESSOR STATUS WORD ADDRESS .MACRO .INH ; PREVENT INTERRUPTS MOV PS.EXP,-(SP) ; SAVE THE CURRENT PROGRAM ; STATUS BIS #340,PS.EXP ; SET PROCESSOR PRIORITY TO 7 .ENDM .INH

**Reenable Interrupts and Task Switching:**

;PROCESSOR STATUS WORD ADDRESS .MACRO .ENB ;ENABLE INTERRUPTS MOV (SP)+,PS.EXP ;RESET PROGRAM STATUS TO ;PREVIOUS PRIORITY LEVEL .ENDM .ENB

#### **1.6 System Data Structures**

A device handler task makes use of a number of data structures that are internal to the host operating system. These structures reside in SCOM, which is accessible only to privileged tasks (see Chapter 6). Detailed information describing these data structures is provided in Appendix B.

#### 1.6.1 Physical Unit Directory (PUD)

The physical unit directory (PUD) is a system table that contains descriptive information for each physical device in the system. The table is created during system generation. Each PUD entry is 26 (decimal) words long. References to physical devices from other system tables point to the corresponding PUD entry.

### 1.6.2 System Task Directory (STD)

The system task directory (STD) is a table that provides information about each task installed in the system. The information recorded in a task's STD entry includes:

- Information required when the task is not active (for example, receive linked list listhead),

- Information required to load a task into memory (for example, task name, disk address of image)

#### 1.6.3 Active Task List (ATL)

The active task list (ATL) contains an entry for each active task. Information contained in each entry includes event flag settings and I/O counts.

#### 1.6.4 I/O Request Node

For each I/O request issued, the host operating system creates an I/O request node to record information about the request. This node is linked into the I/O Request Queue (IRQ) for the particular device handler to perform the I/O operation. The handler dequeues an I/O request node each time it is ready to perform another I/O operation.

The IRQ for the handler is a deque of I/O request nodes that are linked to the handler task's header, at offset H.IOQ. The IAS Executive Facilities Reference Manual describes the IRQ and the task header more fully.

#### 1.7 Multiuser Device Handlers

Some tasks are built such that several copies of those tasks can run simultaneously. Such tasks are called multiuser tasks.

For some devices (for example, line printers, card readers) there is one hardware controller for each device unit. In such a case, it is convenient to write the device handler for just one unit, to build it as a multi-user task, and to run a separate copy of that task for each unit to be serviced. The handler does not have to cope with several simultaneous transfers, and each unit can operate at full speed.

The concept can be extended to systems that have several controllers of one kind where each controller governs several units. The handler can be written for one controller, then built and run as a multiuser task to service many controllers.

A multiuser device handler has the following features:

- 1 It is task built with the multiuser attribute (/MU MCR switch or /MULTIUSER PDS command qualifer).

- 2 It has as much code and data as possible in read-only program sections. Such sections are shared when a task is run as multiuser to reduce the amount of resident code.

- 3 The handlers' TI assignment always refers to the controller that it is servicing, not, as with a single-user handler, to the invoking terminal.

This TI assignment provides a way of associating a particular running copy of the handler with a particular controller. See Section 2.1 for details.

4 The handler declares itself resident in a slightly different way from a single-user handler. See Section 3.1.

### **1.8 Use Of Ancillary Control Processors**

QIO functions can be handled in one of two ways:

- 1 The handler can perform the required processing by executing code routines within the handler task.

- 2 They can be directed to an ancillary control processor (ACP) for processing.

The method to be used for each QIO function is indicated by the entry for that function code in the dispatch table within the handler task (see Section 2.2). According to this information, the handler dispatches the QIO either to the appropriate internal routine (using a JMP instruction) or to the ACP task for the device (using a SEND/REQUEST directive). Section Section A.4.3 describes the HNDLIB routine ...DISP, which performs the dispatching.

The ACP method of processing is useful for complicated or multifunction QIOs. Offloading QIO processing to an ACP frees the handler to process other QIOs.

Typically, ACPs perform the following functions:

- File processing operations

- Network protocol operations

- Common I/O database maintenance

# 2 Device Handler Tables

Each device handler task must set up two tables that are used to communicate with the system subroutines:

- Unit identification table (see Section 2.1)

- Dispatch table (see Section 2.2)

Because the system subroutines use the unit identification table and the dispatch table, both tables must be in the format specified in the following sections.

#### 2.1 Unit Identification Table

Use the unit identification table (UIT) for dequeuing I/O requests. The UIT consists of a 5-word header area, followed by one or more 3-word entries. One 3-word entry is required for each unit serviced by the handler task (for example, a single-unit handler has one entry).

Table 2-1 describes the content of the UIT.

The third column of Table 2–1 shows the values to which the table elements must be preset by the device handler task. The following comments concern word A:

- 1 For a single-user handler servicing one or more units, word A must be preset to a, b, c ... in successive entries corresponding to the unit number of each unit to be serviced, where a, b, c ... are usually 0, 1, 2 ... After loading, the handler's TI is assigned to the invoking terminal.

- 2 For a handler written to drive one unit, and built and run as a multi-user task to service many such units, word A holds a unit validity mask, which must be set to zero.

When the command to load the handler, say for a device type CD, is given, the Executive searches the PUD for all devices CDn. For each CDn, the Executive loads a copy of the handler with its TI assigned to the corresponding unit CDn. The handler code uses this assignment to refer to the appropriate unit.

3 A handler can also be written to service a single controller, which itself governs a number of units. The handler can be built and run as a multi-user task to service many such controllers. The maximum number of units supported by the controller must always be a power of 2. Call this number r.

In this case the first occurrence of word A must be preset to r-1 to form the unit validity mask. Presets of word A for subsequent units are ignored.

When the command is given to load the handler, (for example, EF) the Executive attempts to run a handler for each unit EFn found in the PUD and to run it with a corresponding TI assignment. The system subroutine ...DSMU (see Section 3.1) then compares the mask with the unit number. If the unit number is not a multiple of r, the handler is terminated.

This ensures that handlers can be loaded only as follows:

a copy to service EF0, EF1, ... , EF(r-1) with TI assigned to EF0

and/or

a copy to service EFr, EF(r+1), ... , EF(2r-1) with TI assigned to EFr

and so on, as far as necessary.

It also follows that if unit  $EF(r^*j+k)$ , with 0 < k < r, has been declared at system generation, it can be serviced only if  $EF(r^*j)$  is also declared. Thus with r=2 and three units, the units can be EF0, EF1 and EF2. But with EF0, EF1 and EF3 a handler is loaded for EF0 and EF1, but not for EF3.

| Word | Byte | Initial Content                                        | Eventual Content                                                                                            |

|------|------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 0    | 0,1  | Address of the Dispatch<br>Table                       | Unchanged                                                                                                   |

| 1    | 0    | Maximum number of units<br>serviced by the handler     | Unchanged                                                                                                   |

| 1    | 1    | Zeros                                                  | Actual number of units to be serviced. Set up byDSUT or byDSMU                                              |

| 2    | 0    | Zeros                                                  | Unit number of the last normal request dequeued.<br>Changed byDQRN                                          |

| 2    | 1    | Zeros                                                  | Unit number of the last express request dequeued.<br>Changed byDQRE                                         |

| 3    | 0,1  | Reserved                                               | Reserved                                                                                                    |

| 4    | 0,1  | Reserved                                               | Reserved                                                                                                    |

|      |      | Each Unit Entry Contair                                | ns the Following Information                                                                                |

| A    | 0,1  | Unit number (single-user<br>handler) or                | Pointer to start of PUD entry for the unit. Changed byDSUT or byDSMU.                                       |

|      |      | Unit validity mask–multiuser handler; see Section 2.1. |                                                                                                             |

| В    | 0,1  | Zeros                                                  | Pointer to start of current normal request node. Changed byDQRN when a normal request is dequeued.          |

| С    | 0,1  | Zeros                                                  | Pointer to start of current express request node.<br>Changed byDQRE when an express request is<br>dequeued. |

Table 2–1 Unit Identification Table Contents

#### 2.2 Dispatch Table

The dispatch table enables validation of the user task's access rights to the device. Validation is based on the function code of the I/O request and the device class specified.

The dispatch table contains read-only information; its contents are never altered. It contains a 2word header followed by one 2-word entry for each function code serviced by the handler task. The high-order byte of the function code indicates the order in which the codes occur in the table. For example, the first three entries in a dispatch table could be Special Function (00), Write Logical (01), and Read Logical (02). Table 2-2 provides the layout and content of the dispatch table.

| Word | Byte | Content                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0,1  | Address to branch to if a SEND/REQUEST failure occurs. <sup>1</sup>                                                                                                                                                                                                                                                                                                                                        |

| 1    | 0,1  | Address to branch to if SEND/REQUEST is successful. <sup>3</sup> .                                                                                                                                                                                                                                                                                                                                         |

|      |      | Each Function Code Entry Contains the Following Information                                                                                                                                                                                                                                                                                                                                                |

| A    | 0    | Volume characteristics mask. If set, the bits in word A indicate the following.                                                                                                                                                                                                                                                                                                                            |

|      |      | Bit 7 = The volume must be mounted to perform this I/O function.<br>Bit 6 = The device must be a FILES-11 volume to perform this function.<br>Bit 5 = The volume must not be set for unloading to perform this function.<br>Bit 4 = The volume must be attachable to perform the I/O function.<br>Bit 3 = Device control functions must be permitted to perform this I/O function.<br>Bits 2-0 = Reserved. |

| Α    | 1    | Control variable. If set, the bits in the first word indicate the following:                                                                                                                                                                                                                                                                                                                               |

|      |      | Bit 15 = Word U.DACP of the PUD entry for the device contains the first three characters<br>(in RAD50) of the taskname for the SEND/REQUEST.<br>Bit 14 = The 5 high-order bits of the subfunction code must be 0; otherwise, the request<br>is not valid.<br>Bit 13 = The express bit (bit 1) of the subfunction code must be 0; otherwise, the request<br>is not valid.<br>Bit 12 = Reserved.             |

|      |      | Bit 11 = The user task must have delete privileges; otherwise, the request is not valid.<br>Bit 10 = The user task must have extend privileges; otherwise, the request is not valid.<br>Bit 9 = The user task must have write privileges; otherwise, the request is not valid.<br>Bit 8 = The user task must have read privileges; otherwise, the request is not valid.                                    |

|      |      | Bits 11 through 8 above determine the minimum access rights required, as defined in the volume control block for that user, to allow the user to perform a given I/O function.                                                                                                                                                                                                                             |

| В    | 0,1  | If bit 15 of word A for this entry is 0, word B contains the starting address of the routine to process the function code. <sup>3</sup>                                                                                                                                                                                                                                                                    |

|      |      | OR                                                                                                                                                                                                                                                                                                                                                                                                         |

|      |      | If bit 15 is 1, word B is unused.                                                                                                                                                                                                                                                                                                                                                                          |

Table 2–2

Dispatch Table Content and Layout

<sup>1</sup>Function codes can be processed by the handler (READ/WRITE); or by using SEND/REQUEST to the file processor (OPEN/CLOSE); or by using SEND/REQUEST to Files-11 ACP functions (for example .FIND).

<sup>3</sup>When the second word contains the address of the routine to process the I/O request, it indicates the I/O function code to be executed. If the function is not recognized by the handler (for example, a Create function for a Terminal), the routine addressed by word B immediately returns a valid status (essentially a NOP) or illegal function status by putting the status value in R3 and jumping to the I/O done routine (..IODN). See the discussion of ..IODN in Section A.3.1.

# **3** Initialization Code

Under normal operation, a newly generated system has only a terminal and a disk handler task initialized and ready to process I/O requests. All other handler tasks must be loaded. The handler task is started at the beginning of the initialization code, which is specified as the transfer address in the same manner as for any other task (for example, .END INIT).

The initialization code must perform the following functions, which are basic to all device handler tasks:

- 1 Declare the handler task to be resident.

- 2 Connect to the interrupts.

- 3 Set up the optional I/O bus activity bit mask (for error logging).

- 4 Set up the optional I/O statistics buffer (double precision), which must be picked from the system node pool area using either ..PICV or ..PENV (see Appendix A).

- 5 Perform initialization specific to the device class.

- 6 Allocate UMRs (UNIBUS mapping registers), if necessary (see Chapter 8).

- 7 Set up the power failure recovery AST.

### 3.1 Declaring the Handler Task Resident (..DSUT/..DSMU)

The device handler task calls one of the system subroutines ..DSUT or ..DSMU to declare itself resident and ready to handle I/O requests. ..DSMU is used by multiuser handlers (see Section 1.7), and ..DSUT by non-multiuser handlers. ..DSMU performs some additional checking required by multiuser handlers, then calls ..DSUT. ..DSUT places the active task list (ATL) node address of the handler task in each physical unit directory (PUD) entry corresponding to the device for that handler task. ..DSUT also sets the handler-resident bit in each PUD entry and replaces the unit number in the UIT with a pointer to the first word of the PUD entry for that unit. It also places the virtual address of the UIT entry of the device in offset U.SL of the PUD.

Once ...DSUT has set up the UIT and PUD entries for the device, requests can be queued to the handler task. Prior to this point, the system returned the handler-not-resident status on attempted I/O requests.

The ...DSUT subroutine and the ...DSMU subroutine require the following registers to be preset:

- R0 must contain the address of the UIT.

- R2 must contain the 2-character ASCII device type, for example, TT for the terminal handler.

- R3 must contain the flag byte to be inserted in the PUD flag word. This register is usually set to the global symbol UF.RH implying that the handler task is resident.

- For a disk handler task, UF.TL should also be set (that is, R3 = UF.RH!UF.TL). UF.TL indicates that tasks can be loaded from the device.

After successful execution of the appropriate routine, R1 contains the number of units found, and the C condition code in the Processor Status word is clear. If the routine is not successful, the C condition code is set.

..DSUT or ..DSMU returns an error if:

- 1 No unit of the specified device type is found.

- 2 Another handler task is found servicing the unit.

In addition, .. DSMU returns an error if:

- 1 The device name in the handler's TI assignment does not match the device type declared in R2.

- 2 The unit validity mask (see Section 2.1) shows that the handler is being run for an illegal unit.

After ...DSUT has returned control to the handler, the handler task should ensure that residency was declared successfully by testing the C condition code in the processor status word. Additional checking might also be useful; for example, the handler could verify the number of PUD entries.

If the handler task is to service a DMA device attached to the UNIBUS of a PDP-11/44 or a PDP-11/70, it must allocate UMRs. Allocation can occur before connecting to an interrupt or dynamically for each transfer. Refer to Chapter 8.

#### 3.2 Connecting to a Vector (..CINT)

Once a device handler task has declared itself resident, it can connect to an interrupt vector. To do so, the handler calls ...CINT. The ...CINT subroutine creates an intermediate program node between the unit's interrupt vector and the device handler's interrupt service routine and calculates the I/O bus activity bit mask based upon the vector address passed to ...CINT as a parameter. ...CINT sets the interrupt vector PC to point to the program node. The program node sets the processor status word to the correct priority, to the desired condition codes for use upon entry to the ISR when an interrupt occurs for the unit, and to Kernel mode.

The ...CINT subroutine must be called once for each interrupt vector serviced by the handler. For example, the terminal handler calls ...CINT twice for each unit serviced: once for the receive interrupt vector, and once for the transmit interrupt vector.

Calling ...CINT locks the handler task into its current memory area. See Section 4.8.3.

If an interrupt service routine is not resident in the same contiguous area of memory as the device handler task (for example, if the interrupt service routine is in an SGA), calling ...CINT fails.

The ...CINT subroutine requires the following registers to be preset:

- R0 must contain the address of the hardware interrupt vector.

- R1 must contain the address of the entry point of the ISR.

- R2 must contain the base address of the ISR area. The base address is usually zero.

- R3 must contain the low-order byte of the Processor Status word (priority and condition codes) available when the ISR begins.

The I/O bus activity bit map enables the system to monitor the traffic on the UNIBUS. The device handler can optionally set the corresponding bit while initiating a data transfer or related function. This bit is automatically cleared in the intermediate program node at the time of interrupt.

If the load on the UNIBUS causes an error to occur, the system error logging capability aids in detecting this type of problem. Error logging uses this to determine all other devices with outstanding requests. Interrupt service routines can be position-independent code to enable their use under Kernel APR3. However, interrupt service routines are not restricted to position-independent code and its implied addressing mode restrictions. By setting R2 (base of the ISR) to 0, Kernel APR3 maps directly over the user APR0 at interrupt time. Therefore, the relative APR offset for any address while running under Kernel APR3 is 60000(8).

For example, while position-independent code precludes use of an instruction such as the following:

MOV ADR(R1), (R2)

The ISR can achieve the same result using the following instruction:

MOV ADR+60000(R1), (R2)

The handler tasks can use the connect to interrupt routine (..CINT) to set condition codes in the PS. Upon entry to an ISR, the condition codes specified in R3 can serve a vitally needed function for multiple-unit handlers with a single ISR. Any number of different interrupts can map into the same ISR. The ISR can use these codes to determine which device has interrupted by examining the four condition code bits (N,Z,V,C) in the Processor Status word. See Chapter 5.

R3 also contains the software priority of the ISR. Normally, it is the same as the hardware interrupt priority. Making the two priorities the same eliminates the need to write reentrant interrupt service routines.

### 3.3 Device-Specific Initialization

Special initialization code depends on the nature of the device being serviced and varies from handler to handler. For example, the terminal handler task sets the read enable interrupt and selects a read ahead node for each unit it services.

If any errors occur during initialization (usually error exits from system subroutines), the handler task should exit after undoing those functions that have already been successfully performed, as described in Section 4.9.

Normally, it is good programming procedure to make the initialization code the first part of the task such that it is contiguous with the task's stack, and the last instruction of the initialization code a JSR SP,xxx. The designation xxx is the start of the device handling (active) code. Thus, the entire initialization code can be used as stack space. This procedure implies a small initial stack size at task build (link) time and a correspondingly smaller task size at run time.

The handler task build (link) must ensure that sufficient stack space is available. Because handler tasks map the external page, overflowing the stack destroys the content of location 177776 (that is, the processor status word) and usually causes a system crash.

### 3.4 Setting Up the Power Failure AST

To set up the AST for recovery after power failure, the handler task uses a system directive. The macro SPRA\$ defines the address of the routine that performs power failure recovery.

Section 4.7 describes the action you should take on power failure recovery.

# 4 Handler Task Main Code

The main code of the device handler task dequeues I/O requests and performs the specified input/output operation. The queue contains I/O requests of two types: normal requests and express requests. The difference between normal and express requests is that express requests require immediate attention from the handler (for example, I/O RUNDOWN) whereas normal requests require attention according to their queued priority.

The main code of the handler task performs the following functions:

- 1 Waits for an I/O completion flag to be set or a request to be queued,

- 2 Performs the necessary I/O completion functions,

- 3 Tries to dequeue the next request,

- 4 Validates the request, if one is dequeued,

- 5 Dispatches the request to the appropriate I/O function routine, and

- 6 Exits on request.

Power failure recovery, if present in the handler task, is included in the main code.

#### 4.1 Waiting For I/O Completion or a Request

Among the first steps in the main portion of a device handler task is a wait loop. The loop usually tests for any of the following significant events using the Wait For Logical Or of Event Flags (WTLO\$) system directive:

- 1 Completion of an I/O operation which sets an event flag (normally flag 3),

- 2 The queuing of an express request which sets event flag 2,

- **3** The queuing of a normal request which sets event flag 1.

Most of the time it is resident in memory, the handler task is waiting for an event to happen. That wait location is referred to as IDLE in this manual. When an event occurs, the handler must determine exactly what action is required. Therefore, the handler should read its own event flag word and clear the I/O done flag only if an I/O event has completed. The following is an example of the code required:

> .INH ;;;INHIBIT INTERRUPTS MACRO MOV .CRTSK,R3 ;;;GET TASK'S OWN ATL ADDRESS MOV A.EF(R3),R5 ;;;GET EVENT FLAG WORD BIC #4,A.EF(R3) ;;;CLEAR I/O DONE EVENT FLAG .ENB ;;ENABLE INTERRUPTS MACRO

Unlike event flags 1 and 2, which are reset by the system dequeuing subroutines (...DQRN and ...DQRE), the I/O done flag must be cleared by the device handler.

After the code illustrated above has executed, the event flags are located in R5. The first flag to be checked by the handler task is the I/O done flag, which is set by the ISR on I/O completion. If the I/O done flag is not set, the handler task tests for an express request and then a normal request, in that order. If I/O done event flag is set, the handler should complete any I/O processing necessary

#### Handler Task Main Code

within the handler and then call the system subroutine ..IODN to notify the requesting task of I/O completion.

All device handler tasks supplied by Digital to date have assumed the following: the ISR is used only to process normal requests; express requests are processed at the handler level. Therefore, the request just completed by the ISR was a normal request. The request node address (RNA) for the completed I/O operation is in word B of the 3-word UIT entry that corresponds to the unit on which the I/O operation occurred. For single-unit handlers, the request node address is in UIT+14. UIT is the starting address of the unit identification table.

For multiple-unit handler tasks, I/O completion processing is more complex than for single-unit handler tasks because an I/O operation may have completed on more than one unit. Therefore, the multiple-unit handler makes three checks for each unit it services:

- 1 Is word A of the UIT not equal to zero (that is, is the unit present)?

- 2 Is word B of the UIT not equal to zero (that is, is an I/O operation currently in progress on the unit)?

- 3 Is the done bit set? The done bit is located in an internal mask word specified for each unit and is set by the ISR upon I/O completion.

If the answer to all three questions is yes, I/O completion must take place for the unit.

#### 4.2 **Performing I/O Completion (...IODN)**

I/O completion is similar for single-unit and multiple-unit handlers. The handler task calls the ..IODN subroutine to return the request node to the pool and, if specified in the node, to place the indicated I/O status in the user's area and set the event flag or enable the AST indicated by the user for I/O completion.

The .. IODN subroutine requires the following registers to be preset:

- R1 must contain the request node address from UIT word B.

- R2 must contain the adjustment to the decrement for the user's I/O in progress count. R2 is normally 0. Setting R2 to -1 locks the user task in memory and has a function similar to ATTACH. The function similar to DETACH is to set R2 to +1.

The user task cannot exit while an I/O operation is in progress. Thus, a task attaching a device cannot exit without I/O RUNDOWN, even if the ATTACH request has been processed and returned and no other requests are queued.

To set R2 to anything but zero is an extremely dangerous operation and should only be done if no other solution can be found. The following points should be borne in mind:

- 1 If a task's I/O in progress count is nonzero, it cannot exit without I/O RUNDOWN being invoked.

- 2 A task cannot be checkpointed or swapped with a nonzero I/O in progress count.

- **3** The checkpointing and swapping algorithms assume that:

- Tasks with I/O in progress can be checkpointed (if they are built as being checkpointable) or swapped (if they are scheduler controlled tasks) when their I/O in progress counts become zero;

- The I/O in progress counts will become zero in a finite amount of time without the need to dequeue any more I/O requests for the task.

The system therefore prohibits the dequeuing of I/O requests while a task is marked for checkpointing or swapping. Thus, if a task's I/O in progress count is nonzero and it will not become zero except by dequeuing another I/O request, and the task is marked for checkpointing or swapping, then a potentially dangerous situation occurs.

R3,R4 must contain the two I/O status words to be reported to the user. The status words are stored in the requesting task if an I/O status address was provided in the Queue I/O directive parameter block.

Some handlers, particularly those for complex devices (such as overlapped seek disk handlers), might attempt to dequeue requests by calling ..DQRN while a transfer is in progress for a unit. Such handlers should unconditionally call ..DQRN (or equivalently should set their own normal request event flag, event flag 1) after performing I/O done processing. This is true because requests might be queued for that unit while it is busy. In this case ..DQRN will have indicated, correctly, that no requests could be dequeued. Now that requests can be dequeued, it is necessary to indicate that the situation has changed by calling ..DQRN.

This complication does not apply to handlers that do not attempt to dequeue normal requests while performing a transfer.

#### 4.3 Dequeuing a Request (..DQRN and ..DQRE)

When an I/O request has been queued, the handler task determines whether the request is normal or express by looking at its event flags. If an express request is indicated (flag 2), the handler calls the system subroutine ..DQRE. If a normal request is indicated (flag 1), the handler calls ..DQRN. If neither flag is set, the handler should return to its IDLE code to await further events.

Because ..DQRN performs the same functions for a normal request as ..DQRE does for an express request, they are described together in this section. Both should be coded using the same path. The following information pertains to both subroutines:

- 1 Both subroutines attempt to dequeue the highest priority request in the queue (normal or express). However, ...DQRN is restricted if a user task is attached to the unit; only requests from that task or from tasks with a privileged UIC (group code less than 10) are dequeued.

- 2 Both subroutines dequeue requests only for a unit whose UIT request node address (RNA) is zero. For ..DQRN, the RNA is in word B of the unit entry. For ..DQRE, the RNA is in word C of the unit entry. See Table 2-1.

- **3** Both subroutines attempt to take the request node from the queue, place the request node address in the UIT entry word (either B or C) and in R1, and place the address of word A of the unit's UIT entry in R2.

- 4 If the attempt in 3 above is unsuccessful, ...DQRN and ...DQRE attempt to handle other units, if any, associated with this handler. If they cannot dequeue any requests, they set the C condition code in the Processor Status word and reset the appropriate event flag (1 for ...DQRN and 2 for ...DQRE).

The subroutines ...DQRN and ...DQRE require R0 to be preset to the starting address of the UIT. Once set to the starting address, R0 should remain unaltered.

The dequeuing subroutines cannot be called from the interrupt service routine.

The exit conditions are as follows:

- R0 Is the address of the UIT.

- R1 Is the address of the request node or is undefined if no node is found.

• R2 - Is a pointer to the PUD pointer in the UIT or is zero if no node is found.

#### 4.4 Validating a Request (..VACC)

Once an I/O request is dequeued, the handler task must validate it. The validation process consists of two steps: handler task validation of the function code, and validation of the ..VACC subroutine.

Because ...VACC validates the I/O request based only on the contents of the dispatch table, the handler task must validate the function code to see if it falls within a legitimate range (normally 0 through 27). If the function code is not in the legal range, the request node must be returned to the system by means of the ...IODN subroutine and an error status must be set for the user in R3.

If the function code is within range, the handler task calls ..VACC. The following registers (that have already been initialized by either ..DQRN or ..DQRE) are passed to ..VACC:

- R0 contains the address of the UIT.

- R1 contains the request node address.

- R2 contains a pointer to word A of the unit's UIT entry.

To validate the user's right to issue the I/O request, ..VACC examines the following:

- 1 The volume control block for the unit,

- 2 The handler's dispatch table entry for the function code specified, and

- 3 The user's UIC.

If validation of any of the above checks fails, ...VACC returns to the handler with the C condition code set, and the handler returns an error code to the user. If the request is valid, ...VACC returns the C bit as zero and the handler task then jumps to the dispatch routine (...DISP).

#### 4.5 **Dispatching the Request (..DISP)**

Unlike all other system routines, ...DISP is not a subroutine; the handler task must execute a JMP instruction, rather than a JSR, to reach it. ...DISP uses the dispatch table to determine the I/O processing routine or the SEND/REQUEST function to be performed.

The following registers must be preset:

- R0 must contain the address of the UIT.

- R1 must contain the request node address.

- R2 must contain a pointer to word A of the unit's UIT entry.

R0 acts as a pointer to the dispatch table's address, which is stored in the first location of the UIT.

At this point, the I/O request has been dequeued, validated, and routed to the I/O processing routine that performs the specific function requested.

#### 4.6 **Processing the I/O Functions**

The host operating system provides numerous I/O function codes, most of which are serviced by one of seven I/O processors. Normally, an I/O processor can handle many codes for various device handler tasks. The processor to be selected is indicated in the function code. The IAS Device Handlers Reference Manual lists the function codes.

The seven I/O processors presented in this manual are as follows:

| I/O Processor     | Code                                                                |

|-------------------|---------------------------------------------------------------------|

| Special Functions | 0                                                                   |

| Write Logical     | 1                                                                   |

| Read Logical      | 2                                                                   |

| Attach            | 3                                                                   |

| Detach            | 4                                                                   |

| NOP               | Any legal code that requires no special action by the handler task. |

| Error             | Any illegal code for the device.                                    |

Of the seven processors, only Write Logical and Read Logical require interrupt service routines for execution; for these two, I/O is initialized. The other I/O processors and any error conditions that are detected require a separate path for I/O completion (that is, a call to ..IODN). Since no event flags are set for the special functions, Attach, Detach, NOP, and Error processors, the I/O completion path is identical to that described in Section 4.2, with the following exceptions:

- 1 The normal request's queued event flag does not need to be set again because ...DQRN or ...DQRE was not called after the current request was dequeued.

- 2 The request node address (RNA) in either word B or word C of the unit's UIT entry, depending on whether the request is normal or express, must be cleared if dequeueing is to proceed. Therefore the function code of the current request must be saved, the ..IODN subroutine called, and the following code executed:

MOV (SP)+,R3 ;ASSUME FUNCTION CODE WAS ON STACK BIC #177775,R3 ;CLEAR ALL BUT EXPRESS BIT TST (R2)+ ;ADVANCE R2 FROM FIRST WORD OF UIT ;TO 2ND WORD OF UNIT ENTRY ADD R3,R2 ;IF FUNCTION JUST PROCESSED WAS ;EXPRESS R2 IS NOW AT THE 3RD ;WORD OF UIT ENTRY CLR (R3) ;CLEAR RNA AND REENABLE DEQUEUER

#### 4.6.1 Special Functions Processor

The special functions processor, indicated by function code 0, handles three different subfunctions:

- 1 KILL ALL REQUESTS (subfunction code 12),

- 2 I/O RUNDOWN (subfunction code 22), and

- **3** UNLOAD HANDLER (subfunction code 42).

All three are express requests (bit 1 of the subfunction code is set) and are dequeued accordingly.

A user task issues KILL ALL REQUESTS to a logical unit to cancel all requests from that task that are incomplete on that unit and to clear the attach bit in the device's PUD entry if it is set.

I/O RUNDOWN occurs whenever a task exits or is aborted with I/O requests pending. Since a task's memory cannot be reused while data transfers still can be initiated by I/O requests that have not been dequeued, the system issues an I/O RUNDOWN node sequentially to each unit defined in the PUD. The node identifies the task for which the rundown is to occur. The handler task aborts all I/O request nodes that remain in the task's queue and usually terminates any requests in progress for the task. This process is essentially the same as KILL ALL REQUESTS.

The system issues a request to unload the handler whenever the MCR UNLOAD or the DCL STOP/HANDLER commands are used. The handler task is expected to complete all current requests and then exit. New requests are prevented from being queued.

#### 4.6.1.1 KILL ALL REQUESTS and I/O RUNDOWN

Because KILL ALL REQUESTS and I/O RUNDOWN are similar in function, their respective function processors should handle them identically, with the following exceptions:

- 1 The I/O RUNDOWN request node should be checked to ensure that it came from the Executive and not from a user task. If RNA is in R1, R.AT(R1) contains the ATL address of the issuing task. It is zero if the Executive issued the request.

- 2 The KILL ALL REQUESTS node from a user task must have its parameter words set identically to those of an I/O RUNDOWN request node. The three parameters that must be set by the handler follow:

Parameter word 1 = active task list (ATL) address for the task,

Parameter word 2 = system task directory (STD) address for the task, and

Parameter word 3 = starting address of PUD entry for the unit.

Once the parameter words are set, the handler task can call the system subroutine ...FLSH to remove all I/O requests for the specified task from the queue. Now the handler task can return the express request node to the node pool. It also can check for the following events:

- 1 Is there an I/O operation currently in progress on the unit?

- 2 Was the operation requested by the user task?

If the response to both checks is yes, and if the I/O operation can take a significant time (for example, a read operation on a terminal), the handler task should use the following procedures:

- 1 Terminate the I/O operation. For example, for a terminal you should set the characters received to equal the maximum-characters-asked value (to prevent further reads) and set the write enable bit.

- 2 Return the request node of the I/O operation. In order to return the node, the following information in the node must be zeroed before calling ..IODN:

The I/O status block buffer address, The event flag word, and The AST word.

Resetting this information to zero prevents ..IODN from altering any status bits associated with the task. This makes it appear that the node for the I/O operation in progress was also flushed.

The RNA of the I/O operation in progress is located in word B of the UIT entry for the unit.

#### 4.6.1.2 UNLOAD HANDLER

When a device handler receives an UNLOAD HANDLER request, it should check first to ensure that the request comes from the Executive (that is, if RNA is in R1, R.AT(R1) = 0). If the call is not from the Executive, an error code must be returned. If it is from the Executive, the handler task should set an exit flag for itself and return the node.

The IDLE code (that is, that section of code executed when the handler is waiting for requests to be queued) should contain a check to determine whether the exit flag is set. This check should precede the system directive to wait for multiple event flags. When the flag is set, the IDLE code should check every unit to see if any I/O operations are in progress (word B of every UIT entry should equal zero). If no I/O operations are in progress, the handler task should branch to its exit code; otherwise, it should execute the WAIT FOR directive. In this manner, the handler task exits only when no I/O operations are in progress on any unit.

#### 4.6.2 Read Logical and Write Logical Processors

The servicing of Read Logical and Write Logical I/O functions essentially is device dependent; however, strong similarities exist in the handling of the two functions in different handlers. A typical processing scheme is described in the following paragraphs.

Both read and write functions usually have a user buffer where data is stored or retrieved. The buffer must be validated to determine whether the entire buffer is in the user's area. By convention, the first two parameter words in a read or write I/O request node define the buffer in the following format:

- Parameter word 1 = start of the buffer in the user's virtual area, and

- Parameter word 2 = size of the buffer specified in bytes.

A handler for a non-DMA device must, after checking the buffer, set up three internal locations for use by the ISR:

- UBASR = APR value for the start of the buffer,

- UBSAP = offset of the first location in the buffer from the APR address, and

- UBCAP = offset of the current location in the buffer from the APR address.

Using these locations, the ISR replaces the current address and descriptor registers for Kernel APR2 with UBASR and 77406 (4K read/write segment), respectively. Thus, setting the three locations directly maps the ISR into the user's buffer.

An ISR that uses (Kernel) APR2 must first save the contents of the corresponding memory management registers and afterwards restore them.

The handler task calls the ..VXFR system subroutine to set the locations. It requires the following preset registers:

- R1 must contain the RNA (already set).

- R2 must contain the starting address of the buffer (parameter 1 of the RNA or R.PB(R1)).