#### **PDP-11 Family**

# student workbook introduction to the pdp11

digital equipment corporation · maynard. massachusetts

#### Copyright © 1976, 1977, by Digital Equipment Corporation

The reproduction of this workbook, in part or whole, is strictly prohibited. For copy information contact the Educational Services Department, Digital Equipment Corporation, Maynard, Massachusetts 01754.

Printed in U.S.A.

After completing this study unit you should be able to ...

- ★ List the four major categories of computers in the PDP-11 family and identify by model number the PDP-11 computers that fall into each of the four categories.

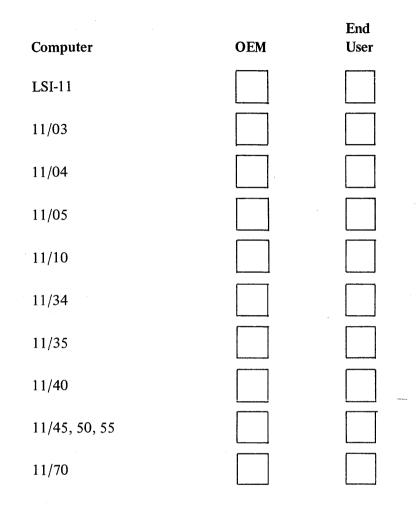

- ★ Specify the *principal market area* for each PDP-11 computer (OEM, End-User, or OEM and End-User).

- ★ Draw a simple block diagram of an LSI-11 computer system that contains the following system components:

- Microcomputer Module

- Core Memory Module

- 1K and 4K MOS Modules

- PROM Module

- Serial Line Interface

- Parallel Line Interface

- LSI-11 Bus

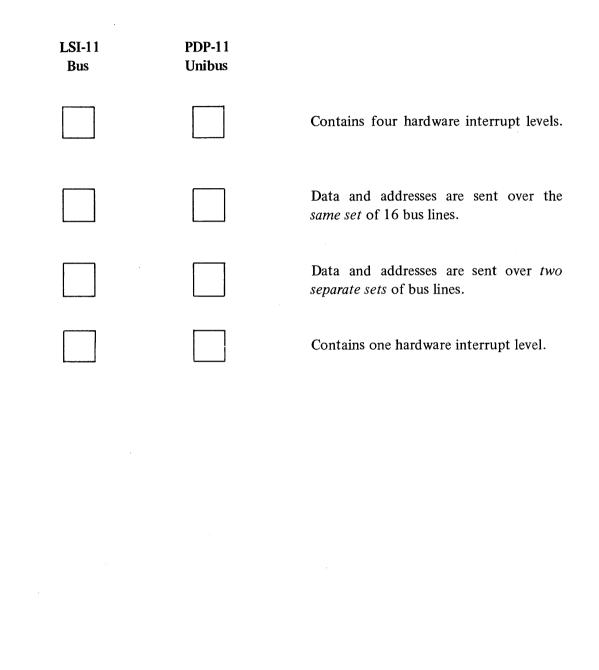

- \* Differentiate between the LSI-11 Bus and the PDP-11 Unibus in terms of:

- Hardware Interrupt Levels

- Data and Address Lines

- \* List the three major functions performed by the memory management unit.

- ★ Differentiate between the PDP-11 Programmer's Console and the Operator's Panel in terms of:

- Implementation of load, examine, deposit, and start functions.

- Customer option or standard hardware on 11/04 and 11/34 computers.

(continued on next page)

#### objectives-

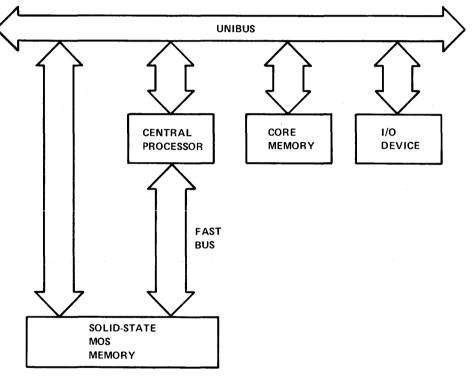

- ★ Draw a simple block diagram of an 11/45 computer system and label the following system components:

- Central Processor

- Core Memory

- Solid-State MOS Memory

- I/O Device

- Unibus

- Fast Bus

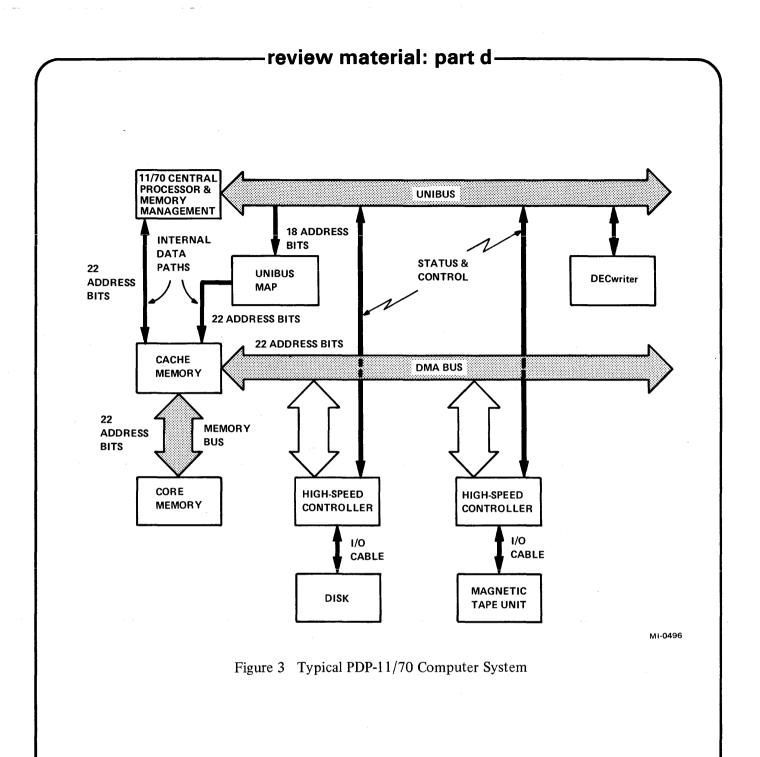

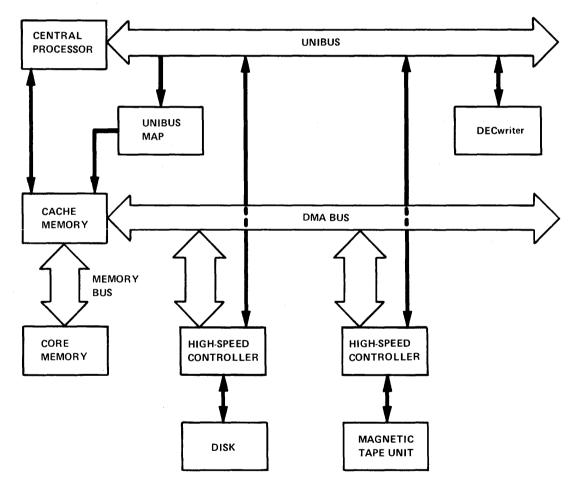

- ★ Draw a simple block diagram of an 11/70 computer system and label the following system components:

2

read on |

- Central Processor

- DECwriter (I/O Device)

- Disk

- Magnetic Tape Unit

- High-Speed Controllers (two)

- Core Memory

- Cache Memory

- Unibus Map

- Unibus

- DMA Bus

- Memory Bus

★ List the major characteristics of each computer in the PDP-11 family. These characteristics include:

3

read on

- Names of Processing Modes

- Number of General-Purpose Registers

- Number of Hardware Interrupt Levels

- Number of Software Interrupt Levels

- Maximum Address Space

- Maximum Memory Size

- Bus Structure

- Types of Memory

- Number of Hardware Stacks

- Memory Management (not available, optional, standard)

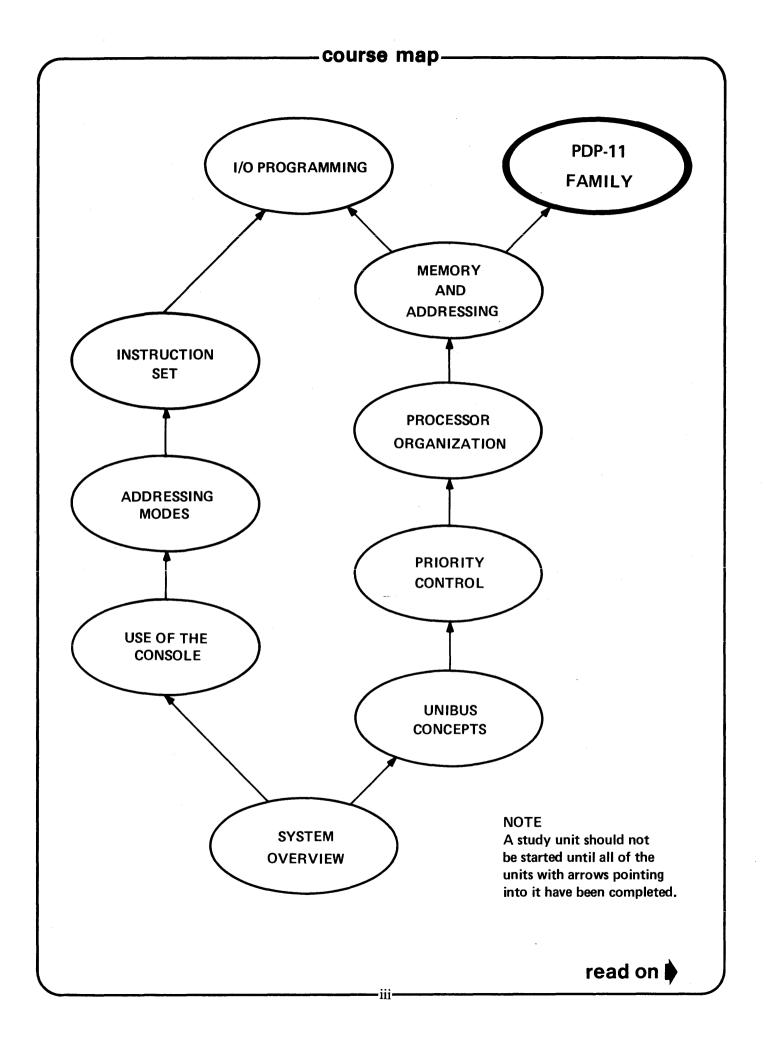

### -----review material: part a------

| Topic                     | Key Points                                                                                                                                                    | Visual Ref. |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| PDP-11                    | ★ The PDP-11 Computer family consists of                                                                                                                      | 1 .         |

| Computer Family           | • A series of compatible central processors, and                                                                                                              |             |

|                           | • A variety of peripheral devices, operating systems, and applications software.                                                                              |             |

| common<br>characteristics | ★ The following characteristics are common to all processors in the PDP-11 family:                                                                            | 2–5         |

|                           | <ul> <li>16-bit machines (the processors can work<br/>with 16-bit words or 8-bit bytes).</li> </ul>                                                           |             |

|                           | • Common set of instructions.                                                                                                                                 |             |

|                           | • Similar architecture.                                                                                                                                       |             |

| upward<br>compatibility   | ★ Because of their common characteristics, the processors are upward compatible (PDP-11 users can upgrade their systems without rewriting existing programs). | 6           |

| end user<br>versus OEM    | ★ The PDP-11 computer family includes<br>processors intended primarily for end users and<br>equivalent models for original equipment<br>manufacturers (OEMs). | 7–10        |

|                           | • An <i>end user</i> purchases the computer for direct use.                                                                                                   |             |

|                           | • An <i>OEM</i> purchases the basic hardware and incorporates it into systems for resale to other customers (end users).                                      |             |

|                           | (continued on n                                                                                                                                               | ext page)   |

|                           |                                                                                                                                                               |             |

|                           |                                                                                                                                                               |             |

|                           |                                                                                                                                                               |             |

### -----review material: part a-----

| Topic                            | Key Points                                                                                                                                                                                                                                 | Visual Ref. |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| end user<br>versus OEM (Cont)    | • Processors designed specifically for the end-user market generally have more standard features and hardware than equivalent OEM models. Also, supporting services (documentation, training, etc.) are supplied with the end-user system. |             |

|                                  | • In OEM computers, many of the supporting services are "unbundled" and offered as <i>optional</i> items.                                                                                                                                  |             |

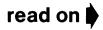

| major<br>categories<br>of PDP-11 | The family of PDP-11 processors is divided into four major categories:                                                                                                                                                                     | 11-15       |

| processors                       | • Microcomputers,                                                                                                                                                                                                                          |             |

|                                  | • Minicomputers for dedicated applications,                                                                                                                                                                                                |             |

|                                  | • Minicomputers for multi-task applications,                                                                                                                                                                                               |             |

|                                  | • Medium-scale computers for large multi-user, multi-task applications.                                                                                                                                                                    |             |

| microcomputers                   | ★ The LSI-11 and PDP-11/03 are classified as microcomputers.                                                                                                                                                                               | 16, 17      |

|                                  | • They execute the same basic set of instructions as the larger PDP-11 processors. However, their processing speeds are slower.                                                                                                            |             |

|                                  |                                                                                                                                                                                                                                            |             |

|                                  |                                                                                                                                                                                                                                            |             |

|                                  |                                                                                                                                                                                                                                            |             |

.6

### \_review material: part a\_\_\_\_\_

| Topic                                       | Key Points                                                                                                                                | Visual Ref. |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| LSI-11                                      | ★ The LSI-11 is constructed using large scale integration (LSI) techniques.                                                               | 18-21       |

| ·                                           | • Four semiconductor chips make up the processor section of the LSI-11 microcomputer.                                                     |             |

|                                             | • Up to 4K of MOS memory is also provided on the microcomputer module.                                                                    |             |

|                                             | • Memory expansion modules and I/O interfaces are contained on separate printed circuit boards.                                           |             |

| PDP-11/03                                   | ★ The PDP-11/03 is a "packaged" version of the LSI-11 that includes                                                                       | 22          |

|                                             | • LSI-11 microcomputer                                                                                                                    |             |

|                                             | • Main memory                                                                                                                             |             |

|                                             | • Power supply                                                                                                                            |             |

|                                             | • Serial line interface for a teleprinter or display terminal                                                                             |             |

|                                             | • Operator's panel                                                                                                                        |             |

|                                             | • Enclosure                                                                                                                               |             |

| principal<br>markets                        | ★ The 11/03 is marketed to both OEMs and<br>high-volume end users; the LSI-11 is sold<br>primarily to OEMs.                               | 23          |

| minicomputers:<br>dedicated<br>applications | ★ The 11/04, 11/05, and 11/10 minicomputers are designed for <i>dedicated</i> applications such as data acquisition or numerical control. | 24–27       |

|                                             |                                                                                                                                           |             |

7

### -review material: part a------

| Topic                                        | Key Points                                                                                                                                                                                                                                                                  | Visual Ref. |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 11/04                                        | • The 11/04 is marketed to OEMs and end<br>users. It offers customers a choice of<br>non-volatile core memory or solid-state MOS<br>memory.                                                                                                                                 |             |

| 11/05                                        | • The 11/05 is only marketed to OEMs. It uses non-volatile core memory.                                                                                                                                                                                                     |             |

| 11/10                                        | • The 11/10 is electrically identical to the 11/05. However, it is packaged for end users and, therefore, offers more standard features and expansion space.                                                                                                                |             |

| minicomputers:<br>multi-task<br>applications | ★ Our third category of computers includes the<br>11/34, 11/35, and 11/40. These minicomputers<br>can handle several problems (tasks)<br>simultaneously such as in timesharing<br>applications where many users are interacting<br>with the computer on a concurrent basis. | 28–34       |

| 11/35 and<br>11/40                           | • The 11/35 and 11/40 use core memory and are electrically similar. However, the 11/35 is directed at the OEM market, while the 11/40 is packaged for end users.                                                                                                            |             |

| 11/34                                        | • The 11/34 is marketed to OEMs and end<br>users. It offers customers a choice of MOS<br>memory or core memory. Features such as<br>memory management and an extended<br>instruction set are an integral part of the<br>11/34 processor. These features are optional        |             |

### \_\_\_\_\_review material: part a\_\_\_\_\_

| Topic                                   | Key Points                                                                                                                                                                                                      | Visual Ref. |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| medium-scale<br>computers               | ★ The 11/45, 11/50, 11/55, and 11/70 are classified as medium-scale computers.                                                                                                                                  | 35, 36      |

|                                         | • These computers are generally used for large, multi-user, multi-task applications.                                                                                                                            |             |

|                                         | • Each of these computers is a complete system<br>that can be marketed to OEMs and end users<br>(separate model designations are not used to<br>distinguish an OEM system from an end-user<br>system).          |             |

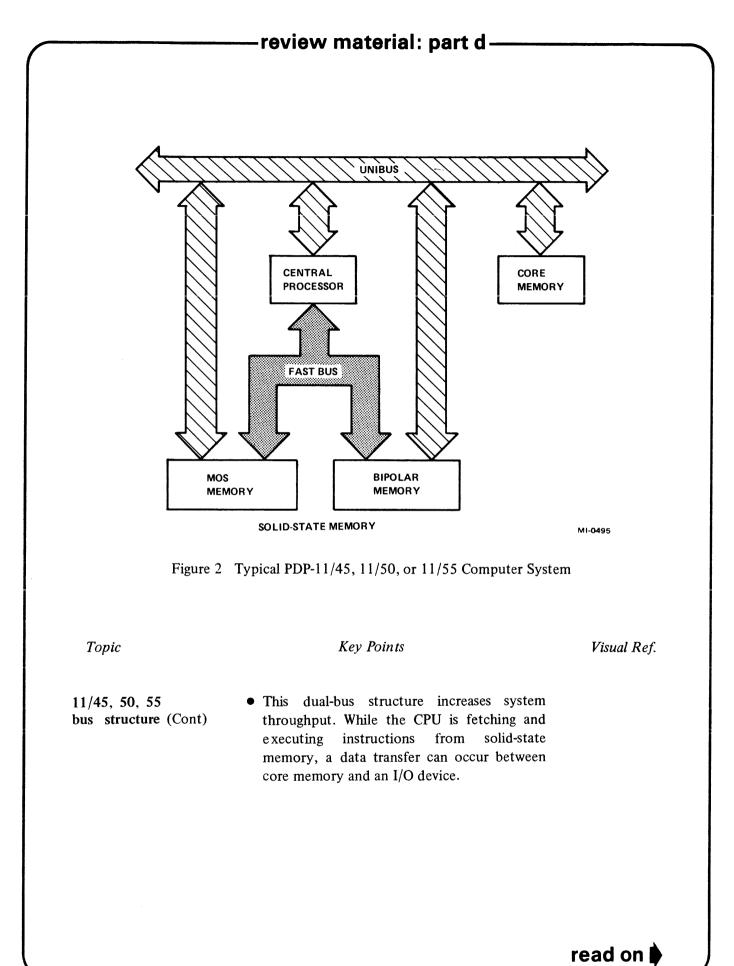

| 11/45, 11/50,<br>and 11/55              | ★ The 11/45, 11/50, and 11/55 use the same basic CPU and bus structure. However, different types of memory are supplied in the <i>basic</i> system package.                                                     | 37-41       |

|                                         | • Main storage in the <i>basic</i> 11/45 system consists of 32K of core memory.                                                                                                                                 |             |

|                                         | • The basic 11/50 system uses faster MOS memory or a mixture of MOS and core memory.                                                                                                                            |             |

|                                         | • The basic 11/55 system is supplied with 32K of bipolar memory or a mixture of bipolar and core memory.                                                                                                        |             |

|                                         | • Larger 11/45 and 11/50 systems can be expanded using combinations of bipolar, MOS, and core memory.                                                                                                           |             |

| floating-point<br>processor<br>(FP11-C) | <ul> <li>★ The 11/55 can accommodate a very fast floating-point processor option (the FP11-C). The FP11-C is used in combination with bipolar memory for high-speed "number crunching" applications.</li> </ul> | 42          |

|                                         |                                                                                                                                                                                                                 |             |

.9.

read on 🗼

#### -review material: part a-

Figure 1 Major Categories of PDP-11 Computers

Table 1 Principal Markets

|        | OEM          | End<br>User  |

|--------|--------------|--------------|

| LSI-11 | $\checkmark$ |              |

| 11/03  | $\checkmark$ | $\checkmark$ |

| 11/04  | $\checkmark$ | $\checkmark$ |

| 11/05  | $\checkmark$ |              |

| 11/10  |              | $\checkmark$ |

| 11/34  | $\checkmark$ | $\checkmark$ |

| 11/35  | $\checkmark$ |              |

| 11/40  |              | $\checkmark$ |

| 11/45  | $\checkmark$ | $\checkmark$ |

| 11/50  | $\checkmark$ | $\checkmark$ |

| 11/55  | $\checkmark$ | $\checkmark$ |

| 11/70  | $\checkmark$ | $\checkmark$ |

-11-

#### —exercises: part a—

- 1. A customer who purchases a computer system for *direct use* is called an \_\_\_\_\_

- 2. A customer who purchases the *basic* computer hardware and then incorporates it into systems for resale to other customers is called an \_\_\_\_\_\_

3. Complete the following chart by:

......

(a) Listing the *four major categories* of PDP-11 computers,

------

- (b) Specifying the *model numbers* of the PDP-11 computers that fall into each category, and

- (c) Specifying the *principal market* for each PDP-11 computer (OEM, End User, or OEM and End User).

| (a)            | (b)                                   | (c)                                   |

|----------------|---------------------------------------|---------------------------------------|

| Major Category | Model<br>Number(s)                    | Principal<br>Market(s)                |

|                |                                       |                                       |

|                |                                       |                                       |

|                | · · · · · · · · · · · · · · · · · · · |                                       |

|                |                                       |                                       |

|                |                                       |                                       |

|                |                                       | · · · · · · · · · · · · · · · · · · · |

|                |                                       |                                       |

|                |                                       |                                       |

|                |                                       |                                       |

|                |                                       |                                       |

|                |                                       |                                       |

-13-

#### answer sheet: part a-

- 1. A customer who purchases a computer system for *direct use* is called an \_\_\_\_\_ End User\_\_\_.

- 3. Complete the following chart by:

- (a) Listing the *four major categories* of PDP-11 computers,

- (b) Specifying the *model numbers* of the PDP-11 computers that fall into each category, and

- (c) Specifying the *principal market* for each PDP-11 computer (OEM, End User, or OEM and End User).

| (a)                                                                        | (b)                              | (c)                               |

|----------------------------------------------------------------------------|----------------------------------|-----------------------------------|

| Major Category                                                             | Model<br>Number(s)               | Principal<br>Market(s)            |

| Microcomputers                                                             | LSI-11<br>11/03                  | OEM<br>OEM & End User             |

| Minicomputers for<br>dedicated applications                                | 11/04<br>11/05<br>11/10          | OEM & End User<br>OEM<br>End User |

| Minicomputers for<br>multi-task applications                               | 11/34<br>11/35<br>11/40          | OEM & End User<br>OEM<br>End User |

| Medium-scale computers<br>for large multi-user,<br>multi-task applications | 11/45<br>11/50<br>11/55<br>11/70 | OEM &<br>End User                 |

Mark your place in the workbook and return to the A-V program.

14

read on 🌢

### ------review material: part b------

| Topic                          | Key Points                                                                                                              | Visual Ref.   |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------|

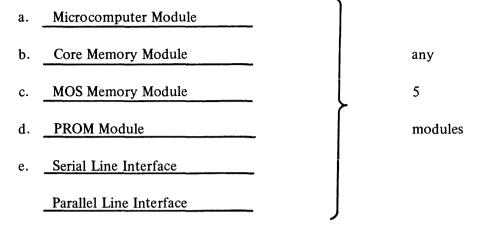

| LSI-11                         | <ul> <li>★ The LSI-11 is configured by selecting a specific combination of printed circuit boards (modules).</li> </ul> | 46–48         |

|                                | • The modules plug into a backplane assembly.                                                                           |               |

| <i>,</i>                       | • The backplane assembly distributes power and bus signals to all of the modules.                                       |               |

| microcomputer<br>module        | ★ The LSI-11 microcomputer module contains<br>three system components:                                                  | 49, 50        |

|                                | <ul> <li>16-bit central processor (consists of four<br/>semiconductor chips),</li> </ul>                                |               |

|                                | • I/O bus port,                                                                                                         |               |

|                                | • Up to 4K of MOS memory.                                                                                               |               |

| extended<br>instruction<br>set | <ul> <li>★ An optional, fifth semiconductor chip extends<br/>the LSI-11 instruction set to include</li> </ul>           | 51            |

|                                | • <i>Fixed-point</i> multiply, divide and multiple shift instructions.                                                  |               |

|                                | • Floating-point add, substract, multiply, and divide instructions.                                                     | •<br>•• •• •• |

| general-<br>purpose            | ★ Eight general-purpose registers are provided in the LSI-11:                                                           | 52            |

| registers                      | • R6 and R7 are normally used as the stack pointer and program counter.                                                 |               |

|                                | • The other 6 registers (R0–R5) are general registers; they are not dedicated to specific functions.                    |               |

|                                |                                                                                                                         |               |

|                                |                                                                                                                         |               |

|                                |                                                                                                                         |               |

-15-

### -----review material: part b-----

| Topic                | Key Points                                                                                                                                                      | Visual Ref. |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| LSI-11<br>memory and | The LSI-11 can be expanded using the following modules:                                                                                                         | 53-56       |

| I/O modules          | • Core memory (expandable in 4K-word increments)                                                                                                                |             |

|                      | • MOS memory (expandable in 1K or 4K-word increments)                                                                                                           |             |

|                      | • Programmable read-only memory or PROM (expandable in 256-word increments to 2K; or 512-word increments to 4K)                                                 |             |

|                      | • Serial line interface (for serial communications devices such as a teleprinter or display terminal)                                                           |             |

|                      | <ul> <li>Parallel line interface (a 16-bit general-purpose interface)</li> </ul>                                                                                |             |

| LSI-11 bus           | ★ All LSI-11 modules communicate over a single<br>I/O bus. The LSI-11 I/O bus differs from the<br>Unibus in two key areas:                                      | 57-60       |

|                      | • Data and addresses are transmitted over the same set of bus lines (the Unibus has one set of lines for data and another separate set of lines for addresses). |             |

|                      | • A <i>single</i> hardware interrupt level is implemented in the LSI-11 bus (the Unibus has 4 hardware interrupt levels).                                       |             |

| LSI-11<br>address    | ★ The LSI-11 can reference a maximum of 32K words (64K bytes) using the 16-bit address.                                                                         | 61-63       |

| space                | • The top 4K of the address space is available for referencing I/O registers.                                                                                   |             |

|                      | • The balance of the address space (28K) is used for main memory.                                                                                               |             |

|                      |                                                                                                                                                                 | read on 🖡   |

### -----review material: part b------

| Key Points                                                                                                                                                                  | Visual Ref.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ★ The PDP-11/03 uses the same printed circuit modules as the LSI-11.                                                                                                        | 64, 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| • These modules are installed in a rack-mountable enclosure.                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| • The enclosure also houses a power supply, cooling fans, and an operator's panel.                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ★ The LSI-11 is sold primarily to OEMs; the 11/03 is marketed to OEMs and high-volume end users.                                                                            | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ★ The 11/04, 11/05, and 11/10 minicomputers are<br>used primarily for <i>dedicated</i> applications. The<br>following characteristics are common to these<br>minicomputers: | 67–72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| • Eight general-purpose registers.                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| • Same bus structure; the 56-line Unibus with four hardware interrupt levels and one NPR (non-processor request) level for DMA transfers.                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| • Memory management hardware is not used;<br>therefore, the maximum address space is 32K<br>words (4K for I/O register addresses; 28K for<br>main memory).                  | • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                             | <ul> <li>The PDP-11/03 uses the same printed circuit modules as the LSI-11.</li> <li>These modules are installed in a rack-mountable enclosure.</li> <li>The enclosure also houses a power supply, cooling fans, and an operator's panel.</li> <li>The LSI-11 is sold primarily to OEMs; the 11/03 is marketed to OEMs and high-volume end users.</li> <li>The 11/04, 11/05, and 11/10 minicomputers are used primarily for <i>dedicated</i> applications. The following characteristics are common to these minicomputers:</li> <li>Eight general-purpose registers.</li> <li>Same bus structure; the 56-line Unibus with four hardware interrupt levels and one NPR (non-processor request) level for DMA transfers.</li> <li>Memory management hardware is not used; therefore, the maximum address space is 32K words (4K for I/O register addresses; 28K for</li> </ul> |

### -review material: part b------

| Topic                                                 | Key Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Visual Ref. |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| major<br>differences:<br>11/04 versus<br>11/05, 11/10 | <ul> <li>The 11/04 differs from the 11/05 and 11/10 in the following areas:</li> <li>Memory types – the 11/04 offers customers a choice of MOS memory (725 ns cycle time) or core memory (980 ns); the 11/05 and 11/10 use core memory only.</li> <li>Processing speed – the 11/04 executes instructions faster than the 11/05 or 11/10 (example: ADD R0, R1 takes 2.7 μs in the 11/04 versus 3.7 μs for the 11/05 and 11/10).</li> <li>Standard features – a programmer's console, real-time clock, and serial communication line interface are standard features in the 11/05 and 11/10; these features are optional in the 11/04.</li> </ul> | 73–80       |

| programmer's<br>console                               | ★ The programmer's console that is used in the<br>11/05 and 11/10 contains switches and lamps<br>for depositing data in memory and examining<br>previously stored data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 81          |

| operator's<br>panel                                   | <ul> <li>Most switches and lamps are excluded from the 11/04 operator's panel.</li> <li>The operator's panel works in combination with a ROM front panel emulator.</li> <li>Special routines are hardwired into the ROM so that it replaces (emulates) basic console functions (load, examine, deposit, start, etc.) when the appropriate keys are pressed on an ASCII terminal.</li> </ul>                                                                                                                                                                                                                                                     | 82, 83      |

| real-time<br>clock                                    | <ul> <li>The real-time clock generates an internal timing<br/>signal (program interrupt) that allows the CPU<br/>to keep track of when events happen.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84, 85      |

|                                                       | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | read on 🌢   |

-18-

# -review material: part b ------

| Topic                      | Key Points                                                                                                                                                                 | Visual Ref. |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| SCL<br>interface           | ★ The serial communication line (SCL) interface<br>handles all communications between the CPU<br>and a <i>local terminal</i> (console teleprinter or<br>keyboard display). | 86, 87      |

|                            | • The SCL interface is not connected to the Unibus; it communicates with the CPU over an internal bus.                                                                     |             |

| ROM<br>bootstrap<br>loader | ★ A ROM bootstrap loader is standard on the 11/04 and is optional on the 11/05 and 11/10.                                                                                  | 88, 89      |

| JUAUEI                     | • This hardware feature allows the CPU to automatically load system programs into main memory from standard peripheral devices.                                            |             |

|                            | • A separate bootstrap loader is preprogrammed<br>into the ROM for each type of peripheral<br>device.                                                                      |             |

| initiating<br>the 11/04    | ★ On the 11/04 the bootstrap loader can be initiated three ways:                                                                                                           | 90          |

| bootstrap<br>loader        | • automatically whenever a "power-up" condition occurs,                                                                                                                    |             |

|                            | • manually by pressing the BOOT switch on the operator's panel, or                                                                                                         |             |

|                            | • by typing in a bootstrap command from an ASCII terminal.                                                                                                                 |             |

| summary                    | ★ Table 2 summarizes the major characteristics of<br>the LSI-11 and 11/03 microcomputers and the<br>11/04, 11/05, and 11/10 minicomputers.                                 |             |

|                            |                                                                                                                                                                            |             |

|                            |                                                                                                                                                                            |             |

|                                                          | LSI-11              | 11/03               | 11/04             | 11/05  | 11/10    |

|----------------------------------------------------------|---------------------|---------------------|-------------------|--------|----------|

| PRINCIPAL MARKETS                                        | OEM                 | OEM &<br>End User   | OEM &<br>End User | OEM    | End User |

| NUMBER OF GPRs                                           | 8                   | 8                   | 8                 | 8      | 8        |

| NUMBER OF HARDWARE<br>INTERRUPT LEVELS                   | 1                   | 1                   | 4                 | 4      | 4        |

| MAXIMUM ADDRESS<br>SPACE (words)                         | 32K                 | 32K                 | 32K               | 32K    | 32K      |

| MAXIMUM MEMORY<br>SIZE (words)                           | 28K                 | 28K                 | 28K               | 28K    | 28K      |

| BUS STRUCTURE                                            | LSI-1 1<br>Bus      | LSI-11<br>Bus       | Unibus            | Unibus | Unibus   |

| TYPES OF MAIN<br>MEMORY                                  | Core<br>MOS<br>PROM | Core<br>MOS<br>PROM | Core<br>MOS       | Core   | Core     |

| PROGRAMMER'S CONSOLE<br>(PC)<br>OPERATOR'S PANEL<br>(OP) | none                | OP                  | OP*               | РС     | РС       |

Table 2Major Characteristics of the LSI-11, 11/03, 11/04, 11/05, and 11/10

\* The Programmer's Console is available on the 11/04 as a customer option.

read on 🌢

#### -exercises: part b-

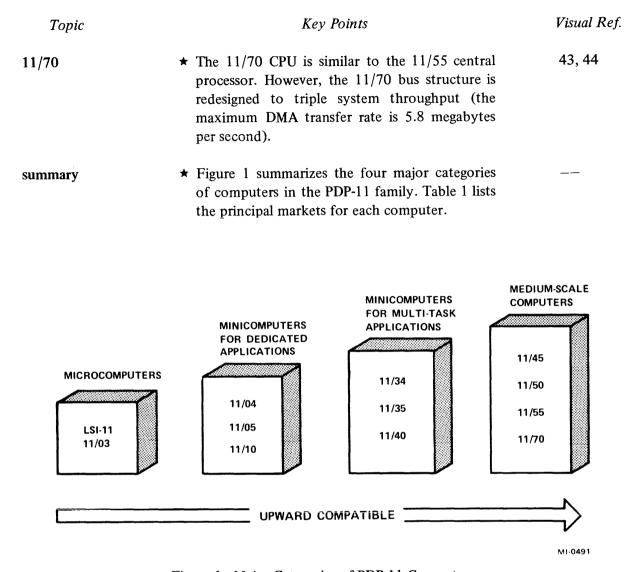

1. An LSI-11 can be configured using various combinations of printed circuit modules. Name at least five of these modules.

|    | a        | •                                  |             |                                                                               |

|----|----------|------------------------------------|-------------|-------------------------------------------------------------------------------|

|    | b        |                                    |             |                                                                               |

|    | с        | •                                  |             |                                                                               |

|    | đ        | •                                  |             |                                                                               |

|    | e        | •                                  |             |                                                                               |

| 2. | A "packa | aged" version of the               | LSI-11 is c | alled the                                                                     |

| 3. |          | ach term in the left<br>Id column. | -hand colu  | amn with one or more of the descriptions in the                               |

|    | а.       | LSI-11 Bus                         | ( )         | Transmits data over one set of lines and addresses over another set of lines. |

|    | b.       | PDP-11 Unibus                      | (* )        | Transmits data and addresses over the same set of lines.                      |

|    |          |                                    | ( )         | Contains one hardware interrupt level.                                        |

|    |          |                                    | ( )         | Contains four hardware interrupt levels.                                      |

|    |          |                                    | ( )         | Used in the $11/04$ , $11/05$ and $11/10$ computers.                          |

|    |          |                                    |             |                                                                               |

|    |          |                                    |             |                                                                               |

1. An LSI-11 can be configured using various combinations of printed circuit modules. Name at least five of these modules.

- 2. A "packaged" version of the LSI-11 is called the \_\_\_\_\_\_ 11/03.

- 3. Match each term in the left-hand column with one or more of the descriptions in the right-hand column.

| a. | LSI-11 Bus    | (b)   | Transmits data over one set of lines and addresses over another set of lines. |

|----|---------------|-------|-------------------------------------------------------------------------------|

| b. | PDP-11 Unibus | ( a ) | Transmits data and addresses over the same set of lines.                      |

|    |               | ( a ) | Contains one hardware interrupt level.                                        |

|    |               | (b)   | Contains four hardware interrupt levels.                                      |

(b) Used in the 11/04, 11/05 and 11/10 computers.

- 4. Draw a simple block diagram of an LSI-11 computer system and label the following system components:

- Microcomputer Module

- Core Memory Module

- 1K and 4K MOS Modules

- PROM Module

- Serial Line Interface

- Parallel Line Interface

- LSI-11 Bus

- 4. Draw a simple block diagram of an LSI-11 computer system and label the following system components:

- Microcomputer Module

- Core Memory Module

- 1K and 4K MOS Modules

- PROM Module

- Serial Line Interface

- Parallel Line Interface

- LSI-11 Bus

MI-0494

read on 🌢

5. Fill in the missing information in the chart below.

|                                        | LSI-11<br>& 11/03                     | 11/04 | 11/05<br>& 11/10 |

|----------------------------------------|---------------------------------------|-------|------------------|

| NUMBER OF GPRs                         |                                       |       |                  |

| NUMBER OF HARDWARE<br>INTERRUPT LEVELS |                                       |       |                  |

| MAXIMUM ADDRESS<br>SPACE (words)       |                                       |       |                  |

| MAXIMUM MEMORY<br>SIZE (words)         |                                       |       |                  |

| BUS STRUCTURE                          | · · · · · · · · · · · · · · · · · · · |       |                  |

| TYPES OF MEMORY                        |                                       |       |                  |

5. Fill in the missing information in the chart below.

|                                        | LSI-11<br>& 11/03   | 11/04       | 11/05<br>& 11/10 |

|----------------------------------------|---------------------|-------------|------------------|

| NUMBER OF GPRs                         | 8                   | 8           | 8                |

| NUMBER OF HARDWARE<br>INTERRUPT LEVELS | 1                   | 4           | 4                |

| MAXIMUM ADDRESS<br>SPACE (words)       | 32K                 | 32K         | 32K              |

| MAXIMUM MEMORY<br>SIZE (words)         | 28K                 | 28K         | 28K              |

| BUS STRUCTURE                          | LSI-11<br>Bus       | Unibus      | Unibus           |

| TYPES OF MEMORY                        | Core<br>MOS<br>PROM | Core<br>MOS | Core             |

Mark your place in the workbook and return to the A-V program.

### ------review material: part c------

| Topic                             | Key Points                                                                                                                                                                                                       | Visual Ref. |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 11/34, 11/35,<br>and 11/40        | ★ The 11/34, 11/35, and 11/40 minicomputers<br>accommodate additional features that are<br>required for multi-task applications such as<br>timesharing. Two of the most important features<br>are:               | 99, 100     |

|                                   | • memory management hardware and                                                                                                                                                                                 |             |

|                                   | • dual processing modes.                                                                                                                                                                                         |             |

| memory<br>management              | ★ Memory management is standard on 11/34 systems and is optional on the 11/35 and 11/40.                                                                                                                         | 101         |

| memory<br>management<br>functions | ★ Memory management performs three system functions:                                                                                                                                                             | 102         |

| Tunctions                         | • Address expansion                                                                                                                                                                                              |             |

|                                   | • Memory protection                                                                                                                                                                                              |             |

|                                   | • Program relocation                                                                                                                                                                                             |             |

| address<br>expansion              | <ul> <li>★ When the memory management unit is enabled,<br/>it converts 16-bit addresses supplied by the CPU<br/>(virtual addresses) into expanded 18-bit<br/>addresses that are sent over the Unibus.</li> </ul> | 103, 104    |

|                                   | • The 18-bit address increases the maximum address space to 128K words.                                                                                                                                          |             |

|                                   | • 124K is available for referencing locations in main memory; the other 4K is reserved for I/O and CPU registers.                                                                                                |             |

|                                   |                                                                                                                                                                                                                  |             |

|                                   |                                                                                                                                                                                                                  |             |

|                                   |                                                                                                                                                                                                                  |             |

|                                   |                                                                                                                                                                                                                  |             |

# -review material: part c-----

| Topic                | Key Points                                                                                                                                                                                                       | Visual Ref. |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| memory<br>protection | ★ When several programs are resident in main<br>memory, the memory management unit provides<br>hardware facilities that protect these programs<br>from unauthorized access or modification.                      | 105-108     |

|                      | <ul> <li>Protection is accomplished by first dividing<br/>main storage into smaller segments called<br/>"pages."</li> </ul>                                                                                      |             |

|                      | • The starting address of each page is<br>established using page address registers<br>(PARs) in the memory management unit.                                                                                      |             |

|                      | • Access to individual pages is controlled by special access keys that are stored in page descriptor registers (PDRs).                                                                                           |             |

| access<br>keys       | ★ Three types of access keys are implemented in the 11/34, 11/35, and 11/40:                                                                                                                                     | 109-112     |

|                      | • Non-resident key – protects the corresponding page from both read and write operations (the page is declared inaccessible to user programs).                                                                   |             |

|                      | • Read-only key – allows information to be<br>read from the page, but aborts any attempts<br>to write into that page (this key protects the<br>contents of the page from willful or<br>accidental modification). |             |

|                      | • <i>Read-write key</i> – allows complete read access and write access to the page.                                                                                                                              |             |

|                      |                                                                                                                                                                                                                  |             |

|                      |                                                                                                                                                                                                                  |             |

|                      |                                                                                                                                                                                                                  |             |

|                      |                                                                                                                                                                                                                  | read on 🛊   |

### –review material: part c——

| Topic                       | Key Points                                                                                                                                                                                                                                                                      | Visual Ref. |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| program<br>relocation       | ★ Program relocation involves the page address<br>registers (PARs) that are part of the memory<br>management unit.                                                                                                                                                              | 113–116     |

|                             | • When a program is stored in main memory, its starting address is derived from a program relocation constant that is held in one of the PARs.                                                                                                                                  |             |

|                             | • Later, when the program is executed, its relocation constant is automatically combined with each 16-bit virtual address issued by the CPU. The resulting 18-bit address is then used to access main memory.                                                                   |             |

| dual<br>processing<br>modes | <ul> <li>★ If an 11/34, 11/35, or 11/40 system contains<br/>memory management hardware, the CPU may<br/>be operated in two processing modes – Kernel<br/>mode and User mode. (Remember, the 11/03,<br/>11/04, 11/05, and 11/10 can only operate in<br/>Kernel mode.)</li> </ul> | 117–119     |

|                             | • <i>Kernel mode</i> allows the program currently running in the CPU to have complete control over the system. (The system monitor is executed in Kernel mode because it requires unrestricted use of the computer.)                                                            |             |

|                             | • User mode inhibits the CPU from executing certain instructions such as HALT or RESET (user programs are executed in User mode).                                                                                                                                               |             |

| two<br>hardware<br>stacks   | ★ When there are two processing modes, there are also two hardware stacks. Each stack requires its own stack pointer (SP).                                                                                                                                                      | 120, 121    |

|                             |                                                                                                                                                                                                                                                                                 |             |

# -review material: part c-----

| Topic                                 | Key Points                                                                                                                                                                                                              | Visual Ref. |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| nine<br>GPRs                          | <ul> <li>★ 11/34, 11/35, and 11/40 systems equipped with<br/>memory management contain nine GPRs.</li> </ul>                                                                                                            | 122         |

|                                       | • Two registers function as the Kernel and User stack pointers.                                                                                                                                                         |             |

|                                       | • One register serves as the program counter.                                                                                                                                                                           |             |

|                                       | • The six remaining GPRs are general registers;<br>they are not used for special functions.                                                                                                                             |             |

| major<br>differences:<br>11/34 versus | ★ The 11/34 differs from the 11/35 and 11/40 in the following areas:                                                                                                                                                    | 127–131     |

| 11/34 versus<br>11/35, 11/40          | <ul> <li>Memory types – the 11/34 offers customers a choice of core memory (1 μs cycle time) or MOS memory (775 ns cycle time); the 11/35 and 11/40 are only available with core memory (980 ns cycle time).</li> </ul> |             |

|                                       | • Standard features – memory management, a<br>ROM bootstrap loader, and an extended<br>instruction set are built into all 11/34<br>systems; in the 11/35 and 11/40 these<br>features are available as customer options. |             |

|                                       | • Console – the 11/35 and 11/40 use the programmer's console; the 11/34 uses a simplified operator's panel.                                                                                                             |             |

|                                       |                                                                                                                                                                                                                         |             |

### -review material: part c-----

| Topic                            | Key Points                                                                                                                                                                                                                                               | Visual Ref. |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| extended<br>instruction<br>set   | ★ The extended instruction set (EIS) provides<br>hardware facilities for executing multiply,<br>divide, and arithmetic shift instructions (the EIS<br>instructions are directly compatible with<br>instructions used in the larger PDP-11<br>computers). | 132–135     |

|                                  | • In the 11/34, the EIS hardware is an integral part of the CPU.                                                                                                                                                                                         |             |

|                                  | • In the 11/35 and 11/40, the EIS is<br>implemented on a separate printed circuit<br>module (KE11-E) that connects to the<br>Unibus.                                                                                                                     |             |

| programmer's<br>console          | ★ The 11/35 and 11/40 programmer's console<br>contains switches and lamps for performing<br>LOAD, EXAMINE, DEPOSIT, and START<br>functions.                                                                                                              | 136, 137    |

| operator's<br>panel              | ★ The 11/34 operator's panel has a limited number of switches and lamps.                                                                                                                                                                                 | 138–140     |

|                                  | • This operator's panel is used in combination with a ROM console emulator.                                                                                                                                                                              |             |

|                                  | • The ROM emulator permits console<br>functions, such as LOAD, EXAMINE,<br>DEPOSIT, and START, to be performed<br>simply by typing in the appropriate code on<br>the keyboard of the ASCII terminal.                                                     |             |

| 11/34<br>programmer's<br>console | <ul> <li>★ A programmer's console is available as optional<br/>hardware on 11/34 systems (the ROM console<br/>emulator can be used in conjunction with this<br/>optional programmer's console).</li> </ul>                                               | 141         |

| summary                          | ★ Table 3 summarizes the major characteristics of<br>the 11/34, 11/35, and 11/40 minicomputers.                                                                                                                                                          |             |

| · · · · · ·                      |                                                                                                                                                                                                                                                          |             |

|                                  |                                                                                                                                                                                                                                                          | read on 🌢   |

|                                  | 21                                                                                                                                                                                                                                                       |             |

.31

|                                                    | 11/34             | 11/35            | 11/40            |

|----------------------------------------------------|-------------------|------------------|------------------|

| PRINCIPAL MARKETS                                  | OEM &<br>End User | OEM              | End User         |

| PROCESSING MODES                                   | Kernel &<br>User  | Kernel &<br>User | Kernel &<br>User |

| NUMBER OF GPRs                                     | *9                | *9               | *9               |

| NUMBER OF HARDWARE<br>INTERRUPT LEVELS             | 4                 | 4                | 4                |

| MAXIMUM ADDRESS<br>SPACE (words)                   | *128K             | *128K            | *128K            |

| MAXIMUM MEMORY<br>SIZE (words)                     | *124K             | *124K            | *124K            |

| BUS STRUCTURE                                      | Unibus            | Unibus           | Unibus           |

| TYPES OF MAIN<br>MEMORY                            | Core<br>MOS       | Core             | Core             |

| NUMBER OF<br>HARDWARE STACKS                       | *2                | *2               | *2               |

| MEMORY MANAGEMENT                                  | Standard          | Optional         | Optional         |

| ROM BOOTSTRAP LOADER                               | Standard          | Optional         | Optional         |

| EXTENDED INSTRUCTION<br>SET                        | Standard          | Optional         | Optional         |

| PROGRAMMER'S CONSOLE (PC)<br>OPERATOR'S PANEL (OP) | **OP              | PC               | PC               |

Table 3Major Characteristics of the 11/34, 11/35, and 11/40

\*With Memory Management

\*\* The Programmer's Console is available as an option.

|                         | exercise                   | s: part c                                                                                                       |

|-------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------|

| 1. List the three       | major functions of the mer | nory management unit                                                                                            |

|                         | -                          | nory management unit.                                                                                           |

|                         |                            |                                                                                                                 |