# PDP-11/40 system manual

Gunnar Barbro

digital

OT

# PDP-11/40 system manual

Gunnar Barbro

digital equipment corporation · maynard. massachusetts

$\left( \right)$

### TABLE OF CONTENTS

# Page

| 1.1   | Scope                            | 1 - 1        |

|-------|----------------------------------|--------------|

| 1.2   | System Components                | 1=3          |

| 1.3   | Functional Description           | 1-10         |

| 1.3.1 | Unibus                           | 1-11         |

| 1.3.2 | KD11-A Processor                 | 1-14         |

| 1.3.3 | KY11-D Programmer's Console      | 1-17         |

| 1.3.4 | MF11-L Core Memory               | <b>1-1</b> 8 |

| 1.3.5 | Optional Memory Systems          | 1-20         |

| 1.3.6 | DECwriter System                 | 1-22         |

| 1.3.7 | DL11 Asynchronous Line Interface | 1-24         |

| 1.3.8 | Power System                     | 1-26         |

| 1.4   | Applicable Documentation         | 1-28         |

| 1.5   | Engineering Drawings             | 1-38         |

CHAPTER 2 INSTALLATION

| 2.1   | Scope                       | 2-1   |

|-------|-----------------------------|-------|

| 2.2   | Site Preparation            | 2-3   |

| 2.2.1 | Physical Dimensions         | 2-4   |

| 2.2.2 | Fire and Safety Precautions | 2 - 7 |

| 2.2.3 | Environmental Requirements  | 2-9   |

Page

| 2.2.3.1 | Humidity and Temperature          | 2-10          |

|---------|-----------------------------------|---------------|

| 2.2.3.2 | Air Conditioning                  | 2-11          |

| 2.2.3.3 | Acoustical Damping                | 2-12          |

| 2.2.3.4 | Lighting                          | 2-13          |

| 2.2.3.5 | Special Mounting Conditions       | 2-14          |

| 2.2.3.6 | Static Electricity                | 2 <b>-1</b> 5 |

| 2.2.4   | Electrical Requirements           | 2-16          |

| 2.3     | Installation Procedures           | 2-17          |

| 2.3.1   | Unpacking                         | 2 <b>-1</b> 8 |

| 2.3.2   | Inspection                        | 2-21          |

| 2.3.3   | Cabinet Installation              | 2-23          |

| 2.3.4   | AC Power Connections              | 2-25          |

| 2.3.5   | Intercabinet Connections          | 2=27          |

| 2.3.5.1 | Unibus Connections                | 2=28          |

| 2.3.5.2 | Remote Power Connections          | 2-29          |

| 2.3.5.3 | Ground Strapping                  | 2-30          |

| 2.3.6   | Pemote Peripheral Interconnection | 2-31          |

| 2.3.7   | Installation Verification         | 2-33          |

| 2.3.8   | Initial Power Turn-On             | 2=44          |

| 2.4     | Initial Operation and Programming | 2-46          |

| 2.5     | Customer Acceptance               | 2-50          |

iv

# Page

# CHAPTER 3 SYSTEM OPERATION

| 3.1   | Scope                       | 3 <b>- 1</b>      |

|-------|-----------------------------|-------------------|

| 3.2   | KY11-D Programmer's Console | 3 = 2             |

| 3.3   | DECwriter                   | 3 - 1 8           |

| 3.4   | Teletype                    | 3-21              |

| 3.5   | Basic Operation             | 3 <b>-</b> 27     |

| 3.5.1 | Power On                    | 3 <del>-</del> 28 |

| 3.5.2 | Basic Console Control       | 3-30              |

| 3.5.3 | Manual Loading              | 3 = 3 4           |

| 3.5.4 | Automatic Loading           | 3-41              |

| 3.5.5 | Running Programs            | 3-48              |

| 3.6   | Basic Programming           | 3-50              |

CHAPTER 4 PROCESSOR INSTRUCTIONS AND OPTIONS

| 4.1   | Scope                           |  | 4 - 1        |

|-------|---------------------------------|--|--------------|

| 4.2   | Instruction Set                 |  | 4 <b>-</b> 2 |

| 4.2.1 | Address Modes                   |  | 4 - 4        |

| 4.2.2 | Basic Instruction Set           |  | 4-7          |

| 4.2.3 | Extended Instruction Set        |  | 4-21         |

| 4.3   | Processor Options               |  | 4-24         |

| 4.3.1 | KE11-E Extended Instruction Set |  |              |

|       | (EIS) Option                    |  | 4-26         |

# Page

.

| 4.3.2     | KE11-F Floating Instruction Set    |         |

|-----------|------------------------------------|---------|

|           | (FIS) Option                       | 4-30    |

| 4.3.3     | KJ11-A Stack Limit Register Option | 4-34    |

| 4.3.4     | KT11-D Memory Management Option    | 4-37    |

| 4.3.5     | KW11-L Line Frequency Clock Option | 4 - 4 1 |

| 4.3.6     | KM11-A Maintenance Module Option   | 4-43    |

| 4.3.7     | Small Peripheral Controller Slot   | 4 - 44  |

| 4.4       | Memory Options                     | 4-45    |

| 4.4.1     | MM11-L Core Memory                 | 4-46    |

| 4.4.2     | MF11-L Core Menory                 | 4=49    |

| 4.4.3     | ME11-L Core Memory                 | 4-50    |

| 4.4.4     | MM11-S Core Memory                 | 4-52    |

|           |                                    |         |

| CHAPTER 5 | UNIBUS AND SYSTEM OPTIONS          |         |

|           |                                    |         |

| 5.1   | Scope                                   | 5-1   |

|-------|-----------------------------------------|-------|

| 5.2   | Unibus                                  | 5-2   |

| 5.3   | Unibus Options                          | . 5-8 |

| 5.3.1 | PC11 High-Speed Paper-Tape Reader/Punch | 5 - 9 |

| 5.3.2 | LP11 High-Speed Line Printer            | 5-10  |

| 5.3.3 | CP11 Card Reader                        | 5-11  |

| 5.3.4 | TC11/TU56 DECtape System                | 5-13  |

| 5.3.5 | TM11/TU10 DECmagtape System             | 5-15  |

vi

# Page

| RC11/RS64 DECdisk Memory                      | 5-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RF11/RS11 Disk System                         | 5 <b>-</b> 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RK11-C DECpack Disk Cartridge System          | 5-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VT01 Storage Display                          | 5-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VR01 Oscilloscope Display                     | 5-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VR14 Point Plot Display                       | 5-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VT05 Alphanumeric Display                     | 5 <b>-</b> 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RT01 DEClink Terminal                         | 5-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Communications Options                        | 5 <b>-27</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AFC11 Low-Level Analog Input Subsystem        | 5-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AD01-D Analog-to-Digital Conversion Subsystem | 5-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AA11-D Digital-to-Analog Conversion Subsystem | 5-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| EQUIPMENT MOUNTING AND POWEP                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Scope                                         | 6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| System Mounting Box                           | 6 = 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

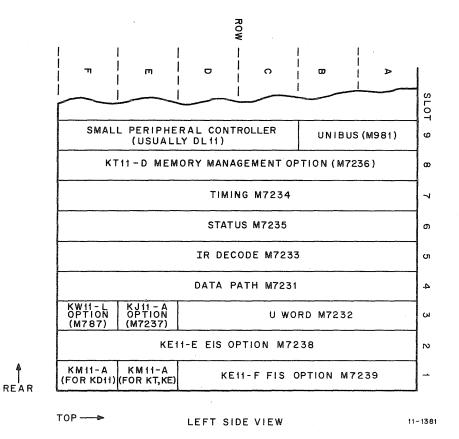

| Processor Module Allocations                  | 6 - 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Memory Module Allocations                     | 6 = 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Programmer's Console Mounting                 | 6-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                               | RF11/RS11 Disk System<br>RK11-C DECpack Disk Cartridge System<br>VT01 Storage Display<br>VR01 Oscilloscope Display<br>VR14 Point Plot Display<br>VT05 Alphanumeric Display<br>RT01 DEClink Terminal<br>Communications Options<br>AFC11 Low-Level Analog Input Subsystem<br>AD01-D Analog-to-Digital Conversion Subsystem<br>AA11-D Digital-to-Analog Conversion Subsystem<br>EQUIPMENT MOUNTING AND POWEP<br>Scope<br>System Mounting Box<br>Processor Module Allocations<br>Memory Module Allocations |

6.3Cabinet and System Mounting6-76.3.1System Cabinet6-86.3.2System Configuration6-9

| 6.4     | Power Control System                         | 6-13          |

|---------|----------------------------------------------|---------------|

| 6.4.1   | 860 Power Control Unit                       | 6-14          |

| 6.4.1.1 | 860 Physical Description                     | 6-16          |

| 6.4.1.2 | 860 Functional Description                   | 6-17          |

| 6.4.1.3 | 860 Circuit Desc ription                     | 6-19          |

| 6.4.2   | 861 Power Control Unit                       | 6-21          |

| 6.5     | PDP11/40 Basic Power Supply                  | 6-22          |

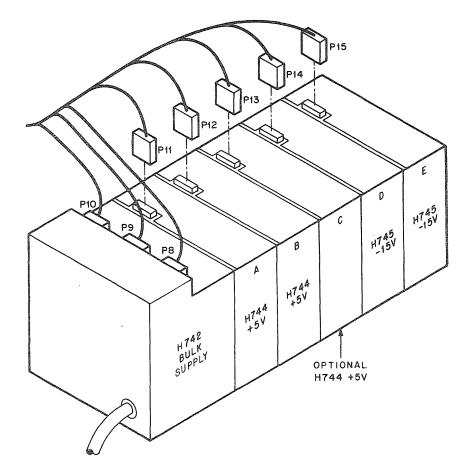

| 6.5.1   | H742 Bulk Power Supply                       | 6=23          |

| 6.5.1.1 | +15V and +8V of the H742 Supply              | 6-25          |

| 6.5.1.2 | Clock Output of the H742 Supply              | 6-26          |

| 6.5.1.3 | AC LO and DC LO Circuits                     | 6-27          |

| 6.5.2   | H744 +5V Regulator                           | 6-29          |

| 6.5.2.1 | H744 Regulator Circuit                       | 6 <b>-</b> 30 |

| 6.5.2.2 | +5V Overcurrent Sensing Circuit of the H744  | 6=33          |

| 6.5.2.3 | +5V Overvoltage Crowbar Circuit of the H744  | 6-34          |

| 6.5.3   | H745 -15V Regulator                          | 6-35          |

| 6.5.3.1 | -15V Regulator Circuit of the H745           | 6-3.6         |

| 2.5.3.2 | -15V Overcurrent Sensing Circuit of the H745 | 6-37          |

| 6.5.3.3 | -15V Overvoltage Crowbar Circuit of the H745 | 6-38          |

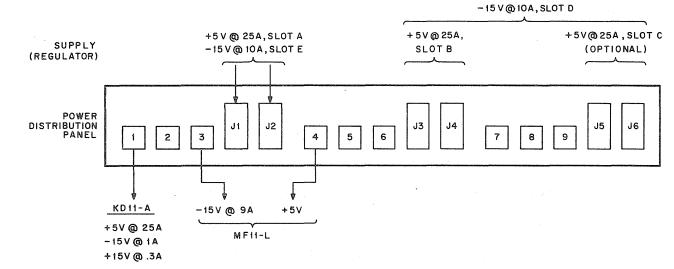

| 6.5.4   | DC Power Distribution                        | 6=39          |

| 6.5.5   | Maintenance of Power System                  | 6-42          |

viii

# Page

## CHAPTER 7 GENERAL MAINTENANCE

| 7.1     | Scope                                            | 7-1            |

|---------|--------------------------------------------------|----------------|

| 7.2     | Overall Maintenance Techniques                   | 7 <b>-</b> 2'  |

| 7.2.1   | Knowledge of Proper Hardware Operation           | 7 - 3          |

| 7.2.2   | Detection and Isolation of Error Condition       | <b>7 -</b> 5   |

| 7.2.3   | Means of Repairing the Error Condition           | 7 - 7          |

| 7.2.4   | Digital Field Service                            | 7 = 8          |

| 7.3     | Maintenance Equipment Required                   | 7 - 9          |

| 7.4     | Preventive Maintenance                           | 7-13           |

| 7.4.1   | Physical Checks                                  | 7-14           |

| 7.4.2   | Electrical Checks and Adjustments                | 7-16           |

| 7.4.2.1 | Voltage Regulator Checks                         | 7-17           |

| 7.4.2.2 | 860 Power Control                                | 7 <b>-</b> 19  |

| 7.3.2.3 | AC Power Connector Receptacles                   | 7-20           |

| 7.4.3   | ASR33 Teletype                                   | 7 - 21         |

| 7.4.3.1 | Preventive Maintenance Checks                    | 7-21           |

| 7.4.3.2 | Lubrication                                      | 7-22           |

| 7.4.4   | LA30 DECwriter                                   | 7-24           |

| 7.4.4.1 | Preventive Maintenance Schedule                  | 7 - 24         |

| 7.4.4.2 | Cleaning Procedures                              | <b>7 - 2</b> 6 |

| 7.4.5   | PC05 High-Speed Paper-Tape Reader/Punch (option) | 7-28           |

| 7.4.5.1 | Mechanical Checks                                | 7 <b>-</b> 29  |

| 7.4.5.2 | Electrical Checks                         | 7-30           |

|---------|-------------------------------------------|----------------|

| 7.5     | Use of Module Extenders                   | <b>7 -</b> 3 1 |

| 7.6     | PDP-11/40 Power System Maintenance        | 7-32           |

| 7.6.1   | Circuit Tracing                           | 7-33           |

| 7.6.2   | Voltage REgulator Tests (Off-Line Repair) | <b>7-</b> 34   |

| 7.6.3   | Voltage Regulator Test (After REpair)     | 7-39           |

### ILLUSTRATIONS

| 2=1              | PDP=11/40 Connector                         | 2 <b>-1</b> 6A |

|------------------|---------------------------------------------|----------------|

| 2 ∞ 3            | D.C. Cable Harness                          | 2-45A          |

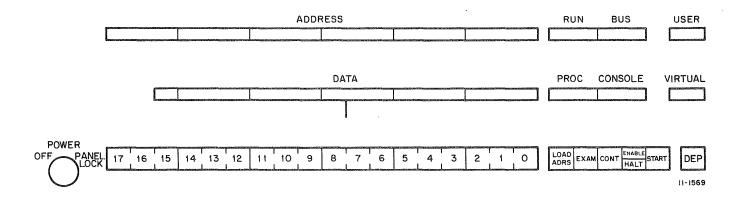

| 3-1              | PDP-11/40 Programmer's Console              | 3 - 4          |

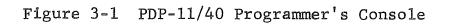

| 3 - 2            | DECwriter Controls                          | 3-19           |

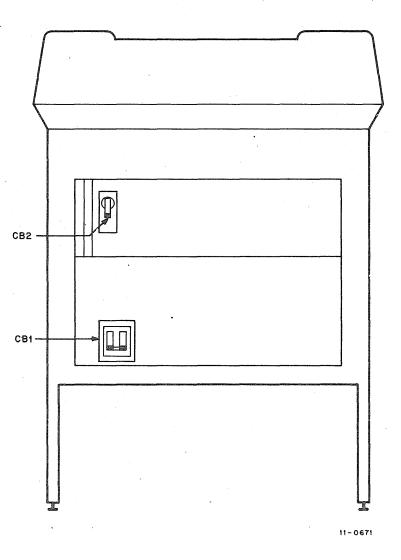

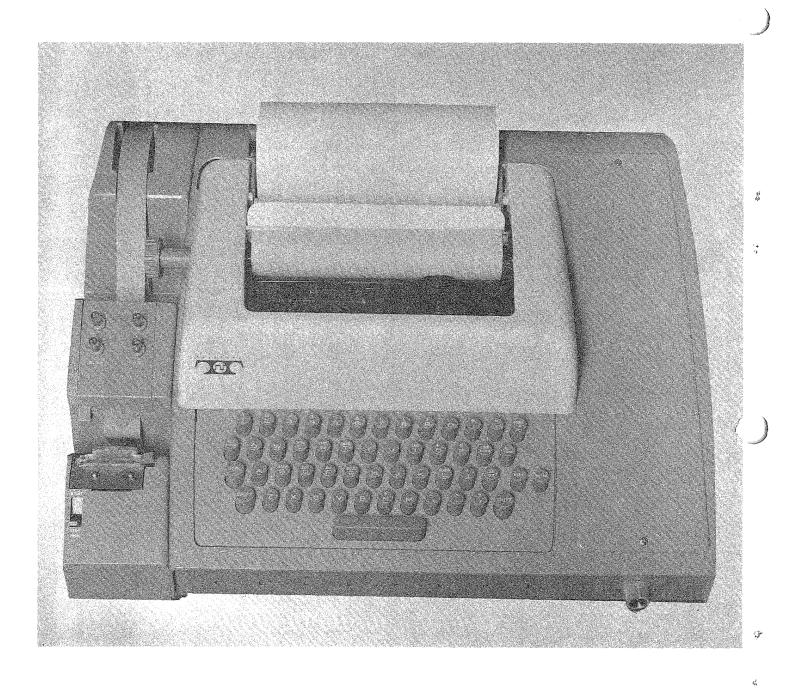

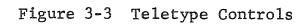

| 3-3              | Teletype Controls                           | 3-22           |

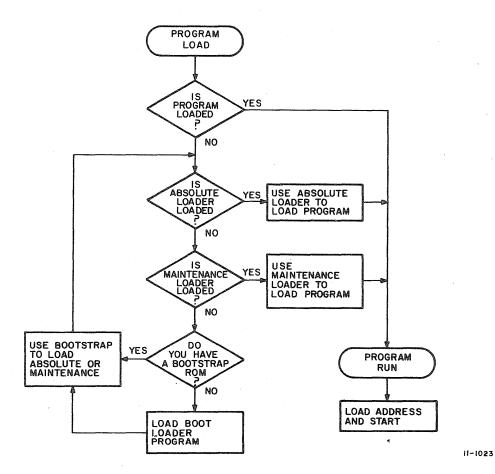

| 3 - 4            | Flowchart of Procedure for Running Programs | 3 <b>-</b> 37  |

| <u>4</u> = 1     | Double and Single Operand Address Modes     | 4-6            |

| <u>4</u> = 2     | Instruction Formats                         | 4 = 9          |

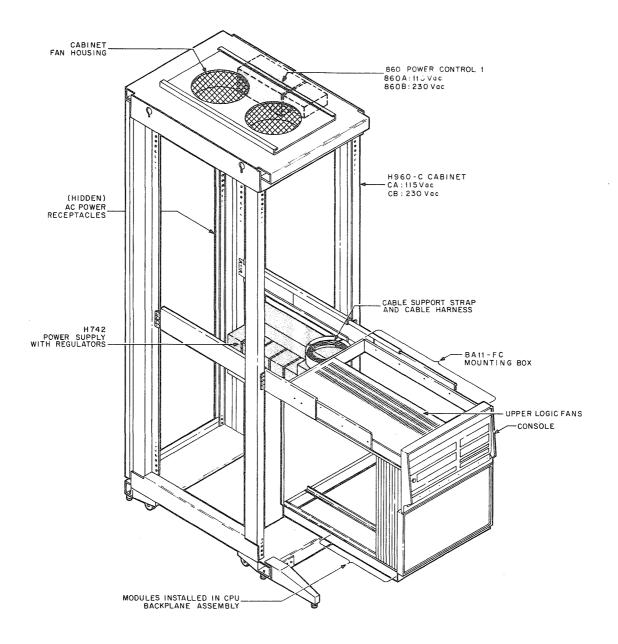

| 6-1              | PDP-11/40 System Cabinet                    | 6-3A           |

| 6 <del>-</del> 2 | PDP-11/40 Mounting Box (BA11-FC)            | 6 <b>-</b> 3B  |

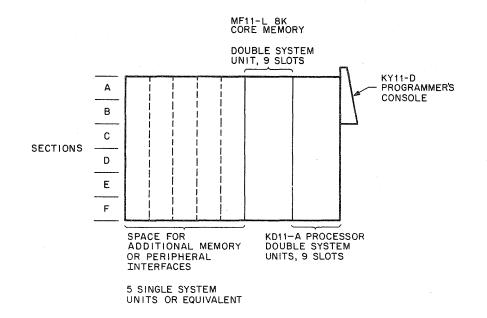

| 6-3              | Module Allocation - KD11-A Processor,       |                |

|                  | Basic (*) and Options                       | 6 <b>-</b> 4A  |

| 6 - 4            | Module Allocation - MF11-L Memory,          |                |

|                  | Basic (*) and Optional MM11-Ls              | 6 <b>-</b> 6A  |

# ILLUSTRATIONS (Cont)

| Ρ | a | q | е |

|---|---|---|---|

|   |   |   |   |

| 6 - 5 | Typical Multiple Cabinet System Cinfiguration | 6 <b>-1</b> 0A |

|-------|-----------------------------------------------|----------------|

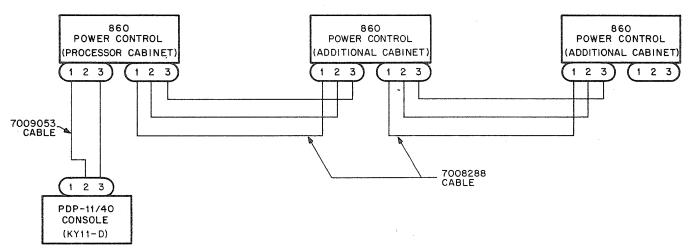

| 6-6   | Power Control Interconnection                 | 6 <b>-1</b> 6A |

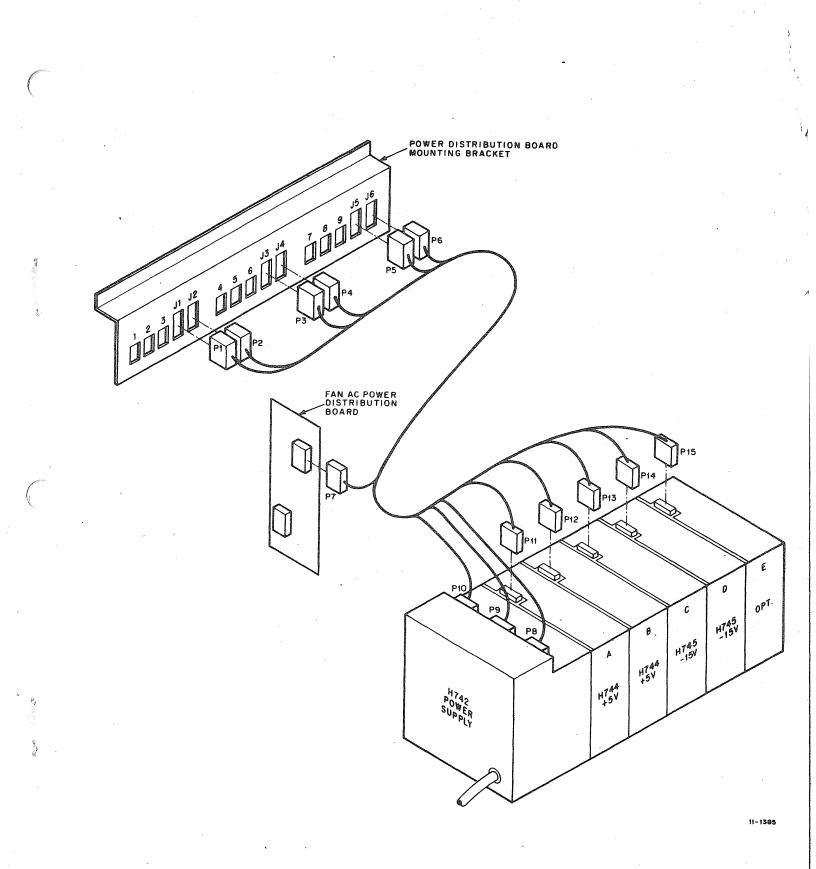

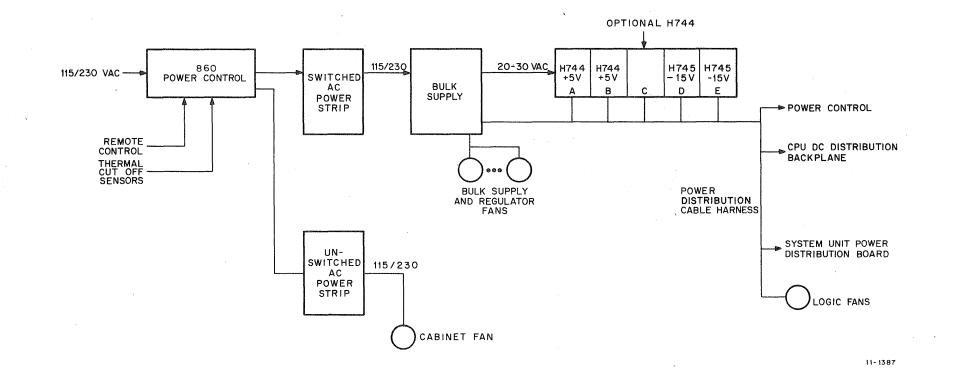

| ნ ∞ 8 | PDP-11/40 Power System Block Diagram          | 6 <b>-</b> 22A |

| 6-9   | PDP-11/40 Power Supply                        | 6 <b>-</b> 22B |

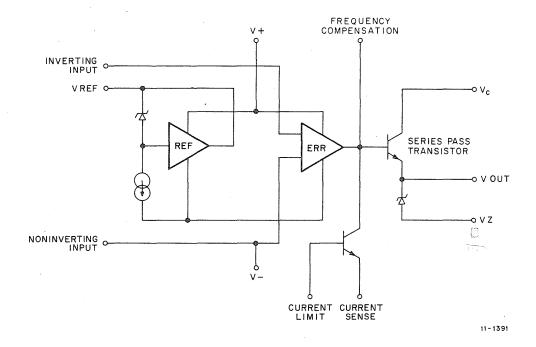

| 6-10  | Simplified Diagram of Precision Voltage       |                |

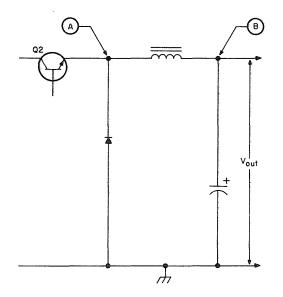

|       | Regulator E1                                  | 6-30A          |

| 6-11  | DC Power Distribution                         | 6-41A          |

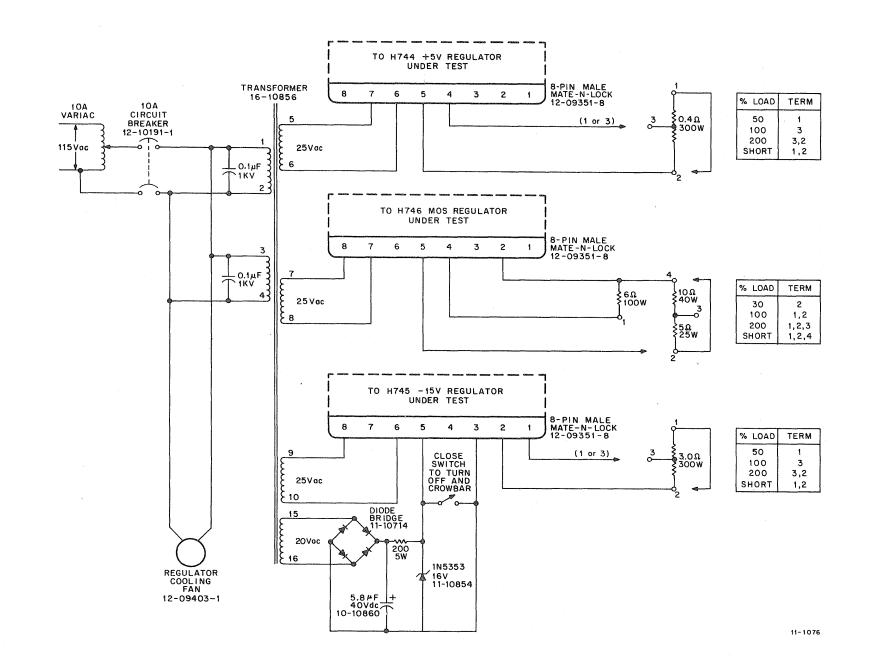

| 7 - 1 | Voltage Regulator Test Bench Source and Loads | 7-35A          |

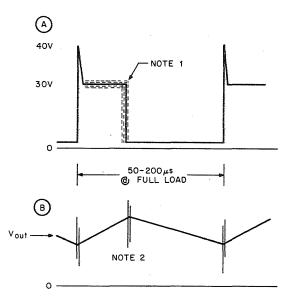

| 7 = 2 | Typical Voltage Regulator Output Waveforms    | 7-40A          |

xi

#### CHAPTER 1 INTRODUCTION

#### 1.1 SCOPE

This manual, the PDP11/40 System Manual, provides a general introduction to the PDP11/40 system and includes sections on installation, operation, the instruction set, options, mounting and power, and maintenance. This overview is supplemented with references to other manuals in the PDP11/40 series for detailed explanations.

The PDP11/40 manuals provide the user with the theory of operation necessary to understand, operate, and maintain the PDP11/40 System. These manuals reference associated engineering drawings, both are listed in Table 1-2. Please note that the associated drawings are separate volumes and documented by their Drawing Directory number (not the manual number). Both volumes are necessary.

The level of discussion in each manual assumes that the reader is familiar with basic digital computer theory. The maintenance philosophy presents information about normal system operation and enables the user to recognize trouble symptoms and to perform necessary corrective action. Each individual manual contains theory of operation, diagrams, maintenance techniques. Logic drawings for the specific component covered are contained in separate volumes.

This chapter describes the basic system components (paragraph 1.2) and provides a functional description of the overall PDP-11/40 system and each of its major components (paragraph 1.3). The remainder of the chapter covers applicable documents (paragraph 1.4), engineering drawings (paragraph 1.5), and terminology (paragraph 1.6).

#### **1.2** SYSTEM COMPONENTS

The PDP-11/40 System consists of six basic components: processor, programmer's console, core memory, DECwriter with associated control, power supply, and mounting box. Possible variation to this basic system are listed in Table 1-1.

Options and peripherals added to the basic PDP-11/40 System are covered in separate manuals delivered with the system. Manuals are included only for those options specifically ordered with an individual system.

### Table 1-1

# Possible PDP-11/40 Variations

Major Component

### Possible Variations

\*KY11-D Programmer's

None

Console

### Possible PDP-11/40 Variations

Major Component

Possible Variations

Core Memory

- MM**11-**L

- 8K core memory, 900 ns cycle time, 350 ns internal access time

\*MF11-L - MM11-L memory plus backplane, space exists for two additional MM11-Ls

ME11-L - MM11-L memory plus backplane, mounting box, and power supply (complete memory system)

MM11-S

MM11-L memory, interleaved, plus backplane (may be used for expansion of memory above 24K)

### Possible PDP-11/40 Variations

Major Component

Possible Variations

Core Memory (Cont)

#### NOTES

Memory systems compatible with the PDP-11/20 may also be used in the PDP-11/40. These memories are:

| MM11-E           | -         | 4K  | hv  | 16  | bit        |

|------------------|-----------|-----|-----|-----|------------|

| MM11-F           | Nga       | 4K  | by  | 16  | bit        |

| MM <b>11-</b> FP | -         | 4K  | by  | 16  | bit,       |

|                  |           |     |     |     |            |

|                  |           | wit | h p | ari | ty         |

| MM <b>11-</b> H  | <b>68</b> |     |     |     | lty<br>bit |

These memories cannot be mounted within or powered within the basic PDP11/40 mounting box.

### Possible PDP-11/40 Variations

Major Component

Possible Variations

DECwriter

\*\*LA30

Standard 97-character keyboard. Optional 128-character keyboard available. (LA30-S is a serial DECwriter and is controlled by a DL11 control; LA30-P is a parallel DECwriter and is controlled by an LC11 control.)

Teletype Unit

\*\*33 ASR 33 KSR 35 ASR 35 KSR Each unit is available in 120V or 240V models.

| DL11-A          | Teletype, display, or LA30-S control |

|-----------------|--------------------------------------|

| DL <b>11-</b> B | EIA terminal control                 |

| DL11-C          | Teletype, display, or LA30-S control |

| DL11-D          | EIA terminal control                 |

| DL11-E          | Dataset control                      |

|                 | DL11-B<br>DL11-C<br>DL11-D           |

### Possible PDP-11/40 Variations

Major Component

Possible Variations

KL11-BSimilar to KL11-A. DifferKL11-Cprimarily in baud rates asKL11-Edescribed in KL11 manual.KL11-F

LC11 LA30-P DECwriter control

Power System \*H742 Power Supply (may be jumpered for either 120V or 240V, 50/60 Hz)

> \*H744 +5V regulator, 25A (two normally supplied with basic system; additional unit may be included to handle system options)

\*H745 -15V regulator, 10A (two)

### Possible PDP-11/40 Variations

Major Component

### Possible Variations

\*860 Power Control - mounted in top of cabinet. Two versions available:

860A - requires 120V input 860B - requires 240V input

Mounting Box

k

\*BA11-FC Mounting Box

- An asterisk indicates that this is the normal configuration shipped with the basic machine, unless otherwise specified by the customer.

- \*\* Either the LA30 DECwriter or the Teletype Unit may be used as the basic PDP-11/40 System input/output device.

#### 1.3 FUNCTIONAL DESCRIPTION

The PDP-11/40 is a 16-bit, general-purpose, parallel-logic, microprogrammed computer using 1- and 2-address instructions and 2s complement arithmetic. The system contains a variable instruction length processor, which directly addresses all of core memory. All communication among system components (including processor, core memory, and peripherals) is performed on a single high-speed bus, the Unibus. Because of the bus concept, all peripherals are compatible, and device-to-device transfers can be accomplished at the rate of 2,500,000 words-per-second. All peripherals are in the basic system address space; therefore, all instructions are I/O instructions. All system components and peripherals are linked by the Unibus and power connectors.

Subsequent paragraphs present a brief functional description of basic PDP-11/40 System components. A functional description of all processor options is presented in Chapter 4 of this manual.

#### 1.3.1 Unibus

The Unibus is a single high-speed bus that provides communication between system components. The Unibus, with bidirectional data, address, and control lines, allows data transfers between all units on the bus with control of the bus an important factor in these transfers. The fixed repertoire of bus operations is flexible enough for speed and design economy, yet provides a fixed specification for interfaces. The asynchronous nature of these operations also eases design and operation. The repertoire of bus operations is:

DATI, DATIP, DATO, DATOB - data operations INTR, PTR (BR, NPR) - control operations

Full 16-bit words or 8-bit bytes of information can be transferred on the bus between the master and slave. The DATI, DATIP operations transfer data into the master; the DATO, DATOB operations transfer data out of the master. When a device is capable of becoming bus master and requests use of the bus, it is generally for one of two purposes: to make a direct memory access (DMA) transfer of data directly to, or from, another device without processor intervention; or to interrupt (INTR) program execution and force the processor to branch to a specific address where an interrupt service routine is located.

Bus control is obtained under a non-processor request (NPR) for the direct memory access (DMA) or under a bus request (BR)

for an interrupt (INTR). A device can perform a DMA after acquiring bus control by a BR: bus control acquisition is at a lower priority.

Requests for the bus can be made at any time on the bus request (BR) and non-processor request (NPR) lines. Transfer of bus control from one device to another is made by the processor priority arbitration logic which grants control of the bus to the device having the highest priority. The NPR's are serviced before and directly after Unibus data cycles, in addition to specific times during WAIT or TRAP sequences. The BR's are serviced at the end of the instruction if the requesting priority exceeds that of the processor.

The processor has a special role in bus control operations as it performs the priority arbitration to select the next bus master. The processor assumes bus control when no other dev ice has control.

The Unibus originates in the processor with the Internal Unibus and Terminator module (M981) that carries the Unibus from the processor to the next system unit. All 56 Unibus signals and 17 grounds are carried in this one module. In addition, a 120-conductor Flexprint cable may be used to connect system units in different mounting boxes or to connect a peripheral device removed from the mounting box.

A complete description of the Unibus, including specifications, is presented in the PDP-11 Peripherals and Interfacing Handbook.

#### 1.3.2 KD11-A Processor

The KD11-A Processor decodes instructions, modifies data, makes decisions, and controls allocation of the Unibus among external devices. The processor contains eight hardware programming registers which are used as arithmetic accumulators, index register, autoincrement and autodecrement registers, and stack pointer registers. Two registers are specifically used for the processor:s program counter (PC) and stack pointer (SP).

Because of the flexibility of hardware registers, address modes, instruction set, and direct memory access, PDP-11/40 programs are written in directly relocatable codes. The processor also includes a full complement of instructions that manipulate byte operands, including provisions for byte swapping. Either words or bytes may be displayed on the programmer's console.

Any of the eight internal registers can be used to build last-in, first-out stacks. One register serves as a processor (or machine) stack pointer for automatic stacking. This stack handling capability permits save and restore of the program counter and status word in conjunction with subroutine calls and interrupts. This feature allows true reentrant codes and automatic nesting of subroutines. Addition of the KJ11 Stack Limit Register Option permits alteration of the stack overflow limit and provides both warning (yellow) and fatal (red) stack error indications.

The Unibus is used by the processor and all peripheral devices; therefore, there must be a priority structure to determine which device becomes bus master. A device generally requests use of the bus to make a nonprocessor transfer of data directly to or from memory, or to interrupt program execution and force the processor to branch to an interrupt service routine. A nonprocessor request (NPR) is granted by the processor at the end of bus cycles and allows device-to-device data transfers without processor intervention. A bus request (BR) is granted by the processor at the end of an instruction and allows the device to interrupt the current processor task. The entire instruction set is then available for manipulating device registers.

The processor recognizes four levels of hardware bus requests; each major level contains sublevels. Many devices can be attached on each major level with the device that is electrically closest to the processor given priority over other devices on the same priority level. The priority level of the processor itself is programmable within the hardware levels; therefore, a running program can select the priority level of permissible interrupts.

Additional speed and power are added to the interrupt structure through the use of the PDP-11/40 fully vectored interrupt scheme. With vectored interrupts, the device identifies itself, and a unique interrupt service routine is automatically selected by the processor. This eliminates device polling, and permits nesting of device service routines. The device interrupt

priority and service routine priority are independent to allow dynamic adjustment of system behavior in response to real-time conditions.

The address mapping of the system is dependent on the three most significant bits of the 16 bits in the KD11-A processor address for the basic processor. If these bits are all 1s, the two most significant bits of the Unibus address are forced to 1s; otherwise, the two most significant bits of the 18-bit Unibus address are forced to 0s. The KT11-D Memory Management Option coverts these 16-bit addresses into full 18-bit physical Unibus addresses.

A detailed description of the processor is presented in the KD11 Processor Manual, DEC-11-HKDAA-A-D.

The KY11-D Programmer's Console provides the programmer with a direct system interface. The console allows the user to start, stop, load, modify, step, or continue a program. Console displays indicate data and address as well as which device is controlling the bus; thus, operations can be monitored.

The programmer's console interacts with the processor, with microprogram control for the processor operation located in the processor. The console contains only indicators (light emitting diodes), switches, and the contact bounce filtering circuits for the control switches. Console operation does require certain Unibus operations through the processor: DATO for DEP and DATI for EXAM. For single-step operation, the processor responds to a console bus request (CBR). The CBR priority supersedes all other BR priorities. Note that use of the KM11 Maintenance Console option provides further display of machine states and allows single microstate stepping.

The programmer's console is mounted as the front panel of the BA11-FC mounting box and is connected to the processor by means of two cables.

Console operation, including descriptions of all controls and indicators, is presented in Chapter 3 of this manual. Detailed descriptions of console logic circuits are covered in the KD11 Processor Manual, DEC-11-HKDAA-A-D.

### 1.3.4 MF11-L Core Memory

The MF11-L Core Memory used in the PDP-11/40 System is a random access, coincident current, magnetic core, read/write memory with a cycle time of 900 ns and an internal access time of 350 ns. The memory consists of ferrite cores wired in a planar 3-D, 3-wire configuration that uses a shared sense/inhibit line. The basic memory unit consists of the backplane and three modules capable of storing 8192 (8K) 16-bit words. Provision for additional memory is made by this 9-slot, 2-system unit equivalent backplane. Two MM11-Ls, each consisting of three modules providing 8192 (8K) words, can be added.

The core memory uses the Unibus for data transfers to and from the processor and other devices; however, core memory is never bus master. Because the memory is always a slave device, a DATO or DATOB indicates information transferred out of the master into the memory. Because of the Unibus structure, the memory can be directly addressed by the processor or any other master device; every location in core can function as a true arithmetic accumulator.

The memory does not enter the priority structure because it is never bus master. The master device, however, can request use of the memory through either a bus request (BP) or a non-processor request (NPR). Because the memory is completely independent of the processor, any master device can perform direct data transfers with memory without processor intervention.

A detailed description of the memory is presented in the ME11-L Core Memory manual, DEC-11-HMELA-A-D. Note that the ME11-L is basically an MF11-L with the addition of a mounting box and power supply.

Note that the instruction timing specified for the PDP-11/40 System applies only for the MF11-L and MM11-S memories. These memories employ a special MSYN signal between the processor and the memory housed in the same mounting box.

#### 1.3.5 Optional Memory Systems

There are two types of optional memory systems that may be used with the PDP-11/40 System: core memories similar to the MM11-L, and core memories used with other members of the PDP-11 family.

There are four memory systems similar to the MM11-L. The prime difference is packaging. These four memories are:

- MM11-L 8K by 16 bit, 900 ns cycle time, modules and stack only.

- MF11-L MM11-L memory plus backplane accomodating three MM11-L memories in a double system unit.

- ME11-L Complete memory system consisting of MM11-L memory, backplane, mounting box, and power supply.

- MM11-S MM11-L memory singularly in a single system unit.

There are five core memories designed for use with the PDP-11/20 System that may be used, if desired, with the PDP-11/40 System provided they are powered by H720 type power supplies. These memories are:

| MM <b>11-</b> E  | 82           | 4K by 16 bit, 1.2 us access time      |

|------------------|--------------|---------------------------------------|

| MM11-F           | . , <b>.</b> | 4K by 16 bit, 950 ns access time      |

| MM <b>11-</b> FP |              | an MM11-F with parity option included |

| MM <b>11-</b> H  |              | 1K by 16 bit, 950 ns access time      |

| MM11-J           | , .          | 2K by 16 bit, 950 ns access time      |

Both the MM11-E and MM11-F memories may be expanded up to 28K in 4K increments. Each 8K segment may be interleaved.

#### 1.3.6 DECwriter System

The LC11 DECwriter System is a high-speed teletypewriter system designed to interface with the PDP-11 family of processors to provide both input (keyboard) and output (printer) functions for the system. It can be used as the console input/output device. The system can receive characters from the keybaord or can print at speeds up to 30 characters per second in standard ASCII formats. The LC11 System consists of two distinct components: an LA30 DECwriter and a DEC PDP-11 interface unit, which is referred to as the LC11 Controller.

The LA30 DECwriter is a dot matrix impact printer and keyboard for use as a full-scale hard copy I/O terminal teletypewriter. The keyboard is either 97 or 128 characters. The print set is 64 ASCII characters, 80 characters per line, 10 characters per inch.

The LC11 Controller is the interface between the DECwriter and the PDP-11 Unibus. It controls data transfers between the DECwriter and other devices in the system. It also monitors print status, indicates when the keyboard buffer is full, and enables the interrupt logic.

The LC11 controller consists of a single quad module that can be mounted in the processor small peripheral controller slot. The LA30 DECwriter is covered in detail in the LA30 DECwriter manual,

DEC-00-LA30-DA and the LC11 is covered in the LC11 DECwriter System manual, DEC-11-HLCB-D.

Note that the LC11 Controller is only used with the LA30-P parallel word DECwriter. If an LA30-S serial word DECwriter is used, it is controlled by the DL11 interface.

#### 1.3.7 DL11 Asynchronous Line Interface

The DL11 Asynchronous Line Interface provides an interface between a communications device, such as a Teletype, and the PDP-11/40 Unibus. Serial information read or written by the device is assembled or disassembled by the control for parallel transfer to, or from, the Unibus. The control also formats the data from the Unibus so that it is in the format required by the device. The interface provides the flags that initiate these data transfers and cause a priority interrupt to indicate the availability of the device. The DL11 is used when a Teletype is used as a system input/output device. It is also used with other types of communications devices such as datasets.

The interface transfers data via processor DATI and DATOB bus cycles. Although a DATO can be used, normal operation consists of a DATOB transfer because the device and the interface handle byte, rather than word, data. The interface can acquire bus control by a bus request (BR) and is normally set at the BR4 priority level. Because the interface operates by a means of an interrupt, no non-processor request (NPR) can be made.

There are five available DL11 interface options (DL11-A through DL11-E) in order to provide the flexibility needed to handle a variety of terminals. For example, the user can select an option for interfacing a Teletype or display keyboard, for handling EIA data, or for handling dataset devices. In addition, depending

on the option used, the user has a choice of line speeds, character size, stop-code length, and parity.

The DL11 interface consists of a single quad module. This module contains address selection logic for decoding the incoming bus address, an interrupt control for generating the interrupt, and receiver/transmitter logic that performs the conversion and formatting functions. The interface can be mounted in a standard processor small peripheral controller slot.

A detailed description of the DL11 interface is presented in the DL11 Asynchronous Line manual, DEC-11-HDLAA-A-D.

#### 1.3.8 Power System

The PDP-11/40 Power System provides power for the basic system and for expansion units (e.g., extra memory or device interfaces) mounted within the basic BA11-FC mounting box. Expansion within the box is limited by space and availab le power.

The basic power system consists of a base H742 power supply, two H745 -15V regulators, and two H744 +5V regulators. There is additional space in the H742 base power system for an additional power regulator unit (either H744 or H745) depending on the requirments of the particular system.

All regulated outputs are protected with current limiting circuits. In addition, a crowbar overvoltage circuit protects the +5V output and the -15V output. An unregulated, partially filtered +5V output is supplied for the indicators on the programmer's console.

In addition to voltage, other outputs are provided by the power system: a line frequency signal, a DC LO logic signal, and an AC LO logic signal. The line frequency signal, which is a sine wave clipped at both ground and +5V, is used by the line frequency interrupt clock option (KW11-L) within the processor. The DC LO signal indicates that the dc voltage outputs are not at the proper value; the AC LO signal indicates insufficient ac voltage.

The basic power system is controlled by a cabinet-mounted 860 power control unit. This power control unit provides thermal and overload protection for the base power supply. Overloads in the switched ac line are handled by a circuit breaker and a thermal switch removes input power in the event of excessive heat or fire. The power control, which is controlled by the OFF/PWR/PANEL LOCK switch on the console, applies power to the base H742 power supply and to the cabinet ac power connectors.

#### 1.4 APPLICABLE DOCUMENTATION

PDP-11 documents related to the PDP-11/40 System are listed in Table 1-2 in two main categories: general handbooks and PDP-11/40 System manuals. System manuals cover the hardware manuals specifically related to the PDP-11/40 and have associated engineering drawings. General documentation covers overall PDP-11 system descriptions, instruction set, addressing modes, basic logic mdoules, Unibus description, interfacing information. Also covered is general software documentation covering basic programs necessary for developing, loading, running, and diagnostic applications. A current list of other available programs may be obtained from the DEC program library.

Both the PDP-11/40 series of manuals and the general handbooks must be used together for a complete understanding of PDP-11/40 systems. The prime subject of this series is the processor and related internal options unique to the PDP-11/40 system. Other handbooks discuss the Unibus used to connect the processor to peripherals, the peripherals themselves, and programming information. A detailed hardware description of each peripheral is provided in its associated hardware maintenance manual supplied with the peripheral.

## Table 1-2

# Applicable Documents

Associated

Title

Drawing Set

Description

PDP-11/40 Processor N/A Handbook DEC,1972 A general PDP-11/40 System handbook covering system architecture, addressing modes, the instruction set, programming techniques, memory management, internal processor options, console operation, and system specifications.

A general peripheral interface handbook. The first part is devoted to a discussion of the various peripherals used with PDP-11 Systems. The second part provides detailed theory, flow, and logic (continued next page)

PDP-11 Peripherals

N/A

and Interfacing

Handbook

DEC, 1972

## Applicable Documents

Associated

Title

Drawing Set Description

descriptions of the Unibus and external device logic; methods of interface construction; and examples of typical interfaces.

Logic Handb ook

N/A

DEC, 1972

Presents functions and specifications of the M-series logic modules and accessories used in PDP-11 interfacing (includes other types of logic produced by DEC but not used with the PDP-11.

## Applicable Documents

Associated

Title

Drawing Set

Description

Paper-Tape Software N/A

Programming

Handbook

DEC-11-GGPB-D

Detailed discussion of the PDP-11 software system used to load, dump, edit, assemble, and debug PDP-11 programs; input/output programming; and the floating point and math package.

PDP-11/40 System

PDP-11/40 Systems

Manual

DEC-11-H405A

A general introduction to the basic PDP-11/40 system including sections on installation, operation, and the instruction set. Also provides detailed information, including maintenance, of the system power supply.

# Applicable Documents

#### Associated

Title

Drawing Set

Description

Block diagram dis-

KD11 Processor

PDP-11/40 Systems

#### Manual

DEC-11-HKDAA-A-D

cussion, flow diagram discussion, theory of operation, and maintenance for the KP11-A processor, KY11-D programmer's console, KJ11 stack limit register option, KW11-L line frequency - clock option, and KM11 maintenance console option.

ME11-L Core Memory PDP-11/40 System

Manual

DEC-11-IIMELA-A-D

General description. detailed description, and maintenance of the MM11-L core memory. (Note that ME11-L is the memory system; MM11-L the basic (continued next page)

Ka

## Applicable Documents

Associated

Title

Drawing Set

PDP-11/40 System

Description

core memory. The MF11-L uses the backplane and core memory of the ME11-L without the box and power supply.

Installation, configuration, programming, and theory of operation of the DL11 interface. Covers DL11-A through DL11-E. The DL11-A or C is normally used as a control for the Teletype of LA30-S DECwriter but the DL11 can be used for a variety of communications devices.

DL11 Asynchronous Line Interface Manual

DEC-11-HDLAA-A-D

## Applicable Documents

Associated

Title

Drawing Set

KT11-D Memory

Management

Description

KE11 Instruction Set Options Manual

DEC-11-HKEFA-A-D

KE11-E ExtendedAInstruction Setp(EIS) Option andcKE11-F FloatingmInstruction SetK(FIS) OptionI

Algorithms, data programming, theory of operation, and maintenance for the KE11-E Extended Instruction Set (EIS) option and the KE11-F Floating Instruction Set (FIS) otpion.

KT11-D Memory Management Option Manual DEC-11-HKTDA-A-D Operation, programming, and detailed theory of operation for the KT11-D Memory Management option.

#### Applicable Documents

Associated

Title

Drawing Set

Description

LA30 DECwriter Manual DEC-00-LA30-DA

DEC-11-HLCB-D

Presents a detailed discussion of the DECwriter including installation, operation, principles of operation, maintenance, troubleshooting, and engineering drawings.

Provides general and detailed descriptions, programming, and operation for the LC11 DECwriter interface. The LC11 is used when an LA30-P (parallel) DECwriter is used as a system input/output device.

LC11 DECwriter

System Manual

## Applicable Documents

Associated

Title

Drawing Set

Description

KL11 Teletype

Control Manual

DEC-11-HR4C-D

detailed descriptions, programming, adjustments, and maintenance for the KL11 Teletype Control that may be used instead of

Provides general and

the DL11 Control.

Describes operation and maintenance of the Model 33 ASR Teletype unit that can be used as an input/output device with the PDP-11/40 System. Comparable manuals available for other Teletype models.

Automatic Send-Receive Sets, Manual Bulletin 273B, two volumes, Teletype Corp.

# Applicable Documents

## Associated

Title

Drawing Set

Description

Model 33 Page Printer Set,

Parts

Bulletin 1184B, Teletype Corp. Contains an illustrated parts breakdown to serve as a guide for disassembly, reassembly, and parts ordering for the Model 33 ASR Teletype Unit. Comparable manuals available for other Teletype models.

#### 1.5 ENGINEERING DRAWINGS

A complete set of engineering drawings and module circuit schematics is provided with each PDP-11/40 System. These prints sets were noted in Table 1-2 of paragraph 1-4 either under a Drawing Directory reference or as a second volume to the Maintenance Manual. The engineering drawings are necessary and interrelate with the manual discussion. The DDI (Drawing Directory Index) provides a list of prints included in the set and includes drawing number, title, and revision numbers. An X in the column labled CUSTOMER PRINT SET indicates each drawing that is provided for the customer. The 1972 DEC Logic Handbook contains general logic symbols used on DEC drawings. A more detailed discussion of drawing set conventions is contained in the KD11 Processor Manual, DEC-11-HKDAA-A-D with this convention directly applicable to the processor and processor options of the PDP-11/40.

An overall corporate convention is useful in identifying prints and is noted below:

#### D-CS-M7233-0-1

Original drawing size

Drawing type

Series

Manufacturing variation Module type, equipment type, or a 7-digit DEC part number.

- CS: Circuit schematic

- BS: Block schematic

- BD: Block diagram

- FD: Flow diagram

- DD: Drawing directory

- MU: Module utilization

- AD: Assembly drawing

- UA: Unit Assembly

- WL: Wire list

- PL: Parts list

- AL: Accessory list

In addition to the basic drawing number, a second type of number is used with logic drawings. It consists of a 3-digit number located in the title block. For example:

#### KT-3

KT11-D Option drawing set Sheet 3 of this specific drawing set

The processor drawing set uses a number designation for each module. Thus, K2-4 indicates sheet 4 of the K2 drawing set. K2 indicates the U WORD drawing set. Processor drawing set designations are listed in the KD11-A Processor Manual along with a description of the flow chart and logic diagram conventions.

#### CHAPTER 2 INSTALLATION

#### 2.1 SCOPE

This chapter provides installation information and recommendations to ensure proper installation, and subsequent operation of the PDP-11/40 System.

Only installation of the basic PDP-11/40 System and processor options is included in this chapter. A section on installation of peripherals is not provided because of the modular and Unibus concepts of the system. To install a peripheral, for example, it is usually only necessary to insert the interface module(s) into the basic system mounting box and connect appropriate cabling between the interface and the peripheral. Installation and maintenance of the peripheral itself is normally covered in associated manuals.

It is recommended that sufficient time be given to site planning and preparation with particular attention given to the user's specific system configuration especially if a large number of peripherals are part of the system.

There are two DEC documents that aid in proper site planning: the PDP-11 Configuration Worksheet and the PDP-11 Site Preparation Worksheet.

The configuration worksheet permits the user to lay out the system prior to ordering so that he is aware of drawer layout, cabinet layout, and Unibus interconnection. This ensures that the proper number of drawers and cabinets are used and that Unibus length is sufficient for the system.

The Site PREPARATION Worksheet permits the user to determine the power requirements, environmental preparations, and physical arrangement of his system. The worksheet provides data on operating environment, power requirements, service and access requirements, and physical specifications for the basic system and available peripherals.

A final layout plan should be approved jointly by the user and DEC prior to delivery of equipment. It is recommended that any modifications to the installation site be effected prior to shipment and installation of the system.

DEC Sales Engineers and Field Service Engineers are available for consultation and planning and it is recemmended that a qualified DEC representative either install the system, or be present during the installation process.

## 2.2 SITE PREPARATION

Adequate site planning and preparation can greatly simplify the installation process, resulting in more efficient and reliable PDP-11/40 installation. DEC Sales Engineers and Field Service Engineers are available for consultation and planning with customer representatives regarding objectives, course of action, and progress of the installation. The information in this paragraph is provided primarily to permit review of the site planning.

#### 2.2.1 Physical Dimensions

The overall dimensions and total weight of the particular PDP-11/40 System as well as dimensions, weights, and cable lengths of any optional cabinets and free-standing peripherals should be known prior to shipment of the equipment.

The route the equipment is to travel from the customer receiving area to the installation site should be studied and measurements of doors, passageways, etc. should be taken to facilitate delivery of equipment. All measurements and floor plans should be submitted to the DEC Sales Engineer and DEC Field Service to ensure that the equipment is packed to suit the installation site facilities. Any restrictions (such as bends or obstructions in ahllways, etc.) should be reported to DEC.

If an elevator is to be used for transferring the PDP-11/40 and its related equipment to the installation site, DEC should be notified of the size and gross weight limitations so that the equipment can be shipped accordingly.

Installation site space requirements are determined by the specific system configuration to be installed and, when applicable, provision for future expansion. To determine the exact area required for a specific configuration, a machine-room floor plan layout can be helpful. When applicable, space should be provided in the machine room for storage of

tape reels, printer forms, card files, etc. The integration of the work area with storage area can be considered in relation to the work flow requirements between areas.

In large installations where test equipment is maintained, DEC recommends that the test equipment storage area be within or adjacent to the machine room.

Operational requirements determine the specific location of the various options and free-standing peripherals of the system. Dimensions, weights and cable lengths of free-standing peripheral equipment must be known prior to installation; preferably during site preparation and planning. The system peripherals must not be located at distances from the basic system where connecting cables exceed maximum limits. The following points should be considered when planning the PDP-11/40 layout:

- a. Ease of visual observation of input/output devices by operating personnel.

- Adequate work area for installing tapes, access to console, etc.

- c. Space availability for contemplated future expansion.

- d. Proximity of the cabinets to peripherals.

- e. Proximity of cabinets and peripherals to any humidity controlling or air conditioning equipment.

The final layout should be reviewed by the DEC Sales Engineer, DEC Field Service, and in-house engineering personnel to ensure that cable limitations have not been exceeded and that proper clearances have been maintained. 2.2.2 Fire and Safety Precautions

The following fire and safety precautions are presented as an aid in providing an installation that affords adequate operational safeguards for personnel and system components.

- a. If an overhead sprinkler system is used, a "dry pipe" system is recommended. This type of system, upon detection of a fire, removes source power to the room and then opens a master value to fill the room's overhead sprinklers.

- b. If the fire detection system is the type that shuts off the power to the installation, a battery-operated emergency light source should be provided.

- c. If an automatic carbon-dioxide fire protection system is used, an alarm should sound prior to release of the CO to warn personnel within the 2 installation.

- d. If power connections are made beneath the floor of a raised-floor installation, waterproof electrical receptacles and connections should be used.

e. An adequate earth ground connection should be provided for the protection of operating personnel.

2.2.3 Environmental Requirements

An ideal computer room type environment has an air distribution system which provides cool, well-filtered, humidified air. The room air pressure should be kept higher than that of adjacent areas to prevent dust infiltration. 2.2.3.1 Humidity and Temperature - The PDP=11/40 electronics are designed to operate in a temperature range of from 50 F  $(10^{\circ}C)$  to  $122^{\circ}F$  (50°C) at a relative humidity of 20 to 95% without condensation. However, typical system configurations that use I/O devices such as magnetic tape units, card readers, etc., require an operational temperature range of from 60°F  $(15^{\circ}C)$  to 80°F (27°C) with 40 to 60% relative humidity. Nominal operating conditions for a typical system configuration are a temperature of 70°F (20°C) and a relative humidity of 45%. 2.2.3.2 Air Conditioning - When used, computer room air-conditioning equipment should conform to the requirements of the 'Standard for the Installation of Air Conditioning nad Ventilating Systems (non-residential)'', N.F.P.A Number 90A; as well as the requirements of the 'Standard for Electronic Computer Systems'', N.F.P.A. Number 75. 2.2.3.3 Acoustical Damping - Some peripheral devices (such as line printers and magnetic tape transports) are quite noisy. In installations that use a group of high noise level devices, an acoustically damped ceiling reduces the noise. Operator comfort and efficiency is a major concern here. 2.2.3.4 Lighting - If cathode-ray tube (CRT) peripheral devices are part of the system, the illumination surrounding these peripherals should be reduced to enable the operator to conveniently observe the display. 2.2.3.5 Special Mounting Conditions - If the PDP-11/40 is to be subjected to rolling, pitching, or vibration of the mounting surface (e.g., aboard a ship), the cabinets should be securely anchored to the installation floor by mounting bolts. Since such installations require modifications to the system cabinets, DEC must be notified upon placement of the order so that necessary modifications can be made. 2.2.3.6 Static Electricity - Static electricity can be an annoyance to personnel and can, in extreme cases, affect the operational characteristics of the PDP-11/40 System and related peripherals. If carpeting is installed on the installation room floor, it should be of a type designed to minimize the effects of static electricity. Flooring consisting of metal panels, or flooring with metal edges, should be adequately grounded.

## 2.2.4 Electrical Requirements

The PDP-11/40 can be operated from a nominal 115V, 50/60 Hz or 230V, 50/60 Hz ac power source. The primary ac operational voltages should be maintained within the defined tolerances.

Line voltage tolerance should be maintained within 10% of the nominal value and the 50/60 Hz line frequency should not vary more than 3 Hz.

Primary power to the system should be provided on a line separate from lighting, air-conditioning, etc., so that computer operation is not affected by voltage surges or fluctuations.

The PDP-11/40 cabinet grounding point should be connected to the building power transformer ground or to the building ground point. Direct any questions regarding power requirements and installation wiring to the DEC Sales Engineer or Field Service Engineer.

Primary power outlets at the installation site must be compatible with the PDP-11/40 primary power input connectors. The PDP-11/40 basic system requires only one receptacle. Figure 2-1 shows the ac plug.

## 115V, OR 230V, 60Hz, SINGLE-PHASE, 30A (PIN VIEW OF MALE PLUG)

NOTE: Hubbell 2610 Nema L5-30P (plug) L5-30R (receptacle) REUTRAL OR RETURN (WHITE)

11-1134

# Figure 2-1 PDP-11/40 Connector

## 2.3 INSTALLATION PROCEDURES

The procedures presented in the following paragraphs are provided to assist in unpacking, inspection, and installation of the PDP-11/40 System and associated processor options.

## CAUTION

Do not attempt to install the system until DEC has been notified and a DEC Field Service Representative is present.

### 2.3.1 Unpacking

Before unpacking the equipment, check the shipment against the packing list provided. Check that the correct number of packages has been delivered and that each package contains all the items listed on the accompanying packing slip. Also, check that all items on the accessories list in the Customer Acceptance Procedures have been included in the shipment. Unpack the cabinets as described in the following procedure.

Procedure

1

2

5

Remove outer shipping container.

#### NOTE

The container may be either heavy corrugated cardboard or plywood. In either case remove all metal straps first and then remove any fasteners and cleats securing the container to the skid. If applicable, remove wood framing and supports from around the cabinet perimeter.

Remove the polyethylene cover from the cabinets.

- 3 Remove the tape or plastic shipping pins, as applicable, from the cabinet(s) rear access door(s).

- 4 Unbolt cabinet(s) from the shipping skid. Access to the bolts, located on the lower supporting siderails, is facilitated by opening the access door(s). Remove the bolts.

- Raise the leveling feet so that they are above the level of the roll-around casters.

- 6 Use wood blocks and planks to form a ramp from the skid to the floor and carefully roll the cabinet onto the floor.

- 7 Roll the system to the proper location for installation.

- 8 If applicable, repeat Steps 1 through 7 for the expansion cabinets.

- 9 When the cabinets are oriented properly follow the procedure of Paragraphs 2.3.2 and 2.3.3 to install the cabinet(s).

### 2.3.2 INSPECTION

After removing the equipment packing material, inspect the equipment, and report any damage to the local DEC slaes office. Inspect as follows:

Step

1

4

### Procedure

Inspect external surfaces of the cabinets and related equipments for surface, bezel, switch, and light damage, etc.

2 Remove the shipping bolts from the rear door, then open the rear door of the cabinet, and internally inspect the cabinet for console, processor, and interconnecting cable damage; loose mounting rails, loose or broken modules, blower or fan damage, any loose nuts, bolts, screws, etc.

3 Inspect the wiring side of the logic panels for bent pins, broken wires, loose external components and foreign material.

Inspect the power supply for proper seating of fuses and power connections.

### Procedure

5

Step

Inspect all peripheral equipment for internal and external damage. This includes inspection of magnetic tape and DECtape transport heads, motors, paper-tape sprockets, etc.

### CAUTION

Do not operate any peripheral device which employs motors, tape heads, sprockets, etc., if they appear to be damaged in shipment.

#### 2.3.3 Cabinet Installation

The PDP-11/40 cabinets are provided with roll-around casters and adjustable leveling feet. It is not necessary to bolt the cabinet to the mounting floor unless conditions indicate otherwise (e.g., shipboard installation). Cabinet installation procedures are as follows:

#### NOTE

In multiple cabinet installation, receiving restrictions may necessitate shipping cabinets individually or in pairs. In such cases the cabinets are connected at the installation site.

Step

1

#### Procedure

With the cabinets positioned in the room, install H952-GA filler strips between cabinet groups (filler strips are shipped attached to the end of a cabinet group). Remove 4 bolts each from the front and rear filler strips. Butt the cabinet groups together while holding the filler strips in place and rebolt through both cabinets and the filler strips (see Drawing C-UA-H952-G-O). Do not tighten the bolts securely at this time.

- 2 Lower the leveling feet so that the cabinet(s) are not resting on the roll-around casters but are supported on the leveling feet.

- 3 Use a spirit level to level all cabinets and ensure that all leveling feet are firm against the floor.

- 4 Tighten the bolts that secure the cabinet groups together and then recheck the cabinet leveling. Again ensure that all leveling feet are planted firmly on the floor

- 5 Remove the shipping bracket that secures the extendable BA11-FC Mounting Box in the cabinet.

2.3.4 Ac Power Connections

A 3-wire cable is used to connect the site source power to the power control in the top of the H960-C cabinet (see Figure 2-1 for connector type). The cable is connected at the factory for either 230V, 50 Hz or 115V, 60 Hz operation. Most cabinets in a PDP-11/40 system include a power control and a single ac power cab le; power is distributed within the cabinet from the power control.

Power cables are intended to be connected to a site power system that provides ac power on a single-phase, 2-wire plus ground system. One of the two wires should maintain a constant (neutral) voltage, while the supply voltage is developed on the other (phase) wire.

The cabinets should be grounded to an earth ground, with ground straps connecting all the cabinets to each other. In addition, the frame ground wire in each power cable connects the cabinet ground system to the site power system ground.

The power controls in all the cabinets are connected together to provide a central control of power turn-on and turn-off. These connections require that the phase of the voltage supplied to each power control be the same as the phase of the voltage supplied to all other power controls in the same system.

Before connecting any power cables to the site source power, check all customer wiring. Ensure that power receptacles of the appropriate types have been provided for each cabinet, and that the receptacles are positioned close enough to the cabinet positions to allow connecting the cables without stretching or crossing the cables. In particular, check that the phase and neutral wires have been connected to the same pins in each receptacle, so that all cabinet power controls receive the same voltage phase.

Å

2.3.5 Intercabinet Connections

When a multi-cabinet system is assembled, three types of electrical connections must be made between cabinets (see Paragraph 2.3.3 for mechanical connections). These connections are:

- a. Unibus connections a BC11-A cable must connect the last system unit in a cabinet to the first system unit in the next cabinet.

- b. Remote power connections all cabinet power controls are connected to a 3-wire control bus that provides for system turn-on and turn-off, and

- c. Ground strapping the frame ground of the system is distributed through the cabinets by direct electrical connections between the cabinet frames.

2.3.5.1 Unibus Connections - To connect the Unibus between the H960-C cabinet and an H960-D Expansion Cabinet, insert the BC11-A cable in the rear system unit slot of the BA11-FC mounting box of the H960-C Cabinet. The cable then runs through a cable clamp in the upper left corner at the rear of the BA11-FC mounting box, and is passed under the power supply mounting rails into the next cabinet. In the H960-D cabinet, the cable passes through a similar cable clamp, and is inserted in the appropriate slot of the first system unit of the mounting box. The BA11-FC is noted above as an example, other mounting boxes might be the last box. 2.3.5.2 Remote Power Connections - Each cabinet in the system has one 860 power control. All the power controls are connected by a 3-wire bus that carries a remote turn-on signal, an emergency turn-off signal, and a control ground; there are three Mate-N-Lok connectors on each power control for the 3-wire bus. A cable is supplied with each cabinet to connect the power control of that cabinet to the next cabinet. Because each 860 power control must be capable of connecting to the 860 power controls in the preceding and following cabinets, two Mate-N-Lok connectors are reserved for the intercabinet cables. A third connector is provided for connection to the on/off switch, the thermal switch, or other emergency shut-off devices within the cabinet. 2.3.5.3 Ground Strapping - Electrical safety is provided by connecting all the cabinet frames to the ground level of the site power system. This is done by connecting a wire in each power cable between the frame and the power system ground; this is not a load carrying wire, and is intended only as an emergency ground path. The green wire in each power cable is the frame ground, while the white wire is the neutral, or return wire, that carries the load current.

To improve the level of safety provided by the frame ground connections, all cabinet frames are connected by braided copper straps of 4 AWG solid wire with crimp-on lugs, which are fastened to copper studs that are welded to the frames (this also prevents the generation of ground loops between cabinets that are connected by signal-carrying cables). The studs are welded to the bottom side rails of the cabinet frame, facing inward; the stud on the left side of the cabinet is slightly forward of center while the stud on the right side is slightly to the rear.

The ground strap supplied with each cabinet is fastened to one stud, passed over the side rail of that cabinet and the side rail of the adjacent cabinet, and fastened to the stud in that cabinet. The copper studs are threaded, and nuts are supplied on the studs.

ji.

2.3.6 Remote Peripheral Interconnection

Installation instructions for remote peripherals, such as line printers, card readers, and magnetic tape units, are covered in the appropriate peripheral maintenance manual. Normally, the peripheral itself is a free-standing unit and the peripheral controller is mounted in one of the system drawers. The controller and peripheral must be interconnected and the peripheral must also be connected to an ac power source.

In a basic PDP-11/40 System, there is a small peripheral controller mounting slot that houses the controller for the system input/output device (LA30 DECwriter or Teletype Unit). This device is characteristic of remote peripherals installation.

When installing the system, it is necessary to interconnect the system and the input/output device (Teletype or DECwriter) as described in the following steps:

Step

1

#### Procedure

Place the freestanding DECwriter or Teletype in the desired position next to the system cabinet.

#### Procedure

Run the control cable from the DECwriter or Teletype unit through the back of the system cabinet and through the cable clamp at the rear of the mounting box. Note that, because of the size of the control cable connector, the cable clamp must first be removed before the connector is brought into the box. Once this is done, the clamp can be replaced.

- 3 Connect the control cable connector to the receptacle on the controller (DL11, KL11, or LC11) mounted in the small peripheral controller slot of the processor.

- 4 Verify that the controller module is plugged securely into the small controller slot.

- 5 Connect the power cable from the DECwriter or Teletype unit into one of the cabinet power receptacles.

2

### 2.3.7 Installation Verification

Prior to turning power on, proper installation of all processor internal options and memory should be verified. Although memory and processor options are installed in the system at the factory, installation should be verified at the site.

Installation verification procedures for the available processor options are given in Table 2-1. Verification procedures for core memory, as well as procedures for installing additional memory, are given in Table 2-2. A diagram of the memory system unit is shown in Figure 2-2.

### Table 2-1

# Option Installation Verification

Option

#### Procedure

KE11-E Extended Instruction1. Verify that KE11-E module M7238Set (EIS) Optionis installed in slot 2 (section)

Verity that KE11-E module M7238 is installed in slot 2 (sections A-F) of processor backplane assembly.

- 2. Ensure that jumper W1 on print K3-8 of KD11-A processor module M7233 (located in slot 5, sections A-F) has been removed.