EK-SBC01-UG-001

# SBC-11/21 Single-Board Computer User's Guide

EK-SBC01-UG-001

# SBC-11/21 Single-Board Computer User's Guide

Prepared by Educational Services of Digital Equipment Corporation

## Copyright © 1982 by Digital Equipment Corporation All Rights Reserved

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

#### Printed in U.S.A.

The manuscript for this book was created on a DIGITAL Word Processing System and, via a translation program, was automatically typeset on DIGITAL's DECset-8000 Typesetting System. Book production was done by Educational Services Development and Publishing in Marlboro, MA.

The following are trademarks of Digital Equipment Corporation:

| DEC          | EduSystem | RSTS    |

|--------------|-----------|---------|

| DECnet       | IAS       | RSX     |

| DECUS        | MASSBUS   | TOPS-10 |

| DECsystem-10 | MINC-11   | TOPS-20 |

| DECSYSTEM-20 | OMNIBUS   | UNIBUS  |

| DECwriter    | OS/8      | VAX     |

| DIBOL        | PDP       | VMS     |

| digital      | PDT       | VT      |

## **CONTENTS**

## PREFACE

## CHAPTER 1 INTRODUCTION

| 1.1   | INTRODUCTION                 | 1-1 |

|-------|------------------------------|-----|

| 1.2   | SPECIFICATIONS               |     |

| 1.2.1 | Physical                     | 1-3 |

| 1.2.2 | Power Requirements           | 1-3 |

| 1.2.3 | Bus Loading                  | 1-3 |

| 1.2.4 | Environmental                | 1-4 |

| 1.3   | BACKPLANE PIN IDENTIFICATION | 1-4 |

| 1.4   | RELATED DOCUMENTS            | 1-7 |

## CHAPTER 2 INSTALLATION

| 2.1     | INTRODUCTION                       | 2-1  |

|---------|------------------------------------|------|

| 2.2     | SELECTING OPERATIONAL FEATURES     | 2-1  |

| 2.2.1   | Battery Backup                     | 2-1  |

| 2.2.2   | Wake Up Circuit                    | 2-8  |

| 2.2.3   | Starting Address                   | 2-8  |

| 2.2.4   | Interrupts                         | 2-8  |

| 2.2.5   | Parallel I/O                       | 2-11 |

| 2.2.6   | Serial I/O                         | 2-12 |

| 2.2.7   | Memories                           | 2-16 |

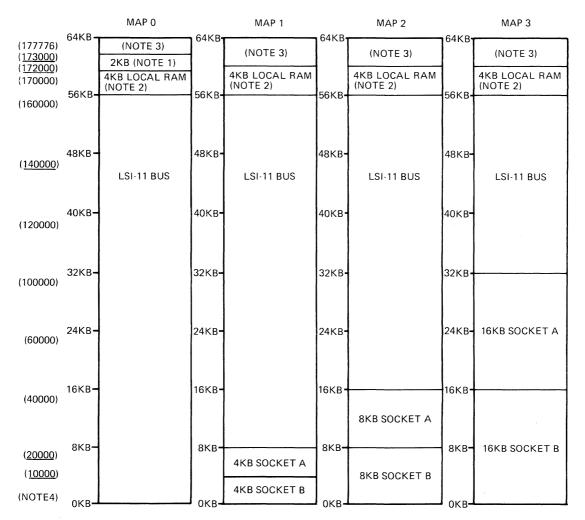

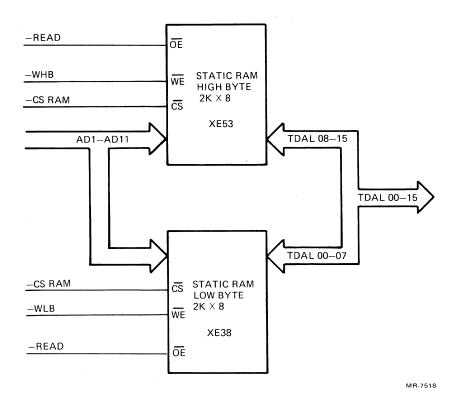

| 2.2.7.1 | Memory Maps                        | 2-16 |

| 2.2.7.2 | PROMs/EPROMs                       | 2-16 |

| 2.2.7.3 | RAMs                               |      |

| 2.3     | SELECTING BACKPLANES AND OPTIONS   | 2-22 |

| 2.4     | POWER SUPPLY                       | 2-22 |

| 2.5     | EXTERNAL CABLES                    | 2-22 |

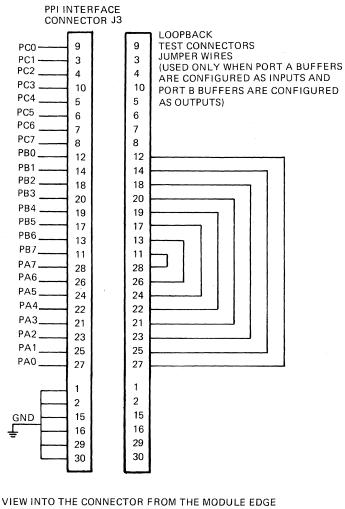

| 2.5.1   | Parallel I/O Interface (J3)        | 2-23 |

| 2.5.2   | Serial Line Interfaces (J1 and J2) | 2-25 |

| 2.6     | VERIFYING OPERATION                | 2-28 |

| 2.6.1   | Macro-ODT Option                   | 2-28 |

| 2.6.2   | Loopback Connectors                |      |

| 2.6.3   | Verification Procedure             | 2-28 |

|         |                                    |      |

## CHAPTER 3 OPTIONS

| 3.1 | INTRODUCTION        | 3-1 |

|-----|---------------------|-----|

| 3.2 | SUPPORTED OPTIONS   | 3-1 |

| 3.3 | UNSUPPORTED OPTIONS | 3-4 |

## Page

## CHAPTER 4 MACRO-ODT

| 4.1        | INTRODUCTION                               | 4-1  |

|------------|--------------------------------------------|------|

| 4.2        | INSTALLATION AND CONFIGURATION             | 4-1  |

| 4.3        | ENTRY CONDITIONS                           | 4-1  |

| 4.3.1      | Macro-ODT Input Sequence                   | 4-1  |

| 4.3.2      | Macro ODT Output Sequence                  | 4-1  |

|            | Macro-ODT Output Sequence                  |      |

| 4.4        | MACRO-ODT COMMANDS                         | 4-2  |

| 4.4.1      | /(ASCII 057) Slash                         | 4-2  |

| 4.4.2      | <cr> (ASCII 15) Carriage Return</cr>       | 4-5  |

| 4.4.3      | <lf> (ASCII 12) Line Feed</lf>             | 4-5  |

| 4.4.4      | R (ASCII 122) Internal Register Designator | 4-5  |

| 4.4.5      | S (ASCII 123) Processor Status Word (PSW)  | 4-6  |

| 4.4.6      | G (ASCII 107) Go                           | 4-6  |

| 4.4.7      | P (ASCII 120) Proceed                      | 4-6  |

| 4.4.8      | DD, DX, DY Bootstraps                      | 4-6  |

| 4.4.9      | V (A SCIL 120) Disgraphics                 | 4-8  |

|            | X (ASCII 130) Diagnostics                  |      |

| 4.5        | INITIALIZATION                             | 4-8  |

| 4.6        | WARNINGS AND PROGRAMMING HINTS             | 4-8  |

| 4.6.1      | Error Decoding                             | 4-8  |

| 4.6.2      | ODT Stack Warning                          | 4-8  |

| 4.6.3      | Addresses to Avoid                         | 4-8  |

| 4.6.4      | CPU Priority                               | 4-8  |

| 4.6.5      | Terminal Related Problems                  | 4-8  |

| 4.6.6      | Spurious Halts                             | 4-8  |

| 4.6.7      |                                            | 4-9  |

|            | Serial I/O Protocol                        |      |

| 4.6.8      | Interrupt Vector Initialization            | 4-9  |

| CHAPTER 5  | SYSTEM ARCHITECTURE                        |      |

| <b>c</b> 1 |                                            | 2.1  |

| 5.1        | INTRODUCTION.                              | 5-1  |

| 5.2        | MICROPROCESSOR ARCHITECTURE                | 5-1  |

| 5.2.1      | Registers                                  | 5-1  |

| 5.2.1.1    | General Registers                          | 5-1  |

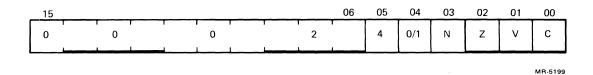

| 5.2.1.2    | Status Register                            | 5-1  |

| 5.2.2      | Hardware Stack                             | 5-2  |

| 5.2.3      | Interrupts                                 | 5-2  |

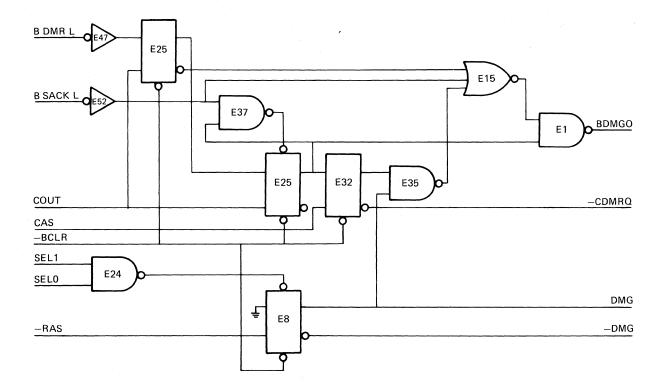

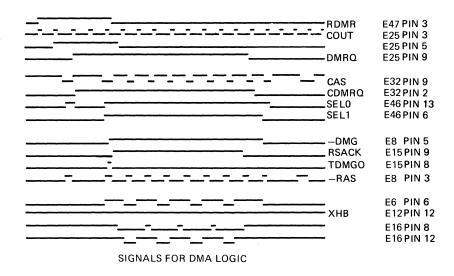

| 5.3        | DMA (DIRECT MEMORY ACCESS)                 | 5-4  |

| 5.4        | MEMORY ORGANIZATION                        | 5-4  |

|            |                                            |      |

| 5.5        | POWER-UP/POWER-DOWN FACILITY               | 5-4  |

| CHAPTER 6  | PROGRAMMING INFORMATION                    |      |

| 6.1        | INTRODUCTION                               | 6-1  |

| 6.2        | ASYNCHRONOUS SERIAL LINE UNITS             |      |

|            |                                            |      |

| 6.2.1      | Data Baud Rates                            | 6-1  |

| 6.2.2      | Interrupts                                 |      |

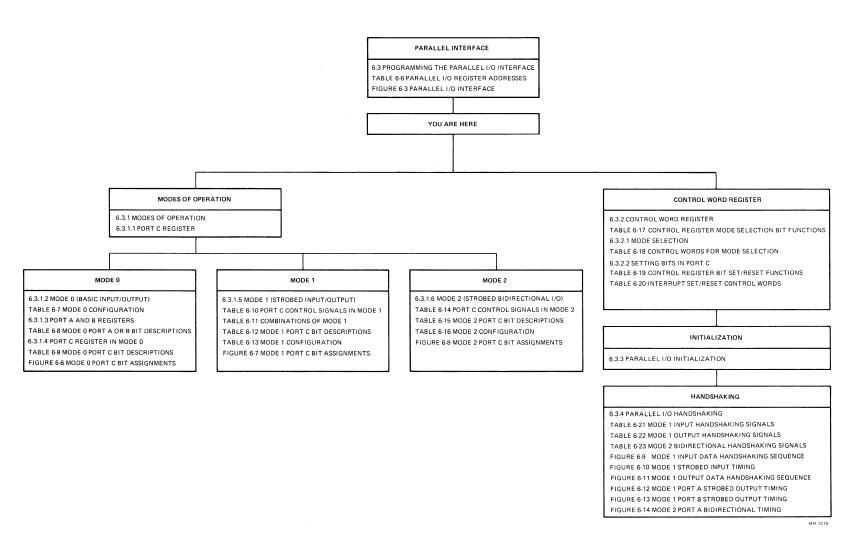

| 6.3        | PROGRAMMING THE PARALLEL I/O INTERFACE     |      |

| 6.3.1      | Modes of Operation                         | 6-7  |

| 6.3.1.1    | Port C Register                            | 6-10 |

| 6.3.1.2   | Mode 0 Basic Input/Output                              |      |

|-----------|--------------------------------------------------------|------|

| 6.3.1.3   | Port A and B Registers                                 | 6-11 |

| 6.3.1.4   | Port C Register in Mode 0                              | 6-11 |

| 6.3.1.5   | Mode 1 (Strobed Input/Output)                          | 6-11 |

| 6.3.1.6   | Mode 2 (Strobed Bidirectional I/O)                     | 6-18 |

| 6.3.2     | Control Word Register                                  |      |

| 6.3.2.1   | Mode Selection                                         |      |

| 6.3.2.2   | Setting Bits in Port C                                 |      |

| 6.3.3     | Parallel I/O Initialization                            |      |

| 6.3.4     | Parallel I/O Handshaking                               |      |

| CHAPTER 7 | ADDRESSING MODES AND INSTRUCTION SET                   |      |

| 7.1       | INTRODUCTION                                           | 7-1  |

| 7.2       | ADDRESSING MODES                                       |      |

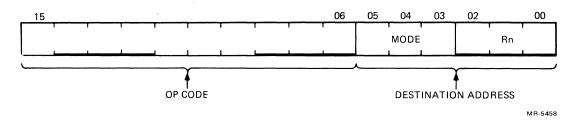

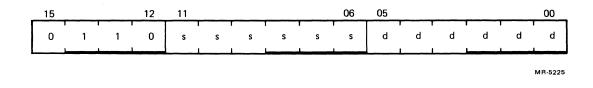

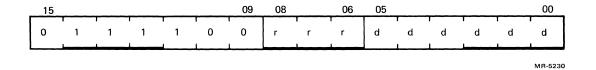

| 7.2.1     | Single Operand Addressing                              |      |

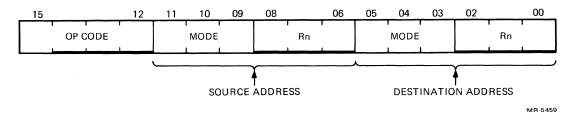

| 7.2.2     | Double Operand Addressing                              | 7-3  |

| 7.2.3     | Direct Addressing                                      | 7-5  |

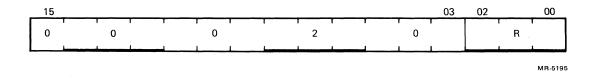

| 7.2.3.1   | Register Mode (Mode 0)                                 | 7-6  |

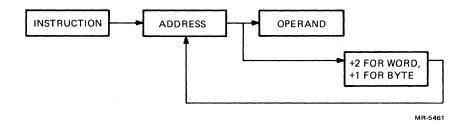

| 7.2.3.2   | Autoincrement Mode (Mode 2)                            | 7-8  |

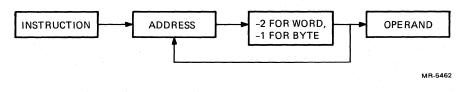

| 7.2.3.3   | Autodecrement Mode (Mode 2)                            |      |

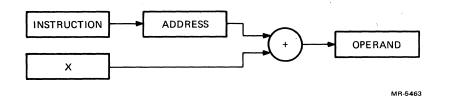

| 7.2.3.4   | Index Mode (Mode 6)                                    |      |

| 7.2.4     | Deferred (Indirect) Addressing                         |      |

| 7.2.5     | Use of the PC as a General-Purpose Register            |      |

| 7.2.5.1   | Immediate Mode                                         |      |

| 7.2.5.2   |                                                        |      |

| 7.2.5.3   | Absolute Addressing                                    |      |

| 7.2.5.4   | Relative Addressing                                    |      |

|           | Relative Deferred Addressing                           |      |

| 7.2.6     | Use of the Stack Pointer as a General-Purpose Register |      |

| 7.3       | INSTRUCTION SET                                        |      |

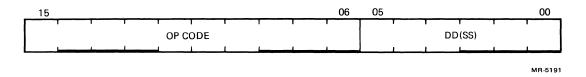

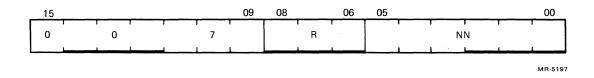

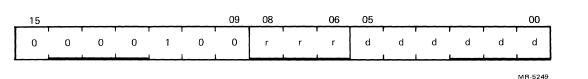

| 7.3.1     | Instruction Formats                                    |      |

| 7.3.2     | List of Instructions.                                  |      |

| 7.3.3     | Single Operand Instructions                            |      |

| 7.3.3.1   | General                                                |      |

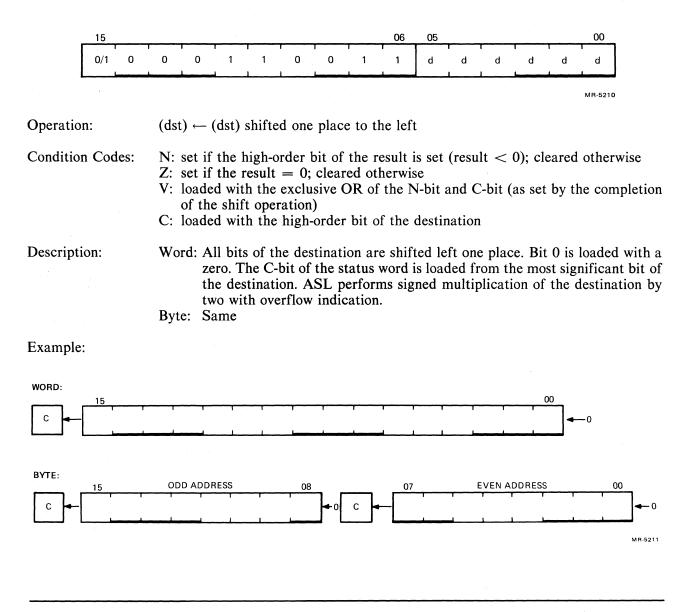

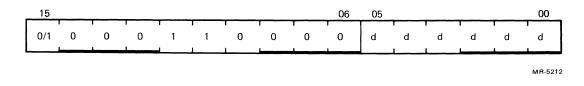

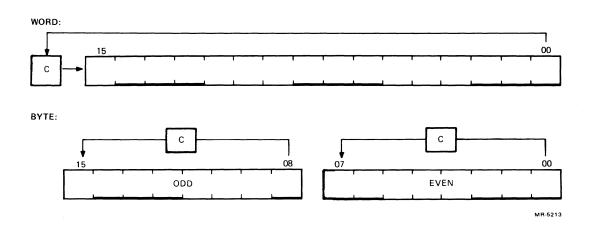

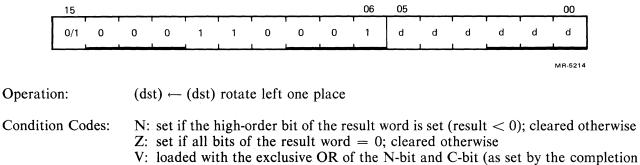

| 7.3.3.2   | Shifts and Rotates                                     |      |

| 7.3.3.3   | Multiple Precision                                     |      |

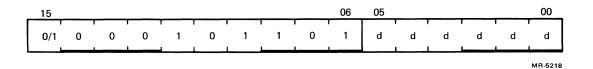

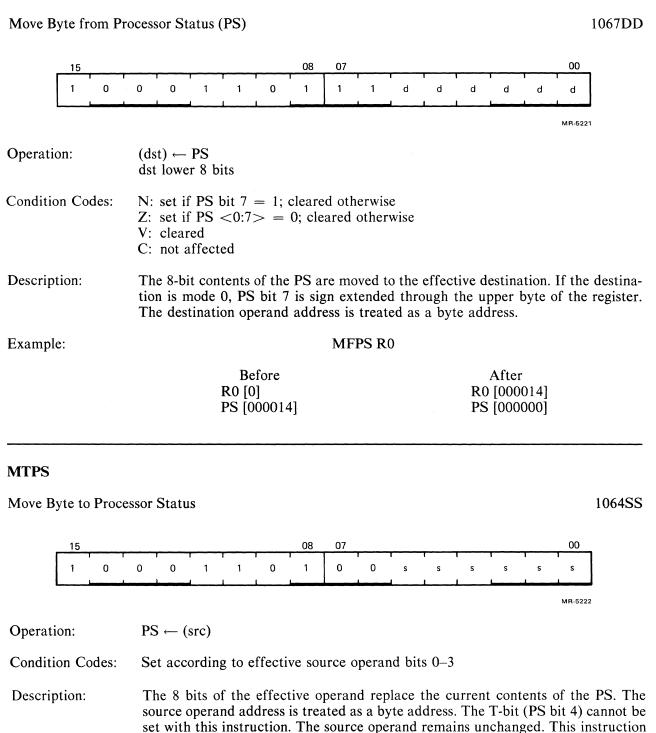

| 7.3.3.4   | PS Word Operators                                      |      |

| 7.3.4     | Double Operand Instructions                            | 7-41 |

| 7.3.4.1   | General                                                |      |

| 7.3.4.2   | Logical                                                |      |

| 7.3.5     | Program Control Instructions                           |      |

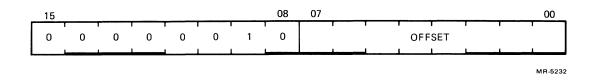

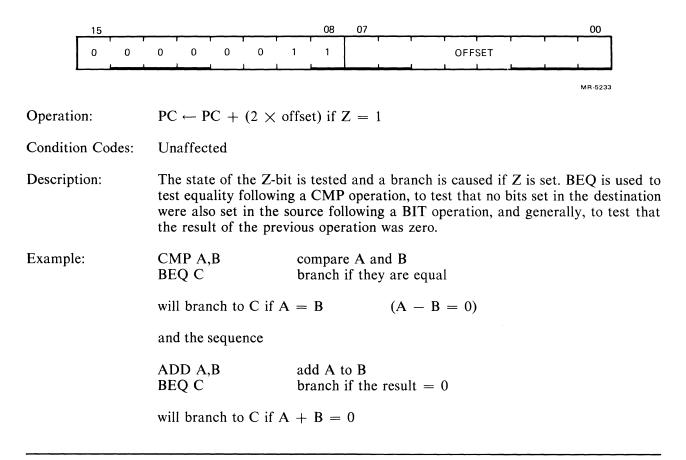

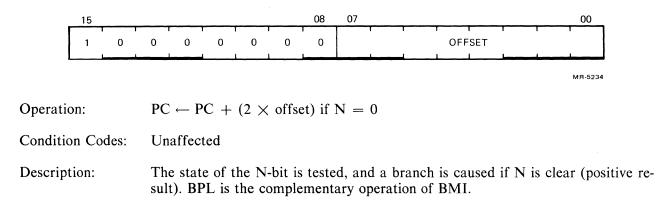

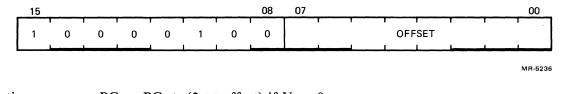

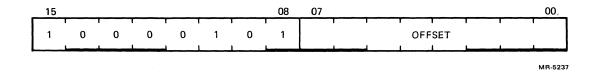

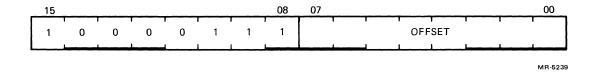

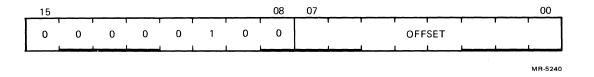

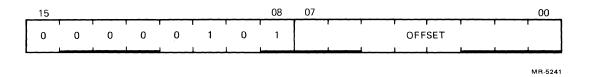

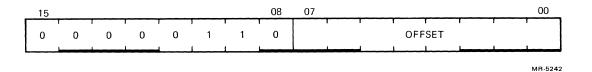

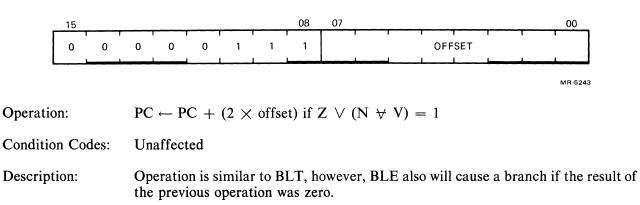

| 7.3.5.1   | Branches                                               |      |

| 7.3.5.2   | Signed Conditional Branches                            |      |

| 7.3.5.3   | Unsigned Conditional Branches                          |      |

| 7.3.5.4   | Jump and Subroutine Instructions                       |      |

| 7.3.5.5   | Traps                                                  |      |

| 7.3.5.6   | Reserved Instruction Traps                             | 7-65 |

| 7.3.5.7   | HALT Interrupt                                         | 7-65 |

| 7.3.5.8   | Trace Trap                                             |      |

| 7.3.5.9   | Power Failure Interrupt                                | 7-65 |

## Page

| 7.3.5.10  | Interrupts                          | 7-65 |

|-----------|-------------------------------------|------|

| 7.3.5.11  | Special Cases (T-bit)               |      |

| 7.3.6     | Miscellaneous Instructions          |      |

| 7.3.7     | Condition Code Operators            |      |

| CHAPTER 8 | THEORY OF OPERATION                 |      |

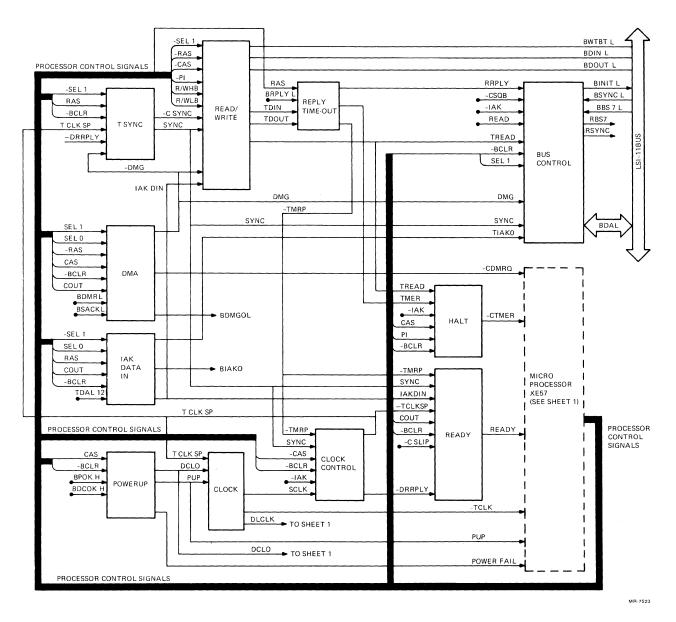

| 8.1       | INTRODUCTION                        | 8-1  |

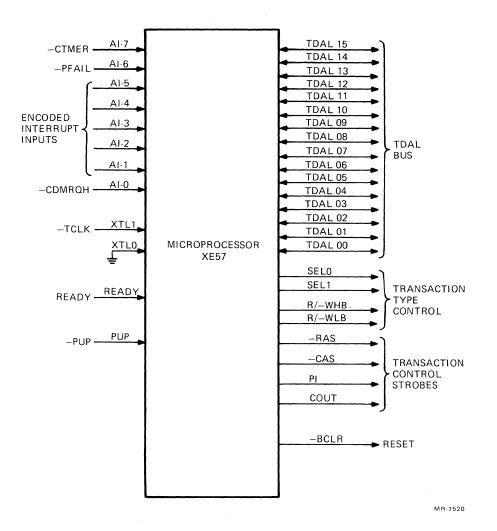

| 8.2       | MICROPROCESSOR                      | 8-1  |

| 8.2.1     | Microprocessor Initialization       | 8-1  |

| 8.2.1.1   | RESET Instruction                   | 8-4  |

| 8.2.1.2   | Power-up Input (PUP)                |      |

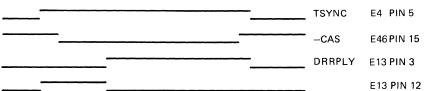

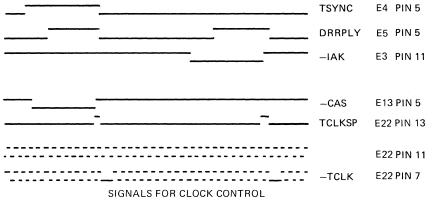

| 8.2.2     | Clock Input (– TCLK).               | 8-5  |

| 8.2.3     | Ready Input (READY)                 | 8-5  |

| 8.2.4     | Microprocessor Control Signals      |      |

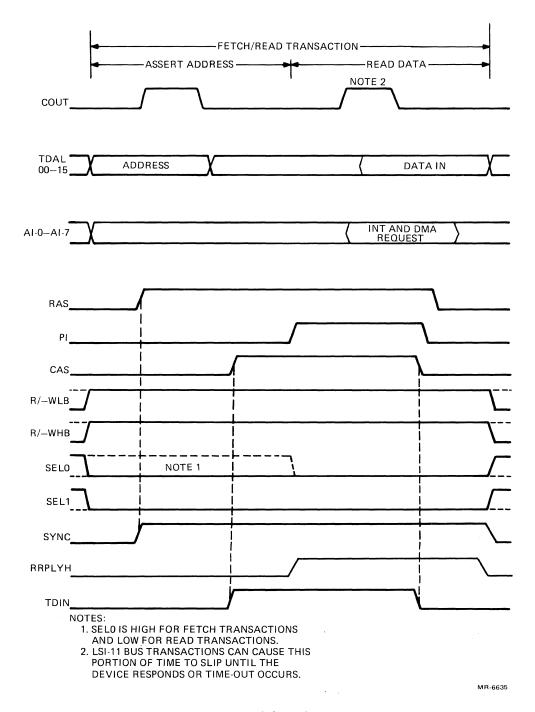

| 8.2.4.1   | Row Address Strobe (RAS)            | 8-5  |

| 8.2.4.2   | Column Address Strobe (CAS)         | 8-5  |

| 8.2.4.3   | Priority In (PI)                    |      |

| 8.2.4.4   | Read/Write $(R/-WHB$ and $R/-WLB$ ) |      |

| 8.2.4.5   | Select Output Flags (SEL0 and SEL1) | 8-5  |

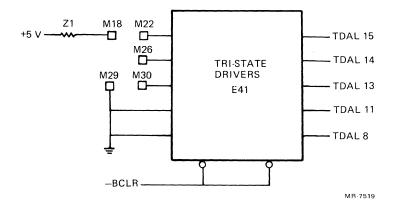

| 8.2.4.6   | Bus Clear (BCLR)                    | 8-6  |

| 8.2.4.7   | Clock Out (COUT)                    | 8-6  |

| 8.2.5     | Microprocessor Transactions         |      |

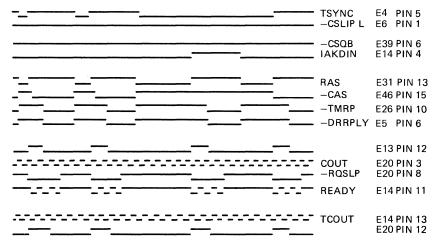

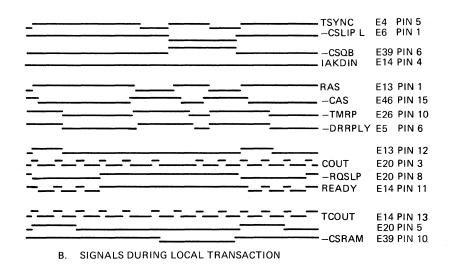

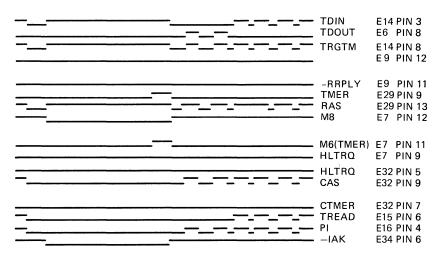

| 8.2.5.1   | Fetch/Read                          | 8-6  |

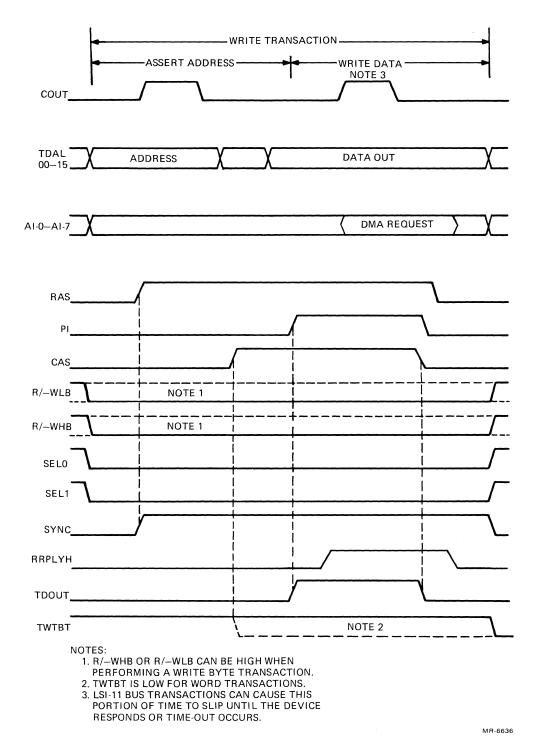

| 8.2.5.2   | Write                               | 8-8  |

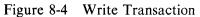

| 8.2.5.3   | IAK                                 | 8-8  |

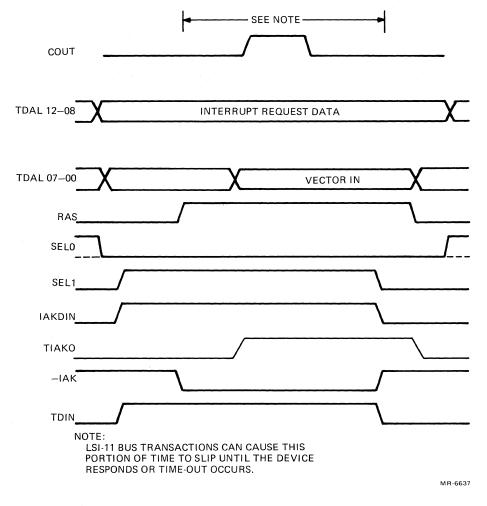

| 8.2.5.4   | DMA                                 | 8-8  |

| 8.2.5.5   | ASPI                                | 8-8  |

| 8.2.5.6   | NOP                                 |      |

| 8.3       | MODE REGISTER CONTROL               |      |

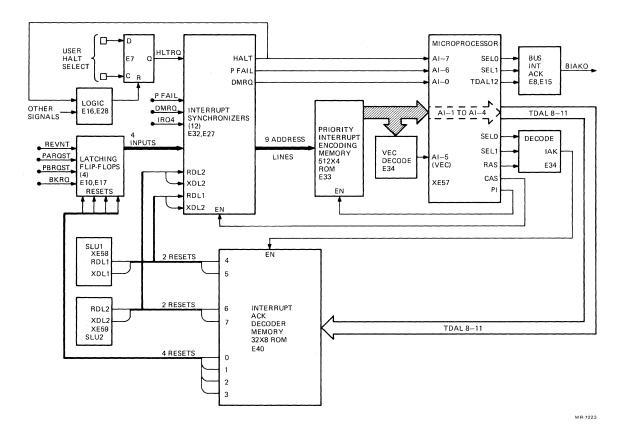

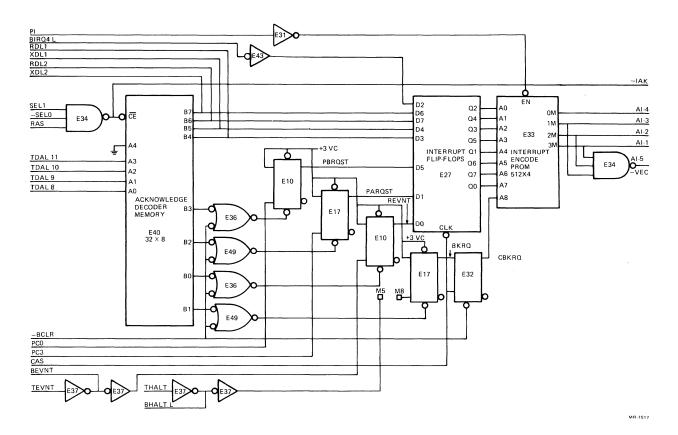

| 8.4       | INTERRUPT CONTROL                   |      |

| 8.4.1     | Interrupt Control Logic             |      |

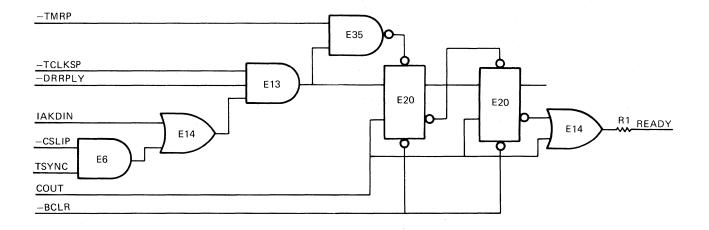

| 8.4.2     | Ready Logic                         |      |

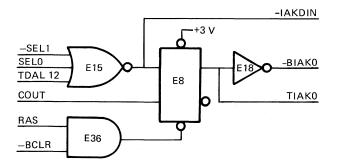

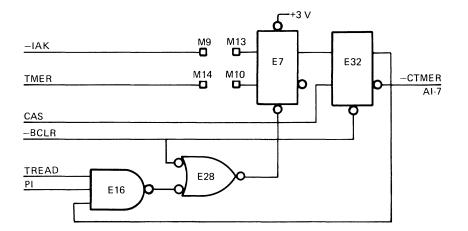

| 8.4.3     | IAK Data In (IAKDIN)                |      |

| 8.4.4     | HALT Interrupt                      |      |

| 8.4.5     | Power Fail (–PFAIL)                 |      |

| 8.4.6     | Local                               |      |

| 8.4.7     | External                            |      |

| 8.4.8     | DMA Interrupt                       |      |

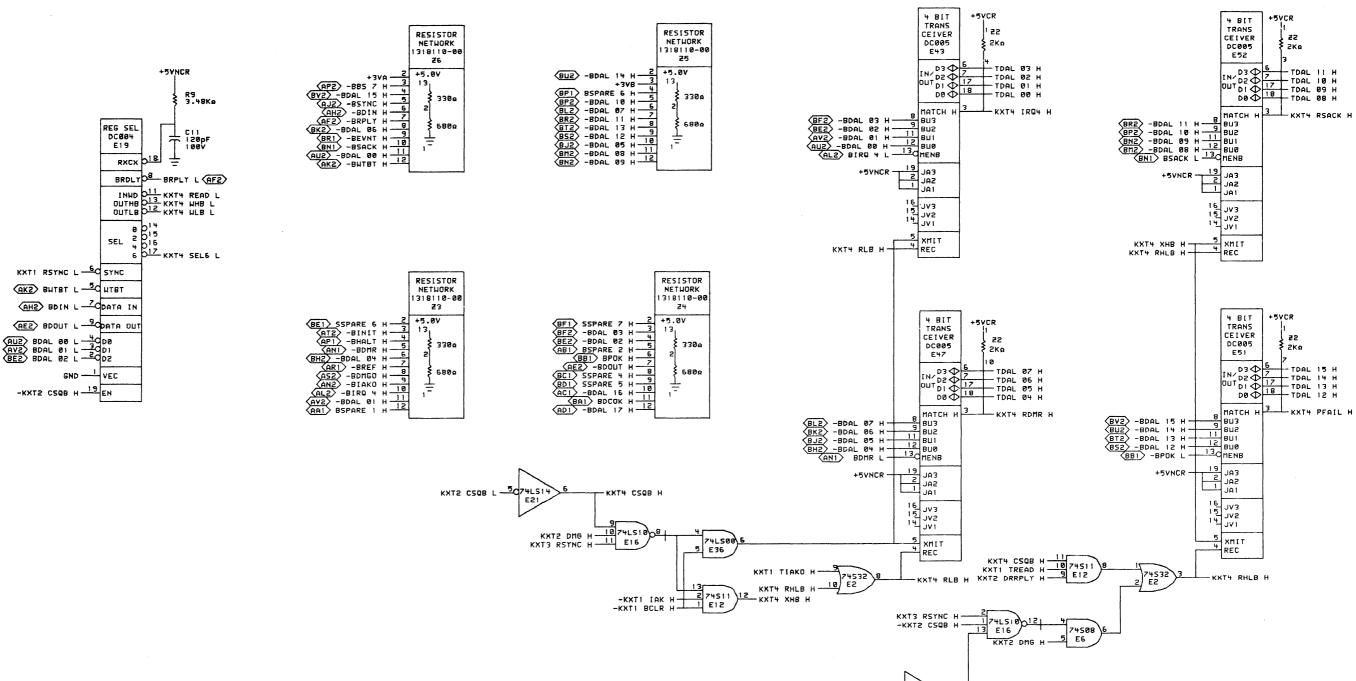

| 8.5       | DC004 PROTOCOL                      |      |

| 8.6       | ADDRESS LATCH                       |      |

| 8.7       | MEMORY ADDRESS DECODE               |      |

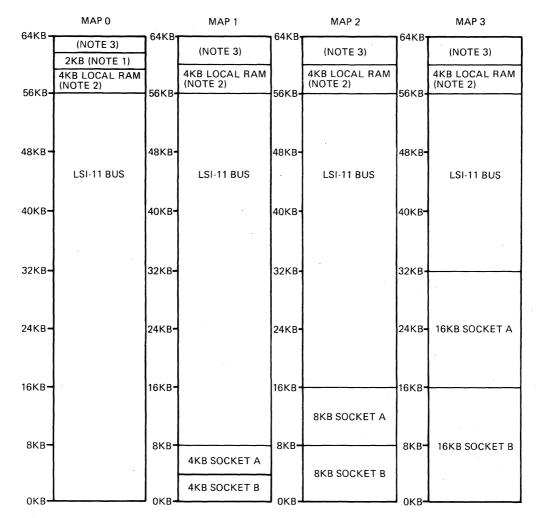

| 8.8       | RAM MEMORY                          |      |

| 8.9       | ROM/RAM MEMORY SOCKETS              |      |

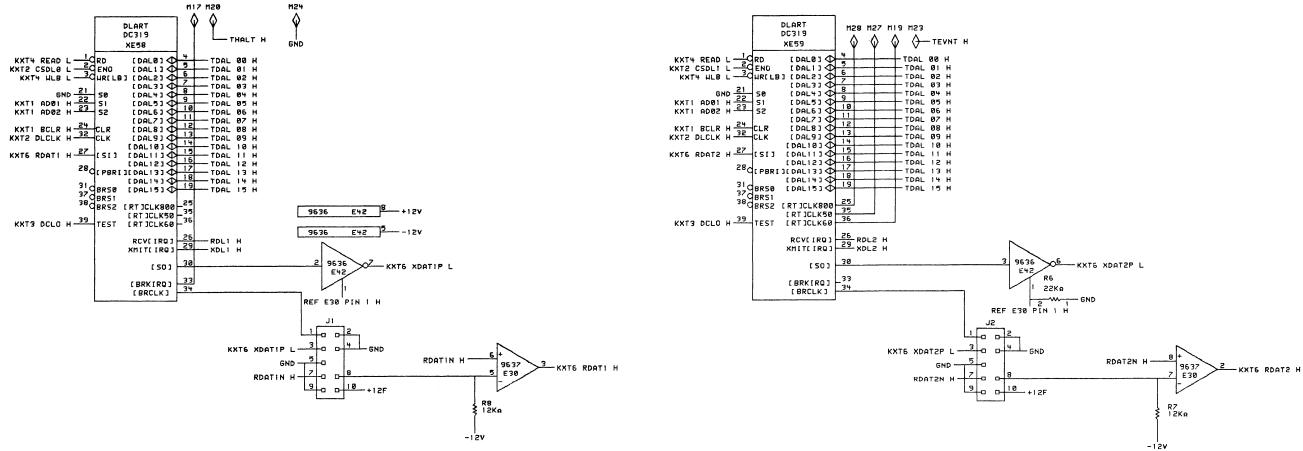

| 8.10      | SERIAL LINE INTERFACE UNITS         |      |

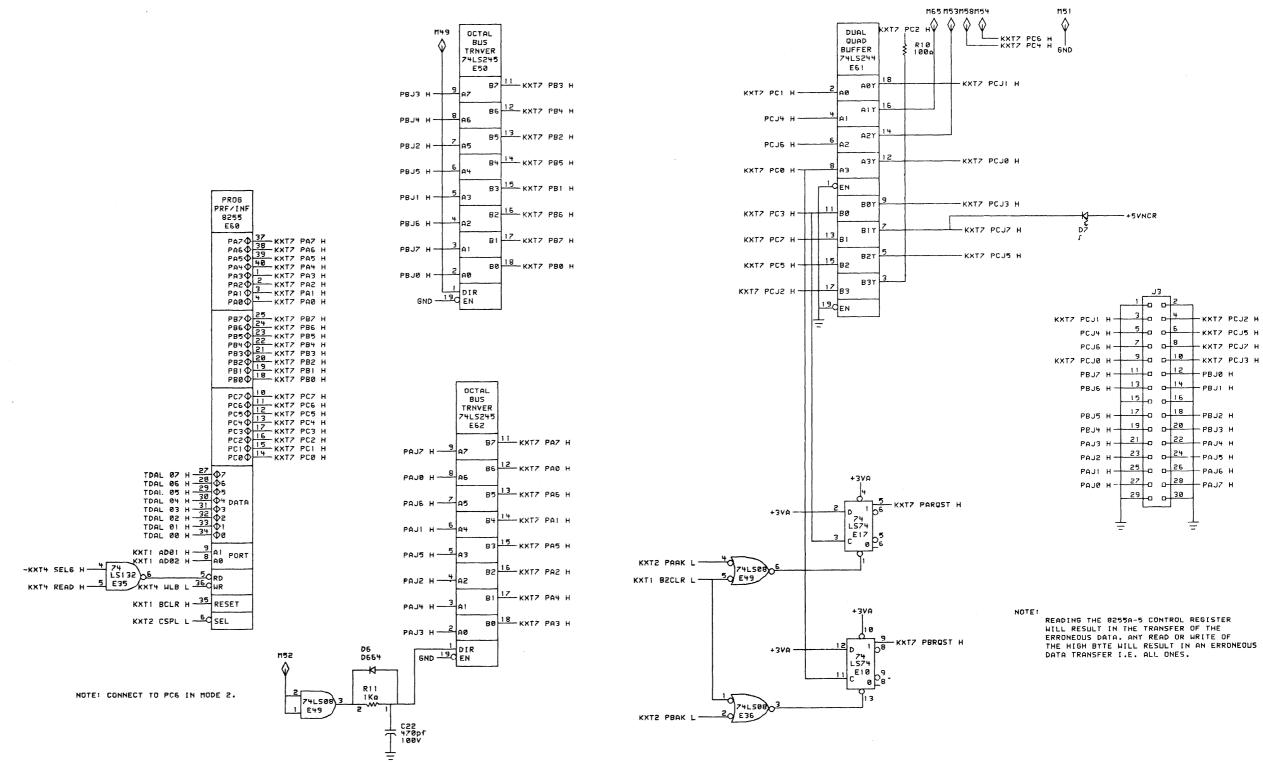

| 8.11      | PARALLEL I/O INTERFACE              |      |

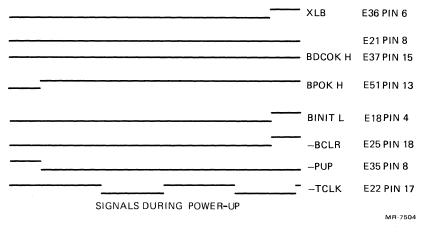

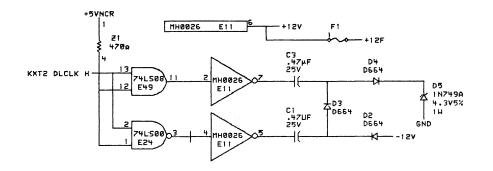

| 8.12      | POWER-UP                            |      |

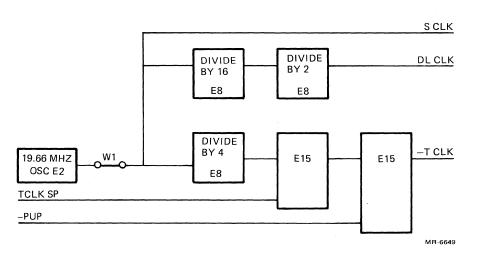

| 8.13      | CLOCK                               |      |

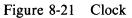

| 8.14      | CLOCK CONTROL                       |      |

| 8.15      | DMA                                 |      |

| 0.10      |                                     | 0-52 |

## Page

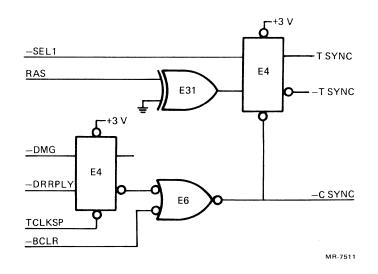

| 8.16 | TSYNC          | 8-35 |

|------|----------------|------|

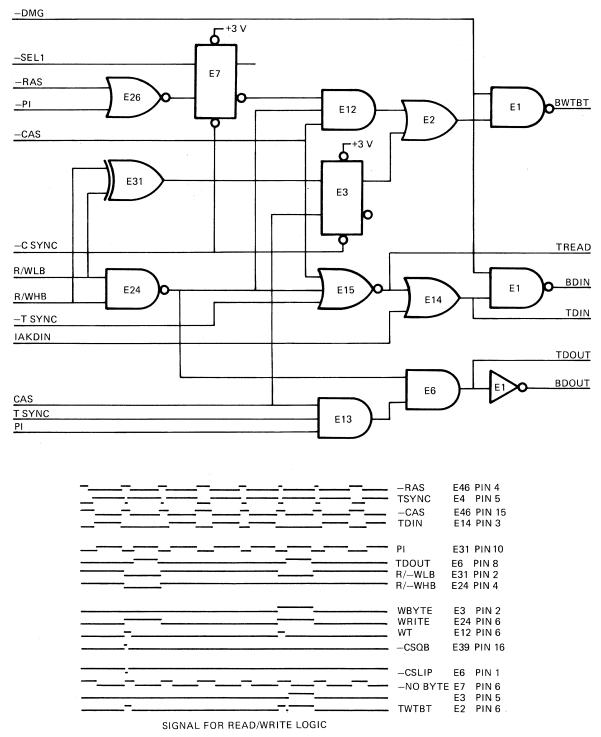

| 8.17 | READ/WRITE     |      |

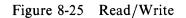

| 8.18 | REPLÝ TIME-OUT | 8-37 |

| 8.19 | BUS CONTROL    | 8-37 |

## CHAPTER 9 LSI-11 BUS

| 9.1   | INTRODUCTION                          |      |

|-------|---------------------------------------|------|

| 9.2   | SBC-11/21 SINGLE-BOARD COMPUTER       |      |

| 9.3   | MASTÉR/SLAVE RELATIONSHIP             |      |

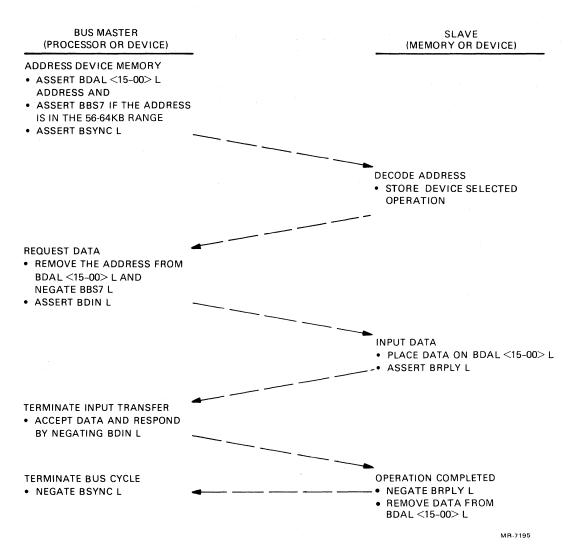

| 9.4   | DATA TRANSFER BUS CYCLES              |      |

| 9.4.1 | Bus Cycle Protocol                    |      |

| 9.4.2 | Direct Memory Access                  |      |

| 9.5   | INTERRUPTS                            |      |

| 9.5.1 | Device Priority                       |      |

| 9.5.2 | Interrupt Protocol                    |      |

| 9.6   | CONTROL FUNCTIONS                     |      |

| 9.6.1 | Halt                                  |      |

| 9.6.2 | Initialization                        |      |

| 9.6.3 | Power Status                          |      |

| 9.6.4 | Power-Up/Power-Down Protocol          |      |

| 9.7   | LSI-11 BUS ELECTRICAL CHARACTERISTICS |      |

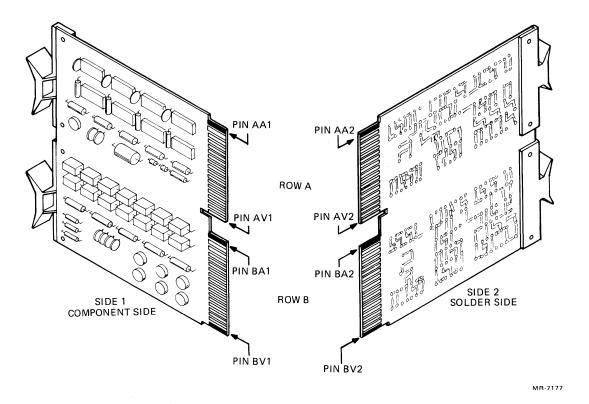

| 9.8   | MODULE CONTACT FINGER IDENTIFICATION  | 9-16 |

- APPENDIX A INSTRUCTION TIMING

- APPENDIX B PROGRAMMING DIFFERENCE LIST

- APPENDIX C SOFTWARE DEVELOPMENT

- APPENDIX D MACRO-ODT ROM

- APPENDIX E SBC-11/21 SCHEMATICS

- APPENDIX F GLOSSARY

- INDEX

## **FIGURES**

## Figure No.

## Title

Page

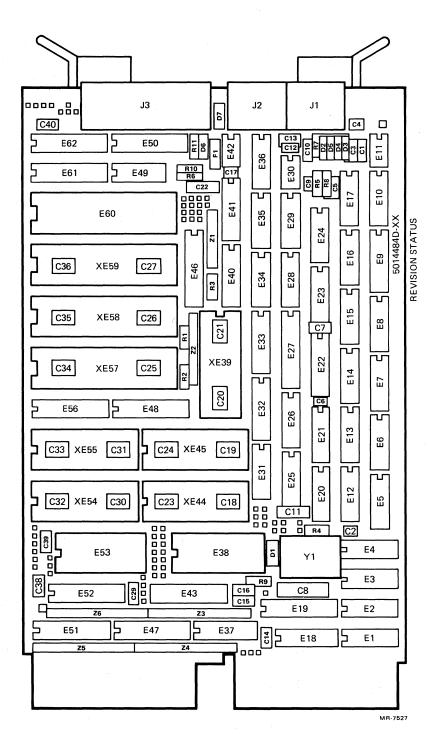

| 1-1 | KXT11-AA (M8063-BA) SBC-11/21 Module             | 1-2  |

|-----|--------------------------------------------------|------|

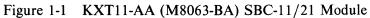

| 2-1 | SBC-11/21 Module Layout                          | 2-2  |

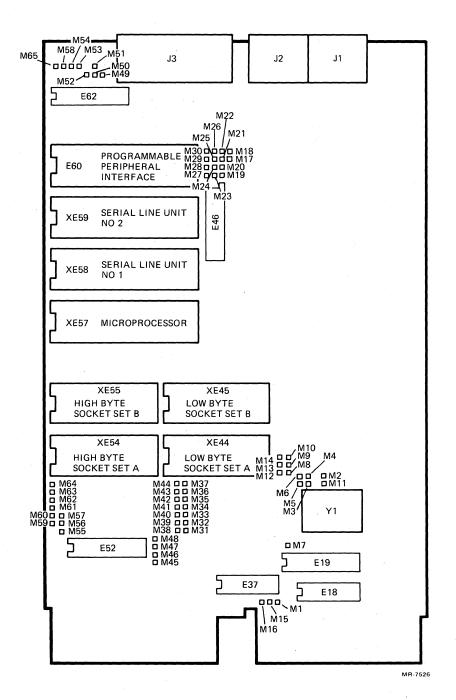

| 2-2 | Interrupt Configurations                         |      |

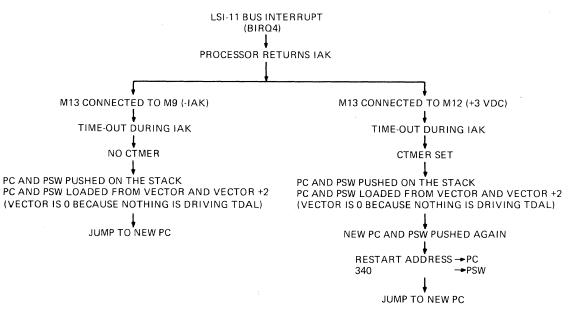

| 2-3 | Time-out During LSI-11 Bus Interrupt Acknowledge | 2-11 |

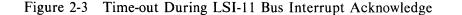

| 2-4 | Parallel I/O Configuration                       | 2-12 |

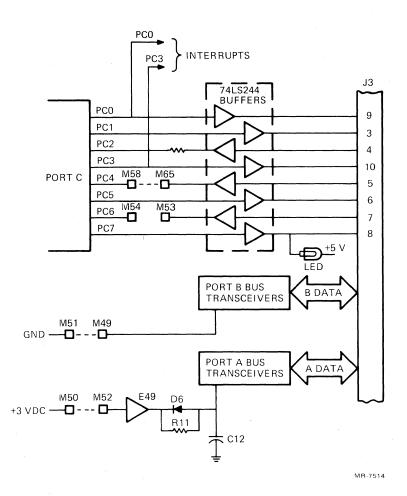

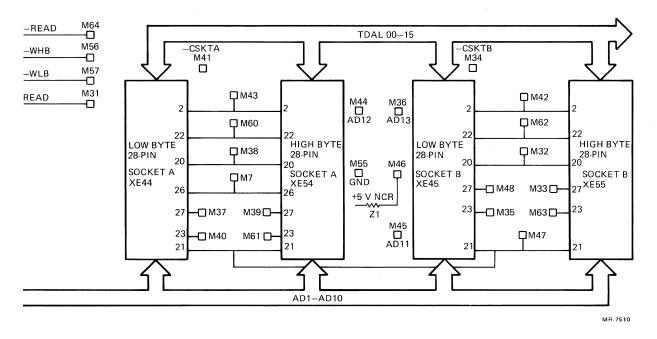

| 2-5 | Socket Sets A and B Interconnection              | 2-17 |

| 2-6 | Memory Configuration                             | 2-18 |

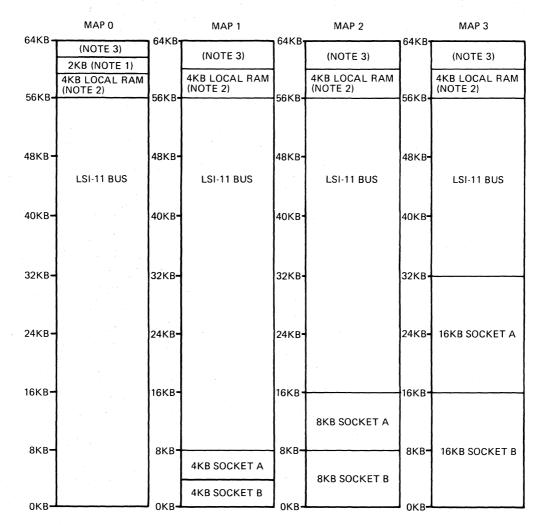

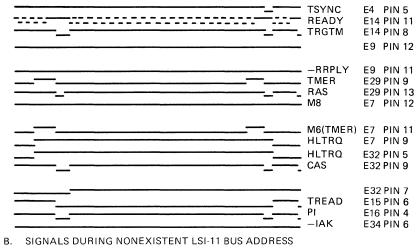

| 2-7 | Memory Maps                                      | 2-19 |

# FIGURES (Cont)

| Figure No. | Title                                   | Page   |

|------------|-----------------------------------------|--------|

| 2-8        | 30-Pin Parallel I/O Connector           | . 2-24 |

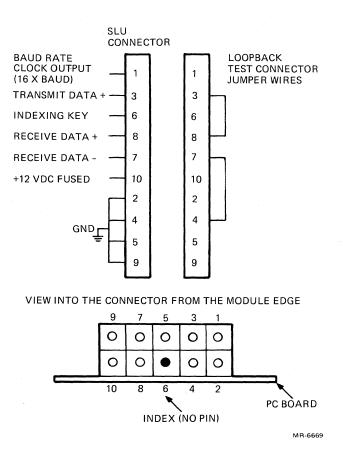

| 2-9        | 10-Pin Serial Line Unit Connector       |        |

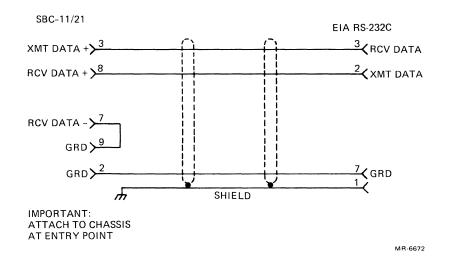

| 2-10       | BC20N-05 Null Modem Cable               |        |

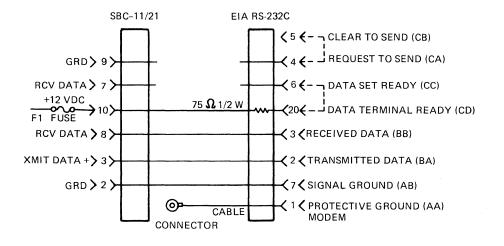

| 2-11       | BC21B-05 Modem Cable                    |        |

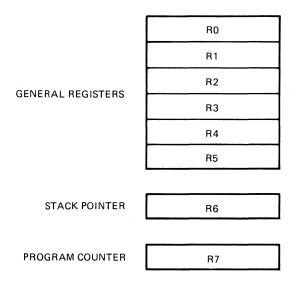

| 5-1        | Registers and Processor Status Word     |        |

| 5-2        | Memory Maps                             |        |

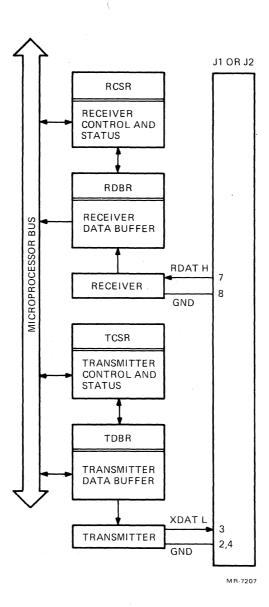

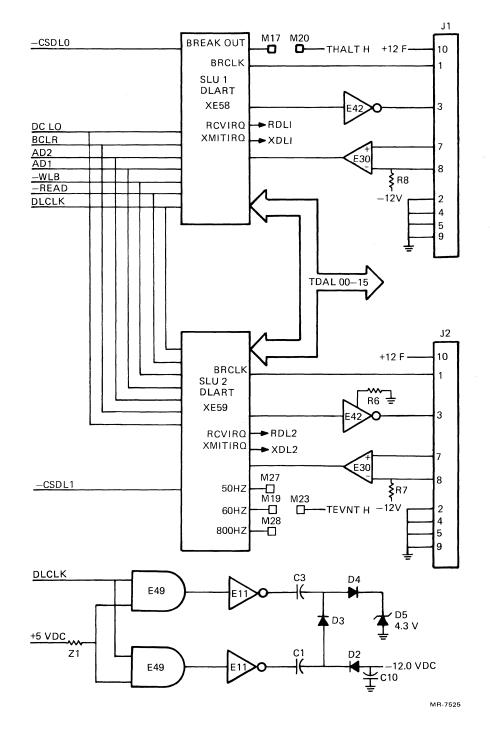

| 6-1        | Serial Line Unit (SLU) Interface        | . 6-2  |

| 6-2        | Serial Line Unit Register Bit Maps      | . 6-3  |

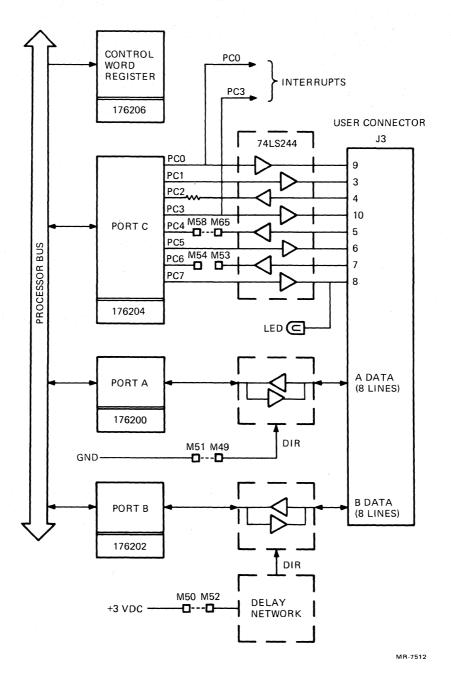

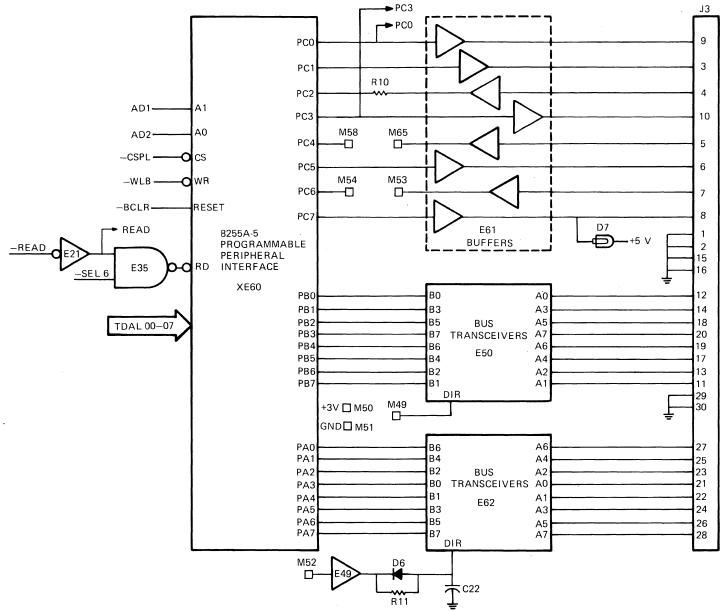

| 6-3        | Parallel I/O Interface                  |        |

| 6-4        | Parallel I/O Flowchart                  | . 6-9  |

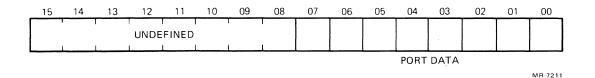

| 6-5        | Mode 0 Port A or B Bit Assignments      | . 6-11 |

| 6-6        | Mode 0 Port C Bit Assignments           | . 6-12 |

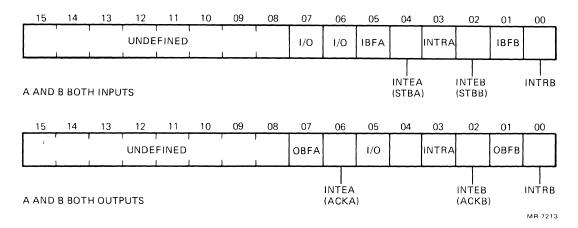

| 6-7        | Mode 1 Port C Bit Assignments           | . 6-15 |

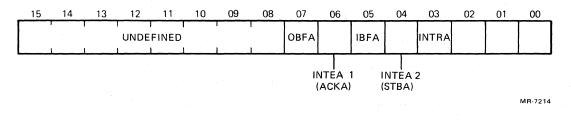

| 6-8        | Mode 2 Port C Bit Assignments           | . 6-20 |

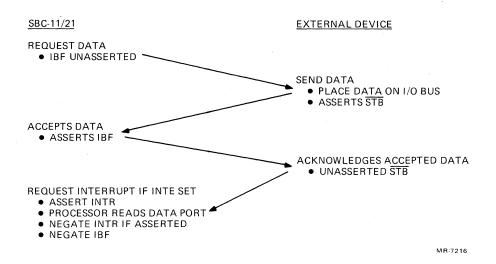

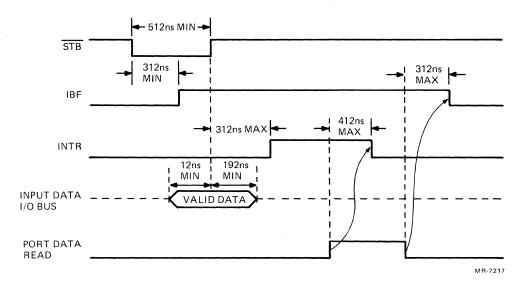

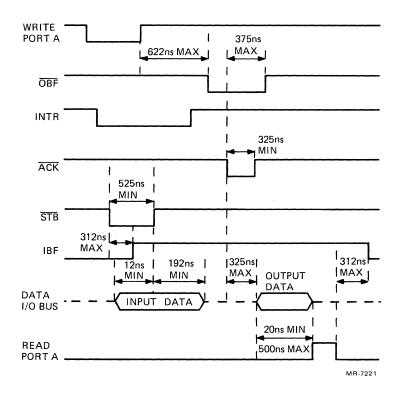

| 6-9        | Mode 1 Input Data Handshaking Sequence  | 6-26   |

| 6-10       | Mode 1 Strobed Input Timing             | . 6-26 |

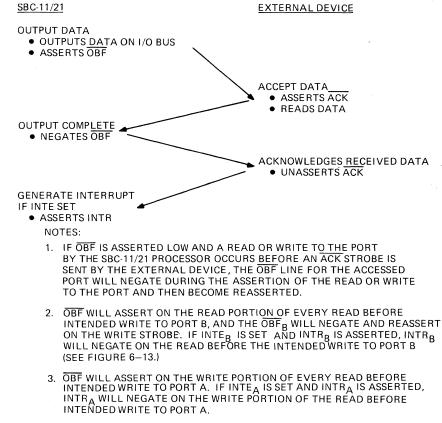

| 6-11       | Mode 1 Output Data Handshaking Sequence |        |

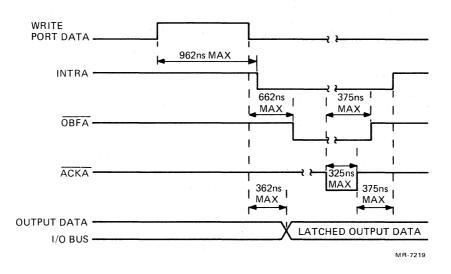

| 6-12       | Mode 1 Port A Strobed Output Timing     | 6-28   |

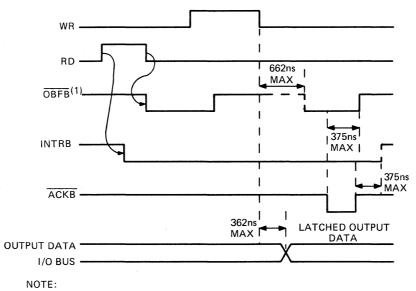

| 6-13       | Mode 1 Port B Strobed Output Timing     | 6-28   |

| 6-14       | Mode 2 Port A Bidirectional Timing      | . 6-29 |

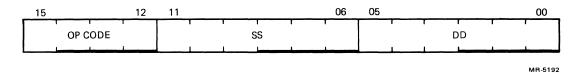

| 7-1        | Single Operand Addressing               | . 7-3  |

| 7-2        | Double Operand Addressing               | . 7-3  |

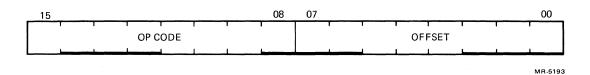

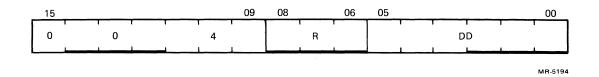

| 7-3        | Mode 0 Register                         | . 7-5  |

| 7-4        | Mode 2 Autoincrement                    |        |

| 7-5        | Mode 4 Autodecrement                    | . 7-6  |

| 7-6        | Mode 6 Index                            | . 7-6  |

| 7-7        | INC R3                                  | . 7-7  |

| 7-8        | ADD R2,R4                               | . 7-7  |

| 7-9        | COMB R4                                 | . 7-8  |

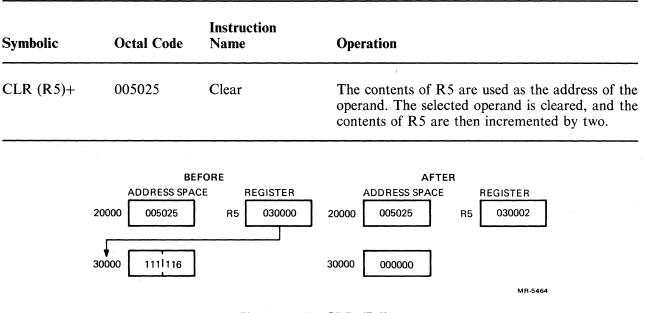

| 7-10       | CLR (R5) +                              | . 7-8  |

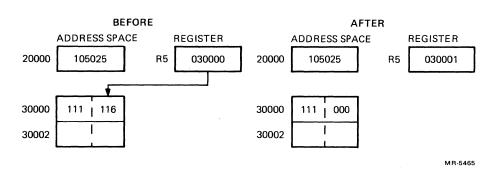

| 7-11       | CLRB (R5) +                             | . 7-9  |

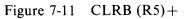

| 7-12       | ADD (R2)+,R4                            | . 7-9  |

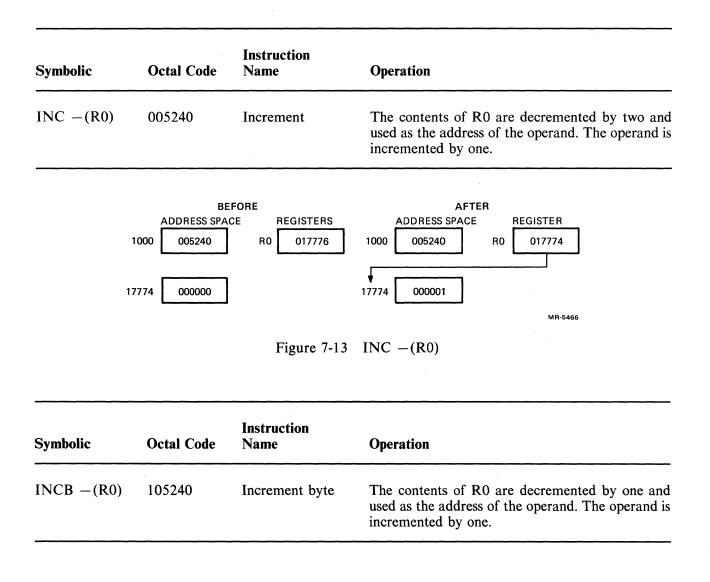

| 7-13       | INC –(R0)                               | . 7-10 |

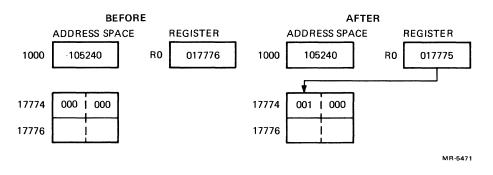

| 7-14       | INCB – (R0)                             | . 7-11 |

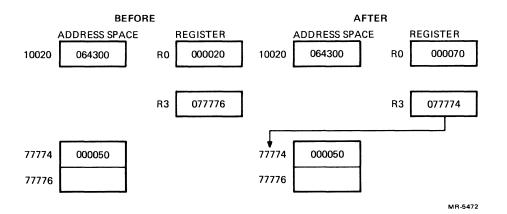

| 7-15       | ADD – (R3),R0                           | . 7-11 |

| 7-16       | CLR 200(R4)                             | . 7-12 |

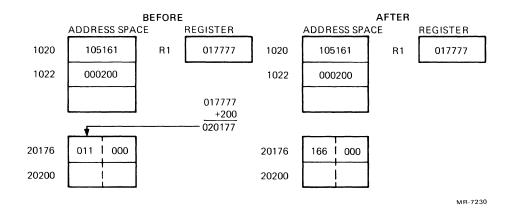

| 7-17       | COMB 200(R1)                            |        |

| 7-18       | ADD 30(R2),20(R5)                       | . 7-13 |

| 7-19       | Mode 1 Register Deferred                |        |

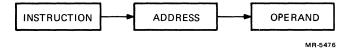

| 7-20       | Mode 3 Autoincrement Deferred           |        |

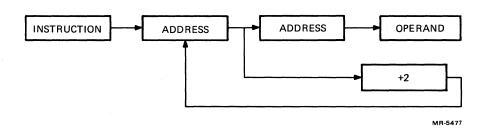

| 7-21       | Mode 5 Autodecrement Deferred           |        |

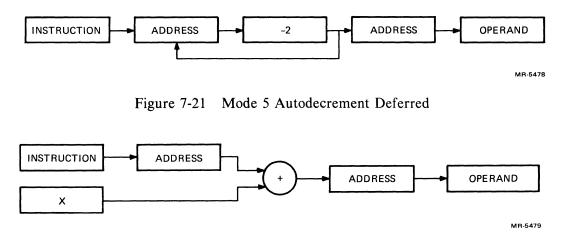

| 7-22       | Mode 7 Index Deferred                   | . 7-15 |

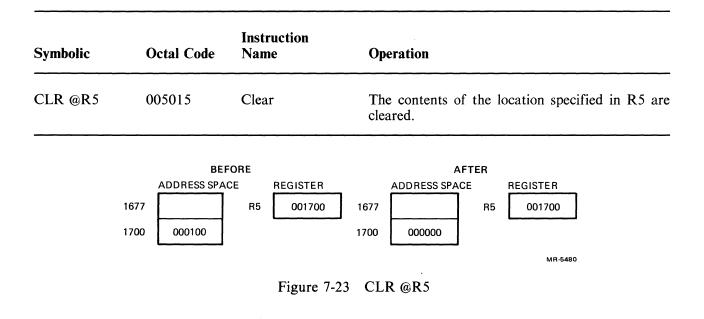

| 7-23       | CLR @R5                                 | . 7-15 |

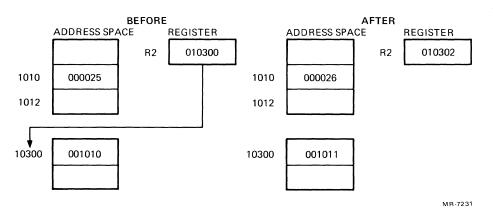

| 7-24       | INC @(R2)+                              |        |

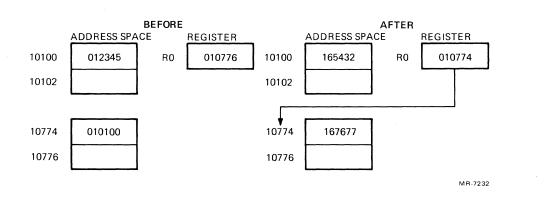

| 7-25       | COM @ -(R0)                             |        |

| 7-26       | ADD @1000(R2),R1                        |        |

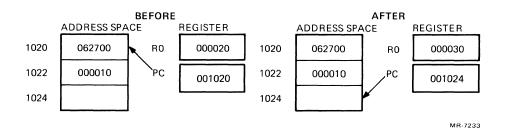

| 7-27       | ADD #10,R0                              |        |

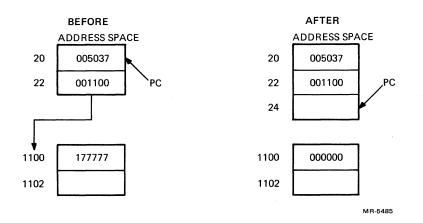

| 7-28       | CLR @#1100                              |        |

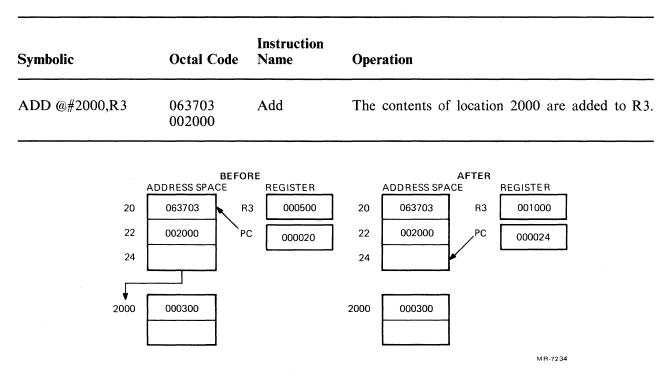

| 7-29       | ADD @#2000,R3                           |        |

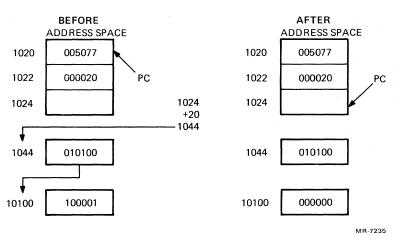

| 7-30       | INC A                                   |        |

| 7-31       | CLR @A                                  | . 7-22 |

# FIGURES (Cont)

| Figure No. | Title                                              | Page   |

|------------|----------------------------------------------------|--------|

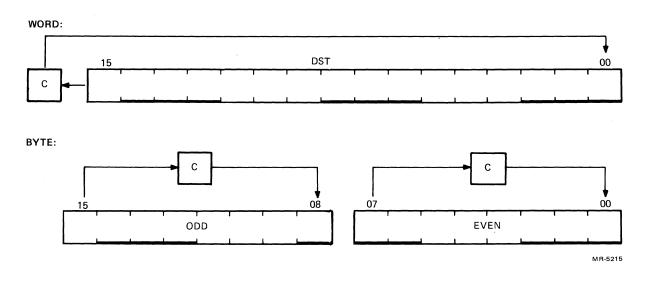

| 7-32       | Byte Instructions                                  | 7-25   |

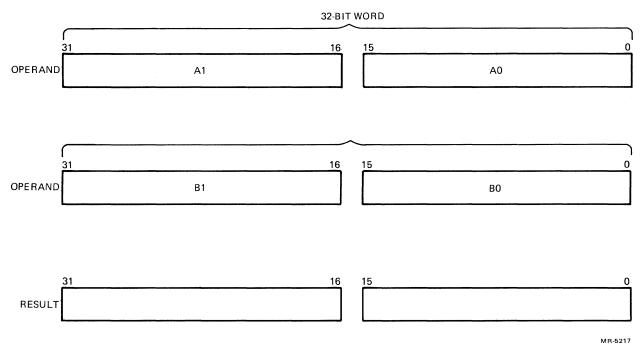

| 7-33       | Multiple Precision                                 | 7-37   |

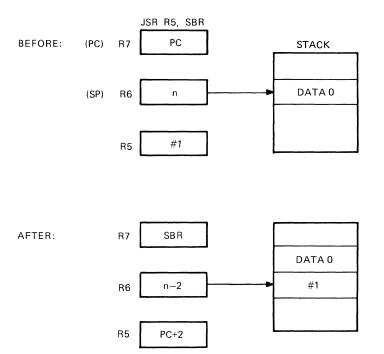

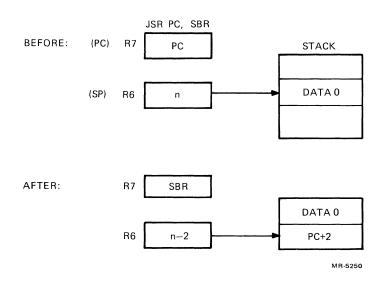

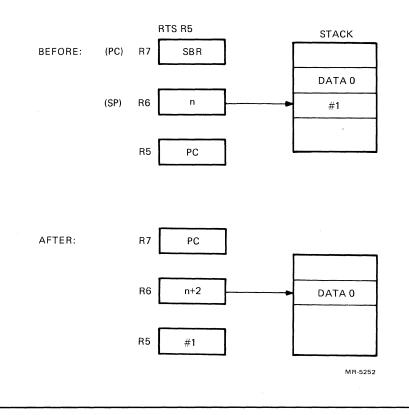

| 7-34       | JSR Example                                        | 7-59   |

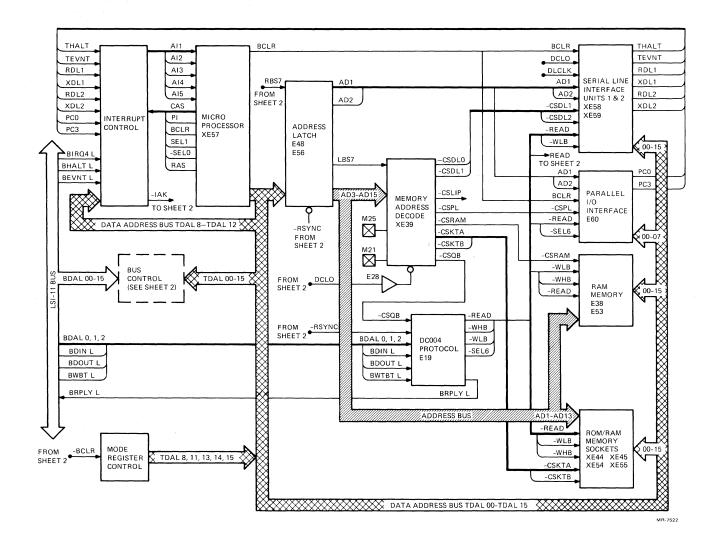

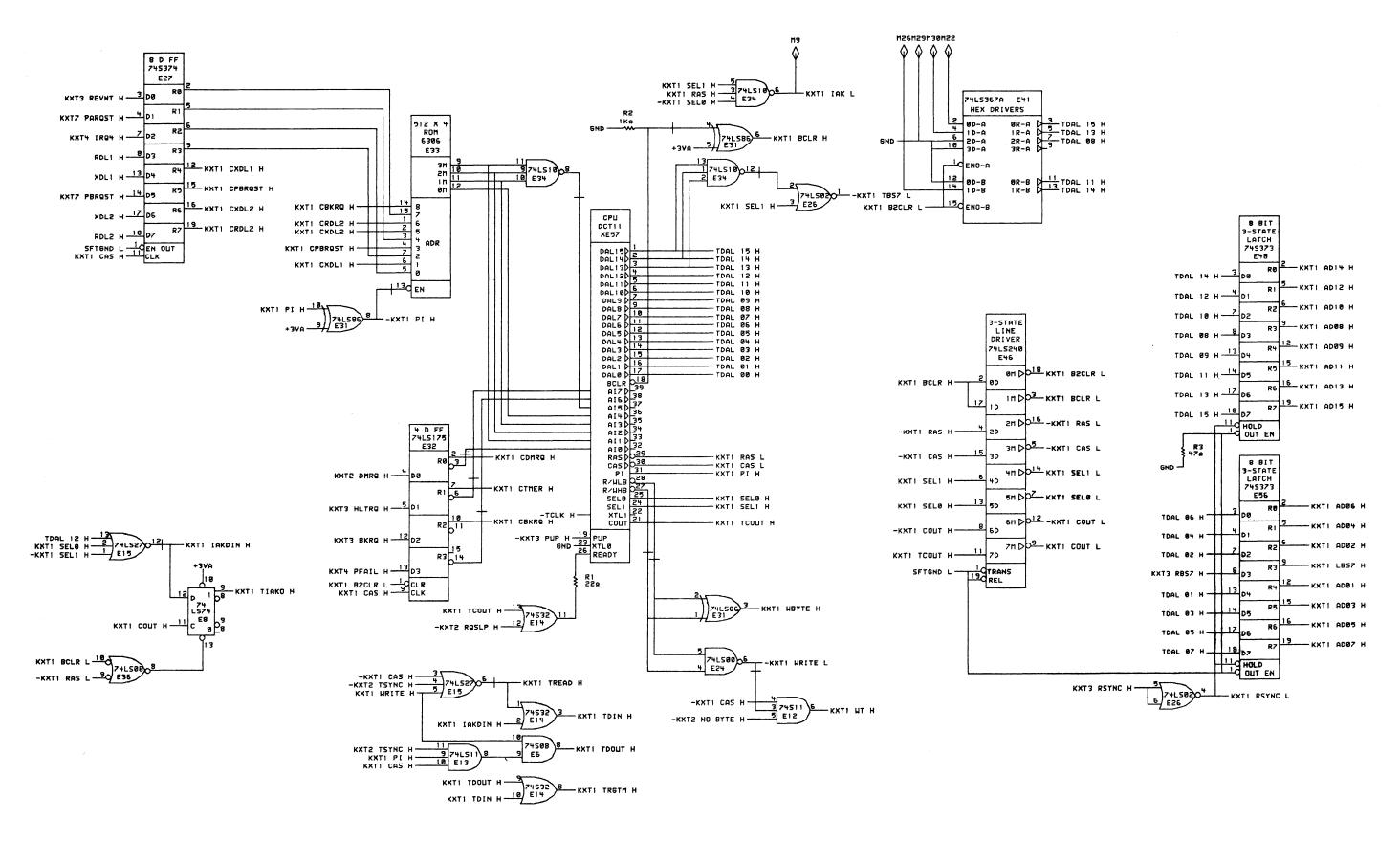

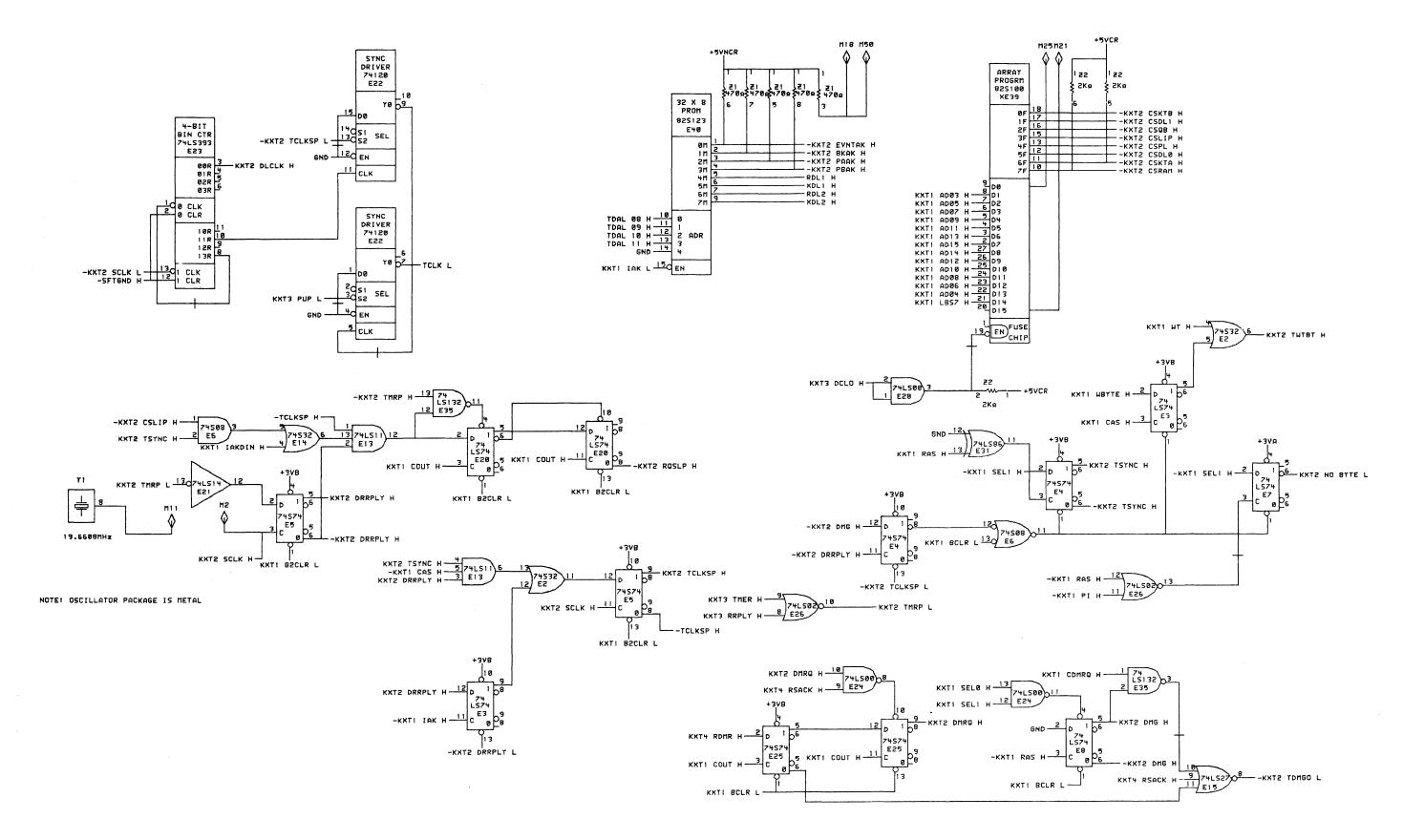

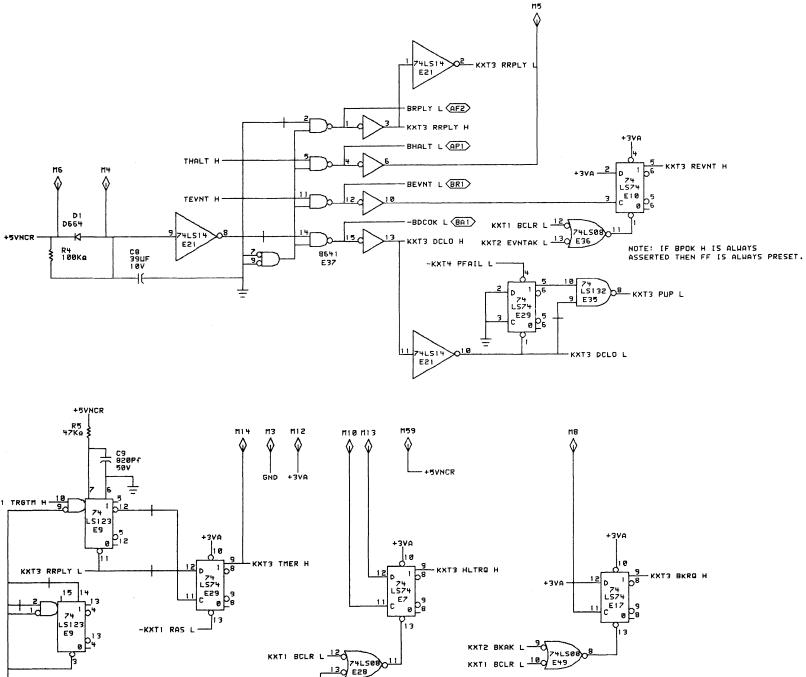

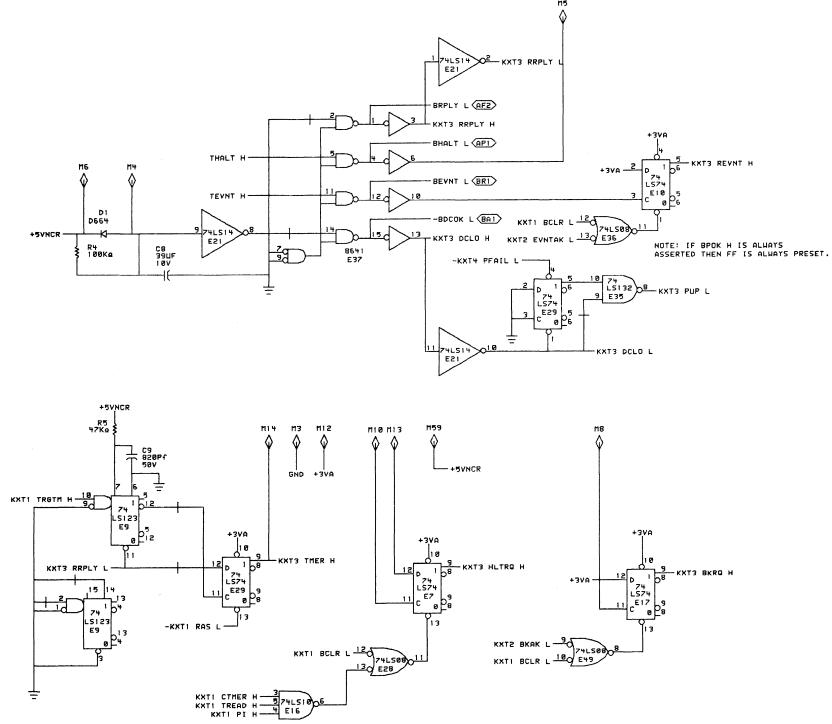

| 8-1        | SBC-11/21 Functional Block Diagram                 |        |

| 8-2        | SBC-11/21 Microprocessor                           | 8-4    |

| 8-3        | Fetch/Read Transaction                             |        |

| 8-4        | Write Transaction                                  | 8-9    |

| 8-5        | IAK Transaction                                    |        |

| 8-6        | DMA Transaction                                    | 8-11   |

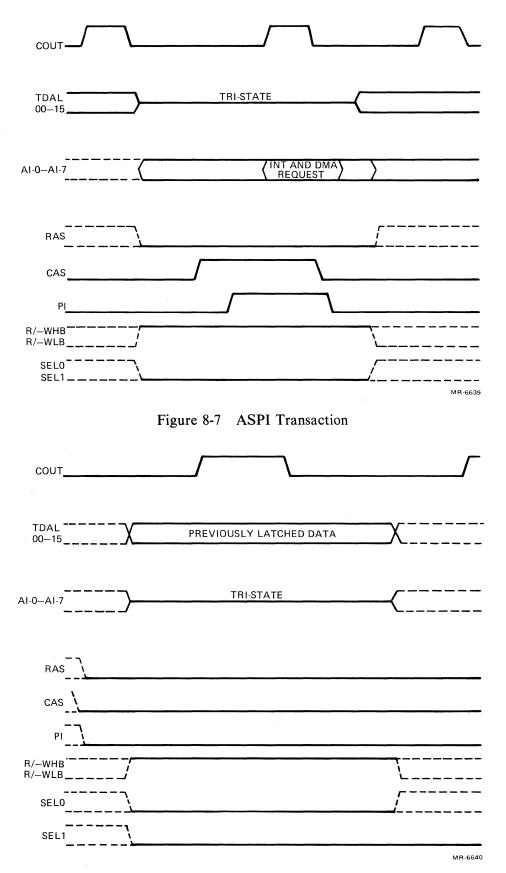

| 8-7        | ASPI Transaction                                   |        |

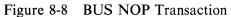

| 8-8        | BUS NOP Transaction                                |        |

| 8-9        | Mode Register Control                              |        |

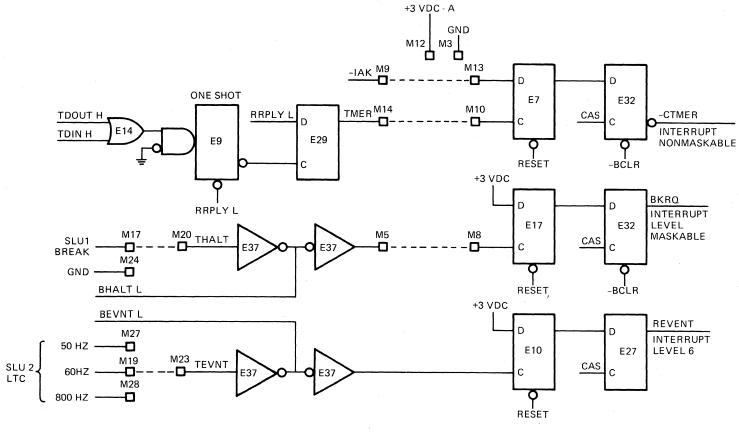

| 8-10       | SBC-11/21 Interrupt Control                        |        |

| 8-11       | Interrupt Control Logic                            |        |

| 8-12       | Ready                                              |        |

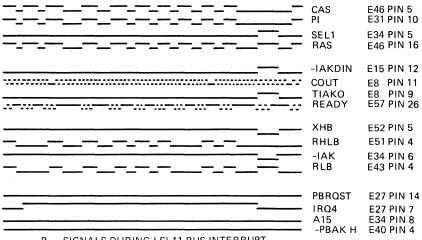

| 8-13       | IAKĎIN                                             |        |

| 8-14       | HALT Interrupt                                     |        |

| 8-15       | Memory Maps                                        |        |

| 8-16       | RAM Memory                                         |        |

| 8-17       | ROM/RAM Memory Sockets                             |        |

| 8-18       | Serial Line Interface Units                        |        |

| 8-19       | Parallel I/O Interface                             |        |

| 8-20       | Power-up                                           |        |

| 8-21       | Clock                                              |        |

| 8-22       | Clock Control                                      |        |

| 8-23       | DMA                                                |        |

| 8-24       | TSYNC                                              |        |

| 8-25       | Read/Write                                         |        |

| 8-25       | Reply Time-out                                     |        |

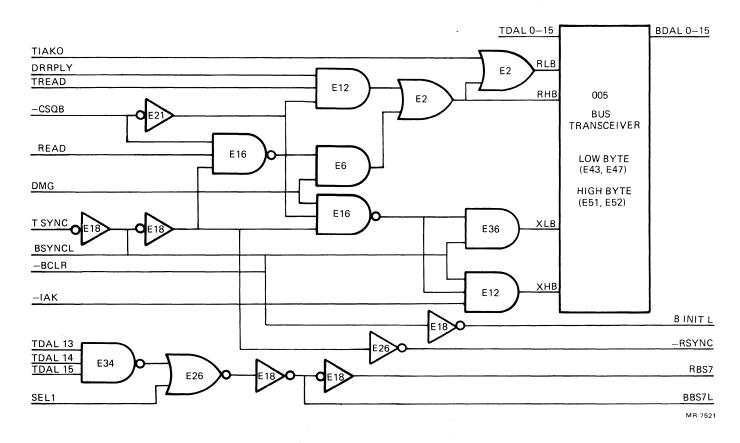

| 8-27       | Bus Control                                        |        |

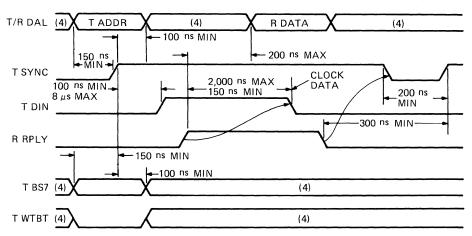

| 9-1        | DATI Bus Cycle                                     |        |

| 9-2        | DATI Bus Cycle Timing                              |        |

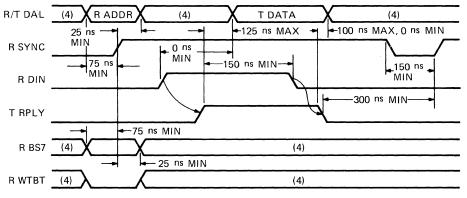

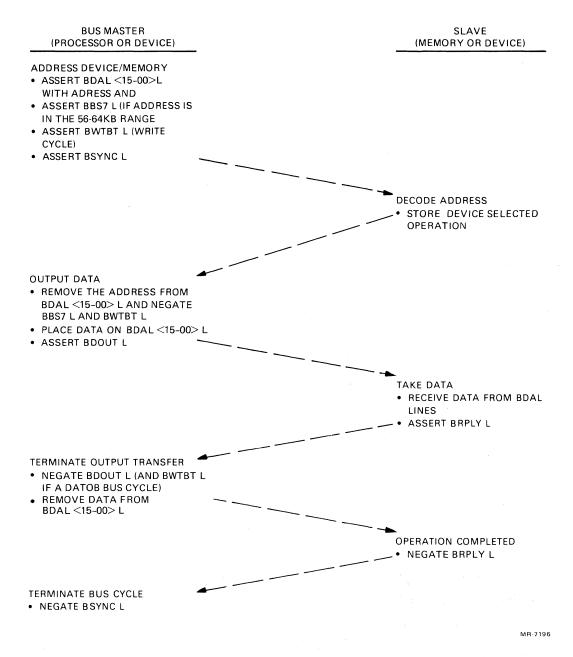

| 9-2<br>9-3 | DATO or DATOB Bus Cycle                            |        |

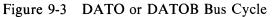

| 9-4        | DATO or DATOB Bus Cycle Timing                     | 0.10   |

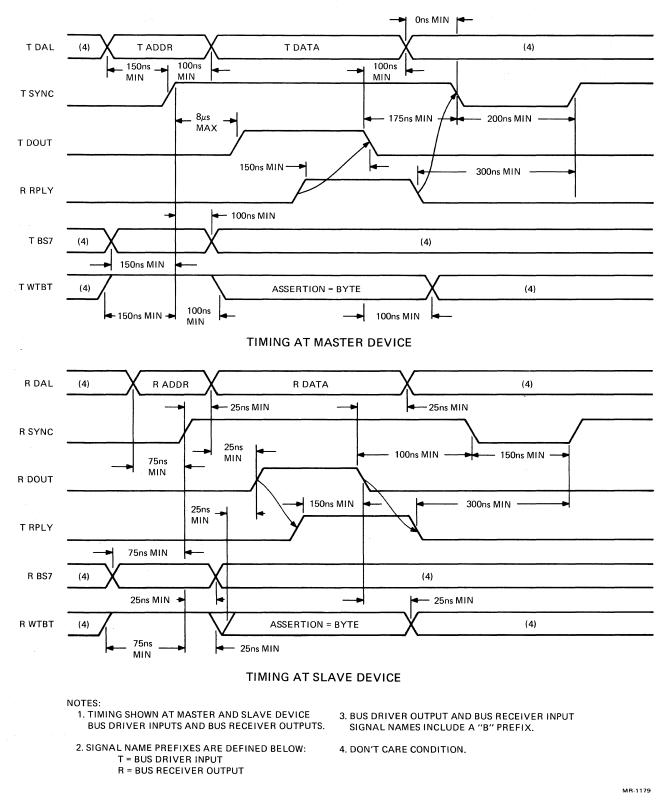

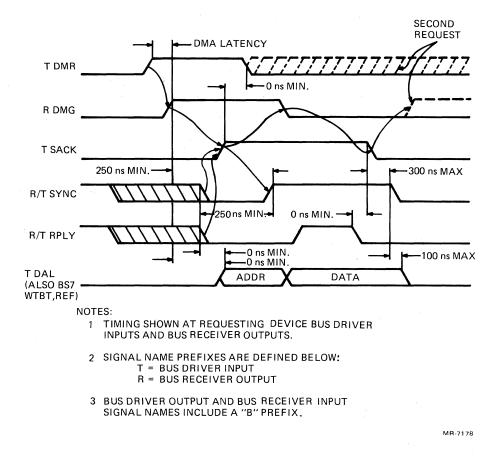

| 9-4<br>9-5 | DMA Protocol                                       |        |

| 9-5<br>9-6 | DMA Protocol<br>DMA Request/Grant Timing           | . 9-12 |

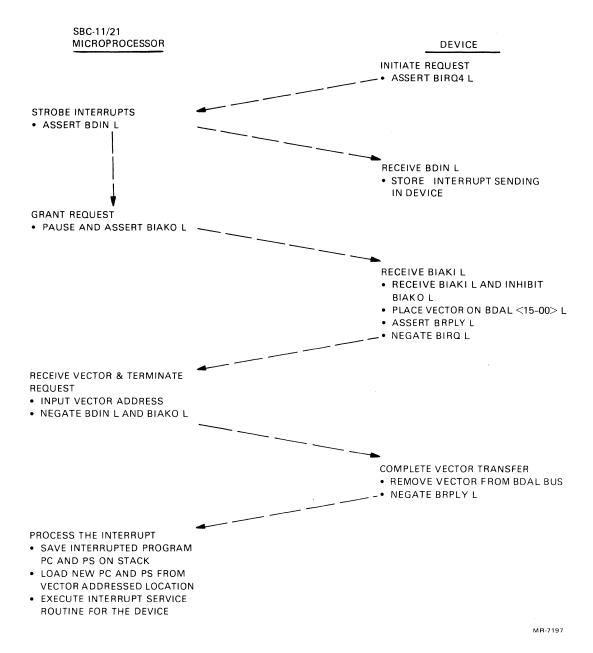

| 9-0<br>9-7 | Interrupt Request/Acknowledge Sequence             |        |

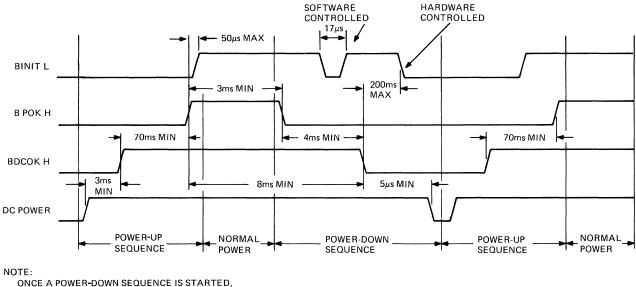

| 9-7<br>9-8 | Power-Up/Power-Down Timing                         |        |

| 9-8<br>9-9 | Double-Height Module Contact Finger Identification |        |

| 9-9<br>C-1 | 0 0                                                |        |

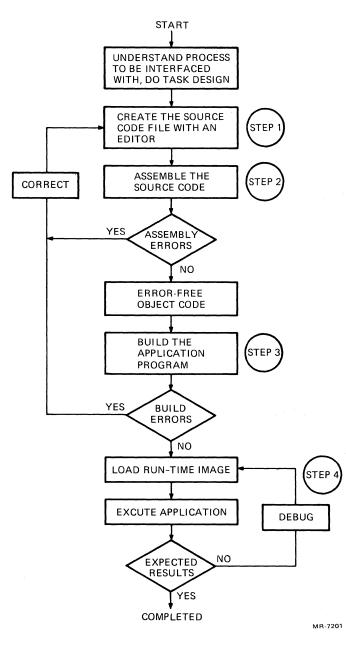

| C-1<br>C-2 | Overview of Software Development                   |        |

| C-2<br>C-3 | Application Overview                               |        |

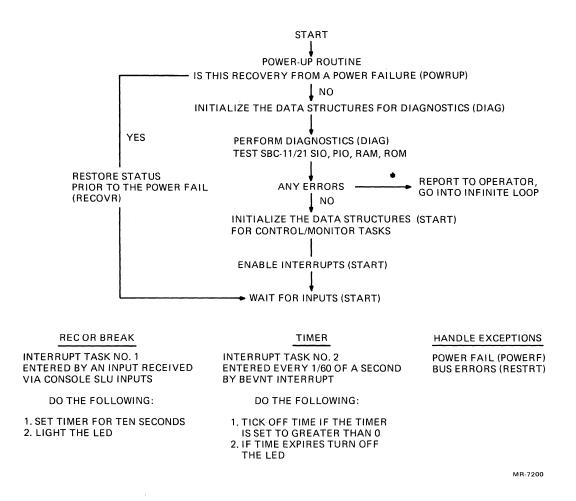

|            | Monitor Program                                    |        |

| C-4        | Load Map                                           |        |

| C-5        | Power-up Task                                      |        |

| C-6        | Power Fail Recovery                                |        |

| C-7        | SLU Diagnostic Task                                |        |

| C-8        | RAM Diagnostic Task                                |        |

| C-9        | ROM Diagnostic Task                                |        |

| C-10       | Parallel I/O Diagnostic Task                       |        |

| C-11       | Control Task                                       |        |

| C-12       | Power Fail Task                                    | C-13   |

## TABLES

#### Title Table No. Page SBC-11/21 Module Backplane Pin Identification...... 1-5 1-1 Related Documentation ..... 1-2 1-7 Configuration Pin Definitions 2-1 2-32 - 2Configuration Pin Functions ..... 2-5 2-3 2-4 2-52-6 2-72-8 2-9 2-10 Socket Set B Configuration for EPROM/PROM...... 2-21 2 - 112 - 122 - 132-14 2 - 154-1 Macro-ODT Commands 4-3 4-2 Macro-ODT States and Valid Input Characters..... 4-4 5-1 Processor Status Word Bit Descriptions 5-3 5-2 PSW Interrupt Levels 5-3 5-3 6-1 Serial Line Unit Register Addresses..... 6-3 Receiver Control and Status Bit Descriptions 6-2 6-4 6-3 Receiver Data Buffer Bit Descriptions 6-4 6-4 6-5 6-6 6-7 6-8 6-9 6-10 6-11 6-12 6-13 6-14 6-15 6-16 6-17 6-18 6-19 6-20 6-21 6-22 6-23 7-1 7-2 7-3 7-4 7-5

Х

# TABLES(Cont)

## Table No.

-----

## Title

## Page

| 8-1 | Start Address Configurations                   | 8-13       |

|-----|------------------------------------------------|------------|

| 8-2 | Designated Interrupts                          |            |

| 8-3 | Serial Line Unit Registers                     | 8-28       |

| 8-4 | PPI Addressable Registers                      |            |

| 9-1 | Signal Assignments                             | 9-3        |

| 9-2 | Data Transfer Operations                       | 9-4        |

| 9-3 | Bus Signals Used in Data Transfer Operations   | 9-4        |

| 9-4 | Bus Pin Identifiers                            | 9-17       |

| A-1 | Instruction Timing                             | A-1        |

| B-1 | SBC-11/21, LSI-11/2, and LSI/11/23 Comparisons | <b>B-1</b> |

| B-2 | Illegal Address Traps                          | <b>B-6</b> |

## PREFACE

This User's Guide provides the user with configuration, system architecture, and programming information for the SBC-11/21 single-board computer. The configuration requirements are described in Chapter 2, and the system architecture is presented in Chapter 5. The programming techniques are described in Chapter 6, and the instruction set is listed in Chapter 7. Operational theory is presented in Chapter 8, and the schematics are in Appendix E. The Macro-ODT option is described in Chapter 4, and the listing is in Appendix D. Options for use on the LSI-11 bus are listed in Chapter 3, and the module bus requirements are described in Chapter 9. An example of software development is covered by Appendix C. Appendix A summarizes the instruction timing, and Appendix B compares the SBC-11/21 to other LSI-11 microprocessors.

#### NOTE

This User's Guide is for use with the SBC-11/21 module, M8063 Revision D and subsequent revisions only. This revision is identified by the circuit board #501448D-XX located on the module as described in Figure 1-1. Use manual EK-KXT11-UG for Revision C modules.

## CHAPTER 1 INTRODUCTION

#### **1.1 INTRODUCTION**

The KXT11-AA (M8063-BA) module, called the SBC-11/21 single-board computer, is shown in Figure 1-1. It is a complete computer system on an  $8.5 \times 5.2$  inch printed circuit board that executes the well-known PDP-11 instruction set (see Appendix B). The SBC-11/21 module contains 4Kb (kilobytes) of RAM, sockets for up to 32Kb of PROM or additional RAM, two serial I/O lines, twenty-four lines of parallel I/O, and a 50 Hz, 60 Hz, or 800 Hz real-time clock. In addition, the SBC-11/21 supports the complete LSI-11 bus interface that enables it to communicate with most of Digital's large family of modules (see Chapter 3) described in the *Microcomputer Interfaces* and *Microcomputers and Memories* handbooks.

The SBC-11/21 computer features the following:

- A powerful processor running the PDP-11 instruction set.

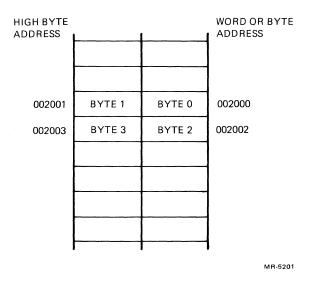

- Direct addressing of 32K, 16-bit words or 64K, 8-bit bytes (K = 1024).

- Efficient processing of 8-bit characters without the need to rotate, swap, or mask.

- On-board 4Kb of static read/write memory.

- Sockets for up to 32Kb of PROM for a wide range of memory types from many vendors. Additional RAM can also be installed in these sockets.

- Hardware memory stack for handling data, subroutines, and interrupts.

- Direct memory access for high data rate devices.

- Eight general-purpose registers for data storage, pointers, and accumulators; two are dedicated: stack pointer (SP) and program counter (PC).

- Fast on-board bus for high throughput when external memory access is not needed.

- LSI-11 bus structure that provides position dependent priority for peripheral device interfaces connected to the bus.

- Fast vectored interrupt response without device polling.

- A powerful set of instructions.

- Two serial I/O interfaces, compatible with EIA RS-232C and EIA RS-423, with software programmable baud rates over the range of 300 to 38,400 baud.

- One parallel I/O interface with two bidirectional 8-bit input/output ports and one 8-bit control port.

- Real-time clock that can be set by the user to 50 Hz, 60 Hz, or 800 Hz.

- Jumper-selected operating modes, including four memory maps, exception handling, start and restart addresses, parallel I/O configurations, and real-time clock frequency.

- Optional PROM resident Macro-ODT containing module diagnostics, bootstrap programs for mass storage devices (TU58, RX01, and RX02), console communications, and on-line debugging facility.

#### **1.2 SPECIFICATIONS**

The SBC-11/21 module specifications follow:

#### 1.2.1 Physical

| Height                             | 13.2 cm (5.2 in)      |

|------------------------------------|-----------------------|

| Length<br>(includes module handle) | 22.8 cm (8.9 in)      |

| Width                              | 1.27 cm (0.5 in)      |

| Weight                             | 360 g (12 oz) maximum |

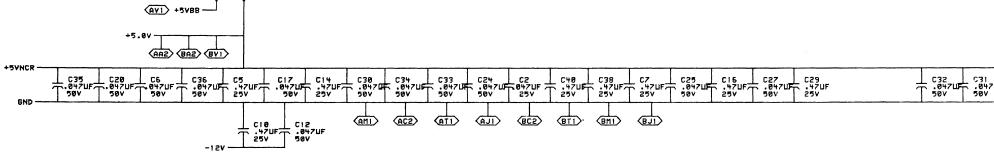

### **1.2.2** Power Requirements

Power Supply:

| $+5.0 V \pm 5\%$  | 2.5 A (typical), 2.8 A (maximum)                                                                                                                        |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| $+12.0 V \pm 5\%$ | 60 mA (typical) used by on-board circuitry, 1.1 A (maximum) includes current provided to outside interface through pin 10 of the serial $I/O$ connector |

#### Battery Backup:

|  | $+5.0 V \pm 5\%$ | 170 mA (typical), 260 mA | (maximum) |

|--|------------------|--------------------------|-----------|

|--|------------------|--------------------------|-----------|

#### NOTE

The +12.0 V typical current is measured with no connections at pin 10 of the serial I/O connectors (fused line).

#### **1.2.3** Bus Loading

| AC Loads | 2.4 |

|----------|-----|

| DC Loads | 1.0 |

Temperature:

Storage Operating -40° C to 65° C (-40° F to 150° F) 5° C to 60° C (41° F to 140° F)

#### NOTE

The module must be brought into the operating temperature environment and allowed to stabilize before operating.

Relative Humidity:

Storage Operating 10% to 90% (no condensation) 10% to 90% (no condensation)

Altitude:

Storage Operating Up to 15 km (50,000 ft) Up to 15 km (50,000 ft) (90 mm mercury minimum)

#### NOTE

Lower the maximum operating temperature by 1° C (1.8° F) for each 300 m (1,000 ft) of altitude above 2.4 km (8,000 ft).

Environment:

Air must be noncaustic.

Airflow (operating):

There must be enough airflow to limit the input to output temperature rise across the module to 5° C (9° F) when the input temperature is 60° C (140° F). For operation below 55° C (131° F), there must be enough airflow to limit the input to output temperature rise across the module to 10° C (18° F) maximum.

#### NOTE

These are design limits. Lower temperature limits will help increase the life of the product.

### **1.3 BACKPLANE PIN IDENTIFICATION**

Table 1-1 lists backplane pin connections for the SBC-11/21 module, pin identification and signal names unique to the SBC-11/21 module, and standard LSI-11 bus backplane names assigned to each pin. Although the signal names may differ, the module is completely LSI-11 bus compatible with the exception of bus refresh transaction (BREF) which is not performed by the SBC-11/21. Signals STOP L, SRUN L, and START L are not used on the LSI-11 bus. These are TTL level signals unique to the SBC-11/21.

|   | Backplane<br>Pin | SBC-11/21<br>Signal Function | LSI-11 Bus<br>Signal Name |  |

|---|------------------|------------------------------|---------------------------|--|

|   | Side 1 (Compor   | ent Side)                    |                           |  |

|   | AA1              | Bus terminator               | BIRQ5 L                   |  |

|   | AB1              | Bus terminator               | BIRQ6 L                   |  |

|   | AC1              | Bus terminator               | BDAL16 L                  |  |

|   | AD1              | Bus terminator               | BDAL17 L                  |  |

|   | AE1              | STOP L                       | SSPARE1                   |  |

|   | AF1              | SRUN L                       | SSPARE2                   |  |

|   | AH1              | Not connected                | SSPARE3                   |  |

| * | AJ1              | GND                          | GND                       |  |

|   | AK1              | Not connected                | MSPAREA                   |  |

|   | AL1              | GND                          | MSPAREA                   |  |

|   | AM1              | GND                          | GND                       |  |

|   | AN1              | BDMR L                       | BDMR L                    |  |

|   | AP1              | BHALT L                      | BHALT L                   |  |

|   | AR1              | Bus terminator               | BREF L                    |  |

|   | AS1              | Not connected                | +12B                      |  |

|   | AT1              | GND                          | GND                       |  |

|   | AU1              | Not connected                | PSPARE1                   |  |

|   | AV1              | +5 VB (battery)              | +5B                       |  |

|   |                  |                              |                           |  |

|   | BA1              | BDCOK H                      | BDCOK H                   |  |

|   | <b>BB</b> 1      | врок н                       | врок н                    |  |

|   | BC1              | Bus terminator               | SSPARE4                   |  |

|   | BD1              | Bus terminator               | SSPARE5                   |  |

|   | BE1              | Bus terminator               | SSPARE6                   |  |

|   | BF1              | Bus terminator               | SSPARE7                   |  |

|   | BH1              | START L                      | SSPARE8                   |  |

|   | BJ1              | GND                          |                           |  |

|   | BK1              | Not connected                | MSPAREB                   |  |

| , | BL1              | Not connected                | MSPAREB                   |  |

|   | <b>BM</b> 1      | GND                          |                           |  |

|   | BN1              | BSACK L                      | BSACK L                   |  |

|   | BP1              | Bus terminator               | BIRQ7 L                   |  |

|   | BR1              | BEVNT L                      | BEVNT L                   |  |

|   | BS1              | Not connected                | +12B                      |  |

|   | BT1              | GND                          | GND                       |  |

|   | BU1              | Not connected                | PSPARE2                   |  |

|   | BV1              | +5  V                        | +5  V                     |  |

Table 1-1

SBC-11/21 Module Backplane Pin Identification

|       | Backplane<br>Pin     | SBC-11/21<br>Signal Function | LSI-11 Bus<br>Signal Name |

|-------|----------------------|------------------------------|---------------------------|

| · · · | Side 2 (Solder Side) |                              |                           |

|       | AA2                  | +5 V                         | +5 V                      |

|       | AB2                  | Not connected                | -12  V                    |

|       | AC2                  | GND                          | GND                       |

|       | AD2                  | +12 V                        | +12 V                     |

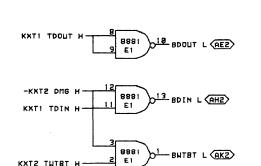

|       | AE2                  | BDOUT L                      | BDOUT L                   |

|       | AF2                  | BRPLY L                      | BRPLY L                   |

|       | AH2                  | BDIN L                       | BDIN L                    |

|       | AJ2                  | BSYNC L                      | BSYNC L                   |

|       | AK2                  | BWTBT L                      | BWTBT L                   |

|       | AL2                  | BIRQ4 L                      | BIRQ4 L                   |

|       | AM2                  | Not connected                | BIARI L                   |

|       | AN2                  | BIAKO L                      | BIAKOL                    |

|       | AP2                  | BBS7 L                       | BBS7 L                    |

|       | AR2                  | Not connected                | BDMGI L                   |

|       | AS2                  | BDMGO L                      | BDMGO L                   |

|       | AT2                  | BINIT L                      | BINIT L                   |

|       | AU2                  | BDAL0 L                      | BDAL0 L                   |

|       | AV2                  | BDAL1 L                      | BDAL1 L                   |

|       |                      |                              |                           |

|       | BA2                  | +5 V                         | +5 V                      |

|       | BB2                  | Not connected                | -12 V                     |

|       | BC2                  | GND                          | GND                       |

|       | BD2                  | +12 V                        | +12 V                     |

|       | BE2                  | BDAL2 L                      | BDAL2 L                   |

|       | BF2                  | BDAL3 L                      | BDAL3 L                   |

|       | BH2                  | BDAL4 L                      | BDAL4 L                   |

|       | BJ2                  | BDAL5 L                      | BDAL5 L                   |

|       | BK2                  | BDAL6 L                      | BDAL6 L                   |

|       | BL2                  | BDAL7 L                      | BDAL7 L                   |

|       | BM2                  | BDAL8 L                      | BDAL8 L                   |

|       | BN2                  | BDAL9 L                      | BDAL9 L                   |

|       | BP2                  | BDAL10 L                     | BDAL10 L                  |

|       | BR2                  | BDAL11 L                     | BDAL11 L                  |

|       | BS2                  | BDAL12 L                     | BDAL12 L                  |

|       | BT2                  | BDAL13 L                     | BDAL13 L                  |

|       | BU2                  | BDAL14 L                     | BDAL14 L                  |

|       | BV2                  | BDAL15 L                     | BDAL15 L                  |

|       | - <u>`</u> .         |                              |                           |

Table 1-1

SBC-11/21 Module Backplane Pin Identification (Cont)

## **1.4 RELATED DOCUMENTS**

This User's Guide is the primary reference document for the SBC-11/21. Important information about other LSI-11 bus compatible products may be found in the publications listed in Table 1-2.

| Title                                              | Document Number |

|----------------------------------------------------|-----------------|

| Microcomputers and Memories Handbook, 1982 Edition | EB-20912-20     |

| Microcomputer Interfaces Handbook, 1980 Edition    | EB-20175-20     |

| PDP-11 Bus Handbook, 1979 Edition                  | EB-17525-20     |

| Table 1-2 | <b>Related Documentation</b> |

|-----------|------------------------------|

|           | Related Documentation        |

These documents can be ordered from:

Digital Equipment Corporation Printing and Circulation Services 444 Whitney Street Northboro, MA 01532

Attention: Communications Services (NR2/M15) Customer Services Section

## CHAPTER 2 INSTALLATION

#### 2.1 INTRODUCTION

The installation of the SBC-11/21 single-board computer module is discussed in this chapter. The following five items, which are an integral part of the installation procedure, are covered in detail.

## **NOTE** It is best to leave the factory configuration as is until module performance has been verified.

- 1. Installing jumpers to select operational features.

- 2. Selecting and mounting an LSI-11 bus-structured backplane and adding any required LSI-11 bus options.

- 3. Selecting and connecting an appropriate power supply.

- 4. Providing appropriate cables to connect external devices to the serial line and parallel I/O interfaces.

- 5. Verifying operation of the module.

## 2.2 SELECTING OPERATIONAL FEATURES

The module has sixty-five wirewrap pins with which the user configures the module for the operating modes necessary to meet any requirements. This is done by either installing or removing jumper wires between the wirewrap pins. The locations and identification numbers of the wirewrap pins are illustrated in Figure 2-1. Table 2-1 defines the wirewrap pins, and Table 2-2 lists the pin functions by the features they support. The selectable features are battery backup, power-up, starting address, interrupts, parallel I/O buffers, and memory maps. Detailed requirements for each of these configurations are described in the following paragraphs. The standard factory configuration is described in Table 2-3.

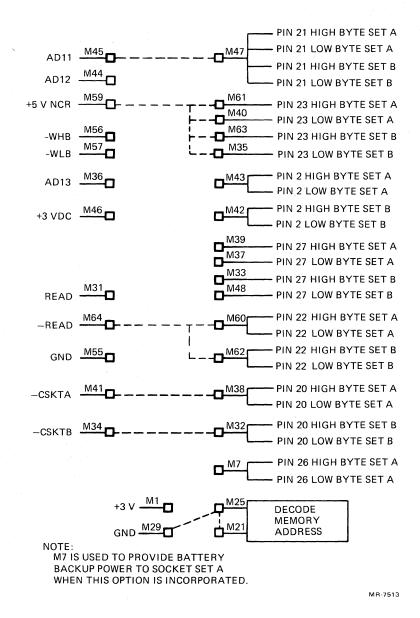

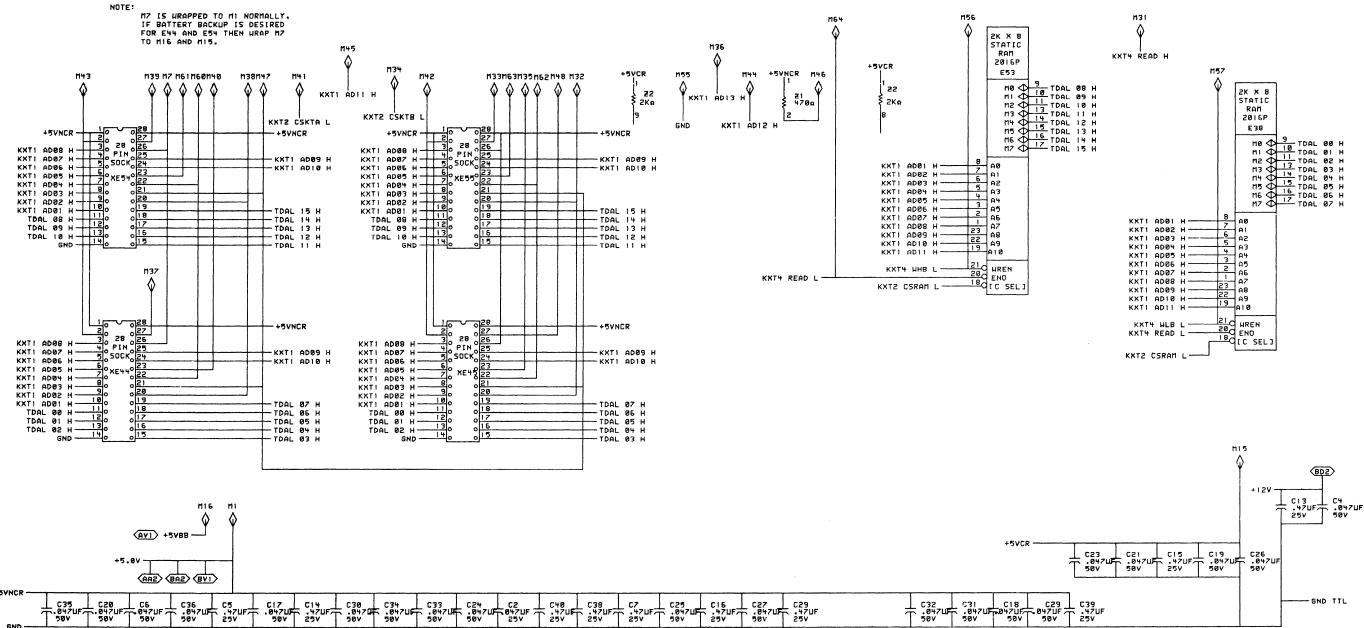

#### 2.2.1 Battery Backup

The user can select the battery backup mode to maintain a + 5 Vdc battery supply to the 4Kb of static RAM and, if needed, to the two 28-pin sockets that are defined as socket set A. The +5 Vdc battery supply is provided through the LSI-11 bus via pin AV1. A maximum of 260 mA is required. This supply is connected to wirewrap pin M16. To enable battery backup of 4Kb of static RAM, the jumper wire between M1 and M15 is removed, and a jumper wire is installed between M16 and M15. To provide backup for socket set A, the jumper wire between M7 and M1 is removed, and a jumper wire is installed between M15 and M7.

Figure 2-1 SBC-11/21 Module Layout

| Pin        | Schematic<br>Sheet<br>Number | Description                                                     |  |

|------------|------------------------------|-----------------------------------------------------------------|--|

| <b>M</b> 1 | 1                            | System +5 V power                                               |  |

| M2         | 1                            | Clock system input                                              |  |

| M3         | 3                            | System GND                                                      |  |

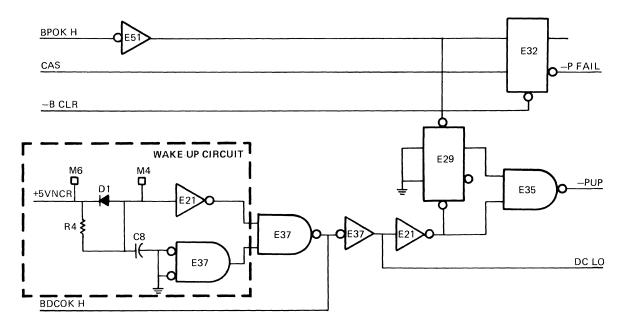

| M4         | 3                            | Wake up circuit diode, anode side                               |  |

| M5         | 3                            | Receive side of BHALT line transceiver                          |  |

| M6         | 3                            | Wake up circuit diode, cathode side                             |  |

| M7         | 5                            | Socket set A, pin 26, high and low byte                         |  |

| M8         | 3                            | BHALT interrupt request input (edge sensitive)                  |  |

| M9         | 1                            | Interrupt acknowledge (-IAK) output                             |  |

| M10        | 3                            | -CTMER interrupt request input (edge sensitive)                 |  |

| M11        | 1                            | Clock oscillator output                                         |  |

| M12        | 3                            | High logic level (+3 Vdc)                                       |  |

| M13        | 3                            | -CTMER interrupt enable                                         |  |

| M14        | 3                            | Time-out error (TMER) output                                    |  |

| M15        | 1                            | +5 Vdc power distribution to support static RAM                 |  |

| M16        | 1                            | Battery backup +5 Vdc power source                              |  |

| M17        | 6                            | Serial line unit (SLU) 1 BREAK detect, interrupt request output |  |

| M18        | 2                            | High logic level (+3 Vdc)                                       |  |

| M19        | 6                            | 60 Hz real-time clock output                                    |  |

| M20        | 6                            | Transmit side of BHALT line transceiver                         |  |

| M21        | 2                            | Memory map select (MSB)                                         |  |

| M22        | 1                            | Start address control (TDAL 15)                                 |  |

| M23        | 6                            | Transmit side of BEVNT line transceiver                         |  |

| M24        | <b>6</b>                     | System GND                                                      |  |

| M25        | 2                            | Memory map select (LSB)                                         |  |

|            | _                            |                                                                 |  |

| M26        | 1                            | Start address control (TDAL 14)                                 |  |

| M27        | 6                            | 50 Hz real-time clock output                                    |  |

| M28        | 6                            | 800 Hz real-time clock output                                   |  |

| M29<br>M30 | 1                            | System GND<br>Start address control (TDAL 13)                   |  |

| 10130      | 1                            | Start address control (IDAL 15)                                 |  |

| M31        | 5                            | Read strobe (READ)                                              |  |

| M32        | 5                            | Socket set B, high and low byte, pin 20                         |  |

| M33        | 5                            | Socket set B, high byte, pin 27                                 |  |

| M34        | 5                            | Socket set B, chip select, $(-CSKTB)$                           |  |

| M35        | 5                            | Socket set B, low byte, pin 23                                  |  |

| M36        | 5                            | Address line 13                                                 |  |

| M37        | 5                            | Socket set A, low byte, pin 27                                  |  |

| M38        | 5                            | Socket set A, high and low byte, pin 20                         |  |

| M39        | 5                            | Socket set A, high byte, pin 27                                 |  |

| M40        | 5                            | Socket set A, low byte, pin 23                                  |  |

| Pin         | Schematic<br>Sheet<br>Number | Description                                    |  |

|-------------|------------------------------|------------------------------------------------|--|

|             |                              |                                                |  |

| M41         | 5                            | Socket set A, chip select, $(-CSKTA)$          |  |

| M42         | 5                            | Socket set B, high and low byte, pin 2         |  |

| M43         | 5                            | Socket set A, high and low byte, pin 2         |  |

| M44         | 5                            | Address line 12                                |  |

| M45         | 5                            | Address line 11                                |  |

| M46         | 5                            | High logic level for PROMs                     |  |

| M47         | 5                            | Socket sets A and B, high and low byte, pin 21 |  |

| M48         | 5                            | Socket set B, low byte, pin 27                 |  |

| M49         | 7                            | Port B buffer direction control                |  |

| M50         | 2                            | High logic level (+3 Vdc)                      |  |

| M51         | 7                            | System GND                                     |  |

| M52         | 7                            | Port A buffer direction control                |  |

| M53         | ,<br>7                       | Port C buffered output, to J3 pin 7            |  |

| M54         | ,<br>7                       | Port C PC6 output (8255A-5 pin 11)             |  |

| M55         | 5                            | System GND                                     |  |

| M56         | 5                            | High byte write strobe (-WHB)                  |  |

| M57         | 5                            | Low byte write strobe (-WLB)                   |  |

| M58         | 7                            | Port C PC4 output (8255A-5 pin 13)             |  |

| M59         | 3                            | +5 Vdc voltage level                           |  |

| M60         | 5                            | Socket set A, high and low byte, pin 22        |  |

| <b>M</b> 61 | 5                            | Socket set A, high byte, pin 23                |  |

| M62         | 5                            | Socket set B, high and low byte, pin 22        |  |

| M63         | 5                            | Socket set B, high byte, pin 23                |  |

| M64         | 5                            | Read strobe (-READ)                            |  |

| M65         | 7                            | Port C buffered output, to J3 pin 5            |  |

| Pin                                  | Function                                                    | Description                                                                                                                                                                                  |

|--------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | Clock oscillator                                            |                                                                                                                                                                                              |

| M2<br>M11                            |                                                             | Clock system input<br>Clock oscillator output                                                                                                                                                |

|                                      | Battery backup                                              |                                                                                                                                                                                              |

| M1<br>M15<br>M16<br>M7               | ,                                                           | System +5 V power<br>+5 Vdc power distribution to support static RAM<br>Battery backup +5 V power source<br>Socket set A, pin 26, high and low byte                                          |

|                                      | Nonmaskable interrupt<br>and trap to the restart<br>address |                                                                                                                                                                                              |

| M10<br>M14<br>M13<br>M9<br>M3<br>M12 |                                                             | -CTMER interrupt request input (edge sensitive)<br>Time-out error (TMER) output<br>-CTMER interrupt enable<br>Interrupt acknowledge (-IAK) output<br>System GND<br>High logic level (+3 Vdc) |

|                                      | Serial line unit (SLU) 1                                    |                                                                                                                                                                                              |

| M24<br>M20<br>M17                    |                                                             | System GND<br>Transmit side of BHALT line transceiver<br>Serial line unit (SLU) 1 BREAK detect, interrupt request output                                                                     |

|                                      | Power-up                                                    |                                                                                                                                                                                              |

| M6<br>M4                             |                                                             | System $+5$ V power, wake up circuit diode, cathode side<br>Wake up circuit diode, anode side                                                                                                |

|                                      | Serial line unit (SLU) 2                                    |                                                                                                                                                                                              |

| M23<br>M27<br>M19<br>M28             |                                                             | Transmit side of BEVNT line transceiver<br>50 Hz real-time clock output<br>60 Hz real-time clock output<br>800 Hz real-time clock output                                                     |

|                                      | Memory map decoder                                          |                                                                                                                                                                                              |

| M18<br>M25<br>M21<br>M29             |                                                             | High logic level (+3 Vdc)<br>Memory map select (LSB)<br>Memory map select (MSB)<br>System GND                                                                                                |

Table 2-2

Configuration Pin Functions

| Pin        | Function                               | Description                                                               |

|------------|----------------------------------------|---------------------------------------------------------------------------|

|            | 0                                      |                                                                           |

|            | Start address<br>(mode register)       |                                                                           |

| M30        |                                        | Start address control                                                     |

| M26        |                                        | Start address control                                                     |

| M22        |                                        | Start address control                                                     |

| M18        |                                        | High logic level (+3 Vdc)                                                 |

|            | BHALT interrupt<br>(level 7, maskable) |                                                                           |

| M3         |                                        | System GND                                                                |

| M5         |                                        | Receive side of BHALT line transceiver                                    |

| M8         |                                        | BHALT interrupt request input (edge sensitive)                            |

|            | Memory                                 |                                                                           |

|            | Wiemory                                |                                                                           |

| M45        |                                        | Address line 11                                                           |

| M46        |                                        | High logic level, for PROMs                                               |

| M61<br>M33 |                                        | Socket set A, high byte, pin 23                                           |

| M48        |                                        | Socket set B, high byte, pin 27<br>Socket set B, low byte, pin 27         |

| M38        |                                        | Socket set B, how byte, pin 27<br>Socket set A, high and low byte, pin 20 |

| M63        |                                        | Socket set B, high byte, pin 23                                           |

| M32        |                                        | Socket set B, high and low byte, pin 20                                   |

| M62        |                                        | Socket set B, high and low byte, pin 22                                   |

| M35        |                                        | Socket set B, low byte, pin 23                                            |

| M40        |                                        | Socket set A, low byte, pin 23                                            |

| M43        |                                        | Socket set A, high and low byte, pin 2                                    |

| M42        |                                        | Socket set B, high and low byte, pin 2                                    |

| M36        |                                        | Address line 13                                                           |

| M34        |                                        | Socket set B, chip select, $(-CSKTB)$                                     |

| M37        |                                        | Socket set A, low byte, pin 27                                            |

| M39        |                                        | Socket set A, high byte, pin 27                                           |

| M44<br>M55 |                                        | Address line 12                                                           |

| M64        |                                        | System GND<br>Read strobe (-READ)                                         |

| M31        |                                        | Read strobe (READ)                                                        |

| M57        |                                        | Low byte write strobe (-WLB)                                              |

| M56        |                                        | High byte write strobe (-WHB)                                             |

| M41        |                                        | Socket set A, chip select, (-CSKTA)                                       |

| M60        |                                        | Socket set A, high and low byte, pin 22                                   |

| M47        |                                        | Socket sets A and B, high and low byte, pin 21                            |

| M59        |                                        | +5 Vdc voltage level                                                      |

## Table 2-2 Configuration Pin Functions (Cont)

| Pin | Function              | Description                         |

|-----|-----------------------|-------------------------------------|

|     | Parallel input/output |                                     |

| M49 |                       | Port B buffer direction control     |

| M51 |                       | System GND                          |

| M65 |                       | Port C buffered output, to J3 pin 5 |

| M53 |                       | Port C buffered output, to J3 pin 7 |

| M58 |                       | Port C PC4 output (8255A-5 pin 13)  |

| M54 |                       | Port C PC6 output (8255A-5 pin 11)  |

| M50 |                       | High logic level $(+3)$ Vdc)        |

| M52 |                       | Port A buffer direction control     |

|     |                       |                                     |

Table 2-2

Configuration Pin Functions (Cont)

## Table 2-3 Standard Factory Configuration

| Function                                                       | Jumpers<br>Installed<br>Between                                                                                                     |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Standard LSI-11 bus power<br>(No battery backup)               | M1 and M15<br>M1 and M7                                                                                                             |

| Wake up circuit enabled                                        | No jumpers                                                                                                                          |

| System clock                                                   | M2 and M11                                                                                                                          |

| Start address*<br>Start address 10000<br>Restart address 10004 | M30 and M26<br>M26 and M29<br>M22 and M18                                                                                           |

| Memories:                                                      |                                                                                                                                     |

| Memory map 0                                                   | M25 and M21<br>M21 and M29                                                                                                          |

| $2K \times 8$ INTEL EPROM                                      | M61 and M40<br>M59 and M61<br>M41 and M38<br>M45 and M47<br>M63 and M35<br>M59 and M63<br>M60 and M62<br>M34 and M32<br>M64 and M62 |

.

| Function                                                                                        | Jumpers<br>Installed<br>Between           |

|-------------------------------------------------------------------------------------------------|-------------------------------------------|

| Interrupts:                                                                                     |                                           |

| Time-out traps to restart address<br>except during LSI-11 bus IAK                               | M9 and M13<br>M14 and M10                 |

| SLU1 BREAK asserts BHALT and it<br>is received as level 7 interrupt<br>(vector 140)             | M20 and M17<br>M5 and M8                  |

| SLU2 60 Hz real-time clock<br>asserts LSI-11 BEVNT                                              | M19 and M23                               |

| Parallel I/O in mode 1:<br>Port A receive data, with STROBE A<br>on PC4<br>Port B transmit data | M49 and M51<br>M50 and M52<br>M65 and M58 |

#### Table 2-3 Standard Factory Configuration (Cont)

M53, M54, M55, M56, M57

\*Before use with Macro-ODT, the start address must be changed to 172000 as described in Table 2-4.

## 2.2.2 Wake Up Circuit

The module has an on-board power wake up circuit designed for use in systems without the LSI-11 bus power sequencing protocol. This circuit holds the BDCOK line negated until one second after +5 V power is applied. When the module is used in an LSI-11 backplane that has a power sequencing routine, the module wake up circuit must be disabled. To do this, a jumper wire is installed between M6 and M4. The jumper wire is removed when using power supplies without power sequencing. The module requires the +5 Vdc and +12 Vdc power supplies to have a rise time of less than 50 ms.

#### 2.2.3 Starting Address

The user selects the starting address for the microprocessor via wirewrap pins. When the module is powered up, the microprocessor loads this value into R7 (program counter) as the first fetch address. The wirewrap pins are M22, M26, M29, M30, and M18, and are defined in Table 2-1. The user can select from eight available starting addresses. Table 2-4 lists these available addresses and the jumper connections required for each address. The restart address is always the start address incremented by four. The wirewrap pin locations are shown in Figure 2-1.

#### 2.2.4 Interrupts

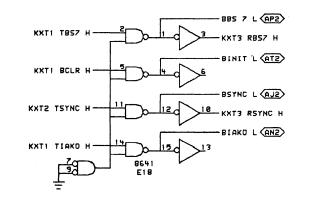

The SBC-11/21 implements a multilevel interrupt system that has eleven separate interrupts. See Table 5-3 for a complete list of system interrupts. Three interrupts, CTMER, BKRQ, and REVNT, are user configurable by means of jumper wires as shown in Figure 2-2 and are discussed here.

| Start<br>Address | Restart<br>Address | Connect<br>M22 to | Connect<br>M26 to | Connect<br>M30 to |

|------------------|--------------------|-------------------|-------------------|-------------------|

| 000000           | 000004             | M18               | M29               | M18               |

| 010000*          | 010004             | M18               | M29               | M29               |

| 020000           | 020004             | M29               | M18               | M18               |

| 040000           | 040004             | M29               | M18               | M29               |

| 100000           | 100004             | M29               | M29               | M18               |

| 140000           | 140004             | M29               | M29               | M29               |

| 172000           | 172004             | <b>M</b> 18       | M18               | M18               |

| 173000           | 173004             | M18               | M18               | M29               |

\*Factory setting. The start address should be selected in conjunction with the memory map configuration. Figure 2-6 shows how the available start addresses fit into the memory maps.

The CTMER interrupt is at the highest level (nonmaskable). It is caused by a time-out, that is, a failure to detect RRPLY during a fetch/read, write, or IAK transaction. For the factory configuration, -IAK is connected to the D input of flip-flop E7 via M9 to M13 jumper. This prevents setting that flip-flop and inhibits CTMER for time-outs occurring during IAK transactions. Such a condition could occur only if the peripheral that caused the interrupt failed to return BRPLY during the vector reading operation. See Chapter 8 for a discussion of external interrupts. To help the user evaluate the advantages and disadvantages of this jumper option, Figure 2-3 describes the sequence of events that takes place during the IAK time-out.

A time-out during IAK causes a zero vector to be read in by the microprocessor. This occurs in both examples described in Figure 2-3. If CTMER is allowed to set, this causes the second stacking of PC and PSW followed by a jump to restart.

The other two interrupts the user can select are BKRQ and REVNT. Their vectors and priorities are described in Table 5-3. All jumper combinations, which are "electrically correct" as described in Figure 2-2, are legal.

A description of some typical configurations follows to familiarize the user with the different combinations available.

| Install jumpers between | M14 and M8  |

|-------------------------|-------------|

| — <b>•</b>              | M13 and M12 |

|                         | M10 and M17 |

|                         | M24 and M20 |

|                         | M23 and M28 |

This arrangement allows the SLU1 BREAK input to set the -CTMER nonmaskable interrupt and trap to the restart address. The time-out (TMER) input sets the BKRQ level 7 maskable interrupt. The BHALT L bus signal is ignored. The SLU2 800 Hz line time clock and the BEVNT L bus signal enable the REVNT interrupt.

Figure 2-2 Interrupt Configurations

MR-7515

MR-7516

Install jumpers between

M10 and M5 M17 and M8 M13 and M12 M20 and M24 M23 and M24

This arrangement allows the BHALT L bus signal to set the -CTMER nonmaskable interrupt and trap to the restart address. The SLU1 BREAK input sets the BKRQ level 7 maskable interrupt, and only the BEVNT L bus signal enables the REVNT interrupt.

Install jumpers between M14 and M10 M13 and M12 M17 and M20 M5 and M8 M23 and M12

This arrangement allows the time-out (TMER) to set the -CTMER nonmaskable interrupt for all time-outs. The SLU1 BREAK or the BHALT bus signal set the BKRQ level 7 maskable interrupt, and the BEVNT L bus line is clamped low and therefore, no interrupts can be generated by BEVNT L.

#### 2.2.5 Parallel I/O

The parallel I/O is implemented with the 8255A-5 programmable peripheral interface (PPI) and connects to the user's interface through the J3 connector. Figure 2-4 illustrates the wirewrap pins used for the configuration of the parallel I/O. (These pins are defined in Table 2-1.) The dash lines in Figure 2-4 represent the factory configuration jumpers installed. (The wirewrap pin locations are shown in Figure 2-1.) The directions of port A and port B transceivers are dependent on the logic level connected to M49 and M52. Wirewrap pin 52 connects to port A through a 200 ns minimum rise time edge delay circuit. When M50 (+3 Vdc) is jumpered to pins M49 and M52, port A and port B buffers are inputs to the PPI from the J3 connector. When M51 (GND) is jumpered to pins M49 and M52, port A and port A and port B buffers are outputs from the PPI to the J3 connector.

Figure 2-4 Parallel I/O Configuration

The direction of port A and port B can also be controlled by a user's program. To make this possible, M58 and M54 must be jumpered to M49 and M52. The data outputs via port C will control the voltage levels at the direction control inputs to ports A and B. The software required to do this control is discussed in Chapter 6.

Wirewrap pins M65 and M53 can be jumpered to M49 and M52 to allow the user to control the direction of the transceivers via J3 connector pins 5 and 7. When not using wirewrap pins M58 and M65 or M54 and M53 to control the direction of ports A and B, jumpers connected between M58 and M65 and between M54 and M53 allow PC4 and PC6 to be used as inputs to the PPI from the J3 connector.

#### NOTE

If pins M65, M53, M58, or M54 are used for program control of port A or B, the user must ensure that the PPI and the buffer do not contend as driver output to driver output. If this condition is allowed to occur, damage to both drivers may result.

The programmable peripheral interface can function in three modes selected by software. The jumper configurations and the handshake signals for each of these modes are shown in Table 2-5, Table 2-6, and Table 2-7. See Chapter 6 for programming information.

#### 2.2.6 Serial I/O

The jumper options relating to the serial I/O determine the interrupt response of the system and were explained in Paragraph 2.2.4. All responses to the BREAK detection by SLU1 are listed in Table 2-8.

| PPI<br>Element | To Act<br>as Input | To Act<br>as Output                             | Program Control<br>via Port C |

|----------------|--------------------|-------------------------------------------------|-------------------------------|

| Port A         | M52 to M50         | M52 to M51                                      | M52 to M54 or M58             |

| Port B         | M49 to M50         | M49 to M51                                      | M49 to M54 or M58             |

| PC7            | Never an input     | Always an output                                |                               |

| PC6            | M54 to M53         | Never an external output                        |                               |

| PC5            | Never an input     | Always an output                                |                               |

| PC4            | M58 to M65         | Never an external output                        |                               |

| PC3            | Never an input     | Interrupt A<br>(vector 134)<br>Always an output |                               |

| PC2            | Always an input    | Never an output                                 |                               |

| PC1            | Never an input     | Always an output                                |                               |

| PC0            | Never an input     | Interrupt B<br>(vector 130)<br>Always an output |                               |

Table 2-5

Mode 0 Buffer Configuration (No Handshake)

| PPI<br>Element | To Act<br>as Input                                           | To Act<br>as Output                 | Program Control<br>via Port C |

|----------------|--------------------------------------------------------------|-------------------------------------|-------------------------------|

| Port A         | M52 to M50                                                   | M52 to M51                          | N/A                           |

| Port B         | M49 to M50                                                   | M49 to M51                          | M49 to M54 or M58             |

| PC7            | Never an input                                               | Indicates<br>buffer A full          |                               |

| PC6            | M54 to M53<br>(Acknowledge A)*                               | Never an external output            |                               |

| PC5            | Never an input                                               | Indicates<br>buffer A full          |                               |

| PC4            | M58 to M65<br>(Strobe A)                                     | Never an external output            |                               |

| PC3            | Never an input                                               | Interrupt A                         |                               |

| PC2            | Strobe B<br>in input mode<br>Acknowledge B in<br>output mode | Never an output                     |                               |

| PC1            | Never an input                                               | Buffer B full<br>on input or output |                               |

| PC0            | Never an input                                               | Interrupt B<br>(vector 130)         |                               |

# Table 2-6 Mode 1 Buffer Configuration (Strobed I/O)

\*User's hardware acknowledges receipt of data output by port A.

| PPI Element | Input Signal             | Output Signal        |

|-------------|--------------------------|----------------------|

| Port A      | Bidirectional bus        | If M52 to M54 to M53 |

| Port B      | Not used in mode 2       | Not used in mode 2   |

| PC7         | Never an input           | Output buffer A full |

| PC6         | Acknowledge A            | Never an output      |

| PC5         | Never an input           | Input buffer A full  |

| PC4         | Strobe A (if M65 to M58) | Never an output      |

| PC3         | Never an input           | Interrupt A          |

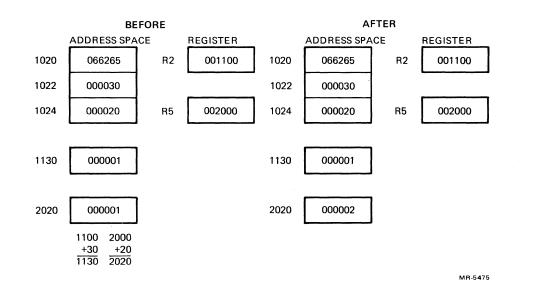

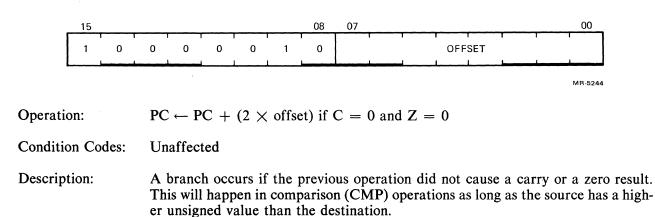

| PC2         | Always an input          | Never an output      |