# United States Patent [19]

### Levy et al.

#### [54] SECONDARY STORAGE FACILITY FOR DATA PROCESSING SYSTEMS

- [75] Inventors: John V. Levy, Maynard; Steven R. Jenkins, Medford; Victor Ku, Westboro; Peter McLean, Stow; Thomas N. Hastings, Arlington, all of Mass.

- [73] Assignee: Digital Equipment Corporation, Maynard, Mass.

- [22] Filed: Jan. 10, 1974

- [21] Appl. No.: 432,140

- [44] Published under the second Trial Voluntary Protest Program on March 23, 1976 as document No. B 432,140.

- [51] Int. Cl.<sup>2</sup> ...... G06F 3/00

- [58] Field of Search ...... 340/172.5

#### [56] References Cited

#### **UNITED STATES PATENTS**

| 3,618,041 | 11/1971 | Horikoshi   | 340/172.5 |

|-----------|---------|-------------|-----------|

| 3,623,022 | 11/1971 | Daye        | 340/172.5 |

| 3,643,223 |         | Ruth et al. |           |

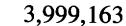

# [11] в **3,999,163**

# [45] Dec. 21, 1976

| 3,699,532 | 10/1972 | Schaffer et al  | 340/172.5 |

|-----------|---------|-----------------|-----------|

| 3,742,457 | 6/1973  | Calle et al.    | 340/172.5 |

| 3,760,364 | 9/1973  | Yamauchi et al. | 340/172.5 |

| 3,766,526 | 10/1973 | Buchanan        | 340/172.5 |

| 3,810,105 | 5/1974  | England         | 340/172.5 |

| 3,828,325 | 8/1974  | Stafford et al  |           |

Primary Examiner—Charles E. Atkinson Attorney, Agent, or Firm—Cesari and McKenna

#### [57] ABSTRACT

A secondary storage facility including magnetic tape, disk or drum units or other sequential access storage units. Each storage unit or drive connects to a controller by means of a device bus with asynchronous and synchronous paths. Status and controller information is coupled between the controller and a selected drive unit asynchronously over the asynchronous bus. Actual data transfers occur between the controller and a drive over the synchronous bus and between other units in the system and the controller using direct memory access or equivalent data transfers.

#### 32 Claims, 21 Drawing Figures

> CONTROL DATA(CD) 84 DATA SET 81 PARITY(CPA) 85 **8**0 FIG.4 >DS 86 ADDRESS SET 82 RS 87 ► CTOD 90 DEM 91 - TRA 92 CONTROL SET 83 ATTN 94 ►INIT 95 DATA SECTION 100 103 DATA PARITY (DPA) DATA SET IOI DATA (102 105 - SCLK 106 O7 WCLK RUN CONTROL SET 104 - EBL 110-► EXC - occ DEVICE BUS CONTROLLER DRIVE ÌI2

CONTROL SECTION 80

U.S. Patent Dec. 21, 1976 Sheet 5 of 19 3,999,163

U.S. Patent Dec. 21, 1976 Sheet 6 of 19 3,999,163

U.S. Patent Dec. 21, 1976 Sheet 9 of 19 3,999,163

U.S. Patent Dec. 21, 1976 Sheet 11 of 19 3,999,163

|                                             | DRIVE REGISTER                                     |  |  |  |

|---------------------------------------------|----------------------------------------------------|--|--|--|

| CONTROL & STATUS<br>REGISTER 140            | DVA FUNCTION GO                                    |  |  |  |

| STATUS<br>REGISTER 141                      |                                                    |  |  |  |

| ERROR<br>REGISTER 142                       | DCKUNSOPI DTEMLELAE AO PARRMR ILR IFE              |  |  |  |

| MAINTENANCE<br>REGISTER 144                 | WR OPTION SP DMD                                   |  |  |  |

| ATTENTION SUM-<br>MARY REGISTER 145         | ATA            |  |  |  |

| DESIRED TRACK<br>SECTOR<br>REGISTER 146     | TRACK ADDRESS SECTOR ADDRESS                       |  |  |  |

| DRIVE TYPE<br>REGISTER 147+                 | NSA TAPMOH7CH DRO SPR DRIVE I D                    |  |  |  |

| LOOK AHEAD<br>REGISTER 148+                 | CURRENT SECTOR SECTOR FRACTION                     |  |  |  |

| SERIAL NUMBER<br>REGISTER 250               | DRIVE SERIAL NUMBER                                |  |  |  |

| ECC POSITION<br>REGISTER 251                |                                                    |  |  |  |

| ECC PATTERN<br>REGISTER 252                 |                                                    |  |  |  |

| OFFSET<br>REGISTER 253                      | TIMING AMP MARGIN ECI HCI OFFSET                   |  |  |  |

| DESIRED CYLINDER<br>ADDRESS REGISTER<br>254 | CYLINDER ADDRESS                                   |  |  |  |

| CURRENT CYLINDER<br>ADDRESS REGISTER<br>255 | CURRENT ARM ADDRESS                                |  |  |  |

|                                             | FIG. 13                                            |  |  |  |

|                                             | CONTROL REGISTER                                   |  |  |  |

| CONTROL AND STAT<br>US REGISTER 133         |                                                    |  |  |  |

| CONTROL AND STAT<br>US REGISTER 134         | T-DLTWCEUPENEDNEMPGEMXFMPEOR IR CLRPAT BAI U02-U00 |  |  |  |

| WORD COUNT<br>REGISTER 136                  | WORD COUNT                                         |  |  |  |

| BUS ADDRESS<br>REGISTER 137                 | SYSTEM BUS ADDRESS                                 |  |  |  |

| <u> </u>                                    | FIG 12                                             |  |  |  |

FIG. 12

FIG. 15

FIG. 17

FIG. 19

U.S. Patent Dec. 21, 1976 Sheet 18 of 19

3,999,163

FIG. 20A

FIG. 20B

#### SECONDARY STORAGE FACILITY FOR DATA PROCESSING SYSTEMS

#### **BACKGROUND OF THE INVENTION**

This invention generally relates to data processing systems and more specifically to secondary storage facilities connected in such systems.

Secondary storage facilities comprise elements which are not an integral part of a central processing unit and 10 its random access memory element, but which are directly connected to and controlled by the central processing unit or other elements in the system. These facilities are also known as "mass storage" elements and include magnetic tape memory units, disk units and 15 drum units.

These facilities are also termed "sequential access storage units" because the information stored in one of these units becomes available, or is stored, only in a "one-after-the-other" sequence, whether or not all the 20 information or only some of it is desired. For example, it is usual practice to retrieve information from a disk unit on a "sector-by-sector" basis, even though only one of several information records in a sector is needed. Similarly, a physical record on a tape is analo- 25 such a facility in which the controller design and operagous to a sector on a disk and a complete physical record may be retrieved even though it may contain more than one relevant information record.

These devices are also "serial storage devices". In a serial storage device time and sequential position are 30 factors used to locate any given bit, character, word or groups of words appearing one after the other in time sequence. The individual bits appear or are read serially in time.

In modern data processing systems a secondary stor- 35 age facility includes a controller and one or more drives connected thereto. The controller operates in response to signals from the data processing system, usually on an input/output bus which connects together other elements in the system including the central processing 40 unit. A drive contains the recording medium (e.g., tape or a rotating disk), the mechanism for moving the medium, and electronic circuitry to read data from or store data on the medium and also to convert the data between serial and parallel formats.

The controller appears to the rest of the system as any other system element on the input/output bus. It receives commands over the bus which include command information about the operation to be performed, the drive to be used, the size of the transfer, 50 the starting address on the drive for the transfer, and the starting address in some other system element, such as a random access memory unit. The controller converts all this command information into the necessary signals to effect the transfer between the appropriate 55 drive and other system element. During the transfer itself, the controller routes the data to or from the appropriate drive and from or to the input/output bus or a memory bus.

In prior systems, each secondary storage facility was 60 unique. That is, a controller was designed to link a specific drive to a specific data processing system and a drive was designed to be connected to a specific controller. If a new drive was developed, a new controller was also developed. This was especially true if the new 65 drive was a different type of drive. For example, if a new magnetic tape drive was developed for a system, it was not possible to use an existing disk drive controller

for that system in conjunction with the new tape drive. Rather, it was necessary to design a new magnetic tape drive controller.

This procedure, of course, led to duplications of engineering effort, even when the same manufacturer 5 introduced new drives or data processing systems. Entirely new secondary storage facilities were usually developed. The uniqueness of each of the drives and controllers also led to user problems. If a user already had a system, he often had to replace both drives and controllers to obtain the benefits of a new drive. Furthermore, a controller was adapted to operate with one type of drive, so it was not possible to intermix the same types of drives (e.g., different disk drives) on one controller. This sometimes necessitated a different controller for each drive even though neither controller was used to capacity.

Therefore, it is an object of this invention to improve the operation of a secondary storage facility including a controller and a drive.

Another object of this invention is to provide such a facility in which the drive design is independent of a particular controller or data processing system.

Still another object of this invention is to provide tion are independent of the controlled drive.

Yet another object of this invention is to provide such a facility in which a single controller can control different types of drives.

Still yet another object of this invention is to provide such a facility in which a single drive can be used with different kinds of data processing systems.

#### SUMMARY OF THE INVENTION

In accordance with this invention, two distinct paths interconnect a controller and drive. One is an asynchronous drive control path including data, address and control lines. The signals over this path perform control functions and include control signals for effecting information transfers to or from addressed storage locations in the drive. The starting address in the drive and the size of the transfer are typical items of information which are sent to the drive over this path.

The second path is a synchronous data path which 45 transfers the data itself. It contains data and control lines. The control lines carry signals used for synchronizing the controller and drive, starting a data transfer and signalling any malfunctions which might occur during the transfer.

The signals on these two paths constitute a standard set of signals which can control disk drives, magnetic tape drives, magnetic drum drives and other sequential access or serial storage devices. If a system contains a controller constructed in accordance with this invention, then any drive which is constructed in accordance with this invention can be interchanged without altering the controller. Further, a set of these drives can be connected to another type of data processing system just by changing only a part of the controller. No changes are necessary to the drives. In fact, if the new data processing system already has a controller constructed in accordance with this invention, then drives from the former system can be connected without any further alterations. Thus, a controller is independent of the drive it controls and the drive is independent of the controller and system to which it connects.

This invention is pointed out with particularity in the appended claims. The above and further objects and 5

advantages of this invention may be attained by referring to the following description taken in conjunction with the accompanying drawings.

## BRIEF DESCRIPTION OF THE DRAWINGS

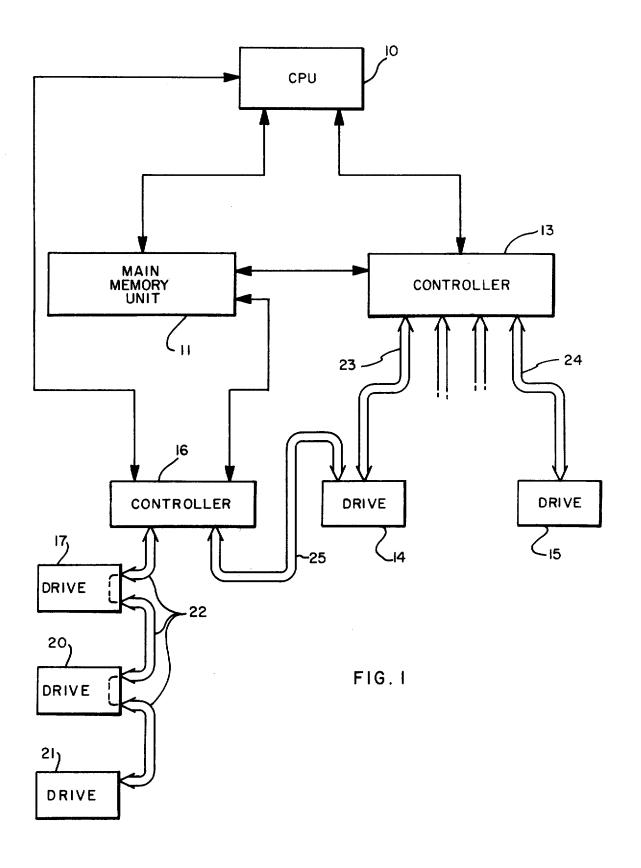

FIG. 1 is a generalized block diagram of a data processing system adapted to use this invention;

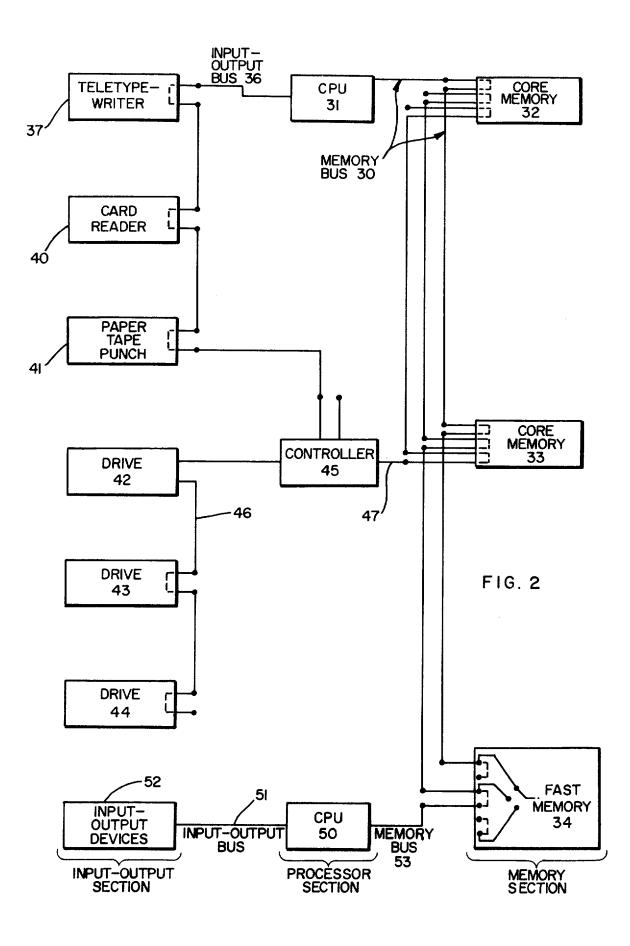

FIG. 2 is a block diagram of one type of data processing system shown in FIG. 1 in which separate memory and input/output buses link elements in the system;

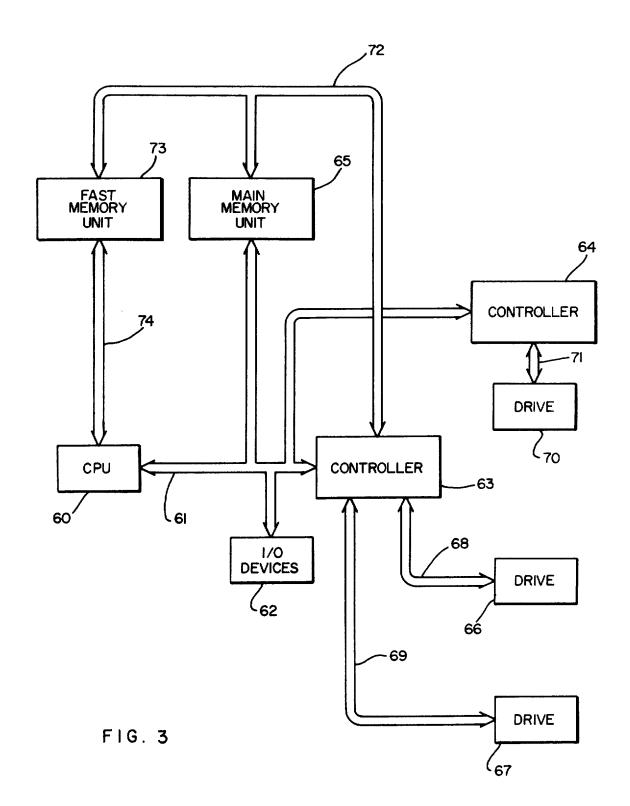

FIG. 3 is a block diagram of another type of data processing system shown in FIG. 1 in which a single bus is common to all elements in the system;

FIG. 4 depicts an interconnecting bus between a drive and controller in accordance with this invention. 15

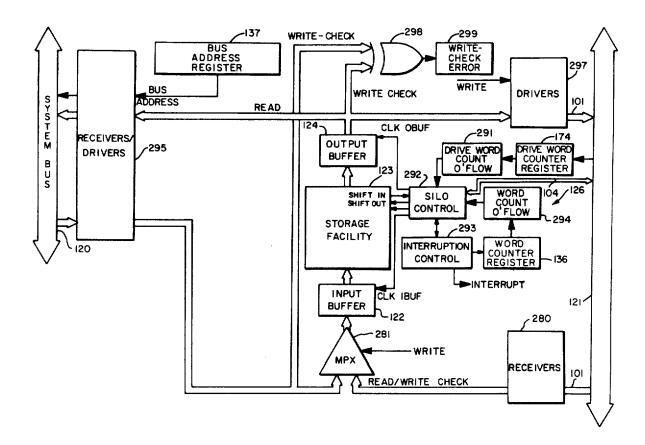

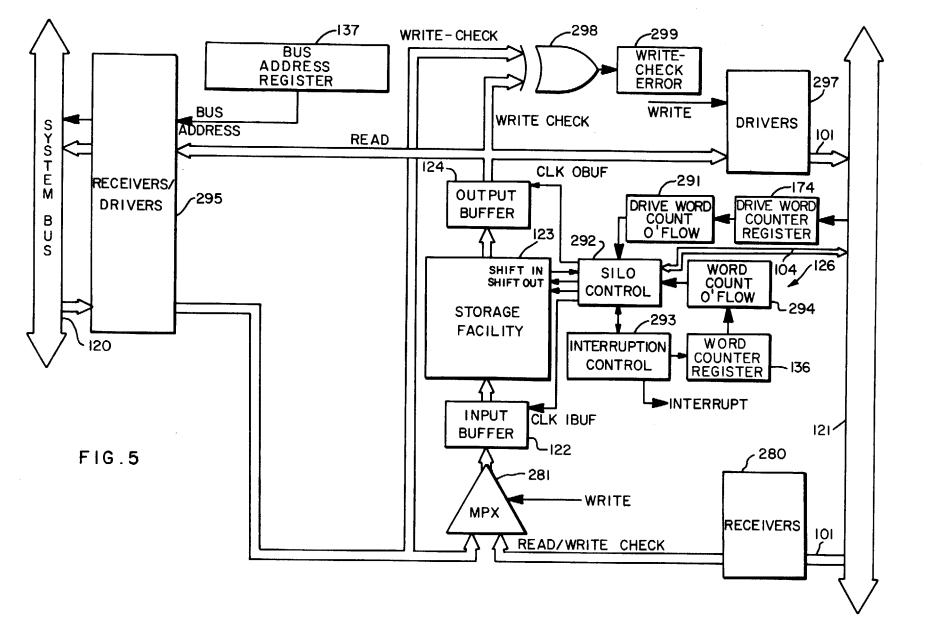

FIG. 5 is a block diagram of a synchronous data path in the controller as adapted for connection to a system as shown in FIGS. 2 or 3;

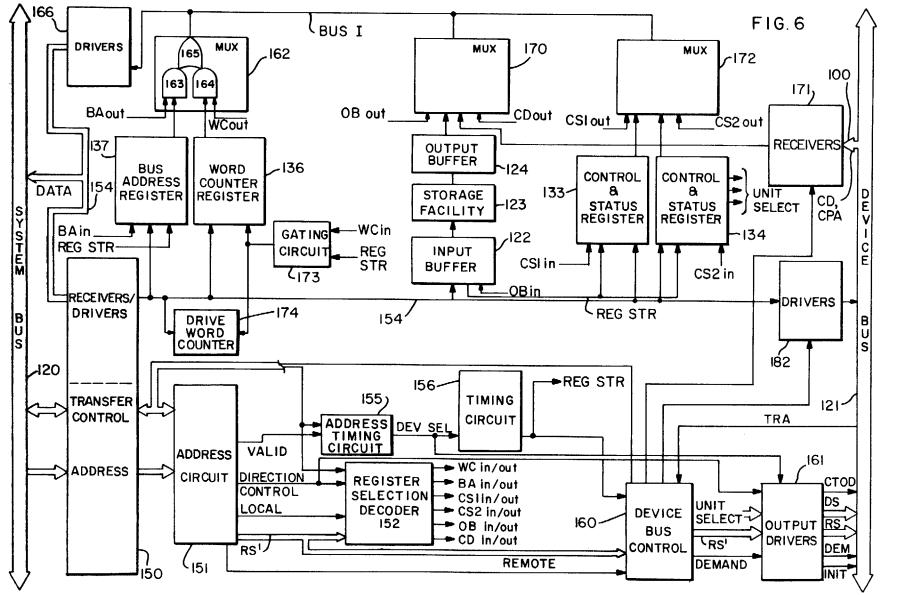

FIG. 6 is a block diagram of an asynchronous drive control path in a controller as adapted for connection 20 vice buses in several different configurations. If, for to a system as shown in FIGS. 2 or 3;

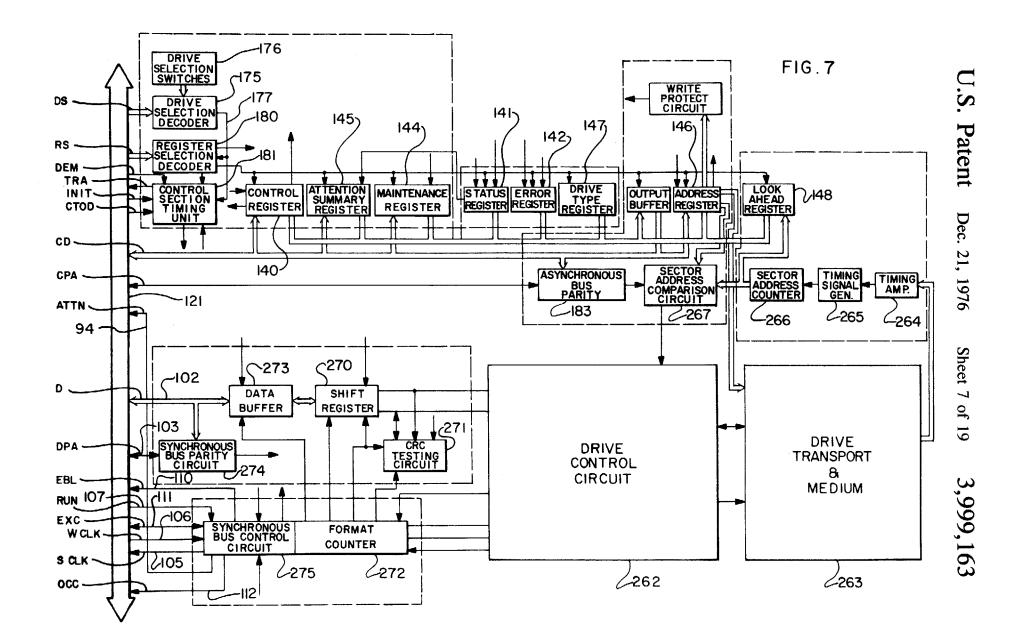

FIG. 7 is a block diagram of a drive constructed in accordance with this invention;

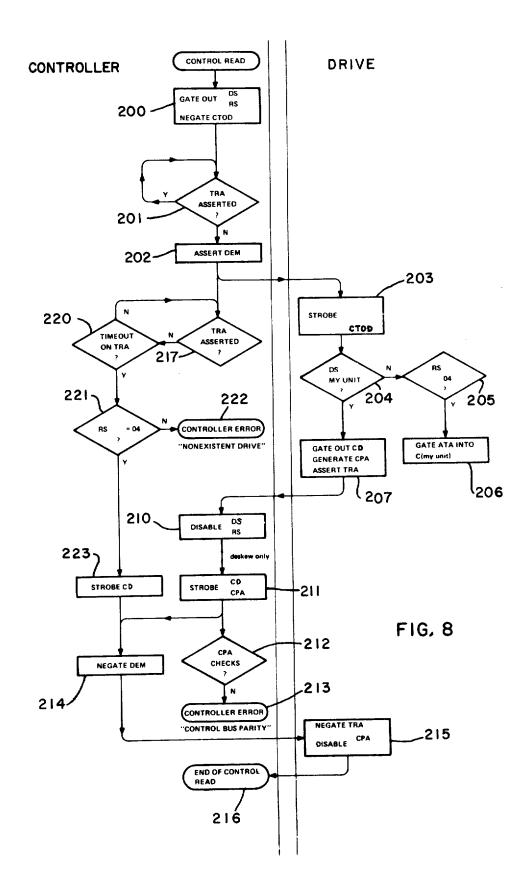

FIG. 8 is a flow chart of the operation for retrieving information in a register shown in FIG. 7;

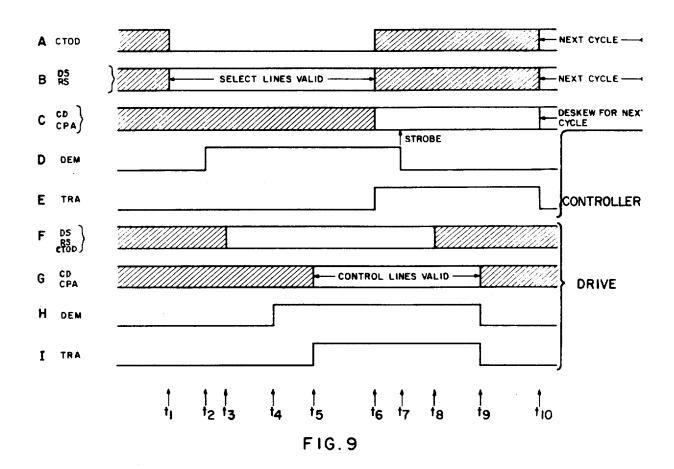

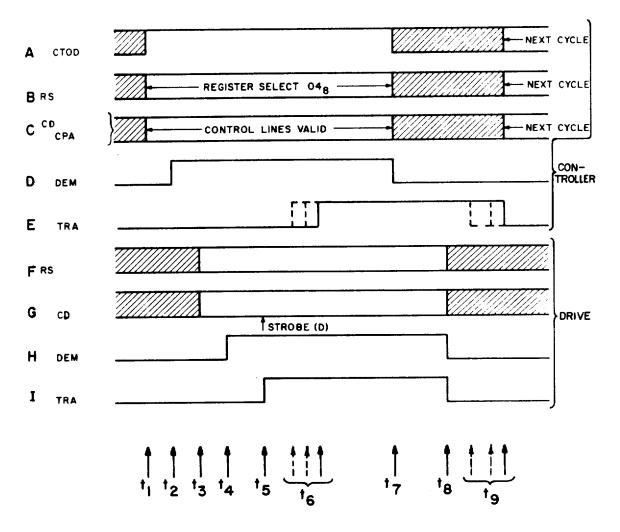

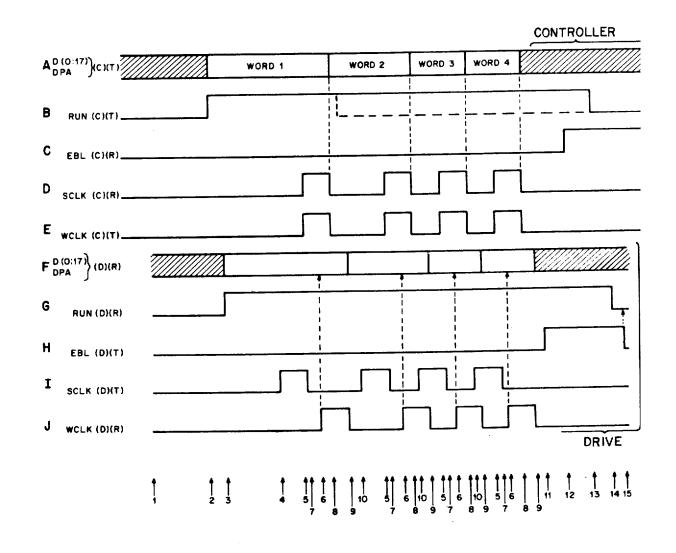

FIG. 9 includes timing charts corresponding to FIG. 8:

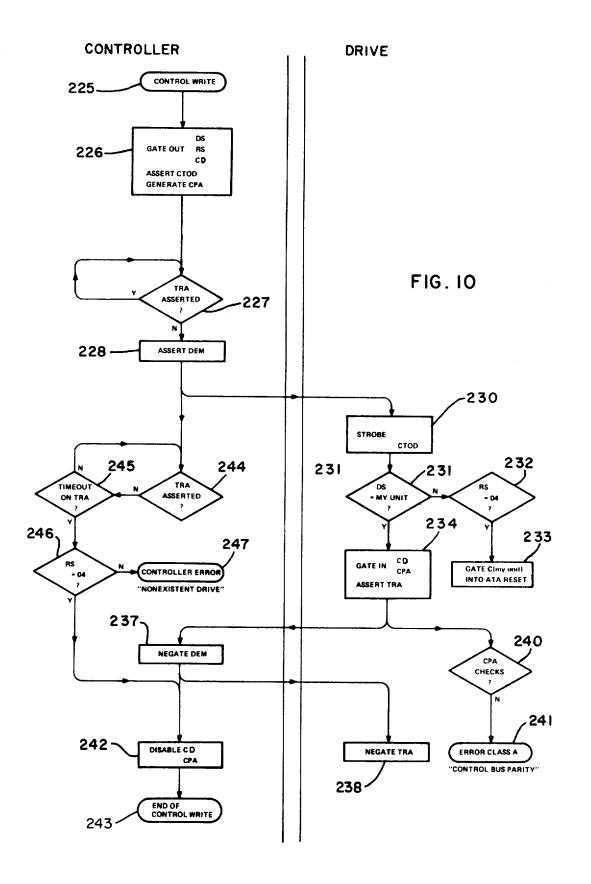

FIG. 10 is a flow chart of the operation for storing information in a register shown in FIG. 7;

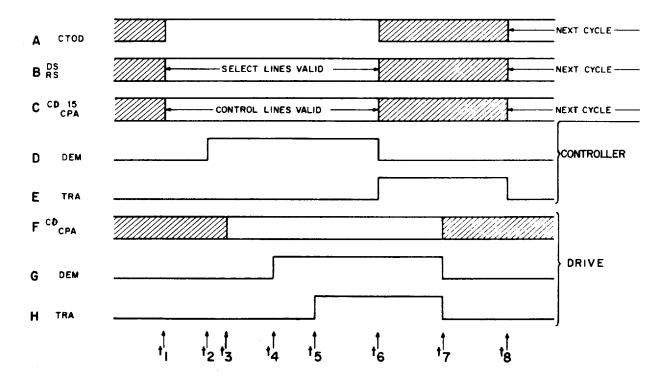

FIG. 11 includes timing charts corresponding to FIG. 30 thus in a "dual controller-single drive" configuration. 10;

FIG. 12 depicts the organization of registers adapted for use in a controller;

FIG. 13 depicts the organization of registers adapted for use in a drive;

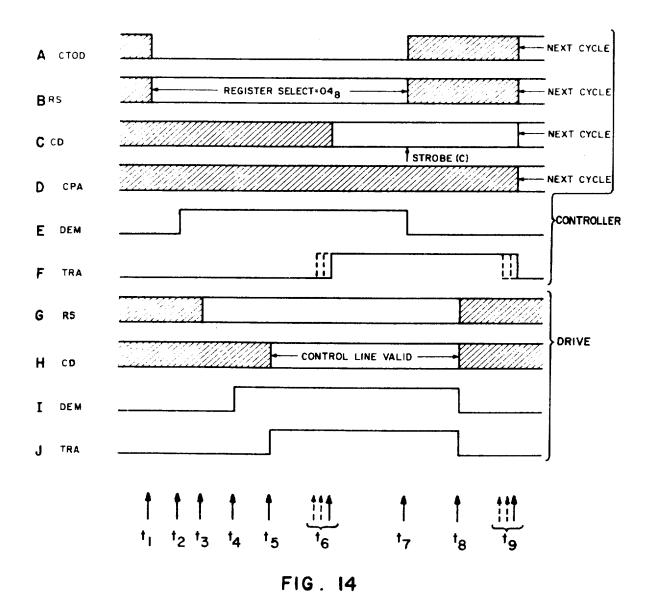

FIG. 14 includes timing charts for retrieving information from a specific register;

FIG. 15 includes timing charts for storing information in a specific register;

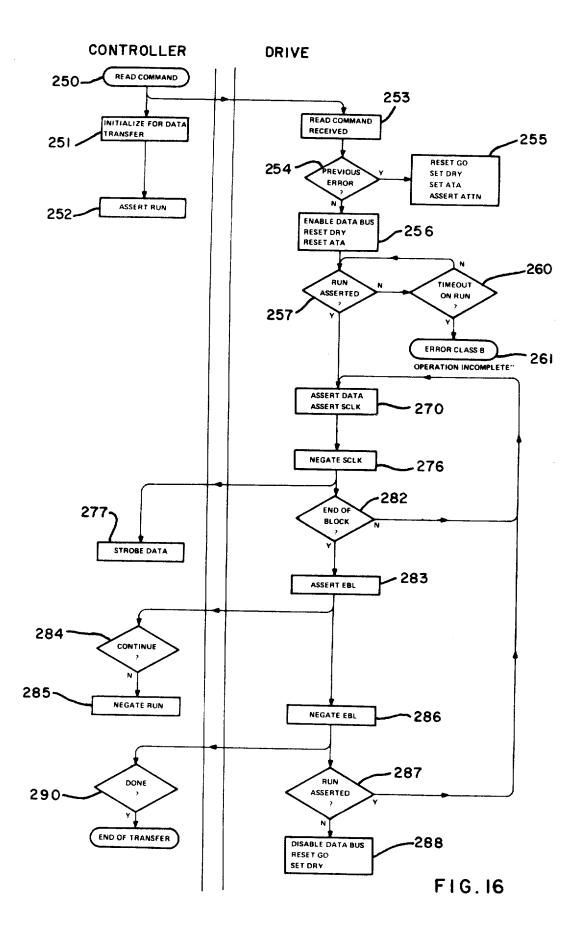

FIG. 16 is a flow chart of the operation of a controller 40 and drive to retrieve data from the drive;

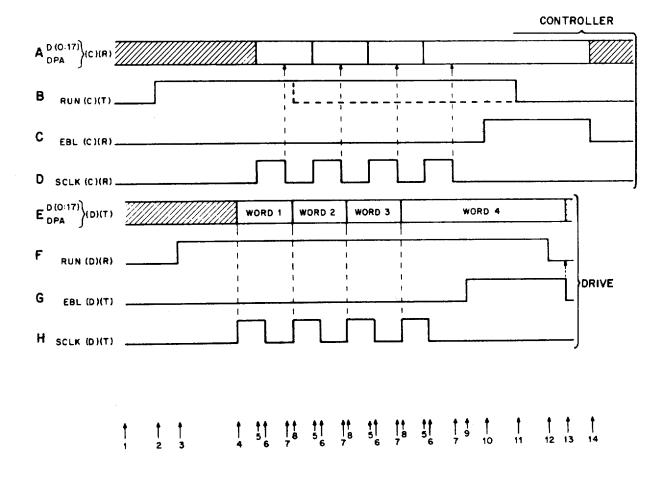

FIG. 17 includes timing charts corresponding to FIG. 16:

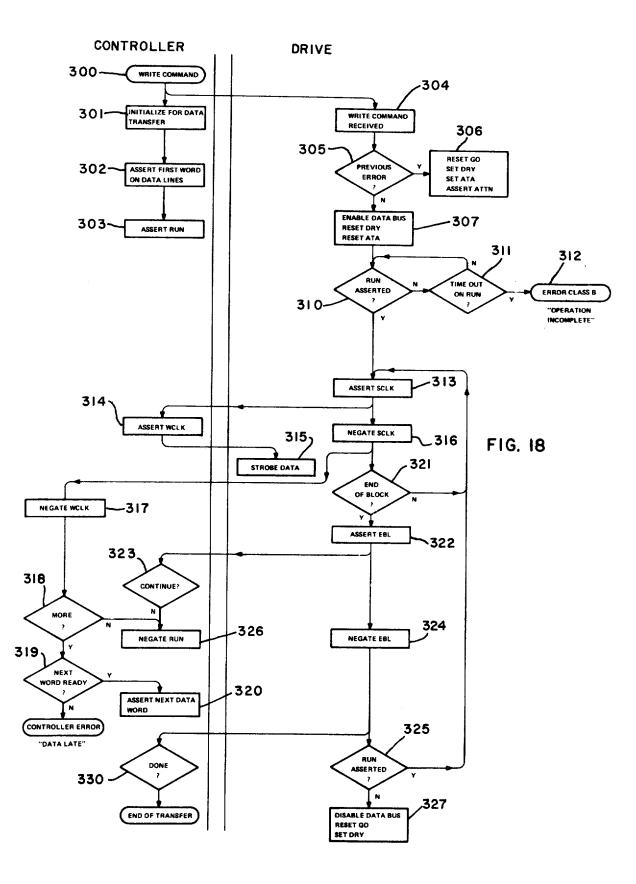

FIG. 18 is a flow chart of the operation of a controller and device bus to store data in the drive;

FIG. 19 includes timing charts corresponding to FIG. 18: and

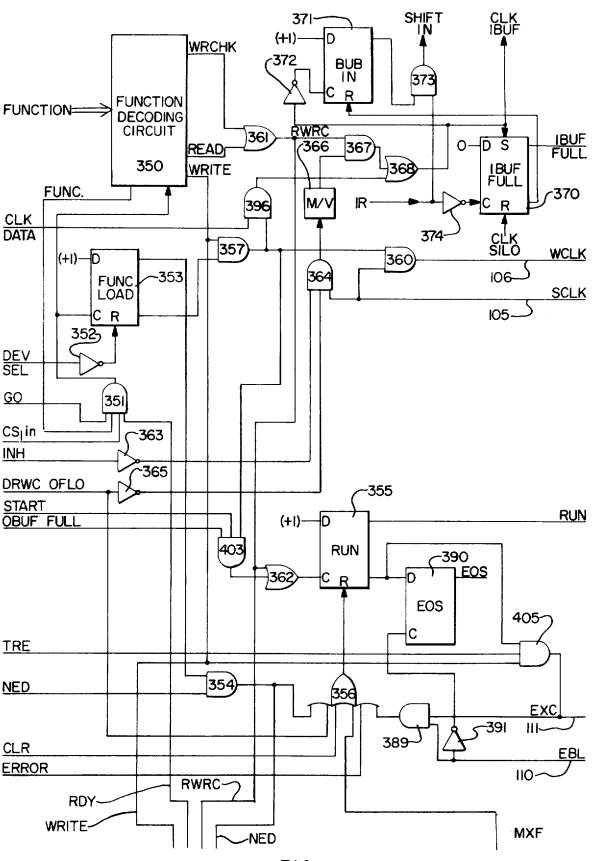

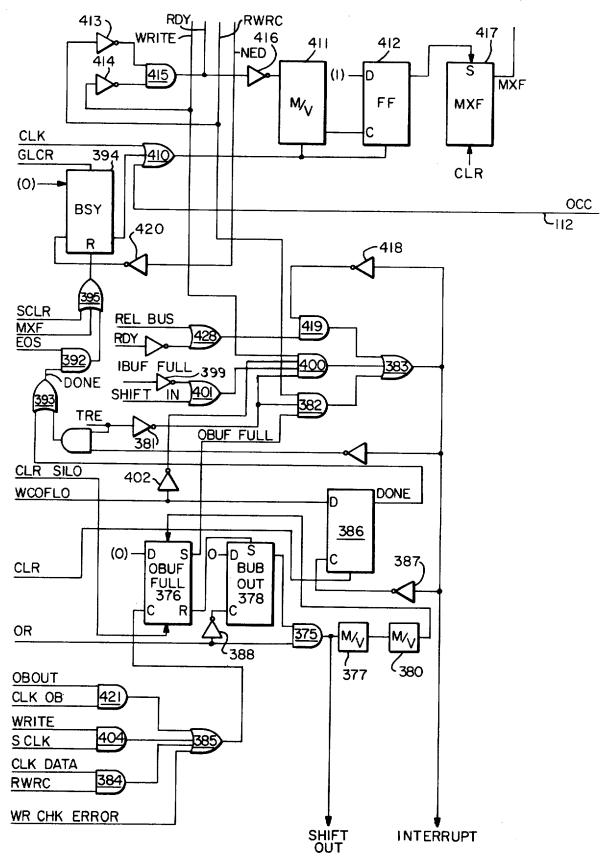

FIGS. 20A and 20B are detailed circuit diagrams of control circuits shown in FIG. 5.

### DESCRIPTION OF ILLUSTRATIVE **EMBODIMENTS**

I. General Description

FIG. 1 depicts the general organization of a data processing system comprising a central processing unit 55 (CPU) 10 and a main memory unit 11, normally a random access memory unit. Information also may be transferred to or from a secondary storage facility including a controller 13 and several drives, drives 14 and 15 being shown by way of example. Another such 60 storage facility includes a controller 16 and drives 17, 20 and 21. This facility is also coupled to the central processing unit 10 and the main memory unit 11.

As previously indicated, a "drive" includes a recording medium and the mechanical and electrical compo- 65 nents for recording data on or reading from the recording medium in the context of this invention. For example, it can comprise a fixed or movable head disk mem-

ory unit, a magnetic drum memory unit or a magnetic tape unit, as well as non-mechanically driven memory units. Timing signals derived from the medium normally synchronize data transfers with movement of the medium. A typical drive contains control, status, error

and other registers for controlling and monitoring drive operations.

A controller 13 or 16 may be located physically separately from the central processing unit 10 as shown in 10 FIG. 1 or may be an integral part of a central processing unit. Controllers serve as "interfaces" between the central processing unit and the drive. They contain the circuits for exchanging data with either the central processing unit 10 or the main memory unit 11. Buffer registers in the controller 13 or 16 compensate for the usually different transfer rates between the controller and main memory unit 11, on the one hand, and between the controller and drive, on the other hand.

Drives are connected to controllers by means of deexample, the controller 16 were connected to drive 17 only, the arrangement would be termed a "single drive" configuration. Actually, as shown in FIG. 1, the drives 17, 20 and 21 are interconnected by a device bus 25 22 which is threaded from one drive to the next. This is an example of a "daisy-chain" configuration. Device buses 23 and 24 connect drives 14 and 15, respectively, in a "radial" configuration. Drive 14 is linked to the controller 16 by way of a device bus 25; the drive 14 is

It will become apparent from the following discussion that this invention is adapted for all these configurations. The user of a system will determine his own specific configuration. It also will become apparent that if 35 drive 14 is one type of magnetic disk memory unit, drive 15 can be another unit of the same type, a magnetic disk memory unit of another type, or even a magnetic tape or magnetic drum unit or other type of sequential access memory. Moreover, drives 17, 20 and 21 could be directly connected to controller 13 without any modification to either the controller 13 or any of the drives.

This interchangeability and resultant flexibility result because each of the device buses 22, 23, 24 and 25 45 contains a standard set of corresponding conductors for transferring signals according to this invention, notwithstanding the drive connected to the device bus or the data processing system which is involved. As new drives are developed with improved storage media such as tapes and disks with higher recording density or even 50 of new media, it will only be necessary to have the drive itself conform to the standard set of signals, no new

controller development will be necessary. New drives will also be independent of the type of data processing systems to which they connect. FIGS. 2 and 3 depict diverse types of data processing systems. The nature of the data processing system has no effect on the drive itself. Although these two data processing systems form no part of the invention, the fact that they are diverse types of systems emphasizes the flexibility that this invention provides to secondary storage facilities. Also, specific examples of data processing systems will facilitate an understanding of the detailed discussion of this invention.

FIG. 2 illustrates a data processing system containing two separate data paths. The system is also segregated into input-output, processor and memory sections. A memory bus 30 connects a first central processing unit (CPU) 31 with a memory section including, for example, a core memory 32, a core memory 33 and a fast or volatile memory 34. An input-output bus 36 connects the central processing unit 31 with several input-output devices such as a teletypewriter 37, a card reader 40, 5 and a paper tape punch 41. The memory bus 30 and the input-output bus 36 carry control, address and data signals in two directions. The signals on each bus are transferred in parallel, as distinguished from serial transmission.

The central processing unit 31 can also control the transfer of data between the memory section and a secondary storage facility. In FIG. 2 this storage facility comprises drives 42, 43 and 44 connected to a controller 45 by a device bus 46 in a daisy-chain configuration. <sup>15</sup> In accordance with this invention, the controller 45 receives control information over the input-output bus 36 to be processed by an asynchronous drive control path within the controller 45. A synchronous data path in the controller may transfer data to the memory bus <sup>20</sup> 30 or, as shown, to a second memory bus 47. Thus, transfers between the secondary storage facility and the memory section occur only with minimum use of the input-output bus 36 and the central processing unit 31 25 because data can be transferred directly through the controller 45 to the memory section. As also shown in FIG. 2 a second central processing unit 50 connects through an input-output bus 51 to other input-output devices 52. The central processing unit 50 also con-30 nects to the memory section through a bus 53, which enables the unit 50 to use the memory units 32, 33 and 34 in common with the processing unit 31 including data supplied to the memory section by the secondary storage facility.

As previously stated, this is an example of a data processing system which has separate input-output and memory buses. In operation, the central processing unit 31 might require some program stored in the drive 42. A second program already stored in the memory sec- 40 tion would contain the necessary instructions to transfer a command to the controller 45 over the bus 36 to identify a particular drive, such as the drive 42, the starting location in the drive (e.g., the track and sector numbers in a disk memory unit) and other necessary 45 information, as known in the art. Once the controller 45 receives that information, it retrieves data from the drive 42 and then transfers it to the memory bus 47 directly for storage and subsequent use by the central processing unit 31 or even the central processing unit 50 50.

Analagous transfers occur in a system using a common bus to interconnect the system elements. Such a system is shown in FIG. 3 and comprises a central processing unit (CPU) 60 and a first common bus 61. The 55 bus 61 contains address, data and control conductors. It connects the central processing unit 60 in parallel with input-output devices 62 and controllers 63 and 64 associated with two secondary storage facilities.

The system in FIG. 3 includes a main memory unit 65 60 connected to the bus 61. Data transfers can occur over the bus 61 between the main memory unit 65 and any of the drives 66 and 67 connected to the controller 63 in a radial configuration by device buses 68 and 69, respectively, or a drive 70 connected in a single drive 65 configuration to controller 64 by a device bus 71. These transfers occur over the bus 61 without requiring the CPU 60 to perform an interruption routine.

The controller 63 has an additional connection for another bus 72 which is identical to the bus 61. The bus 72 is coupled to a second part of the main memory 65, which is a "dualport" memory. This bus 72 also connects to a fast memory 73, which is coupled to the central processing unit 60 through dedicated bus 74.

With this data processing system, the central processing unit 60 can transfer a command to the controller 63 over the bus 61. The controller 63 then can prepare a 10 drive, such as the drive 66 for an operation by transferring control information over the drive control path in the device bus 68. Data can then pass over the synchronous data path in the device bus 68 through the controller 63 and then either onto the bus 61 or, for more efficient operation, over the bus 72 directly into the memory 65 or 73. If the transfer is being made to another one of the input-output devices 62, the data may pass over the bus 61.

The signals over each of the device buses 46 in FIG. 2 and 68, 69 and 71 in FIG. 3 are the same. This means that the controllers 45, 63 and 64 have the same circuitry at their respective device bus connections. The only required differences between the controllers are those necessary for connection to the data processing system buses.

As the drives are connected only to device buses and all device buses are the same, the drive circuits are independent of any particular system. Of course, different data processing systems have different word sizes which can range from 8 bits to 36 bits or more. Circuit modifications in the controllers or the drives can be made to accomodate these different word sizes. At this point it is sufficient to consider the use of a basic 18-bit word. No modification is necessary for a central processing unit using 18-bit words. To provide a 36 bit 35 word for other data processing systems the controller merely needs to concatenate pairs of 18-bit words. Other arrangements can be used when the data processing system word length is not an exact multiple of a drive word length.

II. The Device Bus

To understand the interaction between a controller and device it is helpful to discuss first the specific signals which appear on the device bus and the functions each performs. A device bus, with its signal designations, is shown in FIG. 4; and the same mnemonic identifies a wire or group of wires and the signals they carry. Every device bus has the same construction. A drive control section 80 contains conductors segregated into a data set 81, an address set 82 and a control set 83. Within the data set 81 there are bidirectional control data (CD) wires 84 for carrying control and status information between a controller and any of its respective drives. A bidirectional CPA wire 85 carries a parity bit. The control information includes commands which control the operation of the drive. Some of the commands initiate data transfer and include READ, WRITE and WRITE CHECK commands. Other commands initiate control operations such as positioning heads in a movable head disk drive, winding a tape in a magnetic tape drive or clearing registers in a drive.

Within the address set 82, there are drive selection (DS) wires 86 and register selection (RS) wires 87. The DS wires 86 carry DS signals from a controller to provide information for selecting a drive for an ensuing transfer of control or status information. A controller also transmits the RS signals. Within the drive identified by the DS signals the RS signals define a specific register which is to be involved in a transfer.

The control set 83 includes a controller-to-drive transfer (CTOD) wire 90. When a controller asserts a CTOD signal (i.e., a logic ONE signal level), the following transfer over the data set 81 is from the controller to the selected register in the selected drive. When 5 the CTOD signal is not asserted, (i.e., is at a logic ZERO signal level), the transfer is from the selected drive register to the controller.

A demand (DEM) wire 91 and a transfer (TRA) wire 92 carry asynchronous timing signals. Specifically, the 10 controller puts a DEM signal onto the wire 91 to initiate a transfer of control information. The selected drive transmits the TRA signal to indicate the receipt of control information or the availability of status information

Whenever any drive requires some interaction with the controller and data processing system, it transmits an ATTN signal onto a single ATTN wire 94 which is common to all drives. Usually the controller responds by interrupting the data processing system. 20

AN INIT signal on a wire 95 serves as a facility resetting signal. Upon receipt of the INIT signal, a drive immediately terminates its operation, clears all error conditions and becomes available to the controller and system for further operations.

A synchronous data section 100 shown in FIG. 4 carries blocks of data at high transmission speeds between the controller and drives. These blocks of data are carried in response to READ, WRITE and WRITE-CHECK commands previously sent to a controller and 30 its respective drive with related transfers occuring over the control section 80. The data section 100 also serves as a link for control signals which initiate and terminate the block transmissions. Bidirectionally conducting wires in a data set 101 comprise data wires 102 for 35 carrying the data itself and a data parity (DPA) wire 103. A control set 104 includes a SCLK wire 105 and a WCLK wire 106. The drive uses timing signals derived from the recording medium to produce SCLK signals on the SCLK wire 105 to synchronize the read- 40 ing of data from the data wires 102 and DPA wire 103 when the data moves to the controller. When the data is to be stored in the drive, the controller receives SCLK signals and transmits WCLK signals back to the drive. The WCLK signals control the writing of data 45 registers, which are called "local" registers. They inonto the recording medium in the device.

A RUN signal controls the initiation of a data transfer and the overall duration of the transfer; it appears on a RUN wire 107. The controller asserts the RUN signal to start a data transfer in accordance with a command 50 which was previously transferred to the drive over the drive control section 80. Subsequently, circuits in the drive use the RUN signal to determine the time for terminating the transfer. An EBL signal transmitted by the drive on a wire 110 signals the end of a "block". 55 ber of words to be transferred; it counts each data word Any transfer terminates if, at the end of an EBL signal, the RUN signal is not asserted. Otherwise, the transfer operation continues through the next "block". In this connection the term "block" has a conventional meaning as applied to magnetic tape memory units and is 60 either sending or receiving the data. equivalent to a "sector" as that term is conventionally applied to magnetic disk memory units. Thus, in this description, "block" is used in a generic sense to indicate a conveniently sized group of data bits to be sent 65 as a unit.

An EXC wire 111 in the synchronous data section 100 is a bidirectional wire for carrying exception (EXC) signals. When the drive transmits the EXC sig-

nal, some error has occurred during the transmission. This signal remains asserted until the last EBL signal during the transfer terminates. An EXC signal from a controller, on the other hand, causes the drive to terminate any action it was performing in response to a command.

There is also an occupied (OCC) wire 112. Whenever a drive begins to perform a data transfer over the synchronous section 100, the drive transmits an OCC signal to a controller. This positively indicates that a drive connected to that controller is busy with a data transfer.

With this understanding of the signals which appear on a device bus, it is possible to discuss generally the circuits in a controller. Looking first at the synchro-15 nous data path in FIG. 5, it will be apparent that only one drive connected to a controller may respond to a READ, WRITE or WRITE-CHECK command at any given time because the data section 100 (FIG. 4) is connected to all the drives a controller supervises. Data transfers pass between a system bus 120 and a device bus 121. The system bus might be the memory bus 30 in FIG. 2 or either of the buses 61 or 72 in FIG. 3. Reference numerals used to designate wires in FIG. 4 are applied to corresponding wires in FIGS. 5 through 25 7 as all device buses are the same.

Incoming data from either a system bus 120 in response to a WRITE command or the data section 101 of a device bus 121 in response to a READ or WRITE-CHECK command is loaded into an input buffer 122 for transfer into a storage facility 123. When the facility 123 is filled, the first word in is loaded into an output buffer 124. A data path control circuit, generally 126, then either effects a transfer onto the device bus 121 for transfer to the device or a transfer onto the system bus 120 for transfer to a designated location in the data processing system. The controller also contains the necessary circuits for generating the appropriate address signals to identify a memory location which either stores the data to be transferred to the controller or which is to receive the data from the drive.

III. Drive Control Path

A typical drive control path is shown in FIGS. 6 and 7. The controller shown in FIG. 6 contains several clude:

1. Control and status registers 133 and 134 for receiving commands and for receiving and storing operational status information for the controller;

2. The output buffer 124; this register has a connection 124 (FIG. 5) to the drive control path and its contents may be retrieved under system control for diagnostic and other purposes;

3. A word counter register 136 for storing the numas it is transferred and disables the drive upon the completion of the transfer;

4. A bus address register 137 for storing the address of a location connected to the system bus 120, which is

FIG. 7 depicts a fixed-head disk memory unit as a typical drive for purposes of explanation. Such a drive contains the following registers, which are called "remote" registers:

1. A control register 140 analagous to the control and status register 133 (FIG. 6); it stores commands and other control information; the control register 140 and the control and status register 133 can be considered as a single register in which stages are distributed among the controller and each drive connected to the controller;

2. A status register 141 for storing non-error status bits and a summary error bit; one bit position, for ex-5 ample, indicates whether the drive is in a ready state;

An error register 142 for storing error information; other drives may contain more than one such register;

4. A maintenance register 144 for storing information useful in diagnostic and maintenance operations;

5. A stage in attention summary register 145; each drive has one stage for indicating whether it has generated an ATTN signal; this register can be considered as having individual stages distributed among each of the drives.

6. A desired track and sector address register 146 for storing the number of the drive track and sector at which a transfer is to start;

7. A drive type register 147 for storing information concerning the nature of the drive; and

8. A look-ahead register 148 for storing information concerning the actual rotational position of the disk.

Other registers which might be included in a fixedhead or other type of drive include:

of the device serial number; and

2. ECC position and pattern registers in drives having error-correcting codes for storing the position of an ECC pattern burst and the pattern itself.

Moving-head magnetic disk memory units normally 30 will include:

1. An offset register for storing the amount of head offset in a moving head disk memory unit; such a register might also store information for controlling the enabling of header information or error correction 35 circuits.

2. A desired cylinder address register for storing the cylinder address which is to be reached; and

3. A current cylinder address register for storing the actual head position over the disk in terms of a disk 40 cylinder.

These registers are discussed more fully in connection with the operation of the drive control path.

All operations of controller and drives in a secondary storage facility constructed in accordance with this 45 register and the direction of the transfer. Each "coninvention are under the control of information stored in these registers in the controller (FIG. 6) and the drive (FIG. 7). For example, a transfer of data between the recording medium and a memory unit requires the formation into the local and remote registers. The identification of the drive to be involved in the transfer is loaded into the control and status register 134 (FIG. 6). The register 134, in turn, produces corresponding unit select signals. The bus address register 137 receives the 55 initial memory address while the word counter register 136 receives a number (usually in two's complement) defining the number of data words in the block to be transferred.

Once the control and status register 134 contains the 60 drive information, additional transfers are made to specific remote registers in that drive (FIG. 7). The track and sector address is loaded into the track and sector address register 146. If the disk were a movinghead disk, then other information might be loaded into 65 offset and desired cylinder address registers. Still other information concerning the function to be performed would be loaded into the control register 140. As ap-

parent, each of these transfers involves operations for loading information into drive registers from the control section 80 in the device bus 121. Thus, they can be designated "writing" operations. It is also necessary, from time to time, to retrieve the

contents of certain registers to learn the status of the drive and controller (i.e., perform a "reading" operation). For example, the status register 141 contains a DRY bit position which indicates whether the drive is 10 busy. The look-ahead register 148 may be read to determine the actual position of the disk.

Any time there is to be a transfer into or out of a local or remote register, address signals and transfer control signals appear on the system bus 120 shown in FIG. 6 15 including one set of direction control signals which indicate whether the transfer involves a reading or writing operation. For example, the transfer control signals discussed in U.S. Pat. No. 3,710,324 include C0 and CI direction control signals. CONI and CONO

signals discussed in U.S. Pat. No. 3,376,554 perform 20 the same function. When the information is to move into a register, the information may appear on the system bus data lines simultaneously with or slightly after address and transfer control signals appear on the ad-1. A serial number register for displaying part or all 25 dress and transfer control lines, depending upon the characteristics of the particular system.

> A receivers/drivers circuit 150 in a controller (FIG. 6) comprises buffer circuits and pass the address signals and direction control signals to an address circuit 151. Each register has a unique address which the address signals designate and the address circuit 151 uses the address signals to indicate whether the address is for a register in the controller or in an associated drive. Thus, these signals implicitly indicate whether the designated register is a local or remote register and the address circuit 151 produces a corresponding LOCAL or REMOTE signal. Register selection signals (RS') from the circuit 151 pass to a register selection decoder 152 and to a device bus control circuit 160.

A. Local Transfers

When the address signals indicate that a register in the controller is to be selected (i.e., the address circuit 151 generates a LOCAL signal), the decoder 152 subsequently produces a signal which selects both the local ductor" from the decoder 152 is really two wires; one wire corresponds to a writing operation; the other, a reading operation. Thus, the decoder produces a "WCin" selection signal when a word count is to be central processing unit to transfer several items of in- 50 stored in the word counter register 136. To read the contents of the word counter register 136, the decoder would produce a "WCout" selection signal.

> Other transfer control signals from the bus 120, usually delayed for some period following the appearance of the address signals, enable the decoder 152 to produce an appropriate selection signal and enable an address timing circuit 155. These transfer signals may be either DATI, DATO, CONI or CONO signals in the system of FIG. 2 or MSYN and SSYN signals in the system of FIG. 3. The address timing circuit 155 produces a delayed DEV SEL signal in response to a first synchronizing signal if the address circuit has validated the incoming address and produced a VALID signal. The DEV SEL signal energizes a timing circuit 156.

> The timing circuit 156 transmits a REG STR pulse after the appearance of a signal from the decoder 152 and, in a writing operation, loads information on control data wires 154 into the selected local register. The timing

circuit 156 may also couple the DEV SEL signal to the device bus control circuit 160 to produce another transfer control signal on the system bus 120 to indicate that the transfer is complete (when such a signal is necessary for a system operation).

To read the contents of the word counter register 136, for example, the address and transfer control signals cause the decoder 152 to transmit the WCout selection. This signal is one input to a multiplexer 162 which selectively couples the output of either the word 10 register in a drive, the address circuit 151 produces a counter register 136 or the bus address register 137 onto an intermediate bus designated BUSI. Specifically, the multiplexer 162 includes an AND gate 163 which receives the output from the bus address register 137 and an BAout signal from the decoder 152; and an 15 AND gate 164 which receives the output of the word counter register 136 and the WCout signal from the decoder 152. An OR gate 165 couples the selected one of the AND gates 163 and 164 onto the BUSI bus and then, through drivers 166, onto the system bus 120.

The multiplexer 162 is shown diagramatically only. In an actual circuit there would be an AND gate associated with each bit position in each of the registers 137 and 136. The BAout and WCout signals would then enable all the AND gates associated with the respective 25 121 as RS, DS and CTOD signals respectively. In addiregisters.

The drive control path shown in FIG. 6 also contains multiplexers 170 and 172. Multiplexer 170 selectively couples signals onto the BUSI bus either from the output buffer 124 or from the drive coupled from the 30 device bus through receivers 171 in response to OBout or CDout signals from the decoder 152. CS1out and CS2out signals from the decoder 152 control the multiplexer 172 so it selects and couples the output of either the register 133 or the register 134 onto the BUSI bus. 35

While reading control information from a local register, the device bus control circuit 160 may, if the system requires it, issue another synchronizing control signal which indicates the transfer is complete. Once the REG STR signal terminates and the optional syn- 40 chronizing control signal appears, the controller and system have completed the transfer (i.e., the selected local register has been read).

The steps for loading information into a local register are similar. The direction control signals from the ad- 45 dress circuit 151 indicate a writing operation. Thus, an input conductor for a selected register, rather than a multiplexer, is energized by the decoder 152. When new information is to be stored in the word counter register 136, the decoder 152 produces the WCin sig- 50 nal. The information to be stored appears on the bus 154 which is equivalent to the control data wires 84 in FIG. 4. The coincidence of the REG STR and WCin signals loads the word counter register 136.

Normally the selection signal from the decoder 152 55 and the REG STR signal from the timing circuit 156 are applied directly to input gating circuits in their respective registers. FIG. 6, however, shows a gating circuit 173 whose output is applied to both the register 136 and a drive word counter register 174. The register 174 60 stores the number of words transferred between the controller and drive. As shown in FIG. 6, this register is not connected to the BUSI bus, so its contents cannot be read.

Thus, transfers of control information to or from 65 local registers use the same sequence as the transfer of similar information to or from analogous registers in other units connected to an input-output bus or a com-

mon bus in the two disclosed systems. When the transfer involves a remote register, the controller must route the control information to involve the appropriate remote register. The control information still passes through the controller, but the controller must additionally control each transfer with the designated register.

**B.** Remote Transfers

When an address on the system bus 120 designates a REMOTE signal which is applied to the device bus control 160. In response to this signal the device bus control 160 is enabled to pass the RS' signals from the address circuit 151 to the output drivers 161. The UNIT SELECT signals from the control and status register 134 and the direction control signals are also inputs to the drivers 161.

The appearance of a valid address, with its concomitant VALID signal, and the transfer synchronizing sig-20 nal from the system bus 120 produce the DEV SEL and the REG STR signals as previously discussed. The DEV SEL enables the output to the device bus drivers 161 to couple the RS', UNIT SELECT, and direction control signals onto wires in the control set 83 of the device bus tion, the REG STR signal causes the control 160 to produce a DEMAND signal which passes through the enabled output drivers 161 as the DEM signal.

Now referring to FIG. 7, a drive selection decoder 175 in each drive compares the incoming DS signals with signals from drive selection switches 176 to determine whether the DS signals identify that particular drive. If they do, the decoder 175 produces an enabling signal on a conductor 177 to activate a register selection decoder 180 and a control section timing unit 181. The register selection decoder 180 receives the RS signals and in response produces signals which are coupled to the selected register in the drive, e.g., registers 140, 141, 142, 144, 145, 146, 147 or 148. These selection signals enable subsequent timing signals from the timing unit 181 to effect a transfer. The timing unit 181 also receives the DEM and CTOD signals from the bus 121 and transfers a TRA signal onto the bus indicating that the drive has moved control information onto the data set 81 or that the data on the data set 81 has been stored.

Referring again to FIG. 6, the device bus control 160 receives the TRA signal and then either enables data to pass through the receivers 171 in response to the CDout signal from the register selection decoder 152, or enables the drivers 182 if the decoder has produced the CDin signal. In addition, the control 160 can produce the previously discussed optional synchronizing signal for controlling the transfer between the system and the controller. Thus, the decoder 152 produces a CDin or CDout signal during each remote register transfer.

A more thorough understanding of these remote register transfers will be obtained from a discussion of reading and writing operations in some detail in terms of the signal transfers between the controller in FIG. 6 and the registers in FIG. 7.

**1 Reading Operation**

FIG. 8 is a flow chart of the steps necessary to read control information in a remote register while FIG. 9 illustrates the timing of such signals. Step 200 and Charts 9A and 9B represent the process of placing the appropriate values of the DS, RS and CTOD signals onto the device bus 121 from the output drivers 161 shown in FIG. 6 at time t1. If a TRA signal from a previous transfer with any drive connected to the controller is asserted, the controller waits for it to terminate as represented by step 201. At the completion of 5 this interval, step 202 and Chart 9D indicate that the device bus control 160 and the output drivers 161 couple the DEM signal onto the device bus at time t2.

Now referring to FIGS. 6, 7, 8 and 9, the signals on the drive at time t3 (Chart 9F), the interval from t1 to 13 representing a bus signal propagation delay. After a similar delay from time t2, the DEM signal is received at the drive at time 14 (Chart 9H), causing the control signal as represented by step 203. The drive selection decoder 175 will have already determined whether the drive is the selected drive. If the DS signals do not designate the drive (step 204), the drive in step 205 summary register. If a register other than the attention summary system is designated, but the DS bits do not select a drive, no further steps occur in that drive. If the attention summary register is addressed, then the ATA signal is sent (step 206) as described later.

Assuming that the DS signals identify the drive in FIG. 7, the control section timing unit 181 at time 15 loads the information from the selected register onto the control data lines in the bus 121 as disclosed in step 207A and Chart 9G. At the same time a control bus 30 parity circuit 183 generates a parity bit which is loaded onto the CPA wire 85 and the unit 181 transmits the TRA signal at time t5 as shown in Chart 9I.

When the controller receives the control information and the TRA signal as shown in Charts 9C and 9E at 16, 35 the device bus control 160 may immediately disable the DS, RS and CTOD signals (Charts 9A and 9B and step 210). After a short delay, the device bus control 160 opens the receivers 171 at time t7 to load the control through the multiplexer 170 and drivers 166 onto the system bus 120 (step 211). When the system receives the control information, the control 160 terminates the DEM signal (Chart 9D and step 214) so that the drive senses the transition of the DEM signal (Chart 9H) and 45 terminates the TRA signal (Chart 9I and step 215) and the control data and parity signal. Once the controller senses the termination of the TRA signal at time t10(Chart 9E), the transfer is complete (step 216).

As apparent, the control information at the receivers 50 171 in FIG. 6 is valid from time t6 to time t10 (Chart 9C). The TRA signal can therefore be used to synchronize operations on the system bus 120 and the device bus 121.

Referring to FIG. 8, once the controller transmits the 55 DEM signal in step 202, it begins timing a response interval. This is represented by steps 217 and 220. If the drive transmits the TRA signal before the predetermined time interval expires, the interval timing operation terminates in step 217. If not, the controller, at the 60 end of this interval, determines whether the attention summary register 145 is being read (step 221). If it is not, then no device has responded and a non-existent drive has been designated. Thus, step 221 branches to step 222, and the controller sets an NED bit position 65 described later in the control and status register 134 (FIG. 6). If the attention summary register 145 has been addressed, step 221 branches to step 223, and all

the information on the data set 81 is sensed before terminating the DEM signal at step 214.

If a parity error is discovered in step 212 during a transfer of information from a drive (step 211), step 213 causes an MCPE bit position in the status and control register 133 to be set.

2 Writing Operation

FIG. 10 is a flow chart for writing control information into a remote register while FIG. 11 is a corresponding DS, RS and CTOD wires from the controller arrive at 10 timing diagram. When the controller receives a command to write control information (step 225) it transfers DS, RS and CTOD signals onto the control information lines and a parity signal onto appropriate wires in the control section 80. This occurs at step 226, section timing unit 181 to load (or strobe) the CTOD 15 which corresponds to time t1 as shown in Charts 11A, B and C. The control information passes through the drivers 182, shown in FIG. 6, under the control of a gating signal from the device bus control 160, which responds to the DEV SEL signal as previously disdetermines whether the RS bits designate the attention 20 cussed. The control signals pass through the output drivers 161.

> If a TRA signal from a previous transfer with any drive connected to the controller is still asserted, the controller waits for it to terminate as shown in step 227 25 and discussed with respect to the reading operation. Then at time  $t^2$  the controller, in step 228, transmits the DEM signal onto the device bus 121 as shown in Chart 11D. Steps 230, 231, 232 and 233 are analogous to steps 203, 204, 205 and 206 in FIG. 8. The control information on the data set 81 arrives at the drive at time 13 (Chart 11F) and the DEM signal arrives at time t4 (Chart 11G). In response to these signals, the control section timing unit 181 in the drive (FIG. 7), in step 234 and at 15 in Chart 11H, loads the control information into the designated register and the CPA signal into the parity circuit 183. In steps 240 and 241, the circuit 183 provides a parity error signal if an error exists to set a PAR bit position in the error register 142.

At 15 the drive also transmits the TRA signal (Chart information and parity signal from the device bus 121 40 11H), which arrives back at the controller at t6 (Chart 11E). In response, the device bus control 160 turns off the drivers 182 and the output drivers 161 thereby effectively disconnecting the controller and drive by terminating all signals from the controller on the device bus at t6 as shown in Charts 11A, B and C and including the DEM signal (Chart 11D). At t7, Chart 11F shows that the control information and parity signal from the controller on the data set 81 terminate at the drive as does the DEM signal. Thus, at 17 the drive terminates the TRA signal (Chart 11H) and the controller senses this termination at t8 (Chart 11E). This completes the writing operation and permits initiation of another cycle.

Now referring to FIG. 10, after the controller asserts the DEM signal in step 228, it starts timing a response interval like that in a reading operation. Steps 244, 245, 246 and 247 are analogous to steps 217, 220, 221 and 222 in FIG. 8. If the attention summary register 145 is being loaded, then the information remains on the control data wires until the end of the time-out period as described later. The controller then completes the writing operation by removing the control information in step 242 to complete the operation with step 243.

C. Local and Remote Registers

Local registers in the controller and remote registers in the drives store control and status information. Some registers, such as the word counter register 136, contain one item of information, such as the word count, so 5

Ill bit positions or stages are interrelated. Other regisers store diverse information in one or more groups of egisters. For example, the control and status register 133 has a stage for indicating special conditions and inother stage for indicating that a transfer related error has occurred. Registers in which all stages are interreated may be arranged so either data can only be rerieved from them by the system (i.e., read-only regiser) or data can be retrieved or altered in them by the ner category are denoted by a cross to the right of the designation in FIGS. 12 and 13. In registers which conain independent stages, each stage may be arranged so ts data either may only be retrieved (i.e., a read only stage) or may be retrieved or altered (i.e., a read/write 15 stage). A cross above a stage indicates that it is a readonly stage.

The particular assignment of bit positions or stages made in the following discussion of local and remote registers is for purposes of explanation only. Other 20 assignments may be made. Further, certain of the defined stages and the information they represent may be omitted and other stages representing other information may be substituted or added.

1 Control and Status Register 133

The control and status register 133 is a multi-stage or multiple bit position register. Some stages are located in the controller; others are located in each drive in what is designated the control and status register 140. The controller stages are shown in FIG. 12. One such 30 stage is an SC stage which is set to indicate that (1) a transfer related error has occurred (i.e., a TRE bit position is set), (2) that an MCPE bit position has been set because a parity error was detected during a remote register reading operation as previously discussed, or 35 (3) that some drive connected to the controller has produced an ATTN signal on the wire 94 in the control set 83 (FIG. 4). The controller resets the SC bit position in response to a system resetting (INIT) signal on the wire 95 in the control set 83, to a controller clear- 40 ing signal which sets a CLR bit position in a control and status register 134 or in response to the correction of the condition causing the drive to assert the ATTN signal. This stage is located in the controller itself.

The TRE stage is a read/write stage in the register 45 133. It is set in response to the occurrence of a transfer related error signalled by certain stages in the control and status register 134 or in response to the simultaneous assertion of EXC and EBL signals on the wires 110 and 111 in the control set 104. The previously 50 discussed INIT and CLR signals can reset the stage. In addition, the system can clear the TRE bit position by means of a local register writing operation.

As previously indicated, the controller checks the parity signal on the wire 85 in the data set 81 (FIG. 4). 55 If a parity error is detected, the MCPE bit position is set. The MCPE stage is a read only stage. Both INIT and CLR signals cause it to be cleared. A local register writing operation may also clear this stage.

A PSEL bit position is used when the synchronous 60 stage sets, the TRE stage in the register 133 is set. data path can be selectively coupled to either of two system buses. It is cleared when the selected system bus is also the bus which connects to the control data path. When this stage is set, data is routed to the other system bus. An INIT or CLR signal or a local register writing 65 operation will clear the stage to thereby restore the connection between the system bus which connects to the control data path.

The control and status register 133 shown in FIG. 12 also contains A17 and A16 bit positions which are read/write stages. These positions can augment the contents of the bus address register 137 if the address is not sufficient uniquely to identify a location. Either the INIT or CLR signal or a local register writing operation can clear these two bit positions.

An RDY bit position indicates the condition of the synchronous data path in the controller and comprises system (i.e., read/write register). Registers in the for- 10 a read/write register stage. It sets when power is applied and at the completion of each transfer operation over the synchronous data path. Whenever a data transfer function is received in the register 133 with the GO bit set, the RDY stage is reset.

An IE bit position is set by a local register writing operation to cause the controller to interrupt the system connected to the system bus 120 in response to the assertion of a RDY or ATTN signal. It enables other controller circuits to respond to various error conditions or to the completion of an operation to produce an interrupting signal. This bit position is reset when the system interruption circuitry recognizes the interruption or in response to an INIT or CLR signal. If a local register writing operation resets this stage, the 25 controller can not interrupt the system and any pending interruptions are cancelled.

Several FUNCTION signals designate a specific operation the drive is to perform. They are received by the controller, although the corresponding register stages are located in the control and status register 140 in each drive. These signals define various functions which may involve a data transfer. The register stages are cleared by an INIT or CLR signal. A DRIVE CLEAR operation defined by the FUNCTION bits causes the stages to be cleared. Typical FUNCTION signals also produce the previously discussed READ, WRITE and WRITECHECK operations or a SEARCH operation to locate a particular area in the drive without a data transfer taking place.

When a GO bit position is set, the drive performs the operation identified by the FUNCTION bits. The INIT signal will clear the GO bit and abort any operation in response to a command. The GO bit is also cleared when an operation over the synchronous data path is completed. Setting the GO bit also can reset various error condition bit positions as discussed below.

2 Control and Status Register 134

All stages in the control and status register 134 are located in the controller. Individual register stages reflect the operation and status of the controller, especially error conditions which might exist. A DLT bit position is one example of such a stage which is set when the controller is not able to supply or accept in a timely fashion a data word over the synchronous data path during a writing or reading operation, respectively. In a two-port operation when the PSEL stage in the system 133 is set, an INIT signal at the second system bus also sets the DLT stage if a transfer is then occurring over that second bus. Any time the DLT

A WCE bit position is set during a WRITE CHECK operation when the recorded data from the drive does not match the corresponding word in a memory location in the system. This stage sets the TRE stage in the register 133.

A UPE bit position is set during a data transfer in response to a WRITE or WRITE-CHECK command over the synchronous data path when a parity error is detected on the system bus 120. The TRE stage also sets in response to such a parity error.

An NED bit position indicates a non-existent drive and is set by the controller as described with reference to FIGS. 8 and 10. This also causes the TRE stage to be 5 set.

If a system location specified by the controller does not exist, the controller senses an incompleted transfer operation and thereby sets an NEM bit position and the TRE stage.

When the system sends a READ, WRITE or WRITE-CHECK command while the controller is already involved in another transfer, the controller sets a PGE bit position in the register 134. This causes the TRE stage to set.

Any time a drive does not respond to a data transfer command within a predetermined time, the controller sets MXF and the TRE bit positions.

An MPE and the TRE bit positions set if the controller detects a parity error during a transfer over the 20 device bus in response to a READ or WRITE-CHECK COMMAND.

All the foregoing stages in the register 134 can be cleared by any one of four procedures. First, a system resetting signal clears the stages. Secondly, the system 25 can issue a clearing command to set the CLR bit position as discussed later. Thirdly, the system can load the register 133 with the combination of FUNCTION bits which designate a data transfer operation and set the GO bit position. Finally, a word can be loaded into the 30 register 133 which clears the TRE bit position. In addition, the UPE and MXF bit positions can be cleared directly by a local register writing operation.

OR and IR bit positions in the register 134 are used in diagnostic operations and are set when the output buf- 35 and GO bits previously described with respect to the fer register 124 is full or the input buffer register 122, in the synchronous data path is empty.

A system resetting signal, a local register writing operation to set the CLR bit, or an operation for reading the information in the respective buffers clears the 40 OR stage or sets the IR stage.

Sometimes it is desirable to use either even or odd parity coding during a transmission over the data paths. A PAT bit position in the status register 134 can be set to produce odd parity operations. A local register writing operation alters the state of the stage.

Normally the bus address register 137 is incremented or altered during each transfer to identify system locations in succession. A BAI stage in the register 134 can 50 be set during a local register writing operation to inhibit the incrementing steps, provided the controller is not then involved in a data transfer. This condition is indicated when the RDY stage is set. Either a system resetting signal or CLR signal can clear the BAI stage.

The U02 through U00 bit positions receive their information during a local system writing operation. These stages are cleared in response to a system resetting signal or to a CLR signal. Once a transfer starts, they can be altered without interfering with the trans- 60 methods do not clear the error indicators themselves. fer.

3 Word Counter Register 136

The word counter register 136 initially stores the initial word count, i.e., the number of words to be involved in a data transfer. The number stored is usually 65 the two's complement of the actual word count and the register, which is a counter, is incremented during each transfer of a word over the synchronous data path be-

tween the controller and the system. When the register 136 reaches ZERO (i.e., the register overflows or issues a CARRY), the requested transfer is finished. This register can only be cleared by transferring a ZERO value to it through a local register writing operation.

4 Bus Address Register 137

Locations in the system from which data is retrieved or to which data is sent over the synchronous data path are identified by the bus address register 137. The A16 and A17 bit positions in the register 133 augment this 10 information as noted above. The register 137 is a counter which is incremented in response to each data word transfer in order to identify the successive locations corresponding to the successive words involved in a transfer operation. Either a system resetting or CLR

signal clears the register 137.

5 Data Register

A data register can be addressed, primarily for diagnostic purposes although may be no physical register. Specifically, if the data register is addressed during a local register writing operation and the IR signal indicates that the storage facility 123 is not full, the information on the control data wires 84 is loaded into the input buffer 122 (FIG. 6). This condition is represented by an OBin signal. On the other hand, an OBout signal is produced when the data register is addressed during a local register reading operation and OR signal indicates that data is present. The OBout signal causes the information in the output buffer 124 to be loaded onto the system bus 120.

6 Status and Control Register 140

Now referring to FIG. 13, which contains in diagrammatic form, the organization of typical registers in a drive, the control register 140 stores the FUNCTION control and status register 133. Whenever the register 133 is loaded, the controller produces a remote writing operation to load FUNCTION and GO bits into corresponding stages in the designated drive. A DVA stage is set whenever the drive is available for operation and is a read-only position.

7 Status Register 141

The status register 141 contains the status of the drive. The contents of any bit position in the register to produce even parity coding and decoding and reset 45 141 are dependent only upon monitoring circuits within the drive. This register cannot be loaded from the controller.

Within the register 141, an ATA bit position and an ERR bit position are related. The ERR bit position is set whenever any other stage in the error register 142 sets. This, in turn, sets the ATA bit position in the drive, which is also set whenever operations in response to a SEARCH command are complete. A system resetting or a CLR signal will clear the ATA and ERR 55 stages. It is also possible to clear the ATA stage by clearing the corresponding location in the attention summary register 145 as described later or by using a local writing operation to transfer a new command to the drive which sets the GO bit position. The last two

Whenever an operation in response to a SEARCH command is in progress, a PIP stage is set. Seeking operations, as apparent, are applicable only to a moving-head disk memory or equivalent units. Once the operation is completed, this stage is cleared.

Still referring to the register 141, MOL and DRY stages are set when the drive is in an operating condition; that is, the MOL stage is set when the drive power is on and, in the case of a continuous moving medium such as a disk or drum, the medium is up to speed. The DRY stage is set to indicate that the drive can accept a command while the drive is not in an operating condition; the DRY bit position is cleared in response to a data transfer command with the GO bit position set. Any change of state of the MOL stage also causes the ATA stage in the drive to be set.

A WRL stage is set whenever an address in the desired track/sector register 146 identifies a track which 10 is protected against writing operations. Otherwise, this stage is cleared.

An LBT bit position is set during a transfer over the data set 101 (FIG. 4) to or from the highest sector (i.e., the "last" sector) on a drive. This stage can be cleared 15 by a system resetting a CLR signal, by transferring a new address into the register 146 or by clearing the drive.

8 Error Register 142

position is set whenever circuitry in the drive detects an error during a reading operation over the data set 101 in response to a READ or WRITE-CHECK command.

If the power supply voltage for the drive falls below a safe level, a UNS stage sets; it is reset only when the 25 specific drive have been identified, the LBT stage in the supply voltage is above the minimum safe level.

During a data transfer operation circuits in the drive monitor index marks on the medium. If some number (e.g., three) of index marks pass after a data transfer command and the RUN signal is still absent, an OPI 30 stage is set indicating a controller failure. In a disk unit, the passage of the number of index marks signifies more than two disk revolutions. If a SEARCH command does not terminate within two disk revolutions, a drive failure has occurred and the OPI stage is also set. 35

The occurrence of any timing fault, such as the loss or addition of index or clock pulses, causes a DTE stage to set

If the WRL bit position in the register 141 is set and a writing operation is attempted, the drive sets a WLE 40 drive and an SPR bit position could indicate the presstage.

A remote transfer which loads a non-existent address into the desired track address register 146 causes the drive to set a IAE stage.

An AO bit position is set if, when the last block of the 45 last track of a disk is read, the word counter register 136 in the controller does not indicate that the transfer is finished.

Any time a parity error is detected, either on the synchronous data path or the asynchronous control 50 can be used in reducing disk latency times to thereby path, a PAR stage in the error register 142 sets.

If the GO bit position in the register 140 is set and the system attempts to load the control register 140, the error register 142 or the desired address register 146, an RMR stage sets.

Whenever the register selection (RS) signals do not identify a register in a designated drive, the drive sets an ILR stage.

FUNCTION bits which define an operation that the drive cannot perform cause an ILF bit position to be 60 drives with removable disks. The contents of the regisset.

The error stages are set immediately upon the condition being detected. This may result, in some cases, in an immediate interruption of the system, or in an interruption at the end of the complete transfer. In either 65 case, the drive asserts the ATTN signal at the appropriate time to initiate the interruption. With the exception of the UNS stage, the other stages can be cleared by a

system resetting signal or CLR signal or in response to a remote register writing operation designating the register 143. In addition, a DRIVE CLEAR command code sent to the register 140 clears the corresponding stages in the designated drive.

9 Maintenance Register 144

The maintenance register 144 is used for various diagnostic operations to facilitate an analyses of facility operation. It may contain, for example, a WRCLK bit position or stage to aid in simulating drive clocking pulse, an SP bit position to aid in simulating a sector or block pulse and other similar bit positions. Usually the maintenance register also contains a DMD bit position to place the drive in the maintenance or diagnostic mode of operation when that stage is set.

10 Desired Track/Sector Address Register 146

In the track/sector register 146 TRACK ADDRESS and SECTOR ADDRESS bit positions identify, respectively, the track and sector on a disk to be involved in Now referring to the error register 142, a DCK bit 20 a transfer. In a fixedhead unit, the TRACK ADDRESS bits identify a specific head. The register 146 can be incremented by successive sector signals so that successive sector and tracks can be involved in a transfer. When the last track and sector address allotted to any status register 141 is set. The contents of the register 146 can be reset in response to system resetting or CLR signal or a DRIVE CLEAR command.

11 Drive Type Register 147

The drive type register 147 contains preset values to identify the nature of the drive. It might contain, for example, an NSA bit position to indicate a drive which does not use sector addressing or a TAP bit position to indicate a tape, rather than a disk, drive. An MOH bit position indicates whether a disk is a moving head disk while a 7CH bit position indicates, on a tape unit, whether the tape has seven or nine channels. A DRQ stage could indicate that a drive connects to two controllers. Sometimes a given drive might have a slave ence of such a drive. DRIVE ID bit positions might identify the drive type and major variations.

12 Look-ahead Register 148

The look-ahead register 148 is a counter which contains the sector address of the sector currently passing beneath the read/write heads in CURRENT SECTOR stages. SECTOR FRACTION stages are incremented periodically to identify the fractional portion of the sector which has passed the heads. This information improve disk transfer rates.

The remaining registers shown in FIG. 13 are not necessary for the operation of a fixed head disk unit such as shown in FIG. 6. They are, however, useful in 55 the operation of other drives and may be incorporated in them.

13 Drive Serial Number Register 250

For example, it may be desirable to include a drive serial number register 250 in magnetic tape drives or ter will then identify the drive unit during regular operation or during maintenance operations. The contents might be recorded in binary coded decimal notation.

14 Error Correction Code Register 251 and 252

The function of the ECC position and the ECC pattern registers 251 and 252 shown in FIG. 13 has been discussed previously. The use of these registers with error-correcting code drives is known. The position

and pattern are stored directly in the respective registers. They can be read through a remote register reading operation.

15 Offset Register 253

FIG. 13 also shows an offset register 253. TIMING 5 MARGIN and AMP MARGIN bit positions are useful in providing timing and amplitude offsets for various operations. If an ECI bit position is set and the drive has an error-correcting code function, the function is inhibheader comparison circuits. OFFSET bit positions contain the actual offset value to provide a proper incremental positioning of the read/write heads over the medium.

16 Desired-Cylinder and Current-Cylinder Address 15 Registers 254 and 255

Two other registers useful in moving head disk memory units are a desired-cylinder-address register 254 and a current-cylinder-address register 255. The drive cylinder-address register 254 and then transfers the contents of the register 254 into the current-cylinderaddress register 255. The register 255 then identifies the actual head position and is useful, for example, in heads from a current position to other positions.

17 Attention Summary Register 145

A status register 141 in each drive contains an ATA stage as previously described. The information in this remote reading operation in which the register 141 is identified. Each ATA stage in each drive is a stage in the attention summary register 145 which has its own remote address. That is, within the register 145 there is (i.e., the wire in the control data wires 84 which receives the output of the ATA stage) and a drive, each ATA stage being coupled to a unique wire when the attention summary register is read.

corresponding ATA stage sets. This causes the drive to issue an ATTN signal onto the common ATTN wire 94 to thereby cause system operations to be interrupted. One of the first operations in the ensuing interruption routine is the reading of the attention summary register 45 145. This reading operation is essentially the same as shown in FIG. 8. In this specific operation, however, the address circuit 151 produces RS' signals with a value of 048, and the RS signals from the output drives 161 have the same value. The controller performs steps 50 transfers data from the drive into the system in re-200 through 202 as shown in FIG. 8 and by charts 14Å, 14B and 14E at times t1 and t2 in FIG. 14. After a delay, the signals are received by all the drives on the device bus at time t3. Now each drive uses step 204 to branch to step 205 because the DS signals have no 55 meaning. As the RS signals identify register 048, step 205 causes step 206 to transfer the output of the ATA stage in each drive status and control error register 141 onto a corresponding wire in the data set 81 sometime after the DEM signal arrives at 14. At time 15 in Chart 60 issuance of any of these data transfer commands. The 14J each drive transmits its TRA signal and the controller receives all of these in some time interval shown as time t6 in Chart 14F.

Several different signals may be received; however, so the controller timing interval is completed by time 17. Then, in step 221, the controller branches to step 223 and reads the data at time t7 as shown in Chart

14C thereby transferring the ATA signals from all drives to the controller. This is also the time that the controller may terminate the DEM signal as shown in step 214, so that at time t8 the control information is removed and the drives all terminate their respective TRA signals. Then, the reading operation is completed, as previously described, by time t9. Thus, when the reading operation is completed, the system "knows" exactly which drive or drives sent ATA signals and can ited. Similarly, setting an HCI bit position inhibits 10 immediately begin reading their respective error registers or other registers without any intervening polling operations.