# TM03 Magnetic Tape Formatter Technical Manual

digital equipment corporation • maynard, massachusetts

### 1st Edition, July 1978 2nd Printing (Rev), July 1979

Copyright © 1978, 1979 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS      |

|---------|--------------|--------------|

| DEC     | DECSYSTEM-20 | OMNIBUS      |

| PDP     | DIBOL        | <b>OS</b> /8 |

| DECUS   | EDUSYSTEM    | RSTS         |

| UNIBUS  | VAX          | RSX          |

|         | VMS          | IAS          |

# CONTENTS

| CHAPTER 1 | GENERAL INFORMATION                                     | Page               |

|-----------|---------------------------------------------------------|--------------------|

| 1.1       | INTRODUCTION                                            | 1-1                |

| 1.2       | GENERAL DESCRIPTION                                     |                    |

| 1.3       | FUNCTIONAL DESCRIPTION.                                 | 1-7                |

| 1.3.1     | Introduction                                            |                    |

| 1.3.2     | System Operation                                        |                    |

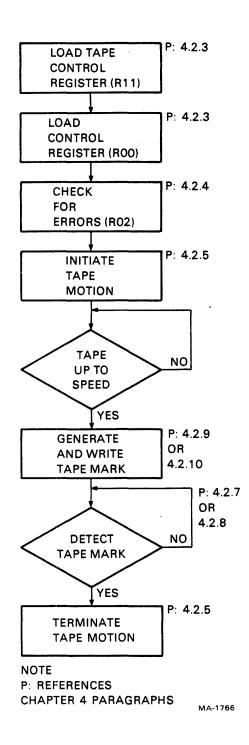

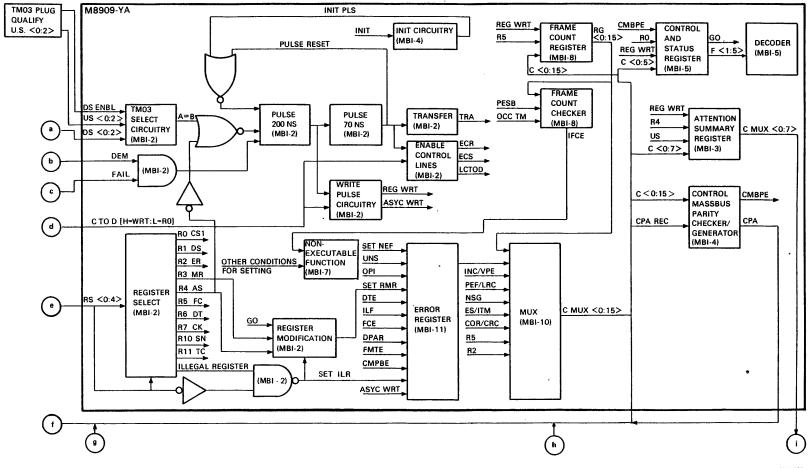

| 1.3.2.1   | Massbus Interface Module (M8909-YA)                     | 1-7                |

| 1.3.2.2   | Rit Fiddler Module                                      | 1-7                |

| 1.3.2.3   | Bit Fiddler Module                                      | 1-10               |

| 1.3.2.4   | Tape Control-NRZI Module (M8934)                        | 1_10               |

| 1.3.2.5   | Data Sync-PE Module (M8901)                             | 1_11               |

| 1.3.2.6   | Tape Control-PE Module (M8932)                          | 1_11               |

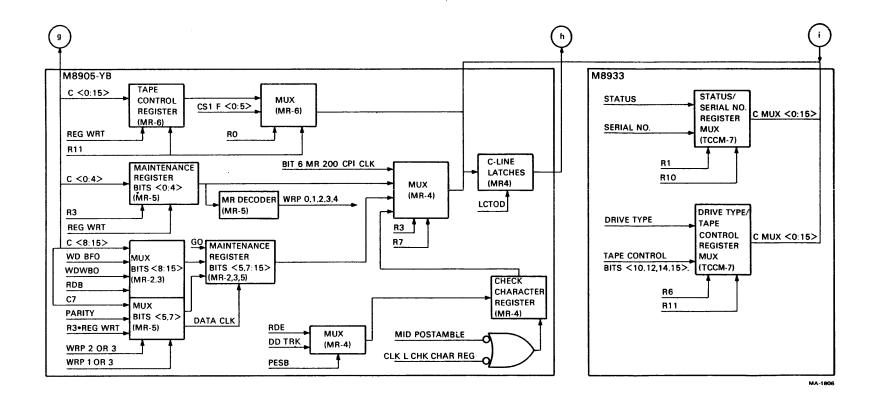

| 1.3.2.7   | Tape Control Common Mode (TCCM) Module (M8933)          | 1_11               |

| 1.4       | RELATED DOCUMENTS.                                      | 1_12               |

| 1.4       | UNIT SPECIFICATIONS                                     | 1-12               |

| 1.5       |                                                         |                    |

| CHAPTER 2 | PROGRAMMING INFORMATION                                 |                    |

| 2.1       | REGISTER FUNCTIONS AND FORMATS                          | 2-1                |

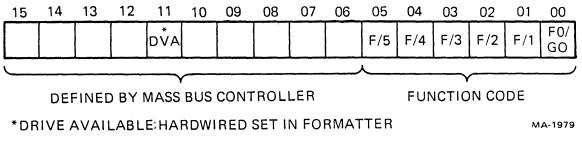

| 2.1.1     | Control Register [(CS1) Register 008]                   | 2-5                |

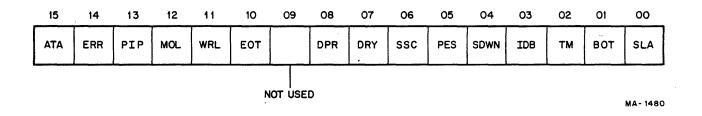

| 2.1.2     | Status Register [(DS) Register 018]                     | 2-7                |

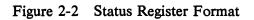

| 2.1.3     | Error Register [(ÈR) Register 028]                      | 2-10               |

| 2.1.4     | Maintenance Register [(MR) Register 038]                | 2-14               |

| 2.1.5     | Attention Summary Register [(AS) Register 0-48]         | 2-16               |

| 2.1.6     | Frame Count Register [(FC) Register 058]                | 2-16               |

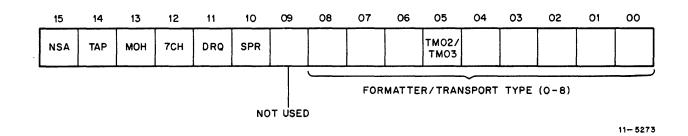

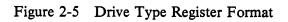

| 2.1.7     | Drive Type Register $[(DT)$ Register $06_8]$            |                    |

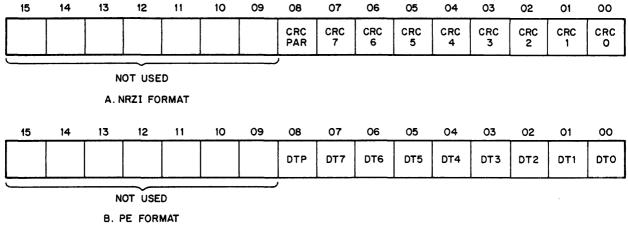

| 2.1.8     | Check Character Register [(CK) Register 078]            | 2-19               |

| 2.1.9     | Serial Number Register [(SN) Register 10 <sub>8</sub> ] | 2-19               |

| 2.1.10    | Tape Control Register [(TC) Register 11 <sub>8</sub> ]  | 2-19               |

| 2.2       | DATA FORMATS                                            | 2-22               |

| 2.2.1     | Massbus/TM03 Transfers                                  | 2_22               |

| 2.2.2     | TM03/Tape Frame Packing                                 | ····· 2 22<br>2_23 |

| 2.3       | COMMAND FUNCTIONS                                       | 2-25               |

| 2.3.1     | No-Op                                                   | 2-23               |

| 2.3.2     | Rewind, Off-Line                                        | ,                  |

| 2.3.3     | Rewind.                                                 |                    |

| 2.3.4     | Drive Clear.                                            |                    |

| 2.3.4.1   | Drive Clear Resets                                      | 2-20<br>2-28       |

| 2.3.4.2   | Drive Clear versus Initialize (INIT)                    |                    |

| 2.3.5     | Read-In Preset                                          | 2-20<br>2-20       |

| 2.3.6     | Erase                                                   | ····· 2-29<br>2 20 |

| 2.3.7     | Write Tape Mark.                                        | ····· 2-29<br>2 20 |

| 2.3.8     | Space Forward.                                          | ····· 2-27<br>2 20 |

|           | Space Reverse                                           | 2-23               |

| 2.3.9     | Read Forward/Write Check Forward                        | 2-29               |

| 2.3.10    |                                                         |                    |

| 2.3.11    | Read Reverse/Write Check Reverse                        |                    |

| 2.3.12    | Write                                                   |                    |

| 2.4       | PROGRAMMING NOTES.                                      | ····· 4-30         |

| 2.5       |                                                         |                    |

| 2.5.1     | NRZI Error Correction                                   | 2-33               |

,

|                    | Pag                                      | e |

|--------------------|------------------------------------------|---|

| 2.5.2              | Auto Density Select                      | 3 |

| 2.5.3              | Other Notes                              | 3 |

| CHAPTER 3          | INSTALLATION                             |   |

| CHAITER J          |                                          |   |

| 3.1                | SITE PLANNING AND CONSIDERATIONS         | 1 |

| 3.2                | UNPACKING 3-                             |   |

| 3.3                | INSPECTION                               |   |

| 3.4                | INSTALLATION PROCEDURES 3-               |   |

| 3.4.1              | TM03 Cabling 3-                          | 1 |

| 3.4.2              | Massbus Cabling to Transport Cabinet 3-  |   |

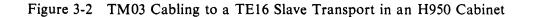

| 3.4.2.1            | H950 Cabinet 3-                          |   |

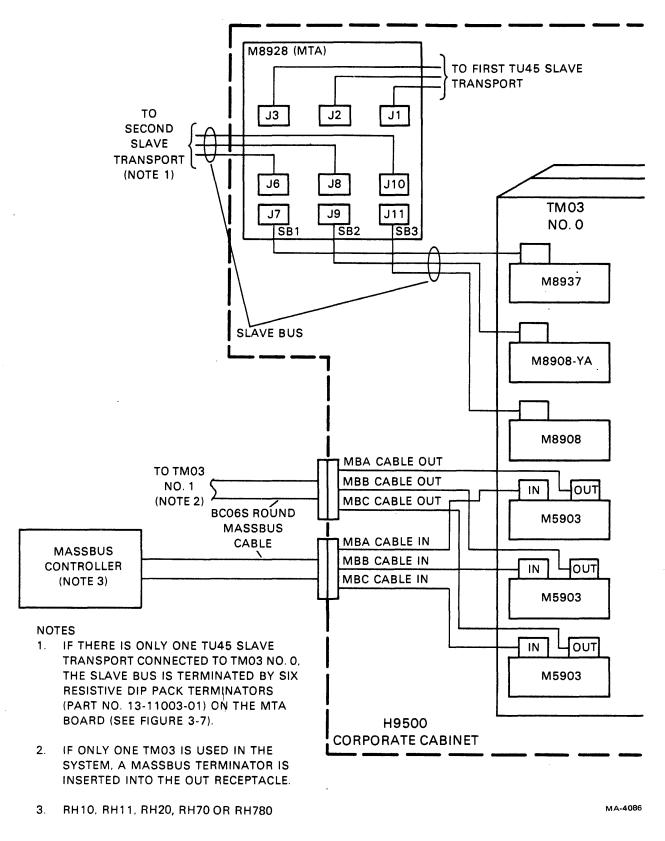

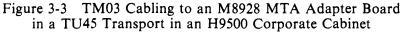

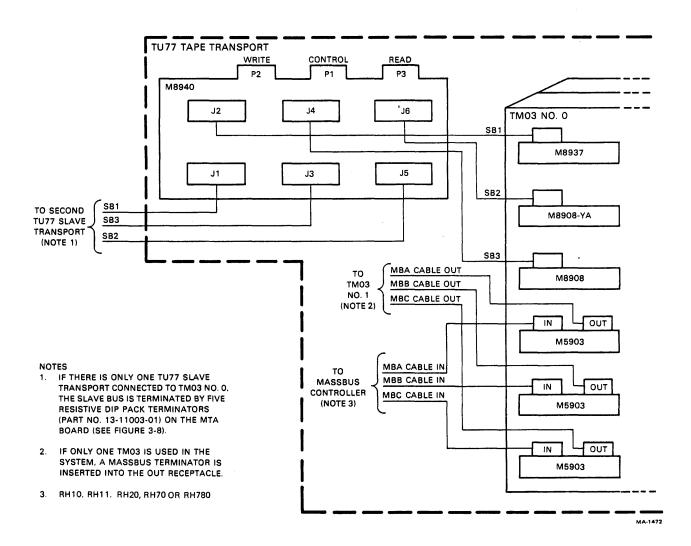

| 3.4.2.2            | H9500 Corporate Cabinet 3-0              |   |

| 3.4.3              | Slave Bus Cabling to Tape Transport 3-   |   |

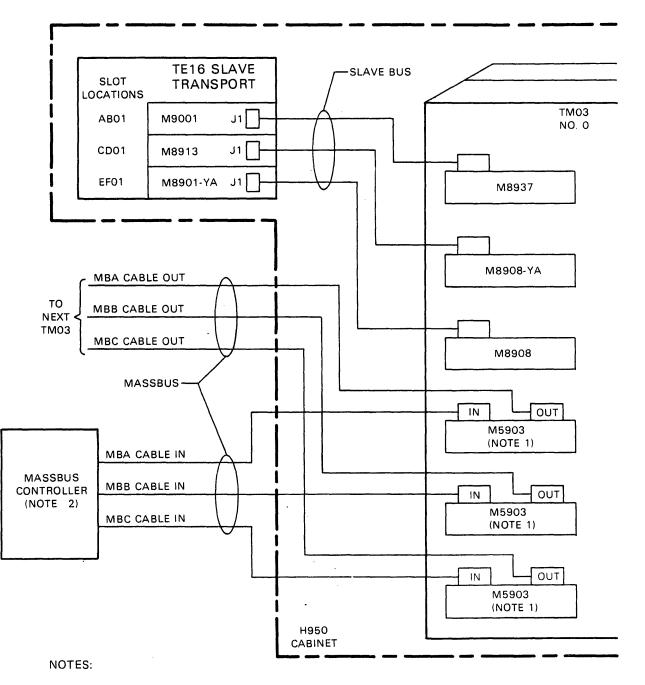

| 3.4.3.1            | TE16 Transport 3-                        | 6 |

| 3.4.3.2            | TU45 Transport                           |   |

| 3.4.3.3            | TU77 Transport 3-10                      |   |

| 3.5                | ACCEPTANCE TESTING 3-10                  | 0 |

| <b>CHAPTER 4</b>   | THEORY OF OPERATION                      |   |

|                    |                                          |   |

| 4.1                | GENERAL OPERATION 4-                     |   |

| 4.1.1              | Write Data Path 4-                       |   |

| 4.1.2              | Read Data Path 4-1                       |   |

| 4.1.3              | Rewind Operational Sequence 4-1          |   |

| 4.1.3.1            | Command Initiation 4-1                   |   |

| 4.1.3.2            | Command Execution                        |   |

| 4.1.3.3            | Command Termination                      |   |

| 4.1.4              | Space Operational Sequence               |   |

| 4.1.4.1            | Command Initiation                       |   |

| 4.1.4.2            | Command Execution                        |   |

| 4.1.4.3            | Command Termination                      |   |

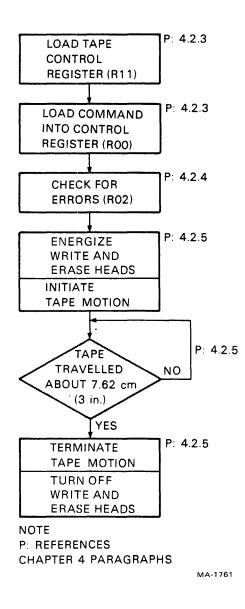

| 4.1.5              | Erase Operational Sequence               |   |

| 4.1.5.1<br>4.1.5.2 | Command Initiation                       |   |

| 4.1.5.2            | Command Execution                        |   |

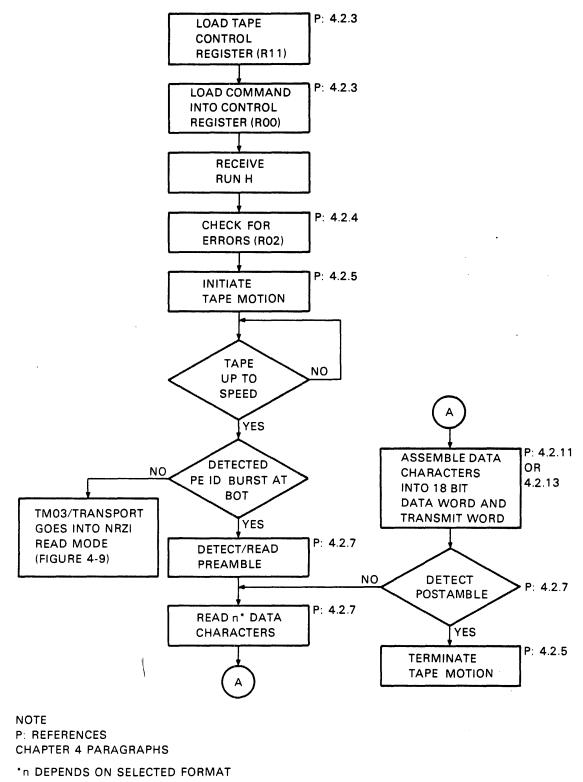

| 4.1.5              | PE Data Read Operational Sequence        |   |

| 4.1.6.1            | Command Initiation                       |   |

| 4.1.6.2            | Command Execution                        |   |

| 4.1.6.3            | Command Termination                      |   |

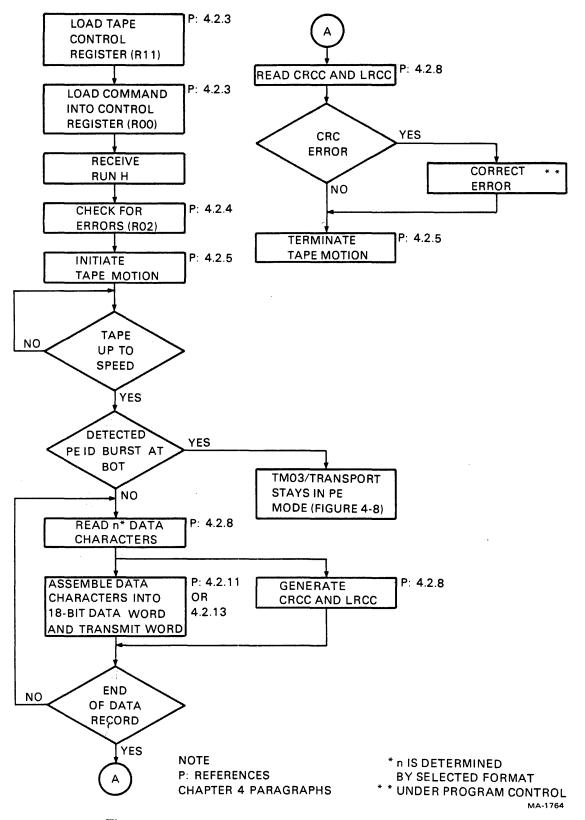

| 4.1.7              | NRZI Data Read Operational Sequence      |   |

| 4.1.7.1            | Command Initiation                       |   |

| 4.1.7.2            | Command Execution                        |   |

| 4.1.7.3            | Command Termination. 4-2                 |   |

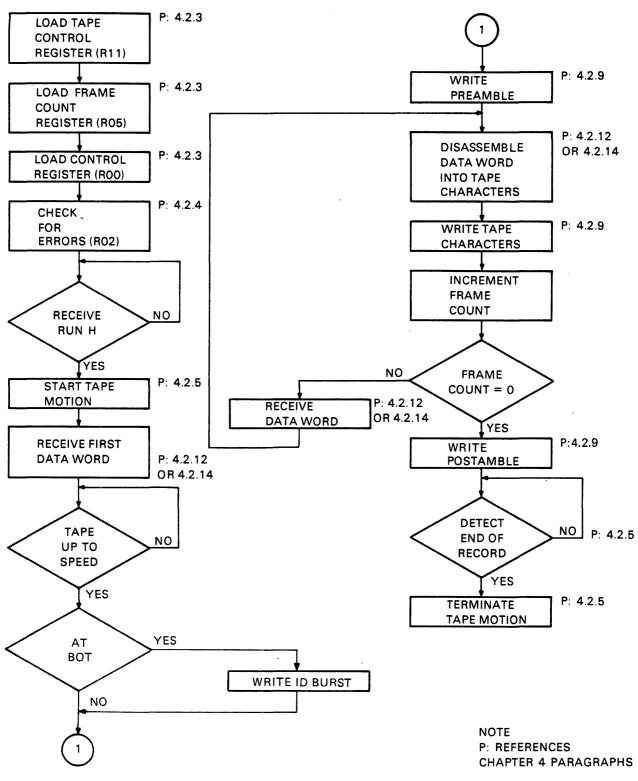

| 4.1.8              | PE Data Write Operational Sequence       |   |

| 4.1.8.1            | Command Initiation                       |   |

| 4.1.8.2            | Command Execution                        |   |

| 4.1.8.3            | Command Termination. 4-2                 |   |

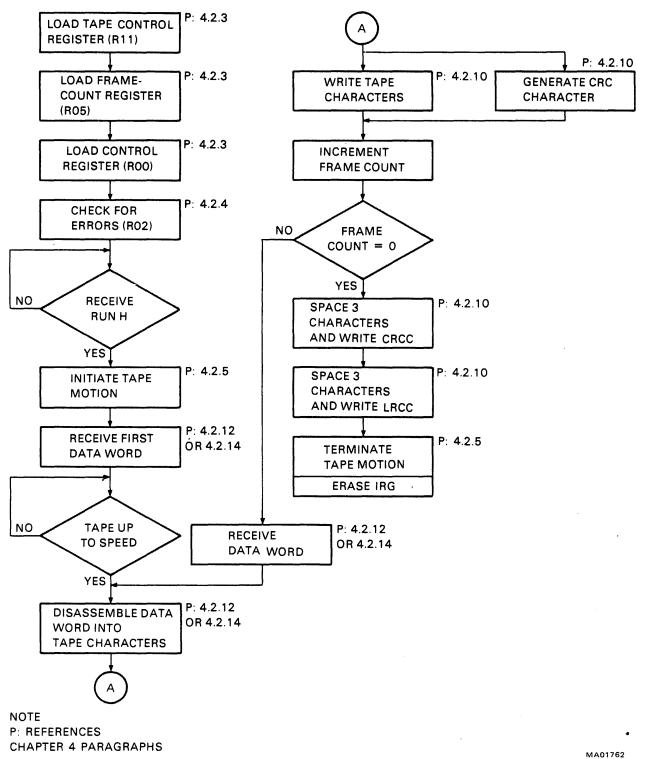

| 4.1.9              | NRZI Data Write Operational Sequence 4-2 |   |

|                    |                                          |   |

.

4

|          |                                                      | Page   |

|----------|------------------------------------------------------|--------|

| 4.1.9.1  | Command Initiation                                   | . 4-23 |

| 4.1.9.2  | Command Execution                                    |        |

| 4.1.9.3  | Command Termination                                  | . 4-25 |

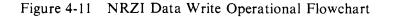

| 4.1.10   | Write Tape Mark Operational Sequence                 | . 4-25 |

| 4.1.10.1 | Command Initiation                                   |        |

| 4.1.10.2 | Command Execution                                    | . 4-25 |

| 4.1.10.3 | Command Termination                                  |        |

| 4.2      | FUNCTIONAL DESCRIPTIONS                              |        |

| 4.2.1    | Maintenance Modes                                    | . 4-27 |

| 4.2.2    | TM03 Clocks                                          |        |

| 4.2.2.1  | Clock (SB)                                           | . 4-30 |

| 4.2.2.2  | WRT ČLK (SB)                                         |        |

| 4.2.3    | Register Reading and Writing                         |        |

| 4.2.3.1  | Register Write                                       |        |

| 4.2.3.2  | Register Read                                        |        |

| 4.2.3.3  | Attention Summary Register (R04)                     |        |

| 4.2.4    | Errors.                                              |        |

| 4.2.4.1  | Error Check                                          |        |

| 4.2.4.2  | Attention (ATTN)                                     |        |

| 4.2.4.3  | Exception (EXC)                                      |        |

| 4.2.5    | Tape Motion – On-Line                                |        |

| 4.2.5.1  | Transport Selection and Status Reporting             | . 4-45 |

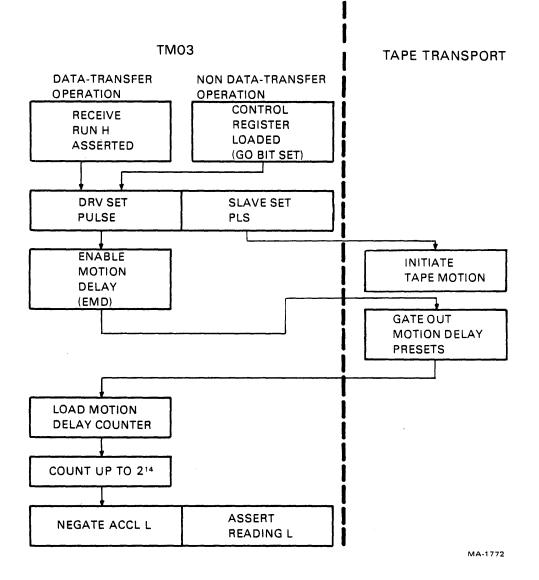

| 4.2.5.2  | Tape Motion Initiation (On-Line)                     | . 4-45 |

| 4.2.5.3  | Tape Motion Termination (Read)                       |        |

| 4.2.5.4  | Tape Motion Termination (Write)                      |        |

| 4.2.5.5  | Tape Motion Termination (Erase)                      | . 4-48 |

| 4.2.5.6  | Tape Motion Termination (Space)                      |        |

| 4.2.5.7  | Tape Motion Termination (Rewind)                     | . 4-50 |

| 4.2.5.8  | Tape Motion Termination – Operation Incomplete (OPI) |        |

| 4.2.6    | Density Select/Tape Speed Select                     |        |

| 4.2.6.1  | Density Select                                       |        |

| 4.2.6.2  | Tape Speed Select                                    |        |

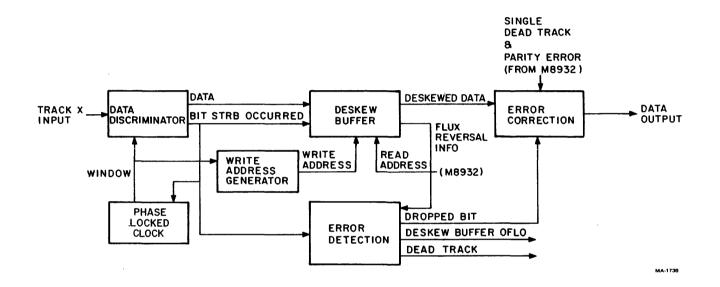

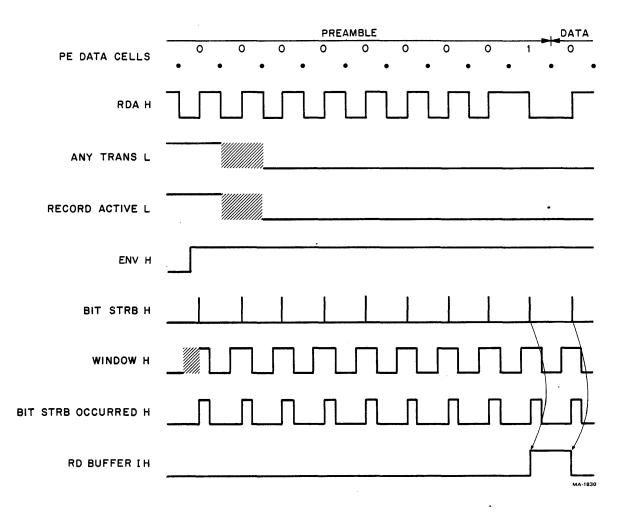

| 4.2.7    | Read (PE)                                            |        |

| 4.2.7.1  | Data Śync                                            |        |

| 4.2.7.2  | Preamble Detection                                   |        |

| 4.2.7.3  | Data Detection                                       |        |

| 4.2.7.4  | Error Detection and Correction                       |        |

| 4.2.7.5  | IRG Detection                                        |        |

| 4.2.7.6  | IDB Detection                                        | . 4-64 |

| 4.2.7.7  | Tape Mark Detection                                  |        |

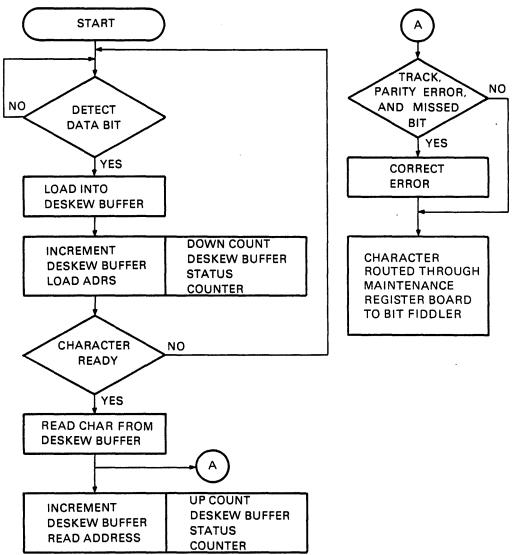

| 4.2.8    | Read (NRZI)                                          | . 4-66 |

| 4.2.8.1  | Tape Control – Read Data Path                        | 4-66   |

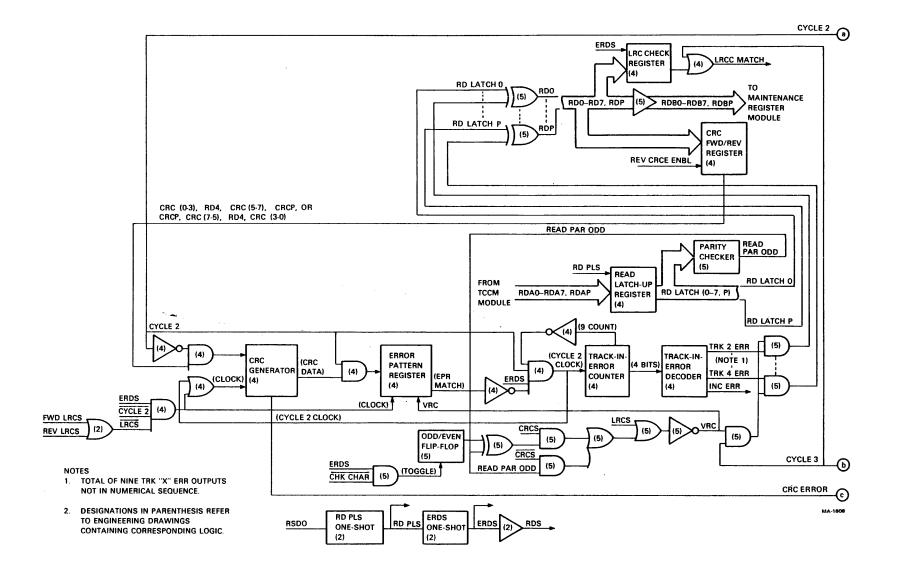

| 4.2.8.2  | CRCC Generation and Read                             |        |

| 4.2.8.3  | NRZI Error Correction                                | . 4-66 |

| 4.2.8.4  | LRCC Generation and Read                             | . 4-69 |

| 4.2.8.5  | IRG Detection                                        |        |

| 4.2.8.6  | Tape Mark Detection                                  | . 4-74 |

| 4.2.9    | Write (PE)                                           | 4-74   |

| 4.2.9.1  | PE Data Write                                        | . 4-74 |

|           | Page                                    |

|-----------|-----------------------------------------|

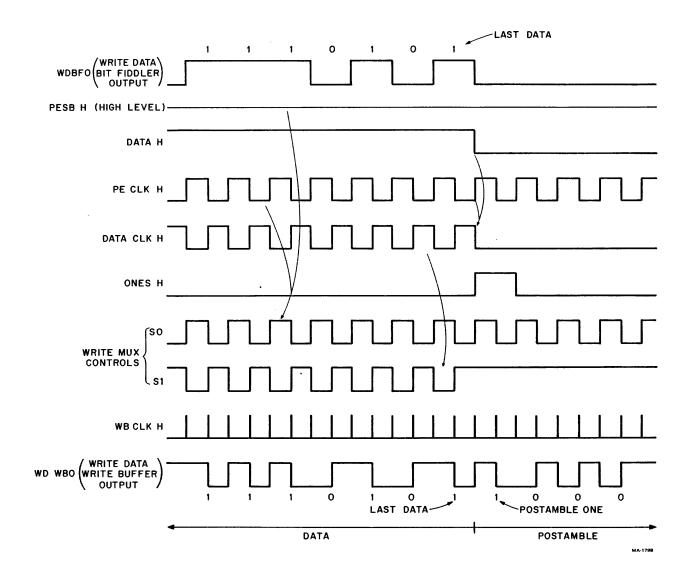

| 4.2.9.2   | PE Data Write Timing 4-75               |

| 4.2.9.3   | Preamble Write Timing 4-75              |

| 4.2.9.4   | Postamble Write Timing 4-75             |

| 4.2.9.5   | PE Tape Mark Generation 4-77            |

| 4.2.9.6   | IDB Generation 4-77                     |

| 4.2.10    | Write (NRZI) 4-77                       |

| 4.2.10.1  | NRZI Data Write 4-77                    |

| 4.2.10.2  | NRZI Data Write Timing 4-77             |

| 4.2.10.3  | CRCC Generation                         |

| 4.2.10.4  | CRCC and LRCC Write Timing 4-78         |

| 4.2.10.5  | NRZI Tape Mark Generation. 4-79         |

| 4.2.10.6  | Tape Mark Write Timing.    4-79         |

| 4.2.11    | Bit Fiddler – M8915-YA 4-80             |

| 4.2.11.1  | General                                 |

| 4.2.11.2  | Data Transfer Formats 4-80              |

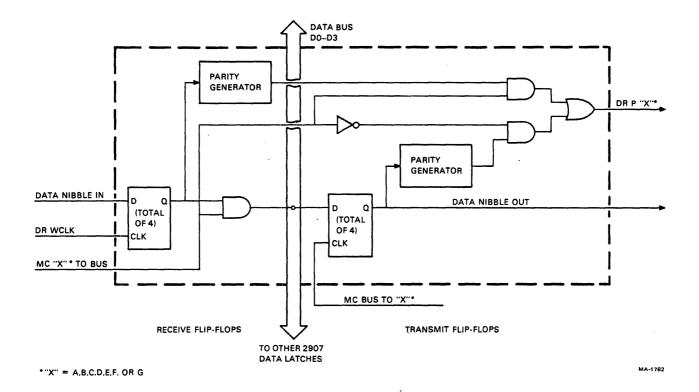

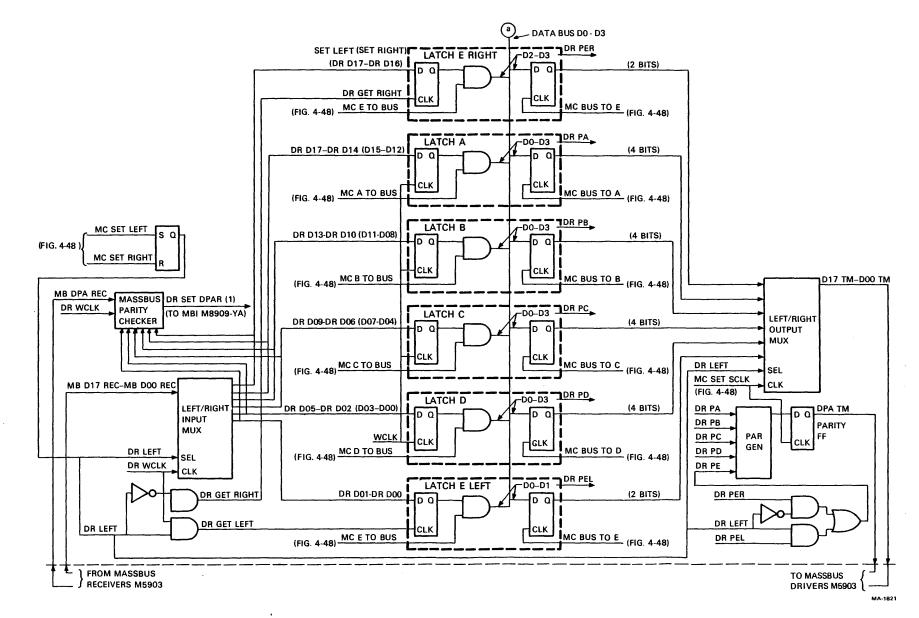

| 4.2.11.3  | 2907 Data Latches                       |

| 4.2.11.4  | Write Data Path 4-85                    |

| 4.2.11.5  | Read Data Path 4-85                     |

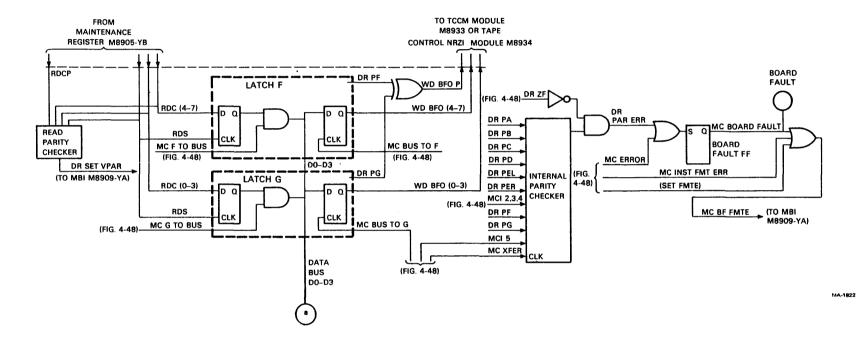

| 4.2.11.6  | Data Parity                             |

| 4.2.11.7  | Program Control 4-88                    |

| 4.2.11.8  | Program Errors 4-91                     |

| 4.2.11.9  | Program Timing 4-92                     |

| 4.2.11.10 | Operational Flow Diagrams 4-92          |

| 4.2.12    | Bit Fiddler Read (M8906) 4-104          |

| 4.2.12.1  | M8906 Bit Fiddler Operating Modes 4-106 |

| 4.2.12.2  | M8906 Bit Fiddler Read Operation 4-106  |

| 4.2.13    | Bit Fiddler Write (M8906) 4-110         |

| 4.2.13.1  | Bit Fiddler Initialization. 4-110       |

| 4.2.13.2  | Bit Fiddler Formatting 4-110            |

| 4.2.13.3  | Bit Fiddler Timing                      |

| 4.2.13.4  | Parity Generation 4-113                 |

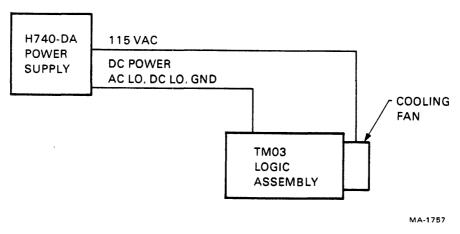

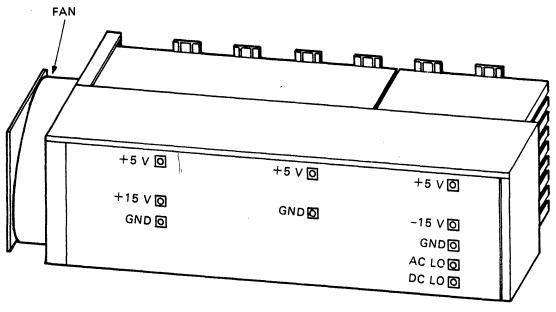

| 4.2.14    | Power                                   |

# CHAPTER 5 MAINTENANCE

| 5.1     | SCOPE                                          | 5-1 |

|---------|------------------------------------------------|-----|

| 5.2     | MAINTENANCE PHILOSOPHY                         | 5-1 |

| 5.3     | TEST EQUIPMENT                                 | 5-1 |

| 5.4     | PREVENTIVE MAINTENANCE                         |     |

| 5.4.1   | PM Schedule                                    | 5-2 |

| 5.4.2   | PM Checks                                      | 5-2 |

| 5.4.2.1 | DC Voltage Check                               | 5-2 |

| 5.4.2.2 | Fan Check                                      |     |

| 5.4.2.3 | Diagnostics                                    | 5-2 |

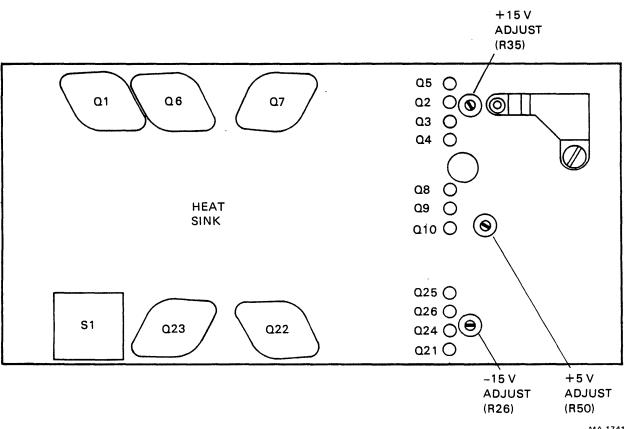

| 5.5     | TM03 ADJUSTMENTS                               | 5-2 |

| 5.6     | MODULE/SYSTEM COMPATIBILITY AND MODULE JUMPERS | 5-2 |

| 5.6.1   | Module/System Compatibility                    |     |

| 5.6.1.1 | Data Sync Modules                              |     |

| 5.6.1.2 | Bit Fiddler Modules                            | 5-4 |

| Pa | ige |

|----|-----|

|----|-----|

| 5.6.1.3 | NRZI Tape Control Modules                    | 5-4 |

|---------|----------------------------------------------|-----|

| 5.6.2   | Module Jumpers.                              |     |

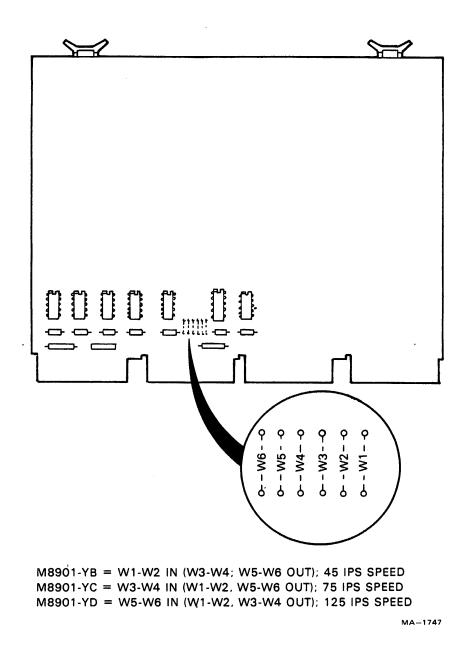

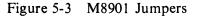

| 5.6.2.1 | PE Data Sync Module (M8901)                  |     |

| 5.6.2.2 | NRZI Tape Control Module (M8934 or M8934-YA) | 5-5 |

| 5.6.2.3 | Maintenance Register Module (M8905-YB)       | 5-7 |

| 5.6.2.4 | Control and Write Drivers (M8937)            | 5-7 |

| 5.7     | REMOVAL AND REPLACEMENT                      | 5-7 |

| 5.8     | CORRECTIVE MAINTENANCE 5                     |     |

| 5.8.1   | Diagnostics                                  |     |

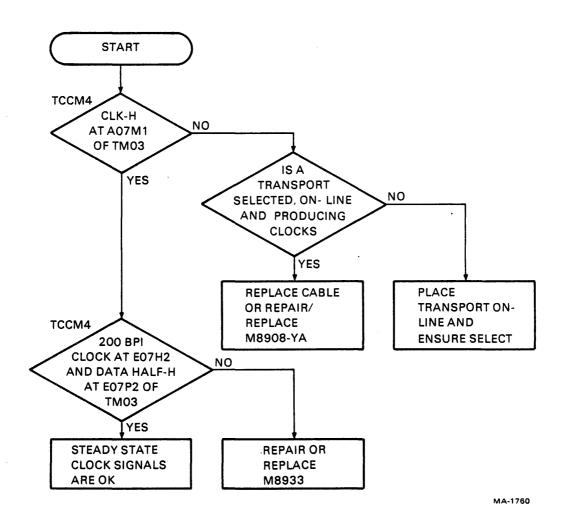

| 5.8.2   | Clock Trouble Analysis 5                     |     |

| 5.8.3   | Register Read/Write Trouble Analysis 5       |     |

| 5.8.4   | Error Detection Trouble Analysis 5           | -15 |

| 5.8.5   | Tape Motion Trouble Analysis    5            |     |

| 5.8.6   | Data Read/Write Circuits Trouble Analysis 5  | -17 |

| 5.8.7   | Bit Fiddler Error Analysis 5                 |     |

# APPENDIX A GLOSSARY

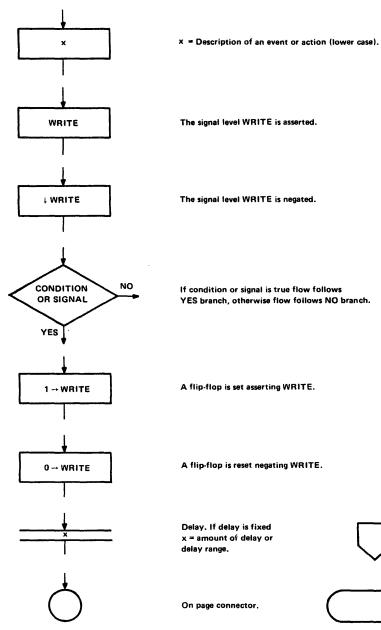

## APPENDIX B FLOWCHART GLOSSARY

# APPENDIX C RECORDING TECHNIQUES

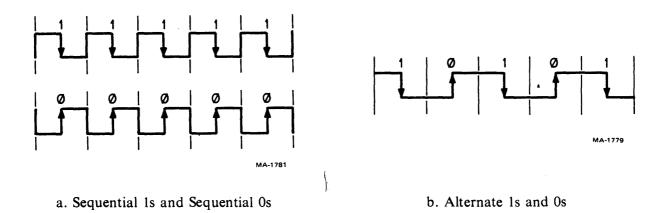

| C.1   | NRZI (Non-Return to Zero Inverted) C-1 |

|-------|----------------------------------------|

| C.1.1 | Definition                             |

| C.1.2 | Format                                 |

| C.2   | PE (Phase Encoding) C-1                |

| C.2.1 | Definition                             |

| C.2.2 | Format                                 |

| C.2.3 | PE Characteristics C-5                 |

### APPENDIX D TM03 INTERFACE SIGNALS

# **FIGURES**

## Figure No.

### Title

## Page

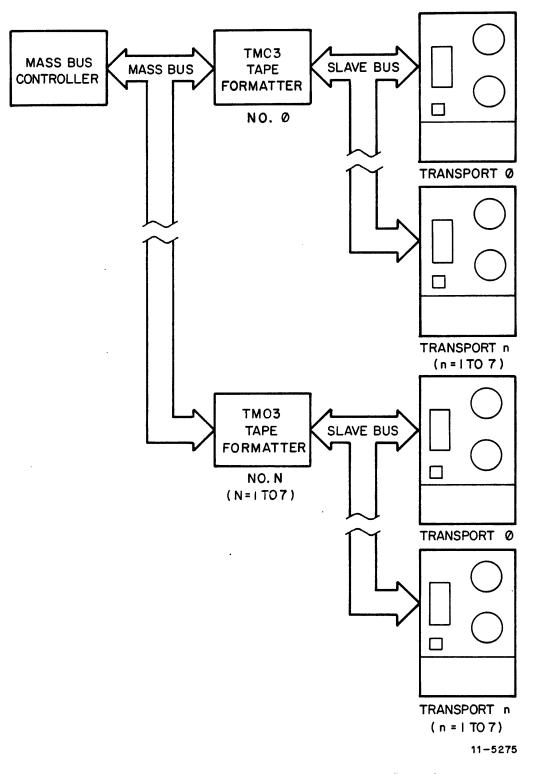

| 1-1 | TM03 Tape Transport System Configuration 1-2                 |

|-----|--------------------------------------------------------------|

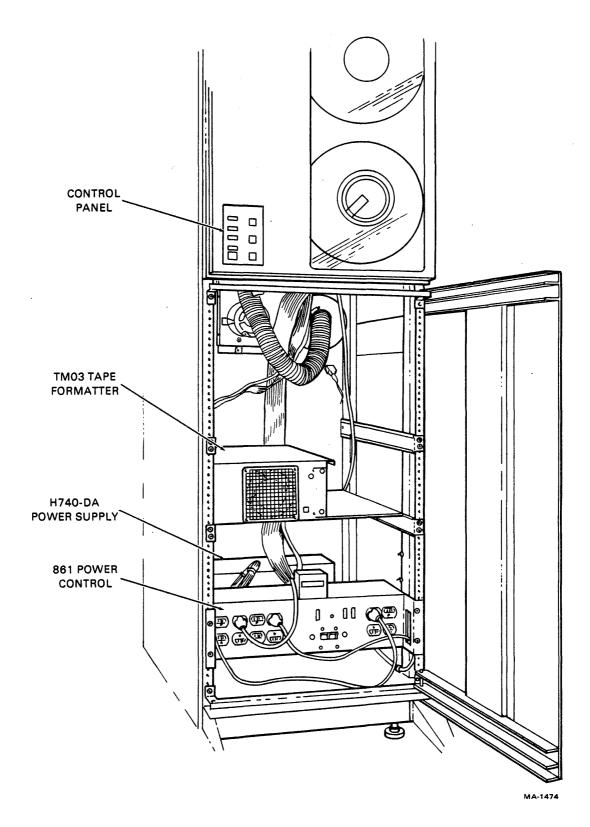

| 1-2 | TM03 with TE16 Tape Transport in H950 Cabinet                |

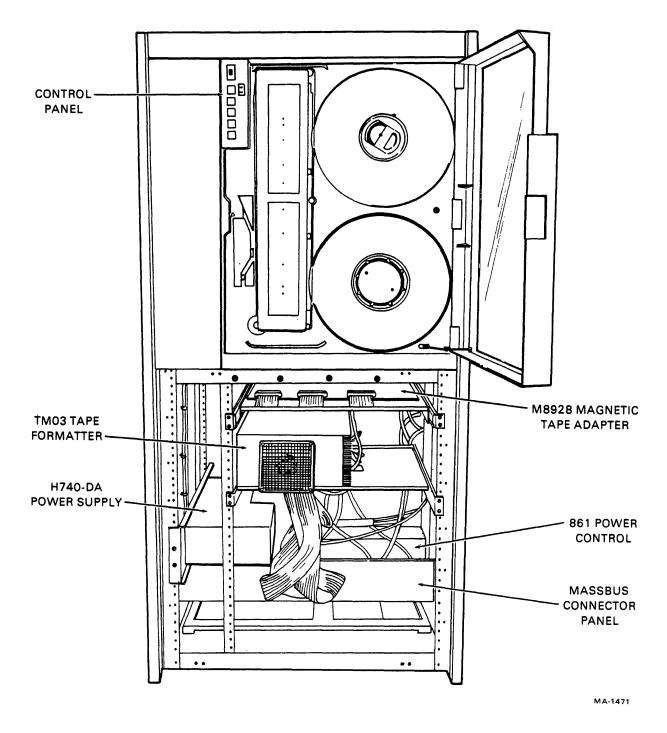

| 1-3 | TM03 with TU45 Tape Transport in H9500 Corporate Cabinet 1-4 |

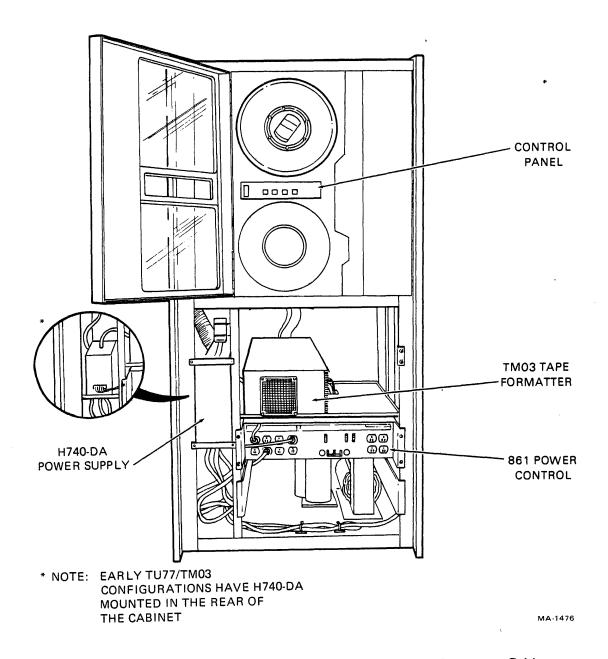

| 1-4 | TM03 with TU77 Tape Transport in H9500 Corporate Cabinet 1-5 |

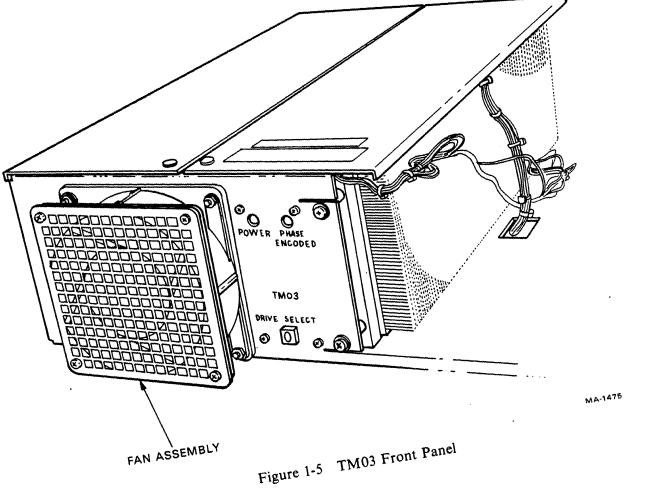

| 1-5 | TM03 Front Panel                                             |

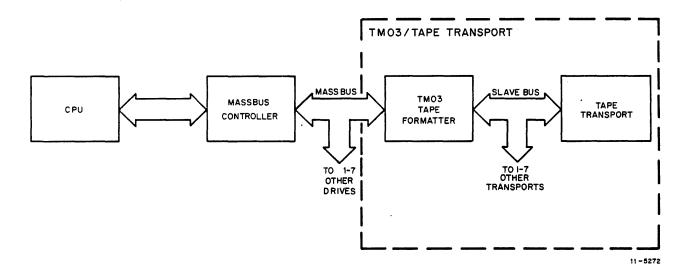

| 1-6 | TM03 in a System Configuration 1-8                           |

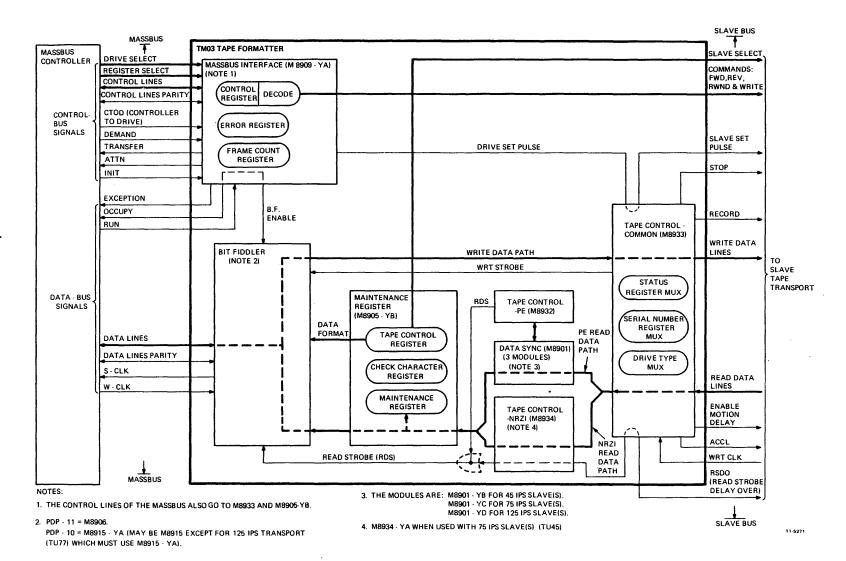

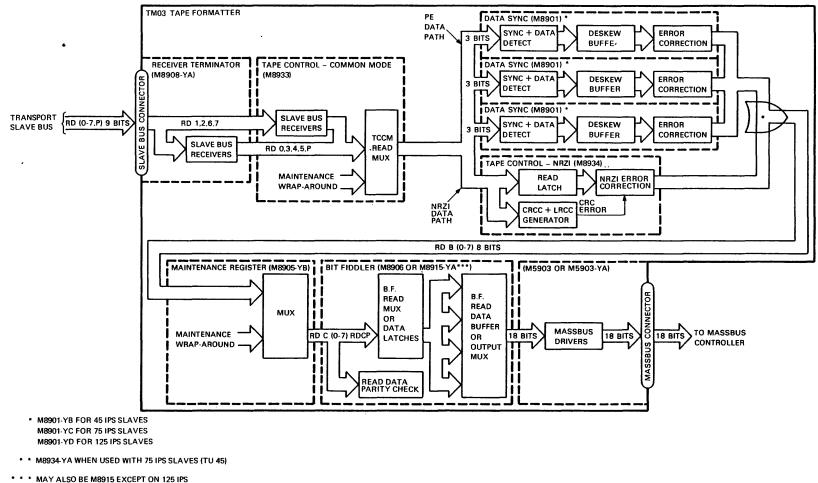

| 1-7 | TM03 Basic Block Diagram 1-9                                 |

| 2-1 | Control Register Format                                      |

| 2-2 | Status Register Format                                       |

| 2-3 | Error Register Format                                        |

| 2-4 | Maintenance Register Format 2-15                             |

| 2-5 | Drive Type Register Format                                   |

| 2-6 | Check Character Register Format 2-21                         |

# FIGURES (Cont)

| Figure No. | Title                                                                  | Page   |

|------------|------------------------------------------------------------------------|--------|

| 2-7        | Serial Number Register Format                                          | . 2-21 |

| 2-8        | Tape Control Register Format                                           | . 2-21 |

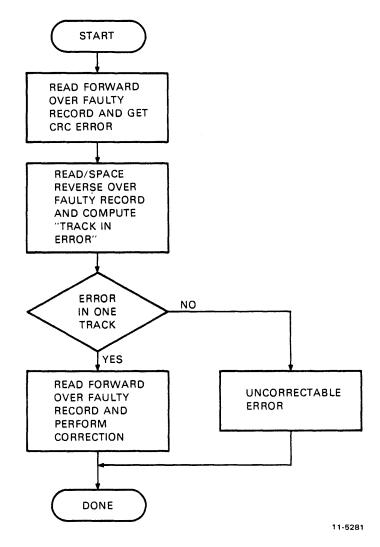

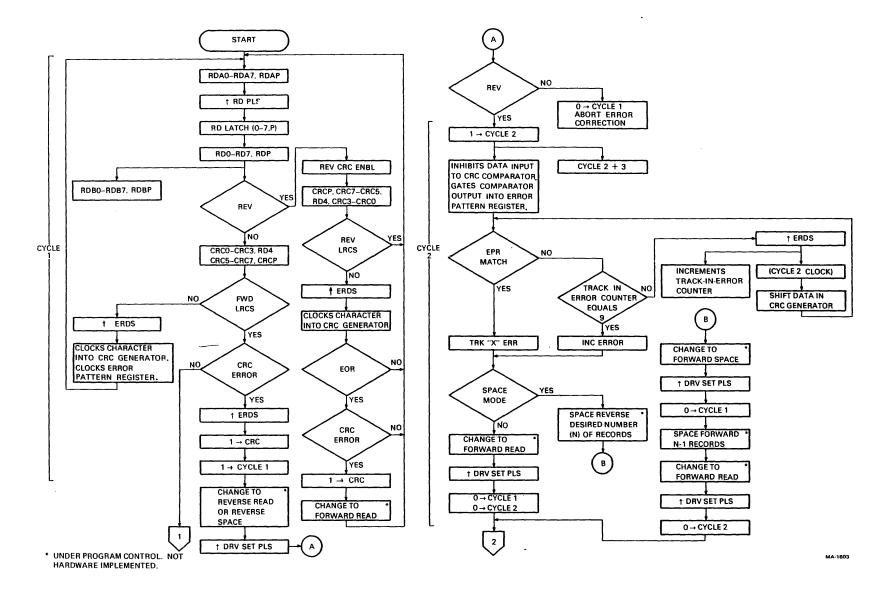

| 2-9        | Simplified NRZI Error Correction Flow Diagram                          | . 2-31 |

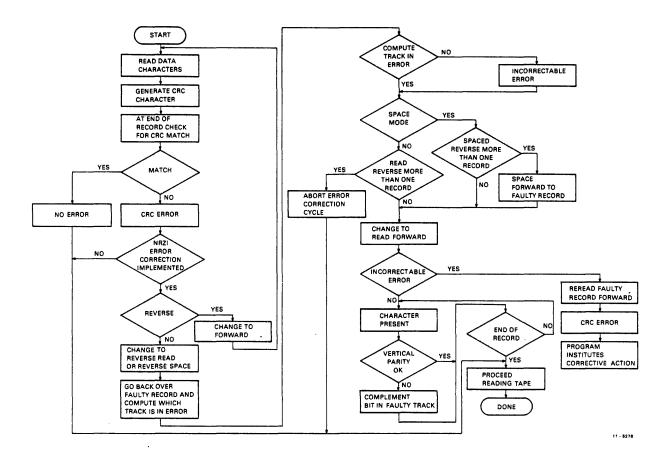

| 2-10       | NRZI Error Correction Flow Diagram                                     |        |

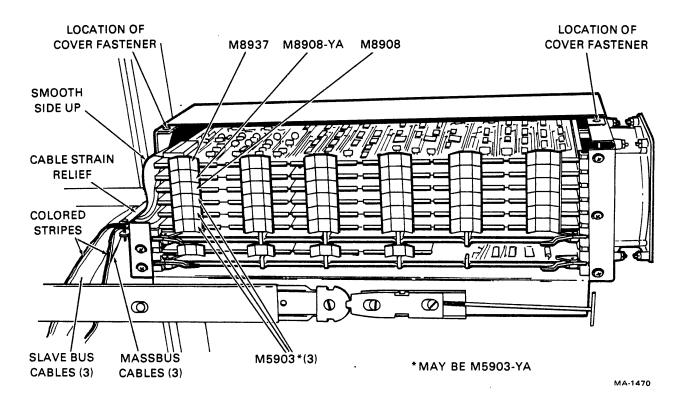

| 3-1        | TM03 Formatter with Cover Removed                                      |        |

| 3-2        | TM03 Cabling to a TE16 Slave Transport in an H950 Cabinet              |        |

| 3-3        | TM03 Cabling to an M8928 MTA Adapter Board in a TU45 Transport         |        |

|            | in an H9500 Corporate Cabinet                                          | 3-4    |

| 3-4        | TM03 Cabling to an M8940 MTA Adapter Board in a TU77 Transport         |        |

|            | in an H9500 Corporate Cabinet                                          | 3-5    |

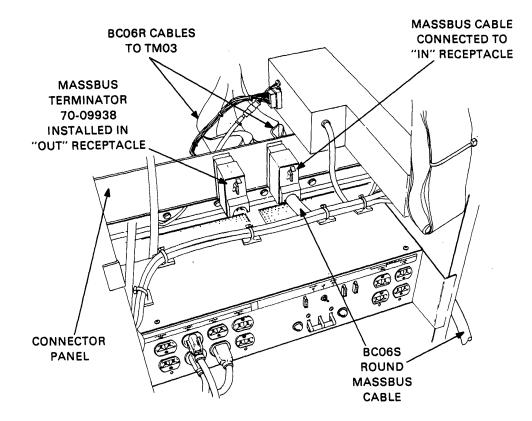

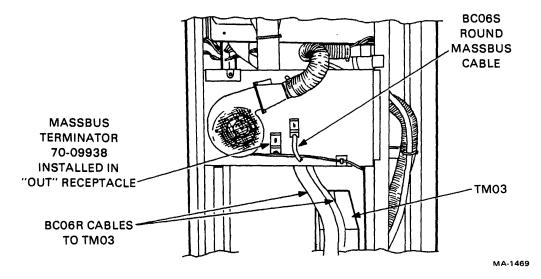

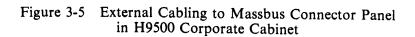

| 3-5        | External Cabling to Massbus Connector Panel in H9500 Corporate Cabinet |        |

| 3-6        | Internal Cabling to Massbus Connector Panel In H9500 Corporate Cabinet |        |

|            |                                                                        |        |

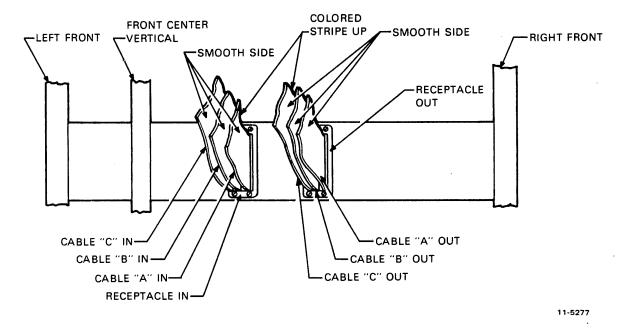

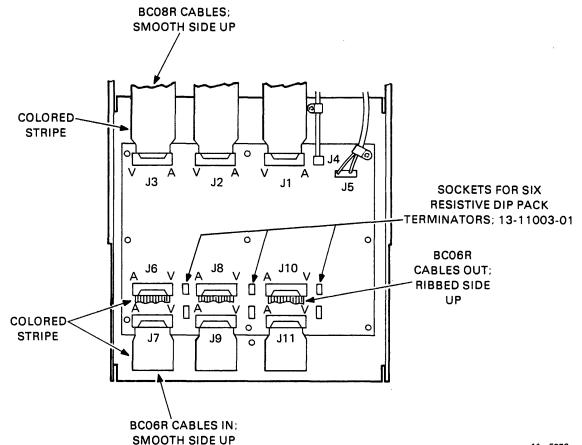

| 3-7        | Cable Orientation on M8928 MTA Module                                  |        |

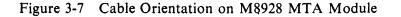

| 3-8        | Cable Orientation on M8940 MTA Module                                  |        |

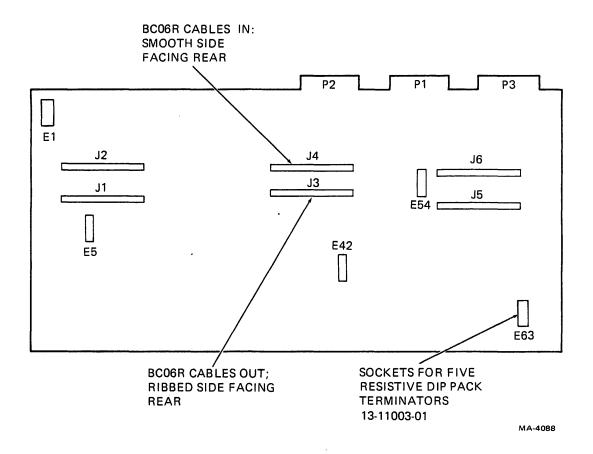

| 4-1        | TM03 Interface Signals                                                 |        |

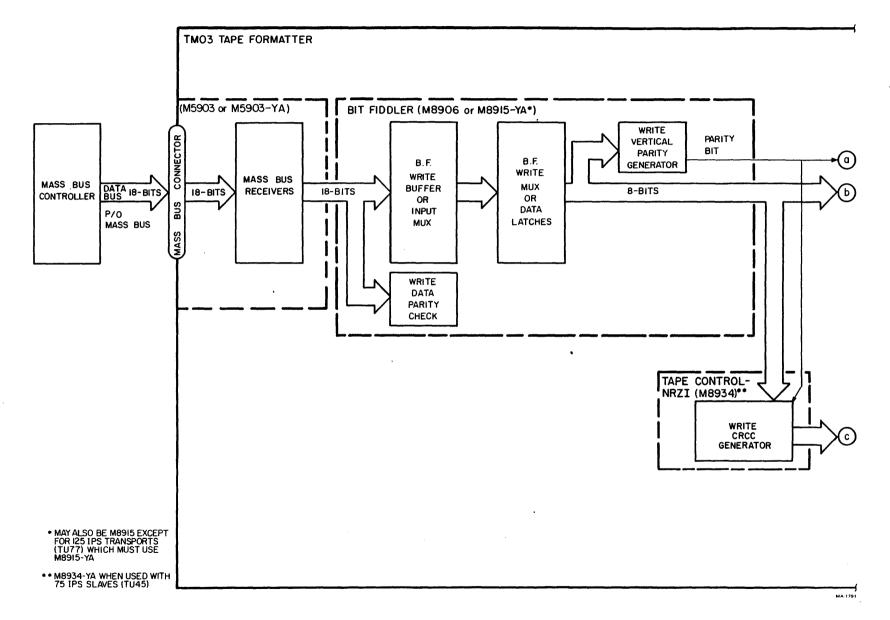

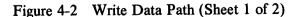

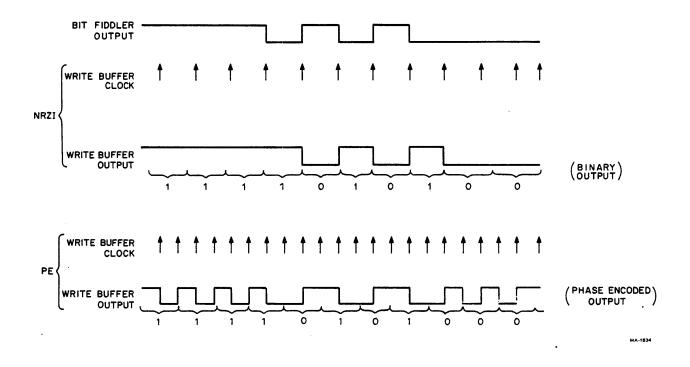

| 4-2        | Write Data Path.                                                       |        |

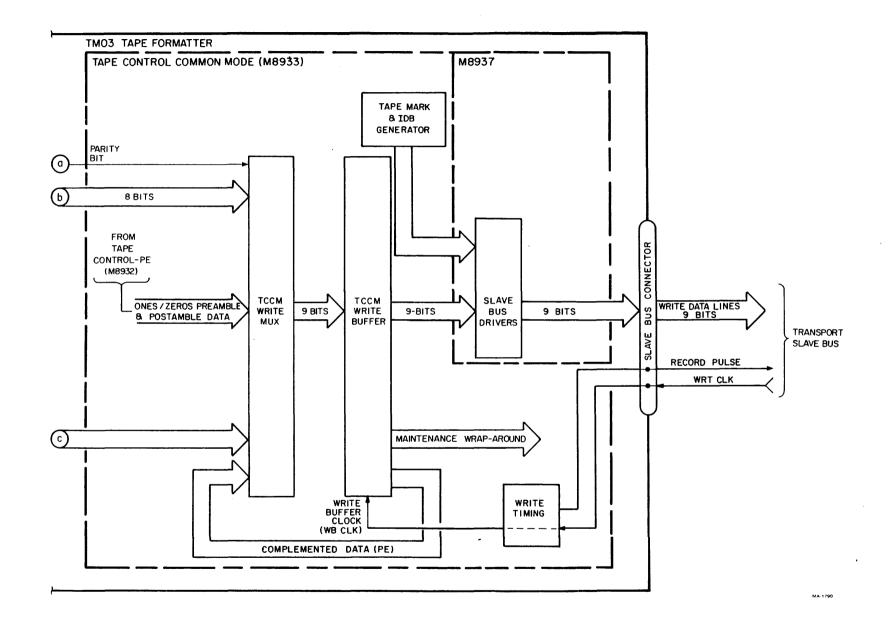

| 4-3        | TCCM Write Timing                                                      |        |

| 4-4        | Read Data Path                                                         | 4-12   |

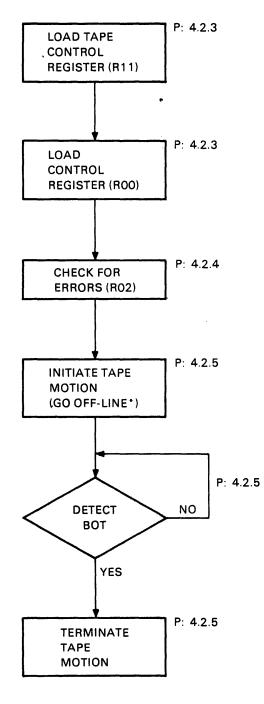

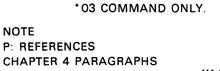

| 4-5        | Rewind Operational Flowchart                                           |        |

| 4-6        | Space Operational Flowchart                                            |        |

| 4-7        | Erase Operational Flowchart                                            |        |

| 4-8        | PE Read Operational Flowchart                                          |        |

| 4-9        | NRZI Read (Forward) Operational Flowchart                              |        |

| 4-10       | PE Data Write Operational Flowchart                                    |        |

| 4-11       | NRZI Data Write Operational Flowchart                                  |        |

| 4-12       | Write Tape Mark Operational Flowchart                                  |        |

| 4-13       | Global Wrap-Around (WRP0 and WRP4)                                     |        |

| 4-14       | Partial Wrap-Around (WRP1)                                             | 4-29   |

| 4-15       | Formatter Write Wrap-Around (WRP2)                                     | 4-29   |

| 4-16       | Formatter Read Wrap-Around (WRP3)                                      | 4-31   |

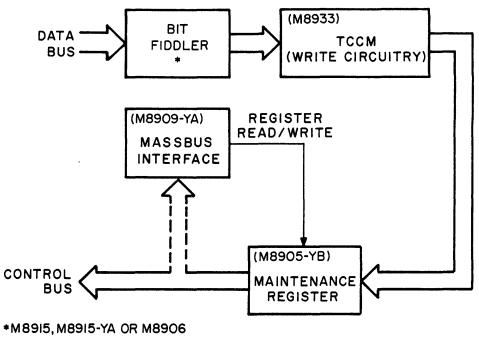

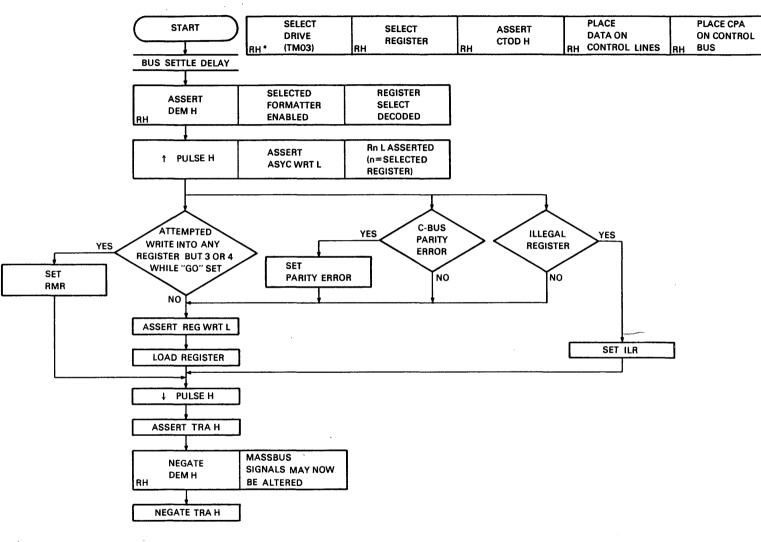

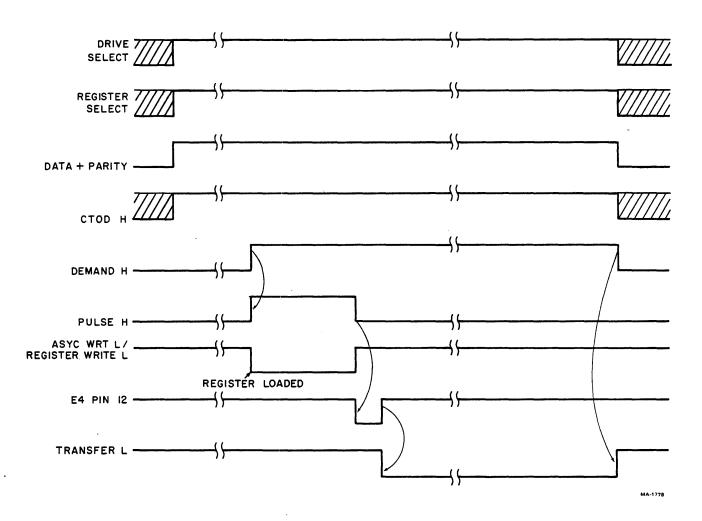

| 4-17       | Register Write Flowchart                                               |        |

| 4-18       | Register Write Timing Diagram                                          | 4-34   |

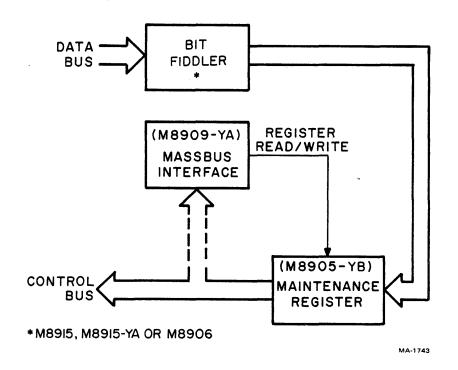

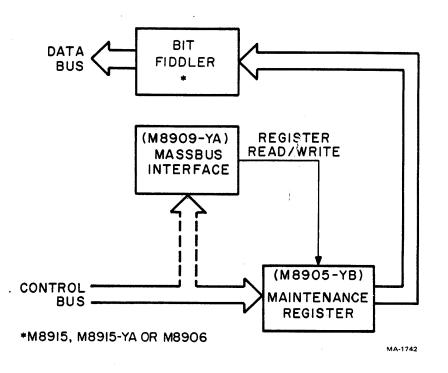

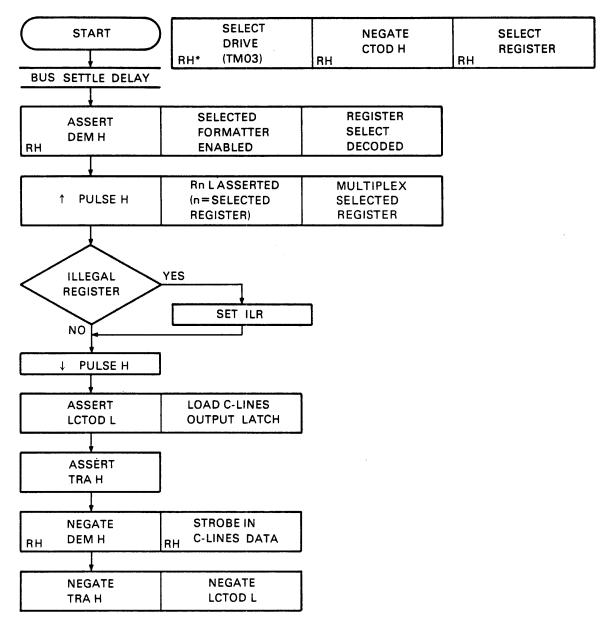

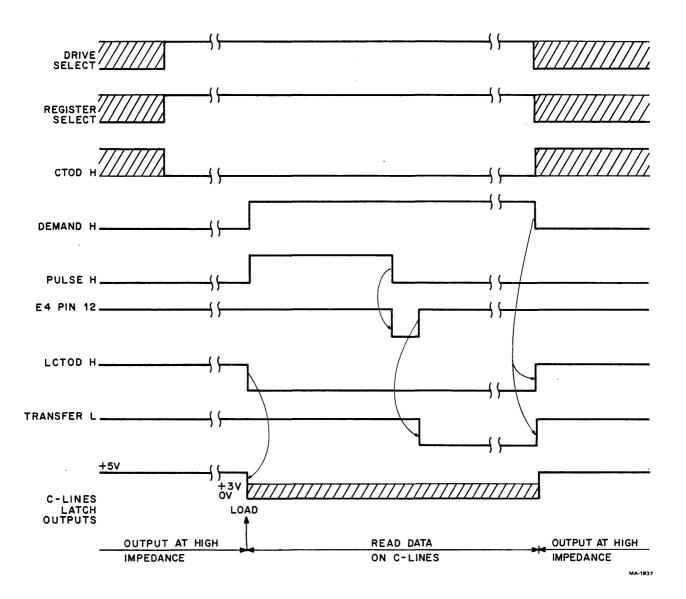

| 4-19       | Register Read Flowchart                                                | 4-36   |

| 4-20       | Register Read Timing Diagram                                           | 4-37   |

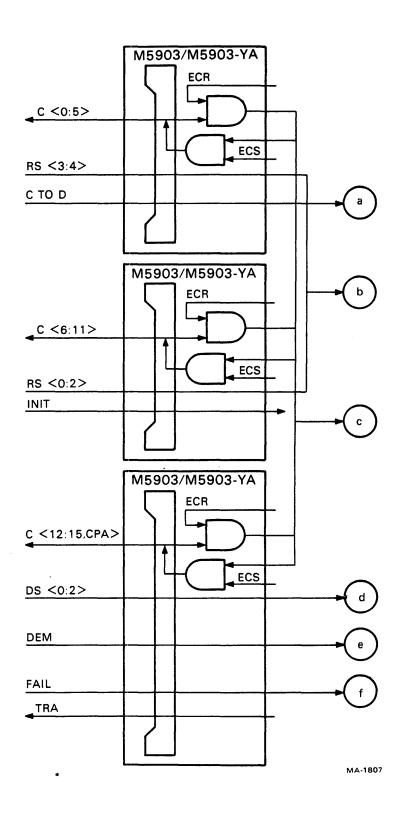

| 4-21       | TM03 Register Read/Write                                               | 4-38   |

| 4-22       | Attention Summary Register Read                                        | 4-42   |

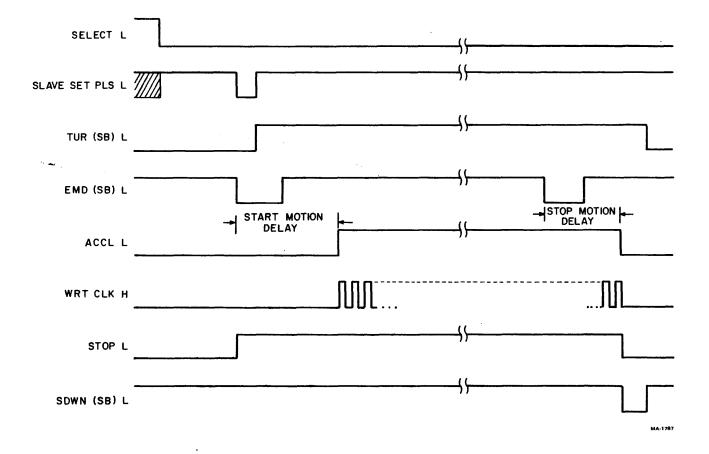

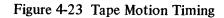

| 4-23       | Tape Motion Timing                                                     | 4-46   |

| 4-24       | Tape Motion Initiation Flowchart                                       | 4-47   |

| 4-25       | Tape Motion Termination Flowchart.                                     | 4-49   |

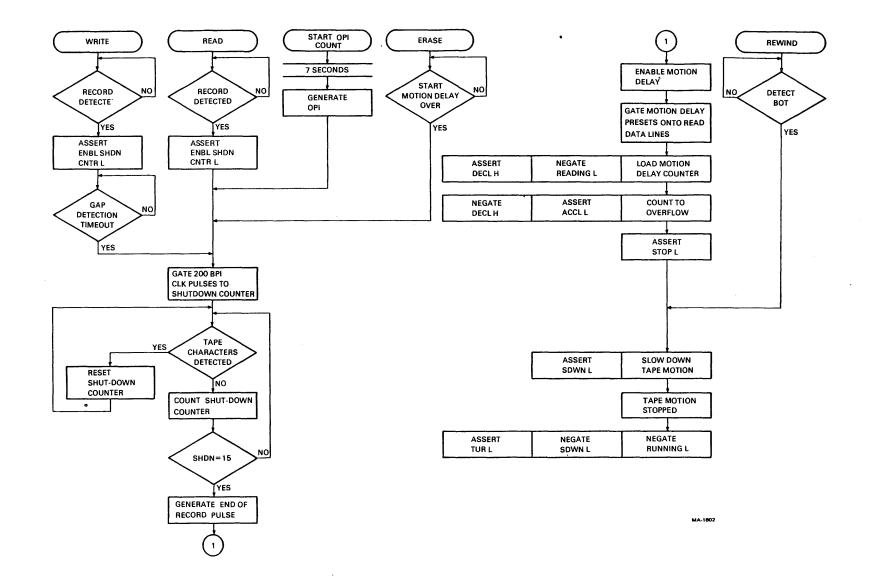

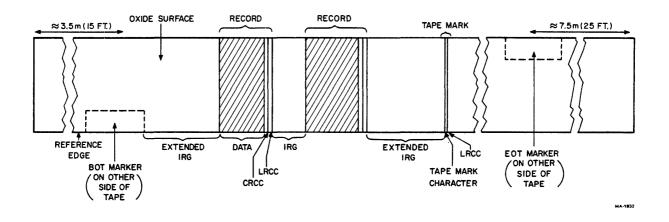

| 4-26       | Magnetic Tape Positioned at BOT                                        | 4-51   |

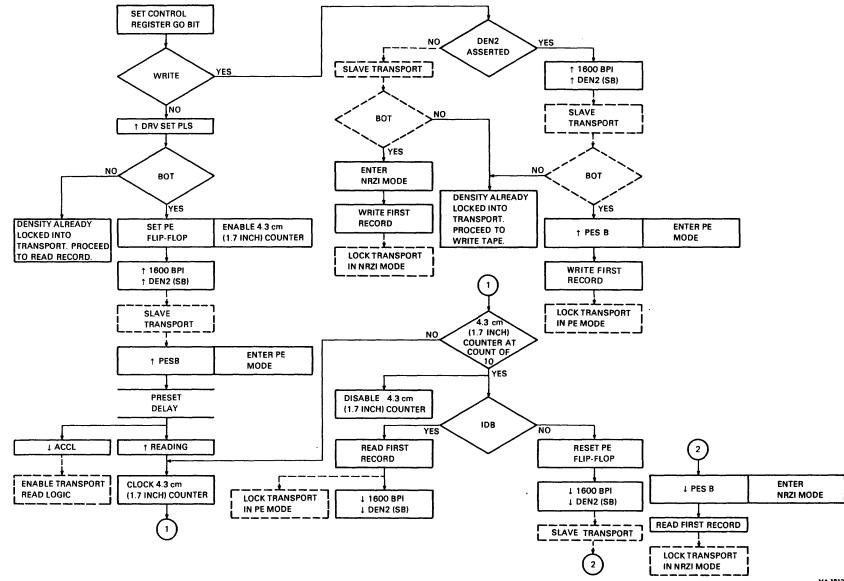

| 4-27       | Density Select Flow Diagram                                            |        |

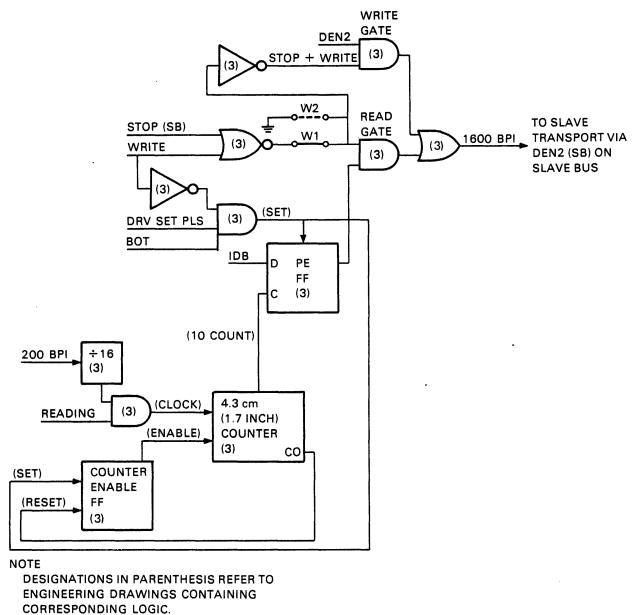

| 4-28       | Density Select Block Diagram                                           |        |

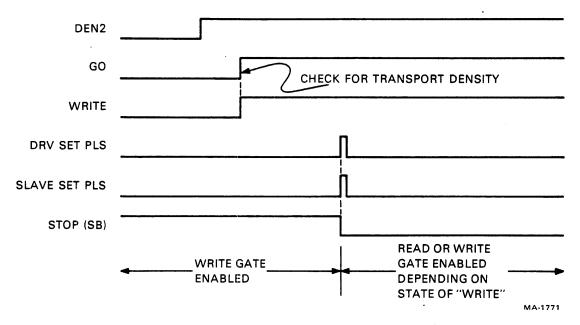

| 4-29       | Density Select Timing                                                  | 4-54   |

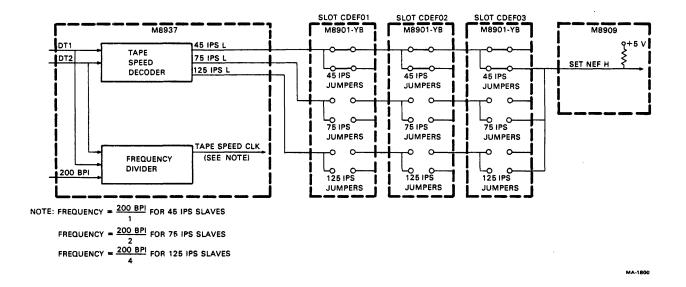

| 4-30       | Tape Speed Selection Block Diagram                                     | 4-56   |

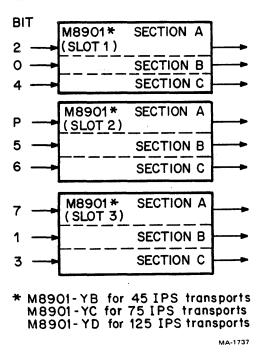

| 4-31       | Data Sync Channels                                                     | 4-57   |

| 4-32       | One Section of the Data Sync Module                                    | 4-58   |

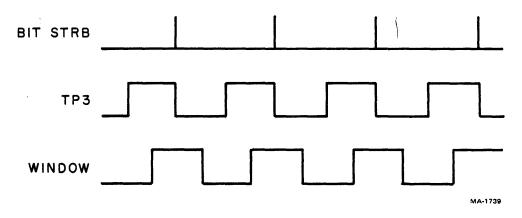

| 4-33       | Data Window Generation                                                 | 4-59   |

| 4-34       | Data Discriminator Timing Diagram                                      | 4-61   |

•

# FIGURES (Cont)

.

Figure No.

# Title

# Page

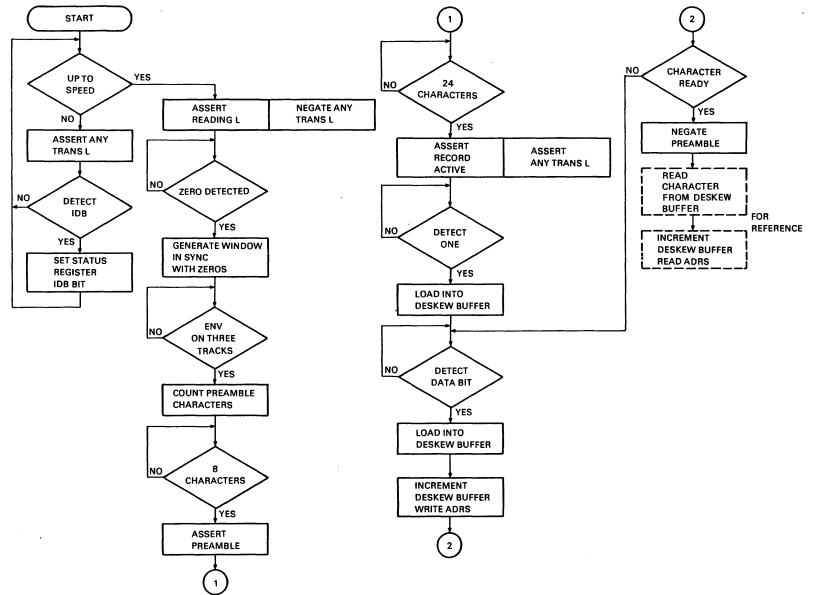

| 4-35       | Preamble/IDB Detection Flowchart 4-62                      |

|------------|------------------------------------------------------------|

| 4-36       | Data Sync Data Read Flowchart 4-63                         |

| 4-37       | IDB Detection Timing Diagram                               |

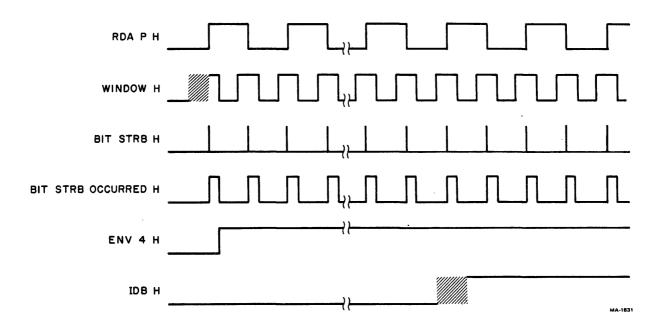

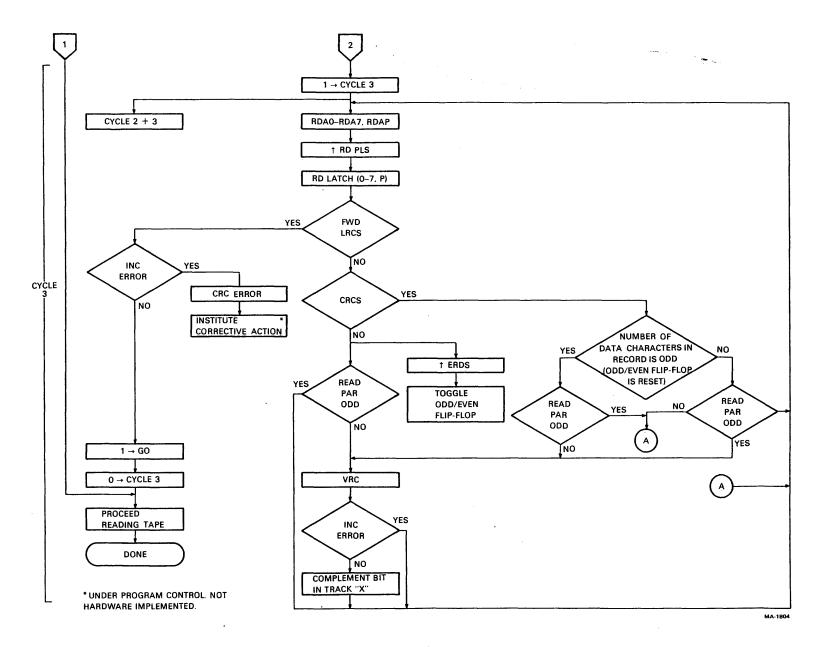

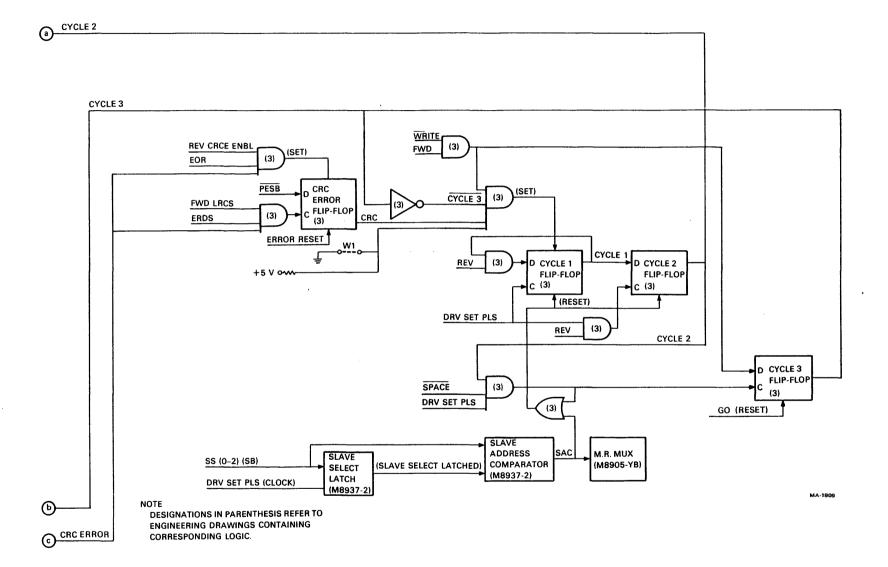

| 4-38       | NRZI Error Correction Cycle Flow Diagram 4-70              |

| 4-39       | NRZI Error Correction Block Diagram 4-72                   |

| 4-40       | TCCM Write Operation Timing (PE) 4-76                      |

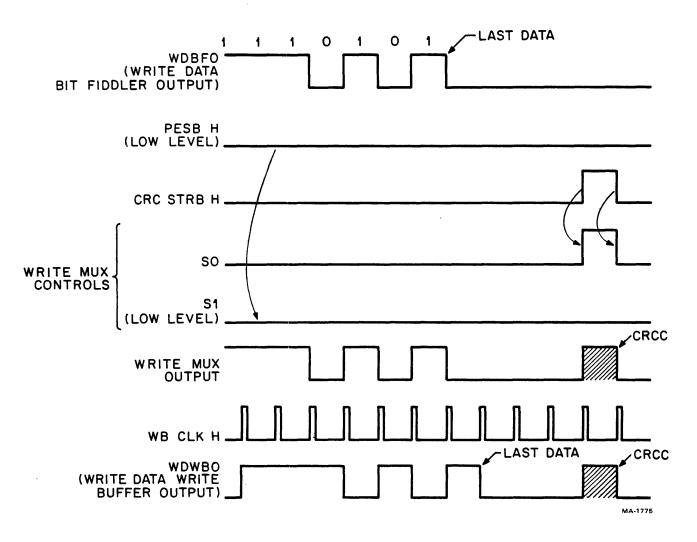

| 4-41       | TCCM Write Operation Timing (NRZI, 1 of 9 tracks)          |

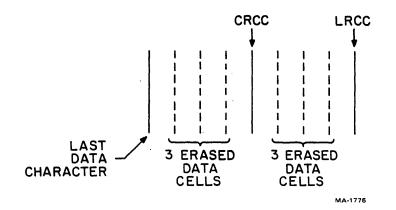

| 4-42       | CRCC and LRCC Timing                                       |

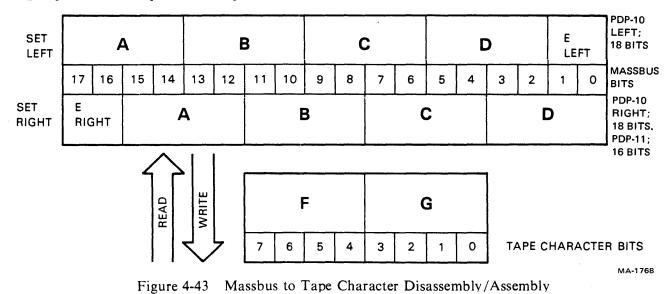

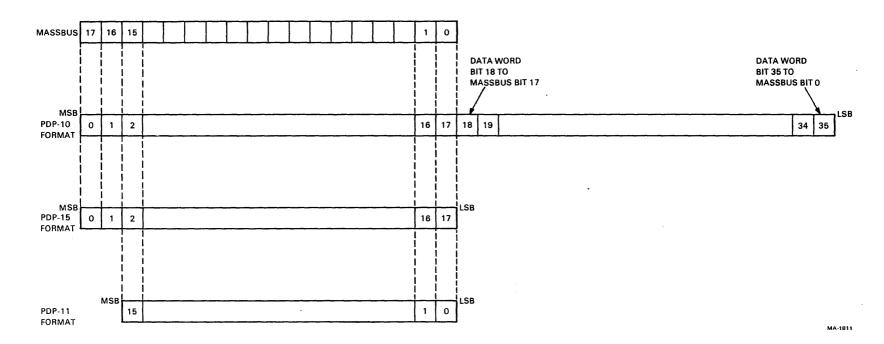

| 4-43       | Massbus to Tape Character Disassembly/Assembly 4-80        |

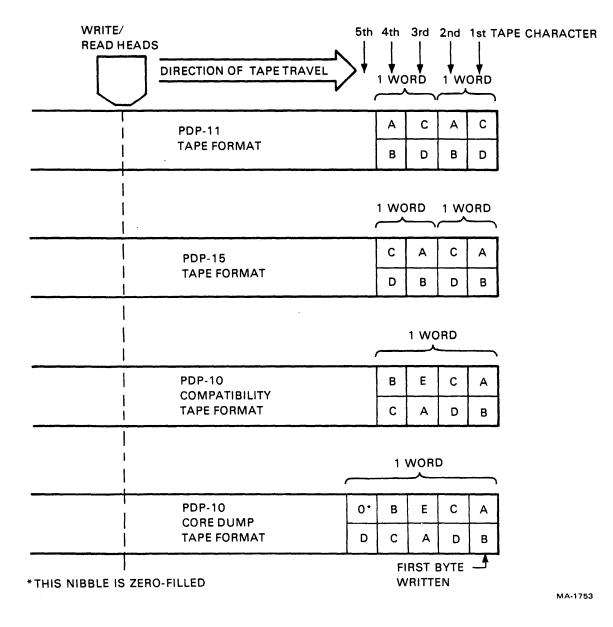

| 4-44       | Tape Recording Formats    4-81                             |

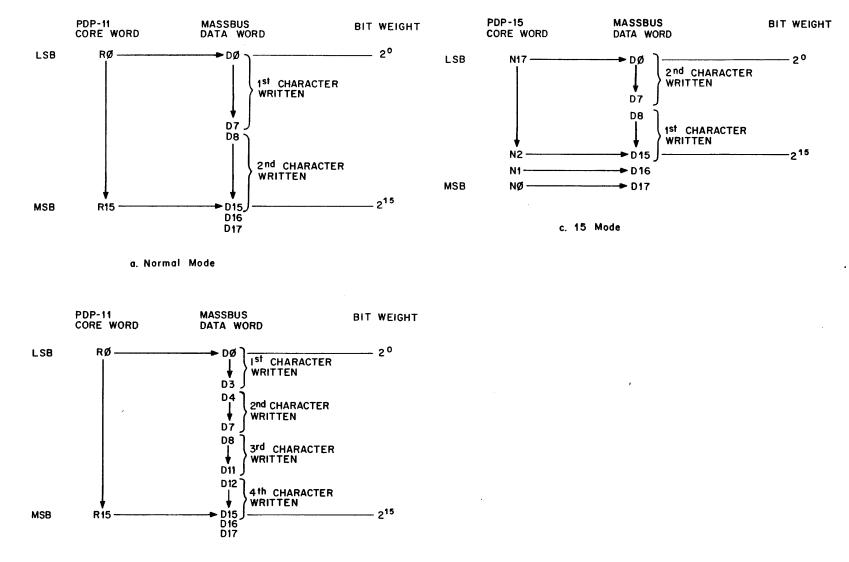

| 4-45       | Processor Data Word Formats on Massbus                     |

| 4-46       | 2907 Latch Logic                                           |

| 4-47       | Write/Read Data Paths 4-86                                 |

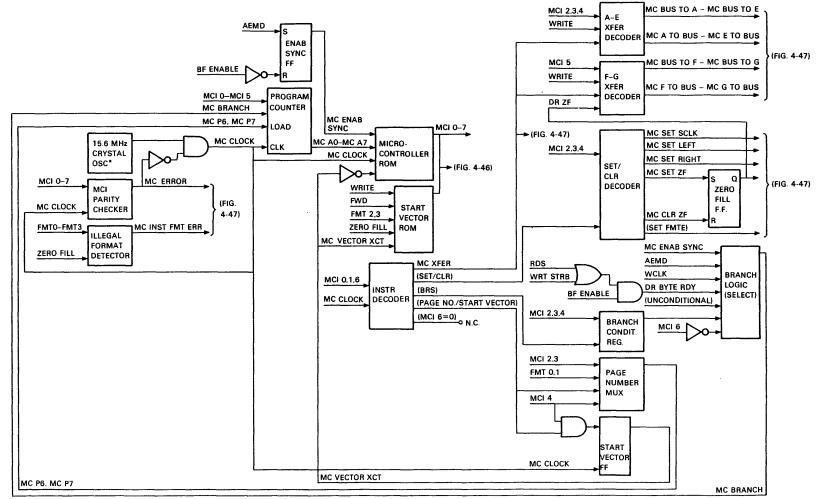

| 4-48       | Bit Fiddler Program Control Block Diagram 4-89             |

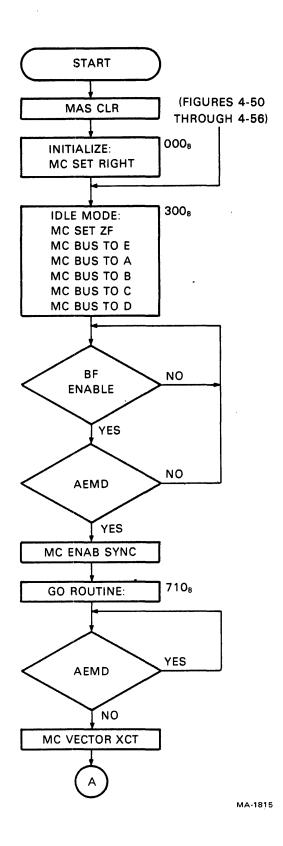

| 4-49       | Program Startup Flow Diagram                               |

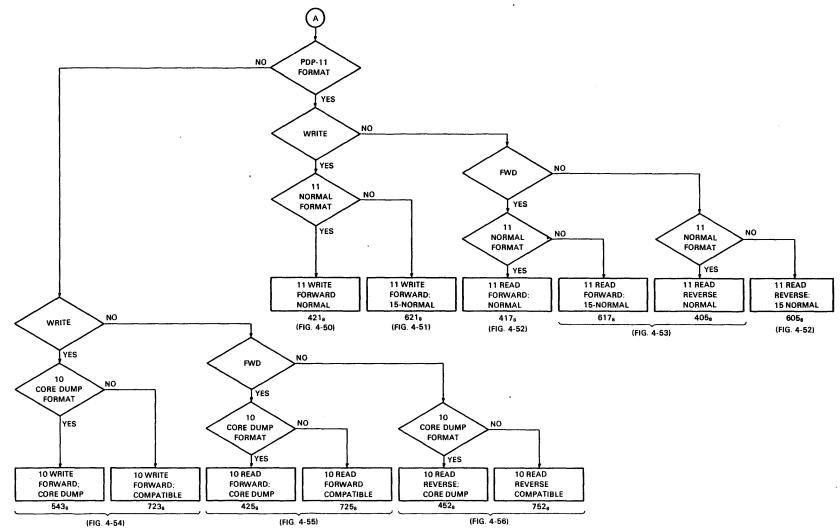

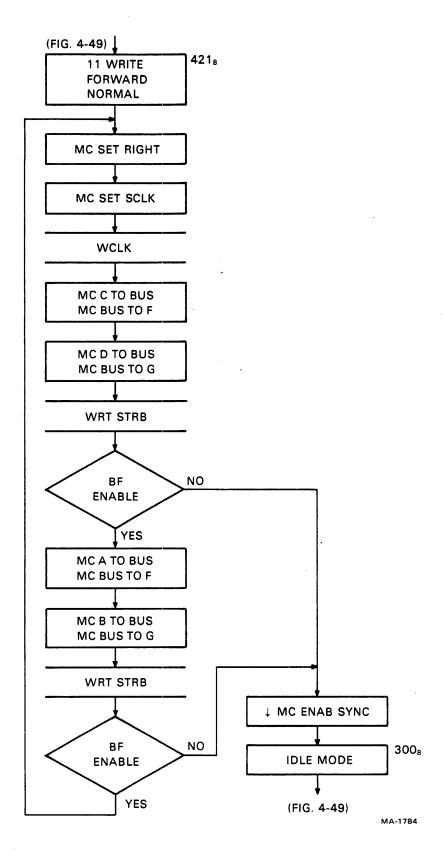

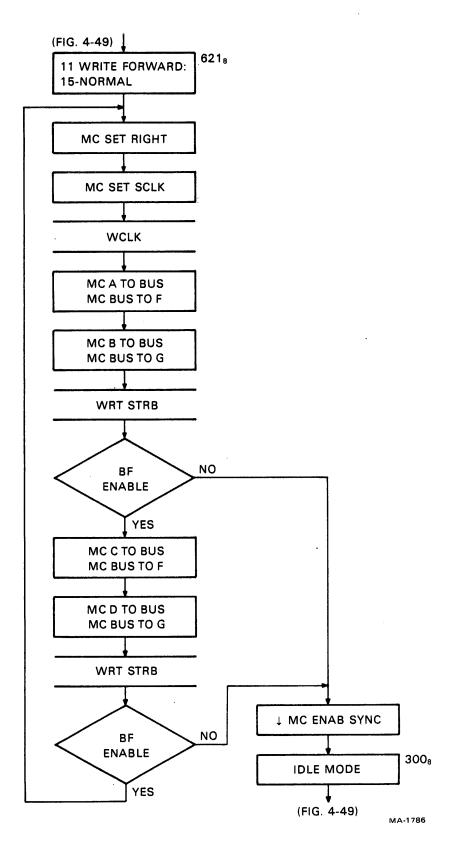

| 4-50       | PDP-11 Write Forward Normal Flow Diagram                   |

| 4-51       | PDP-11 Write Forward: (15-Normal) Flow Diagram             |

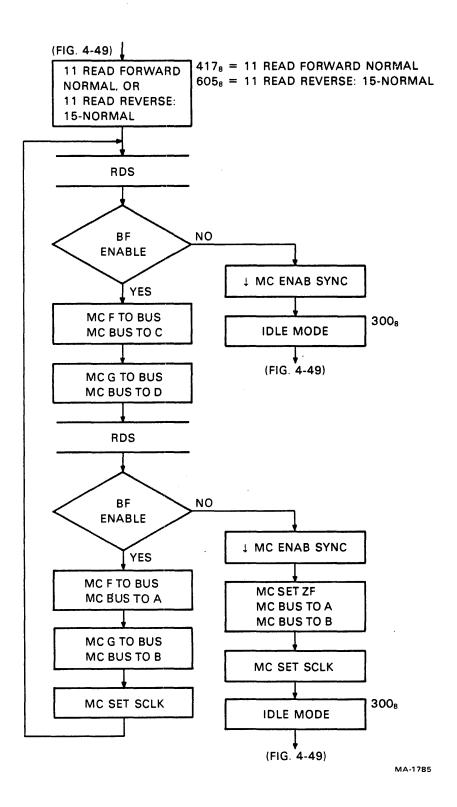

| 4-52       | PDP-11 Read Forward Normal/PDP-11 Read Reverse (15-Normal) |

|            | Flow Diagram                                               |

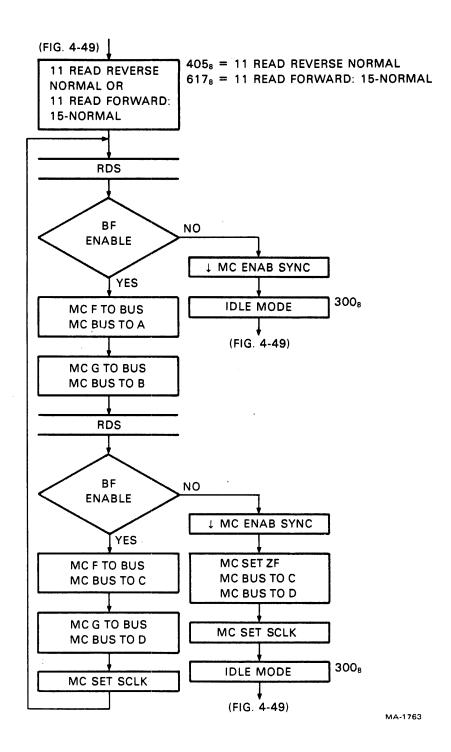

| 4-53       | PDP-11 Read Reverse Normal/PDP-11 Read Forward (15-Normal) |

|            | Flow Diagram                                               |

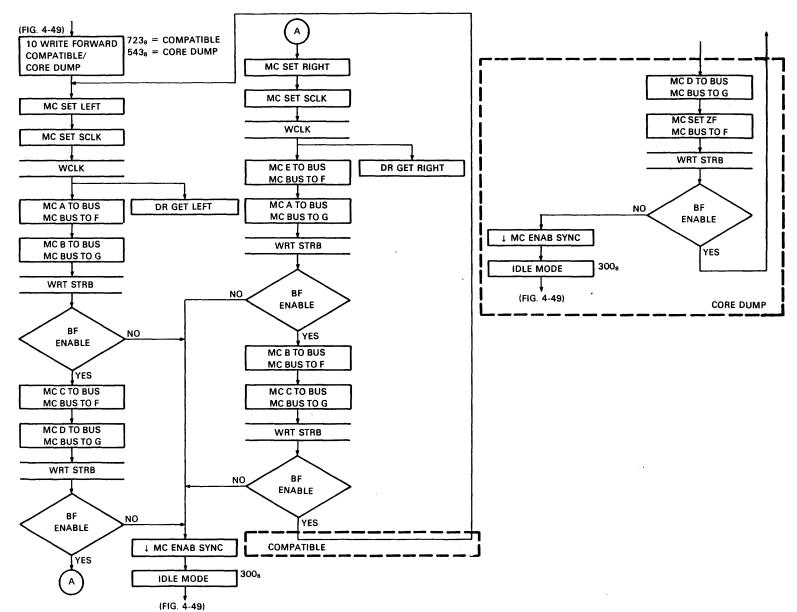

| 4-54       | PDP-10 Write Forward Flow Diagram                          |

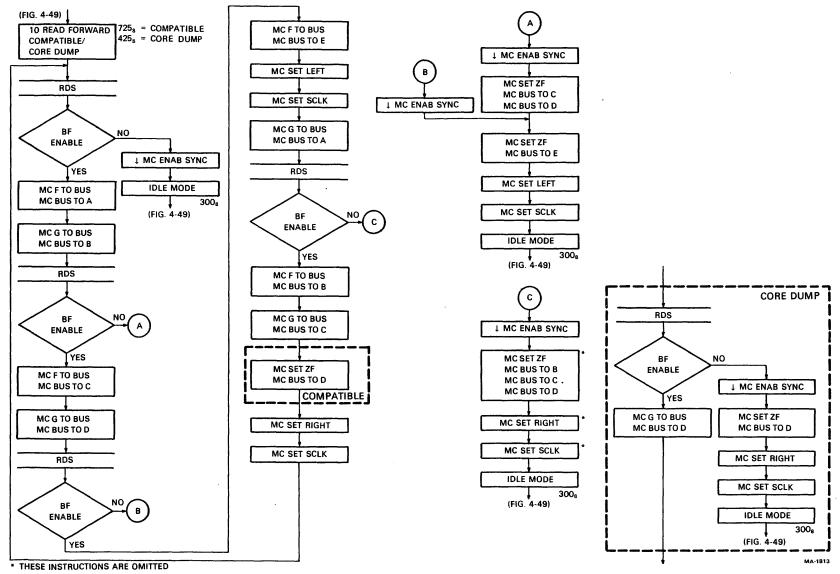

| 4-55       | PDP-10 Read Forward Flow Diagram                           |

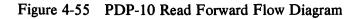

| 4-56       | PDP-10 Read Reverse Flow Diagram                           |

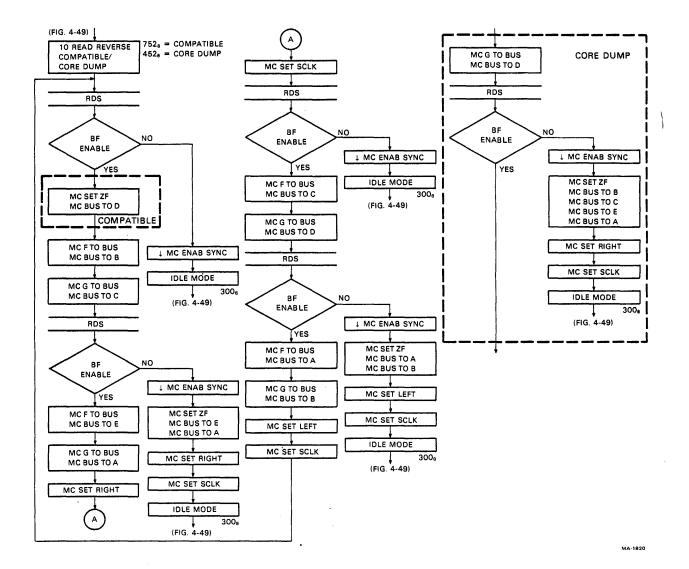

| 4-57       | M8906 Bit Fiddler Read Operation Flowchart                 |

| 4-58       | Bit Fiddler Read Forward Operation in Core Dump Mode       |

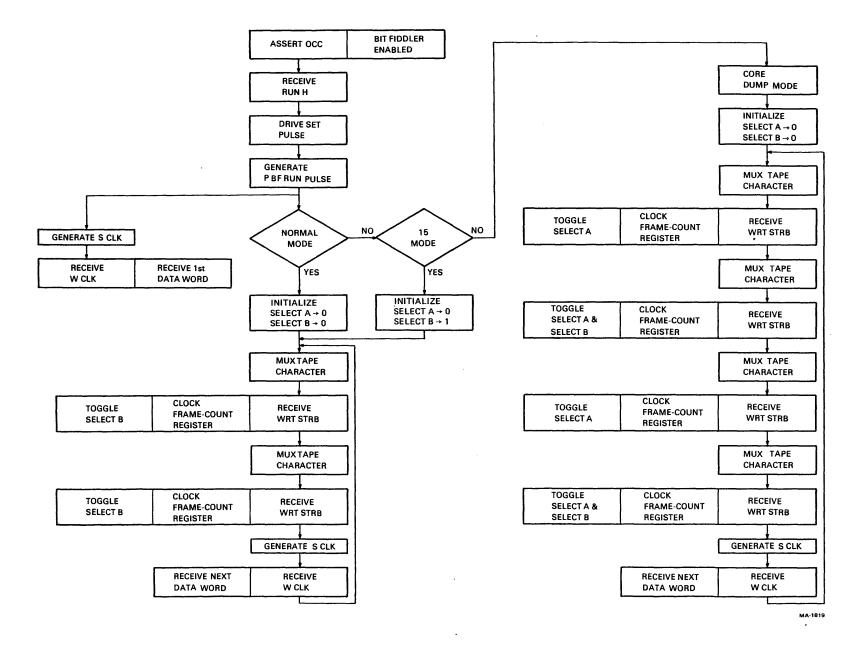

| 4-59       | M8906 Bit Fiddler Write Operation Flowchart                |

| 4-60       | M8906 Bit Fiddler Write Formats                            |

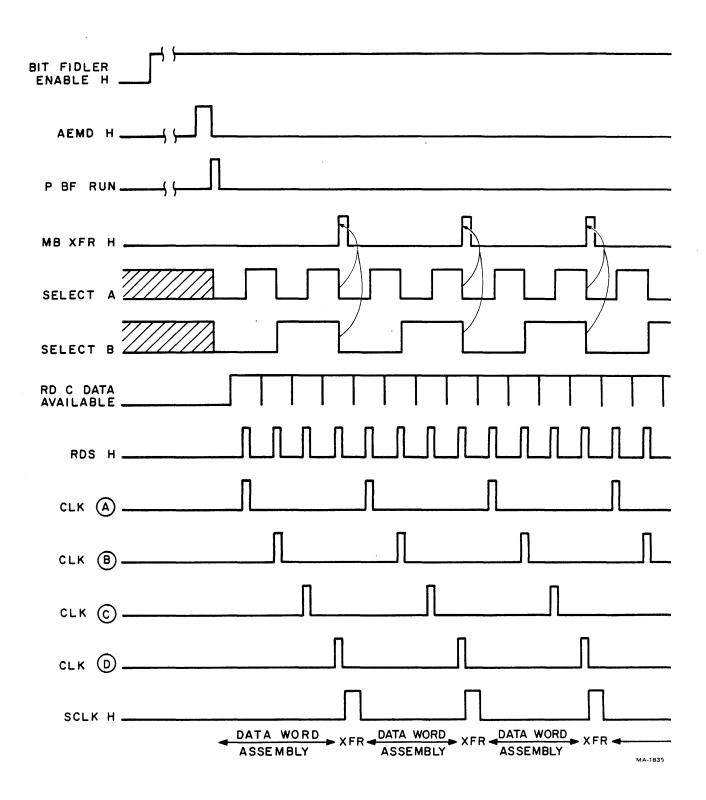

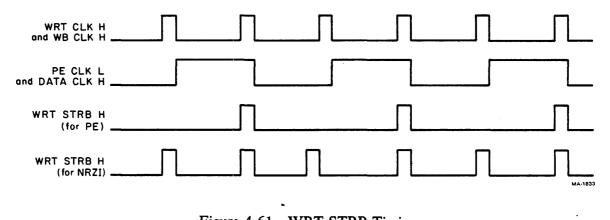

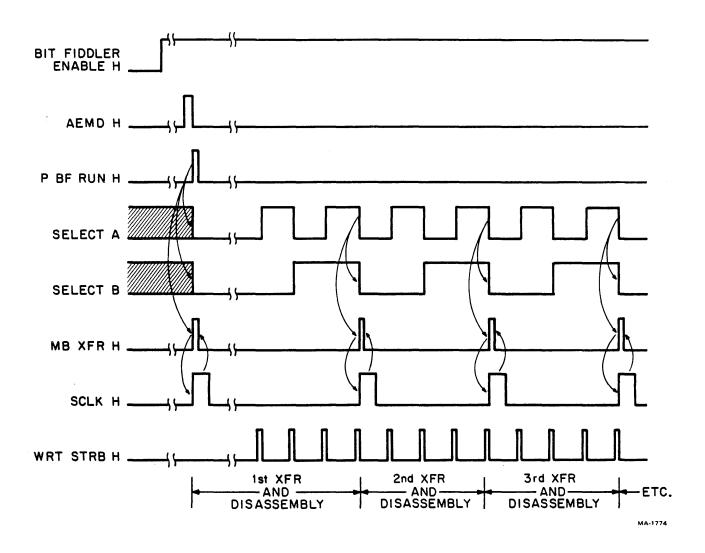

| 4-61       | WRT STRB Timing                                            |

| 4-62       | Bit Fiddler Write Operation in Core Dump Mode              |

| 4-63       | TM03 Power System                                          |

| 5-1        | DC Voltages on TM03 Backplane                              |

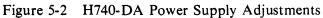

| 5-2        | H740-DA Power Supply Adjustments                           |

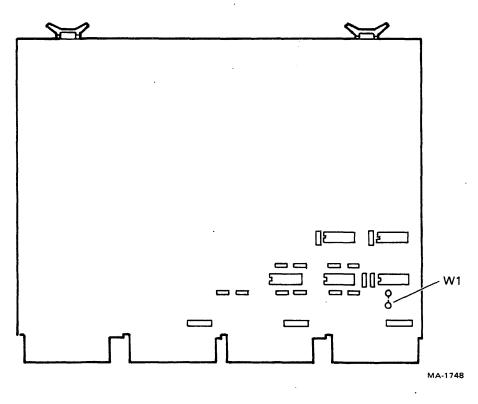

| 5-3        | M8901 Jumpers                                              |

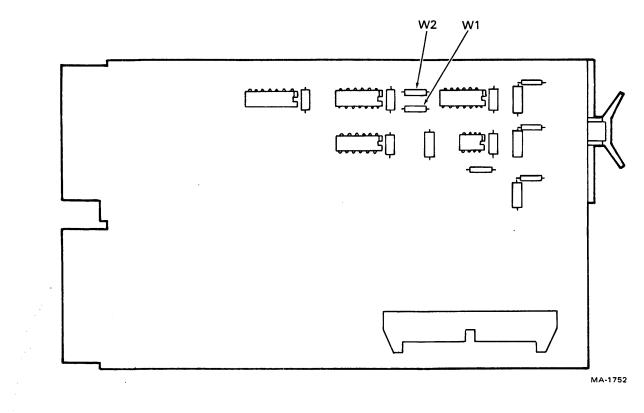

| 5-4        | M8934 Jumpers                                              |

| 5-5        | M8905-YB Jumper                                            |

| 5-6        | M8905-1D Jumper                                            |

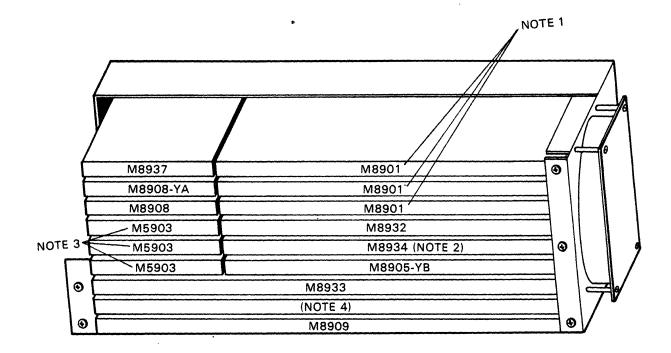

| 5-7        | Location of TM03 Modules                                   |

| 5-8        | Steady State Clock Trouble Analysis                        |

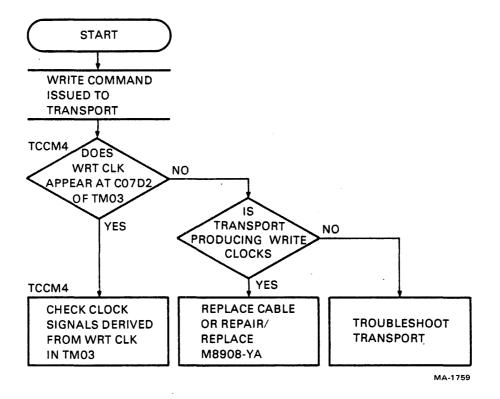

| 5-9        | Write Clock Trouble Analysis                               |

| C-1        | NRZI Format (Nine-channel)                                 |

| C-1<br>C-2 | PE Waveforms                                               |

| C-2<br>C-3 |                                                            |

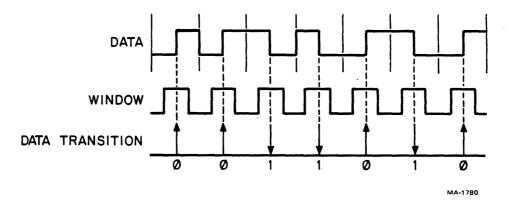

| C-3<br>C-4 | Data Window                                                |

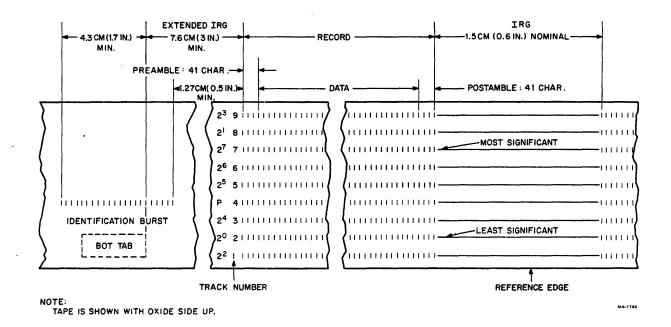

|            | PE Recording Format                                        |

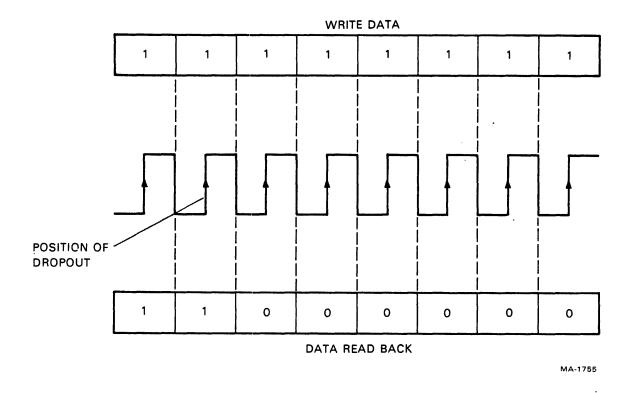

| C-5        | Potential Error Caused by Single Bit Dropout in PE C-6     |

# TABLES

| 1-1       Related Documents       1-12         1-2       Unit Specifications       1-13         2-1       TM03 Registers       2-2         2-2       Command Function Codes       2-5         2-3       Status Register Bit Positions       2-7         2-4       Error Register Bit Indicators       2-10         2-5       Maintenance Register Bit Positions       2-11         2-6       Drive Type Register Bit Positions       2-17         2-7       Tape Control Register Bit Positions       2-17         2-8       PDP-10 Massbus Word Format       2-22         2-9       PDP-11 Massbus Word Format       2-23         2-10       PDP-15 Massbus Word Format       2-23         2-11       PDP-10 Core Dump Mode – Format Code 0001       2-23         2-12       PDP-10 Core Dump Mode – Format Code 1001       2-24         2-14       PDP-11 Core Dump Mode – Format Code 1001       2-24         2-15       PDP-15 Normal Mode – Format Code 0001       2-24         2-16       PDP-15 Normal Mode – Format Code 0001       2-24         2-17       Command Functions       4-23         3-13       TM03 Clock Signal Frequencies       4-32         4-14       Massbus Interface Signals                                                                                                                     | Table No. | Title                                            | Page  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------|-------|

| 2-1TM03 Registers2-22-2Command Function Codes2-52-3Status Register Bit Positions2-72-4Error Register Bit Indicators2-102-5Maintenance Register Bit Positions2-112-6Drive Type Register Bit Positions2-172-7Tape Control Register Bit Positions2-122-9PDP-10 Massbus Word Format2-222-9PDP-10 Compatability Mode – Format Code 00012-232-11PDP-10 Compatability Mode – Format Code 00002-232-12PDP-10 Compatability Mode – Format Code 11002-242-14PDP-11 Normal Mode – Format Code 11012-242-15PDP-15 Core Dump Mode – Format Code 11002-242-16PDP-15 Core Dump Mode – Format Code 11102-242-17Command Functions2-254-1Massbus Interface Signals4-14-2Slave Bus Interface Signals4-34-3TM03 Clock Signal Frequencies4-334-4Register/Multiplexer Locations4-344-5Possible Errors During TM03/Transport Operations4-464-6Conditions Prevailing When CRC Character Has No Parity Error4-694-7Legal Format Codes4-1064-8Bit Fiddler Initialization/Operation4-1064-9Read Formatting Codes4-1064-10CLK A, B, C, and D Sequences4-1064-11Write Formatting Codes5-155-3Bit Fiddler Initialization/Operation5-16<                                                                                                                                                                                                                     | 1-1       | Related Documents                                | 1-12  |

| 2-2Command Function Codes.2-52-3Status Register Bit Positions2-102-4Error Register Bit Indicators2-102-5Maintenance Register Bit Positions2-112-6Drive Type Register Bit Positions2-112-7Tape Control Register Bit Positions2-122-9PDP-10 Massbus Word Format.2-222-9PDP-11 Massbus Word Format.2-232-11PDP-10 Core Dump Mode – Format Code 00112-232-12PDP-10 Core Dump Mode – Format Code 0000.2-232-13PDP-11 Normal Mode – Format Code 11002-242-14PDP-15 Normal Mode – Format Code 11002-242-15PDP-15 Normal Mode – Format Code 10012-242-16PDP-15 Core Dump Mode – Format Code 00012-242-17Command Functions.2-254-1Massbus Interface Signals4-14-2Slave Bus Interface Signals4-14-3TM03 Clock Signal Frequencies4-324-4Register/Multiplexer Locations.4-344-5Possible Errors During TM03/Transport Operations.4-344-6Conditions Prevailing When CRC Character Has No Parity Error.4-694-7Legal Format Codes4-1064-8Bit Fiddler Initialization/Operation4-104-9Read Formatting Codes4-104-11Write Format Tice Signals5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, S                                                                                                                                                                                                  | 1-2       | Unit Specifications                              | 1-13  |

| 2-3       Status Register Bit Positions       2-7         2-4       Error Register Bit Positions       2-10         2-5       Maintenance Register Bit Positions       2-11         2-6       Drive Type Register Bit Positions       2-14         2-6       PDP-10 Massbus Word Format       2-22         2-9       PDP-10 Massbus Word Format       2-22         2-10       PDP-15 Massbus Word Format       2-23         2-11       PDP-10 Compatability Mode – Format Code 0011       2-23         2-12       PDP-10 Core Dump Mode – Format Code 1100       2-24         2-14       PDP-11 Normal Mode – Format Code 1100       2-24         2-15       PDP-15 Normal Mode – Format Code 1100       2-24         2-16       PDP-15 Normal Mode – Format Code 0001       2-24         2-17       Command Functions       2-25         4-16       PDP-15 Normal Mode – Format Code 0001       2-24         2-17       Command Functions       4-3         4-3       TM03 Clock Signals       4-4         4-2       Slave Bus Interface Signals       4-3         4-3       TM03 Clock Signal Frequencies       4-33         4-4       Register/Multiplexer Locations       4-45         4-5       Possible Erro                                                                                                            | 2-1       | TM03 Registers                                   | 2-2   |

| 2-4       Error Register Bit Indicators       2-10         2-5       Maintenance Register Bit Positions       2-10         2-6       Drive Type Register Bit Positions       2-17         2-7       Tape Control Register Bit Positions       2-19         2-8       PDP-10 Massbus Word Format.       2-22         2-9       PDP-11 Massbus Word Format.       2-23         2-10       PDP-10 Compatability Mode – Format Code 0011       2-23         2-11       PDP-10 Compatability Mode – Format Code 0000       2-23         2-13       PDP-11 Core Dump Mode – Format Code 1100       2-24         2-14       PDP-11 Core Dump Mode – Format Code 1101       2-24         2-16       PDP-15 Normal Mode – Format Code 1101       2-24         2-16       PDP-15 Coren Dump Mode – Format Code 0001       2-24         2-17       Command Functions       4-2         3-13       FUGO Colock Signals       4-1         4-2       Slave Bus Interface Signals       4-1         4-2       Slave Bus Interface Signals       4-3         4-3       TM03 Clock Signal Frequencies       4-33         4-4       Register/Multiplexer Locations       4-35         4-5       Possible Errors During TM03/Transport Operations       4-46 </td <td>2-2</td> <td>Command Function Codes</td> <td> 2-5</td>                     | 2-2       | Command Function Codes                           | 2-5   |

| 2-5       Maintenance Register Bit Positions       2-14         2-6       Drive Type Register Bit Positions       2-14         2-7       Tape Control Register Bit Positions.       2-19         2-8       PDP-10 Massbus Word Format.       2-22         2-9       PDP-11 Massbus Word Format.       2-23         2-11       PDP-16 Compatability Mode – Format Code 0011.       2-23         2-12       PDP-10 Core Dump Mode – Format Code 0000.       2-23         2-13       PDP-11 Core Dump Mode – Format Code 1100.       2-24         2-14       PDP-15 Normal Mode – Format Code 1101.       2-24         2-15       PDP-15 Normal Mode – Format Code 1100.       2-24         2-16       PDP-15 Normal Mode – Format Code 1001.       2-24         2-17       Command Functions.       2-25         4-1       Massbus Interface Signals       4-4         4-2       Slave Bus Interface Signals       4-4         4-3       TM03 Clock Signal Frequencies       4-33         4-4       Register/Multiplexer Locations.       4-43         4-5       Possible Errors During TM03/Transport Operations.       4-44         4-6       Conditions Prevailing When CRC Character Has No Parity Error       4-66         4-10       Click A, B, C, and D                                                                 | 2-3       | Status Register Bit Positions                    | 2-7   |

| 2-6       Drive Type Register Bit Positions       2-17         2-7       Tape Control Register Bit Positions       2-19         2-8       PDP-10 Massbus Word Format       2-22         2-9       PDP-11 Massbus Word Format       2-23         2-10       PDP-10 Compatability Mode – Format Code 0011       2-23         2-12       PDP-10 Compatability Mode – Format Code 0000       2-23         2-13       PDP-11 Core Dump Mode – Format Code 1101       2-24         2-15       PDP-15 Normal Mode – Format Code 1101       2-24         2-16       PDP-15 Core Dump Mode – Format Code 1101       2-24         2-17       Command Functions.       2-25         4-14       PDP-15 Core Dump Mode – Format Code 1101       2-24         2-17       Command Functions.       2-25         4-1       Massbus Interface Signals       4-1         4-2       Slave Bus Interface Signals       4-3         4-3       TM03 Clock Signal Frequencies       4-33         4-4       Register/Multiplexer Locations.       4-35         4-5       Possible Errors During TM03/Transport Operations       4-43         4-6       Conditions Prevailing When CRC Character Has No Parity Error.       4-69         4-7       Legal Format Codes       4-                                                                         | 2-4       | Error Register Bit Indicators                    | 2-10  |

| 2-7       Tape Control Register Bit Positions.       2-19         2-8       PDP-10 Massbus Word Format.       2-22         2-9       PDP-11 Massbus Word Format.       2-22         2-10       PDP-11 Massbus Word Format.       2-23         2-11       PDP-10 Corne Dump Mode – Format Code 0011.       2-23         2-12       PDP-10 Corne Dump Mode – Format Code 0000.       2-23         2-13       PDP-11 Normal Mode – Format Code 1100.       2-24         2-14       PDP-11 Core Dump Mode – Format Code 1001.       2-24         2-15       PDP-15 Normal Mode – Format Code 0001.       2-24         2-16       PDP-15 Normal Mode – Format Code 0001.       2-24         2-17       Command Functions.       2-25         4-1       Massbus Interface Signals       4-1         4-2       Slave Bus Interface Signals       4-3         4-3       TM03 Clock Signal Frequencies       4-33         4-4       Register/Multiplexer Locations.       4-43         4-5       Possible Errors During TM03/Transport Operations.       4-43         4-6       Conditions Prevailing When CRC Character Has No Parity Error.       4-69         4-7       Legal Format Codes       4-10         4-8       Bit Fiddler Initialization/Operation                                                                        | 2-5       | Maintenance Register Bit Positions               | 2-14  |

| 2-7       Tape Control Register Bit Positions.       2-19         2-8       PDP-10 Massbus Word Format.       2-22         2-9       PDP-11 Massbus Word Format.       2-22         2-10       PDP-11 Massbus Word Format.       2-23         2-11       PDP-10 Corne Dump Mode – Format Code 0011       2-23         2-12       PDP-10 Corne Dump Mode – Format Code 0000.       2-23         2-13       PDP-11 Normal Mode – Format Code 1100       2-24         2-14       PDP-11 Core Dump Mode – Format Code 0001.       2-24         2-15       PDP-15 Normal Mode – Format Code 0001.       2-24         2-16       PDP-15 Normal Mode – Format Code 0001.       2-24         2-17       Command Functions.       2-25         4-1       Massbus Interface Signals       4-1         4-2       Slave Bus Interface Signals       4-3         4-3       TM03 Clock Signal Frequencies       4-33         4-4       Register/Multiplexer Locations.       4-34         4-5       Possible Errors During TM03/Transport Operations       4-43         4-6       Conditions Prevailing When CRC Character Has No Parity Error.       4-69         4-7       Legal Format Codes       4-10         4-8       Bit Fiddler Initialization/Operation                                                                           | 2-6       | Drive Type Register Bit Positions                | 2-17  |

| 2-8         PDP-10 Massbus Word Format.         2-22           2-9         PDP-11 Massbus Word Format.         2-22           2-10         PDP-15 Massbus Word Format.         2-23           2-11         PDP-10 Compatability Mode – Format Code 0001.         2-23           2-12         PDP-10 Core Dump Mode – Format Code 1000.         2-24           2-13         PDP-11 Normal Mode – Format Code 1101.         2-23           2-14         PDP-11 Sormal Mode – Format Code 1100.         2-24           2-15         PDP-15 Normal Mode – Format Code 1110.         2-24           2-16         PDP-15 Core Dump Mode – Format Code 0001.         2-24           2-17         Command Functions.         2-25           4-1         Massbus Interface Signals         4-1           4-2         Slave Bus Interface Signals         4-3           4-3         TM03 Clock Signal Frequencies         4-32           4-4         Register/Multiplexer Locations.         4-43           4-5         Possible Errors During TM03/Transport Operations.         4-43           4-6         Conditions Prevailing When CRC Character Has No Parity Error.         4-66           4-9         Read Formatting Codes.         4-106           4-10         CLK A. B. C. and D Sequences.         4-1                     | 2-7       | Tape Control Register Bit Positions              | 2-19  |

| 2-9       PDP-11 Massbus Word Format.       2-22         2-10       PDP-15 Massbus Word Format.       2-23         2-11       PDP-10 Compatability Mode – Format Code 0011.       2-23         2-12       PDP-10 Core Dump Mode – Format Code 1100.       2-24         2-14       PDP-11 Normal Mode – Format Code 1101.       2-24         2-14       PDP-11 Core Dump Mode – Format Code 1101.       2-24         2-15       PDP-15 Normal Mode – Format Code 1101.       2-24         2-16       PDP-15 Core Dump Mode – Format Code 0001.       2-24         2-17       Command Functions.       2-25         4-1       Massbus Interface Signals       4-3         4-2       Slave Bus Interface Signals       4-3         4-3       TM03 Clock Signal Frequencies       4-34         4-4       Register/Multiplexer Locations       4-35         4-5       Possible Errors During TM03/Transport Operations       4-43         4-6       Conditions Prevailing When CRC Character Has No Parity Error.       4-69         4-7       Legal Format Codes       4-91         4-8       Bit Fiddler Initialization/Operation       4-106         4-10       CLK A, B, C, and D Sequences       4-106         4-11       Write Formatting Codes <t< td=""><td>2-8</td><td>PDP-10 Massbus Word Format</td><td> 2-22</td></t<> | 2-8       | PDP-10 Massbus Word Format                       | 2-22  |

| 2-11PDP-10 Compatability Mode – Format Code 0011.2-232-12PDP-10 Core Dump Mode – Format Code 0000.2-232-13PDP-11 Normal Mode – Format Code 1100.2-242-14PDP-11 Core Dump Mode – Format Code 1101.2-242-15PDP-15 Core Dump Mode – Format Code 1110.2-242-16PDP-15 Core Dump Mode – Format Code 0001.2-242-17Command Functions.2-254-1Massbus Interface Signals4-14-2Slave Bus Interface Signals4-34-3TM03 Clock Signal Frequencies4-324-4Register/Multiplexer Locations.4-354-5Possible Errors During TM03/Transport Operations4-494-6Conditions Prevailing When CRC Character Has No Parity Error.4-694-7Legal Format Codes4-1064-9Read Formatting Codes4-1064-10CLK A, B, C, and D Sequences4-134-11Write Formatting Codes4-164-12Bit Fiddler Initialization/Operation4-164-12Bit Fiddler Initialization/Operation4-164-12Bit Fiddler Modules vs System Processor5-45-3Bit Fiddler Modules vs System Processor5-45-4TM03/Transport Operations5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Trouble Analysis5-155-9Analysis of Data Error                                                                                                                                                               | 2-9       |                                                  |       |

| 2-12       PDP-10 Core Dump Mode – Format Code 0000.       2-23         2-13       PDP-11 Normal Mode – Format Code 1100       2-24         2-14       PDP-11 Core Dump Mode – Format Code 1101.       2-24         2-16       PDP-15 Normal Mode – Format Code 1110       2-24         2-16       PDP-15 Core Dump Mode – Format Code 0001.       2-24         2-17       Command Functions.       2-25         4-1       Massbus Interface Signals       4-3         4-2       Slave Bus Interface Signals       4-3         4-3       TM03 Clock Signal Frequencies       4-32         4-4       Register/Multiplexer Locations.       4-43         4-5       Possible Errors During TM03/Transport Operations       4-43         4-6       Conditions Prevailing When CRC Character Has No Parity Error.       4-69         4-7       Legal Formatting Codes       4-106         4-8       Bit Fiddler Initialization/Operation       4-106         4-10       CLK A, B, C, and D Sequences       4-108         4-11       Write Formatting Codes       5-1         5-2       TM03 DC Voltages.       5-1         5-3       Bit Fiddler Initialization/Operation       5-16         5-4       TM03/Transport Diagnostics       5-16 <td>2-10</td> <td>PDP-15 Massbus Word Format</td> <td> 2-23</td>                      | 2-10      | PDP-15 Massbus Word Format                       | 2-23  |

| 2-13       PDP-11 Normal Mode – Format Code 1100       2-24         2-14       PDP-11 Core Dump Mode – Format Code 1101       2-24         2-15       PDP-15 Normal Mode – Format Code 1110       2-24         2-16       PDP-15 Core Dump Mode – Format Code 0001       2-24         2-17       Command Functions       2-25         4-1       Massbus Interface Signals       4-1         4-2       Slave Bus Interface Signals       4-3         4-3       TM03 Clock Signal Frequencies       4-32         4-4       Register/Multiplexer Locations       4-35         4-5       Possible Errors During TM03/Transport Operations       4-43         4-6       Conditions Prevailing When CRC Character Has No Parity Error       4-69         4-7       Legal Formatt Codes       4-10         4-8       Bit Fiddler Initialization/Operation       4-106         4-9       Read Formatting Codes       4-106         4-11       Write Formatting Codes       4-110         4-12       Bit Fiddler Initialization/Operation       4-113         5-1       Standard Tools and Test Equipment Required       5-1         5-2       TM03 DC Voltages       5-15         5-3       Bit Fiddler Modules vs System Processor       5-4                                                                                         | 2-11      | PDP-10 Compatability Mode – Format Code 0011     | 2-23  |

| 2-14       PDP-11 Core Dump Mode – Format Code 1101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-12      | PDP-10 Core Dump Mode – Format Code 0000         | 2-23  |

| 2-15       PDP-15 Normal Mode – Format Code 1110       2-24         2-16       PDP-15 Core Dump Mode – Format Code 0001       2-24         2-17       Command Functions       2-25         4-1       Massbus Interface Signals       4-1         4-2       Slave Bus Interface Signals       4-3         4-3       TM03 Clock Signal Frequencies       4-32         4-4       Register/Multiplexer Locations       4-33         4-5       Possible Errors During TM03/Transport Operations       4-43         4-6       Conditions Prevailing When CRC Character Has No Parity Error       4-69         4-7       Legal Format Codes       4-91         4-8       Bit Fiddler Initialization/Operation       4-106         4-9       Read Formatting Codes       4-106         4-10       CLK A, B, C, and D Sequences       4-106         4-11       Write Formatting Codes       4-106         4-12       Bit Fiddler Initialization/Operation       4-133         5-1       Standard Tools and Test Equipment Required       5-1         5-2       TM03 DC Voltages       5-15         5-3       Bit Fiddler Modules vs System Processor       5-4         5-4       TM03/Transport Diagnostics       5-15         5-5 </td <td>2-13</td> <td></td> <td></td>                                                              | 2-13      |                                                  |       |

| 2-15       PDP-15 Normal Mode – Format Code 1110       2-24         2-16       PDP-15 Core Dump Mode – Format Code 0001       2-24         2-17       Command Functions       2-25         4-1       Massbus Interface Signals       4-1         4-2       Slave Bus Interface Signals       4-3         4-3       TM03 Clock Signal Frequencies       4-32         4-4       Register/Multiplexer Locations       4-33         4-5       Possible Errors During TM03/Transport Operations       4-43         4-6       Conditions Prevailing When CRC Character Has No Parity Error       4-69         4-7       Legal Format Codes       4-91         4-8       Bit Fiddler Initialization/Operation       4-106         4-9       Read Formatting Codes       4-106         4-10       CLK A, B, C, and D Sequences       4-106         4-11       Write Formatting Codes       4-106         4-12       Bit Fiddler Initialization/Operation       4-133         5-1       Standard Tools and Test Equipment Required       5-1         5-2       TM03 DC Voltages       5-15         5-3       Bit Fiddler Modules vs System Processor       5-4         5-4       TM03/Transport Diagnostics       5-15         5-5 </td <td>2-14</td> <td>PDP-11 Core Dump Mode – Format Code 1101</td> <td> 2-24</td>                 | 2-14      | PDP-11 Core Dump Mode – Format Code 1101         | 2-24  |

| 2-16PDP-15 Core Dump Mode – Format Code 0001.2-242-17Command Functions.2-254-1Massbus Interface Signals4-14-2Slave Bus Interface Signals4-34-3TM03 Clock Signal Frequencies4-34-4Register/Multiplexer Locations4-34-5Possible Errors During TM03/Transport Operations4-434-6Conditions Prevailing When CRC Character Has No Parity Error.4-694-7Legal Format Codes4-1064-8Bit Fiddler Initialization/Operation4-1064-9Read Formatting Codes4-1064-10CLK A, B, C, and D Sequences4-1104-12Bit Fiddler Initialization/Operation4-1135-1Standard Tools and Test Equipment Required5-15-2TM03 DC Voltages5-45-3Bit Fiddler Modules vs System Processor.5-45-4TM03/Transport Diagnostics5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-195-1Ms908-YA/Slave Bus Interface SignalsD-4D-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                              | 2-15      |                                                  |       |

| 4-1Massbus Interface Signals4-14-2Slave Bus Interface Signals4-34-3TM03 Clock Signal Frequencies4-324-4Register/Multiplexer Locations4-334-5Possible Errors During TM03/Transport Operations4-434-6Conditions Prevailing When CRC Character Has No Parity Error4-694-7Legal Format Codes4-914-8Bit Fiddler Initialization/Operation4-1064-9Read Formatting Codes4-1064-10CLK A, B, C, and D Sequences4-1064-11Write Formatting Codes4-1135-1Standard Tools and Test Equipment Required5-15-2TM03 DC Voltages5-25-3Bit Fiddler Modules vs System Processor5-45-4TM03/Transport Diagnostics5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-195-9Analysis of Data Errors5-195-9Analysis of Data Errors5-195-10D-1M5903/Massbus Interface SignalsD-4D-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                                                  | 2-16      |                                                  |       |

| 4-2Slave Bus Interface Signals4-34-3TM03 Clock Signal Frequencies4-324-4Register/Multiplexer Locations4-354-5Possible Errors During TM03/Transport Operations4-434-6Conditions Prevailing When CRC Character Has No Parity Error.4-694-7Legal Format Codes4-914-8Bit Fiddler Initialization/Operation4-1064-9Read Formatting Codes4-1064-10CLK A, B, C, and D Sequences4-1064-11Write Formatting Codes4-1104-12Bit Fiddler Initialization/Operation4-1135-1Standard Tools and Test Equipment Required5-15-2TM03 DC Voltages5-25-3Bit Fiddler Modules vs System Processor5-45-4TM03/Transport Diagnostics5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-195-9Analysis of Data Errors5-195-10Meso3/Jassbus Interface SignalsD-1D-2M8937/Slave Bus Interface SignalsD-4Ho-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                            | 2-17      | Command Functions                                | 2-25  |

| 4-2Slave Bus Interface Signals4-34-3TM03 Clock Signal Frequencies4-324-4Register/Multiplexer Locations4-354-5Possible Errors During TM03/Transport Operations4-434-6Conditions Prevailing When CRC Character Has No Parity Error.4-694-7Legal Format Codes4-914-8Bit Fiddler Initialization/Operation4-1064-9Read Formatting Codes4-1064-10CLK A, B, C, and D Sequences4-1064-11Write Formatting Codes4-1104-12Bit Fiddler Initialization/Operation4-1135-1Standard Tools and Test Equipment Required5-15-2TM03 DC Voltages5-25-3Bit Fiddler Modules vs System Processor5-45-4TM03/Transport Diagnostics5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-195-9Analysis of Data Errors5-195-10Meso3/Jassbus Interface SignalsD-1D-2M8937/Slave Bus Interface SignalsD-4Ho-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                            | 4-1       |                                                  |       |

| 4-3TM03 Clock Signal Frequencies4-324-4Register/Multiplexer Locations4-354-5Possible Errors During TM03/Transport Operations4-434-6Conditions Prevailing When CRC Character Has No Parity Error4-64-7Legal Format Codes4-914-8Bit Fiddler Initialization/Operation4-1064-9Read Formatting Codes4-1064-10CLK A, B, C, and D Sequences4-1084-11Write Formatting Codes4-1104-12Bit Fiddler Initialization/Operation4-1135-1Standard Tools and Test Equipment Required5-15-2TM03 DC Voltages5-25-3Bit Fiddler Modules vs System Processor5-45-4TM03/Transport Diagnostics5-115-5Register Read/Write Trouble Analysis5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-195-1Ms93/Slave Bus Interface SignalsD-1D-2M8937/Slave Bus Interface SignalsD-4D-3Ms908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                                                   | 4-2       | Slave Bus Interface Signals                      | 4-3   |

| 4-4Register/Multiplexer Locations.4-354-5Possible Errors During TM03/Transport Operations.4-354-6Conditions Prevailing When CRC Character Has No Parity Error.4-694-7Legal Format Codes4-914-8Bit Fiddler Initialization/Operation4-1064-9Read Formatting Codes4-1064-10CLK A, B, C, and D Sequences4-1064-11Write Formatting Codes4-1104-12Bit Fiddler Initialization/Operation4-1135-1Standard Tools and Test Equipment Required5-15-2TM03 DC Voltages5-25-3Bit Fiddler Modules vs System Processor5-45-4TM03/Transport Diagnostics5-115-5Register Read/Write Trouble Analysis5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-195-1M5903/Massbus Interface SignalsD-1D-2M8937/Slave Bus Interface SignalsD-4D-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                                                                                    | 4-3       |                                                  |       |

| 4-5Possible Errors During TM03/Transport Operations4-434-6Conditions Prevailing When CRC Character Has No Parity Error4-694-7Legal Format Codes4-914-8Bit Fiddler Initialization/Operation4-1064-9Read Formatting Codes4-1064-10CLK A, B, C, and D Sequences4-1084-11Write Formatting Codes4-1104-12Bit Fiddler Initialization/Operation4-1135-1Standard Tools and Test Equipment Required5-15-2TM03 DC Voltages5-25-3Bit Fiddler Modules vs System Processor5-45-4TM03/Transport Diagnostics5-115-5Register Read/Write Trouble Analysis5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-195-9Analysis of Data Errors5-195-9Analysis Interface SignalsD-1D-1M8903/Massbus Interface SignalsD-4D-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-4       |                                                  |       |

| 4-6Conditions Prevailing When CRC Character Has No Parity Error.4-694-7Legal Format Codes4-914-8Bit Fiddler Initialization/Operation4-1064-9Read Formatting Codes4-1064-10CLK A, B, C, and D Sequences4-1084-11Write Formatting Codes4-1014-12Bit Fiddler Initialization/Operation4-1135-1Standard Tools and Test Equipment Required5-15-2TM03 DC Voltages5-25-3Bit Fiddler Modules vs System Processor5-45-4TM03/Transport Diagnostics5-115-5Register Read/Write Trouble Analysis5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-195-9Analysis of Data Errors5-195-1MesoNus Interface SignalsD-1D-2M8937/Slave Bus Interface SignalsD-4D-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-5       |                                                  |       |

| 4-7Legal Format Codes4-914-8Bit Fiddler Initialization/Operation4-1064-9Read Formatting Codes4-1064-10CLK A, B, C, and D Sequences4-1084-11Write Formatting Codes4-1104-12Bit Fiddler Initialization/Operation4-1135-1Standard Tools and Test Equipment Required5-15-2TM03 DC Voltages5-25-3Bit Fiddler Modules vs System Processor5-45-4TM03/Transport Diagnostics5-115-5Register Read/Write Trouble Analysis5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-19D-1M5903/Massbus Interface SignalsD-1D-2M8937/Slave Bus Interface SignalsD-4D-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-6       |                                                  |       |

| 4-8Bit Fiddler Initialization/Operation4-1064-9Read Formatting Codes4-1064-10CLK A, B, C, and D Sequences4-1084-11Write Formatting Codes4-1104-12Bit Fiddler Initialization/Operation4-1135-1Standard Tools and Test Equipment Required5-15-2TM03 DC Voltages5-25-3Bit Fiddler Modules vs System Processor5-45-4TM03/Transport Diagnostics5-115-5Register Read/Write Trouble Analysis5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-19D-1M5903/Massbus Interface SignalsD-1D-2M8937/Slave Bus Interface SignalsD-4D-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-7       |                                                  |       |

| 4-10CLK A, B, C, and D Sequences4-104-11Write Formatting Codes4-104-12Bit Fiddler Initialization/Operation4-1135-1Standard Tools and Test Equipment Required5-15-2TM03 DC Voltages5-25-3Bit Fiddler Modules vs System Processor5-45-4TM03/Transport Diagnostics5-115-5Register Read/Write Trouble Analysis5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-19D-1M5903/Massbus Interface SignalsD-1D-2M8937/Slave Bus Interface SignalsD-4D-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-8       |                                                  |       |

| 4-11Write Formatting Codes4-1104-12Bit Fiddler Initialization/Operation4-1135-1Standard Tools and Test Equipment Required.5-15-2TM03 DC Voltages.5-25-3Bit Fiddler Modules vs System Processor.5-45-4TM03/Transport Diagnostics5-115-5Register Read/Write Trouble Analysis5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-19D-1M5903/Massbus Interface SignalsD-1D-2M8937/Slave Bus Interface SignalsD-4D-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-9       | Read Formatting Codes                            | 4-106 |

| 4-11Write Formatting Codes4-1104-12Bit Fiddler Initialization/Operation4-1135-1Standard Tools and Test Equipment Required5-15-2TM03 DC Voltages5-25-3Bit Fiddler Modules vs System Processor5-45-4TM03/Transport Diagnostics5-115-5Register Read/Write Trouble Analysis5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-19D-1M5903/Massbus Interface SignalsD-1D-2M8937/Slave Bus Interface SignalsD-4D-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-10      |                                                  |       |

| 5-1Standard Tools and Test Equipment Required.5-15-2TM03 DC Voltages.5-25-3Bit Fiddler Modules vs System Processor.5-45-4TM03/Transport Diagnostics5-115-5Register Read/Write Trouble Analysis5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-19D-1M5903/Massbus Interface SignalsD-1D-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-11      | Write Formatting Codes                           | 4-110 |

| 5-1Standard Tools and Test Equipment Required.5-15-2TM03 DC Voltages.5-25-3Bit Fiddler Modules vs System Processor.5-45-4TM03/Transport Diagnostics5-115-5Register Read/Write Trouble Analysis5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-19D-1M5903/Massbus Interface SignalsD-1D-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-12      | Bit Fiddler Initialization/Operation             | 4-113 |

| 5-3Bit Fiddler Modules vs System Processor.5-45-4TM03/Transport Diagnostics5-115-5Register Read/Write Trouble Analysis5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-19D-1M5903/Massbus Interface SignalsD-1D-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-1       |                                                  |       |

| 5-4TM03/Transport Diagnostics5-115-5Register Read/Write Trouble Analysis5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-19D-1M5903/Massbus Interface SignalsD-1D-2M8937/Slave Bus Interface SignalsD-4D-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-2       | TM03 DC Voltages.                                | 5-2   |

| 5-4TM03/Transport Diagnostics5-115-5Register Read/Write Trouble Analysis5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-19D-1M5903/Massbus Interface SignalsD-1D-2M8937/Slave Bus Interface SignalsD-4D-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-3       | Bit Fiddler Modules vs System Processor          | 5-4   |

| 5-5Register Read/Write Trouble Analysis5-155-6Possible Errors During TM03/Transport Operations5-165-7Massbus Controller, Massbus Cable, Software, and<br>Power Supply Error Analysis5-185-8Tape Read/Write Error Analysis5-195-9Analysis of Data Errors5-19D-1M5903/Massbus Interface SignalsD-1D-2M8937/Slave Bus Interface SignalsD-4D-3M8908-YA/Slave Bus Interface SignalsD-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | TM03/Transport Diagnostics                       | 5-11  |