# VL82C106 PC/AT COMBO I/O CHIP

# FEATURES

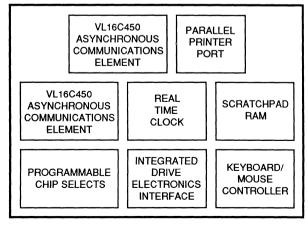

Combines the following PC/AT<sup>®</sup> Peripheral Chips:

VL16C450 UART - COM1: VL16C450 UART - COM2: Parallel Printer Port - LPT1: Keyboard/Mouse Ctrl. - KBD Real Time Clock

- · Serial ports fully 16C450 compatible

- · Bidirectional line printer port

- Software control of PS/2<sup>®</sup>-compatible enhancements (LPT Port, Mouse)

- CMOS direct drive of Centronics-type parallel interface

- PC/AT- or PS/2-compatible keyboard and mouse controller

- 146818A-compatible Real Time Clock (RTC)

- 16 bytes of additional standby RAM (66 bytes total)

- IDE bus control signals included (two external 74LS245 and one 74ALS244

or equivalent - buffers are required)

- Seven battery-backed programmable chip select registers for auto configuration

- Preprogrammed default chip selects

- Programmable wait state generation

- 5 µA standby current for RTC, RAM, and chip select registers

- Single 128-pin plastic quad flatpack

### DESCRIPTION

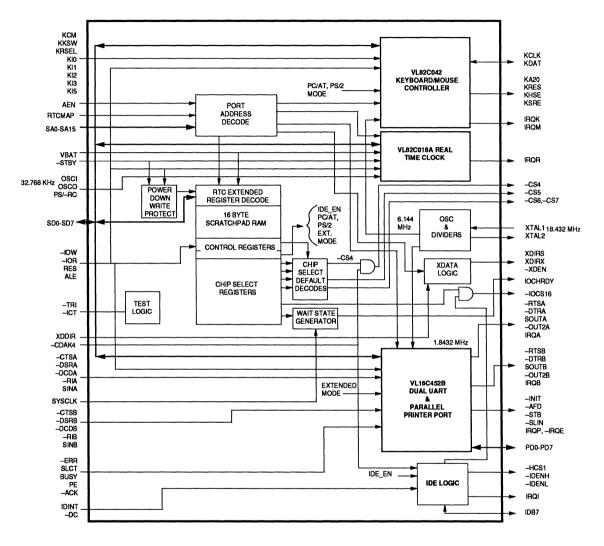

The VL82C106 Combo chip replaces with a single 128-pin chip, several of the commonly used peripherals found in PC/AT-compatible computers. This chip when used with the VLSI PC/ATcompatible chip set allows designers to implement a very cost effective, minimum chip count motherboard containing functions that are common to virtually all PCs.

The on-chip UARTs are completely software compatible with the VL16C450 ACE.

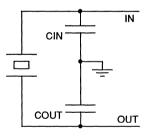

The bidirectional parallel port provides a PS/2 software compatible interface between a Centronics-type printer and the VL82C106. Direct drive is provided so that all that is necessary to interface to the line printer port is a resistor - capacitor network. The bidirectional feature (option) is software programmable for backwards PC/AT-compatibility.

The keyboard/mouse controller is selectable as PC/AT- or PS/2-compatible.

The Real Time Clock is 146818Acompatible and offers a standby current drain of 5  $\mu$ A at 3.0 V.

Included is the control logic necessary for the support of the Integrated Drive Electronics (IDE) hard disk bus interface.

The Combo I/O chip also includes seven programmable chip selects, three internal and four external. Each chip select has a programmable 16-bit base address and a mask register that allows the number of bytes corresponding to each chip select to be programmed (e.g. 3F8H-3FFH has a base address of 3F8H and a range of 8 bytes). Each chip select can be programmed for number of wait states (0-7) and 8- or 16-bit operation. 16-bit decoding is used for all I/O addresses. A default fixed decode is provided on reset for the on-chip serial ports, printer port, and off-chip floppy and hard disk controllers, which may be changed to batterybacked programmable chip selects via a control bit.

### ORDER INFORMATION

| Part<br>Number | Package               |  |

|----------------|-----------------------|--|

| VL82C106-FC    | Plastic Quad Flatpack |  |

Note: Operating temperature range is 0°C to +70°C.

# **INTERNAL FUNCTIONAL DIAGRAM**

PC/AT® and PS/2® is the registered trademark of IBM Corporation.

# **BLOCK DIAGRAM**

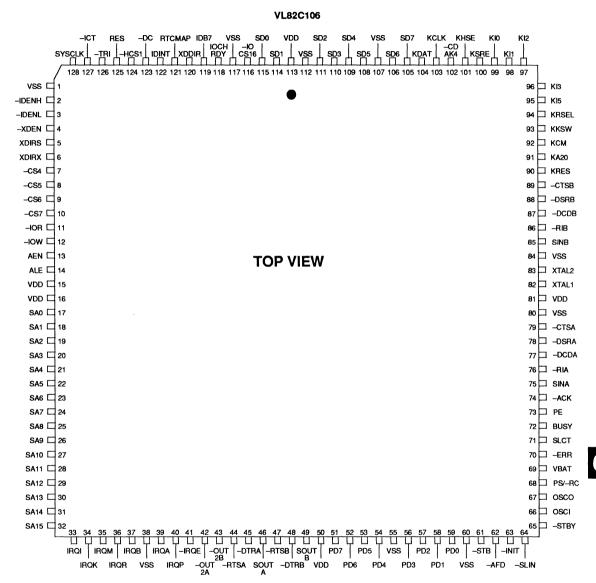

# **PIN DIAGRAM**

6

| Signal<br>Name | Pin<br>Number | Signal<br>Type | Signal<br>Description       |

|----------------|---------------|----------------|-----------------------------|

| COMMUNIC       | TIONS PORT A  |                |                             |

| -RTSA          | 44            | 01             | Request to Send, Port A     |

| -DTRA          | 45            | 01             | Data Terminal Ready, Port A |

| SOUTA          | 46            | 01             | Serial Data Output, Port A  |

| -CTSA          | 79            | 14             | Clear to Send, Port A       |

| -DSRA          | 78            | 14             | Data Set Ready, Port A      |

| -DCDA          | 77            | 14             | Data Carrier Detect, Port A |

| -RIA           | 76            | 14             | Ring Indicator, Port A      |

| SINA           | 75            | 14             | Serial Input, Port A        |

| IRQA           | 39            | O6             | Interrupt Request, Port A   |

| -OUT2A         | 42            | 01             | Output 2, Port A            |

|                | ATIONS PORT B | <b>.</b>       |                             |

| -RTSB          | 47            | 01             | Request to Send, Port B     |

| -DTRB          | 48            | 01             | Data Terminal Ready, Port B |

| SOUTB          | 49            | 01             | Serial Data Output, Port B  |

| -CTSB          | 89            | 14             | Clear to Send, Port B       |

| -DSRB          | 88            | 14             | Data Set Ready, Port B      |

| -DCDB          | 87            | 14             | Data Carrier Detect, Port B |

| -RIB           | 86            | 14             | Ring Indicator, Port B      |

| SINB           | 85            | 14             | Serial Input, Port B        |

| IRQB           | 37            | O6             | Interrupt Request, Port B   |

| -OUT2B         | 43            | O1             | Output 2, Port B            |

|                | PRINTER PORT  |                |                             |

| PD0            | 59            | 105            | Printer Data Port, Bit 0    |

| PD1            | 58            | 105            | Printer Data Port, Bit 1    |

| PD2            | 57            | 105            | Printer Data Port, Bit 2    |

| PD3            | 56            | 105            | Printer Data Port, Bit 3    |

| PD4            | 54            | 105            | Printer Data Port, Bit 4    |

| PD5            | 53            | 105            | Printer Data Port, Bit 5    |

| PD6            | 52            | 105            | Printer Data Port, Bit 6    |

| PD7            | 51            | 105            | Printer Data Port, Bit 7    |

| –INIT          | 63            | O4             | Initialize Printer Signal   |

| –AFD           | 62            | O4             | Autofeed Printer Signal     |

| –STB           | 61            | O4             | Data Strobe to Printer      |

| -SLIN          | 64            | 04             | Select Signal to Printer    |

| -ERR           | 70            | 14             | Error Signal from Printer   |

| SLCT           | 71            | 14             | Select Signal from Printer  |

VL82C106

and a second design of the second second

6

| Signal<br>Name        | Pin<br>Number    | Signal<br>Type | Signal<br>Description                                                      |  |

|-----------------------|------------------|----------------|----------------------------------------------------------------------------|--|

| BUSY                  | 72               | 14             | Busy Signal from Printer                                                   |  |

| PE                    | 73               | 14             | Paper Error Signal from Printer                                            |  |

| –ACK                  | 74               | 14             | Acknowledge Signal from Printer                                            |  |

| IRQP                  | 40               | O6             | Printer Interrupt Request Output                                           |  |

| -IRQE                 | 41               | O1             | Printer Interrupt Request Enabled Signal                                   |  |

| REAL TIME C           | CLOCK PORT<br>69 | NA             | Standby Power - Normally 3 V to 5 V, battery backed.                       |  |

| -STBY                 | 65               | 15             | Power Down Control                                                         |  |

| osci                  | 66               | NA             | Crystal Connection Input - 32 KHz                                          |  |

| osco                  | 67               | NA             | Crystal Connection Output - 32 KHz                                         |  |

| PS/-RC                | 68               | 15             | Power Sense/RAM Clear Input                                                |  |

| IRQR                  | 36               | 01             | Real Time Clock Interrupt Request Output                                   |  |

| RTCMAP                | 121              | 14             | High - RTC is mapped to 70H and 71H, Low - RTC is mapped to 170H and 171H. |  |

| KEYBOARD              | CONTROLLER P     | ORT            |                                                                            |  |

| KCLK                  | 103              | 104            | Keyboard Clock                                                             |  |

| KDAT                  | 104              | 104            | Keyboard Data                                                              |  |

| KCM                   | 92               | 14             | General purpose input, normally color/monochrome.                          |  |

| KKSW                  | 93               | 14             | General purpose input, normally keyboard switch.                           |  |

| KA20                  | 91               | 01             | General purpose output, normally A20 Gate.                                 |  |

| KRES                  | 90               | 01             | General purpose output, normally reset.                                    |  |

| KHSE                  | 101              | 01/104         | General purpose input, normally speed select.                              |  |

| KSRE                  | 100              | 01/104         | General purpose output, normally shadow RAM enable.                        |  |

| IRQK                  | 34               | 01             | Keyboard Interrupt Request                                                 |  |

| IRQM                  | 35               | 01             | Mouse Interrupt Request                                                    |  |

| KRSEL                 | 94               | 14             | General purpose input, normally RAM select.                                |  |

| KIO                   | 99               | 14             | General purpose input, bit 0.                                              |  |

| KI1                   | 98               | 14             | General purpose input, bit 1.                                              |  |

| KI2                   | 97               | 14             | General purpose input, bit 2.                                              |  |

| KI3                   | 96               | 14             | General purpose input, bit 3.                                              |  |

| KI5                   | 95               | 14             | General purpose input, bit 5.                                              |  |

| IDE BUS I/O<br>-IDENH | 2                | O1             | IDE Bus Transceiver High Byte Enable                                       |  |

| -IDENL                | 3                | O1             | IDE Bus Transceiver Low Byte Enable                                        |  |

| IDINT                 | 122              | 14             | IDE Bus Interrupt Request Input                                            |  |

| IDB7                  | 119              | 106            | IDE Bus Data Bit 7                                                         |  |

| -DC                   | 123              | 14             | Floppy Disk Change Signal                                                  |  |

| -HCS1                 | 124              | 01             | IDE Host Chip Select 1                                                     |  |

| -IRQI                 | 33               | O6             | IDE Interrupt Request Output                                               |  |

6-189

| Signal<br>Name | Pin<br>Number | Signal<br>Type | Signal<br>Description                                         |

|----------------|---------------|----------------|---------------------------------------------------------------|

| COMMON B       | US I/O        |                |                                                               |

| SD0            | 115           | 102            | System Bus Data, Bit 0                                        |

| SD1            | 114           | 102            | System Bus Data, Bit 1                                        |

| SD2            | 111           | 102            | System Bus Data, Bit 2                                        |

| SD3            | 110           | 102            | System Bus Data, Bit 3                                        |

| SD4            | 109           | 102            | System Bus Data, Bit 4                                        |

| SD5            | 108           | 102            | System Bus Data, Bit 5                                        |

| SD6            | 106           | 102            | System Bus Data, Bit 6                                        |

| SD7            | 105           | 102            | System Bus Data, Bit 7                                        |

| SA0            | 17            | 11             | SystemBus Address, Bit 0                                      |

| SA1            | 18            | 11             | System Bus Address, Bit 1                                     |

| SA2            | 19            | 11             | System Bus Address, Bit 2                                     |

| SA3            | 20            | 11             | System Bus Address, Bit 3                                     |

| SA4            | 21            | 11             | System Bus Address, Bit 4                                     |

| SA5            | 22            | 11             | System Bus Address, Bit 5                                     |

| SA6            | 23            | 11             | System Bus Address, Bit 6                                     |

| SA7            | 24            | 11             | System Bus Address, Bit 7                                     |

| SA8            | 25            | 11             | System Bus Address, Bit 8                                     |

| SA9            | 26            | 11             | System Bus Address, Bit 9                                     |

| SA10           | 27            | 11             | System Bus Address, Bit 10                                    |

| SA11           | 28            | 11             | System Bus Address, Bit 11                                    |

| SA12           | 29            | 11             | System Bus Address, Bit 12                                    |

| SA13           | 30            | 11             | System Bus Address, Bit 13                                    |

| SA14           | 31            | 11             | System Bus Address, Bit 14                                    |

| SA15           | 32            | 11             | System Bus Address, Bit 15                                    |

| XTAL1          | 82            | NA             | Crystal/Clock Input - 18.432 MHz                              |

| XTAL2          | 83            | NA             | Cystal/Clock Output - 18.432 MHz                              |

| -IOR           | 11            | н              | System Bus I/O Read                                           |

| -IOW           | 12            | 11             | System Bus I/O Write                                          |

| RES            | 125           | 11             | System Reset                                                  |

| AEN            | 13            | 11             | System Bus Address Enable                                     |

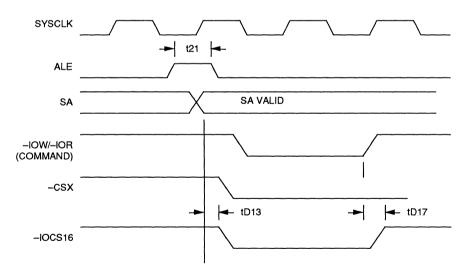

| ALE            | 14            | 11             | System Bus Address Latch Enable                               |

| -IOCS16        | 116           | O8             | System Bus I/O Chip Select 16                                 |

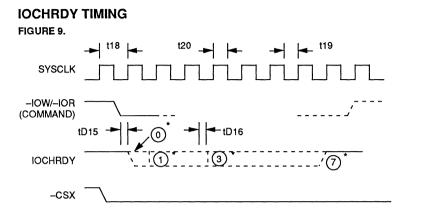

| IOCHRDY        | 118           | O8             | System Bus I/O Channel Ready                                  |

| SYSCLK         | 128           | 11             | System Clock - Processor clock divide by 2.                   |

| –CS4           | 7             | 01             | Chip Select 4 - Normally for external floppy disk controller. |

| -CS5           | 8             | 01             | Chip Select 5 - Normally –HCS0 for IDE.                       |

VL82C106

| Signal<br>Name          | Pin<br>Number                              | Signal<br>Type | Signal<br>Description                                                                                                   |

|-------------------------|--------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------|

| –CS6                    | 9                                          | 01             | Chip Select 6 - Normally for external floppy disk controller.                                                           |

| -CS7                    | 10                                         | O1             | Chip Select 7 - Normally for external floppy disk controller.                                                           |

| -CDAK4                  | 102                                        | 11             | DMA Acknowledge forces –CS4 active.                                                                                     |

| XDDIR                   | 120                                        | 11             | X Data Bus Transceiver Direction                                                                                        |

| XDIRS                   | 5                                          | 01             | Modified X Data Bus Transceiver Direction Control Signal - Excludes real<br>time clock and keyboard controller decodes. |

| XDIRX                   | 6                                          | 01             | X Data Bus Transceiver Control Signal - Includes all CS decodes gener-<br>ated on chip.                                 |

| -XDEN                   | 4                                          | 01             | X Data Bus Transceiver Enable                                                                                           |

| -TRI                    | 126                                        | 14             | Three-state Control Input - For all outputs to isolate chip for board tests.                                            |

| –ICT                    | 127                                        | 14             | In Circuit Test Mode Control                                                                                            |

| <b>POWER, GR</b><br>VDD | OUND, & UNCOMM<br>15, 16, 50,<br>81, 113   | ITTED          | System Power: +5 V                                                                                                      |

| VSS                     | 1, 38, 55,<br>60, 80, 84,<br>107, 112, 117 |                | System Ground                                                                                                           |

# I/O LEGEND

|     | mA | Туре   | Comment                                |

|-----|----|--------|----------------------------------------|

| 01  | 2  | TTL    |                                        |

| 02  | 24 | TTL    |                                        |

| 04  | 12 | TTL-OD | Open drain, weak pull-up, no VDD diode |

| 06  | 4  | TTL-TS | Three-State                            |

| 07  | 24 | TTL-TS | Three-State                            |

| 08  | 24 | TTL-OD | Open drain, fast active pull-up        |

| 11  | _  | TTL    |                                        |

| 12  | -  | CMOS   |                                        |

| 14  | -  | TTL    | 30k Ω pull-up                          |

| 15  | -  | TTL    | Schmitt-trigger                        |

| 102 | 24 | TTL-TS | Three-State                            |

| 104 | 12 | TTL-OD | Open drain, slow turn-on               |

| 105 | 12 | TTL-TS | Three-State                            |

| 106 | 24 | TTL-TS | Three-State, 30k $\Omega$ pull-up      |

·····

VL82C106

. . . . . . . . . . . .

### FUNCTIONAL DESCRIPTION

Below is a detailed explanation of each of the major building blocks of the VL82C106 Combo chip. The following functional blocks are covered:

- · 16C450 Serial Ports

- Parallel Printer Port

- 146818A-Compatible Real Time Clock

- Keyboard Controller

- · Control and Chip Selects

- · IDE Interface

#### SERIAL COMMUNICATIONS PORTS

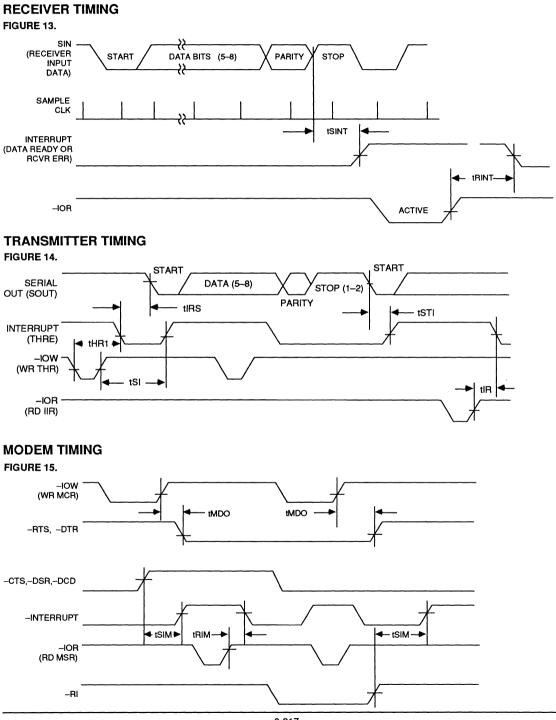

The chip contains two UARTs, based on the VL16C450 Megacell core. Each of these UARTs share a common baudrate clock, which is the XTAL1 input (18.432 MHz) divided by ten. The 18.432 MHz) divided by ten. The 18.432 MHz signal is shared with the keyboard controller, which divides it by three to get an approximate 6 MHz reference clock. Please refer to the VL16C452B data sheet for the register descriptions and timing parameters for the UARTs.

COMA is accessed via internally generated CS1, while COMB uses internally generated CS2.

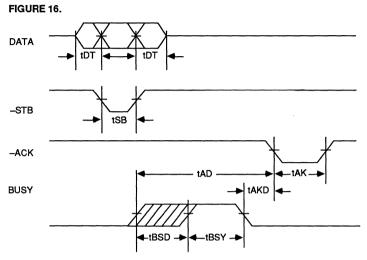

#### LINE PRINTER PORT

The Line Printer Port contains the functionality of the port included in the VL16C452B, but offers a software programmable Extended Mode, which include a Direction Control Bit and Interrupt Status Bit. These features are disabled on initial power-up, but may be turned on by clearing the –EMODE bit of Control Register 0 (RTC Register 69H in AT or PS/2 mode or I/O PORT 102H in PS/2 mode). When the –EMODE bit is set, the part functions exactly as a PC/AT-compatible printer port.

The Line Printer Port is accessed via internally generated programmable chip select CS3.

Register 0 - Line Printer Port Data The Line Printer (LPT) Port is either unior bidirectional, depending on the state of the Extended Mode and Data Direction Control bits.

Compatibility Mode (-EMODE bit = 1) -Read operations to this register return the last data that was written to the LPT Port. Write operations immediately output data to the LPT Port.

Extended Mode (-EMODE bit = 0) -Read operations return either the data last written to the LPT Data Register if the Direction Bit is set to output ("0") or the data that is present on the pins of the LPT Port if the direction is set to input ("1"). Write operations latch data into the output register, but only drive the LPT Port when the Direction Bit is set to output.

In either case, the bits of the LPT Data Register are defined as follows:

| Bit | Description |

|-----|-------------|

| 0   | Data Bit 0  |

| 1   | Data Bit 1  |

| 2   | Data Bit 2  |

| 3   | Data Bit 3  |

| 4   | Data Bit 4  |

| 5   | Data Bit 5  |

| 6   | Data Bit 6  |

| 7   | Data Bit 7  |

|     |             |

#### **Register 1 - LPT Port Status**

The LPT Status Register is a read-only register that contains interrupt status and real time status of the LPT connector pins. The bits are described as follows:

| Bit | Description |

|-----|-------------|

| 0   | Reserved    |

| 1   | Reserved    |

| 2   | –IRQ        |

| 3   | -ERROR      |

| 4   | SLCT        |

| 5   | PE          |

| 6   | -ACK        |

| 7   | -BUSY       |

|     |             |

Bits 0 and 1 - Reserved, read as "1's".

# VL82C106

Bit 2 - Interrupt Status bit, a "0" indicates that the printer has acknowledged the previous transfer with a ACK handshake (bit 4 of the control register must be set to "1").

When in AT mode, bit 1 RTC Register 6AH = 1, the IRQP output follows the -ACK input if enabled. When in PS/2 mode, IRQP is set during the inactive transition of the -ACK signal, and cleared following a read of the LPT status register.

Bit 3 - Error Status bit, a "0" indicates that the printer has had an error. A "1" indicates normal operation. This bit follows the state of the –ERR pin.

Bit 4 - Select Status bit, indicates the current status of the SLCT signal from the printer. A "0" indicates the printer is currently not selected (off-line). A "1" means the printer is currently selected.

Bit 5 - Paper Empty Status bit, a "0" indicates normal operation. A "1" indicates that the printer is currently out of paper. This bit follows the state of the PE pin.

Bit 6 - Acknowledge Status bit, a "0" indicates that the printer has received a character and is ready to accept another. A "1" indicates that the last operation to the printer has not been completed yet. This bit follows the state of the –ACK pin.

Bit 7 - Busy Status bit, a "0 indicates that the printer is busy and cannot receive data. A "1" indicates that the printer is ready to accept data. This bit is the inversion of the BUSY pin.

#### **Register 2 - LPT Port Control**

This port is a read/write port that is used to control the LPT direction as well as the Printer Control lines driven from the port. Write operations set or reset these bits, while read operations return the status of the last write operation to this register (except for bit 5 which is write only and is always read back as a "1"). The bits in this register are defined as follows:

Bit 0 - Printer Strobe Control bit, when set ("1") the STROBE signal is asserted on the LPT interface, causing the

| Bit | Description      |

|-----|------------------|

| 0   | STROBE           |

| 1   | AUTO FD XT       |

| 2   | -INIT            |

| 3   | SLCT IN          |

| 4   | IRQ EN           |

| 5   | DIR (Write Only) |

| 6   | Reserved         |

| 7   | Reserved         |

|     |                  |

printer to latch the current data. When reset ("0") the signal is negated.

Bit 1 - Auto Feed Control bit, when set ("1") the AUTO FD XT signal will be asserted on the LPT interface, causing the printer to automatically generate a line feed at the end of each line. When reset ("0") the signal is negated.

Bit 2 - Initialize Printer Control bit, when set ("1") the signal is negated. When reset ("0") the INIT signal is asserted to the printer, forcing a reset.

Bit 3 - Select Input Control bit, when set ("1") the SLCT IN signal is asserted, causing the printer to go "on-line". When reset ("0") the signal is negated.

Bit 4 - Interrupt Request Enable Control bit, when set ("1") enables interrupts from the LPT Port whenever the –ACK signal is asserted by the printer. When reset ("0") interrupts are disabled.

Bit 5 - When EMODE = 1, Direction (DIR) Control bit, when set ("1") the output buffers in the LPT Port are disabled, allowing data driven from external sources to be read from the LPT Port. When reset ("0"), the output buffers are enabled, forcing the LPT pins to drive the LPT pins. The poweron-reset value of this is cleared ("0"). When -EMODE = 1, this write only bit has no effect and should be read as "1".

Bits 6 and 7 - Reserved, read as "1's".

#### **REAL TIME CLOCK**

The Real Time Clock (RTC) is the equivalent of the Motorola MC146818A Real Time Clock component. It is also compatible with the Dallas Semiconductor DS1287A RTC when an external battery and crystal are provided. Clock functions include the following:

- · Time of Day Clock

- Alarm Function

- 100 Year Calendar Function

- Programmable Periodic Interrupt Output

- Programmable Square Wave Output

- 50 Bytes of User RAM

- User RAM Preset Feature

### RTC PROGRAMMERS MODEL

The RTC memory consists of ten RAM bytes which contain the time, calendar, and alarm data, four control and status bytes, and 50 general purpose RAM bytes. The address map of the real time clock is shown below.

| Add.  | Function              | Range |

|-------|-----------------------|-------|

| 00-09 | Time Regs.            | 0-99  |

| 0A    | RTC Register A        | (R/W) |

| 0B    | RTC Register B        | (R/W) |

| 0C    | RTC Register C        | (R O) |

| 0D    | RTC Register D        | (R O) |

| 0E-3F | User RAM<br>(Standby) |       |

All 64 bytes are directly readable and writable by the processor program except for the following:

Registers C and D are read only.

Bit 7 of Register A is read only.

The RTC is normally accessed via internally decoded PORT 070H (RTC register address) and PORT 071H (RTC data read/write).

The RTC address and data ports can be moved to Port 170H, Port 171H by pulling the RTCMAP pin (121) to ground. This pin can be left not connected or tied high for normal port addressing.

The RTC address map also includes additional standby RAM, plus control registers for Combo chip configuration and chip select control. The RAM and Chip Select control registers are powered via the VBAT power supply for battery-backed operation.

| Add. (HEX) | Function                         |  |

|------------|----------------------------------|--|

| 00-0D      | Time Portion of RTC              |  |

| 0E-3F      | RAM Portion of RTC               |  |

| 40-4F      | Additional Standby RAM           |  |

| 50-68      | Reserved                         |  |

| 69-7F      | Chip Select/Control<br>Registers |  |

VL82C106

The total address map is shown below: The processor program obtains time and calendar information by reading the appropriate locations. The program may initialize the time, calendar, and alarm by writing to these RAM locations. The contents of the ten time, calendar, and alarm bytes may be either binary or binary-coded decimal (BCD).

#### **Time of Day Register**

The contents of the Time of Day registers can be either in Binary or BCD format. They are relatively straightforward, but are detailed here for

| Add. | Function        | Range                  |

|------|-----------------|------------------------|

| 0    | Seconds (Time)  | 0-59                   |

| 1    | Seconds (Alarm) | 0-59                   |

| 2    | Minutes (Time)  | 0-59                   |

| 3    | Minutes (Alarm) | 0-59                   |

| 4    | Hours (Time)    | 1-12,<br>12 Hr<br>Mode |

| 4    | Hours (Time)    | 0-23,<br>24 Hr<br>Mode |

| 5    | Hours (Alarm)   | 0-23                   |

| 6    | Day of Week     | 1-7                    |

| 7    | Date of Month   | 1-31                   |

| 8    | Month           | 1-12                   |

| 9    | Year            | 0-99                   |

|      |                 |                        |

completeness. The address map of these registers is shown next:

Address 0 - Seconds (Time): The range of this register is 0-59 in BCD mode, and 0-3BH in Binary mode.

Address 1 - Seconds (Alarm): The range of this register is 0-59 in BCD mode, and 0-3BH in Binary mode.

Address 2 - Minutes (Time): The range of this register is 0-59 in BCD mode, and 0-3BH in Binary mode.

Address 3 - Minutes (Alarm): The range of this register is 0-59 in BCD mode, and 0-3BH in Binary mode.

| Range   | Mode   | Time |

|---------|--------|------|

| 1-12    | BCD    | AM   |

| 81-92   | BCD    | РМ   |

| 01H-0CH | Binary | AM   |

| 81H-8CH | Binary | РМ   |

Address 4 - Hours (Time): The range of this register is:

| Range   | Mode   | Time |

|---------|--------|------|

| 1-12    | BCD    | АМ   |

| 81-92   | BCD    | РМ   |

| 01H-0CH | Binary | АМ   |

| 81H-8CH | Binary | РМ   |

Address 5 - Hours (Alarm): The range of this register is:

Address 6 - Day of Week: The range of this register is 1-7 in BCD mode, and 1-7H in Binary mode.

Address 7 - Date: The range of this register is 1-31 in BCD mode, and 1-1FH in Binary mode.

Address 8 - Month: The range of this register is 1-12 in BCD mode, and 1-0CH in Binary mode.

Address 9 - Year: The range of this register is 0-99 in BCD mode, and 0-63H in Binary mode.

#### **RTC CONTROL REGISTER**

The RTC has four registers which are accessible to the processor program. The four registers are also fully accessible during the update cycle.

| Add.  | Function           | Туре |

|-------|--------------------|------|

| 0A    | RTC Register A     | R/W  |

| 0B    | RTC Register B     | R/W  |

| 0C    | RTC Register C     | RO   |

| 0D    | RTC Register D     | RO   |

| 0E-3F | User RAM (Standby) | R/W  |

#### **Register A**

This register contains control bits for the selection of Periodic Interrupt, Input Divisor, and the Update In Progress Status bit. The bits in the register are defined as follows:

| Bit | Description Abbr.  |     |

|-----|--------------------|-----|

| 0   | Rate Select Bit 0  | RS0 |

| 1   | Rate Select Bit 1  | RS1 |

| 2   | Rate Select Bit 2  | RS2 |

| 3   | Rate Select Bit 3  | RS3 |

| 4   | Divisor Bit 0      | DV0 |

| 5   | Divisor Bit 1      | DV1 |

| 6   | Divisor Bit 2      | DV2 |

| 7   | Update in Progress | UIP |

Bits 0 to 3 - The four rate selection bits (RS0 to RS3) select one of 15 taps on the 22-stage divider, or disable the divider output. The tap selected may be used to generate a periodic interrupt. These four bits are read/write bits which are not affected by RESET. The Periodic Interrupt Rate that results from the selection of various tap values is as follows:

# VL82C106

| RS<br>Value | Periodic Interrupt<br>Rate |    |  |

|-------------|----------------------------|----|--|

| 0           | None                       |    |  |

| 1           | 3.90625                    | ms |  |

| 2           | 7.8125                     | ms |  |

| 3           | 122.070                    | μs |  |

| 4           | 244.141                    | μs |  |

| 5           | 488.281                    | μs |  |

| 6           | 976.562                    | μs |  |

| 7           | 1.953125                   | ms |  |

| 8           | 3.90625                    | ms |  |

| 9           | 7.8125                     | ms |  |

| 0AH         | 15.625                     | ms |  |

| 0BH         | 31.25                      | ms |  |

| 0CH         | 62.5                       | ms |  |

| 0DH         | 125                        | ms |  |

| 0EH         | 250                        | ms |  |

| 0FH         | 500                        | ms |  |

Bits 4 to 6 - The three Divisor Selection bits (DV0 to DV2) are fixed to provide for only a five-state divider chain, which would be used with a 32 KHz external crystal. Only bit 6 of this register can be changed allowing control of the reset for the divisor chain. When the divider reset is removed, the first update cycle begins one-half second later. These bits are not affected by power-on reset (external pin).

| DV<br>Value | Condition                             |

|-------------|---------------------------------------|

| 2           | Operation Mode, Divider<br>Running    |

| 6           | Reset Mode, Divider in<br>Reset State |

Bit 7 - The Update In Progress (UIP) bit is a status flag that may be monitored by the program. When UIP is a "1", the update cycle is in progress or will scon begin. When UIP is a "0", the update cycle is not in progress and will not be for at least 244  $\mu$ s. The time, calendar, and alarm information in RAM is fully available to the program when the UIP

bit is "0". The UIP bit is a read-only bit, and is not affected by reset. Writing the SET bit in Register B to a "1" will inhibit any update cycle and then clear the UIP status bit.

### **Register B**

Register B contains command bits to control various modes of operations and interrupt enables for the RTC. The bits in this register are defined as follows:

| Bit | Description                    | Abbr. |

|-----|--------------------------------|-------|

| 0   | Daylight Savings<br>Enable     | DSE   |

| 1   | 24/12 Mode                     | 24/12 |

| 2   | Data Mode (Binary<br>or BCD)   | DM    |

| 3   | Not Used                       |       |

| 4   | Update End Interrupt<br>Enable | UIE   |

| 5   | Alarm Interrupt<br>Enable      | AIE   |

| 6   | Periodic Interrupt<br>Enable   | PIE   |

| 7   | Set Command                    | SET   |

Bit 0 - The Daylight Savings Enable (DSE) bit is a read/write bit which allows the program to enable two special updates (when DSE is "1"). On the first Sunday in April the time increments from 1:59:59 AM to 3:00:00 AM. On the first Sunday in October when the time first reaches 1:59:59 AM it changes to 1:00:00 AM. These special updates do not occur when the DSE bit is a "0". DSE is not changed by any internal operations or reset.

Bit 1 - The 24/12 control bit establishes the format of the hours bytes as either the 24-hour mode ("1") or the 12-hour mode ("0"). This is a read/write bit, which is affected only by software.

Bit 2 - The Data Mode (DM) bit indicates whether time and calendar updates are to use binary or BCD formats. The DM bit is written by the processor program and may be read by the program, but is not modified by any internal functions or reset. A "1" in DM signifies binary data, while a "0" in DM specifies binary-coded-decimal (BCD) data. Bit 3 - This bit is unused in this version of the RTC, but is used for Square Wave Enable in the Motorola MC146818.

Bit 4 - The UIE (Update End Interrupt Enable) bit is a read/write bit which enables the Update End Interrupt Flag (UF) bit in Register C to assert an IRQ. The reset pin being asserted or the SET bit going high clears the UIE bit.

Bit 5 - The Alarm Interrupt Enable (AIE) bit is a read/write bit which when set to a "1" permits the Alarm Interrupt Flag (AF) bit in Register C to assert an IRQ. An alarm interrupt occurs for each second that the three time bytes equal the three alarm bytes (including a "don't care" alarm code of 11XXXXXb). When the AIE bit is a "0", the AF bit does not initiate an IRQ signal. The reset pin clears AIE to "0". The internal functions do not affect the AIE bit.

Bit 6 - The Periodic Interrupt Enable (PIE) bit is a read/write bit which allows the Periodic Interrupt Flag (PF) bit in Register C to cause the IRQ pin to be driven low. A program writes a "1" to the PIE bit in order to receive periodic interrupts at the rate specified by the RS3, RS2, RS1, and RS0 bits in Register A. A "0" in PIE blocks IRQ from being initiated by a periodic interrupt, but the Periodic Interrupt Flag (PF) bit is still set at the periodic rate. PIE is not modified by any internal functions, but is cleared to "0" by a reset.

Bit 7 - When the SET bit is a "0", the update cycle functions normally by advancing the counts once-per-second. When the SET bit is written to a "1", any update cycle in progress is aborted and the program may initialize the time and calendar bytes without an update occurring in the midst of initializing. SET is a read/write bit which is not modified by reset or internal functions.

#### **Register C**

Register C contains status information about interrupts and internal operation of the RTC. The bits in this register are defined as follows:

# VL82C106

| Bit | Description                  | Abbr. |

|-----|------------------------------|-------|

| 0   | Not Used, Read<br>as 0       |       |

| 1   | Not Used, Read<br>as 0       |       |

| 2   | Not Used, Read<br>as 0       |       |

| 3   | Not Used, Read<br>as 0       |       |

| 4   | Update End<br>Interrupt Flag | UF    |

| 5   | Alarm Interrupt Flag         | AF    |

| 6   | Periodic Interrupt<br>Flag   | PF    |

| 7   | IRQ Pending Flag             | IRQF  |

Bits 0 to 3 - The unused bits of Status Register 1 are read as "0's", and cannot be written.

Bit 4 - The Update Ended Interrupt Flag (UF) bit is set after each update cycle. When the UIE bit is a "1", the "1" in UF causes the IRQF bit to be a "1", asserting IRQ. UF is cleared by a Register C read or a reset.

Bit 5 - A "1" in the AF (Alarm Interrupt Flag) bit indicates that the current time has matched the alarm time. A "1" in the AF causes the IRQ pin to go low, and a "1" to appear in the IRQF bit, when the AIE bit also is a "1". A reset or a read of Register C clears AF.

Bit 6 - The Periodic Interrupt Flag (PF) is a read only bit which is set to a "1" when a particular edge is detected on the selected tap of the divider chain. The RS3 to RS0 bits establish the periodic rate. PF is set to a "1" independent of the state of the PIE bit. PF being a "1" initiates an IRQ signal and sets the IRQF bit when PIE is also a "1". The PF bit is cleared by a reset or a software read of Register C.

Bit 7 - The Interrupt Request Pending Flag (IRQF) is set to a "1" when one or more of the following are true:

PF = PIE = 1 AF = AIE = 1 UF = UIE = 1

The logic can be expressed in equation form as:

$IRQF = PF \cdot PIE + AF \cdot AIE + UF \cdot UIE$

Any time the IRQF bit is a "1", the IRQ pin is asserted. All flag bits are cleared after Register C is read by the program or when the reset pin is asserted.

#### **Register D**

This register contains a bit that indicates the status of the on-chip standby RAM. The contents of the registers are described as the following:

| Bit | Description                | Abbr. |

|-----|----------------------------|-------|

| 0   | Not Used, Read<br>as 0     |       |

| 1   | Not Used, Read<br>as 0     |       |

| 2   | Not Used, Read<br>as 0     |       |

| 3   | Not Used, Read<br>as 0     |       |

| 4   | Not Used, Read<br>as 0     |       |

| 5   | Not Used, Read<br>as 0     |       |

| 6   | Not Used, Read<br>as 0     |       |

| 7   | Vaild RAM Data<br>and Time | VRT   |

Bits 0 to 6 - The remaining bits of Register D are unused. They cannot be written, but are always read as "0's".

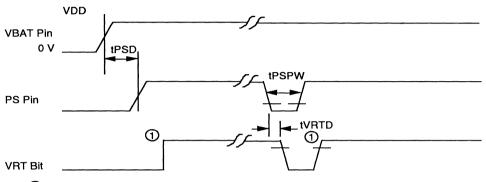

Bit 7 - The Valid RAM Data and Time (VRT) bit indicates the condition of the contents of the RAM, provided the power sense (PS) pin is satisfactorily connected. A "0" appears in the VRT bit when the power-sense pin is low. The processor program can set the VRT bit when the time and calendar are initialized to indicate that the RAM and time are valid. The VRT is a read only bit which is not modified by the reset pin. The VRT bit can only be set by reading Register D.

Pulling the PS/-RC pin low for a minimum of 2  $\mu$ s also sets all RAM bytes from address OE through 3F to all ones.

#### **CMOS STANDBY RAM**

The 66 general purpose RAM bytes are not dedicated within the RTC. They can be used by the processor program, and are fully available during the update cycle.

#### GENERAL RTC NOTES Set Operation

Before initializing the internal registers. the SET bit in Register B should be set to a "1" to prevent time/calendar updates from occurring. The program initializes the ten locations in the selected format (binary or BCD), then indicates the format in the Data Mode (DM) bit of Register B. All ten time, calendar, and alarm bytes must use the same Data Mode, either binary or BCD. The SET bit may now be cleared to allow updates. Once initialized the RTC makes all updates in the selected Data Mode. The Data Mode cannot be changed without reinitializing the ten data bytes.

#### **BCD vs Binary Format**

The 24/12 bit in Register B establishes whether the hour locations represent 1to-12 or 0-to-23. The 24/12 bit cannot be changed without reinitializing the hour locations. When the 12-hour format is selected, the high-order bit of the hours byte represents PM when it is a "1".

#### **Update Operation**

The time, calendar, and alarm bytes are not always accessible by the processor program. Once-per-second the ten bytes are switched to the update logic to be advanced by one second and to check for an alarm condition. If any of the ten bytes are read at this time, the data outputs are undefined. The update lockout time is 1948  $\mu$ s for the 32.768 KHz time base. The Update Cycle section shows how to accommodate the Update Cycle in the processor program.

#### **Alarm Operation**

The three alarm bytes may be used in two ways. First, when the program inserts an alarm time in the appropriate hours, minutes, and seconds alarm locations, the Alarm Interrupt is initiated at the specified time each day if the alarm enable bit is high. The second usage is to insert a "don't care" state in one or more of three alarm bytes. The "don't care" code is any byte from 0C0H to 0FFH. An Alarm Interrupt each hour is created with a "don't care" code in the hours alarm location. Similarly, an alarm is generated every minute with "don't care" codes in the hours and minutes alarm bytes. The "don't care"

codes in all three alarm bytes create an interrupt every second.

VL82C106

#### Interrupts

The RTC plus RAM includes three separate fully automatic sources of interrupts to the processor. The Alarm Interrupt may be programmed to occur at rates from one-per-second to one-a-day. The Periodic Interrupt may be selected for rates from half-a-second to  $30.517 \ \mu$ s. The Update Ended Interrupt may be used to indicate to the program that an update cycle is completed.

The processor program selects which interrupts, if any, it wishes to receive. Three bits in Register B enable the three interrupts. Writing a "1" to an interrupt-enable bit permits that interrupt to be initiated when the event occurs. A "0" in the interrupt-enable bit prohibits the IRQ pin from being asserted due to the interrupt cause.

If an interrupt flag is already set when the interrupt becomes enabled, the IRQ pin is immediately activated, though the interrupt initiating the event may have occurred much earlier. Thus, there are cases where the program should clear such earlier initiated interrupts before first enabling new interrupts.

When an interrupt event occurs, a flag bit is set to a "1" in Register C. Each of the three interrupt sources have separate flag bits in Register C, which are set independent of the state of the corresponding enable bits in Register B. The flag bit may be used with or without enabling the corresponding enable bits.

#### **Divider Control**

The Divider Control bits are fixed for only 32.768 KHz operation. The divider chain may be held in reset, which allows precision setting of the time. When the divider is changed from reset to an operating time base, the first update cycle is one-half a second later. The Divider Control bits are also used to facilitate testing the RTC.

#### **Periodic Interrupt Selection**

The Periodic Interrupt allows the IRQ pin to be triggered from once every 500 ms to once every  $30.517 \ \mu$ s. The Periodic Interrupt is separate from the Alarm Interrupt which may be output from once-per-second to once-per-day.

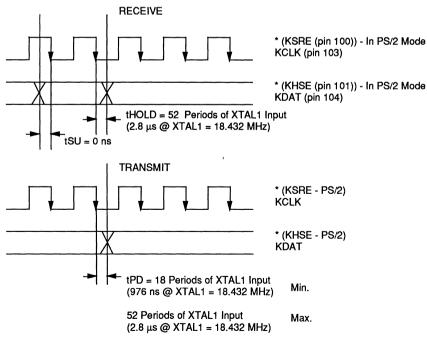

### KEYBOARD CONTROLLER

The keyboard controller on-chip ROM contains the code that is required to support the PC/AT and PS/2 command sets and 128 bytes of conversion code.

Keyboard serial I/O is handled with hardware implementations of the receiver and transmitter. Both functions depend on an 8-bit timer for time-out detection. Enhanced status reporting is provided in hardware to simplify error handling in software. This logic is duplicated for the mouse interface.

User RAM support is provided. The program writes a command 20-3FH (read) or 60-7FH (write) with the lower five bits representing the RAM address. Data from a read or for a write are accessed through port 60H DBB.

Parallel Port 1 (input) is provided and Parallel Port 2 (output) has defined functions depending on whether the controller is in PC/AT or PS/2 mode.

Support for PORT 60H DBB (reads and writes) and Status Register (reads and writes) is provided in hardware for interface to the PC host.

#### KEYBOARD CONTROLLER INTERFACE TO PC/AT

The interface to the PC/AT consists of one register pair (PORT 60H/64H) for the keyboard and mouse. The PORT 60H read operations output the contents of the Output Buffer to D0-D7 and clears the status of the Output Buffer Full (OBF/Status Register bit 0) bit.

Status read operations output the contents of the Status Register to D0-D7. No status is changed as a result of the read operation.

The PORT 60H write operations cause the Input Buffer DBB to be changed. The state of the C/D bit is cleared (Status Register bit 3, "0" indicates data) and the Input Buffer Full (IBF/ Status Register bit 1) bit is set ("1").

Command write operations are to PORT 64H. The C/D bit will be set to ("1") when a valid command has been written to PORT 64H.

#### KEYBOARD PORT INTERFACE PROTOCOL

Data transmission between the controller, the keyboard, and mouse consist of a synchronous bit stream over the data and clock lines. The bits are defined as follows:

| Bit | Function             |

|-----|----------------------|

| 1   | Start Bit (Always 0) |

| 2   | Data Bit 0 (LSB)     |

| 3-8 | Data Bits 1-6        |

| 9   | Data Bit 7 (MSB)     |

| 10  | Parity Bit (Odd)     |

| 11  | Stop Bit (Always 1)  |

|     |                      |

#### **PROGRAMMER INTERFACE**

The programmer interface to the keyboard controller is quite simple, consisting of four registers:

VL82C106

| Register      | R/W | I/O |

|---------------|-----|-----|

| Status        | R   | 64H |

| Command       | w   | 64H |

| Output Buffer | R   | 60H |

| Input Buffer  | w   | 60H |

The behavior of these registers differ according to the mode of operation (PC/ AT or PS/2). There exists only one mode register and one Status Register with different bit definitions for PC/AT mode and PS/2 mode. The bit definitions for each register in each mode follows.

#### 6 5 3 2 0 7 4 1 KBD DKB 0 ксс INH SYS 0 EKI ENABLE KBD INTERRUPT 0 = INT DISABLED 1 = INT ENABLED RESERVED, SET TO 0 SYSTEM FLAG 0 = SETS STATUS REG (2) = 0 1 = SETS STATUS REG (2) = 1 KEY LOCK INHIBIT OVERRIDE 0 = ENABLE KEY LOCK FUNCTION 1 = DISABLE KEY LOCK FUNCTION DISABLE KEYBOARD 0 = ENABLED 1 = DISABLED KEYBOARD TYPE 0 = AT STYLE KEYBOARD 1 = PC STYLE KEYBOARD **KEYCODE CONVERSION** 0 = NO CONVERSION OF KEYCODES 1 = CONVERSION ENABLED RESERVED, SET TO 0

#### FIGURE 1. PC/AT MODE REGISTER (READ PORT 60H AFTER WRITE COMMAND 20H TO PORT 64H)

#### PC/AT MODE REGISTER

Bit 0 - Enable Keyboard Interrupt (EKI), when set ("1") causes the controller to generate a keyboard interrupt whenever data (keyboard or controller) is written into the output buffer.

Bit 1 - Reserved, should be written as "0".

Bit 2 - System Flag (SYS), when set ("1") writes the System Flag bit of the Status Register to "1". This bit is used to indicate a switch from virtual to real mode when set.

Bit 3 - Inhibit Override (INH), when set ("1") disables the keyboard lock function (KKSW Input).

Bit 4 - Disable Keyboard (DKB), when set ("1") disables the keyboard by holding the -KCKOUT line low.

Bit 5 - Keyboard Type (KBD), when set ("1") allows for compatibility with PC-

style keyboards. In this mode, parity is not checked and scan codes are not converted.

Bit 6 - Keycode Conversion (KCC), when set ("1") causes the controller to convert the scan codes to PC format. When reset, the codes (AT keyboard) are passed along unconverted.

Bit 7 - Reserved, should be written as "0".

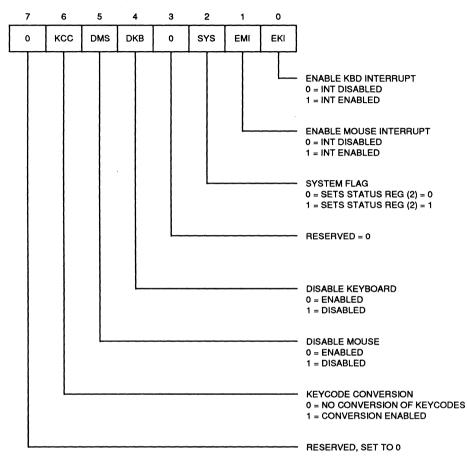

#### FIGURE 2. PS/2 MODE REGISTER (READ PORT 60H AFTER WRITE COMMAND 20H TO PORT 64H)

#### **PS/2 MODE REGISTER**

Bit 0 - Enable Keyboard Interrupt (EKI), when set ("1") causes the controller to generate a keyboard interrupt whenever data (keyboard or command) is written into the output buffer.

Bit 1 - Enable Mouse Interrupt (EMI), when set ("1") allows the controller to generate a mouse interrupt when mouse data is available in the output register. Bit 2 - System Flag (SYS), when set ("1") writes the System Flag bit of the Status Register to "1". This bit is used to indicate a switch from virtual to real mode when set.

Bit 3 - Reserved, "0".

Bit 4 - Disable Keyboard (DKB), when set ("1") disables the keyboard by holding the –KCKOUT low. Bit 5 - Disable Mouse (DMS), when set ("1") disables the mouse by holding the –MCKOUT low.

Bit 6 - Keycode Conversion (KCC), when set ("1") causes the controller to convert the scan codes to PC format. When reset, the codes (PS/2 keyboard) are passed along unconverted.

Bit 7 - Reserved, "0".

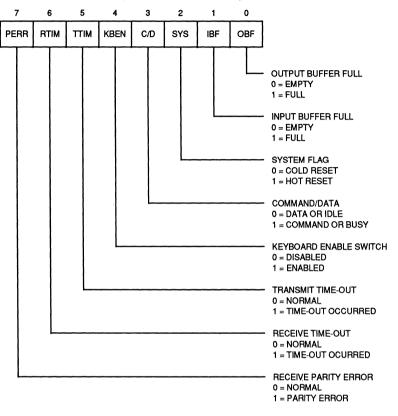

#### FIGURE 3. PC/AT STATUS REGISTER (READ ONLY - PORT 64H)

#### PC/AT Status Register

Bit 0 - Output Buffer Full (OBF), when set ("1") indicates that data is available in the controller Data Bus Buffer, and that the CPU has not read the data yet. CPU reads to PORT 60H to reset the state of this bit.

Bit 1 - Input Buffer Full (IBF), when set ("1") indicates that data has been written to PORT 60H or 64H, and the controller has not read the data.

Bit 2 - System Flag (SYS), when set ("1") indicates that the CPU has changed from virtual to real mode.

Bit 3 - Command/Data (CD), when set ("1") indicates that a command has been placed into the Input Data Buffer of the controller. The controller uses this bit to determine if the byte written is a command to be executed.

Bit 4 - Keyboard Enable (KBEN), indicates the state of the "keyboard inhibit" switch input (KKSW). "0" indicates the keyboard is inhibited.

Bit 5 - Transmit Time-out (TTIM), when set ("1") indicates that a transmission to the keyboard was not completed before the controller's internal timer timed-out. Bit 6 - Receive Time-out (RTIM), when set ("1") indicates that a transmission from the keyboard was not completed before the controller's internal timer timed-out.

Bit 7 - Parity Error (PERR), when set ("1") indicates that a parity error (even parity = error) occurred during the last transmission (received scan code) from the keyboard. When a parity error is detected, the output buffer is loaded with FFH, the OBF Status bit is set and the KIRQ pin is set ["1" if the EKI bit/ Mode Register bit 0 is set ("1")].

#### FIGURE 4. PC/AT KEYBOARD SCAN CODE TRANSLATION TO PC/XT SCAN CODE

| KEYBOARD<br>SCAN CODE | SYSTEM<br>SCAN CODE | KEYBOARD<br>SCAN CODE | SYSTEM<br>SCAN CODE | KEYBOARD<br>SCAN CODE | SYSTEM<br>SCAN CODE |

|-----------------------|---------------------|-----------------------|---------------------|-----------------------|---------------------|

| 00                    | ff                  | 30                    | 69                  | 60                    | 55                  |

| 01                    | 43                  | 31                    | 31                  | 61                    | 56                  |

| 02                    | 41                  | 32                    | 30                  | 62                    | 77                  |

| 03                    | 3f                  | 33                    | 23                  | 63                    | 78                  |

| 04                    | 3d                  | 34                    | 22                  | 64                    | 79                  |

| 05                    | 3b                  | 35                    | 15                  | 65                    | 7a                  |

| 06                    | 3c                  | 36                    | 07                  | 66                    | oe                  |

| 07                    | 58                  | 37                    | 5e                  | 67                    | 7b                  |

| 08                    | 64                  | 38                    | 6a                  | 68                    | 7c                  |

| 09                    | 44                  | 39                    | 72                  | 69                    | 4f                  |

| 0a                    | 42                  | 3a                    | 32                  | 6a                    | 7d                  |

| 0b                    | 40                  | 3b                    | 24                  | 6b                    | 4b                  |

| 0c                    | 3e                  | 3c                    | 16                  | 6c                    | 47                  |

| 0d                    | Of                  | 3d                    | 08                  | 6d                    | 7e                  |

| 0u<br>0e              | 29                  | 3e                    | 09                  | 6e                    | 76<br>7f            |

| Of                    | 59                  | 3f                    | 5f                  | 6f                    | 6f                  |

|                       |                     |                       |                     |                       |                     |

| 10                    | 65                  | 40                    | 6b                  | 70                    | 52                  |

| 11                    | 38                  | 41                    | 33                  | 71                    | 53                  |

| 12                    | 2a                  | 42                    | 25                  | 72                    | 50                  |

| 13                    | 70                  | 43                    | 17                  | 73                    | 4c                  |

| 14                    | 1d                  | 44                    | 18                  | 74                    | 4d                  |

| 15                    | 10                  | 45                    | 0b                  | 75                    | 48                  |

| 16                    | 02                  | 46                    | 0a                  | 76                    | 01                  |

| 17                    | 5a                  | 47                    | 60                  | 77                    | 45                  |

| 18                    | 66                  | 48                    | 6c                  | 78                    | 57                  |

| 19                    | 71                  | 49                    | 34                  | 79                    | 4e                  |

| 1a                    | 2c                  | 4a                    | 35                  | 7a                    | 51                  |

| 1b                    | 1f                  | 4b                    | 26                  | 7b                    | 4a                  |

| 1c                    | 1e                  | 4c                    | 27                  | 7с                    | 37                  |

| 1d                    | 11                  | 4d                    | 19                  | 7d                    | 49                  |

| 1e                    | 03                  | 4e                    | 0c                  | 7e                    | 46                  |

| 1f                    | 5b                  | 4f                    | 61                  | 7f                    | 54                  |

|                       |                     |                       |                     |                       |                     |

| 20<br>21              | 67<br>2e            | 50<br>51              | 6d<br>73            | The following scar    | codes are converte  |

|                       |                     |                       | 28                  | by inline code:       |                     |

| 22                    | 2d                  | 52                    |                     | ,                     |                     |

| 23                    | 20                  | 53                    | 74                  | <b>-</b>              | - <u> </u>          |

| 24                    | 12                  | 54                    | 1a                  | KEYBOARD              | SYSTEM              |

| 25                    | 05                  | 55                    | 0d                  | SCAN CODE             |                     |

| 26                    | 04                  | 56                    | 62                  |                       |                     |

| 27                    | 5c                  | 57                    | 6e                  | 83                    | 41                  |

| 28                    | 68                  | 58                    | 3a                  | 84                    | 54                  |

| 29                    | 39                  | 59                    | 36                  | - '                   |                     |

| 2a                    | 2f                  | 5a                    | 1c                  |                       |                     |

| 2b                    | 21                  | 5b                    | 1b                  | Note: All other       | PC/AT scan codes    |

| 2c                    | 14                  | 5c                    | 75                  |                       | ed to the system    |

| 2d                    | 13                  | 5d                    | 2b                  | untransla             |                     |

| 2e                    | . 06                | 5e                    | 63                  |                       | -                   |

| 2f                    | 5d                  | 5f                    | 76                  |                       |                     |

# 6

-

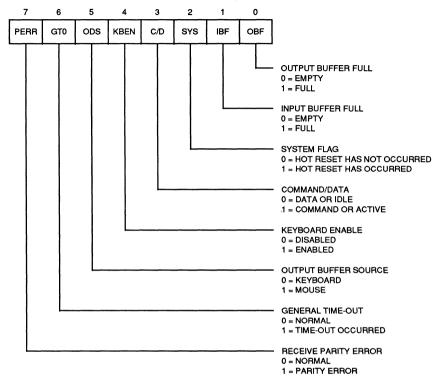

#### FIGURE 5. PS/2 STATUS REGISTER (READ ONLY - PORT 64H)

#### **PS/2 Status Register**

Bit 0 - Output Buffer Full (OBF), when set ("1") indicates that data is available in the controller Data Bus Buffer, and that the CPU has not read the data yet. The CPU reads to PORT 60H reset the state of this bit.

Bit 1 - Input Buffer Full (IBF), when set ("1") indicates that data has been written to PORT 60H or 64H, and the controller has not read the data.

Bit 2 - System Flag (SYS), when set ("1") indicates that the CPU has changed from virtual to real mode.

Bit 3 - Command/Data (CD), when set ("1") indicates that a command has been placed into the Input Data Buffer of the controller. The controller uses this bit to determine if the byte written is a command to be executed. This bit is not reset until the command has completed its operation.

Bit 4 - Keyboard Enable (KBEN) indicates the state of the "keyboard inhibit" switch input (KKSW). "0" indicates the keyboard is inhibited.

Bit 5 - Output Buffer Data Source (ODS), when set ("1") indicates that the data in the output buffer is mouse data. When reset, it indicates the data is from the keyboard.

Bit 6 - Time-out Error (TERR), when set ("1") indicates that a transmission was

started and that it did not complete within the normal time taken (approximately 11 KCKIN cycles). If the transmission originated from the controller, a FEH is placed in the output buffer. If the transmission originated from the keyboard, a FFH is placed in the output buffer.

Bit 7 - Parity Error (PERR), when set ("1") indicates that a parity error (even parity = error) occurred during the last transmission from the keyboard. When a parity error is detected, the output buffer is loaded with FFH, the OBF Status bit is set and the KIRQ pin is set ["1" if the EKI bit/Mode Register bit 0 is set ("1")].

#### COMMAND SET

The command set supported by the keyboard controller supports two modes of operation, and a set of extensions to the AT command set for the PS/2. In both modes, the command is implemented by writing the command byte to PORT 64H. Any subsequent data is read from PORT 60H (see description of command 20) or written to PORT 60H (see description 60H (see description of command PORT 60H). The commands for each mode are shown in the table below:

#### PC/AT Mode:

| Comm. | Description                                  |  |

|-------|----------------------------------------------|--|

| 20    | Read Mode Register                           |  |

| 21-3F | Read Keyboard Controller<br>RAM (Byte 1-31)  |  |

| 60    | Write Mode Register                          |  |

| 61-7F | Write Keyboard Controller<br>RAM (Byte 1-31) |  |

| AA    | Self Test                                    |  |

| AB    | KBD Interface Test                           |  |

| AC    | Diagnostic Dump                              |  |

| AD    | Disable Keyboard                             |  |

| AE    | Enable Keyboard                              |  |

| CO    | Read Input Port (P10-P17)                    |  |

| D0    | Read Output Port (P20-P27)                   |  |

| D1    | Write Output Port                            |  |

| E0    | Read Test Inputs (T0, T1)                    |  |

| F0-FF | Pulse Output Port (P20-P27)                  |  |

Note: If data is written to the data buffer (PORT 60H) and the command preceding it did not expect data from the port (PORT 60H) the data will be transmitted to the keyboard. Added PS/2 Commands:

| Comm. | Description                             | A5         |

|-------|-----------------------------------------|------------|

| A4    | Test Password                           |            |

| A5    | Load Password                           |            |

| A6    | Enable Password                         |            |

| A7    | Disable Mouse                           |            |

| A8    | Enable Mouse                            |            |

| A9    | Mouse Interface Test                    |            |

| C1    | Poll in Port Low<br>(P10-P13 -> S4-S7)  |            |

| C2    | Poll in Port High<br>(P14-P17 -> S4-S7) | <b>A</b> 6 |

| D1    | Write Output Port                       |            |

| D2    | Write Keyboard Output Buffer            |            |

| D3    | Write Mouse Output Buffer               | ,          |

| D4    | Write to Mouse                          |            |

|       |                                         |            |

The following is a description of each command:

- Read the keyboard controller's Mode Register (PC/AT and PS/ 2) - The keyboard controller sends its current mode byte to the output buffer (accessed by a read of PORT 60H).

- 21-3F Read the keyboard controller's RAM (PC/AT and PS/2) - Bits D4-D0 specify the address.

- 60 Write the keyboard controller's Mode Register (PC/AT and PS/ 2) - The next byte of data written to the keyboard data port (PORT 60H) is placed in the controller's mode register.

- 61-7F Write the keyboard controller's RAM (PC/AT and PS/2) - This command writes to the internal keyboard controller RAM with the address specified in bits D4-D0.

- A4 Test Password Installed (PS/2 only) - This command checks if there is currently a password installed in the controller. The test result is placed in the output buffer (the OBF bit is set) and KIRQ is asserted (if the EKI bit is set). Test result - FAH means

VL82C106

that the password is installed, and F1H means that it is not.

- Load Password (PS/2 only) -This command initiates the password load procedure. Following this command, the controller will take data from the input buffer port (PORT 60H) until a 00H is detected or a full eight byte password including a delimiter (e.g. <cr>) is loaded into the password latches. Note: this means that during password validation, the password can be a maximum of seven bytes with a delimiter such as <cr>.

- Enable Password (PS/2 only) -This command enables the security feature. The command is valid only when a password pattern is written into the controller (see A5 command). No other commands will be "honored" until the security sequence is completed and command A6 is cleared.

- A7 Disable Mouse (PS/2 only) -This command sets bit 5 of the Mode Register which disables the mouse by driving the -MCKOUT line low.

- A8 Enable Mouse (PS/2 only) This command resets bit 5 of the Mode Register, thus enabling the mouse.

- A9 Mouse Interface Test (PS/2 only) - This command causes the controller to test the mouse clock and data lines. The results are placed in the output buffer (the OBF bit is set) and the KIRQ line is asserted (if the EKI bit is set). The results are as follows:

| Data | Meaning                     |

|------|-----------------------------|

| 00   | No Error                    |

| 01   | Mouse Clock Line Stuck Low  |

| 02   | Mouse Clock Line Stuck High |

| 03   | Mouse Data Line Stuck Low   |

| 04   | Mouse Data Line Stuck High  |

- AA Self Test command (PC/AT and PS/2) - This commands the controller to perform internal diagnostic tests. A 55H is placed in the output buffer if no errors were detected. The OBF bit is set and KIRQ is asserted (if the EKI bit is set).

- AB Keyboard Interface Test (PC/AT and PS/2) - This command causes the controller to test the keyboard clock and data lines. The test result is placed in the output buffer (the OBF bit is set) and the KIRQ line is asserted (if the EKI bit is set). The results are as follows:

| Data | Meaning                        |

|------|--------------------------------|

| 00   | No Error                       |

| 01   | Keyboard Clock Line Stuck Low  |

| 02   | Keyboard Clock Line Stuck High |

| 03   | Keyboard Data Line Stuck Low   |

| 04   | Keyboard Data Line Stuck High  |

- AC Diagnostic Dump (PC/AT only, Reserved on PS/2) - Sends 16 bytes of the controller's RAM, the current state of the input port, and current state of the output port to the system.

- AD Keyboard Disable (PC/AT and PS/2) - This command sets bit 4 of the Mode Register to a "1". This disables the keyboard by driving the clock line (-KCKOUT) high. Data will not be sent or received.

- AE Keyboard Enable (PC/AT and PS/2) - This command resets bit 4 of the mode byte to a "0". This enables the keyboard again by allowing the keyboard clock to free-run.

- C0 Read P1 Input Port (PC/AT and PS/2) - This command reads the keyboard input port and places it in the output buffer. This command overwrites the data in the buffer.

- C1 Poll Input Port low (PS/2 only) -P1 bits 0-3 are written into Status

Register bits 4-7 until a new command is issued to the keyboard controller.

- C2 Poll Input Port high (PS/2 only) -P1 bits 4-7 are written into Status Register bits 4-7 until a new command is issued to the keyboard controller.

- D0 Read Output Port (PC/AT and PS/2) - This command causes the controller to read the P2 output port and place the data in its output buffer. The definitions of the bits are as follows:

| Bit | Pin | PC/AT<br>Mode         | PS/2<br>Mode |

|-----|-----|-----------------------|--------------|

| 0   | P20 | -RC                   | –RC          |

| 1   | P21 | A20 Gate              | A20 Gate     |

| 2   | P22 | Speed Sel             | -MDOUT       |

| 3   | P23 | Shadow<br>Enable      | -MCKOUT      |

| 4   | P24 | Output<br>Buffer Full | KIRQ         |

| 5   | P25 |                       | MIRQ         |

| 6   | P26 | -KCKOUT               | -KCKOUT      |

| 7   | P27 | KDOUT                 | -KDOUT       |

- Note: P22 (bit 2) is the speed control pin used by Award BIOS, and this is different from what is used by Phoenix and AMI.

- D1 Write Output Port (PC/AT and PS/2) - The next byte of data written to the keyboard data port (PORT 60H) will be written to the controller's output port. The definitions of the bits are as defined above. In PC/AT mode, P26 and P27 are not modified. In PS/2 mode, P22, P23, P26 and P27 are not modified.

- D2 Write Keyboard Output Buffer (PS/2 only) - The next byte written to the data buffer (PORT 60H) is written to the output buffer (60H) as if initiated by the keyboard [the OBF bit is set ("1") and KIRQ will be set if the EKI bit is set ("1")].

# VL82C106

- D3 Write Mouse Output Buffer (PS/ 2 only) - The next byte written to the data buffer (PORT 60H) is written to the output buffer as if initiated by the mouse [the OBF bit is set ("1") and MIRQ will be set if the EMI bit is set ("1")].

- D4 Write to Mouse (PS/2 only) -The next byte written to the data buffer (PORT 60H) is transmitted to the mouse.

- E0 Read Test Inputs (PC/AT and PS/2) - This command causes the controller to read the T0 and T1 input bits. The data is placed in the output buffer with the following meanings:

| Bit | PC/AT Mode     | PS/2 Mode      |

|-----|----------------|----------------|

| 0   | Keyboard Data  | Keyboard Clock |

| 1   | Keyboard Clock | Mouse Clock    |

| 3-7 | Read as 0's    | Read as 0's    |

F0-FF Pulse Output Port (PC/AT and PS/2) - Bits 0-3 of the controller's output port may be pulsed low for approximately 6 µs. Bits 0-3 of the command specify which bit will be pulsed. A "0" indicates that the bit should be pulsed; a "1" indicates that the bit should not be modified. FF is treated as a special case (Pulse Null Port). In PC/AT mode, bits P26 and P27 are not pulsed. In PS/2 mode, bits P26, P27, P22 and P23 are not pulsed.

#### IDE Bus Interface Control

Integrated Drive Electronics bus interface control signals are provided by the VL82C106 Combo chip. The timing and drive for these lines are consistent with the Conner Peripherals CP342 Integrated Hard Disk Manual.

A set of signals are used for this interface when the VL82C106 Combo chip is configured to support the IDE interface via IDE\_EN, bit 5 of Control Register 1 (RTC Register 6AH).

The Combo chip has duplicated bit 1 of the "Fixed Disk Register" (I/O 3F6H) to enable IRQI.

Input Signals:

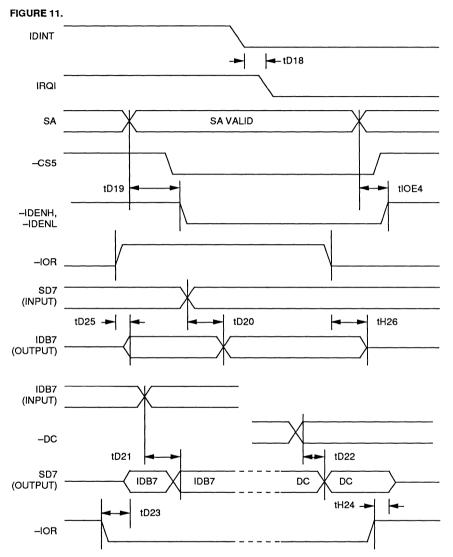

IDINT This signal indicates an interrupt request to the system. It is used to generate IRQI.

Output Signals:

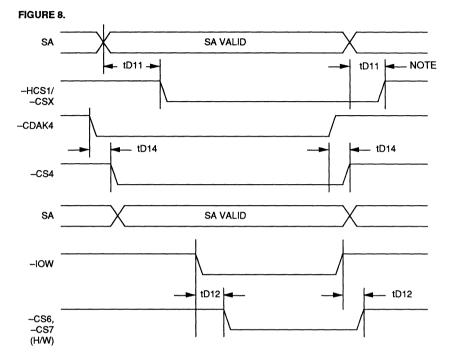

- -CS4 Chip Select 4. This signal is used as the floppy disk chip select. The default decode is 03F4H-03F5H, but may be redefined as described in the section on Combo Chip Control Registers. The IDE\_EN control bit of Control Register 1 has no effect on this signal. -CS4 is also active when -CDAK4 is active.

- -CS5 Chip Select 5. This signal is used as the -HOST CS0 of the IDE bus. The default decode is 01F0H-01F7H, but may be redefined as described in the section on Combo Chip Control Registers. The IDE\_EN control bit of Control Register 1 has no effect on this signal.

- -HCS1 This signal is active (low) for address 03F6H-03F7H and is used as -HOST CS1 of the IDE bus.

- -IDENH This signal is used to drive the -OE pin of an external 74LS245 buffering bits 8-15 of the IDE data bus to the SD bus. It is active (low) when:

-CS5 is active AND SA2-SA0 = 000.

-IDENL This signal is used to drive the -OE pin of an external 74LS245 buffering bits 0-6 of the IDE data bus. It is active (low) when:

> -CS5 is active OR SA0-SA9 = 3F6 OR 3F7.

This allows a simple implementation for an IDE bus that includes both the hard disk controller and the floppy disk controller.

- IRQI This is the three-state interrupt request to the CPU. It is normally tied directly to the IRQ14 signal of the system. It reflects the state of the IDINT input and is enabled by writing bit 1 = 0 of I/O 3F6H as long as IDE\_EN=1. Reset or disabling the IDE system three-states IRQI.

- -IOCS16 The VL82C106 Combo chip has multiple sources for this signal. It is driven active (low) when:

(-CS5 is active AND SA0-SA2 = 000 AND IDE\_EN = 1 AND {(CS\_MODE = 0) OR (CS\_MODE = 1 AND 16-bit operation selected for CS5)}} OR (any other CS is active with 16-bit operation selected AND CS\_MODE = 1) OR (IDE\_EN = 0 AND CS5 is active AND 16-bit operation is selected AND CS MODE = 1).

**Bidirectional Signals:**

IDB7, -DC The control for the transceiver between IDB7, -DC, and SD7 is as follows:

IDB7 -> SD7 when:

(-CS5 is active OR SA0-SA9 = 3F6) AND -IOR is active AND IDE\_EN = 1 AND NOT SA0-SA9 = 3F7H.

-DC -> SD7 when SA0-SA9 = 3F7H AND -IOR is active AND IDE\_EN = 1. SD7 -> IDB7 at all other times when IDE\_EN=1, three-stated (with internal pull-up) if IDE\_EN=0.

#### **Combo Chip Control Ports:**

Contained in the VL82C106 are a set of 26 registers used for programming peripheral chip select base addresses. chip select address ranges, and enabling options. Each base address register is a 16-bit register with bits corresponding to address bits A15-A0. In addition to base address registers, there is an address range register that can be used to "don't-care" bits (A0-A4) used in the address range comparison, effectively controlling the address space occupied by the chip select from 1 to 32 bytes. There are also programmable bits to selectively generate wait states, and assert -IOCS16 whenever the corresponding address range is present. These registers are used in groups of three per chip select, and are defined as shown below:

Base Address Register (LSB):

| Bit | Description          |

|-----|----------------------|

| 0   | Base Address, Bit A0 |

| 1   | Base Address, Bit A1 |

| 2   | Base Address, Bit A2 |

| 3   | Base Address, Bit A3 |

| 4   | Base Address, Bit A4 |

| 5   | Base Address, Bit A5 |

| 6   | Base Address, Bit A6 |

| 7   | Base Address, Bit A7 |

Base Address Register (MSB):

| Bit | Description           |

|-----|-----------------------|

| 0   | Base Address, Bit A8  |

| 1   | Base Address, Bit A9  |

| 2   | Base Address, Bit A10 |

| 3   | Base Address, Bit A11 |