-

PUBLICATION 900.006A JANUARY 8, 1987

ARCNET

LOCAL AREA NETWORK

CONTROLLER

DESIGNER'S GUIDE

~

# Table of Contents

|  |  | ~ | - | - | - | - | - | - | - | - | - | - | - | - | - | - | - | - | - | - | - |

|--|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|--|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1.0         | GENERAL INFORMATION                              | 1  |

|-------------|--------------------------------------------------|----|

|             | 1.1 ARCNET-PC FAMILY DESCRIPTION                 | 1  |

| 2.0         | SPECIFICATIONS                                   | 3  |

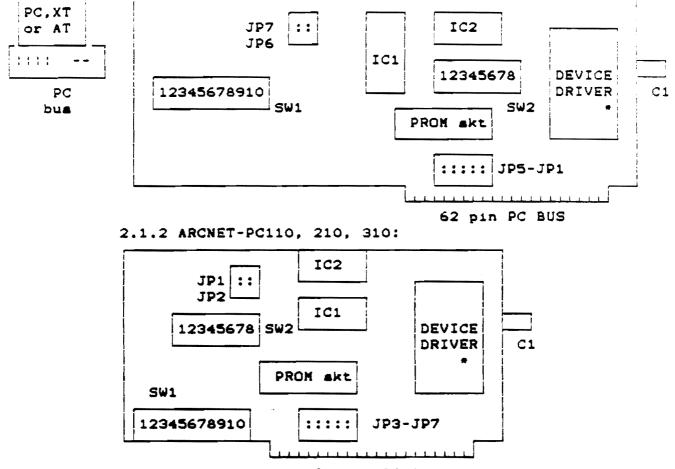

|             | 2.1 ARCNET-PC FAMILY BLOCK DIAGRAM               | -  |

|             | 2.1.1 ARCNET- PC100, 200, 300                    |    |

|             | 2.1.2 ARCNET-PC110, 210, 310:                    |    |

|             | 2.2 PHYSICAL SPECIFICATIONS                      |    |

|             | 2.3 TOPOLOGICAL SPECIFICATIONS                   |    |

|             | 2.3.1 ARCNET-PC 100,110                          |    |

|             | 2.3.2 ARCNET-PC 200, 210                         |    |

|             | 2.3.3 ARCNET-PC 300, 310                         |    |

|             | 2.3.4 TOPOLOGY EXAMPLE                           | 5  |

|             | ARCNET-PC SWITCH CONFIGURATION                   | (  |

|             | 3.1 SWITCH GROUPS OVERVIEW                       |    |

|             | 3.2 SWITCH GROUP #2 SETTINGS                     |    |

|             | 3.2.1 SWITCHES 1 - 8 NODE ADDRESS VALUE          | (  |

|             | 3.3 SWITCH GROUP #1 SETTINGS                     | ť  |

|             | 3.3.1 SWITCHES 1 - 6 I/O ADDRESS VALUE           | (  |

|             | 3.3.2 SWITCHES 7 - 10 RAM BUFFER ADDRESS VALUE . | -  |

| 1.0         | ARCNET-PC JUMPER CONFIGURATION                   | -  |

| 5.0         | ARCNET-PC REGISTERS                              | ł  |

| 5.0         | ARCNET-PC HEMORY ADDRESSING                      | ٤  |

| 7.0         | THEORY OF OPERATION                              | ٤  |

|             | 7.1 Address Decoding                             | 4  |

|             | 7.1 Address Decoding                             | 4  |

|             | 7.2 Internal Address-Data Bus                    | ¢  |

|             | 7.3 Weit State Generator                         | Ś  |

|             | 7.4 Interrupts                                   | 4  |

|             | 7.5 Cable Transceiver                            | 10 |

| 8.0         | PROGRAMMING CONSIDERATIONS                       | 10 |

| <b>v</b> .v |                                                  |    |

### 1.0 GENERAL INFORMATION

#### 1.1 ARCNET-PC FAMILY DESCRIPTION

SMC's ARCNET-PC family of network controller boards provides the user with a simplified interface between the IBM PC bus and an ARCNET modified token passing Local Area Network. The ARCNET-PC, in addition, provides the complete controller for the local area network, which results in virtually user transparent network operation and control.

The ARCNET local area network was originally developed by the Datapoint Corporation as a high performance local area network used interconnect sophisticated computing systems. Now the to performance capabilities of this network are available to users of IBM PC and PC compatible computer systems. The ARCNET-PC family incorporates the Standard Microsystems single chip COM 9026 Local Area Network Controller and COM 9032 ARCNET Local Area Network Transceiver LSI circuits to provide complete ARCNET protocol handling on a single board. A 2K on-board Data Packet Buffer is used to provide four pages of packet storage. This may be dynamically user defined to provide double buffering for both transmit and receive functions. The controller may be polled or interrupt driven. An on-board SK PROM socket is available to the user for auto boot PROM installation thus enabling a floppy-less PC to access a Local Area Network. The memory mapped Data Packet Buffer, I/O-mapped CON 9026 Controller and SK PRON mocket provide a flexible well rounded PC Local Area Network Controller.

ARCNET-PC100, PC110 - The ARCNET PC100 contains the SMC HYC9068 hybrid RG-62/U coaxiel transceiver which connects computers to the ARCNET TOKEN PASSING LOGICAL RING Configuration [i.e. Free Form Tree topology]. The maximum distance for communication between active device units is 2000'. The ARCNET-PC110 contains the same logic, but is a Surface Mounted Helf Slot board.

ARCNET-PC200, PC210 - Contains the SHC 9058 High Impedance Transceiver hybrid that allows up to 8 ARCNET- PC200's to be daisy chained over a maximum distance of 1000'. The PC210 is a short slot SMT version of the ARCNET-PC200 and both these units are compatible with the PC100, PC110's.

ARCNET-PC300, PC310 - Contains a Fiber Optic Transceiver hybrid that will allow ARCNET-PC300'S, PC310's to communicate over a distance of 4000' between active units and is well suited as a transmission medium in a high noise/RF environment. The ARCNET-PC310 is a helf slot Surface Mount Devices version of the ARCNET-PC300.

# 1.2 ARCNET FAMILY FEATURES :

- Provides a simplified interface between IBM/IBM compatible personal computers and the ARCNET modified token passing Local Area Network.

- Compatible with ARCNET baseband coax transmission network

- Uses Standard Microsystems' CON 9026 LAN Controller and COM 9032 LAN Transceiver to simplify the physical and link level ARCNET protocols.

- Supports up to 255 nodes per network segment

- Complete network controller

- 2.5 Megabit data rate

- On-board 2K Data Packet Buffer holds up to four data packets to provide double buffered transmit and receive functions

- Multi transmission media capability

COAX CABLE, FIBER OPTIC

- On-board Transceiver hybrid provides greater reliability

- On-board 8K x 8 PROM socket

- Base address of 8K PROM and Data Packet Buffer is switch selectable in 64K segments

- COM 9026 I/O base address is switch selectable in 16 byte segments

- Controller may be polled or interrupt driven with interrupts jumpered to IR02, IR03, IR05, or IR07

2

### 2.0 SPECIFICATIONS

#### 2.1 ARCNET-PC FAMILY BLOCK DIAGRAM

62 pin PC BUS

LEGEND:

C1 BNC RG62 Coex Connector/SMA 200 micron Fiber Optic Connector IC1 SMC COM 9026 LAN Controller SW1 1-6 I/O Address Select IC2 SMC COM 9032 LAN Transceiver SW1 7-10 Memory buffer address SW2 1-8 Node Address selector

|                             | PC110 TYPE | PC100 TYPE        |

|-----------------------------|------------|-------------------|

| Extended timeout jumpers:   | JP1, JP2   | <b>JP3 - JP</b> 7 |

| Interrupt selector jumpers: | JP7, JP6   | JP5 - JP1         |

- DEVICE DRIVERS :

ARCNET-PC100, 110 - SMC9068 HYBRID RG62/U COAX TRANSCEIVER ARCNET-PC200, 210 - SMC9058 HIGH IMPEDANCE RG62/U HYBRID TRANSCEIVER ARCNET-PC300, 310 - FIBER OPTIC TRANSCEIVER 2.2 PHYSICAL SPECIFICATIONS:

| ARCNET Controller:       | SMC COM 9026 LAN Controller               |

|--------------------------|-------------------------------------------|

| Cable Transceiver:       | SMC COM 9032 LAN Transceiver              |

| Network Implementation:  | Compatible with Datapoint ARCNET LAN      |

|                          | network apecifications. Uses a base band  |

|                          | system with RG62/U (93 chm) coax or 200   |

|                          | aicron step index fiber optic cable.      |

| System Bus:              | Compatible with IBM Personal Computer Bua |

| Memory:                  | 2K x 8 Static Ram Data Packet Buffer      |

|                          | 8K x 8 PROM Location                      |

| Power Requirement:       | +5 volta @ 900 ma. max.+                  |

|                          | -5 volts @ 42.5 ma. max.                  |

| Physical Dimensions      |                                           |

| ARCNET-PC100,200,300:    | 8.5" by 3.9"                              |

| ARCNET-PC110,210,310:    | 5.25" by 3.9"                             |

| Environmental Operation: | 0° to 70° C                               |

| Coax Connector:          | Isolated Ground BNC                       |

| Fiber Optic Connector:   | SMA 200 micron step index single fiber    |

| POWER REQUIREMENTS for   | the PC200.210 would have an increase      |

POWER REQUIREMENTS for the PC200,210 would have an increase of 60 ma 8 +5 volts 10 ma 8 -5 volts

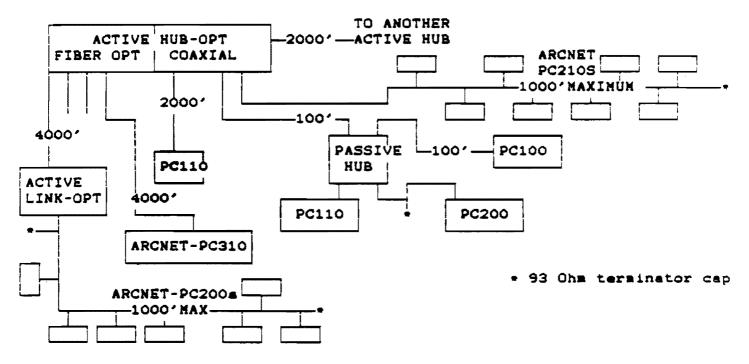

# 2.3 TOPOLOGICAL SPECIFICATIONS

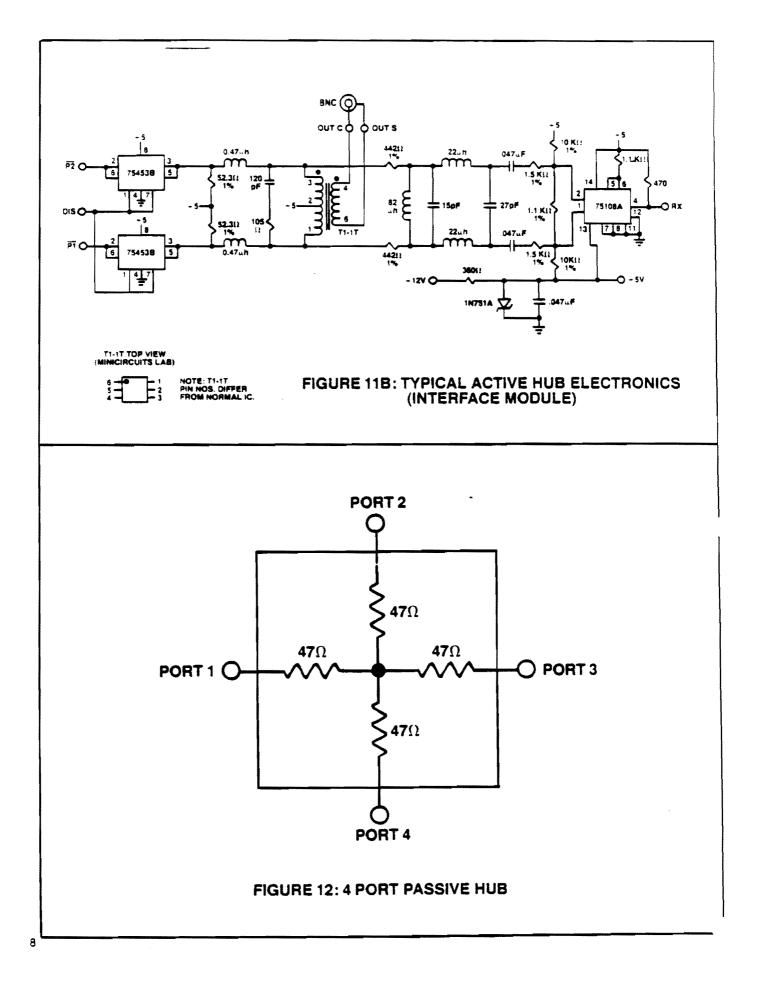

2.3.1 ARCNET-PC 100,110

The PC100,110 products are used in a Free-Form Tree topology with the following distance restrictions:

- 1 2000 feet maximum distance between active hubs and/or ARCNET-PC 100,110 controller boards.

- 2 100 feet maximum distance between passive hub port and an active hub port or ARCNET-PC 100,110 board.

## 2.3.2 ARCNET-PC 200, 210

The ARCNET-PC 200,210 controller boards are used in a physical Bus Format topology while retaining a logical Token Passing ring format. The topological restrictions are as follows:

- 1 Maximum bus length of 1000 feet with up to 8 ARCNET-PC200,210 boards tapped off the bus using "T" coaxial connectors.

- 2 Each end of the bus is to be terminated by either an active hub port or a 93 Ohm terminator.

2.3.2 ARCNET-PC 200, 210 cont.

- 3 For extended Bus lengths, a single PC200 node on a 1000 foot bus can be replaced by one port of a 2 Port SMC ACTIVE LINK which can then extend the bus an additional 1000 feet with up to 7 ARCNET-PC200, 210 units tapped off.

- 4 An ARCNET-PC 200 or PC210 CAN be used in place of ARCNET-PC 100 or PC110 if it is used in conjunction with a "T" and Terminator on the PC100 coaxial cable - See diagram.

2.3.3 ARCNET-PC 300, 310

The ARCNET-PC 300, 310 are Fiber Optic ARCNET boards that can be used in a network with the following constraints:

- 1 Maximum distance is 4000 feet of 200 micron fiber optic cable.

- 2 To use with an existing ARCNET network, the ARCNET-PC 300,310 can be connected to either an SMC ACTIVE LINK-OPT for use with PC200,210 based system or an SMC ACTIVE HUB-OPT for use with multiple Fiber Optic ARCNET units.

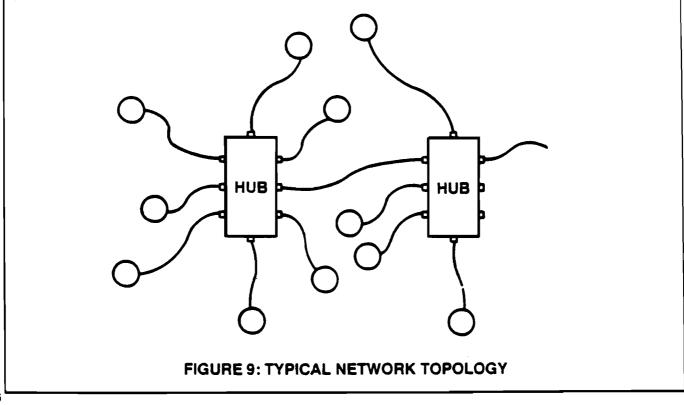

#### 2.3.4 TOPOLOGY EXAMPLE

The following example of a physical network layout is intended to demonstrate the interconnectability of SMC ARCNET:

## 3.0 ARCNET-PC SWITCH CONFIGURATION

#### 3.1 SWITCH GROUPS OVERVIEW:

A switch is equivalent to logical 1 when rocker or slide is set to the down position and logical 0 when the rocker or slide is set to the up position. The switches within the Switch Group represent the binary equivalent of the address value required for proper software operation. Refer to your Software documentation for the proper address and interrupt values.

#### 3.2 SWITCH GROUP #2 SETTINGS:

## 3.2.1 SWITCHES 1 - 8 NODE ADDRESS VALUE

All the switches in Switch Group #2 are used to set the station address. The station address value must be unique to each station. The LSB for the node address is switch 1.

| EXAMPLE:          | switches                               |

|-------------------|----------------------------------------|

|                   | 1 2 3 4 5 6 7 8                        |

| SWITCH<br>Group 2 | U U U U U U<br>D D D = down, off, open |

This setting has a value of 4 + 8 = 12 Decimal or OC HEX for a station address or NODE ID of OC.

## 3.3 SWITCH GROUP #1 SETTINGS:

3.3.1 SWITCHES 1 - 6 I/O ADDRESS VALUE

Switches 1-6 set the base I/O address whose value is 16 times the HEX value of the switches. The LSB for the I/O Address is switch 6.

| EXAMPLE:          | ewitches<br>1 2 3 4 5 6 |                                           |

|-------------------|-------------------------|-------------------------------------------|

| SWITCH<br>Group 1 | - U U<br>D - D D D -    | U = up, on, closed<br>D = down, off, open |

|                   |                         |                                           |

The value of the above setting is equal to 32 + 8 + 4 + 2 = 46Decimal or 2E HEX which is used as a base I/O address of 2EO. 3.3.2 SWITCHES 7 - 10 RAM BUFFER ADDRESS VALUE

Switches 7-10 set the base address (segment) of the memory buffer whose value is 64 K [or 10000 HEX] times the value of the binary representation of the switches. The LSB for the Buffer Address is switch 10.

| EXAMPLE: | switches<br>7 8 9 10 | _                   |

|----------|----------------------|---------------------|

| SWITCH   | U                    | U = up, on, closed  |

| GROUP 1  | D D D -              | D = down, off, open |

The value of the above setting is equal to 8 + 4 + 2 = 14Decimal or E HEX which is used as a RAM buffer eddress of E000:0

#### 4.0 ARCNET-PC JUMPER CONFIGURATION

#### JUNPER

| PC100 TYPE    | PC110 TYPE | FUNCTION                  |     |

|---------------|------------|---------------------------|-----|

| JP1           | JP7        | COM 9026 INTR = IRQ7      | -   |

| JP2           | JP6        | COM 9026 INTR = IRQ5      |     |

| JP3           | JP5        | COM 9026 INTR = IRQ4      |     |

| JP4           | JP4        | CON 9026 INTR = IRQ3      |     |

| JP5           | JP3        | COM 9026 INTR = IRQ2      |     |

| J <b>P6</b> * | JP2        | CON 9026 ET2 (Normally op | en) |

| J <b>P7*</b>  | JP1        | COM 9026 ET1 (Normally op | en) |

|               |            |                           |     |

• Refer to Extended Timeout Function in Appendix A.O.

7

5.0 ARCNET-PC REGISTERS

| AЗ |     | DRESS<br>A1 | -    | REGISTER                                |

|----|-----|-------------|------|-----------------------------------------|

| 0  | 0   | x           | 0    | COM 9026 Interrupt Mask/Status Register |

| 0  | 0   | x           | 1    | COM 9026 Command Register               |

| 1  | 0   | x           | x    | ARCNET-PC Software Reset                |

|    | X = | Don         | 't C | are,                                    |

|    |     |             |      |                                         |

See Appendix A.O COM 9026 Data Sheet for bit definitions of each register.

6.0 ARCNET-PC MEMORY ADDRESSING

| 1   | ADDRES | S   |     |     | MEMORY |                           |  |  |

|-----|--------|-----|-----|-----|--------|---------------------------|--|--|

| A19 | A18    | A17 | A16 | A15 | A14    |                           |  |  |

| X   | x      | x   | x   | 0   | 0      | 2K X 8 Data Packet Buffer |  |  |

| x   | x      | x   | x   | 1   | 0      | SK X S Prom               |  |  |

Address bits A19 through A16 are selected by switches 7 through 10 in switch group 1 respectively.

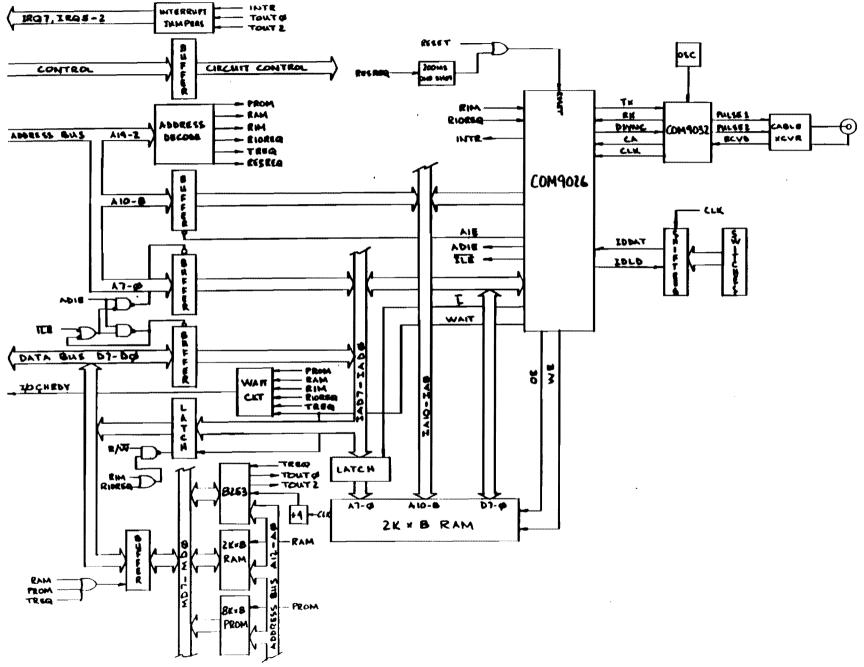

# 7.0 THEORY OF OPERATION

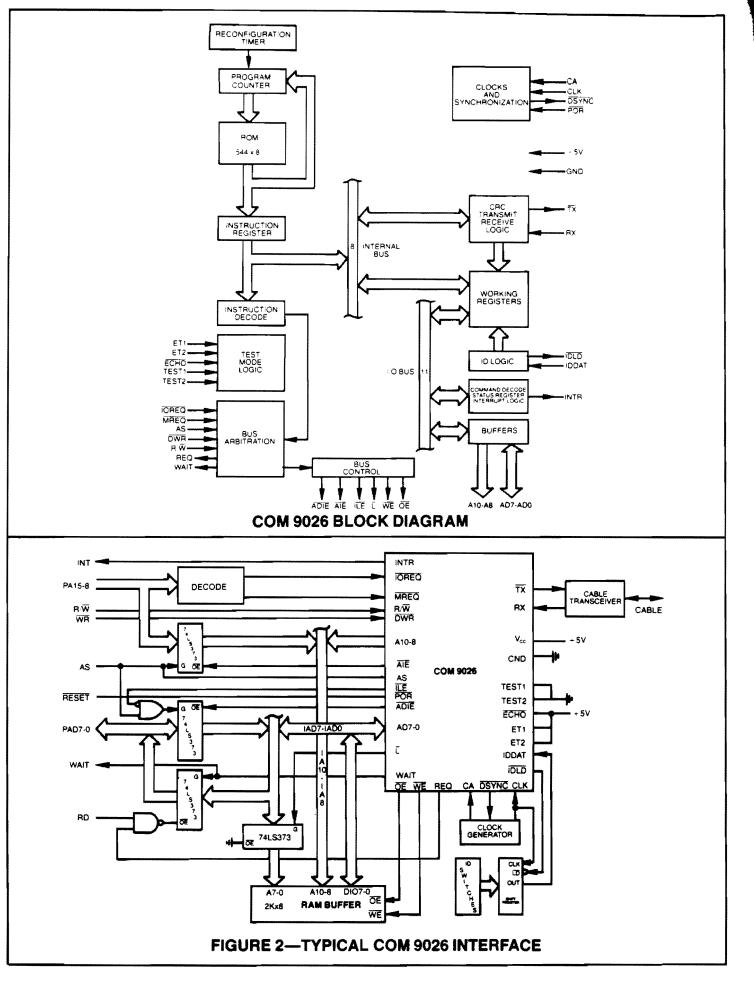

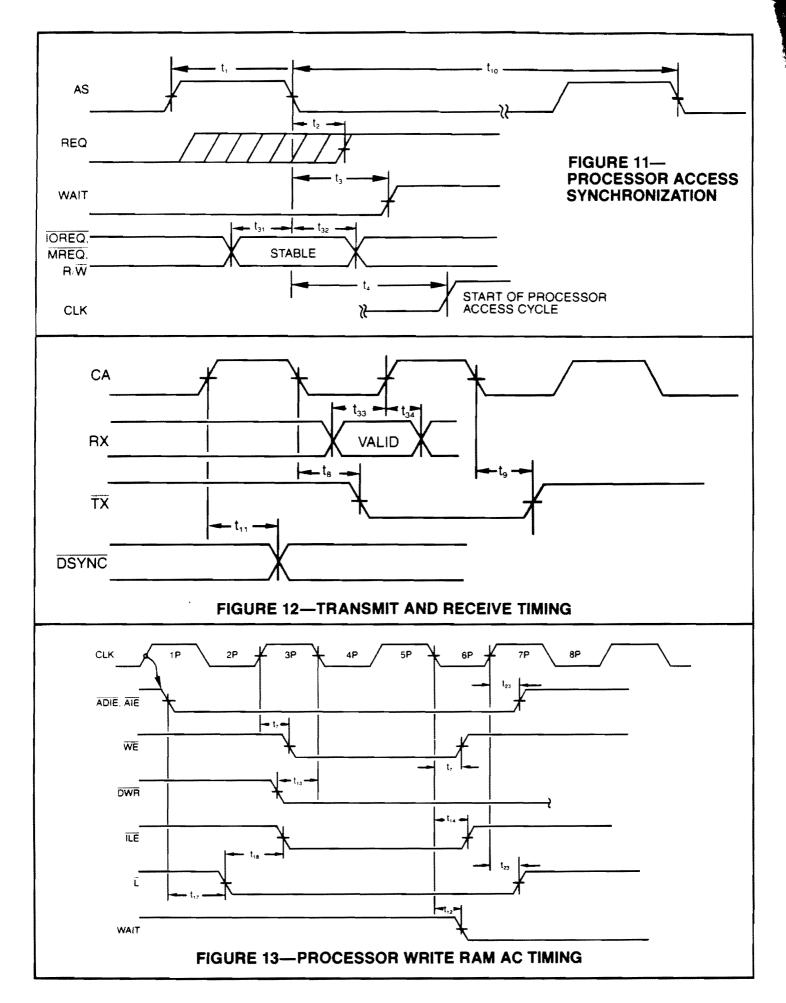

While reading this section refer to Appendix C.O - ARCNET-PC Block Diagram. For a detailed discussion of the COM 9026 refer to the data sheet in Appendix A.O.

#### 7.1 Address Decoding

The ARCNET-PC family is an interface between the IBM Personal computer and the ARCNET modified token passing local area network. The on-board 2K X 8 data packet buffer and 8K X 8 prom are memory mapped in the control system's memory address space, whereas the COM 9026 registers and ARCNET-PC software reset function are IO mapped in the control systems IO address space. Address lines A19 through A16 compare with switches S1-7 through S1-10 to produce signal MREQ\* when a processor cycle requests access to on-board ram or prom.

#### 7.1 Address Decoding cont.

MREQ: is further decoded to produce signals RIM: to access the 9026, RAM: to access the additional 2K X 8 ram, and PROM: to access the 8K X 8 prom. The COM 9026 receives signal RIM: and produces all bus controlling signals to allow the processor synchronized access to the data packet buffer.

Address lines A9 through A4 compare with switches S1-1 to S1-6 to produce signal IOREQ\* when a processor cycle requests access to a COM 9026 register, or wishes to perform an ARCNET-PC software reset. Signal IOREQ\* is decoded further to produce signals RIOREQ\* to access the COM 9026 registers and RESREQ\* to access the ARCNET-PC software reset circuitry. The COM 9026 receives signal RIOREQ\* and produces all bus controlling signals to allow the processor synchronized access to COM 9026 registers. RESREQ\* enables a oneshot timer, of approximately 200 milliseconds, to reset the COM 9026 and COM 9032 under software control. While RESREQ\* is active, the processor should not try to access COM 9026 Registers or the Data Packet Buffer.

### 7.2 Internal Address-Data Bus

All gating of address and data on the internal bus (IAIO through IA8 and IAD7 through IADO) is controlled by the COM 9026. For detailed timing specifications are appendix A.O. Signals ADIE\* and ILE\* allow chips A10 and A27 (74LS244) to gate lower address and data respectively onto the internal bus. Signals WAIT, R/W\*, RIOREO\*, and RIM\* allow data on the internal bus to be driven onto the IBM bus by A26 (74LS373). Signal AIE\* allows address lines A10 through A8 to address the rem buffer.

### 7.3 Wait State Generator

The CON 9026 effects arbitration and synchronous access to the data packet buffer and CON 9026 registers through the use of the I/O CHRDY line. The CON 9026 asserts signal WAIT at the start of a processor 7.3 Wait State Generator cont.

access cycle to indicate it is not ready to transfer data. WAIT asserts I/O CHRDY to produce processor wait cycles. Signals IOREQand MREQ- using A8 (74LS175), A1 (74LS00), and A-25 (7406) assure proper synchronizing of the I/O CHRDY signal. The COM 9026 returns WAIT to its inactive state when it is ready for the processor to complete its cycle.

#### 7.4 Interrupts

The ARCNET-PC Interrupt Circuit consists of jumpers JP1 through JP7, and elements of A24 (74LS244). The COM 9026 is capable of asserting signal INTR when certain status bits become true. A write to the COM 9026 MASK register specifies which status bits can generate the interrupt. Jumpers JP1 through JP5 connect signal INTR to interrupt lines IR07 and IR05 through IR02.

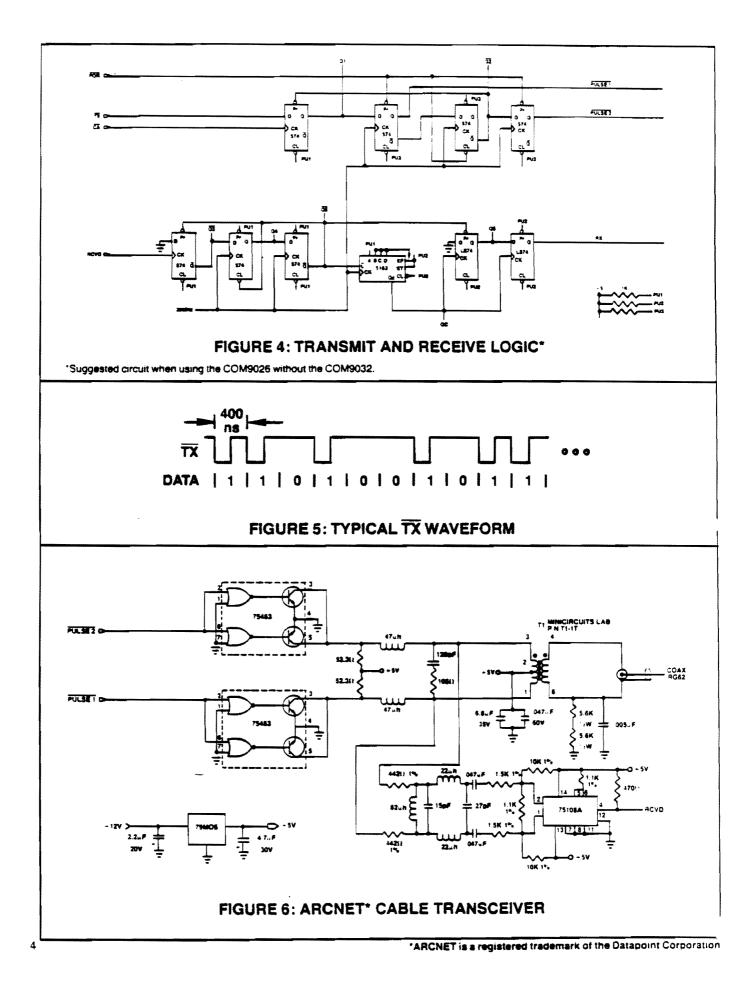

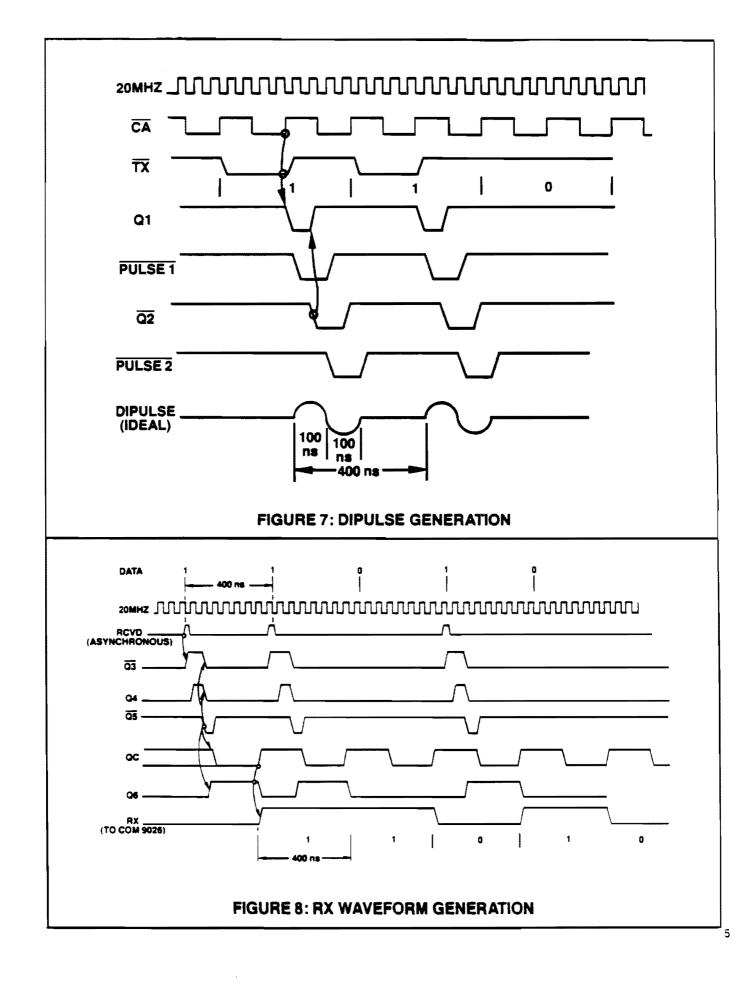

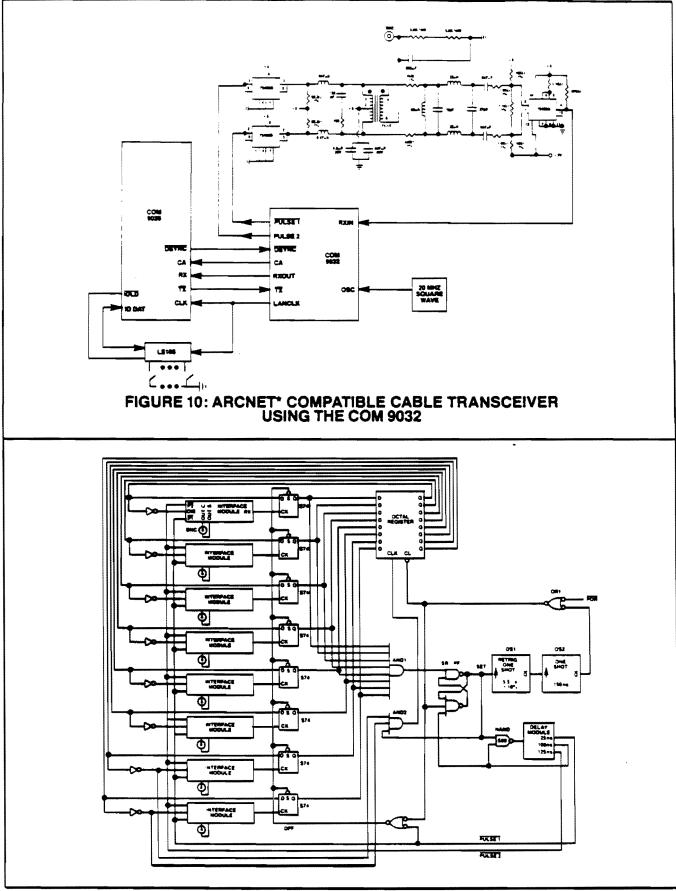

#### 7.5 Cable Transceiver

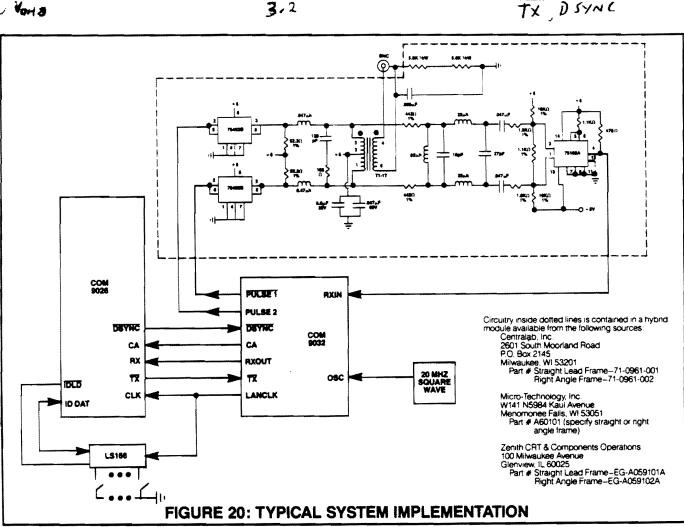

The cable transceiver consists of the CON 9032, either the SMC HYC9058 or SMC HYC9068 hybird coaxiel driver, and BNC connector J1. The cable transceivers function is to convert TX pulses from the COM 9026 to a format required by Datapoint ARCNET local area network specifications, and also to convert signals from the cable to NRZ data required by the COM 9026 RX input. The Datapoint ARCNET implementation uses a baseband system with RG62/U (93 ohm) coax. For a detailed discussion of this implementation, see Appendix B.O.

#### 8.0 PROGRAMMING CONSIDERATIONS

For a description of basic COM 9026 programming considerations, refer to Technical Note TN5-2, Appendix B.O, section titled Programming the COM 9026.

When using the ARCNET-PC software reset function, an IO read or IO write to IO location XX8H, where XX values are determined by IO address selection switches, will produce approximately a 200 millisecond reset of the COM 9026 and COM 9032. During the time these devices are being reset, the processor should not access COM 9026 registers or the Data Packet Buffer.

# COM 9026

# Local Area Network Controller LANC<sup>™</sup>

# FEATURES

- 2.5 M bit data rate

- ARCNET local area network controller

- C Modified token passing protocol

- Self-reconfiguring as nodes are added or deleted from network

- Handles variable length data packets

- 16 bit CRC check and generation

- System efficiency increases with network loading

- Standard microprocessor interface

- Supports up to 255 nodes per network segment

- Ability to interrupt processor at conclusion of commands

- Interfaces to an external 1K or 2K RAM buffer

- Arbitrates buffer accesses between processor and COM 9026

- Replaces over 100 MSI/SSI parts

- C Ability to transmit broadcast messages

- Compatible with broadband or baseband systems

- Compatible with any interconnect media (twisted pair, coax, etc.)

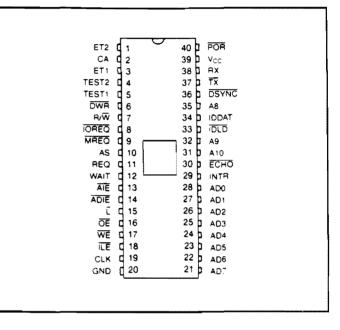

# **PIN CONFIGURATION**

Arbitrary network configurations can be used (star, tree, etc.)

$\Box$  Single + 5 volt supply

# **GENERAL DESCRIPTION**

The COM 9026 is a special purpose communications adapter for interconnecting processors and intelligent peripherals using the ARCNET local area network. The ARCNET local area network is a self-polling "modified token passing" network operating at a 2.5 M bit data rate. A "modified token passing" scheme is one in which all token passes are acknowledged by the node accepting the token. The token passing network scheme avoids the fluctuating channel access times caused by data collisions in so-called CSMA/ CD schemes such as Ethernet.

The COM 9026 circuit contains a microprogrammed sequencer and all the logic necessary to control the token passing mechanism on the network and send and receive data packets at the appropriate time. A maximum of 255 nodes may be connected to the network with each node being assigned a unique ID. The COM 9026 establishes the network configuration, and automatically re-configures the network as new nodes are added or deleted from the network. The COM 9026 performs address decode, CRC checking and generation, and packet acknowledgement, as well as other network management functions. The COM 9026 interfaces directly to the host processor through a standard multiplexed address/ data bus.

An external RAM buffer of up to 2K locations is used to hold up to four data packets with a maximum length of 508 bytes per message. The RAM buffer is accessed both by the processor and the COM 9026. The processor can write commands to the COM 9026 and also read COM 9026 status. The COM 9026 will provide all signals necessary to allow smooth arbitration of all RAM buffer operations.

\*ARCNET is a registered trademark of the Datapoint Corporation.

# DESCRIPTION OF PIN FUNCTIONS (refer to figure 2)

| PIN NO.                              | NAME                                    | SYMBOL      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------|-----------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31, 32, 35                           | ADDRESS 10,<br>9, 8                     | A10, A9, A8 | These three output signals are the three most significant bits of the RAM buffer address. These signals are in their high impedance state except during COM 9026 access cycles to the RAM buffer. A10 and A9 will take on the value nn as specified in the ENABLE RECEIVE or ENABLE TRANSMIT commands to or from page nn and should be viewed as page select bits. For packets less than 256 bytes a 1K buffer can be used with A8 unconnected. For packets greater than 256 bytes, a 2K buffer is needed with A8 connected. |

| 21, 22, 23,<br>24, 25, 26,<br>27, 28 | ADDRESS<br>DATA 7-0                     | AD7-AD0     | These 8 bidirectional signals are the lower 8 bits of the RAM buffer address and the 8 bit data path in and out of the COM 9026. AD0 is also used for I/O command decoding of the processor control or status commands to the COM 9026.                                                                                                                                                                                                                                                                                      |

| 8                                    | I/O REQUEST                             | IOREQ       | This input signal indicates that the processor is requesting the use of the data bus to receive status information or to issue a command to the COM 9026. This signal is sampled internally on the falling edge of AS.                                                                                                                                                                                                                                                                                                       |

| 9                                    | MEMORY<br>REQUEST                       | MREQ        | This input signal indicates that the processor is requesting the use of the data bus to transfer data to or from the RAM buffer. This signal is sampled internally on the falling edge of AS.                                                                                                                                                                                                                                                                                                                                |

| 7                                    | READ/WRITE                              | R∕₩         | A high level on this input signal indicates that the processor's access cycle to the COM 9026 or the RAM buffer will be a read cycle. A low level indicates that a write cycle will be performed to either the RAM buffer or the COM 9026. The write cycle will not be completed, however, until the DWR input is asserted. This signal is an internal transparent latch gated with AS.                                                                                                                                      |

| 10                                   | ADDRESS<br>STROBE                       | AS          | This input signal is used by the COM 9026 to sample the state of the IOREQ.<br>MREQ and R/W inputs. The COM 9026 bus arbitration is initiated on the failing<br>edge of this signal.                                                                                                                                                                                                                                                                                                                                         |

| 11                                   | REQUEST                                 | REQ         | This output signal acknowledges the fact that the processor's $I/Q$ or memory cycle has been sampled. The signal is equal to MREQ or IOREQ passed through an internal transparent latch gated with AS.                                                                                                                                                                                                                                                                                                                       |

| 12                                   | WAIT                                    | WAIT        | This output signal is asserted by the COM 9026 at the start of a processor access cycle to indicate that it is not ready to transfer data. WAIT returns to its inactive state when the COM 9026 is ready for the processor to complete its cycle.                                                                                                                                                                                                                                                                            |

| 6                                    | DELAYED<br>WRITE                        | DWR         | This input signal informs the COM 9026 that valid data is present on the proces-<br>sor's data bus for write <u>cvcles</u> . The COM 9026 will remain in the WAIT state until<br>this signal is asserted. DWR has no effect on read cycles. If the processor is able<br>to satisfy the write data setup time, it is recommended that this signal be<br>grounded.                                                                                                                                                             |

| 29                                   | INTERRUPT<br>REQUEST                    | INTR        | This output signal is asserted when an enabled interrupt condition has occured.<br>INTR returns to its inactive state by resetting the interrupting status condition or the corresponding interrupt mask bit.                                                                                                                                                                                                                                                                                                                |

| 18                                   | INTERFACE<br>LATCH<br>ENABLE            | ILE         | This output signal, in conjunction with ADIE, gates the processor's address/data<br>bus (PAD7-PAD0) onto the interface address/data bus (IAD7-IAD0) during the<br>data valid portion of a Processor Write RAM or Processor Write COM 9026<br>operation.                                                                                                                                                                                                                                                                      |

| 14                                   | ADDRESS/<br>DATA INPUT<br>ENABLE        | ADIE        | This output signal enables the processor's address/data bus (PAD7-PAD0) cap-<br>tured by AS or ILE onto the interface address/data bus (IAD7-IAD0).                                                                                                                                                                                                                                                                                                                                                                          |

| 13                                   | ADDRESS<br>INPUT<br>ENABLE              | AIE         | This output signal enables the processor's upper 3 address bits (PA10-PA8) onto the interface address bus (IA10-IA8).                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15                                   | LATCH                                   | L           | This output signal latches the interface address/data bus (IAD7-IAD0) into a latch which feeds the lower 8 address bits of the RAM buffer during address valid time of all RAM buffer access cycles.                                                                                                                                                                                                                                                                                                                         |

| 17                                   | WRITE                                   | WE          | This output signal is used as a <u>write pulse</u> to the external RAM buffer. Data is ref-<br>erenced to the trailing edge of WE.                                                                                                                                                                                                                                                                                                                                                                                           |

| 16                                   | OUTPUT<br>ENABLE                        | ÔĒ          | This output signal enables the RAM buffer output data onto the interface address/data bus (IAD7-IAD0) during the data valid portion of all RAM buffer read operations.                                                                                                                                                                                                                                                                                                                                                       |

| 33                                   | ID LOAD                                 | ĪDLD        | This output signal synchronously loads the value selected by the ID switches into<br>an external shift register in preparation for shifting the ID into the COM 9026. The<br>shift register is clocked with the same signal that feeds the COM 9026 on pin 19<br>(CLK). The timing associated with this signal and IDDAT (pin 34) is illustrated in<br>figure 19.                                                                                                                                                            |

| 34                                   | ID DATA IN                              | IDDAT       | This input signal is the serialized output from the external ID shift register. The ID is shifted in most significant bit first. A high level is defined as a logic "1".                                                                                                                                                                                                                                                                                                                                                     |

| 1, 3                                 | EXTENDED<br>TIMEOUT<br>FUNCTION 2,<br>1 | ET2, ET1    | The levels on these two input pins specify the timeout durations used by the COM 9026 in its network protocol. Refer to the section entitled "Extended Timeout Function" for details.                                                                                                                                                                                                                                                                                                                                        |

| 37                                   | TRANSMIT<br>DATA                        | TX          | This output signal contains the serial transmit data to the CABLE TRANSCEIVER.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 38                                   | RECEIVE<br>DATA                         | RX          | This input signal contains the serial receive data from the CABLE TRANSCEIVER.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# **DESCRIPTION OF PIN FUNCTIONS (Continued)**

| PIN NO. | NAME                         | SYMBOL          | FUNCTION                                                                                                                                                                                                                                                                                                      |

|---------|------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4, 5    | TEST PIN 2<br>TEST PIN 1     | TEST2<br>TEST1  | These input pins are grounded for normal chip operation. These pins are used in<br>conjunction with ET2 and ET1 to enable various internal diagnostic functions<br>when performing chip level testing.                                                                                                        |

| 30      | ECHO<br>DIAGNOSTIC<br>ENABLE | ECHO            | When this input signal is low, the COM 9026 will re-transmit all messages of length less than 254 bytes. This input should be tied high for normal chip operation and is only utilized when performing chip level testing.                                                                                    |

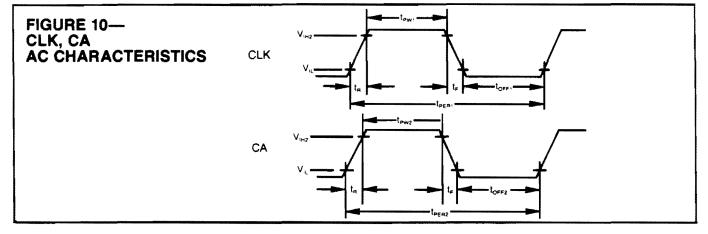

| 19      | CLOCK                        | CLK             | A continuous 5 MHz clock input used for timing of the COM 9026 bus cycles, bus arbitration, serial ID input, and the internal timers.                                                                                                                                                                         |

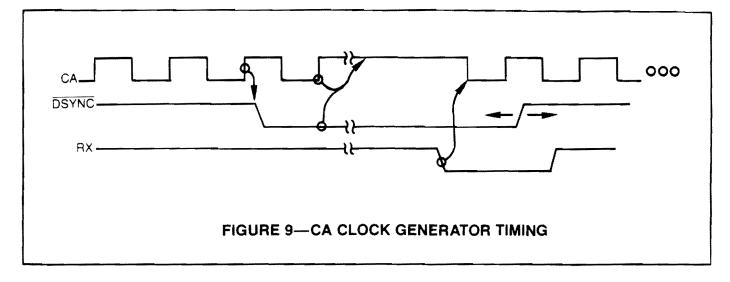

| 2       | CA                           | CA              | This input signal is a 5 MHz clock used to control the operation of the COM 9026<br>microcoded sequencer. This input is periodically halted in the high state by the<br>DSYNC output.                                                                                                                         |

| 36      | DELAYED<br>SYNC              | DSYNC           | This output signal is asserted by the COM 9026 to cause the external clock gen-<br>erator logic to halt the CA clock. Refer to figure 9.                                                                                                                                                                      |

| 40      | POWER ON<br>RESET            | POR             | This input signal clears the COM 9026 microcoded sequencer program counter to zero and initializes various internal control flags and status bits. The POR status bit is also set which causes the INTR output to be asserted. Repeated assertion of this signal will degrade the performance of the network. |

| 39      | + 5 VOLT<br>SUPPLY           | V <sub>cc</sub> | Power Supply                                                                                                                                                                                                                                                                                                  |

| 20      | GROUND                       | GND             | Ground                                                                                                                                                                                                                                                                                                        |

# **PROTOCOL DESCRIPTION**

# LINE PROTOCOL DESCRIPTION

The line protocol can be described as isochronous because each byte is preceded by a start interval and ended with a stop interval. Unlike asynchronous protocols, there is a constant amount of time separating each data byte. Each byte will take up exactly 11 clock intervals with a single clock interval being 400 nanoseconds in duration. As a result, 1 byte is transmitted every 4.4 microseconds and the time to transmit a message can be exactly determined. The line idles in a spacing (logic 0) condition. A logic '0' is defined as no line activity and a logic 1 is defined as a pulse of 200 nanoseconds duration. A transmission starts with an ALERT BURST consisting of 6 unit intervals of mark (logic 1). Eight bit data characters are then sent with each character preceded by 2 unit intervals of mark and one unit interval of space. Five types of transmission can be sent as described below:

# Invitations To Transmit

An ALERT BURST followed by three characters; an EOT (end of transmission—ASCII code 04 HEX) and two (repeated) DID (Destination IDentification) characters. This message is used to pass the token from one node to another.

# **Free Buffer Enquiries**

An ALERT BURST followed by three characters; an ENQ (ENQuiry—ASCII code 05 HEX) and two (repeated) DID (Destination IDentification) characters. This message is used to ask another node if it is able to accept a packet of data.

# **Data Packets**

An ALERT BURST followed by the following characters:

- an SOH (start of header-ASCII code 01 HEX)

- -a SID (Source IDentification) character

- -two (repeated) DID (destination IDentification) characters.

- —a single COUNT character which is the 2's complement of the number of data bytes to follow if a 'short packet'' is being sent or 00 HEX followed by a COUNT character which is the 2's complement of the number

- of data bytes to follow if a "long packet" is being sent. ----N data bytes where COUNT = 256-N (512-N for a "long packet")

- two CRC (Cyclic Redundancy Check) characters. The CRC polynomial used is X<sup>16</sup> + X<sup>15</sup> + X<sup>2</sup> + 1.

# Acknowledgements

An ALERT BURST followed by one character; an ACK (ACKnowledgement—ASCII code 06 HEX) character. This message is used to acknowledge reception of a packet or as an affirmative response to FREE BUFFER ENQUIRIES.

# **Negative Acknowledgements**

An ALERT BURST followed by one character; a NAK (Negative AcKnowledgement—ASCII code 15 HEX). This message is used as a negative response to FREE BUFFER ENQUIRIES.

# **NETWORK PROTOCOL DESCRIPTION**

Communication on the network is based on a "modified token passing" protocol. A "modified token passing" scheme is one in which all token passes are acknowledged by the node receiving the token. Establishment of the network configuration and management of the network protocol are handled entirely by the COM 9026's internal microcoded sequencer. A processor or intelligent peripheral transmits data by simply loading a data packet and its destination ID into the RAM buffer, and issuing a command to enable the transmitter. When the COM 9026 next receives the token, it verifies that the receiving node is ready by first transmitting a FREE BUFFER ENQUIRY message. If the receiving node transmits an ACKnowledge message, the data packet is transmitted followed by a 16 bit CRC. If the receiving node cannot accept the packet (typically its receiver is inhibited), it transmits a Negative AcKnowledge message and the transmitter passes the token. Once it has been established that the receiving node can accept the packet and transmission is complete, the receiving node will verify the packet.

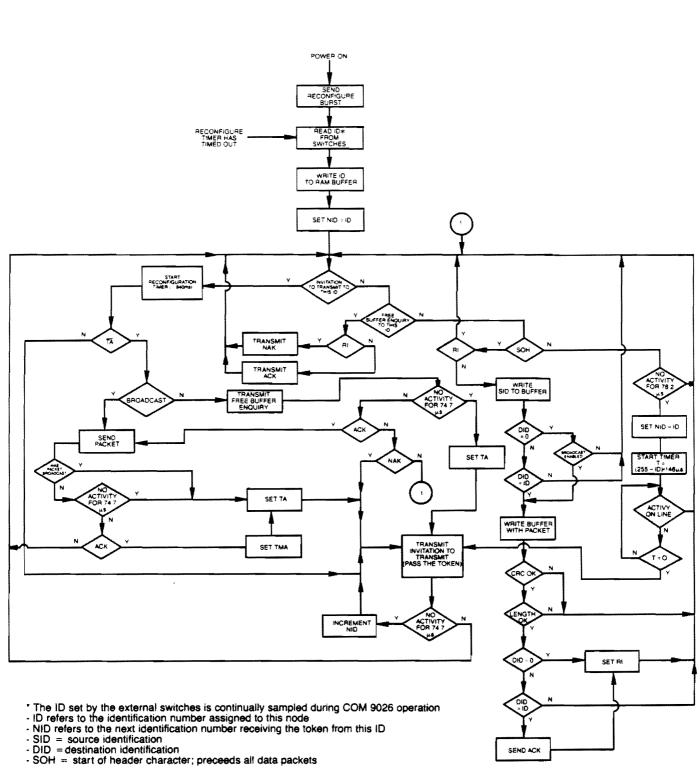

If the packet is received successfully, the receiving node transmits an acknowledge message (or nothing if it is received unsuccessfully) allowing the transmitter to set the appropriate status bits to indicating successful or unsucessful delivery of the packet. An interrupt mask permits the COM 9026 to generate an interrupt to the processor when selected status bits become true. Figure 3 is a flow chart illustrating the internal operation of the COM 9026.

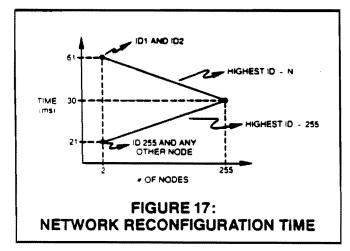

# NETWORK RECONFIGURATION

A significant advantage of the COM 9026 is its ability to adapt to changes on the network. Whenever a new node is activated or deactivated a NETWORK RECONFIGURATION is performed. When a new COM 9026 is turned on (creating a new active node on the network), or if the COM 9026 has not received an INVITATION TO TRANSMIT for 840 milliseconds, it causes a NETWORK RECONFIGURATION by sending a RECONFIGURE BURST consisting of eight marks and one space repeated 765 times. The purpose of this burst is to terminate all activity on the network. Since this burst is longer than any other type of transmission, the burst will interfere with the next INVITATION TO TRANSMIT, destroy the token and keep any other node from assuming control of the line. It also provides line activity which allows the COM 9026 sending the INVITATION TO TRANSMIT to release control of the line.

When any COM 9026 sees an idle line for greater than 78.2 microseconds, which will only occur when the token is lost, each COM 9026 starts an internal time out equal to 146 microseconds times the quantity 255 minus its own ID. It also sets the internally stored NID (next ID representing the next possible ID node) equal to its own ID. If the timeout expires with no line activity, the COM 9026 starts sending INVITATIONS TO TRANSMIT with the DID equal to the currently stored NID. Within a given network, only one COM 9026 will timeout (the one with the highest ID number). After sending the INVITATION TO TRANSMIT, the COM 9026 waits for activity on the line. If there is no activity for 74.7

microseconds, the COM 9026 increments the NID value and transmits another INVITATION TO TRANSMIT using the new NID equal to the DID. If activity appears before the 74.7 microsecond timeout expires, the COM 9026 releases control of the line. During NETWORK RECONFIGURATION, INVITATIONS TO TRANSMIT will be sent to all 256 possible ID's. Each COM 9026 on the network will finally have saved a NID value equal to the ID of the COM 9026 that assumed control from it. From then until the next NET-WORK RECONFIGURATION, control is passed directly from one node to the next with no wasted INVITATIONS TO TRANSMIT sent to ID's not on the network. When a node is powered off, the previous node will attempt to pass it the token by issuing an INVITATION TO TRANSMIT. Since this node will not respond, the previous node will time out and transmit another INVITATION TO TRANSMIT to an incremented ID and eventually a response will be received.

The time required to do a NETWORK RECONFIGURA-TION depends on the number of nodes in the network, the propogation delay between nodes and the highest ID number on network but will be in the range of 24 to 61 milliseconds.

# **BROADCAST MESSAGES**

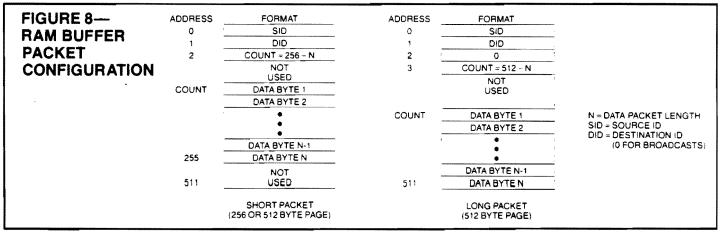

Broadcasting gives a particular node the ability to transmit a data packet to all nodes on the network simultaneously. ID zero is reserved for this feature and no node on the network can be assigned ID zero. To broadcast a message, the transmitting node's processor simply loads the RAM buffer with the data packet and sets the destination ID (DID) equal to zero. Figure 8 illustrates the position of each byte in the packet with the DID residing at address 01 HEX of the current page selected in the TRANSMIT command. Each individual node has the ability to ignore broadcast messages by setting the most significant bit of the ENABLE RECEIVE TO PAGE nn command (see "WRITE COM 9026 COMMANDS") to a logic zero.

# **BUFFER CONFIGURATION**

During a transmit sequence, the COM 9026 fetches data from the Transmit Buffer, a 256 (or 512) byte segment of the RAM buffer. The appropriate buffer size is specified in the DEFINE CONFIGURATION command. When long packets are enabled, the COM 9026 will interpret the packet as a long or short packet depending on whether the contents

# COM 9026 OPERATION

of buffer location 02 is zero or non zero. During a receive sequence, the COM 9026 stores data in the receive buffer, also a 256 (or 512) byte segment of the RAM buffer. The processor I/O command which enables either the COM 9026 receiver or the COM 9026 transmitter also initializes the respective buffer page register. The formats of the buffers (both 256 and 512 byte) are shown below.

# FIGURE 3—9026 OPERATION

SEND ACK

# PROCESSOR INTERFACE

Figure 2 illustrates a typical COM 9026 to processor interface. The signals on the left side of this figure represent typical processor signals with a 16 bit address bus and an 8 bit data bus with the data bus multiplexed onto the lower 8 address lines (PAD7-PAD0). The processor sees a network node (a node consists of a COM 9026, RAM buffer, cable transceiver, etc. as shown in figure 2) as 2K memory locations and 4 I/O locations within the COM 9026.

The RAM buffer is used to hold data packets temporarily prior to transmission on the network and as temporary storage of all received data packets directed to the particular node. The size of the buffer can be as large as 2K byte locations providing four pages at a maximum of 512 bytes per page. For packet lengths smaller than 256 bytes, a 1K RAM buffer can be used to provide four pages of storage. In this case address line IA8 (sourced from either the COM 9026 or the processor) should be left unconnected. Since four pages of RAM buffer are provided, both transmit and receive operations can be double buffered with respect to the processor. For instance, after one data packet has been loaded into a particular page within the RAM buffer and a transmit command for that page has been issued, the processor can start loading another page with the next message in a multimessage transmission sequence. Similarly, after one message is received and completely loaded into one page of the RAM buffer by the COM 9026, another receive command can be issued to allow reception of the next packet while the first packet is read by the processor. In general, the four pages in the RAM buffer can be used for transmit or receive in any combination. In addition, the processor will also use the interface bus (IA10-IA8, IAD7-IAD0) when performing I/O access cycles (status reads from the COM 9026 or command writes to the COM 9026).

To accomplish this double buffering scheme, the RAM buffer must behave as a dual port memory. To allow this RAM to be a standard component, arbitration and control on the interface bus (IA10-IA8, IAD7-IAD0) is required to permit both the COM 9026 and the processor access to the RAM buffer and, at the same time, permit all processor I/O operations to or from the COM 9026.

Processor access cycle requests begin on the trailing edge of AS if either IOREQ or MREQ is asserted. These access cycles run completely asynchronous with respect to the COM 9026. Because of this, upon processor access cycle requests, the COM 9026 immediately puts the processor into a wait state by asserting the WAIT output. This gives the COM 9026 the ability to synchronize and control the processor access cycle. When the processor access cycle is synchronized by the COM 9026, the WAIT signal is eventually removed allowing the processor to complete its cycle.

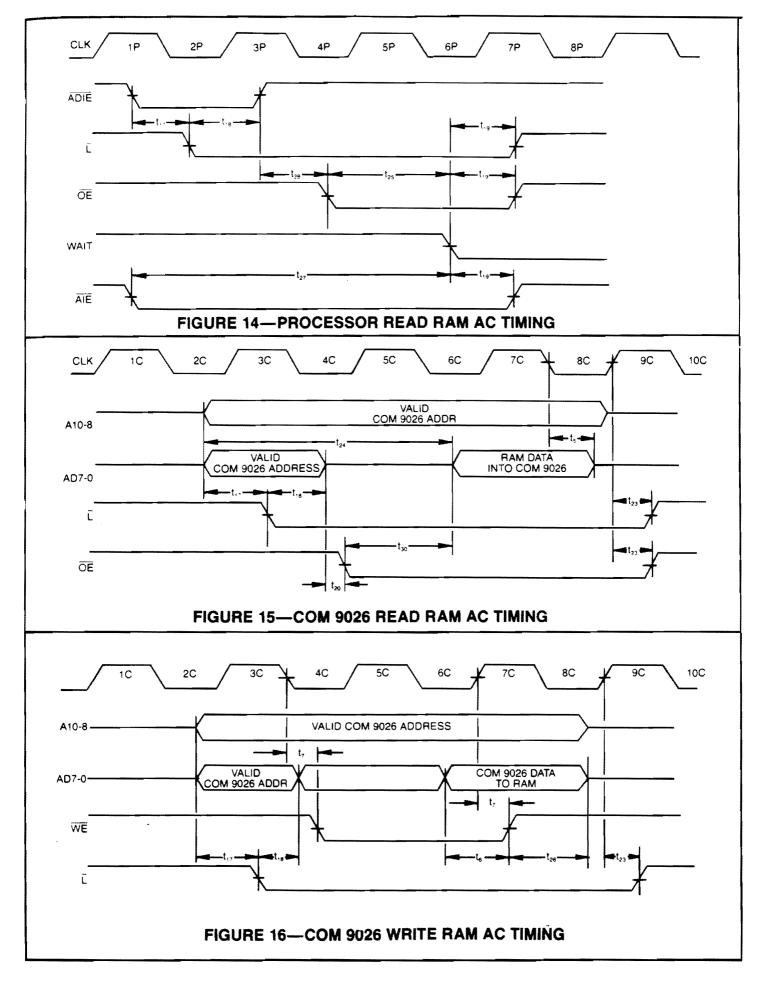

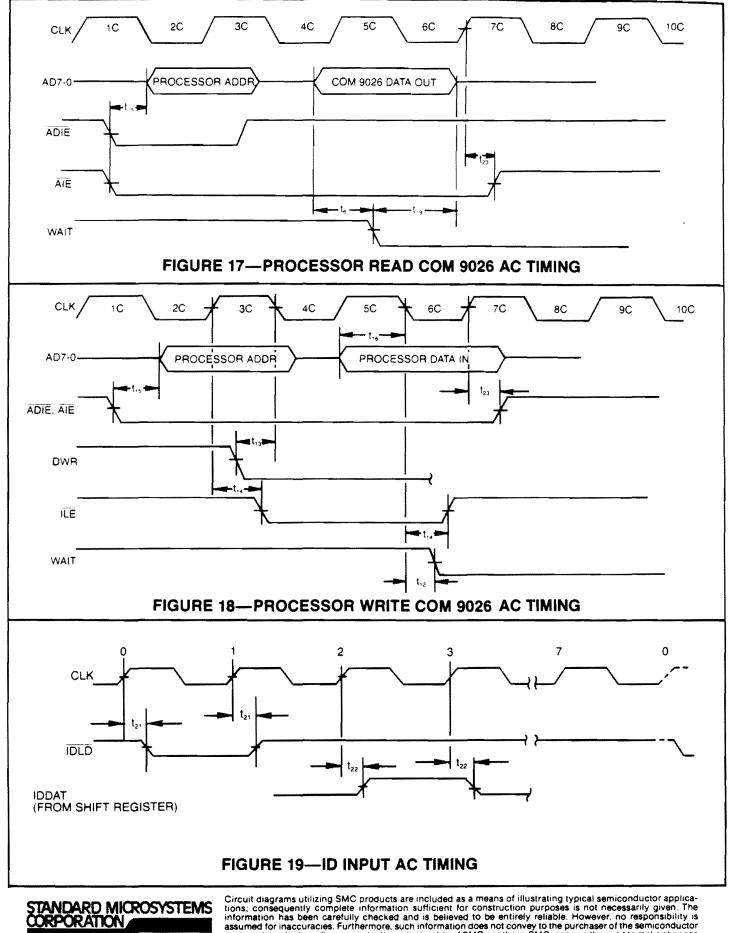

For processor RAM buffer access cycles,  $\overline{AIE}$  and  $\overline{ADIE}$ enable the processor address captured during AS time onto the interface address bus (IA10-IA8, IAD7-IAD0). The signal  $\overline{L}$  will capture the 8 least significant bits of this address (appearing on IAD7-IAD0) before the data is multiplexed onto it. At the falling edge of L, a stable address is presented to the RAM buffer. For read cycles,  $\overline{OE}$  allows the addressed RAM buffer data to source the interface address/ data bus (IAD7-IAD0). In figure 2, this information is passed into a transparent latch gated with WAIT. At the falling edge of WAIT, the data accessed by the processor is captured

and driven out via the logic function RD anded with REQ. For processor I/O read cycles from the COM 9026, ADIE and AIE are used to enable the processor address into the COM 9026. Data out of the COM 9026 is gated through the transparent latch and appears on the processor's data bus with the same control signals used for RAM read cycles.

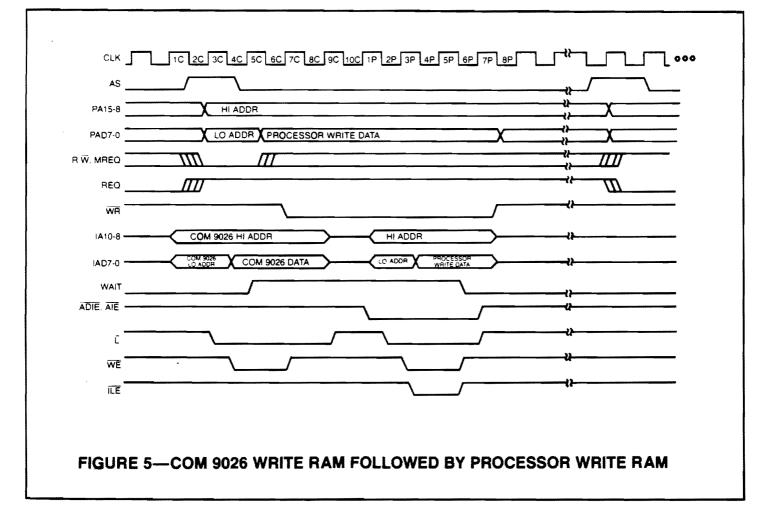

For processor write cycles, after the falling edge of  $\overline{L}$ , the COM 9026 produces a WE (write enable) output to the RAM buffer, and the ILE output from the COM 9026 allows the processor data to source the interface address/data bus (IAD7-IAD0). At this time the COM 9026 waits for DWR before concluding the cycle by removing the WAIT output. DWR should only be used if the processor cannot deliver the data to be written in enough time to satisfy the write setup time requirements of the RAM buffer. By delaying the activation of DWR, the period of the write cycle will be extended until the write data is valid. Since the architecture and operation of the COM 9026 requires periodic reading and writing of the RAM buffer in a timely manner, holding the DWR input off for a long period of time, or likewise by running the processor at a slow speed, can result in a data overflow condition. It is therefore recommended that if the processor write data setup time to the RAM buffer is met, then the DWR input should be grounded.

For processor I/O write cycles to the COM 9026, ADIE and AIE are used to enable the processor's address onto the interface data bus. ILE is used to enable the processor's write data into the COM 9026. Delaying the activation of DWR will hold up the COM 9026 cycle requiring the same precautions as stated for Processor RAM Write cycles.

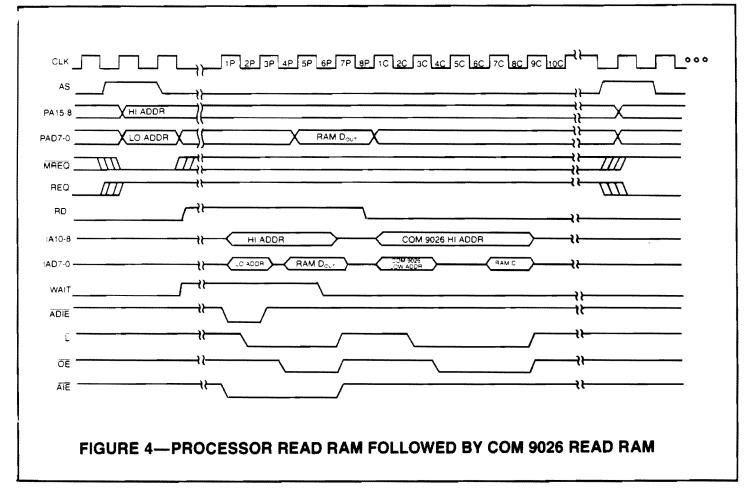

As stated previously, processor requests occur at the falling edge of AS if either IOREQ or MREQ are active. COM 9026 requests occur when the transmitter or receiver need to read or write the RAM buffer in the course of executing the command. If the COM 9026 requests a bus cycle at the same time as the processor, or shortly after the processor. the COM 9026 cycle will follow immediately after the processor cycle. Figure 4 illustrates the timing relationship of a Processor RAM Read cycle followed by a COM 9026 RAM read cycle. Once the AS signal captures the processor address to the RAM buffer and requests a bus cycle, it takes 4 CLK periods for the processor cycle to end. Figure 4 breaks up these 4 CLK periods into 8 half clock interval labeled 1P through 8P. A COM 9026 access cycle will take 5 CLK periods to end. Figure 4 breaks up these 5 CLK periods into 10 half intervals labeled 1C through 10C.

If a processor cycle request occurs after a COM 9026 request has already been granted, the COM 9026 cycle will occur first, as shown in figure 5. Figure 5 illustrates the timing relationship of a COM 9026 RAM Write cycle followed by a Processor RAM Write cycle. Due to the asynchronous nature of the bus requests (AS and CLK), the transition from the end of the COM 9026 cycle to the beginning of the processor cycle might have some dead time. Refering to figure 5. if AS falling edge occurs after the start of half CLK interval 9C, no real contention exists and it will take between 200 and 500 nanoseconds before the processor cycle can start. The start of the processor cycle is defined as the time when the COM 9026 produces a leading edge on both ADIE and AIE. If the processor request occurs before the end of half

CLK interval 5C (figure 5 illustrates this situation), then the processor cycle will always start at half CLK interval 1P. The uncertainty is introduced when the processor request occurs during half CLK intervals 6C, 7C or 8C. In this case, the processor cycle will start between 200 and 500 nanoseconds later depending on the particular timing relation between AS and CLK. The maximum time between processor request and processor cycle start, which occurs when the processor request comes just after a COM 9026 request, is 1300 nanoseconds. It should be noted that all times specified above assume a nominal CLK period of 200 nanoseconds.

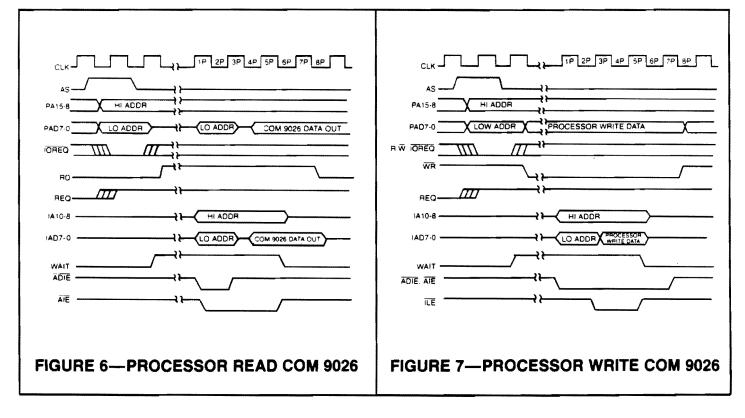

Figures 6 and 7 illustrate timing for Processor Read COM 9026 and Processor Write COM 9026 respectively. These cycles are also shown divided into 8 half clock intervals (1P through 8P) and can be inserted within figures 4 and 5 if these processor cycles occur.

# POWER UP AND INITIALIZATION

The COM has the following power up requirements:

- 1—The POR input must be active for at least 100 milliseconds.

- 2—The CLK input must run for at least 10 clock cycles before the POR input is removed.

- 3—While POR is asserted, the CA input may be running or held high. If the CA input is running, POR may be released asynchronously with respect to CA. If the CA input is held high, POR may be released before CA begins running.

During POR the status register will assume the following state:

BIT 7 (RI) set to a logic "1". BIT 6 (ETS2) not affected BIT 5 (ETS1) not affected BIT 4 (POR) set to a logic "1". BIT 3 (TEST) set to a logic "0". BIT 2 (RECON) set to a logic "0". BIT 1 (TMA) set to a logic "0". BIT 0 (TA) set to a logic "1".

In addition the DSYNC output is reset inactive high and the interrupt mask register is reset (no maskable interrupts enabled). Page 00 is selected for both the receive and the transmit RAM buffer. After the POR signal is removed, the COM 9026 will generate an interrupt from the nonmaskable Power On Reset interrupt. The COM 9026 will start operation four CA clock cycles after the POR signal is removed. At this time, the COM 9026, after reading its ID from the external shift register, will execute two write cycles to the RAM buffer. Address 00 HEX will be written with the data D1 HEX and address 01 HEX will be written with the ID number as previously read from the external shift register. The processor may then read RAM buffer address 01 to determine the COM 9026 ID. It should be noted that the data pattern D1 written into the RAM has been chosen arbitrarily. Only if the D1 pattern appears in the RAM buffer can proper operation be assured.

# **CLOCK GENERATOR**

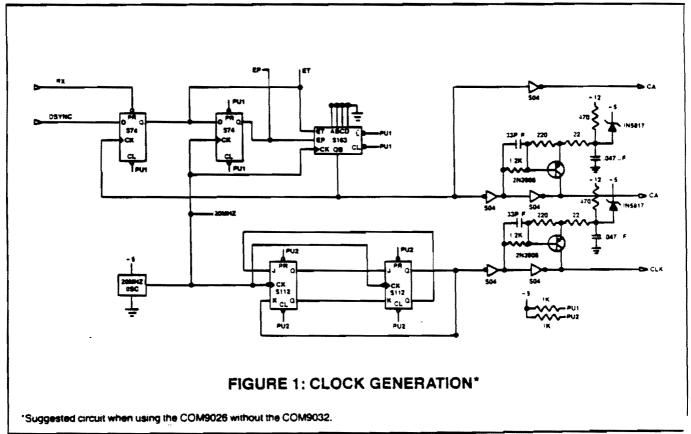

The COM 9026 uses two separate clock inputs namely CA and CLK. The CLK input is a 5 MHz free running clock and the CA input is a start/stop clock periodically stopped and started to allow the COM 9026 to synchronize to the incoming data that appears on the RX input.

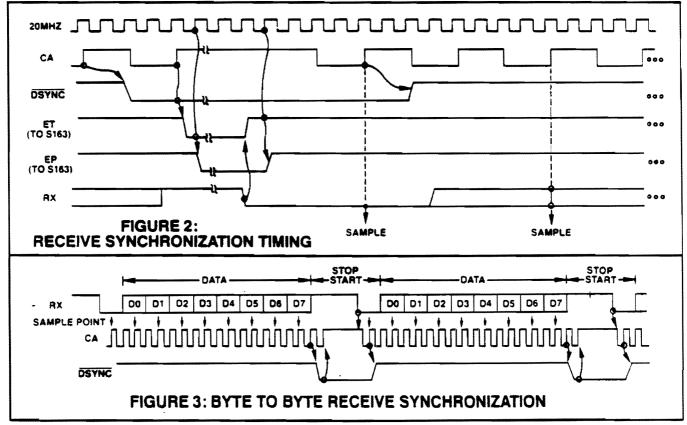

Figure 9 illustrates the timing of the CA clock generator and its relationship to the DSYNC output and the RX input. The DSYNC output is used to control the stopping of the CA clock. On the next rising edge of the CA input after DSYNC is asserted, CA will remain in the high state. The CA clock remains halted in the high state as long as the RX signal remains high. When the RX signal goes low, the CA clock is restarted and remains running until the next falling edge of DSYNC. (See figure 20 for an implementation of this circuit.)

# EXTENDED TIMEOUT FUNCTION

There are three timeouts associated with the COM 9026 operation.

## **Response Time**

This timeout is equal to the round trip propagation delay between the 2 furthest nodes on the network plus the maximum turn around time (the time it takes a particular COM 9026 to start sending a message in response to a received message) which is known to be 12 microseconds. The round trip propagation delay is a function of the transmission media and network topology. For a typical system using RG62 coax in a baseband system, a one way cable propagation delay of 31 microseconds translates to a distance of about 4 miles. The flow chart in figure 3 uses a value of 74.7 microseconds (31 + 31 + 12 + margin) to determine if any node will respond.

## Idle Time

This time is associated with a NETWORK RECONFIGUR-ATION. Refering to figure 3, during a NETWORK RE-CONFIGURATION one node will continually transmit INVI-TATIONS TO TRANSMIT until it encounters an active node. Every other node on the network must distinguish between this operation and an entirely idle line. During NETWORK RECONFIGURATION, activity will appear on the line every 78 microseconds. This 78 microsecond is equal to the response time of 74.7 microseconds plus the time it takes the COM 9026 to retransmit another message (usually another INVITATION TO TRANSMIT). The actual timeout is set to 78.2 microseconds to allow for margin.

# **Reconfiguration Time**

If any node does not receive the token within this time, the node will initiate a NETWORK RECONFIGURATION.

The ET2 and ET1 inputs allow the network to operate over longer distances than the 4 miles stated earlier. DC levels on these inputs control the maximum distances over which the COM 9026 can operate by controlling the 3 timeout values described above. Table 1 illustrates the response time and reconfiguration time as a function of the ET2 and ET1 inputs. The idle time will always be equal to the response time plus 3.5 microseconds. It should be noted that for proper **network** operation, all COM 9026's connected to the same network must have the same response time, idle time and reconfiguration time.

| ET2 | ET1 | RESPONSE<br>TIME (μs) | RECONFIGURATION<br>TIME (ms) |

|-----|-----|-----------------------|------------------------------|

| 1   | 1   | 74.7                  | 840                          |

| 1   | 0   | 283.4                 | 1680                         |

| 0   | 1   | 561.8                 | 1680                         |

| 0   | 0   | 1118.6                | 1680                         |

# TABLE 1 COM 9026 INTERNAL PROGRAMMABLE TIMER VALUES

# I/O COMMANDS

I/O commands are executed by activating the  $\overline{IOREQ}$  input. The COM 9026 will interrogate the AD0 and the R W inputs at the AS time to execute commands according to the following table:

| IOREQ | AD0  | R/W  | FUNCTION                |   |

|-------|------|------|-------------------------|---|

| low   | low  | low  | write interrupt mask    |   |

| low   | low  | high | read status register    |   |

| low   | high | low  | write COM 9026 command  | i |

| low   | high | high | reserved for future use |   |

# **READ STATUS REGISTER**

Execution of this command places the contents of the status register on the data bus (AD7-AD0) during the read portion of the processor's read cycle. The COM 9026 status register contents are defined as follows:

- BIT 7—Receiver inhibited (RI)—This bit, if set high, indicates that a packet has been deposited into the RAM buffer page nn as specified by the last ENABLE RECEIVE TO PAGE nn command. The setting of this bit can cause an interrupt via INTR if enabled during a WRITE INTERRUPT MASK command. No messages will be received until an ENABLE RECEIVE TO PAGE nn command is issued. After any message is received, the receiver is automatically inhibited by setting this bit to a logic one.

- BIT 6—Extended Timeout Status 2 (ETS2)—This bit reflects the current logic value tied to the ET2 input pin (pin 1).

- BIT 5—Extended Timeout Status 1 (ETS1)—This bit reflects the current logic value tied to the ET1 input pin (pin 3).

۱

- BIT 4—Power On Reset (POR)—This bit, if set high, indicates that the COM 9026 has received an active signal on the POR input (pin 40). The setting of this bit will cause a nonmaskable interrupt via INTR.

- BIT 3—Test (TEST)—This bit is intended for test and diagnostic purposes. It will be a logic zero under any normal operating conditions.

- BIT 2—Reconfiguration (RECON)—This bit, if set high, indicates that the reconfiguration timer has timed out because the RX input was idle for 78.2 microseconds. The setting of this bit can cause an interrupt via INTR if enabled by the WRITE INTERRUPT MASK command. The bit is reset low during a CLEAR FLAGS command.

- BIT 1—Transmit Message Acknowledged (TMA)—This bit. if set high, indicates that the packet transmitted as a result of an ENABLE TRANSMIT FROM PAGE nn command has been positively acknowledged. This bit should only be considered valid after the TA bit (bit 0) is set. Broadcast mesages are never acknowledged.

- BIT 0—Transmitter Available (TA)—This bit, if set high, indicates that the transmitter is available for transmitting. This bit is set at the conclusion of a ENA-BLE TRANSMIT FROM PAGE nn command or upon the execution of a DISABLE TRANSMITTER command. The setting of this bit can cause an interrupt via INTR if enabled by the WRITE INTERRUPT MASK command.

# WRITE INTERRUPT MASK

The COM 9026 is capable of generating an interrupt signal when certain status bits become true. A write to the MASK register specifies which status bits can generate the interrupt. The bit positions in the MASK register are in the same position as their corresponding status bits in the STATUS register with a logic one in a bit position enabling the corresponding interrupt. The setting of the TMA, EST1, and EST2 status bits will never cause an interrupt. The POR status bit will cause a non-maskable interrupt regardless of the value of the corresponding MASK register bit. The MASK register takes on the following bit definition:

| BIT 7              | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2          | BIT 1 | BIT 0                    |

|--------------------|-------|-------|-------|-------|----------------|-------|--------------------------|

| RECEIVE<br>INHIBIT | xxx   | xxx   | xxx   | xxx   | RECON<br>TIMER | xxx   | TRANSMITTER<br>AVAILABLE |

The three maskable status bits are anded with their respective mask bits, and the results, along with the POR status bit, are or'ed to produce the processor interrupt signal INTR. This signal returns to its inactive low state when the interrupting status bit is reset to a logic "0" or when the corresponding bit in the MASK register is reset to a logic "0". To clear an interrupt generated as a result of a Power On Reset or Reconfiguration occurance, the CLEAR FLAGS command should be used. To clear an interrupt generated as a result of a completed transmission (TA) or a completed reception (RI), the corresponding masks bits should be reset to a logic zero.

# WRITE COM 9026 COMMANDS

Execution of the following commands are initiated by performing a processor I/O write with the written data defining the following commands:

| WRITTEN DATA | COMMAND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00000000     | reserved for future use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0000001      | DISABLE TRANSMITTER—This command will cancel any pending transmit command<br>(transmission has not yet started) when the COM 9026 next receives the token. This com-<br>mand will set the TA (Transmitter Available) status bit when the token is received.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 00000010     | DISABLE RECEIVER—This command will cancel any pending receive command. If<br>the COM 9026 is not yet receiving a packet, the RI (Receiver Inhibited) bit will be set<br>the next time the token is received. If packet reception is already underway, reception<br>will run to its normal conclusion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 000nn011     | ENABLE TRANSMIT FROM PAGE nn—This command prepares the COM 9026 to<br>begin a transmit sequence from RAM buffer page nn the next time it receives the<br>token. When this command is loaded, the TA and TMA bits are set to a logic "0". The<br>TA bit is set to a logic one upon completion of the transmit sequence. The TMA bit will<br>have been set by this time if the COM 9026 has received an acknowledgement from<br>the destination COM 9026. This acknowledgement is strictly hardware level which is<br>sent by the receiving COM 9026 before its controlling processor is even aware of<br>message reception. It is also possible for this acknowledgement to get lost due to line<br>errors, etc. This implies that the TMA bit is not a guarantee of proper destination<br>reception. Refer to figure 3 for details of the transmit sequence and its relation to the<br>TA and TMA status bits. |

| b00nn100     | ENABLE RECEIVE TO PAGE nn—This command allows the COM 9026 to receive<br>data packets into RAM buffer page nn and sets the RI status bit to a logic zero. if "b"<br>is a logic "1", the COM 9026 will also receive broadcast transmissions. A broadcast<br>transmission is a transmission to ID zero. The RI status bit is set to a logic one upon<br>successful reception of a message.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0000c101     | DEFINE CONFIGURATION—If c is a logic "1", the COM 9026 will handle short as well as long packets. If c is a logic "0", the COM 9026 will only handle short packets (less than 254 bytes).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 000rp110     | CLEAR FLAGS—If p is a logic "1" the POR status flag is cleared. If r is a logic "I", the<br>RECON status flag is cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

All other combinations of written data are not permitted and can result in incorrect chip and/or network operation.

## **MAXIMUM GUARANTEED RATINGS\***

| Operating Temperature Range                         | ) to 70°C |

|-----------------------------------------------------|-----------|

| Storage Temperature Range                           | to 150°C  |

| Lead Temperature (soldering, 10 seconds)            | + 325°C   |

| Positive Voltage on any pin                         | . +8V     |

| Negative Voltage on any pin, with respect to ground | -0.3V     |

\*Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied.

NOTE: When powering this device from laboratory or system power supplies, it is important that the Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies exhibit voltage spikes or "glitches" on their outputs when the AC power is switched on and off. In addition, voltage transients on the AC power line may appear on the DC output. If this possibility exists, it is suggested that a clamp circuit be used.

ŝ

## DC ELECTRICAL CHARACTERISTICS ( $T_A \approx 0^{\circ}C$ to 70°C, $V_{CC} = 5.0V \pm 5\%$ )

|                   | PARAMETER               | MIN                  | TYP | MAX             | UNITS | COMMENTS                   |

|-------------------|-------------------------|----------------------|-----|-----------------|-------|----------------------------|

| V <sub>n</sub>    | input low voltage       | - 0.3                |     | 0.8             | V     |                            |

| V <sub>IH</sub> , | input high voltage 1    | 2.2                  |     | V <sub>cc</sub> | l V   | except CA and CLK          |

| VIH2              | input high voltage 2    | V <sub>cc</sub> -0.5 |     | 6.5             | V V   | for CA or CLK              |

| Vout              | output low voltage 1    |                      |     | 0.4             | V     | $ l_{0}  = 1.6 \text{ ma}$ |

| Vola              | output low voltage 2    |                      |     | 0.5             | V     | $I_{01} = 2.0 \text{ ma}$  |

| VoH               | output high voltage (1) | 2.4                  |     |                 | V     | except TX, DSYNC           |

| 1                 | input leakage current   |                      |     | ± 10            | μΑ    |                            |

| Č                 | input capacitance       |                      |     | 20              | pf    |                            |

| C <sub>De</sub>   | data bus capacitance    |                      |     | 50              | pf    |                            |

| C                 | all other capacitance   |                      |     | 30              | pf    |                            |

| lcc               | power supply current    |                      |     | 350             | ma    |                            |

| Voriz             |                         | 3.2                  |     |                 |       | TY DSYNC                   |

# AC ELECTRICAL CHARACTERISTICS ( $T_{A} = 0^{\circ}$ to 70°C, $V_{CC} = 5.0V \pm 5\%$ )

\_

|                                    | PARAMETER                                                | MIN                | TYP | MAX                   | UNITS | COMMENTS                               |

|------------------------------------|----------------------------------------------------------|--------------------|-----|-----------------------|-------|----------------------------------------|

| tewn                               | CLK pulse width                                          | 65                 |     |                       | ns    |                                        |

| tPERI                              | OUX and all                                              | 190                | 200 | 600                   | ns    |                                        |