# CRAY Y-MP C90<sup>™</sup> System Programmer Reference Manual

CSM-0500-000

Cray Research Proprietary

Cray Research, Inc.

Any shipment to a country outside of the United States requires a letter of assurance from Cray Research, Inc.

This document is the property of Cray Research, Inc. The use of this document is subject to specific license rights extended by Cray Research, Inc. to the owner or lessee of a Cray Research, Inc. computer system or other licensed party according to the terms and conditions of the license and for no other purpose.

Cray Research, Inc. Unpublished Proprietary Information — All Rights Reserved.

Autotasking, CRAY, Cray Ada, CRAY Y-MP, CRAY-1, HSX, MPGS, SSD, UniChem, UNICOS, and X-MP EA are federally registered trademarks and CCI, CF77, CFT, CFT2, CFT77, COS, CRAY S-MP, CRAY X-MP, CRAY XMS, CRAY-2, Cray C++, Cray/REELlibrarian, CRInform, CRI/TurboKiva, CSIM, CVT, Delivering the power . . ., Docview, IOS, OLNET, RQS, SEGLDR, SMARTE, SUPERCLUSTER, SUPERLINK, and Trusted UNICOS are trademarks of Cray Research, Inc.

Requests for copies of Cray Research, Inc. publications should be directed to:

CRAY RESEARCH, INC. Logistics 6251 South Prairie View Road Chippewa Falls, WI 54729

Comments about this publication should be directed to:

CRAY RESEARCH, INC. Hardware Publications and Training 770 Industrial Blvd. Chippewa Falls, WI 54729

# **Record of Revision**

Each time this manual is revised and reprinted, all changes issued against the previous version are incorporated into the new version, and the new version is assigned an alphabetic level which is indicated in the publication number on each page of the manual.

Changes to part of a page are indicated by a change bar in the margin directly opposite the change. A change bar in the footer indicates that most, if not all, of the page is new. If the manual is rewritten, the revision level changes but the manual does not contain change bars.

#### **REVISION**

#### **DESCRIPTION**

February 1992. Original printing.

## PREFACE

The CRAY Y-MP C90 System Programmer Reference Manual describes the hardware architecture and functions of the CRAY Y-MP C90 computer system manufactured by Cray Research, Inc. (CRI). This manual is written primarily for system analysts and system programmers. The primary goal of this manual is to explain and define the special hardware features of the system in enough detail to help programmers write and optimize program code.

This manual is divided into the following tabbed sections.

Section 1, "Computer System Overview," introduces and describes the CRAY Y-MP C90 system components and support equipment.

Section 2, "CPU Shared Resources," describes the hardware shared by all central processing units (CPUs). Its primary emphasis is to define the functions, organization, and special hardware features of central memory, the I/O section, the interprocessor communication section, and the real-time clock. It also explains the shared paths access priority.

Section 3, "CPU Control," describes the basic CPU operations. The section explains the exchange mechanism in detail and defines and explains the deadstart, instruction fetch, and instruction issue sequences. The operations of the programmable clock, the status registers, and the performance monitor are also described.

Section 4, "CPU Computation Section," describes the CPU registers, functional units, and functional unit operations. Logical operations and integer and floating-point arithmetic are defined and explained in detail.

Section 5, "Parallel Processing Features," describes the parallel processing features most closely related to the hardware. This includes information and examples of pipelining and segmentaion, functional unit independence, and multiprocessing and multitasking.

Section 6, "Maintenance Channel," explains the operation of the maintenance channel used to troubleshoot system problems.

Section 7, "CPU Instructions," contains detailed descriptions of all instructions executed by the CRAY Y-MP C90 CPU. The instructions are listed by octal code starting with instruction 000000 and ending with instruction 177ijk. Special cases, hold issue conditions, and execution times are explained for each instruction or group of instructions.

The following conventions are used throughout this manual.

| Convention               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lowercase italic         | Variable information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| x                        | An unused value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| n                        | A specified value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| (value)                  | The contents of the register or memory location designated by value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

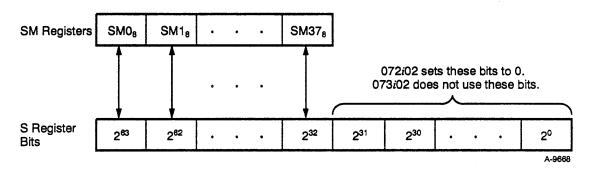

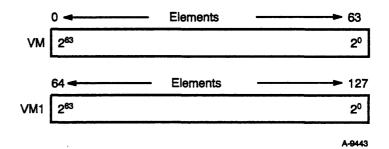

| Register bit designators | Register bits are numbered from right to left as powers of 2. Bit 2 <sup>0</sup> corresponds to the least significant bit of the register. One exception is the vector mask register. The vector mask register bits correspond to a word element in a vector register; bit 2 <sup>63</sup> corresponds to element 0 and bit 2 <sup>0</sup> corresponds to element 63. Another exception is when the state of the 32 1-bit semaphore registers is loaded into an S register. SM0 goes into S register bit position 2 <sup>63</sup> , SM1 goes into S register bit position 2 <sup>62</sup> , and so on. |

| Number base              | All numbers used in this manual are decimal, unless otherwise indicated. Octal numbers are indicated with an 8 subscript. Exceptions are register numbers, the instruction parcel in instruction buffers, and instruction forms, which are given in octal without the subscript.                                                                                                                                                                                                                                                                                                                       |

The following list provides examples of the preceding conventions.

| Example                  | Description                                                                                                      |

|--------------------------|------------------------------------------------------------------------------------------------------------------|

| Transmit $(Ak)$ to $Si$  | Transmit the contents of the A register specified by the $k$ field to the S register specified by the $i$ field. |

| 167 <i>ixk</i>           | Machine instruction 167. The x indicates that the $j$ field is not used.                                         |

| Read n words from memory | Read a specified number of words from memory.                                                                    |

| Bit 2 <sup>63</sup>      | The value represents the most significant bit of an S register or element of a V register.                       |

| 10008                    | The number base is octal.                                                                                        |

# **CONTENTS**

| <u>_</u> | COMPUTER STSTEM OVERVIEW              |      |

|----------|---------------------------------------|------|

|          | Mainframe                             | 1-2  |

|          | I/O Subsystem                         | 1-4  |

|          | SSD-E Solid-state Storage Device      | 1-4  |

|          | Disk Storage Units                    | 1-6  |

|          | Network Interfaces                    | 1-6  |

|          | Operator and Maintenance Workstations | 1-6  |

| 2        | CPU SHARED RESOURCES                  |      |

|          | Central Memory                        | 2-1  |

|          | Memory Instructions                   | 2-1  |

|          | Logical Organization                  | 2-4  |

|          | Memory Paths                          | 2-4  |

|          | Memory Ports                          | 2-5  |

|          | Conflict Resolution                   | 2-8  |

|          | Memory Addressing                     | 2-12 |

|          | Absolute Memory Address Calculating   | 2-12 |

|          | Address Range Checking                | 2-13 |

|          | DBA Register                          | 2-13 |

|          | DLA Register                          | 2-13 |

|          | IBA Register                          | 2-14 |

|          | ILA Register                          | 2-14 |

|          | Error Detection and Correction        | 2-14 |

|          | Central Memory Performance Summary    | 2-18 |

|          | I/O Section                           | 2-19 |

|          | LOSP Channels                         | 2-20 |

|          | Channel Programming                   | 2-21 |

|          | Channel Errors                        | 2-24 |

|          | HISP Channels                         | 2-26 |

## 2 CPU SHARED RESOURCES (continued)

|   | VHISP Channels                                      | 2-26 |

|---|-----------------------------------------------------|------|

|   | Channel Programming                                 | 2-27 |

|   | I/O Interrupts                                      | 2-29 |

|   | Interprocessor Communication Section                | 2-29 |

|   | Clusters                                            | 2-30 |

|   | Shared Registers                                    | 2-31 |

|   | Semaphore Registers                                 | 2-32 |

|   | Deadlock                                            | 2-35 |

|   | Interprocessor Interrupts                           | 2-35 |

|   |                                                     |      |

|   | Real-time Clock                                     | 2-36 |

|   | Shared Paths Access Priority                        | 2-37 |

|   | Shared Register and Real-time Clock Troubleshooting | 2-39 |

| _ |                                                     |      |

| 3 | CPU CONTROL                                         |      |

|   | Exchange Mechanism                                  | 3-1  |

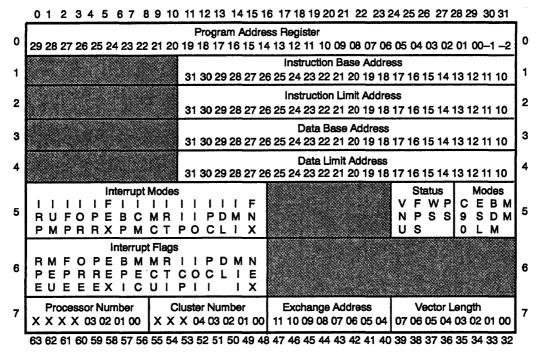

|   | Exchange Package                                    | 3-2  |

|   | Program Address Register Field                      | 3-2  |

|   | Instruction Base Address Register Field             | 3-2  |

|   | Instruction Limit Address Register Field            | 3-4  |

|   | Data Base Address Register Field                    | 3-4  |

|   | Data Limit Address Register Field                   | 3-4  |

|   | Interrupt Modes Field                               | 3-5  |

|   | Interrupt Flags Field                               | 3-6  |

|   | Status Field                                        | 3-9  |

|   | Modes Field                                         | 3-9  |

|   | Processor Number Field                              | 3-9  |

|   | Cluster Number Field                                | 3-10 |

|   | Exchange Address Register Field                     | 3-10 |

|   | Vector Length Register Field                        | 3-10 |

|   | A Register Fields                                   | 3-11 |

|   | S Register Fields                                   | 3-11 |

|   | Exchange Sequence                                   | 3-11 |

|   | Exchange Sequence Timing                            | 3-11 |

|   | Initiating an Exchange Sequence                     | 3-12 |

|   |                                                     |      |

# 3 CPU CONTROL (continued)

| Exchange Package Ma        | anagement 3-14                               |

|----------------------------|----------------------------------------------|

| Instruction Fetch Sequence | 3-15                                         |

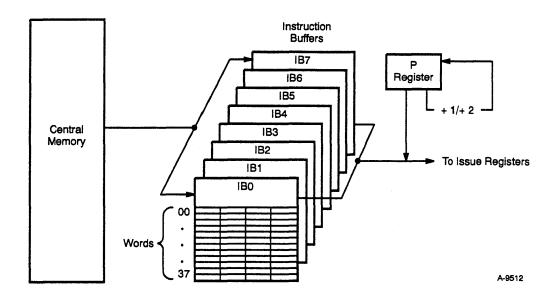

| Instruction Fetch Hard     | lware 3-16                                   |

| Instruction Bu             | ıffers                                       |

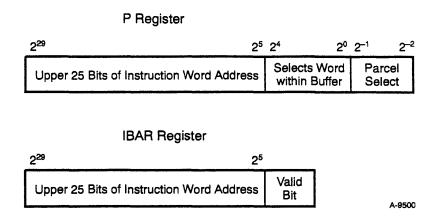

| Program Addi               | ress Register                                |

| Instruction Fetch Open     | ration 3-17                                  |

| Instruction Fe             | tch Timing                                   |

| Instruction Issue          | 3-19                                         |

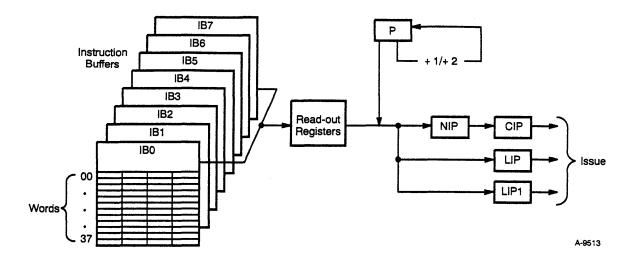

| Instruction Issue Hard     | ware                                         |

| Instruction Bu             | ıffers                                       |

| Program Addr               | ress Register                                |

| Next Instruction           | on Parcel Register 3-21                      |

| Current Instru             | ction Parcel Register 3-21                   |

|                            | tion Parcel and Lower Instruction sters 3-21 |

| Instruction Issue Oper     | ation 3-21                                   |

| Reservations and Hold      | l Issue Conditions 3-29                      |

| Programmable Clock         | 3-30                                         |

| Interrupt Interval Regi    | ster 3-31                                    |

| Operation                  | 3-31                                         |

| Status Registers           | 3-32                                         |

|                            | 3-37                                         |

| Selecting and Reading      | Performance Events 3-38                      |

| Testing Performance C      | Counters                                     |

| 4 CPU COMPUTATION SECTION  |                                              |

| Operating Registers        | 4-2                                          |

| Address (A) Registers      | 4-3                                          |

| A Register Fu              | nctions                                      |

| Special A Reg              | gister Values 4-5                            |

| Bypass Path .              |                                              |

| A Register Ins             | structions 4-6                               |

| Intermediate Address       | (B) Registers 4-10                           |

| A and B Register Trou      | ableshooting 4-12                            |

|                            |                                              |

# 4 CPU COMPUTATION SECTION (continued)

| Scalar (S) Registers                                  | 4-14 |

|-------------------------------------------------------|------|

| S Register Functions                                  | 4-14 |

| Special S Register Values                             | 4-15 |

| S Register Instructions                               | 4-16 |

| Intermediate Scalar (T) Registers                     | 4-22 |

| S and T Register Troubleshooting                      | 4-23 |

| Vector (V) Registers                                  | 4-25 |

| Vector Processing                                     | 4-25 |

| Advantages of Vector Processing                       | 4-27 |

| V Register Functions                                  | 4-27 |

| Vector Instructions                                   | 4-28 |

| Vector Chaining                                       | 4-32 |

| Vector Control Registers                              | 4-33 |

| Vector Length Register                                | 4-33 |

| Vector Mask Register                                  | 4-34 |

| V Register Troubleshooting                            | 4-35 |

| Functional Units                                      | 4-39 |

| Address Functional Units                              | 4-40 |

| Address Add Functional Unit                           | 4-40 |

| Address Multiply Functional Unit                      | 4-40 |

| Scalar Functional Units                               | 4-40 |

| Scalar Add Functional Unit                            | 4-41 |

| Scalar Shift Functional Unit                          | 4-41 |

| Scalar Logical Functional Unit                        | 4-41 |

| Scalar Population/Parity/Leading Zero                 |      |

| Functional Unit                                       | 4-42 |

| Vector Functional Units                               | 4-42 |

| Vector Add Functional Unit                            | 4-43 |

| Vector Shift Functional Unit                          | 4-43 |

| Full Vector Logical Functional Unit                   | 4-43 |

| Second Vector Logical Functional Unit                 | 4-44 |

| Vector Population/Parity/Leading Zero Functional Unit | 4-44 |

| Floating-point Functional Units                       | 4-45 |

| Floating-point Add Functional Unit                    | 4-45 |

| Floating-point Multiply Functional Unit               | 4-46 |

|                                                       | •    |

# 4 CPU COMPUTATION SECTION (continued)

|    |                  | Reciprocal Approximation Functional Unit | 4-46 |

|----|------------------|------------------------------------------|------|

|    |                  | Functional Unit Operations               | 4-47 |

|    |                  | Logical Operations                       | 4-47 |

|    |                  | Integer Arithmetic                       | 4-48 |

|    |                  | Floating-point Arithmetic                | 4-51 |

|    |                  | Floating-point Data Format               | 4-51 |

|    |                  | Exponent Ranges                          | 4-52 |

|    |                  | Normalized Floating-point Numbers        | 4-53 |

|    |                  | Floating-point Range Errors              | 4-54 |

| 5  | PARALLEL PROCESS | SING FEATURES                            |      |

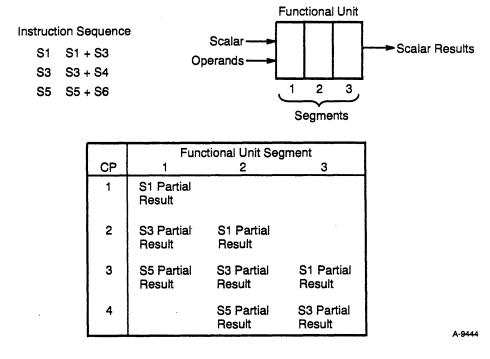

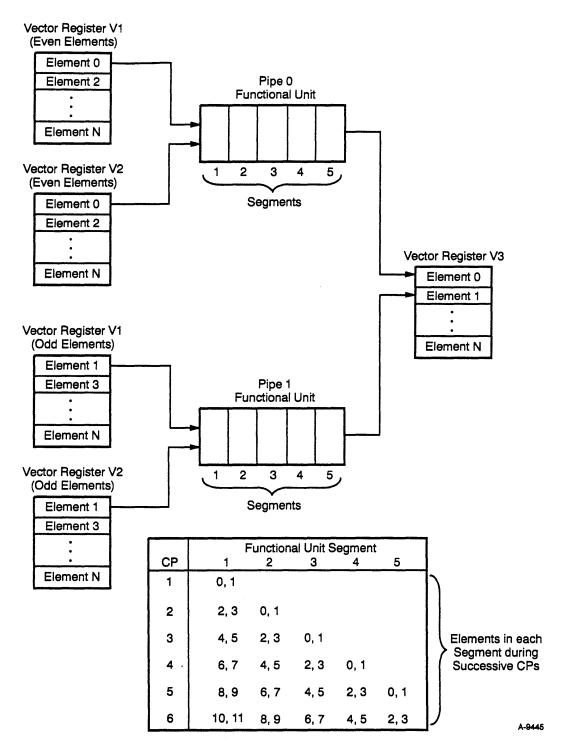

|    |                  | Pipelining and Segmentation              | 5-2  |

|    |                  | Functional Unit Independence             | 5-5  |

|    |                  | Multiprocessing and Multitasking         | 5-5  |

|    |                  | Autotasking                              | 5-6  |

| 6  | MAINTENANCE CHAI | NEL                                      |      |

|    |                  | Theory of Operation                      | 6-1  |

|    |                  | Individual CPU Commands                  | 6-2  |

|    |                  | Broadcast Commands                       | 6-2  |

|    |                  | System Commands                          | 6-2  |

|    |                  | Loopback                                 | 6-3  |

|    |                  | Write Hang                               | 6-3  |

|    |                  | Maintenance Channel Functions            | 6-3  |

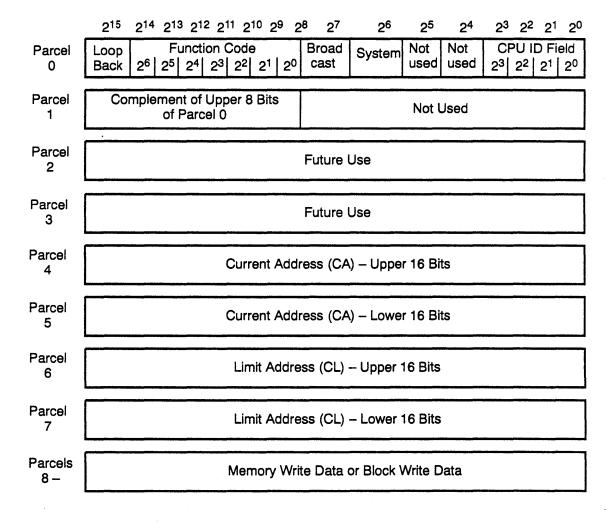

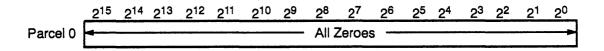

|    |                  | Data Formats                             | 6-8  |

|    |                  | MWS Write Data                           | 6-8  |

|    |                  | Status Read Data                         | 6-9  |

|    |                  | Diagnostic Monitor                       | 6-11 |

| 7_ | CPU INSTRUCTIONS |                                          |      |

|    |                  | Notational Conventions                   | 7-1  |

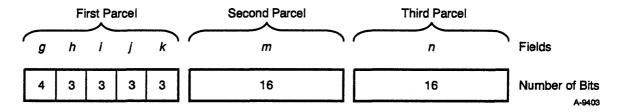

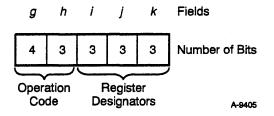

|    |                  | Instruction Formats                      | 7-2  |

# 7 CPU INSTRUCTIONS (continued)

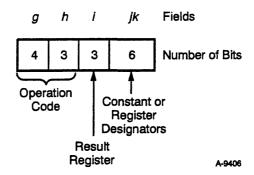

| 1-parcel Instruction Format with Discrete $j$ and $k$    |      |

|----------------------------------------------------------|------|

| Fields                                                   | 7-2  |

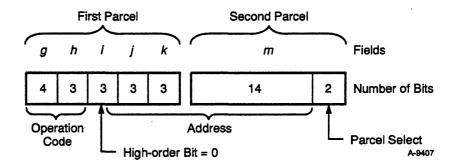

| 1-parcel Instruction Format with Combined j and k Fields | 7-3  |

| 2-parcel Instruction Format with Combined                |      |

| i, j, k, and $m$ Fields                                  | 7-4  |

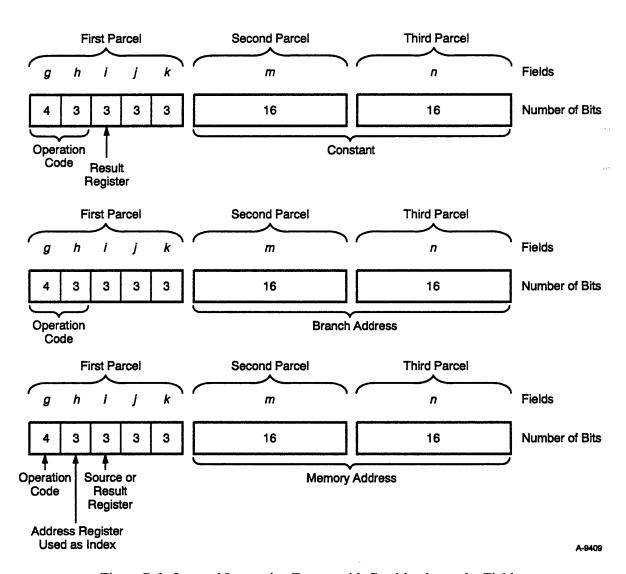

| 3-parcel Instruction Format with Combined m and n Fields | 7-4  |

| Y-MP Mode and C90 Mode Instruction Differences           | 7-6  |

| Special Register Values                                  | 7-9  |

| Monitor Mode Instructions                                | 7-10 |

| Special CAL Syntax Forms                                 | 7-10 |

| CPU Instruction Descriptions                             | 7-10 |

| Functional Units Instruction Summary                     | 7-12 |

| Instruction 000000                                       | 7-13 |

| Instructions 0010 through 0012                           | 7-14 |

| Instruction 0013                                         | 7-17 |

| Instruction 0014                                         | 7-19 |

| Instruction 0015                                         | 7-22 |

| Instruction 0016                                         | 7-23 |

| Instruction 0017                                         | 7-24 |

| Instruction 0020                                         | 7-25 |

| Instructions 0021 through 0026                           | 7-27 |

| Instruction 0027                                         | 7-29 |

| Instruction 0030                                         | 7-31 |

| Instructions 0034, 0036, and 0037                        | 7-33 |

| Instruction 0040                                         | 7-35 |

| Instructions 0050 and 0051                               | 7-36 |

| Instruction 006                                          | 7-38 |

| Instruction 007                                          | 7-40 |

| Instructions 010 through 013                             | 7-42 |

| Instructions 014 through 017                             | 7-45 |

| Instructions 020 through 022                             | 7-48 |

| Instruction 023                                          | 7-50 |

# 7 CPU INSTRUCTIONS (continued)

| Instructions 024 and 025           | 7-52  |

|------------------------------------|-------|

| Instruction 026                    | 7-53  |

| Instruction 027                    | 7-55  |

| Instructions 030 and 031           | 7-57  |

| Instruction 032                    | 7-59  |

| Instruction 033                    | 7-60  |

| Instructions 034 through 037       | 7-63  |

| Instructions 040 and 041           | 7-67  |

| Instructions 042 and 043           | 7-69  |

| Instructions 044 through 051       | 7-71  |

| Instructions 052 through 055       | 7-76  |

| Instructions 056 and 057           | 7-78  |

| Instructions 060 and 061           | 7-80  |

| Instructions 062 and 063           | 7-82  |

| Instructions 064 through 067       | 7-84  |

| Instruction 070                    | 7-86  |

| Instruction 071                    | 7-88  |

| Instruction 072                    | 7-91  |

| Instruction 073                    | 7-93  |

| Instructions 074 and 075           | 7-98  |

| Instructions 076 and 077           | 7-99  |

| Instructions 10h through 13h       | 7-101 |

| Instructions 140 through 147       | 7-104 |

| Instructions 150 and 151           | 7-109 |

| Instructions 152 and 153           | 7-111 |

| Instructions 154 through 157       | 7-118 |

| Instructions 160 through 167       | 7-120 |

| Instructions 170 through 173       | 7-123 |

| Instruction 174 <i>ij</i> 0        | 7-126 |

| Instructions 174ij1 through 174ij3 | 7-128 |

| Instruction 175                    | 7-130 |

| Instructions 176 and 177           | 7-134 |

|                                    |       |

## **BIBLIOGRAPHY**

|         | Bibliography |                                                           | Bib-1 |

|---------|--------------|-----------------------------------------------------------|-------|

| INDEX   |              |                                                           |       |

|         | Index        |                                                           | Ind-1 |

| FIGURES |              |                                                           |       |

|         | Figure 1-1.  | CRAY Y-MP C90 Computer System                             | 1-2   |

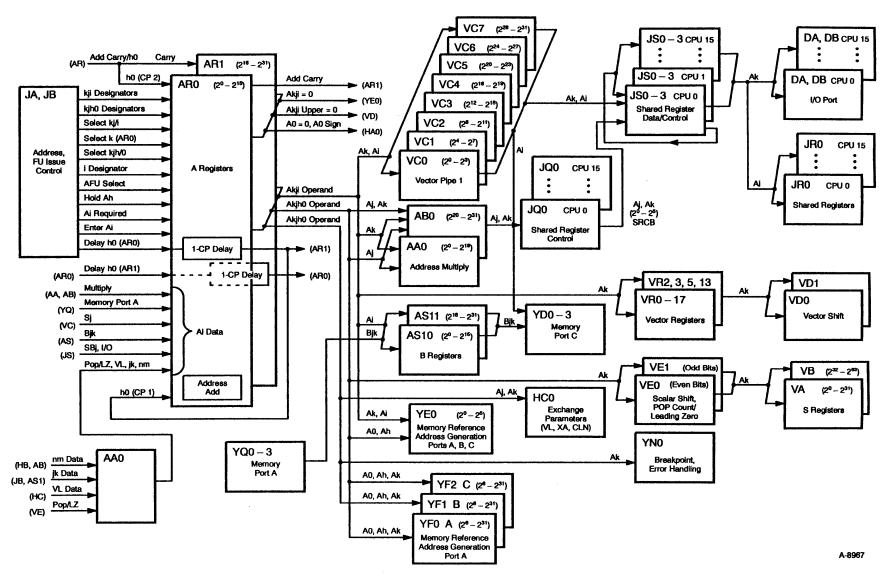

|         | Figure 1-2.  | CRAY Y-MP C90 CPU Block Diagram                           | 1-3   |

|         | Figure 1-3.  | Minimum CRAY Y-MP C90 Configuration with Two I/O Clusters | 1-5   |

|         | Figure 2-1.  | Central Memory Architecture                               | 2-5   |

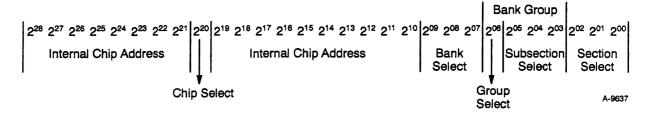

|         | Figure 2-2.  | Memory Addressing                                         | 2-12  |

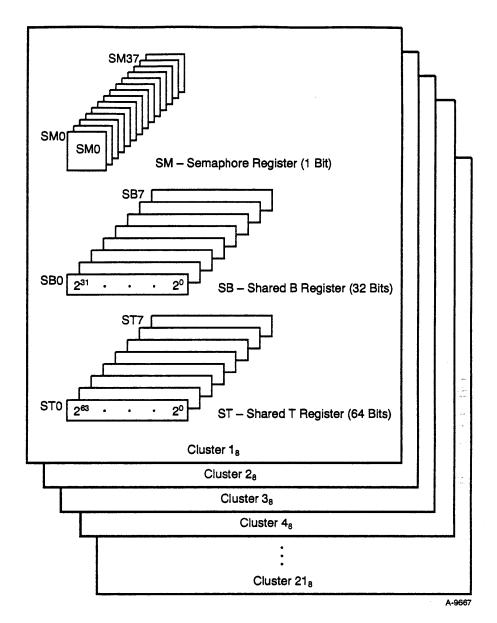

|         | Figure 2-3.  | Shared Registers                                          | 2-31  |

|         | Figure 2-4.  | Relation between SM Registers and S Register Bits         | 2-33  |

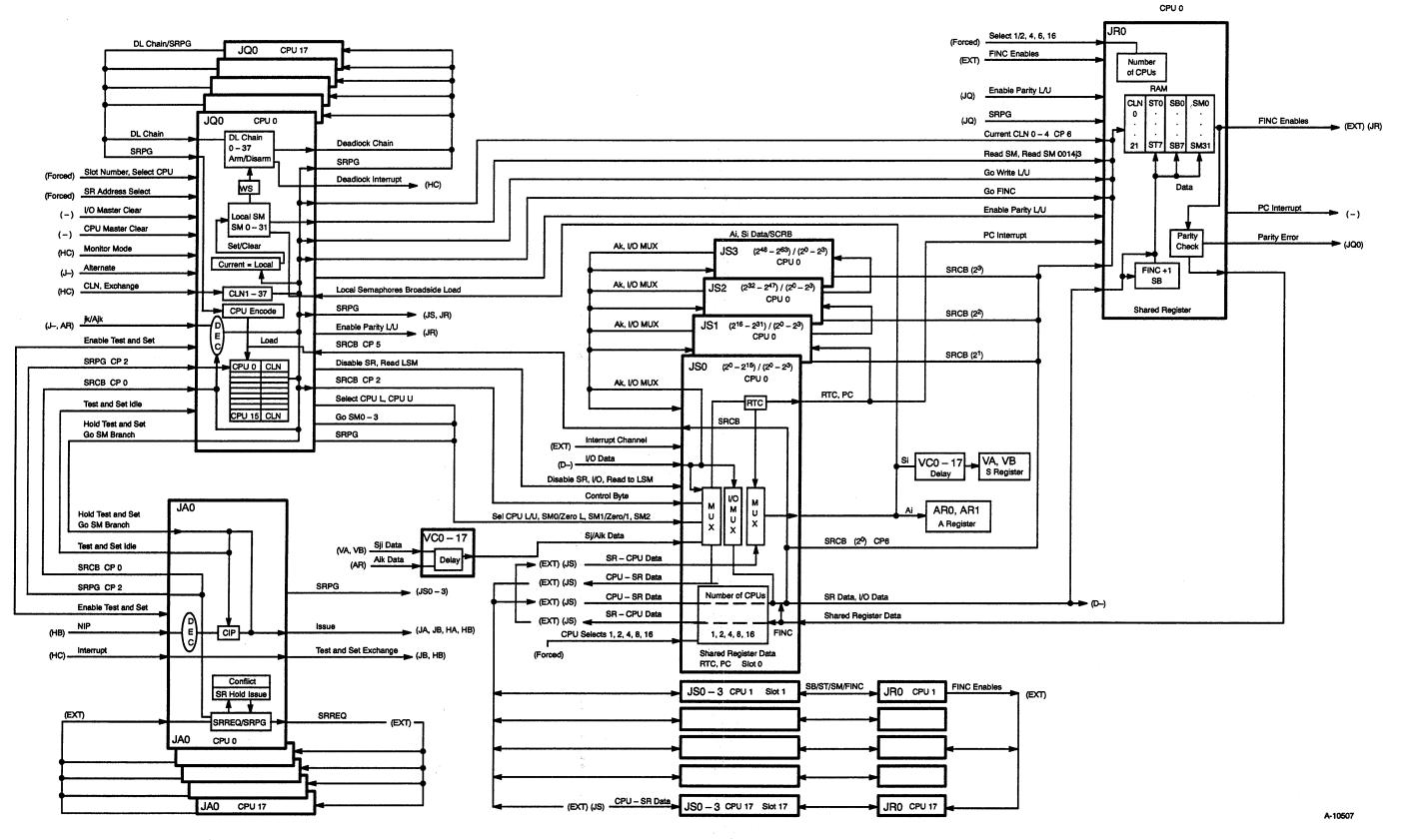

|         | Figure 2-5.  | Shared Registers Block Diagram                            | 2-41  |

|         | Figure 3-1.  | CRAY Y-MP C90 Exchange Package                            | 3-3   |

|         | Figure 3-2.  | Instruction Fetch Block Diagram                           | 3-16  |

|         | Figure 3-3.  | P Register and IBAR Register Address Formats              | 3-17  |

|         | Figure 3-4.  | Instruction Issue Block Diagram                           | 3-20  |

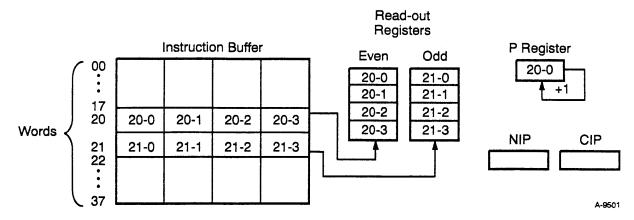

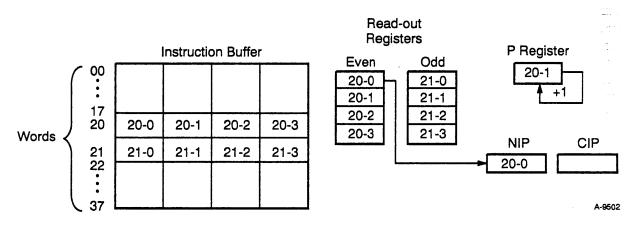

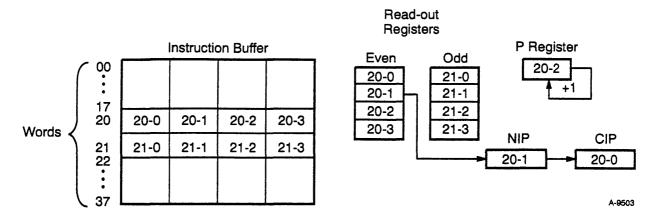

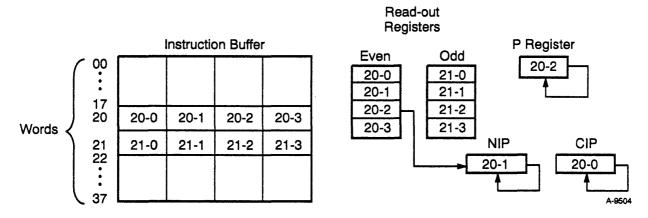

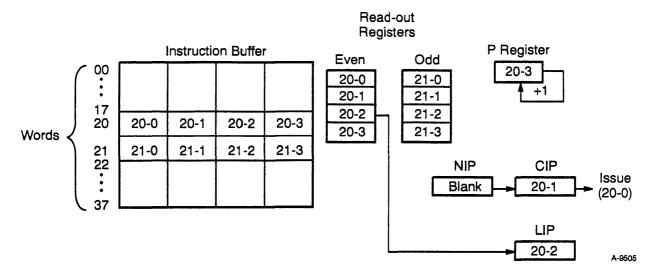

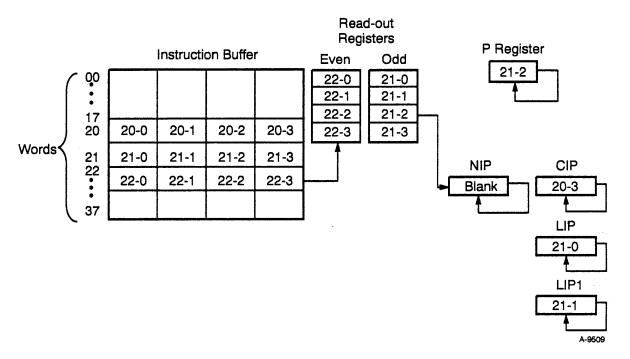

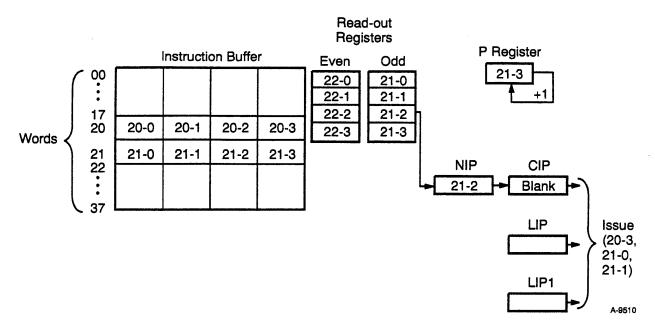

|         | Figure 3-5.  | Instruction Flow through Issue Registers (CPn)            | 3-23  |

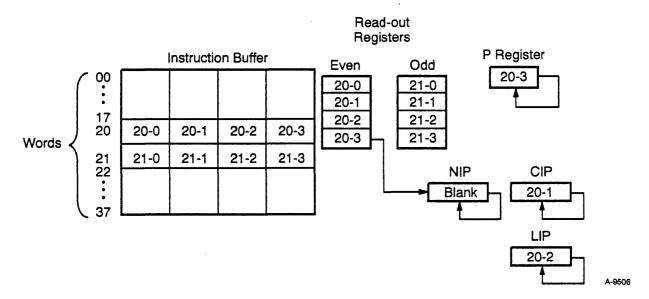

|         | Figure 3-6.  | Instruction Flow through Issue Registers (CPn + 1)        | 3-23  |

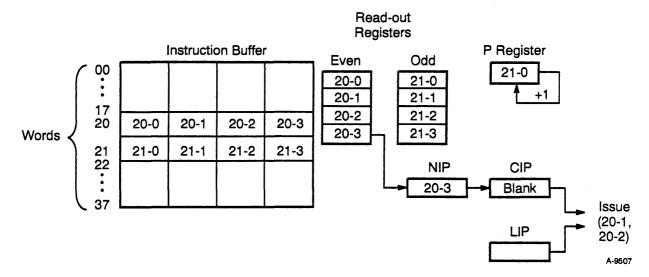

|         | Figure 3-7.  | Instruction Flow through Issue Registers (CPn + 2)        | 3-24  |

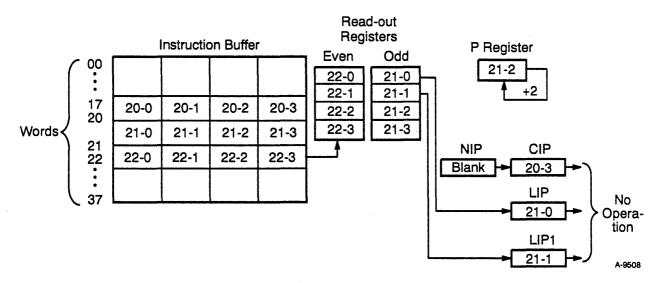

|         | Figure 3-8.  | 1-parcel Instruction Holding 1 CP for Conflict (CPn + 3)  | 3-24  |

|         | Figure 3-9.  | Instruction Flow through Issue Registers (CPn + 4)        | 3-25  |

|         | Figure 3-10. | 2-parcel Instruction Holding 1 CP for Conflict (CPn + 5)  | 3-25  |

|         | Figure 3-11. | Instruction Flow through Issue Registers (CPn + 6)        | 3-26  |

|         | Figure 3-12. | Instruction Flow through Issue Registers (CPn + 7)        | 3-26  |

|         | Figure 3-13. | 3-parcel Instruction Holding 1 CP for Conflict (CPn + 8)  | 3-27  |

|         | Figure 3-14. | Instruction Flow through Issue Registers (CPn + 9)        | 3-28  |

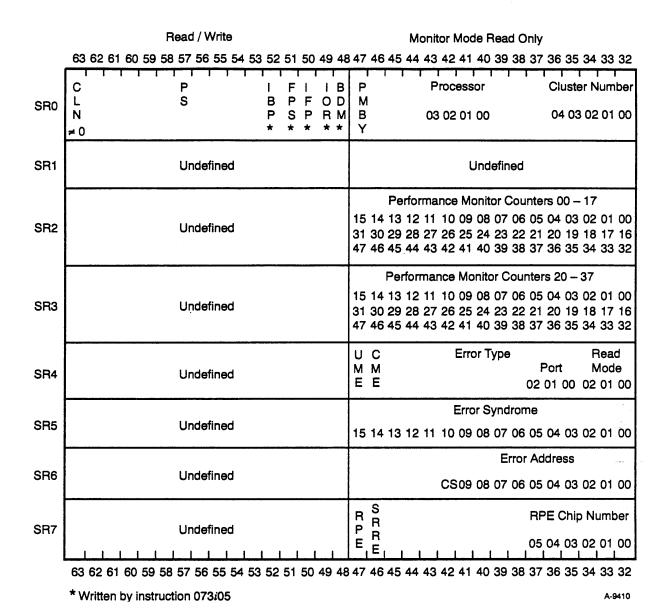

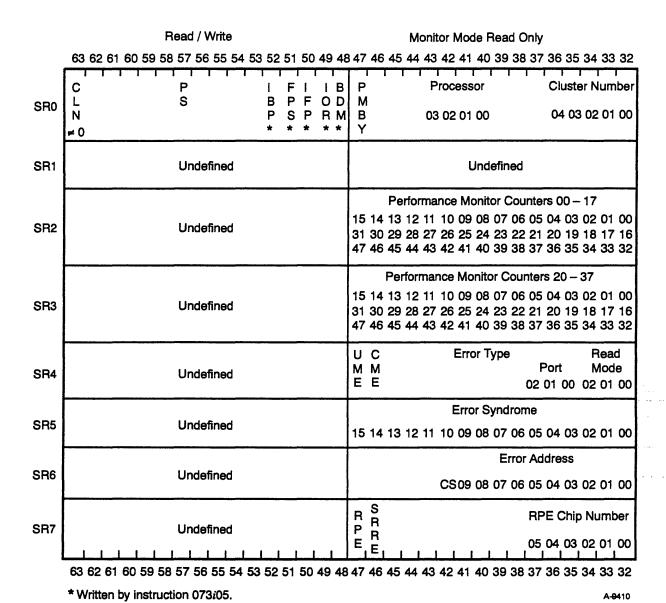

|         | Figure 3-15. | Status Registers                                          | 3-33  |

## FIGURES (continued)

| Figure 4-1.  | A Register Block Diagram                                                       | 4-3  |

|--------------|--------------------------------------------------------------------------------|------|

| Figure 4-2.  | Instruction Timing for a Bypass Operation                                      | 4-6  |

| Figure 4-3.  | A and B Registers Troubleshooting Block Diagram                                | 4-13 |

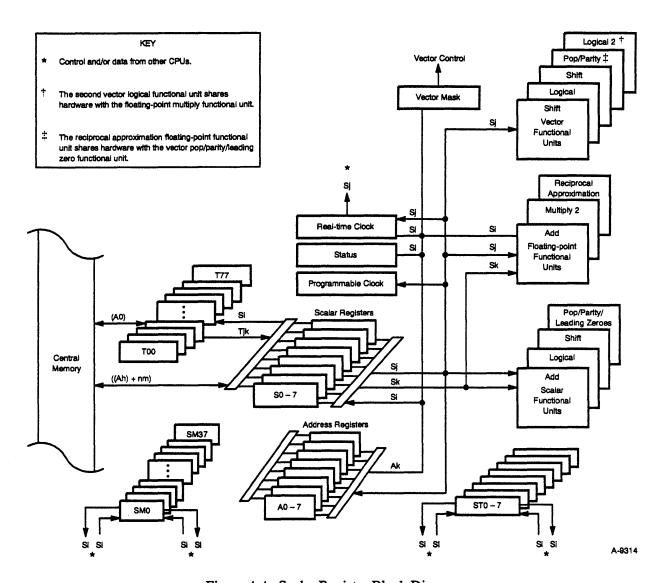

| Figure 4-4.  | Scalar Register Block Diagram                                                  | 4-14 |

| Figure 4-5.  | S and T Registers Troubleshooting Block Diagram                                | 4-24 |

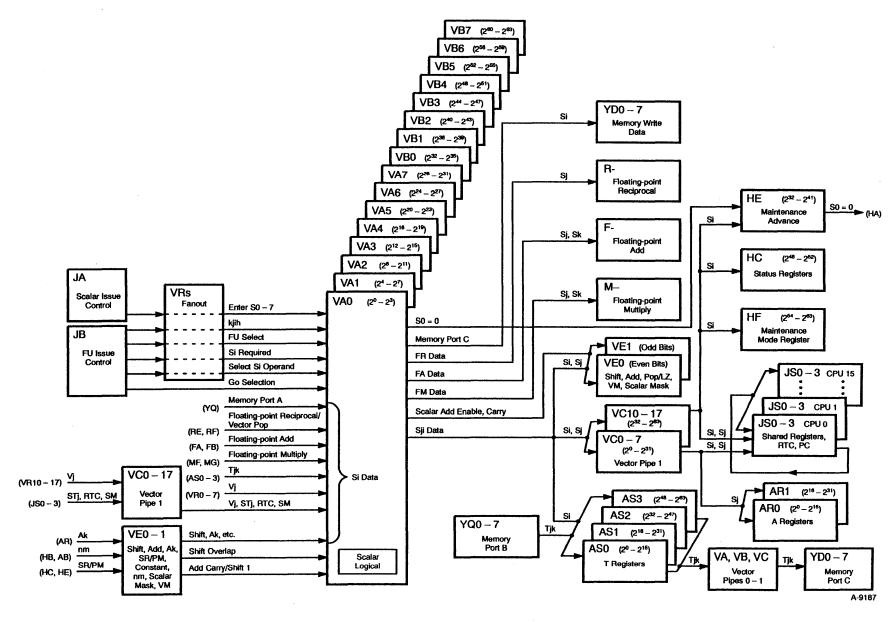

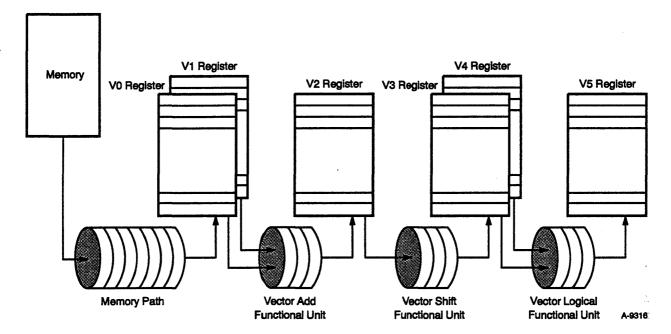

| Figure 4-6.  | V Register Block Diagram                                                       | 4-26 |

| Figure 4-7.  | Vector Chaining Example                                                        | 4-33 |

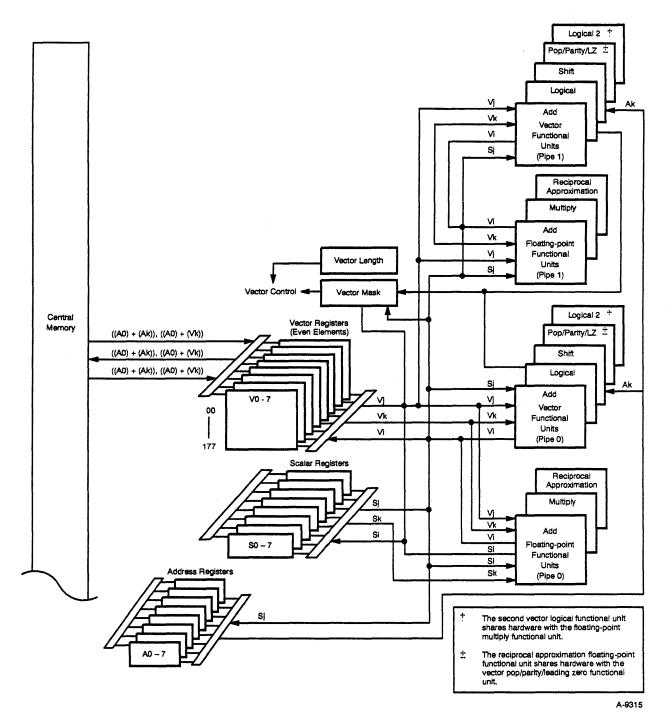

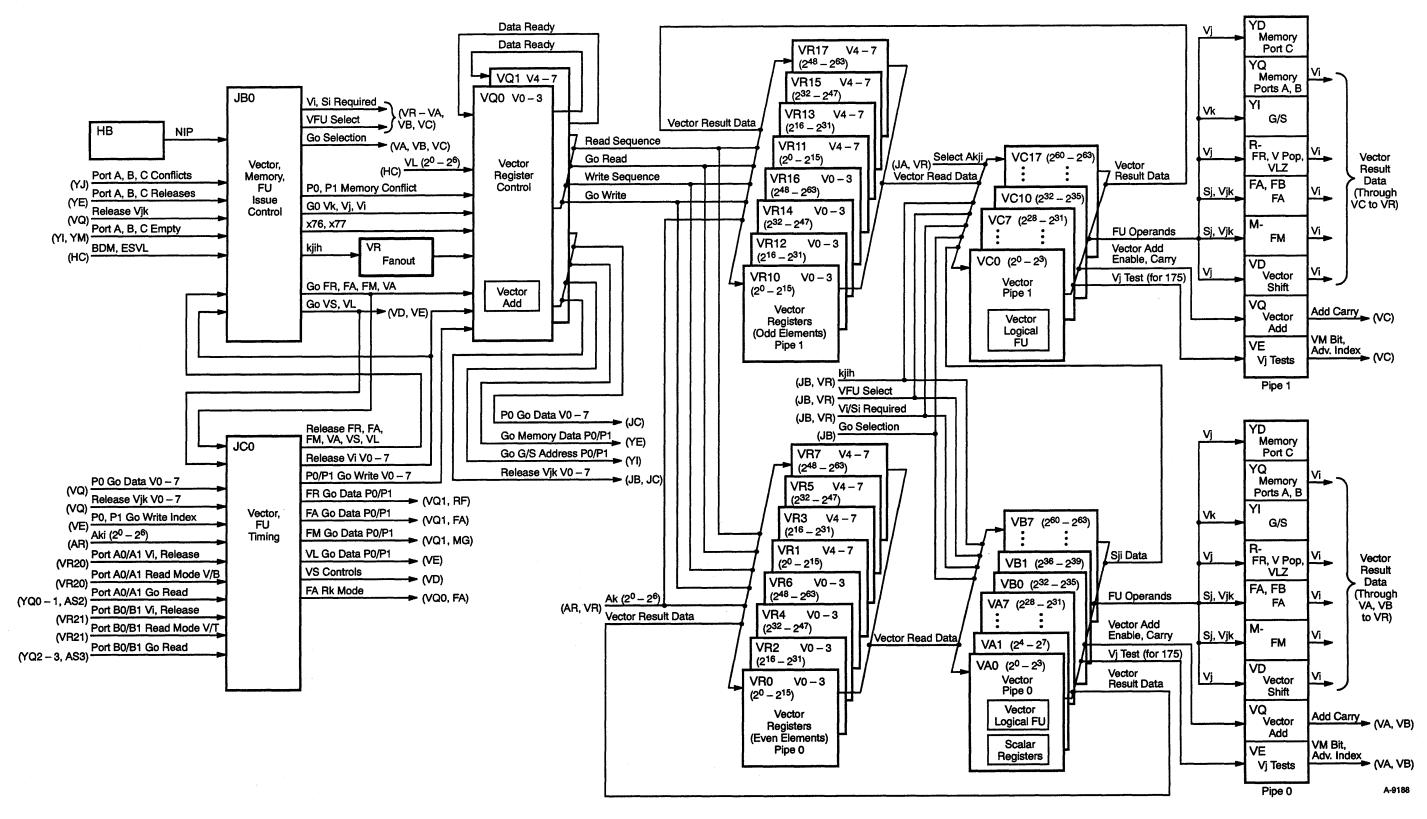

| Figure 4-8.  | Vector Registers Troubleshooting Block Diagram                                 | 4-37 |

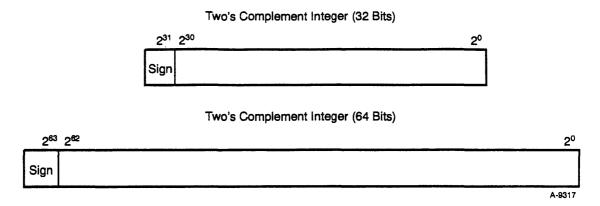

| Figure 4-9.  | Integer Data Formats                                                           | 4-49 |

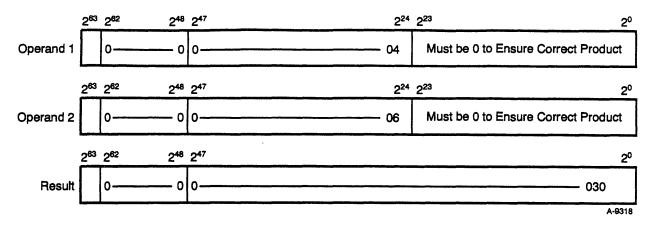

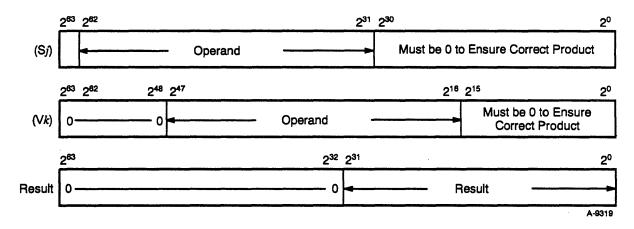

| Figure 4-10. | 24-bit Integer Multiply Performed in a Floating-point Multiply Functional Unit | 4-50 |

| Figure 4-11. | 32-bit Integer Multiply Performed in a Floating-point Multiply Functional Unit | 4-50 |

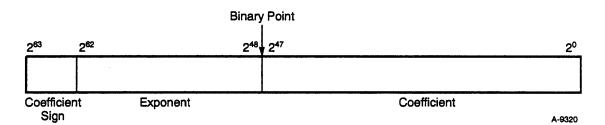

| Figure 4-12. | Floating-point Data Format                                                     | 4-51 |

| Figure 4-13. | Internal Representation of a Floating-point Number                             | 4-52 |

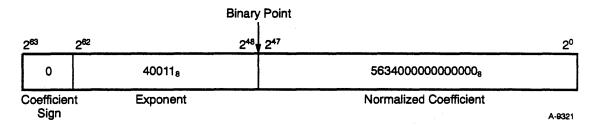

| Figure 4-14. | Biased and Unbiased Exponent Ranges                                            | 4-53 |

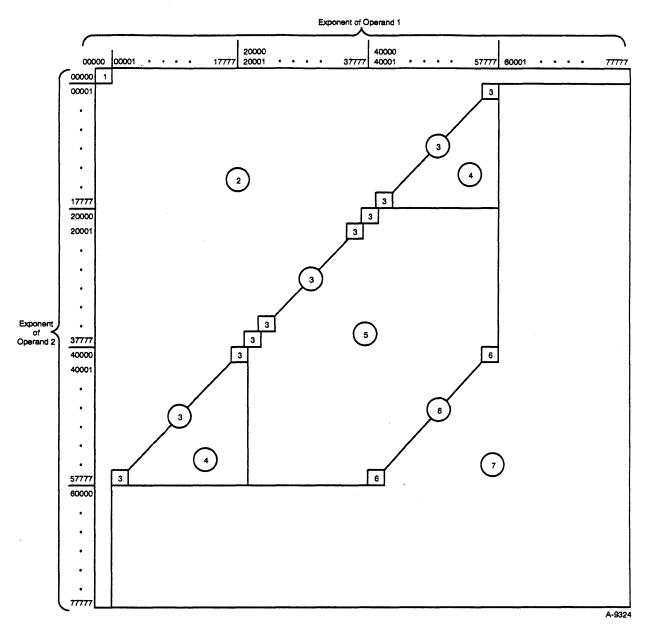

| Figure 4-15. | Floating-point Add and Floating-point Multiply Range Errors                    | 4-55 |

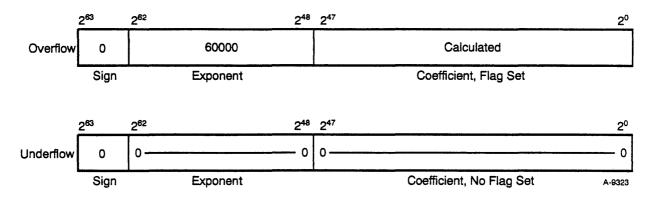

| Figure 4-16. | Exponent Matrix for a Floating-point Multiply Functional Unit                  | 4-56 |

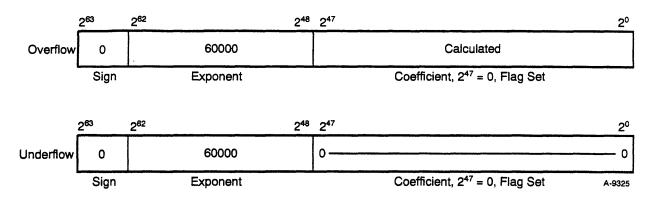

| Figure 4-17. | Floating-point Reciprocal Approximation Range Errors                           | 4-58 |

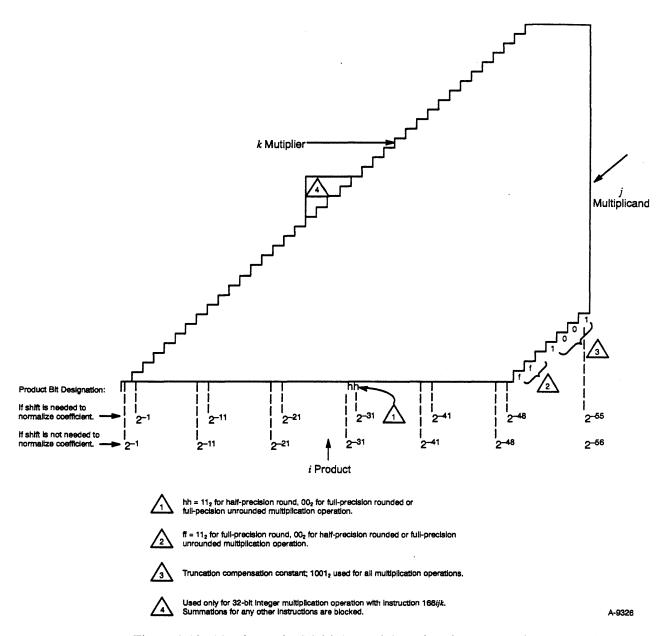

| Figure 4-18. | Floating-point Multiply Partial-product Sums Pyramid                           | 4-60 |

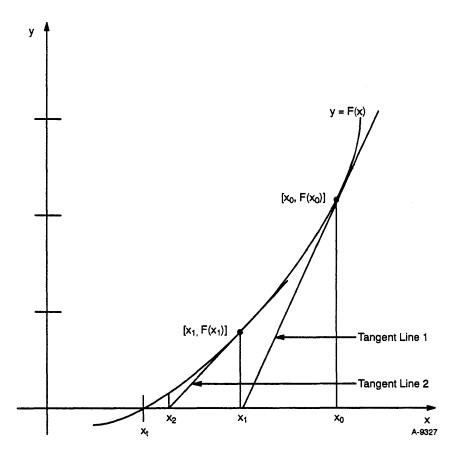

| Figure 4-19. | Newton's Method for Approximating Roots                                        | 4-62 |

| Figure 5-1.  | Scalar Segmentation and Pipelining Example                                     | 5-2  |

| Figure 5-2.  | Vector Segmentation and Pipelining Example                                     | 5-4  |

| Figure 6-1.  | MWS Write Data Format                                                          | 6-8  |

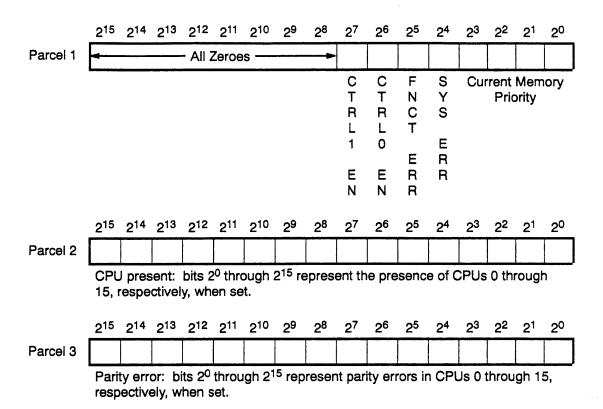

| Figure 6-2.  | System Status Read Format (Parcel 0)                                           | 6-9  |

| Figure 6-3.  | System and Individual CPU Status Read Formats (Parcels 1 through 3)            | 6-11 |

| Figure 7-1.  | Vector Mask Bits                                                               | 7-1  |

| Figure 7-2   | General Instruction Format                                                     | 7-2  |

## FIGURES (continued)

|        | Figure 7-3.  | 1-parcel Instruction Format with Discrete j and k Fields             | 7-3   |

|--------|--------------|----------------------------------------------------------------------|-------|

|        | Figure 7-4.  | 1-parcel Instruction Format with Combined j and k Fields             | 7-4   |

|        | Figure 7-5.  | 2-parcel Instruction Format with Combined $i, j, k$ , and $m$ Fields | 7-4   |

|        | Figure 7-6.  | 3-parcel Instruction Format with Combined m and n Fields             | 7-5   |

|        | Figure 7-7.  | Status Registers                                                     | 7-97  |

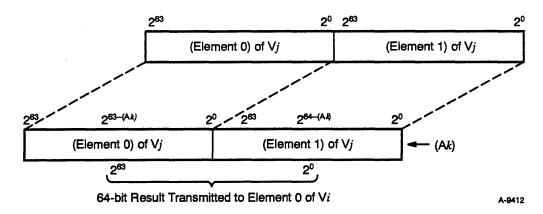

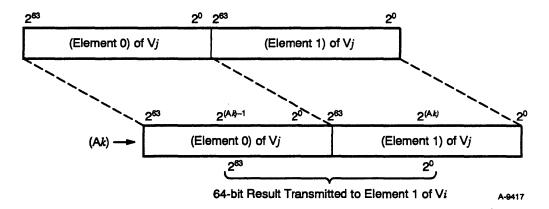

|        | Figure 7-8.  | Vector Left Double Shift, First Element, (VL)>1                      | 7-113 |

|        | Figure 7-9.  | Vector Left Double Shift, Second Element, (VL)>2                     | 7-113 |

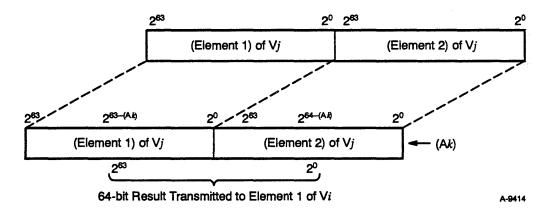

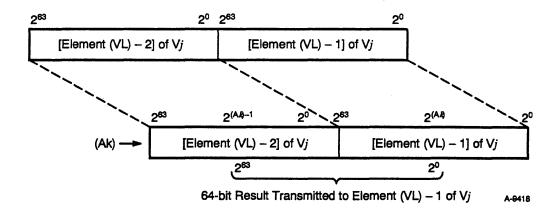

|        | Figure 7-10. | Vector Left Double Shift, Last Element                               | 7-114 |

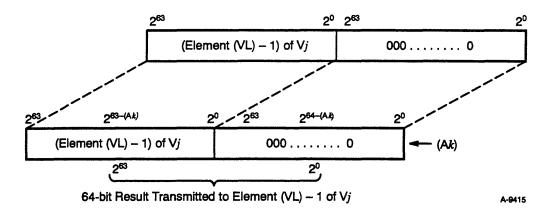

|        | Figure 7-11. | Vector Right Double Shift, First Element                             | 7-115 |

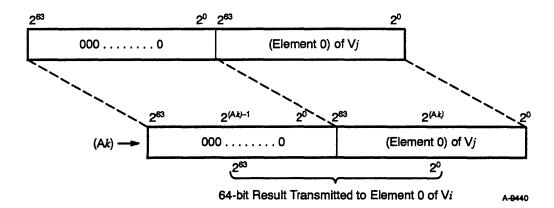

|        | Figure 7-12. | Vector Right Double Shift, Second Element, (VL)>1                    | 7-115 |

|        | Figure 7-13. | Vector Right Double Shift, Last Operation                            | 7-116 |

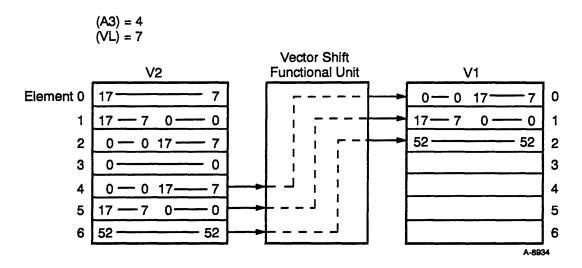

|        | Figure 7-14. | Vector Word Shift                                                    | 7-117 |

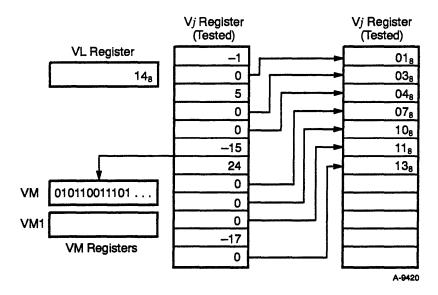

|        | Figure 7-15. | Compressed Index Example for Instruction 175ij4                      | 7-133 |

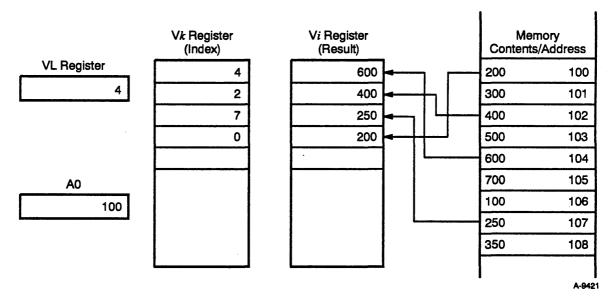

|        | Figure 7-16. | Gather Instruction Example                                           | 7-137 |

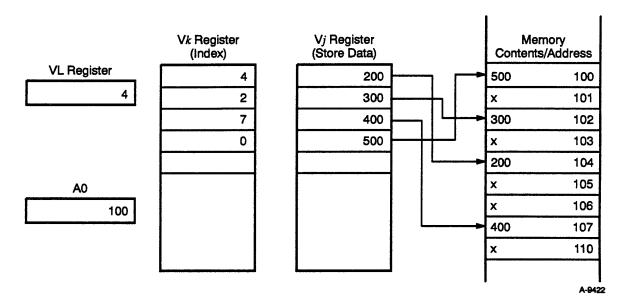

|        | Figure 7-17. | Scatter Instruction Example                                          | 7-138 |

| TABLES |              |                                                                      | 1000  |

|        | Table 2-1.   | Memory Instructions                                                  | 2-2   |

|        | Table 2-2.   | Allocation of Memory References to Ports and Pipes                   | 2-6   |

|        | Table 2-3.   | CPU Priority Matrix                                                  | 2-10  |

|        | Table 2-4.   | Memory Conflicts                                                     | 2-11  |

|        | Table 2-5.   | Check Bit Generation                                                 | 2-16  |

|        | Table 2-6.   | CPU I/O Channel Assignments                                          | 2-19  |

|        | Table 2-7.   | LOSP Channel Instructions                                            | 2-22  |

|        | Table 2-8.   | LOSP Channel Error Flag Settings                                     | 2-25  |

|        |              |                                                                      |       |

| Table 2-9.  | VHISP Channel Instructions                         | 2-27 |

|-------------|----------------------------------------------------|------|

| Table 2-10. | VHISP Channel Status Word                          | 2-28 |

| Table 2-11. | Shared Register Instructions                       | 2-32 |

| Table 2-12. | SM Register Instructions                           | 2-33 |

| Table 2-13. | Interprocessor Interrupt Instructions              | 2-35 |

| Гable 2-14. | RTC Instructions                                   | 2-36 |

| Table 3-1.  | CRAY Y-MP C90 Interrupt Modes                      | 3-5  |

| Гable 3-2.  | CRAY Y-MP C90 Interrupt Flags                      | 3-7  |

| Table 3-3.  | CRAY Y-MP C90 Status Field Bit Assignments         | 3-9  |

| Гable 3-4.  | CRAY Y-MP C90 Operating Modes                      | 3-10 |

| Table 3-5.  | Instruction Issue Sequence                         | 3-28 |

| Гable 3-6.  | Programmable Clock Instructions                    | 3-31 |

| Гable 3-7.  | SR0 Data Fields                                    | 3-32 |

| Table 3-8.  | Read Mode Bits                                     | 3-34 |

| Гable 3-9.  | Port Designator Bits                               | 3-34 |

| Гable 3-10. | Memory Error Address Bits                          | 3-35 |

| Гable 3-11. | Register Parity Error Bits                         | 3-36 |

| Гable 3-12. | Performance Monitor                                | 3-37 |

| Гable 4-1.  | Special A0 Register Values                         | 4-5  |

| Гable 4-2.  | A Register Instructions                            | 4-6  |

| Гable 4-3.  | B Register Instructions                            | 4-11 |

| Γable 4-4.  | Special S0 Register Values                         | 4-16 |

| Гable 4-5.  | S Register Instructions                            | 4-17 |

| Гable 4-6.  | T Register Instructions                            | 4-23 |

| Гable 4-7.  | V Register Instructions                            | 4-29 |

| Table 4-8.  | Vector Mask Instructions                           | 4-34 |

| Table 6-1.  | Maintenance Channel Functions                      | 6-4  |

| Гable 6-2.  | Maintenance Channel Functions in Detail            | 6-5  |

| Table 6-3.  | Individual CPU Status Read Format (Parcel 0)       | 6-10 |

| Гable 7-1.  | CRAY Y-MP C90 and CRAY Y-MP Instruction Comparison | 7-6  |

| Гable 7-2.  | Special Register Values                            | 7-9  |

|             |                                                    |      |

# TABLES (continued)

| Table 7-3. | Channel Status Word             | 7-61 |

|------------|---------------------------------|------|

| Table 7-4  | Maintenance Modes Register Bits | 7-96 |

# 1 COMPUTER SYSTEM OVERVIEW

The Cray Research, Inc. (CRI) CRAY Y-MP C90 computer system is a powerful, general-purpose supercomputer. The large memory, dual vector functional units, and fast clock speed of the CRAY Y-MP C90 computer system provide fast throughput, allowing for more effective use of computing power. The CRAY Y-MP C90 computer system is able to achieve extremely high multiprocessing rates by efficient use of the scalar and vector processing capabilities of the multiple central processing units (CPUs), and by use of the system's solid-state, random-access memory (RAM), and shared registers.

The CRAY Y-MP C90 computer system is carefully designed to deliver optimum overall performance. The unique architecture of the CRAY Y-MP C90 computer system enhances the scalar and vector processing capabilities inherent in all CRI computer systems.

Scalar processing is a sequential operation in which one instruction produces one result. Vector processing, on the other hand, uses a single instruction to perform the same operation sequentially on a whole set of operands to produce a set of results. When two or more vector operations are chained together, two or more different operations are performed simultaneously. Therefore, the computational rate for vector processing greatly exceeds that for conventional scalar processing. Scalar operations complement the vector capability by providing solutions to problems not readily adaptable to vector techniques.

The start-up time for vector operations on the CRAY Y-MP C90 computer system is short enough so that vector processing is more efficient than scalar processing for vectors containing as few as two elements. This feature allows for rapid long and short vector processing to be balanced with high-speed scalar processing while both vector and scalar processing are supported by powerful input/output capabilities.

The multiprocessor environment of the CRAY Y-MP C90 computer system allows the use of multiprocessing or multitasking techniques. Multiprocessing allows several programs to run concurrently on multiple CPUs of a single mainframe. Multitasking allows two or more parts of a single program to run in parallel and share a common memory space.

The CRAY Y-MP C90 computer system is composed of a mainframe; up to two input/output subsystems, model E (IOS-Es); and an optional SSD solid-state storage device, model E (SSD-E). The IOS-E and SSD-E may be housed in a single cabinet. Support equipment for the mainframe

includes a heat exchanger unit (HEU) and a refrigeration condensing unit (RCU). Power distribution occurs inside the mainframe; 400-Hz power is supplied by the mainframe's motor-generator set (MGS). Support equipment for the IOS-E and SSD-E includes RCUs, a power distribution unit (PDU), and an MGS. Figure 1-1 shows a CRAY Y-MP C90 mainframe with an attached IOS-E/SSD-E and two HEUs (one for the mainframe and one for the combined IOS-E/SSD-E). For more information on support equipment for your CRAY Y-MP C90 computer system, refer to the appropriate site planning reference manual.

Figure 1-1. CRAY Y-MP C90 Computer System

Mass storage devices, such as disk drives, tape drives, and front-end interfaces (FEIs) are configured with the system through the IOS-E. A typical configuration is described in the "I/O Subsystem" subsection in this section.

#### Mainframe

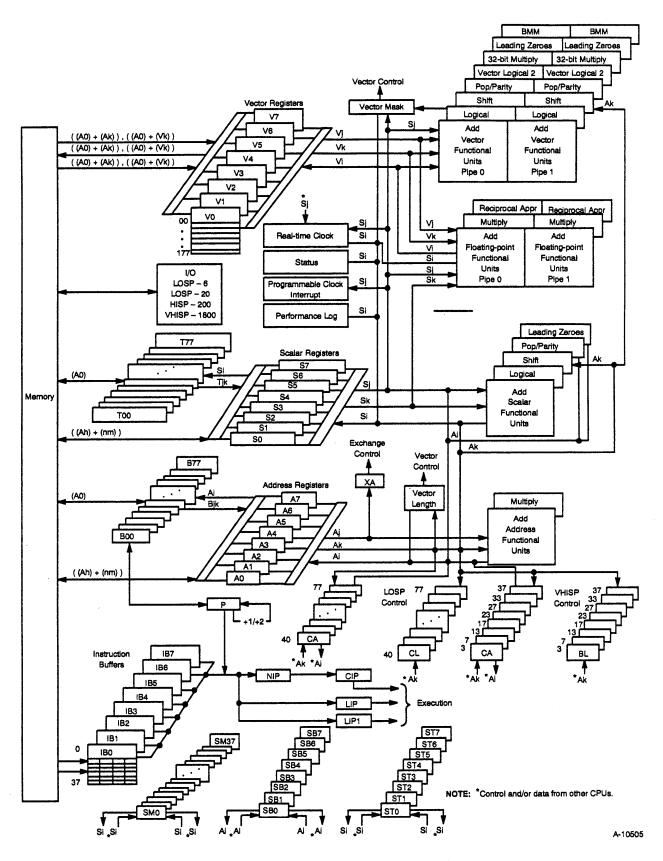

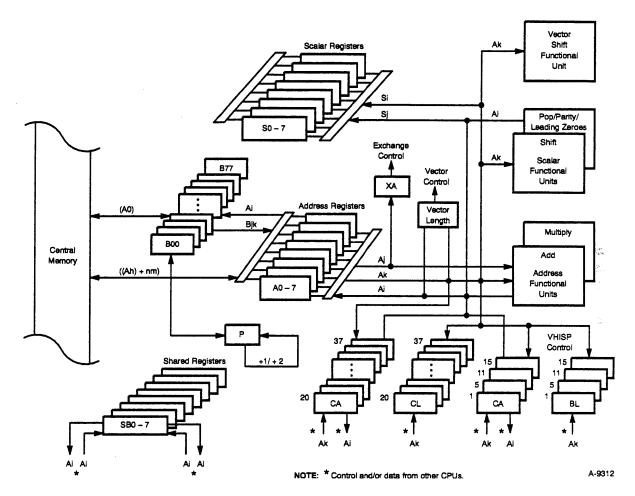

The CRAY Y-MP C90 mainframe contains the CPUs, an I/O section, an interprocessor communication section, a real-time clock, and central memory. Figure 1-2 is a block diagram of a CRAY Y-MP C90 mainframe showing one CPU with the maximum I/O configuration. Each CPU has a computation section consisting of operating registers, functional units, and a control section.

The control section determines instruction issue and coordinates the three types of processing (vector, scalar, and address). The I/O section, interprocessor communication section, real-time clock, and central memory are shared by the CPUs and are called shared resources.

Figure 1-2. CRAY Y-MP C90 CPU Block Diagram

## I/O Subsystem

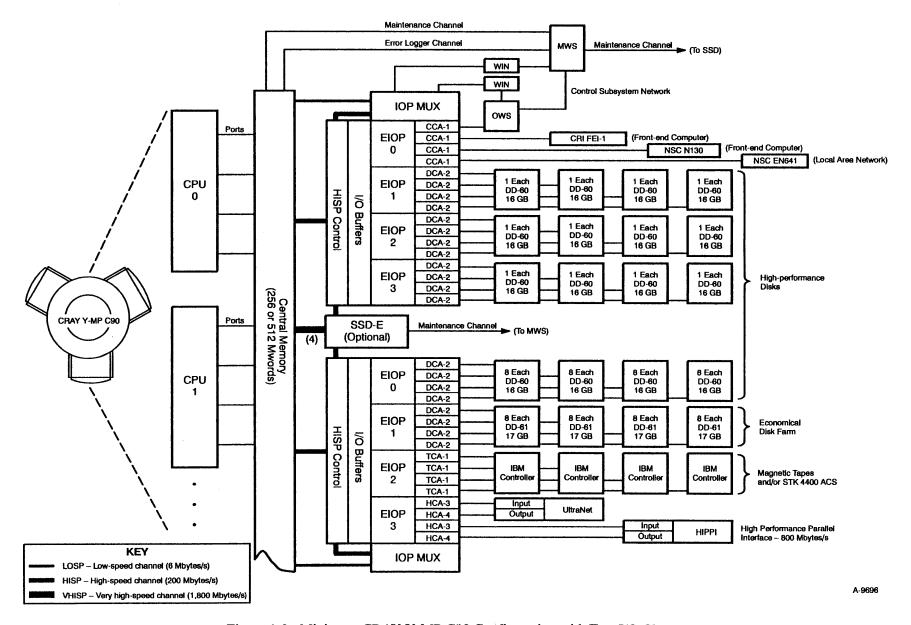

All CRAY Y-MP C90 computer systems include an IOS-E; a second IOS-E is optional. The IOS-E is designed for rapid data transfer between the IOS-E's buffer memory and front-end computers, peripheral devices, and storage devices. The IOS-E also transfers data between its buffer memory and the mainframe's central memory.

Each IOS-E contains up to eight I/O clusters depending on the site specifications. An I/O cluster comprises four I/O processors (EIOPs), each with four independent I/O buffers and four channel adapters. Each channel adapter is dedicated to a specific peripheral device. Each I/O cluster also includes a dedicated low-speed (LOSP) channel and two dedicated high-speed (HISP) channels.

Each EIOP controls different portions of the system. Each EIOP has a memory section, a control section, a computation section, and an I/O section. I/O sections are independent and control some portion of the total I/O data stream for the IOS-E. IOS-E hardware allows simultaneous data transfers between the EIOPs and the mainframe's central memory over HISP channels.

The IOS-E also provides connections to the High Performance Parallel Interface (HIPPI) channel. The HIPPI channel connects external peripheral equipment, such as high-speed graphic devices, to the mainframe. CRI does not provide external peripheral equipment but does provide the hardware connections and software drivers for the HIPPI channel.

Figure 1-3 shows the minimum configuration for a CRAY Y-MP C90 computer system with two I/O clusters. For more information on the IOS-E, refer to the IOS Model E System Programmer Reference Manual, publication number CSM-1010-000.

## SSD-E Solid-state Storage Device

The SSD-E is an optional high-performance device used for temporary data storage. The SSD-E transfers data between the mainframe's central memory and the SSD-E through special very high-speed (VHISP) channels. The actual speed of these transfers depends on the SSD-E and CRAY Y-MP C90 system configuration. The SSD-E can also be connected directly to an IOP through a HISP channel pair.

For more information on the SSD-E, refer to the SSD Solid-state Storage Device System Programmer Reference Manual, publication number CSM-1116-000.

CRAY Y-MP C90 System Programmer Reference Manual

Figure 1-3. Minimum CRAY Y-MP C90 Configuration with Two I/O Clusters

## **Disk Storage Units**

The CRAY Y-MP C90 computer system uses CRI disk storage units (DSUs) for mass data storage. A disk controller unit (DCU) serves as the interface between the DSUs and an EIOP. The EIOP and the DCU can transfer data between the EIOP and multiple DSUs without missing data or skipping revolutions. For more information on the DSUs, refer to the 60 Series Disk Systems Guide, CRI publication number COM-1124-000.

### **Network Interfaces**

The CRAY Y-MP C90 mainframe is designed to communicate easily with front-end computer systems and computer networks.

Standard front-end interfaces (FEIs) connect either the I/O channels of the CRAY Y-MP C90 mainframe or the IOS-E to front-end computer channels. These connections provide input data to the system and receive output from the system for distribution to peripheral equipment. An FEI compensates for differences in channel widths, machine word size, electrical logic levels, and control signals.

Some FEIs are housed in a stand-alone cabinet located near the host computer, and others are installed directly into the front-end computer system. Operation of the FEI is transparent to both the front-end computer and CRI system users.

As an option, a fiber-optic link (FOL-3) is available for some FEIs to provide front-end connections of up to 6,560 ft (2,000 m) and complete electrical separation from the CRAY Y-MP C90 computer system.

The CRAY Y-MP C90 mainframe can be connected to computer networks directly or through a front-end computer system.

## **Operator and Maintenance Workstations**

The operator workstation (OWS-E) and the maintenance workstation (MWS-E) are based on a Sun 4/370 SPARCstation, 12-slot chassis. The SPARCstation is a Sun version of the reduced instruction set computer (RISC) architecture. A VMEbus is provided in slots 4 through 12 of the workstations.

Both workstations run the SunOS 4.1.1 operating system and OpenWindows 2.0 software; the MWS-E also runs the ME maintenance diagnostic software release, and the OWS-E runs the OWS-E software release. The Sun operating system is an enhanced version of UNIX; it combines features of UNIX System Laboratories, Inc.'s System V UNIX and Berkeley Software Distribution's version 4.3 UNIX.

The OWS-E is part of the CRAY Y-MP C90 computer system. The MWS-E is owned by CRI and is supplied as part of the maintenance contract; it enables CRI engineers to perform system maintenance independent of any customer activity on the system.

The OWS-E and MWS-E communicate through the Control Subsystem Network, which is a dedicated, modified, Ethernet cable link used only for maintenance and control-related functions.

The OWS-E provides a dedicated workstation that Cray Research analysts and customer operators use to operate, administrate, and monitor a Cray Research computer system. The OWS-E is also used for system boot, dump, and clear operations and for software and upgrade support.

The OWS-E communicates with the CRAY Y-MP C90 computer system through a LOSP channel from EIOP 0 in the IOS-E. The LOSP channel allows the mainframe to use the tape drives, disk drives, printer, and time-of-day clock. The OWS-E also provides an Ethernet interface to network workstations in a multiple-system site or for multiple-system operators.

The MWS-E provides multiple connections for hardware maintenance and monitoring of the CRAY Y-MP C90 computer system. The MWS-E supports CRI diagnostics, enhanced diagnostic displays, code simulation, and maintenance and error channels. It monitors environmental conditions and can shut down the system if severe variances occur. The MWS-E also serves as a platform for remote support, with customer approval. The MWS-E communicates with the CRAY Y-MP C90 computer system through a LOSP maintenance channel from the IOS-E.

Refer to the following publications for additional information on the OWS-E and MWS-E:

- MWS-E User Guide, CRI publication number CDM-1123-0A0.

- Operator Workstation (OWS) Guide, CRI publication number SN-3030.

- MWS-E and OWS-E Hardware Maintenance Manual, CRI publication number CMM-1122-0A0.

# 2 CPU SHARED RESOURCES

All central processing units (CPUs) in the CRAY Y-MP C90 mainframe share the following resources:

- Central memory

- I/O section

- Interprocessor communication section

- Real-time clock

## **Central Memory**

Central memory consists of solid-state, random-access memory (RAM) that is shared by all the CPUs and the I/O section. Each memory word consists of 80 bits: 64 data bits and 16 error-correction bits (check bits). Storage for data and check bits is provided by 256 Kbyte x 4 bit bipolar complementary metal oxide semiconductor (BiCMOS) chips with a 15-ns access time. In order to improve memory access speed, central memory is divided into multiple banks that can be active simultaneously. The banks have a 6-clock period (CP) cycle time; each bank can be accessed once every 6 CPs.

In each CPU, the operating registers, instruction buffers, and exchange package have access to central memory through memory ports. Each CPU has four ports. Each of these ports is 2 words wide, allowing up to eight simultaneous memory references from each CPU. The I/O section shares one port in each CPU.

## **Memory Instructions**

Table 2-1 shows all the CPU machine instructions that transfer data between CPU registers and central memory, or that affect memory operation. The contents of the data base address (DBA) register are added to instruction-generated memory addresses to form absolute memory addresses. Refer to "Absolute Memory Address Calculating" later in this section.

|                           |                           | Table 2-1. Memory Instructions                                                                   |                |  |  |  |

|---------------------------|---------------------------|--------------------------------------------------------------------------------------------------|----------------|--|--|--|

| Machine<br>Instruction    | CAL<br>Syntax             | Type of<br>Memory Reference                                                                      |                |  |  |  |

| 10 <i>hi</i> 00 <i>nm</i> | Ai exp,Ah                 | Read from $((Ah) + exp + (DBA))$ to Ai.                                                          | Scalar         |  |  |  |

| 11 <i>hi</i> 00 <i>nm</i> | exp,Ah Ai                 | Write (Ai) to ((Ah) + $exp$ + (DBA).                                                             |                |  |  |  |

| 12hi00 nm                 | Si exp,Ah                 | Read from $((Ah) + exp + (DBA))$ to Si.                                                          |                |  |  |  |

| 13 <i>hi</i> 00 <i>nm</i> | exp,Ah Si                 | Write (Si) to ((Ah) + $exp$ + (DBA).                                                             |                |  |  |  |

| 034 <i>ijk</i>            | Bjk,Ai ,A0                | Read (Ai) words starting at address (A0) + (DBA) to B registers starting at register jk.         | Block Transfer |  |  |  |

| 035 <i>ijk</i>            | ,A0 Bjk,Ai                | Write (Ai) words from B registers starting at register $jk$ to memory starting at (A0) + (DBA).  |                |  |  |  |

| 036 <i>ijk</i>            | Tjk,Ai ,A0                | Read (Ai) words starting at address (A0) + (DBA) to T registers starting at register jk.         |                |  |  |  |

| 037 <i>ijk</i>            | ,A0 Tjk,Ai                | Write (Ai) words from T registers starting at register jk to memory starting at (A0) + (DBA).    |                |  |  |  |

| 176 <i>i</i> 0 <i>k</i>   | Vi ,A0,Ak                 | Vi, A0,A $k$ Read (VL) words to $Vi$ starting at address (A0) + (DBA), incrementing by (A $k$ ). |                |  |  |  |

| 1770 <i>jk</i>            | ,A0,Ak Vj                 | Write (VL) words from (Vj) to memory starting at address (A0) + (DBA), incrementing by (Ak).     |                |  |  |  |

| 176 <i>i</i> 1 <i>k</i>   | Vi ,A0,Vk                 | Read (VL) words to $\forall i$ using memory addresses ((A0) + ( $\forall k$ ) + (DBA)).          | Gather         |  |  |  |

| 1771 <i>jk</i>            | ,A0,V <i>k</i> V <i>j</i> | Write (VL) words from (Vj) to memory using memory addresses ((A0) + (Vk) + (DBA)).               | Scatter        |  |  |  |

| 002300                    | ERI                       | Enable interrupt on operand range error.                                                         | None           |  |  |  |

| 002301                    | EBP                       | Enable interrupt on breakpoint.                                                                  |                |  |  |  |

| 002400                    | DRI                       | Disable interrupt on operand range error.                                                        |                |  |  |  |

| 002401                    | DBP                       | Disable interrupt on breakpoint.                                                                 |                |  |  |  |

| 002500                    | DBM                       | Disable bidirectional memory transfers.                                                          |                |  |  |  |

| 002600                    | ЕВМ                       | Enable bidirectional memory transfers.                                                           |                |  |  |  |

| 002700                    | CMR                       | Complete memory references.                                                                      |                |  |  |  |

| 002704                    | СРА                       | Complete port reads and writes.                                                                  |                |  |  |  |

| Table 2-1. Memory Instructions (continued)                          |     |                       |  |  |  |  |  |

|---------------------------------------------------------------------|-----|-----------------------|--|--|--|--|--|

| Machine CAL Type of Instruction Syntax Description Memory Reference |     |                       |  |  |  |  |  |

| 002705                                                              | CPR | None                  |  |  |  |  |  |

| 002706                                                              | CPW | Complete port writes. |  |  |  |  |  |

Instructions 10h through 13h perform scalar references; each instruction causes only 1 word to be transferred to or from memory. Instructions 034ijk through 037ijk perform block transfers. Each instruction transfers a block of from 1 to 127 words to or from consecutive locations in memory. Instructions 176i0k and 1770jk perform stride references. A block of from 1 to 128 words are transferred to or from memory locations separated by a constant increment (stride). Instructions 176i1k and 1771jk perform gather and scatter references. These instructions transfer from 1 to 128 words to or from randomly programmable locations in memory.

Instructions 002300 through 002706 affect memory operation.

Instructions 002300 and 002400 set and clear the interrupt-on-operand range error (IOR) interrupt mode. When this interrupt mode is set and enabled, it allows interrupts on operand range errors. Refer to "Address Range Checking" in this section for a more complete explanation.

Instructions 002301 and 002401 set and clear the interrupt-on-breakpoint (IBP) interrupt mode. When this interrupt mode is set and enabled, it allows interrupts on write references within the breakpoint range, which should be set previously by instruction 0017jk.

Instructions 002500 and 002600 disable and enable the bidirectional memory mode. When this mode is enabled, block read and write operations can operate concurrently. When this mode is disabled, only block read operations can operate concurrently.

Instruction 002700 ensures completion of all memory references within the particular CPU issuing the instruction. Instruction 002700 does not issue until all previous memory references can complete in a fixed number of CPs. For example, a CPU is assured of receiving updated data when it issues a memory read instruction after instruction 002700. Used in conjunction with semaphore instructions, this instruction synchronizes memory references between processors.

Instructions 002704 through 002706 can be used to ensure sequential memory referencing within a CPU. These instructions do not issue until all previous memory references are at a stage of execution such that they

can run to completion before any subsequent memory references. Instruction 002704 ensures that all read and write references are at this stage. Instruction 002705 ensures that all read references are at this stage, and instruction 002706 ensures that all write references are at this stage.

In addition to direct memory references generated by CPU machine instructions, there are three ways that memory references are generated indirectly. First, a no-coincidence condition in a CPU causes an instruction fetch sequence to begin, during which 32 consecutive words are read from central memory to an instruction buffer. Second, an exchange sequence in a CPU causes 16 words to be read from and 16 words to be written into central memory. (For details on the fetch and exchange sequences, refer to "Exchange Mechanism" and "Instruction Fetch Sequence" in Section 3 of this manual.) The third type of indirect memory reference occurs when an I/O transfer to or from an external device causes a block of words to be read from or written to central memory. For details on I/O transfers, refer to "I/O Section" in this section.

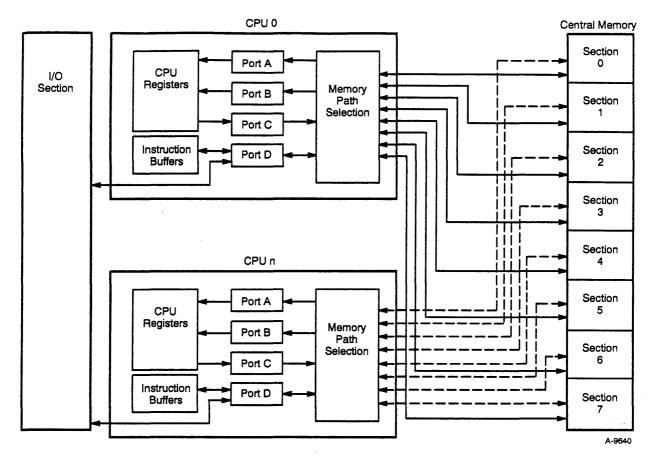

### **Logical Organization**

Figure 2-1 shows a CPU's memory ports and paths to central memory. Refer to this figure while reading the following paragraphs. Central memory is divided into 8 sections. Each section is divided into 8 subsections, and each subsection contains two 8-bank groups. This makes a total of 1,024 banks. This arrangement permits simultaneous memory references (two or more memory references that begin in the same CP) and overlapping memory references (one or more memory references that begin while another reference is in progress).

#### **Memory Paths**

Each CPU has an independent path into each memory section. (The I/O section does not have its own paths, but shares the paths of each CPU.) Independent paths allow each CPU to make up to eight simultaneous memory references, one reference to each section. Each CPU can have overlapping references in different sections without restrictions or within a section as long as each reference uses a different subsection. Simultaneous references to the same section are not permitted because each CPU has only one memory path into each memory section.

Figure 2-1. Central Memory Architecture

Simultaneous and overlapping memory references involving two or more CPUs have fewer restrictions than those involving a single CPU. Simultaneous and overlapping memory references from different CPUs can occur within a section and a subsection; however, each reference must use a different bank.

#### **Memory Ports**

Each CPU has four memory ports through which the CPU accesses its paths to central memory. Each port contains two pipes, allowing up to eight simultaneous memory references per CPU. Table 2-2 lists the specific read and write references allocated to each of the ports and pipes.

| Table 2-2. Allocation of Memory References to Ports and Pipes |      |                |                                                                                                                                                                      |  |  |  |  |

|---------------------------------------------------------------|------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Port                                                          | Pipe | Reference Type | User                                                                                                                                                                 |  |  |  |  |

| A                                                             | 0    | Read           | A registers (10 <i>h</i> instruction) B registers (034 instruction) S registers (12 <i>h</i> instruction) V registers (176 instructions) Exchange data               |  |  |  |  |

| Α                                                             | 1    | Read           | B registers (034 instruction)<br>V registers (176 instructions)                                                                                                      |  |  |  |  |

| В                                                             | 0    | Read           | T registers (036 instruction)<br>V registers (176 instructions)                                                                                                      |  |  |  |  |

| В                                                             | 1    | Read           | T registers (036 instruction)<br>V registers (176 instructions)                                                                                                      |  |  |  |  |

| С                                                             | 0    | Write          | A registers (11h instruction) B registers (035 instruction) S registers (13h instruction) T registers (037 instruction) V registers (177 instructions) Exchange data |  |  |  |  |

| С                                                             | 1    | Write          | B registers (035 instruction)<br>T registers (037 instruction)<br>V registers (177 instructions)                                                                     |  |  |  |  |

| D                                                             | 0    | Read and Write | Instruction buffers<br>I/O section                                                                                                                                   |  |  |  |  |

| D                                                             | 1    | Read and Write | Instruction buffers<br>I/O section                                                                                                                                   |  |  |  |  |

Ports A, B, and C are used by memory reference instructions and by the exchange sequence. Port D is used by the instruction buffers and the I/O section. With the exception of memory reads to vector (V) registers (instructions 176i0k and 176i1k), each type of memory reference uses one specific port. On a read to a V register, port B is used if available. If port B is reserved, port A is used if available. If both ports are reserved, the instruction holds issue until one of the ports is available. If both ports become available at the same time, port B is used.

The usage of either pipe 0 or pipe 1 depends on the type of reference to the port. For vector references, the even elements use pipe 0 and the odd elements use pipe 1. For fetch references, the even-address memory words use pipe 0 and the odd-address memory words use pipe 1. For B

and T register block transfers, the first word transferred always uses pipe 0, and the next word uses pipe 1; subsequent words alternate between the two pipes until the transfer is complete.

Ports A, B, and C

Ports A, B, and C operate differently for block and vector transfers than for scalar transfers. A memory reference instruction that transfers data to or from B, T, or V registers holds issue if the associated port is in use by another memory operation. When the port becomes available, the instruction issues and reserves the port. The port remains reserved until the instruction completes all its memory references. The port reservation is then cleared, making the port available for other memory operations. A block or vector transfer normally reads or writes 2 words of data each clock period (CP). However, if the instruction encounters a memory conflict during its execution, it temporarily suspends operation until the conflict is resolved. Therefore, the number of CPs the instruction runs and the number of CPs the port is reserved are unpredictable. Refer to "Conflict Resolution" in this section for additional information on port conflicts.

Block and vector transfer instructions that use different ports normally operate simultaneously. Under some circumstances, this mode of operation can cause memory references to occur in an unwanted sequence. For example, if instruction 035ijk (write to memory from a block of B registers) precedes instruction 176i0k (read from memory to a V register) and both instructions reference one or more of the same memory addresses, data from some memory addresses may be read before the new data is written to them. Both of these instructions can operate simultaneously, and the read instruction may reference an address before the write instruction.

There are several ways to prevent out-of-sequence references. Instruction 002700 (complete memory references), instruction 002704 (complete port reads and writes), or instruction 002706 (complete port writes) can be inserted between the write and read instructions. Although these instructions do not perform any operation, they prevent the read instruction from issuing until the write instruction completes all its memory references and clears the port C reservation. Usually, instructions 002704 and 002706 are used to insure sequential memory referencing within a CPU, and instruction 002700 is used to synchronize memory references between CPUs.

Clearing the bidirectional memory (BDM) mode in the exchange package also prevents out-of-sequence memory references. In this case, instructions that use port A or B also require port C to be available, and instructions that use port C require ports A and B to be available. The memory read instruction holds issue until the write instruction completes all its memory references.

Before it can issue, a scalar transfer instruction requires that ports A, B, and C be available to ensure sequential operation between block transfers and scalar references within a CPU. A scalar reference conflict is detected in CP 4 of execution. If a conflict occurs, up to two additional scalar references are still allowed to issue. A fourth scalar reference holds issue if the first reference still has a conflict. Scalar references always execute in the order they are issued within a CPU.

#### Port D

An instruction fetch sequence has priority over an I/O transfer in port D. That is, if a fetch request occurs while an I/O transfer is in progress, the I/O transfer is suspended and the fetch begins. When the fetch completes, the I/O transfer continues.

#### **Conflict Resolution**

A memory conflict occurs whenever a memory port tries to access a shared part of memory in use, or whenever two or more ports try to access a shared part of memory at the same time. Intra-CPU conflicts involve ports in the same CPU. Inter-CPU conflicts involve ports in different CPUs. In both cases, conflict resolution logic uses predefined priority schemes to sequence the conflicting memory references and to maximize overall machine throughput.

There are five types of memory conflicts: section, subsection, simultaneous subsection access, bank busy, and write bank busy. The following paragraphs explain each type of conflict and how the conflict is resolved.

#### **Section Conflict**

A section conflict occurs when two or more ports in the same CPU simultaneously attempt to access the same memory section. A section conflict occurs because there is only one path from each CPU to each memory section. The port with the highest priority level and no subsection conflict is allowed to begin its reference. All other conflicting ports hold reference for 1 CP. The following rules determine priorities between conflicting ports:

• Port D has priority over ports A, B, and C when it is used for an instruction fetch sequence.

- Port D normally has a lower priority than ports A, B, and C when it is used for an I/O transfer. However, if a port D I/O memory reference is forced to hold for 32 CPs, port D is temporarily given top priority so that one memory reference can proceed. Port D returns to a low-priority status after the reference begins.

- Among ports A, B, and C, any port that has an odd memory address increment has priority over ports that have an even increment. The following rules determine the type of increment (even or odd) for each port:

- A port used by a block reference instruction has an address increment of 1, which is odd.

- A port used by a stride reference instruction can have any constant increment (even or odd).

- A port used by a gather or scatter instruction can have an increment that changes after each reference. For the purpose of conflict resolution, a gather or scatter instruction is always considered to have an odd increment.

- Among ports A, B, and C with the same type of memory increment, priority is determined by the relative time of instruction issue. The port used by the instruction first issued has the highest priority.

#### **Subsection Conflict**

Subsection conflicts occur because each memory reference by a CPU makes an entire memory subsection unavailable to all ports in the same CPU for 7 CPs. A subsection conflict occurs if any port in the same CPU attempts to make a reference to the same subsection during this interval. The new reference holds for 1 to 6 CPs until the old reference no longer needs the subsection. Subsection conflicts usually involve two or more ports, but may involve two references from the same port.

If two or more references are holding issue because of the same subsection conflict, a section conflict occurs immediately following the resolution of the subsection conflict. Another subsection conflict occurs 1 CP after the section conflict. For example, if port A is using a subsection and ports B and C attempt to use the same subsection while it is busy, ports B and C hold issue because of the subsection conflict. When the reference from port A no longer needs the subsection, the subsection conflicts disappear. Ports B and C are involved in a section conflict, which is resolved according to the priority rules previously described. The port with the higher priority makes its reference, and the port with the lower priority encounters a subsection conflict.

#### Simultaneous Subsection Access Conflict

Simultaneous subsection access conflicts occur when two or more ports in different CPUs attempt to access the same memory bank group at the same time. The CPU with the highest priority is allowed to make its reference. All other CPUs attempting to access the same bank group hold their references for 1 CP. Relative priorities between CPUs are determined by the value stored in a priority counter. This value increments by 1 each CP. For a given value of the priority counter, each of the CPUs is assigned the priority shown in Table 2-3. For example, if the priority count is 5, then CPU 5 has the highest priority and CPU 12 has the lowest priority. Following a simultaneous subsection access conflict, each CPU port forced to hold a reference encounters a bank-busy conflict.

| Table 2-3. CPU Priority Matrix |      |                    |    |    |    |    |    |    |    |       |        |         |    |    |    |    |

|--------------------------------|------|--------------------|----|----|----|----|----|----|----|-------|--------|---------|----|----|----|----|

| Priority<br>Count              | High | Highest Priority - |    |    |    |    |    |    |    | - Low | est Pr | riority |    |    |    |    |

| 0                              | 0    | 1                  | 2  | 3  | 4  | 5  | 6  | 7  | 10 | 11    | 12     | 13      | 14 | 15 | 16 | 17 |

| 1                              | 1    | 0                  | 3  | 2  | 5  | 4  | 7  | 6  | 11 | 10    | 13     | 12      | 15 | 14 | 17 | 16 |

| 2                              | 2    | 3                  | 0  | 1  | 6  | 7  | 4  | 5  | 12 | 13    | 10     | 11      | 16 | 12 | 14 | 15 |

| 3                              | 3    | 2                  | 1  | 0  | 7  | 6  | 5  | 4  | 13 | 12    | 11     | 10      | 17 | 16 | 15 | 14 |

| 4                              | 4    | 5                  | 6  | 7  | 0  | 1  | 2  | 3  | 14 | 15    | 16     | 17      | 10 | 11 | 12 | 13 |

| 5                              | 5    | 4                  | 7  | 6  | 1  | 0  | 3  | 2  | 15 | 14    | 17     | 16      | 11 | 10 | 13 | 12 |

| 6                              | 6    | 7                  | 4  | 5  | 2  | 3  | 0  | 1  | 16 | 17    | 14     | 15      | 12 | 13 | 10 | 11 |

| 7                              | 7    | 6                  | 5  | 4  | 3  | 2  | 1  | 0  | 17 | 16    | 15     | 14      | 13 | 12 | 11 | 10 |

| 10                             | 10   | 11                 | 12 | 13 | 14 | 15 | 16 | 17 | 0  | 1     | 2      | 3       | 4  | 5  | 6  | 7  |

| 11                             | 11   | 10                 | 13 | 12 | 15 | 14 | 17 | 16 | 1  | 0     | 3      | 2       | 5  | 4  | 7  | 6  |

| 12                             | 12   | 13                 | 10 | 11 | 16 | 17 | 14 | 15 | 2  | 3     | 0      | 1       | 6  | 7  | 4  | 5  |

| 13                             | 13   | 12                 | 11 | 10 | 17 | 16 | 15 | 14 | 3  | 2     | 1      | 0       | 7  | 6  | 5  | 4  |

| 14                             | 14   | 15                 | 16 | 17 | 10 | 11 | 12 | 13 | 4  | 5     | 6      | 7       | 0  | 1  | 2  | 3  |

| 15                             | 15   | 14                 | 17 | 16 | 11 | 10 | 13 | 12 | 5  | 4     | 7      | 6       | 1  | 0  | 3  | 2  |

| 16                             | 16   | 17                 | 14 | 15 | 12 | 13 | 10 | 11 | 6  | 7     | 4      | 5       | 2  | 3  | 0  | 1  |

| 17                             | 17   | 16                 | 15 | 14 | 13 | 12 | 11 | 10 | 7  | 6     | 5      | 4       | 3  | 2  | 1  | 0  |

#### Bank-busy Conflict

Bank-busy conflicts occur because each memory reference by a CPU makes the referenced memory bank unavailable to all ports in all other CPUs for 6 CPs. A bank-busy conflict occurs if any port in a different CPU attempts to make a reference to the same bank during this interval. The new reference holds from 1 to 5 CPs until the old reference no longer needs the bank. If two or more CPUs are holding because of the same bank-busy conflict, a simultaneous subsection access conflict occurs immediately following resolution of the bank-busy conflict.

#### Write Bank-busy Conflict

Write bank-busy conflicts occur because within a subsection each write data path is shared between two memory banks. Banks 0 and 4, 1 and 5, 2 and 6, and 3 and 7 share write data paths. When a write reference is made by a CPU to a memory bank, both memory banks in the pair are unavailable to all ports in all other CPUs for 6 CPs. A write bank-busy conflict occurs if any port in a different CPU attempts to make a reference to either bank during this interval. The new reference holds from 1 to 5 CPs until the old write reference no longer needs the bank. If two or more CPUs are holding because of the same write bank-busy conflict, a simultaneous subsection access conflict occurs immediately following resolution of the write bank-busy conflict. Table 2-4 summarizes the five types of memory conflicts.

| Table 2-4. Memory Conflicts          |               |               |                                                                                                    |                                                                                                     |  |  |  |  |

|--------------------------------------|---------------|---------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| Conflict                             | Type          | Duration      | Resolution                                                                                         | Comment                                                                                             |  |  |  |  |

| Section                              | Intra-<br>CPU | 1 CP          | The highest-priority port with no subsection conflict makes reference. Other ports hold reference. | Followed by a subsection conflict if references are made to the same subsection.                    |  |  |  |  |

| Subsection                           | Intra-<br>CPU | 1 to 6<br>CPs |                                                                                                    |                                                                                                     |  |  |  |  |

| Simultaneous<br>Subsection<br>Access | Inter-<br>CPU | 1CP           | The highest-priority CPU makes reference. Other CPUs hold reference.                               | Followed by a bank-busy conflict in each CPU that was forced to hold.                               |  |  |  |  |