# UNISYS

# BTOS Protected Mode

### Programming Guide

Relative to Release Level 1.0

Priced Item

February 1987 Distribution Code SA Printed in U S America 5026065

# UNISYS

# BTOS Protected Mode

Programming Guide

Copyright © 1987, Unisys Corporation Detroit, Michigan 48232

Relative to Release Level 1.0

February 1987 Distribution Code SA Printed in U S America 5026065

Priced Item

NO WARRANTIES OF ANY NATURE ARE EXTENDED BY THIS DOCUMENT. Any product and related material disclosed herein are only furnished pursuant and subject to the terms and conditions of a duly executed Program Product License or Agreement to purchase or lease equipment. The only warranties made by Unisys, if any, with respect to the products described in this document are set forth in such License or Agreement. Unisys cannot accept any financial or other responsibility that may be the result of your use of the information or software material, including direct, indirect, special or consequential damages.

You should be very careful to ensure that the use of this information and/or software material complies with the laws, and regulations of the jurisdictions with respect to which it is used.

The information contained herein is subject to change without notice. Revisions may be issued to advise of such changes and/or additions.

<sup>®</sup>Intel is a registered trademark of Intel Corporation.

Comments or suggestions regarding this document should be submitted on a Field Communication Form (FCF) with the CLASS specified as 2 (S.SW:System Software), the Type specified as 1 (F.T.R.), and the product specified as the seven-diait form number of the manual (for example, 5026065).

## **About This Guide**

Protected mode allows you to address up to 4 Mb of memory on B 28 and B 38 workstations that have BTOS 8.0 installed, limit damage caused by erroneous programs, and dynamically allocate memory more effectively than in real-address mode. This guide describes the protected mode capabilities of the Intel 80286 and 80386 microprocessors. It includes examples specific to BTOS and the B 28 and B 38 workstations.

#### Who Should Use This Guide

This guide will help you if you are an experienced BTOS programmer. To understand the information in this guide, you must be familiar with BTOS 8.0.

#### How to Use This Guide

If you are using the protected mode for the first time, you should read section 1. It contains information you will need to understand basic protected mode concepts.

In any case, if you scan the table of contents and review the topics before you start, you may find this guide easier to use. To find definitions of unfamiliar words or mnemonics, use the glossary; to locate specific information, use the Index.

#### How This Guide is Arranged

This material is divided into sections, with related subjects grouped together. Section 1 describes the basic concepts involved in protected mode operations.

Sections 2 and 3 describe how to write and debug protected mode programs. Section 4 describes the RAM-disk cache facility that the Protected Mode Operating System Service (PMOSS) provides.

Appendixes A and B describe programming interfaces discussed in this guide.

## **Conventions**

The Intel 80386 microprocessor is a proper superset of the 80286 microprocessor. Unless otherwise stated, references to the 80286 microprocessor in this guide include the 80386 microprocessor.

What this guide refers to as a **process**, Intel refers to as a **task**. This guide uses the term **task** to mean an entire executing program, which may contain multiple processes. This guide uses the Intel terminology only when referring to a specific hardware-defined control structure, the task state segment (TSS), which you may think of as a process state segment.

The following conventions are also used in this guide:

| Convention | Meaning                                                                                                                          |

|------------|----------------------------------------------------------------------------------------------------------------------------------|

| LDT        | Local Descriptor Table, which PMOSS constructs and maintains for each run file executing in protected mode.                      |

| RA         | Relative address, which comprises one-half<br>of the linear address. Often referred to as<br>an offset from the segment address. |

| SA         | Segment address, which comprises one-half of the linear address.                                                                 |

| SN         | A segment address that is in protected mode.                                                                                     |

| SR         | A segment address that is a paragraph number (a real-address mode SA).                                                           |

When two keys are used together for an operation, their names are hyphenated. For example, **ACTION-GO** means you hold down **ACTION** and press **GO**.

#### **Related Documentation**

For information on protected mode addressing with the 80286 microprocessor, refer to the *iAPX 286 Programmer's Reference Manual*, published by Intel Corporation.

For information on protected mode addressing with the 80386 microprocessor, refer to the 80386 Programmer's Reference Manual, published by Intel Corporation.

For information on the System Performance Accelerator (SPA), refer to the BTOS System Performance Accelerator (SPA) Installation Guide. (

## **Contents**

| About This Guide                           | v    |

|--------------------------------------------|------|

| Who Should Use This Guide                  | v    |

| How to Use This Guide                      | v    |

| How This Guide is Arranged                 | v    |

| Conventions                                | vi   |

| Related Documentation                      | vii  |

|                                            |      |

| Section 1: Introduction to Protected Mode  | 1-1  |

| Overview of Protected Mode                 | 1-1  |

| Reviewing Segmented Addressing             | 1-2  |

| Reviewing Real Address Mode                | 1-3  |

| Protected Mode Addresses                   | 1-4  |

| The Selector                               | 1-7  |

| Descriptor Tables                          | 1-7  |

| Descriptor Cache Registers                 | 1-8  |

| Faults                                     | 1-9  |

| Descriptor Types                           | 1-10 |

| Segment Descriptors                        | 1-10 |

| Gate Descriptors                           | 1-12 |

| Protection                                 | 1-14 |

| DPL versus RPL                             | 1-19 |

| Current Privilege Level (CPL)              | 1-19 |

| Switching Privilege Levels with Call Gates | 1-20 |

| IOPL                                       | 1-21 |

| General Protection Faults                  | 1-21 |

| Processes and Process Switching            | 1-21 |

| Interrupts                                 | 1-24 |

|                                            |      |

| Section 2: Guide to Compatible Programming | 2-1  |

| 80286 Real Mode Issues                     | 2-1  |

| Guidelines for Addressing Schemes          | 2-1  |

| Linking                                    | 2-15 |

| Version 6 Run File Format                  | 2-15 |

| Marking the Run File                       | 2-15 |

| Contiguous Code and Data                   | 2-17 |

| Remedies for Incompatibilities             | 2-18 |

| Checking for Protected Mode at Run Time    | 2-18 |

| PMOSS Limitations                          | 2-18 |

| Naming Conventions                         | 2-19 |

| New Machine Instructions                   | 2-20 |

| 80286 Instructions                         | 2-20 |

| 80186 Instructions                         | 2-20 |

|                                            |      |

| Section 3: Debugging Protected Mode Programs | 3-1  |

|----------------------------------------------|------|

| Overview                                     | 3-1  |

| The PR Value and Its Meaning                 | 3-1  |

| Looking at Processes: CODE-S                 | 3-4  |

| Entering the Debugger                        | 3-5  |

| Accessing 80286 Registers                    | 3-6  |

| Mnemonics                                    | 3-6  |

| Warnings                                     | 3-7  |

| Finding the BTOS Process                     | 3-7  |

| Breakpoints                                  | 3-8  |

| CODE-B Breakpoints                           | 3-8  |

| CODE-I Breakpoints                           | 3-9  |

| Descriptors: CODE-V                          | 3-10 |

| Segment Descriptors                          | 3-10 |

| Gate Descriptors                             | 3-11 |

| Effect of Call Gates on Debugging            | 3-12 |

| Behavior at a Fault                          | 3-13 |

| Debugging PMOSS Interrupt Service Routines   | 3-14 |

| Allowing the System to Enter the Debugger    | 3-15 |

| Locking the Debugger in Memory               | 3-16 |

|                                              |      |

| Section 4: SPA Mover Interface               | 4-1  |

| Procedural Interfaces                        | 4-1  |

| Mover Segments                               | 4-2  |

| Validation Checks                            | 4-4  |

|                                              |      |

| Appendix A: New Procedural Interfaces        | A-1  |

| AllocAllMemorySL                             | A-2  |

| AllocAreaSL                                  | A-4  |

| AllocMemoryLL                                | A-6  |

| AllocMemorySL                                | A-7  |

| AllocMoverSegment                            | A-9  |

| DeallocMemoryLL                              | A-11 |

| DeallocMemorySL                              | A-12 |

| DeallocMoverSegment                          | A-13 |

| ExpandAreaLL                                 | A-15 |

| ExpandAreaSL                                 | A-16 |

| FComparePointer                              | A-18 |

| ForwardRequest                               | A-20 |

| FProcessorSupportsProtectedMode              | A-21 |

| FProtectedMode                                  | A-22 |

|-------------------------------------------------|------|

| MovbMoverSegment                                | A-23 |

| QueryBigMemÄvail                                | A-25 |

| QueryMemAvail                                   | A-27 |

| SetPStructure                                   | A-28 |

| ShrinkAreaLL                                    | A-31 |

| ShrinkAreaSL                                    | A-32 |

| Appendix B: Summary of GetPStructure Interfaces | B-1  |

| Access to System Data Structures                | B-1  |

| Limitations in Protected Mode                   | B-1  |

| GetPStructure Codes                             | B-2  |

| SetPStructure Cases Supported                   | B-2  |

## Illustrations

| 1-1  | Real Address Mode                              | 1-4  |

|------|------------------------------------------------|------|

| 1-2  | Protected Mode                                 | 1-6  |

| 1-3  | Anatomy of a Selector                          | 1-7  |

| 1-4  | Segment Descriptor                             | 1-11 |

| 1-5  | Gate Descriptor                                | 1-13 |

| 1-6  | Separate Address Spaces Protection Model       | 1-15 |

| 1-7  | PMOSS' Simplified Use of Separate Address      |      |

|      | Space Protection Model                         | 1-16 |

| 1-8  | Ring Protection Model                          | 1-17 |

| 1-9  | PMOSS' Simplified Use of Ring Model            | 1-18 |

| 1-10 | Task State Segment (TSS)                       | 1-22 |

| 2-1  | BTOS Partition Using DS Allocation             | 2-4  |

| 2-2  | Two-way Filter Process (no change required for |      |

|      | protected mode)                                | 2-8  |

| 2-3  | One-way Filter Process (change as shown for    |      |

|      | protected mode)                                | 2-10 |

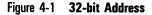

| 4-1  | 32-bit Address                                 | 4-3  |

|      |                                                |      |

# Tables

| B-1 | <b>GetPStructure Cases Supported</b> | <br>B-3 |

|-----|--------------------------------------|---------|

| B-2 | SetPStructure Cases Supported        | <br>B-4 |

## **Introduction to Protected Mode**

This section summarizes protected mode addressing concepts. It serves as an introduction to the Intel *iAPX 286 Programmer's Reference Manual* and *80386 Programmer's Reference Manual*.

**Note:** This guide refers to some Intel conventions differently than the way Intel refers to them. For more information, refer to Conventions, in the introduction.

### **Overview of Protected Mode**

Intel microprocessors beginning with 80286 (for B 28 workstations) and including the 80386 (for B 38 workstations) support protected mode operation. Their predecessors, 8086 (for B 21 and B 22 workstations) and 80186 (for B 26 workstations), support the real address mode only.

Protected mode offers the following advantages over real address mode:

- a much larger address space (memory) is available, eliminating the 1 Mb constraint of real address mode

- program execution is subject to protection checks that limit damage from erroneous programs

- on-chip memory management hardware is available, allowing an operating system to dynamically allocate memory more effectively

- with the Protected Mode Operating System Server (PMOSS), the code segments of the system services can be executed in protected mode

**Note:** PMOSS develops system services that will run on the fully protected mode operating system. It also frees memory space in the real address range.

Two constraints when using protected mode are:

Because addressing concepts are different and the protection hardware encapsulates programs are in private address spaces, you must modify most programs to make them compatible with protected mode. Major enhancements to the operating system are required, in part to support descriptor tables and partially to process state structures that the hardware expects to access directly when it is running in protected mode.

Because of compatibility problems, Unisys B 28 and B 38 workstations support concurrent execution of protected mode and real-mode software.

PMOSS also addresses the second protected mode constraint by enhancing BTOS to manage global and local descriptor tables (GDT/LDT), Task State Segments (TSS), an Interrupt Descriptor Table (IDT), and the memory beyond 1 Mb that is accessible only in protected mode.

### **Reviewing Segmented Addressing**

With Intel microprocessors, instructions do not accept physical addresses as operands; they accept only SA:RA logical addresses. A linear address is formed from two 16-bit parts:

- □ the segment address (SA)

- □ the relative address (RA)

Together, these two parts comprise a logical address. When using the Assembler or Debugger, the syntax SA:RA writes a logical address.

As each instruction executes, the linear address forms from the logical address and addresses physical memory. There is no alternative use of logical addresses, because there is no way to address physical memory directly with an instruction.

The Intel architecture is referred to as a segmented addressing model because every address is always relative to some SA. Observe the contrast to a linear addressing model such as the Motorola architecture, where instructions accept 32-bit linear addresses rather than SA:RA pairs.

1-2

When an SA is a real address mode SA, it may be referred to as an SR to distinguish it from a protected mode SA (which is sometimes called an SN). The term SA applies to either real address or protected mode. In real address mode, all logical addresses are actually SR:RA addresses. In protected mode, they are actually SN:RA addresses. The following text describes the difference between an SR and an SN.

#### **Reviewing Real Address Mode**

Real address mode is the only mode in which 8086 and 80186 microprocessors operate. However, 80286 microprocessors execute initially in real address mode when powered-up or reset, but can switch to protected mode (if the operating system software necessary to support protected mode is present).

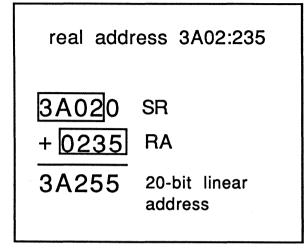

In real mode, to arrive at a 20-bit linear address result, the SR shifts left by four binary places (effectively multiplying by 16) and the RA is added. For example, figure 1-1 shows the logical address 3A02:235 in hexadecimal notation.

The resulting 20-bit quantity can only address 1 Mb of memory (2 exp 20 locations). A 16-byte unit of memory aligned on a 16-byte boundary is called a paragraph. The real address mode SR is a paragraph number, because it denotes a particular 16-byte boundary in the physical address space.

The RA is often referred to as an offset from the SA. In real address mode, the segment registers CS, DS, ES, and SS contain the paragraph numbers corresponding to the base of the current code, data, extra, and stack segments respectively.

These segments are always aligned to start on 16-byte boundaries.

Figure 1-1. Real Address Mode

#### **Protected Mode Addresses**

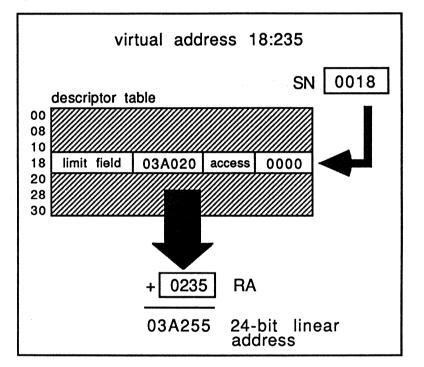

The 80286 microprocessor can address up to 16 Mb of memory (2 exp 24) in protected mode, but it requires a 24-bit linear. The 80386 can address up to 4 gigabytes (Gb) of memory (2 exp 32).

No Intel microprocessor, including the 80286, can address more than one Mb in real mode, because only a 20-bit address is formed by the address calculation described in Reviewing Real Address Mode, in this section.

To achieve this longer address compatibly and allow other features of protected mode to be implemented, the same two-part addressing scheme (the segmented addressing model) is used. The address still consists of an SA:RA, but the SA part of the logical address is interpreted differently. The RA part has the same meaning as in real mode. In protected mode, the 16-bit SA that is held in the CS, DS, ES, or SS register is not a paragraph number; rather, it is an index into a special type of table (called a descriptor table) that is accessible only to the operating system and the hardware. This index is called a selector (SN).

Note: An SN is an SA that is a paragraph number (a real address mode SA).

Paragraph numbers address segments in real mode and selectors address segments in protected mode. For each run file executing in protected mode, PMOSS builds and maintains such a table, called a Local Descriptor Table (LDT) from information that the Linker provides in the header portion of the V6 run file.

**Note:** This is why you must use the **Bind** command, which produces the new V6 run file format, to link programs that will run in protected mode.

Each code or data segment in the program has a unique selector, which the Linker assigns, and a corresponding unique entry in the LDT. The LDT is an array of these entries, called descriptors, which are eight bytes long and contain segment information. The selector is, in fact, an offset into the LDT, with some additional bits used for special purposes.

When an instruction loads a segment register in a protected mode program, the hardware uses the selector to find the descriptor and retrieve a segment base address from the descriptor. This base address is 24 bits long on the 80286. When an instruction refers to an operand (using the segment register and an RA), the RA is added to the base address to obtain a 24-bit operand address. Unlike real address mode, this base address does not shift; it is not a paragraph number, but a true byte address.

Figure 1-2 shows this process schematically. The example, 18:235, is equivalent to the previous example of real address mode shown in figure 1-1.

This time, the descriptor holds the linear base address, 03A020. Instead of the segment register holding the paragraph number 03A02, it holds a selector value, 18, which is used to index into the descriptor table.

**Note:** A logical address (SA:RA) consists of two 16-bit parts in both real and protected modes, the only difference being the value of the SA part.

The protected mode SN:RA logical address is referred to as a virtual address because the SN refers only indirectly to memory via a descriptor table entry. By changing the descriptor table entry, the operating system can make the virtual address refer to different physical memory (for example, to move the segment transparently to the program).

Figure 1-2. Protected Mode

The real address mode SR:RA logical address is referred to as a real address because it always corresponds to the same physical memory address.

Most incompatibilities between real mode and protected mode arise from this difference between paragraph numbers (SRs) and selectors (SNs), which can be subtle.

### **The Selector**

Figure 1-3 shows the anatomy of the 16-bit selector (SN). The high-order 13 bits form the offset that indexes into the descriptor table. The next bit discriminates between two kinds of descriptor tables (LDT and GDT), and the low-order two bits (the Requested Prvilege Level, or RPL) concern a seldom-used feature of the protection scheme. To find the descriptor, the hardware assumes the low-order 3 bits are zero and uses the selector as an offset (since descriptors are 8 bytes long).

The 13 index bits of the selector can generate 2 exp 13, or 8192, possible values. Thus the hardware permits 8192 entries in the LDT and in the GDT. In practice, this means each run file can have a private virtual address space of up to 8192 segments (or other elements).

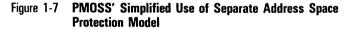

## **Descriptor Tables**

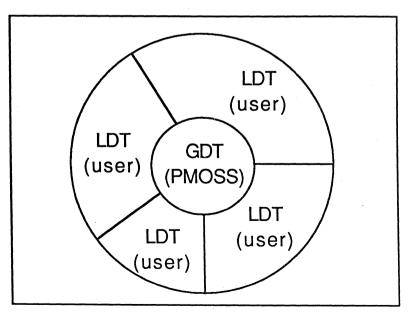

Two kinds of descriptor tables address segments: Local Descriptor Tables (LDTs) and the Global Descriptor Table (GDT). There must be a separate descriptor table for each run file executing in protected mode, including PMOSS. Each user run file has an LDT. PMOSS has the GDT, which you can think of as PMOSS' own LDT.

```

Figure 1-3. Anatomy of a Selector

```

| SN 0018                        |

|--------------------------------|

| 000000000011000                |

| descriptor index Lrpl          |

| L = 1 for LDT<br>L = 0 for GDT |

At any one time, a particular LDT is the current LDT. Each protected mode process is associated permanently with an LDT when the process is created. (Several processes can share the same LDT if they are part of the same program.) When process switching occurs, the firmware changes the current LDT automatically.

The GDT is special because it is never switched. Regardless of which LDT is in effect, the single GDT is always in effect as well. The GDT is PMOSS' LDT and the descriptors in it are only usable when PMOSS' code is executing, never when user code is executing.

**Note:** If the system designer wants, the hardware allows user programs to implement GDT descriptors. PMOSS, however, does not usually use this feature.

Because both the GDT and the current LDT are in effect at the same time, PMOSS can use the descriptors in both the GDT and the currently executing user program's LDT. This allows PMOSS to access the memory of user programs.

Because it has its own always-available descriptor table (the GDT), PMOSS can be called at certain entry points, at any time, as a user process subroutine. The operating system services known as kernel primitives and system common procedures are implemented this way.

**Note:** A protected mechanism known as the call gate limits the user program to calling at legitimate entry points and provides a convenient way to bind the user program to those entry points at program load time.

#### **Descriptor Cache Registers**

When one of the registers CS, DS, ES, or SS is loaded with a selector value, the machine fetches the appropriate descriptor from the GDT or LDT and loads it into an associated descriptor cache register. This internal register is not visible to software.

The presence of these invisible registers alleviates the hardware from fetching information from the descriptor table for every memory operand of an instruction. Instead, descriptors are examined only when segment registers are loaded. **Note:** Loading a segment register is more time-consuming in protected mode than real mode, because of the memory accesses needed to load the descriptor cache register. Ordinary instructions, however, are not more time-consuming.

The descriptor cache register holds the entire contents of the descriptor, which includes other information besides the segment base address. Although descriptors are always eight bytes long, only six bytes are actually used on the 80286.

### **Faults**

Several checks are associated with loading a segment register and its descriptor cache register. There must be an entry in the descriptor table for the selector that was loaded; the system knows the size of the descriptor table (which varies from table to table) and verifies that the selector does not index beyond the end of the table. The system uses information from the descriptor to perform other checks. In addition to the base address, the descriptor contains the size of the segment, the type of segment, and other protection-related information. You cannot access accidentally beyond the end of the segment in protected mode, execute data segments, and write to code segments. You can protect certain data segments from being written and certain code segments from being read.

Not all descriptors describe memory segments. There are other uses for selectors than as components of SN:RA memory addresses. PMOSS uses nonsegment descriptors for many purposes but, except for gate descriptors, they seldom involve user programmers.

If the selector is invalid, a fault results. Faults transfer control automatically to PMOSS. Conceptually, there are two type of faults: restartable faults and exceptions. Restartable faults are, in theory, recoverable; an exception is an error that prevents a program from further executing.

An example of a restartable fault is the not-present fault that occurs when the operating system marks a segment's descriptor to indicate that the segment is not resident, but is swapped out on disk.

- A restartable fault lets the operating system:

- read the missing segment into any available free memory

- load the base address in the descriptor

- mark the descriptor present

- return to the interrupted program (which again tries the instruction that faulted, since the value of IP still points to that instruction)

An example of an exception is a bad selector due to a programming error.

Because PMOSS does not support virtual memory, it treats faults as exceptions. Any fault or exception causes the system to enter the Debugger and displays a diagnostic message.

As a result, you cannot load values other than selectors into the ES register. When you do, the hardware tries to fetch the associated descriptor, resulting in a fault — even before you try to use the segment register to reference anything.

The selector value 0 is special. It can be loaded into a segment register, but causes a fault if it is subsequently used in an address calculation. The 0 value allows the passing of, for example, pbPassword = 0 and cbPassword = 0 in a BTOS OpenFile call. Although you can use 0, do not use the value to calculate an address.

Additional exceptions that can occur later, when using a valid segment register in an address calculation. Trying to address beyond the end of a segment is this type of an exception, called a limit exception.

## **Descriptor Types**

#### **Segment Descriptors**

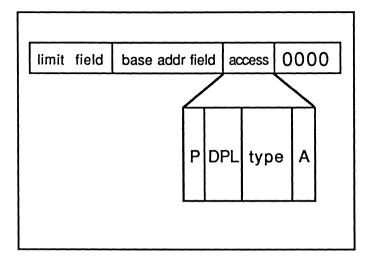

The segment descriptor is involved with SN:RA virtual addresses. Figure 1-4 shows the segment descriptor format used on the 80286.

Figure 1-4 Segment Descriptor

The meanings of the various fields are as follows:

| Field | Meaning                                                                                                                                                                                                                                                                                                            |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ρ     | Present bit. This bit, used in virtual memory management, is 0<br>when the segment is swapped out. When a register is loaded<br>with a selector that fetches this descriptor, if this bit is 0, a<br>fault occurs and the operating system can read the segment in<br>and mark it present.                         |

| DPL   | Descriptor Privilege Level. This field is used for protection (refer to Protection, in this section).                                                                                                                                                                                                              |

| Туре  | Several types of code and data segments are possible. This field<br>also identifies the descriptor as a segment descriptor (as opposed<br>to a call gate, for example).                                                                                                                                            |

| A     | Accessed bit. This bit, used by the least recently used (LRU) algorithms in virtual memory management, is set the first time the descriptor loads into a descriptor cache.                                                                                                                                         |

| Base  | The 24-bit base address.                                                                                                                                                                                                                                                                                           |

| Limit | The maximum RA value that can be used in an SN:RA, where the SN denotes this descriptor. The minimum RA value is zero. A fault occurs if the program tries to access out of segment bounds. The limit is one less than the size of the segment. This field has a different interpretation for some stack segments. |

**Note:** For data segments of a special type called expand-down or grow-down segments, the maximum is always 65535. The limit denotes the minimum allowable RA, which is one less than the minimum legal RA. These segments generally contain stacks, although stacks can also reside in ordinary expand-up segments. For expand-down segments, the base field does not point to the low-order end of the segment; rather, the base plus 65536 points to the high-order end of the segment.

On the 80286 in protected mode, a code segment is implicitly executable and also implicitly not writable. In addition, it may be designated as readable or not readable (for example, to prevent user programs from examining operating system code in a secure system).

A data segment can be designated as writable or not, but cannot be executed.

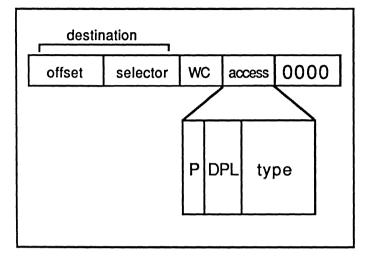

#### **Gate Descriptors**

The gate descriptor is a structure that uses indirection to allow programs to call routines whose addresses they cannot know until the program loads. Generally, any program address that lies outside the run file is unknown until load time. For example, a program can call a system common procedure or kernel call in BTOS, the location of which the Linker cannot supply when resolving the reference.

In the protected mode run file, the Linker resolves this reference as a call via a gate. At load time, PMOSS fills in the gate with the SN:RA virtual address of the desired routine. The actual CALL instructions in the calling code segment do not need to be modified at load time.

In the program code, these calls appear to call an SN:RA address, using an ordinary far CALL instruction. When this call executes, the selector obtains the associated descriptor (as before). The 80286 or 80386 examines the descriptor, which turns out to be a gate descriptor (refer to figure 1-5), and uses the destination fields in place of the original SN:RA to reach to the appropriate routine. The SN from the gate, not the original SN, winds up in the CS register. The original RA is ignored, because the gate destination fields provided a new SN:RA address.

The gate descriptor is also used as part of the protection mechanism. Among other uses, it is a more powerful alternative to the supervisor CALL instruction found on some other processor architectures that feature memory protection. Calls from one run file to another (including operating system calls) use call gates so that entry to the destination program occurs only at certain well-defined entry points that the call receiver establishes. This is why the system ignores the RA supplied by the caller. The gate descriptor fields are as follows:

| Field    | Meaning                                                                                                                                                                                                                                           |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P        | Present bit.                                                                                                                                                                                                                                      |

| DPL      | Descriptor privilege level. This field determines only who can use<br>the gate, not the privilege level at which the called code will run<br>(the DPL of the code segment descriptor to which the gate points<br>determines the privilege level). |

| Туре     | Gates that programs use can be call gates or TSS gates. Only<br>PMOSS uses TSS gates. TSS gates also are involved in interrupt<br>processing, as are two additional types of gates: interrupt gates<br>and trap gates.                            |

| WC       | Word count. Number of words of arguments for procedure being called. This field is only used when the call is to software at a higher level of privilege (such as from a user program to PMOSS).                                                  |

| Selector | The SN of the procedure entry point. Must identify a code segment descriptor with an appropriate DPL. May not identify another call gate descriptor; only one level of call gate indirection is allowed.                                          |

| Offset   | The RA of the procedure entry point.                                                                                                                                                                                                              |

#### Protection

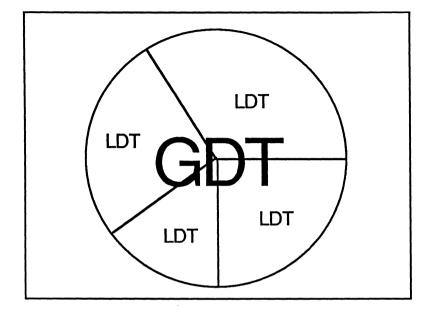

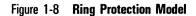

Protected mode on Intel microprocessors uses two models of protection:

- Protection by separate address spaces, shown in figures 1-6 and 1-7, in which a program is restricted to one virtual address space and cannot another address space location. This protection model provides isolation of one run file from another.

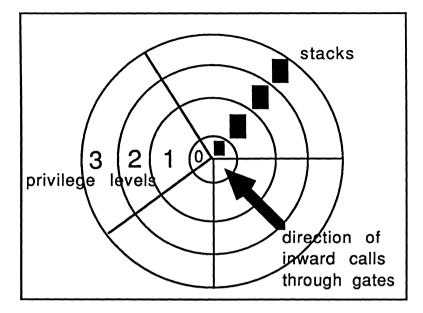

- Protection by privilege level, in which every program executes at one of several levels of authority. This is a ring protection model, shown in figures 1-8 and 1-9. It allows an operating system (like PMOSS) to conveniently protect itself from its clients. A program with a numerically lower privilege level has greater privilege, and can therefore access more restricted locations than a program with a numerically higher privilege.

Both protection models are in effect when in protected mode and both must be satisfied to allow access.

Figure 1-6 Separate Address Spaces Protection Model

On 80286 microprocessors, neither model or protection applies to real mode programs, even when PMOSS is installed. However, the physical memory above 992 Kb is inaccessible to real mode programs.

Each pie slice in figures 1-6 and 1-7 represents a separate address space, described by a separate LDT (the first protection model). Figure 1-6 shows the domain of each descriptor table.

A program in one address space is aware of and can describe only those locations for which it can load (and use) selectors. Only the LDT associated with the current process is in effect at one time. The GDT is in effect all the time. Therefore, the process can only address objects for which there exist descriptors in its own LDT or the GDT. The LDT describes only those objects that it is legitimate for the program to access: the program's code and data, the gates it can use to call other programs, and data that has been received in requests from other programs (if the program is a server).

In PMOSS, the user program generally cannot use the GDT descriptors. PMOSS uses and thinks of the GDT as its own LDT. The existence of this special LDT allows user programs to call PMOSS via call gates, and for PMOSS to access the user program's memory directly (using the user's LDT at the same time as its own LDT, the GDT). Figure 1-7 shows how PMOSS uses the GDT.

Privilege levels regulate calls from user programs to PMOSS (the second protected model). The rings in figure 1-8 correspond to privilege levels. 0 is the level of highest authority or privilege, and 3 is the least privileged level. Each entity in the current address space (everything described by a descriptor in the current LDT or the GDT) is marked with a Descriptor Privilege Level (DPL), which determines its usability.

For example, most GDT descriptors are marked 0 in PMOSS, which means that only a program running at privilege level 0 can use them. Most LDT descriptors are marked 3, indicating that any program in the address space can use them.

**Note:** A level 0 program can use not only level 0 descriptors, but also descriptors with numerically greater DPL. This means that, in figure 1-7, a program in the inner circle can see objects in the outer circles, but a program on the periphery may not see into the protected center.

Each process has a separate stack segment for each privilege level. By using call gate selectors, a program can call inwardly to a more privileged level, but only in ways that allowed the system allows. Control switches to the stack for the inner level when this occurs.

PMOSS uses only levels 0 and 3, as shown in figure 1-9. Levels 1 and 2 are reserved for future expansion. Currently, therefore, only two stacks per process are required, not four. Most PMOSS procedures run at level 0. Level 0 includes only code and data structures that are part of PMOSS (including structures that PMOSS creates to manage user programs, such as LDTs).

User programs run only at privilege level 3 in PMOSS. Most descriptors in LDTs are marked level 3. In effect, the way PMOSS currently employs the privilege level mechanism by dividing the world into supervisor (PMOSS) and user castes. PMOSS can use both its own level 0 descriptors and the current user's level 3 descriptors.

The following text summarize the most important protection rules. The protection hardware has many additional features described in the Intel *iAPX 286 Programmer's Reference Manual* and *80386 Programmer's Reference Manual*.

#### **DPL versus RPL**

Every descriptor contains a DPL in the range 0 through 3 and every selector contains an RPL in the same range, in the low-order two bits.

The RPL bits of the DS and ES registers are not important in user programs and usually remain at zero, as the Linker set them, even in level 3 programs. The DPL, not the RPL, is the final arbiter of privilege. RPL bits have a special function only PMOSS uses, which is beyond the scope of this discussion.

#### **Current Privilege Level (CPL)**

The current privilege level (CPL) is the level at which the process is currently running (essentially, the privilege level of the currently executing code). CPL is stored in the RPL bits of the CS register; it can be displayed by using the Debugger to examine CS. This is true because a process' current privilege level normally is the DPL of the code segment it is executing and, in the case of CS, the RPL bits are copies of the DPL bits in the descriptor for the currently executing code segment.

**Note:** Except in the special case of conforming code segments (not present in user programs).

The SS register has RPL bits that match the CS register's RPL bits (usually 3 in a BTOS user program). Since only PMOSS usually loads SS, user programs are ordinarily not concerned with the SS RPL bits; however, in medium model programs, they are not the same as the RPL bits of DS, which are normally 0. The DS and SS selector values will be identical, except for their RPL bits in a medium model program; in real mode medium model programs, they are identical in all 16 bits, which is why the new procedure FComparePointer is required.

#### Switching Privilege Levels with Call Gates

Call gates support only call statements, not jumps or data accesses. As with any descriptor, the call gate must have a DPL at least as great numerically as the caller's CPL. However, the destination code segment (the descriptor that the call gate descriptor refers to) must have a DPL numerically equal to or less than the caller's CPL because only sideways and inward calls are allowed; outward calls are never allowed. The inner (numerically lower) levels are trustworthy and are therefore compromised if they surrender control to an outer level by calling it.

On an inward call, the hardware switches stacks (saving SS and SP and reloading them to point to the high-order end of a stack reserved for the level being called). It also copies parameters automatically from the caller's stack to the new stack, making them accessible to the called procedure in the normal way. The stack switch prevents a situation in which a call to a routine that is known to function correctly fails because the caller's stack was too short. It also leads to the need for multiple stacks for each process. In PMOSS, there are two stacks per process because only two privilege levels - 0 and 3 - are used. Stacks are not switched on sideways calls, even when using a call gate.

A return can be to the same privilege level (sideways) or to one of greater numeric privilege (outwards). The return examines the RPL of the saved CS in the return address to determine whether a stack switch is necessary.

#### IOPL

The IOPL flag specifies the maximum CPL (numerically) for which I/O and HALT instructions are valid. IOPL is a property of each process (part of the flags word). Under PMOSS, IOPL is always 3 so any process can perform these instructions.

#### **General Protection Faults**

Breaking any of the protection rules generates a general protection fault, exception 13. Under PMOSS, general protection faults activate the Debugger.

#### **Processes and Process Switching**

Associated with every process is a Task State Segment (TSS). The TSS, shown in figure 1-10, contains the complete register state of the process.

The advantage of the TSS is that it permits extremely rapid process switching, despite the protection boundaries between programs. In protected mode, process switching is implemented in hardware and firmware, in response to interrupts or single instructions.

To use a BTOS example, suppose one program does a SEND to an exchange where a program of higher priority is waiting. The kernel can start the waiting process with a single CALL instruction to SN:RA, where SN is the selector of its TSS (the RA is ignored).

This causes the microprocessor to perform an entire process switch:

- store the entire register state of the current process in the current TS (which is identified by a special hardware register - TR)

- switch TR to point to the new TSS, and set the new TSS' back-link field to point to the old TSS

| LDTR (LDT selector)   |  |  |  |  |  |

|-----------------------|--|--|--|--|--|

| DS                    |  |  |  |  |  |

| SS                    |  |  |  |  |  |

| CS                    |  |  |  |  |  |

| ES                    |  |  |  |  |  |

| DI                    |  |  |  |  |  |

| SI                    |  |  |  |  |  |

| BP                    |  |  |  |  |  |

| SP                    |  |  |  |  |  |

| BX                    |  |  |  |  |  |

| DX                    |  |  |  |  |  |

| CX                    |  |  |  |  |  |

| AX                    |  |  |  |  |  |

| FL (flags)            |  |  |  |  |  |

| IP                    |  |  |  |  |  |

| Initial SS level 2    |  |  |  |  |  |

| Initial SP level 2    |  |  |  |  |  |

| Initial SS level 1    |  |  |  |  |  |

| Initial SP level 1    |  |  |  |  |  |

| Initial SS level 0    |  |  |  |  |  |

| Initial SP level 0    |  |  |  |  |  |

| back-link to prev TSS |  |  |  |  |  |

Figure 1-10. Task State Segment (TSS)

- load the entire register state of the new process from the new TSS

- □ set the NT (nested TSS) flag bit

Execution then continues. The operating system does not have to save and load each register.

Using a structure called a TSS gate, you can arrange for an interrupt to perform a process switch automatically (in effect, an automatic CALL to a TSS).

Conversely, when a BTOS process executes a Wait, the kernel can put away the register state of the process in its TSS and resume execution of the next highest priority (NHP) process using a single instruction that reverses the TSS process switch.

**Note:** The IRET that reverses the TSS process switch has different semantics than the real mode IRET instruction. A special flag bit, NT, selects the appropriate IRET - either IRET (the familiar instruction) or TRET (for 7SS *RET*urn) - at any time in protected mode. When the NT bit is 1, IRET does a TRET. User programs do not use either IRET or TRET. Therefore, IRET in protected mode is really two unrelated instructions.

The back link field of the TSS permits nesting of saved states that interrupts or TSS CALL instructions cause. When one interrupt cycle completes, or when a process wants to surrender the processor, execution reverts to the previous TSS via a process switch back to the TSS identified by the back link.

JMP instructions can also be used to cause TSS switches, but PMOSS does not use them.

TSSs have other functions connected with the stack switching operations that call gates perform. This guide is not intended to explain TSSs. For information about TSSs, refer to the Intel *iAPX 286 Programmer's Reference Manual* and the *80386 Programmer's Reference Manual*.

## Interrupts

There are two kinds of interrupts: internal and external. Internal interrupts, initiated synchronously as a result of the execution of an instruction, include software interrupts (which occur when an INT instruction executes), exceptions such as interrupt type 4 (division by zero), and faults including protection faults (type 13). External interrupts, initiated by an asynchronous event outside the processor, include I/O interrupts such as disk and real-time clock interrupts, among others.

Every interrupt has an interrupt type number in the range 0 to 255, which is an index into a special descriptor table, the Interrupt Descriptor Table (IDT). There is one IDT per system. Unlike the analogous structure in real mode (the Interrupt Vector Table, or IVT), it need not be located at physical address 0, but can be anywhere in memory (it is based by a special register, the IDTR). The IDT contains only gate descriptors. For a given interrupt type number, the IDT can contain one of three types of gates:

- a TSS gate

- an interrupt gate

- a trap gate

The type of gate and its contents determine how the interrupt is handled.

When an interrupt is routed through a TSS gate, the hardware switches to the new process indicated by a TSS selector contained in the TSS gate. The process switch is identical to the one that occurs with a TSS CALL instruction (refer to Processes and Process Switching, in this section). All the register state of the interrupted process is saved automatically and the NT bit is set. After the Interrupt Service Routine (ISR) executes, a special instruction switches back and resume the interrupted process.

Note: This instruction is the conceptual TRET type of the IRET instruction (IRET when NT = 1).

If the entry in the IDT for a given interrupt type is in interrupt or trap gate, the effect as if an automatic CALL via a call gate executed. Fewer registers are saved automatically; this type of gate may therefore be faster for very simple ISRs. Like real mode interrupts, interrupt and trap gates push the flag word on the stack then clear the NT bit.

Note: Clearing the NT bit records that the last interrupt was the interrupt gate or trap gate type, rather than the TSS gate type. After the ISR executes, the same special instruction (IRET) resumes the interrupted procedure. However, since NT = 0, IRET reverses the effect of the call-gate-like interrupt or trap gate, rather than performing a full process switch. Because IRET has two entirely different semantics, depending on the current setting of the NT bit, the same ISR can be installed using either type of IDT mechanism without changing its code. Alternatively, it can be installed in a real mode system.

# **Guide to Compatible Programming**

Programs compatible with protected mode can execute on any Intel microprocessor in real address mode or on the 80286 and subsequent Intel microprocessors in protected mode. This section describes how to create compatible programs or adapt existing programs to be compatible.

This section also describes general rules for protected mode programming.

## 80286 Real Mode Issues

The following incompatibilities arise between the B 28 and B 38 (80286) workstations and the B 26 and B 27 (80186) workstations, even when the former operate exclusively in real mode:

- differences in I/0 port addresses (which should be corrected by using GetPStructure)

- timing races with certain peripheral chips due to the 80286 faster execution speed and instruction pipelining (which should be corrected by adding delaying instructions)

# **Guidelines for Addressing Schemes**

These guidelines arise from the differences between segment addresses SAs in real mode (paragraph numbers, called SRs) and protected mode (selectors, called SNs).

You can use real mode SRs as short (16-bit) versions of long pointers, if the objects they address are aligned on 16-byte boundaries. In a certain sense, SRs form a 16-byte-granular linear address space (of up to 1 Mb). In real mode, you may want to subtract two SRs, or add a value to an SR to get another SR.

Protected mode selectors do not form a linear address space because selectors are merely indexes to objects, not object addresses. In protected mode, you never want to add or subtract SNs because there is no relationship between the values of SN and the location of segments in the linear address space. In real mode, when segments are contiguous in memory, you can detect that contiguity by comparing pointers. For example, the segment at 5000:0 of length 20h is contiguous with the segment at 5002:0 because 50000h + 20h + 50020h + Oh.

In protected mode, there is no relationship between the ascending numerical value of selectors and the ordering of segments in memory. A user program cannot know which segments are adjacent. In fact, the operating system reserves the right to move them from time to time without informing the user program.

Observe the following for addressing:

Do not use contiguous data objects larger than 64 Kb.

For example, in real mode, the compiled BASIC runtime takes over all remaining memory in the partition for heap space (potentially more than 64 Kb). Heap nodes are paragraph-aligned and are addressed by use of SRs. Therefore, a future compiled BASIC requires some reimplementation of its heap logic to make it compatible with protected mode.

In protected mode, multisegment objects are not necessarily contiguous in memory. Also, selectors cannot be generated arithmetically.

Compatible programs must use a multisegment rather than a contiguous data object and the segments must be addressed internally using offsets, not paragraph numbers.

Use compatible memory management interfaces.

New memory management requests support programs that are targeted for execution in both real and protected mode:

AllocAreaSL

ExpandAreaLL

ExpandAreaSL

QueryBigMemAvail

ShrinkAreaLL

ShrinkAreaSL

Refer to appendix A for information on these new memory management requests, as well as revised descriptions of the following previously existing memory management requests:

AllocAllMemorySL

AllocMemoryLL

AllocMemorySL

DeallocMemoryLL

DeallocMemorySL

QueryMemAvail

Programs should not generally depend on the descending or ascending nature of segment addresses that memory management operations return.

Avoid using AllocMemory calls for very small, numerous, fixed-length segments. This is a common, harmless practice in real mode because there is no system memory overhead for each segment. However, in protected mode, a 16-byte segment, for example, consumes more system memory for its overhead than for the segment itself.

Do not use SAs as paragraph-aligned (short) pointers.

Some programs convert addresses of objects that are known to be paragraph-aligned into short pointers. A short pointer is an SR made by combining the SR and RA of a long pointer arithmetically. The implied RA of a short pointer is 0. This technique does not work in protected mode.

Compatible programs that require zero offsets for dynamically allocated memory should continue to use AllocMemorySL; however, they cannot depend on the contiguity of segments.

Compatible programs that do not care about zero offsets but do care about contiguity between separately allocated chunks of memory should use AllocAreaSL and ExpandAreaSL. This provides up to 64 Kb of contiguous memory. □ Use ExpandAreaSL to allocate DS-relative memory.

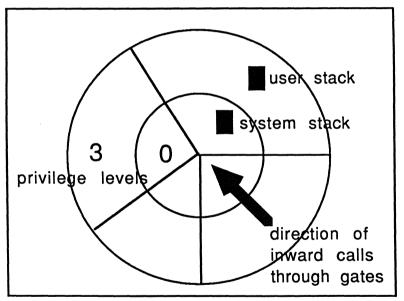

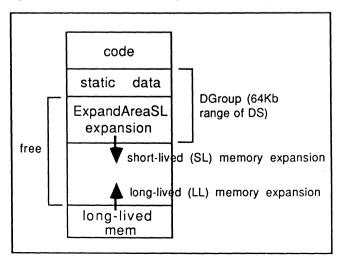

The Linker's DS allocation feature lets you dynamically increase the size of the statically allocated DGroup segment (in which all statically allocated data reside in a medium model program). It does so by locating the statically created data at the high-order end of the 64 Kb range of the DS register, so that the segment may be expanded downwards dynamically (assuming that the program is linked so that DGroup is at the low-order end of the program image). Figure 2-1 shows this arrangement. It permits memory dynamically allocated by the program to be addressable by DS-relative offsets. (Refer to the BTOS *Linker/Librarian Programming Reference Manual* for a further explanation of DS allocation.)

When using DS allocation in protected mode, the Linker and PMOSS cooperate to allocate an expand-down segment for DGroup. Compatible PL/M-86 programs must declare doubleword types that are not virtual addresses as DWORD and incorrect hard-coded occurrences pointer. Pascal programs must use the integer4 type. C programs must use long.

Compatible assembly code must not load ES (or other segment registers) with data. Use DX:AX to return a DWORD function result, and ES:BX only for a POINTER result.

Figure 2-1 BTOS Partition Using DS Allocation

Do not base program variables on system common pointers located at absolute addresses — use GetPStructure instead.

Under PMOSS, many system data structures are the same as for the underlying version of BTOS, but they must be accessed through calls to GetPStructure rather than through pointers initialized to low-memory paragraph-number addresses.

The obsolete way of accessing a system common data structure is to declare a pointer at an absolute address in the scat and base a variable (usually another pointer) on it. You can still use these absolute addresses as arguments to GetPStructure, but do not use them to initialize pointers directly. For more information, refer to Access to System Data Structures, in appendix B.

Pointers contained within system structures are usually real mode pointers, even when the structure is correctly accessed using the GetPStructure. Normally, therefore, protected mode programs cannot retrieve and use pointers from system data structures.

You must use a special operation when performing pointer comparison operations.

A pointer is a PL/M-86 type that is equivalent to Pascal's ADS type (refer to the *BTOS Pascal Compiler Programming Reference Manual*). With BTOS 8.0 and PMOSS, call FComparePointer to compare pointers in protected mode. For example, instead of using If p1=p2, use If FComparePointer (p1, p2).

**Note:** In protected mode, FComparePointer is the only valid way to compare pointers.

For most applications use FComparePointer with the bCompareMode parameter set to mode 0 or 1 (refer to FComparePointer, in appendix A).

Code segments must have classname code.

Protected mode code segments must have the classname code. Different types of descriptors are built for code and data segments; data segments cannot be executed and code segments cannot be written (usually, both can be read). Assembly language routines that omit the code classname from the segment directive work in real mode, but fault in protected mode.

D Writable code segments are not permitted.

Compatible programs cannot have writable variables in the code segment or self-modifying code.

Compatible programs can, however, use SetSegmentAccess to change segment type. For example, COBOL must do so to load an intermediate file (as data) and execute it (as code).

□ Use SetPStructure when modifying system structures.

In real mode, as some programs do, you can directly modify operating system structures (especially per partition data structures that the operating system maintains).

In protected mode, access to operating system data structures is only possible using GetPStructure, which returns a pointer based on a read-only descriptor for most structures. Therefore, GetPStructure alone is not sufficient when you need to modify this kind of structure.

PMOSS supports the SetPStructure call for user programs that have a legitimate reason for modifying specific fields in certain data structures.

SetPStructure is not present in BTOS real mode BTOS and therefore must be used only in protected mode. (Refer to SetPStructure and FProtectedMode, in appendix A.)

Avoid timing loops.

Protected mode compatible programs cannot contain timing loops that depend on instruction execution speed. Certain instructions execute slowly in protected mode (refer to the *iAPX 286 Programmer's Reference* Manual and the 80386 Programmer's Reference Manual).

#### □ Use only compatible instructions.

Programs that are to remain B 21 and B 22 compatible as well as B 26, B 28, and B 38 compatible can use only the 8086 instruction set. Programs that are to be compatible only among the various B 26, B 28, and B 38 processors can use the full 80186 instruction set, but none of the 80286 extensions.

Unisys-supplied compilers normally use only the 8086 instruction set. SRT PL/M-86 use the 80186 instructions (but not the 80286) if the \$MOD186 directive is used. These programs can be recognized with the Debugger because each procedure includes ENTER and LEAVE instructions near its entry and exit points, respectively.

You cannot use the PUSH SP instruction because it differs between the 80186 and the 80286.

□ You can still encode system calls using CS:IP hack.

Compatible programs can continue to encode trap instructions using alternate CS:IP addends to arrive at the same 20-bit address.

This is how to call BTOS for procedural requests, kernel calls, and system common procedure calls. Use exactly the same CS:IP values in programs compatible with protected mode as have always been used in real mode programs.

The Linker, BTOS, and PMOSS support these encoded instructions in both real and protected mode programs for compatibility, but are supported only for compatibility purposes in protected mode. Since these addresses fault in protected mode, they are altered before executing. You cannot use CS:IP hack in protected mode.

The virtual code segment facility (the overlay manager) cannot use the CS:IP hack in protected mode.

□ Filter processes may require a change.

Servers that filter (intercept) requests destined for other servers are called filter processes. A common use of filter processes is to enhance the semantics of an existing request without changing an existing server. Since BTOS is a set of servers, you can use the filter process technique to enhance BTOS by allowing BTOS to load run files in protected mode.

Filter processes commonly use one of two techniques for passing through requests to the original server. One of these techniques does not work in protected mode in its original form and therefore requires the new kernel primitive, ForwardRequest, to make filter processes using those techniques compatible with protected mode.

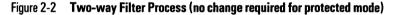

Servers that pass through requests by issuing a second request primitive (or RequestDirect) continue to work in protected mode, without change. This type of two-way filter process, shown in figure 2-2, intercepts the request on its way to the original server and also on its return (the response).

The following is the sequence of typical events of a two-way filter process:

- Client process issues Request.

- Filter processes proceeds from its Wait.

- Filter process changes exchResp field to its own exchange and issues RequestDirect to original server's exchange, then Wait.

- Original server proceeds from its Wait.

- original server issues Respond.

- Filter processes proceeds from its Wait.

- Filter process changes exchResp field back to client exchange and issues Respond.

- Client process proceeds from its Wait.

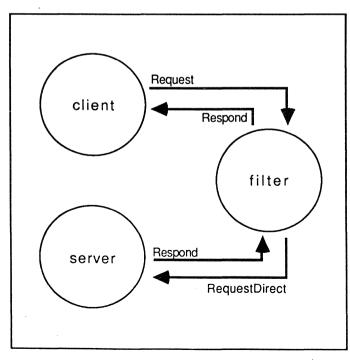

Servers that intercept the request only on its way to the original server, but not on its return trip to the client, traditionally use the Send primitive (or occasionally, the RequestDirect primitive) to forward the request to the original server. This type of one-way filter process, shown in figure 2-2, does not work in protected mode unless modified.

The following is the traditional sequence of events:

- Client process issues Request.

- □ Filter processes proceeds from its Wait.

- Filter process issues Send (or RequestDirect) to original server's exchange.

- original server proceeds from its Wait.

- Original server issues Respond.

- Client process proceeds from its Wait.

Figure 2-3 One-way Filter Process (change as shown for protected mode)

To make the traditional sequence compatible with protected mode, use the new kernel primitive ForwardRequest in place of Send or RequestDirect. This new primitive (described in appendix A) is similar to Send in that no response is expected; by issuing it, the filter process discharges its responsibility for the request as if it performed a Respond. Like RequestDirect, its argument must always be a pointer to a request block.

Using the Send and PSend kernel primitives are subject to restrictions.

Use the pMsg operand of Send and PSend only to send an actual pointer. In particular, the SN of the pMsg must be a valid segment selector or the null selector (zero). There are no restrictions on the RA value when the SN is zero, so you can use Send and PSend rather than a pointer to send two bytes of arbitrary data.

Otherwise, you can use Send and PSend exactly as they are in real mode, provided that the sender and receiver are part of the same task. That is, two processes sharing the same LDT can communicate using Send, or an interrupt service routine can use PSend to communicate with a process using the same LDT. You can only use Send between tasks (when one or both is a protected mode task) if the receiving task already has addressability to the segment that pMsg references. That is, the receiving task must either be a real mode task or already possess a descriptor for the segment that the SN of the pMsg identifies. For example, the following sequence is legal in protected mode:

- Process A issues Request.

- Process B receives the request. The system builds alias descriptors in the LDT of process B for the request block and a pb/cb, then process B proceeds from its Wait.

- Process B issues one or more Send process A, where the pMsg operand is a pointer to the request block, a pb from the request block, or a pointer to something wholly contained within one of the pb/cb fields (in other words, a pointer to something for which process A is known to already have a descriptor).

- Process A receives each pMsg which, upon receipt, is translated to a pointer containing the selector of the descriptor that process A already has in its LDT.

- Process B issues Respond and the alias descriptors are removed from its LDT.

After this, process B cannot issue a Send command using pointers related to that request block.

The restriction occurs because alias descriptors are constructed only upon receiving block sent with Request, RequestDirect, or ForwardRequest. When a pMsg from Send is received, an appropriate descriptor must already exist. (The system finds the descriptor, if it exists.)

This restriction is necessary because there is no paired equivalent to Send (equivalent to Respond) that enables the system to know when to deallocate the alias descriptor, if one was created. Only interrupt service routines, use PSend when communicating with a process. Both the interrupt service routine and the process are usually in the same task. Therefore, this restriction for using intertask pMsg does not occur with PSend.

PMOSS imposes additional restrictions on the use of Send and PSend.

□ Load the SS and CS registers properly to avoid a fault.

Assembly language code that loads SS, or any code that causes CS to be loaded with a value other than a previous value of CS (for example, by manually storing a segment address on the stack and then returning to it), must adhere to special rules of RPL usage.

The Request Privilege Level (RPL) bits are bits 0 and 1 of the selector. The Linker emits selectors that have zero in these bits, even though most programs run at privilege level 3.

In fact, the RPL bits use only the operating system. The DPL bits in the descriptor, not the RPL bits in the selector, protect against unauthorized use of descriptors. The RPL bits have no effect when they are zero, or when the program using the descriptor is running at level 3. When nonzero, they weaken the selector. For example, a program running at level 0 faults if the RPL of the selector is numerically greater than the DPL of the descriptor. The RPL bits are provided so that operating system procedures occasionally can tag selectors they receive (as arguments from the user program) with the user's privilege level. This ensures that the operating system procedure will not successfully access data to which the user is not entitled. This occurs even when the operating system procedure is running at a higher privilege level, which would legalize these accesses if the RPL bits were zero.

When selectors are loaded into DS or ES, the RPL bits remain as the Linker set them (zero). The RPL bits of these segment registers do not usually represent the DPL of the segment to which they refer. (To determine the DPL with the Debugger, use the **CODE-V** command.) However, when CS is loaded during a far CALL or JMP instruction, the DPL of the destination code segment is placed in the RPL bits of the CS register. Although the Linker puts 0 in the RPL bits of all segment addresses (including those in CALL instructions), after a CALL to a user procedure executes, the CS register's RPL bits are 3, not 0.

This occurs so the RET instruction can determine if the return is to be to the same privilege level or not. This requirement exists because RET, like CALL, can be interlevel. Interlevel CALLs are only possible using call gates.

At any time, the RPL bits of the CS register (the current CS) are by definition the current privilege level (CPL), the privilege level at which the processor is executing now.

The SS register's RPL bits are required to match the CS register's RPL bits exactly. Therefore, code that loads SS, like code that manufactures saved CS values, carefully must set these RPL bits to the DPL of the stack segment before loading SS, to avoid a fault. Moreover, the DPL of the stack segment must match CPL exactly.

NIL pointer problems can occur as a result of certain coding sequences.

In protected mode, it is valid to put 0 in a segment register, but not valid to use it to address data. A segment register with 0 in it is out of action temporarily.

Trying to reference data at paragraph number 0 in real mode usually causes an error in a user program.

However, the following construct may be valid in real mode, but fault in protected mode due to the kind of code that the compiler generates:

#### DECLARE

pFoo POINYRT , foo BASED pFoo WORD ; IF (pFoo ← 0) AND (foo = 1), THEN DO; ... END; In PL/M-86, the above construct allows the compiler to test pFoo and foo in either order. However, the access to foo must never occur if pFoo is nil; otherwise a general protection fault occurs. In this case, the code should be rewritten as:

```

IF pFoo ← 0 THEN

IF foo - 1 THEN

DO;

...

END:

```

Pascal programs may require a workaround for a fault that results from an incompatible code generation practice.

Unisys' Pascal compiler can generate code that violates the limit restriction in protected mode when accessing a segment.

This occurs because Pascal sometimes does full-word operand fetches from memory, even when the object being accessed is a byte; it then discards the high-order byte. When the object being accessed is the last byte in a segment, a limit fault occurs. This form of code generation is improper in protected mode.

The problem can occur in servers that are written in Pascal and try to read a byte located at the very end of a pb/cb field passed to them by a client. These fields are always tightly encapsulated segments to the server, even through they may not be located at the end of the client's data segment because PMOSS gives the server its own descriptor for each pb/cb field when the request arrives.

One workaround is to expand the segment or field by padding it with an additional byte. With the pb/cb, this means increasing the cb by 1. Another workaround is to access the last word of the structure, rather than the last byte, and then manually shift to obtain the last byte.

**Note:** For more information on this restriction refer to the *BTOS Pascal Compiler Programming Reference Manual*.

# Linking

### **Version 6 Run File Format**

Programs compatible with protected mode must use version 6 run file format, which is designed to be loaded in either real mode or protected mode. It supports protected mode while preserving single run file compatibility with real mode.

PMOSS never tries to load version 4 run files in protected mode.

**Note:** In the **SystemBuild** field of the BIND command, you must specify PM for protected mode or PMOSS for PMOSS (refer to the *BTOS Linker/Librarian Programming Reference Manual*).

The BIND command (an alternate command case invocation of the Linker version 8.0 and later) produces version 0 run file format. The LINK command produces version 4 run files. V6Link is a synonym for BIND.

Version 6 run file format is acceptable to:

- BTOS workstations 5.0 and later

- □ XE520s that support MS8, which allows the XE520 to accept version 6 run file format

Earlier BTOS versions accept only version 4 run file format, which is not compatible with protected mode.

### **Marking the Run File**

PMOSS will not load a V6 run file in protected mode unless it has been marked executable-in-protected-mode by setting the high-order bit of the *verAlt* field at offset 20th in the runfile header.

Future versions of the Linker (the BIND command) support an option to accomplish this marking.

Currently, however, you must use the following Debug File command sequence to mark the run file after linking:

- 1 With the system at the Executive level, type **Debug File**.

- 2 Press RETURN.

The Debug File command form appears with the cursor in the **File name** field.

- 3 Type MyFile.run.

- 4 Press RETURN.

The cursor moves to the [Write?] field.

- 5 Type yes.

- 6 Press RETURN.

The cursor moves to the [Image mode?] field.

- 7 Type yes.

- 8 Press GO.

The prompt **Debugger 8.0 (File Mode)** appears and the cursor appears next to the % on the line below the prompt.

- 9 Type 20.

- 10 Press Right Arrow.

An arrow  $(\rightarrow)$  appears, followed by a four-digit number, which is part of the run file header.

**Note:** The old value of the verAlt field is usually 0001, as shown. If another value is displayed, the run file is probably a V4 run file.

- 11 Type 8001.

- 12 Press RETURN.

The cursor moves to the %.

13 Press FINISH.

The system returns to the Executive level.

- 14 Type Debug File.

- 15 Press RETURN.

The Debug File command form appears with the cursor in the **File name** field.

- 16 Type MyFile.run.

- 17 Press RETURN.

The cursor moves to the [Write?] field.

- 18 Type yes.

- 19 Press GO.

The prompt **Debugger 8.0 (File Mode)** appears and the cursor appears next to the % on the line below the prompt.

#### 20 Press FINISH.

**Note:** Unless the run file is already marked, you must use the Debug File utility twice: the first time to modify one bit of the header and the second time without modifying anything. This is necessary because when you specify [Image mode?], the system does not recalculate the run file checksum when you finish. Activating the Debug File utility a second time, with [Write?] specified but [Image mode?] left blank, stores the correct run file checksum.

#### **Contiguous Code and Data**

All code segments and all data segments, respectively, must be contiguous in the run file.

PMOSS requires all the code segments in a run file to be physically adjacent. Similarly, all the static data segments must be adjacent to each other. The code and data portions of the run file can occur in either order, however.

The Linker tries to order code and data segments in separate, contiguous regions in the run file. However, improperly classed segments can prevent the Linker from ordering segments properly.

Failing to keep all the code segments together can prevent PMOSS from reclaiming the command to compare the memory consumption of the program when it is running in real mode versus protected mode. The used number should differ by the total amount of code in the program. (These numbers reflect only consumption of real mode memory.)

If they do not (for example, if no code space was saved in protected mode), examine the Linker map for noncontiguous code or data. Pay particular attention to ??SEG segments that the Assembler generates. The ordering of the segment does not matter if it has a length of zero, but can cause a problem if the segment has anything in it. These segments are emitted automatically when code or data appears outside of any segment/ends pair in an assembly language program. Refer to the BTOS Linker/Librarian Programming Reference Manual to resolve any problems with segment ordering.

## **Remedies for Incompatibilities**

The following text describes remedies for a program that cannot conform to the guidelines described in this section.

## **Checking for Protected Mode at Run Time**

Occasionally, there may be good reason for you to use two different algorithms in real and protected modes. You can package these programs as a single run file by including both algorithms with run-time checks in the code to choose between them.

Refer to FProtectedMode, in appendix A, which you can use to make the run-time check.

### **PMOSS Limitations**

If making a program compatible with protected mode seriously impairs its usefulness as a real mode program, you can port the program to protected mode as a separate run file to preserve the appearance of a single program. This technique requires renaming of the real mode program and that the protected mode version replace it. The protected mode program calls FProtectedMode after executing and if it finds itself in real mode, chains to the real mode run file. This technique handles both the case of a processor that cannot support protected mode and a system on which PMOSS is not running.

You might find this technique useful, for example, as an interim measure enabling a program to continue using some facility that increases performance or decreases program size in real mode, but which protected mode does not support, such as the virtual code segment facility (overlays).

## **Naming Conventions**