## Artist TRANSFORMER High Resolution Graphics Controller

## PRELIMINARY

Technical Reference

and

Guide to Operation

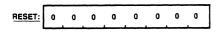

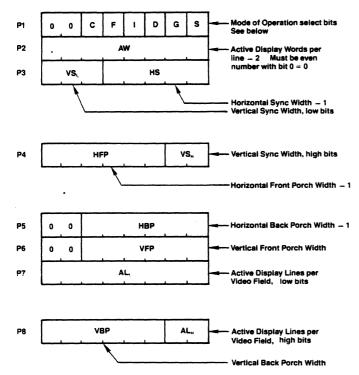

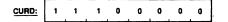

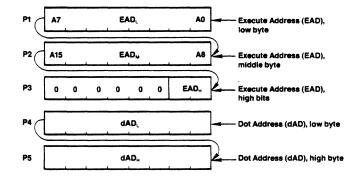

CONTROL SYSTEMS, INC. Minneapolis, MN

## Artist TRANSFORMER High Resolution Graphics Controller

## PRELIMINARY

Technical Reference

and

Guide to Operation

Working Draft of 8/23/85

CONTROL SYSTEMS, INC. Minneapolis, MN

## First Edition: June 1985

Copyright (c) 1985 by CONTROL SYSTEMS, INC. All rights reserved.

Control Systems, Inc. reserves the right to make changes to its hardware and software products and to revise the information about those products contained in this guide, without obligation to notify any person of such revisions or changes.

Control Systems, Inc. makes no representations or warranties with regard to the contents of this guide or to the suitability of the TRANSFORMER for any particular purpose.

Questions or comments regarding this product or documentation should be directed to Control Systems, Inc., 2855 Anthony Lane South, Minneapolis, Minnesota, U.S.A. 55418. Telephone: (612) 789-2421.

#### TRADEMARKS

ARTIST, TRANSFORMER, and ARTLIB are trademarks of Control Systems, Inc. The ARTIST 1, ARTIST 2, and ARTIST TRANSFORMER graphics controller boards and the ARTLIB family of software are products of Control Systems, Inc.

AutoCAD-86 is a trademark of Autodesk, Inc.

IBM is a registered trademark of International Business Machines Corporation. IBM Personal Computer (IBM PC), IBM Personal Computer XT (IBM PC XT), and IBM Personal Computer AT (IBM PC AT) are trade names of IBM. IBM Disk Operating Systems (IBM PC DOS), IBM Compiled BASIC, IBM Pascal, IBM FORTRAN, and IBM Macro Assembler are products of International Business Machines Corporation.

Microsoft is a registered trademark and MS is a trademark of Microsoft Corporation. Microsoft BASIC, Microsoft FORTRAN, Microsoft Macro Assembler, Microsoft MS-DOS, Microsoft Pascal, and the Microsoft Mouse are products of Microsoft Corporation.

#### TABLE OF CONTENTS

Chapter 1 Just What Is the TRANSFORMER and What Exactly Does It Do?

IBM Compatibility / IBM Display Adapter Emulation Modes High Resolution Drawing Mixed graphics modes on a single monitor / overlays and windowing Multiple colors/multiple boards Software features

#### Chapter 2 TRANSFORMER Installation Guide

| 2.1 | What's Shipped in the TRANSFORMER Package? | 2-1  |

|-----|--------------------------------------------|------|

| 2.2 | What You Need                              | 2-2  |

| 2.3 | Preparing the Test Software                | 2-2  |

| 2.4 | Setting Up the TRANSFORMER                 | 2-4  |

| 2.5 | Installing the TRANSFORMER                 | 2-6  |

| 2.6 | Testing the System                         | 2-8  |

| 2.7 | What to Do If You Have a Problem?          | 2-12 |

|     |                                            |      |

## Chapter 3 The TRANSFORMER Hardware

Hardware specifications

Board dimensions Environmental Considerations Power requirements Monitor requirements Output specifications / Video - Light pen TRANSFORMER/IBM Hardware Compatibility/Differences

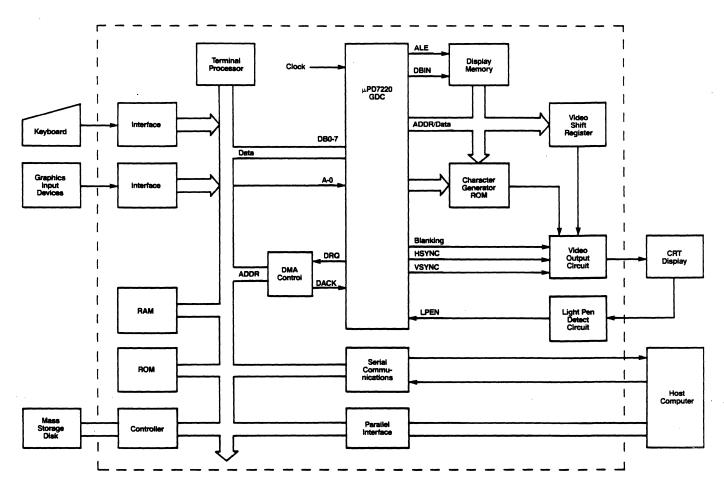

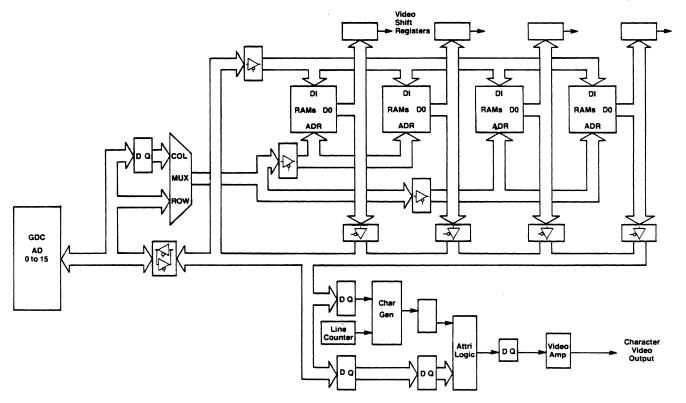

Theory of operation

Operation of major components How Software TRANSFORMed The interceptor ROM ROM Generation of Alpha/numerics and graphics characters Color video output - Analog (with DAC explained) or TTL Memory mapping

#### Chapter 4 TRANSFORMER I/O Port Selection and Addressing

| 4.1 | TRANSFORMER I/O Port Address Selection      | 4-1 |

|-----|---------------------------------------------|-----|

| 4.2 | Selecting an Active Base Address            | 4-2 |

| 4.3 | System Board Address Settings               | 4-3 |

| 4.4 | Software Selection of the Board Address and |     |

|     | Graphics Display Mode                       | 4-4 |

Chapter 5 I/O Port Address Registers: Functions, Bit Maps, and Programming

| 5.1  | The TRANSFORMER I/O Ports                           |      |

|------|-----------------------------------------------------|------|

| 5.2  | Programming the uPD7220 Graphics Display Controller | 5-2  |

| 5.3  | uPD7220 Status/Parameter Register and               |      |

|      | uPD7220 Data/Command Register                       | 5-3  |

| 5.4  | uPD7220 LUT / Zoom Register                         | 5-4  |

|      | 5.4.1 uPD7220 Color Look-Up Table (LUT) Function    | 5-4  |

|      | 5.4.2 uPD7220 Hardware Zoom Function                | 5-5  |

| 5.5  | Memory Configuration Register                       | 5-6  |

| 5.6  | Talking to the MC6845 CRT Controller                | 5-8  |

| 5.7  | IBM Index Register                                  | 5-10 |

| 5.8  | IBM Data Register                                   |      |

| 5.9  | 6845 Index Register                                 |      |

| 5.10 | 6845 Data Register                                  |      |

|      | Mode Select Register                                |      |

|      | Color Select Register                               |      |

|      | Status Port                                         |      |

|      | Clear Light Pen                                     |      |

|      | Set Light Pen                                       |      |

|      | Printer Status Port, Printer Control Port, and      |      |

|      | and I/O Port Base                                   | 5-17 |

|      |                                                     |      |

| Chapter | 6 | Memory | Usage | and | Programming | Notes |  | 6-: | 1 |

|---------|---|--------|-------|-----|-------------|-------|--|-----|---|

|---------|---|--------|-------|-----|-------------|-------|--|-----|---|

## APPENDIXES

| Appendix ( | A Files Distributed in the TRANSFORMER Package                     | A-1 |

|------------|--------------------------------------------------------------------|-----|

| A. 1       | Files Shipped on Both Artist TRANSFORMER<br>Distribution Diskettes | A-1 |

| A.2        | Artist TRANSFORMER Tutor 3 Diskette Files                          |     |

| A.3        | Artist TRANSFORMER Utilities and Graphics Primitives               |     |

|            | Diskette Files                                                     | A-4 |

| with       | B Selecting and Adjusting a Monitor for Use<br>the TRANSFORMER     | B-1 |

| Appendix ( | C NEC uPD7220 Technical Specifications<br>and Programming Notes    | C-1 |

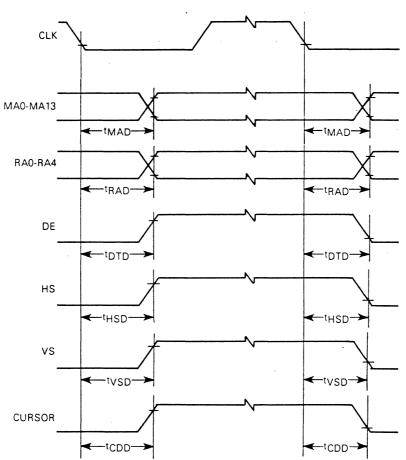

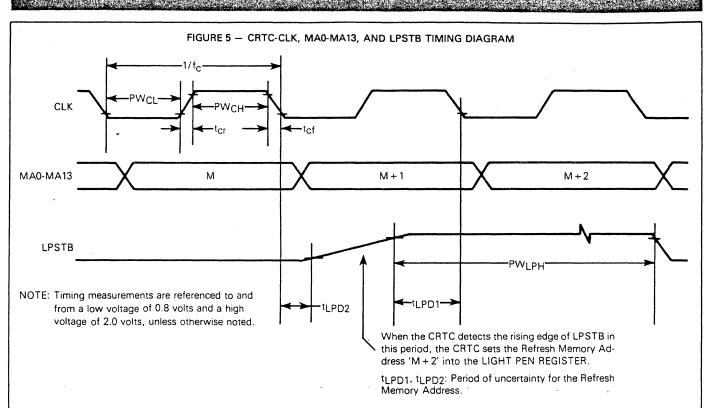

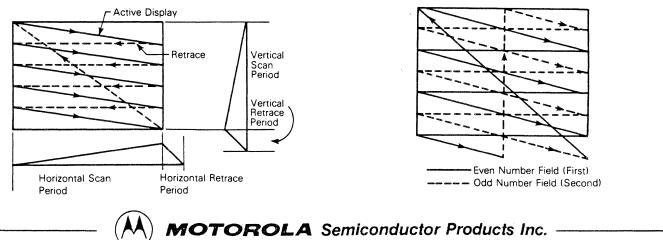

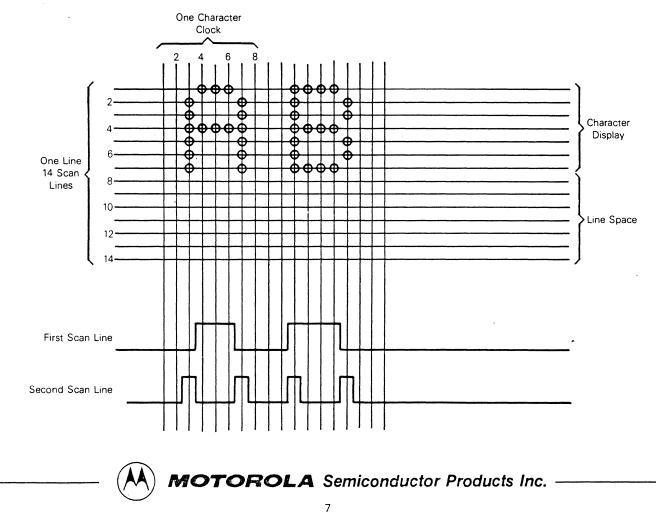

| Appendix 1 | D MC6845 Technical Specifications and Programming Notes            | D-i |

.

.

## TABLES

| 2.1 | System SWICTH 1 Settings                                                                                                                  | 2-8 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     |                                                                                                                                           |     |

| 5.2 | TRANSFORMER I/O Port Addresses and Functions<br>Logical Memory and uPD7220 Plane Configuration<br>Summary of Standard IBM and TRANSFORMER |     |

|     | MC6845 Register Values<br>TRANSFORMER Supported Video Output Modes                                                                        |     |

## FIGURES

| 2.2 | TRANSFORMER Board Layout and Jumper J1<br>System Unit Back Panel Mounting Screws<br>Interior of System Unit               | 2-6 |

|-----|---------------------------------------------------------------------------------------------------------------------------|-----|

|     | TRANSFORMER Board Header J1<br>System SWITCH 1 Settings                                                                   |     |

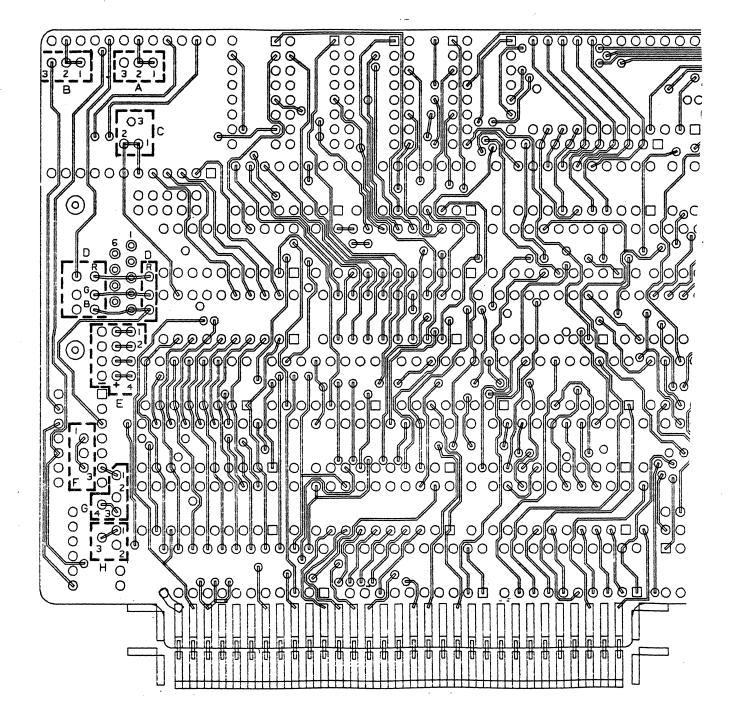

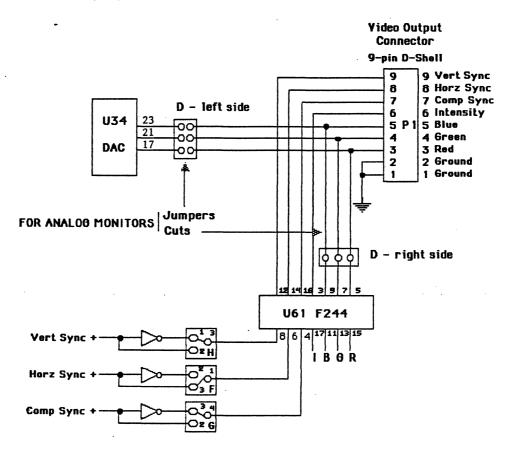

| 7.2 | TRANSFORMER Board Back or Solder Side<br>Schematic of Output Jumpers to 9-pin D-Shell Connector<br>Jumper E Configuration | 7-5 |

v

## Chapter 2 TRANSFORMER Installation Guide

Of course, the first thing you'll want to do when you get your TRANSFORMER is try it out. This setup guide will help install your TRANSFORMER hardware in your IBM PC, IBM PC XT, or compatible computer system. It will also show you how to load and run a special program which allows you to test the installation.

You can usually install the TRANSFORMER and have it up and running in only a few minutes. In these installation instructions, we assume that you are somewhat familiar with your computer's hardware and with DOS software operation. We also assume that the TRANSFORMER will be installed as shipped, without modification, and that it will be operated in addition to or as a direct replacement for an IBM display adapter (that is, using the same I/O port addresses). Read through these setup instructions before you begin. If you are unsure about any of the procedures, consult the references mentioned.

#### 2.1 What's Shipped in the TRANSFORMER Package?

The TRANSFORMER package includes both hardware and software. The package includes:

- The TRANSFORMER board -- configured at the factory for your monitor. A DAC chip is installed if you are using an analog monitor.

- (OPTIONAL) A video interface cable. If you are using an analog monitor, a cable with separate 75 ohm BNC-type connectors for RGB input to your monitor is shipped in the TRANSFORMER package. If you have a TTL monitor, you will be using the video interface cable supplied with your monitor, unless you specifically ordered a monitor cable with your TRANSFORMER.

- A plastic adapter card guide.

- The Artist TRANSFORMER Utilities and Graphics Primitives diskette.

- The Artist TRANSFORMER Tutor 3 diskette (includes INTRO3.COM).

- The TRANSFORMER Setup Specification sheet.

- This User's Guide.

Verify that you have these items. If anything is missing or damaged, contact your dealer. Note that Appendix A of this guide lists the files currently shipped on each distribution diskette.

#### 2.2 What You Need

In addition to the items shipped in the TRANSFORMER package, you will need the following items to complete the TRANSFORMER installation and setup:

- IBM PC, IBM PC XT, IBM PC AT or compatible system with at least one double-sided diskette drive.

- Your graphics monitor (the one specified for use with the TRANSFORMER).

- The video interface cable (if you are supplying this cable).

- A medium size flat head screwdriver or a 3/16" nut-driver or wrench.

- DOS Version 2.0 or later operating system files.

- Two or more blank diskettes.

Optional, but extremely helpful, are your computer and monitor hardware manuals as well as the operating system manuals.

## 2.3 Preparing the Test Software

- 1. If possible, you should make back-up copies of all the disks shipped in your TRANSFORMER package before you proceed with the hardware installation. If you have only one computer and the TRANSFORMER is your only display adapter, you can make the back-up copies after the board is installed. See **Section 2.6 Testing the System** for more information.

- 2. Before you begin the installation, prepare a bootable test diskette so that you can check out the system after the TRANSFORMER is installed.

If you are using a TTL monitor with your TRANSFORMER, you can use any bootable DOS system disk to start the system and operate in a standard IBM mode. All you need to do to prepare a new test disk is to copy the files from the Tutor 3 diskette to any bootable system disk.

If you are using an analog monitor with your TRANSFORMER, you must prepare a bootable DOS system disk which also contains the initialization file LDLT.COM, the system start up file AUTOEXEC.BAT (which includes the command to run LDLT.COM), as well as the files shipped on the Tutor 3 diskette.

If you do not have a display adapter card installed in your system and a working monitor, you can make the bootable system disk after you complete the TRANSFORMER installation. **Section 2.6 Testing the System** explains how to start the system without the test diskette prepared in the steps below. Follow these steps to prepare the test diskette:

- a. Power up the system and start DOS.

- b. With the DOS system disk in drive A and a blank diskette in drive B, enter the command:

#### A) FORMAT B:/S

When the formatting operation is completed, exit FORMAT by typing "N" at the prompt.

c. Insert the TRANSFORMER Tutor 3 disk in drive A and enter this command:

#### A>COPY A:\*.\* B:

When the copy operation is completed, remove the TRANSFORMER Tutor 3 diskette from drive A and put it in a safe place.

d. The test program you will be using is INTRO3.COM. This program should not be operated after the DOS console device driver program ANSI.SYS has been loaded because ANSI.SYS contains a value which resets the TRANSFORMER mode register to 80 x 25 text mode whenever the screen is scrolled. So that a ANSI.SYS device driver is not loaded at start up, you can erase the CONFIG.SYS file shipped on the Tutor 3 diskette and copied to your new diskette in step "c" above. To erase the file, enter the command:

#### A>ERASE B:CONFIG. SYS

Put the diskette that you just made aside. You will use this diskette to test the system when you have completed the installation.

In addition to the test program INTRO3, the TRANSFORMER Tutor 3 diskette contains a program called TUTOR3 which allows you to try out the functions of the ARTLIB graphics primitives library. You may want to prepare a TUTOR3 diskette at this time. To do that, use the second blank diskette and follow these steps:

a. With the DOS system disk in drive A and a blank diskette in drive B, enter the command:

#### A>FORMAT B:/S

When the formatting operation is completed, exit FORMAT by typing "N" at the prompt.

b. TUTOR3 uses the ANSI.SYS console device driver. To copy the DOS file ANSI.SYS to the new diskette, enter this command:

A) COPY A: ANSI. SYS B:

c. Insert the TRANSFORMER Tutor 3 disk in drive A and enter this command:

#### A>COPY A:\*.\* B:

When the copy operation is completed, remove the TRANSFORMER Tutor 3 diskette from drive A and put it in a safe place.

Whenever you want to use the TUTOR3 program, load DOS from this new diskette (at power up or reset the system with CTRL-ALT-DEL) so ANSI.SYS becomes the console driver. When you exit from the TUTOR3 program, reset the system again using a system disk which does NOT contain ANSI.SYS.

#### NOTES for Users of the TRANSFORMER Analog Version:

If you are using an analog version of the TRANSFORMER, the program LDLT.COM **must** be run whenever the system is turned on in order to initialize the TRANSFORMER for standard color output. Although the values loaded by LDLT into memory at power-up are not disturbed at a system reset (CTRL-ALT-DEL), loading LDLT whenever DOS is booted does no harm.

The command file AUTDEXEC.BAT that you copied from the Tutor 3 diskette includes the LDLT command, which tells DOS to search for and load LDLT.COM at each system start up. While you can use this diskette as your boot disk whenever you power up the system, you will probably want to prepare a new system boot disk or modify your present boot disk and include only the TRANSFORMER files necessary for system initialization.

## 2.4 Setting Up the TRANSFORMER

- 1. Remove the TRANSFORMER from its packing material.

- 2. When you ordered your TRANSFORMER, the board was individually configured at the factory to match your monitor type. The TRANSFORMER Setup Specification sheet describes the configuration of your TRANSFORMER board. Check that the board is configured properly for your monitor and system setup.

If you are using an analog monitor, be sure that the DAC chip is installed in the upper right corner of the card. If you ordered a TTL compatible version of the TRANSFORMER, the socket should be empty.

You may also want to check that the TRANSFORMER's video sync outputs match your monitor's inputs. Your monitor manual should list the monitor's video sync input specifications.

Chapter 7 of this manual explains how the TRANSFORMER configuration options are set and how they can be modified.

Control Systems TRANSFORMER User's Guide

3. Install a jumper block across two (2) pins of J1 to select the TRANSFORMER's operating mode -- that is, it selects the I/O port base address. This jumper determines whether the TRANSFORMER operates like an IBM monochrome display adapter, an IBM color/graphics display adapter, or both.

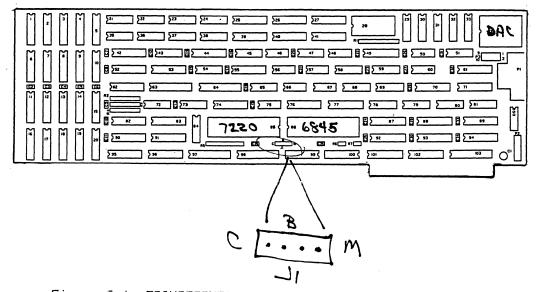

Jumper J1 is a Berg-strip header, located in the lower middle section of the card, below the uPD7220 and MC6845 chips. Your jumper options are "M" -- monochrome, "C" -- color, or "B" -- both.

Figure 2.1 TRANSFORMER Board Layout and Jumper J1

If the TRANSFORMER is the **ONLY** display adapter card installed in the system and you want the TRANSFORMER to simulate both the IBM color/graphics adapter and the IBM monochrome adapter, be sure that the jumper block is installed across the two middle pins of J1.

If you want the TRANSFORMER to operate as if it were an IBM monochrome adapter, place the jumper block across the two pins at the right of J1. Select this option if an IBM color/graphics adapter is also installed in the system.

If you want the TRANSFORMER to operate as if it were an IBM color/graphics adapter, place the jumper block across the two pins at the left of J1. Select this option if an IBM monochrome display adapter is also installed in the system.

#### 2.5 Installing the TRANSFORMER

Follow the steps outlined here to install the TRANSFORMER board in your IBM PC or IBM PC XT. If you are not using an IBM PC or PC XT, these installation instructions may not be exactly correct. If you are using some other compatible hardware system, you will need to consult your computer's hardware manual for guidance in installation of expansion boards.

- 1. Turn the power off the computer's System Unit and all peripherals connected to it.

- 2. Disconnect all power cords and cables from the System Unit.

- 3. If necessary, move the System Unit to a clear work surface.

- 4. Using the screwdriver, nut-driver, or wrench, remove the cover mounting screws on the back of the system unit cabinet. Some System Unit cabinets have only two mounting screws on the lower corners. Other units have five screws, one at each corner and one at the center of the cabinet's back panel.

Figure 2.2 System Unit Back Panel Mounting Screws

- 5. Remove the System Unit cover. To do this, gently slide the cover forward until it stops and then lift slightly to completely remove it.

- 6. Locate the system expansion slot where you will install the TRANSFORMER board. The TRANSFORMER can be installed in any full length slot.

- 7. If there is no other display adapter already installed in the system, or if you are installing the TRANSFORMER in a new slot as a second adapter, remove the blank expansion slot cover from the cabinet back panel at the position where you want to install the TRANSFORMER. First, remove the screw that holds the metal slot cover in place and then, pull the slot cover out. Save the slot cover for later use.

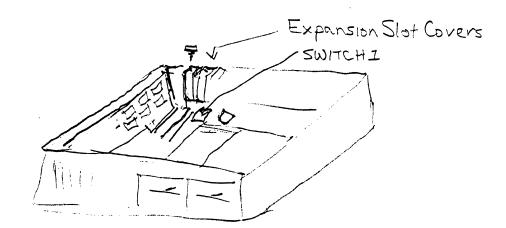

Figure 2.3 illustrates the interior of the System Unit. It shows the expansion slots and the expansion slot covers.

2-6

Figure 2.3 Interior of System Unit

- 8. Snap the plastic card guide into the front of the cabinet opposite the expansion slot you selected. Look for a double row of holes at the front of the cabinet. Position the card guide vertically, parallel to the holes and push it into place.

- 9. If you are replacing a previously installed display adapter card, you must first remove the card you want to replace. Locate the card and remove the screw in the back panel which holds the card's retaining bracket in place. Grasp the top edge of the card and pull firmly to lift the card out of the cabinet.

- 10. Insert the TRANSFORMER card into the selected system expansion slot. Be sure that the front edge of the card slips into the card guide's groove. Then press the TRANSFORMER squarely into the selected expansion slot. Be sure that the TRANSFORMER's 62-pin bus connector is firmly seated in the expansion slot.

- 11. Align the hole on the TRANSFORMER's retaining bracket with the threaded hole on the upper edge of the cabinet's back panel. Insert the screw you removed earlier and tighten it.

- 12. You must set up System SWITCH 1 located on the System Board to correspond to your display adapter setup. This switch setting indicates to the system software the type of display adapter(s) installed and the operating mode you want at system start up.

SWITCH 1 is an 8-position DIP switch. When the System Unit is viewed from the front, you can see SWITCH 1 on the floor of the System Unit cabinet closest to the last system expansion slot on the right, near the center of the System board. Figure 2.3 shows the location of this switch.

Positions 5 and 6 of SWITCH 1 must be configured. Table 2.1 explains the possible settings. Use a pointed object like a ball point pen to set the switches.

| Table 2.1 System SWITCH 1 Set | tings: |  |

|-------------------------------|--------|--|

|-------------------------------|--------|--|

| Monitor Adapter Type                             | SW5 | SW6 |

|--------------------------------------------------|-----|-----|

| MONOCHROME or BOTH                               | OFF | OFF |

| (more than 1 adapter)<br>COLOR (in 80 x 25 mode) | ON  | OFF |

| COLOR (in 40 x 25 mode)                          | OFF | ON  |

If the TRANSFORMER is the only display card installed in the system, you can select any of the these settings. Be sure to set the system switch to **BOTH** if you have a monochrome display adapter and a TRANSFORMER installed in the system, or the monochrome monitor may be damaged.

- 13. Replace the System Unit cover and refasten the screws on the System Unit back panel.

- 14. Connect the monitor to TRANSFORMER board now installed in the System Unit. Locate the TRANSFORMER's 9-pin D-Sub video output socket and connect the 9-pin D-Sub monitor cable plug to it. Connect the other end of the monitor cable to the monitor. If you are using an analog monitor where a separate output is provided for each color, match the output plugs on the cable (they are color coded) to the sockets on your monitor.

- 15. Reconnect the keyboard and all other peripheral cables to the System Unit and reconnect all power cables.

#### 2.6 Testing the System

Now that the TRANSFORMER is installed, you are ready to power up the system to check that the installation is OK. You may also need to make some adjustments to the monitor.

- 1. Turn on the monitor and power up the system.

- 2. Load DOS.

- a. Using the test diskette you made earlier, load DOS from drive A.

At this point, the normal system start up should occur. That is, the system memory check should proceed as normal. When that is completed, DOS loads and you should see the DOS system DATE prompt. Enter the date and, at the TIME prompt, enter the time. Alternatively, press ENTER twice until the system prompt **A** appears.

b. If you were not able to make a test diskette earlier, you will have to use your master diskettes to get up and running. Don't forget to make back-up copies as soon as possible. If you are using a TTL monitor, start DOS as described above from any bootable DOS system disk. Then put your TRANSFORMER Tutor 3 disk in drive A. If you have an analog monitor, start DOS from any bootable DOS system disk. When random color appears on the monitor screen, press ENTER twice. Then, put the TRANSFORMER Tutor 3 disk in drive A and type blindly **LDLT** and press ENTER.

3. Don't be disturbed if you can't read the prompts and the image on your screen is garbled or distorted. It is very common for monitors to require adjustments to the vertical and horizontal hold or height and width (vertical and horizontal sync) controls.

On some monitors, these can be adjusted by controls located on the outside of the monitor. On other monitors, the controls are located inside the monitor case. Locate these controls on your monitor and gradually adjust the controls until the system prompt is readable and displayed in the correct location on the screen.

If you have trouble locating the adjustment controls or adjusting the monitor, consult your monitor manual. Most monitor manuals contain details of where and how to adjust the monitor controls in order to display an undistorted image.

If you need to make adjustments inside the monitor case, be sure to turn off the monitor (and power down the system) before you remove the case. After you have removed the case, you can turn on the monitor and restart DOS. Be very careful when adjusting an unprotected monitor; there are very high voltages present.

4. When you are satisfied with the image displayed at the system prompt, start the TRANSFORMER test program INTRO3. This program allows you to quickly check the TRANSFORMER card functions, including those of the uPD7220 chip. At the system prompt, enter:

#### A> INTRO3

After INTRO3 is started, a series of four prompts are displayed on the monitor. You must answer these prompts to completely initialize the system. If you need to exit from INTRO3 at any time during the initialization procedure, you must type **Ctrl-Alt-Del** to reset the system. After you have initialized the system by answering the first four prompts, you can exit from INTRO3 by entering **A** from the main menu.

5. At the first prompt:

TTL or Analog?

1) TTL

2) Analog

Enter the option, 1 or 2, which corresponds to your monitor type. If you enter any other value or type a number from numeric keypad or the function keys, the computer beeps and waits for an acceptable response. It is not necessary to press the enter or return key.

.....

6. The next prompt requests the TRANSFORMER's I/O port base address. At the prompt:

# Enter I/O Port Base Address

Seven possible I/O port base addresses are shown. An arrow is displayed beside default factory setting 3D0. Enter 7 to select this address. If your board uses an alternate address, select the correct option.

7. INTRO3 next asks you for your monitor parameters. These parameters are used to synchronize operation of the TRANSFORMER and your monitor. This is the prompt :

Graphics controller initialization

1) Input parameters from terminal 2) Input parameters from file

Press 1, 2 or use Function Keys

The initialization parameters can be entered either from a file or from the keyboard.

Files containing parameter lists for most monitors used with the TRANSFORMER are supplied on your Tutor 3 disk. They were copied to the test disk during the software setup. The parameter files are supplied for a variety of monitors. Files are included for these non-interlaced displays:

| Display Type:    | At Resolution: | Parameter File name: |

|------------------|----------------|----------------------|

| NEC 1401         | 640 x 400      | 640X400N. NEC        |

|                  | 640 x 480      | 640X480N.NEC         |

| NEC 1410         | 640 x 400      | 640X400N.410         |

| Gigatek 1331     | 640 x 400      | 640X400N.GIG         |

|                  | 640 x 480      | 640X480N.GIG         |

| PGS SR-12        | 640 x 400      | 640X400N.PGS         |

| Radio Shack      | 640 x 480      | 640X400N.PGS         |

| Tandy CM-1       | 640 x 400      | 640X400N. TAN        |

| IBM Professional |                | 640X400N.PRO         |

| Graphics Display | 640 x 480      | 640X480N.PRD         |

| TAXAN 440        | 640 x 400      | 640X400N.TAX         |

| Electrohome 609  | 640 x 400      | 640X400N.ELH         |

Parameter files are supplied for these monitors operating in interlaced mode:

| Display Type:                 | At Resolution:         | Parameter File name:         |

|-------------------------------|------------------------|------------------------------|

| IBM Color<br>Graphics Display | 640 x 400<br>640 x 480 | 640X400I.IBM<br>640X480I.IBM |

| 50Hz European<br>Display      | 640 x 400<br>640 x 480 | 640X400I.EUR<br>640X480I.EUR |

| CS GENLOCK Option             | 640 x 400<br>640 x 480 | 640X400I.GEN<br>640X480I.GEN |

| Zenith ZVM136                 | 640 x 400<br>640 x 480 | 640X400I.ZVM<br>640X480I.ZVM |

If your monitor is one of those for which a parameter file is supplied, select option **2** for file input. At the prompt:

#### Specify file name:

Enter the file name. Specify a 640 x 400 pixel resolution file for this test. After you enter the file name, INTRO3 reads the data from the file. If INTRO3 cannot find the file you entered, it displays the message **File Not Found** and again asks you to enter the file name. Be sure that the file you enter is on the current disk or specify the drive. INTRO3 will not proceed until you have entered an acceptable file name. If the file or parameters you specify are not correct for your monitor, the screen may display trash. Do not operate the monitor with incorrect parameters; the monitor could be damaged.

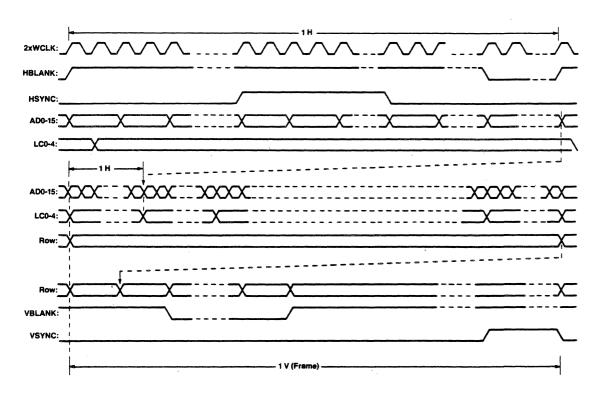

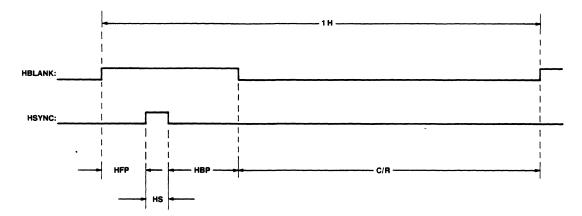

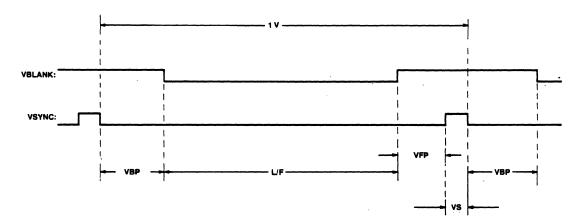

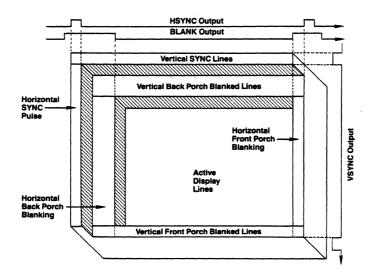

If a parameter file is not supplied for your monitor, you must enter each of the monitor parameters from the keyboard. Select option 1 and at each prompt enter the required information. These values must be entered:

- 1. Interlace mode

- 2. Active words per line (i.e. pitch)

- 3. Horizontal sync (hs)

- 4. Vertical sync (vs)

- 5. Horizontal front porch (hfp)

- 6. Horizontal back porch (hbp)

- 7. Vertical front porch (vfp)

- 8. Vertical back porch (vbp)

- 9. Active display lines (al)

- 10. Display area length (len)

As each prompt is displayed you must enter a value. From these values, INTRO3 calculates the horizontal and vertical resolutions. INTRO3 also asks you if you want to save these parameters in a file. If you answer yes, INTRO3 prompts you to enter the file name where the parameters are to be saved.

If you are unsure of the correct monitor initialization values to enter, Appendix B describes how these values are calculated and how they can be changed based on the monitor's specifications. Contact your dealer or Control Systems if you need additional assistance.

The last initialization prompt displayed by INTRO3 allows you to 8. configure the TRANSFORMER's display planes. For this test, at the prompt:

> Enter number of planes [3,4,5] \_\_\_\_\_

Enter **5** which configures the TRANSFORMER so that five display planes are possible. In this mode, one plane of display memory is used by the MC6845 chip in text mode and four planes are reserved for use by the uPD7220 chip which displays the high resolution bit-mapped graphics.

- As soon you enter the final initialization value, INTRO3 initializes 9. the system using these values. INTRO3 then draws the Control Systems logo. This graphics screen is the first screen displayed during the test which uses and is controlled by the uPD7220 chip. If the logo is distorted or not properly synchronized, the monitor may need additional minor adjustment or the monitor initialization values you entered may not be correct for your system.

- When the logo screen is completely drawn, a menu of possible functions 10. appears in the upper half of the screen. This menu is overlaid on top of the graphics screen.

Enter **C** to clear the logo from the graphics screen. Then, select any of the menu options and enter the corresponding letter from the keyboard. INTRO3 prompts you to enter any additional information it needs to complete the operation you chose. After you enter any necessary information, INTRO3 performs the selected operation and the results appear on the screen. Enter A at any sub-menu to return to the previous menu level or to exit from INTRO3.

Try several of the operations to be sure that your monitor is properly adjusted and that the cabling is correct. Be sure to check the color, especially if you are using an analog monitor. Analog RGB cables can be connected incorrectly.

11. When you are satisfied that your system is operating as expected, enter A to exit INTRO3 and return to the system prompt.

#### 2.7 What To Do If You Have a Problem?

Sometimes things go wrong. Although you've read though all of the instructions and followed them to the letter, your TRANSFORMER won't work right. Well, don't panic and don't give up yet. Read through this checklist of problems and possible solutions first. Be sure to turn off the power to all units before you remove or replace cabinets or boards.

#### PROBLEM: POSSIBLE SOLUTIONS:

No image at all after system power up:

- Be sure the monitor is plugged in and turned on.

- Check that the cables are correctly installed and that all the plugs are correctly seated.

- Be sure that the monitor contrast and brightness adjustments are correct.

- Verify that the jumper is correctly installed at J1.

- Check that System SWITCH 1 is properly configured and that it agrees with the jumper configuration of J1.

- Check that the TRANSFORMER is completely seated in the expansion slot.

System fan doesn't work:

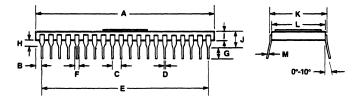

• The system power supply may be overloaded. Each TRANSFORMER board configured for TTL operation draws 3.2 amps. A TRANSFORMER configured for analog operation requires 3.5 amps. If your system power requirements are high, for instance if you are using more that one display adapter and a hard disk sub-system installed in a standard IBM PC, we suggest that you use an IBM PC XT compatible power supply and an external fan.

The IBM PC XT has a 135 watt power supply that allows 11.0 amps in the expansion slots. The IBM PC requires 4.0 amps with 7.0 amps remaining for expansion boards. The IBM PC power supply is rated for 63 watts only.

Screen rolls vertically or horizontally :

- Check that the vertical and horizontal (hold) adjustments on the monitor are correct.

- Verify that the TRANSFORMER's sync type outputs and polarity are correct for your monitor. Compare the TRANSFORMER's sync outputs (see the Setup sheet) with your monitor's input signal requirements. Some monitors have switches inside the cabinet which allow you to select sync options. Be sure that these are set to agree with the video output of the TRANSFORMER.

## PROBLEM: POSSIBLE SOLUTIONS:

Screen rolls vertically or horizontally (cont.):

The default sync output of the TRANSFORMER is compatible with the IBM monochrome display adapter's output. That is:

Sync on Green External Composite Sync + Horizontal Sync - Vertical Sync

On the IBM color/graphics adapter, both horizontal and vertical sync are positive. If necessary, you can modify the TRANSFORMER to adjust the video output sync type and polarity to match your monitor's requirements. Chapter 7 explains how to make these modifications.

Trash on the screen at power up:

- Does the pixel clock installed in the TRANSFORMER match your monitor's scan rate.

- If you are using an analog monitor, did you run LDLT.COM? This file loads the color look-up into the TRANSFORMER'S RAM. If the look-up table is not loaded, the RAM retains random values from system power up. It does no harm to run LDLT.COM even if you have a TTL or monochrome monitor.

Trash on the screen after initialization:

• The initialization parameters you entered, either from a file or from the keyboard, may have been incorrect for your monitor. Do not operate the monitor with incorrect parameters; the monitor could be damaged.

No image or out of sync image in text plane (IBM emulation):

• Are you using the monitor originally specified for use with the TRANSFORMER. Although it is possible to use a different monitor than originally specified, the values sent to the MC6845 chip by the TRANSFORMER's ROM will not be correct for your monitor. The graphics planes generated by the uPD7220 chip should still operate as expected. Control Systems TRANSFORMER User's Guide 2 Installation Guide

#### PROBLEM: POSSIBLE SOLUTIONS:

Unexpected colors:

- If you are using an analog monitor, check that the color outputs of the monitor cable are correctly connected to the monitor's video input connectors.

- If you are using a TTL monitor, be sure that the monitor cable is correctly wired for your monitor.

If you are still not able to pinpoint the problem, there may be a malfunction in your System or in the TRANSFORMER card itself. You may want to try reinstalling your original display adapter card if you have one. Then, consult your dealer or an experienced technician for additional suggestions.

End of Chapter 2

## Chapter 4 TRANSFORMER I/O Port Selection and Addressing

The TRANSFORMER is designed for use as an integral part of the IBM PC family and closely compatible computers. Because the TRANSFORMER can be used as a replacement for both the IBM monochrome and color/graphics adapters or can be installed as the second display adapter in a system with an IBM monochrome or color/graphics adapter already installed, the basic I/O port addresses used by the TRANSFORMER are compatible with those of the IBM display adapters.

The initial I/O port address used by the system to talk to the TRANSFORMER is determined by the configuration of a jumper on the TRANSFORMER and by the monitor type setting of SWITCH 1 on the system board. After the system start up, the currently active I/O port address and the graphics display mode can be selected in software. In most cases, when the standard IBM compatible video I/O port addresses are used, selection of the I/O port address visibly affects only the MC6845 display plane.

#### 4.1 TRANSFORMER I/O Port Address Selection

The operating mode of the TRANSFORMER board is determined by the system bus I/O port addresses used to configure the internal registers of the TRANSFORMER'S MC6845 and uPD7220 chips. I/O port address selection is dependent on the TRANSFORMER'S base address which is determined by board jumpering.

The base address used for system I/O is provided on the TRANSFORMER as a hardware selectable base address pair. The configuration of board jumper J1 selects the current active base address. This arrangement allows the TRANSFORMER to emulate both IBM monochrome and color/graphics adapters, depending on the configuration of J1.

The standard TRANSFORMER base addresses are the I/O ports 3B0 and 3D0. These addresses are the same as those used by IBM for their monochrome adapter (3B0) and color/graphics adapter (3D0). This address pair allows you to operate the TRANSFORMER immediately with no change to standard software packages configured for the IBM PC.

If required for special applications, alternative I/O base addresses are possible. However, you must physically modify the TRANSFORMER board if you wish to use one of the alternate base address pairs. This modification procedure is described in Chapter 7. If you use an alternate base address pair, you may also need to modify existing software which normally ignores the IBM ROM BIOS and talks directly to the IBM hardware (not an unusual situation).

#### 4.2 Selecting an Active Base Address

From the base address pair, an active base address must be selected for system I/O. This address is determined by the position of a jumper across two pins of header J1. J1 is a four-pin single-row Berg type header located on the component side of the TRANSFORMER board. Figure 4.1 shows the general board location and configuration of J1. Look for J1 below the uPD7220 and MC6845 chips. You will notice that the four pins of J1 are not actually numbered on the TRANSFORMER; however, they are numbered here for clarity.

Figure 4.1 TRANSFORMER Board Header J1

Because the jumper configuration determines the actual base address used for system I/O, a jumper block or wire should be installed across the appropriate pins of J1 before the TRANSFORMER is installed in your system.

There are three possible jumper configurations for J1 -- M for monochrome, C for color, or **B** for both. Assuming that the standard base address pair 3B0 and 3D0 are used:

- If the jumper is installed in position "M" across the two pins on the right (pins 3 and 4), the lower base address of the pair (3B0) is selected. The TRANSFORMER responds to the addresses defined for the monochrome adapter. Select this jumper position if the TRANSFORMER is used in system with another color/graphics board already installed.

- If the jumper is installed in position "C" across the two pins on the left (pins 1 and 2), the higher base address of the pair (3D0) is selected. The TRANSFORMER responds to addresses defined for the color/graphics adapter. Use this jumper position when a separate monochrome board is also installed in the system.

- If a jumper is installed in position "B" across the two middle pins (pins 2 and 3), either of the two possible base addresses (3B0 or 3D0) can be software selected. In this configuration, the TRANSFORMER can respond as either a color/graphics or monochrome adapter depending on the base address used by software to access the MC6845's Mode Register. This is the normal jumper setting.

You must jumper J1 before installing the TRANSFORMER if another display adapter card is also installed in the system. If you intend to operate your system with only the TRANSFORMER board installed, the jumper does not actually need to be installed at J1. Pins 2 and 3 of J1 are grounded and position "B" is really only a "storage" position.

#### 4.3 System Board Address Settings

You must configure the system board to reflect the display adapter type(s) installed in your system when you install the TRANSFORMER. Switch settings on the system board indicate to the system software what type of display adapter is installed and the default display adapter operating mode at system start up.

On IBM PC and IBM XT system boards, set SWITCH 1 so that positions 5 and 6 are set to OFF if you have both an IBM monochrome display adapter and a TRANSFORMER installed in your system. If you have a installed the TRANSFORMER in place of the IBM display adapter card, you can select any of the system board switch setting. Set both switch positions 5 and 6 to OFF if you want the system to start up in monochrome display mode. Set position 5 to ON and position 6 to OFF for 80 column color operation at every system start. If you want the TRANSFORMER to start in 40 column mode at boot time, set position 5 to OFF and position 6 to ON.

| Monitor Adapter Type                                | SW5       | SW6 |

|-----------------------------------------------------|-----------|-----|

| MONOCHROME only or BOTH<br>(or more than 1 adapter) | OFF       | OFF |

| COLOR (in 80 x 25 mode)<br>COLOR (in 40 x 25 mode)  | ON<br>OFF | OFF |

#### Figure 4.2 System SWITCH 1 Settings

Be sure to set the system switch to MONOCHROME or BOTH if you have a monochrome display adapter and a TRANSFORMER installed in the system, or the monochrome monitor may be damaged.

If you are installing your TRANSFORMER in an IBM PC AT or some other PC compatible system, these switch settings may not be correct. Check your system's technical reference for details regarding proper system board settings.

#### 4.4 Software Selection of the Board Address and Graphics Display Mode

If the TRANSFORMER is configured to emulate either IBM display adapter or if you have another display adapter installed in your system, the system will always start up with the monitor mode selected by the setting of SWITCH 1. After start up, you can change the TRANSFORMER's display mode by using the DOS MODE command or by running one of the display mode selection programs supplied on the TRANSFORMER Utilities diskette.

These files are supplied:

| Executable Files: | Assembler Files: | Board and Mode:               |  |  |  |  |  |  |  |

|-------------------|------------------|-------------------------------|--|--|--|--|--|--|--|

| MONO. COM         | MONO. ASM        | Monochrome board - monochrome |  |  |  |  |  |  |  |

| 80COLOR.COM       | 80COLOR.ASM      | Color board - 80 x 25 color   |  |  |  |  |  |  |  |

| 40COLOR.COM       | 40COLOR.ASM      | Color board - 40 x 25 color   |  |  |  |  |  |  |  |

| 80BLACK.COM       | 80BLACK.ASM      | Color board - 80 x 25 B & W   |  |  |  |  |  |  |  |

| 40BLACK.COM       | 40BLACK.ASM      | Color board - 40 x 25 B & W   |  |  |  |  |  |  |  |

| 32X20BW.COM       | 32X208W.ASM      | Color board - 320 x 200 B & W |  |  |  |  |  |  |  |

| 32X20CR.COM       | 32X20CR.ASM      | Color board - 320 x 200 color |  |  |  |  |  |  |  |

| 64X20BW.COM       | 64X20BW. ASM     | Color board - 640 x 200 B & W |  |  |  |  |  |  |  |

These files contain all the code necessary to alter the "equipment flag" (a memory location whose value is set by the ROM BIOS at start up by reading SWITCH 1) and to change the ROM BIOS routines which control the graphics display modes. If the TRANSFORMER is the only board installed and J1 is jumpered to be selectable, running any of these programs after start up will select the alternate board address and/or graphics display mode. If you have a TRANSFORMER and another display adapter installed, you can use one of these programs to switch from one board to another without any other system changes. Note that if you are using the TRANSFORMER with a monochrome adapter, the system should be set to always come up in the monochrome.

The .COM files can be run immediately. At any time after start up, enter the command that corresponds to the display mode you want. For example if you set J1 and the System SWITCH 1 to BOTH, the display will come in monochrome mode. To change to 80 x 25 color mode, at the system prompt simply enter the command **BOCOLOR**. The monitor is blanked and the system returns in the new mode. The .ASM files are included as examples of how to prepare your own programs to alter the equipment flag and change the graphics display modes.

End of Chapter 4

4-4

## Chapter 5 I/O Port Address Registers: Functions, Bit Maps, and Programming

## 5.1 The TRANSFORMER I/O Ports

The TRANSFORMER's default I/O port addresses are completely compatible with those used by IBM on its display adapter cards. However, the TRANSFORMER uses several additional I/O ports not used by the IBM display adapters. Briefly, several I/O port addresses reserved by IBM but not normally used for addressing the IBM display adapter cards are used with the TRANSFORMER for control of the uPD7220 graphics controller. The TRANSFORMER also uses two additional ports to control the MC6845 through the TRANSFORMER's on board ROM.

The table below names and briefly describes the function of each I/O address assigned to the TRANSFORMER. The function of each register defined here is separately described in detail in the sections that follow.

| I/O PORT ADDRESS<br>defaults<br>MONO/COLOR |         |     | lts | REGISTER FUNCTION                  |  |  |  |  |  |  |

|--------------------------------------------|---------|-----|-----|------------------------------------|--|--|--|--|--|--|

| Base                                       | Address | 380 | 3D0 | uPD7220 Status/Parameter Registers |  |  |  |  |  |  |

| Base                                       | +1      | 3B1 | 3D1 | uPD7220 Data/Command Registers     |  |  |  |  |  |  |

| Base                                       | +2      | 3B2 | 3D2 | uPD7220 LUT / Zoom Register        |  |  |  |  |  |  |

| Base                                       | +3      | 3B3 | 3D3 | Memory Configuration Register      |  |  |  |  |  |  |

| Base                                       | +4      | 3B4 | 3D4 | IBM Index Register                 |  |  |  |  |  |  |

| Base                                       | +5      | 385 | 3D5 | IBM Data Register                  |  |  |  |  |  |  |

| Base                                       | +6      | 386 | 3D6 | 6845 Index Register                |  |  |  |  |  |  |

| Base                                       | +7      | 387 | 3D7 | 6845 Data Register                 |  |  |  |  |  |  |

| Base                                       | +8      | 3B8 | 3D8 | Mode Select Register               |  |  |  |  |  |  |

| Base                                       | +9      | 3B9 | 3D9 | Color Register                     |  |  |  |  |  |  |

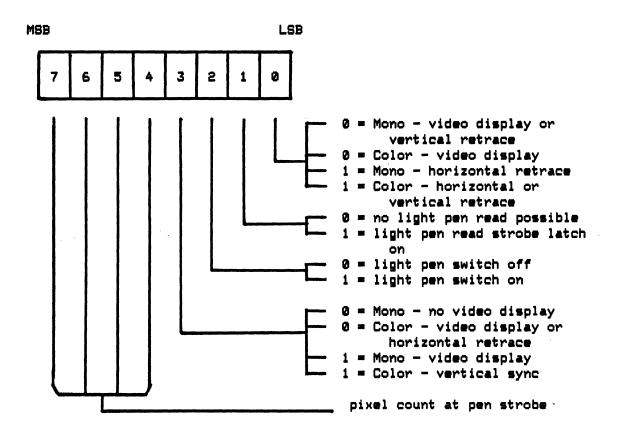

| Base                                       | +10     | 3BA | 3DA | Status Port                        |  |  |  |  |  |  |

| Base                                       | +11     | 3BB | 3DB | Clear Light Pen                    |  |  |  |  |  |  |

| Base                                       | +12     | 3BC | 3DC | Set Light Pen                      |  |  |  |  |  |  |

| Base                                       | +13     | 3BD | 3DD | Not Used                           |  |  |  |  |  |  |

| Base                                       | +14     | 3BE | 3DE | Not Used                           |  |  |  |  |  |  |

| Base                                       | +15     | 3BF | 3DF | Not Used                           |  |  |  |  |  |  |

Table 5.1 TRANSFORMER I/O Port Addresses and Functions

The default I/O addresses shown in the table are based on the TRANSFORMER's default base address pair. If your TRANSFORMER has been configured to use some other base address pair, each I/O port address can be determined by substituting your board's base addresses for 3B0/3D0 and then adding one (+1) for each succeeding register.

In the default configuration, when the TRANSFORMER is set up to operate in monochrome mode (J1 pins 3 and 4 jumpered), the addresses in the MONO column are used for system I/O. If the TRANSFORMER is set up for color operation (J1 pins 1 and 2 jumpered), the addresses shown in the COLOR column are used. When the TRANSFORMER is set up to operate in BOTH mode (J1 pins 2 and 3 jumpered), the addresses shown in both columns are accessible through software control.

Under software control, the TRANSFORMER's mode of operation and system I/O addressing is determined by the specific address used to access the Mode Select Register. As explained in Chapter 4, you can use the IBM DOS MODE command, one of the mode selection commands included in the TRANSFORMER package, or prepare your own software for mode selection.

The function of each I/O port is described below. Each description includes the bit assignment for that address register and additional information which affects programming of that port.

Remember that the addresses noted in the table above and described in detail here assume that you are using the standard IBM PC compatible I/O port addresses. If your system uses another base address pair, the actual address registers used in your system are incremented from those base addresses. For example, the Configuration Register is normally accessed at I/O port base address + 3, that is at 3B3 and/or 3D3. If you are using the alternate base address pair at 2A0/2C0, the Configuration Register is then located at 2A3 or 2C3.

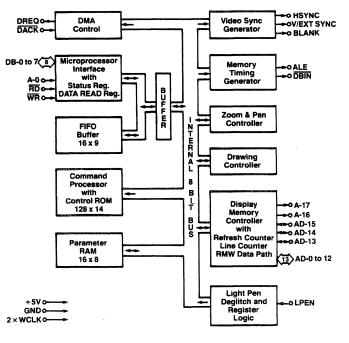

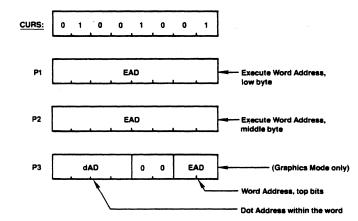

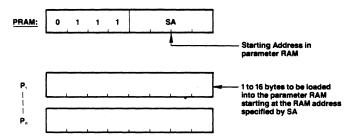

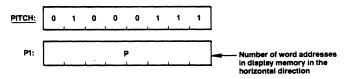

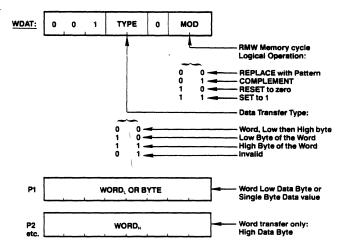

## 5.2 Programming the uPD7220 Graphics Display Controller

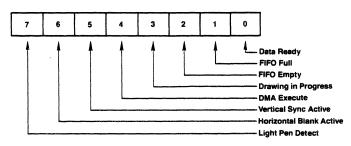

The NEC uPD7220 Graphics Display Controller (GDC) has a bi-directional interface to the system bus. Two addresses are assigned to the uPD7220 through which the uPD7220's status register and FIFO are accessed. Commands and parameters are written into the uPD7220 and the status register and FIFO are read based on the address selected. Commands are written to the uPD7220 in the form of a command byte followed by a series of parameter bytes, as The status register contains the 8 register flags which allow necessary. coordination of the uPD7220 with the monitor and the flow of data between the FIFO buffer and the system bus.

The LUT/Zoom register is used to control the hardware required for proper timing when the uPD7220 ZOOM command is used to zoom the display. While register does not actually talk to the uPD7220, its value must correspond to the zoom value of the uPD7220 for proper display magnification.

## 5.3 uPD7220 Status/Parameter Register (I/O Base Address -- '3B0' or '3D0') and uPD7220 Data/Command Register (I/O Base +1 -- '3B1' or '3D1')

The two ports which control both read and write access to the uPD7220's status registers and FIFO are defined below.

| TRANSFORMER<br>I/O Port | 7220<br>Addr |        | WRITE<br>MODE              |           |

|-------------------------|--------------|--------|----------------------------|-----------|

| 380 or 3D0              | AØ           | Reac   | Write                      |           |

|                         |              | Status | Bit                        | parameter |

|                         |              | Flag   | Definition                 | to FIFO   |

|                         |              | 0      | Data Ready                 |           |

|                         |              |        | 0 = no data or CPU now     |           |

|                         |              |        | transferring data          |           |

|                         |              |        | 1 = byte for CPU read      |           |

|                         |              | 1      | FIFO Full                  |           |

|                         |              |        | 0 = room for at least one  |           |

|                         |              |        | byte in FIFO               |           |

|                         |              |        | 1 = GDC FIFO full          |           |

|                         |              | 2      | FIFO Empty                 |           |

|                         |              |        | 0 = data in FIFO           |           |

|                         |              |        | 1 = FIFO empty, commands   |           |

|                         |              |        | and parameters sent        |           |

|                         |              | 3      | Drawing in Progress        |           |

|                         |              |        | 0 = GDC not drawing now    |           |

|                         |              |        | 1 = GDC drawing graphics   |           |

|                         |              | 4      | DMA Execute                |           |

|                         |              |        | 0 = no DMA in progress     |           |

|                         |              |        | 1 = DMA transfer occurring |           |

|                         |              | 5      | Vertical Sync              |           |

|                         |              | -      | 0 = no vertical sync       |           |

|                         |              |        | occurring                  |           |

|                         |              |        | 1 = vertical sync occuring |           |

|                         |              | 6      | Horizontal Blanking        |           |

|                         |              |        | 0 = no horizontal sync     |           |

|                         |              |        | 1 = horizontal retrace     |           |

|                         |              |        | blanking occurring         |           |

|                         |              | 7      | Light Pen Detect           |           |

|                         |              | ſ      | 0 = no data to transfer    |           |

|                         |              |        | 1 = value ready for read   |           |

|                         |              |        | - verde ready for read     |           |

|                         |              |        |                            | Write     |

| 3B1 or 3D1              | A1           | R      | ad data from uPD7220 FIFO  | command   |

|                         |              |        |                            | into FIFO |

The uPD7220's status register can be read at any time. All other read/write operations through these ports are determined by the state of the bit flags in the status register. The FIFO data register can be read, and commands and parameters are written into the GDC's FIFO using the same two ports, depending on the state of the status register flags. The FIFO read and command and parameter write functions of these two ports is described in Appendix C, which contains detailed programming information for the uPD7220.

. . .

## 5.4 uPD7220 LUT / Zoom Register (I/O Base +2 -- '3B2' or '3D2')

The color look-up table and zoom control or LUT/Zoom I/O port is a writeonly port used for two separate functions. This port, along with the Mode Register port and the Color Register port, is used to program the look-up table located in the output DAC. This port also controls a hardware circuit which, when used in conjunction with the uPD7220 commands, allows the uPD7220 to be zoomed.

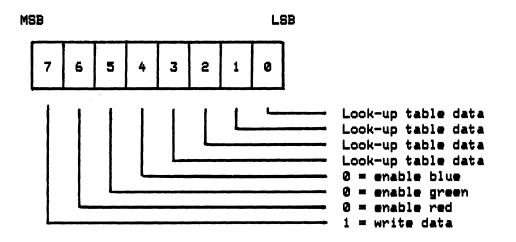

#### 5.4.1 uPD7220 Color Look-Up Table (LUT) Function

The digital-to-analog (DAC) converter used in the TRANSFORMER has a 16 word by 4 bit look-up table for each of the three analog outputs. During normal system display operation, the four bits of information received from the display memory are used as an index of addresses in the look-up table. These addresses call up previously loaded data which is passed on to the digital-to-analog converters.

To enable loading the DAC look-up tables, the Mode Register I/O port is first loaded with the value 40 hex or the binary value of  $01 \times 000 \times x$  (where x indicates a doesn't care condition). This allows the lower four bits of the color register to pass directly to the look-up table address inputs.

While the look-up table is being loaded, the LUT/Zoom bits are defined as shown here:

The upper four bits of the LUT/Zoom I/O port are control lines. The lower four bits are data lines.

Bit 7 must be low while the color register and the look-up tables are loaded. Only one of the enable bits (bits 4, 5 and 6) should be low to enable one of the look-up tables to be loaded at a time.

After a byte of the color look-up table data has been written to the LUT/Zoom, the port must be rewritten with the same data except that bit 7 must be high. The LUT/Zoom port must then be written again with bit 7 low. This procedure produces a write pulse to the look-up tables while keeping all other data constant. This same procedure must be repeated for all 48 data locations (16 locations in each of three look-up tables).

After the look-up tables have been loaded, the top four bits in the LUT/Zoom port should be set low (0). This enables the normal reading action of all three look-up tables. The lower four bits are no longer used by the look-up tables and they can be programmed as needed for the zoom function. The Mode Register and Color Register should also be reloaded with their correct values at this time.

Note that this procedure is not required if the TRANSFORMER is operated in TTL mode, which does not use the DAC look-up tables.

#### 5.4.2 uPD7220 Hardware Zoom Function

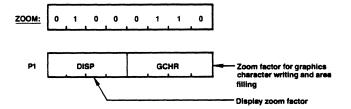

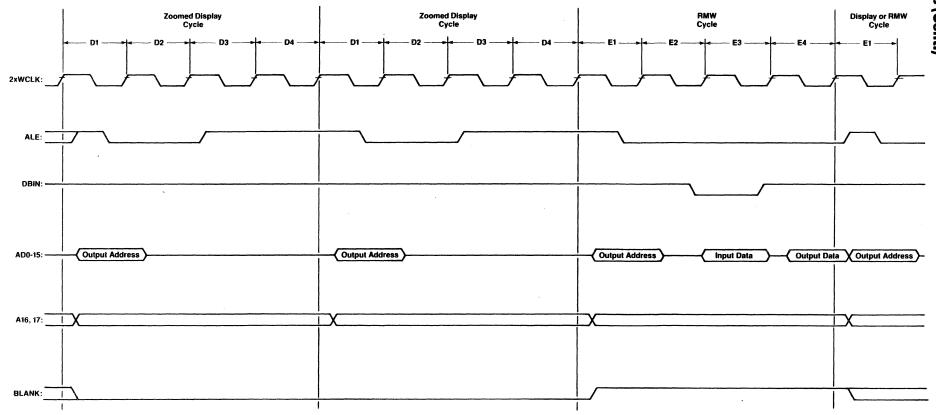

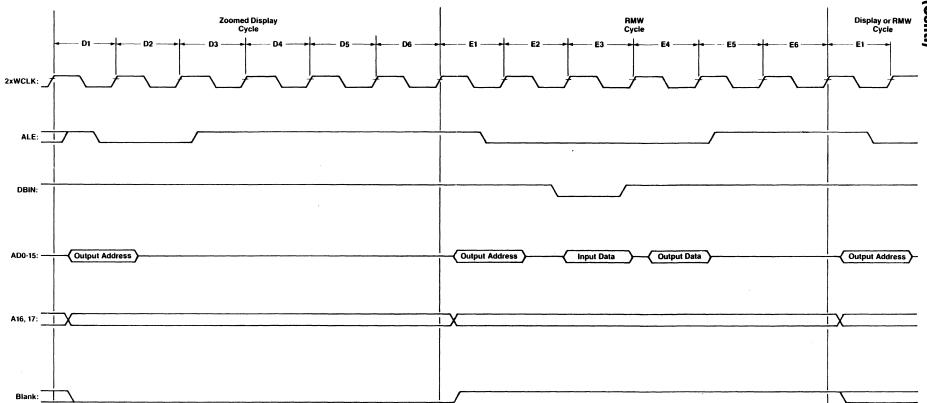

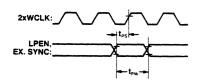

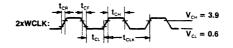

The uPD7220 can display on the monitor a zoomed image of the information contained in its portion of display memory. The display zoom or magnification is implemented by pixel replication. Because the uPD7220 uses two additional clock cycles for each increase in zoom magnification, the TRANSFORMER video timing hardware must be controlled to slow the output of pixels to the monitor to match the zoom factor used by the uPD7220. The LUT/Zoom port controls this hardware.

The uPD7220 uses four bits of the its Zoom command byte to control the display zoom factor. A zoom factor of zero (0) specifies no zoom. Fifteen (15) specifies the maximum zoom factor. The complement of uPD7220 display zoom value must be loaded into the lower four bits of the LUT/Zoom port. This means that if the GDC display zoom factor is set to zero (no zoom), the LUT/Zoom register must be set to 'OF'. Be sure that only the lower four bits are set and the upper four bits remain low. If any value is sent to. the upper four bits, the color look-up table is enabled and the value of the lower four bits is passed to the DAC.

Except at those times when the look-up table is being loaded, the Zoom register bits are defined as follows:

LUT/ZOOM Register:

MSB

| 7     | 6     | 5     | 4     | 3                | 2                | 1                | 0                |

|-------|-------|-------|-------|------------------|------------------|------------------|------------------|

| 00000 | 00000 | 00000 | 00000 | 1<br>1<br>1<br>0 | 1<br>1<br>1<br>0 | 1<br>1<br>0<br>0 | 1<br>0<br>1<br>0 |

GDC Display Zoom Factor:

LSB

when GDC zoom = 0 when GDC zoom = 1when GDC zoom = 2when GDC  $zoom = 3 \dots to$ when GDC zoom = 15

5-5

-

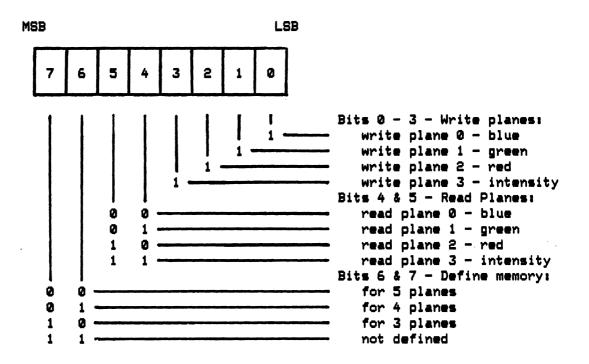

#### 5.5 Memory Configuration Register (I/O Base +3 -- '3B3' or '3D3')

The Memory Configuration Register is a write-only register used to control the TRANSFORMER's display memory organization and operation.

Bits 0 to 3 define which the uPD7220 display planes can be written. Bits 4 and 5 define which uPD7220 display planes can be read by the system. Bits 6 and 7 define the configuration of uPD7220 display memory. The color definition of each plane is meaningful in TTL mode only. In analog versions of the TRANSFORMER, the display color of each plane is defined by the color look-up table values loaded into the DAC.

Bits 0 through 3 of this register are used to define which uPD7220 display memory planes will be written. If more than one bit is set high, both the system and the uPD7220 can write to multiple display planes. This allows any color to be written with a single memory access. These bits are used by both the system and the uPD7220 to determine which display plane to write.

Bits 4 and 5 of the Configuration register define which memory plane will be read by the system. This separate plane read definition is necessary because multiple plane reads are not possible. You should also note that no planes can be read if all four write bits are set to zero.

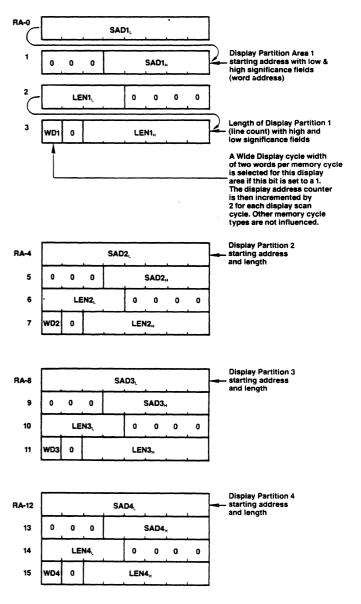

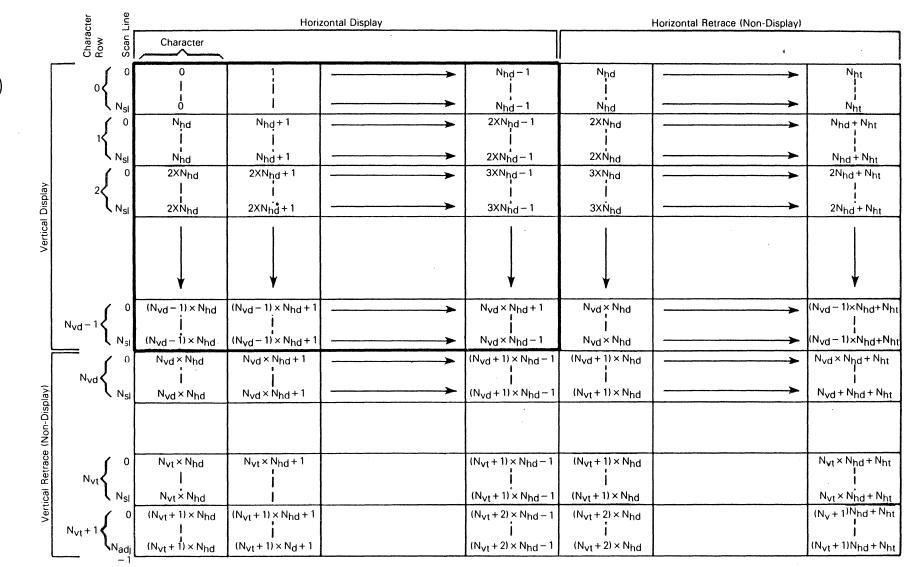

This plane read bit configuration allows multiple TRANSFORMER cards to be installed with all uPD7220 planes located at location A0000. The read bits are used to define the system accesses to the display memory only. The uPD7220 uses its address bits A16 and A17 to read the display memory planes. The uPD7220 chip, where A16 is the LSB and A17 is the MSB, defines which memory plane to read using the same logical bit values as bits 4 and 5 of this register The TRANSFORMER has 160K bytes of display memory. This physical memory is used to store both uPD7220 and MC6845 data. The size and location of the logical memory is controlled by the top two bits of the Configuration Register. The table below shows how the memory mapping is affected by the value of bits 6 and 7.

| Base +3<br>Bits<br>7 6 | Display<br>Resolution | 7220 Plane Configuration<br>No. Size Memory Address | Memory Shared By MC6845<br>At B0000 or B8000 |  |  |  |  |

|------------------------|-----------------------|-----------------------------------------------------|----------------------------------------------|--|--|--|--|

| 00                     | 640 x 400             | 4 40K A0000 - A9FFF                                 | separate 32k memory plane                    |  |  |  |  |

| 01                     | 640 x 480             |                                                     | shares 32K with plane 0                      |  |  |  |  |

| 10                     | 640 x 480             |                                                     | shares 16K with plane 0                      |  |  |  |  |

The MC6845 can access up to 32K bytes of the TRANSFORMER's total display memory. The uPD7220 can use the entire 160K bytes of memory.

The five plane configuration evenly allocates memory for each of five display planes -- four planes of 32Kbytes each are allocated for the uPD7220, leaving 32Kbytes of memory free for the MC6845 plane.

In three and four plane memory configurations, the MC6845 and the uPD7220 must actually share physical memory even though the logical memory address is different. This means that writing into the MC6845 memory buffer may modify the data in the uPD7220 display memory. The four plane configuration allocates 40Kbytes of memory for each of the four uPD7220 display planes. This enables the uPD7220 to be operated at a higher resolution; but, this configuration should not be used when the MC6845 is active because the data written into shared memory locations (the first 32K of plane 0) overwrites and destroys data already present at that address.

To enable the uPD7220 to display at 640 x 480 pixel resolution with a MC6845 display overlay, the three plane configuration moves the start location of the uPD7220 memory away from the normal memory buffer start address of A0000 to A4000. This mode also physically disables plane 3, the uPD7220 intensity plane, which limits the uPD7220 graphics display to a total of eight colors at any one time. The uPD7220 and MC6845 also share 16Kbytes of memory in this mode. However, because the IBM normally only knows about and uses the first 16Kbytes of memory in its display memory buffers, memory sharing in this configuration normally presents no problems. However, if the MC6845 is operated in the 640 x 400 color/graphics mode, the display memory accessed at B8000 will overwrite the uPD7220 graphics.

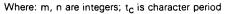

## 5.6 Talking to the MC6845 CRT Controller

IBM assigns two ports for access to the MC6845 CRT controller's internal registers -- the Index Register at 3B4 or 3D4 and the Data Register at 3B5 or 3D5. The TRANSFORMER assigns four I/O ports to this function. Two of the ports -- the IBM Index Register (Base +4) and the IBM Data Register (Base +5) -- are the two ports which IBM normally uses to control the MC6845. When these ports are used, the TRANSFORMER's on-board ROM intercepts and modifies the data before it is sent to the MC6845, allowing the IBM-compatible data to be correctly interpreted by the hardware for high resolution display. The other two ports -- the 6845 Index Register (Base +6) and the 6845 Data Register (Base +7) -- allow direct access from the system bus to the MC6845.

Software written for the IBM PC which talks to an IBM display adapter through the BIOS uses the I/O ports at Base +4 and Base +5. Whenever the TRANSFORMER is used with such software, the values sent to the TRANSFORMER hardware are intercepted, and the values contained in the on-board ROM are substituted and passed on to the MC6845. If the software is not "well behaved" and talks directly to the hardware through another I/O port, the information contained in the TRANSFORMER's ROM is not passed to the IBM Data Register. The display operating modes are, as a result, incorrectly The correct values can also be sent directly to the MC6845 data defined. registers through the second set of I/O ports at Base +6 and Base +7. These ports are also useful if you want to initialize the TRANSFORMER using display values which are different from those contained in the TRANSFORMER's ROM.

The following table defines the MC6845 data registers and the values that are normally loaded into those registers as well as the values substituted by the TRANSFORMER'S ROM. The ROM values shown here are those contained in the ROM firmware used with standard non-interlaced monitors such as the Gigatek 1331 and the Princeton Graphics SR-12. Remember that the values resident in the ROM firmware are dependent on the type of monitor you specified. The MC6845 register initialization values for your monitor type may not be the same as those shown in the table below.

| Add        |     | Register<br>ber & Type       | Units               | R/W | Mo<br>IBM | no<br>ROM | 40 x<br>Alp<br>IBM |    | 80 x<br>Alp<br>IBM |    | Grap<br>IBM | hic <del>s</del><br>ROM |

|------------|-----|------------------------------|---------------------|-----|-----------|-----------|--------------------|----|--------------------|----|-------------|-------------------------|

| 00         | RØ  | Horizontal<br>Total          | Char                | W   | 61        | 67        | 38                 | 33 | 71                 | 67 | 38          | 33                      |

| 01         | R1  | Horizontal<br>Displayed      | Char                | W   | 50        | 50        | 28                 | 28 | 50                 | 50 | 28          | 28                      |

| 02         | R2  | Horizontal<br>Sync Position  | Char                | W   | 52        | 56        | 5D                 | 2B | 5A                 | 56 | 2D          | 2B                      |

| 03         | R3  | Horizontal<br>Sync Width     | Char                | W   | ØF        | Ø6        | ØA                 | 06 | ØA                 | 06 | ØA          | 06                      |

| 04         | R4  | Vertical<br>Total            | Char<br>Row         | W   | 19        | 1F        | 1F                 | 1F | 1F                 | 1F | 7F          | 7F                      |

| 05         | R5  | Vertical<br>Total Adjust     | Scan<br>Line        | W   | 06        | 09        | 06                 | 09 | 06                 | 09 | 06          | 09                      |

| <b>0</b> 6 | R6  | Vertical<br>Displayed        | Char<br>Row         | W   | 19        | 19        | 19                 | 19 | 19                 | 19 | 64          | 64                      |

| 07         | R7  | Vertical<br>Sync Position    | Char<br>Row         | W   | 19        | 1C        | 1C                 | 1C | 1C                 | 1C | 70          | 70                      |

| Ø8         | R8  | Interlace<br>Mode            | See                 | W   | 02        | 02        | <b>0</b> 2         | 02 | Ø2                 | Ø2 | 02          | 02                      |

| 09         | R9  | Maximum Scan<br>Line Address | Scan<br>Line        | W   | ØD        | ØF        | 07                 | OF | 07                 | ØF | 01          | 03                      |

| 0A         | R1Ø | Cursor Start                 | Scan<br>Line        | W   | ØB        | ØC        | Ø6                 | ØC | 06                 | ØC | 06          | ØC                      |

| ØB         | R11 | Cursor End                   | Scan<br>Line        | W   | ØC        | ØE        | 07                 | ØE | 07                 | ØE | 07          | ØE                      |

| ØC         | R12 | Start Address<br>(High)      |                     | W   | 00        |           | 00                 |    | 00                 |    | 00          |                         |

| ØD         | R13 | Start Address<br>(Low)       |                     | W   | 00        |           | 00                 |    | 00                 |    | 00          |                         |

| 0E         | R14 | Cursor Address<br>(High)     |                     | R/W | 00        |           |                    |    |                    |    | -           |                         |

| ØF         | R15 | Cursor Address<br>(Low)      | enne dian kine kine | R/W | 00        |           |                    |    |                    |    | ****        |                         |

| 10         |     | Light Pen (High)             |                     | R   | Rsv       |           |                    |    |                    | -  |             |                         |

| 11         | R17 | Light Pen (Low)              |                     | R   | Rsv       | d -       |                    |    |                    |    |             |                         |

Table 5.3 Summary of Standard IBM and TRANSFORMER MC6845 Register Values

#### Notes:

- 1. All register values are shown in hexadecimal notation. The TRANSFORMER does not intercept or change values sent to registers R12 through R17.

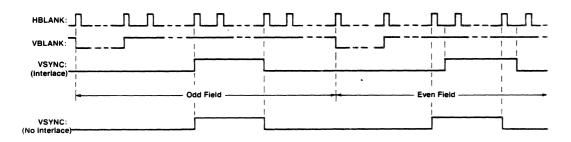

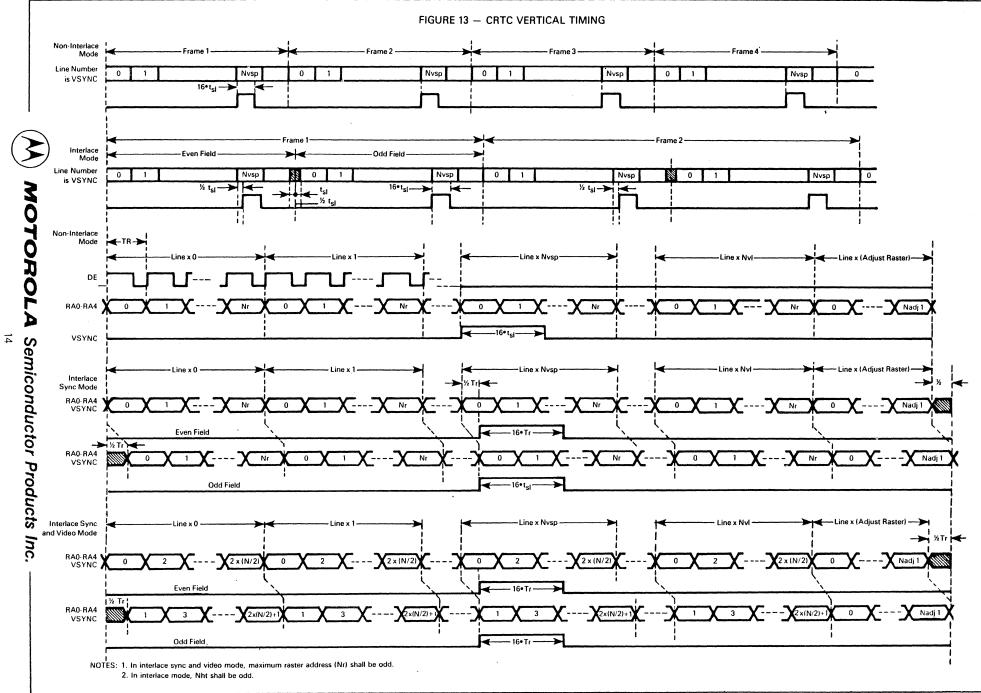

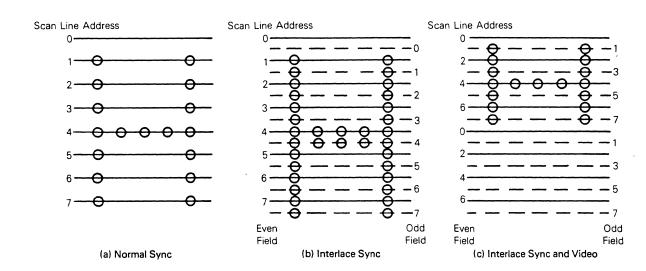

- 2. The MC6845 supports non-interlaced (where R8 value = 0 or 2), interlace sync (value = 1), and interlaced sync and video (value = 3) modes of operation. IBM display adapters supports only non-interlaced monitors and IBM always specifies that mode with the value of 2 at R8. The TRANSFORMER firmware also uses that value when operating in non-interlaced mode for IBM compatibility. The TRANSFORMER also supports use of monitors operating in interlaced mode using the MC6845 interlace sync and video mode. In this mode, the value of R8 is 3.

#### 5.7 IBM Index Register (I/O Base +4 -- '3B4' or '3D4')

The IBM Index Register port accesses the address register of the MC6845. This write-only register is used as pointer to direct the transfer of data to and from the correct data register. As with IBM display adapter cards, the five least significant bits of the I/O bus are loaded from the system into this register with the necessary pointer to the required register.

When a value is detected in this register, the TRANSFORMER ROM intercepts the pointer value and the IBM Data Register value. The ROM firmware then compares these values to the ROM register values. If the register pointed to is one with which the ROM is concerned and if the value of the data sent from the system bus is different from the value of that register contained in the ROM value table, then the value sent from the system is discarded and the data value contained in the ROM is loaded into the IBM Data Register.

#### 5.8 IBM Data Register (I/O Base +5 -- '385' or '3D5')

The IBM Data Register is the I/O port which the IBM normally uses to load data into the MC6845. The TRANSFORMER modifies the data sent to the MC6845 from this port. The values loaded in this register are determined by the values contained in the TRANSFORMER's ROM. Each ROM contains a table of register values in firmware which is calculated for operation with a specific monitor. If the installed ROM isn't configured for the current display monitor, these values will be incorrect.

## 5.9 6845 Index Register (I/O Base +6 -- '386' or '3D6')

The 6845 Index Register directly accesses the MC6845 address register. This write-only register is a pointer which is used to direct the transfer of data to the correct MC6845 register. Use this port to send data directly to the MC6845's address register without going through the TRANSFORMER's interceptor ROM.

#### 5.10 6845 Data Register (I/O Base +7 -- '3B7' or '3D7')

The 6845 Data Register is a write-only I/O port which accesses the MC6845 register pointed to by the 6845 Index Register. The value to be sent directly to the MC6845 register pointed to by the 6845 Index Register is loaded into this port. This value is transferred to the MC6845 register without intervention of the TRANSFORMER ROM.

#### 5.11 Mode Select Register (I/O Base +3 -- '3B8' or '3D8')

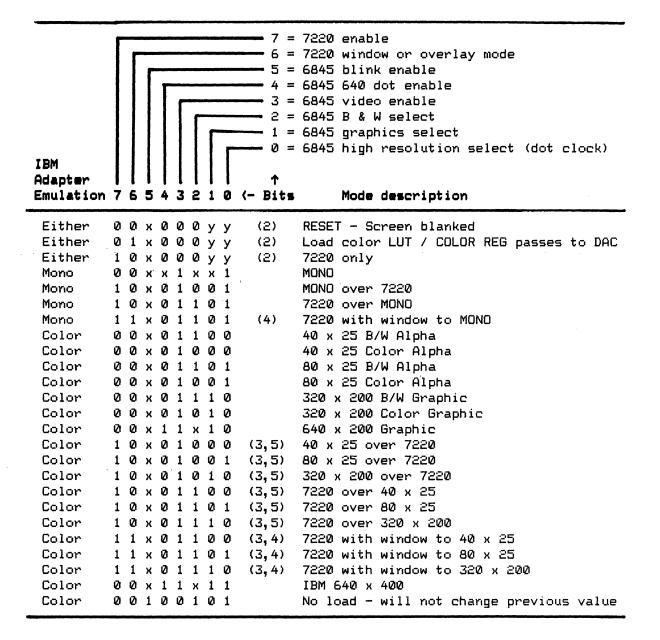

The Mode Select Register is an 8-bit write-only register used to control the video output of the TRANSFORMER. While the TRANSFORMER uses the same basic bit definition as IBM display adapters to maintain compatibility with software written for the IBM adapters, the TRANSFORMER also uses the top two bits to define the uPD7220 operating mode.

When the jumper at J1 is installed in the "BOTH" position, the operating mode of the TRANSFORMER is defined by accesses to the Mode Select Register. If the Mode Select Register is accessed at '3B8', the TRANSFORMER emulates the IBM monochrome adapter where the MC6845 responds only to IBM monochrome compatible mode selections. Accessing the Mode Select Register at '3D8' causes the TRANSFORMER to emulate the IBM color/graphics adapter, permitting selection of only those modes which are compatible with the IBM color/graphics adapter.

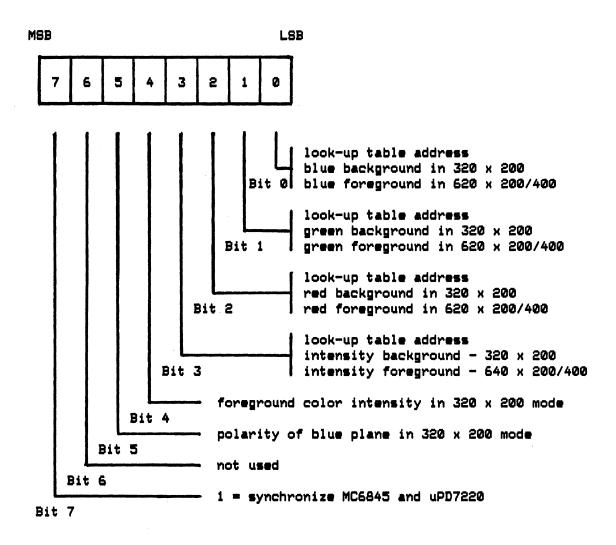

This following diagram shows the bit definitions of the Mode Select port:

MSB LSB 3 2 7 6 5 4 1 0 = 1 ow resolution text 40x25Bit Ø 1 = high resolution text 80x250 = alphanumeric (text) modeBit 1 1 = graphics mode 0 = color mode if bit 7 = 00 = 6845 (color) in foreground if bit 7 = 1Bit 2 = b & w mode if bit 7 = 01 = 6845 (color) in background if bit 7 = 10 = disable MC6845 video Bit 3 1 = enable MC6845 video0 = 320 pixels horizontal graphics Bit 4 1 = enable 640 pixels horizontal for high resolution graphics 0 = no blink/16 color background Bit 5 1 = alphanumeric blink enable/8color background 0 = load LUT if bit 7 = 00 = overlay if bit 7 = 1Bit 6 1 = 6845 only if bit 7 = 01 = window if bit 7 = 10 = disable uPD7220Bit 7 1 = enable uPD7220

5-11

The following table is a summary of the video output modes defined for the TRANSFORMER.

#### Notes:

- 1. x = doesn't care or not defined

y = determined by preceeding and following modes

- Bits 0 and 1 should be the same as the preceding and following modes initialized. If the value of these bits is changed, a sync procedure must be executed.

- 3. If bits 0 and 1 are changed from their previous values. a sync procedure must be executed.

- 4. A window is defined whenever a pixel with the color index value of 7 or unintensified white is written to the uPD7220 display memory. At color index 7, the bit values corresponding to planes 0, 1, 2 have a value of 1 and plane 3 is equal to 0. Wherever a pixel of color index 7 is encountered, the TRANSFORMER hardware turns on the MC6845 output. Note that the window must be defined in uPD7220 memory to enable display of the MC6845 plane. The MC6845 plane is not displayed where no window is defined, although the contents of the MC6845 memory buffer are undisturbed. When the MC6845 plane is displayed in a window, the background is retained.

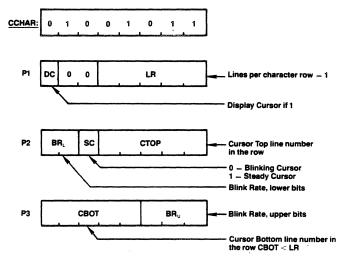

- In overlay modes, only the contents of the MC6845 foreground is 5. displayed; the MC6845 background is suppressed. The contents of the uPD7220 display planes are output to the monitor instead of the MC6845 background color. In effect, whatever is written to the uPD7220 display planes becomes the MC6845 background.