18651 Von Karman, Irvine, California 92713 Tel 714 833 8830 TWX 910 595 1767

CAI Limited

Hertford House, Denham Way, Rickmansworth, Herts WD3 2XD

TEL RICKMANSWORTH 71211 • TELEX 922654

# DISTRIBUTED I/O SYSTEM USER'S MANUAL

91-53629-00B5

May 1977

# REVISION HISTORY

| Revision | Issue Date     | Comments                                                                                              |

|----------|----------------|-------------------------------------------------------------------------------------------------------|

| AO       | April 1975     | Original issue                                                                                        |

| Al       | April 1976     | Adds Positive-true General Purpose<br>Intelligent Cable and User Microprogrammed<br>Intelligent Cable |

| A2       | June 1976      | Adds Magnetic Tape Intelligent Cable                                                                  |

| во       | July 1976      | General revision to add DMA I/O Distributor                                                           |

| Bl       | August 1976    | Revises Magnetic Tape Intelligent Cable Programming Example                                           |

| B2       | September 1976 | Adds IEEE Intelligent Cable                                                                           |

| В3       | March 1977     | Adds Dataproducts Line Printer<br>Intelligent Cable                                                   |

| В4       | April 1977     | Miscellaneous Minor Changes                                                                           |

| B5       | May 1977       | Adds 32-Bit G-P Intelligent Cable                                                                     |

# TABLE OF CONTENTS

| Section |                                                                                                                                                                                                  | Page                                       |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 1       | GENERAL DESCRIPTION                                                                                                                                                                              |                                            |

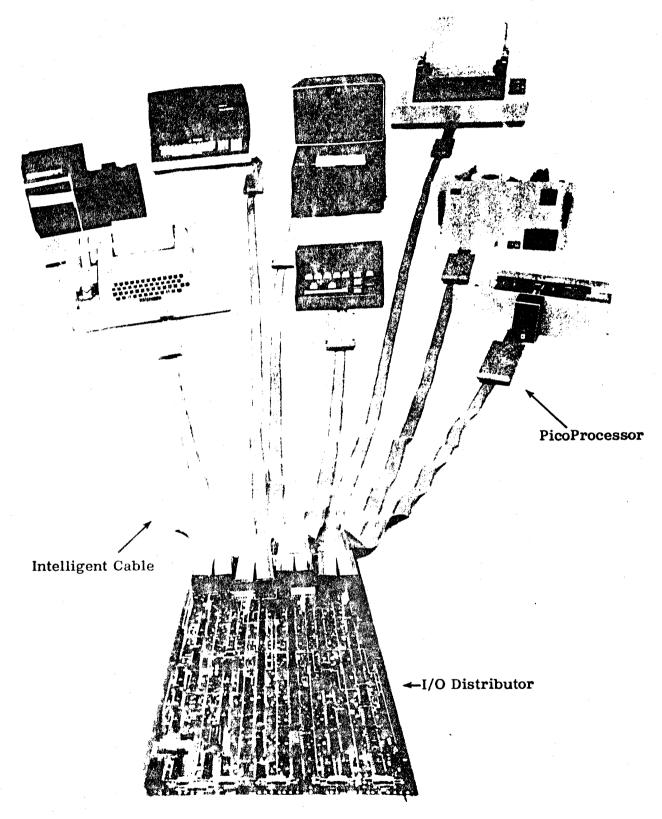

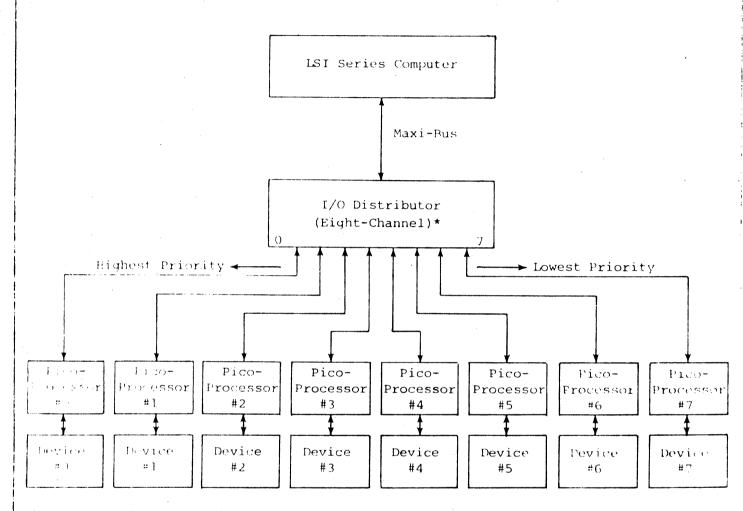

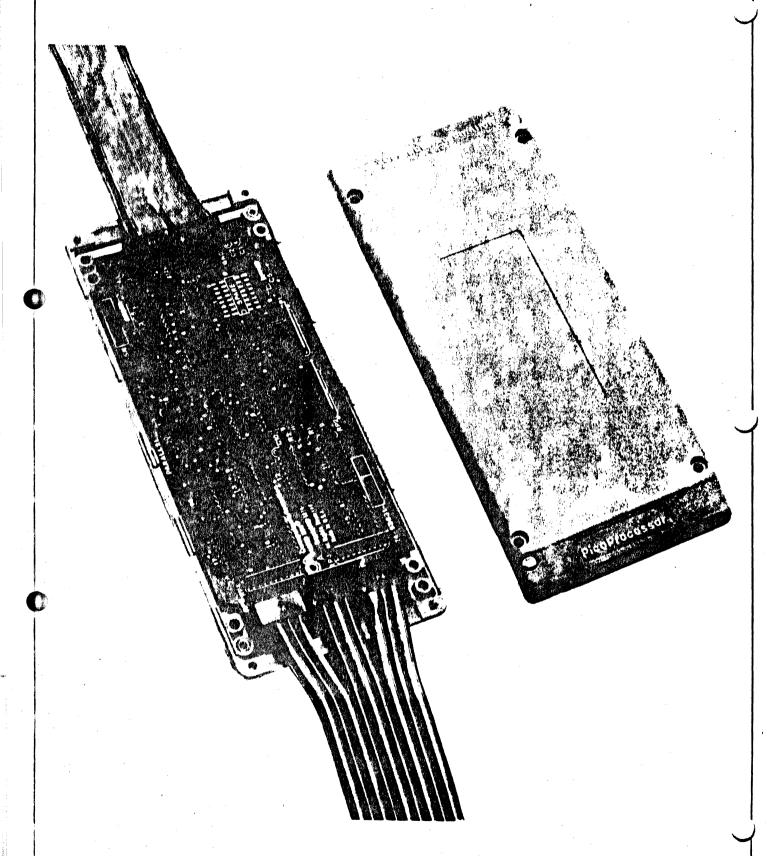

|         | 1.1 DISTRIBUTED I/O SYSTEM CONCEPT                                                                                                                                                               | 1-2                                        |

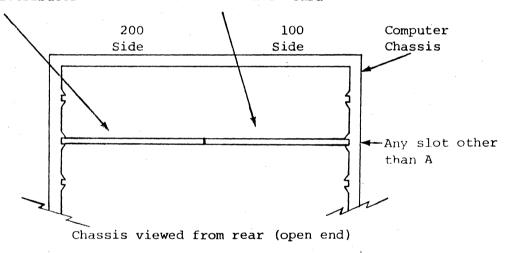

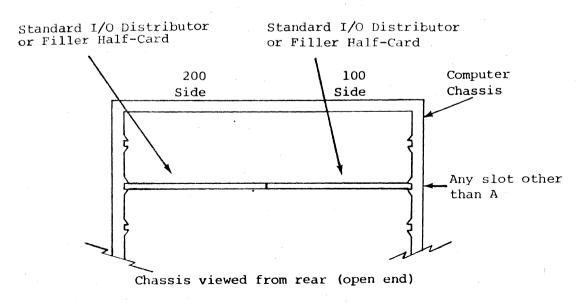

|         | 1.2 1/0 DISTRIBUTORS                                                                                                                                                                             | 1-4                                        |

|         | 1.3 INTELLIGENT CABLES - FUNCTIONAL DESCRIPTION                                                                                                                                                  | 1-5                                        |

|         | 1.4 SPECIFICATIONS  1.4.1 I/O Distributors Available  1.4.2 Device Data Formats  1.4.3 Device Control Configurations  1.4.4 Clocks  1.4.5 Environment  1.4.6 Power Requirements  1.4.7 Bandwidth | 1-7<br>1-7<br>1-7<br>1-7<br>1-8<br>1-8     |

| 2       | OPERATION AND PROGRAMMING                                                                                                                                                                        |                                            |

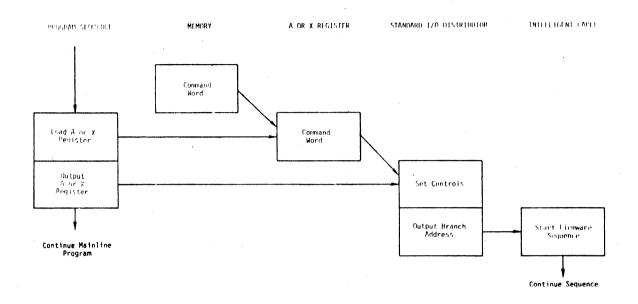

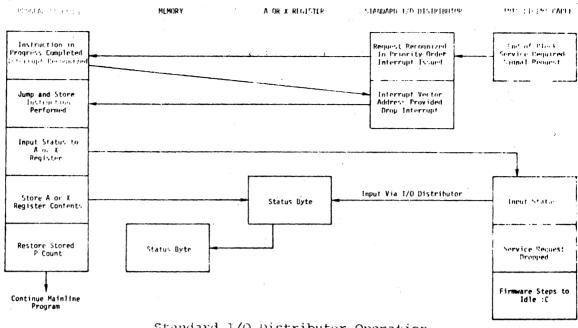

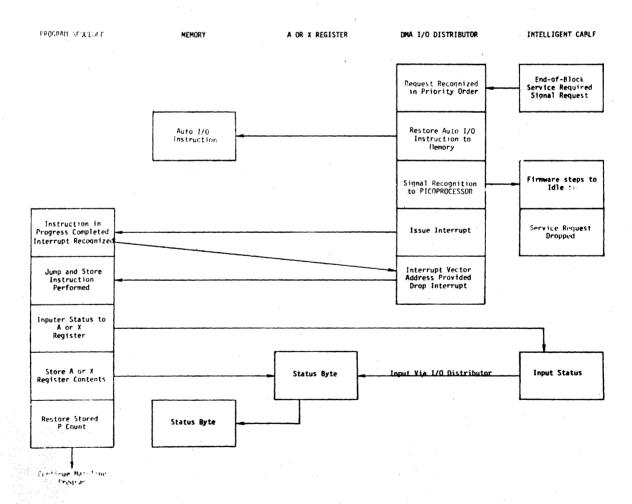

|         | 2.1 SYSTEM OPERATION                                                                                                                                                                             | 2-1<br>2-2<br>2-4                          |

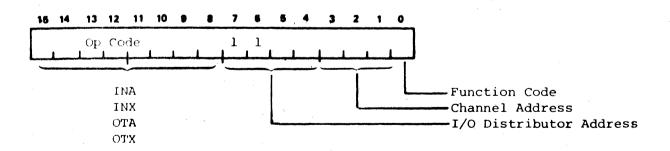

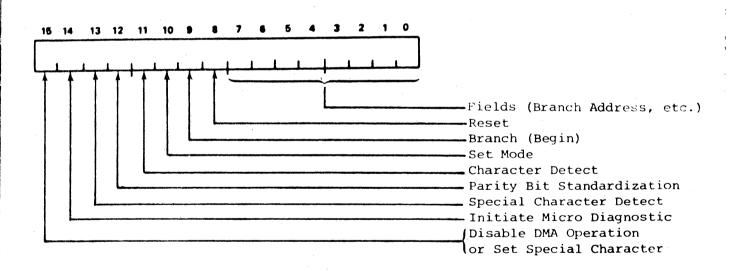

|         | 2.2 PROGRAMMING  2.2.1 Input and Output Instructions  2.2.2 Distributed I/O Command Word  2.2.3 Auto I/O Instruction  2.2.4 Interrupt Vectoring  2.2.5 Status                                    | 2-9<br>2-9<br>2-11<br>2-20<br>2-21<br>2-23 |

|         | 2.3 NON-INTERRUPT/NON-DMA OPERATION                                                                                                                                                              | 2-24                                       |

# TABLE OF CONTENTS (Cont 'd)

| 3.2.1 NOTERFACE LOGIC (Parallel Intelligent Cables) 3.2.2 Input Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Section |      | <u>P</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | age                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 3.2.1 NOUTPUT LOGIC 3.2.2 Input Logic 3.2.2 Input Logic 3.2.3 STANDARD INTELLIGENT CABLE DESCRIPTIONS 3.3.1 Line Printer 3.3.1.1 Description 3.3.1.2 Physical Details 3.3.1.3 Line Printer Status Word 3.3.1.4 Operating Sequence 3.3.1.5 Interface Description 3.3.1.6 Strapping Requirements 3.3.1.7 Device Cable Description 3.3.1.8 Programming Example 3.3.2.1 Description 3.3.2.2 Physical Details 3.3.2.3 Card Reader 3.3.2.4 Operating Sequence 3.3.3.2.5 Interface Description 3.3.2.6 Strapping Requirements 3.3.2.7 Device Cable Description 3.3.2.8 Description 3.3.2.9 Physical Details 3.3.2.1 Description 3.3.3.2.1 Description 3.3.3.2.2 Physical Details 3.3.3.3 Perior Cable Description 3.3.3.4 Operating Sequence 3.3.3.3 Perior Cable Description 3.3.3.4 Perior Cable Description 3.3.4.1 Description 3.3.4.2 Physical Details 3.3.4.3 Programming Example 3.3.4.4 Operating Sequence 3.3.3.4.5 Interface Description 3.3.4.6 Strapping Requirements - None Required 3.3.3.4.7 Device Cable Description 3.3.4.8 Programming Example 3.3.4.9 Description 3.3.4.1 Description 3.3.4.2 Physical Details 3.3.4.3 Programming Example 3.3.4.4 Operating Sequence 3.3.4.5 Interface Description 3.3.4.6 Strapping Requirements 3.3.4.7 Device Cable Description 3.3.4.8 Programming Example 3.3.4.8 High-Speed Paper Tape Punch 3.3.4.9 Description 3.3.4.1 Description 3.3.4.1 Description 3.3.4.2 Physical Details 3.3.4.3 Description 3.3.4.5 Physical Details 3.3.5.1 Description 3.3.5.2 Physical Details                                                                                                                                                                                                                                                       | 3       | STAN | NDARD INTELLIGENT CABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                            |

| 3.2.1 Output Logic 3.2.2 Input Logic 3.2.2 Input Logic 3.3.2.2 Input Logic 3.3.2.2 Input Logic 3.3.3.3.1 Line Printer 3.3.3.1 Line Printer 3.3.3.1.1 Description 3.3.3.1.2 Physical Details 3.3.1.3 Line Printer Status Word 3.3.3.1.4 Operating Sequence 3.3.3.1.5 Interface Description 3.3.3.1.6 Strapping Requirements 3.3.3.1.7 Device Cable Description 3.3.3.1.8 Programming Example 3.3.3.2.1 Description 3.3.3.2.1 Description 3.3.3.2.2 Physical Details 3.3.2.3 Card Reader Status Word 3.3.2.4 Operating Sequence 3.3.3.2.5 Interface Description 3.3.2.6 Strapping Requirements 3.3.2.7 Device Cable Description 3.3.3.3 High-Speed Paper Tape Reader 3.3.3.3 Physical Details 3.3.3.3 Physical Details 3.3.3.3 Operating Sequence 3.3.3.3.7 Device Cable Description 3.3.3.7 Device Cable Description 3.3.3.8 Programming Example 3.3.3.9 Physical Details 3.3.3.9 Physical Details 3.3.3.1 Device Cable Description 3.3.3.4 Description 3.3.3.4 Description 3.3.3.4 Description 3.3.4.1 Description 3.3.4.2 Physical Details 3.3.4.3 High-Speed Paper Tape Punch 3.3.4.4 Operating Sequence 3.3.3.4.7 Device Cable Description 3.3.4.8 High-Speed Paper Tape Punch 3.3.4.9 Description 3.3.4.1 Description 3.3.4.2 Physical Details 3.3.4.3 Device Cable Description 3.3.4.4 Operating Sequence 3.3.4.5 Interface Description 3.3.4.6 Strapping Requirements - None Required 3.3.4.7 Device Cable Description 3.3.4.8 High-Speed Paper Tape Punch 3.3.4.9 High-Speed Paper Tape Punch 3.3.4.1 Description 3.3.4.2 Physical Details 3.3.4.3 Device Cable Description 3.3.4.4 Operating Sequence 3.3.4.5 Interface Description 3.3.4.6 Strapping Requirements 3.3.4.7 Device Cable Description 3.3.4.8 High-Speed Paper Tape Punch 3.3.4.9 Description 3.3.4.1 Description 3.3.4.1 Description 3.3.4.2 Physical Details 3.3.4.3 Description 3.3.4.5 Physical Details 3.3.4.5 Teletype Status Word 3.3.5.5 Teletype Status Word                                                                                                                                                                                    |         | 3.1  | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -1                                                                                                         |

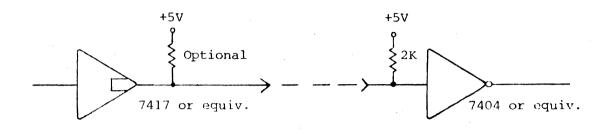

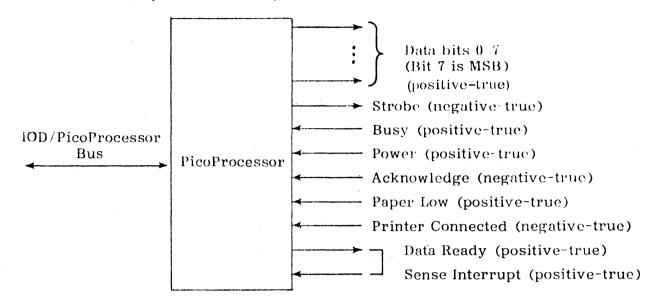

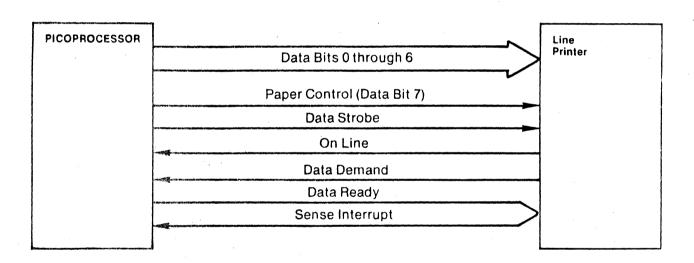

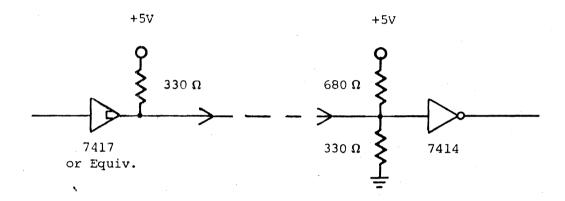

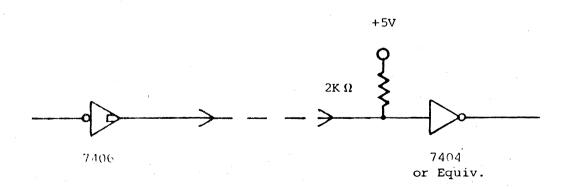

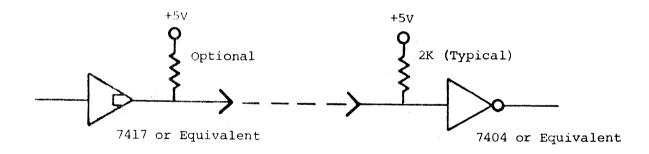

| 3.3.1. Line Printer 3.3.1.1 pescription 3.3.1.2 Physical Details 3.3.1.3 Line Printer Status Word 3.3.3.1.4 Operating Sequence 3.3.3.1.5 Interface Description 3.3.3.1.6 Strapping Requirements 3.3.1.7 Device Cable Description 3.3.1.8 Programming Example 3.3.2.1 Description 3.3.2.2 Physical Details 3.3.2.3 Card Reader 3.3.2.1 Description 3.3.2.2 Physical Details 3.3.2.3 Card Reader Status Word 3.3.2.4 Operating Sequence 3.3.2.5 Interface Description 3.3.2.6 Strapping Requirements 3.3.2.7 Device Cable Description 3.3.3.3 High-Speed Paper Tape Reader 3.3.3.3 Paper Tape Reader Status Word 3.3.3.3 Foregramming Example 3.3.3.4 Description 3.3.3.5 Interface Description 3.3.3.6 Strapping Requirements - None Required 3.3.3.3 Paper Tape Reader Status Word 3.3.3.4 Description 3.3.3.5 Strapping Requirements - None Required 3.3.3.4 Description 3.3.3.5 Description 3.3.5.5 Description 3.3.5.5 Description 3.3.5.5 Description 3.3.5.5 Description                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | 3.2  | 3.2.1 Output Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -1.<br>-1<br>-2                                                                                            |

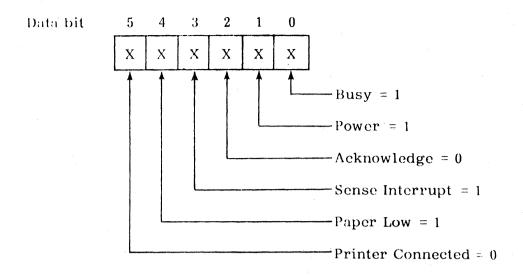

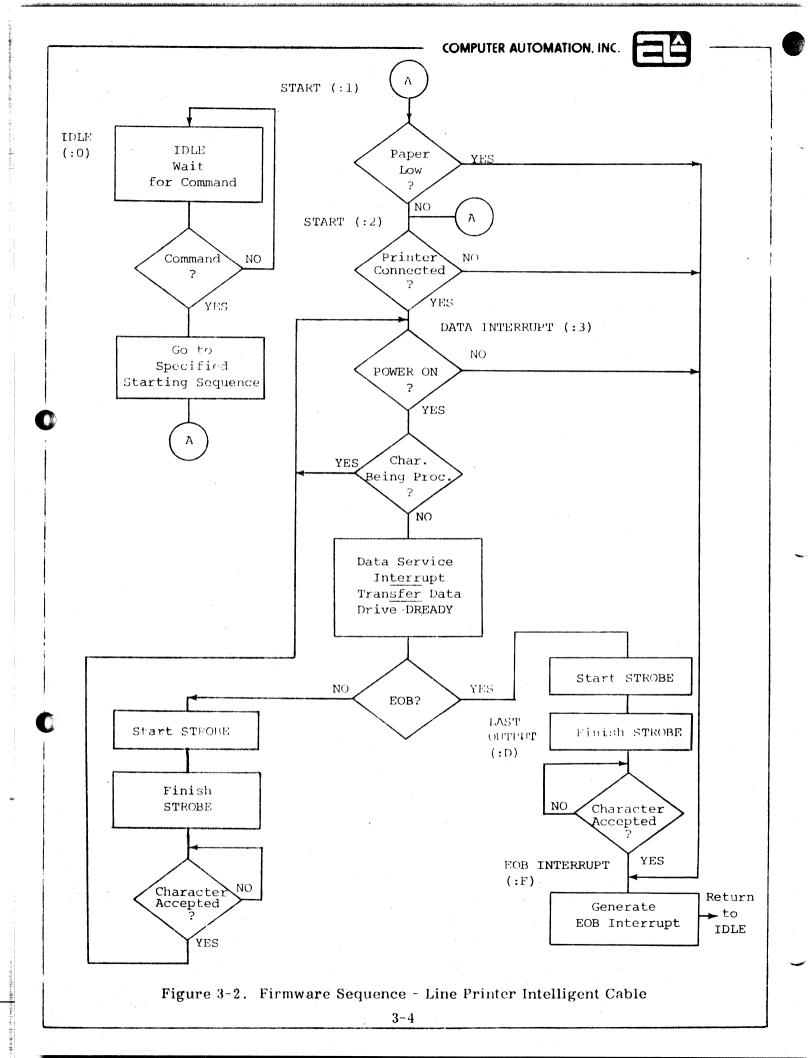

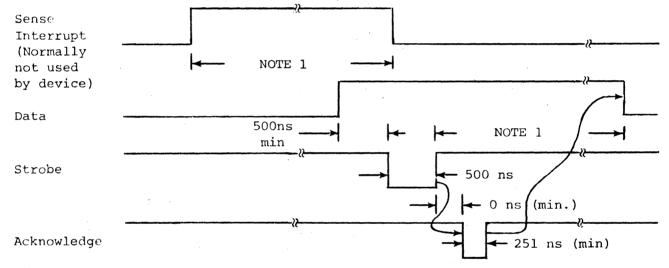

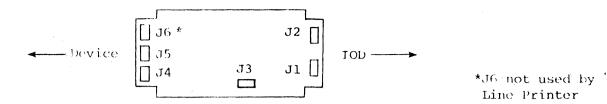

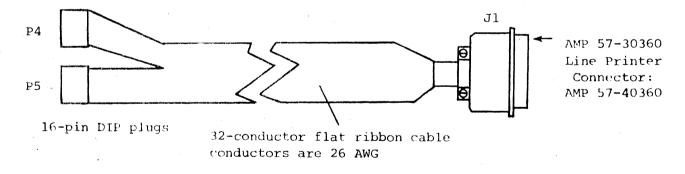

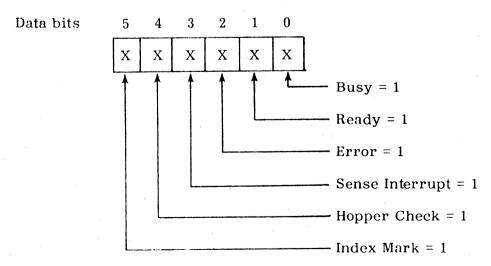

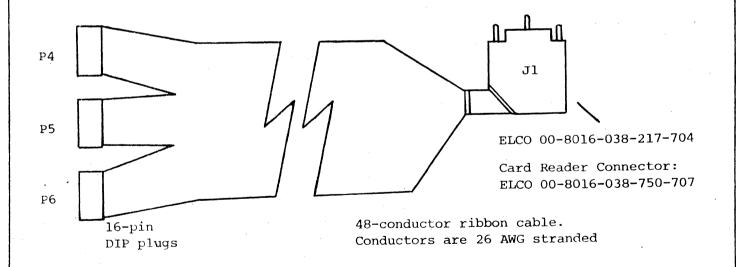

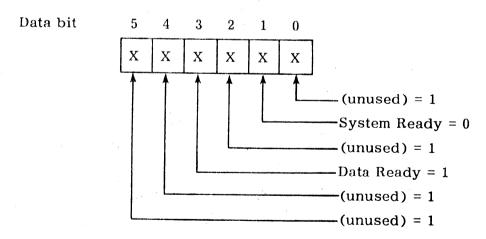

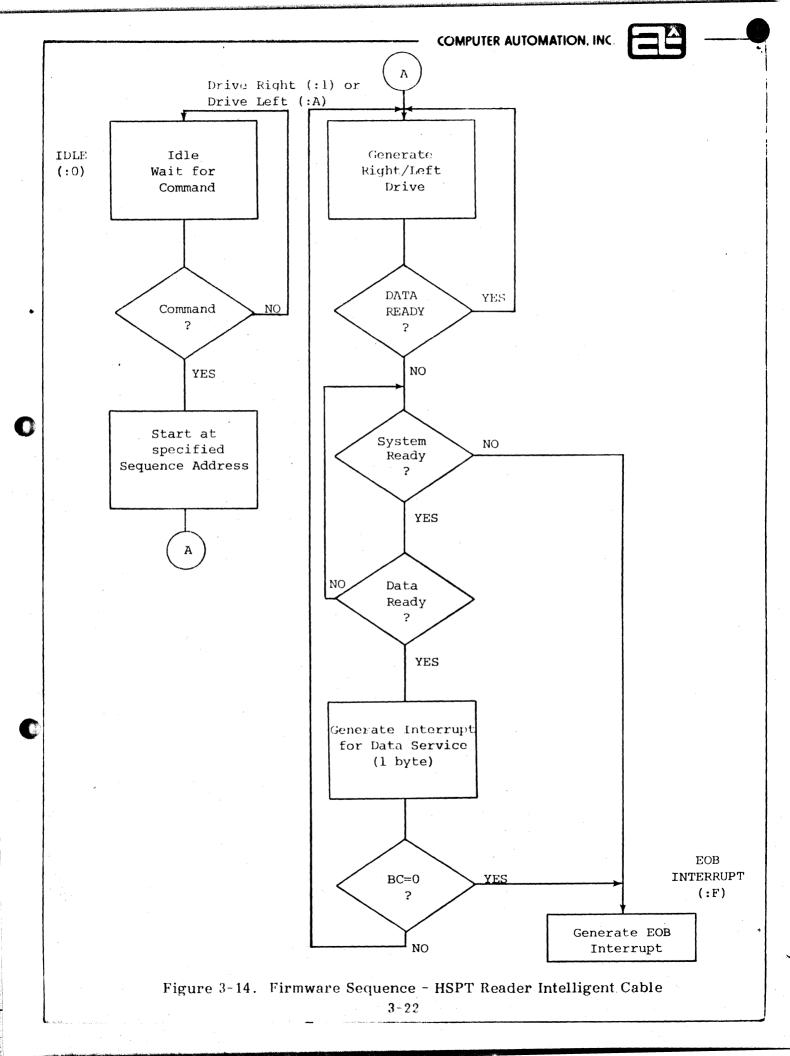

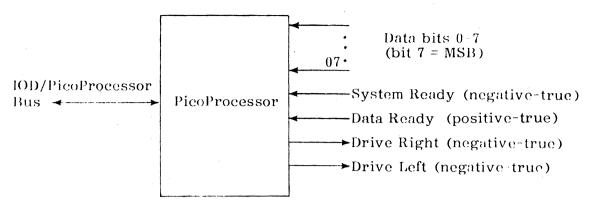

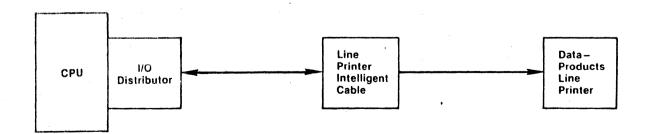

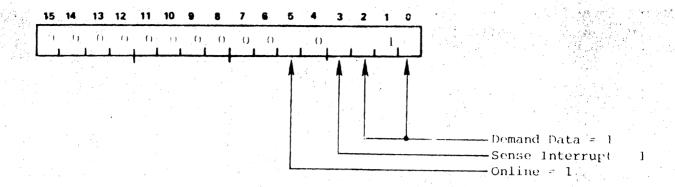

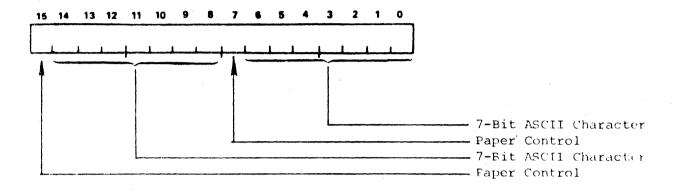

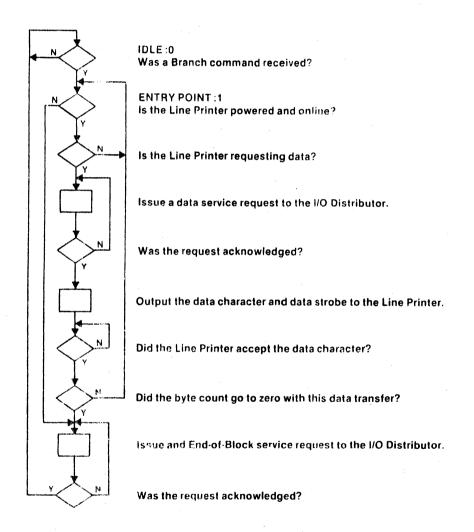

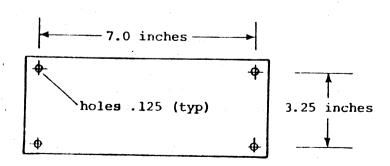

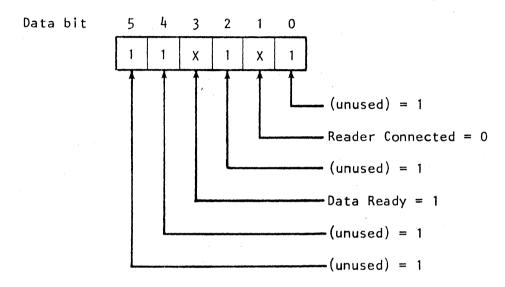

| 3.3.3.3 Paper Tape Reader Status Word 3.3.3.3.4 Operating Sequence 3.3.3.3.5 Interface Description 3.3.3.3.6 Strapping Requirements - None Required 3.3.3.3.7 Device Cable Description 3.3.3.3.8 Programming Example 3.3.3.4 High-Speed Paper Tape Punch 3.3.3.4.1 Description 3.3.4.2 Physical Details 3.3.4.3 HSPT Punch Status Word 3.3.3.4.4 Operating Sequence 3.3.3.4.5 Interface Description 3.3.4.6 Strapping Requirements 3.3.4.7 Device Cable Description 3.3.4.8 HSPT Punch Modification 3.3.3.5.1 Description 3.3.3.5.1 Description 3.3.3.5.2 Physical Details 3.3.5.3 Teletype Status Word 3.3.5.5 Teletype Status Word 3.3.5.5 Teletype Status Word 3.5.5 Teletype St |         | 3.3  | STANDARD INTELLIGENT CABLE DESCRIPTIONS       3         3.3.1 Line Printer       3         3.3.1.1 Description       3         3.3.1.2 Physical Details       3         3.3.1.3 Line Printer Status Word       3         3.3.1.4 Operating Sequence       3         3.3.1.5 Interface Description       3         3.3.1.6 Strapping Requirements       3         3.3.1.7 Device Cable Description       3         3.3.2 Card Reader       3         3.3.2.1 Description       3         3.3.2.2 Physical Details       3         3.3.2.3 Card Reader Status Word       3         3.3.2.4 Operating Sequence       3         3.3.2.5 Interface Description       3         3.3.2.6 Strapping Requirements       3         3.3.2.7 Device Cable Description       3         3.3.3 High-Speed Paper Tape Reader       3 | -2<br>-2<br>-2<br>-2<br>-3<br>-6<br>-7<br>-7<br>-9<br>-11<br>-11<br>-11<br>-12<br>-14<br>-16<br>-20<br>-20 |

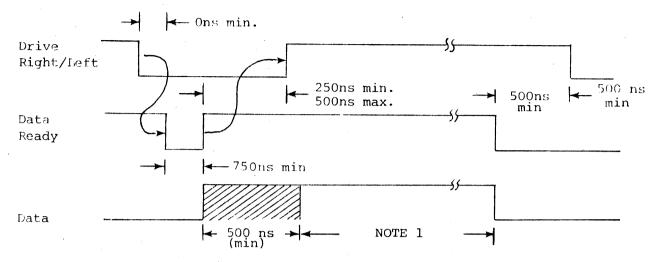

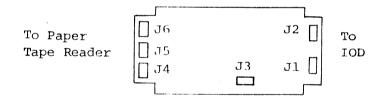

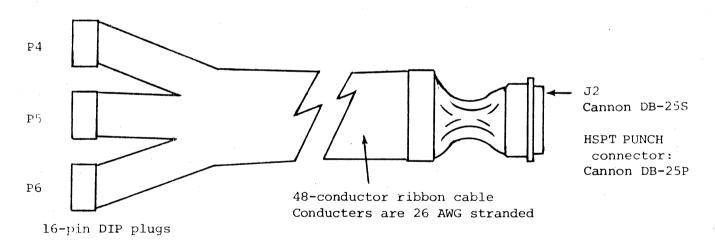

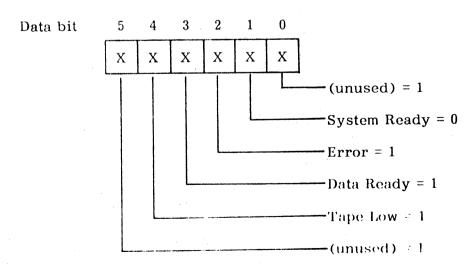

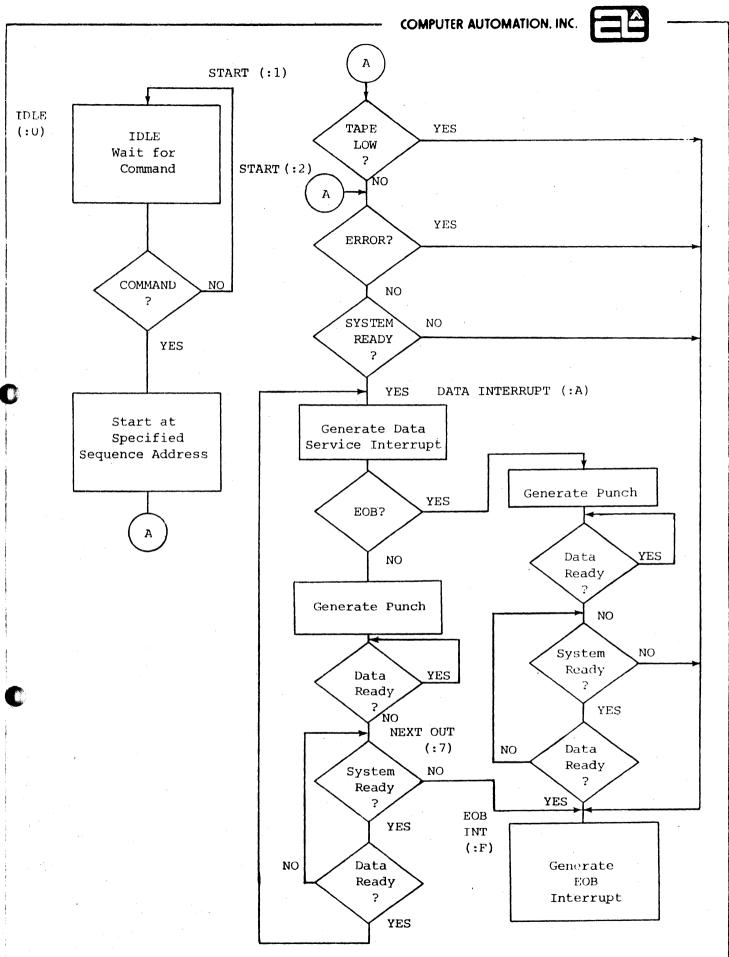

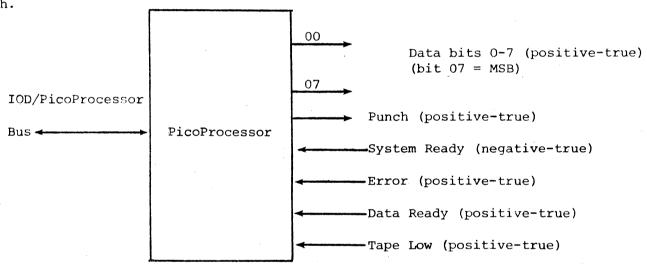

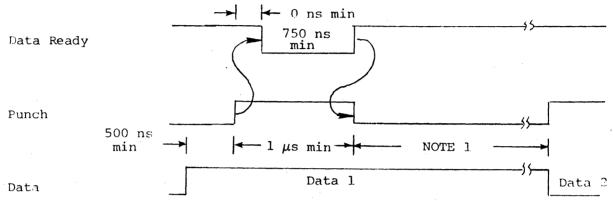

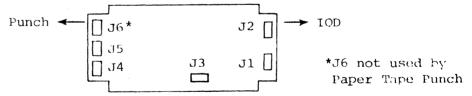

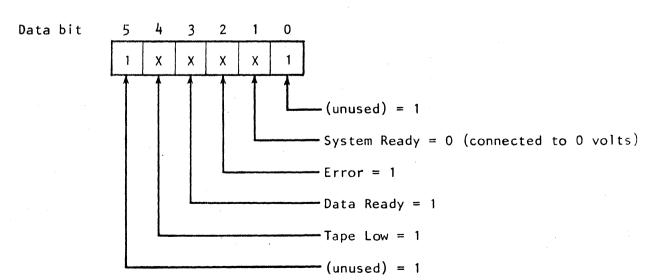

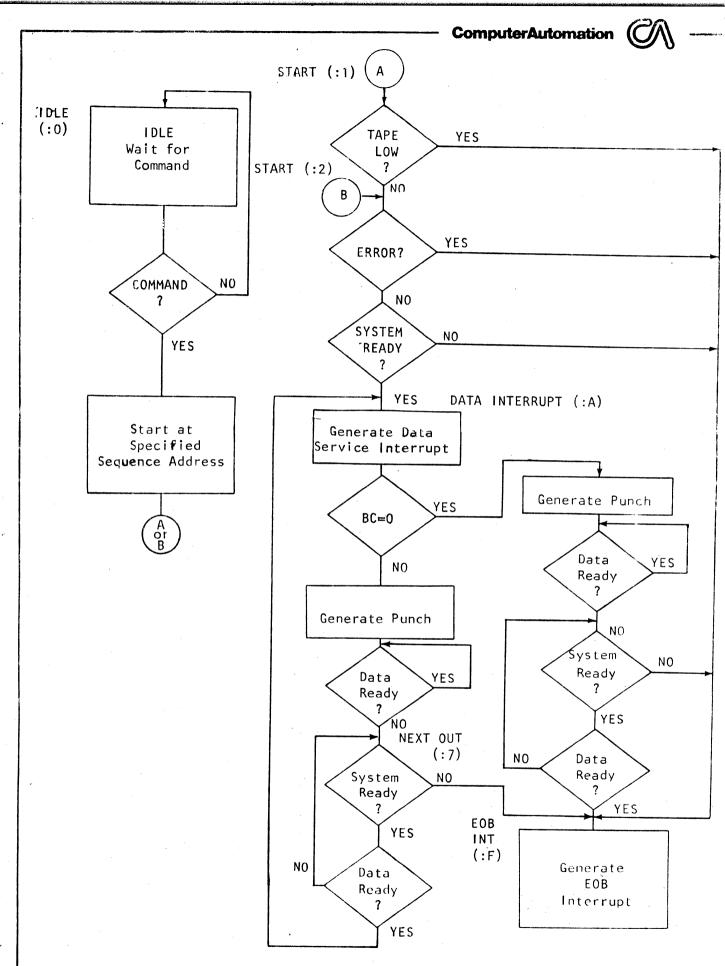

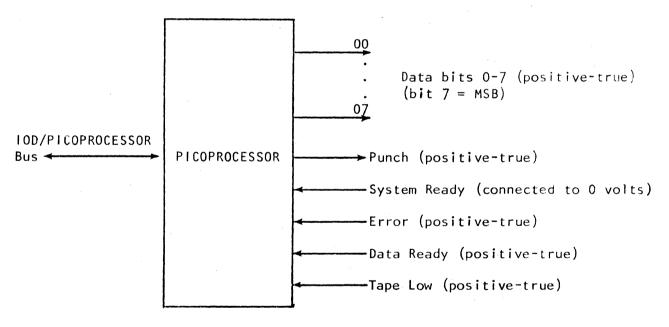

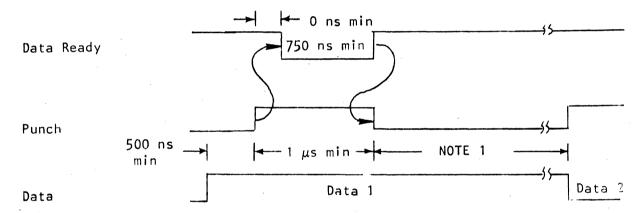

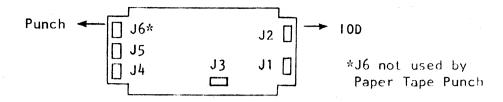

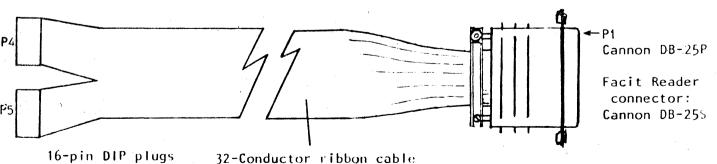

| 3.3.4.4 Operating Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |      | 3.3.3.3 Paper Tape Reader Status Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -20<br>-20<br>-20<br>-21<br>-23<br>-23<br>-26<br>-28<br>-28                                                |

| 3.3.5.4 Mode Bit Significance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |      | 3.3.4.4 Operating Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -28<br>-29<br>-31<br>-32<br>-32<br>-32<br>-38<br>-38<br>-38<br>-39<br>-40<br>-44                           |

įv

# TABLE OF CONTENTS (Cont'd)

|         |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •                                        |                                |

|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------|

| Section |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          | Page                           |

|         |         | . 2 2 6 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Channaina Bassimomenta                   | 2 46                           |

|         |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Strapping Requirements                   | 3-46                           |

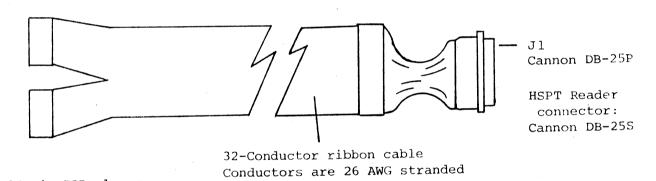

|         | •       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Device Cable Description                 | 3 <b>-</b> 46<br>3 <b>-</b> 48 |

|         | 2 2 6   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Programming Example                      | 3-48                           |

|         | 3.3.0   | 3.3.6.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Description                              | 3-50                           |

|         |         | 3.3.6.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Physical Details                         | 3-50<br>3-50                   |

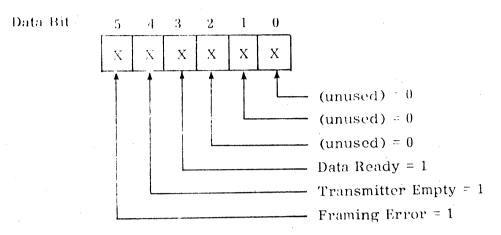

| •       |         | 3.3.6.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Device Status Word                       | 3-51                           |

|         |         | 3.3.6.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Mode Bit Significance                    | 3-52                           |

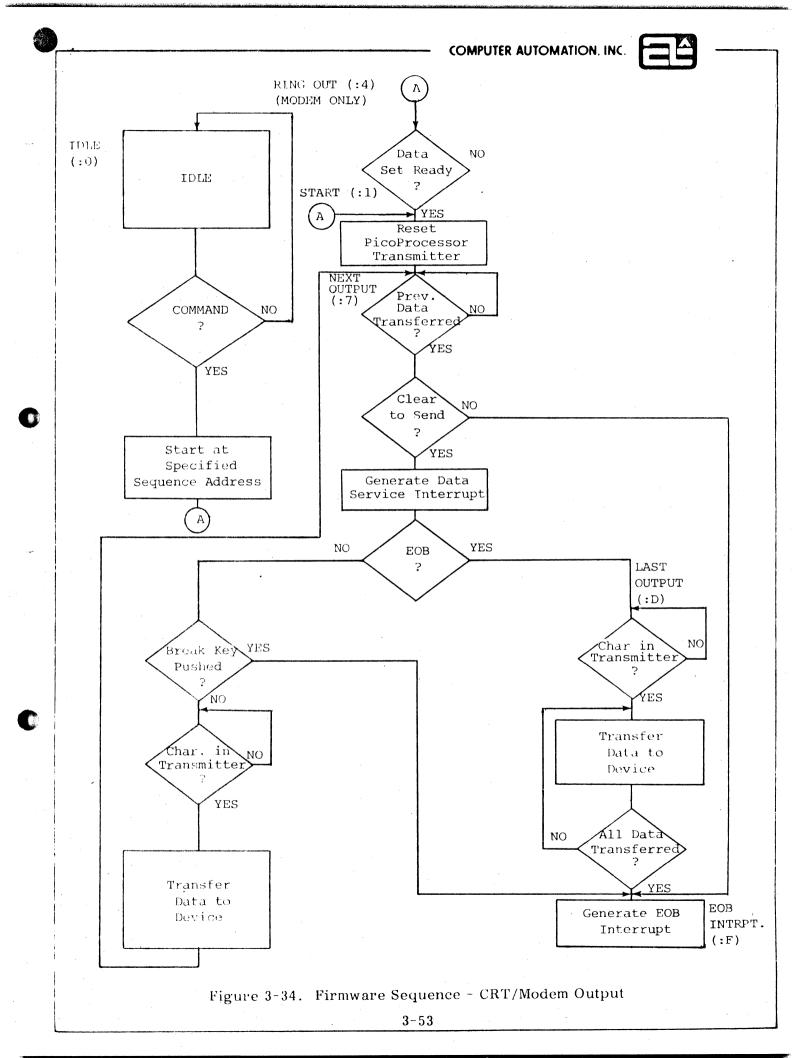

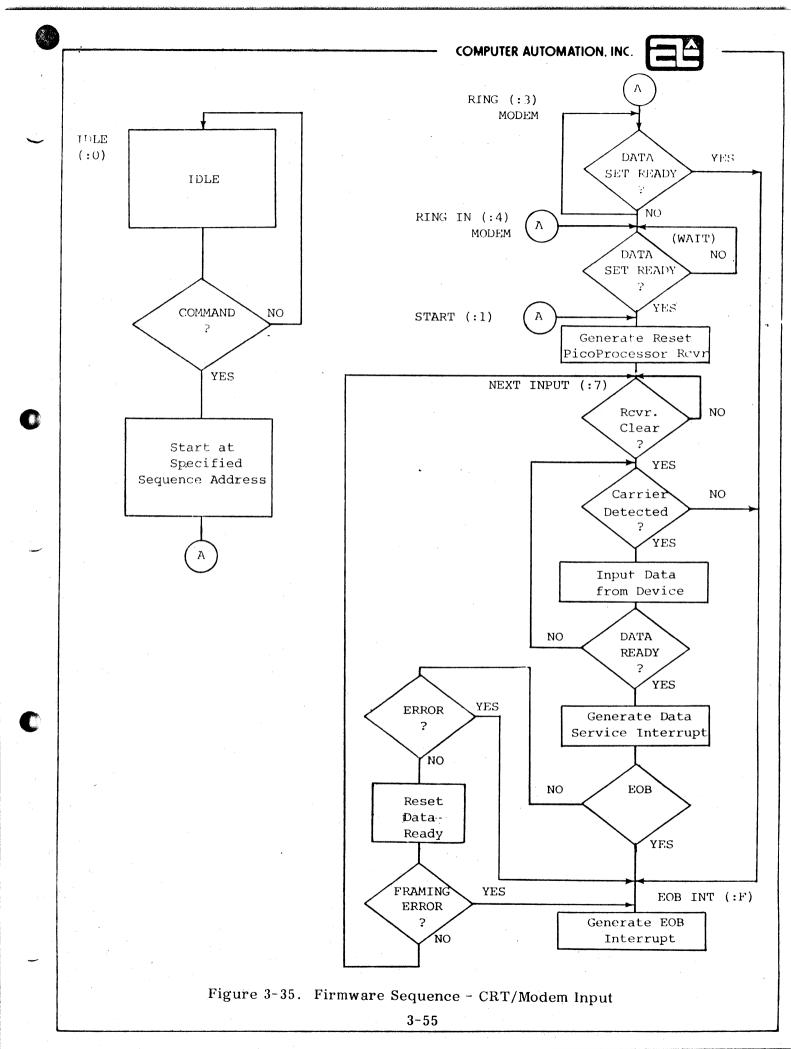

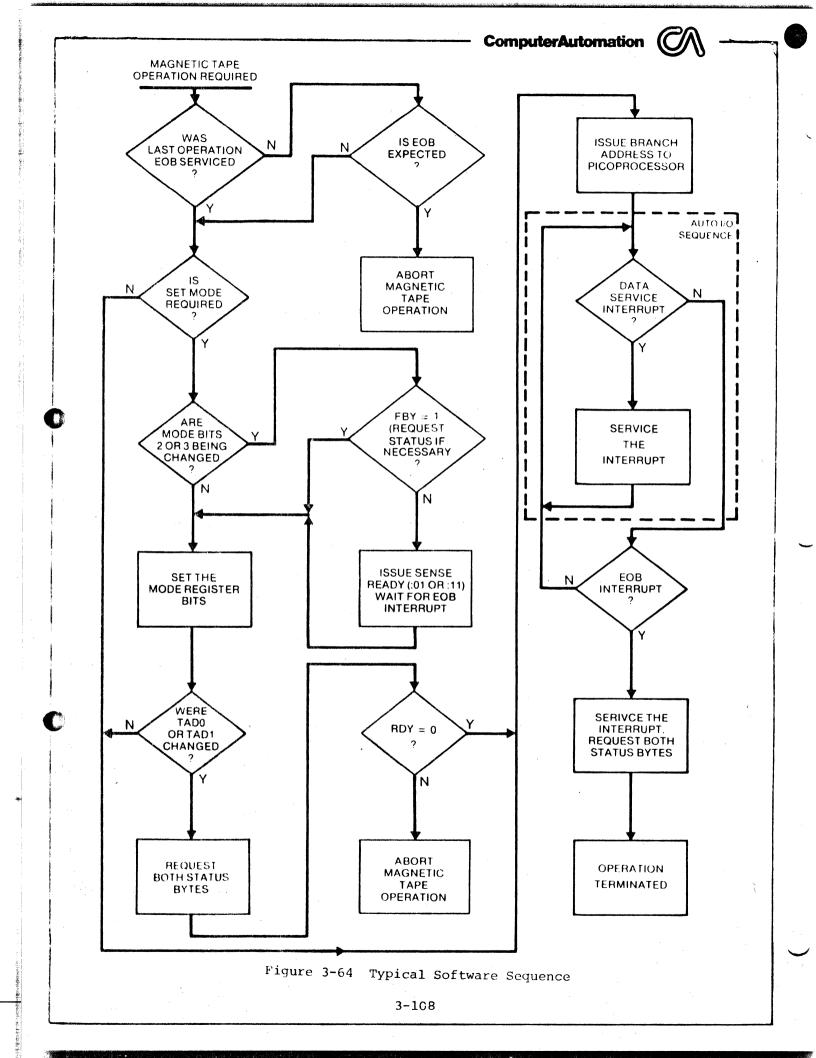

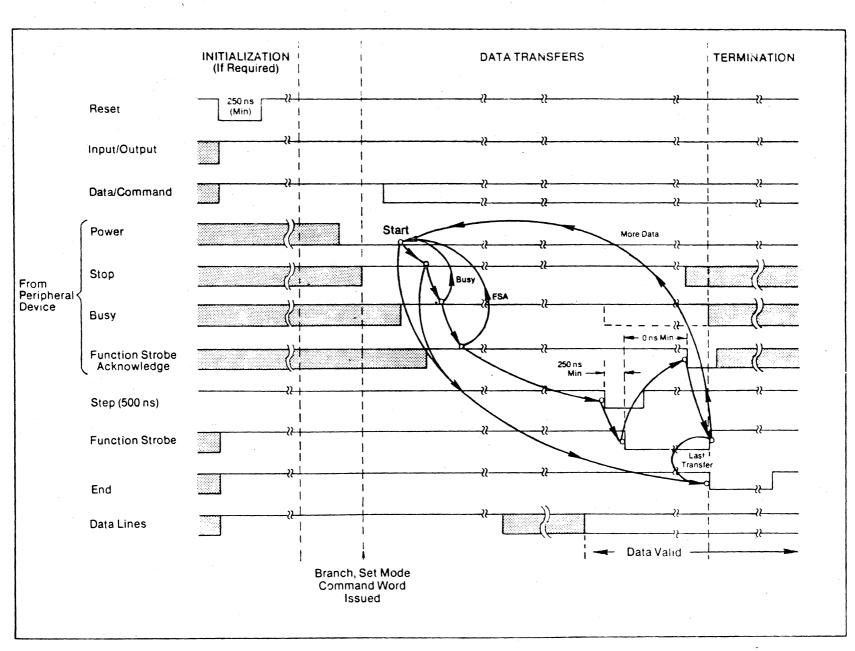

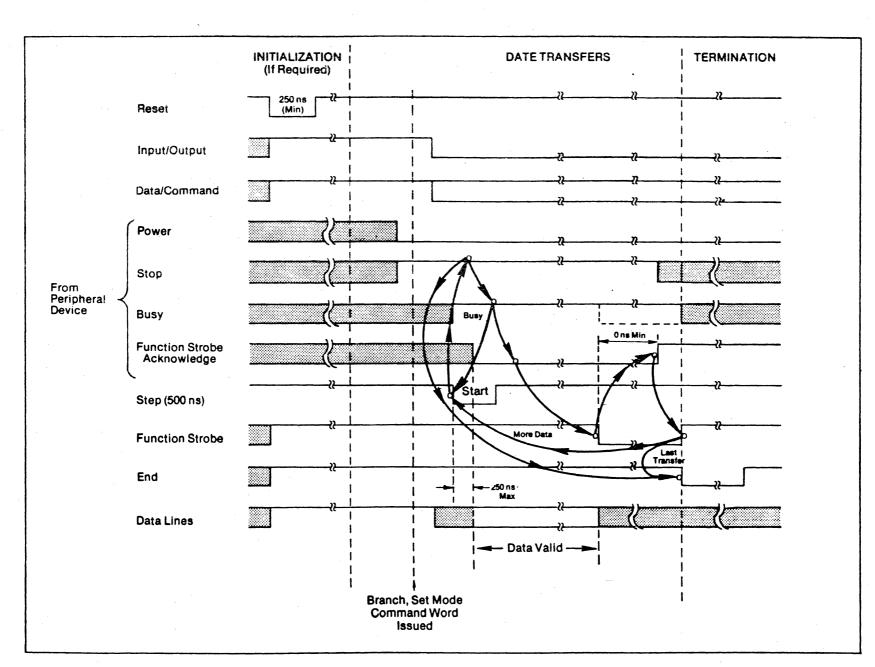

|         |         | 3.3.6.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Operating Sequence                       | 3-52                           |

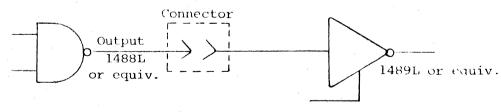

|         |         | 3.3.6.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Interface Description                    | 3-57                           |

|         |         | 3.3.6.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Strapping Requirements                   | 3-60                           |

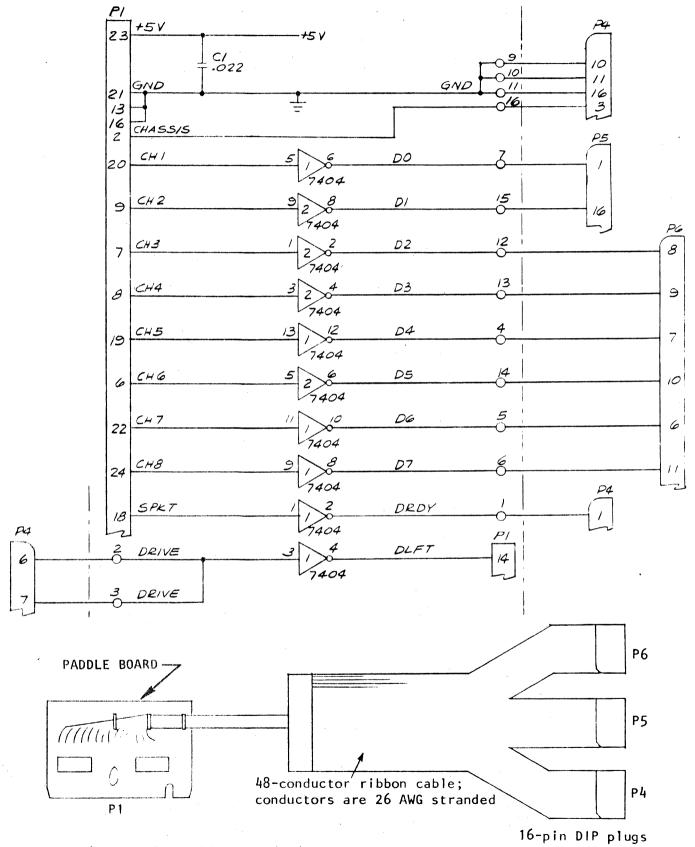

|         |         | 3.3.6.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Device Cable Description                 | 3-61                           |

|         |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Programming Example                      | 3-61                           |

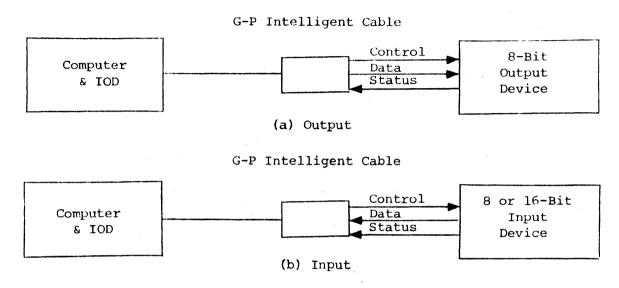

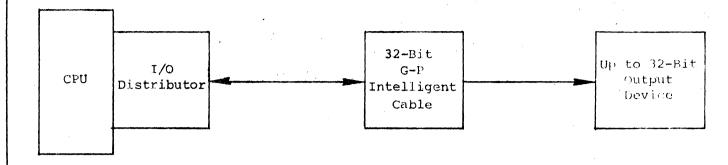

|         | 3.3.7   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Purpose Intelligent Cables               | 3-62                           |

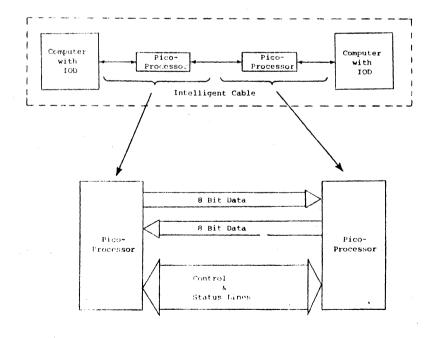

|         | 3.3.7   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | General Description                      | 3-62                           |

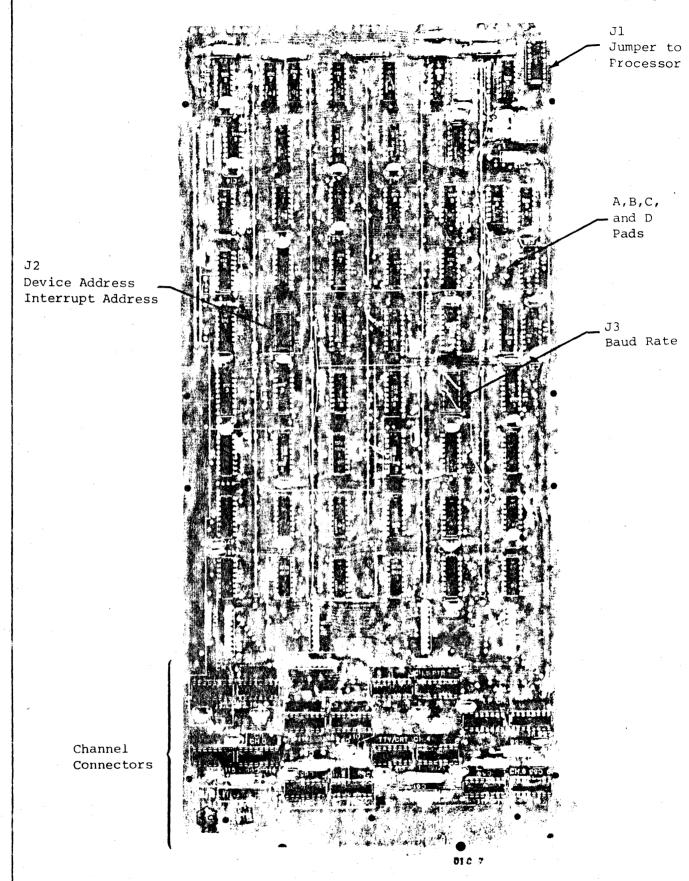

|         |         | 3.3.7.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Specifications                           | 3-62                           |

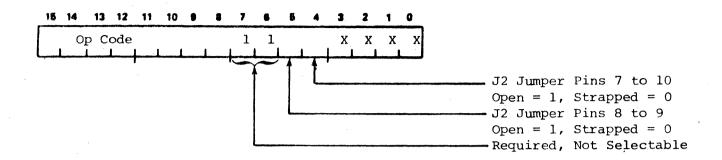

|         |         | 3.3.7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Software Considerations                  | 3-65                           |

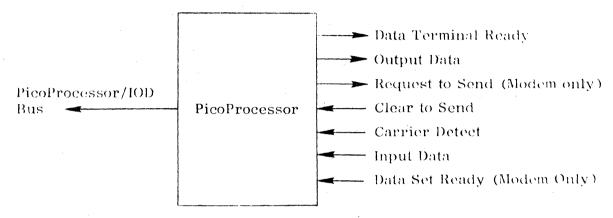

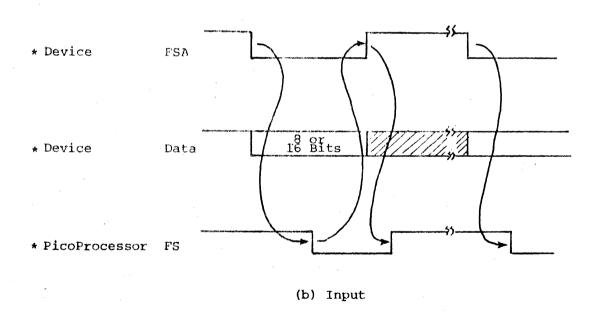

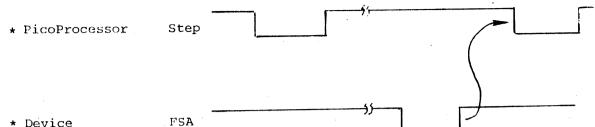

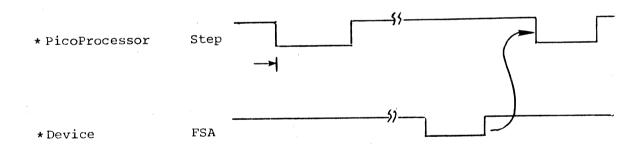

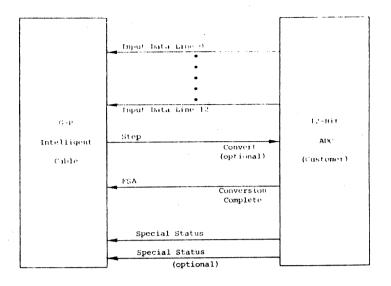

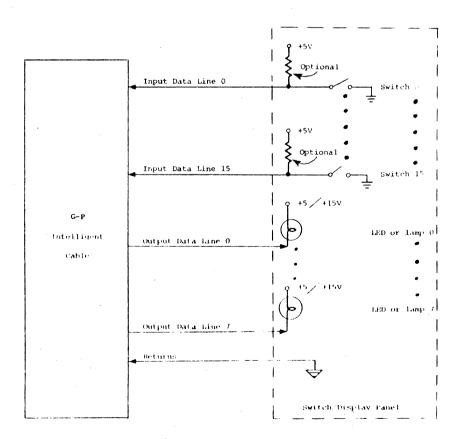

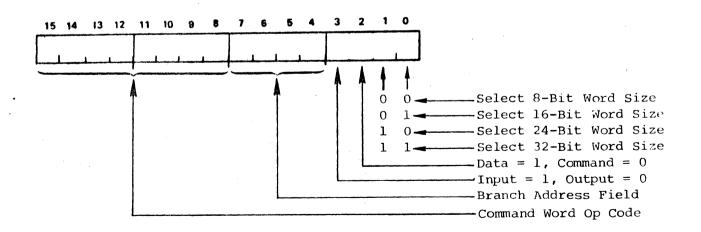

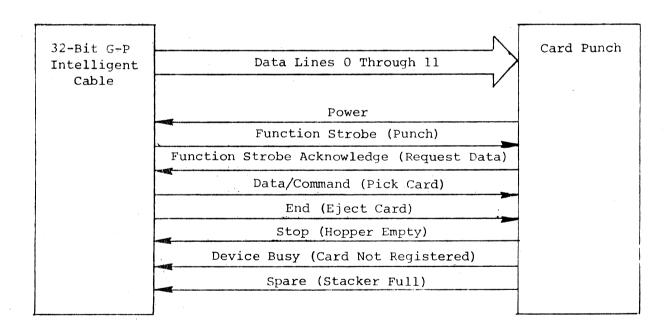

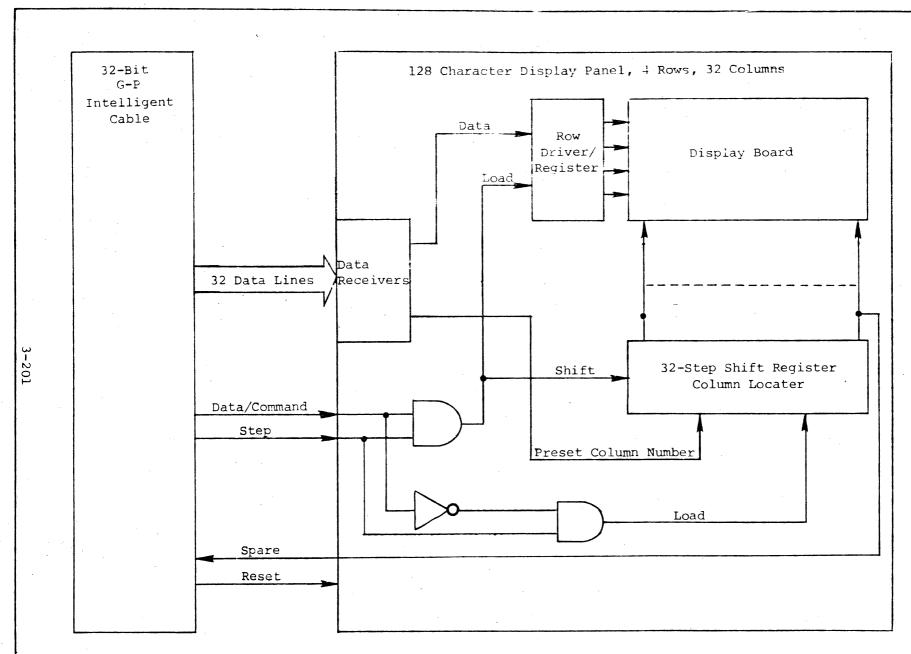

|         |         | 3.3.7.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Use of Interface Lines                   | 3-67                           |

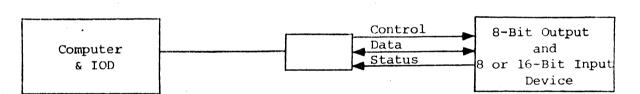

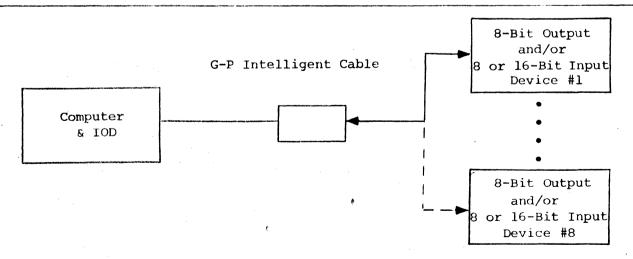

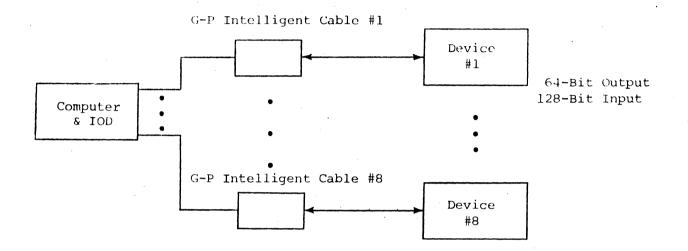

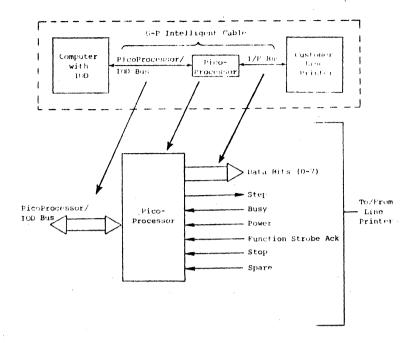

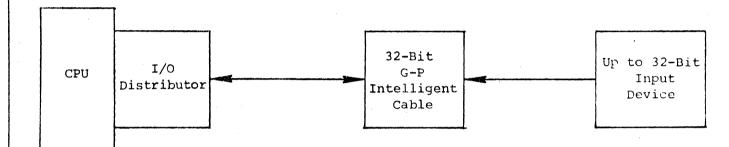

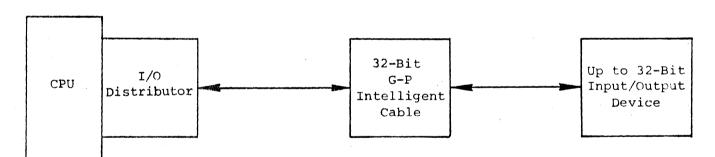

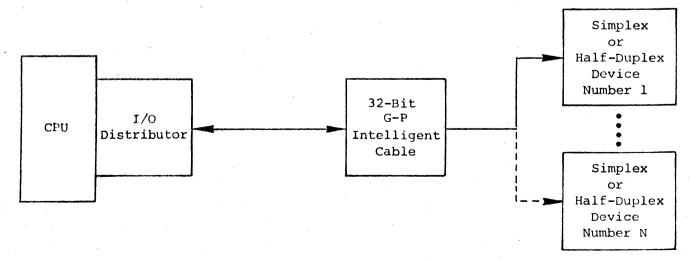

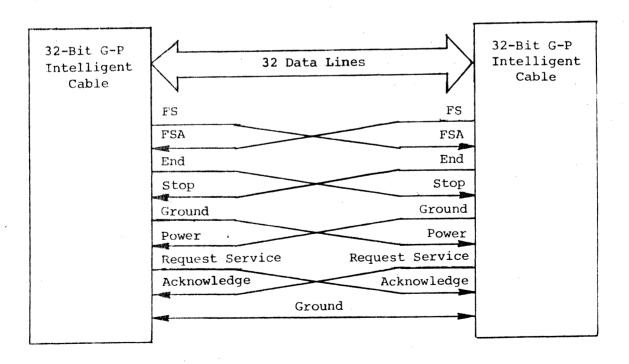

|         |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Configurations                           | 3-72                           |

|         |         | 3.3.7.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Typical Applications                     | 3-72                           |

|         |         | 3.3.7.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Device Interface Line Descriptions       | 3-73                           |

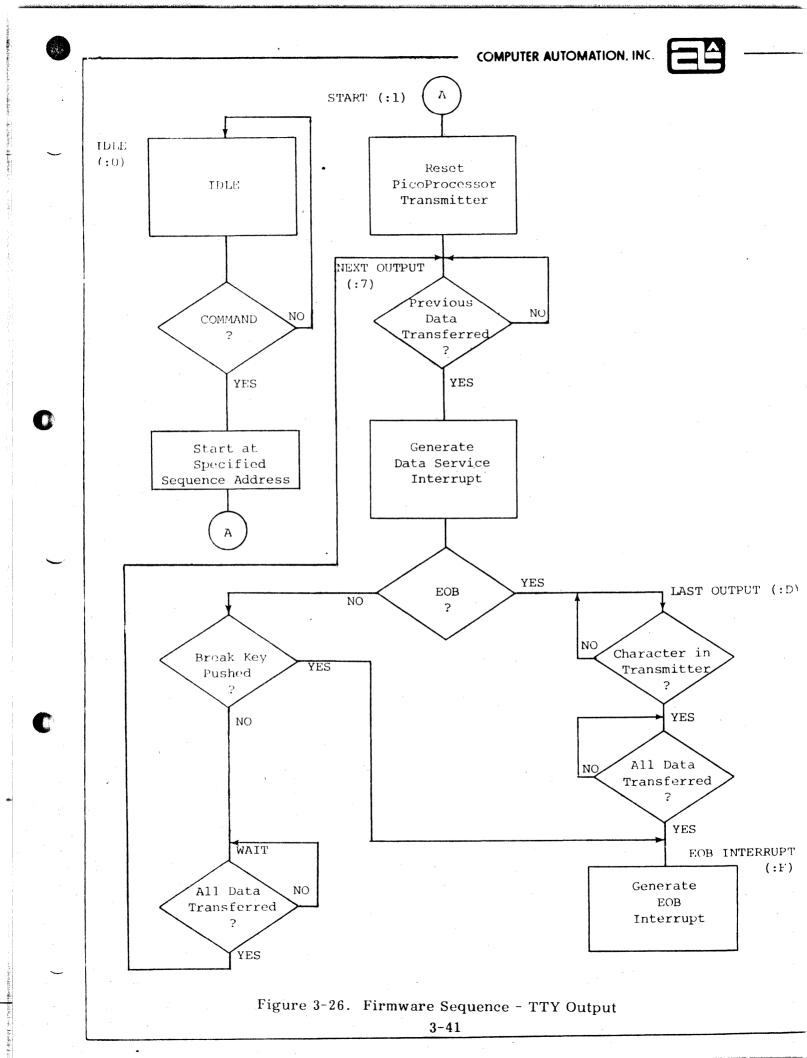

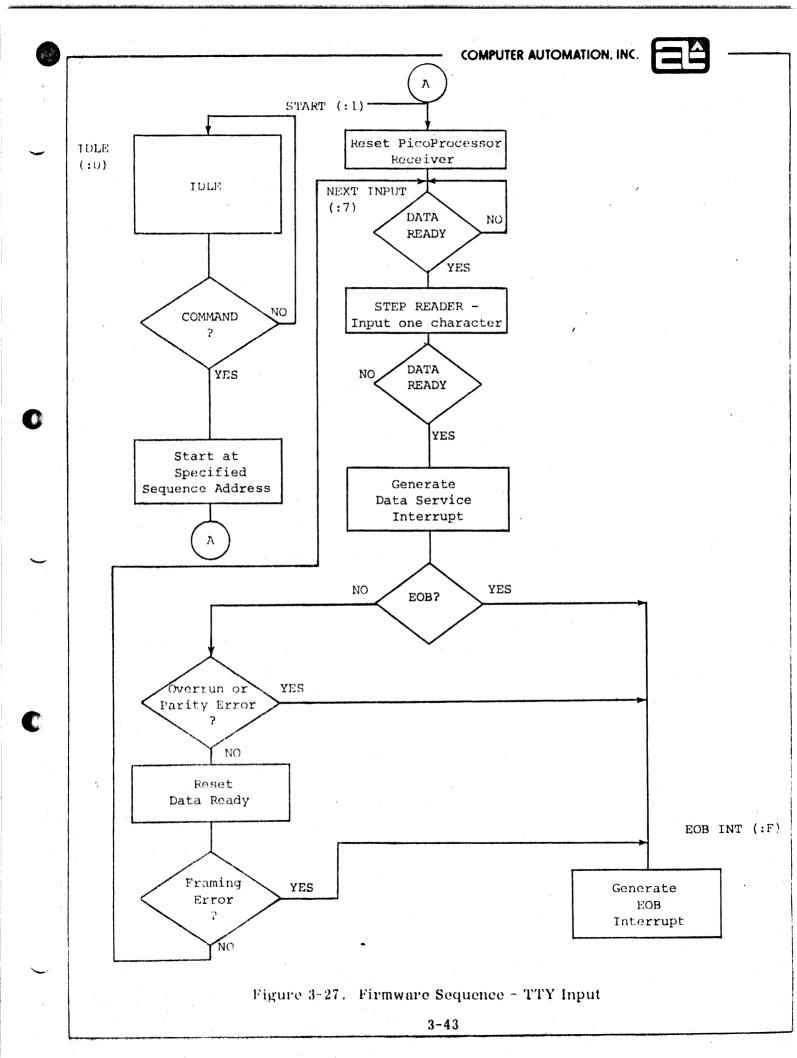

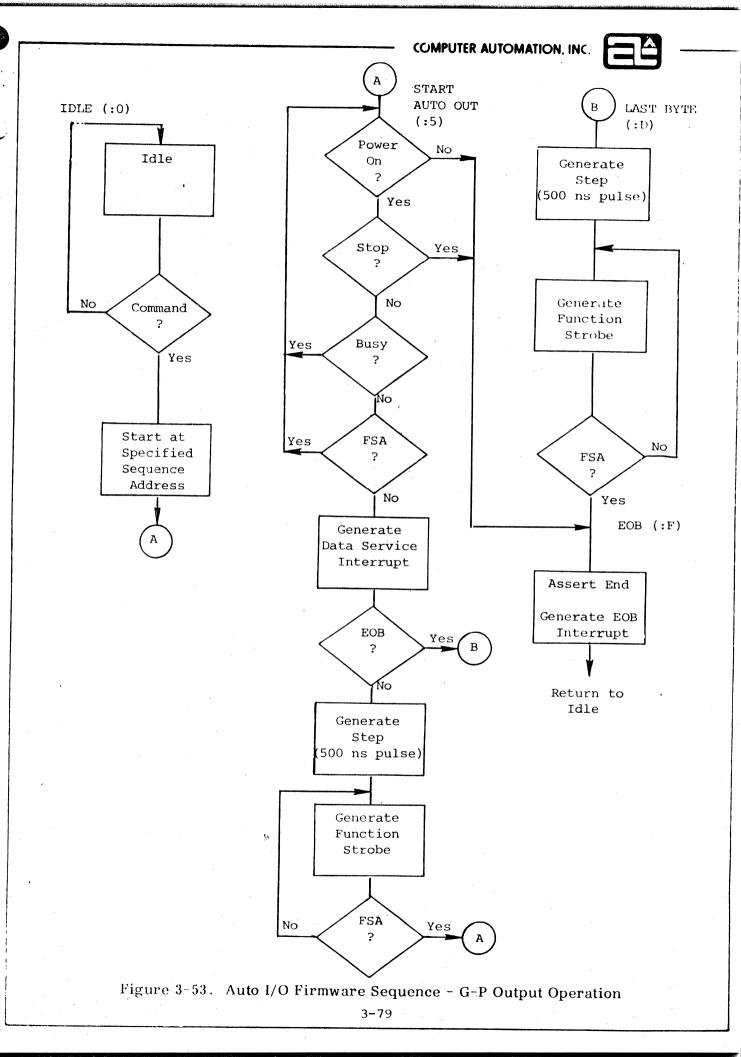

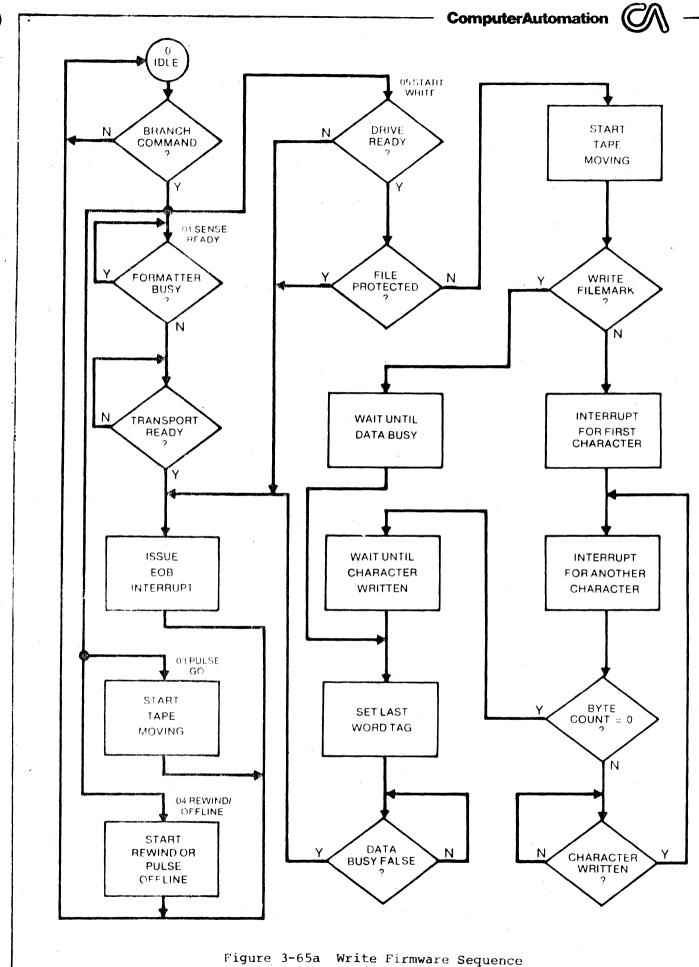

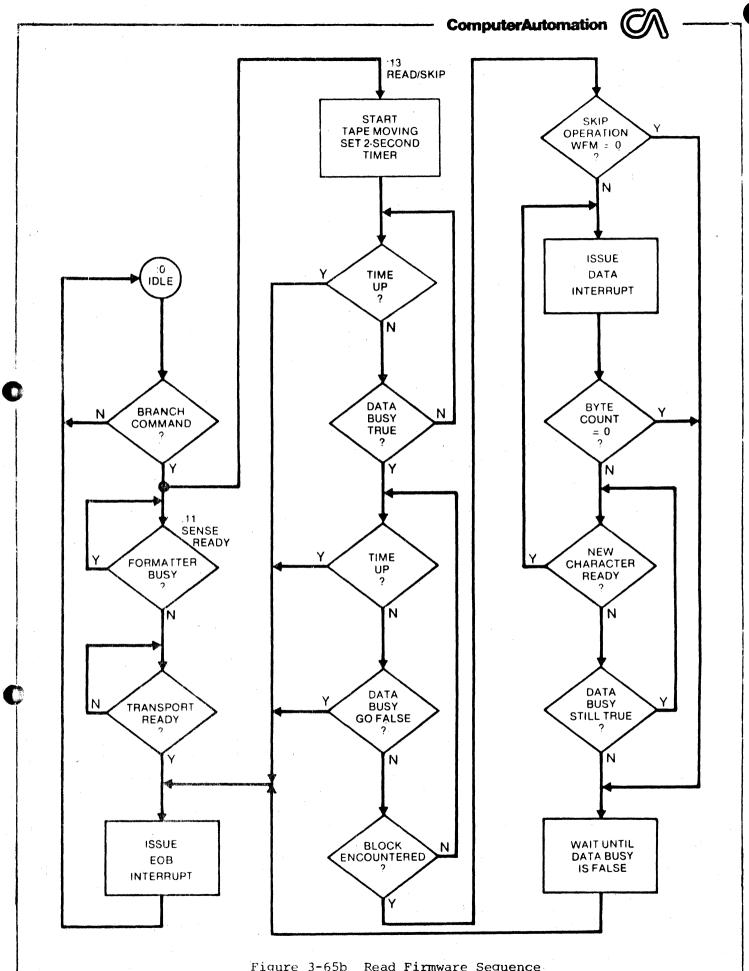

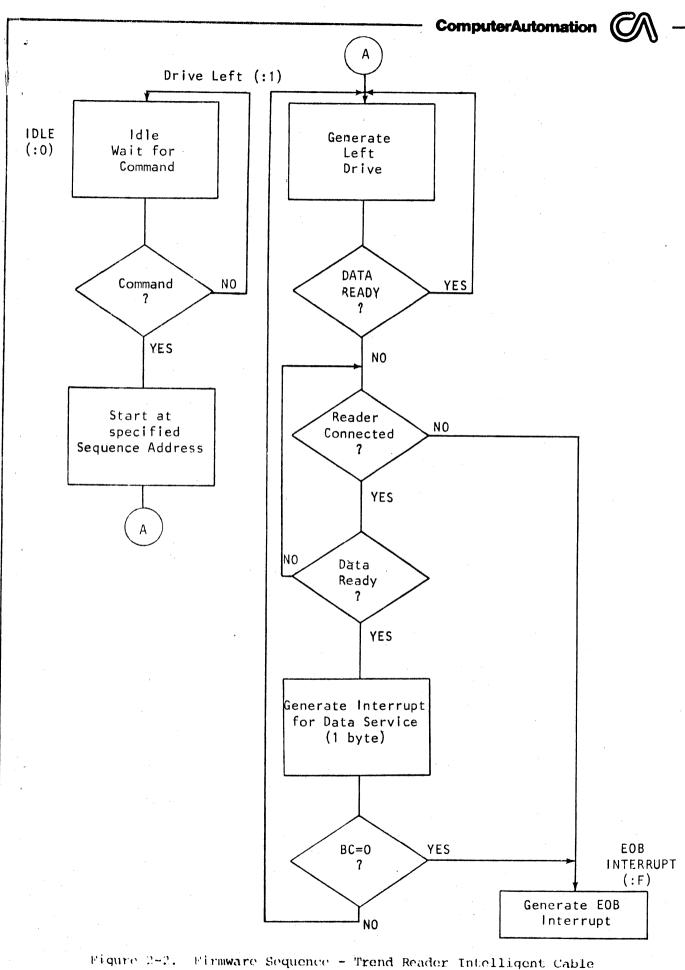

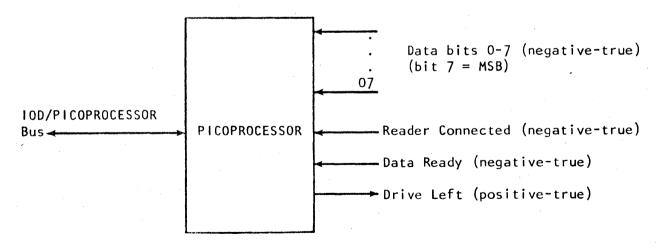

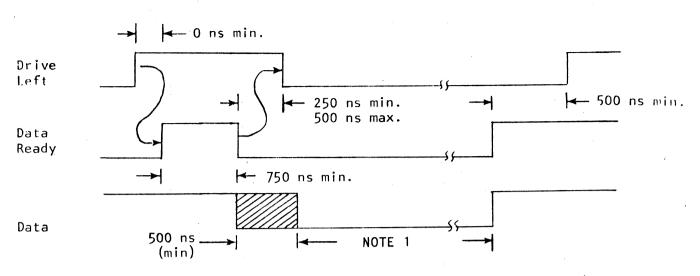

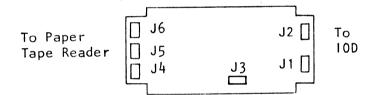

|         |         | A Committee of the Comm | Firmware Sequence                        | 3-78                           |