# MPX - 1 TECHNICAL MANUAL

IEEE 696 / S-100

# MULTIPLEXER CHANNEL 4K or 16K RAM 6 MHz 8085 Processor

#### **BULLDOG COMPUTER**

IBM PC - XT - AT COMPUPRO 1334 Chapel Street New Haven, CT 06511 (203) 777-1476 or -7763 Scanned by Howard M. Harte, March 26, 2003. <a href="www.hartetec.com">www.hartetec.com</a>

# TABLE OF CONTENTS

| WARNING                                             | 5               |

|-----------------------------------------------------|-----------------|

| About MPX-1                                         | 5               |

| Technical overview                                  | 5               |

| How to use the MPX-1                                | 6               |

| MPX-1 block diagram                                 |                 |

| Local address map                                   | 7               |

| Accessing memory on the bus                         | 7               |

| Accessing I/O ports on the bus                      | 8               |

| Getting the MPX-1 attention                         |                 |

| Getting the main system CPU's attention             | 8               |

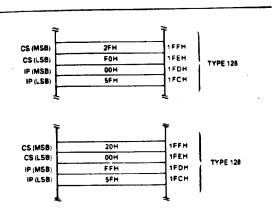

| Interrupt acknowledge response on the bus           | 9               |

| Hardware switch setting and jumper options          |                 |

| Switch settings                                     |                 |

| Switch 1 - ATTN port address select                 | 9               |

| Standard ATTN port address selection                |                 |

| Switch 2                                            | q               |

| Interrupt "CALL" jumpers                            | 10              |

| Selecting and using 4K or 16K RAM chips             | 10              |

| Using 2147 4K x 1 type RAM chips                    |                 |

| Using 2167 16K x 1 type RAM chips                   | 11              |

| Configuring the MPX-1 for different size EPROMS     | $\overline{11}$ |

| Using a 2716 or 2732 EPROM                          | $\frac{-1}{11}$ |

| Using a 2716 or 2732 EPROM                          | 11              |

| Standard software supplied with MPX-1               | 12              |

| Basic command structure and protocol                | 12              |

| Opcode byte                                         | 12              |

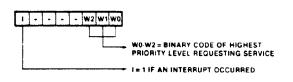

| Status indication byte                              | <br>13          |

| Status indication byte                              | 14              |

| Link address bytes                                  | 14<br>14        |

| Result 1 and result 2 bytes                         | 1 /s            |

| General notes                                       |                 |

| Command descriptions                                | 15              |

| NOP - no operation                                  | 15              |

| RESET - reset the MPX-1                             | 15              |

| SET MASK - mask or unmask interrupt inputs to MPX-1 | 1.5             |

| SENDDEOI - send end-of-interrupt command            | 1)              |

| to interrupt controller                             | 16              |

| READREG - read interrupt controller registers       | 16              |

| SETRESPONSE - set interrupt response byte           | 16              |

| SIZE - indicate whether 4K or 16K MPX-1             | 1 U             |

| LOADRAM - load MPX local RAM from system RAM        | 1/<br>17        |

| EXRAM - execute a program in local RAM              | エノ<br>1フ        |

| BLKMOV - move block of RAM of system bus            | 1 /<br>1 0      |

| FASTMOV - move block of RAM on system bus - fast    | 10<br>10        |

| RESERVED - opcode                                   |                 |

|                                                     |                 |

|            |                                 |        |      |      |     |     |    |     |      |       |      |     |   |     | _ |   |   |     | 19   |

|------------|---------------------------------|--------|------|------|-----|-----|----|-----|------|-------|------|-----|---|-----|---|---|---|-----|------|

| About the  | ROM code<br>ization             |        | •    |      | •   | •   | •  | • • | •    | •     | •    | •   | • | •   | • |   |   |     | 19   |

| 7-4-4-1    | ization                         |        |      |      | •   | •   | •  | • • | •    | • •   | •    | •   | • | •   | • |   |   | _   | 20   |

| initiai    | IZACION                         | • • •  |      |      |     |     |    |     |      |       |      | •   | • | •   | • | • | • | • • | 20   |

| ATTN re    | ization<br>sponse               | • • •  | •    | •    | _ • | •   |    |     | _    |       |      |     |   |     | • | • | ٠ |     | 20   |

| General    | purpose                         | Subi   | Out  | THE  | 9   | ٠.  | _  |     |      |       |      |     |   | _   |   |   |   |     | 20   |

| 17-1-1-1-0 | purpose<br>your ov              | n cus  | stom | co   | mma | ınd | s  | •   | •    | •     | • •  | •   | • | •   | • |   |   | 21  | -28  |

| MITTIE     | your or                         | امعمل  | enf  | twa  | re  | su  | DP | 11  | ed   | W.    | ith  | M   | X | - T | • | • | • | 2.0 | 22   |

| Listin     | your ov                         | lagra  | 501  |      |     |     |    |     |      |       |      | •   |   | •   | • | • | • | 23  | ,-32 |

| Theory of  | operation                       | ) TI • | • •  | • •  | •   | -   |    |     |      |       |      |     |   |     |   |   |   |     |      |

| Appendix   |                                 |        |      | _    |     |     |    |     |      | -n+   | rol  | 116 | r |     |   |   |   | 3:  | 3-53 |

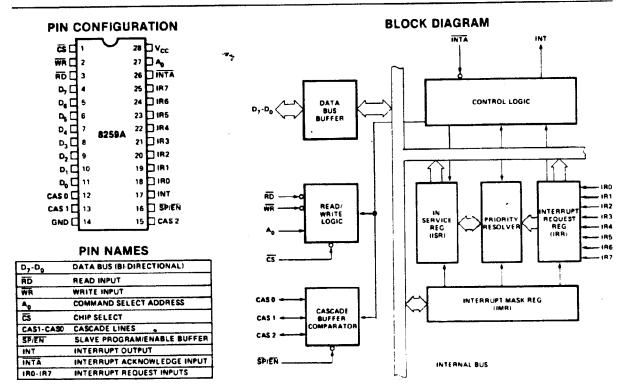

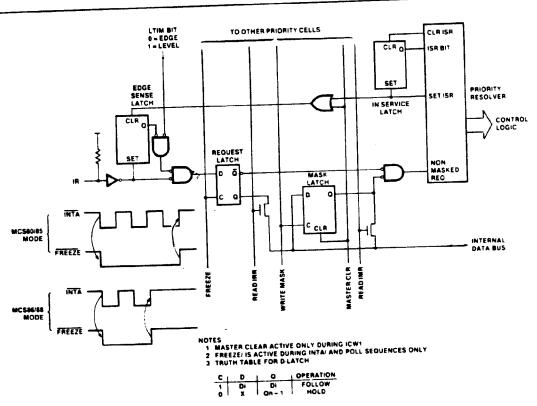

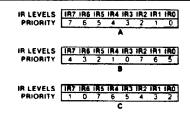

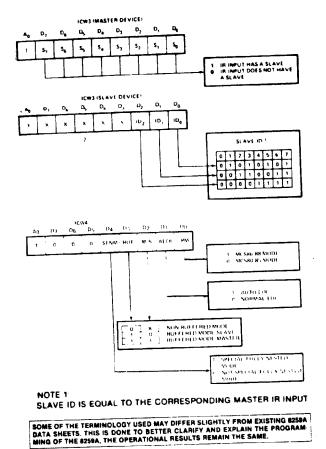

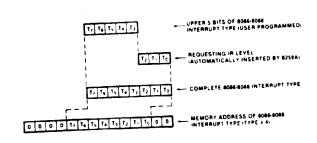

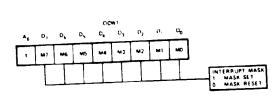

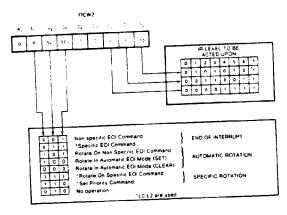

| TNTEL      | 8259A pr                        | ogram  | mab. | le : | int | er  | ru | pτ  | C    | )11 t |      |     | - |     |   |   |   |     |      |

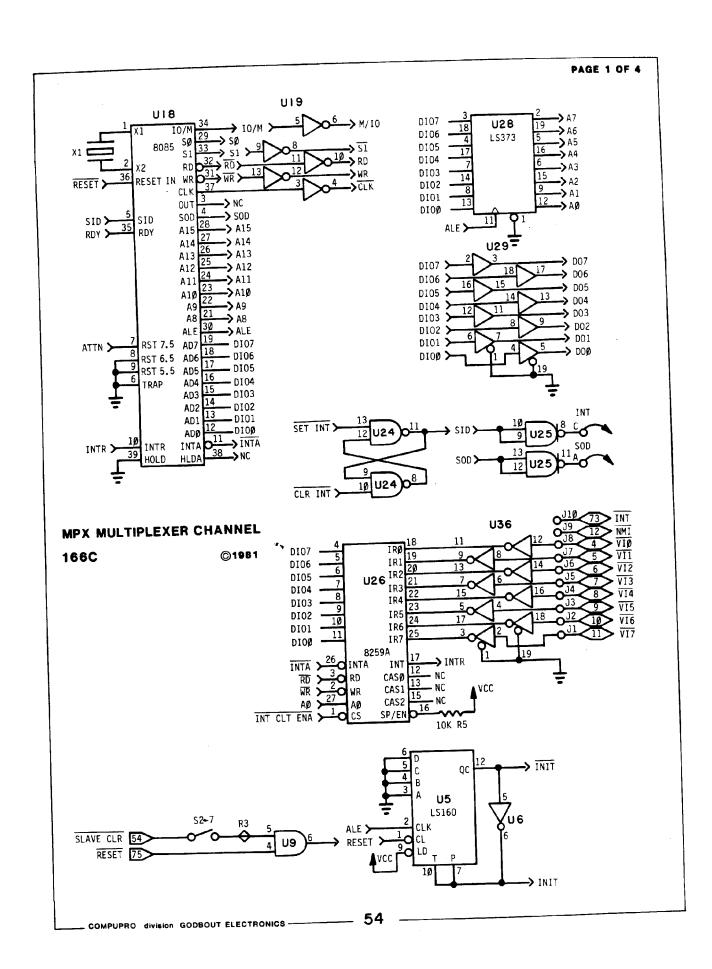

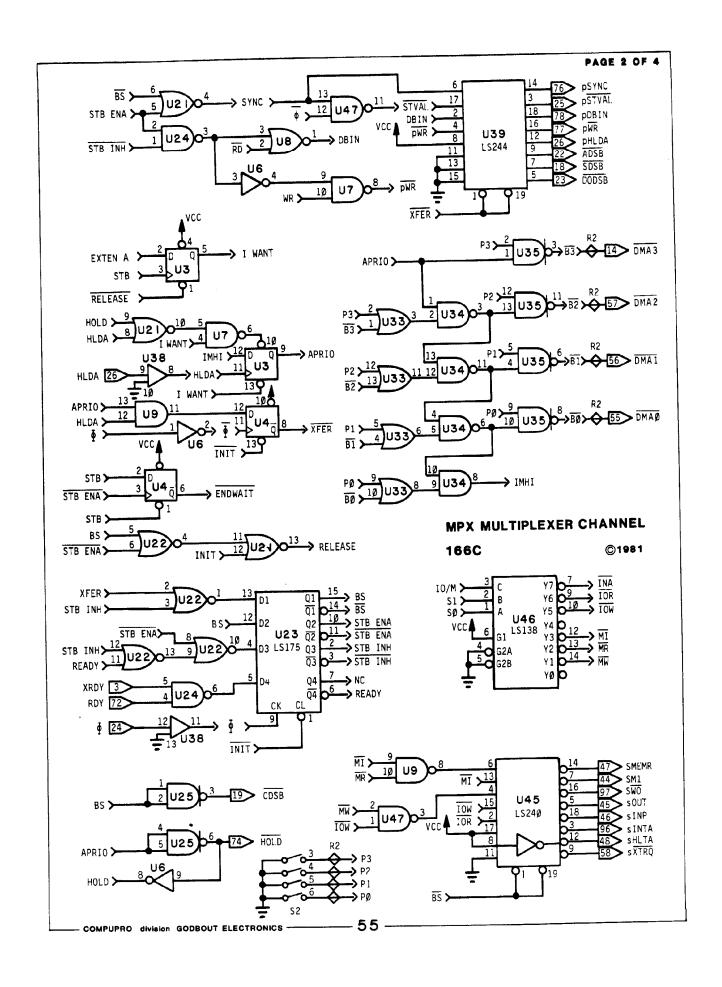

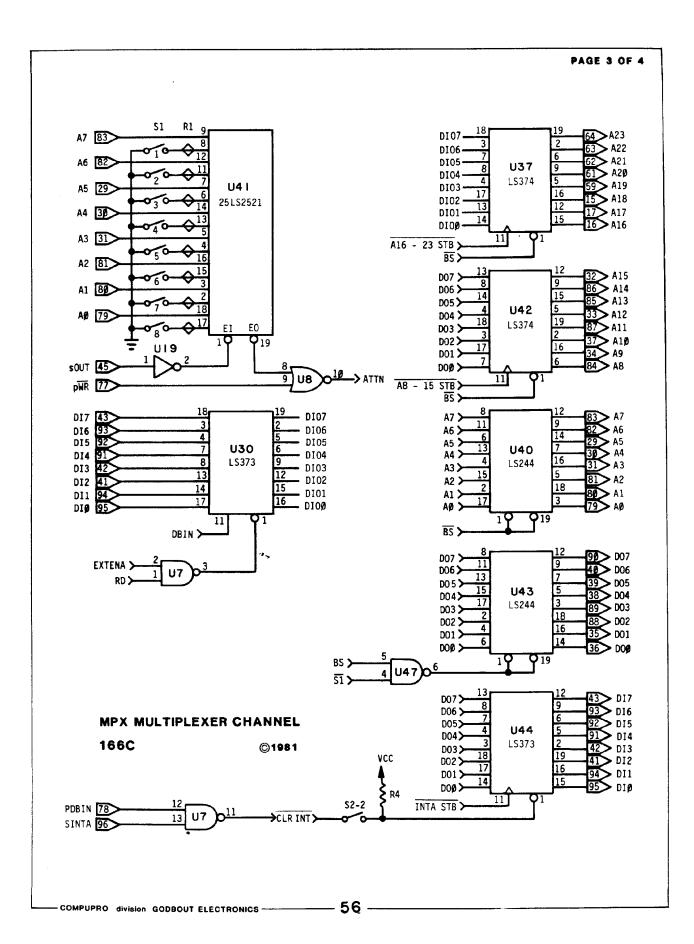

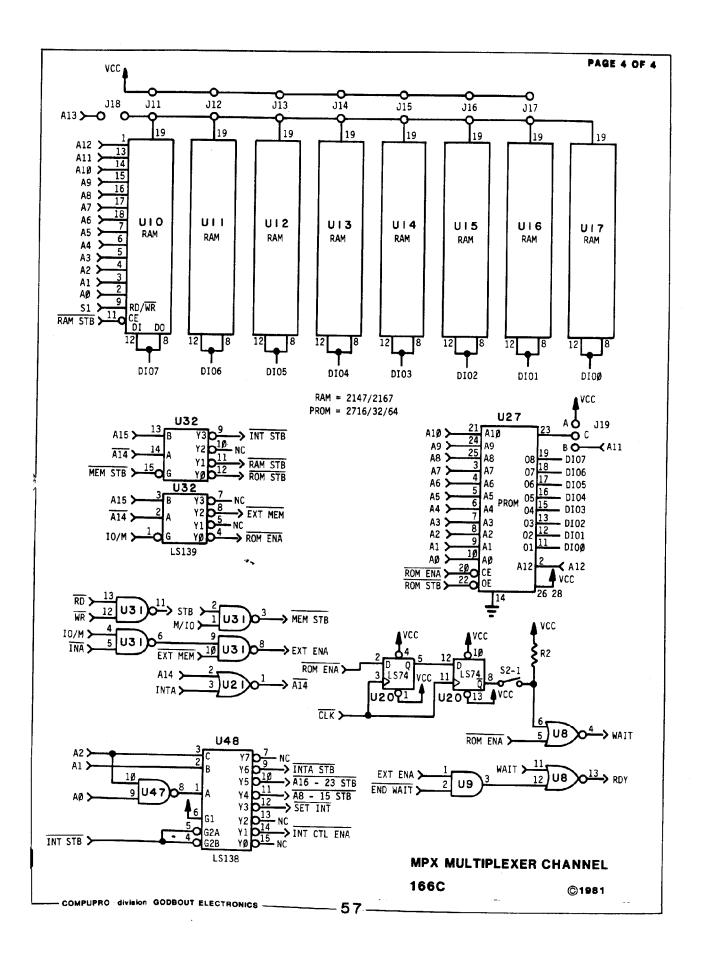

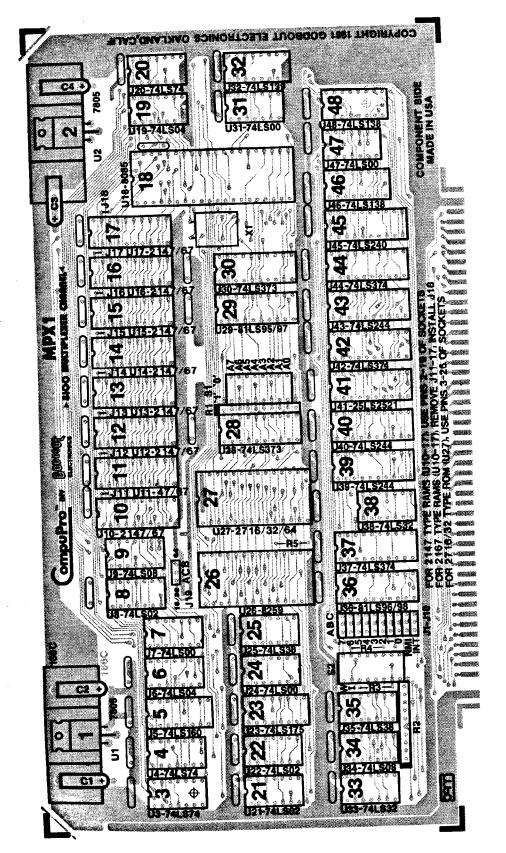

| Hardware   | diagram                         |        |      |      |     |     |    |     |      |       |      |     |   |     |   | _ |   | 54  | 4-57 |

| Hardware   | 14                              | _      |      |      |     |     | •  | •   | •    | ٠     |      | •   | • | •   | • | • | • | -   | 5.8  |

| Logic      | diagram                         | • •    | • •  | •    |     |     |    |     |      |       |      |     | • | •   | • | • | • | •   |      |

| Parts      | diagram<br>list · ·<br>ent layo |        | • •  | •    | • • | •   | •  | •   | •    |       |      |     |   |     |   |   |   | •   | . 59 |

| Customer   | ent lavo                        | ut •   |      | •    | • • | •   | •  | •   | :    | •     |      |     |   |     | _ |   |   |     | . 60 |

| СОшрот     | corvice                         | / 1im  | ite  | i w  | arr | an  | ty | 11  | ni ( | oru   | nat. | LOL | • | •   | • | ٠ |   |     |      |

| Customer   | RETATCE                         | ,      |      |      |     |     |    |     |      |       |      |     |   |     |   |   |   |     |      |

----- DISCLAIMER -----Godbout Electronics makes no representations or warranties with respect to the contents hereof and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, Godbout Electronics reserves the right to revise this publication and to makes any changes from time to time in the content hereof without obligation of Godbout Electronics to notify any person of such revision or changes.

> This document was proofread with the aid of SpellGuard M from ISA, Menlo Park, CA.

#### FIRST - A WORD OR TWO OF WARNING!

This manual is intended to guide the sophisticated systems integrator or OEM through the hardware features of the MPX-1. This manual is not intended for novice or inexperienced users. If you are an end-user who has purchased an MPX-1 all by itself, you should have a thorough knowledge of hardware and software as CompuPro or your local dealer is not prepared to provide applications assistance for this product, (beyond the contents of this manual). If you are an end-user who has purchased a system with an MPX-1 integrated into it, your systems integrator should have done all the work for you. This means that they should have provided the operating system software with the MPX-1 integrated into it already. If this is the case, feel free to read this manual for your information, but you should never have to worry about this manual's contents.

If you don't feel that you are sophisticated enough to handle programming the MPX-1 (be honest with yourself now!), please return it to the place of purchase for a full refund.

#### ABOUT THE MPX-1

The MPX-1 from CompuPro is a very useful addition to any multi-user or interrupt intensive environment. Its extreme versatility and flexibility makes it a very bewildering product on the surface - it can do so much, where do you start? The basic function of the MPX-1 is that of an interrupt pre-processor. It takes the interrupt servicing and handling load off of the main processor in a system. Interrupts in the system are now processed in parallel with other processing resulting in higher system throughput, which is a paramount consideration in multi-user, multi-tasking situations.

The MPX-1 was designed for the IEEE 696/S-100 Bus because of that bus modularity and its unique ability to handle multiple temporary bus masters (of which the MPX-1 is one). The IEEE 696/S-100 bus is the choice of professionals for business, industrial and scientific applications.

#### TECHNICAL OVERVIEW

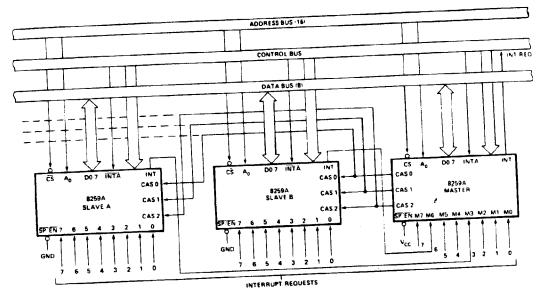

The MPX-1 has its own on-board processor, an Intel 8085AH-1 running at 6 MHz. This processor is supported by either 4K or 16K of fast static RAM and up to 8K of EPROM. In addition, a flexible 8259A interrupt controller monitors the eight vectored interrupt lines on the S-100 Bus. None of these local resources take up any address space on the S-100 Bus.

When an interrupt request occurs on one of the vectored interrupt lines, the interrupt response is handled by the on-board interrupt controller and CPU, taking up no processing time on the bus.

When needed, the MPX-1 can access any system resource on the bus. This means that it can talk to any I/O port or memory location on the bus. It does this by requesting the bus from the permanent master on a cycle-by-cycle basis. This request/grant procedure is fully arbitrated to 16 levels as provided for by the IEEE 696/S-100 bus standard. This allows up to 16 such devices to exist in a system at any given time. Multiple MPX-1s could even be used.

The uses of the MPX-1 are vast. Obvious uses would include terminal interrupt handlers, print spoolers, task allocation and management, and resource control. A unique feature of the MPX-1 allows it to load execution code from the system memory so that the MPX-1's function can be altered dynamically.

# HOW TO USE THE MPX-1

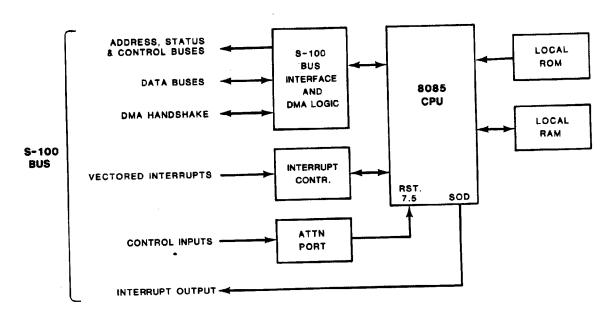

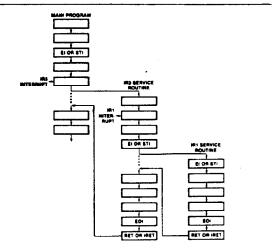

A simplified block diagram of the MPX-1 appears in Figure 1. In the following discussions, it may be useful to refer to the block diagram.

Here is a quick-and-dirty overview of how the MPX-1 works: When the onboard 8085 powers up, it begins executing code from its on-board EPROM. Usually it will be sitting in a loop waiting for something to happen, an external interrupt for example. Suppose an interrupt occurs. The 8085 will be interrupted and vectored to a service routine by the 8259A interrupt controller. The MPX-1 can access any I/O port on the S-100 Bus by simply doing an INPUT or OUTPUT instruction. Since the "ports" on the MPX-1 are all memory mapped, no conflicts occur and all 256 ports can be accessed. The on-board logic takes care of the DMA request, arbitration and the actual running of the bus cycle. The 8085 will "stall" until the operation is completed allowing program execution to continue.

The MPX-1 can also access any memory location on the S-100 Bus. To do this, the program first writes the upper 16 address bits (A8-23) to two registers. Then if a memory reference to address C000 to F000 is made, the lower 8 bits from the reference are used to make up the lower 8 bits of the desired memory location on the bus. If the memory reference is a read operation, then the bus access will also be a read operation. If the memory reference is a write operation, then the bus access will be a write operation. This address space from C000 to F000 is known as the "external window". As in the case of I/O accesses, the on-board logic takes care of the DMA request, arbitration and the actual running of the bus cycle. The 8085 will "stall" until the operation is completed allowing program operation to continue.

Sounds simple, doesn't it? Well, it is. The following sections discuss the above overview in greater detail. First is a local address map showing where everything lives on the MPX-1.

Figure 1. MPX-1 BLOCK DIAGRAM \*>

#### LOCAL ADDRESS MAP

|   | FROM         | TO   | SIZE   | FUNCTION                                        | NOTES         |

|---|--------------|------|--------|-------------------------------------------------|---------------|

| _ | 0000         | 3FFF | 4-16K  | RAM                                             | 1,4           |

|   | 4000         | 5FFF | 2-8K   | EPROM                                           | 1,2,5         |

|   | 8000<br>8002 | 8001 | 2<br>1 | 8259A Registers<br>Set Interrupts Latch         | 2             |

|   | 8004<br>8005 |      | 1<br>1 | DMA Address Bits 8-15<br>DMA Address Bits 16-23 | <b>3</b><br>3 |

|   | 8007         |      | 1      | Interrupt Response Byte                         | 3             |

|   | <b>c</b> 000 | FFFF | 16K    | External Window                                 | 6             |

|   | A11 I/O P    | orts | 256    | External Window                                 | 6             |

Notes:

- 1. RAM and EPROM exchange locations for power-on-jump.

- 2. Read Only.

- 3. Write Only.

- 4. 4K or 16K depending on chips used.

- 5. 2K for 2716, 4K for 2732, 8K for 2764.

- 6. Lower 8 address bits (A0-7) pass through.

#### ACCESSING MEMORY ON THE BUS

An access to memory that resides on the S-100 Bus will be performed if the CPU makes an access to the range noted as the external window in the address map above (addresses C000 to FFFF). The low order 8 bits of the address (A0-7) will be taken from the CPU's address lines directly, while the high order 16 bits (A8-23) will come from the address that has been previously written to the DMA address registers. So the procedure for accessing memory on the bus would be:

- 1. Write desired A8-15 bits to memory location 8004.

- 2. Write desired A16-23 bits to memory location 8005.

- 3. Perform a memory reference to COXX to FOXX, where XX represents the low order 8 bits (AO-7) of the desired address.

If the memory reference to the external window is a read operation, then a memory read will occur on the bus. If the memory reference is write operation, data will be written to the memory on the bus. Note that Ml cycles may also be executed on the bus meaning that the MPX-l may actually execute a small amount of code (less than 256 bytes) directly from the bus.

Note that the high order byte of the external window is insignificant. Any address in the range COOO to FFFF will be treated identically. For example, CO83, BD83, A983, and FF83 would all access the same external memory location - XXXX83, where XXXX are the two bytes from the DMA address registers.

# ACCESSING 1/0 PORTS ON THE BUS

All of the "I/O Ports" local to the MPX-1 are "memory mapped". This means they are decoded in the memory address space rather than in the I/O space. This leaves all 256 I/O addresses free. Any input or output cycle performed by the CPU will cause a corresponding cycle to be executed on the S-100 Bus. Since the lower 8 bits of the DMA Address pass through from the actual lower 8 address bits from the CPU, the port address specified in the I/O instruction will be the one accessed on the bus.

The high order 8 bits of the I/O access will come from the DMA address register as in a memory reference. This allows the port address to be "mirrored" in A8-15 as early S-100 (8080) processors did, or this byte may be loaded with different data to emulate Z-80 I/O modes (the Z-80 passes the accumulator contents on A8-15). This also allows the MPX-1 to emulate the current generation of 16 bit processors such as the CPU 8085/88, CPU 86/87 and the CPU 68K, which can put out 16 bit I/O addresses.

If an input instruction is executed, then an input cycle will be performed on the S-100 Bus. If an output instruction is executed, then an output cycle will be performed on the bus.

#### GETTING THE MPX-1's ATTENTION

In any system it will be necessary for the main CPU in the system to get the attention of the MPX-1. This can be for initial start-up of the MPX-1, or to "interrupt" its current task to be given another. This is done through a mechanism called the ATTN port. This port is on the S-100 Bus and its address is selected by switch S1. When the system CPU executes an output to the ATTN port, a RST 7.5 will be generated to the on-board 8085. Note that no data is accepted by the MPX-1.

# GETTING THE MAIN SYSTEM CPU'S ATTENTION

The MPX-1 may need to get the attention of the system CPU to tell it that a task is complete, a buffer is nearing full, or many other reasons. The MPX-1 may signal the main CPU by causing an interrupt on the bus. This interrupt may occur on the INT\*, NMI\* or any of the vectored interrupt lines. A hardware jumper is used to select which of the ten possible lines are used.

Two methods of causing this interrupt are available, again selected by a jumper. The first type uses the Serial Output Data (SOD) line from the 8085 to cause the interrupt. The state of this line is set and reset by the Set Interrupt Mask (SIM) instruction. The state of the interrupt request must be reset in software.

The second method uses a one bit latch that is set by performing a read from address 8002 (Set Interrupt Latch in the address map above). This latch is automatically reset by the occurrence of an interrupt acknowledge cycle.

Note that if one of the vectored interrupt lines is selected to cause the system interrupt, the corresponding interrupt input to the 8259A should be masked, unless you want the MPX-1 to interrupt itself.

# INTERRUPT ACKNOWLEDGE RESPONSE ON THE BUS

The MPX-1 may provide a single byte of data during bus interrupt acknowledge cycles. This response must be enabled by a switch. The data to be passed during interrupt acknowledge cycles is written to the latch at address 8007 (Interrupt Response Byte in the address map above).

Note that this single byte response may cause an 8080/Z-80 RESTART instruction, or is compatible with the vector information required by 8038/86 or 68000 CPUs. Note that if the response is desired and the CPU is an 8088/86 or 68000, the SOD interrupt call method (described above) should be used. This is because the 8086 and 68000 run two interrupt acknowledge cycles (the first byte of data is ignored) and the interrupt latch used in the second method would be reset prematurely. This may cause a system problem.

# HARDWARE SWITCH SETTINGS AND JUMPER OPTIONS

#### SWITCH SETTINGS

There are two dip-switches on the MPX-1. Switch Sl selects the address of the ATTN port on the S-100 bus. Switch S2 is used to select the various board options and the DMA arbitration address of the MPX-1.

## S1 - ATTN PORT ADDRESS SELECT

| PADI | PADDLE # |    |    |   |   | Ė | <b>ADI</b> | ORI | ESS       | BIT |             |

|------|----------|----|----|---|---|---|------------|-----|-----------|-----|-------------|

| 1    |          |    |    |   |   |   |            |     | A7        |     |             |

| 2    |          |    |    |   |   |   |            | •   | <b>A6</b> |     |             |

| 3    |          |    |    |   |   |   | •          |     | A5        |     | "ON" = "O"  |

| 4    |          |    |    |   |   |   |            |     | Α4        |     |             |

| 5    |          |    |    |   | ٠ |   | ٠          | •   | A3        |     |             |

| 6    |          | .1 | 7. |   | • | • |            | •   | A2        |     | "OFF" = "1" |

| 7    |          |    | •  | • | • | • | •          | •   | A1        |     |             |

| 8    |          |    |    |   |   |   |            |     | A0        |     |             |

# STANDARD ATTN PORT ADDRESS SELECTION

The CompuPro "standard" port address for MPX ATTN calls is Fl hex. To set the MPX-1 to respond to ATTN calls on port Fl hex, set Sl as follows: Paddles 1-4 and paddle 8 should be  $\overline{\text{OFF}}$ . Paddles 5-7 should  $\overline{\text{ON}}$ .

**S**2

| PADD | LE | # | !  |   |   | FUNCTION                                |

|------|----|---|----|---|---|-----------------------------------------|

| 1    |    |   | ٠  |   |   | "ON" enables EPROM wait state.          |

| 2    |    |   |    |   |   | "ON" enables interrupt response byte.   |

| 3    |    |   | ٠. |   |   | DMA priority address 3                  |

| 4    |    |   | ٠  |   |   | DMA priority address 2 ON = 0           |

| 5    | :  |   |    |   |   | DMA priority address 1                  |

| 6    |    |   |    | _ | _ | DMA priority address 0 "OFF" = 1        |

| 7    |    |   |    |   |   | "ON" enables SLAVE CLR* to reset MPX-1. |

|      |    |   |    |   |   | not used                                |

# INTERRUPT "CALL" JUMPERS

The MPX-1 "calls" the system CPU by causing an interrupt on the bus. There are ten possible interrupt lines that the MPX-1 may assert. They are: INT\*, NMI\* or any of the eight vectored interrupt lines (VIO\*-VI7\*). There are also two methods by which the MPX-1 can assert the interrupt request - the SOD line or by setting a hardware latch (described above in the section entitled "Getting the Main System CPU's Attention").

The interrupt line asserted and the method of asserting it are selected by Jumpers J1-10. These jumpers are implemented with push-on shorting plugs and pins soldered into the board. Each jumper has three pins labeled A, B and C. The "A" pin of each jumper is connected to the SOD interrupt source. The "C" pin of each jumper is connected to the interrupt response latch. The "B" pin of each jumper is connected to an interrupt line on the bus according to the chart below:

| JUMPER                                    | # | LEGEND                                      | MARKING | "B" POSITION                                      | CONNECTION |

|-------------------------------------------|---|---------------------------------------------|---------|---------------------------------------------------|------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 |   | 7<br>6<br>5<br>4<br>3<br>2<br>1<br>0<br>NMI |         | VI7* VI6* VI5* VI4* VI3* VI2* VI1* VI0* NMI* INT* |            |

EXAMPLE: To connect the MPX-1 interrupt request output to the INT\* line on the bus with the interrupt source from the SOD line, a shorting plug should be installed at J10 from the "A" to "B" position (left of center).

EXAMPLE: To connect the MPX-1 interrupt request output to the VI3\* line on the bus with the interrupt source from the interrupt latch, a shorting plug should be installed at J5 from the "B" to "C" position (right of center).

NOTE: The software supplied with the MPX-1 assumes the use of the SOD interrupt mode, so if you wish to use the MPX in an interrupt driven mode with the standard software, use only the SOD interrupt source.

# SELECTING AND USING 4K OR 16K RAM CHIPS

The MPX-1 can use either 2147 4Kxl RAM chips, or 2167 16Kxl RAM chips. The MPX-1 should have come from the factory already jumpered correctly for the type of chip that was originally ordered with the board. Should it become necessary to change these jumpers once the board is in the field, here is how different RAMs are jumpered and inserted:

## USING 2147 4Kx1 TYPE RAM CHIPS

To use 2147 type RAM chips, jumpers J11 through J17 should be installed and J18 should be open. J11 through J17 are located in-between the RAM array (U10-

17), and J18 is located at the right-hand side of the RAM array. The RAM chips come in 18 pin packs, but the sockets are 20 pin to accommodate 2167 type RAMs. When using 2147 type RAMs, plug them in so that the chips are in the bottom-most part of the socket, that is pins 1 and 20 are blank.

#### USING 2167 16Kxl TYPE RAM CHIPS

To use 2167 type RAM chips, jumper J18 should be installed and jumpers J11-17 should be open. Jumper J18 is located at the far right-hand side of the RAM array and jumpers J11-17 are located in-between the RAM chips.

# CONFIGURING THE MPX-1 FOR DIFFERENT SIZE EPROMS

The MPX-1 has a JEDEC 28 pin socket for the EPROM (U27). With the use of one jumper, this socket can accommodate a 2716, 2732 or a 2764 type EPROM. This gives 2K, 4K or 8K of storage, respectively.

#### USING A 2716 or 2732 EPROM

To use a 2716 or 2732 type EPROM, jumper J19 should have a shorting plug installed connecting pins "A" and "C" (left of center). J19 is located just above U26. The 2716 or 2732 should be installed at location U27 such that it uses the bottom-most pins of the socket, that is pins 1,2,27 and 28 are left blank.

#### USING A 2764 EPROM

To use a 2764 type EPROM, jumper J19 should have a shorting plug installed connecting pins "C" and "B" (right of center). J19 is located just above U26. The 2764 should be installed at location U27, and all the pins of the socket are used.

## STANDARD SOFTWARE SUPPLIED WITH MPX-1

The MPX-1 is supplied with an EPROM that contains some general purpose utility routines. It contains code to initialize the interrupt controllers (to a benign state), several useful subroutines and a general purpose command interpreter that implements a "channel protocol". Included are several built-in commands to perform useful tasks such as loading and executing programs from system memory, changing the interrupt controller parameters and block memory moves on system RAM. The command structure includes a sophisticated "link" protocol that allows chaining of command sequences and recursion.

Note that no representation is made that this is the most efficient way to program or use an MPX board. Rather, it is intended as partly tutorial and partly a useful way to get "up and running" with the MPX in a minimum amount of time.

What follows is a discussion of the basic command structure and then descriptions of the actual commands. Following that is a discussion of the code itself that explains how to add custom commands and describes several useful subroutines.

### BASIC COMMAND STRUCTURE AND PROTOCOL

When the MPX-1 powers up, it masks all its interrupt inputs, does some internal initialization and waits quietly for an ATTN on its ATTN port. When it receives an ATTN it will read in 16 bytes from the system memory starting at address 50 hex. The meaning of the bytes follows:

```

Byte 0: Opcode Byte

```

Byte 1: Status Indication Byte

Byte 2: General Purpose Parameter Byte 0

Byte 10: General Purpose Parameter Byte 8

Byte 11: Link Address (least significant byte)

Byte 12: Link Address

Byte 13: Link Address (most significant byte)

Byte 14: Result 1 byte Byte 15: Result 2 byte

The following is a more detailed description of the bytes shown above:

#### OPCODE BYTE

The opcode byte contains the information that tells the MPX what command to execute, and also contains two bits that control the completion interrupt and link structures. The actual bit coding of the opcode byte is shown below:

| Bi | t 7 |   |     |   |   |   |     |   |   |     |   |   |     |   |  |     |   |   | Bit | t ( | ) |

|----|-----|---|-----|---|---|---|-----|---|---|-----|---|---|-----|---|--|-----|---|---|-----|-----|---|

|    |     |   |     |   |   |   |     |   |   |     |   |   |     |   |  |     |   |   |     |     | - |

|    | ONT | 1 | INT | 1 | 0 | - | BIT | 4 | 1 | BIT | 3 | 1 | BIT | 2 |  | BIT | 1 | 1 | BIT | 0   | 1 |

|    |     |   |     |   |   |   |     |   |   |     |   |   |     |   |  |     |   |   |     |     |   |

Bits 0 through 4 of the opcode contain the "command number" of which there are a possible 31 (one command is reserved). The first 10 commands have already been defined and the remaining 21 may be implemented by you.

Command "OF" is reserved, and if invoked will be translated internally to a NOP command.

The INT bit (bit 6) of the opcode byte is the INTERRUPT ENABLE bit. If this bit is set to one in the opcode, the MPX will cause an interrupt (SOD interrupt) when it has completed the command. If this bit zero, an interrupt will not be generated when the command has completed execution. Note that in order for the interrupt to make it to the bus, it must be jumpered to an interrupt line (see the hardware configuration section of this document for further details).

The CONT bit (bit 7) of the opcode byte is the CONTINUE bit and is associated with the link structure. If the CONT bit is set high, execution of the next command (pointed to by the link address) will commence immediately after execution of the current command is complete. If the CONT bit is zero, the MPX will stop when execution of the current command is complete, and wait for another ATTN before executing the next command.

There are two considerations when using the CONT bit. The first is that the INT bit is ignored if the CONT bit is set. This means that an interrupt will only occur if no command is to follow, which is the way one would normally want things to happen when executing a sequence of commands.

Secondly, if the link address points to the beginning of this same instruction (pointing to itself) and the CONT bit is set, endless execution of the instruction will occur. This could be useful. The way to stop execution would be to change the opcode so that the CONT bit is zero. The opcode could be changed to a NOP, or merely the same opcode with the CONT bit zeroed. Either the system CPU or the MPX could change the opcode. DO NOT try to change the link address on the fly! \*>

Bit 5 is unused and is really a "don't care" bit, but a good practice would be to always set this bit to zero.

#### STATUS INDICATION BYTE

This byte is used to "handshake" with the MPX when the use of a completion interrupt is not desired, or they may be used in conjunction. This byte should be set to zero before an ATTN is sent to the MPX. When the MPX is done executing the command, it will set this byte to FF hex. In a non-interrupt environment, this byte should be checked before another command is sent to the MPX.

If the CONT bit is set in the command opcode, the status byte for that particular command will NOT be set to FF hex. This means that in a sequence of commands, only the status byte in the last command (the one with CONT = 0) will be set to FF hex.

## GENERAL PURPOSE PARAMETER BYTES 0 through 8

These bytes are used to send parameters to the MPX along with the command. The parameter(s) sent vary with the command. Only the block move commands use all nine bytes, and they would contain the starting, ending and destination addresses for the block move (3 bytes each). Sometimes only a few bytes are used and sometimes none are used at all. The exact usage of these bytes is detailed in each individual command description.

#### LINK ADDRESS BYTES

These three bytes are a pointer to the place at which the next command line is resident in the system memory. When not executing multiple commands (CONT bit = 0), this address would normally point to the beginning of the same command. When executing a sequence of commands, this address would point to the address of the next command.

The address is stored low byte first and is a full 24 bit address.

The initial link address is 50 hex, but the NOP instruction may be used to change the link address to any other system address.

Note that the link address is read only once and at the start of each command, not at the end. This means that the command itself may modify the link address, but it will only affect the following command (not the where the next command will be fetched). The main system CPU should not modify the current link address unless the MPX is not active.

#### RESULT 1 AND RESULT 2 BYTES

Sometimes it is desirable to have the MPX return parameters to the caller, and that is the purpose of these two bytes. Only two of the built-in commands return data to these locations, but user generated commands should use these bytes for that purpose as well.

#### GENERAL NOTES

Commands are assumed to be resident on 16 byte boundaries ie: 50H, 60H, 180H, etc.

The only bytes in the command line that the MPX modifies are the status indication and result bytes. All others are left intact.

#### COMMAND DESCRIPTIONS

#### NOP - No Operation

OPCODE BIT CODING:

|   | Bit 7 |      |      |      |      |      | ,]   | Bit O | ) |

|---|-------|------|------|------|------|------|------|-------|---|

| _ |       | <br> | <br> | <br> | <br> | <br> | <br> |       | - |

| İ | CONT  |      |      |      |      |      |      |       |   |

|   |       | <br> | <br> | <br> | <br> | <br> | <br> |       |   |

PARAMETERS PASSED: Link Address.

PARAMETERS REURNED: None.

DESCRIPTION: This command seems useless on the surface, but in reality has many uses. This command may be used to change the link address if address 50 hex is not a good one for your system. It may also be used to reset the interrupt output from the MPX if it was set by the completion of a previous command (of course the INT bit should be zero). This command is also useful in debugging a command sequence since it may be used to cause execution to skip the command that is replaced with a NOP.

#### RESET - Reset the MPX-1

OPCODE BIT CODING:

| Bit 7 |   |  |  |  |  |   |  | I | 3it ( | ) |

|-------|---|--|--|--|--|---|--|---|-------|---|

|       |   |  |  |  |  |   |  |   |       |   |

| CONT  | i |  |  |  |  | 0 |  |   |       |   |

PARAMETERS PASSED: None. PARAMETERS RETURNED: None.

DESCRIPTION: This command resets the MPX-1 to its initial starting state. The internal command table will be cleared (so any custom commands you have loaded into RAM will now be ignored). The address where the MPX picks up its first command line will be set to 50H. All interrupts will be masked and the interrupt controller will be re-initialized.

## SET MASK - Mask or Unmask interrupt inputs to MPX-1

OPCODE BIT CODING:

|   | Bit 7 |      |   |   |   |   |   |   |   |   |   | I | 3it C | ) |

|---|-------|------|---|---|---|---|---|---|---|---|---|---|-------|---|

| _ |       | <br> |   |   |   |   |   |   |   |   |   |   |       |   |

|   | CONT  | l    | 0 | 1 | 0 | 1 | 0 | } | 0 | 1 | 1 |   | 0     | ١ |

PARAMETERS PASSED: Mask Byte, Link Address.

PARAMETERS RETURNED: None.

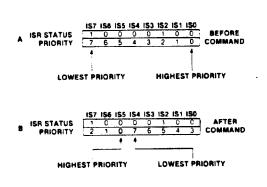

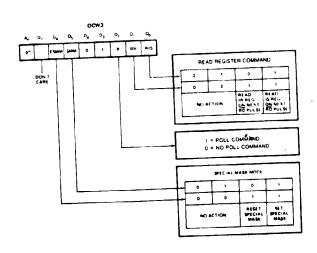

DESCRIPTION: This command is used to mask or unmask interrupt inputs to the MPX-1. The byte passed in Parameter Byte 0 is written to the mask register of the 8259A interrupt controller. If a bit in the mask byte is set to one, the corresponding interrupt will be masked. Conversely, if a bit is zero, that interrupt will be unmasked. Bit 0 of the mask byte corresponds to VIO\* on the bus, and Bit 7 corresponds to VI7\* on the bus. This is the same as sending OCW1 to the interrupt controller (see the 8259A application note in the appendix of this document for more information).

# SENDEOI - SEND END-OF-INTERRUPT COMMAND TO INTERRUPT CONTROLLER

OPCODE BIT CODING:

|   | Rit 7        |     |     |   |     |   |     |   |   |   |     |   | F   | 3it 0 | )   |

|---|--------------|-----|-----|---|-----|---|-----|---|---|---|-----|---|-----|-------|-----|

|   | <b>510</b> . |     |     |   |     |   |     |   |   |   |     |   |     |       |     |

|   |              |     |     |   |     |   |     | _ |   | ^ | - 1 | 1 | - 1 | 1     | - 1 |

| 1 | CONT         | INT | - 1 | 0 | - 1 | O | - 1 | U | ı | U | ı   | + | ı   | -     | •   |

| • |              |     |     |   |     |   |     |   |   |   |     |   |     |       |     |

PARAMETERS PASSED: EOI Command Byte, Link Address. PARAMETERS RETURNED: None.

DESCRIPTION: This command is used to send an End-of-Interrupt Command to the 8259A interrupt controller. It is also useful for rotating the interrupt priority levels. The byte to be sent to the 8259A is passed in Parameter Byte 0. This is equivalent to sending OCW2 to the 8259A. For more information on what this byte does to the 8259A, refer to the 8259A application note contained in the appendix of this document.

# READREG - READ INTERRUPT CONTROLLER REGISTERS

OPCODE BIT CODING:

| Bit 7       |       |    |   |     |   |   |   |     |   |   |   | <b>B</b> : | it O |     |

|-------------|-------|----|---|-----|---|---|---|-----|---|---|---|------------|------|-----|

|             |       |    |   |     |   |   |   |     |   |   |   |            |      | -   |

|             |       |    |   |     |   |   |   |     |   |   | _ | 1          | ^    | 1   |

| 1 00000 1 7 | · NTT | 1  | Λ | 100 | Λ | 1 | 0 | - 1 | 1 |   | 0 | - 1        | U    | - 1 |

| CONT   I    | TNI   | į. | U | 1 7 | U |   | v | •   | _ | • |   | -          |      | _   |

|             |       |    |   |     |   |   |   |     |   |   |   |            |      | -   |

|             |       |    |   |     |   |   |   |     |   |   |   |            |      |     |

PARAMETERS PASSED: Link Address.

PARAMETERS RETURNED: Contents of IS and IR registers in 8259A.

DESCRIPTION: This command is used to read the contents of the Interrupt Request (IR) and In Service (IS) registers in the 8259A. It returns the contents of the IR register in the Result  $\tilde{1}$  Byte location and the contents of the IS register in the Result 2 Byte location. For more information on the meaning of the IS and IR registers, see the 8259A application note in the appendix of this document.

# SETRESPONSE - SET INTERRUPT RESPONSE BYTE

OPCODE BIT CODING:

| Bit 7    |     |   |     |   |   |   |   |   |     |   | I | 3it ( | )   |

|----------|-----|---|-----|---|---|---|---|---|-----|---|---|-------|-----|

| DIC.     |     |   |     |   |   |   |   |   |     |   |   |       |     |

|          |     |   |     |   |   |   |   |   |     | _ |   | -     | 1   |

| CONT     | 1   | ^ | - 1 | Λ | 1 | Λ |   | 1 | - 1 | 0 | 1 | 1     | - 1 |

| I CONT I | INT | U | ı   | U | ı | v | ı | - | '   | - | • |       |     |

| •        | •   |   |     |   |   |   |   |   |     |   |   |       |     |

|          |     |   |     |   |   |   |   |   |     |   |   |       |     |

PARAMETERS PASSED: Response Byte, Link Address.

PARAMETERS RETURNED: None.

DESCRIPTION: The MPX-1 is capable of putting an 8 bit value on the system data

bus during system interrupt acknowledge cycles. The value is called the interrupt response byte and may be set as desired with this command. Note that this response will only appear on the bus if this feature in enabled by a hardware switch. See the hardware section of this document for more information.

#### SIZE - INDICATE WHETHER 4K OR 16K MPX-1

OPCODE BIT CODING:

|   | Bit 7 |     |   |      |      |      |      | 1    | Bit ( | ) |

|---|-------|-----|---|------|------|------|------|------|-------|---|

| _ |       |     |   | <br> | <br> | <br> | <br> | <br> |       |   |

| 1 | CONT  | INT | • | -    |      |      |      |      |       |   |

PARAMETERS PASSED: Link Address.

PARAMETERS RETURNED: Size indication.

DESCRIPTION: This command is used by the system to determine the amount of memory installed in this particular MPX-1. The Result 1 Byte is set to 00 hex if this is a 4K MPX-1 and is set to FFH if this is a 16K MPX-1.

#### LOADRAM - LOAD MPX LOCAL RAM FROM SYSTEM RAM

OPCODE BIT CODING:

|   | Bit 7 |     |   |   |      |  |   |   |   |   |   | I | Bit ( | ) |

|---|-------|-----|---|---|------|--|---|---|---|---|---|---|-------|---|

|   | CONT  | INT | 1 | 0 | 0    |  | 0 | 1 | 1 | l | 1 | 1 | 1     | 1 |

| _ |       |     |   |   | <br> |  |   |   |   |   |   |   |       |   |

PARAMETERS PASSED: Starting Address in System RAM (3 bytes)

Ending Address in System RAM (3 bytes)

Destination Address in Local RAM (2 bytes)

Link Address

PARAMETERS RETURNED: None.

DESCRIPTION: This command is used to load the MPX local RAM from system RAM. Three addresses are passed to the MPX: The starting address of the block to be loaded, its ending address, and the starting address of the place to put it in local RAM. The starting and ending addresses are 3 bytes long and the destination address is only two bytes long. All addresses are stored low byte first and the starting address is at Parameter Bytes 0-2, the ending address is at Parameter Bytes 3-5, and the destination address is at bytes 6-7.

#### EXRAM - EXECUTE A PROGRAM IN LOCAL RAM

OPCODE BIT CODING:

|  | Bit 7 |     |   |   |   |   |   |   |   |   |   |   | - | Bit ( |   |

|--|-------|-----|---|---|---|---|---|---|---|---|---|---|---|-------|---|

|  | CONT  | INT | 1 | 0 | 1 | 0 | 1 | 1 | l | 0 | 1 | 0 | ļ | 0     | ١ |

PARAMETERS PASSED: Execution Address (2 bytes), Link Address.

PARAMETERS RETURNED: None.

DESCRIPTION: This command is used to cause a routine stored in local RAM on the MPX-1 to be executed. A "call" is made to the routine, so when it has finished executing a RETURN instruction will pass control back to the interpreter (assuming a clean stack). The starting address of the routine is two bytes long and is stored low byte first at Parameter Bytes 0 and 1.

# BLKMOV - MOVE A BLOCK OF RAM ON THE SYSTEM BUS

OPCODE BIT CODING:

| 77         |   |   |     |   |     |   |   | • |   |   | I | 3it ( | 0   |

|------------|---|---|-----|---|-----|---|---|---|---|---|---|-------|-----|

| Bit 7      |   |   |     |   |     |   |   |   |   |   |   |       |     |

|            |   |   |     |   |     | • | 1 | ^ | 1 | Λ | 1 | 1     | - 1 |

| CONT   INT | 1 | 0 | - 1 | O | - 1 | T | 1 | 0 | ł | • |   |       | `   |

|            |   |   |     |   |     |   |   |   |   |   |   |       |     |

PARAMETERS PASSED: Starting Address in System RAM (3 bytes).

Ending Address in System RAM (3 bytes).

Destination Address in System RAM (3 bytes).

Link Address.

PARAMETERS RETURNED: None.

DESCRIPTION: This command is used to move a block of RAM (of any size) on the S-100 bus. Three addresses are passed: The starting address of the block to be moved, its ending address and the destination address of where it's being moved to. Each address is three bytes long and is stored low byte first. The starting address should be at Parameter Bytes 0-2, the ending address should be at Parameter Bytes 3-5 and the destination address should be at Parameter Bytes 6-8. Note that this command is useful for putting code in extended pages that normal 8 bit processors cannot talk to without a lot of effort.

# FASTMOV - MOVE A BLOCK OF RAM ON THE SYSTEM BUS - FAST

OPCODE BIT CODING:

|   | Bit 7 |   |         |   |   |     |   |     |   |     |   |   |   | 1   | Bit C | ) |

|---|-------|---|---------|---|---|-----|---|-----|---|-----|---|---|---|-----|-------|---|

|   | BIC / |   |         |   |   |     |   |     |   |     |   |   |   |     |       |   |

| - |       |   |         |   |   |     |   |     |   |     |   |   | _ | 1   | ^     | 1 |

|   | CONT  | 1 | T 3 107 | 1 | Λ | 1   | n | - 1 | 1 | l i | 0 |   | 1 | - 1 | U     | 1 |

| 1 | CONT  | - | INI     | ţ | U | - 1 | U | ı   | - | •   |   | • |   |     |       |   |

| • |       |   |         |   |   |     |   |     |   |     |   |   |   |     |       |   |

PARAMETERS PASSED: Starting Address in System RAM (3 bytes).

Ending Address in System RAM (3 bytes). Destination Address in System RAM (3 bytes).

Link Address.

PARAMETERS RETURNED: None.

DESCRIPTION: This command is almost the same as above, except that all blocks must be a multiple of 256 bytes, and begin on 256 byte boundaries. This allows the transfer to occur at a much higher rate. Three addresses are passed: The starting address of the block to be moved, its ending address and the destination address of where it's being moved to. Each address is three bytes long and is stored low byte first. The starting address should be at Parameter Bytes 0-2, the ending address should be at Parameter Bytes 3-5 and the destination address should be at Parameter Bytes 6-8. Note that even though each address is three bytes long, the low byte is assumed to be 00 hex.

#### RESERVED - DO NOT USE

OPCODE BIT CODING:

|  | Bit 7 |     |   |  |  |  |  | I | 3it ( | ) |

|--|-------|-----|---|--|--|--|--|---|-------|---|

|  |       |     |   |  |  |  |  |   |       |   |

|  | CONT  | INT | • |  |  |  |  |   |       |   |

Note: This opcode is reserved and should not be used by custom command routines. Attempts to call this opcode will be translated internally to NOP opcodes (link address will still be valid, however). The reason this opcode is reserved is because its jump table address is used by the ATTN routine.

#### ABOUT THE ROM CODE

This is a brief description of what goes on in the standard software routine.

The first thing in the code is a jump to the actual beginning of the code. The reason this is there is because of the way the MPX-1 does its "power-on-jump" sequence. The ROM appears at address 0000H for the first three cycles and then appears at 4000H thereafter.

#### INITIALIZATION

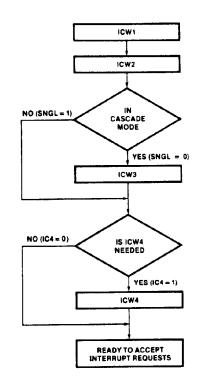

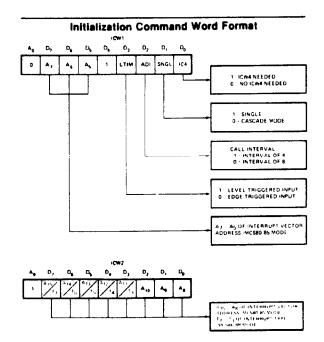

The first thing that happens is to set up the interrupt controller with all interrupts masked, and the interrupt vector table at address 80H (4 byte interval).

Starting at 0000H in RAM are two tables: the command jump table and the interrupt vector table. The first thing that happens is that all these jump locations are initialized to point to a routine called DUMMY, which is nothing more than a RET instruction. This is where all interrupts and all unused commands go to, (until you change the table). The next thing that happens is to patch the command jump table with the addresses of the ten command routines that are supplied in the ROM. Next the stack pointer is initialized leaving about 77 bytes free for stack usage. That should be more than enough, the routines in the ROM never get more than about 6 bytes deep.

Next the initial link address is set up to point address 50H and then the ATTN interrupt (RST 7.5) is armed and the MPX sits quietly waiting for an ATTN.

#### ATTN RESPONSE

When an ATTN occurs, first the interrupt output is cleared, the ATTN interrupt input is masked and the last link address is copied into CURRENT. Then 16 bytes are read from the system memory (pointed to by CURRENT) into a buffer called CMNDBUF. The opcode byte is read from the buffer and decoded. A call is then made to the address pointed to by the lower 5 bits of the opcode. The opcode is first checked to see if it is the same as the ATTN jump address. If it is, a NOP command is substituted instead. Control has now been transfered to the actual command routine. When the command is done executing, all it need do is a RET instruction to get back to the main interpreter loop.

When a command is finished, the program branches to CHECK. This routine checks to see if the CONT bit was set in that opcode. If it was, a jump occurs to the ATTN routine and the next command is executed. If the CONT bit is not set, the INT bit is checked. If it is set, the status byte is set to FFH and the SOD interrupt output is set and the MPX then waits for the next ATTN. If the INT bit is not set, the status byte is set to FFH and the MPX waits for the next ATTN.

# GENERAL PURPOSE SUBROUTINES

The ROM contains several useful subroutines that may be utilized by your own custom commands. They include functions such as managing the address pointers, storing them in appropriate registers for bus accesses, and reading and writing bytes on the system bus. Their functions are pretty well documented in the assembly listing that follows.

# WRITING YOUR OWN CUSTOM COMMANDS ...

Ten commands are used by the standard ROM and one is reserved, so that leaves a total of 21 command opcodes that are available for your custom usage. Less than 1/4th of the 2K bytes in the ROM are used by the standard routines, so custom commands could be added to the ROM if you have access to an EPROM burner. If not, commands can be assembled to run from the ample free RAM space and loaded using the LDRAM command. The command jump table is kept in RAM (from 0000H to 007FH) so it may also be changed with the LDRAM command. Control may be passed to the new commands by use of the opcode protocol or by the EXRAM command.

Some considerations about writing into the internal RAM: Be careful not to overwrite the buffer, stack or ATTN jump locations (the ATTN jump resides at 3C - 3FH). The program does not use RAM above 200H at any time, so all RAM above this address is free for your use. It is a good idea to issue a SIZE command to determine the amount of RAM available (4K or 16K) before issuing a LDRAM command. This is because the RAM in a 4K MPX-1 "wraps around" and appears in eack 4K block in the 16K RAM space.

## LISTING OF STANDARD SOFTWARE SUPPLIED WITH THE MPX-1

```

:MPX PROM VERSION 1.0

:WRITTEN 1-7-82 BY MARK GARETZ

:COPYRIGHT 1982 BY GODBOUT ELECTRONICS

Multiple command linking bug fixed-llo

:VERSION 1.1

; EQUATES

H0008

:Interrupt Controller

= 0008

INTCLA EQU

INTCLB EQU

8001H

8001 =

;DMA Addr. Bits A8-15

8004 =

DMALO

EQU

8004H

8005 =

DMAHI

EQU

8005H

;DMA Addr. Bits A16-23

8007 =

INTRSP

EQU

8007H

:Interrupt Response Byte Reg.

OCOH

;External Window

0000 =

WINDOW EQU

;Command Jump Table

0000 =

CMNDTBL EQU

H0000

:Interrupt Response Jump Table

0080 =

INTTBL EQU

H0800

;Temporary Command Buffer

HOAOO

00A0 =

CMNDBUF EQU

;Starting Address, 3 bytes

CMNDBUF+2

00A2 =

STRTAD EQU

;Ending Address, 3 bytes

00A5 =

ENDAD

EQU

STRTAD+3

ENDAD+3

;Destination Address, 3 bytes

= 8A00

DESTAD EQU

;Link Address, 3 bytes

DESTAD+3

00AB =

LINKAD EQU

;Result byte 1

00AE =

RESULT1 EQU

LINKAD+3

;Result byte 2

00AF =

RESULT2 EQU

RESULT1+1

;Current Command Address, 3 bytes

ООВОН

00B0 =

CURRENT EQU

OOFF =

OOFFH

:Stack Space

EQU

STACK

0100 =

0100H

;Fast Block Move Buffer

BUFFER EQU

;SIM INSTRUCTION

0030 =

SIM

EQU

30H

;Beginning of Code

4000

ORG

4000H

4000 C33140

:3 Init Bytes

JMP

START

'VERS. 1.0'

4003 564552532E

DB

COPYRIGHT 1982 BY GODBOUT ELECTRONICS

400C 434F505952

DR

4031 3E9E

START: MVI

A,9EH

; ICW1

4033 320080

STA

INTCLA

4036 3E00

MVI

A,O

;ICW2

4038 320180

STA

INTCLB

403B 320180

STA

INTCLB

;ICW3 too

403E 3EFF

MVI

A,OFFH

;OCWl Mask all interrupts

4040 320180

;Done with interrupt controllers

STA

INTCLB

The following code initializes the Command Jump Table and

:Interrupt Jump Table. Unused entries jump to DUMMY

; Note: all entries are first initialized to DUMMY, then

; patched for commands and ATTN.

4043 210000

LXI

H, CMNDTBL

;D gets DUMMY addr.

4046 117B42

LXI

D.DUMMY

4049 0100C3

;JUMP and a NOP

LOOP1:

LXI

в, осзоон

404C 7D

MOV

A,L

```

```

OAOH ; check for end

CPI

404D FEAO

MORE

JΖ

404F CA5D40

M,B

;the JUMP

MOV

4052 70

H

INX

4053 23

; the DUMMY addr.

M,E

MOV

4054 73

Н

4055 23

INX

M,D

MOV

4056 72

H

INX

4057 23

;the NOP

M,C

MOV

4058 71

H

INX

4059 23

LOOP1

JMP

405A C34940

;addr. of ATTN routine

H,ATTN

LXI

405D 21E040

MORE:

003DH

SHLD

4060 223D00

;This part of the code writes the addresses of the command

; routines into the command table.

;address of NOP routine

H, NOPR

4063 21CE41

LXI

CMNDTBL+1

4066 220100

SHLD

; RESET jump

H,START

4069 213140

LXI

CMNDTBL+5

SHLD

406C 220500

;set mask routine

LXI

H, SETMSK

406F 21CF41

CMNDTBL+9

SHLD

4072 220900

;EOI routine

H.SETEOI

LXI

4075 21D641

CMNDTBL+13

SHLD

4078 220D00

; INT regester read routine

H, READRG

LXI

407B 21DD41

CMNDTBL+17

407E 221100

SHLD

;set response byte routine

H.SETRSP

LXI

4081 21F841

SHLD

CMNDTBL+21

4084 221500

;return size routine

H,SIZE

LXI

4087 21FF41

CMNDTBL+25

SHLD

408A 221900

;load RAM routine

→, H, LDRAM

LXI

408D 213342

CMNDTBL+29

SHLD

4090 221D00

:execute RAM routine

H, EXRAM

LXI

4093 214B42

CMNDTBL+33

4096 222100

SHLD

;block move routine

H, BLKMOV

4099 214F42

LXI

CMNDTBL+37

SHLD

409C 222500

;fast block move routine

H, FSTMOV

409F 216542

LXI

CMNDTBL+41

SHLD

40A2 222900

SP, STACK

LXI

40A5 31FF00

LXI

H, LINKAD

40A8 21AB00

;low order initial link addr.

MVI

M, 50H

40AB 3650

INX

H

40AD 23

XRA

Α

40AE AF

MOV

M,A

40AF 77

Н

40BO 23

INX

MOV

M,A

40B1 77

;This routine arms the attention interrupt and waits.

A, 1BH

40B2 3E1B

REARM:

MVI

SIM

DB

40B4 30

40B5 FB

EI

40B6 76

HLT

```

;This routine checks the CONT and INT bits of the opcode ; and acts accordingly.

| 40B7 3AA000 CHECK 40BA E680 40BC C2DC40 40BF 3AA000 40C2 E640 40C4 CAD340 40C7 CD1041 40CA 23 40CB 36FF 40CD 3ECB 40CF 30 40D0 C3B240 40D3 CD1041 40D6 23 40D7 36FF 40D9 C3B240 | LDA CMNDBUF ANI 80H JNZ ATTNO LDA CMNDBUF ANI 40H JZ DONE CALL PUTCMD INX H MVI M, OFFH MVI A, OCBH DB SIM JMP REARM CALL PUTCMD INX H MVI M, OFFH | ;Check the CONT bit ;lf set then a successive command ;get it again ;Check the INT bit ;if not set ;put current addr into regs ;for status byte addr. ;set status byte in memory ;set SOD high |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

;This is the main command interpreter routine. It first copies ;the LINK addr. into CURRENT and then reads in the command ;bytes. Then an indirect call is executed to the address of ;the command. It also unsets the interrupt output (SOD).

| 40DC 21H<br>40DF E5<br>40E0 3E5<br>40E2 30<br>40E3 3AA<br>40E6 32H                   | F ATTN:                    | LXI<br>PUSH<br>MVI<br>DB<br>LDA<br>STA                | H,CHECK H A,5FH SIM LINKAD CURRENT      | ;ADDRESS TO RETURN TO ;PUT ON STACK ;reset SOD and mask 7.5 ;copy LINKAD into CURRENT                                                                                             |

|--------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40E9 3AA<br>40EC 32I<br>40EF 3AA<br>40F2 32I                                         | 100<br>D00                 | LDA<br>STA;<br>LDA<br>STA                             | LINKAD+1 CURRENT+1 LINKAD+2 CURRENT+2   |                                                                                                                                                                                   |

| 40F5 CD4<br>40F8 3A<br>40FB E6<br>40FD 11<br>4100 D5<br>4101 21                      | 4941<br>A000<br>LF<br>DF41 | CALL<br>LDA<br>ANI<br>LXI<br>PUSH<br>LXI              | GETCMD CMNDBUF 1FH D, BACK D H, CMNDTBL | ;get the command line from memory<br>;get the opcode byte<br>;mask the INT and CONT bits<br>;put return addr. in D<br>;and put in on the stack<br>;HL gets addr. of command table |

| 4104 07<br>4105 07<br>4106 FE<br>4108 C2<br>410B 3E<br>410D 6F<br>410E E9<br>410F C9 | OD41                       | RLC<br>RLC<br>CPI<br>JNZ<br>MVI<br>MOV<br>PCHL<br>RET | 3CH<br>ATTN1<br>A,0<br>L,A              | ; shift the opcode for pointer; check for reserved op-code; skip next if OK; otherwise, do a nop command; L gets low byte; and go there; we're done                               |

;General Purpose Subroutines Follow:

;This subroutine puts: CURRENT+2 into DMAHI, CURRENT+1;into DMALO, CURRENT into L reg and WINDOW into H

```

CURRENT+2

PUTCMD: LDA

4110 3AB200

DMAHI

STA

4113 320580

CURRENT+1

LDA

4116 3AB100

DMALO

STA

4119 320480

CURRENT

LDA

411C 3AB000

L,A

MOV

411F 6F

H, WINDOW

MVI

4120 26C0

RET

4122 C9

;This subroutine puts: STRTAD+2 into DMAHI, STRTAD+1

;into DMALO, STRTAD into L reg and WINDOW into H

STRTAD+2

LDA

PUTST:

4123 3AA400

DMAHI

STA

4126 320580

STRTAD+1

LDA

4129 3AA300

DMALO

STA

412C 320480

STRTAD

LDA

412F 3AA200

MOV

L,A

4132 6F

H, WINDOW

MVI

4133 26C0

RET

4135 C9

;This subroutine puts: DESTAD+2 into DMAHI, DESTAD+1

;into DMALO, DESTAD into L reg and WINDOW into H

DESTAD+2

PUTDST: LDA

4136 3AAA00

DMAHI

STA

4139 320580

DESTAD+1

LDA

413C 3AA900

DMALO

STA

413F 320480

DESTAD

LDA

4142 3AA800

L,A

MOV

4145 6F

H. WINDOW

MVI

4146 26C0

RET

4148 C9

;This subroutine gets 16 bytes from system memory pointed to

; by CURRENT and puts them into CMNDBUF.

;set up the registers

PUTCMD

GETCMD: CALL

4149 CD1041

D, CMNDBUF

LXI

414C 11A000

B,16

MVI

414F 0610

;get bus byte

A,M

MOV

GET1:

4151 7E

;put in buffer

STAX

4152 12

Η.

INX

4153 23

D

INX

4154 13

В

DCR

4155 05

GET 1

JNZ

4156 C25141

RET

4159 C9

;This subroutine increments STRTAD (3 bytes) and DESTAD

;(3 bytes). Entry at BUMP2 bumps only the upper two bytes.

STRTAD

415A 3AA200

LDA

BUMP:

415D 3C

INR

STRTAD

STA .

415E 32A200

DESTAD

LDA

4161 3AA800

INR

4164 3C

```

```

DESTAD

STA

4165 32A800

RNZ

4168 CO

LDA

STRTAD+1

BUMP2:

4169 3AA300

INR

Α

416C 3C

STRTAD+1

STA

416D 32A300

DESTAD+1

LDA

4170 3AA900

INR

4173 3C

DESTAD+1

STA

4174 32A900

4177 CO

RNZ

STRTAD+2

4178 3AA400

LDA

INR

417B 3C

STRTAD+2

STA

417C 32A400

DESTAD+2

417F 3AAA00

LDA

4182 3C

INR

DESTAD+2

4183 32AA00

STA

4186 C9

RET

```

;This subroutine has two entry points: CMPAR3 checks all three; bytes of both STRTAD and ENDAD for equality. CMPAR2 checks; only the upper two bytes. Returns with Z flag set if equal.

```

CMPAR3: LDA

STRTAD

4187 3AA200

MOV

B,A

418A 47

ENDAD

LDA

418B 3AA500

CMP

В

418E B8

418F CO

RNZ

CMPAR2: LDA

STRTAD+1

4190 3AA300

MOV

B,A

4193 47

LDA

ENDAD+1

4194 3AA600

4197 B8

CMP

4198 CO

RNZ

LDA

STRTAD+2

4199 3AA400

MOV

B,A

419C 47

LDA

ENDAD+2

419D 3AA700

R

CMP

41A0 B8

41A1 C9

RET

```

;This subroutine reads a byte from external memory pointed to ;by STRTAD. The byte read returns in A.

```

41A2 CD2341 RDEXT: CALL PUTST

41A5 7E MOV A,M

41A6 C9 RET

```

;This subroutine writes a byte to exteral memory pointed to by ;DESTAD. The byte to be written should be in A.

```

41A7 F5 WREXT: PUSH PSW

41A8 CD3641 CALL PUTDST

41AB F1 POP PSW

41AC 77 MOV M,A

41AD C9 RET

```

; This subroutine reads 256 bytes from external memory pointed ; to by STRTAD and puts them into  ${\tt BUFFER.}$

Į

```

PUTST

RD256: CALL

41AE CD2341

;zero L reg.

;DE gets BUFFER address

L,O

MVI

41B1 2E00

D, BUFFER

LXI

;get byte

41B3 110001

A,M

VOM

;store it in buffer

RD2:

41B6 7E

D

STAX

41B7 12

Ε

INR

41B8 1C

L

INR

41B9 2C

RD2

JNZ

41BA C2B641

RET

41BD C9

;This subroutine writes 256 bytes from BUFFER to external

;memory pointed to by DESTAD.

PUTDST

WR256: CALL

41BE CD3641

L,O

MVI

41C1 2E00

D, BUFFER

;A gets byte from buffer

LXI

41C3 110001

LDAX

D

WR2:

41C6 1A

MOV

M,A

41C7 77

INR

Ε

41C8 1C

L

INR

41C9 2C

WR2

JNZ

41CA C2C641

RET

41CD C9

;The actual commands start below:

; Command does nothing, but is useful anyway.

RET

NOPR:

41CE C9

;Command to set OCW1 (Mask Byte)

;Get the mask byte

*STRTAD

SETMSK: LDA

41CF 3AA200

INTCLB

STA

41D2 320180

RET

41D5 C9

;Command to send EOI to interrupt controller (OCW2)

;get the EOI byte

STRTAD

SETEOI: LDA

41D6 3AA200

INTCLA

STA

41D9 320080

RET

41DC C9

;Command to read the IR and IS registers in the Interrupt

;Controller. Puts IR in RESULT1 and IS in RESULT2.

PUTCMD

READRG: CALL

41DD CD1041

A,L

MOV

offset of RESULT1

41E0 7D

OEH

ADI

41E1 C60E

L,A

MOV

;read IR command

41E3 6F

A, OAH

MVI

41E4 3E0A

INTCLA

STA

;read it

41E6 320080

INTCLA

;Store it external

LDA

41E9 3A0080

M,A

MOV

;read IS command

41EC 77

A, OBH

MVI

41ED 3EOB

INTCLA

STA

41EF 320080

; read it

INTCLA

;offset of RESULT2

LDA

41F2 3A0080

INR

L

41F5 2C

```

```

;Store it external

M,A

MOV

41F6 77

RET

41F7 C9

;Command to set the interrupt response byte

STRTAD

SETRSP: LDA

41F8 3AA200

INTRSP

STA

41FB 320780

RET

41FE C9

;Command to return size of MPX1 (4K or 16K). If 4K MPX1,

; sets RESULT1 to 0, if 16K MPX1, sets RESULT1 to FFH

;top of 4K RAM

OFFFH

LDA

SIZE:

41FF 3AFFOF

; save it on the stack

PUSH

PSW

4202 F5

;top of 16K RAM

3FFFH

LDA

4203 3AFF3F

; save it as well

PUSH

PSW

4206 F5

A, OAAH

IVM

4207 3EAA

OFFFH

STA

4209 32FF0F

IVM

A.55H

420C 3E55

3FFFH

STA

420E 32FF3F

OFFFH

4211 3AFF0F

LDA

;is it 4K?

55H

4214 FE55

CPI

IS4K

JZ

4216 CA1E42

A, OFFH

MVI

4219 3EFF

SIZE2

421B C32042

JMP

A,0

MVI

421E 3E00

IS4K:

PSW

PUSH

4220 F5

SIZE2:

PUTCMD

CALL

4221 CD1041

MOV

A,L

4224 7D

OEH

ADI

4225 C60E

MOV

L,A

4227 6F

PSW

POP

4228 F1

MÕ₹

M,A

4229 77

POP

PSW

422A F1

3FFFH

STA

422B 32FF3F

PSW

POP

422E F1

OFFFH

STA

422F 32FF0F

RET

4232 C9

;Command to load local RAM from external memory.

:read the byte

LDRAM:

CALL

RDEXT

4233 CDA241

4236 2AA800

LHLD

DESTAD

MOV

M,A

4239 77

;Bump the pointers

CALL

BUMP

423A CD5A41

;are they equal?

CMPAR3

423D CD8741

CALL

LDRAM

4240 C23342

JNZ

; once more for last byte

RDEXT

CALL

4243 CDA241

LHLD

DESTAD

4246 2AA800

4249 77

MOV

M,A

RET

424A C9

```

;Command to execute program in local RAM. A "call" is made ;to the execution address, so all the program has to do is a ;RET to get back to the main loop.

```

;address in HL

STRTAD

EXRAM: LHLD

424B 2AA200

;go there

PCHL

424E E9

; Command to move a block of RAM on the external bus

;(slow version).

RDEXT

BLKMOV: CALL

424F CDA241

WREXT

CALL

4252 CDA741

BUMP

CALL

4255 CD5A41

CMPAR3

CALL

4258 CD8741

BLKMOV

JNZ

425B C24F42

RDEXT

CALL

425E CDA241

WREXT

CALL

4261 CDA741

RET

4264 C9

; Command to move a block of RAM on the external bus

;(fast version).

RD256

FSTMOV: CALL

4265 CDAE41

WR256

CALL

4268 CDBE41

BUMP2

CALL

426B CD6941

CMPAR2

CALL

426E CD9041

FSTMOV

JNZ

4271 C26542

RD256

CALL

4274 CDAE41

WR256

CALL

4277 CDBE41

RET

427A C9

;Dummy routine that does nothing but return.

DUMMY: RET

427B C9

```

#### MPX - THEORY OF OPERATION

The MPX is designed around the Intel 8085 microprocessor. In this application, the 8085 may access resources which are local to the MPX without use of the S-100 bus. Resources external to the MPX may be accessed through a temporary master interface as defined in the IEEE 696/S-100 specification.

The 8085 is a single chip microprocessor which requires very few external support chips. The processor includes a built in oscillator. An external crystal is provided for oscillation at 12.000 Mhz which results in a 166 nsec "T" state. Use of this oscillator rather than the S-100 bus clock makes MPX internal operations asynchronous with activities on the S-100 bus, but allows the MPX to operate at 6 Mhz independent of the external bus speed. (i.e. the MPX may execute local code at 6 Mhz even though the external bus is 2 Mhz). An LS373 (U28) is used to latch the low order address byte from the multiplexed Address-/Data bus. This IC is controlled by the Address Latch Enable (ALE) signal provided by the 8085 for that purpose. A buffer (U29) is provided for a group of loads which are inputs only.

The MPX local environment includes both RAM and ROM memory. The processor Read and Write strobes are "OR"ed and qualified with MEMORY status (by U31) to produce a MEMORY STROBE signal. This signal is used to enable a one of four decoder (U32) which decodes the two high order address lines A14 and A15. The resulting outputs are RAM STB which is decoded for addresses in the range of 0000 through 3FFF, ROM STB which is decoded for addresses of 4000 through 7FFF and INT STB (INT for Internal) which is decoded for 8000 through BFFF.

The RAM consists of either eight 2147 or 2167 type ICs (U10-U17) which are each either 4K or 16K by 1 bit. The high order address inputs A8-A11 come directly from the 8085 while the lower eight lines come from the address latch described above. The data input and data output lines of each IC are tied together to provide a bidirectional connection to the internal data bus. The remaining inputs are Chip Enable (CE) which is driven by the RAM STB as described above and Write Enable (WE) which is controlled by 8085 S1 line. If WE is false, CE will cause the contents of the addressed location to be driven onto the data bus. If WE is true, the memory outputs are forced to their high Z state. CE will cause the data on the bus to be written at the addressed location.

ROM storage is provided by a 2716, 2732 or 2764 EPROM. The ROM STB described above is used to drive the Output Enable (OE). A ROM ENA signal is derived from address and status information (without strobes) by a decoder (U32). This "look ahead" signal is used to drive Chip Enable CE of the ROM and to generate a wait state.

The 8085 samples its RDY input at the rising edge of the clock to determine if a wait state is required. Because of set-up and hold time requirements, the RDY line is held low for a full "T" state from the falling edge of the clock preceding the ROM STB. This function is controlled by a pair of "D" flip-flops (U20) and enabled by S2-1.

The 8085 will fetch the first instruction following a Reset from location 0000. The interrupt flexibility of the MPX requires RAM memory at the interrupt vector locations. This apparent dilemma is resolved by having the ROM and RAM exchange locations during initialization. S-100 bus signals RESET\* or SLAVE CLR\*

clear a counter (U5) which in turn generates INIT. INIT is "OR"ed with address line A14 (U21) so that memory accesses in the range of 0000 to 3FFF will actually access 4000 to 7FFF when INIT is active. The initial instruction fetch by the 8085 will actually come from location 4000 which is the start of the ROM. The ROM contains a jump to 4003 (or the actual start of the code) at this location. When the 8085 goes to fetch the next instruction, the initialization counter which has been counting ALEs counts to 4 removing INIT and hanging the counter. The 8085 address will be used directly to fetch the next address in the ROM.

The remaining features of the MPX hardware make up its interface to the external bus.

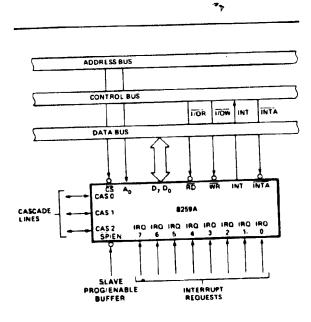

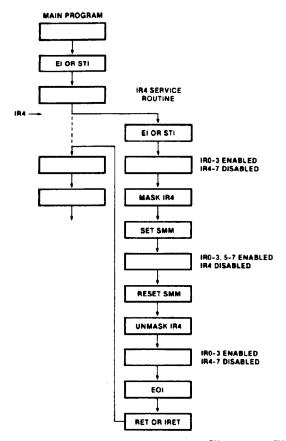

The primary function of the MPX is to assist the bus CPU in the servicing of interrupts. To facilitate the capability, the MPX data bus includes an 8259A interrupt controller (U26). The eight active low S-100 bus vectored interrupt lines (VIO\* - VI7\*) are tied through inverters (U36) to the eight active high interrupt request lines (IRO - IR7) of the 8259A. (See the 8259A application note in the appendix of this document for a complete description of the 8259A.) The resulting INT line from the 8259A is tied directly to the INTR input of the 8085 and the 8085 Interrupt Acknowledge line (INTA) is tied back to the 8259A INTA input. Thus, bus interrupts that are not masked will interrupt the 8085 directly and 8085 interrupt acknowledge cycles will accept data from the 8259A. Programming the 8259A requires two eight bit ports.

The LS138 one of eight decoder (U48) decodes the three low order address lines (AO - A2) qualified by Internal Strobe (INT STB) described above to obtain Interrupt Controller Enable (INT CTL ENA), Set Interrupt (SET INT), Interrupt Acknowledge Strobe (INTA STB), A8-15 STB and A16-23 STB making all of these facilities memory mapped within the 8000 to BFFF range. The INT CTL ENA is generated for a pair of addresses as required for programming the 8259A as described above.

An S-100 bus I/O port with a switch selectable address is decoded by the LS2521 (U41). No data is accepted by this port, however writing to the port will generate an attention signal (ATTN) to the 8085 by causing RST7.5 to be asserted.

Two methods are provided for the MPX to call the bus CPU. The SET INT signal described above may set a latch (U24). The output of the latch is buffered (U25). It may be jumpered to any of the S-100 interrupt lines, including NMI and INT. The latch is cleared by an interrupt acknowledge cycle on the S-100 bus which is decoded by (U7). The other CPU call option uses the 8085 Serial Output Data line (SOD). The buffered SOD output (U25), may also be jumpered to any of the S-100 bus interrupt lines.

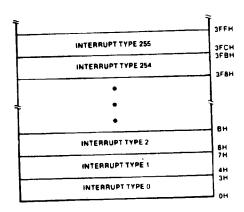

For environments where the MPX is the only interrupt controller in the system, the MPX may provide a single byte response to the CPU interrupt acknowledge cycle which results from a call by the MPX to the bus CPU. (This response would normally be a RST instruction for 8080 type CPUs, or vector information for 8086/88 or 68Q00 type processors). Another of the addresses decoded by the LS138 is INTERRUPT RESPONSE. The resulting strobe loads an eight bit latch with the contents of the data bus. The buffered latch will enable its outputs onto the S-100 DI bus during a bus interrupt acknowledge cycle if the interrupt response enable switch is on.

The MPX may also communicate with the S-100 bus as a temporary master. As the name implies, the bus CPU or permanent master will give up the bus for a short time allowing a temporary master to take control. The protocol for transfer of the bus as defined in the IEEE 696/S-100 specification must be carefully adhered to if proper operation is to be obtained. Once the bus is obtained, the temporary master will generate all of the bus signals usually provided by the CPU (with the exception of INTA cycles or releasing the bus to other temporary masters).

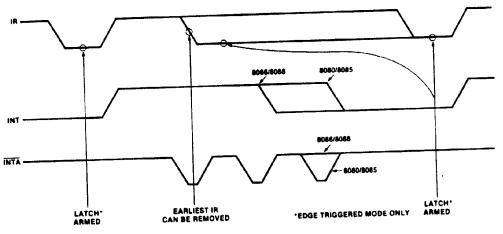

The MPX will perform a DMA cycle if either a memory address in the range of COOO - FFFF is accessed or an I/O port is accessed. Since there are no port addresses used on the MPX, all port accesses must be external. The signal External Enable (EXT ENA) is generated on EXT MEM which was decoded from the high order address lines or on I/O status and not interrupt acknowledge. EXT ENA will assert a false level on the 8085 RDY line making the 8085 hang in a wait. If EXT ENA (which was decoded entirely from status signals) has remained until the leading edge of the 8085 strobe, the flip-flop I WANT will be set. When the bus is available as determined by the signals HOLD\* and Hold Acknowledge (pHLDA) both being inactive, I WANT will set Assert Priority (APRIO). APRIO will assert HOLD\* and enable the priority arbitration logic.

Priority arbitration is handled by the three ICs U33,34 and 35. The S-100 bus DMA address bus consists of four open collector lines which are active low. To understand this process, consider the arbitration of the most significant bit DMA3\*. If a device has set APRIO and the most significant bit of its priority is a "l", it will assert DMA3\* by pulling the line low. If a different device also has APRIO set, but the most significant bit of its priority is a "O", its open collector output will be unable to pull DMA3\* high. Based on consideration of this single bit, the second device will see that some device on the bus has a priority bit of "l" where he has a "O" and will know that he is not the highest priority device on the bus at this time. The first device on the other hand will see his own address bit assexted and know that he is the highest priority device (based on consideration of this single bit only).

If a device has asserted a given bit of his priority and there are no other devices asserting a higher priority in that bit, it may enable the next most significant bit. The operation of the bits is cascaded. In a finite amount of time, the address of the highest priority device will have stabilized on the DMA address lines. The device asserting the least significant bit and not finding a higher priority bit on the least significant address line will generate the signal IMHI.