# *+INTERFACER4* **TECHNICAL MANUAL**

IEEE 696 / S-100

# **3 CHANNEL SERIAL I/O BOARD** with CENTRONICS and Universal Parallel Ports

A GODBOUT COMPANY

# TABLE OF CONTENTS

| How to Get Your Interfacer 4 Board Up and                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Running in a CompuPro System in Five Minutes                                                                                                          |

| or Less Without Reading the Manual                                                                                                                    |

|                                                                                                                                                       |

| HARDWARE SECTION                                                                                                                                      |

| About Interfacer 4                                                                                                                                    |

| Technical Overview                                                                                                                                    |

| Port Map                                                                                                                                              |

| Port Addressing                                                                                                                                       |

| User/Board Selection                                                                                                                                  |

| User Select Register                                                                                                                                  |

| Data Bus Select Switch S3                                                                                                                             |

| Relative User $0 - 2$ Swap Option $\dots \dots \dots$ |

|                                                                                                                                                       |

| Wait State Selection                                                                                                                                  |

| Cables                                                                                                                                                |

| Using Interrupts                                                                                                                                      |

| Interrupt Control Registers                                                                                                                           |

| Interrupt Status Registers                                                                                                                            |

|                                                                                                                                                       |

| SERIAL INFORMATION SECTION                                                                                                                            |

| USART Initialization                                                                                                                                  |

| USART Initialization Sequence                                                                                                                         |

| Data Registers                                                                                                                                        |

| Status Registers                                                                                                                                      |

| Mode Registers                                                                                                                                        |

| Command Register                                                                                                                                      |

| Serial Mode Jumpers                                                                                                                                   |

| Programming Jumpers                                                                                                                                   |

| RS-232C Control Lines                                                                                                                                 |

| USART Handshaking Lines                                                                                                                               |

| Synchronous Mode Clock Driver/Receivers                                                                                                               |

| Relative User 2 Synchronous Mode Jumpers                                                                                                              |

| Relative User 3 Synchronous Mode Jumpers                                                                                                              |

|                                                                                                                                                       |

| Selecting Rate of On-Board Baud Rate Generator 21                                                                                                     |

| UNIVERSAL PARALLEL CHANNEL                                                                                                                            |

|                                                                                                                                                       |

| Technical Overview                                                                                                                                    |

| I/O Address Assignment                                                                                                                                |

| Status-P Register Bit Assignment                                                                                                                      |

| Port Control Lines                                                                                                                                    |

| Input Strobe Line                                                                                                                                     |

| Input Examples                                                                                                                                        |

| Output Enable Line                                                                                                                                    |

| Attention Line                                                                                                                                        |

| Output Examples                                                                                                                                       |

.

| CENTRONICS STYLE PARALLEL CHANNEL                         |

|-----------------------------------------------------------|

| Technical Overview                                        |

| Status-C Register Bit Assignment                          |

| Control-C Register Bit Assignment                         |

| Transmit Interrupt 26                                     |

| Interface Signal Designations                             |

| Signal Differences between EPSON and CENTRONICS 26        |

| Control-C Line Jumpering                                  |

| Jumper Description                                        |

| Light Emitting Diode                                      |

|                                                           |

| Sense Dip Switch                                          |

| THEORY OF OPERATION                                       |

| S-100 Bus Drivers                                         |

| I/O Port Decode Logic                                     |

| Strobe Generation Logic                                   |

| Wait State Logic                                          |

| Interrupt Control/Status Logic                            |

|                                                           |

| RS-232/Current Loop Level Conversion Logic                |

|                                                           |

| CENTRONICS Parallel Logic                                 |

| Universal Parallel Logic                                  |

| SOFTWARE SECTION                                          |

| Sample Program Using Interfacer 4 as the CP/M Console 33  |

| CENTRONICS Test Routine                                   |

| Interfacer 4 Serial Test Routine                          |

| Interfacer 4 Serial lest Routine                          |

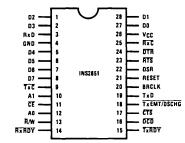

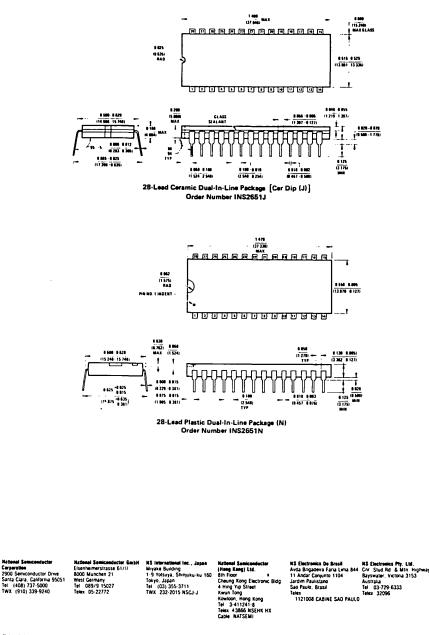

| INS2651 Programmable Communications Interface 41-47       |

|                                                           |

| HARDWARE DESCRIPTION                                      |

| Parts List                                                |

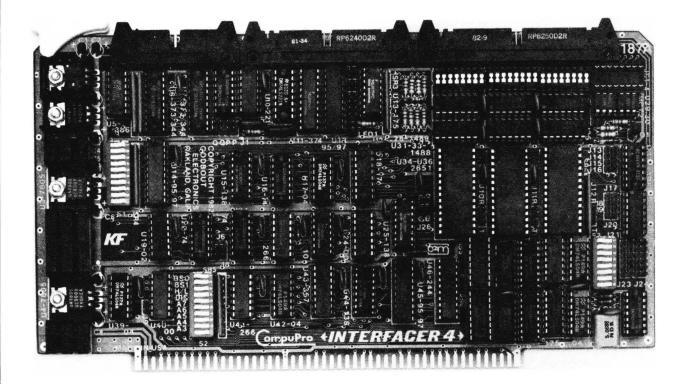

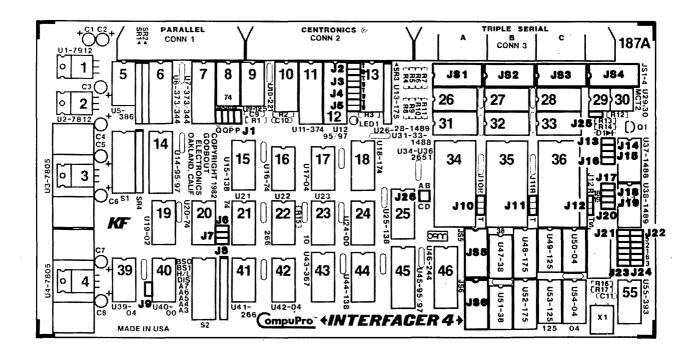

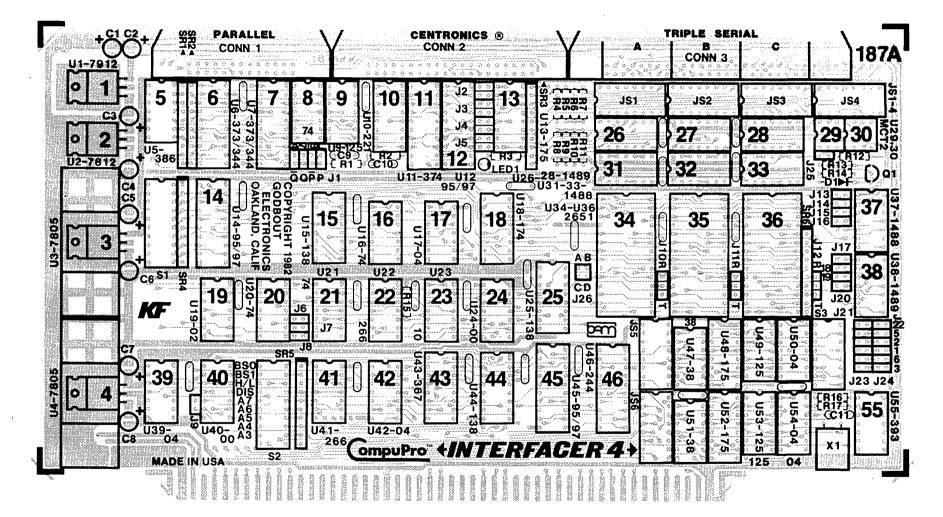

| Component Layout                                          |

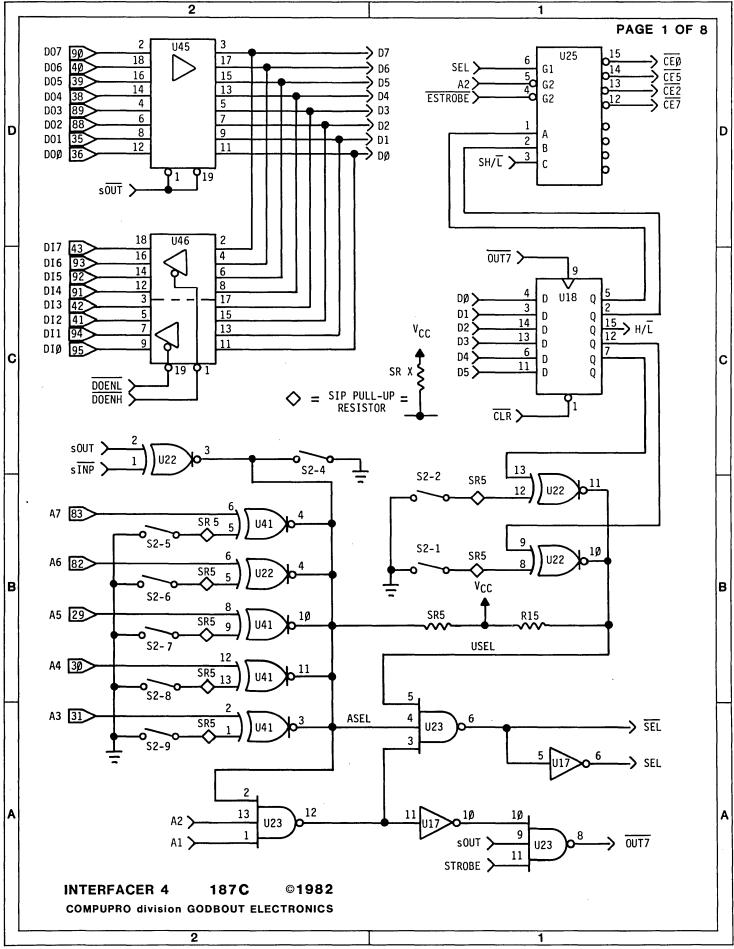

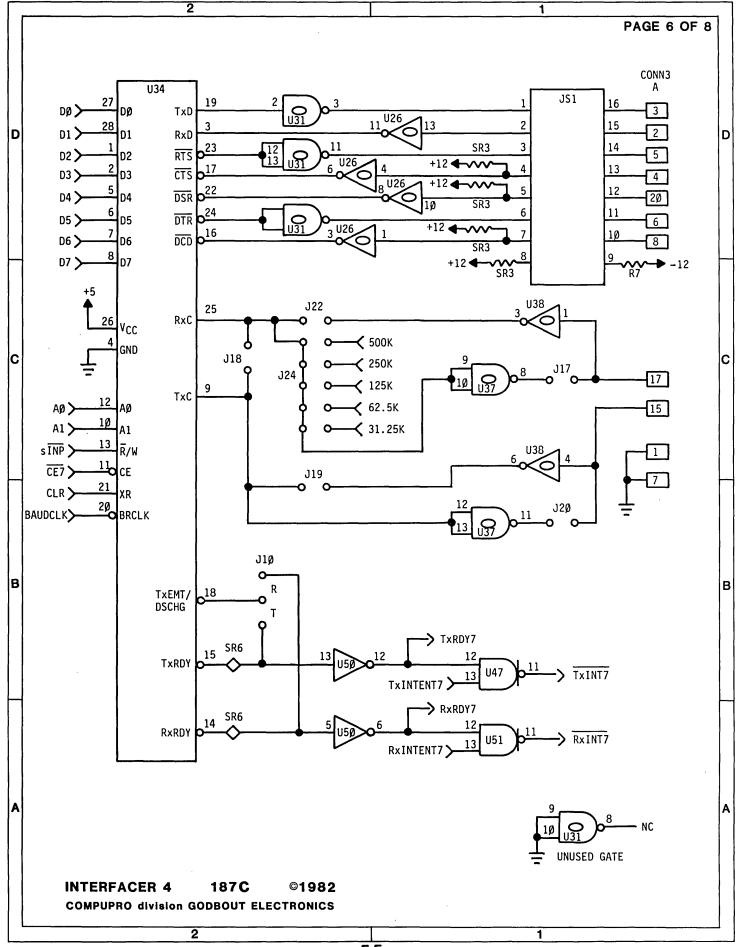

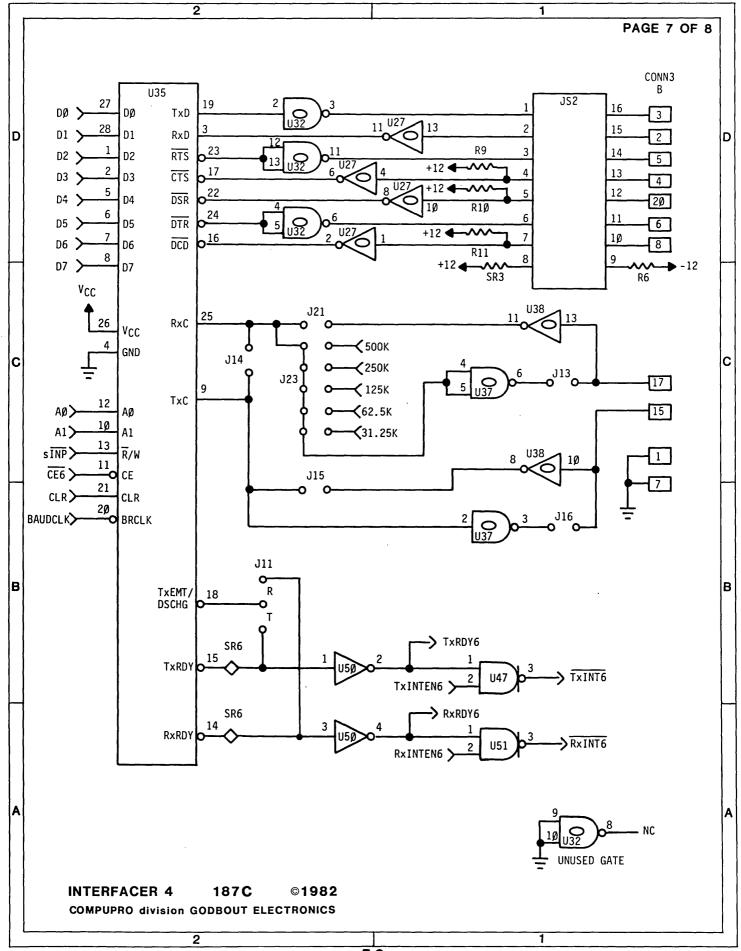

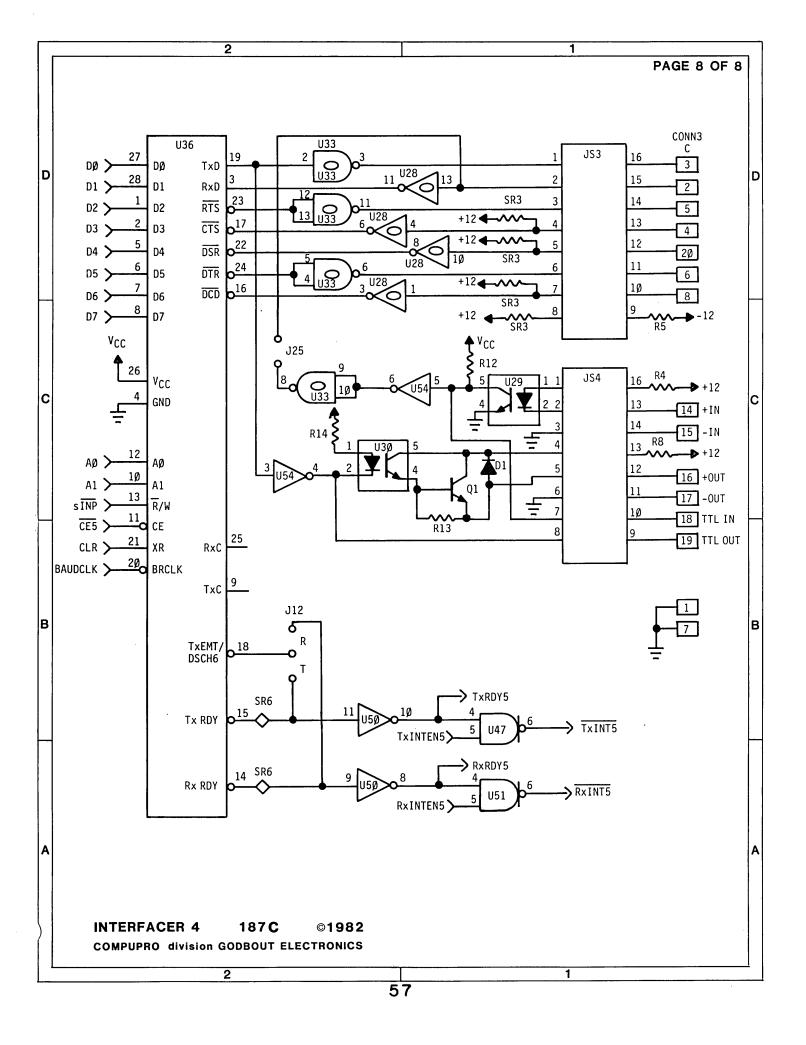

| Logic Diagram                                             |

| Jumper and Switch Index                                   |

| CUSTOMER SERVICE / LIMITED WARRANTY INFORMATION BACK PAGE |

| Document #11877                                           |

----- DISCLAIMER ------

Godbout Electronics makes no representations or warranties with respect to the contents hereof and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, Godbout Electronics reserves the right to revise this publication and to make any changes from time to time in the content hereof without obligation of Godbout Electronics to notify any person of such revision of changes.

This document was proofread with the aid of SpellGuard<sup>TM</sup> from SORCIM, Santa Clara, CA.

# How to Get Your INTERFACER 4 Board Up and Running in a CompuPro System in Five Minutes or Less Without Reading the Manual

This section allows the user to configure an **INTERFACER 4** in a standard **CompuPro** system running CP/M-80 or CP/M-86 so that the **INTERFACER 4** DRIVES the console, list and UL1 devices. If, after reading and following the directions in this section, your board appears not to function, or if you are planning to use this board in other than a standard **CompuPro** system, DON'T CALL!!! READ THE MANUAL FIRST!!!

# SWITCHES

DIP SWITCH S1

This switch is not used by either the CP/M-80 or the CP/M-86 BIOS, so we recommend that you turn all positions "OFF".

# DIP SWITCH S2

This switch controls the port addressing and board selection number for the board. It should be set as described in the table below. These settings will put the INTERFACER 4 at ports 10-17H as users 4-7.

| POSITION | LABELED | HOW TO SET IT |

|----------|---------|---------------|

| 1        | BSO     | ON            |

| 2        | BS1     | ON            |

| 3        | H/L     | OFF           |

| 4        | DIS     | OFF           |

| 5        | A7      | ON            |

| 6        | A6      | ON            |

| 7        | A5      | ON            |

| 8        | A4      | OFF           |

| 9        | A3      | ON            |

| 10       | -       | ON (NOT USED) |

# DIP SWITCH S3

This switch should be set with positions 1-4 "ON", and positions 5-8 "OFF".

# JUMPER SOCKETS

The jumper sockets should have either an 8 position shunt or an 8 position DIP header as indicated below.

JUMPER SOCKET

JS1 ----- SHUNT INSTALLED JS2 ----- SHUNT INSTALLED JS3 ----- SHUNT INSTALLED JS4 ----- HEADER INSTALLED WITH NO WIRES JS5 ----- HEADER INSTALLED WITH NO WIRES JS6 ------ HEADER INSTALLED WITH NO WIRES

# JUMPERS

The pin shunt jumpers should be installed or removed as indicated.

JUMPER CONDITION

| J1      | NO PINS NEED TO BE INSTALLED                     |

|---------|--------------------------------------------------|

| J2      | BOTTOM INSTALLED WITH EPSON / NO SHUNT OTHERWISE |

| J3      | TOP INSTALLED WITH EPSON / NO SHUNT OTHERWISE    |

| J4      | BOTTOM INTSALLED WITH BOTH EPSON AND CENTRONICS  |

| J5      | REMOVED                                          |

| J6      | INSTALLED FOR 1 WAIT STATE / REMOVED OTHERWISE   |

| J7      | INSTALLED FOR 2 WAIT STATES / REMOVED OTHERWISE  |

| J8      | INSTALLED FOR 3 WAIT STATES / REMOVED OTHERWISE  |

| J9      | NO JUMPER                                        |

| J10-J25 | REMOVED                                          |

| J26     | JUMPER A-B and C-D for the CENTRONICS CHANNEL    |

|         | as USER 4.                                       |

|         | JUMPER A-C and B-D for the CENTRONICS CHANNEL    |

|         | as USER 6.                                       |

# DIAGRAM - JUMPER AND JUMPER SOCKET LAYOUT

NOTE: Under MP/M 8-16 or an interrupt driven mode, J26 MUST be jumpered A-B and C-D.

# HARDWARE SECTION

# ABOUT INTERFACER 4

Congratulations on your decision to purchase the INTERFACER 4 multi-purpose I/O board. INTERFACER 4 has been designed to be the most flexible and highest performance I/O interface available that fully complies with the IEEE 696/S-100 bus standard. Due to its provision for ready expansion and modification as the state of the computing art improves, the S-100 bus is the professional level choice for commercial, industrial, and scientific applications. We believe that this board, along with the rest of the S-100 portion of the CompuPro family, is one of the best boards available for that bus.

The INTERFACER 4 boasts several innovative features not found on currently available I/O boards. The primary innovation stems from its full software compatibility with the INTERFACER 3 as well as the ability to intermix INTERFACER 3 and 4 boards at the same port addresses. Additional features include 3 fully programmable asynchronous serial channels, 2 of which are capable of high speed synchronous transmission and one capable of current loop operation, five RS-232 handshaking lines per channel plus bi-directional clock drivers on both the synchronous channels, a pin compatible CENTRONICS parallel interface port with the full complement of handshaking lines, a universal parallel port with 16 data and 3 handshaking lines, expandability to 32 users with eight boards using only 8 port addresses, a flexible interrupt structure with full maskability and pending status on both transmit and receive interrupts, and conservative design for operation with most CPUs operating to beyond 10 MHz. Other features standard to all CompuPro boards include thorough bypassing of all supply lines to suppress transients, on-board regulators, and low power Schottky TTL and MOS technology integrated circuits for reliable, cool operation. All this and sockets for all IC's go onto a double sided, solder masked printed circuit board with a complete component legend.

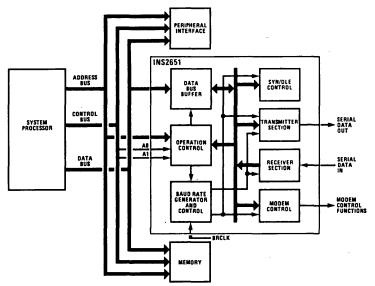

# TECHNICAL OVERVIEW

The INTERFACER 4 was designed for efficient operation in interrupt driven/ multi-user microcomputer systems as well as polled mode single user systems. Eight distinct interrupts are generated on-board by the three USARTs and two parallel ports, and these are brought out for jumpering by the user to the eight vectored interrupt lines on the S-100 bus. Since these interrupt lines are open collector, they may be configured to interrupt on any or all of the vectored interrupt lines. In addition, a transmit and receive interrupt mask port is provided for inhibiting unwanted interrupts.

The INTERFACER 4 provides multi-user operation with a minimum number of I/O ports by incorporating a user select register to activate the required I/O channel. This five bit register is used to select a particular channel, which allows up to 32 users (up to eight boards) on the same 8 port addresses. When a particular user is selected, the four USART registers associated with that specific serial channel or the parallel registers are made available for examination and alteration by the host processor or other temporary bus master. In addition, whenever a particular channel is selected, the interrupt registers on that particular board as well as the registers on another board in the same group of eight users are available for examination and alteration.

The typical sequence of operation would require all channels on the INTER-FACER 4 to be mode initialized and the interrupt mask registers set for operation. All parameters of the USART or parallel ports may be altered by selecting that particular channel and writing a new set of mode and command words to the proper registers. If running in a non-interrupt environment, the interrupt status registers may be polled and checked in roughly the same manner as a standard single channel serial board.

All three of the serial channels on the INTERFACER 4 are designed for direct connection to DATA TERMINAL EQUIPMENT (DTE) or DATA COMMUNICATION EQUIPMENT (DCE) in asynchronous mode without alteration of the cables. This allows direct connection to all types of RS-232 equipment including modems. In addition, two channels are capable of high speed synchronous operation using internal or external clocks and one channel may be connected to current loop devices.

The CENTRONICS parallel channel was designed for direct connection to printers using standard ribbon cable connectors. In addition, all handshaking lines have been implemented for maximum flexibility and ease of interfacing.

### PORT MAP

The INTERFACER 4 interface uses a block of eight port addresses for communication between it and the host processor. The address of the first port is switch selectable to any address which is a multiple of eight. The ports will be referred to as RELATIVE PORTS 0 - 7.

| RELATIVE PORT | FUNCTION                                                                                           |

|---------------|----------------------------------------------------------------------------------------------------|

| 0             | USART / CENTRONICS / DIPSWITCH DATA-C Register (R/W)                                               |

| 1             | USART / CENTRONICS STATUS-C Register (R)<br>SYN1/SYN2/DLE Register / CENTRONICS CONTROL-C Reg. (W) |

| 2             | USART Mode Register / Parallel DATA-P Register (R/W)                                               |

| 3             | USART Command Register / Parallel STATUS-P Register (R/W)                                          |

| 4             | Transmit Interrupt Status Register(R)Transmit Interrupt Mask Register(W)                           |

| 5             | Receive Interrupt Status Register(R)Receive Interrupt Mask Register(W)                             |

| 6             | Not used                                                                                           |

| 7             | User Select Register (write only)                                                                  |

# PORT ADDRESSING

DIP switch S2, positions 4 thru 9 are used to select the base address of the eight port block in a binary fashion as shown in the following table:

8

**EXAMPLE:** To address this board at addresses 10H thru 17H for the CompuPro CP/M-80 or CP/M-86 operating system or the Phase 1 OASIS operating system, position 4 and 8 would be "OFF" and positions 5 thru 7 and positions 9 would be "ON".

# USER/BOARD SELECTION

To select a particular channel and to select which board that channel will be on (when running more than 4 users), requires the use of the User Select Port and three board select switches. The five bit User Select Register determines which of 32 possible users will be selected at a particular time. The two board select switches (S2-1 and S2-2) determine whether a board will respond to users 0 thru 7, 8 thru 15, 16 thru 23, and 24 thru 31 and the HIGH/LOW select switch (S2-3) determines whether the board is the high or low 4 users in a particular block of eight. A particular user (0-31) is selected by outputting the five bit number that represents that user. The diagram shown below describes the relation between the board select switches and the User Select Register.

# USER SELECT REGISTER

| NAME | FUNCTION                  |

|------|---------------------------|

|      |                           |

| US0  | USER SELECT 0 (LSB)       |

| US1  | USER SELECT 1             |

| H/LS | HIGH/LOW SELECT           |

| BSO  | BOARD SELECT O (LSB)      |

| BS1  | BOARD SELECT 1 (MSB)      |

|      | NOT USED                  |

|      | NOT USED                  |

|      | NOT USED                  |

|      | USO<br>US1<br>H/LS<br>BSO |

Since each INTERFACER 4 will support 4 users, we will refer to these 4 as RELATIVE USERS 0-3. These 4 ports are physically configured with RELATIVE USER 0 as the CENTRONICS and Universal Parallel ports, RELATIVE USER 1 as the far right serial channel with current loop capabilities (CONN 3 C), RELATIVE USER 2 is the middle channel (CONN 3 C), and RELATIVE USER 3 as the far left channel (CONN 3 A).

To determine the EXACT USER number, the RELATIVE USER number must be added to the USER OFFSET number. The RELATIVE USER number corresponds to the 2 bits above called USER SELECT 0-1, and the USER OFFSET number corresponds to the 3 bits above called BOARD SELECT 0 and 1, and HIGH/LOW SELECT. These 5 bits determine the exact user number.

9

|       |        | RELA     | TIVE   |        |         |             |

|-------|--------|----------|--------|--------|---------|-------------|

| US1   | . USO  | USER     | NUMBER | STAND  | ARD COI | NFIGURATION |

|       |        |          |        |        |         |             |

| 0     | 0      | US       | ER O   | CENTR  | ONICS , | / PARALLEL  |

| 0     | 1      | US       | ER 1   | RIGHT  | SERIAI  | L CHANNEL   |

| 1     | 0      | US       | ER 2   | MIDDL  | E SERIA | AL CHANNEL  |

| 1     | 1      | US       | ER 3   | LEFT   | SERIAL  | CHANNEL     |

|       |        |          |        |        |         |             |

|       |        |          |        |        |         |             |

| BOARD | SELECT | SWITCHES | BOARD  | SELECT | BITS    | USER        |

| S2-3  | s2-2   | S2-1     | H/LS   | BS1    | BSO     | OFFSET      |

|       |        |          |        |        |         |             |

| ON    | ON     | ON       | 0      | 0      | 0       | 0           |

| OFF   | ON     | ON       | 1      | 0      | 0       | 4           |

| ON    | ON     | OFF      | 0      | 0      | 1       | 8           |

| OFF   | ON     | OFF      | 1      | 0      | 1       | 12          |

| ON    | OFF    | ON       | 0      | 1      | 0       | 16          |

| OFF   | OFF    | ON       | 1      | 1      | 0       | 20          |

| ON    | OFF    | OFF      | 0      | 1      | 1       | 24          |

| OFF   | OFF    | OFF      | 1      | 1      | 1       | 28          |

|       |        |          |        |        |         |             |

# DATA BUS SELECT SWITCH S3

Switch S3 is used to steer either the high (D4-D7) or the low (D0-D3) nibble of status/control information to and from the interrupt logic on the INTERFACER 4. This switch was designed in to provide software compatibility with the INTERFACER 3 board.

When the INTERFACER 4 is addressed as EXACT USERS 0-3 + N, (where N is 0, 8, 16, or 24) we would like the low nibble (D0-D3) of status and control information to be used. This would require switch S3 to have positions 1-4 "OFF" and positions 5-8 "ON".

When the INTERFACER 4 is addressed as EXACT USERS 4-7 + N, (where N is 0, 8, 16, or 24) we would like the high nibble (D4-D7) of status and control information to be used. This would require switch S3 to have positions 1-4 "ON" and positions 5-8 "OFF".

**NOTE!:** SETTING SWITCH S3 DIFFERENTLY THAN DESCRIBED ABOVE WILL CAUSE IMPROPER BOARD OPERATION AND POSSIBLE BOARD DAMAGE!

**EXAMPLE:** To address the INTERFACER 4 to respond to EXACT USERS 4 thru 7 (the CompuPro standard), switches S2-1 and S2-2 would be "ON", and S2-3 would be "OFF". To select a particular user in the group from 4 to 7, BS1 (D4) and BSO (D3) of the User Select Register must be "O", and H/LS (D2) must be "1" for the board to respond. Switch S3 must have positions 1-4 "ON" and 5-8 "OFF". To select EXACT USER 5, a O5H must be sent to the USER SELECT REGISTER.

**EXAMPLE:** To address the INTERFACER 4 to respond to users 16 thru 19, switch S2-1 and S2-3 would be "ON", and switch S2-2 would be "OFF". Switch S3 must have positions 1-4 "OFF" and 5-8 "ON". To select a particular user in the group from 16 to 19, BS1 must be a "1", BS0 must be "0", and H/LS must be a "0" for the board to respond. To select EXACT USER 18, a 12H must be sent to the USER SELECT REGISTER.

# RELATIVE USER 0 - 2 SWAP OPTION

The INTERFACER 4 may be configured so that RELATIVE USERS 0 and 2 may be swapped by re-jumpering J26. This will configure the CENTRONICS and UNIVERSAL Parallel channels as RELATIVE USER 2 instead of 0, and the middle serial channel as RELATIVE USER 0 instead of 2. This option allows EXACT USER 6 to be either a serial channel or the CENTRONICS channel for compatibility with the standard CompuPro CP/M BIOS. (This allows the LPT LIST device to be either serial or parallel without changing the BIOS.)

The standard configuration has "A" connected to "B", and "C" connected to "D" on J26. This provides the CENTRONICS as RELATIVE USER "O". To swap this, jumper "A" to "C", and "B" to "D" on J26, and the CENTRONICS channel will be RELATIVE USER 2 and the middle serial channel will be RELATIVE USER 0.

# WAIT STATE SELECTION

The INTERFACER 4 was designed to run in very fast microcomputer systems by allowing up to three wait states to be added when accessing the USART/PARALLEL registers. Since the user select and interrupt control registers are capable of higher speed operation than the USART registers, no wait states are inserted even when they are enabled on the board.

The 3 sets of vertical pins (J6, J7, and J8) control the enabling of one, two, or three wait states. With the black pin shunt on J6, one wait state will be inserted. With the pin shunt on J7, two wait states will be inserted. With the pin shunt on J8, three wait states will be inserted. If the pin shunt is left removed, no wait states will be inserted.

**NOTE:** If multiple INTERFACER 4 boards are inserted, they should be set to the same number of wait states.

# CABLES

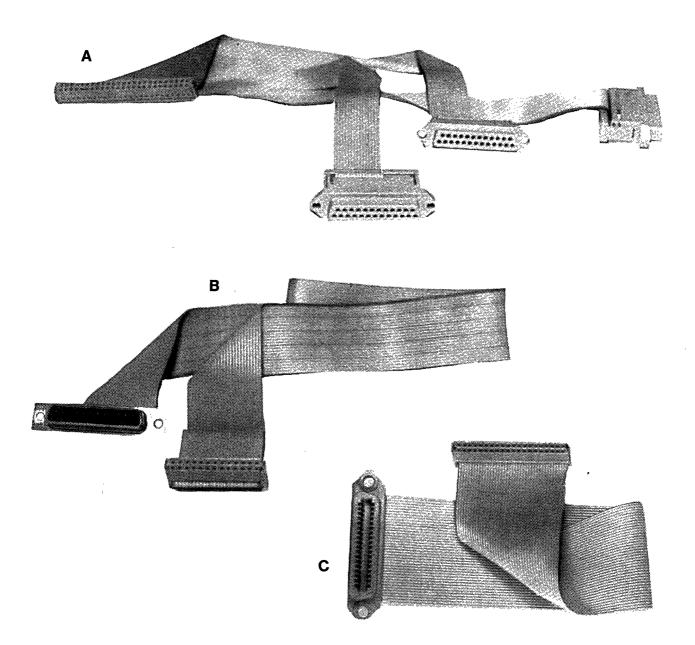

The INTERFACER 4 is designed to use 3 different cable assemblies. The serial channels use a custom 50 conductor cable that splits into three DB-25S connectors. The Universal Parallel channel uses a standard 26 conductor cable identical to those used on the INTERFACER 1 and INTERFACER 2, and the CENTRONICS Parallel channel uses a custom 40 pin cable that mates to a 36 pin "D" Shell connector for interfacing to the printer.

The serial channels (CONN 3, 50 pin connector on the far right) use a custom 3 user cable (see photo A page 12). This cable consists of a female 50 pin insulation displacement connector that splits into thirds and connects to three female DB-25 connectors. The actual cable has positions 1-16 (pin 1 on the far left side of the connector) on the first DB-25, positions 17-32 on the second DB-25, and positions 33-50 on the third DB-25. NOTE: The pin numbers on the circuit diagram show the pin numbers on the DB-25 connector and not the 50 pin connector.

The Universal Parallel channel (CONN 1, 26 pin connector on the far left) uses the CompuPro standard RS-232 I/O cables (see photo B page 12). This cable consists of a female 26 pin insulation displacement connector that mates to a

female DB-25 (the 26th conductor is not used). NOTE: The pin numbers on the circuit diagram show the pin numbers on the DB-25 connector and not the 26 pin connector.

The CENTRONICS Parallel channel (CONN 2, 40 pin connector in the middle of the board) uses another custom cable (see photo C page 12). This cable consists of a 40 pin female transition connector that mates with a 36 pin female "D" shell connector identical to those on the back of CENTRONICS interface printers. **NOTE:** The pin numbers on the circuit diagram show the pin numbers on the D-36 connector and not the 40 pin connector, and that pin 1 of the 40 pin connector does not correspond to pin 1 of the D-36 connector. If the user wishes to make this cable, the 36 conductors from the D-36 connector should be centered in the 40 pin connector, with 2 unused pins on each edge.

### USING INTERRUPTS

The INTERFACER 4 has a simple but elegant interrupt structure that allows considerable flexibility. Each USART generates both a transmit and receive interrupt. The CENTRONICS Channel generates an interrupt upon receiving an ACKNOWLEDGE from the printer, and the Universal Parallel channel generates an interrupt after being STROBED by an external device for a total of 8 distinct interrupts for the board. A transmit interrupt indicates that the USART or the CENTRONICS transmit register is empty and it is ready to accept a character. A receive interrupt indicates that data is available from the receiver data register on either the USART or the Universal Parallel channel. Each of these interrupts may be masked "OFF" or "ON" by altering the INTERRUPT CONTROL REGISTERS as described below. Each of these interrupts are open collector, and may be individually tied to any of the 8 vectored interrupt lines (VIO-VI7). The status of each interrupt line may be sampled by reading the INTERRUPT STATUS REGISTERS as described below.

Since each of the 8 interrupts generated on the INTERFACER 4 may be tied to any of the 8 vectored lines, almost any type of priority scheme may implemented. All transmit interrupts are brought out twice on one side of jumper socket JS5, and all receive interrupts are brought out twice on one side of jumper socket JS6. On the opposite side of each socket, each of the 8 vectored interrupt lines are brought out. By using the provided headers, any USART interrupt may be connected to any VI line. The pin-out of JS5 and JS6 are shown below.

| INTERRUPT | JS5  | VI LINE | <b>JS6</b> | INTERRUPT |

|-----------|------|---------|------------|-----------|

| TxINT 0   | 9 8  | VIO     | 8 9        | RxINT O   |

| TxINT 1   | 10 7 | VI1     | 7 10       | RxINT 1   |

| TxINT 2   | 11 6 | VI2     | 6 11       | RxINT 2   |

| TxINT 3   | 12 5 | VI3     | 5 12       | RxINT 3   |

| TxINT 0   | 13 4 | VI4     | 4 13       | RxINT O   |

| TxINT 1   | 14 3 | VI5     | 3 14       | RxINT 1   |

| TxINT 2   | 15 2 | VI6     | 2 15       | RxINT 2   |

| TxINT 3   | 16 1 | VI7     | 1 16       | RxINT 3   |

|           | L    | l l     |            |           |

**EXAMPLE:** If we wish to generate an interrupt on vectored interrupt line VI3 when data becomes available from RELATIVE USER 3, a wire should be soldered between pins 5 and 12 of JS6.

**EXAMPLE:** If we wish to generate an interrupt on vectored interrupt line VI6 when data becomes available from RELATIVE USERS 0, 1, 2, and 3, a wire should be soldered to connect pins 1, 13,14,15, and 16 of JS6.

**EXAMPLE:** If we wish to generate an interrupt on vectored interrupt line VIO when RELATIVE USER 2 is ready to accept a character, a wire should be soldered to connect pins 8 and 11 of JS5.

All serial channels are capable of generating a third interrupt called TxEMT/DSCHG\*. This interrupt occurs when the transmitter has completed serialization of the last character loaded or a change has occurred in the state of the DSR or DCD RS-232 status lines. Additional information on this line may be found in the 2651 data sheet in this manual. The TxEMT/DSCHG\* output from the 2651 may be jumpered to generate either a transmit or receive interrupt. Due to the wire-OR capability of the interrupt outputs from the 2651, when jumpered, the transmit interrupt will become TxRDY OR TxEMT/DSCHG\* or the receive interrupt will become RxRDY OR TxRDY/DSCHG\*. Therefore, when jumpered, the user must check the status register to determine what condition caused the interrupt.

The following table will demonstrate where to install the shorting plug to generate the appropriate interrupt.

| CHANNEL | TO CAUSE A TXEMT/DSCHG | INTERRUPT ON THE: |

|---------|------------------------|-------------------|

| NUMBER  | TXRDY LINE             | RxRDY LINE        |

| 1       | INSTALL J10T           | INSTALL J10R      |

| 2       | INSTALL J11T           | INSTALL J11R      |

| 3       | INSTALL J12T           | INSTALL J12R      |

# INTERRUPT CONTROL REGISTERS

Two registers are provided for individually masking the transmit and receive interrupts from the bus. On power-up or reset, all interrupts are disabled on the INTERFACER 4. Alteration of the interrupt registers may be accomplished in groups of eight users for compatibility with the INTERFACER 4. To gain access to these registers, a user channel must be enabled in the particular group of 8 users. (You cannot alter any interrupt register on a pair of boards set for users 0 thru 7 unless you have selected one of those 8 users)

If an INTERFACER 4 is installed in a system where it is selected as EXACT USERS 0-3 + "N", where "N" is 0, 8, 16, or 24 (i.e. users 0-3, 8-11, etc.), a Transmit or Receive interrupt may be enabled by outputting a "1" to the proper bit of the appropriate register. The registers are configured so that Data Bit 0 will mask RELATIVE USER 0, D1 will mask RELATIVE USER 1, D2 will mask RELATIVE USER 2, and D3 will mask RELATIVE USER 3.

If an INTERFACER 4 is installed in a system where it is selected as EXACT USERS 4-7 + "N", where "N" is 0, 8, 16, or 24 (i.e. users 4-7, 12-15, etc.), a Transmit or Receive interrupt may be enabled by outputting a "1" to the proper bit of the appropriate register. The registers are configured so that Data Bit 4 will mask RELATIVE USER 4, D5 will mask RELATIVE USER 5, D6 will mask RELATIVE USER 6, and D7 will mask RELATIVE USER 7. This is true for both the Transmit Interrupt Control Register (relative port 4) and the Receive Interrupt Control Register (relative port 5).

**EXAMPLE:** To enable all Transmit Interrupts on a particular INTERFACER 4, you should send to relative port 4 either a OFH if the board is selected as a 0-3 group or send a OFOH if the board is selected as a 4-7 group.

**EXAMPLE:** To enable the Transmit Interrupt on relative users 1, 4 and 6 in a pair of INTERFACER 4 boards configured as a group of eight users, you should send a 52H to relative port 4.

**EXAMPLE:** To disable all Receive Interrupts on a particular INTERFACER 4 selected as a 4-7 group, you should send a OFH to relative port 5.

**EXAMPLE:** To enable the Receive Interrupt on relative users 2, 3 and 7 in a pair of INTERFACER 4 boards, you should send a 8CH to relative port 5.

# INTERRUPT STATUS REGISTERS

Two registers are provided for checking the status of pending transmit and receive interrupts. To gain access to these registers, a user channel must be enabled on the particular board or pair of boards in a group of eight users to be altered. The INTERFACER 4 board has the intelligence to allow you to read the interrupt status from a pair of boards simultaneously. (You cannot read any interrupt register on a pair of boards set for users 0 thru 7 unless you have selected one of those 8 users).

If a Transmit or Receive interrupt is pending, a "1" will be present in the proper bit of the status register. The registers are configured so that Data Bit 0 contains the status of EXACT USER 0+N, Dl contains the status of EXACT USER 1+N, and so on with D7 containing the status of EXACT USER 7+N, where N is 0, 8, 16, or 24. This is true for both the Transmit Interrupt Status Register (relative port 4) and the Receive Interrupt Status Register (relative port 5). Remember, these status registers are read only! Writing into these registers will alter the Interrupt Control Mask. In addition, the status of a channel's interrupts are available even if those interrupts are masked "OFF". The Interrupt Control Register does not affect the reading of the status from a register.

**EXAMPLE:** If all Transmit Interrupts on a particular pair of INTERFACER 4 boards are asserted, you will read a OFFH at relative port 4.

**EXAMPLE:** If Transmit Interrupts are pending on EXACT USERS 1, 4 and 6 (+N), you will read a 52H from relative port 4.

**EXAMPLE:** If there are no Receive Interrupts pending on a single INTERFACER 4 in a system, (no data available), you will read either a OFOH from relative port 5 if the board is set for EXACT USERS 0-3 (+N), or you will read a OFH if the board is set for EXACT USERS 4-7 (+N). The reason for the nibble of value "F" is the processor will read binary "1"s from non-driven lines.

**EXAMPLE:** If Receive Interrupts are pending on EXACT USERS 2 and 3 (+N) with a single INTERFACER 4 in the system, you will read a OFCH from relative port 5.

# SERIAL INFORMATION SECTION

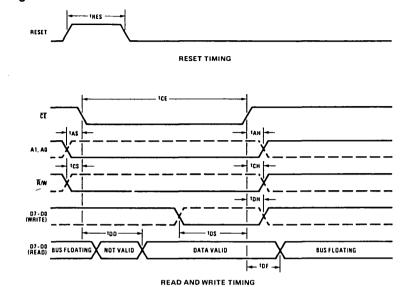

# USART INITIALIZATION

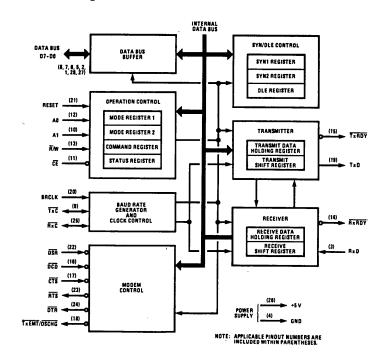

The serial channels on the INTERFACER 4 are implemented with a 2651 type USART from either National Semiconductor or Signetics. Several of the USART parameters and channel control functions are programmed by writing into or reading from certain registers in the 2651. They are:

- 1. The baud rate.

- 2. The word length.

- 3. Whether or not a parity bit is generated.

- 4. Whether the parity is even or odd (if generated).

- 5. The number of stop bits.

- 6. Enabling and disabling the transmitter and receiver.

- 7. Setting and testing the RS-232 handshake lines.

- 8. Synchronous or asynchronous operation.

In addition, the normal status indication and data transfer functions are also handled through the USART's registers.

A table of the various registers and where they appear in the I/O port map is shown in a previous section and in the following tables.

"READ" or "INPUT" Ports

| Relative Port Address | UART Register Function                  |

|-----------------------|-----------------------------------------|

| 00 hex                | Data Port, read received data.          |

| 01 hex                | Status Port, read UART status info.     |

| 02 hex                | Mode Registers, read current UART mode. |

| 03 hex                | Command Register, read current command. |

"WRITE" or "OUTPUT" Ports

| Relative Port Address | UART Register Function                    |

|-----------------------|-------------------------------------------|

| 00 hex                | Data port, write transmit data.           |

| 01 hex                | SYN1/SYN2/DLE register, write sync bytes. |

| 02 hex                | Mode registers, write mode bytes.         |

| 03 hex                | Command register, write command byte.     |

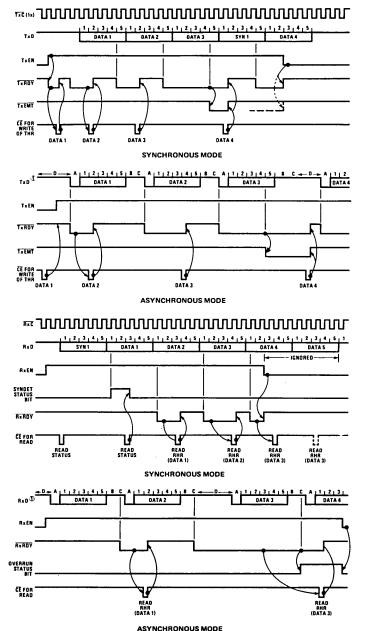

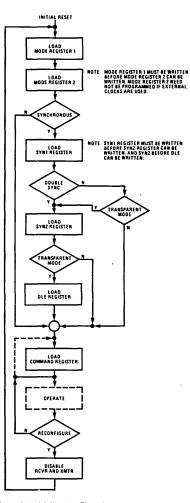

# USART INITIALIZATION SEQUENCE

When bringing up the USART in asynchronous mode, the following sequence of events must occur:

- 1. Set Mode Register 1

- 2. Set Mode Register 2

- 3. Set Command Register

- 4. Begin normal USART operation

When bringing up the USART in transparent synchronous mode, all of the following sequence of events must occur. If bringing up the USART in non-transparent synchronous mode, step 5 may be omitted.

Set Mode Register 1

Set Mode Register 2

Set SYN1 Register

Set SYN2 Register

Set DLE Register

Set Command Register

Begin normal USART operation

# DATA REGISTERS

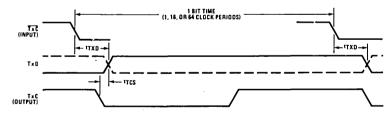

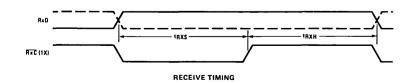

The USART data registers are straight-forward in their operation. You write a byte to the data register when you want to transmit that byte to an external serial device and you read the byte in the data register to receive a byte from an external serial device. The USART will automatically add the proper start and stop bits when transmitting and will remove them when receiving.

1

# STATUS REGISTER

. . .

The status register is used to determine the current state of the USART. Each bit of the status register has a different meaning depending on whether it is high or low. (High means a logic one or high level and low means a logic zero or low level.) The following table describes the meaning of the status bits:

STATUS REGISTER FORMAT

|                                                                          | BIT NUMBERS                                                                   |                                                                                                                   |                                              |                                                                                                                                         |                                                                                                         |                                                                                                         |                                                                                                        |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| SR-7                                                                     | SR-6                                                                          | SR-5                                                                                                              | SR-4                                         | SR-3                                                                                                                                    | SR-2                                                                                                    | SR-1                                                                                                    | SR-0                                                                                                   |

| DATA SET<br>READY<br>0 - OSR INPUT<br>IS HIGH<br>1 - OSR INPUT<br>IS LOW | DATA CARRIER<br>DETECT<br>0 + DCD INPUT<br>IS HIGH<br>1 + DCD INPUT<br>IS LOW | FE/SYN DETECT<br>ASYN:<br>0 - NORMAL<br>1 - FRAMING ERROR<br>SYNC:<br>0 - NORMAL<br>1 - SYN CHARACTER<br>DETECTED | OVERUN<br>0 - NORMAL<br>1 - OVERRUN<br>ERROR | PE/DLE DETECT<br>ASYNC:<br>D = NORMAL<br>1 = PARITY ERROR<br>SYNC:<br>D = NORMAL<br>1 = PARITY ERROR<br>OR DLE<br>CHARACTER<br>RECEIVED | T x EMT/DSCHG<br>0 = NORMAL<br>1 = CHANGE IN<br>DSR OR DCD OR<br>TRANSMIT SHIFT<br>REGISTER IS<br>EMPTY | Ax RDY<br>0 - RECEIVE<br>HOLDING<br>REGISTER<br>EMPTY<br>1 - RECEIVE<br>HOLDING<br>REGISTER<br>HAS DATA | T x RDY<br>0 - TRANSMIT<br>HOLDING<br>REGISTER<br>BUSY<br>1 - TRANSMIT<br>HOLDING<br>REGISTER<br>EMPTY |

### STATUS REGISTER FORMAT TABLE

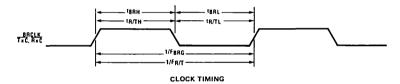

NOTE 1. BAUD RATE FACTOR IN ASYNCHRONOUS MODE APPLIES ONLY IF EXTERNAL CLOCK IS SELECTED. FACTOR IS 18x IF INTERNAL CLOCK IS SELECTED.

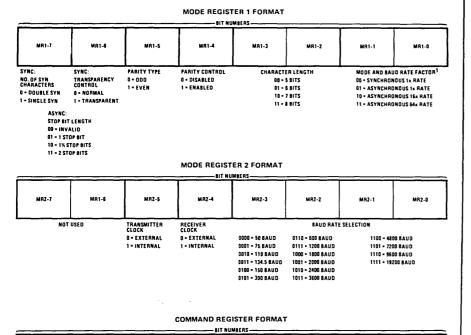

## MODE REGISTERS

When bringing up the USART, its two mode registers must be set with various bit patterns that will determine the operating modes. Although there are two registers, they occupy only one I/O port address. This is accomplished with internal sequencing logic that allows you to write the first register (Mode Register 1) and then the second register (Mode Register 2). It is important to write to Mode Register 1 first.

The meanings of the various bits in the mode registers are described in the following tables:

# MODE REGISTER 1 AND 2 FORMAT TABLES

|                                                                                                                                                                                                                                                  | 7     |                                                      | BIT NU                                            | IMBERS                                                                                                         |                                                                                                                                  |                                                                                                                                                             |                    |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|

| MR1-7                                                                                                                                                                                                                                            | MR1-6 | MR1-5                                                | MR1-4                                             | MR1-3                                                                                                          | MR1-2                                                                                                                            | MR1-1                                                                                                                                                       | MR1-0              |  |

| SYNC: SYNC <sup>.</sup><br>NO. OF SYN TRANSPARENCY<br>CHARACTERS CONTROL<br>0 - DOUBLE SYN 0 - NORMAL<br>1 - SINGLE SYN 1 - TRANSPARENT<br>ASYNC:<br>STOP BIT LENGTH<br>00 - INVALID<br>01 - 1 STOP BIT<br>10 - 1% STOP BITS<br>11 - 2 STOP BITS |       | PARITY TYPE<br>0 - ODD<br>1 - EVEN                   | PARITY CONTROL<br>0 • DISABLED<br>1 • ENABLED     | CHARACTER LENGTH<br>00 = 5 BITS<br>01 = 6 BITS<br>10 = 7 BITS<br>11 = 8 BITS                                   |                                                                                                                                  | MODE AND BAUD RATE FACTOR <sup>1</sup><br>00 - Synchronous 1x Rate<br>01 - Asynchronous 1x Rate<br>10 - Asynchronous 16x Rate<br>11 - Asynchronous 64x Rate |                    |  |

|                                                                                                                                                                                                                                                  |       |                                                      |                                                   | ER 2 FORMAT                                                                                                    | c                                                                                                                                |                                                                                                                                                             |                    |  |

| MR2-7                                                                                                                                                                                                                                            | MR1-6 | MR2-5                                                | MR2-4                                             | MR2-3                                                                                                          | MR2-2                                                                                                                            | MR2-1                                                                                                                                                       | MR2-0              |  |

| NOT USED                                                                                                                                                                                                                                         |       | TRANSMITTER<br>CLOCK<br>0 - EXTERNAL<br>1 - INTERNAL | RECEIVER<br>CLOCK<br>0 - EXTERNAL<br>1 - INTERNAL | 0000 - 50 BAUD<br>0001 - 75 BAUD<br>0010 - 110 BAUD<br>0011 - 134.5 BAUD<br>0100 - 150 BAUD<br>0101 - 300 BAUD | BAUD RATE<br>0110 - 600 BAUD<br>0111 - 1200 BAUD<br>1000 - 1800 BAUD<br>1001 - 2000 BAUD<br>1010 - 2400 BAUD<br>1011 - 3600 BAUD | SELECTION<br>1100 - 48<br>1101 - 72<br>1110 - 96<br>1111 - 19                                                                                               | DO BAUD<br>Do BAUD |  |

MODE REGISTER 1 FORMAT

That completes the description of the Mode Registers. Remember that you must always write both mode registers, with Mode Register 1 first.

# COMMAND REGISTER

The Command Register is used to set the operating mode (sync or async), enable or disable the receiver and/or transmitter, force a "break" condition, reset the error flags and control the state of the RTS and DTR outputs.

# COMMAND REGISTER TABLE

|                                                                      |                                                                                                           |                                                                                     | BIT NU                                                                                                   | MBERS-                                                                                                    | •                                                         | ······································                                                  | ·····                                            |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------|

| CR-7                                                                 | CR-6                                                                                                      | CR-S                                                                                | CR-4                                                                                                     | CR-3                                                                                                      | CR-2                                                      | CR-1                                                                                    | CR-0                                             |

| 00 - NORMA<br>01 - Async<br>Echo M<br>Sync S<br>Dle St<br>10 - Local | L<br>ING MODE<br>AUTOMATIC<br>AUTOMATIC<br>NODE<br>SYN AND/OR<br>RIPPING MODE<br>LOOP BACK<br>E LOOP BACK | REQUEST TO<br>SEND<br>D - FORCES ATS<br>OUTPUT HIGH<br>1 - FORCES ATS<br>DUTPUT LOW | RESET ERROR<br>0 - NORMAL<br>1 - RESET ERROR<br>FLAG IN STATUS<br>REGISTER (FE,<br>DE, PE/DLE<br>DETECT) | ASYNC:<br>FORCE BREAK<br>0 - NORMAL<br>1 - FORCE BREAK<br>SYNC:<br>SEND DLE<br>0 - NORMAL<br>1 - SEND DLE | RECEIVE<br>CONTROL<br>(R×EN)<br>0 = DISABLE<br>1 = ENABLE | DATA TERMINAL<br>READY<br>0 - FORCES OTR<br>OUTPUT HIGH<br>1 - FORCES OTR<br>OUTPUT LOW | TRANSMIT<br>CONTROL<br>0 - DISABLE<br>1 - ENABLE |

COMMAND REGISTER FORMAT

# SERIAL MODE JUMPERS

The INTERFACER 4 board with its serial programming jumpers allows the user to adapt all three channels to all standard RS-232 pin configurations and Relative User 1 to standard current loop configurations. In RS-232 mode, these jumpers may be set so that this board operates in a "master" mode where it behaves as the Data Terminal Equipment (DTE), or it may be set so that the board operates in a "slave" mode where it behaves as the Data Communication Equipment (DCE). With almost all CRT terminals and serial interface printers, the INTERFACER 4 serial mode jumpers (JS1-JS3) must be set in the "slave" or DCE mode. When connected to a Modem, the serial mode jumpers (JS1-JS3) of the INTERFACER 4 should be set in the "master" mode as shown on the following table. In current loop mode on Relative User 1, JS3 should be removed and JS4 and J25 installed. The proper configuration of JS4 depends on whether the on-board or an off-board 20mA current source is used. The wiring of the mating DB-25 connector should have pins 14 and 15 as the + and - inputs, and 16 and 17 as the + and - outputs. For special applications, pins 18 and 19 of the DB-25 are TTL IN and OUT if pin 7 and 10, and 8 and 9 of JS4 are shorted.

### PROGRAMMING JUMPERS

SLAVE MODE, JS1-JS3: for connections to CRT terminals, printers, etc.

CURRENT LOOP - on board current source, JS4: Example TTY.

MASTER MODE, JS1-JS3: for connection to MODEMS.

CURRENT LOOP - external current source, JS4.

# **RS-232C CONTROL LINES**

The RS-232 control and data lines are defined as shown below. The EIA RS-232 standard defines a signal line at greater than +3V (+12V typical) to be "SPACING" and a signal line at less than -3V (-12V typical) to be "MARKING".

| PIN# | CIRCUIT | DIR.       | NAME | DESCRIPTION             |

|------|---------|------------|------|-------------------------|

| 1    | AA      |            |      | PROTECTIVE GROUND       |

| 2    | BA      | TO DCE     | TxD  | TRANSMITTED DATA        |

| 3    | BB      | TO DTE     | RxD  | RECEIVED DATA           |

| 4    | CA      | TO DCE     | RTS  | REQUEST TO SEND         |

| 5    | CB      | TO DTE     | CTS  | CLEAR TO SEND           |

| 6    | CC      | TO DTE     | DSR  | DATA SET READY          |

| 7    | AB      |            |      | SIGNAL GROUND           |

| 8    | CF      | TO DTE     | DCD  | REC'D LINE SIGNAL DET.  |

| 15   | DB      | DCE SOURCE | TSET | TRANS. SIG. ELE. TIMING |

| 17   | DD      | DCE SOURCE | RSET | REC'D SIG. ELE. TIMING  |

| 20   | CD      | TO DCE     | DTR  | DATA TERMINAL READY     |

Five RS-232 handshaking signals are provided for interfacing to equipment needing these lines as shown below. Output lines may be set either "MARKING" or "SPACING" and their state may be altered by software commands as described in the USART INITIALIZATION Section under Command Register.

# USART HANDSHAKING LINES

| OUTPUT LINES | NAME | RS-232 LINE | DB25 PIN CONNECTION |

|--------------|------|-------------|---------------------|

|              | DTR  | CD          | 20 OR 6 *           |

|              | RTS  | CA          | 4 OR 5 *            |

| INPUT LINES  | NAME | RS-232 LINE | DB25 PIN CONNECTION |

|              | DSR  | CC          | 6 OR 20 *           |

|              | CTS  | CB          | 5 OR 4 *            |

|              | DCD  | CF          | 8                   |

\* NOTE: Pin numbers with no asterisk indicate the DB25 pin number when the Serial Mode Jumpers are set for "master" mode. Pin numbers with an asterisk indicate the DB25 pin number when the Serial Mode Jumpers are set for "slave" mode.

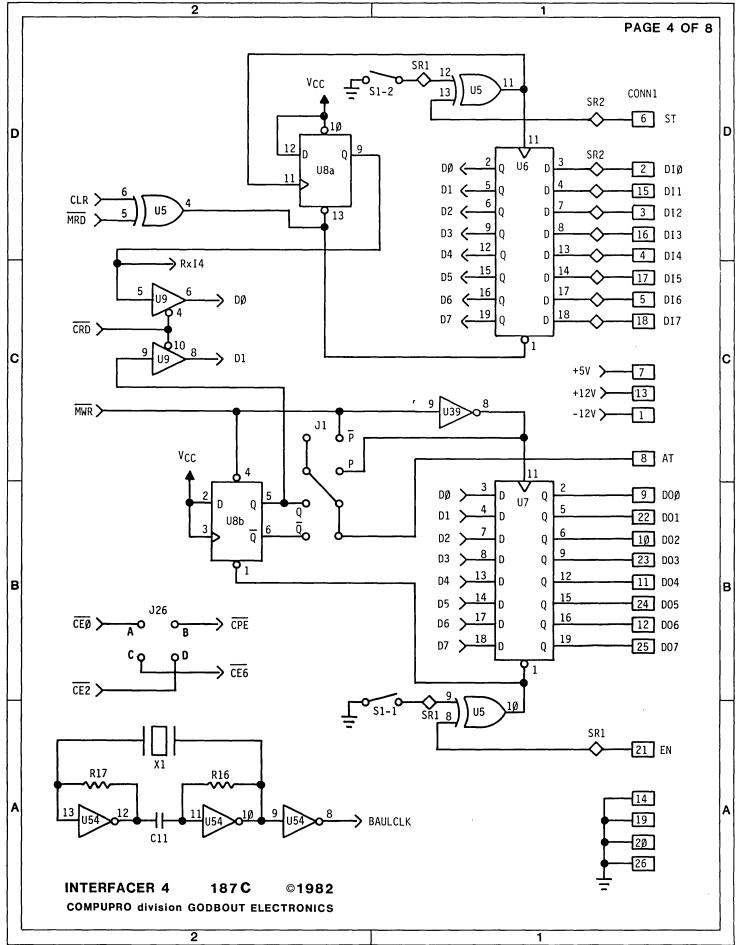

# SYNCHRONOUS MODE CLOCK DRIVER/RECEIVERS

RELATIVE CHANNELS 2 and 3 can either transmit or receive the synchronous timing element signals. The typical configuration requires that the DATA COMMUNICATION EQUIPMENT (DCE) be the source of the of the synchronous transmit and receive clocks. The INTERFACER 4 is capable of independently transmitting or receiving the sync clocks in either DCE or DTE modes.

For using either channel in a synchronous mode, there are two major options. The first option is whether or not you will be using the USART internal baud rate generator or the on-board high speed baud rate generators. The second option is whether you will be transmitting the sync clocks to the external device or receiving them from the external device. The following table will describe how each pin shunt should be set.

# **RELATIVE USER 2 SYNCHRONOUS MODE JUMPERS**

| INTERNAL BAUD RATE                                     | USE - LOW  | SPEED OPERATION       |

|--------------------------------------------------------|------------|-----------------------|

| TRANSMITTING SYNC CLOCKS                               |            | RECEIVING SYNC CLOCKS |

| INSTALL J13, J16                                       |            | INSTALL J15, J21      |

| EXTERNAL BAUD RATE                                     | USE - HIGH | SPEED OPERATION       |

| TRANSMITTING SYNC CLOCKS                               |            | RECEIVING SYNC CLOCKS |

| INSTALL J13, J14 , J16<br>INSTALL J23 FOR DESIRED RATE |            | INSTALL J15, J21      |

| RLATIVE USER 3 SYNCHRONOUS MODE JUM                    | PERS       |                       |

| INTERNAL BAUD RATE                                     |            | SPEED OPERATION       |

| TRANSMITTING SYNC CLOCKS                               |            | RECEIVING SYNC CLOCKS |

| INSTALL J17, J20                                       |            | INSTALL J19, J22      |

| EXTERNAL BAUD RATE                                     | USE - HIGH | SPEED OPERATION       |

| TRANSMITTING SYNC CLOCKS                               |            | RECEIVING SYNC CLOCKS |

| و ب ب ب ب ب ب ب ب ب ب ب ب ب ب ب ب ب ب ب                | -          |                       |

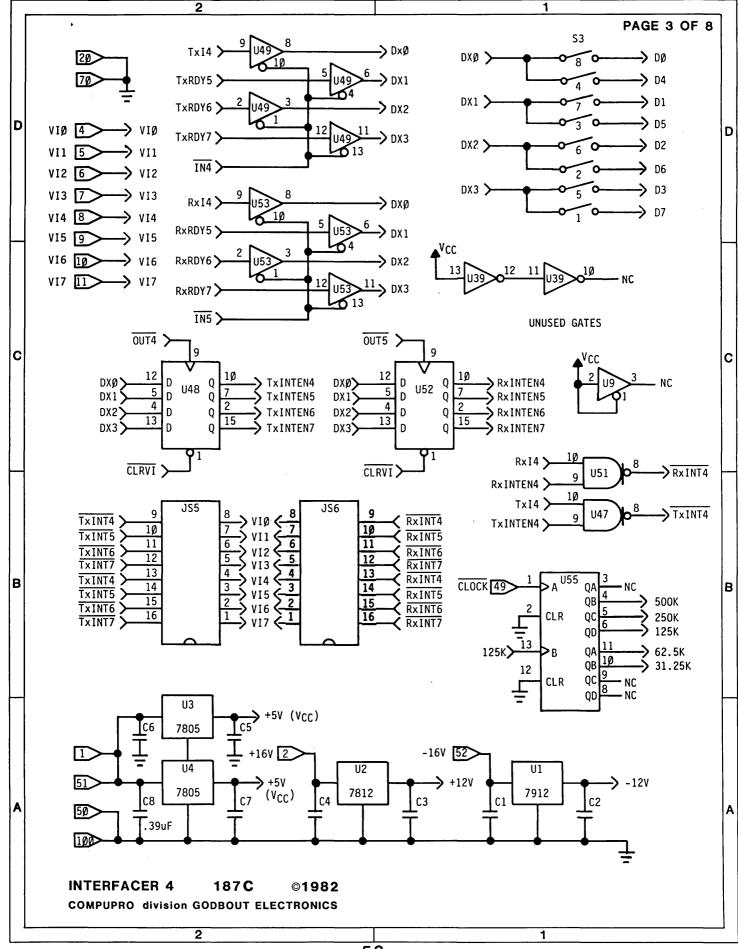

# SELECTING THE RATE OF THE ON-BOARD BAUD RATE GENERATOR

Either or both of the synchronous channels may use the on-board high speed baud rate generator for communication at rates greater than that available from the USART. The rates available on-board include 31.25K, 62.50K, 125K, 250K, and 500K baud, however, it is unlikely that 500K baud will be usable in most applications due to the slew rate limitations of the RS-232 drivers and receivers. The table below describes the jumper block that allows selection of these rates.

|        | J23 J24                     |    |

|--------|-----------------------------|----|

| J21    | *   *     *   *   J22       | 2  |

| 500К   | 5   *   *     *   *   5 500 | )K |

| 250K   | 2   *   *     *   *   2 250 | )K |

| 125K   | 1   *   *   *   *   1 12    | 5K |

| 62.5K  | 6   *   *     *   *   6 62. | 5K |

| 31.25К |                             | 5K |

For relative user 2, jumper the proper rate across on J23. For relative user 3, jumper the proper rate across on J24.

# UNIVERSAL PARALLEL CHANNEL

# TECHNICAL OVERVIEW

The UNIVERSAL PARALLEL section of the INTERFACER 4 consists of a full duplex latched parallel port for I/O data and one port for status. The use of TTL latches rather than a MOS parallel interface chip eliminates the need for mode selection and initialization, and allows the port to have strobe, attention and enable bits, an input interrupt, and 16 true data lines.

# **I/O ADDRESS ASSIGNMENT**

The UNIVERSAL PARALLEL channel on the INTERFACER 4 board is addressed as the MODE and CONTROL registers of RELATIVE USER 0. The DATA-P register of the channel is addressed at the PORT BASE + 2 (USART equivalent is the MODE register), and the STATUS-P register is addressed at PORT BASE + 3 (USART equivalent is the CONTROL register). In the STATUS-P register only data bits 0 and 1 are significant.

# STATUS-P REGISTER BIT ASSIGNMENT

Inputs to the processor from the STATUS-P register are defined as follows:

| DATA BIT          | NAME                     | SIGNAL                                       |

|-------------------|--------------------------|----------------------------------------------|

| DO<br>D1<br>D2-D7 | DAVO<br>TKNO<br>NOT USED | DATA AVAILABLE CHANNEL<br>DATA TAKEN CHANNEL |

# PORT CONTROL LINES - INPUT STROBE LINE

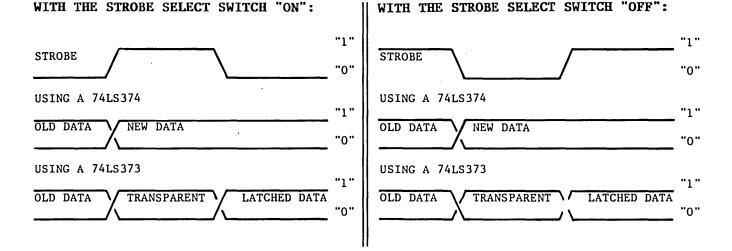

The STROBE line on the input Channel is used to latch the data into the input register when a 74LS374 or 74LS373 latch is used. This line also sets the status flag so that the processor can tell if data has been entered.

If a 74LS374 is used as the input register, a transition on the strobe line latches the data and sets the status flag. The strobe polarity select switch should be set as described below so that your data is valid during the transition. With the select switch (S1-2) ON, a low to high transition on strobe will latch the data. With the select switch OFF, a high to low transition on strobe will latch the data.

If a 74LS373 is used as the input register, the strobe line can assume two different modes. The first mode is similar to the latched mode of the 74LS374 described above except that during the strobe pulse the data is transparent through the latch to the processor. At the end of the strobe pulse, the data will be latched and stable for the processor to access. With the strobe select switch (S1-2) "ON", a positive going strobe pulse will latch the data at the end of the pulse. With the select switch "OFF", a negative going strobe pulse will latch the data at the end of the pulse. The second mode is the fully transparent mode where the data is never latched but is available for inputting at any time by the processor. This mode is useful whenever the data has no strobe bit associated with it. This mode is entered when the strobe line is left open with the strobe select switch "ON". See the table below for strobing data.

## INPUT EXAMPLES

Some examples of typical applications might include connecting a ASCII keyboard or a set of sense switches to the input Channel of the INTERFACER 4. A keyboard usually has a strobe line to indicate that it has current valid data on its lines. Therefore, using one of the 74LS374 latches would be best. The keyboard data lines would be connected accordingly to input data lines, and the strobe line would be connected, and the strobe select switch would be "ON" for a positive keyboard strobe, and "OFF" for a negative keyboard strobe. If connecting some sense switches to the input lines, a 74LS373 would be the best choice because there are usually no strobe lines associated with switches. The switches should be connected to the input lines so that they ground the inputs (no pullup resistors are needed since they are supplied on the board) and the STROBE LINE should be left floating with the strobe select switch "ON". This allows the processor to input the data from the switches at any time.

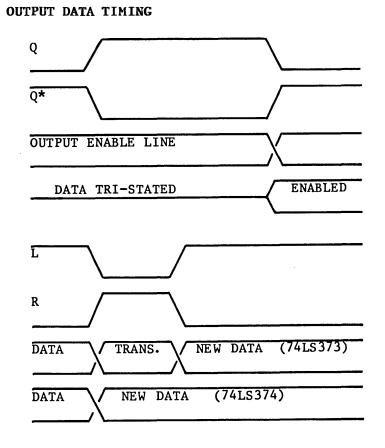

# - OUTPUT ENABLE LINE

The OUTPUT ENABLE LINE on the Channel serves two functions depending on the user's configuration. In handshaking operations, it is used to enable the output of the DATA-P register which is normally tri-stated. This line also resets the ATTENTION bit and informs the processor, through the status port, that the data has been taken from the latch. In strobed operations, the OUTPUT ENABLE LINE is used to enable the output of the register at all times. When the select switch (S1-1) is "ON", the OUTPUT ENABLE LINE must be low to enable the outputs. With the select switch "OFF", the OUTPUT ENABLE LINE must be high to enable the output.

### - ATTENTION LINE

The ATTENTION LINE is used to inform an external device that new data is now available for it. This line may be jumpered (J1) to provide any one of four different outputs. With the Common (top row of four pins) jumpered to either Q or Q\*, and the OUTPUT ENABLE LINE set so that the output of the register is Tri-Stated, then the ATTENTION LINE will go high (Q) or low (Q\*) when data is

23

strobed into the output register. When the OUTPUT ENABLE LINE level is changed to enable the data, then the ATTENTION LINE will return to its original level. In this mode, the OUTPUT ENABLE LINE is used to transfer the data out of the register and reset the attention flag. Since the level of the ATTENTION LINE may be sampled by the processor through the status port, a high speed handshaking data transfer can occur.

With the Common tied to either the "P" or the "P\*", the ATTENTION LINE becomes a positive (P) or negative (P\*) going strobe pulse with a width of the system pWR\* strobe (between 150 and 1000ns). In this mode, the state of the OUTPUT ENABLE LINE should be set so that the data is enabled at all times. This mode is best used when the external device needs the data strobed into it. See the diagrams below for the output data timing using either a 74LS373 or a 74LS374 as an output register.

# - OUTPUT EXAMPLES

Some examples of typical applications might include connecting an A to D converter or some LED's to the output lines. An A to D converter will probably require 8 data lines be connected in addition to a strobe line. In many cases, the strobe (P or P\*) connected to the ATTENTION LINE will be sufficiently long for the converter and can be connected directly with the proper polarity for correct operation. If only 7 data lines are required for the converter, then the eighth data line may be used.

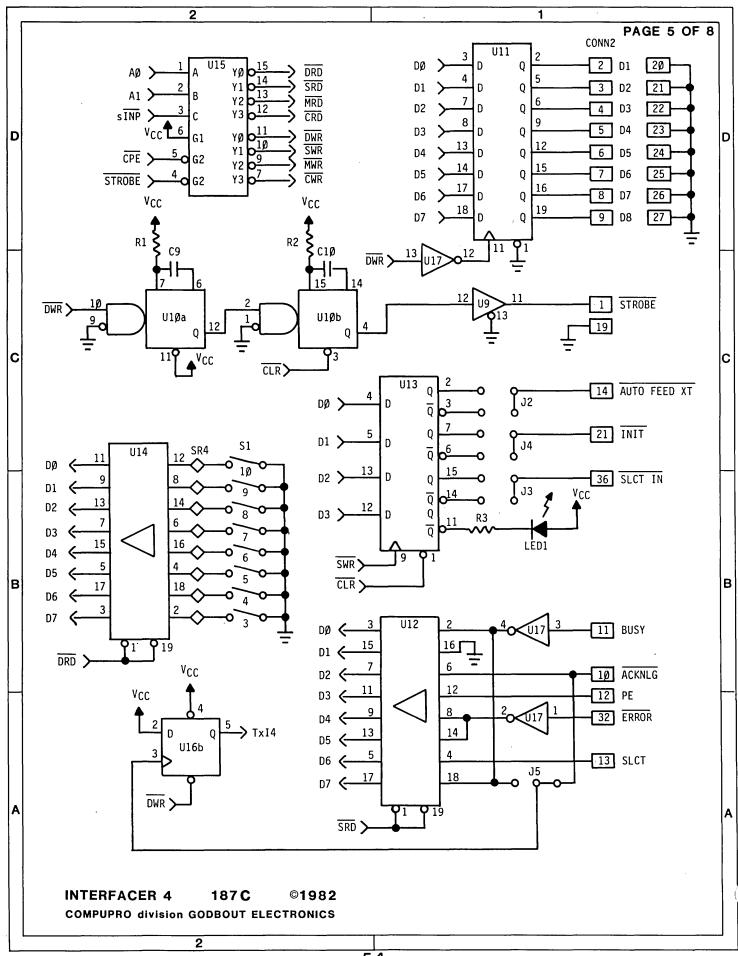

# CENTRONICS STYLE PARALLEL CHANNEL

# TECHNICAL OVERVIEW

The CENTRONICS PARALLEL section of the INTERFACER 4 consists of an 8 bit latched output port for data and a full complement of status and control lines. The output STROBE line timing conforms with the timing specifications of all known CENTRONICS interface printers, and power-up programming of the control lines allows flexible initialization procedures.

# I/O ADDRESS ASSIGNMENT

The CENTRONICS PARALLEL channel on the INTERFACER 4 board is addressed as the DATA and STATUS registers of RELATIVE USER 0. The DATA-C register of the channel is addressed at the PORT BASE + 0 and the STATUS-C / CONTROL-C register is addressed at PORT BASE + 1.

# STATUS-C REGISTER BIT ASSIGNMENT

Inputs to the processor from the STATUS-C register are defined as follows:

DATA BIT NAME SIGNAL

| D0 | PBMT     | PRINTER BUFFER EMPTY - READY FOR CHARACTER WHEN HIGH |

|----|----------|------------------------------------------------------|

| D1 | NOT USED | ALWAYS LOGIC "O"                                     |

| D2 | ACKNLG   | TRANSFER ACKNOWLEDGE - 10uS LOW PULSE                |

| D3 | PE       | PAPER ERROR - PRINTER OUT OF PAPER WHEN HIGH         |

| D4 | ERROR    | PRINTER ERROR WHEN HIGH                              |

| D5 | ERROR    | PRINTER ERROR WHEN HIGH                              |

| D6 | SLCT     | PRINTER SELECTED "ON" WHEN HIGH                      |

| D7 | BUSY*    | PRINTER BUSY WHEN LOW                                |

The status register bit assignment was designed to minimize the amount of software alteration required to use a parallel printer. As configured, the status word should be compatible with most currently available BIOS routines. With this channel selected as EXACT USER 6, it is 100% compatible with standard CompuPro software.

# CONTROL-C REGISTER BIT ASSIGNMENTS

Outputs to the CONTROL-C register from the processor are defined as follows:

| DATA BIT | NAME   | SIGNAL                                           |

|----------|--------|--------------------------------------------------|

| DO       | AFX    | AUTO FEED EXTERNAL - AUTO LINE FEED AFTER RETURN |

| D1       | INIT   | INITIALIZE – INITIALIZE PRINTER                  |

| D2       | SLCTIN | SELECT INPUT - PRINTER SELECT INPUT              |

| D3       | LED    | LIGHT EMITTING DIODE - HIGH = $ON$               |

| D4-D7    | NC     | NOT USED                                         |

# CENTRONICS TRANSMIT INTERRUPT

The INTERFACER 4 comes configured to generate an interrupt upon receiving an ACKNOWLEDGE pulse from the printer indicating that it is ready to accept another byte of data. Provisions have been made to generate an interrupt upon the printer's change from BUSY to NOT BUSY. This may be accomplished by cutting the shorting trace at jumper J5 TOP, and installing a shorting plug on J5 BOTTOM.

# CENTRONICS INTERFACE SIGNAL DESIGNATIONS

The following table describes the CENTRONICS cable pinout designations as defined by EPSON. There exist several minor differences between the CENTRONICS signal designations and those of EPSON. The EPSON designations are shown here because they are somewhat more complete. All differences will be marked with a "\*" and explained below.

| SIGNAL | GROUND | SIGNAL       | SIGNAL                              |   |

|--------|--------|--------------|-------------------------------------|---|

| PIN #  | PIN #  | NAME         | DESCRIPTION                         |   |

|        |        |              |                                     |   |

| 1      | 19     |              | ACTIVE LOW DATA STROBE PULSE        |   |

| 2      | 20     |              | DATA BIT 1                          |   |

| 3      | 21     |              | DATA BIT 2                          |   |

| 4      | 22     | DATA 3       | DATA BIT 3                          |   |

| 5      | 23     | DATA 4       | DATA BIT 4                          |   |

| 6      | 24     | DATA 5       | DATA BIT 5                          |   |

| 7      | 25     | DATA 6       | DATA BIT 6                          |   |

| 8      | 26     | DATA 7       | DATA BIT 7                          |   |

| 9      | 27     | DATA 8       | DATA BIT 8                          |   |

| 10     | 28     | ACKNLG*      | ACKNOWLEDGE PULSE ACTIVE LOW        |   |

| 11     | 29     | BUSY         | PRINTER BUSY ACTIVE HIGH            |   |

| 12     | 30     | PE           | PAPER ERROR ACTIVE HIGH             |   |

| 13     |        | SLCT         | PRINTER "ON" WHEN HIGH              |   |

| 14     |        | AUTO FEED XT | AUTO LINE FEED WHEN LOW             | * |

| 15     |        | NC           | NOT USED                            | * |

| 16     |        | ov           | LOGIC GROUND LEVEL                  |   |

| 17     |        | CHASGND      | PRINTER CHASSIS GROUND              |   |

| 18     |        | NC           | NOT USED                            | * |

| 19-30  |        | GND          | GROUND RETURN LINES                 |   |

| 31     |        | INIT*        | PRINTER INITIALIZE WHEN LOW > 50 uS |   |

| 32     |        | ERROR*       | PRINTER ERROR WHEN LOW              |   |

| 33     |        | GND          | GROUND                              |   |

| 34     |        | NC           | NOT USED                            | * |

| 35     |        | NC           | NOT USED                            | * |

| 36     |        | SLCT IN*     | PRINTER SELECT INPUT WHEN LOW       | * |

|        |        |              |                                     |   |

# SIGNAL DIFFERENCES BETWEEN EPSON AND CENTRONICS

LINE 14 This line is defined as OV or signal ground by CENTRONICS. J2 should be removed when used with a CENTRONICS Printer. LINE 15 This line is designated as OSCXT by CENTRONICS. This is not a conflict.

| LINE 18 | This line is designated as +5V by CENTRON | ICS. This is not |

|---------|-------------------------------------------|------------------|

|         | a conflict.                               |                  |

LINE 34 This line is designated LINE COUNT PULSE by CENTRONICS. This is not a conflict.

LINE 35 This line is designated as a ground return by CENTRONICS. This is not a conflict.

- LINE 36 This line is not used by CENTRONICS, however, J3 should be removed when used with a CENTRONICS Printer.

- NOTE: The user should always refer to the interface specifications of his printer before connecting it to the INTERFACER 4.

# CENTRONICS CONTROL-C LINE JUMPERING

The printer control lines handled by the CONTROL-C register may be set to power-up either high or low by the proper setting of jumpers J2-J4. This allows the user to select the power-up condition of the printer independent of the initialization procedure used. Jumper J5 is not a CONTROL-C jumper, but controls whether the interrupt is generated on ACKNLG\* or BUSY. It is included in this section because it is located in the same block of jumpers. The following section describes the position of the jumpers and their effects.

Jumpers J2-J5 are located in between U13 and U14, and above LED1, and are arranged in the following format.

| J2 | TOP    |   | * |   | * | 1 |

|----|--------|---|---|---|---|---|

| J2 | BOTTOM | 1 | * | 1 | * | 1 |

| J3 | тор    |   | * |   | * | 1 |

| J3 | BOTTOM | 1 | * | 1 | * |   |

| J4 | TOP    |   | * |   | * |   |

| J4 | BOTTOM | 1 | * | 1 | * | 1 |

| J5 | TOP    | 1 | * |   | * | Ι |

| J5 | BOTTOM |   | * |   | * |   |

|    |        |   |   |   |   |   |

# JUMPER DESCRIPTION

| J2 | AUTO FEED XT*       | This signal controls whether the printer does an automatic line feed after receiving a "return". |  |  |  |

|----|---------------------|--------------------------------------------------------------------------------------------------|--|--|--|

|    | J2 TOP<br>J2 BOTTOM | Low on power-up when jumpered.<br>High on power-up when jumpered.                                |  |  |  |

| J3 | SLCT IN*            | This signal enables the printer to receive data when Low. Printer disabled when High.         |

|----|---------------------|-----------------------------------------------------------------------------------------------|

|    | J3 TOP<br>J3 BOTTOM | Low on power-up when jumpered.<br>High on power-up when jumpered.                             |

| J4 | INIT*               | This signal initializes the printer controller when low for more than 50 uS. High normally.   |

|    | J4 TOP<br>J4 BOTTOM | Low on power-up when jumpered.<br>High on power-up when jumpered.                             |

| J5 | INTERRUPT           | This jumper determines whether the CENTRONICS interrupt is generated from ACKNLG* or BUSY.    |

|    | J5 TOP<br>J5 BOTTOM | Interrupt on ACKNLG* - shorted as shipped on board<br>Interrupt on BUSY - MUST CUT TOP SHORT! |

# LIGHT EMITTING DIODE

LIGHT EMITTING DIODE LED1 is controlled by the CONTROL-C register bit D3, and may be turned "ON" or "OFF" when outputting to this port. The LED will always be "OFF" upon power-up or RESET, and may be turned "ON" by outputting a logic "1" to D3.

# SENSE DIP SWITCH

By reading the DATA-C register, the state of DIP switch S1, positions 3-10 may be determined under program control. When read, an "ON" position will read as a "0", and an "OFF" position will be read as a "1". Positions 3 thru 10 correspond to DATA bits 7 thru 0 when read.

**EXAMPLE:** If a OFh is read, positions 3-6 are "ON", and positions 7-10 are "OFF".

NOTE: Maximum allowable length for the Centronics cable from enclosure to printer is six feet.

# THEORY OF OPERATION

The INTERFACER 4 can be roughly divided into 9 subsections for describing its operation. These sections include: The S-100 Bus Drivers, the I/O Port Decode Logic, the Strobe Generation Logic, the Wait State Logic, the Interrupt Control/Status Logic, the USART, the RS-232/CURRENT LOOP Level Conversion Logic, The CENTRONICS Parallel Logic, and the Universal Parallel Logic.

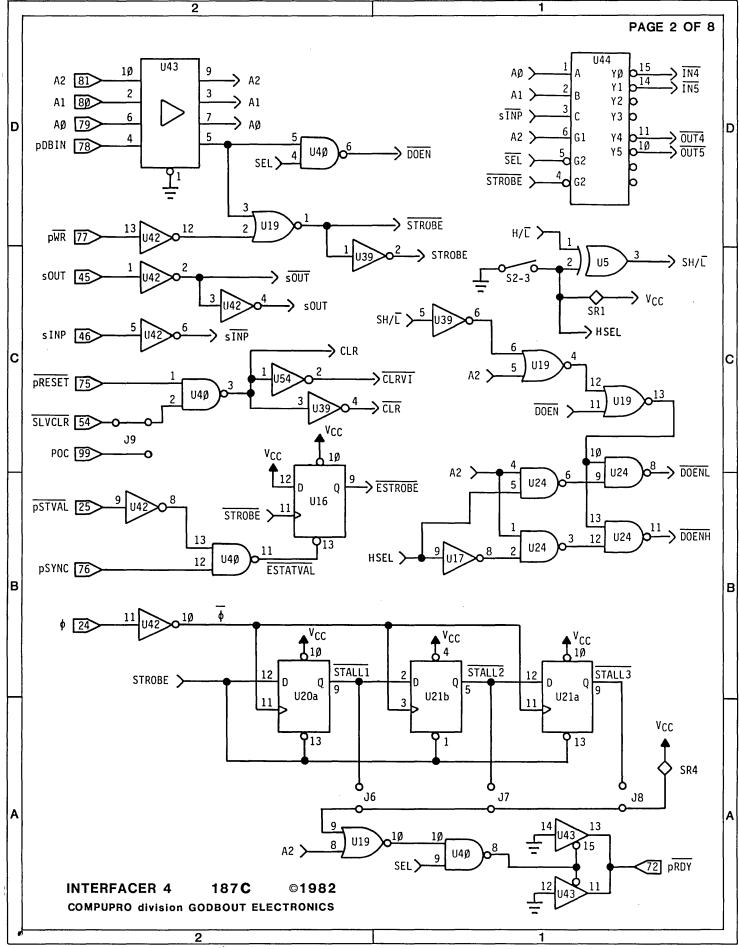

# S-100 BUS DRIVERS

The separate data input and output data buses of the S-100 bus are converted to a bi-directional data bus by octal drivers U45 and U46. Data from the S-100 bus is driven onto the internal data bus by U45 only when sOUT goes high, indicating an output operation. The internal data bus is driven onto the S-100 bus either as a high or low nibble, or as a full byte. When DOEN\* goes low, indicating that valid board select (SEL) and pDBIN are high (NAND-U40), and A2 is low, both DOENL\* and DOENH\* go low and enable a full byte onto the bus. When A2 is high, either the high or low nibble is gated out onto the bus depending on the state of HSEL (U5, U24). This allows the interrupt status to be read from 2 boards at the same time, each suppling the proper nibble of data.