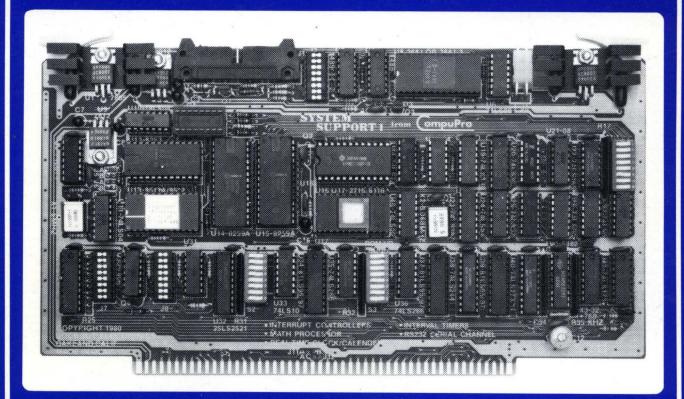

# System Support 1 **USER MANUAL**

IEEE 696 / S-100

- INTERRUPT CONTROLLERS

- INTERVAL TIMERS

- MATH PROCESSOR RS232 SERIAL CHANNEL

- REAL TIME CLOCK/CALENDAR 4K RAM/ROM

# TABLE OF CONTENTS

| HOW TO CONFIGURE YOUR SYSTEM SUPPORT 1 IN UNDER 5 MINUTES, |            |

|------------------------------------------------------------|------------|

| WITHOUT READING THE MANUAL                                 |            |

| Other options and jumpers                                  | 6          |

| Important note about system memory                         | $\epsilon$ |

|                                                            |            |

| ABOUT SYSTEM SUPPORT 1                                     | 7          |

| Technical overview                                         | 7          |

|                                                            |            |

| CONFIGURING THE SYSTEM SUPPORT 1                           | 9          |

| Setting I/O address                                        | 9          |

| Setting memory address                                     | 10         |

| Other memory options                                       | 11         |

| Disabling the memory                                       | 11         |

| Global/extended address selection                          | 11         |

| Phonton Transport and  | 12         |

| Phantom* response options                                  |            |

| Battery back-up for CMOS RAM                               | 12         |

| Wait states                                                | 12         |

| Using higher speed 9511A or 9512                           | 13         |

| Interrupt jumpers and options                              | 13         |

| Using a 9511 or 9512 with interrupts                       | 15         |

| Interval timer options                                     | 15         |

| Configuring the serial channel                             | 16         |

| Other miscellaneous hardware options                       | 17         |

| Connecting the battery                                     | 18         |

| Mounting the battery holder                                | 18         |

| Replacing the battery                                      | 18         |

| I/O port map                                               | 19         |

| 1/0 port map                                               | 1 )        |

| PROGRAMMING CONSIDERATIONS FOR THE SYSTEM SUPPORT 1        | 20         |

|                                                            | 20         |

| Power-up initialization                                    |            |

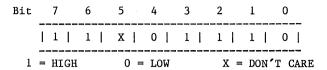

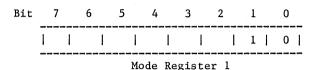

| Programming the serial channel                             | 20         |

| UART initialization                                        | 25         |

| Sample UART program                                        | 25         |

| Programming the real time clock                            | 26         |

| Clock programming sequence                                 | 28         |

| Sample clock program                                       | 29         |

| Programming the interrupt controllers                      | 35         |

| Important note about using DDT to debug interrupts         | 35         |

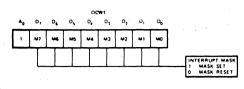

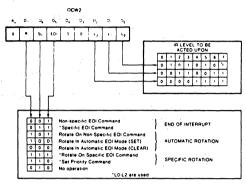

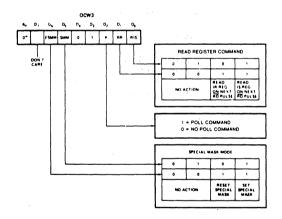

| "INTEL 8259A Programmable Interrupt Controller"            | 36         |

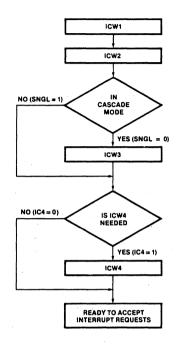

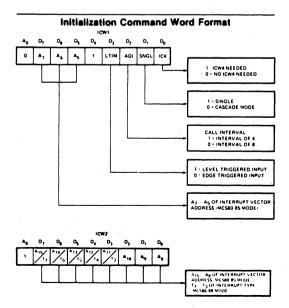

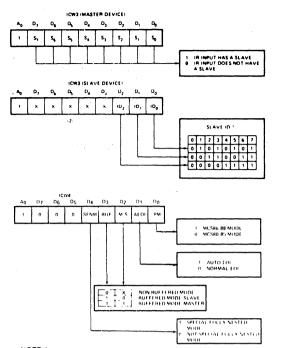

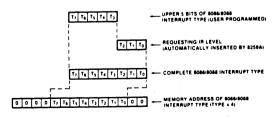

| Initializing the 8259A                                     | 56         |

| Routine for initializing master/slave 8259As               | 56         |

| Disabling the 8259As                                       |            |

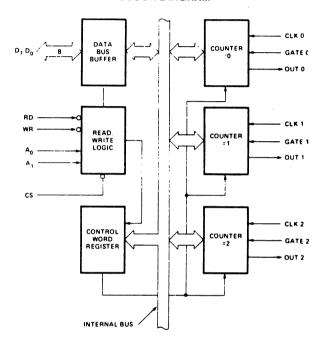

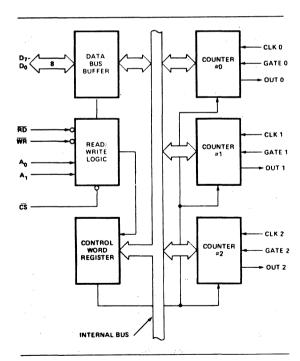

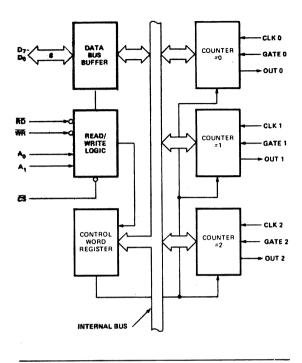

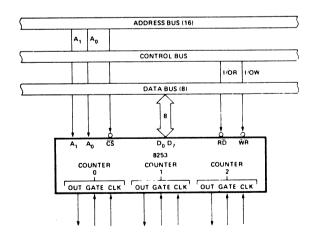

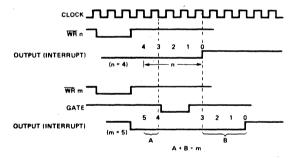

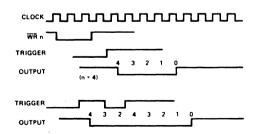

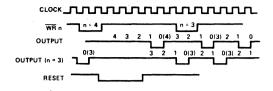

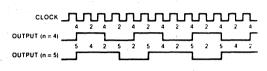

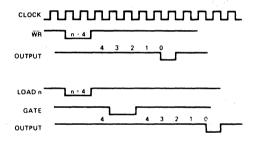

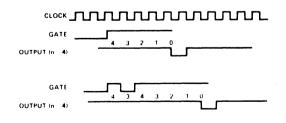

| Programming the interval timer                             | 58         |

| "INTEL 8253/8253-5 Programmable Interval Timer"            | 59         |

|                                                            |            |

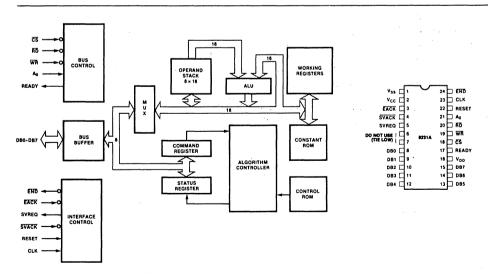

| Programming the 9511 or 9512 math processor                | 66         |

| "INTEL 8231 Arithmetic Processing Unit"                    | 69         |

| "INTEL 8232 Floating Point Processing Unit"                | 75         |

| THEORY OF OPERATION        | -    |      |       |      |       |      |     |      | _  |   |     | _    |   |              | 83   |

|----------------------------|------|------|-------|------|-------|------|-----|------|----|---|-----|------|---|--------------|------|

| Address decode             |      | •    | •     | •    | •     |      |     | •    | ٠  | • | Ţ   | •    | Ť | •            | Q:   |

| nduress decode · · · · ·   | •    | • •  | • '   | • •  |       | •    | .•  | • •  | .* | • | •   | •    | • | / <b>.</b> . | 0.   |

| ROM/RAM circuitry          | •    | • •  | •     | • •, | • •   | •    | •   | •, • | •  | • | •   | , •  | • | • "          | 84   |

| Interrupt controllers .    | •    |      | •     | • •. | • •   | •    | •   |      | •  | • | • , | •    | • | •            | 8,4  |

| Interval timer             | •    |      |       |      |       |      | •   |      | •  | • | •   | ٠. ' |   |              | 86   |

| Serial channel             |      |      |       |      |       |      |     |      |    |   |     |      |   |              | 86   |

| Math chip                  |      |      |       |      |       |      |     |      |    |   |     |      |   |              |      |

| Real-time clock/calendar   |      |      |       |      |       |      |     |      |    |   |     |      |   |              |      |

| Power-fail driver          |      |      |       |      |       |      |     |      |    |   |     |      |   |              |      |

| rower-rair driver          | •    | • •  | •     | • •  | · •   | •    | •   | • •  | •  | • | •   | •    | • | . •          | . 07 |

| Wait state generator       | •    | • •  | •     | • •  | • . • |      | •   | • •  | •  | • | •   | •    | • | •            | 8/   |

| Data bus                   | •    | • •  | •     |      |       | •    | •   | •    | •  | • | •   | •    | • | •            | 88   |

| 3                          |      |      |       |      |       |      |     | , ,  |    |   |     |      |   |              |      |

| HARDWARE SECTION           | •    |      |       |      | • •   |      | •   |      | •  | • | •   | •    | • | •            | 89   |

| Parts list                 |      |      |       |      |       |      |     |      |    |   |     |      |   |              | 89   |

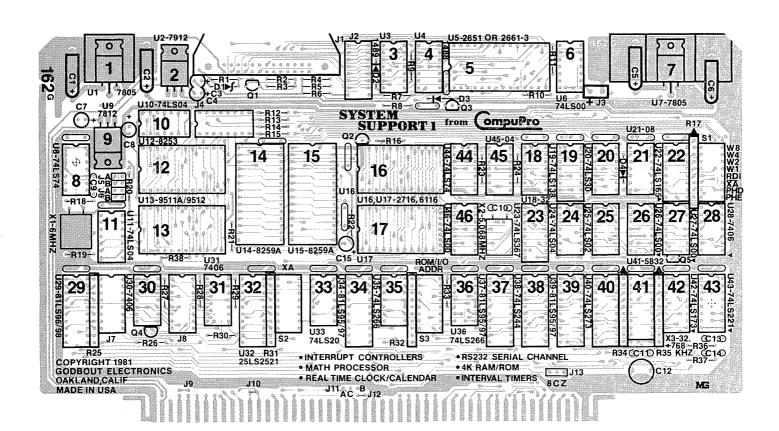

| Component layout           |      |      |       |      |       |      |     |      |    |   |     |      |   |              |      |

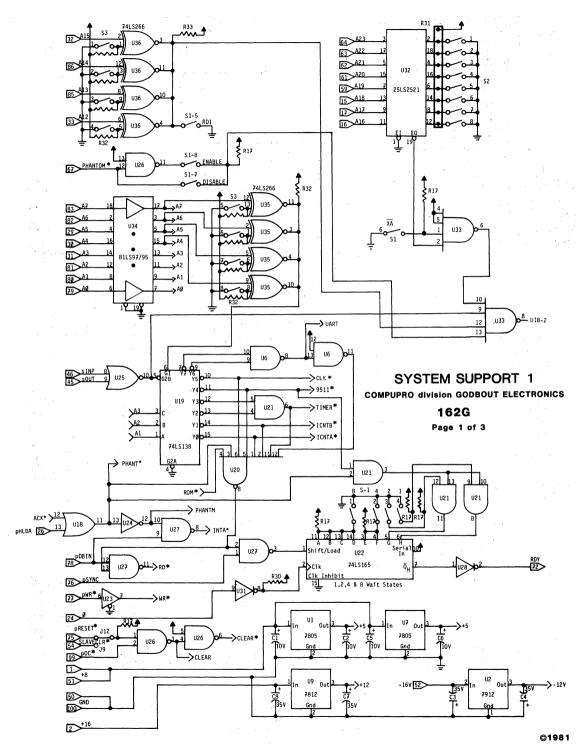

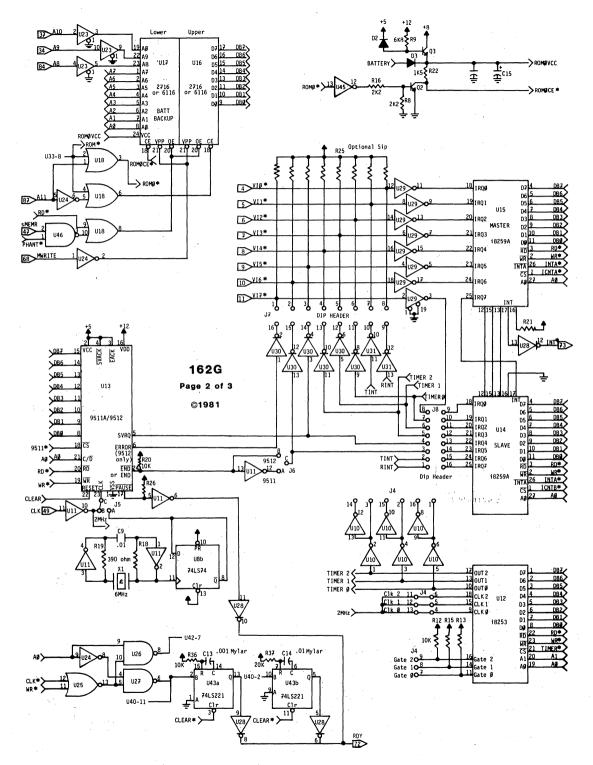

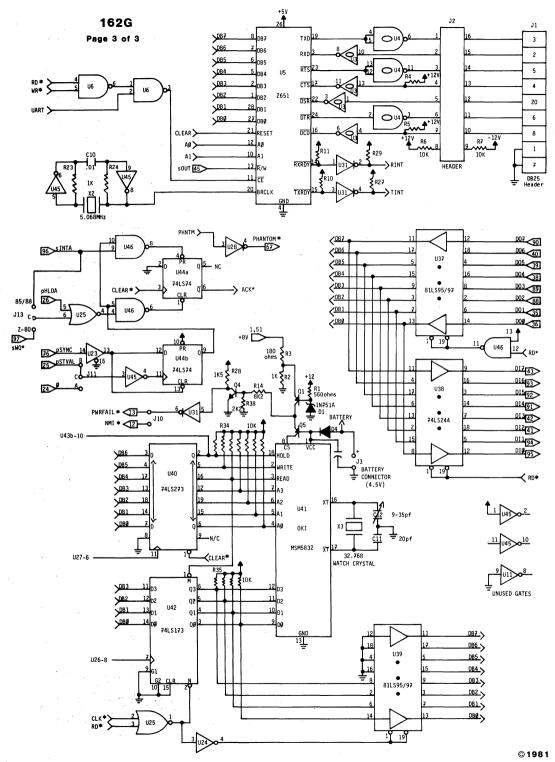

| Logic diagram              |      |      |       |      |       |      |     |      |    |   |     |      |   |              |      |

| bogic diagram              | •    | •, • | • .   | •    | • •   | •    | •   | • •  | •  | • | •   | •    | • | •            | 71   |

| INDEX                      |      |      |       |      |       |      |     |      |    |   |     |      |   |              | 95   |

| THOUX                      | •    | • •  | •     | • •  | • •   | •    | •   | • •  | •  | • | •   | ٠    | ٠ | •            | ,,   |

| CUSTOMER SERVICE /I IMITED | τσαι | DDAN | עידע. | TNI  | ZORN  | ſΔTT | UNI |      | _  | _ |     |      |   |              | 96   |

# ----- DISCLAIMER -----

Godbout Electronics makes no representations or warranties with respect to the contents hereof and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, Godbout Electronics reserves the right to revise this publication and to make any changes from time to time in the content hereof without obligation of Godbout Electronics to notify any person of such revision or changes.

This document was proofread with the aid of SpellGuard  $^{\intercal\,M}$  from ISA, Menlo Park, CA.

# HOW TO CONFIGURE YOUR SYSTEM SUPPORT 1 IN UNDER 5 MINUTES, WITHOUT READING THE MANUAL

This section is for those of you that can't wait long enough to read the manual to find out if your System Support 1 board works. WE STRONGLY RECOMMEND THAT YOU RELAX, AND READ THE MANUAL!!! If, after reading and following the directions in this section, your board appears not to function, DON'T CALL!!! READ THE MANUAL FIRST!!!

#### SWITCHES

DIP SWITCH 1 - is located near the right hand edge of the PC board and is used to select the number of wait states, and various memory options.

| Position | Labeled | How to Set It                                               |   |

|----------|---------|-------------------------------------------------------------|---|

| 1        | W8      | OFF                                                         |   |

| 2        | Ŵ4      | OFF                                                         |   |

| 3        | W2      | OFF                                                         |   |

| 4        | W1      | ON if you have a 4 MHz or greater CPU otherwise, OFF.       | , |

| 5        | RDI     | OFF if you are using the RAM/ROM, ON otherwise.             |   |

| 6        | XA      | ON if you are not using extended addressing, OFF otherwise. |   |

| 7        | PHD     | ON                                                          |   |

| 8        | PHE     | OFF                                                         |   |

|          |         |                                                             |   |

DIP SWITCH 2 - is located between U32 and U33 and is used to set the <u>extended</u> address that the ROM/RAM responds to. If you are not using extended addressing or the ROM/RAM then turn all switch positions of Dip Switch 2 OFF. Otherwise they are set according to the following table:

| Pos | it | :i | on |   |   |   |   |   | Ado | dress | Bit |           |

|-----|----|----|----|---|---|---|---|---|-----|-------|-----|-----------|

|     | 1  |    | •  | • | • | • |   | • | •   | A23   |     |           |

|     | 2  |    | •  | • |   |   | • |   | •   | A22   |     |           |

|     | 3  |    |    |   |   |   |   |   |     | A21   |     | ON = "0"  |

|     | 4  | •  |    |   |   |   |   |   | •   | A20   |     |           |

|     | 5  |    | •  | • |   |   |   |   | •   | A19   |     |           |

|     | 6  | •  | •  |   |   | • | • |   | •   | A18   |     | OFF = "1" |

|     |    |    |    |   |   |   |   |   |     | A17   |     |           |

|     | 8  | •  | •  |   | • | • | • |   | •   | A16   |     | . '       |

|     |    |    |    |   |   |   |   |   |     |       |     |           |

DIP SWITCH 3 - is located between U35 and U36 and is used to set the address of the I/O ports and the ROM/RAM. Positions 1 through 4 are used to set the ROM/RAM address. If you are not using the ROM/RAM then turn positions 1 through 4 OFF. If you are using the ROM/RAM then they are set according to the following table:

| Positio | on |  |  | Z | Ad | dress Bit |             |

|---------|----|--|--|---|----|-----------|-------------|

| 1.      |    |  |  |   |    | A15       | in a second |

| 2 .     |    |  |  |   |    | A14       | 0N = "0"    |

| 3.      |    |  |  |   |    | A13       | OFF = "1"   |

| 4 -     |    |  |  |   |    | A12       |             |

Positions 5 through 8 are used to set the address of the I/O ports. To set them for the **CompuPro** standard (block of ports at 50 hex) then set the switches as shown in the following table:

| Posi | tio | on |   |   | I | oF. | V | to | Set | Ιt |

|------|-----|----|---|---|---|-----|---|----|-----|----|

| 5    |     | •  |   |   |   |     |   | 10 | N   |    |

| 6    |     |    |   | • |   |     |   | 01 | FF  |    |

| 7    | •   | •  |   |   |   |     | • | 10 | N   |    |

| 8    |     |    | • | • |   |     |   | 01 | FF  |    |

#### OTHER OPTIONS AND JUMPERS

Insert a dip shunt in locations J2 and J8. J2 is located at the top of the board between the serial connector and U2. J8 is located at the bottom left-hand side of the board between U30 and U31.

Connect the battery cable by plugging it onto J3 (which is located near the top right-hand side of the board just to the right of the regulator). The connector is polarized but make sure the red wire is towards the left.

If you are using the **System Support 1** with our **CPU 8085/88** board or any other 8085/8088/8086 type board, then install the shorting plug at jumper J13 so that the pins labeled "8" and "C" are connected together (shorting plug will be left of center).

If you are using the **System Support 1** with our **CPU Z** or any other Z-80 or 8080 type CPU board (like an old IMSAI CPU), then install the shorting plug at jumper J13 so that the pins labeled "Z" and "C" are connected together (shorting plug will be right of center).

J13 is located at the bottom right hand corner of the PC board.

# IMPORTANT NOTE ABOUT SYSTEM MEMORY

When using the **System Support 1** with its on-board interrupt controllers, and you are using an 8080 or Z-80 CPU, it is important that all your system memory respond (become disabled) to the S-100 PHANTOM\* signal which is on bus pin 67. Therefore you must configure all your system memory to respond to PHANTOM\*.

# ABOUT THE SYSTEM SUPPORT 1

Congratulations on your purchase of the **System Support 1** board - a multifunction module designed specifically for full electrical and mechanical compatibility with the IEEE 696/S-100 Bus standard. The S-100 bus is the professional level choice for commercial, industrial and scientific applications. This bus provides for ready expansion and modification as the state of the art improves. We believe that this board, along with the rest of the **CompuPro** family, is one of the best boards available for the S-100 Bus.

The System Support 1 board combines many of the most often desired "extras" in an S-100 computer system. Most of these features don't take up enough board space to justify an entire board devoted to performing specifically that function. For example, if every function that is performed by the System Support were put on a separate board, it would take up 7 slots! By integrating all these functions into one multi-function board, we have conserved slots, power, and cost.

This board provides the system with sophisticated control of bus interrupts, 3 independent interval timers, a "real time" clock/calendar that provides BCD hours/minutes/seconds /month/day/year with battery backup, a full RS-232 serial channel which includes full handshaking, space for 4K of RAM or EPROM with provision for battery back-up for 2K of CMOS RAM, provision for adding a high performance math processor to increase system throughput, and generation of the new S-100 signal PWRFAIL\*.

No other S-100 board has been so packed with features at such a reasonable cost as the **System Support 1**, and that makes it proud to be another member of the **CompuPro** family.

Thank you for choosing a **CompuPro** product....welcome to the family of satisfied computer users.

# TECHNICAL OVERVIEW

The System Support 1 provides the system with the following functions:

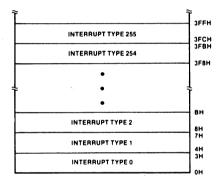

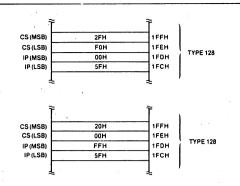

- (1) Two sophisticated LSI interrupt controllers. These handle the eight vectored interrupts from the S-100 Bus, as well as 7 interrupts generated onboard. Thus, the on-board interrupt sources do not use up any of the S-100 bus interrupt pins. The interrupt controllers provide sophisticated control of interrupt's priority, fully independent masking, and vectors to a service routine table that may be located virtually anywhere in memory. The interrupt controllers can function in an 8080/8085/Z-80 environment, as well as the 8088/86 environment.

- (2) Three independent interval timers. These are 16 bit counters that can be written to, read from, and can cause interrupts. They are clocked by a 2 MHz source, but provision has been made to allow external clock inputs, or the counters may be cascaded for longer counts. A gate input is provided for each counter to allow timing of external events. The counters can operate in one of six modes: Interrupt on Terminal Count, Programmable One-Shot, Rate Generator, Square Wave Generator, Software Triggered Strobe and Hardware Triggered Strobe.

- (3) A full RS-232 serial channel. This serial channel provides features like: Full modem and handshaking control lines, master/slave jumper options, fully software programmable UART features such as parity, word length and baud rate, and provision to run in an interrupt driven mode. The baud rates are crystal controlled.

- (4) A real time clock/calendar with battery back-up. Our real time clock keeps "real time"; hours, minutes etc. Our clock is not just an interrupt every few milliseconds that requires processor overhead to actually keep track of the time and date. (But you could use the interval timers to do that!) Included are features like 12 or 24 hour format, hour/minute/second /month/day/year/day-of-week indication, individually accessible digits, BCD format, battery back-up with a battery life of more than one year, and crystal controlled time-base.

- (5) Sockets for 4K of RAM or EPROM. You can use two 2716 type EPROMs or two of the new "byte-wide" RAMs or one of each. Provision is made to power one of the sockets from the clock battery if desired for use with the Hitachi 6116 CMOS RAM chip. The power consumption from the battery is so low that the data will be retained for over one year, and that includes running the clock. The memory space is addressable on any 4K boundary via a dip-switch, and may also respond to the full 24 bits of IEEE extended addressing. The extended address is also selectable by a dip-switch. The memory may also respond to the PHANTOM\* signal; it may appear or disappear when PHANTOM\* is asserted. The PHANTOM\* polarity is selected by a dip-switch. The memory may be disabled with a dip-switch.

- (6) A socket for a 9511A or 9512 LSI math processor. This chip is not provided with the standard board since the price/performance tradeoff may not be justified in all systems. But if you really need the higher system throughput, the chips are available from us, or you may add your own. In any case, the capability for later expansion is provided, should your need arise. Provision has been made for either math chip, whichever you prefer. The math chip can run in an interrupt driven mode, which allows the math functions to occur in parallel with other processing on the bus. The math chips currently run at 2 MHz, but provision has been made for an on-board crystal oscillator so that you can use the faster versions of these chips. Buying a math processor all by itself on a separate S-100 board usually costs more than the price of an entire System Support 1.

- (7) Implementation of the S-100 Bus Signal PWRFAIL\*. This signal does not meet the exact spec as defined by the new IEEE 696/S-100 Standard, but is asserted well before the regulators drop out of regulation. This allows thousands of instructions to be executed before the system crashes. Couple this with the battery back-up RAM capability and now you have a useful power-fail system that will allow you to recover in an orderly fashion. Provision is made on-board to jumper the PWRFAIL\* line to the NMI\* line.

- (8) The **System Support 1** takes up a block of 16 I/O ports and is addressable on any 16 port boundary. Provision is made to generate one, two, four or eight wait states to insure operation with the fastest of processors. This board was designed for full compliance with the IEEE 696/S-100 specifications to insure complete compatibility for today and the future.

For a more complete discussion of the actual implementation of these features, refer to the Theory Of Operation section of this manual.

By now you can see that the **System Support 1** is the perfect addition to any S-100 system, but when coupled with one of our CPUs, can make a complete system with just two boards! Many long hours of thought and revision went into this product, and we at **CompuPro** are confident that it will provide years of solid service. We sincerely hope that you will enjoy it.

#### CONFIGURING THE SYSTEM SUPPORT 1

The **System Support 1** occupies a group of 16 I/O ports, and 4K of memory space, if the memory is to be used. The I/O ports can reside on any 16 port boundary and the memory on any 4K byte boundary. Both addresses are set with Switch 3.

Switch 3 is located in between U35 and U36 in the lower row of chips and is marked "ROM/I/O ADDR".

#### SETTING THE I/O ADDRESS

The I/O address is set by Switch 3, positions 5 through 8. Each switch position corresponds to a particular address bit:

```

SWITCH 3 Position 5 . . . . . . Address Bit 7

Position 6 . . . . . . Address Bit 6

Position 7 . . . . . . Address Bit 5

Position 8 . . . . . . Address Bit 4

```

When a switch is "ON", that matches a "0" bit on the corresponding address line. When a switch is "OFF", that matches a "1" bit on the corresponding address line.

The following table shows all possible I/O addresses that the **System Support 1** can reside at, and the associated switch settings.

SWITCH 3

| I            | /o <i>I</i> | Ado | dr | es     | s<br> |   |   | 5     | _ | witch<br>6 | Pos | sition<br>7 | <br>8    | _ |

|--------------|-------------|-----|----|--------|-------|---|---|-------|---|------------|-----|-------------|----------|---|

|              | 00          | (1  | ne | <br>х) | •     | • | • | -0N-  |   | <br>ON-    |     | -0N-        | <br>-ON- |   |

|              | 10          | •   | •  | •      | •     | • |   | -ON-  | - | ON-        |     | -ON-        | -OFF-    |   |

|              | 20          |     |    |        |       |   |   | -ON-  | - | on-        |     | -OFF-       | -ON-     |   |

|              | 30          | •   |    | •      |       |   |   | -ON-  | - | ON-        |     | -OFF-       | -OFF-    |   |

|              | 40          |     |    |        |       |   |   | -ON-  | _ | OFF-       |     | -ON-        | -ON-     |   |

| <b>-&gt;</b> | 50          |     |    |        |       |   |   | -ON-  | _ | OFF-       |     | -ON-        | -OFF-    | ÷ |

|              | 60          |     |    |        | •     |   |   | -ON-  | _ | OFF-       |     | -OFF-       | -ON-     |   |

|              | 70          | •   |    | •      |       | • | • | -ON-  | _ | OFF        |     | -OFF-       | -OFF-    |   |

|              | 80          | •   |    |        |       |   | • | -OFF- | - | on-        |     | -ON-        | -ON-     |   |

|              | 90          | •   | •  | •      | •     | • | • | -OFF- | _ | ON-        |     | -ON-        | -OFF-    |   |

|              | Α0          |     |    | •      | •     |   |   | -OFF- | - | on-        |     | -OFF-       | -ON-     |   |

|              | В0          |     |    |        |       |   |   | -OFF- | _ | ON-        |     | -OFF-       | -OFF-    |   |

|              | C0          | •   | •  | •      | •     |   |   | -OFF- | - | OFF-       |     | -ON-        | -ON-     |   |

|              | D0          | •   | •  | •      | •     |   |   | -OFF- | - | OFF-       |     | -ON-        | -OFF-    |   |

|              | ΕO          | •   |    |        |       | • | • | -OFF- | - | OFF-       |     | -OFF-       | -ON-     |   |

|              | FO          | •   | é  | •      | •     | • | • | -OFF- | _ | OFF-       |     | -OFF-       | -OFF-    |   |

|              |             |     |    |        |       |   |   |       |   |            |     |             |          |   |

The "standard" port block that we have assigned to the **System Support 1** is the block at 50 hex. All of the software provided by **CompuPro** and other vendors will assume that you have the board addressed to this block. To set the **System Support 1** to block 50 hex, set switch positions 5=0N, 6=0FF, 7=0N, and 8=0FF.

#### SETTING THE MEMORY ADDRESS

The **System Support 1** has a 4K block of EPROM or RAM. This memory may reside at any 4K byte boundary in the system. The address of the block is set by two switches: part of Switch 3 and all of Switch 2. Switch 3 is used to set which block in the 64K "page" that the memory uses, and Switch 2 is used to select which of the 256 possible 64K "pages" (corresponding to the new address lines 256 Al6-23) is to be used.

The 4K block address within the 64K page is set by Switch 3, positions 1 through 4. Switch 3 is located in between U35 and U36 in the lower row of chips and is marked "ROM/I/O ADDR".

Each of the four switch positions correspond to a particular address bit:

When a switch is "ON", that matches a "0" bit on the corresponding address line. When a switch is "OFF", that matches a "1" bit on the corresponding address line.

The following table shows all possible 4K byte boundaries that the memory may start at, and the associated switch settings:

SWITCH 3

| Memory Address     | 1         | Switch Position<br>2 3 | 4       |

|--------------------|-----------|------------------------|---------|

| 0000 (hex)         | • • -ON-  | -ONON-                 | -on-    |

| 1000               | • • -ON-  | -ONON-                 | -OFF-   |

| 2000               | ON-       | -ONOFF-                | -on-    |

| 3000               | • • -ON-  | -ONOFF-                | -OFF-   |

| 4000               | • • -ON-  | -OFFON-                | -ON-    |

| 5000               | • • -ON-  | -OFFON-                | -OFF-   |

| 6000               | • • -ON-  | -OFFOFF-               | -ON-    |

| 7000               | • • -ON-  | -OFF -OFF-             | -OFF-   |

| 8000               | OFF-      | -ONON-                 | -ON-    |

| 9000               | • • -OFF- | -ONON-                 | -OFF-   |

| A000               | • -OFF-   | -ONOFF-                | -ON-    |

| вооо               | • • -OFF- | -ONOFF-                | -OFF-   |

| C000               | • • -OFF- | -OFFON-                | -ON-    |

| D000               | • • -OFF- | -OFFON-                | -OFF-   |

| E000               | • • -OFF- | -OFFOFF-               | -ON-    |

| $\rightarrow$ F000 | • • -OFF- | -OFFOFF-               | -0FF- ← |

NOTE: Ul6 occupies the upper 2K of the 4K address space and Ul7 occupies the lower 2K of address space. For example, if the memory were addressed at F000 hex then Ul7 would reside at F000 to F7FF and Ul6 would reside at F800 to FFFF.

The "extended address" that the memory responds to is set with Switch 2. Switch 2 is located between U32 and U33 in the lower row of chips.

Each switch position corresponds to a particular address bit (see following):

| SWITCH | 2 | Position | 1 |   |   |   |   |   |   |   |   | Address | Bit | 23 |

|--------|---|----------|---|---|---|---|---|---|---|---|---|---------|-----|----|

|        |   | Position | 2 |   | • |   |   |   | • |   | • | Address | Bit | 22 |

|        |   | Position | 3 |   | • | • |   | • |   |   |   | Address | Bit | 21 |

|        |   | Position | 4 |   |   |   |   |   | • |   |   | Address | Bit | 20 |

|        |   | Position | 5 |   | • | • |   | • | • | • | • | Address | Bit | 19 |

|        |   | Position | 6 | • | • | • | • | • | • |   | • | Address | Bit | 18 |

|        |   | Position | 7 |   | • |   | • |   |   |   | • | Address | Bit | 17 |

|        |   | Position | 8 |   |   |   |   |   |   |   |   | Address | Rit | 16 |

When a switch is "ON", that matches a "0" bit on the corresponding address line. When a switch is "OFF", that matches a "1" on the corresponding address line.

If you don't want the memory to respond to the extended address bits, see the section below on "Global/Extended Address Selection".

#### OTHER MEMORY OPTIONS

Most of the other memory options are selected with part of Switch 1. Switch 1 is located just to the right of U22.

First is a quick chart of the memory options associated with Switch 1, then we will give you a more detailed description of each of the switch's functions.

| SWITCH 1 - | Switch<br>Position | Labeled | Function                                |

|------------|--------------------|---------|-----------------------------------------|

|            | 5                  | RDI     | ON to disable memory.                   |

|            | 6                  | XA      | ON to disable extended addressing.      |

|            | 7                  | PHD     | ON to allow PHANTOM* to disable memory. |

|            | 8                  | PHE     | ON to allow PHANTOM* to enable memory.  |

#### DISABLING THE MEMORY

Position 5 of Switch 1 is used to entirely disable the memory space on the System Support 1. This will mainly be used if you don't wish to use any onboard memory at all.

To disable the on-board memory entirely, turn position 5 of Switch  $1\ \underline{ON}$ . If you don't want the on-board memory space to be disabled (if you're going to use some kind of memory), turn position 5 of Switch  $1\ \underline{OFF}$ .

# GLOBAL/EXTENDED ADDRESS SELECTION

Position 6 of Switch 1 is used to determine whether or not the memory responds to the lower 16 address bits and ignores the upper 8 address bits, or responds to the entire 24 address bits.

When the memory ignores the upper 8 address bits, it will appear in each 64K page. This is called "global" memory. If you have a processor card that is only capable of generating 16 address bits, then you will want to use the memory as global.

If you want the memory to respond to the full 24 address bits, turn position 6 of switch 1  $\overline{\text{OFF}}$ . If you want the memory to be global, then turn position 6 of Switch 1  $\overline{\text{ON}}$ .

Note that if you want the memory to respond to the extended address, you will have to set Switch 2 to the proper extended address. See the above section "Setting the Memory Address" for information on how to set Switch 2.

#### PHANTOM\* RESPONSE OPTIONS

Positions 7 and 8 are used to determine how the memory on the **System Support** 1 responds to the S-100 Bus signal PHANTOM\*. The memory can respond in one of three ways when PHANTOM\* is asserted on the bus. The memory may ignore the PHANTOM\* signal entirely, may become disabled or may become enabled.

If you want the memory to ignore the PHANTOM\* signal, leave both position 7 and position 8 of Switch 1  $\overline{\text{OFF}}$ .

If you want the memory to become disabled (disappear) when PHANTOM\* is asserted, then turn position 7  $\underline{ON}$  and position 8  $\underline{OFF}$ . This is the most often desired setting.

If you want the memory to be enabled only when PHANTOM\* is asserted, then turn position 7 OFF and position 8 ON.

**NEVER** turn both positions 7 and 8 ON at the same time!

#### BATTERY BACK-UP FOR CMOS RAM

If you are using the Hitachi HM6116 CMOS RAM chip in location U17 and wish to have it powered by the clock battery on power-down, then you will need to install a lN914 type diode at location D3, (just below U4 and U5 near the top of the board).

If you obtained the HM6116 from us, we have provided the diode along with the RAM chip. Be sure to install the diode with the banded end facing towards the left. Take care not to create any solder bridges between adjacent traces when soldering in the diode, and use a temperature controlled soldering iron (or be sure it's less than 40 watts).

If you ever decide to use an EPROM in that socket, be sure to remove the diode, otherwise the clock battery will be drained excessively (and who needs to battery back-up an EPROM?). If you wish to use the RAM in that location but don't care whether its contents are retained on power-down, then you may leave the diode out and reduce the current drain on the clock battery.

#### WAIT STATES

The **System Support 1** has circuitry that enables it to generate one, two, four or eight wait states. This will mostly be used in systems where the processor is running at a very high speed. In this industry it has always been the case that the speed of the CPU chips increases years before the speed of the LSI peripheral chips. Since the **System Support 1** makes extensive use of these LSI peripheral chips, it may be necessary to add wait states to all accesses made to the board.

Part of Switch S1 is used to add wait states to all accesses made to the board. S1 is located just to the right of U22 at the right hand edge of the board. Positions 1 through 4 of S1 are used to select the number of wait states to be generated according to the following table:

| Number of   |       | Switch Pos | sition |       |

|-------------|-------|------------|--------|-------|

| Wait States | 1(W8) | 2(W4)      | 3(W2)  | 4(W1) |

| None        | -OFF- | -OFF-      | -OFF-  | -OFF- |

| 1           | -OFF- | -OFF-      | -OFF-  | -ON-  |

| 2           | -OFF- | -OFF-      | -ON-   | -ON-  |

| 4           | -OFF- | -ON-       | -ON-   | -ON-  |

| 8           | -ON-  | -ON-       | -ON-   | -ON-  |

NOTE: These wait states affect the entire board, I/O ports and memory accesses.

#### USING A HIGHER SPEED 9511A OR 9512

As supplied, the **System Support 1** is designed to use either a 9511A or 9512 math processor chip running at 2 MHz. This is the lowest cost version of these chips. The 2 MHz clock is taken from S-100 Bus pin 49 which is specified by the S-100 Standard to be a 2 MHz clock signal.

But we have made a provision for using an on-board crystal oscillator instead of the 2 MHz signal from the S-100 Bus. This was done primarily for two reasons:

- 1. Some users may desire to use the higher speed (3 and 4 MHz) versions of the 9511A or 9512.

- 2. Some of the older S-100 systems may not have the 2 MHz clock signal available on pin  $\,49 \cdot$

If your requirements fit any of the above, then you will want to install the extra crystal required for the on-board oscillator.

This is crystal XI and is located just to the right of U11 at the left-hand edge of the board. Note that this crystal should be <u>twice</u> the frequency that you require. If you are using a standard speed 9511A or 9512 (2 MHz) but there is no 2 MHz clock on pin 49, then XI should be a 4 MHz crystal. If you are using a 3 MHz 9511A or 9512 then XI should be 6 MHz. If you are using a 4 MHz version then XI should be 8 MHz. A proper crystal is available from **CompuPro**. Be sure to specify a frequency of twice the operating speed of your math chip.

You will also need to install a jumper at location J5 (located upwards and to the right of X1) and also cut a trace at J5. If you are using the on-board oscillator option, then you must cut the trace connecting the two pads in the "B" block of J5. This trace is located on the back (solder) side of the PC board. Use an XACTO knife and be extremely careful not to damage any other traces. Then you will need to install a jumper between the two pads in the "A" block of J5.

If you are not using a higher speed 9511A or 9512, or you have 2 MHz on pin 49 in your system, or if you are not using a math processor at all, then do nothing with J5 or install no crystal at X1.

# INTERRUPT JUMPERS AND OPTIONS

IMPORTANT NOTE ABOUT USING THE ON-BOARD INTERRUPT CONTROLLERS: The System Support 1's interrupt system has been designed to work with 8080/8085/Z-80/8088 CPUs. In order to account for an idiosyncracy in the 8080 and Z-80 CPUs, the interrupt circuitry asserts the S-100 bus signal PHANTOM\* which is on bus pin 67. Therefore it is necessary to configure all your system memory to be disabled when PHANTOM\* is asserted (if you are using a Z-80 or 8080 CPU). For a discussion about why this is necessary, see the Theory of Operation section of this manual. Note that the memory on the System Support 1 will always be disabled when the interrupt circuitry requires, regardless of how you have set the PHD and PHE switches.

JUMPER J13 - is located at the lower right hand corner of the PC board, and it is used to select how the System Support 1 treats interrupt acknowledge cycles depending on what type of CPU you are running.

If you are using the **System Support 1** with our CPU **8085/88** board or any other 8085/8088/8086 type board, then install the shorting plug at J13 so that the pins labeled "8" and "C" are connected together (shorting plug is left of center).

If you are using the **System Support 1** with our **CPU Z** or any other Z-80 or 8080 type of CPU (such as an old IMSAI CPU), then install the shorting plug at J13 so that the pins labeled "Z" and "C" are connected together (shorting plug is right of center).

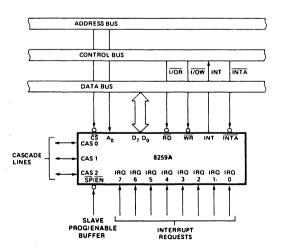

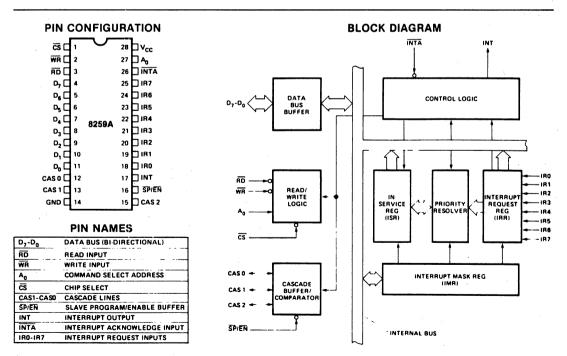

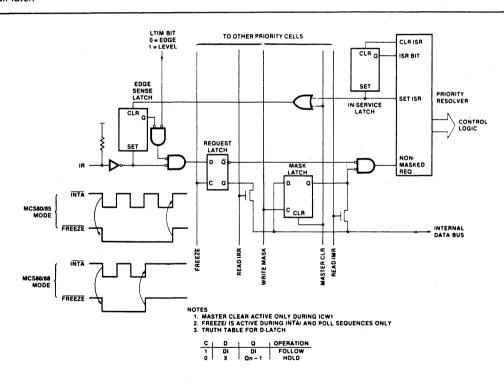

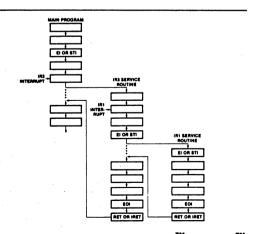

The interrupt structure of the **System Support 1** has been designed to be both easy to use and at the same time very flexible. There are two interrupt controllers on the board; one is the "master" and the other is the "slave". The two interrupt controllers look at 15 different interrupt sources. Eight of these come from the S-100 Vectored Interrupt lines and seven interrupts may be generated from various sources on the board itself.

In general, the master interrupt controller's "interrupt request" inputs have a higher priority than those of the slave interrupt controller. The master looks at seven of the S-100 Bus Vectored Interrupts (VIO-6\*) and the slave looks at the eighth vectored interrupt and seven interrupt sources that are generated on the **System Support 1.** This is the "standard" configuration, but through the use of dip headers and jumpers, almost any configuration is possible. For example, if an interrupt controller already exists in your system, the on-board interrupts may be jumpered to any of the S-100 vectored interrupt lines. This means that the interrupting capability of the various board functions are not lost even though you are not using the on-board interrupt controllers. Or some interrupts may be handled on board and some off board, or an on-board interrupt may be given a higher priority by jumpering it to an S-100 interrupt line which is responded to by the master.

To allow the **System Support 1** to be easily configured, a "standard" set of interrupt assignments may be selected by merely plugging in a dip-shunt in one location, (J8), and leaving J7 open. If you don't want a standard configuration, you may custom program these jumper areas with dip-headers instead of the shunts. If the shunt is plugged into location J8 and location J7 is left open then the board's interrupt configuration, (see the following figure):

|            | VIO* >  IRQ O INT                                | ->S-100 INT* line. |

|------------|--------------------------------------------------|--------------------|

|            | VI1* > IRQ 1                                     |                    |

| S-100      | VI 2* >   IRQ 2                                  |                    |

| Vectored   | VI3* > IRQ 3                                     | 8259A MASTER       |

| Interrupts | VI4* >  IRQ 4                                    | (U15)              |

| -          | VI5* > IRQ 5                                     |                    |

|            | VI6* > IRQ 6                                     |                    |

|            | VI7* > 1- IRQ 7                                  |                    |

|            |                                                  |                    |

|            |                                                  |                    |

| On-Board   | <slave< td=""><td>interrupt output</td></slave<> | interrupt output   |

| Interrup   | ts                                               |                    |

|            | i   IRQ0                                         |                    |

| TİM        | ERO OUT> IRQ1                                    |                    |

| TIM        | ER1 OUT> IRO2                                    |                    |

| TIM        | ER2 OUT> IR03                                    | 8259A SLAVE        |

| 951        | 1 SVRQ >   IRQ4                                  | (U14)              |

| 951        | 1 1                                              | (,/                |

| 265        | 1 TxRDY> IRQ6                                    |                    |

|            | 1 RxRDY>   IRQ7                                  |                    |

|            |                                                  |                    |

|            |                                                  |                    |

If you wish to "scramble-wire" the interrupts, all interrupt sources and destinations appear at jumpers J7 and J8. They may be jumpered in any conceivable configuration by using dip-headers. The interrupts appear at these jumpers as shown in the following diagrams:

| Sources     | J7 |          | Destinations |

|-------------|----|----------|--------------|

|             | 37 |          |              |

| 1           |    |          |              |

| 9512 ERROR> | 16 | 1 >S-10  | ) VI,7*      |

| 9511 END >  | 15 | 2  >S-10 | ) VI6*       |

| 9511 SVRQ > | 14 | 3>S-10   | ) VI5*       |

| TIMER2 OUT> | 13 | 4  >S-10 | ) VI4*       |

| TIMER1 OUT> | 12 | 5  >S-10 | ) VI3*       |

| TIMERO OUT> | 11 | 6  >S-10 | ) VI2*       |

| 2651 TxRDY> | 10 | 7  >S-10 | ) VI1*       |

| 2651 RxRDY> | 9  | 8>S-10   | *0IV         |

|             |    |          |              |

|                                        | J8 |            |      |  |  |  |  |  |  |  |  |  |

|----------------------------------------|----|------------|------|--|--|--|--|--|--|--|--|--|

| 400 also care care care care care care |    |            |      |  |  |  |  |  |  |  |  |  |

| S-100 VI7*>                            | 8  | 9  >SLAVE  | IRQ0 |  |  |  |  |  |  |  |  |  |

| TIMERO OUT>                            | 7  | 10  >SLAVE | IRQ1 |  |  |  |  |  |  |  |  |  |

| TIMER1 OUT>                            | 6  | 11 >SLAVE  | IRQ2 |  |  |  |  |  |  |  |  |  |

| TIMER2 OUT>                            | 5  | 12  >SLAVE | IRQ3 |  |  |  |  |  |  |  |  |  |

| 9512 SVRQ >                            | 4  | 13  >SLAVE | IRQ4 |  |  |  |  |  |  |  |  |  |

| 9512 END >                             | 3  | 14  >SLAVE | IRQ5 |  |  |  |  |  |  |  |  |  |

| 2651 TxRDY>                            | 2  | 15  >SLAVE | IRQ6 |  |  |  |  |  |  |  |  |  |

| 2651 RxRDY>                            | 1  | 16  >SLAVE | IRQ7 |  |  |  |  |  |  |  |  |  |

|                                        |    |            |      |  |  |  |  |  |  |  |  |  |

# USING A 9511 OR 9512 WITH INTERRUPTS

The "END" interrupt from the 9511 or 9512 is not actually connected directly to J7 and J8 as is shown above. This is because the polarity of the END signal is different between the 9511 and the 9512. J6 is used to select the appropriate polarity for this signal depending on which math processor you are using.

If you are using a 9511A then install a jumper in the "A" block at J6. If you are using a 9512 then install a jumper in the "B" block at J6.

If you are using either math chip but are not running it "interrupt driven", then you do not need to install any jumper at J6.

Also note that the "ERROR" output from the 9512 (9511A does not have this output) is not available at both J7 and J8 as the other math chip outputs are. The ERROR signal is only available at J7.

#### INTERVAL TIMER OPTIONS

The three interval timers on the **System Support 1** are implemented with an 8253 IC. It contains three independent timer sections. Each section has a clock input, gate input and timer output. These 9 inputs and outputs appear at J4 so that the different sections may be cascaded for longer time delays or so that

the signals may be connected to external devices. The following diagram shows the connections at J4:

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 16 >TIMER 0 OUTPUT                              |

| INVERTED TIMER 1 OUTPUT<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3 14 >TIMER 2 OUTPUT                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52   Hz SOURCE                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62 MHz SOURCE                                     |

| and the second s | 7 10 NO CONNECTION                                |

| TIMER 1 GATE INPUT>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8 9  <timer 2="" gate="" input<="" td=""></timer> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                   |

NOTES: All gate inputs are pulled up with a 4.7K ohm resistor. Pins 4 and 13 are connected together, pins 5 and 12 are connected together and pins 6 and 11 are connected together. All timer outputs are buffered.

To cascade sections or use external clocks, the appropriate trace(s) must be cut on the solder side of the board to remove the 2 MHz clock source. Then the output of another section or an external input may be connected to the clock inputs (TTL ONLY!). Use a dip header to make the interconnections.

#### CONFIGURING THE SERIAL CHANNEL

The Serial Channel on the **System Support 1** has been designed to be as flexible as possible. It may be used in the "master" or "slave" mode and provides full RS-232C handshaking lines. A standard 26 pin transition connector has been provided at J1 to facilitate easy connection of a ribbon cable that usually has a DB-25 style connector on the other end. Such a cable is available from us or your **CompuPro** dealer.

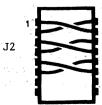

All of the serial signals appear at J2 which allow them to be wired as either a master or slave device. An example of a master device would be a terminal or printer and an example of a slave device would be a modem or other computer. Therefore, the serial channel must be configured to complement the device it is connected to. In other words, if you are using the serial channel with a terminal (a master device) then you will want to configure the serial channel to act as a slave. Conversely, if you are using the serial channel with a modem (a slave device) then you will want to configure the serial channel to act as a master.

Since the most common configuration will be that of a slave, we have made it easy for you to install this configuration. This may be accomplished merely by installing a dip-shunt in location J2. Again, you will want to use this configuration if you are hooking up the serial channel to a standard terminal or printer.

To configure the serial channel to act as a master, then you will need to cross-wire J2 by using a dip-header. This configuration is shown in the following diagram:

For reference purposes, the signals appearing at J2 and J1 are as follows:

|      | J2  |    |              | Jl |            |        |                      |

|------|-----|----|--------------|----|------------|--------|----------------------|

|      |     |    |              |    |            |        |                      |

| TxD> | 1   | 16 |              | 3  | l          |        |                      |

| RxD< | 2 . | 15 |              | 2  | 1          |        |                      |

| RTS> | 3   | 14 |              | 5  | 1          |        |                      |

| CTS< | 4   | 13 |              | 4  | İ          | 26 Pin | Transition Connector |

| DSR< | 5   | 12 |              | 20 |            | and 25 | Pin DB-25 Connector  |

| DTR> | 6   | 11 |              | 6  | <b> </b> . |        | •                    |

| DCD< | 7 . | 10 |              | 8  | 1          |        |                      |

| +12V | 8   | 9  | <sub> </sub> | 1  |            | -GND   | *                    |

| •    |     |    | İ            | 7  |            | -GND   | •                    |

|      | •   |    | 1            | -  |            |        |                      |

| -12V |     |    | !            |    |            |        |                      |

TxD = Transmitted Data RxD = Received Data

RTS = Request To Send CTS = Clear To Send

DSR = Data Set Ready DTR = Data Terminal Ready

DCD = Data Carrier Detect GND = Ground

DIAGRAM OF J2-J1-SERIAL SIGNAL RELATIONSHIPS

Setting the baud rate, stop bits, parity and other UART parameters is done in software and will be covered in a later section called "Programming The Serial Channel".

# OTHER MISCELLANEOUS HARDWARE OPTIONS

Use of pSTVAL\* - The System Support 1 uses the new S-100 Signal pSTVAL\* that appears on S-100 Bus pin 25. If you are using a CPU from CompuPro (or any other CPU that meets the IEEE/696 standard), then this signal will be generated by the CPU and you need not worry about this next jumper.

If you are using an older generation CPU board that does not generate pSTVAL\*, then you will need to make a small modification to the System Support 1. Proceed as follows:

Locate Jll. It is located near the edge connector in approximately the center of the board. Jll has three pads labeled A, C and B. If you look on the back (solder) side of the board you will notice that there is a small trace connecting pad B to pad C. Using an XACTO knife, carefully cut this trace. Take care not to damage any other traces on the PC board. Then install a jumper between pads A and C. That completes this modification.

Use of SLAVE CLR\* Instead of RESET\* - The S-100 signal SLAVE CLR\* (bus pin 54) is specifically designated for clearing slave devices (the System Support 1 is a slave device). However, it is usually more convenient in most systems to use RESET\* instead of SLAVE CLR\*. The System Support 1 is currently wired to use RESET\* to clear the various circuits on the board. Provision has been made to use SLAVE CLR\* instead of RESET\* if you so desire.

To do this, locate J9 and J12. J9 is a single jumper pad located at the bottom left-hand corner of the board just above the edge connector fingers. J12 is also located at the bottom of the board just above the edge connector

fingers, but near the center of the board. J12 has two pads that are connected together by a trace on the back (solder) side of the board. This trace must be cut with an XACTO knife. Be sure not to damage any other traces. Then, using a length of insulated wire (such as wire-wrap wire), install a jumper between the pad of J9 and the left-most pad of J12 (the one closest to the "C"). This will cause the circuitry on the board to be cleared in response to POC\* and SLAVE CLR\*.

PWRFAIL\* and NMI\* - The System Support 1 generates the S-100 PWRFAIL\* signal which is used to indicate that a loss of power is imminent. You will usually want this signal to cause a non-maskable interrupt (NMI\*) to the CPU. The CPU can then save any data it deems relevant. Provision has been made to jumper the PWRFAIL\* signal to the NMI\* line on the S-100 Bus. Thus both PWRFAIL\* and NMI\* would be asserted low about 15 milliseconds before the regulators in the system drift out of regulation. (The exact time will depend on your system's power supply and loading.)

If you desire to have the PWRFAIL\* signal cause an NMI\*, then install a jumper at location J10. J10 is located at the bottom left hand side of the board, just above the edge connector fingers. If you don't care about the PWRFAIL\* signal, then you need not do anything with J10.

As an option, the PWRFAIL\* signal is available at the right-most pad of J10. It could conceivably be hooked to any other S-100 interrupt pin via a header at J7. It should be mentioned, however, that this would not be a good practice because any of the other interrupts could be "masked" at the time of power failure, thus defeating the purpose of the PWRFAIL\* signal.

# CONNECTING THE BATTERY

The battery connector supplied with the **System Support 1** is semi-polarized so that it should only plug onto J3 easily in one direction. To double check, the red wire which connects to the + side of the battery should correspond to the + marking on the board.

If you desire to use a different battery than the one supplied (for example three 1.5 volt penlight cells in series for longer battery life) then you should take care to keep the polarities correct. The circuitry on the **System Support 1** is protected from reverse polarity so no damage will occur if the battery is reversed, but the board won't function properly.

The battery is shipped already plugged into its holder, but should it become necessary to remove it, be sure to orient the + end of the battery to correspond to the + stamped in battery holder.

# MOUNTING THE BATTERY HOLDER

The battery holder is intended to be mounted <u>outside</u> the computer enclosure. This is because batteries, although sealed, under some conditions can still leak, outgas or otherwise do nasty things to the sensitive components and contacts inside your computer. Therefore, we strongly recommend that the battery be mounted outside the computer enclosure and not inside.

# REPLACING THE BATTERY

The 4.5 volt alkaline battery that is supplied with the **System Support 1** should last approximately 1.5 years with normal use. However, to insure that a loss of time or memory data does not occur due to battery failure, we recommend that the battery be replaced once every year. The battery can be replaced while

the system power is on, so that operation of the clock or memory data will not be lost, (unless of course you get a power failure at the exact instant that you remove the battery).

The type of battery used is a Mallory PX21 or Eveready 523. Replacement batteries are available from us or possibly your local dealer. You can probably also obtain this battery from a photo store or possibly a "drug" store with a well stocked photo department. This battery is also used in some smoke alarms, so you may also find it in a well stocked hardware store.

If you plan to keep a replacement battery handy, be aware that the average shelf life of an alkaline battery is two years. This can be extended significantly by storing the battery in a refrigerator. Before using a battery that has been stored in the refrigerator, allow it to come up to room temperature and make sure that there is no moisture present on any of the contacts.

IMPORTANT NOTE: Please do not use anything other than an alkaline battery. Mercury cells may seem like a good choice for this application, but they do not fare too well under the light load presented by the System Support 1. Carbon-Zinc cells can leak, causing damage to the computer (usually irreparable). Nicads will not be recharged by the board's circuitry. Also note that using any battery other than the ones specified will void your warranty.

# I/O PORT MAP

The **System Support 1** uses a block of 16 I/O port addresses. This block may begin at any 16 port boundary. Each of the I/O ports performs a specific function and each will always appear at an address that is relative to the base address. The following chart shows the I/O port's relative positions, and their actual address when the **System Support 1** is addressed to the block at 50H (CompuPro standard address).

| Port Function                  | Relative Position | Address |

|--------------------------------|-------------------|---------|

| Master 8259A lower port (A0=0) | Base+ 0 dec 0 hex | 50 hex  |

| Master 8259A upper port (A0=1) | Base+ 1 dec 1 hex | 51 hex  |

| Slave 8259A lower port (A0=0)  | Base+ 2 dec 2 hex | 52 hex  |

| Slave 8259A upper port (A0=1)  | Base+ 3 dec 3 hex | 53 hex  |

| Timer/Counter 0                | Base+ 4 dec 4 hex | 54 hex  |

| Timer/Counter 1                | Base+ 5 dec 5 hex | 55 hex  |

| Timer/Counter 2                | Base+ 6 dec 6 hex | 56 hex  |

| Timer/Counter Control Register | Base+ 7 dec 7 hex | 57 hex  |

| 9511A/9512 Data Port           | Base+ 8 dec 8 hex | 58 hex  |

| 9511A/9512 Command Port        | Base+ 9 dec 9 hex | 59 hex  |

| Clock/Calendar Command Port    | Base+10 dec A hex | 5A hex  |

| Clock/Calendar Data Port       | Base+11 dec B hex | 5B hex  |

| 2651 Data Register             | Base+12 dec C hex | 5C hex  |

| 2651 Status Register           | Base+13 dec D hex | 5D hex  |

| 2651 Mode Registers            | Base+14 dec E hex | 5E hex  |

| 2651 Command Register          | Base+15 dec F hex | 5F hex  |

#### PROGRAMMING CONSIDERATIONS FOR THE SYSTEM SUPPORT 1

The following section of this manual will discuss some of the software considerations that will be necessary to use this board. We will provide you with a few actual programs, but these programs are presented as either examples or for testing purposes and are not necessarily the best way to do something. The listings were prepared using the standard CP/M assembler (ASM.COM) and sometimes assume a CP/M system (like for I/O calls).

First we will discuss the power-up initialization of the **System Support 1** and then we will discuss the programming considerations for the various functions of the board.

#### POWER-UP INITIALIZATION

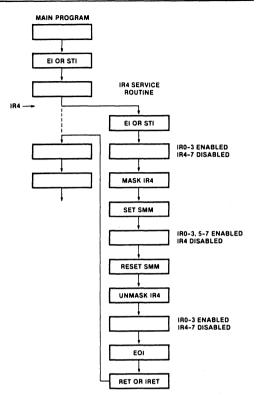

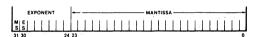

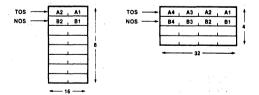

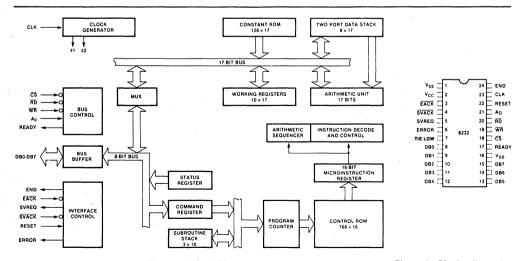

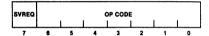

When you turn on your system, the first thing that usually happens is to boot in the disk operating system or execute some kind of program stored in ROM. Somewhere at the beginning of these programs is usually some code to initialize the system. This may do things like set the stack pointer, clear some registers and send a set of initial parameters to I/O peripherals. This latter example is what needs to be done with the System Support 1.