Printed 1 May, 1984

Document No. 130-0101-03

"Q-Timer" is a trademark of CODAR Technology, Inc.

<sup>&</sup>quot;Intellec" is a trademark of the Intel Corporation.

"DEC" and "RSX" are trademarks of Digital Equipment Corporation.

## **TABLE OF CONTENTS**

- I. Introduction

- II. Q-Timer Configurations

- III. Tables & Figures

- Table 1 "Q-TIMER SPECIFICATIONS"

- Table 2 "Q-TIMER DEVICE ADDRESSES"

- Table 3 "SOFTWARE MONITOR BOOT COMMANDS"

- Table 4 "34-PIN CONNECTOR PINOUT"

- Table 5 "10-PIN CONNECTOR PINOUT"

- Table 6 "WATCHDOG TIMER JUMPERS"

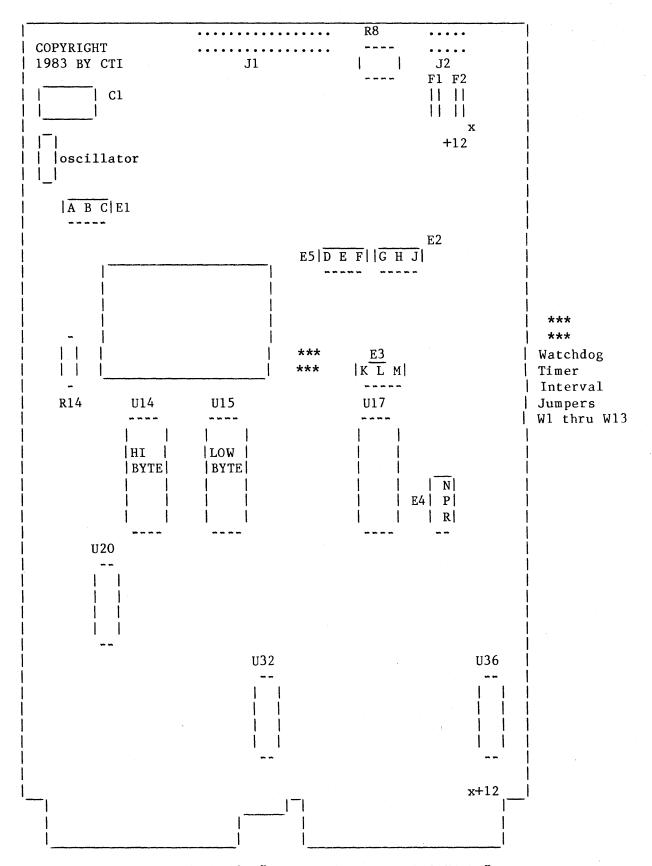

- Figure 1 "Q-TIMER COMPONENT LOCATIONS"

- IV. Q-Timer Installation (This section will get you up and running!)

- ...includes:

- Calendar Clock Software Integration (Step 4)

- V. Q-Timer Software Monitor Operation

- ...includes:

- **Boot Commands**

- Setting the Calendar Clock Time

- **EPROM Page Register Function**

- VI. Calendar Clock

- VII. Watchdog Timer

- VIII. CMOS RAM

- IX. Line Time Clock

- ...includes:

- LTC Jumper Configuration

- X. I/O Ports & Other Items

- ...includes:

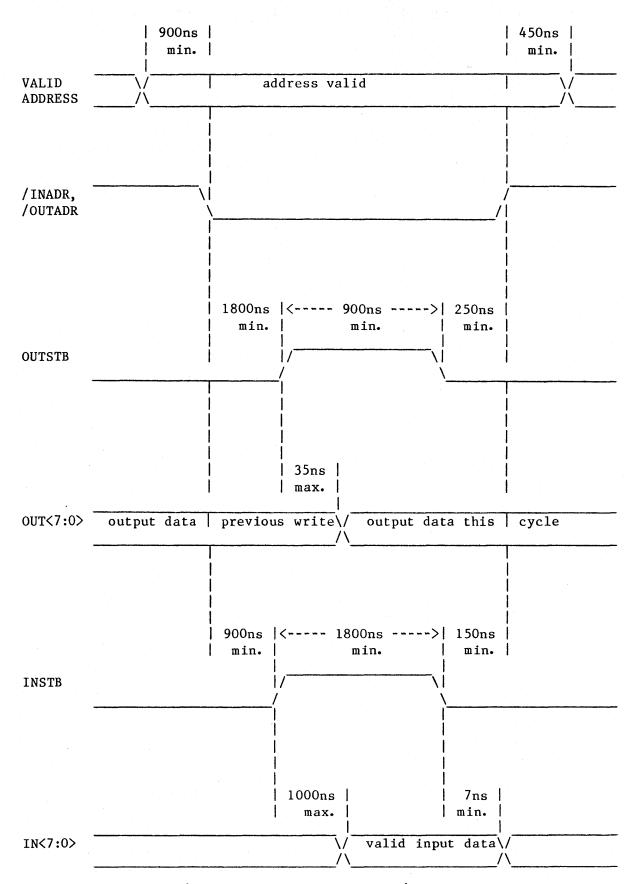

- 34-Pin I/O Port Configuration & Timing (Figure 2)

- 10-Pin Auxiliary Connector Configuration

- Bus Termination By The Q-Timer

- LED/Switch Panel (Test Plug) Use

- On-Board Rechargeable Batteries

- XI. Warranty

- XII. Errata (Please check here first for changes!)

## INTRODUCTION

The Q-Timer is a dual-wide module that is fully compatible with the LSI-11 bus (Q-Bus). It provides the following functions: calendar clock, non-volatile 2KW CMOS RAM, Line Time Clock generation, Line Time Clock control register, 4KW EPROM memory, 8-bit output port, 8-bit input port, watchdog timer and bus termination. Included in the EPROM memory is a monitor program that will read and set the time, boot from a number of different devices, run a system memory test, run a Q-Timer self-test, and down-load a program from a remote computer. This manual contains complete instructions for integrating the Q-Timer into the RSX-11M and the RT-11 operating systems.

All memory and device addresses appear in the I/O page. EPROM memory appears as 16 pages of 256 words and CMOS RAM memory appears as 8 pages of 256 words. The calendar clock provides time information from tenths of seconds through months with the year being stored in CMOS RAM. The Q-Timer may either generate a 60 HZ Line Time Clock signal or it may turn on or off an existing Line Time Clock signal depending on how it is jumpered. The Watchdog Timer function, which must be enabled by jumper, will automatically do a RESTART operation after a certain time interval if a specific memory location is not read. The bus termination function may be removed by pulling the three terminating resistor networks from their sockets. The operation of all of these features is explained in detail in this manual.

## **Q-TIMER CONFIGURATIONS**

### STANDARD (STD) configuration:

All Q-Timer addresses are in the I/O page. The Q-Timer, as shipped standard from the factory, has the CMOS RAM at address 766000 octal, the Software Monitor (including boot routines, diagnostic routines and Calendar Clock format/read routines) at address 773000, and the Line Time Clock (LTC) and the LTC Software Control Register enabled.

### MOVE BOOT (MB) configuration:

If your system currently has an operating boot routine in the DEC I/O page at address 773000 octal, then you must either disable your current boot routine at that address or order the Q-Timer Configuration MOVE BOOT which moves the Q-Timer Software Monitor (including boot code, diagnostic routines and Q-Timer Calendar Clock format/read routines) to address 771000 octal.

This situation of boot conflict often occurs due to the fact that some micro-processor based disk and tape controllers contain their own on-board boot code which responds to the address 773000. It is preferred that you disable your current boot to resolve this conflict, so that the Q-Timer boot features can be implemented at the standard start-up address of 773000. If however, you choose to move the Q-Timer Software Monitor via the MB configuration to address 771000, the Software Monitor will implement all its features but must be entered at address 771000.

## LTC DISABLE (LD) configuration:

If your system currently has an operating Line Time Clock (LTC) and you do not wish to use the Q-Timer LTC, then the Q-Timer requires the LTC DISABLE configuration which disables the Q-Timer LTC and the Q-Timer LTC Software Control Register. A complete discussion of the LTC function is provided in the LINE TIME CLOCK section of this manual.

#### FALCON (FAL) configuration:

If your system currently has RAM (or any other device) residing in the I/O page at address 766000 octal, then the Q-Timer requires the FALCON configuration which moves the Q-Timer CMOS RAM to address 775000 octal. (Note this configuration is required for Falcon implementations to avoid conflict with the Falcon RAM.)

#### FALCON WITH DEC ODT (FDO) configuration:

If your FALCON has the optional ODT chip set, then your Q-Timer requires this configuration which moves the Q-Timer CMOS RAM to 775000 octal and moves the Q-Timer Software Monitor to 774000 octal. Again, the Software Monitor will implement all its features but must be entered at address 774000.

#### SPECIAL (SP) configuration:

These are special configurations for custom applications or for test purposes.

NOTE: A version of the Q-Timer Monitor is available which includes console ODT for FALCON SBC 11/21 systems. With this feature, you can have ODT without tying up the 11/21's on-board memory sockets which otherwise must be used for the Macro-ODT chips. Call CTI for further information.

Following is a graphical presentation of the labeled EPROM's that are shipped with each of the Q-Timer conigurations. Thus, a user can ascertain their Q-Timer configuration via inspection of the EPROM set on a given board.

| STANDARD (STD)        | STD                                          | STD                                                 | STD                                             |

|-----------------------|----------------------------------------------|-----------------------------------------------------|-------------------------------------------------|

|                       | D V .                                        | LB V .                                              | HB                                              |

|                       | 34 30 50 50 50 50 50 50 50 50 50 50 50 50 50 | per per per per per per per tro tro tro tro tro tro | 200 200 100 200 200 200 200 200 200 000 0       |

|                       |                                              |                                                     |                                                 |

| MOVE BOOK (MB)        | lyp                                          | lwn                                                 | lwp 1                                           |

| MOVE BOOT (MB)        | MB                                           | MB V .                                              | MB                                              |

|                       | V_•1                                         | LD                                                  | IID                                             |

|                       |                                              |                                                     |                                                 |

|                       |                                              |                                                     |                                                 |

|                       | \$6 50 50 50 50 50 50 50 50 50 50 50 50 50   | ******                                              |                                                 |

| LTC DISABLE (LD)      | LD                                           | LD                                                  | LD                                              |

|                       | D V .                                        | LB V.                                               | HB V .                                          |

|                       | 200 200 200 200 200 000 000 000 000 000      |                                                     |                                                 |

|                       |                                              |                                                     |                                                 |

|                       |                                              |                                                     |                                                 |

| THE CONT. (THE)       |                                              | 1mar                                                | I mar                                           |

| FALCON (FAL)          | FAL                                          | FAL                                                 | FAL                                             |

|                       | D V                                          | LB                                                  | HB                                              |

|                       |                                              |                                                     |                                                 |

|                       |                                              |                                                     |                                                 |

|                       |                                              |                                                     |                                                 |

| FALCON WITH ODT (FDO) | FDO                                          | FDO                                                 | FDO                                             |

| •                     | D V .                                        | LB V .                                              | HB                                              |

|                       | her her her her her her her her ner ere ner  | 26 56 56 56 56 56 36 26 56 56 56 56                 | the gas has her has her has not not not not not |

|                       |                                              |                                                     |                                                 |

The upper left corner designates the configuration or option.

The lower left corner designates the PROM as an Address Decoder, Data lo-byte, or Data hi-byte chip.

The lower right corner designates the version of the EPROM code.

If an EPROM set is configured with two options, the second option will appear in the upper right corner, i.e.:

|MB LD| designates the MOVE BOOT and |D V\_.\_| the LTC DISABLE option.

## **TABLE & FIGURES**

Module Size: 5.2 x 8.9 inches dual-wide

Operating Power: 5V +/- 5% 1.2 Amp with bus terminators

0.7 Amp without bus terminators

Operating Temperature: 0 deg. to 50 deg. C

Relative Humidity: 5% to 95% noncondensing

Bus Loading: 1 LSI-11 bus load per I/O line

Batteries: 3 x 1.2 Volt Ni-Cad, 180 ma hours

Battery Back-up: 60 days minimum, 75 days typical

Battery Life: 3 to 5 years typical

Clock Accuracy: 8 sec/month typical error, 15 deg. to 40 deg. C

Address EPROM: 4096 x 8-bit, one 2732, 450 ns max access time

Boot EPROM: 4096 x 16-bit, two 2732's, 450 ns max access

CMOS Memory: 2048 x 16-bit static CMOS RAM

I/O Cycle Time: 6 micro-sec maximum for DATI and DATO

9 micro-sec maximum for DATIO

60 Hz LTC Phase Jitter: 0.2% maximum (33 micro sec), non-accumulating

Parallel I/O: TTL compatible, 120 ohm input termination

Table 1 "Q-TIMER SPECIFICATIONS"

Q-Timer Config. CMOS RAM Memory 256 locations 766000-766777 STD, MB, LD 775000-775777 FAL, FDO STD, LD, FAL EPROM Memory 256 locations 773000-773777 (holds the Q-Timer 771000-771777 MBSoftware Monitor) 774000-774777 FDO 16 ports 777200-777236 a11 8-Bit Output Ports 16 ports 777240-777276 a11 8-Bit Input Ports Calendar Clock 16 registers 777300-777336 a11 EPROM Page Register & l location 777340 a11 Watchdog timer reset CMOS RAM Page Register 1 location 777342 a11 | Line Time Clock (LTC) 777546 Software Control Reg. 1 location all

Table 2 "Q-TIMER DEVICE ADDRESSES"

|    |     |                | HARDWARE DEVICE ABBREVIATIONS                                    |

|----|-----|----------------|------------------------------------------------------------------|

|    | DD  | •              | TU58 cartridge tape                                              |

| -1 | DK  | •              | RK05 disk                                                        |

| -  | DL  | -              | RLO1 or RLO2 disk                                                |

| -  | DM  | -              | RKO6/RKO7 disk                                                   |

| -  | DP  | -              | RP02/RP03 disk                                                   |

|    | DR  | -              | RMO2 disk                                                        |

| 1  | DX  | -              | RXO1 or RXO2 diskette                                            |

| ļ  | ΜT  | -              | TM11 magnetic tape                                               |

|    |     |                | SOFTWARE FEATURE ABBREVIATIONS                                   |

| ١  | MDO | -              | LSI-11 Main Memory Test 16-bit or 18-bit systems                 |

| ١  | MD1 | <b>-</b>       | LSI-11 Main Memeory Test 22-bit system                           |

|    | OB  |                | Other Boot                                                       |

| ļ  | SLO | , <del>~</del> | Serial Downline Loader "Intellec" format & Terminal Emulator     |

|    | SL1 | -              | Serial Downline Loader "Intellec" format                         |

| 1  | SL2 | -              | Serial Downline Loader "abs loader" format & Terminal Emululator |

| ١  | SL3 |                | Serial Downline Loader "abs loader" format                       |

| 1  | ST  |                | Q-Timer Self-Test                                                |

| 1  | TT  |                | Terminal Emulator                                                |

Table 3 "SOFTWARE MONITOR BOOT COMMANDS"

Figure 1 "Q-TIMER COMPONENT LOCATIONS"

|      |          | Congress Confession Co | Application of the first of the second | 1   |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----|

| PIN  | FUNCTION | PIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | FUNCTION                               |     |

| 1    | GND      | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GND                                    |     |

| 2    | /OUTADR  | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IN O                                   | 1   |

| 3    | GND      | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IN 1                                   | į   |

| 4    | OUTSTB   | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IN 2                                   | - 1 |

| 5    | GND      | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IN 3                                   |     |

| 6    | OUT O    | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IN 4                                   | 1   |

| 1 7  | OUT 1    | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IN 5                                   | 1   |

| 8    | OUT 2    | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IN 6                                   | 1   |

| 9    | OUT 3    | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | IN 7                                   | I   |

| 10   | OUT 4    | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GND                                    |     |

| 1 11 | OUT 5    | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ADR 1                                  | 1   |

| 12   | OUT 6    | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ADR 2                                  | !   |

| 13   | OUT 7    | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ADR 3                                  | .   |

| 14   | GND      | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ADR 4                                  | 1   |

| 15   | /INADR   | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GND                                    |     |

| 16   | GND      | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GND                                    | 1   |

| 17   | INSTB    | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GND                                    |     |

Table 4 "34-PIN CONNECTOR (J1) PINOUT"

|     | PIN | FUNCTION                                                |   |

|-----|-----|---------------------------------------------------------|---|

| i   | 1   | GND                                                     |   |

|     | 2   | 32,768 Hz output, TTL levels, 5 unit loads              | 1 |

| 1   | 3   | +5 volt output (Fl must be fused at 0.5 amp)            |   |

| -   | 4   | 32,768 Hz input, +5 volt CMOS levels                    | ١ |

| -   |     | ( $Vi1 < 1.5 \text{ volts}, Vih > 3.5 \text{ volts}$ )  |   |

| 1   | 5   | +12 volt output (F2 must be fused at 0.5 amp)           |   |

|     | 6   | External LTC signal input, TTL levels, 1/4 unit load    | l |

|     | 7   | External battery input (5.25 volt maximum)              |   |

|     | 8   | 32,768 Hz output, CMOS level, 150 Kohm output impedance | 1 |

| 1   | 9   | Q-Timer logic clock output, TTL levels, 5 unit loads    |   |

| - 1 |     | (1  MHz + or - 5%)                                      |   |

|     | 10  | GND                                                     |   |

Table 5 "10-PIN CONNECTOR (J2) PINOUT"

| Jumper | Time-Out<br>Interval | Jumper | Time-Out<br>Interval | Jumper | Time-Out<br>Interval |   |

|--------|----------------------|--------|----------------------|--------|----------------------|---|

| 1-D    | 0.133 sec            | 8-D    | 17.07 sec            | 12-D   | 273.1 sec            | į |

| 4-D    | 1.067 sec            | 9-D    | 34.13 sec            | 1.3~D  | 546.1 sec            | 1 |

| 5-D    | 2.133 sec            | 10-D   | 68.27 sec            | 14~D   | 1092.0 sec           | 1 |

| 6-D    | 4.267 sec            | E-D    | 136.50 sec           | F-D    | disabled             | 1 |

| 7-D    | 8.533 sec            |        |                      |        |                      | 1 |

Table 6 "WATCHDOG TIMER JUMPERS"

### **Q-TIMER INSTALLATION**

includes: Calendar Clock Software Routine Integration (Step 4)

This section provides a 6-step procedure to permit a quick installation of the Q-Timer.

#### STEP (1) BUS TERMINATION CHECK

If the Q-Timer is to be used as a bus terminator, the resistor DIP packs U2O, U32, and U36 must be installed. If not, they must be removed. If the Q-Timer is to be used as a bus terminator, it must be placed in the slot in which the bus lines end. In most backplanes this is the slot directly to the right of the CPU. If not, it can be placed in any vacant board slot (i.e. it does not require bus continuity). The power should always be off when removing or installing boards. See Section III, Figure 1, for the DIP pack locations.

### STEP (2) LINE TIME CLOCK (LTC) CHECK

Proper configuration of the LTC function is crucial to the correct operation of the LSI-11 system. Each processor and system provides various implementations of these functions. The LTC must be provided by either the system or the Q-Timer (in which case it will be a good crystal-controlled LTC). Multiple LTC registers or LTC signals will cause improper system operation. See Section IX, LINE TIME CLOCK, for an explanation of the LTC function and implementation.

#### STEP (3) ADDRESS CONFLICT CHECK

Before installing the Q-Timer, verify that there will be no address conflicts. To do this you must be in ODT. ODT may be entered on most systems by placing the RUN/HALT switch in the HALT position. When you are in ODT you will receive an "@" prompt on your console terminal. After the prompt you may type the octal memory address you wish to examine followed by a "/". If the memory address is nonexistent, which is the response you are looking for, ODT will type "?"; otherwise it will type the contents of the location.

If you obtain any response from these address checks other than "?" (i.e. ODT shows contents at one of the locations), you must decide whether to disable the function residing at the conflicting address on your present system, or to disable or move the device residing at the conflicting address on the Q-Timer. Changing any of the Q-Timer addresses will necessitate changes in the Q-Timer Software Monitor program (EPROM) as well. Contact CTI

for additional information. Q-Timer Addresses have been chosen which are either used identically for equivalent DEC functions, or are listed as unused in the current DEC Q-BUS address map.

Verify that there is no conflict with the CMOS RAM address space:

```

@766000/ ? with STD, MB, LD configuration

@766776/ ?

@

@775000/ ? with FAL, FDO configuration

@775777/ ?

@

```

This procedure checks the first and last locations of CMOS RAM. It is possible that there are address conflicts between the two limits. If you are so concerned, you should test every location between.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

Falcon installations will experience an address conflict at address 766000 due to the Falcon on-board CMOS RAM. Additionally, if the DEC FALCON ODT is in use, conflict will also occur at address 773000 (see below). This can be solved by ordering the Q-Timer with configuration FAL or FDO. See the Q-TIMER CONFIGURATIONS section of this manual.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

Verify that there is no conflict with the EPROM address space:

```

@773000/ ? with STD, LD, FAL configuration @773777/ ? @ with MB configuration @771777/ ? @ with FDO configuration @774777/ ?

```

Again, this procedure checks only the first and last location of the address space.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

Any existing boot board such as the DEC BDV11 will produce a conflict at address 773000. Additionally, many of the new generation LSI-11 system disk controllers contain on-board boots which are addressed at 773000. The controller boot must be disabled, or the Q-Timer boot address must be moved via the Q-Timer MB configuration. See the Q-TIMER CONFIGURATIONS section of this manual.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

Verify that there is no conflict with the 8-bit Output Port address space:

Verify that there is no conflict with the 8-bit Input Port address space:

```

@777240/ ?

@777242/ ?

.

.

.

.

.

.

.

.

.

.

.

```

Verify that there is no conflict with the Calendar Clock address space:

```

@777300/ ?

@777302/ ?

.

.

.

.

.

.

```

Verify that there is no conflict with the EPROM Page Register, the CMOS RAM Page Register, or the Line Time Clock Software Control Register address space:

```

@777340/ ?

@777342/ ?

@777546/ ?

```

#### STEP (4) CALENDAR CLOCK SOFTWARE INTEGRATION

The following contains software routines to integrate the Calendar Clock into RSX-11M version 3.2, RSX-11M version 4.0, or RT-11, to allow automatic setting of date and time in your operating system.

#### FOR INTEGRATION into RSX-11M, version 3.2:

Included in this section are the source and command file listings used to build a program (QTIME.TSK) which will read the calendar clock, and then set the RSX11M/S system time. Note that this program must be built with the privileged (/PR) attribute. This program illustrates one technique by which a program can execute Q-Timer EPROM subroutines. It does not link to the resident library shown below because, as a task with privileged mapping, it will already be mapped to the I/O page.

We suggest that you put QTIME.TSK into SY:[sysuic], and insert the line:

#### RUN \$QTIME

```

in your startup command file (SY:[1,2]STARTUP.CMD). This will ensure that your system loads the proper date and time every time it boots.

```

```

; QTIME.MAC

; Copyright (C) 1983 Codar Technology, Inc.

; The following listing is provided for tutorial purposes only.

; Note that this program does not check for "busy" status of the EPROM RTIME

; subroutine.

;Note that if you have chosen the MOVE BOOT configuration, change $QROM

; below from 173000 to 171000 to reflect the new EPROM Software Monitor

; starting address.

.MCALL EXIT$S

173000

; Starting address of EPROM

$QROM =

; RTIME subroutine entry (in page 0)

RTIME =

$QROM+062

$QRPAG = 177340

; EPROM page select register

; Rl --> date/time buffer

BEGIN: MOV

#ARGS,R5

CLR

SQRPAG

JSR

PC,RTIME

; Call RTIME routine in EPROM

EMT

376

; Switch to system state, with

.WORD

EXIT

; return to user state at "EXIT:"

; RO --> RSX time locations

MOV

#$TTNS-14,R0

MOV

(R1)+,(R0)+

; Year since 1900 (TTNS-14)

MOV

(R1)+,(R0)+

; Month ($TTNS-12)

MOV

#MTBL-2,R2

; R2 --> days per month table

ADD

-(R1),R2

ADD

(R1)+,R2

; R2 --> this month in days per month table

MOV

(R2),R2

; R2 := max days in this month plus one

; February?

CMP

-2(R1), #2

; If NE no

BNE

10$

#3,-4(R1)

BIT

; Yes -- leap year?

; If NE no

BNE

10$

INC

R2

; Yes -- add one for leap day

; Set RSX days per month parameter

10$:

R2,$TKPS-10

MOV

MOV

(R1)+,(R0)+

; Day ($TTNS-10)

(R1)+,(R0)+

; Hour ($TTNS-6)

MOV

; Minute ($TTNS-4)

MOV

(R1)+,(R0)+

; Second ($TTNS-2)

MOV

(R1)+,(R0)+

(R0)+

CLR

; Clear RSX clock ticks

RTS

PC

; Return to user state

EXIT:

EXIT$S

MTBL:

.WORD

32.

; January

29.

.WORD

; February (non leap years)

32.

; March

.WORD

.WORD

31.

; April

```

continued on next page

```

32.

.WORD

; May

.WORD

31.

; June

; July

•WORD

32.

; August

•WORD

•WORD

31.

; September

; October

.WORD

32.

; November

.WORD

31.

.WORD

32.

; December

ARGS:

•BYTE

1,0

; Argument list for "CALL RTIME"

.WORD

DATIME

DATIME: .BLKW

9.

;

.END

BEGIN

```

The following command file will assemble and link the QTIME task. You must ensure that the file RSX11M.STB (or RSX11S.STB, if you are building QTIME to run under an RSX-11S system) is in the directory LB:[sysuic] during the task-build. This is the file that defines the locations within the RSX executive that contain the date and time information.

The STB file will have been left in the proper directory by SYSGEN.

```

٠;

.; Copyright(C) 1983 Codar Technology, Inc.

.; The following listing is provided for tutorial purposes only.

.;

.ENABLE SUBSTITUTION

MAC QTIME=QTIME

.OPEN BUILD.CMD

.ENABLE DATA

QTIME/PR=QTIME, LB: '<SYSUIC>'RSX11M.STB/SS

PRI=148

STACK=32

UNITS=0

//

.DISABLE DATA

.CLOSE

TKB @BUILD

PIP BUILD.CMD; */DE,QTIME.OBJ; *

PIP QTIME.*/PU

*******************************

```

## END OF RSX-11M version 3.2 INTEGRATION BEGINNING OF RSX-11M version 4.0 INTEGRATION \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

### FOR INTEGRATION into RSX-11M, version 4.0:

The following program will set the date and time for RSX-11M version 4.0.

```

•ENABL LC

.TITLE QTIME Set RSX11M/S V4.0 system date/time

.MCALL STIM$C,EXIT$S

.IDENT /02.02/

```

```

; The program shown previously for RSX-11M version 3.2, will actually work under

; any version of RSX11M or RSX11S.

; However, the shorter program shown here can be used specifically under version

4.0, if the STIM$ directive was included during system generation.

\$QROM = 173000

; Starting address of EPROM

; RTIME subroutine entry (in page 0)

RTIME = $QROM+062

$QRPAG = 177340

; EPROM page select register

#ARGS,R5

; R5 --> argument list

BEGIN: MOV

; Select EPROM page 0

CLR

$QRPAG

; Call RTIME routine in EPROM

JSR

PC, RTIME

#-1,DATIME+S.TICP ; Use sysgen ticks/second parameter

MOV

; Set RSX system time

STIM$C DATIME

EXIT$S

ARGS:

•BYTE

1,0

; FORTRAN compatible arg list for CALL RTIME

•WORD

DATIME

DATIME: .REPT

; Buffer for date/time

; (Init to "default")

•WORD

-1

• ENDR

.END

BEGIN

END OF RSX-11M version 4.0 INTEGRATION

BEGINNING OF RT-11 INTEGRATION

FOR INTEGRATION into RT-11:

The following program will set the date and time for RT-11 version 4.

Include the command "RUN QTIME" in the file STARTS.COM .

Information

regarding older RT-11 versions 2 and 3 is available on request.

; Copyright 1983, Codar Technology Inc.

; Note that if you have chosen the MOVE BOOT configuration, change $QROM below

from 173000 to 171000 to reflect the new EPROM Software Monitor starting

; address.

.MCALL

.EXIT,.SDTTM

.GLOBL

JTIME

$QROM=173000

; Starting address of EPROM

; RTIME subroutine entry (in page 0)

RTIME=$QROM+062

$MUL=$QROM+040

; $MUL subroutine

$QRPAG=177340

MOV #ARGS, R5

BEGIN:

; R5 --> argument list

CLR $QRPAG

JSR PC, RTIME

; Call RTIME subroutine in EPROM

```

continued on next page

```

MOV R1,R5

; Copy pointer

MOV (R5)+,R2

; Get year since 1972 in <04:00>

SUB #72.,R2

MOV (R5)+R0

plus month of year in <13:10>

MOV

#2000,R1

JSR

PC,$MUL

BIS

R1,R2

MOV

(R5)+,R0

plus day of month in <09:05>

MOV #40,R1

JSR PC, $MUL

R1,R2

BIS

; Date is 1st word in RT list

MOV R2, RTDTM

MOV #JHR,RO

; Copy hours for CALL JTIME

MOV (R5)+,(R0)+

MOV (R5)+,(R0)+

; Copy minutes

MOV (R5)+,(R0)+

; Copy seconds

CLR (R0)+

; No ticks for now

MOV

#JARGS,R5

; Convert to RT-style 32-bit integer

JSR PC, JTIME

.SDTTM #AREA, #RTDTM ;

•EXIT

2

.BLKW

AREA:

ARGS:

.BYTE

1.0

.WORD

DATIME

DATIME:

.BLKW

9.

JARGS:

.BYTE

5,0

.WORD

JHR

.WORD

JMI

.WORD

JSE

.WORD

JTI

.WORD

RTDTM+2

1

JHR:

.BLKW

1

JMI:

.BLKW

1

JSE:

.BLKW

1

JTI:

.BLKW

3

RTDTM:

.BLKW

.END

BEGIN

*************************************

```

### END OF SOFTWARE INTEGRATION

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

#### STEP (5) SYSTEM STARTUP

Once the board is in place and the power restored, the system should be started at location 773000. This may happen automatically on power-up if your LSI-11 has been so configured, or it may be done from ODT by typing "773000G" for STD, LD, and FAL configurations; "771000G" for MB confuration; or "774000G" for FDO configuration.

#### STEP (6) Q-TIMER SOFTWARE MONITOR OPERATION

The Q-Timer Software Monitor (as delivered) should type the time and date and a prompt "\*" (if the Q-Timer has previously been configured to auto-boot a device, it will attempt to do so after printing the date and time). following section of this manual explains the use of the Software Monitor.

### **Q-TIMER SOFTWARE MONITOR OPERATION**

includes: Boot Commands

Setting the Calendar Clock Time EPROM Page Register Function

Please note that a version of the Q-Timer is available which includes console ODT for FALCON SBC 11/21 systems. With this feature, you can have ODT without tying up the 11/21's on-board memory sockets which otherwise must be used for the DEC Macro-ODT chips. Call CTI for further information.

The EPROM Q-Timer Software Monitor code resides at the standard LSI-11 restart address of 773000 octal with Q-Timer configurations STD, LD, or FAL; at address 771000 octal with Q-Timer configuration MB; or at address 774000 with Q-Timer configuration FDO. If your LSI-11 CPU is configured for automatic boot on power-up, it will automatically go to 773000 and, if the Q-Timer has configuration STD, LD, or FAL, enter the Q-Timer Software Monitor. If the LSI-11 is configured for ODT mode on power-up (i.e. gives you an "@" prompt), the user should type 773000G or 771000G or 774000G to enter the Software Monitor routine.

If you have set the Q-Timer to auto-boot a designated hardware device (using the "S" command as explained later in this section), it will print the date and time as shown below and then attempt to boot the selected device. You can abort this auto bootstrap operation by typing two or three <CTRL C>'s immediately after the date/time message is printed.

If you have not set the Q-Timer to auto-boot, the Software Monitor will print to the system console device the day/date/time and the version number and the processor type, followed by a prompt. For example:

MON 24-MAY-82 16:28:31 V03.00 11/23

If you have the LED/Switch Panel (Test Plug) plugged onto the Q-Timer's 34-pin Connector (I/O Port), the LED's will flash briefly during power-up. The LED's are turned on (i.e. the parallel outputs are set to 1), a read/write check of the Q-Timer's CMOS RAM is performed, and if it succeeds the LED's are then turned off (i.e. the parallel outputs are cleared to 0). If the system hangs with the LED's illuminated a CMOS RAM failure is indicated. Note this is an actual RAM error, and is not caused by loss of battery backup power. Installation of the LED/Switch Panel is not mandatory.

The user may next enter (in response to the Q-Timer's "\*" prompt) one of eight commands: "E", "T", "J", "S", "B", "1", "2", or "A" followed by a carriage return.

## EXITING THE Q-TIMER MONITOR: "E"

The "E" command may be entered in response to the Q-Timer's "\*" prompt to cause an exit to console ODT. This is useful in some systems on which the BREAK feature is disabled. Q-Timer execution can be resumed via the ODT "P" command if relevant system status is not changed (e.g. PC, PS, registers, EPROM and CMOS RAM pages etc.).

### SETTING THE CALENDAR CLOCK TIME: "T"

Typing "T" yields:

\* DDD DD-MM-YY HH:MM

Thus the Software Monitor indicates the exact format for time information entry ("-" is the prompt). Leading zeros must be typed or the format will not be accepted.

Typing a RETURN without entering all time information will cause the current Calendar Clock date and time to be printed. To set the time, however, the user should type the format indicated. For example, the user may enter:

TUE 05-MAY-82 16:42

Seconds are cleared when you type <RETURN>.

NOTE: to handle leap year correctly, the Q-Timer's date and time must be set (using the Q-Timer monitor's "T" command) during the interval between 1-JAN 00:00:00.0 and 28-FEB 23:59:59.9 of each leap year.

# JUMP COMMAND: "J"

"J" is the jump command and can be used to transfer control to any location in the EPROM (by PDP-11 convention control must be to a word address, not a byte address). "J" must be followed by the octal jump address which can range from 00000 to 17776. This command allows implementation of customer generated programs, diagnostics, etc.

## AUTOMATIC BOOT: "S"

"S" is the set automatic boot command and is used to specify a device for automatic boot when the Software Monitor is entered (this automatic device specification is stored in the last page of the CMOS memory). "S" must be followed by one of the same device abbreviations as given for the "B" boot command explained below. The automatic boot is cancelled by typing S<RETURN>.

If a device is selected for automatic boot, the question arises as to how one may obtain the Q-Timer Software Monitor prompt since every time the Software Monitor is entered, it automatically boots the device. There are two methods: take the current boot device off-line, or type two or three <CTRL C>'s immediately after the Q-Timer prints out the initial date/time (upon power up).

The "S" command is very powerful, as it eliminates the need to remove a board and change jumpers or DIP switches to select a different boot device. The selected boot device is protected with a series of check bits in CMOS RAM. If an invalid boot device is detected, control returns automatically to the Q-Timer Monitor. This virtually eliminates the possibility of an attempted boot from an erroneous device due to corruption of the Q-Timer CMOS RAM.

BOOT COMMANDS: "B"

"B" is the boot command, and must be followed by one of the two or three-character abbreviations listed in Table 3, Section III.

#### HARDWARE DEVICES

With the 2-character device abbreviations listed in the top half of Table 3, one can add an optional unit designator. As an example, "B MT2" will attempt to boot from unit 2 of the system tape drive. The space after the B is automatically echoed.

#### SOFTWARE FEATURES

"MDO for 16 or 18-bit systems; MD1 for 22-bit systems."

This performs a test of the LSI-11 main memory. On unmapped systems, memory will be tested up to the limit of 56 KB. If the processor has memory management hardware, it will be employed to test memory up to the limit of 248 KB on 18-bit systems, or 4088 KB on 22-bit systems.

A message in the format

"[mmmmmm] aaaaaa cccccc vvvvvv" (all values are octal)

will be printed for each failing word of memory encountered. "vvvvvv" is the incorrect value actually read from the faulty cell, while "cccccc" is the value which should have been returned. For unmapped systems, "aaaaaa" is the physical address (0 - 157776) of the bad cell. For 18-bit or 22-bit mapped systems, "mmmmm" is the content of the MMU page address register (0 - 177600) and "aaaaaa" is the virtual address (1 - 17776), mapping the bad cell. The physical address (P) can be computed as follows:

P = (mmmmm \* 100) + aaaaaa (all values are octal)

For example, the line

17400 7746 0 2

indicates that physical location 1740000 + 7746, or 1747746, read back as 2, when it should have contained a 0.

"OB"

Other Boot provides a means of transferring control to other locations in memory. If you have a Q-Timer with an alternate EPROM address, then "B OB" will transfer control to 773000 octal. It may also be used in conjunction with the "A" command to transfer control to anywhere in the lower 56KB of main memory.

"TT"

"B TT" executes a program which allows the local computer to act as a "terminal emulator" (or "virtual terminal") for a remote computer. In this terminal emulator mode, the local computer is transparent to the local (user) terminal/console. Thus the local terminal interacts in a direct manner with the remote computer. In this mode the transparent local computer maintains a

64-character buffer for characters received from the remote computer for transmission to the local terminal. If the buffer is about to overflow, an X-off character is sent to the remote computer. When the buffer is almost empty an X-on character is sent. If the remote computer responds to these control characters, then it is not necessary to match the baud rates between the local terminal and the remote computer. Otherwise the remote computer baud rate must be less than or equal to the local terminal baud rate to prevent data loss from the remote computer.

"SL"

All SL commands and the TT command use the serial line interface at addresses 776500-776507.

"SL1"