Technical Manual No. 799804-800 Revision F

## ADDENDUM H - EMBEDDED FORMATTER (DUAL-MODE)

Cipher Data Products 10225 Willow Creek Road San Diego, California 92131

•Copyright 1982 by Cipher Data Products, Inc. Printed in U.S.A. January 1984

.

#### ADDENDUM H

## DUAL-MODE EMBEDDED FORMATTER

This addendum presents a physical and electrical description of the dual-mode embedded formatter installed on the Cipher Magnetic Tape Transport to which this manual is assigned. The addendum, together with the special-configuration also included in the manual, presents all additional operational and maintenance information necessitated by the addition of the formatter to the transport. (For design information, refer to the product specification.) Please read this addendum, the supplement, and the manual thoroughly before operating or placing the transport into the system.

## TABLE OF CONTENTS

| SECTION | TITLE                                          | AGE NO. |

|---------|------------------------------------------------|---------|

| I       |                                                | 1-1     |

|         | PHYSICAL DESCRIPTION                           | 1-1     |

|         | FUNCTIONAL DESCRIPTION                         | 1-1     |

|         | MECHANICAL AND ELECTRICAL SPECIFICATIONS       | -       |

|         | INTERFACE SPECIFICATIONS                       | -       |

| П       | INSTALLATION, SWITCH SETTINGS, AND JUMPERS     | 2-1     |

|         | INSTALLATION                                   | 2-1     |

|         | SWITCHES                                       | 2-1     |

|         | Density Selection                              | 2-1     |

|         | Parity Selection                               | 2-1     |

|         | Formatter Address                              | 2-1     |

|         | Speed Selection                                | 2-1     |

|         | Host Transport Address                         | 2-2     |

|         | JUMPER OPTIONS                                 | 2-2     |

| 111     | INTERFACE CONNECTIONS                          | 3-1     |

|         | CONNECTORS                                     | 3-1     |

|         | PIN ASSIGNMENTS                                | 3-1     |

|         | FORMATTING INTERFACING                         | 3-8     |

|         | INTERFACE INPUTS (CONTROLLER TO FORMATTER)     | ) 3-8   |

|         | Initiate Command (IGO)                         | 3-8     |

|         | Command Lines                                  | 3-8     |

|         | Rewind (IREW)                                  | 3-9     |

|         | Off-line Command (IOFL-IRWU)                   | 3-9     |

|         | Last Word (ILWD)                               | 3-10    |

|         | Formatter Enable (IFEN)                        | 3-10    |

|         | Write Data Lines, Write Parity                 | 3-10    |

|         | Load and On-Line (ILOL)                        | 3-10    |

|         | INTERFACE OUTPUTS<br>(FORMATTER TO CONTROLLER) | 3-10    |

|         | Identification/Check Character Gate            | 3-11    |

## TABLE OF CONTENTS (Continued)

SECTION

III Con't.

| Т | 17 | П | F | - |

|---|----|---|---|---|

| Hard Error (IHER)                             | 3-11 |

|-----------------------------------------------|------|

| Corrected Error (ICER) (PE Only)              | 3-12 |

| File Mark (IFMK)                              | 3-12 |

| Transport Address                             | 3-12 |

| Write Strobe (IWSTR)                          | 3-12 |

| Read Strobe (IRSTR)                           | 3-12 |

| Read Data Lines (IRP, IR0-IR7)                | 3-12 |

| INTERFACE OUTPUTS<br>(FORMATTER TO TRANSPORT) | 3-12 |

| Transport Select Lines (ISLT0-ISLT3)          | 3-12 |

| Synchronous Forward Command (ISFC)            | 3-12 |

| Synchronous Reverse Command (ISRC)            | 3-13 |

| Rewind Command (IRWC)                         | 3-13 |

| Off-Line Command (IOFC)                       | 3-13 |

| Set Write Status (ISWS)                       | 3-13 |

| Overwrite (IOVW)                              | 3-13 |

| Read Threshold 2 (IRTH2)                      | 3-13 |

| Read Threshold I (IRTHI)                      | 3-13 |

| Write Amplifier Reset (IWARS)                 | 3-13 |

| Write Data Strobe (IWDS)                      | 3-14 |

| Write Data (IWDP, IWD0-IWD7)                  | 3-14 |

| Data Density Select (IDDS-Optional)           | 3-14 |

| Load and On Line (ILOL)                       | 3-14 |

| INTERFACE INPUTS<br>(TRANSPORT TO FORMATTER)  | 3-14 |

| Ready (IRDY)                                  | 3-14 |

| On Line (IONL)                                | 3-14 |

| Rewinding (IRWD)                              | 3-14 |

| File Protect (IFPT)                           | 3-14 |

| Load Point (ILDP)                             | 3-14 |

| End of Tape (IEOT)                            | 3-15 |

| Data Density Indicator (IDDI)                 | 3-15 |

| NRZI (INRZ)                                   | 3-15 |

# TABLE OF CONTENTS (continued)

| SECTION    | TITLE                                     | PAGE NO. |

|------------|-------------------------------------------|----------|

| III Con't. | Seven-Track (I7TR)                        | . 3-15   |

|            | Single (ISGL)                             | . 3-15   |

|            | Speed (ISPEED)                            | . 3-15   |

|            | Read Data Strobe (IRDS) (NRZI Only)       | . 3-15   |

|            | Read Data Lines (IRDP, IRD0-IRD7)         | . 3-15   |

| IV         | OPERATION                                 | . 4-1    |

|            | NRZI MODE                                 | . 4-1    |

|            | Gap Generation                            | . 4-1    |

|            | Writing                                   | . 4-4    |

|            | Reading                                   | . 4-4    |

|            | File Mark                                 | . 4-4    |

|            | Parity                                    | . 4-4    |

|            | Density Selection                         | . 4-4    |

|            | BCD Zero Conversion                       | . 4-5    |

|            | Error Checking                            | . 4-5    |

|            | Options                                   | . 4-5    |

|            | PHASE-ENCODE MODE                         | . 4-5    |

|            | Identification Burst                      | . 4-5    |

|            | Preamble                                  | . 4-5    |

|            | Postamble                                 | . 4-5    |

|            | Data                                      | . 4-6    |

|            | File Mark                                 | . 4-6    |

|            | Gaps                                      | . 4-6    |

|            | Parity                                    | . 4-6    |

|            | Dropout and Error Correction              | . 4-6    |

| V          | DETAILED ELECTRICAL AND LOGIC DESCRIPTION | . 5-1    |

|            |                                           | . 5-1    |

|            | INTERNAL FORMATTER SIGNALS                | . 5-1    |

|            | INTERFACE SIGNALS                         | . 5-1    |

## TABLE OF CONTENTS (continued)

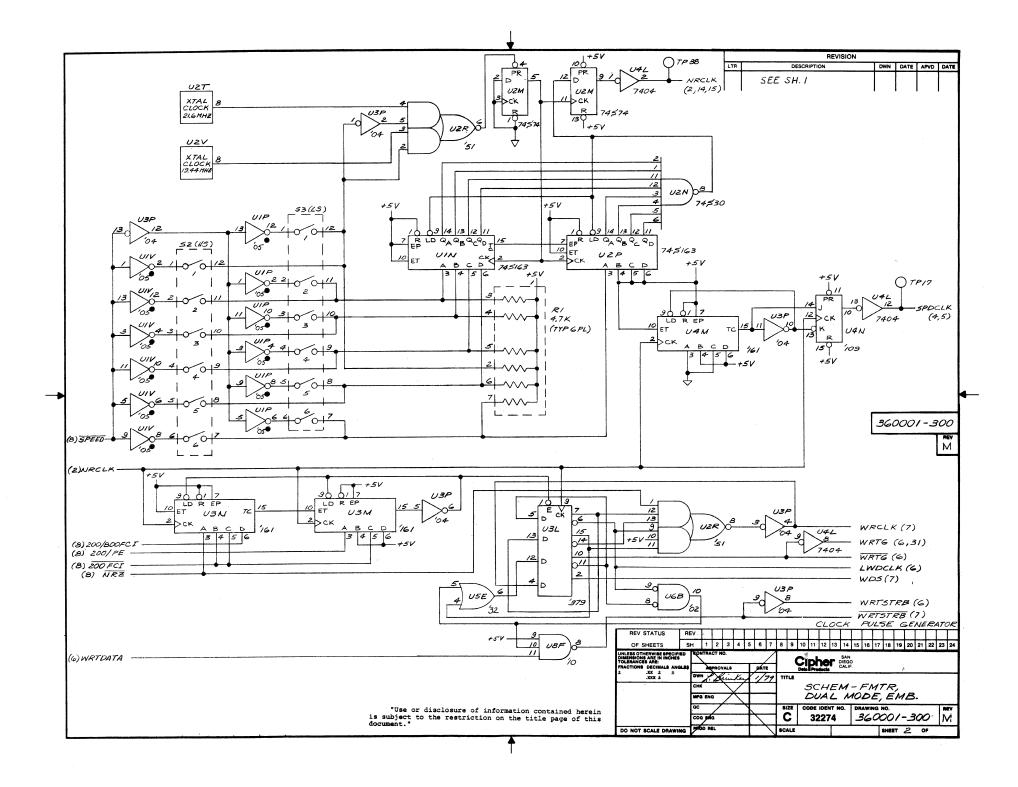

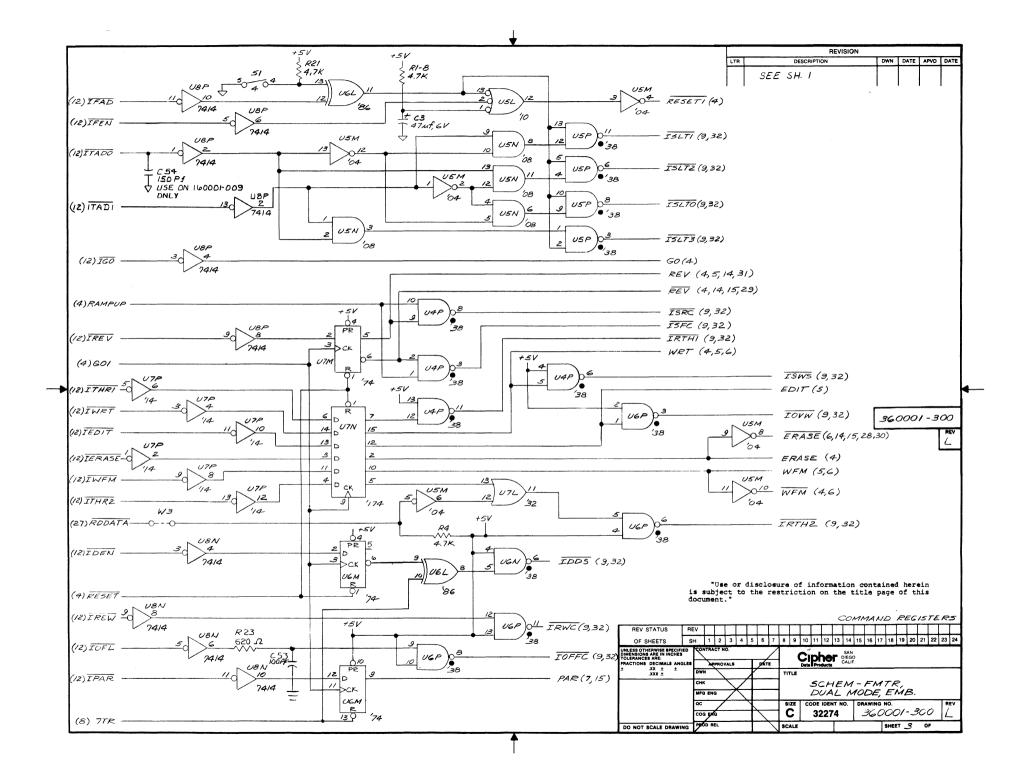

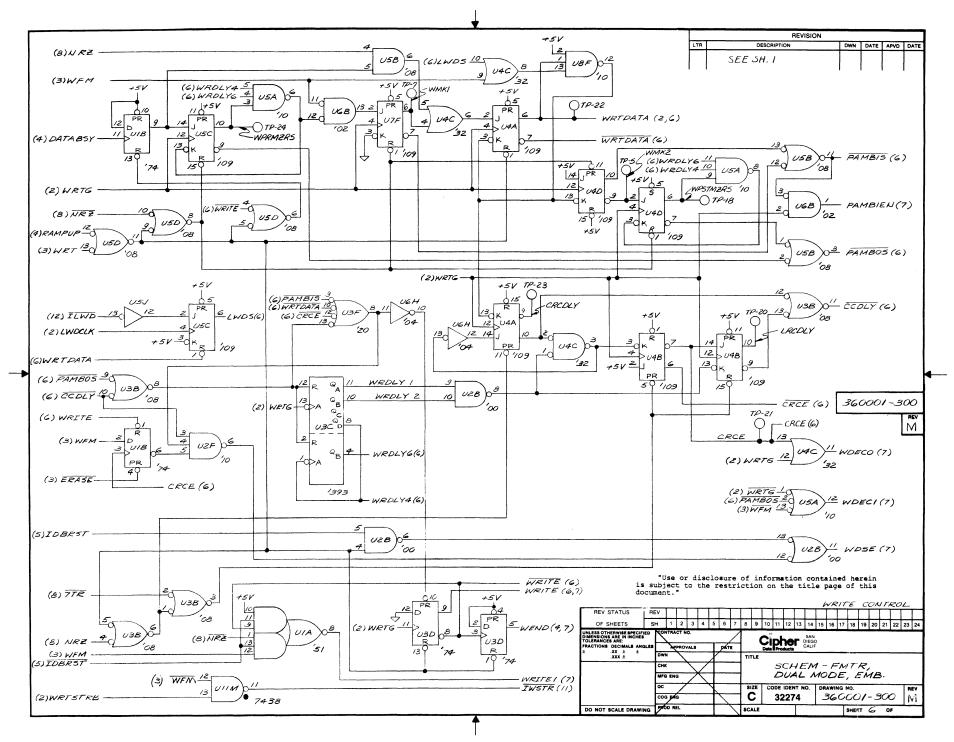

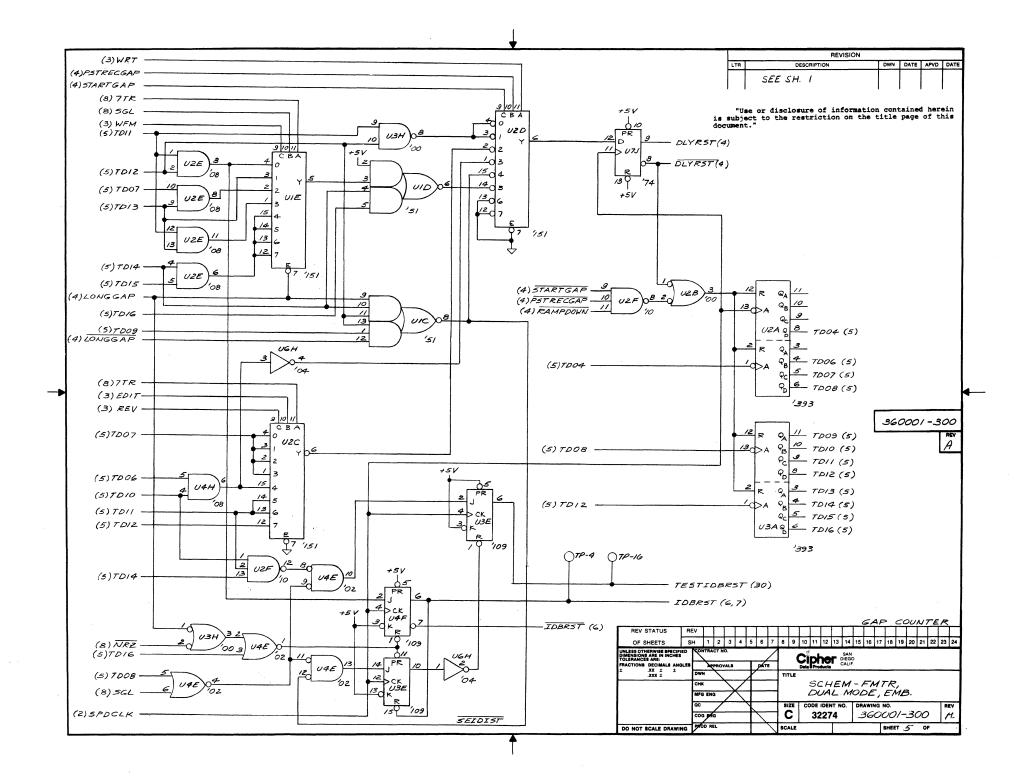

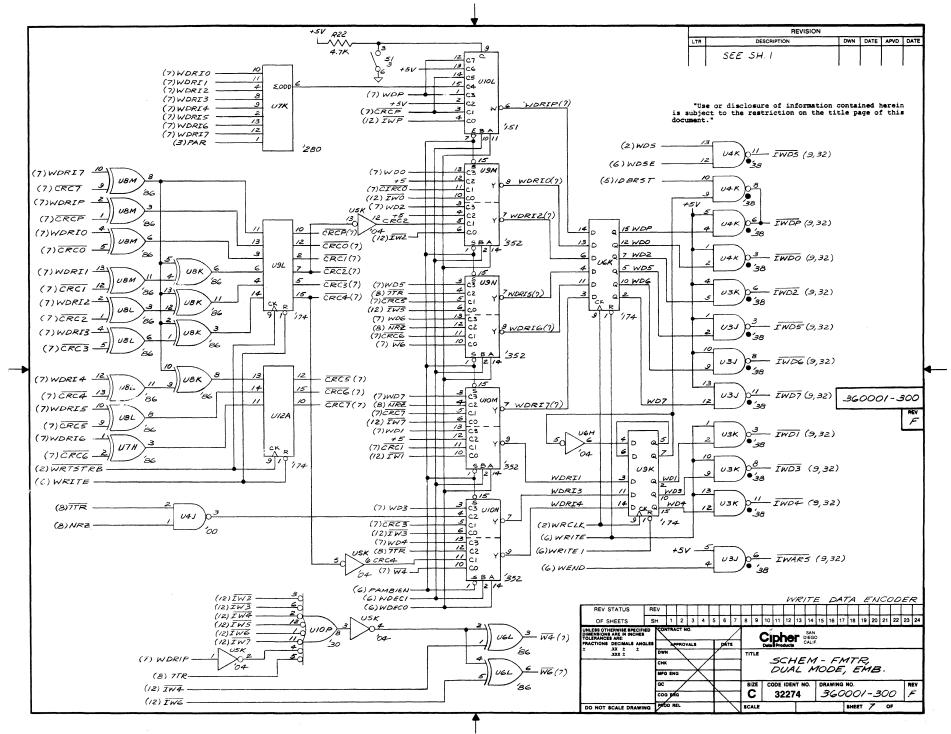

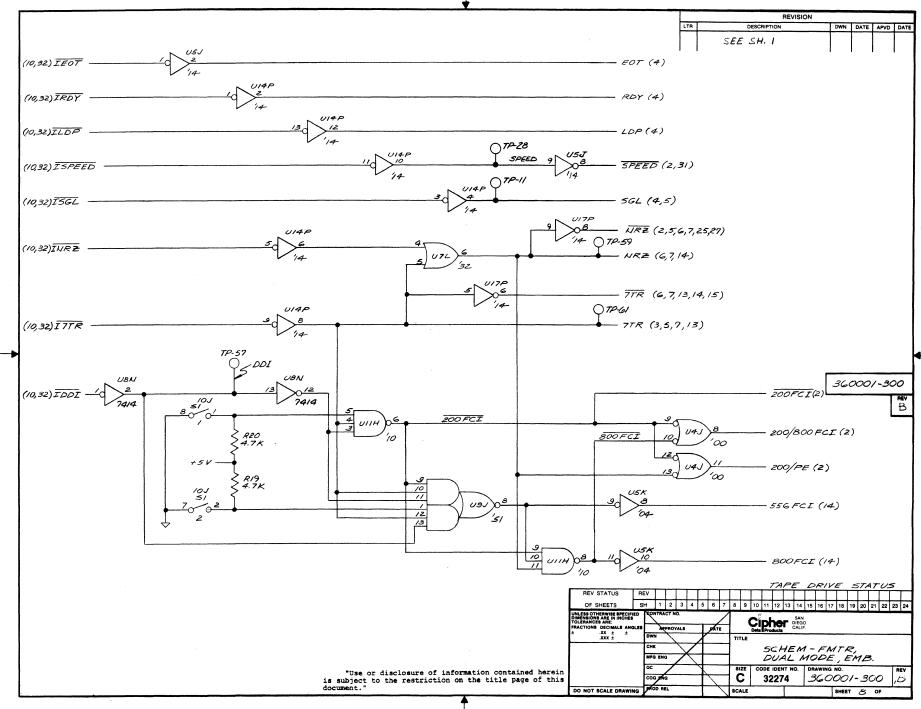

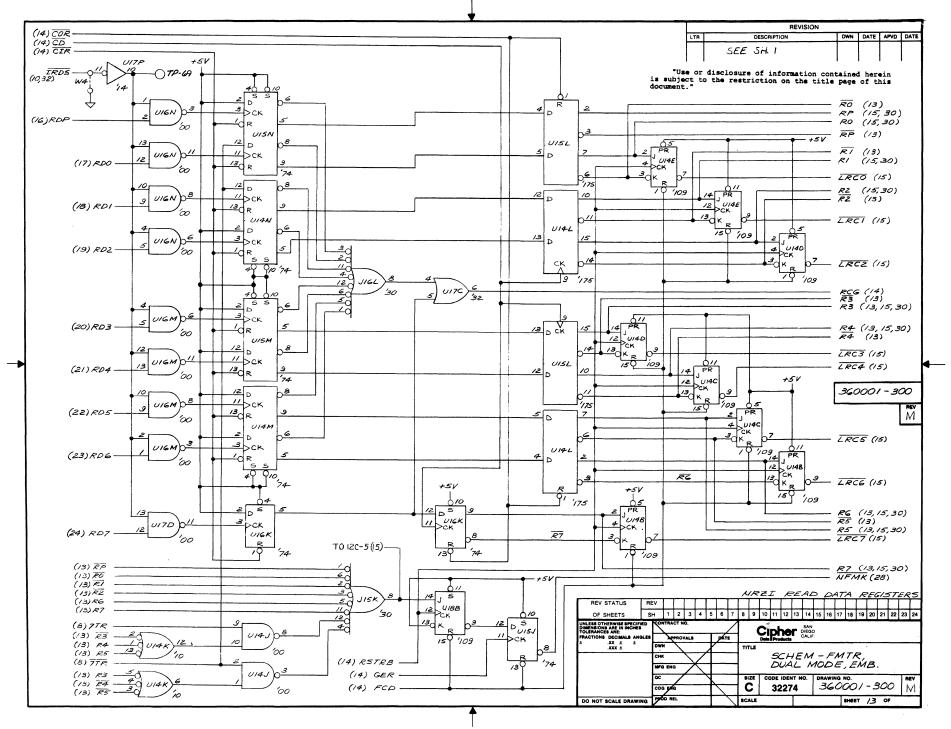

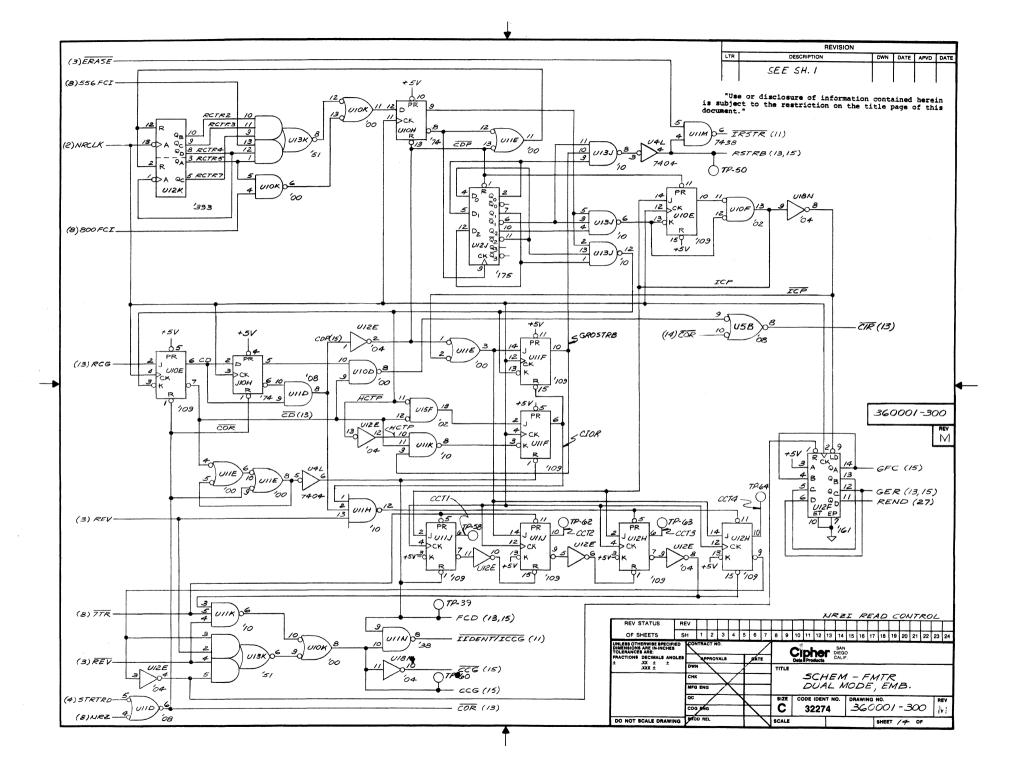

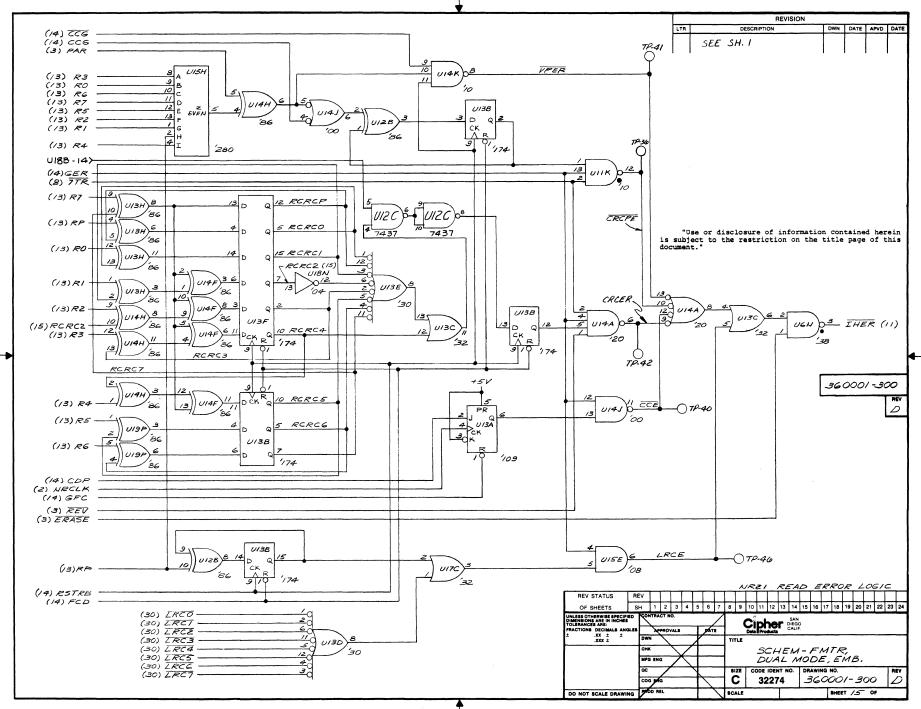

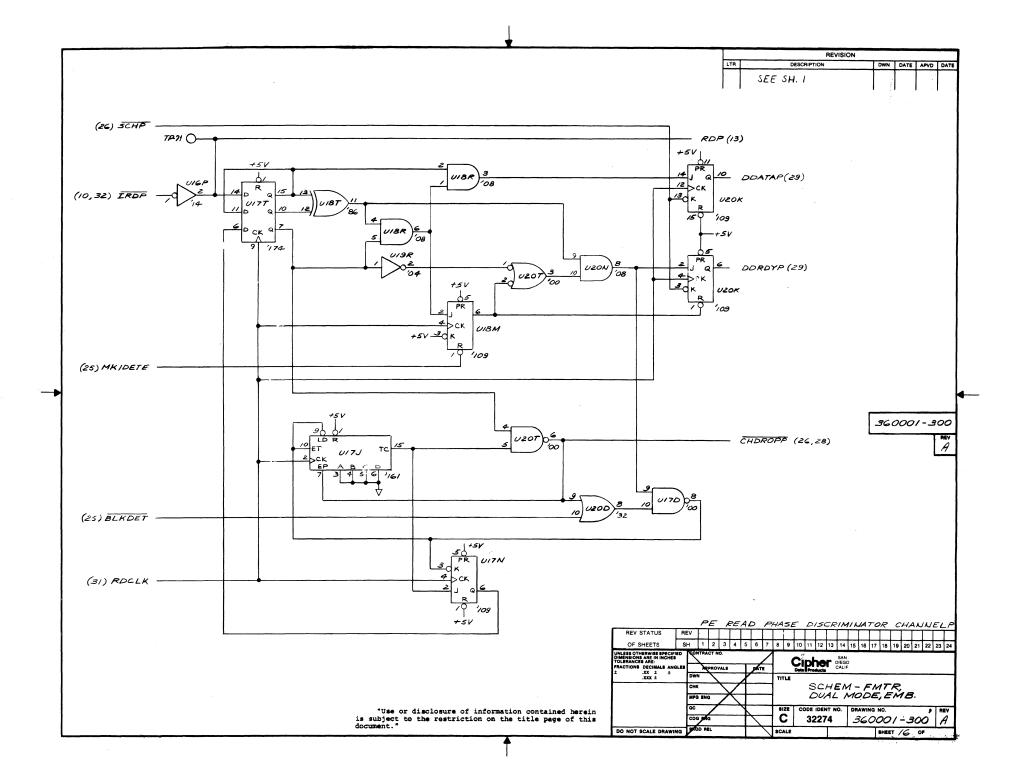

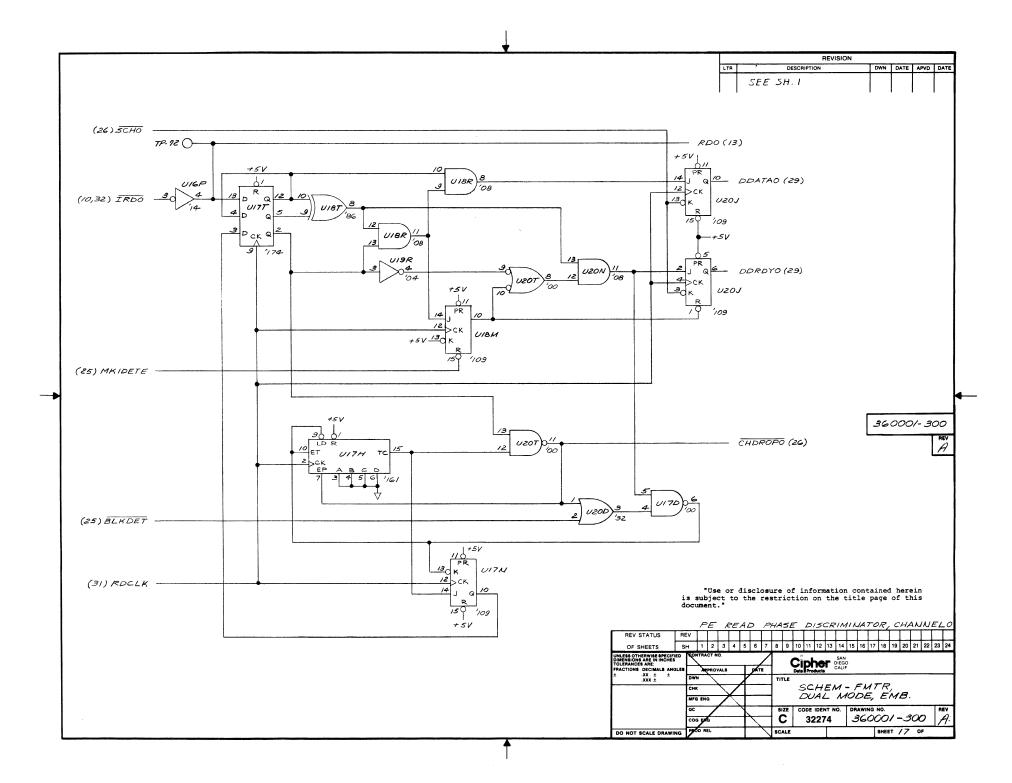

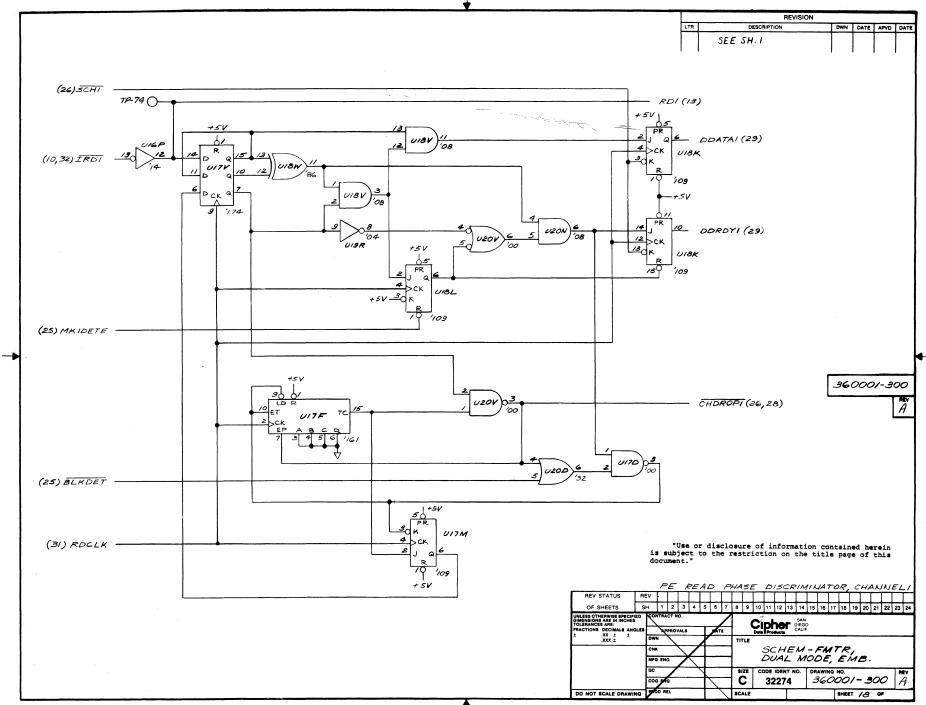

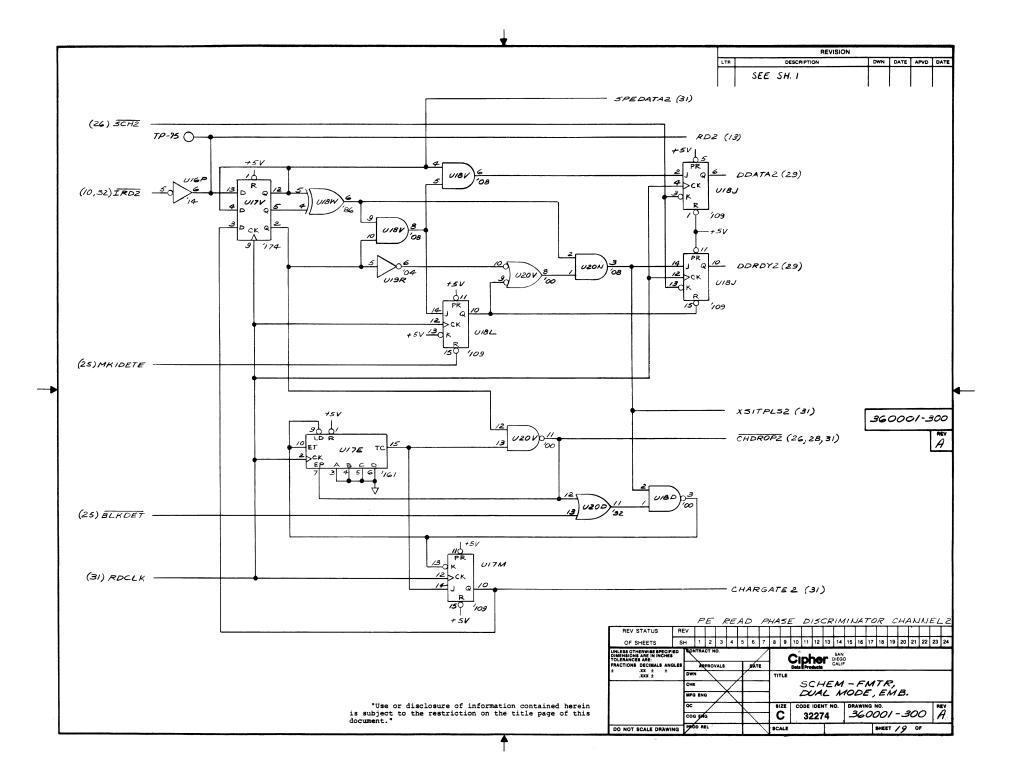

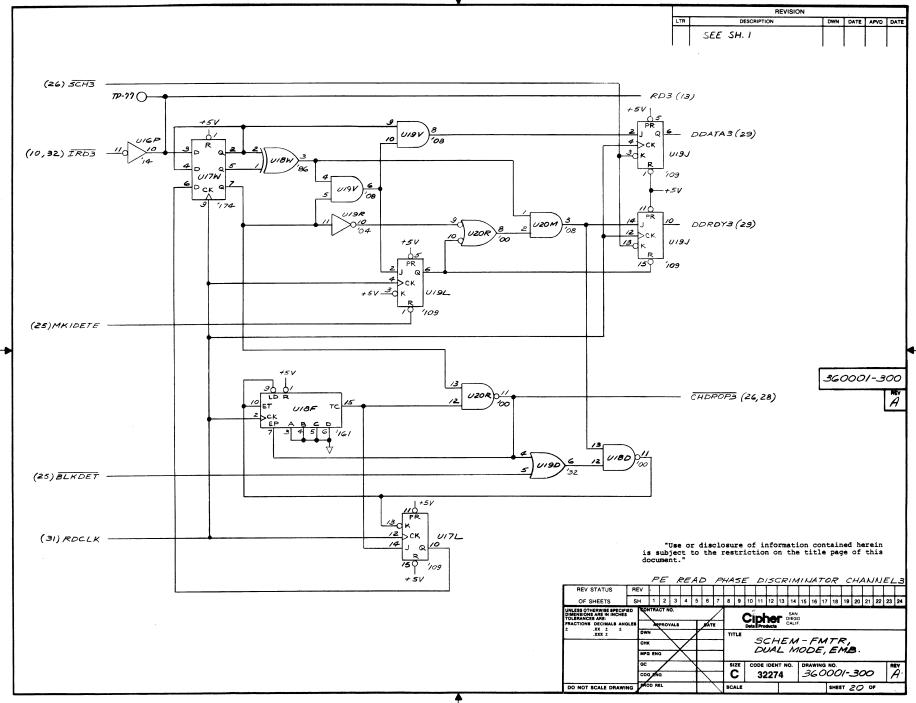

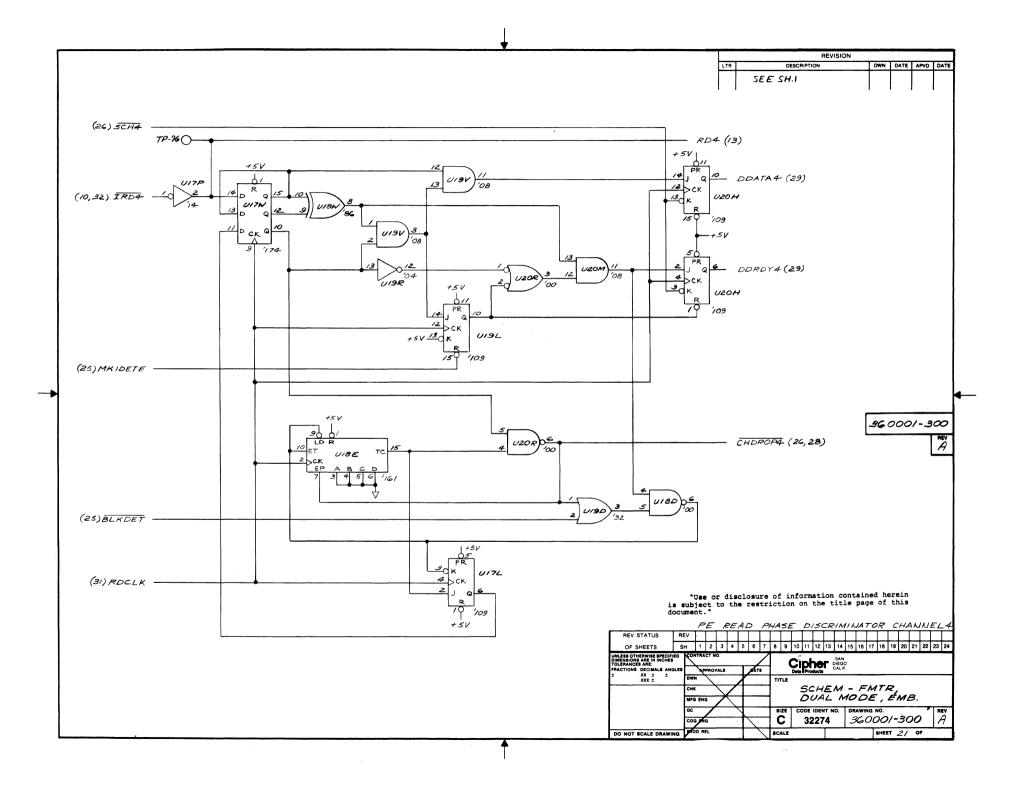

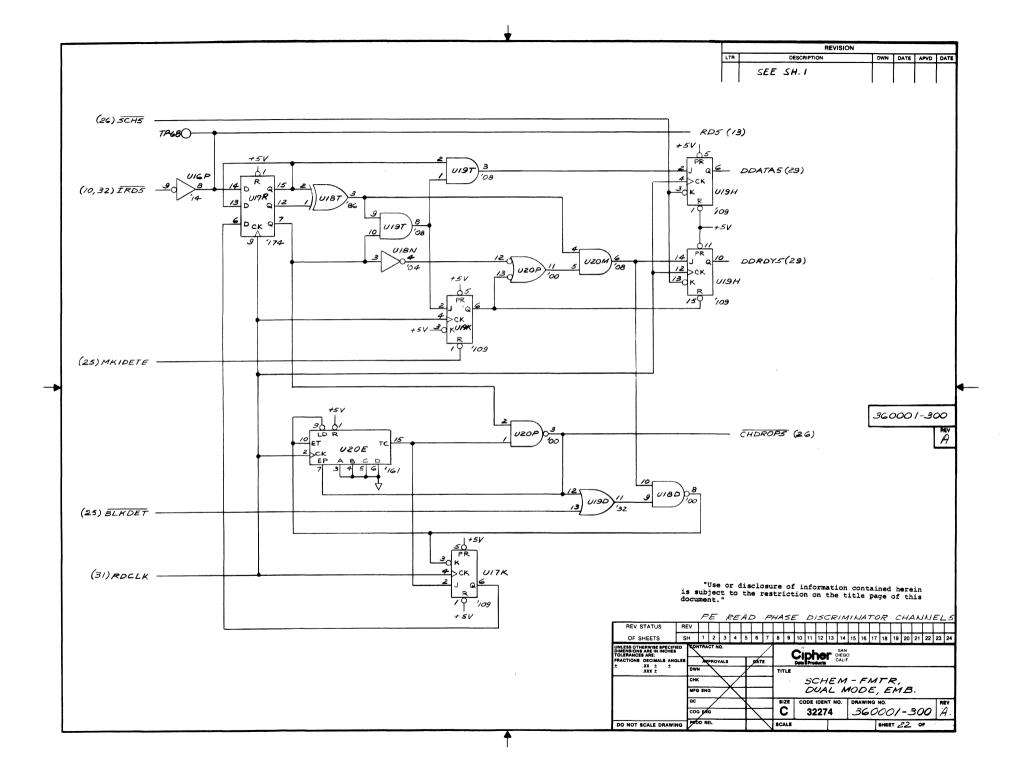

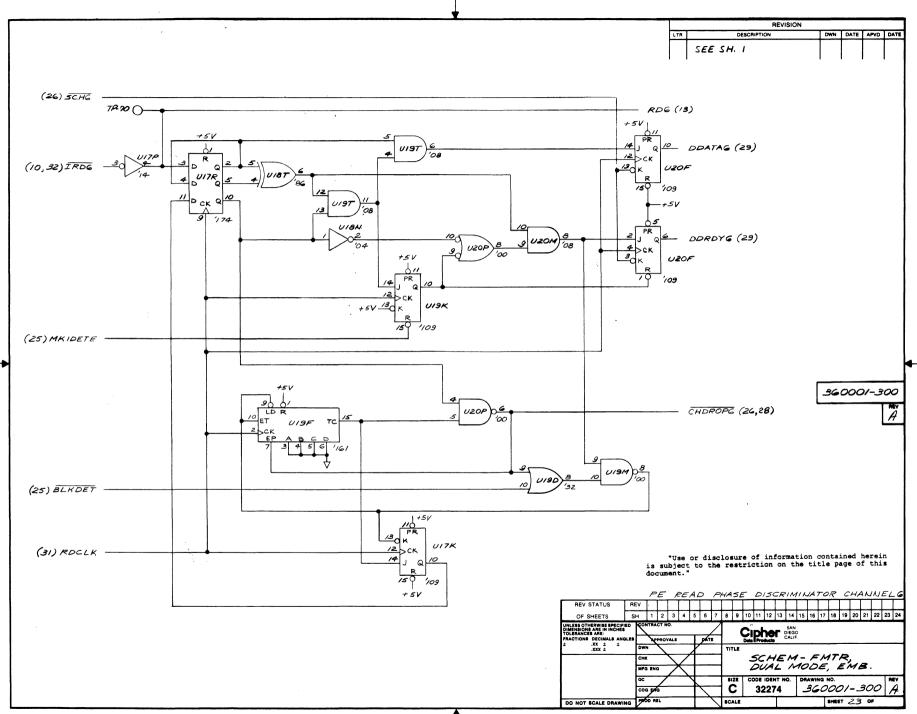

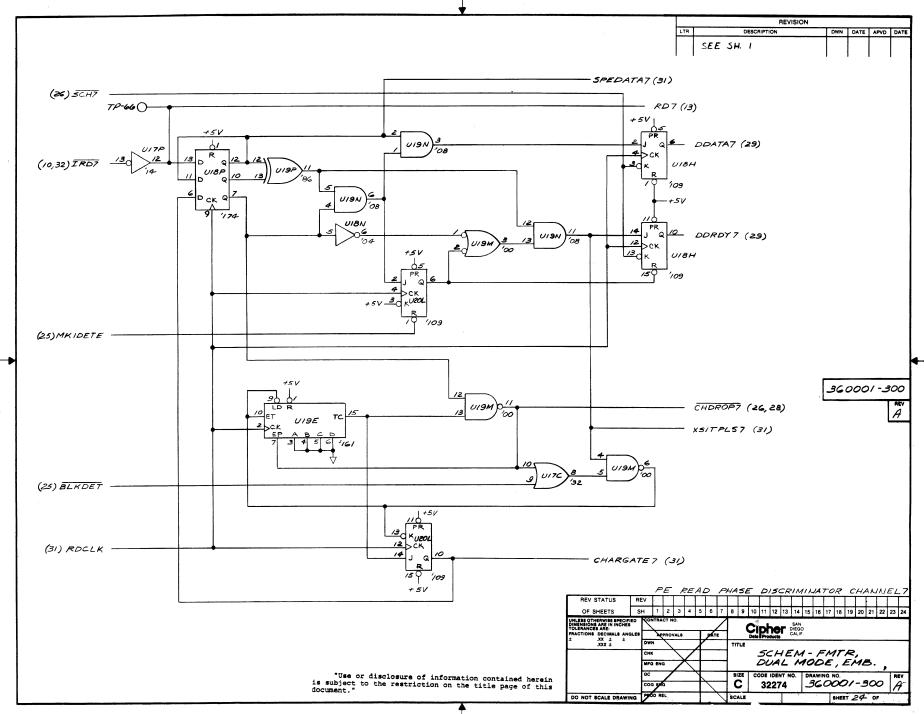

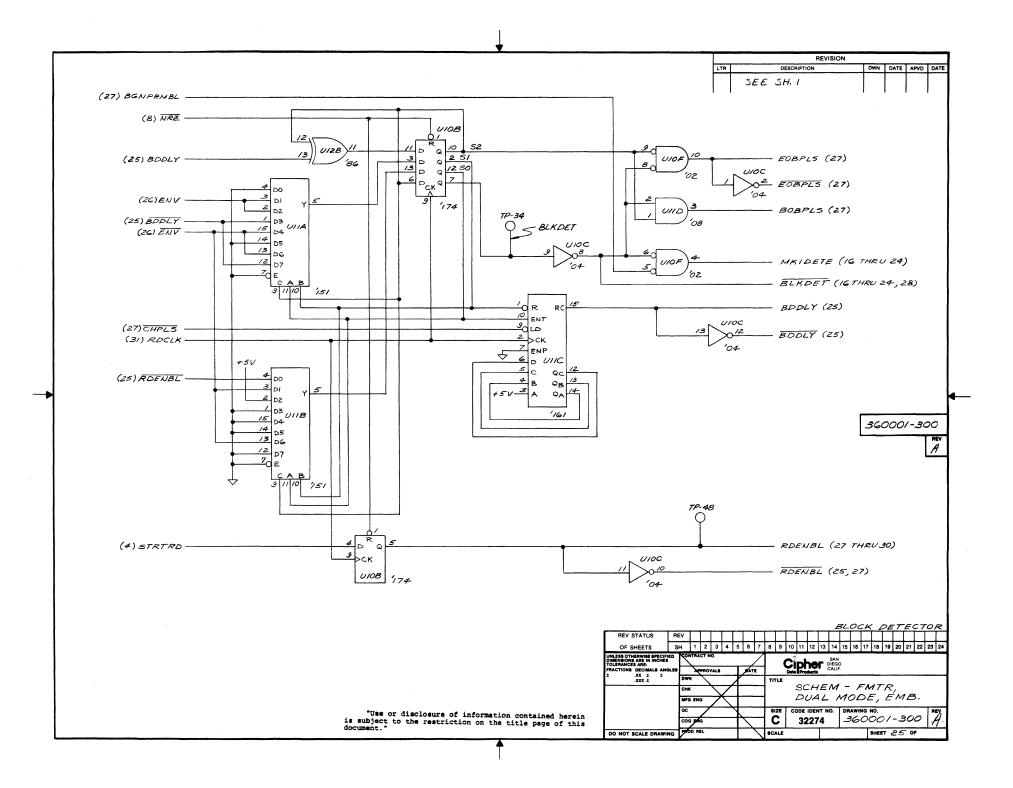

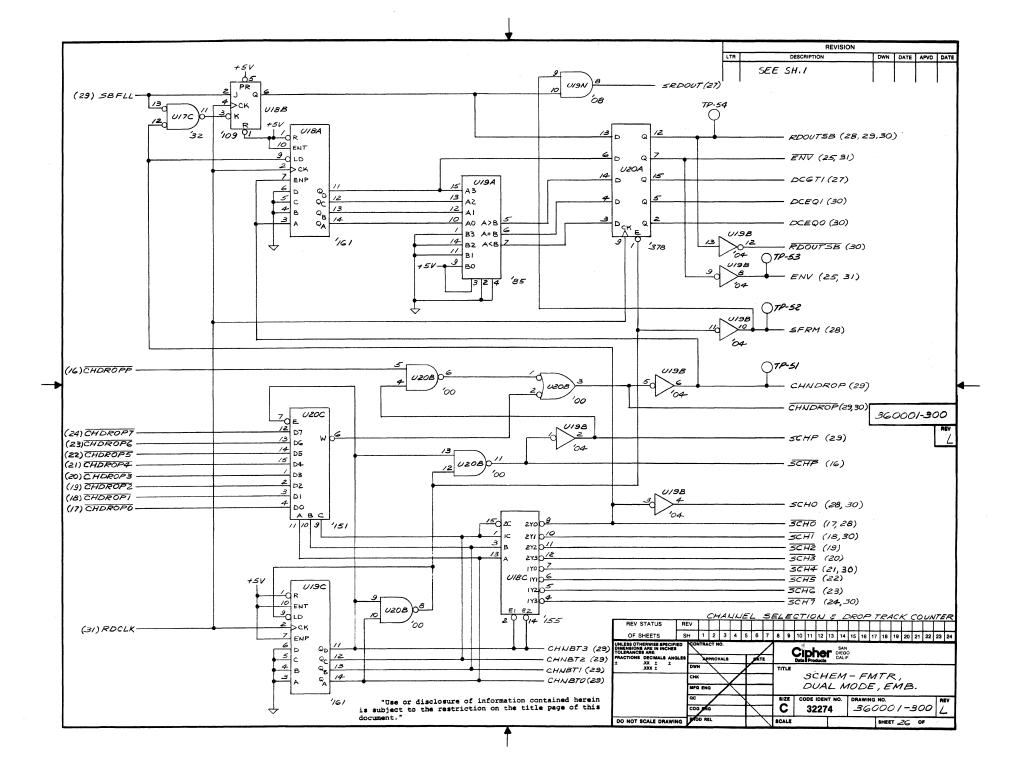

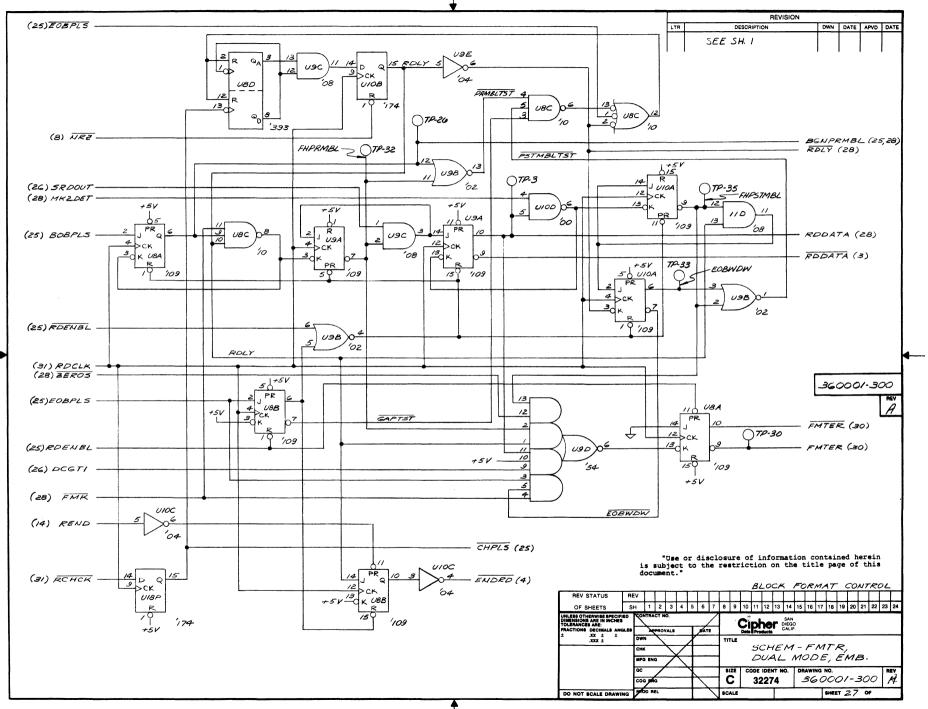

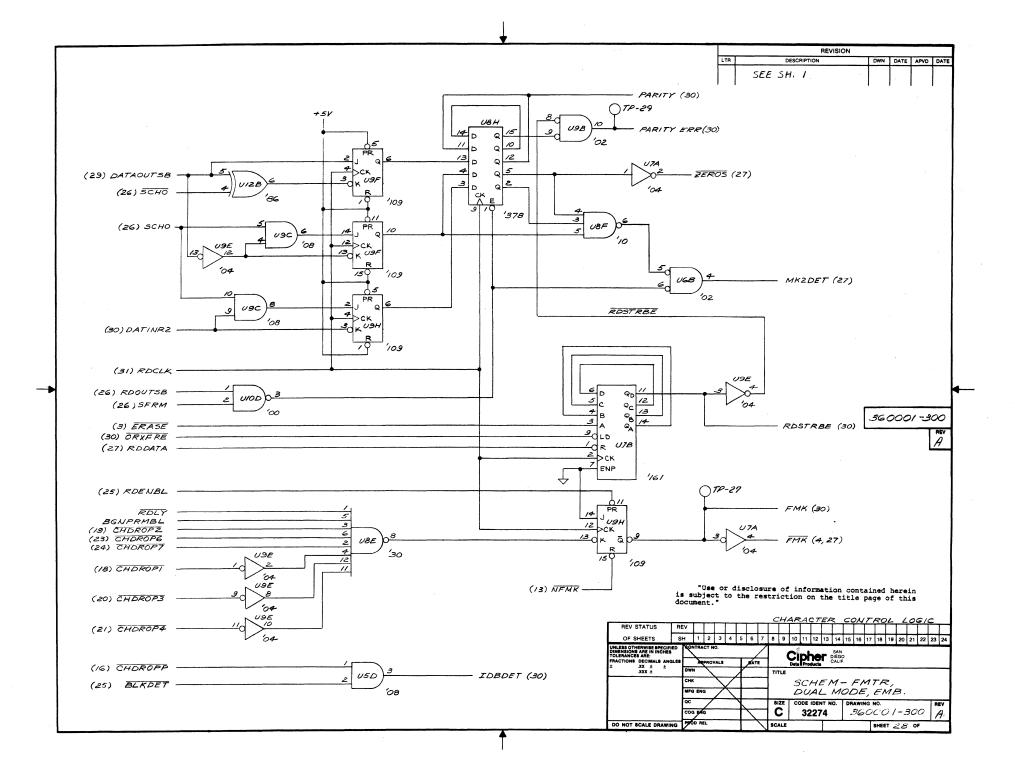

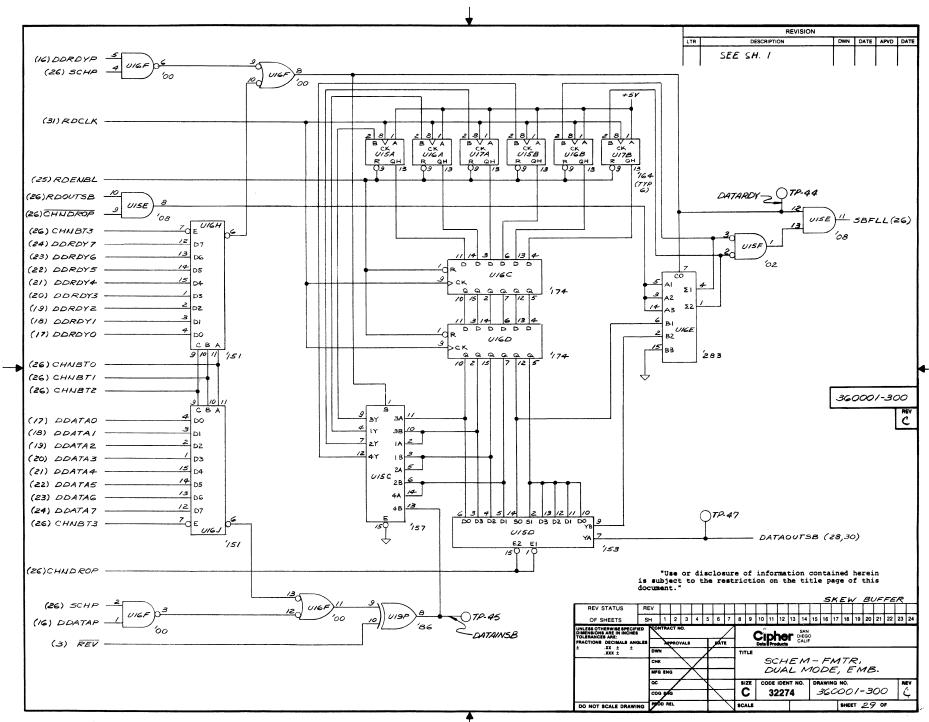

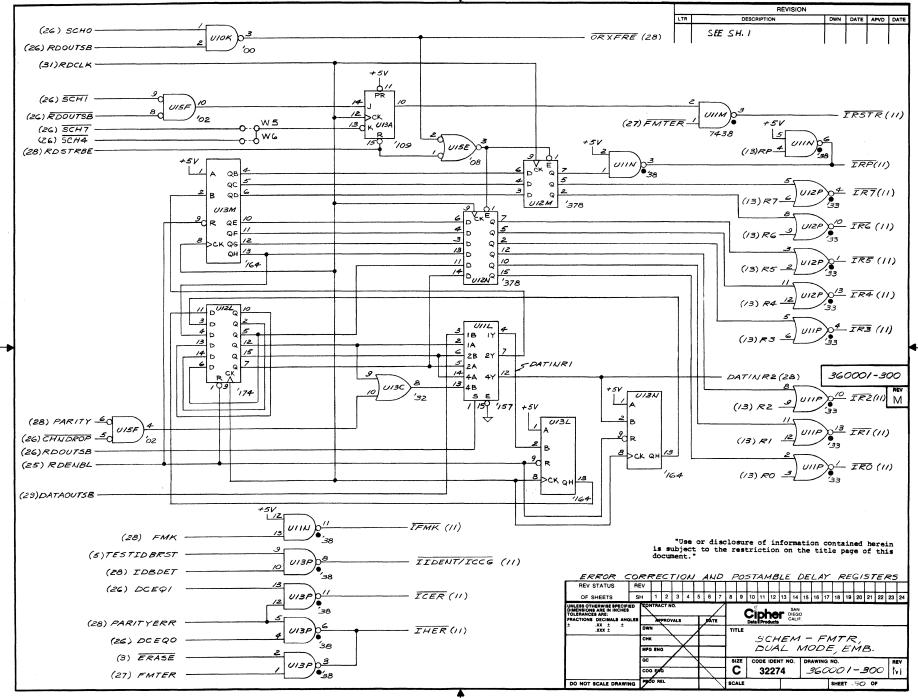

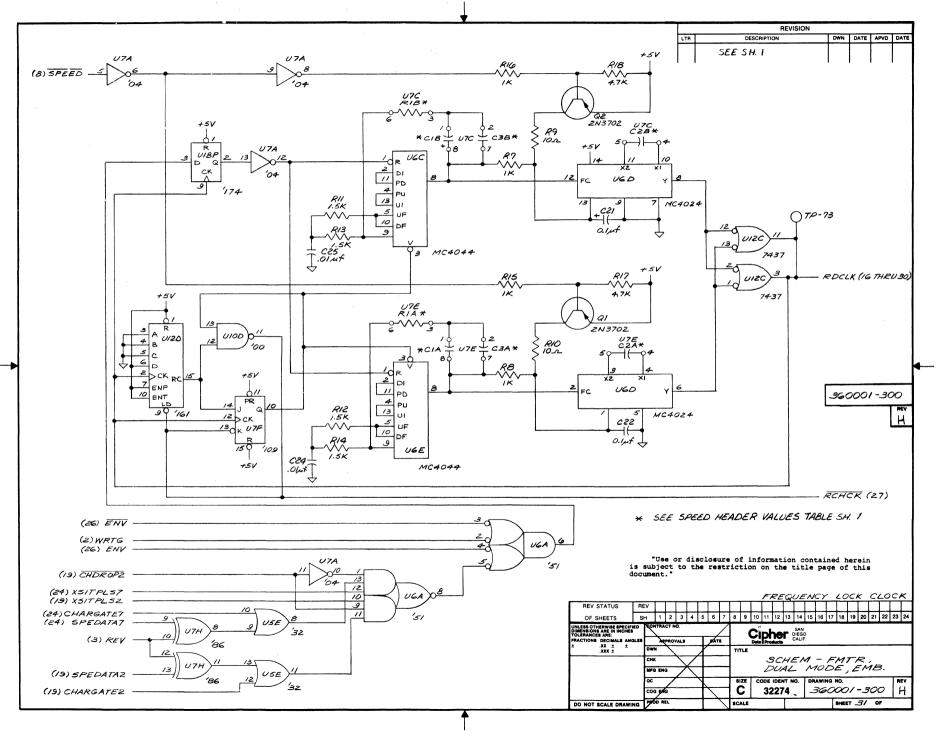

#### PAGE NO. SECTION TITLE LOGIC ELEMENTS AND SYMBOLS ..... V Con't. 5-1 EMBEDDED DUAL-MODE FORMATTER PWB ..... 5-11 CIRCUIT OPERATION AND DESCRIPTION Clock Logic ..... 5-12 Clock Pulse Generator ..... 5-12 5-14 Command Registers ..... Gap Control ..... 5-14 Gap Counter..... 5-21 Write Control..... 5-23 Write Data Encoder ..... 5-24 NRZI Read Data Registers ..... 5-29 NRZI Read Error Logic ..... 5-29 PE READ RECOVERY LOGIC ..... 5 - 305-30 Block Format Control Logic ..... Character Control..... 5-32 Channel Selection ..... 5-36 PE Detectors ..... 5-38 Skew Buffer ..... 5-40 Error Logic..... 5-41 Read Strobe Pulse Generator ..... 5-42 VI ENGINEERING DOCUMENTATION ..... 6-1

# LIST OF ILLUSTRATIONS

## FIGURE

TITLE

| -    | Interface Configuration                 | 1-2  |

|------|-----------------------------------------|------|

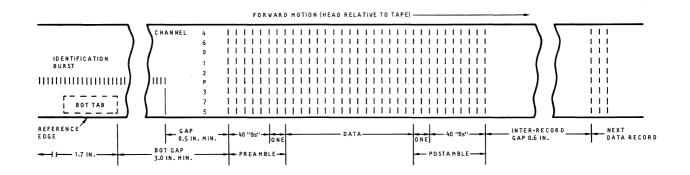

| 4-1  | Seven-Track NRZI Format                 | 4-2  |

| 4-2  | Nine-Track NRZI Format                  | 4-2  |

| 4-3  | Nine-Track PE Tape Format               | 4-3  |

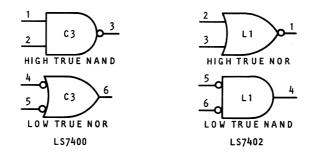

| 5-I  | Logic Symbols, LS7400 and LS7402        | 5-12 |

| 5-2  | Logic Symbols, 74LS38 and 74LS05        | 5-12 |

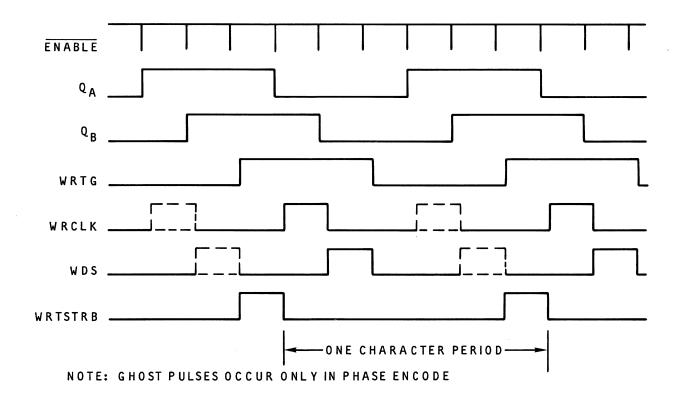

| 5-3  | Write Encoding Clock Pulses             | 5-13 |

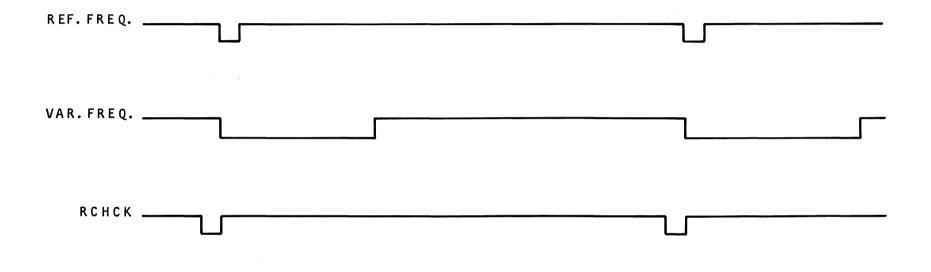

| 5-4  | Read Clock Waveforms                    | 5-15 |

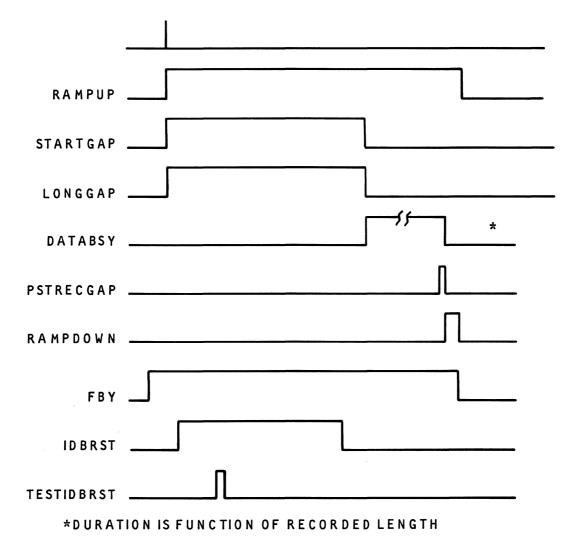

| 5-5  | Gap Timing, Write From Load Point in PE | 5-17 |

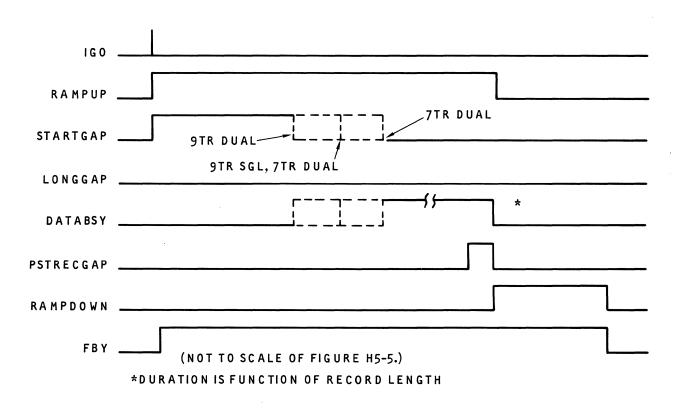

| 5-6  | Gap Timing, Normal Write                | 5-18 |

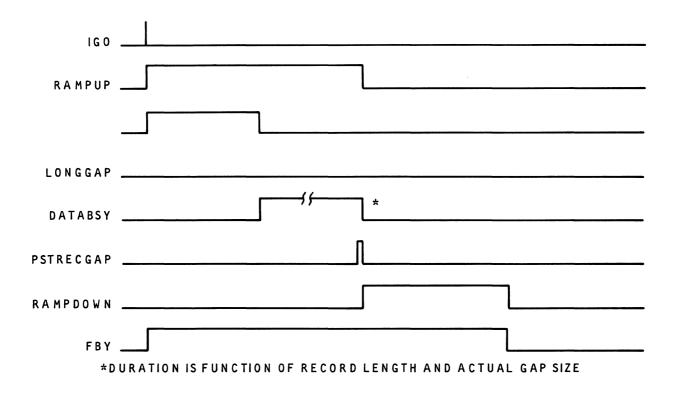

| 5-7  | Gap Timing, Read Forward                | 5-19 |

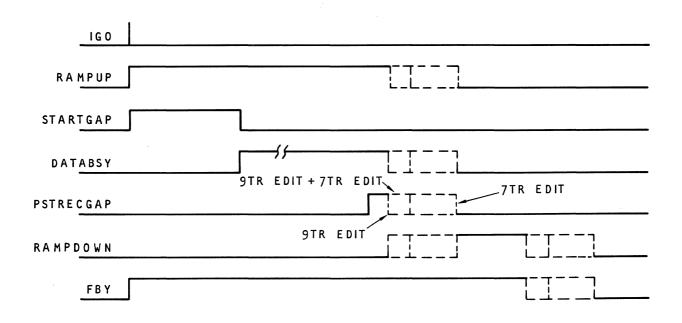

| 5-8  | Gap Timing, Read Reverse                | 5-19 |

| 5-9  | Gap Timing, File Search                 | 5-20 |

| 5-10 | Gap Timing, Reverse Operation at LDP    | 5-21 |

| 5-11 | Gap Timing, Initiate Synchronization    | 5-22 |

| 5-12 | Gap Counter Timing Illustration         | 5-22 |

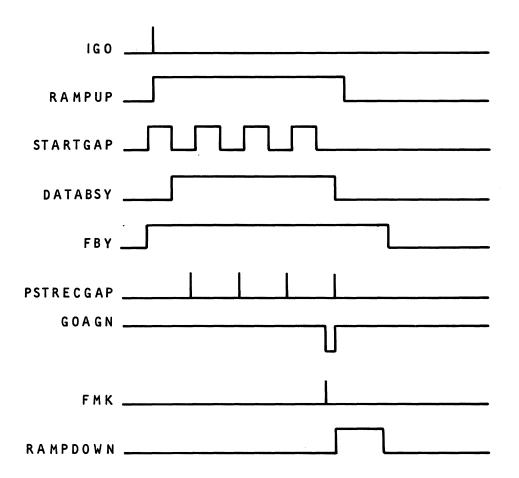

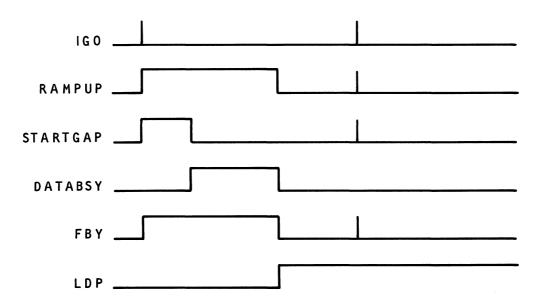

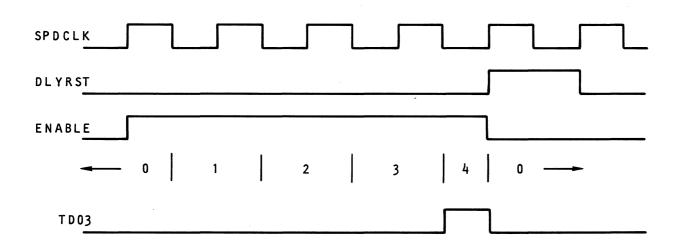

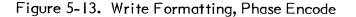

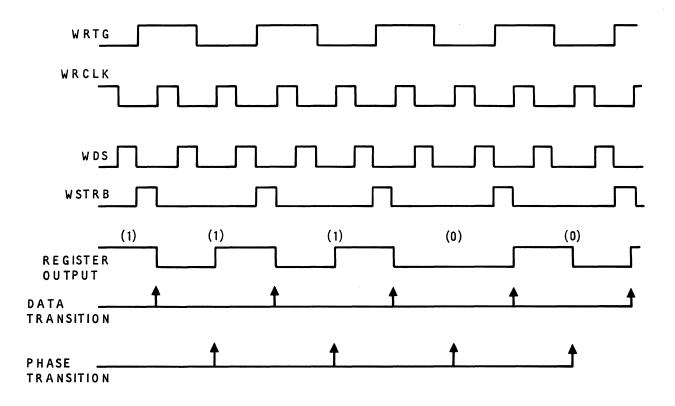

| 5-13 | Write Formatting, Phase Encode          | 5-23 |

| 5-14 | PE Writer Data Timing                   | 5-26 |

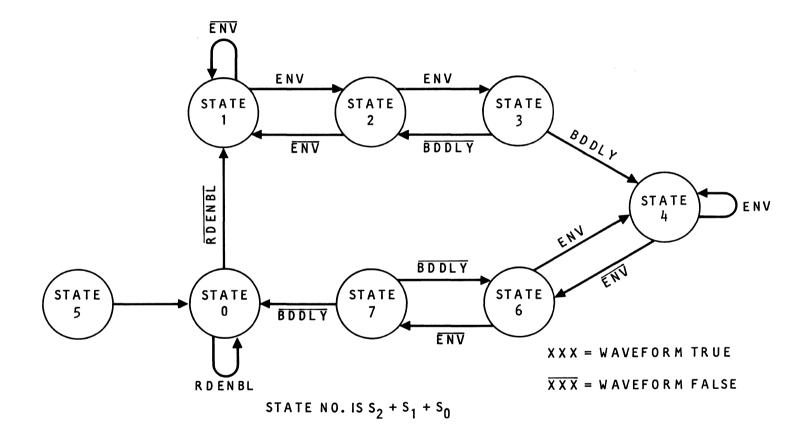

| 5-15 | Block Detector Transition Diagram       | 5-31 |

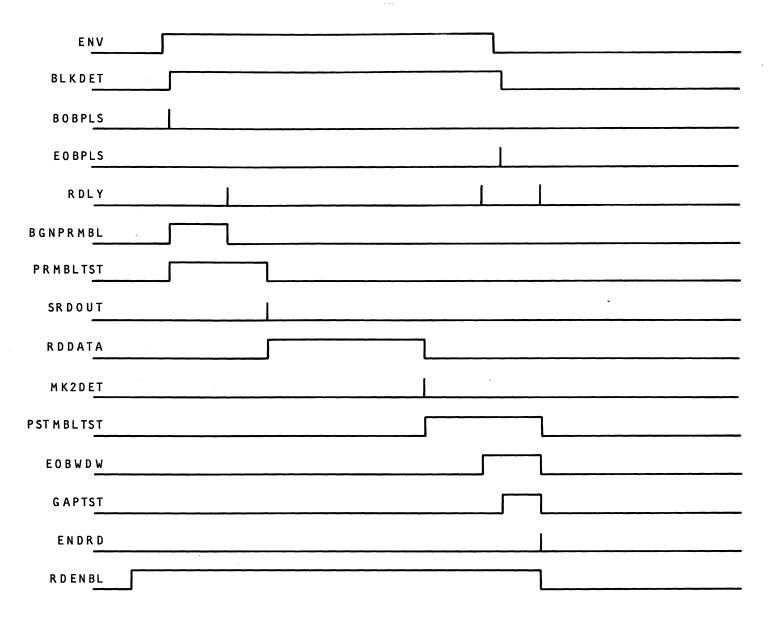

| 5-16 | Read Record Timing                      | 5-33 |

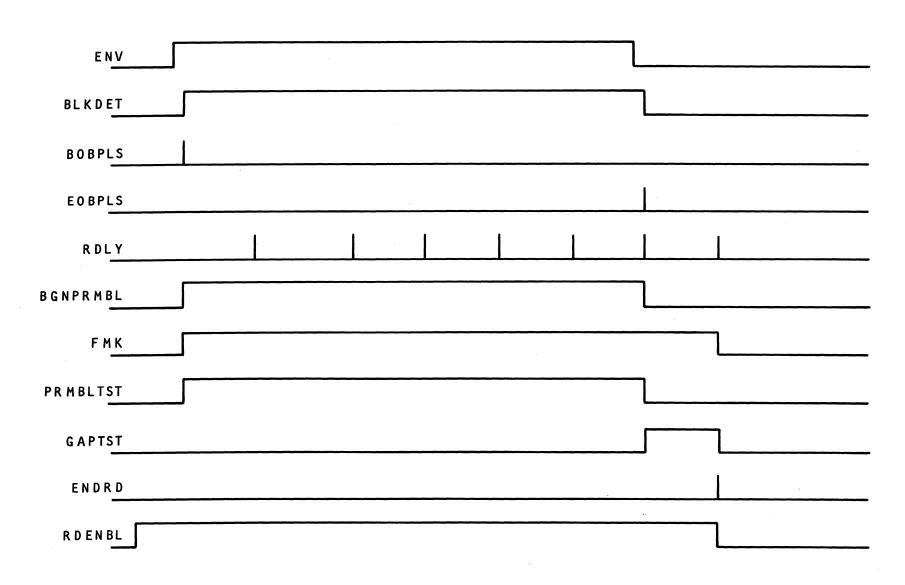

| 5-17 | Read FMK Timing                         | 5-34 |

| 5-18 | Channel Select Timing                   | 5-37 |

| 5-19 | PE Detector                             | 5-39 |

|      |                                         |      |

# LIST OF TABLES

## TITLE

TABLE

| 2-1 | Speed Selection                               | 2-2  |

|-----|-----------------------------------------------|------|

| 2-2 | Component Values in Speed Headers U7E and U7C | 2-3  |

| 3-1 | Interface Connections, Formatter/Controller   | 3-2  |

| 3-2 | Transport/Formatter Interface Connections     | 3-5  |

| 3-3 | Plus 5-volt Power Connections                 | 3-7  |

| 3-4 | Transport Addressing                          | 3-8  |

| 4-1 | Command Coding                                | 4-3  |

| 5-1 | Formatter Signals, Functions, and Mnemonics   | 5-2  |

| 5-2 | Gap Control Delays                            | 5-16 |

|     |                                               |      |

### SECTION I

#### DESCRIPTION

## PHYSICAL DESCRIPTION

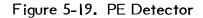

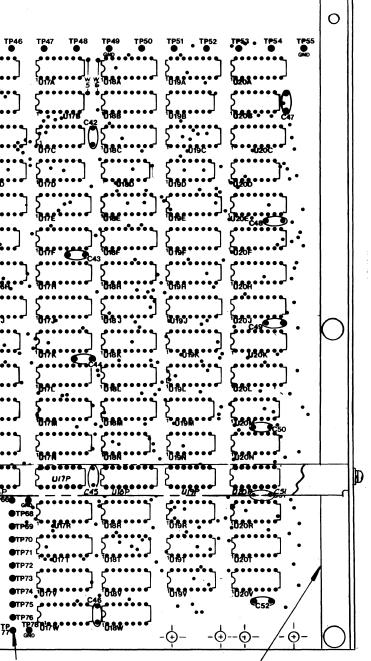

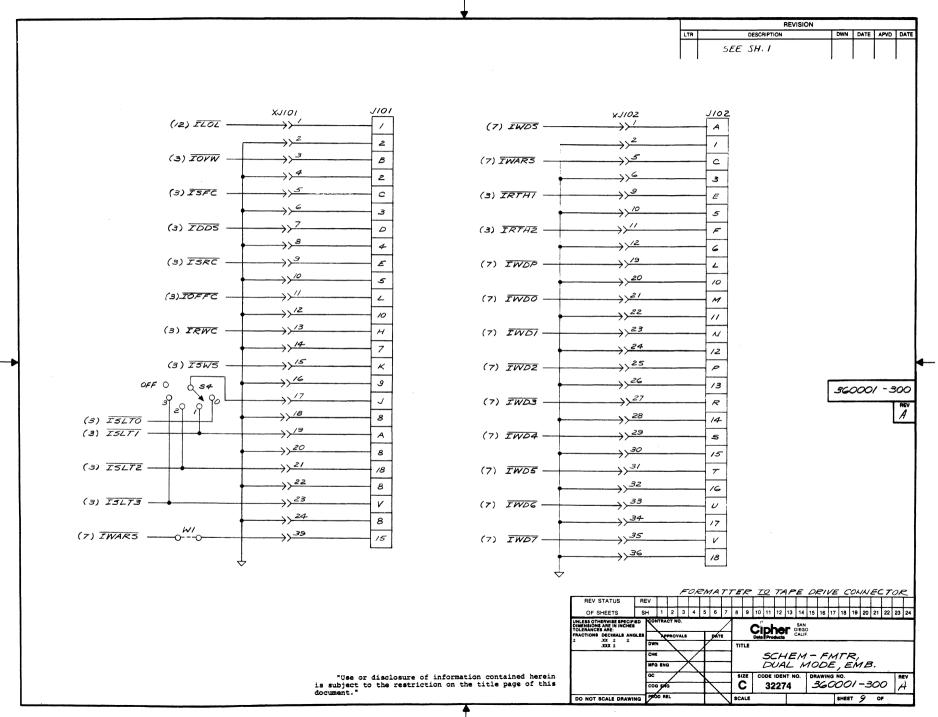

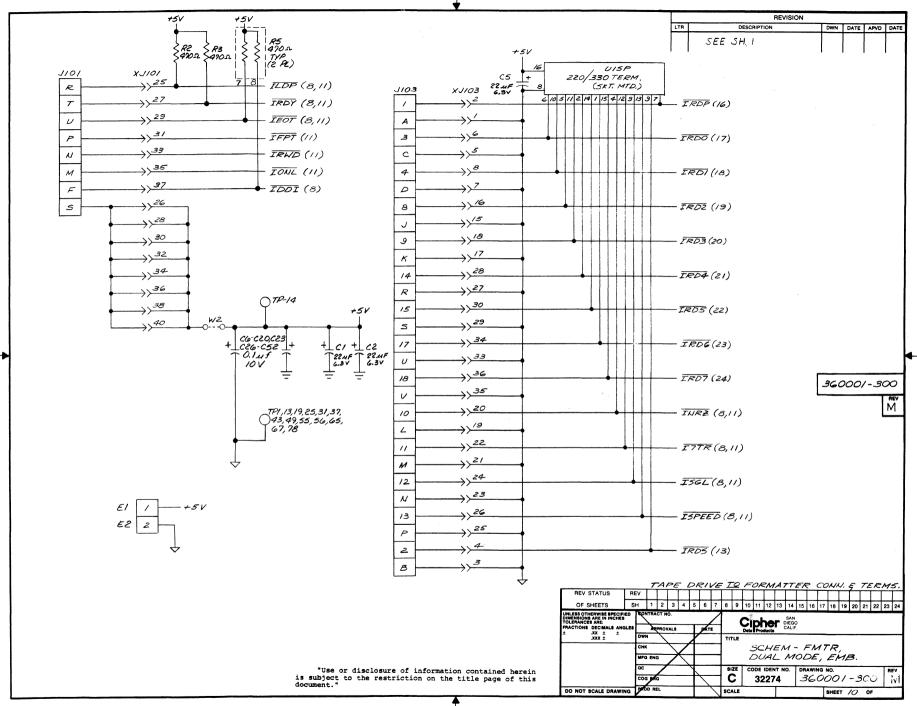

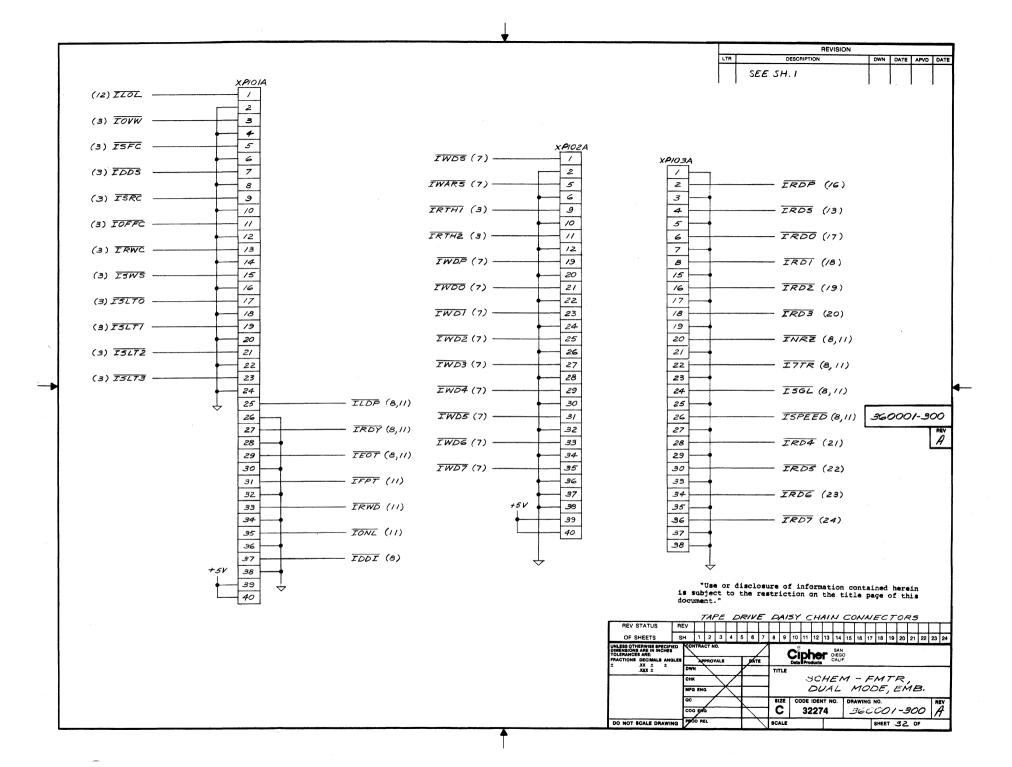

1-1. All components and circuitry of the formatter embedded within the chassis of the Cipher magnetic tape transport are incorporated on a single printed-wiring board. Also mounted on this board are six connectors, XJ101, XJ102, XJ103, XP101A, XP102A and XP103A, which provide all interface connections between the formatter and the transport(s), and another connector, IP101, which provides all connections from the board to the interface harness from the system. Connector IP101 is readily accessible from the rear of the transport.

1-2. The embedded formatter has no separate power supply or controls. These facilities are provided through the interface connections with the transport and/or the system.

## FUNCTIONAL DESCRIPTION

1-3. The embedded formatter contains all logic and functions associated with the reading and writing of IBM/ANSI-compatible PE and NRZI magnetic tapes. Its circuitry includes all logic required for the generation of data records, CRC, LRC, file-mark patterns, and ID bursts involved in magnetic tape recording, and for the data recovery operations of data decoding, buffering, and error and file-mark detection. It performs all timing necessary for the writing of compatible interblock gaps and proper head positioning within the block.

## MECHANICAL AND ELECTRICAL SPECIFICATIONS

1-4. Mechanical and electrical specifications are compatible with those of the transport on which the formatter is mounted.

## INTERFACE SPECIFICATIONS

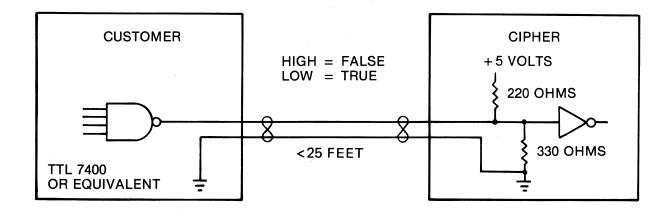

1-5. Interface specifications for the formatter are the same as those for the transport, as described in the basic manual. The formatter interface configuration is as shown in Figure 1-1 of this addendum.

. (

Figure I-I. Interface Configuration

## SECTION II

## INSTALLATION, SWITCH SETTINGS, AND JUMPERS

## INSTALLATION

2-1. As noted in Section I, the formatter is installed on the transport during manufacture. The manner of installation and all parts and components involved therein are shown in the drawing and parts list presented in the SPECIAL-CONFIGURATION SUPPLEMENT preceding this addendum.

## SWITCHES

2-2. The dual-mode formatter PWB incorporates one four-position DIP switch (S1), two six-position DIP switches (S2 and S3), one five-position rotary switch (S4), and four jumpers, all of which are used to implement various configuration parameters. The functions of each of these switches and jumpers are presented here as a check list and guide to the technician in making any desired changes in the various modes of operation.

2-3. Density Selection. Switch SI, positions I and 2, are used with seven-track transports to select high-low density combinations.\* SI-I OFF, SI-2 ON selects densities of 800 and 200 bpi; SI-I ON, SI-2 ON, 800 and 566 bpi; SI-I OFF, 556 and 200 bpi.

2-4. Parity Generation. Switch SI-3, in OFF position, selects internal parity generation. ON position selects external parity generation.

2-5. Formatter Address. Switch SI-4, in OFF position, selects formatter address 0; SI-4 ON selects formatter address 1.

2-6. Speed Selection. Switches S2 and S3, in conjunction with the proper headers, are used to set the formatter for operation at either of any two standard tape speeds from 12.5 to 125 ips. Switch S2, with header U7E, sets the high speed, and switch S3, with header U7C, sets the low speed. (See Table 2-1 for switch settings and Table 2-2 for header component values for different speeds.) When transport-to-formatter input ISPEED is true, operation will be at the high-speed setting.

\*The host transport must not be a seven-track machine.

2-7. Host Transport Address. For transports not having a logical unit address select switch, rotary switch S4 is used to set the address of the host transport. With S4 in OFF position, the host transport is selected. Transport address 0, 1, 2, or 3 is obtained by turning S4 to position 0, 1, 2, or 3, respectively. In a transport with a logical unit address switch, switch S4 should be set in the address 0 position.

## JUMPER OPTIONS

2-8. Jumper WI is used to route the formatter-to-transport output IWARS to J101 in the host transport. This jumper is used only on transports (such as Model 100X) in which IWARS is not routed within the transport to the control section.

2-9. Jumper W2 routes +5-volt power from the transport via J101-S to the formatter. This jumper must be removed if power is to be supplied from the system interface through IP101, or through E1, E2. In this case, the +5-volt power supply on the transport must be readjusted to compensate for the decrease in load.

2-10. Jumper W3, in the PE mode, causes IRTH2 to be forced true during the data portion of the record.

|                | SWITCH S2 AND S3 POSITIONS |     |     |     |     |     |                        |

|----------------|----------------------------|-----|-----|-----|-----|-----|------------------------|

| SPEED<br>(ips) | I                          | 2   | 3   | 4   | 5   | 6   | FREQ. AT TP38<br>(MHz) |

| 125            | ON                         | ON  | OFF | OFF | OFF | OFF | 10.8                   |

| 112.5          | OFF                        | ON  | OFF | OFF | OFF | OFF | 9.72                   |

| 75             | OFF                        | OFF | ON  | OFF | OFF | OFF | 6.48                   |

| 50             | ON                         | OFF | OFF | ON  | OFF | OFF | 4.32                   |

| 45             | OFF                        | OFF | OFF | ON  | OFF | OFF | 3.89                   |

| 37.5           | OFF                        | ON  | OFF | ON  | OFF | OFF | 3.24                   |

| 25             | OFF                        | OFF | OFF | OFF | ON  | OFF | 2.16                   |

| 25 (alt.)      | ON                         | ON  | OFF | OFF | ON  | OFF | 2.16                   |

| 22.5           | OFF                        | ON  | OFF | OFF | ON  | OFF | 1.94                   |

| 18.75          | OFF                        | ON  | ON  | OFF | ON  | OFF | I <b>.</b> 62          |

| 12.5           | OFF                        | ON  | OFF | OFF | OFF | ON  | 1.08                   |

| 12.5 (alt.)    | ON                         | ON  | ON  | OFF | OFF | ON  | 1.08                   |

2-11. Jumper W4 provides for the use of transports with no Read Data strobes.

Table 2-1. Speed Selection Switch Settings

| SPEED | HEADER COMPONENTS |        |        |                  |

|-------|-------------------|--------|--------|------------------|

| (ips) | CI                | C2     | C3     | RI               |

| 12.5  | lμf               | 470pf  | lμf    | IK               |

| 18.75 | lf                | 330pf  | lμf    | IK               |

| 25    | .47μf             | 270pf  | .22μf  | 1 <b>.</b> 3K    |

| 37.5  | .47μf             | 180pf  | .47μf  | 820 <sub>Ω</sub> |

| 45    | .47μf             | l 20pf | .47μf  | 820 <sub>Ω</sub> |

| 75    | .47μf             | 68pf   | N/A    | IK               |

| 125   | .47μf             | 33pf   | .47 μf | 430Ω             |

## Table 2-2. Component Values in Speed Headers U7E and U7C

2)

## SECTION III

## INTERFACE CONNECTIONS

## **CONNECTORS**

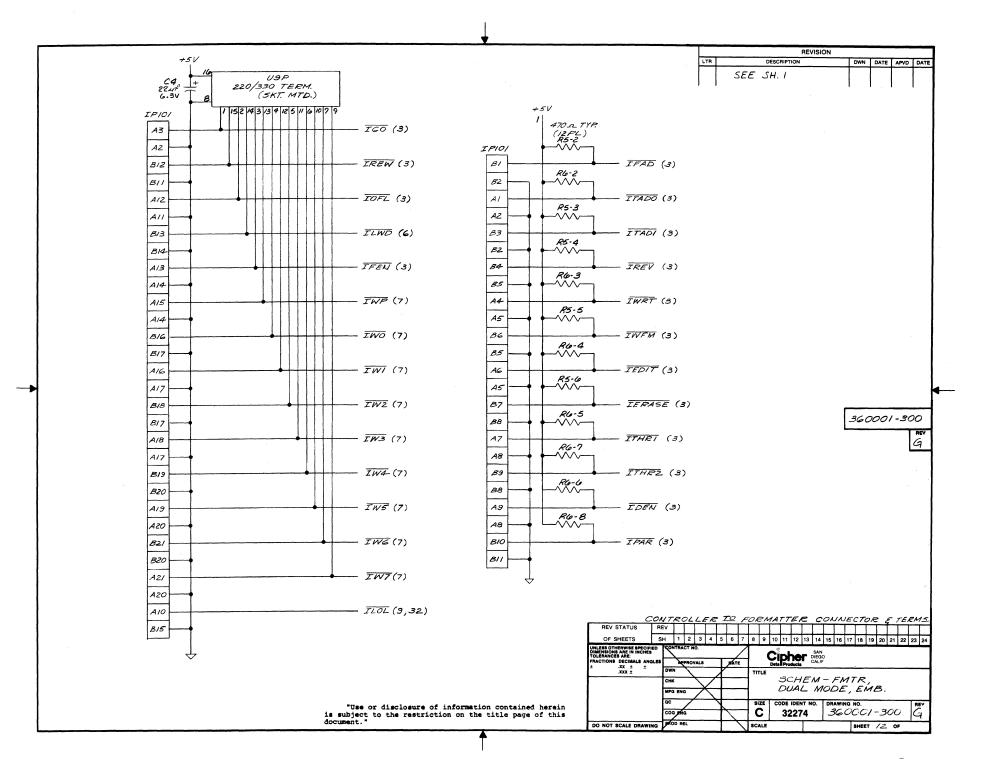

3-1. As noted in paragraph 1-2 of this addendum, all interface connections to the formatter are made through seven connectors: XJ101, XJ102, XJ103, XP101A, XP102A and XP103A from formatter to transport and IP101 from formatter to controller harness. Connectors XJ101, XJ102, and XJ103 are connected by cables to J101, J102, and J103, respectively, on the host transport, and connectors XP101A, XP102A, and XP103A are used for daisy chaining. Up to three additional external drives may be attached to the formatter, using Cipher daisy-chain cables.

## **PIN ASSIGNMENTS**

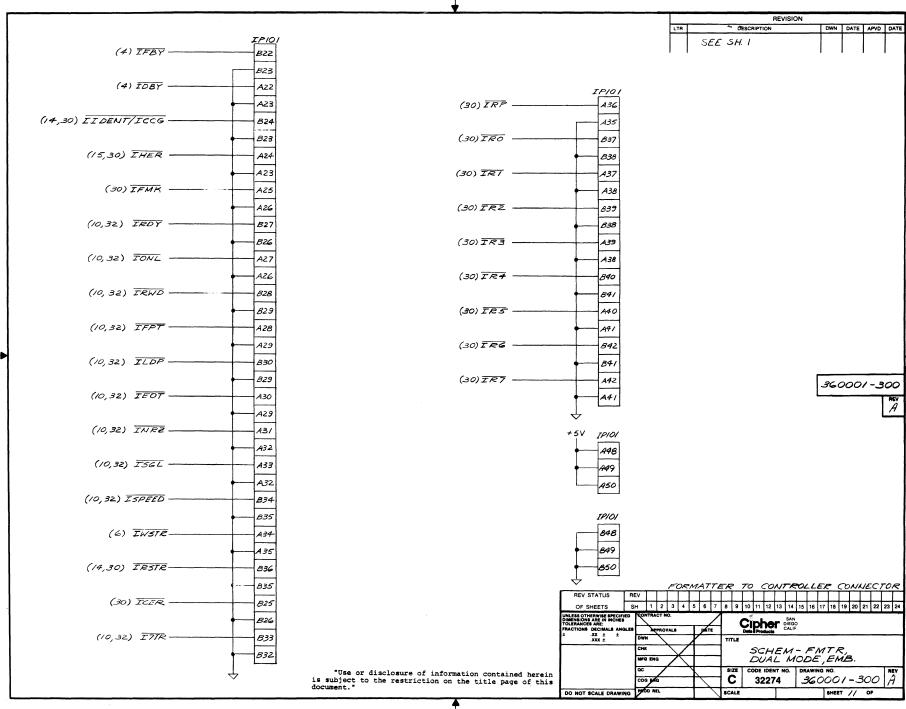

3-2. The signals, mnemonics, and connector pin assignments pertaining to the interface of the formatter and controller are presented in Table 3-1. (Note that all interface mnemonics are prefixed with the letter "I".) Formatter/transport interface signals and pin assignments are as presented in Table 3-2. Plus 5-volt connectors and pin assignments are shown in Table 3-3.

| CONNECTOR                  | LIVE<br>PIN | GROUND<br>PIN | SIGNAL*                                  |

|----------------------------|-------------|---------------|------------------------------------------|

| IP101                      | BI          | B2            | Formatter Address (IFAD)                 |

| Controller to<br>Formatter | AI          | A2            | Transport Address (ITADO)                |

|                            | В3          | В2            | Transport Address (ITAD1)                |

|                            | A3          | A2            | Initiate Command (IGO)                   |

|                            | B4          | В5            | Reverse (IREV)                           |

|                            | A4          | A5            | Write (IWRT)                             |

|                            | B6          | B5            | Write File Mark (IWFM)                   |

|                            | A6 (        | A5            | Edit (IEDIT)                             |

|                            | B7          | B8            | Erase (IERASE)                           |

|                            | Α7          | A8            | Threshold Level 1 (ITHR1) (NRZI<br>only) |

|                            | B9          | B8            | Read Threshold Level 2 (ITHR2)           |

|                            | A9          | A8            | Density Select (IDEN) (NRZI only)        |

|                            | B10         | BH            | Parity Select (IPAR) (NRZI only)         |

|                            | A10         | B15           | Load and Online (ILOL)                   |

|                            | B12         | BII           | Rewind (IREW)                            |

|                            | A12         | AH            | Off-Line (IOFL)                          |

|                            | B13         | B14           | Last Word (ILWD)                         |

|                            | A13         | A14           | Formatter Enable (IFEN)                  |

|                            | A15         | A14           | Write Data Parity (IWP)                  |

|                            | B16         | B17           | Write Data 0 (IW0)                       |

|                            | A16         | A17           | Write Data I (IWI)                       |

|                            | B18         | B17           | Write Data 2 (IW2)                       |

\*See Section III for definitions of interface functions.

# Table 3-1. Interface Connections, Formatter/Controller

| CONNECTOR                  | LIVE<br>PIN | GROUND<br>PIN | SIGNAL*                      |

|----------------------------|-------------|---------------|------------------------------|

| IP101                      | A18         | A17           | Write Data 3 (IW3)           |

| Controller to<br>Formatter | B19         | B20           | Write Data 4 (IW4)           |

|                            | A19         | A20           | Write Data 5 (IW5)           |

|                            | B21         | B20           | Write Data 6 (IW6)           |

|                            | A21         | A20           | Write Data 7 (IW7)           |

|                            | B22         | B23           | Formatter Busy (IFBY)        |

| Formatter to<br>Controller | A22         | A23           | Data Busy (IDBY)             |

|                            | B24         | B23           | Identification (IIDENT/ICCG) |

|                            | A24         | A23           | Hard Error (IHER)            |

|                            | B25         | B26           | Corrected Error (ICER)       |

|                            | A25         | A26           | File Mark (IFMK)             |

|                            | B27         | B26           | Ready (IRDY)                 |

|                            | A27         | A26           | On Line (IONL)               |

|                            | B28         | B29           | Rewinding (IRWD)             |

|                            | A28         | A29           | File Protect (IFPT)          |

|                            | B30         | B29           | Load Point (ILDP)            |

|                            | A30         | A29           | End of Tape (IEOT)           |

|                            | A31         | A32           | NRZI (INRZ)                  |

|                            | B33         | B32           | 7 Track (I7TR) (NRZI only)   |

|                            | A33         | A32           | Single (ISGL)                |

|                            | B34         | B35           | Speed (ISPEED)               |

|                            | A34         | A35           | Write Strobe (IWSTR)         |

\*See Section III for definitions of interface functions.

A A

Table 3-1. Interface Connections, Formatter/Controller (Continued)

Revised\_\_\_\_\_

ę

| CONNECTOR             | LIVE<br>PIN | GROUND<br>PIN | SIGNAL*                |

|-----------------------|-------------|---------------|------------------------|

| IP101<br>Formatter to | B36         | B35           | Read Strobe (IRSTR)    |

| Controller            | A36         | A35           | Read Data Parity (IRP) |

|                       | B37         | B38           | Read Data 0 (IR0)      |

|                       | A37         | A38           | Read Data 1 (IR1)      |

|                       | B39         | B 38          | Read Data 2 (IR2)      |

|                       | A39         | A38           | Read Data 3 (IR3)      |

|                       | B40         | B41           | Read Data 4 (IR4)      |

|                       | A40         | A41           | Read Data 5 (IR5)      |

|                       | B42         | B41           | Read Data 6 (IR6)      |

|                       | A42         | A41           | Read Data 7 (IR7)      |

\*See Section III for definitions of interface functions.

Table 3-1. Interface Connections, Formatter/Controller (Continued)

Revised\_\_\_\_

| CONNECTOR      | LIVE<br>PIN | GROUND<br>PIN    | SIGNAL                        |

|----------------|-------------|------------------|-------------------------------|

| XJ101 - XP101A | 27          | See<br>Table 3-3 | Ready (IRDY)                  |

|                | 35          |                  | On Line (IONL)                |

|                | 33          |                  | Rewinding (IRWD)              |

|                | 31          |                  | File Protect (IFPT)           |

|                | 25          |                  | Load Point (ILDP)             |

|                | 29          |                  | End of Tape (IEOT)            |

|                | 37          |                  | Data Density Indicator (IDOI) |

| XJI03 - XPI03A | 20          | 19               | NRZI (INRZ)                   |

|                | 22          | 21               | Seven Track (I7TR)            |

|                | 24          | 23               | Single (ISGL)                 |

|                | 26          | 25               | Speed (ISPEED)                |

|                | 4           | 3                | Read Data Strobe (IRDS)       |

|                | 2           | 1                | Read Data Parity (IRDP)       |

|                | 6           | 5                | Read Data 0 (IRD0)            |

|                | 8           | 7                | Read Data I (IRDI)            |

|                | 16          | 15               | Read Data 2 (IRD2)            |

|                | 18          | 17               | Read Data 3 (IRD3)            |

|                | 28          | 27               | Read Data 4 (IRD4)            |

|                | 30          | 29               | Read Data 5 (IRD5)            |

|                | 34          | 33               | Read Data 6 (IRD6)            |

|                | 36          | 35               | Read Data 7 (IRD7)            |

| XJ101 - XP101A |             | 2                | Load and On Line (ILOL)       |

|                | 17          | 18               | Select 0 (ISLT0)              |

Table 3-2. Transport/Formatter Interface Connections

Revised

| CONNECTOR      | LIVE<br>PIN | GROUND<br>PIN    | SIGNAL                                |

|----------------|-------------|------------------|---------------------------------------|

| XJ101 - XP101A | 19          | 20               | Select I (ISLTI)                      |

|                | 21          | 22               | Select 2 (ISLT2)                      |

|                | 23          | 24               | Select 3 (ISLT3)                      |

|                | 5           | 6                | Synchronous Forward Command<br>(ISFC) |

|                | 9           | 10               | Synchronous Reverse Command<br>(ISRC) |

|                | 13          | 14               | Rewind Command (IRWC)                 |

|                | 11          | 12               | Off-Line Command (IOFFC)              |

|                | 15          | 16               | Set Write Status (ISWS)               |

| (XJ101 only)   | 39          | See<br>Table 3-3 | (IWARS) (JUMPER OPTION)               |

|                | 3           | 4                | Overwrite (IOVW)                      |

|                | .7          | 8                | Data Density Select (IDDS)            |

| JI02 - XPI02A  | 11          | 12               | Read Threshold 2 (IRTH2)              |

|                | 9           | 10               | Read Threshold I (IRTHI)              |

|                | 5           | 6                | Write Amplifier Reset (IWARS)         |

|                | I           | 2                | Write Data Strobe (IWDS)              |

|                | 19          | 20               | Write Data Parity (IWDP)              |

|                | 21          | 22               | Write Data 0 (IWD0)                   |

|                | 23          | 24               | Write Data I (IWDI)                   |

|                | 25          | 26               | Write Data 2 (IWD2)                   |

|                | 27          | 28               | Write Data 3 (IWD3)                   |

|                | 29          | 30               | Write Data 4 (IWD4)                   |

|                | 31          | 32               | Write Data 5.(IWD5)                   |

# Table 3-2. Transport/Formatter Interface Connections (Continued)

.

Revised

| CONNECTOR     | LIVE<br>PIN | GROUND<br>PIN | SIGNAL              |

|---------------|-------------|---------------|---------------------|

| J102 - XP102A | 33          | 34            | Write Data 6 (IWD6) |

|               | 35          | 36            | Write Data 7 (IWD7) |

Table 3-2. Transport/Formatter Interface Connections (Continued)

| Connector +5 V | Connector +5 VOLTS<br>Pin |        | ROUND<br>Pin |

|----------------|---------------------------|--------|--------------|

| 101LX          | 26                        | XP101A | 26           |

|                | 28                        |        | 28           |

|                | 30                        |        | 30           |

|                | 32                        |        | 32           |

|                | 34                        |        | 34           |

|                | 36                        |        | 36           |

|                | 38                        |        | 38           |

|                | 40                        |        |              |

| XPIOIA         | 39                        |        |              |

|                | 40                        |        |              |

| XP102A         | 39                        | XP102A | 37           |

|                | 40                        |        | 38           |

Table 3-3. Plus 5-volt Power Connections

## FORMATTER INTERFACING

3-3. The formatter is designed so that any two Cipher formatters may be daisychained on the formatter/controller interface.

3-4. All interface lines are low-true at the interface, with the true level being less than 0.8V and the false level being greater than 2.4V. All pulses widths must be at least 1 microsecond.

## INTERFACE INPUTS (CONTROLLER TO FORMATTER)

3-5. Formatter Address (IFAD). This is a level which selects one of two possible formatters. A true level on the IFAD line selects formatter address 1; a false level selects formatter address 0. The formatter address is determined by switch SI-4: in OFF position, formatter address is 0; in ON position, formatter address is 1.

3-6. Transport Address (ITAD0, ITAD1). The levels on these two lines determine which of the four possible transports is connected to the formatter. These lines are decoded by the formatter/transport interface. See Table 3-4.

3-7. Initiate Command (IGO). This is a pulse which initiates the command specified by the command lines. The information on the command lines is copied into the corresponding formatter flip-flops on the trailing edge of the IGO pulse. If the formatter and the selected transport are ready, the command is accepted by the formatter, and the IFBY signal is set true.

| ITADI | ADDR                       |

|-------|----------------------------|

| 0     | SLT0                       |

| l ,   | SLTI                       |

| 0     | SLT2                       |

| I     | SLT3                       |

|       | ITAD I<br>0<br>I<br>0<br>I |

| Table 3-4. 7 | Transport | Addressing |

|--------------|-----------|------------|

|--------------|-----------|------------|

3-8. Command Lines. The levels on these lines specify commands to the formatter. The levels on the command lines are transferred to the formatter on the trailing edge of the IGO pulse. The levels must be held steady from 0.5 microsecond before to 0.5 microsecond after the trailing edge of IGO. Table 4-1 defines the command coding for various tape operations.

- a. Reverse (IREV). This is a level which, when true, specifies reverse tape motion and when false, specifies forward tape motion.

- b. Write (IWRT). This is a level which, when true, specifies the write mode of operation and when false, specifies the read mode of operation.

Revised

- c. Write File Mark (IWFM). This is a level which, when true and IWRT is also true, causes a file mark to be written on the tape. When this level is true and IWRT is false, a file search is initiated. The operation terminates when a file mark is detected or if load point is encountered in reverse. Read data will also be available during the operation.

- d. EDIT (IEDIT). This is a level which, when true during a read reverse operation, modifies the read reverse stop delay to optimize head positioning for a subsequent edit operation. When this level is true and IWRT is true, the IOVW line is activated, and the selected transport operates in the edit mode.

- e. ERASE (IERASE). This is a level which, when true in conjunction with a true level in the IWRT line, causes the formatter to execute a dummy write command. The formatter will be conditioned to execute a normal write command but no data will be recorded. A length of tape, as defined by ILWD, will be erased. Alternately, if IERASE, IWRT, and IWFM command lines are true, the formatter is conditioned to execute a dummy write file mark command. A fixed length of tape approximately 3.75 inches will be erased.

- f. Read Threshold Level 2 (ITHR2). The levels on this line are utilized in transports with extra low read threshold capabilities. When true, the extra low threshold is specified, and when false, the normal threshold is specified. The true level should be used only when it is required to recover data of very low amplitude.

- g. Read Threshold Level I (ITHR1). The levels on this line are utilized only in transports with single-gap heads to specify the operating level of the read threshold circuits. A true level specifies selection of the high read threshold level, and a false level specifies the normal read threshold. The true level is normally used only when it is required to perform a readafter-write data check.

- h. Density Select (IDEN) (Optional Seven-Track). When the external density select option is incorporated in seven-channel transports, the levels on this line control the packing density of data transfers to and from tape. This level, when true, selects the lower of two possible packing densities. When false, the higher packing density is selected.

- i. Parity Select (IPAR). The levels on this line are effective only for sevenchannel transports. They control the parity mode for write and read data transfers. When true, this level selects the even (BCD) parity mode. When false, it selects the odd (binary) parity mode.

3-9. Rewind (IREW). This is a pulse which causes the selected transport to rewind to the load point. This pulse is routed directly to the transport and does not cause the formatter to go busy.

3-10. Off-line Command (IOFL-IRWU). This is a pulse which causes the selected transport to revert to the off-line mode. Depending on the tape transport configuration, this line will also cause the selected transport to rewind and unload. This pulse is routed directly to the transport and does not cause the formatter to go busy.

## NOTE

# Current Cipher transports are not equipped with the IRWU option.

3-11. Last Word (ILWD). This is a level which, when true during a WRITE or ERASE (variable-length) command, indicates that the next character to be strobed into the formatter is the last character of the record. It is set true by the controller at the time the last data character of the record is placed on the interface lines.

3-12. Formatter Enable (IFEN). This is a level which, when false, causes the formatter to reset to the quiescent state. This signal is not gated by FAD; hence, if two formatters are connected to the interface, both will reset simultaneously upon receipt of a false-going IFEN level. This line may be used to disable the formatter if controller power is lost, or to clear the formatter logic in the case of illegal commands or unusual conditions.

3-13. Write Data Lines, Write Parity (IW0-IW7, IWP). The eight Write Data lines are utilized to transmit write data from the controller to the formatter. IW0 corresponds to the most significant bit and IW7 to the least significant bit of each character.

3-14. For nine-channel operation, the eight data bits appearing on W0-7 are written onto the corresponding channels on tape. For seven-channel operation, W0 and W1 are not utilized and the remaining six data bits are written onto tape. In either case, W7 corresponds to the least significant bit of the character. Line WP is optional and is used only if it is required to write the parity bit specified by the customer. When this option is not employed, the formatter generates parity internally on the basis of data contained on W0-7, together with the current parity mode.

3-15. The first character of a record should be available on these lines a minimum of one-half cell time before the first IWSTR and remain until the trailing edge of the first IWSTR is issued by the formatter. The next character of information must then be placed on these lines within one-half a character period. Subsequent characters of a record are processed in this manner, until ILWD is set true by the controller when the last character is transmitted.

3-16. Load and On-Line (ILOL). This is a pulse which causes a remote load sequence. A second pulse, spaced a minimum I second from the initial pulse, causes the transport to be placed on line. This pulse is routed directly to the transport interface and may be used only on transports equipped with this option.

## NOTE

Current Cipher transports are not equipped with this option.

## INTERFACE OUTPUTS (FORMATTER TO CONTROLLER)

3-17. Formatter Busy (IFBY). This level is normally utilized by the controller to inhibit further commands to the formatter. The level goes true on the trailing edge of the IGO when a command is issued by the controller and will remain true until tape motion ceases after the execution of the command.

3-18. Data Busy (IDBY). This is a level which goes true when the tape on the selected transport has reached operating speed and traversed the IBG, and the formatter is about to write a preamble on the tape or look for a read signal from the tape. IDBY remains true until the data transfer is completed and the appropriate postrecord delay is completed. IDBY goes false as the capstan starts to decelerate the tape.

3-19. Identification/Check Character Gate (IIDENT/ICCG). The functions of this line differ depending upon mode of operation. These functions are described for PE and NRZI mode in paragraphs 3-20 and 3-21, respectively.

3-20. PE Mode. This is a level which goes true to identify phase-encoded (PE) tapes. When reading forward off of the BOT, the formatter inspects the parity channel for the presence or absence of the identification burst, which distinguishes PE tapes. If an identification burst is detected, this line is set true for a short period as the BOT tab passes over the read head.

3-21. NRZI Mode. This level is set true by the formatter when the read information being transmitted to the controller is a cyclic redundancy check character (CRCC) or a longitudinal redundancy check character (LRCC). It is false when data characters are being transmitted. Data and check information can be distinguished by gating read strobe (RSTR) with CCG or its inverse.

3-22. Hard Error (IHER). This is a pulse or level which, when true, indicates that an uncorrectable read error has been detected by the formatter. When the ERASE command is given to the formatter, the IHER line is disabled. In NRZI mode, this line will be set true for one or more of the following:

- a. Vertical parity error on data character.

- b. Longitudinal parity error.

- c. CRCC parity error.

- d. Improper record format.

- e. CRC error.

3-23. In the case of a vertical parity error, the HER line will be pulsed at the time that the read strobe (RSTR pulse) is issued for the character in error. In all other cases, HER will be pulsed after the complete record has been read. All error information will be transferred to the controller before Data Busy (DBY) goes false. In PE mode, IHER is true for one or more of the following:

- a. False preamble detection.

- b. False postamble detection.

- c. Multichannel dropout.

- d. Parity error without associated channel dropouts.

3-24. In all cases except parity error, the formatter will cease transmission of further read data and search for the IBG. When a parity error is detected, the erroneous character will be transmitted and labeled by a pulse on the IHER line at RSTR time.

3-25. Corrected Error (ICER) (PE Only). This is a pulse which indicates that a single-track dropout has been detected and that the formatter is performing error correction. When the ERASE command is given to the formatter, the ICER line is disabled.

#### NOTE

## When a read-after-write operation is being performed, the record should be rewritten if either a HER or CER error is detected.

3-26. File Mark (IFMK). This is a pulse which indicates that the formatter read logic has detected a file mark. This may be during any READ FORWARD or READ REVERSE command, or during a WRITE FILE MARK command for a read-after-write transport.

3-27. Transport Status. These lines indicate the status of the selected transport and are defined exactly the same as in the interface inputs description. Status lines are as follows: IRDY, IONL, IRWD, IFPT, ILDP, IEOT, INRZ, ISGL, ISPEED, and I7TR.

3-28. Write Strobe (IWSTR). This is a pulse for each data character to be written on the tape. The write data lines (IWP, IW0-IW7) are sampled by IWSTR and are copied character by character into the formatter write logic. The first character must be available before the first IWSTR is generated, and subsequent characters must be set up on the lines within one-half a character period after the trailing edge of each IWSTR pulse. This line will be active during ERASE (variable-length) commands, but data copied into the formatter will have no meaning.

3-29. Read Strobe (IRSTR). This is a pulse which indicates that a read character is present on the controller interface. The read strobes will have the same period as the write data over long-term data transfers. However, due to skew and velocity changes, the instantaneous rate may vary. The controller logic must sample the Read Data lines (IRP, IR0-IR7) at RSTR time. Read strobes (IRSTR) are disabled if the ERASE command is specified. The transmission of check characters (CRC and LRC) is flagged by the check character gate line (ICCG).

3-30. Read Data Lines (IRP, IR0-IR7). The nine read data lines transmit read data from the formatter to the controller. Each character read from the tape is available by sampling these lines in parallel by RSTR. Data remains on IRP, IR0-IR7 for a full character period. The corresponding IRSTR pulse is one-third of a character period wide and is timed to occur during the center of each character period.

## INTERFACE OUTPUTS (FORMATTER TO TRANSPORT)

3-31. Transport Select Lines (ISLT0-ISLT3). The levels of these four lines are utilized to select one transport from the possible four. The levels are generated in the formatter by decoding address lines ITAD0 and ITAD1. Only one line can be true at a time. When a transport is selected all interface lines to and from the transport are activated, and the transport is connected to the formatter.

3-32. Synchronous Forward Command (ISFC). This is a level which, when true and the selected transport is ready and on line, causes the tape to move in the forward direction at the specifed speed. When the level goes false, tape motion ceases.

3-33. Synchronous Reverse Command (ISRC). This is a level which, when true and the selected transport is ready and on-line, causes the tape to move in the reverse direction at the specified speed. When the level goes false, tape motion ceases.

3-34. Rewind Command (IRWC). This is a pulse which, if the selected transport is ready and on-line, causes the transport to rewind to BOT.

3-35. Off-Line Command (IOFC). This is a pulse which places the selected transport under local control. An off-line command can be given while a rewind is in progress, provided IOFC is separated by at least 1 microsecond from IRWC.

3-36. Set Write Status (ISWS). The level on this line is the output of a flip-flop within the formatter which identifies the read/write status specified in the last command. The level on this line controls the selected transport's read/write electronics. When this level is set true, it causes the selected transport to enter the write mode of operation. When this level is false, the transport will enter the read mode of operation.

3-37. Regardless of the state of the ISWS line, the transport will be forced into the read mode of operation under any one of the following conditions:

- a. An RWC or OFC is received.

- b. Transport is switched to the off-line mode.

3-38. Overwrite (IOVW). This is a level which, when true, causes special action in the write electronics of the selected transport to facilitate the editing of tapes. The level is the output of a flip-flop in the formatter logic which stores the condition edit as specified in the last command.

3-39. Read Threshold 2 (IRTH2). The level on this line is the output of a flip-flop within the formatter which stores the condition of IRTH2 specified in the last command. The output on this line is used only by transports which have extra low read threshold capabilities. When this level is true, the read electronics of the selected transport are conditioned to operate in the extra low read threshold mode. When false, the transport reverts to the normal read threshold.

3-40. Read Threshold I (IRTHI). The level on this line is the output of a flip-flop within the formatter which stored the condition of ITHRI specified in the last command. When this level is true and the transport has a single-gap head, the read electronics of the transport are conditioned to operate in the high read threshold mode. When false, the transport reverts to the normal read threshold.

3-41. Write Amplifier Reset (IWARS). This pulse occurs at the end of a write operation. In NRZI mode it causes the LRC character to be written onto tape. In nine-channel NRZI systems, WARS occurs four character periods after the CRC character is written. In seven-channel NRZI systems, WARS occurs four character periods after the last data character is written. In phase-encode mode the WARS pulse occurs immediately following the last character of the postamble during all write operations.

3-42. The leading edge of the IWARS pulse resets the write register in the selected transport at the end of skew delays. This reset action causes all channels to be erased in a uniform direction in the inter-record gap (IRG). Additionally, the WARS pulse is utilized to control the early turn-off of write current during edit operations.

3-43. Write Data Strobe (IWDS). In NRZI mode, this is a pulse for each data character to be written onto tape. In PE operation the frequency of the WDS pulse is twice that of the data transfer rate. The trailing edge of each WDS pulse is utilized to copy data appearing on WDP, WD0-WD7 into the write register in the selected transport logic. The formatter logic holds WDP, WD0-7 steady for the duration of each WDS.

3-44. In nine-channel NRZI systems, the CRC character is written by an additional WDS pulse. This WDS pulse occurs four character periods after the last data character has been written. The appropriate CRC data on WDP, WD0-7 accompanies this pulse.

3-45. Write Data (IWDP, IWD0-IWD7). These nine lines are utilized to transfer the phase-encoded data from the formatter to the selected transport. The information is copied on the edge of each IWDS pulse into the selected transport write logic and written directly onto the tape.

3-46. Data Density Select (IDDS - Optional). The level on this line is the output of a flip-flop in the formatter which stores the condition of DEN as specified in the last command. The levels on this line control the packing density of data transfers to and from tape. IDDS is routed to the Density Indicator line (IDDI). When used with a NRZI, seven-channel transport, a true level on this line selects the lower of two possible packing densities, a false level, the high of the two. When used with a dual-mode transport, the true level selects NRZI and the false level selects PE.

3-47. Load and On Line (ILOL). This signal is described in paragraph 3-16 as a controller-to-formatter input.

## INTERFACE INPUTS (TRANSPORT TO FORMATTER).

3-48. Ready (IRDY). This is a level which is true only when the transport is ready to receive external commands. The following conditions must exist:

- a. Initial load or rewind sequence is complete.

- b. Transport is on line.

- c. Transport is not rewinding.

3-49. On Line (IONL). This is a level which, when true, indicates that the selected transport is under remote control. This level is false when the transport is off line and cannot be operated remotely.

3-50. Rewinding (IRWD). This is a level which is true when the selected transport is engaged in a rewind operation.

3-51. File Protect (IFPT). This is a level which is true when the transport power is on and a reel of tape without a write enable ring is mounted on the transport.

3-52. Load Point (ILDP). This is a level which is true when the BOT tab is located under the photo-tab sensor. The ILDP level goes false when the tab leaves the photo-tab sensor.

3-53. End of Tape (IEOT). This is a level which, when true, indicates that the EOT reflective tab is positioned under the photo-tab sensor. This level is not staticized, and transitions to and from the true state are not necessarily clean.

3-54. Data Density Indicator (IDDI). The levels on this line are relevant only to seven-channel systems. They select either the high or low-density mode of operation for both transport and formatter. When true, the high-density mode is selected; when false, the low-density mode is selected. DDI is normally controlled by the density select switch (HI DEN) located on the selected transport. Alternatively, if the selected transport contains the external density select option, density selection may be controlled from the customer's equipment via the DEN and DDS interface lines.

3-55. NRZI (INRZ). This is a level which, when true, indicates that the transport is of the NRZI type. When false, this level indicates that the transport is of the PE type. When the level on this line is true, the PE circuitry is disabled. When the level is false, the NRZI circuitry is disabled.

3-56. Seven-Track (I7TR). This level, when true, indicates that a seven-channel transport has been selected. When false, it indicates that a nine-channel transport has been selected. This line also forces the formatter to the NRZI mode of operation.

3-57. Single (ISGL). This level, when true, indicates that the selected transport has a single-gap read/write head. When false, the level indicates that the selected transport has a dual-gap read-after-write head. The levels on this line condition the formatter to generate appropriate delays for the generation of the IRG and for head positioning.

3-58. Speed (ISPEED). This line is used when it is desired to attach transports of two different tape speeds to the formatter. When false, it indicates the selected transport is a high-speed unit; when true, it indicates the selected transport is a low speed one.

3-59. Read Data Strobe (IRDS) (NRZI Only). This pulse is generated for each character of information read from tape on the selected transport. The formatter logic samples read data appearing on RDP, RD0-7 on the trailing edge of each RDS pulse.

3-60. Read Data Lines (IRDP, IRD0-IRD7). The nine read data lines are employed to transmit read data from the selected transport to the formatter. In NRZI mode, each character of information is identified by a pulse on the RDS line and is copied into the formatter logic on the trailing edge of RDS.

3-61. In PE mode, these lines are the outputs of nine peak detectors, individually gated with the output of a threshold detector associated with each channel. The read signals are replicas of the PE waveforms used to drive the write amplifiers.

Revised

## SECTION IV

## OPERATION

#### BASIC OPERATION

4-1. The formatter is capable of executing the commands listed in Table 4-1. When a command is received from the customer's controller, the formatter "goes busy" and performs all control and timing functions necessary to execute the command. Any errors occuring during execution of the command are reported to the controller. On completion of the command execution, the formatter signals the controller, and the controller is then free to issue a further command. Two other command lines, which cause the transport to rewind or to be switched off line, are provided. These commands are routed directly to the selected transport and do not cause the formatter to go busy.

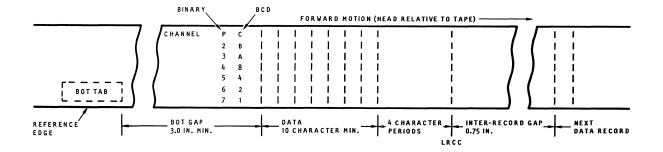

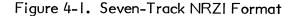

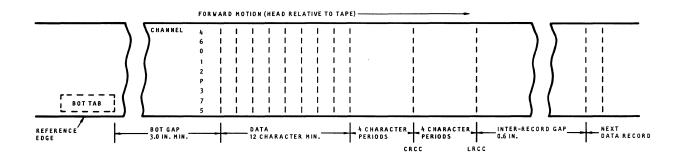

4-2. An automatic read-after-write data check is performed during each WRITE command for transports with dual-gap heads. Read-after-write data is transmitted to the controller in the same manner as during READ commands. NRZI seven- and nine-channel tape formats are illustrated in Figures 4-1 and 4-2, respectively, and Figure 4-3 illustrates the nine-track PE tape format.

#### NRZI MODE

4-3. Operations performed by the formatter in the NRZI mode are described in the subparagraphs hereof.

4-4. Gap Generation. The formatter provides all timing necessary for generation of the following gaps for nine- and seven-channel tape formats:

a. Interblock gap: a gap between each record with a nominal length on a nine-channel tape of 0.6 inch (minimum, 0.5 inch); on a seven-channel tape, 0.75 inch (minimum, 0.68 inch). Maximum interblock gap length depends on the number of consecutive erasures and is not limited by the formatter.

.

#### NOTES

- 1. 2.

- 3.

- TAPE SHOWN WITH OXIDE SIDE UP. CHANNELS 2 THROUGH 7 CONTAIN DATA BITS IN DESCENDING ORDER OF SIGNIFICANCE. CHANNEL P (PARITY) CONTAINS ODD DATA PARITY FOR BINARY TAPES, OR EVEN PARITY FOR BCD TAPES. EACH BIT OF THE LRCC IS SUCH THAT THE TOTAL NUMBER OF "I" BITS IN THAT TRACK (INCLUDING THE LRCC) IS EVEN. IT IS POSSIBLE IN THAT TRACK (INCLUDING THE LRCC) IS EVEN. IT IS POSSIBLE IN THAT TRACK (INCLUDING THE LRCC) IS EVEN. IT IS POSSIBLE IN THAT TRACK (INCLUDING THE LRCC) IS EVEN. IT BE ALL ZEROS. IN WHICH CASE A READ DATA STROBE WILL NOT BE GENERATED. A FILE MARK IS A SINGLE CHARACTER RECORD HAVING "I" BITS IN CHANNELS 4, 5, 6, AND 7 FOR BOTH THE DATA CHARACTER AND THE LRCC. THIS RECORD IS SEPARATED BY 3.5 INCHES FROM THE PREVIOUS AND BY A NORMAL IRG (0.75 IN.) FROM THE FOLLOWING RECORD. DATA PACKING DENSITY MAY BE 200, 256, OR 800 BITS PER INCH. 4.

- 5.

- 6. INCH.

NOTES

- TAPE SHOWN WITH OXIDE SIDE UP. CHANNELS 5 THROUGH 7 CONTAIN DATA BITS IN DESCENDING ORDER OF SIGNIFICANCE. CHANNEL P (PARITY) ALWAYS CONTAINS ODD DATA PARITY. 1. 2.

- 3. 4.

- 5.

- 6.

- CHANNEL P(PARITY) ALWAYS CONTAINS ODD DATA PARITY. EACH BIT OF THE LRCC IS SUCH THAT THE TOTAL NUMBER OF "" BITS IN THAT TRACK (INCLUDING THE CRCC AND LRCC) IS EVEN. IN THE 9-TRACK FORMAT THE LRCC WILL NEVER BE AN ALL-ZEROS CHARACTER. IT IS POSSIBLE FOR THIS CRCC CHARACTER TO BE ALL ZEROS, IN WHICH CASE A READ DATA STROBE WILL NOT BE GENERATED. A FILE MARK IS A SINGLE CHARACTER RECORD HAVING "I" BITS IN CHANNELS 3, 6, AND 7 FOR BOTH THE DATA CHARACTER AND THE LRCC. THE CRCC CONTAINS ALL ZEROS. THIS RECORD IS SEPARATED BY 3.5 INCHES FROM THE PREVIOUS RECORD AND BY A NORMAL IRG (0.6 IN.) FROM THE FOLLOWING RECORD. DATA PACKING DENSITY IS FIXED AT 800 BITS PER INCH.

- 7.

Figure 4-2. Nine-Track NRZI Format

Revised

Figure 4-3. Nine-Track PE Tape Format

- b. Initial gap: a gap preceding the writing of the first data character of the first record from BOT, extending approximately 3.5 inches past the trailing edge of the BOT tab.

- c. File mark gap: a gap of approximately 3.5 inches of tape preceding the file mark. The file mark is followed by a normal IBG.

| REV | / WRT             | WFM | EDIT | ERASE | COMMAND                           |

|-----|-------------------|-----|------|-------|-----------------------------------|

| 0   | 0                 | 0   | 0    | 0     | Read Forward                      |

| 1   | 0                 | 0   | 0    | 0     | Read Reverse                      |

|     | 0                 | 0   | I    | I     | Read Reverse Edit                 |

| 0   | 1                 | 0   | 0    | 0     | Write                             |

| 0   | I                 | 0   | I    | 0     | Write Edit                        |

| 0   | 1                 | I   | 0    | 0     | Write File Mark                   |

| 0   | I                 | 0   | 0    | 1     | Erase Variable Length             |

| 0   | 1                 | I   | 0    | l     | Erase Fixed Length                |

| 0   | 0                 | 0   | 0    | 1     | Space Forward                     |

| 1   | 0                 | 0   | 0    | I     | Space Reverse                     |

| 0   | 0                 | l   | 0    | 0     | File Search Forward               |

| 1   | 0                 | l   | 0    | 0     | File Search Reverse               |

| 0   | 0                 | 1   | 0    | 1     | File Search Forward (ignore data) |

| l   | 0                 | 1   | 0    | 1     | File Search Reverse (ignore data) |

| l = | I = true 0 = fals |     |      |       |                                   |

4-5. Writing. During a write operation, the formatter controls the transfer of write data from the controller to the selected transport. The data transfer rate is a function of the tape speed and the data packing density. The CRC and LRC check characters are generated internally by the formatter and are inserted automatically at the end of the record.

4-6. Reading. During reading, data is transferred character by character from the transport to the formatter. The formatter separates data and check characters, performs various error checks, and retransmits the information to the controller via nine data lines and a strobe line, RSTR. Both the data and check characters are identified by a special interface line (CCG), which is true when the check characters are being transmitted.

#### NOTE

Under certain circumstances, the CRC or LRC character may not exist on tape (all 0's character). In this case, no character (or associated RSTR pulse) will be transmitted to the controller.

4-7. File Mark. When executing a Write File Mark (WFM) command, the formatter automatically generates the appropriate file mark patterns to record onto tape. During any read operation (read forward, read reverse, or read-after-write), the formatter tests for the presence of the file mark pattern. When this is detected, the FMK interface line to the controller is pulsed. In addition, the file mark characters read from tape are transmitted to the controller. When reading in a forward direction, the first character is transmitted as a data character (CCG false), and the second is transmitted as a check character (CCG true). When reading is in reverse, the two characters are reversed.

4-8. In the case of seven-channel operations in the binary (odd parity) mode, the file mark data character (0001111) has "incorrect" parity, and a data parity error (HER) is signalled to the controller. The controller should therefore be designed to ignore error conditions when a file mark is detected.

4-9. Parity. For nine-channel operation, all data transfers take place in the odd parity mode. For seven-channel operation, data parity may either be odd (binary mode) or even (BCD mode) and is selected by the controller via interface line IPAR.

4-10. When writing, the formatter generates the appropriate parity bit from the data present on the eight data lines. A switch option which allows the parity bit to be supplied externally by the controller is provided. In a read operation, the data received from the transport is checked for parity.

4-11. Density Selection. In nine-channel operation, all data transfers take place at a data packing density of 800 bpi. In seven-channel operation, the formatter can perform data transfers at either of two of the three possible packing densities of 800, 556, and 200 cpi. A seven-track machine must not be used as the host transport. The desired density combination (800/556, 800/200) must be identical for both formatter and transport.

4-12. The current density (high or low) can be controlled by a density select switch (HI DEN) on the front panel of the selected transport. When the switch is illuminated, the formatter is conditioned to operate in the high-density mode.

4-13. As an alternative to this, an optional feature in the transport logic permits selection of the current operating density by the controller via the interface line, IDEN.

4-14. BCD Zero Conversion. In the seven-channel BCD (even parity) mode, an all-0's character is invalid. In this mode, the formatter detects the presence of an all-0's character from the controller and automatically substitutes a BCD ten (001010) character.

4-15. Error Checking. During any read operation (read forward, read reverse, or read-after-write) the formatter performs the following checks:

- a. Vertical parity check on each data character.

- b. Vertical parity check on CRC character.

- c. Longitudinal parity check.

- d. Improper record format.

- e. CRC check.

- 4-16. Options. The following options are available:

- a. Formatter address: 0 or 1.

- b. Internal or external write parity generation.

- c. Seven-channel density combinations.

#### PHASE-ENCODE MODE

4-17. Operations performed by the formatter in the PE mode are described in the subparagraphs hereof.

4-18. Identification Burst (Figure 4-3). When performing any write operation from BOT, the formatter automatically writes an IBM-compatible identification mark on the tape. This mark consists of a series of flux reversals at 1600 cpi in channel P, with all other channels erased. Three inches of tape are then erased before the first block of data is written.

4-19. When reading from BOT, the formatter samples the output of the parity track. If the identification mark is found, the IDENT line is pulsed.

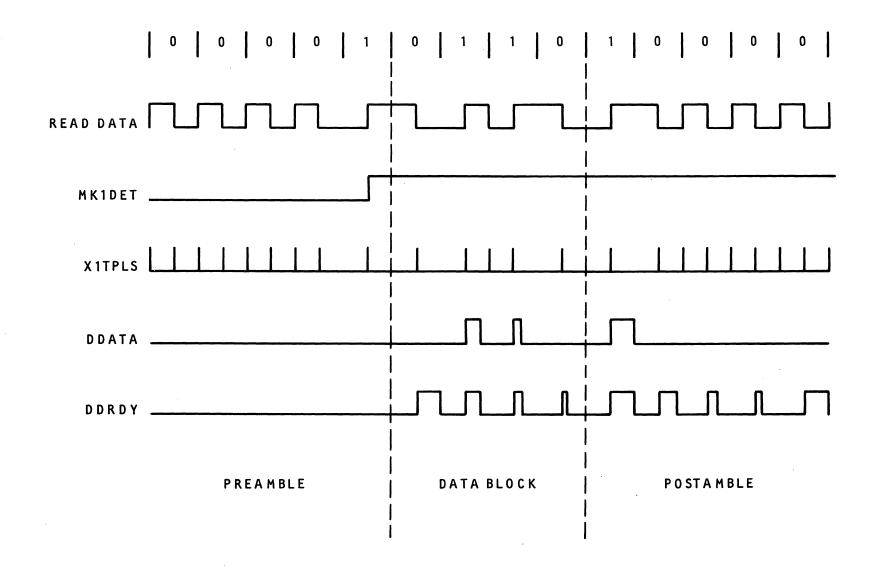

4-20. Preamble. When writing, the formatter generates a preamble which precedes the data field of the record. The preamble consists of 40 zero bits, followed by a one bit, recorded in each of the nine tracks.

4-21. Postamble. A postamble is written following the data field of the record. The postamble also consists of 40 zero characters preceded by a one character in each of the nine tracks. When reading, the formatter separates the preamble and postamble from the data.

4-22. Data. When writing, the formatter accepts data character by character and converts it into a phase-encoded signal in which the following conditions exist:

- a. A 0 bit is characterized as a flux transition in the middle of the bit cell away from the erase direction of magnetization.

- b. A 1 bit is characterized by a transition in the middle of the bit cell toward the erase direction of magnetization.

4-23. File Mark. When in the write mode of operation the formater generates the IBM/ANSI-compatible file mark, preceded by a long (3.5 inches) gap of erased tape. With the formatter in the read mode, the compatible file mark is detected and verified by the file mark status line (IFMK).

4-24. Gaps. The formatter provides the timing required to generate the following gaps:

- a. Interblock gap (IRG): a gap with a nominal length of 0.6 inch written between each record.

- b. Initial gap: when writing from BOT, an identification burst, followed by a 3-inch gap, written before the first record.

- c. File mark gap: a gap of approximately 3.75 inches preceding a file mark.

4-25. All gaps are written by saturating the tape in the erase direction of magnetization.

4-26. Parity. During a write operation, the formatter generates odd parity derived from the data present on the eight data channels. When reading, the formatter checks that the parity of the nine tracks is odd. An error is signaled when the parity check fails.

4-27. Dropout and Error Correction. The formatter provides single and multipletrack dropout detection. When a single-track dropout occurs, the formatter corrects the data by the use of the data in the other seven tracks and the parity bits. A status line to the controller indicates when error correction is taking place. After a dropout has been detected, the output of the affected track will be ignored, and no attempt will be made to resynchronize the discriminators of that track.

#### SECTION V

#### DETAILED ELECTRICAL AND LOGIC DESCRIPTION

#### INTRODUCTION

5-1. This section consists of a detailed description of the formatter logic operation. Relevant schematic and assembly drawings are presented at the end of Section VII. Reference should also be made to Section IV for a discussion of the block diagram level. Before proceeding, it will be useful to list some of the conventions that have been adopted concerning waveform names, logic levels, and logic symbols.

#### INTERNAL FORMATTER SIGNALS

5-2. The formatter logic levels are 0 volts and +4 volts (approximately). The basic waveform names within the formatter have been chosen to correspond to the high-true condition (e.g., the waveform WRT is at +4 volts when writing and at 0 volts when not writing). (See Table 5-1 for detailed descriptions of all waveforms and mnemonics.) The inverse waveform (low-true equivalent) usually retains the same basic name but has an asterisk preceding the mnemonic (e.g., WRT, \*WRT). Logic signals which perform gating functions are identifed at the gate in the form which will satisfy the gate logic.

#### INTERFACE SIGNALS

5-3. All signals on the controller/formatter and formatter/transport interfaces are low-true, with signal levels of +3 volts for false and 0 volts for true. The false level of +3 volts is determined by a 220/330-ohm resistor chain which terminates each line at the receiver end. Interface waveform names are always prefixed by the letter "!", e.g., IWRT.

#### LOGIC ELEMENTS AND SYMBOLS

5-4. The formatter logic is designed primarily around the low-power Schottky TTL series of integrated circuit (IC) elements. The ICs on the PWB are in a grid array, with each location identified by row (letter) and column (number). The symbol for each logic element includes the appropriate U number and identifies each input and output pin. The device type is listed as well. Two different types of gating elements are employed: the high-true NAND and the high-true NOR. Both types consist of a gating function followed by an inversion.

| WAVEFORM MNEMONICS                                                  | FUNCTION                                                                                                                                                                                                               |  |  |  |  |  |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| BDDLY (Block Detect Delay)<br>(Sheet 25, Drawing No.<br>360001-300) | Pulse which initiates BLKDET after ENV has<br>remained true for four character periods or<br>terminates BLKDET after ENV is lost for<br>four character periods.                                                        |  |  |  |  |  |

| BGNPRMBL (Begin Preamble)<br>(Sheet 27)                             | Indicates data being read is first of preamble. Also enables file mark detector.                                                                                                                                       |  |  |  |  |  |

| BLKDET (Block Detect) (Sheet 25)                                    | Indicates data envelope has been detected.                                                                                                                                                                             |  |  |  |  |  |

| BOBPLS (Beginning of Block<br>Pulse) (Sheet 25)                     | Pulse occuring on rising edge of BLKDET.<br>Initiates block format control logic.                                                                                                                                      |  |  |  |  |  |

| CHARGATE (Character Gate)<br>(Sheets 19 and 24)                     | Distinguishes data transitions from phase<br>transitions. When true, indicates next<br>transition should be data bit. After data<br>transition, CHARGATE will be set false for<br>three quarters of the bit cell time. |  |  |  |  |  |

| CCDLY (Check Character Delay)<br>(Sheet 6)                          | This signal causes a four-character delay before writing of a check character.                                                                                                                                         |  |  |  |  |  |

| CCE (Check Character Error)<br>(Sheet 15)                           | Signifies that an additional character was detected following the check characters.                                                                                                                                    |  |  |  |  |  |

| CCG (Check Character Gate)<br>(Sheet 15)                            | This line goes true whenever a check<br>character is being transmitted to the<br>controller.                                                                                                                           |  |  |  |  |  |

| CDP (Character Detect Pulse)<br>(Sheet 14)                          | A pulse generated each time a NRZ character has been detected.                                                                                                                                                         |  |  |  |  |  |

| CHDDROP (P, 0-7) (Channel<br>Drop) (Parity, 0-7) (Sheets 16-24)     | Indicates channel has been dropped (i.e., data<br>transition did not occur within specified<br>time). Once set true, will remain true for<br>entire record.                                                            |  |  |  |  |  |

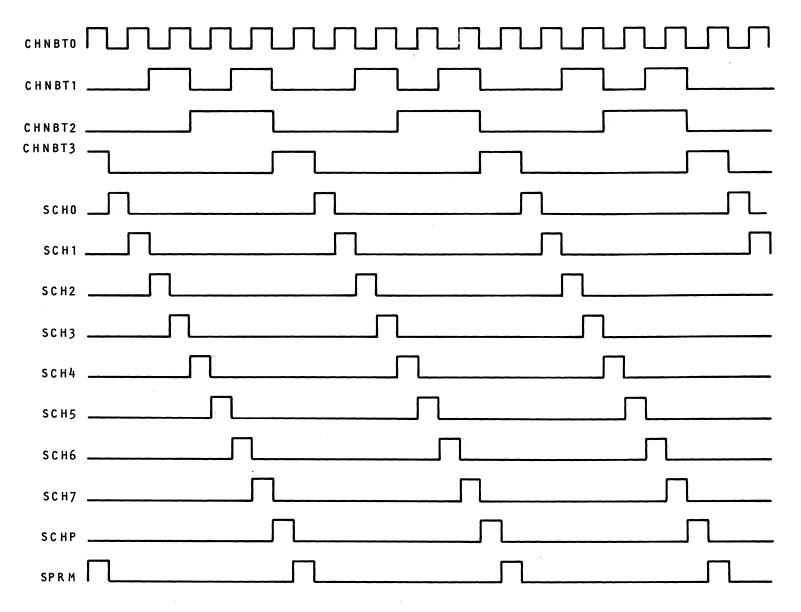

| CHNBIT (0-3) (Channel Bit) (0-3)<br>(Sheet 26)                      | These four bits are used to time-multiplex nine data channels                                                                                                                                                          |  |  |  |  |  |

| CHNDROP (Channel Drop) (Sheet<br>26)                                | Time-multiplexed channel drop signal derived from CHDDROP (P, 0-7).                                                                                                                                                    |  |  |  |  |  |

| CHPLS (Character Pulse)<br>(Sheet 27)                               | Pulse occurring at character frequency.<br>Used to increment block delay counter.                                                                                                                                      |  |  |  |  |  |

## Table 5-1. Formatter Signals, Functions, and Mnemonics

| WAVEFORM MNEMONICS                                              | FUNCTION                                                                                                                   |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| CIR (Clear Input Register)<br>(Sheet 14)                        | This signal clears the input register after a character has been loaded into the output register.                          |

| COR (Clear Output Registers)<br>(Sheet 15)                      | This signal clears the output registers at the end of a NRZI read operation.                                               |

| CRCE (CRC Enable) (Sheet 6)                                     | When true, conditions the write logic to write the CRC character.                                                          |

| CRCPE (CRC Parity Error)<br>(Sheet 15)                          | Signifies that a parity error has occurred in the CRC character.                                                           |

| CRCER (CRC Error) (Sheet 15)                                    | Indicates that the computed CRC character did not agree with the CRC character read.                                       |

| CRCDLY (CRC Delay) (Sheet 6)                                    | A four-character delay before writing of the CRC character.                                                                |

| CRCP, 0-7 (CRC Parity, 0-7)<br>(Sheet 7)                        | CRC character bits.                                                                                                        |

| DATABSY (Data Busy) (Sheet 4)                                   | Signal indicating data transfer in progress.<br>Set true after prerecord gap. Set false at<br>beginning of postrecord gap. |

| DATAIN (R1, R2, R3) (Data In)<br>(Registers 1, 2, 3) (Sheet 30) | Serial data entering postamble delay register<br>1, 2, or 3.                                                               |

| DATAINSB (Data in Skew Buffer<br>(Sheet 29)                     | Serial data to be entered into skew buffer.<br>Valid only during DATARDY.                                                  |

| DATAOUTSB (Data Out Skew<br>Buffer) (Sheet 29)                  | Serial data out of skew buffer. Valid only during RDOUTSB.                                                                 |

| DATARDY (Data Ready)<br>(Sheet 29)                              | Indicates that a data bit is ready to be entered into the skew buffer.                                                     |

| DATAXFER (Data Transfer)<br>(Sheet 4)                           | Indicates data transfer in progress. Set true<br>after prerecord gap. Set false upon<br>completion of RAMPDWN.             |

| DCEQ0 (Drop Channel Equal To<br>Zero) (Sheet 26)                | Indicates no channels dropped.                                                                                             |

| DCEQI (Drop Channel Equal to 1)<br>(Sheet 26)                   | Indicates one channel dropped.                                                                                             |

| WAVEFORM MNEMONICS                                             | FUNCTION                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCGTI (Drop Channel Greater<br>Than I) (Sheet 26)              | Indicates more than one channel dropped.                                                                                                                                                                                                                             |

| DDATA (P, 0-7) (Detected Data)<br>(Parity, 0-7) (Sheets 16-24) | Indicates data transition has occurred and allows corresponding DDATA line to be entered into skew buffer.                                                                                                                                                           |