# PUNCHED CARD EQUIPMENT TRAINING MANUAL

FIRST EDITION

# FOR TRAINING PURPOSES ONLY

This manual was compiled and written by members of the instructional staff of

CONTROL DATA INSTITUTE CONTROL DATA CORPORATION

CDI 60239300 August, 1967 History: This manual obsoletes the Punched Card Equipment Training Manual (081966) and the Punched Card Equipment Workbook.

First printing January, 1967

Former publication number 010567A

Several changes and corrections were incorporated into this manual in November, 1969.

> Copyright 1967, Control Data Corporation Printed in the United States of America

### FOREWORD

The <u>Punched Card Equipment Training Manual</u> provides information on punched card technology and equipments found in modern computer systems. The equipments considered in this manual, though products of Control Data Corporation, are representative of those used in the computer industry.

This manual contains five discrete subjects. Chapter I provides information fundamental to punched cards. Chapter II explains the CONTROL DATA 405 Card Reader. Chapter III contains information concerning the CONTROL DATA 3248 Card Reader Controller. Chapter IV explains the CONTROL DATA 415 Card Punch. Chapter V provides information regarding the CONTROL DATA 3245 Card Punch Controller.

To aid the reader, study questions are located at the end of each **chapter** and should be completed before continuing to subsequent chapters. Answers to the questions are located in Appendix A.

## CONTENTS

## CHAPTER I. STANDARD DATA CARDS

| Introduction                                     |   |

|--------------------------------------------------|---|

| Punched Cards                                    |   |

| Explanation of Hollerith and BCD Formats 1-5     |   |

| Hollerith to BCD Conversion on Punched Cards 1-8 |   |

| Card Specifications                              | 2 |

| Study Questions                                  | 5 |

CHAPTER II. 405 CARD READER

| Introduction                    |

|---------------------------------|

| Detailed Specifications         |

| Functional Description          |

| Logic Description               |

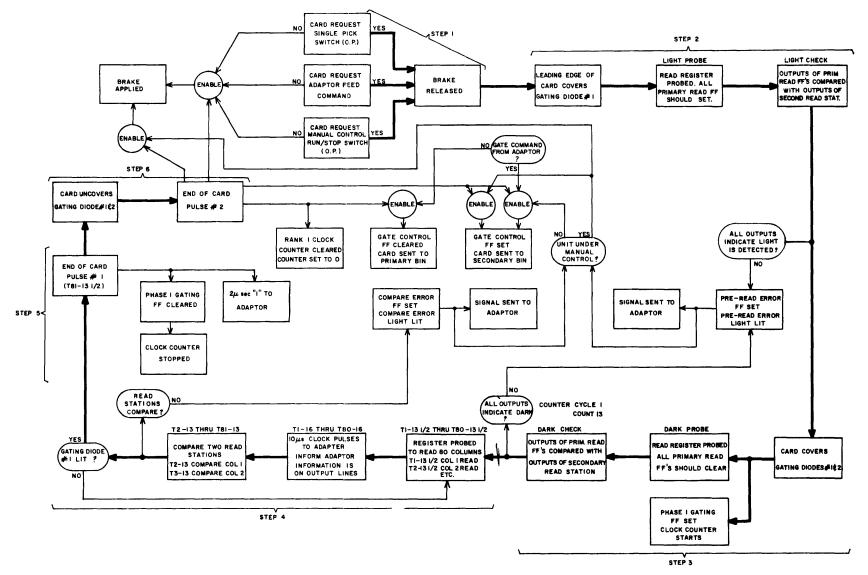

| Flow Chart of Card Movement     |

| Sequence of Operation           |

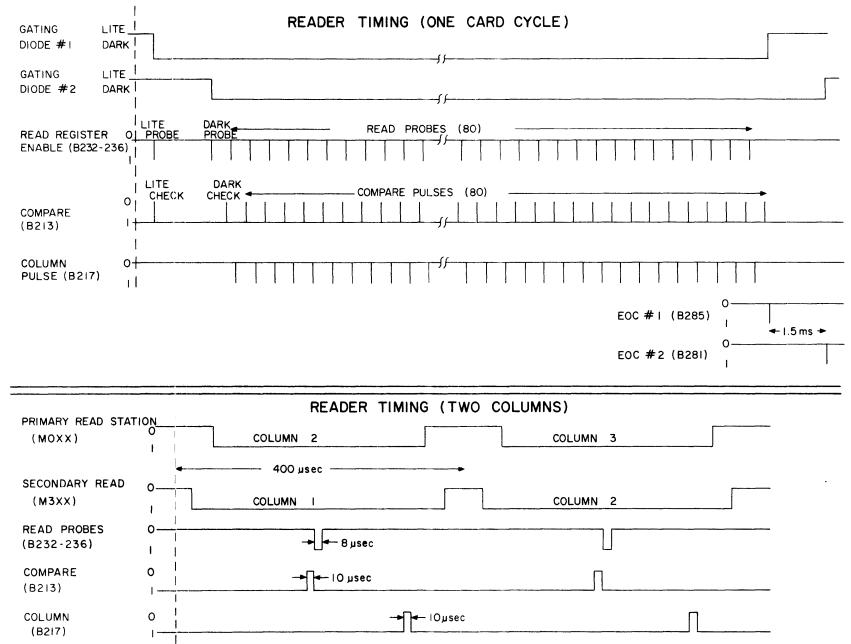

| Card Reader Timing              |

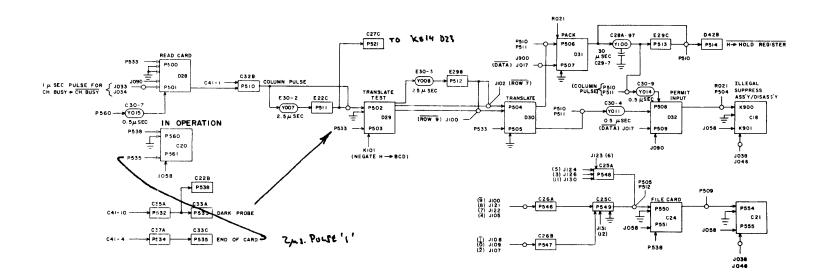

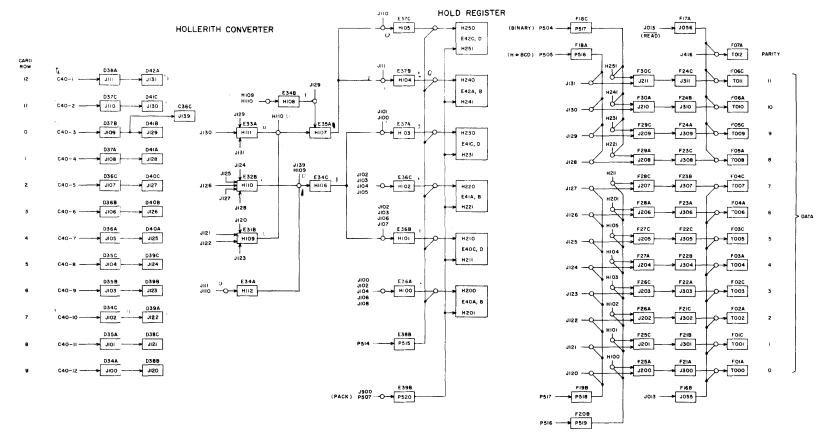

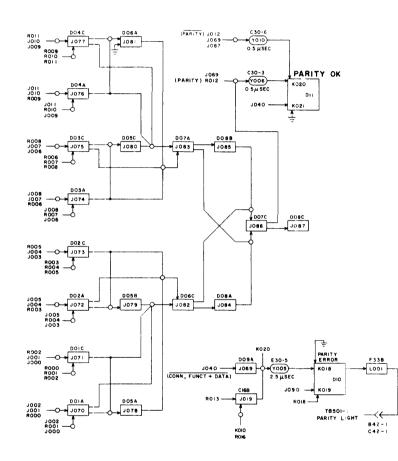

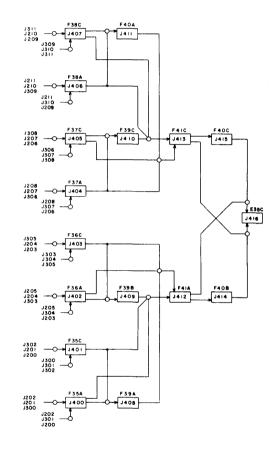

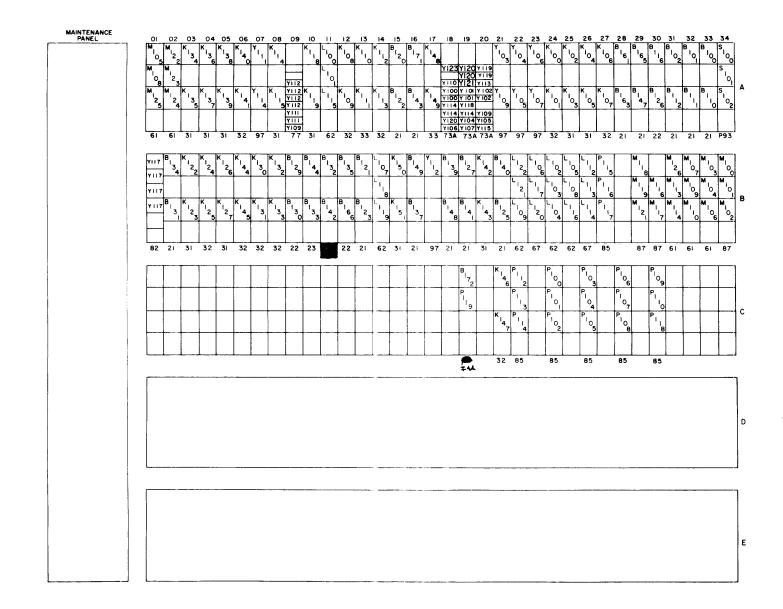

| Logic Prints                    |

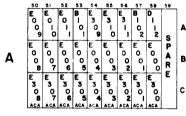

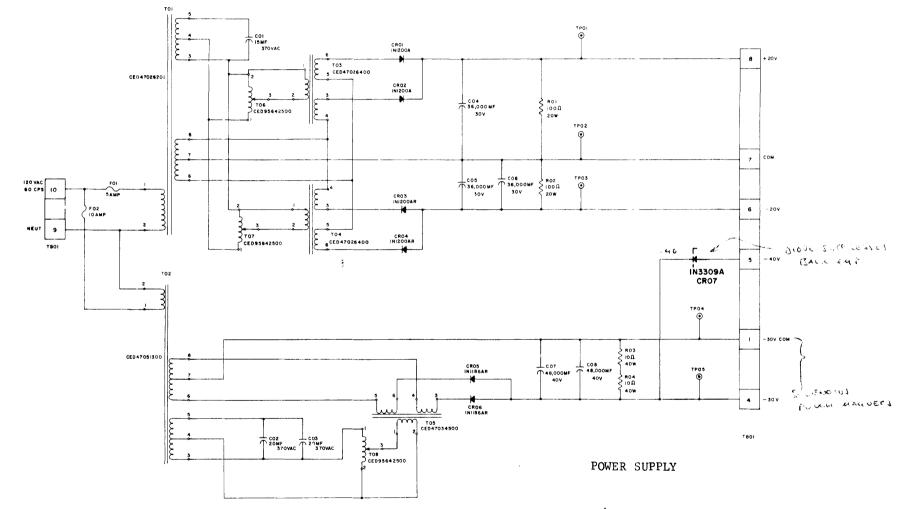

| Power Supply                    |

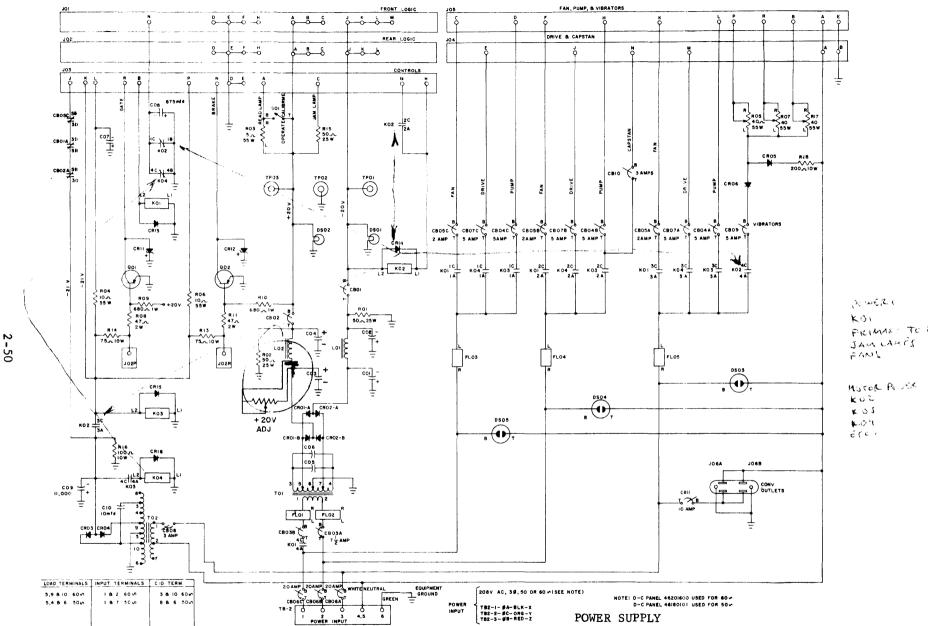

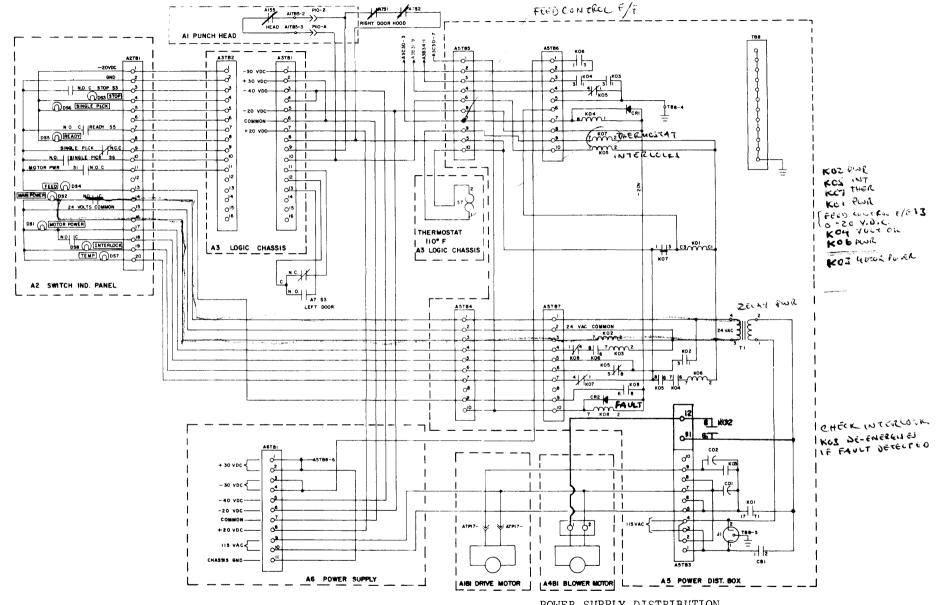

| Wiring Diagram                  |

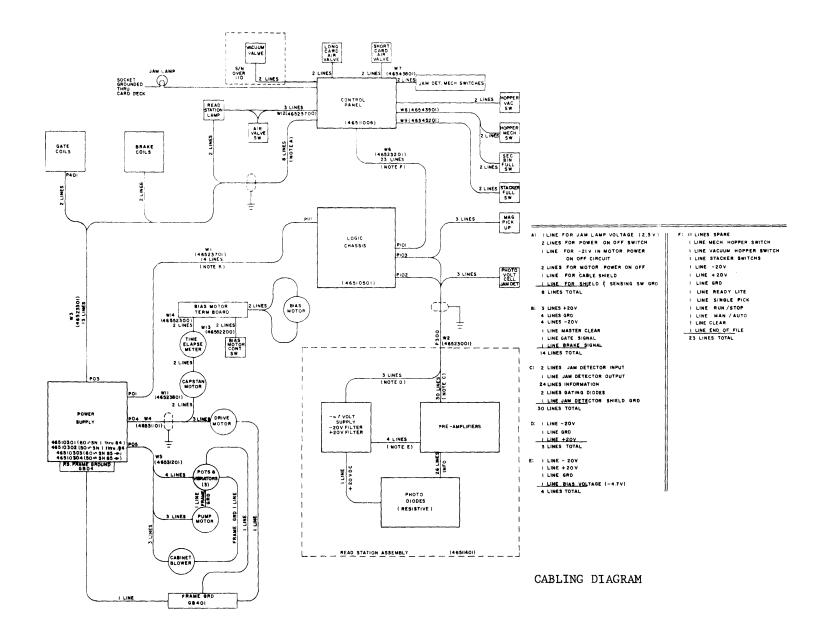

| Cabling Diagram                 |

| Practical Application Exercises |

| Study Questions                 |

# CHAPTER III. 3248 CARD READER CONTROLLER

| Introduction                                   |

|------------------------------------------------|

| Codes                                          |

| Program Concepts                               |

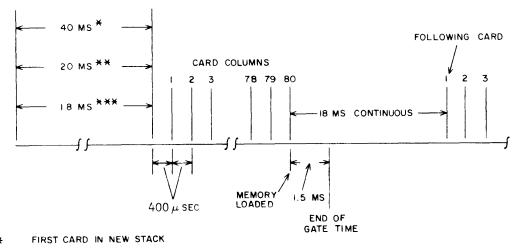

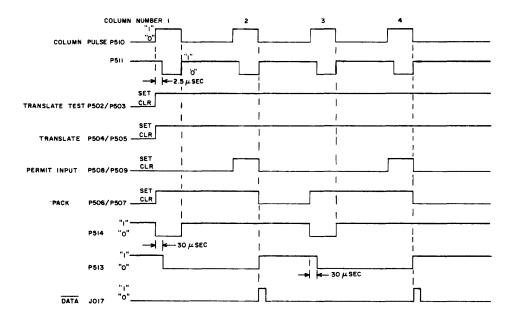

| Program Timing                                 |

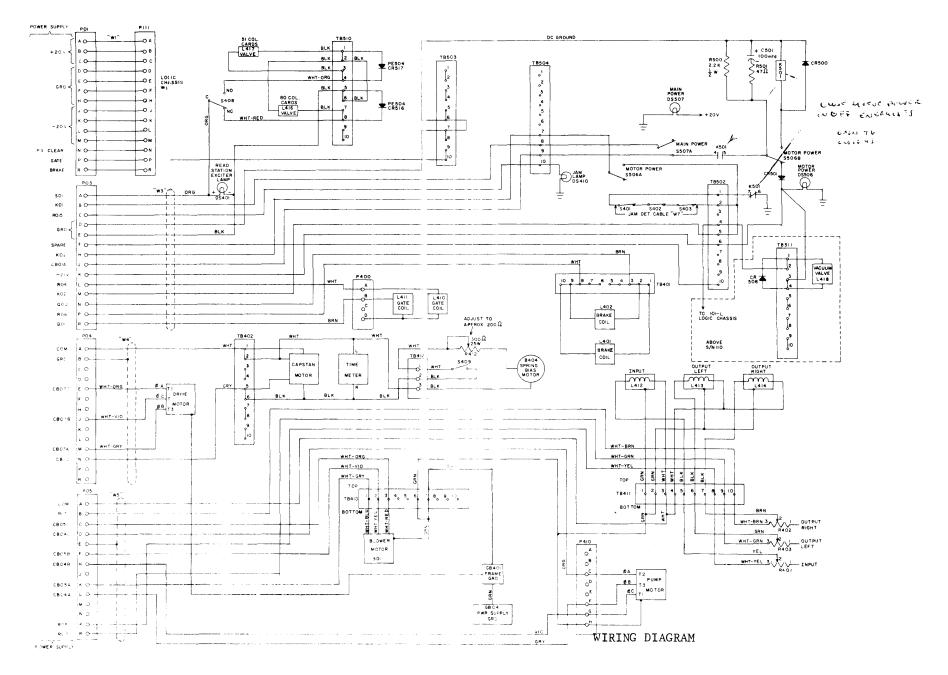

| Suppress Assembly Mode (6-Bit Character Input) |

| BCD/Hollerith Codes                            |

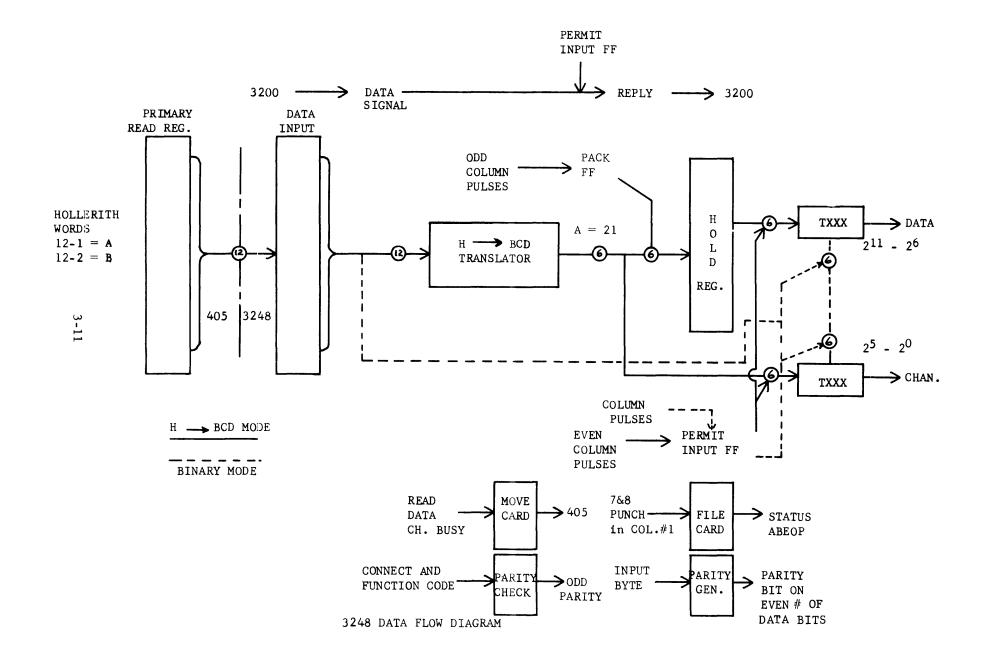

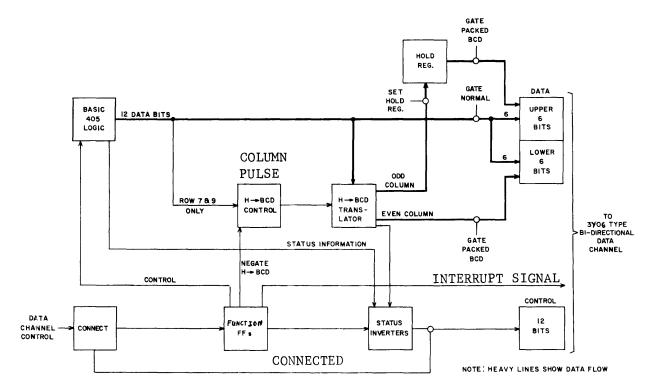

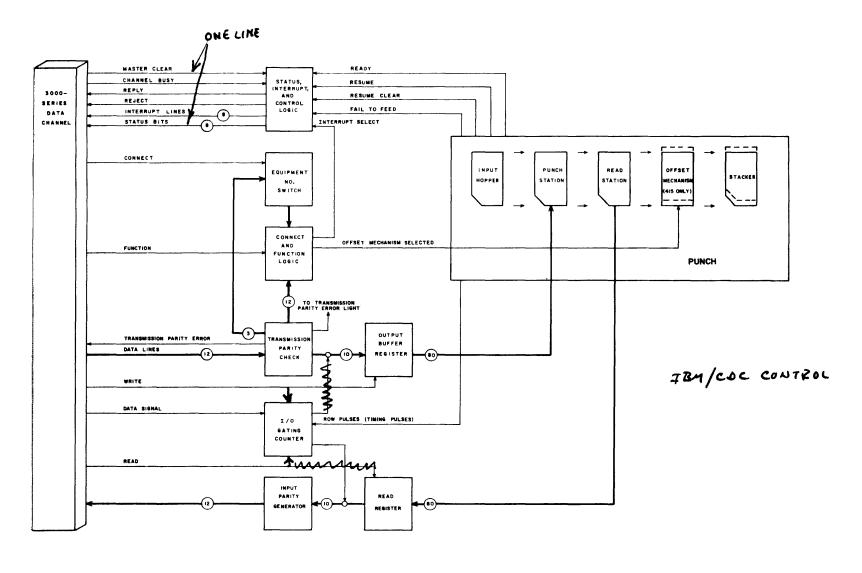

| Data Flow Diagram                              |

| Sequence of Operation                          |

| Timing for Pack Mode                           |

| Block Diagram                                  |

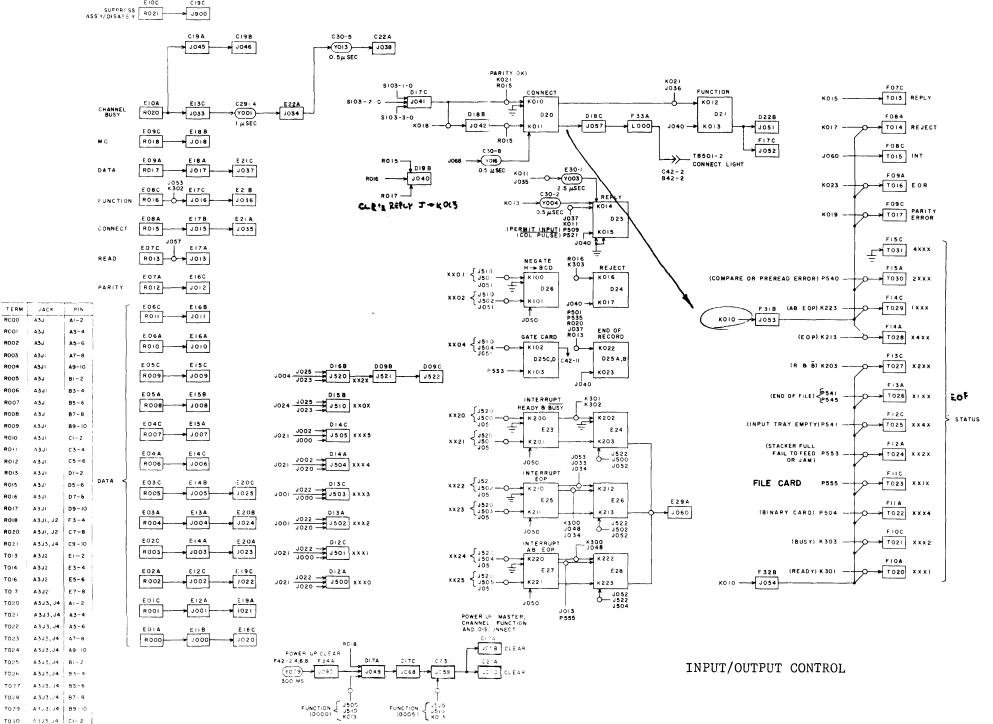

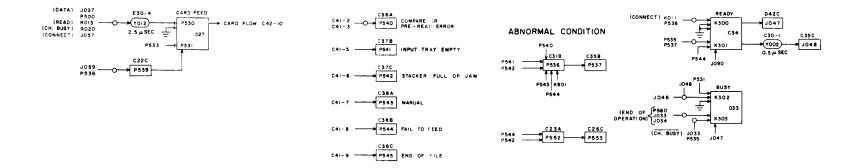

| Logic Prints                                   |

| Cabling Diagram                                |

| Study Questions                                |

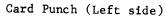

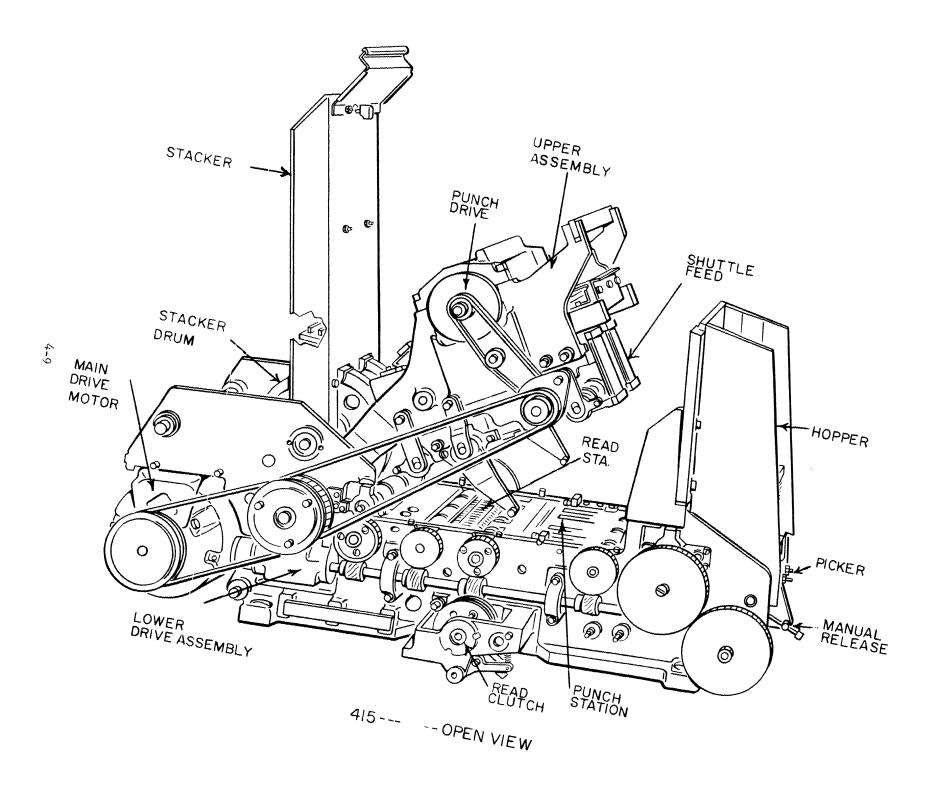

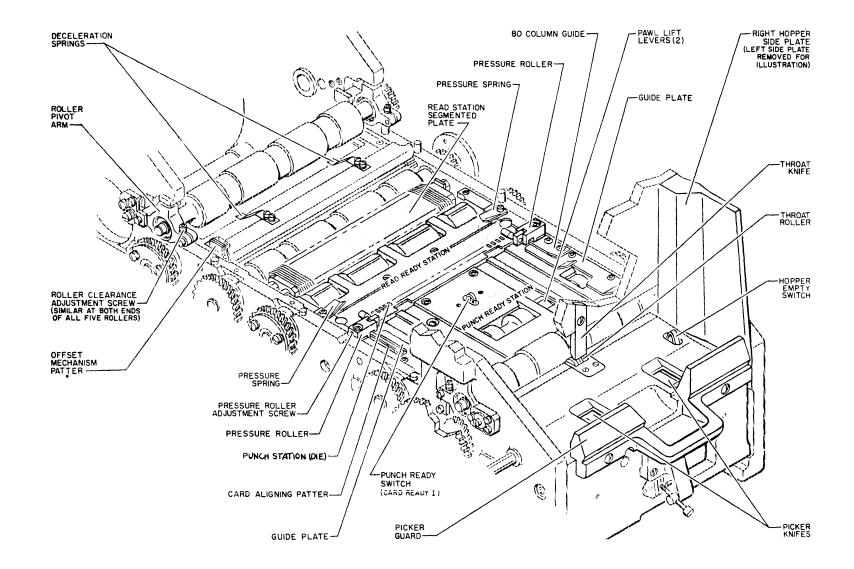

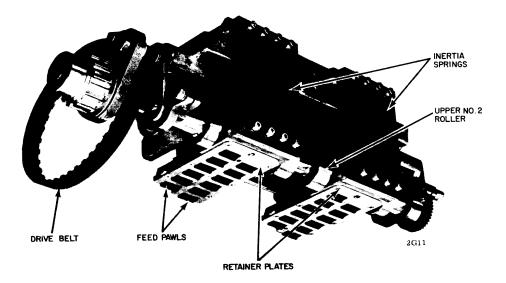

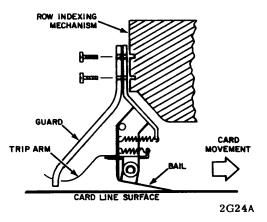

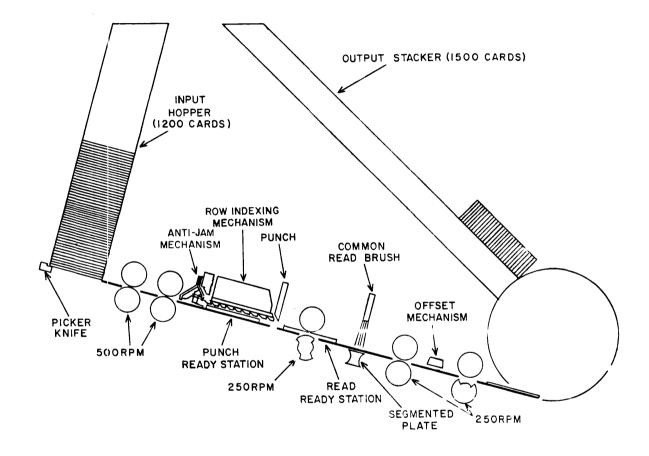

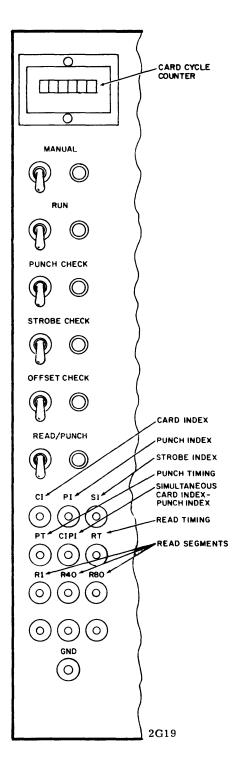

# CHAPTER IV. 415 CARD PUNCH

| ntroduction                     |

|---------------------------------|

| unctional Description           |

| Controls and Indicators         |

| ogic Description                |

| equence of Operation            |

| nput - Output Control Signals   |

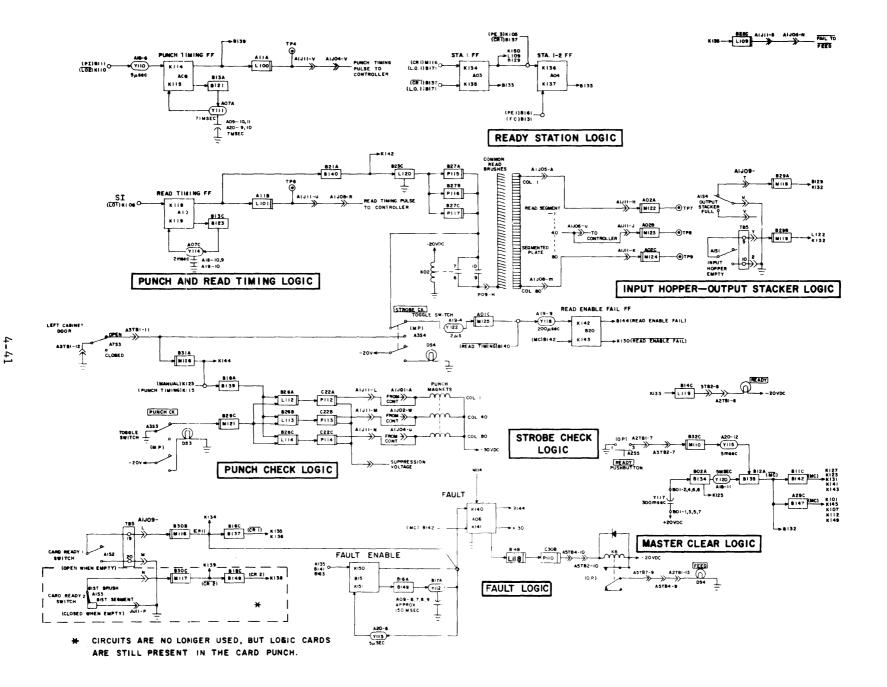

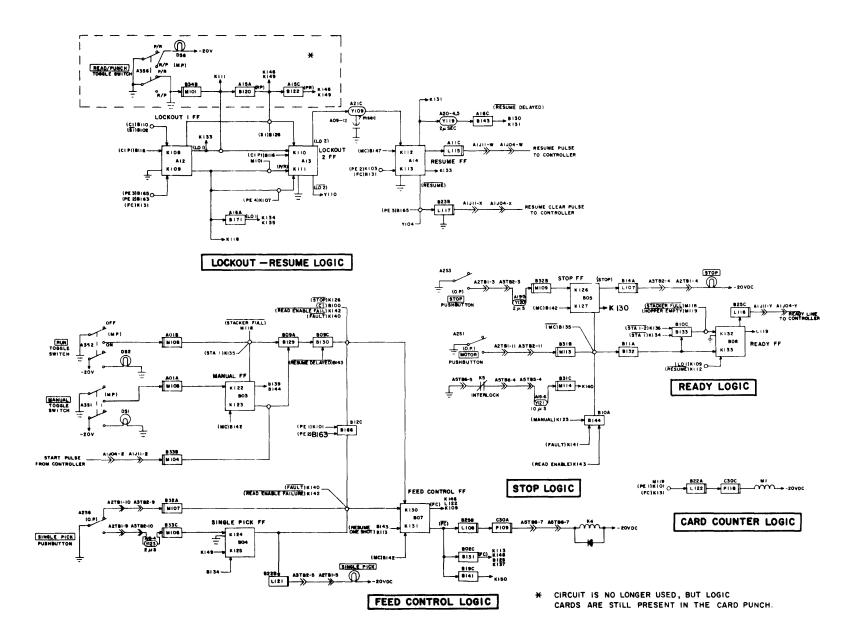

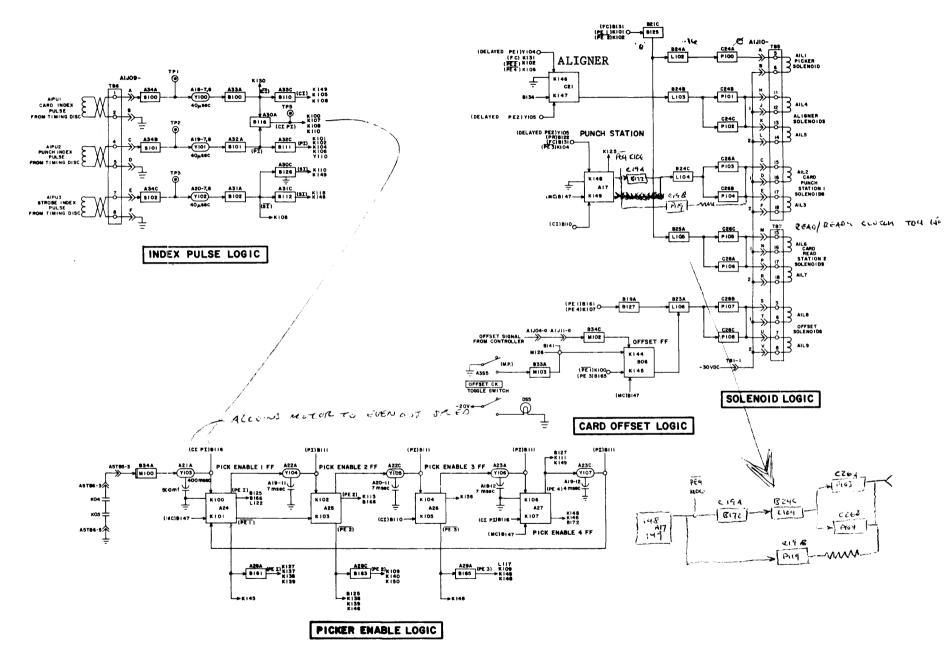

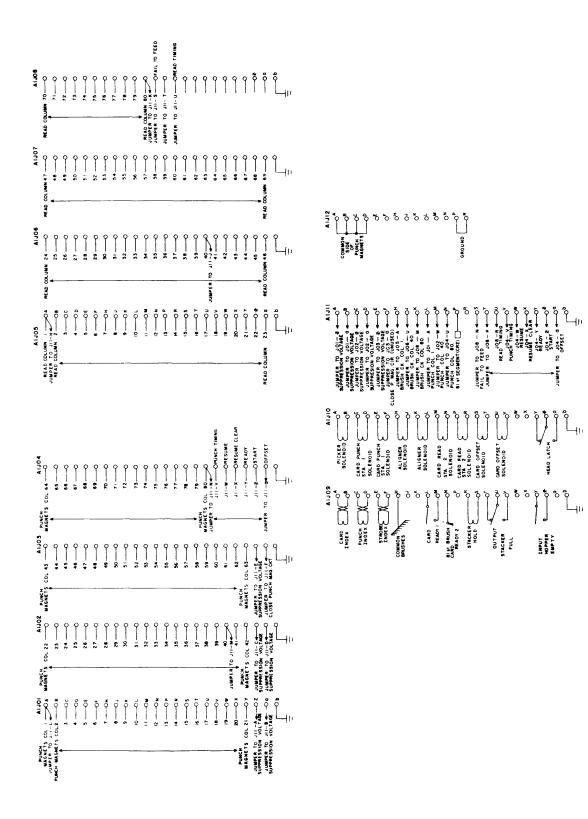

| ogic Prints                     |

| Power Supply                    |

| Power Supply Distribution       |

| Practical Application Exercises |

| tudy Questions                  |

# CHAPTER V. 3245 CARD PUNCH CONTROLLER

| Introduction             | 1  |

|--------------------------|----|

| Codes                    | 4  |

| Program Concepts         | б  |

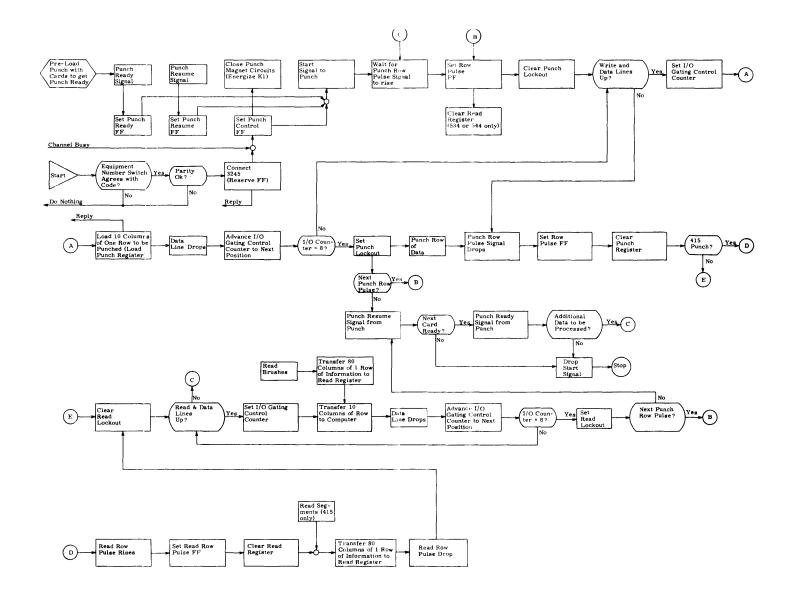

| Flow Chart               | 11 |

| Sequence of Operation    | 12 |

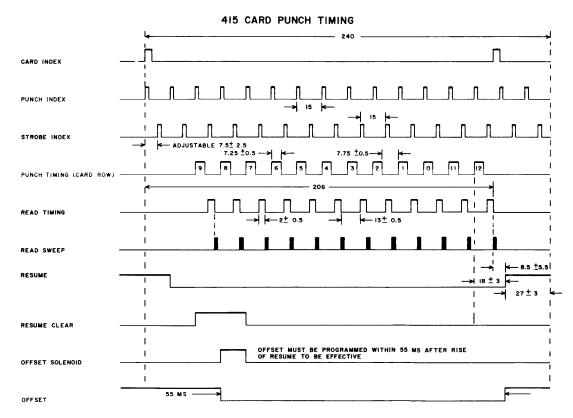

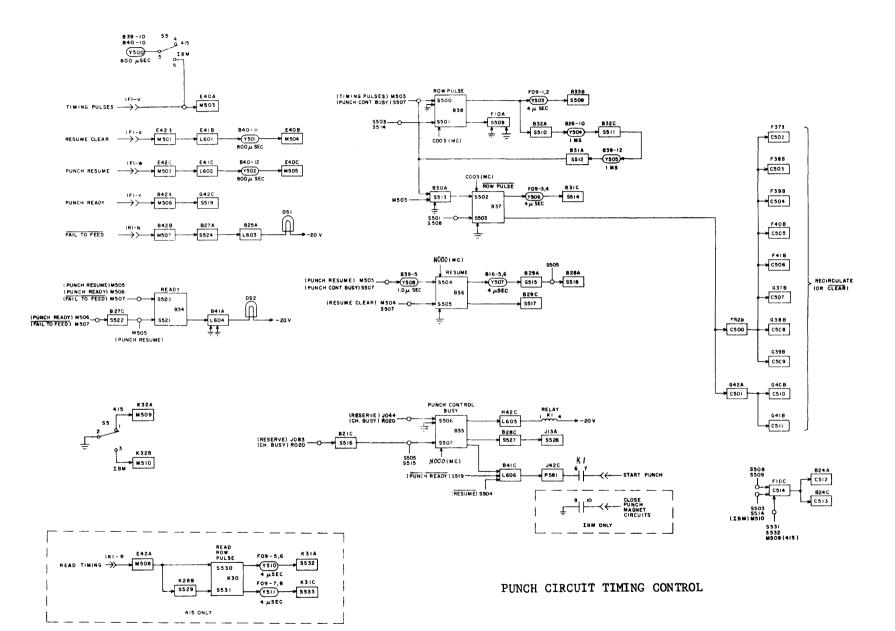

| 415 Card Punch Timing    | 17 |

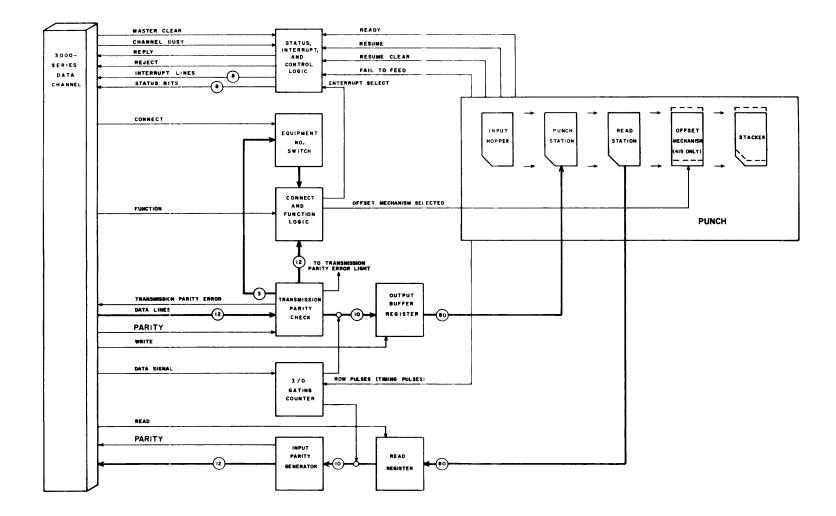

| Functional Block Diagram | 19 |

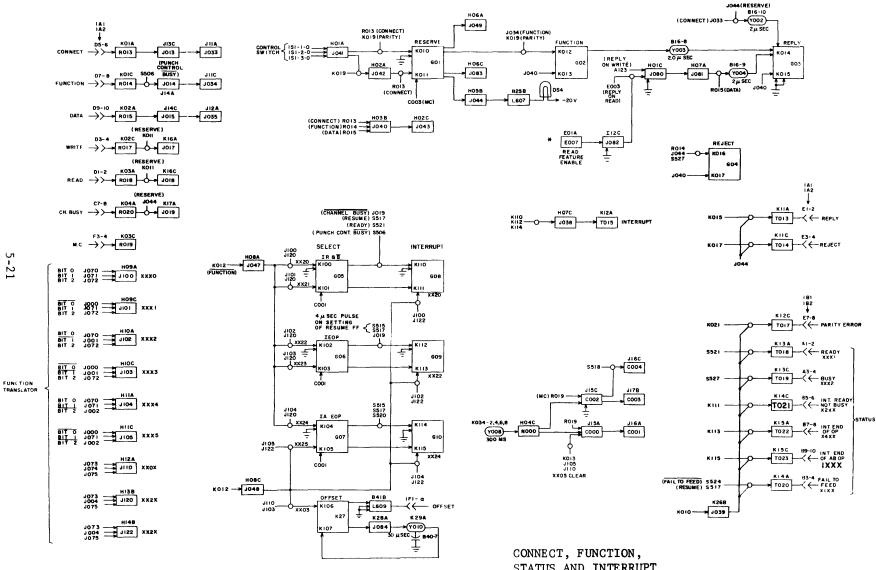

| Logic Prints             | 21 |

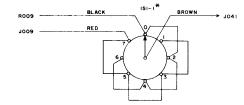

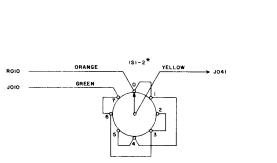

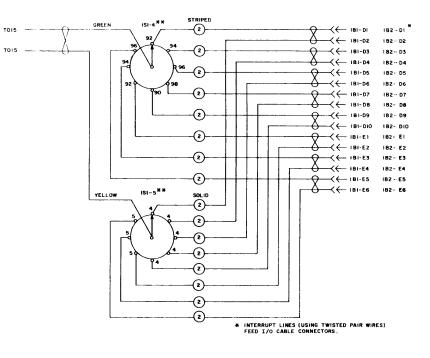

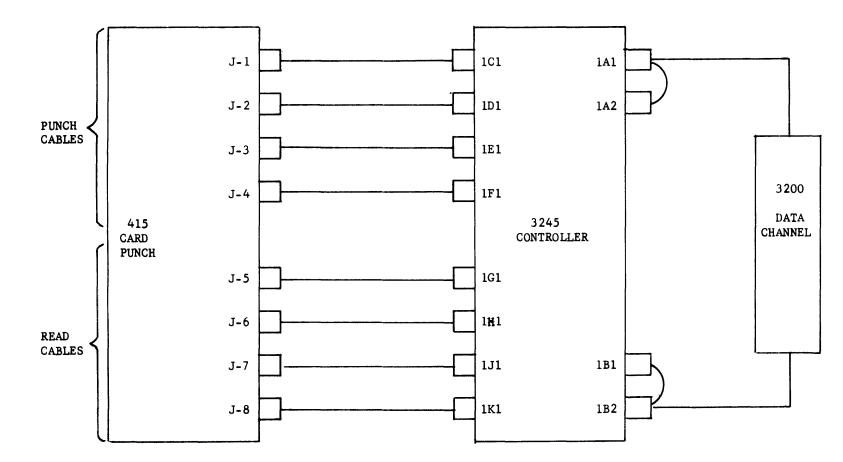

| Cable Identification     | 34 |

| Study Questions          | 36 |

APPENDIX A. STUDY QUESTION ANSWERS

CHAPTER I

STANDARD DATA CARDS

### CHAPTER I

# STANDARD DATA CARDS

#### INTRODUCTION

The use of punch cards for storing data or information goes back to the early 19th century. In New England a form of the punched card was used in the textile industry to control the weaving looms to weave different patterns in the material from cotton and wool fibers. Later in the 19th century men of advance education began experimenting with forms of mechanical machines that could add and subtract numbers, but the rate of entering data into the machines was very slow until Hollerith devised a coding system. This Hollerith system allowed data to be punched on cards to provide a higher entry rate of information into these types of machines. The data card as we know today was standardized by IBM, since they were essentially the first company to enter the computer field.

The standard data card is used in computer systems as a means of inputting data for programs or storing information outputted by the computer after the computations are completed. The computer interprets the information as a logical one or zero and processes it accordingly.

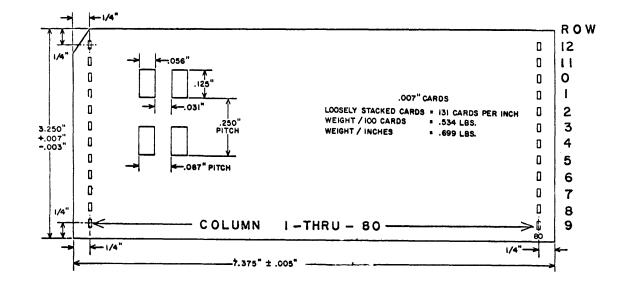

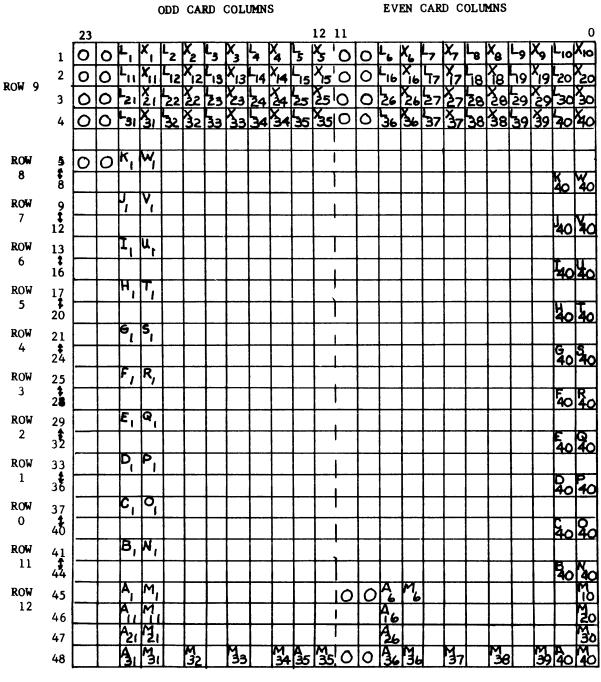

The standard data card is 7.3 inches in length and 3.25 inches in width and contains 80 columns of information. Each column contains 12 bits of information with one or more columns making up a computer word. As the card is fed through the card reader, each column of data is tranferred to the computer. The computer will use the information as the computer program directs.

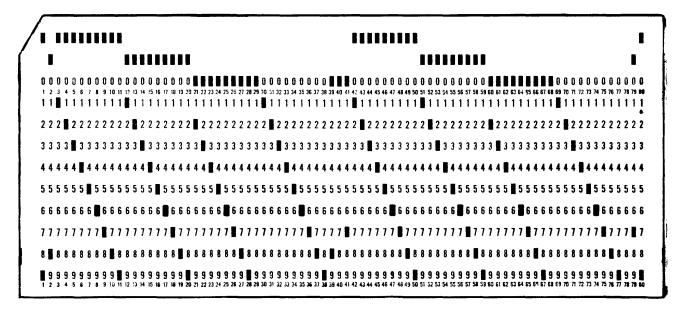

Data stored on the card is indicated by the presence or absence of punched holes in each column on the card. The holes punched in each column can be in the format of several coding systems such as Hollerith, Binary, and Binary Coded Decimal. These coding systems allow a variety of data to be used in computer systems for varied applications.

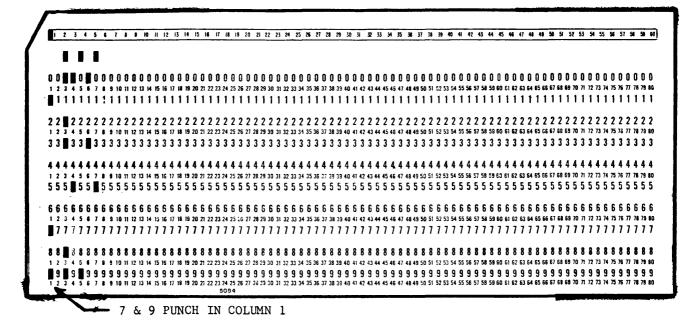

The Binary coding system can represent numbers (based on the powers of 2) in numerical applications or it can represent the contents of a card memory "dumped" on punched cards. Cards using the binary format will contain a 12 bit word in each column on the card and each card will be identified by a 7 and 9 punch in column 1.

The Hollerith system is considered to be the standard coding system for the computer industry. The Hollerith coding system has a wide application, since it represents alphanumeric characters and punctuation marks. Cards using the Hollerith format will contain a 12-bit word (representing a character) in each column on the card and each card will be identified by not having a "7 and 9" punch in column 1. It should be pointed out that Control Data computer systems have logic components wired to recognize the identification codes used in column 1 of each card and will process it accordingly. Binary data will be transferred directly to the computer. Hollerith data must first be converted to another coding format called Binary Coded Decimal before it can be transferred to the computer.

The Binary Coded Decimal (BCD) system was devised by IBM to replace the Hollerith system for use of data transfer on higher speed computer systems. The BCD system is equivalent to the Hollerith system except it uses a 6 bit word per character instead of a 12 bit word and it has no identification code in Column 1. Cards using the BCD format are used with a computer instruction called "Negate Translation" to transfer the data directly to the computer.

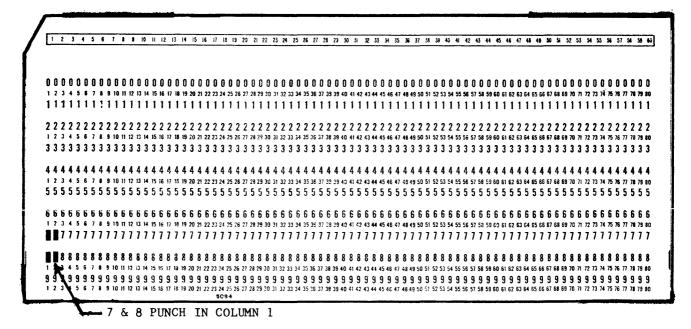

Regardless of the type of coding system used data cards are grouped together to make a program deck. Each card is considered to be a record of information. Records of information are combined to make a file of information, called the program deck, which can be divided in control cards, data cards, and an End of File card. The control cards contain the computer instructions which will be used to execute the program. The data cards contain the information to be processed. The End of File card, identified by a 7 and 8 punch in column 1, indicates the last card of the program deck is present and can be used to transfer program control elsewhere in memory.

Standard data cards have a limited, usable life, but this can be extended by proper care of the cards when not being used. Cards are normally stored at room temperature in a humidity range of 35% - 65%. Excessive temperature or humidity changes should be avoided, since it can cause the cards to warp or increase in size. These changes can also cause incorrect feeding of cards through card readers or punches.

Data cards provide an inexpensive means of storing information for computer programs, allow easy revision of programs when being updated or debugged, and can be used repeatedly to input information into the computer.

#### PUNCHED CARDS

### HANDLING

Punched cards may be adversely affected by extreme climate changes or by careless handling. However a few precautions in storage and handling will assure that the cards always give top performance.

#### ENVIRONMENT

Relative humidity affects the size and weight of punched cards. As humidity rises the card stock absorbs moisture and tends to expand, causing warpage if cards are not tightly clamped in their containers. As humidity falls the card stock loses moisture and shrinks, causing card buckling. The recommended relative humidity in the equipment and storage areas should be stable and within the range of 35% - 65%. The lower humidity is preferred. When the relative humidity is under 35% or over 65% for a long time, permanent warp may develop.

Temperature changes also affect punched cards. When cards are moved from a cold area to a warm area, moisture condenses on them and temporary warping occurs.

CORRECTING WARP DUE TO HUMIDITY

Cards warped by exposure to abrupt changes in humidity usually regain their shape when they achieve equilibrium with the room humidity. If 30% relative humidity differential exists between storage room and machine room, the acclimatization period should be two to three weeks. If the differential is 20%, the period is from 1 to  $1\frac{1}{2}$  weeks. A differential of 10% or less normally does not require a waiting period. If storage facilities are available in the machine room, it is good practice to process all incoming cards for a week.

## HANDLING

Keep cards in their original containers until they are used. When the quantity of card permits, stack the boxes so that the cards lie flat. Pressure block cards in partially filled boxes and do not stack these boxes. Also pressure block cards when they are in a card tray.

If the cards appear curved, carefully flex them back and forth a few times. Prior to feeding cards into the 405 align them with a joggle plate. If static electricity makes joggle plate alignment difficult, fan the cards after each card pass. Newly punched cards or cards that have been stored for a long time (1 year or more) should be thoroughly fanned before feeding. CORRECTING WARP DUE TO INPROPER HANDLING OR STORAGE

Warping caused by stacking half-filled boxes of cards, by storing cards under very humid conditions, etc., is more serious than that due to changes in climate. Such warping is recognizable by the uneven nature of the card warp.

If the warp is not severe or of long duration, it may be corrected by storing the cards under pressure at a constant humidity. The relative humidity in the area should be from 35% - 65%.

Card dust should be removed from newly punched cards by fanning the deck before reading.

#### EXPLANATION OF HOLLERITH AND BCD FORMATS

#### HOLLERITH

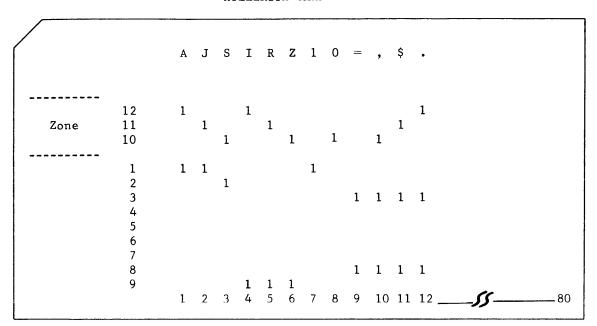

The Hollerith System is a numeric code by which data can be stored on a punched card. There are 12 Rows on a punch card. Rows 1 to 9 are called the numeric portion of the card and are used in an incrementing manner. Rows 12, 11, and 0 are called the zone portion of the card. Identical punches in rows 1 to 9 can have the meaning changed by selecting a different zone.

Alpha characters can be represented by utilizing different combinations of zones and numerics as can special characters such as the comma, slash, cent, etc.

Alpha characters A to I are represented by selecting Row 12 and incrementing Rows 1-9. Example: A = Rows 12 and 1 punched B = Rows 12 and 2 punched Etc. to I = Rows 12 and 9 punched Alpha characters J to R are represented by selecting Row 11 and incrementing Rows 1-9. Example: J - Rows 11 and 1 punched K = Rows 11 and 2 punched Etc. to R = Rows 11 and 9 punched Alpha characters S to Z are represented by selecting Row 0 and incrementing Rows 2-9. Example: S = Rows 0 and 2 punched T = Rows 0 and 3 punched Etc. to Z = Rows 0 and 9 punched Numerals are represented by punching Rows 0 to 9 without using a zone. Example: 0 = Row 0 punched 1 = Row 1 punched Etc. to 9 = Row 9 punched

Except for the slash (/) which is represented by a Row 0 and 1 punch, the rest of the special characters are represented by a combination of one zone and two numeric punches.

#### EXTERNAL BCD

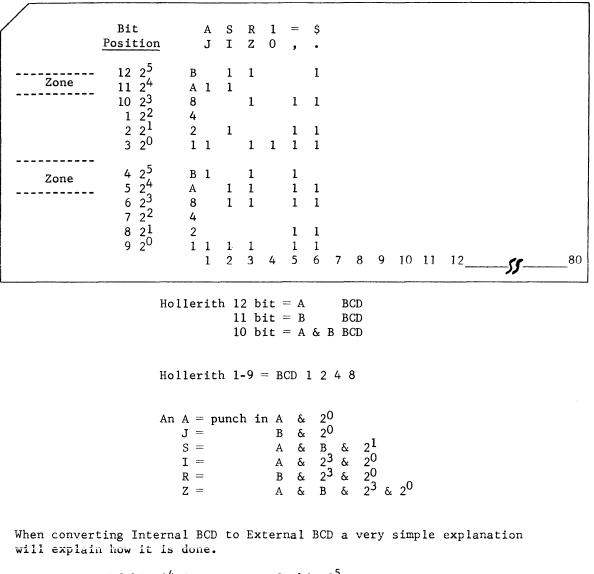

Since the Hollerith System is only compatible with punched card equipment, it must be converted to a code which will be compatible with other input/ output equipment as well as computers. This code is called BCD (Binary-Coded Decimal) and is in a 6-bit format with bit position "0" the least significant and bit position "B" the most significant. Following is the format for a BCD word:

## B A 8 4 2 1

The "1" is bit position "0", the "2" is bit position "1", etc. on through the "B" being bit position "5". Bits 0 to 3 are assigned binary values of  $2^0$  at bit position "0",  $2^1$  at bit position "1",  $2^2$  at bit position "2" and  $2^3$  at bit position "3". Bit position "4" is labeled "A" and bit position "5" is labeled "B". Bit positions 0 to 3 represent the numeric portion of the punched card and bit positions "A" and "B" represent the zone portion of the card.

A punch in zone 12 of the card will be represented by "1" bits in both the A and B positions of the BCD word. A punch in zone 11 of the card will be represented by a "1" bit only in

the "B" position of the BCD word. A punch in zone 0 of the card will be represented by a "1" bit only in the "A" position of the BCD word.

Numerals do not have bits in the zones. A value of one has a "1" bit in position "0" of the BCD word. Two = position "1", three = positions 0 and 1, four = position 2, five = positions 0 and 2, six = positions 1 and 2, seven = positions 0, 1, and 2, eight = position 3, and nine = positions 0 and 3.

Example: <u>B A 8 4 2 1</u> 0 0 0 0 0 0 1 = 1 0 0 0 0 1 0 = 2 0 0 0 0 1 1 = 3 0 0 0 1 0 0 = 4Etc. to 0 0 1 0 0 1 = 9

Alpha characters A to I, which are zone 12 characters, will have "1" bits present in the B and A positions of the BCD word and will increment bit positions 0 to 3.

Example: <u>B A 8 4 2 1</u> 1 1 0 0 0 1 = A = 12,1 punch = 618 1 1 0 0 1 0 = B = 12,2 punch = 628 Etc. to 1 1 1 0 0 1 = I = 12,9 punch = 718

Alpha characters J to R, which are zone 11 characters, will have "1" bits present in the B position of the BCD word and will increment bit positions 0 to 3.

Example: B A 8 4 2 1

$1 \ 0 \ 0 \ 0 \ 1 = J = 11,1 \ punch = 41_8$ 1 0 0 0 1 0 = K = 11,2 punch = 42\_8 Etc. to 1 0 1 0 0 1 = R - 11,9 punch = 51\_8

Alpha characters S to Z, which are zone O characters, will have "1" bits present in the A position of the BCD word and will increment bit positions O to 3.

Example: <u>B A 8 4 2 1</u> 0 1 0 0 1 0 = S = 0,2 punch = 22<sub>8</sub> 0 1 0 0 1 1 = T = 0,3 punch = 23<sub>8</sub> Etc. to 0 1 1 0 0 1 = Z = 0,9 punch = 31<sub>8</sub>

INTERNAL BCD

Analyzing the above BCD codes the following is found to be true:

- 1. Numerals are represented by a straight Decimal to Binary conversion

- 2. Letters A through I are equivalent to 618 to 718

3. Letters J through R are equivalent to  $41_8$  to  $51_8$

4. Letters S through Z are equivalent to 228 to 318

These alpha codes make sorting operations difficult within computer systems. For this reason, another coding system, called Internal BCD, was developed and is used by some computer systems including Control Data.

The character codes were re-arranged so the numerical progression would coincide with the alpha character progression. J through R codes remained unchanged while the other two groups were reversed. The numeric value for A through I, then, went below 41 to 51 and the numeric value for S through Z went above 41 to 51. It was found that this reversal could be accomplished by complementing the upper most bit (bit 5) of groups A to I and S to Z. However, this complement must not affect the 41 to 51 codes. Upon close examination of the codes, it was found that bit position 4 is only present (a "1") in groups A to I and S to Z. From this resulted the rule for converting from Internal BCD to External BCD or vice-versa:

"When bit 4 is a "1" complement bit 5; when bit 4 is a "0" leave bit 5 alone".

Thus, the resultant Internal BCD Codes are:

1. A to I = 21 to 31 2. J to R = 41 to 51

3. S to Z = 62 to 71

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CHARACTER | HOLLERITH<br>CODE | EXTERNAL<br>CODE | INTERNAL<br>CODE | CHARACTER | HOLLERITH<br>CODE | EXTERNAL<br>CODE | INTERNAL<br>CODE |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------|------------------|------------------|-----------|-------------------|------------------|------------------|

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                   |                  |                  |           |                   |                  |                  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0         | Ο                 | 12               | 00               | -         | 11                | 40               | 40               |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                   |                  |                  | L J       | 1                 |                  |                  |

| 3       3       03       03       L       11,3       43       43         4       4       04       04       M       11,4       44       44         5       5       05       05       N       11,5       45       45         6       6       06       06       0       11,6       46       46         7       7       07       07       P       11,7       47       47         8       8       10       10       Q       11,8       50       50         9       9       11       11       R       11,9       51       51         =       8,3       13       13       %       11,3,8       53       53         4       8,4       14       14       \$       \$       11,3,8       53       53         \$       8,6       16       16       1       11,5,8       55       55         \$       0,1       21       61       +       12,1       61       21         \$       0,2       22       62       A       12,1       61       21         \$       0,2       2 |           |                   |                  |                  |           |                   |                  |                  |

| 440404M11,44444550505N11,54545660606011,64646770707P11,747881010Q11,85050991111R11,95151=8,313137%11,05252 $\neq$ 8,41414\$11,4,85454 $\uparrow$ 8,61616111,5,85555 $f$ 8,71717 $\bullet$ 11,6,85656blankunpunched2060>11,7,85757/0,32363B12,26222U0,42464C12,36323V0,52565D12,46424W0,62666E12,56525X0,72767F12,66626Y0,83070G12,76727Z0,93171H12,8703010,2,83272I12,97131,0,3,83374.12,3,87333 $\bullet$ 0,6,83676 $\geq$ <td< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                   |                  |                  |           |                   |                  |                  |

| 5       5       05       05       N       11,5       45       45         6       6       06       06       0       11,6       46       46         7       7       07       07       P       11,7       47       47         8       8       10       10       Q       11,8       50       50         9       9       11       11       R       11,9       51       51         =       8,3       13       13       %       11,3,8       53       53 $\neq$ 8,4       14       14       \$       \$       11,5,8       55       55 $f$ 8,6       16       16 $f$ 11,5,8       55       55 $f$ 8,7       17       17 $f$ 11,6,8       56       56         blank       unpunched       20       60       >       11,7,8       57       57 $f$ 0,1       21       61       +       12       60       20         S       0,2       22       62       A       12,1       61       21         T                                                                        |           |                   |                  |                  |           |                   |                  |                  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                   |                  |                  |           |                   |                  | 45               |

| 77070707P11,74747881010Q11,85050991111R11,95151=8,31313 $\chi$ 11,05252\$\nothermole\$8,61616\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6         | 6                 |                  |                  | 1         |                   | 46               | 46               |

| 8       8       10       10       Q       11,8       50       50         9       9       11       11       R       11,9       51       51 $\neq$ 8,3       13       13       13       %       11,0       52       52 $\neq$ 8,4       14       14       14       5       11,3,8       53       53 $\neq$ 8,6       16       16 $\star$ 11,4,8       54       54 $t$ 8,6       16       16 $\star$ 11,4,8       54       54         blank       unpunched       20       60       >       11,7,8       55       55 $t$ 0,1       21       61       +       12       60       20 $f$ 0,1       21       61       +       12       60       20 $f$ 0,3       23       63       B       12,2       62       22 $f$ 0,6       26       66       E       12,3       63       23 $f$ 0,5       25       65       D       12,4       64       24       <                                                                                                              |           |                   |                  |                  |           |                   | 47               | 47               |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                   |                  |                  | Q         | 1                 | 50               | 50               |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                   | 11               |                  |           | 11,9              | 51               | 51               |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | 8.3               | 13               | 13               | %         |                   | 52               | 52               |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>≠</b>  |                   |                  |                  | \$        |                   | 53               | 53               |

| $\overline{T}$ 8,61616111,5,85555 $I$ 8,71717171711,6,85656 $J$ 0,12161+126020S0,22262A12,16121T0,32363B12,26222U0,42464C12,36323U0,42464C12,36323V0,52565D12,46424W0,62666E12,56525X0,72767F12,66626Y0,83070G12,76727Z0,93171H12,87030J0,2,83272I12,97131,0,3,83373<12,3,87333 $\leftarrow$ 0,5,83575)12,4,87434 $=$ 0,6,83676 $\geq$ 12,5,87535                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <         |                   |                  |                  | *         |                   | 54               | 54               |

| $ \begin{bmatrix} 8,7 & 17 & 17 & 17 & 11,6,8 & 56 & 56 \\ 11,7,8 & 57 & 57 & 57 & 57 & 57 & 57 & 57 & 5$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1         |                   | 16               | 16               | 1         |                   | 55               |                  |

| $/$ $0,1$ $21$ $61$ $+$ $12$ $60$ $20$ S $0,2$ $22$ $62$ A $12,1$ $61$ $21$ T $0,3$ $23$ $63$ B $12,2$ $62$ $22$ U $0,4$ $24$ $64$ C $12,3$ $63$ $23$ V $0,5$ $25$ $65$ D $12,4$ $64$ $24$ W $0,6$ $26$ $66$ E $12,5$ $65$ $25$ X $0,7$ $27$ $67$ F $12,6$ $66$ $26$ Y $0,8$ $30$ $70$ G $12,7$ $67$ $27$ Z $0,9$ $31$ $71$ H $12,8$ $70$ $30$ J $0,2,8$ $32$ $72$ I $12,9$ $71$ $31$ , $0,3,8$ $33$ $73$ $<$ $12,0$ $72$ $32$ ( $0,4,8$ $34$ $74$ . $12,3,8$ $73$ $33$ $=$ $0,6,8$ $36$ $76$ $\geq$ $12,5,8$ $75$ $35$                                                                                                                                                                                                                                                                                                                                                                                                                                       | l r       |                   | 17               |                  |           | 11,6,8            |                  |                  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | blank     | unpunched         | 20               | 60               | >         |                   |                  |                  |

| T $0,3$ $23$ $63$ B $12,2$ $62$ $22$ U $0,4$ $24$ $64$ C $12,3$ $63$ $23$ V $0,5$ $25$ $65$ D $12,4$ $64$ $24$ W $0,6$ $26$ $66$ E $12,5$ $65$ $25$ X $0,7$ $27$ $67$ F $12,6$ $66$ $26$ Y $0,8$ $30$ $70$ G $12,7$ $67$ $27$ Z $0,9$ $31$ $71$ H $12,8$ $70$ $30$ J $0,2,8$ $32$ $72$ I $12,9$ $71$ $31$ , $0,3,8$ $33$ $73$ $<$ $12,0$ $72$ $32$ ( $0,4,8$ $34$ $74$ . $12,3,8$ $73$ $33$ $ 0,5,8$ $35$ $75$ . $12,4,8$ $74$ $34$ $=$ $0,6,8$ $36$ $76$ $\geq$ $12,5,8$ $75$ $35$                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           | 0,1               |                  |                  | +         | t                 | ,                |                  |

| U $0,4$ $24$ $64$ C $12,3$ $63$ $23$ V $0,5$ $25$ $65$ D $12,4$ $64$ $24$ W $0,6$ $26$ $66$ E $12,5$ $65$ $25$ X $0,7$ $27$ $67$ F $12,6$ $66$ $26$ Y $0,8$ $30$ $70$ G $12,7$ $67$ $27$ Z $0,9$ $31$ $71$ H $12,8$ $70$ $30$ J $0,2,8$ $32$ $72$ I $12,9$ $71$ $31$ , $0,3,8$ $33$ $73$ $<$ $12,0$ $72$ $32$ ( $0,4,8$ $34$ $74$ . $12,3,8$ $73$ $33$ $\rightarrow$ $0,5,8$ $35$ $75$ $12,4,8$ $74$ $34$ $=$ $0,6,8$ $36$ $76$ $\geq$ $12,5,8$ $75$ $35$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | S         | 0,2               |                  |                  | A         |                   |                  |                  |

| V $0,5$ $25$ $65$ D $12,4$ $64$ $24$ W $0,6$ $26$ $666$ E $12,5$ $65$ $25$ X $0,7$ $27$ $67$ F $12,6$ $666$ $26$ Y $0,8$ $30$ $70$ G $12,7$ $67$ $27$ Z $0,9$ $31$ $71$ H $12,8$ $70$ $30$ J $0,2,8$ $32$ $72$ I $12,9$ $71$ $31$ , $0,3,8$ $33$ $73$ $<$ $12,0$ $72$ $32$ ( $0,4,8$ $34$ $74$ . $12,3,8$ $73$ $33$ $ 0,5,8$ $35$ $75$ ) $12,4,8$ $74$ $34$ $=$ $0,6,8$ $36$ $76$ $\geq$ $12,5,8$ $75$ $35$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Т         | 0,3               | 23               | 63               | В         | 12,2              |                  |                  |

| W $0,6$ $26$ $66$ E $12,5$ $65$ $25$ X $0,7$ $27$ $67$ F $12,6$ $66$ $26$ Y $0,8$ $30$ $70$ G $12,7$ $67$ $27$ Z $0,9$ $31$ $71$ H $12,8$ $70$ $30$ J $0,2,8$ $32$ $72$ I $12,9$ $71$ $31$ , $0,3,8$ $33$ $73$ $<$ $12,0$ $72$ $32$ ( $0,4,8$ $34$ $74$ . $12,3,8$ $73$ $33$ $ 0,5,8$ $35$ $75$ ) $12,4,8$ $74$ $34$ $=$ $0,6,8$ $36$ $76$ $\geq$ $12,5,8$ $75$ $35$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | U         | 0,4               | 24               |                  | С         |                   |                  |                  |

| X0,72767F12,66626Y0,83070G12,76727Z0,93171H12,87030I0,2,83272I12,97131,0,3,83373 $\boldsymbol{<}$ 12,07232(0,4,83474.12,3,87333 $\boldsymbol{-}$ 0,5,83575)12,4,87434=0,6,83676 $\boldsymbol{\geq}$ 12,5,87535                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | v         | 0,5               | 25               |                  |           |                   |                  |                  |

| Y $0,8$ $30$ $70$ G $12,7$ $67$ $27$ Z $0,9$ $31$ $71$ H $12,8$ $70$ $30$ J $0,2,8$ $32$ $72$ I $12,9$ $71$ $31$ , $0,3,8$ $33$ $73$ $<$ $12,0$ $72$ $32$ ( $0,4,8$ $34$ $74$ . $12,3,8$ $73$ $33$ $ 0,5,8$ $35$ $75$ ) $12,4,8$ $74$ $34$ $=$ $0,6,8$ $36$ $76$ $\geq$ $12,5,8$ $75$ $35$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | W         | 0,6               |                  |                  |           |                   |                  |                  |

| Z $0,9$ $31$ $71$ H $12,8$ $70$ $30$ J $0,2,8$ $32$ $72$ I $12,9$ $71$ $31$ , $0,3,8$ $33$ $73$ $<$ $12,0$ $72$ $32$ ( $0,4,8$ $34$ $74$ . $12,3,8$ $73$ $33$ $\leftarrow$ $0,5,8$ $35$ $75$ ) $12,4,8$ $74$ $34$ $=$ $0,6,8$ $36$ $76$ $\geq$ $12,5,8$ $75$ $35$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Х         | 0,7               | 27               | 67               |           |                   |                  |                  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Y         | 0,8               | 30               | 70               |           |                   | [                |                  |

| , $0,3,8$ $33$ $73$ $12,0$ $72$ $32$ ( $0,4,8$ $34$ $74$ . $12,3,8$ $73$ $33$ $\rightarrow$ $0,5,8$ $35$ $75$ ) $12,4,8$ $74$ $34$ $=$ $0,6,8$ $36$ $76$ $\geq$ $12,5,8$ $75$ $35$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Z         | 0,9               |                  |                  |           | 12,8              |                  |                  |

| , $0,3,8$ $33$ $73$ $12,0$ $72$ $32$ ( $0,4,8$ $34$ $74$ . $12,3,8$ $73$ $33$ $\rightarrow$ $0,5,8$ $35$ $75$ ) $12,4,8$ $74$ $34$ $=$ $0,6,8$ $36$ $76$ $\geq$ $12,5,8$ $75$ $35$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ] ]       | 0,2,8             |                  |                  |           |                   |                  |                  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | 0,3,8             |                  |                  | <         |                   |                  |                  |

| $=$ 0,6,8 36 76 $\geq$ 12,5,8 75 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |                   |                  |                  | •         |                   |                  |                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -•        | 0,5,8             |                  |                  |           |                   |                  |                  |

| $\sim$ 0.7.8 37 77 $\sim$ 12.6.8 76 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | =         | 0,6,8             |                  |                  | ≥         |                   |                  |                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ~         | 0,7,8             | 37               | 77               | ?         | 12,6,8            |                  |                  |

| : illegal 00 12 ; 12,7,8 77 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | :         | <b>i</b> llegal   | 00               | 12               | ;         | 12,7,8            | 77               | 37               |

## HOLLERITH TO BCD CONVERSION ON PUNCHED CARDS

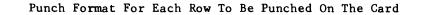

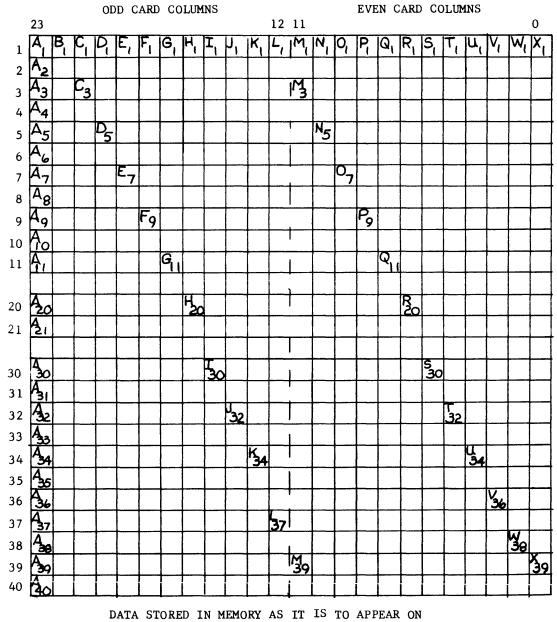

Hollerith codes are made from a combination of "1"s and "0"s in one column on a card (12 bits). BCD codes consist of 6 bits allowing two codes to be put into each column. On the following pages are three cards; a Hollerith, card, an External BCD card and an Internal BCD card.

| In <b>a col</b> umn <b>a</b> hole | 12 signifies characters A-Í            |

|-----------------------------------|----------------------------------------|

| punched in row                    | <pre>11 signifies characters J-R</pre> |

|                                   | 10 signifies characters S-Z            |

| An A | = | punch | in | 12 | and | а | punch | in | 1 |  |

|------|---|-------|----|----|-----|---|-------|----|---|--|

| J    | = |       |    | 11 |     |   |       |    | 1 |  |

| S    | = |       |    | 10 |     |   |       |    | 2 |  |

| I    | = |       |    | 12 |     |   |       |    | 9 |  |

| R    |   |       |    | 11 |     |   |       |    | 9 |  |

| Z    | = |       |    | 10 |     |   |       |    | 9 |  |

|      |   |       |    |    |     |   |       |    |   |  |

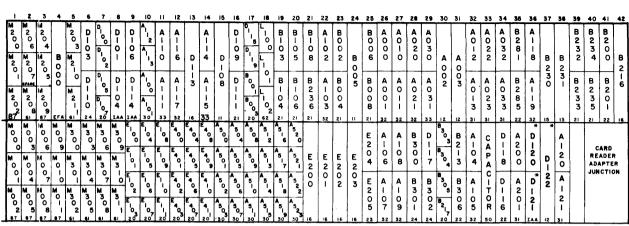

HOLLERITH CARD

|      |                                                                                                                     | Bit<br>Position                                                                         |                     | A<br>J         | S<br>I      | R<br>Z      | 1<br>0                | =                               | \$                               | Upper 6 Bits<br>Lower 6 Bits |

|------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------|----------------|-------------|-------------|-----------------------|---------------------------------|----------------------------------|------------------------------|

|      | Zone                                                                                                                | - 12 2 <sup>5</sup><br>11 2 <sup>4</sup>                                                | <b>В</b><br>А       | 1<br>1         | 1           | 1           |                       |                                 | 1                                |                              |

|      |                                                                                                                     | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                   | 4<br>2              |                | 1           |             | 1                     | 1                               | 1                                |                              |

|      | Zone                                                                                                                | 4 2 <sup>5</sup><br>_ 5 2 <sup>4</sup>                                                  | B<br>A              | 1              |             | 1           |                       | 1                               | 1<br>1                           |                              |

| Repr | Binary<br>esentation                                                                                                | $ \left\{\begin{array}{c} 6 & 2^3 \\ 7 & 2^2 \\ 8 & 2^1 \\ 9 & 2^0 \end{array}\right. $ | 8<br>4<br>2<br>1    | 1<br>1         | 1<br>1<br>2 | 1<br>1<br>3 |                       | 1                               | 1<br>1<br>1<br>6                 |                              |

| L    | Hollerith 12 bit = A & B BCD<br>Hollerith 11 bit = B BCD<br>Hollerith 10 bit = A BCD<br>Hollerith 1-9 = BCD 1 2 4 8 |                                                                                         |                     |                |             |             |                       |                                 |                                  |                              |

|      |                                                                                                                     |                                                                                         | n A =<br>J =<br>S = | = pu<br>=<br>= | nch         |             | A<br>B<br>A<br>A<br>B | & E<br>& 2<br>& "<br>& E<br>& 2 | 3 &<br>0<br>121   <br>3 &<br>3 & | 2 <sup>0</sup>               |

EXTERNAL BCD CARD

INTERNAL BCD CARD

If bit  $2^4$  is a one toggle bit  $2^5$ . If bit  $2^4$  is a zero leave bit  $2^5$  alone.

| <u>Int A</u>   | Ext A  | <u>Int M</u> | Ext M  |

|----------------|--------|--------------|--------|

| 21             | 61     | 44           | 44     |

| <b>0</b> 10001 | 110001 | 100100       | 100100 |

Standard thickness of a punched card is .007" ( $\pm .0004"$ ). The following card dimensions are specified at 50% relative humidity. The corner cut indicates the top of the card. It may be found at the column 1 or 80 corner.

Hollerith Card

BINARY CARD

END OF FILE CARD

### STUDY QUESTIONS

- 1. The best humidity range of data cards is?

- a. 35 65%

- b. 30 50%

- c. 20 30%

- d. 50%

- 2. If the differential of storage area and machine room humidity is 20% the maximum acclimatization of data cards should be:

- a. overnight

- b. 48 hours

- c. one and a half weeks

- d. no time

- 3. An oil stained paper card would probably:

- a. Present no problem on any machine

- b. Never read correctly

- c. Present extraneous data pick up on photo electric readers

- d. Would shrink the card size too much

- 4. To correct the curve due to warping found in stored cards what would be done before using them?

- a. Condition them for a longer period at machine humidity conditions

- b. Turn them over before placing them in the machine

- c. Fan them gently several times before placing them in the machine

- d. Flex them carefully back and forth a few times

- 5. Data cards stored in half-filled storage containers:

- a. Presents no problem no matter how they are handled

- b. Must be pressure blocked in partially filled containers and must not be stacked

- c. Present no problem provided they are used again within four to six weeks

- d. Present no problem if humidity is controlled at 20%

- 6. The space between column punched holes is:

- a. .125"

- b. .250"

- c. .056"

- d. .031"

- 7. The standard thickness of a paper punched card is:

- a. .009" (<u>+</u>.0004")

- b. .007" (<u>+</u>.0004")

- c. .0004" (±.007)

- d. .003" (no tolerance)

- 8. A loosely packed deck of cards measuring ten inches would have approximately how many cards in it?

- a. 1000 cards

- b. 131 cards

- c. 699 cards

- d. 1310 cards

9. The weight of the cards in the previous problem is approximately:

- a. 10.68 lbs.

- b. 1.068 lbs.

- c. 6.99 lbs.

- d. .699 lbs.

10. Data bits to be stored on standard 80 column cards are indicated by:

- a. Blank areas left in the row positions in each column on the card

- b. Holes punched in the row positions in each column on the card

- c. Data bits are not punched on 80 column cards

- d. Holes punched in between the row positions in each column on the card

- 11. Data bit positions in a word punched on the card are arranged:

- a. With 2<sup>o</sup>bit position in Row 12 through 2" bit position in Row 9 in Column Binary Word

- b. With 2" bit position in Column 1 through 2<sup>o</sup> bit position in column 12 in Row Binary Word

- c. With 2" bit position in Row 12 through 2<sup>°</sup> bit position in Row 9 in a Column Binary Word

- d. None of the above answers are correct

- 12. An End of File Card is identified by:

- a. A 7 and 9 punch in Column #1 of each card

- b. A 7, 8, and 9 punch in Column #1 of each card

- c. No 7 or 9 punch in Column #1 of each card

- d. A 7 and 8 punch in Column #1 of each card

- e. No identification is required for an End of File Card

13. Translate the following external BCD code statement

61 63-46-44-47-24-23-65-51 33 26-71-23-70-46-24-23 61 47-51-46-67-51-61-44 33 71-22 61 70-71-67-70 22-47-65-65-64 44-46-51-46-45

14. The first data card, in a program deck of cards punched in the Binary format, is the only card that is required to have an identification code.

a. True

b. False

CHAPTER II

405 CARD READER

#### CHAPTER II

### 405 CARD READER

#### INTRODUCTION

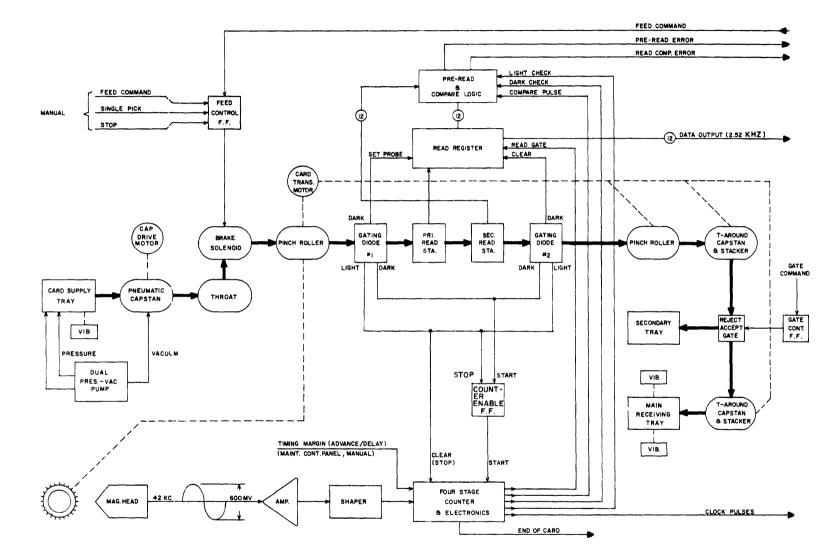

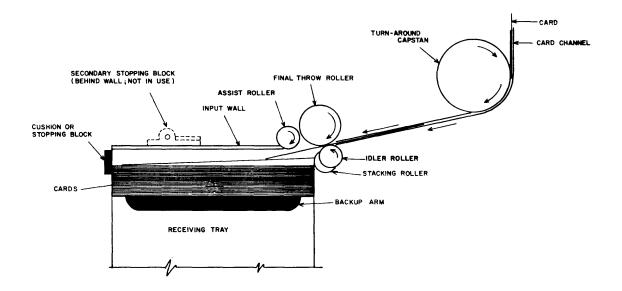

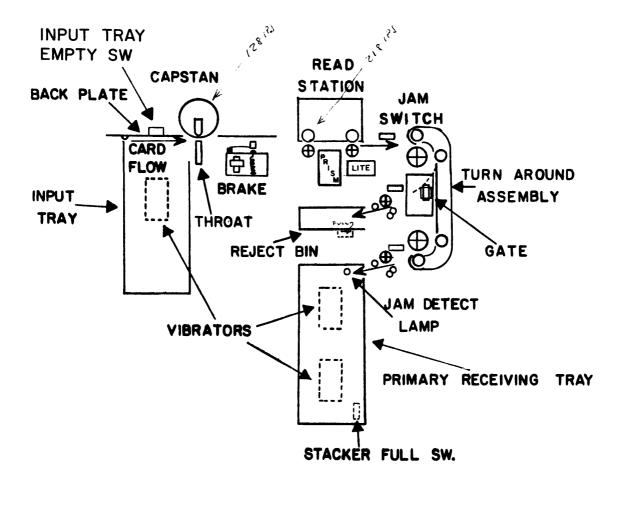

During a Read operation, cards are transported from the Input (supply) Tray past the dual read station to the main receiving tray. Each tray accommodates up to 4000 punched cards of either the 80 column or 51 column type.

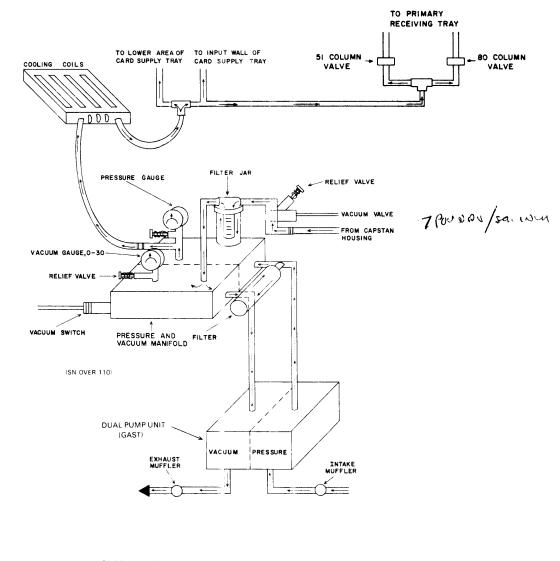

While the cards are being transported, both trays vibrate to overcome friction between cards and tray. The backup arm applies force to the end of the card supply and moves the stack toward the capstan. Air under pressure is injected at the lower left end of the input tray to provide positive separation between cards as they approach the capstan. Pressure is also provided at the left wall of the input tray to insure minimum friction drag on the card when being picked from the stack.

Punched cards are propelled from the supply tray past the read station to the receiving tray by a pneumatic capstan and a series of pinch rollers. The perforated capstan rotates continually. When vacuum is applied to the inner core of the capstan, a card is pulled against the capstan and moved through the card channel. Pinch rollers then move the card past the read station to the receiving tray.

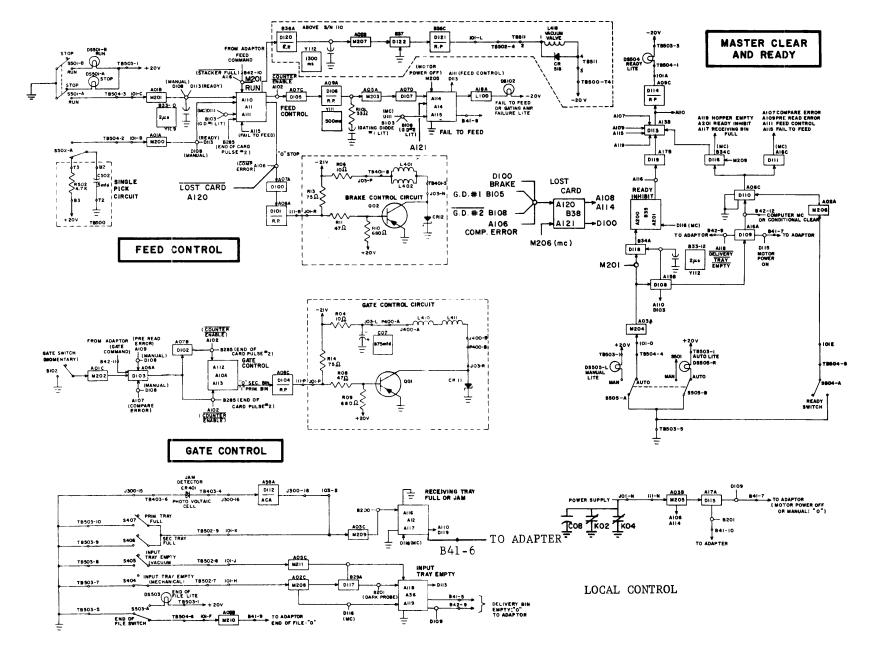

An electromechanical brake assembly serves as a gate in the card channel. If the card read operation has not been initiated, the braking force overcomes the pulling force being applied to the card at the capstan and the card remains stationary. Once released, either manually or via the control unit, the braking shoe is pulled back to permit the card to pass to the dual read station.

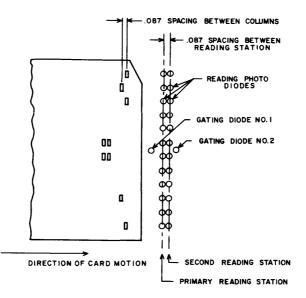

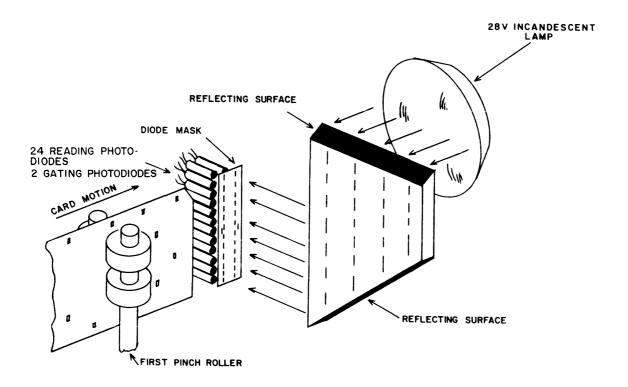

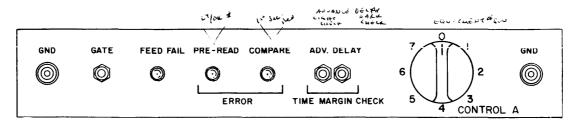

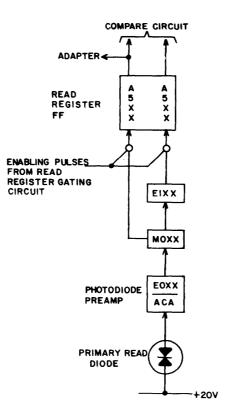

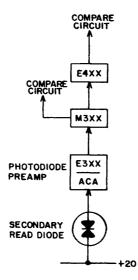

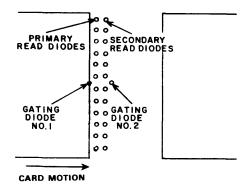

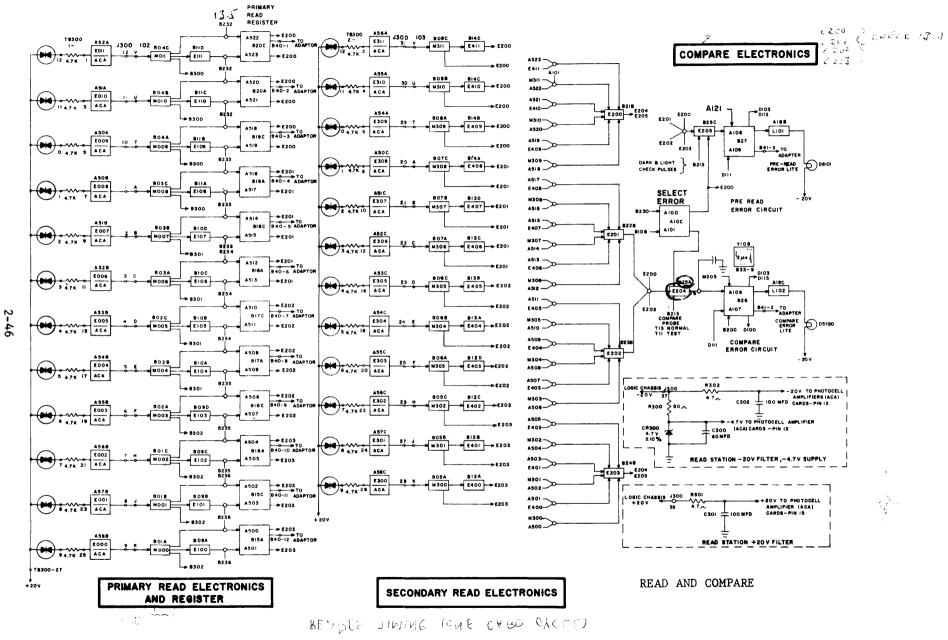

The Read Station consists of two vertical columns of twelve photodiodes each, which sense information holes in the punched cards. Holes punched in each card column are read in parallel mode. The same column is then read by the second row of photodiodes and the results of the two read operations are compared. If the two information groups do not compare, the card is routed to a small secondary bin, in the manual mode of operation. In the automatic mode a "not compare" sends a signal to the adapter for use in external programming.

If no error was detected, the card continues into the primary receiving tray. The original orientation and sequence of the deck is preserved except those cards sorted to the secondary bin.

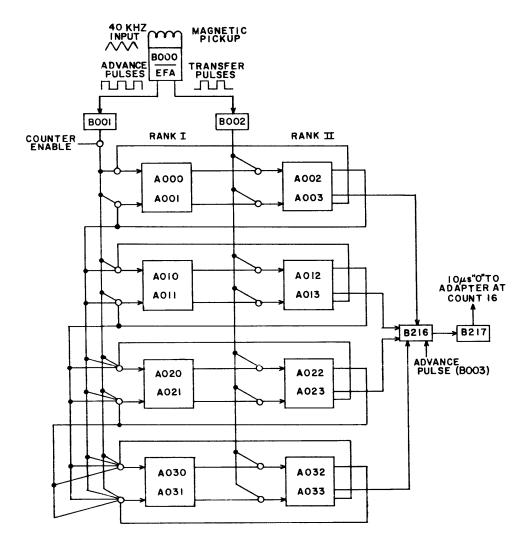

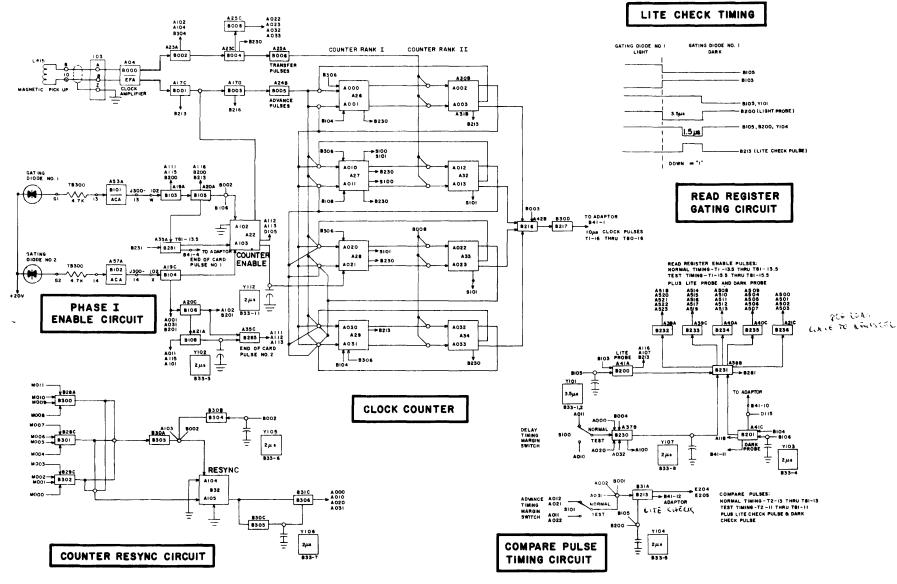

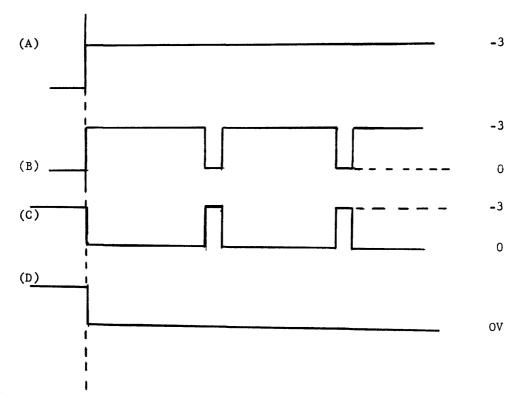

Information readout is executed by a clock pulse generated within the reader itself and occurs only when holes of the card column are centered on the read diodes. Clock pulses are resynchronized along the length of the card to compensate for poor card registration or card expansion due to temperature or humidity.

## DETAILED SPECIFICATIONS

| CARD<br>READ ING         | Method               | Two rows of 12 photodiodes read and check punched cards column by column                                                                                                                   |

|--------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | Dual Read<br>Station | One column (0.087 in.) separation between read stations                                                                                                                                    |

|                          | Preread<br>Checks    | Primary and secondary read station outputs<br>compared. Automatic card rejection if com-<br>parison error exists in off-line mode. When<br>on-line, the program controls rejection.        |

|                          | Rate                 | 120080 column cards read per minute<br>160051 column cards read per minute                                                                                                                 |

| CARD<br>FEEDING          | Input Tray           | 4000 card capacity<br>Vibrating tray and pneumatic card separation<br>for low friction card feeding                                                                                        |

|                          | Card Picking         | Asynchronous (i.e. no waiting period between card selections)                                                                                                                              |

|                          | Method               | Vacuum capstan applies $\frac{1}{2}$ pound pull between<br>horizontal rows of card punches. Card reaches<br>capstan velocity within 2 ms.                                                  |

|                          | Card Drive           | Pinch rollers at each side of read station<br>receive card from capstan and move card past<br>read station                                                                                 |

|                          | Card Speed           | At capstan 130 ips<br>At pinch rollers 218 ips<br>At read station 218 ips                                                                                                                  |

|                          | Card Channel         | Card input throat (0.0095 to 0.011 in.) permits<br>passage of only a single card. Beveled upper<br>and lower corners of card throat permit passage<br>of cards with frayed or bent corners |

|                          | Card Brake           | Solenoid controlled<br>Stop time 3 milliseconds maximum<br>Start time 14 milliseconds maximum                                                                                              |

| CARD<br>DELI <b>VERY</b> | Receiving<br>Trays   | Original card orientation maintained in<br>receiving trays<br>4000 card primary receiving tray<br>240 card secondary receiving tray<br>Vibrating trays for low friction card receiving     |

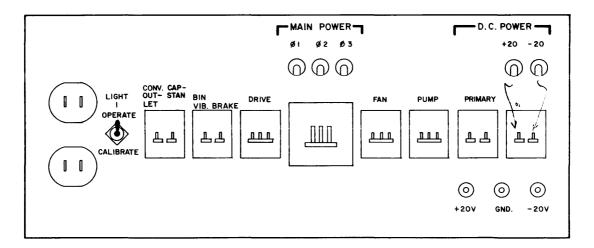

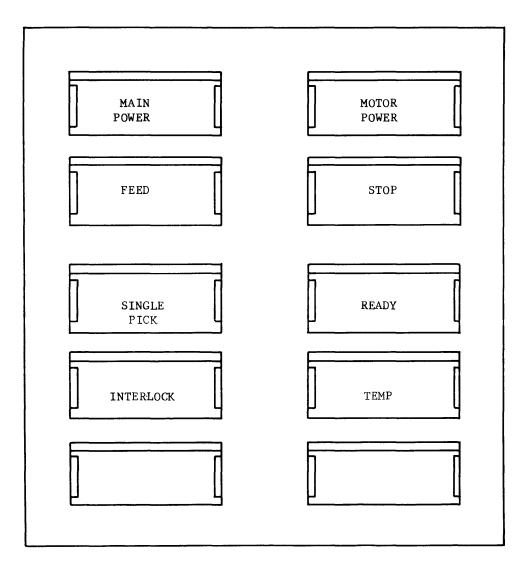

| FRONT<br>CONTROL<br>PANEL | Operator Controls<br>with Indicators | Main Power<br>Motor Power<br>Auto/Man<br>End of File                                                       | Ready<br>Single Pick<br>Run/Stop   |  |  |

|---------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|

| ELECTRICAL                | Power Source                         | 208V <sup>+</sup> 10%, 60 cycl<br>phase, 8 amps per p                                                      | cycle (Mod A)*, three<br>per phase |  |  |

|                           | Input/Output                         | All input and outpu<br>as represented by n<br>voltage levels. Si<br>presented and recei<br>B40 through B42 | gnal voltages are                  |  |  |

WEIGHT 1060 LBS.

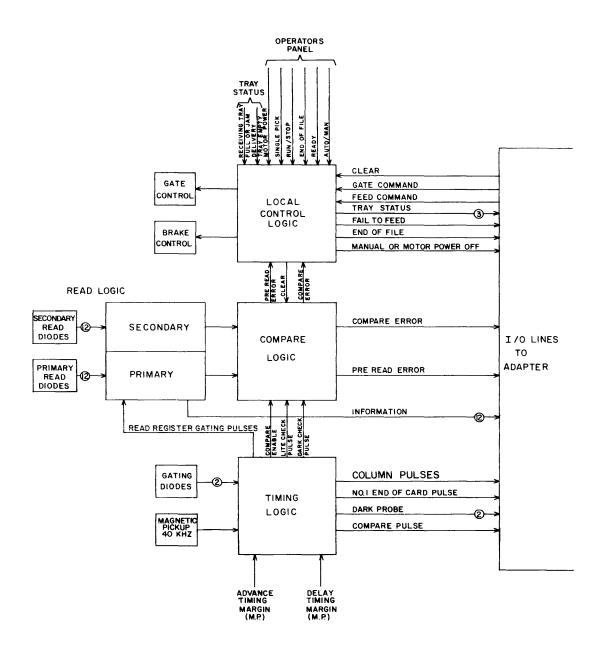

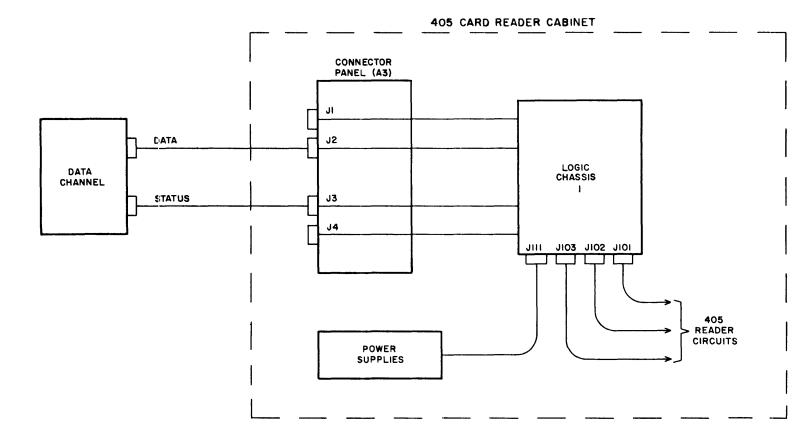

#### Block Diagram

For purposes of discussion, the 405 logic is divided into four general Control sections: read, timing, compare and local. The Block Diagram shows the relationship of these sections to the adapter (control unit).

## FUNCTIONAL DESCRIPTION

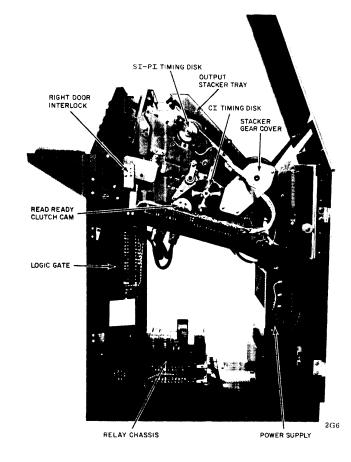

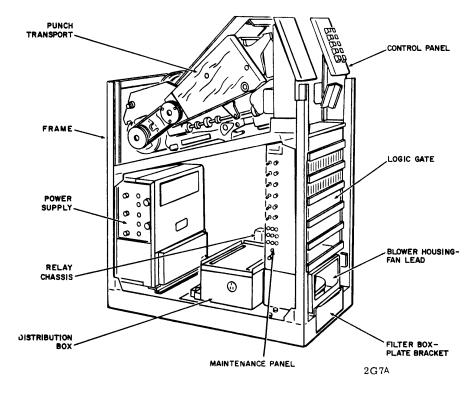

Functional sections of the 405 Card Reader may be divided into the following categories: The card transport mechanism, dual read station, pneumatic system and cabinet cooling system. This chapter discusses each equipment section in detail, explaining construction characteristics and their function in the overall equipment.

CARD TRANSPORT MECHANISM (Refer to system block diagram)

The basic card transport channel is formed by a cast aluminum structure which guides the card from the input throat assembly to one of two output positions. The pneumatic capstan, pinch rollers and assist rollers propel the card (edgewise) along its route in the transport channel.

Bold lines indicate the route of card travel and the various components that act upon the card during its travel. Solid lines indicate paths of information flow as well as the source and destination of control signals; dotted lines indicate areas of mechanical coupling.

Supply Tray and Receiving Tray -- The card supply tray and receiving tray are constructed in a similar manner. Each stainless steel tray is mounted on a base structure comprised of laminated birch wood, which forms a solid platform for the individual tray. The platform, in turn, is mounted on four shock absorbers. The steel trays are constructed such that they form two parallel halves. When the narrow half is removed, turned end-for-end and remounted, the raised metal strip forms a marginal guide for the type of punched card being used (80-column or 51-column). The broad half of each tray is fixed to the laminated platform.

A single electromagnetic vibrator unit is fixed to the bottom side of the supply tray. Because the receiving tray must stack as well as accommodate large numbers of cards, two vibrator units are employed in this assembly (the only significant difference between the two card trays). The vibrator receives pulsating current at the rate of 60 Hertz, causing vibrations to be induced into the card tray assembly. Hence, the vibrating action reduces friction forces between cards and the tray surface, requiring minimum mechanical force in feeding cards to the pneumatic capstan and in assembling cards in the receiving tray.

Each card tray contains a backup arm which supports the cards at the right end of the stack and travels over the entire length of the tray. This arm has a dual function; to hold the card stack in an upright position, and to apply a slight pressure to the entire stack as cards move across the tray. In the supply tray, the backup pressure is greatest when a large number of cards are being carried toward the capstan, and pressure decreases as the card supply is reduced. Pressure is applied to the backup arm by a coil spring element, which is contained within a circular housing and connected to the arm by a cable and pulley arrangement. When the last card has been pulled from the supply tray, the condition is sensed by a switch plunger which protrudes from the feed wall of the tray. As long as a single card is contained in the tray, the plunger is depressed. When removed, however, the switch plunger passes through a hole in the backup arm and a circuit is closed. The empty tray signal is transmitted to the computer (via adapter circuits) when the leading edge of the last card covers gating diode No. 2. A pneumatic switch is employed in detecting a supply tray empty condition. This switch is located in the pneumatic circuit which applies vacuum to the feed capstan. When the supply tray is empty, vacuum to the capstan drops from its normal level of 15 inches of mercury to one inch, and the switch is activated to produce the desired signal.

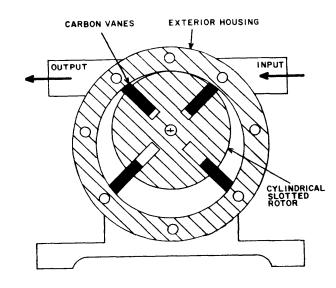

Pneumatic Capstan -- With vibration of the card supply deck and mechanical force being applied at the right end of the card stack, the cards move toward the capstan area. Air under pressure is injected at the bottom of the card stack, near the left end of the tray, insuring positive separation between cards. Distribution of air from below is via a series of 26 holes, arranged in two columns across the width of the card tray. Air is also injected from the forward, or left wall of the tray, in a direction perpendicular to the cards. This combination of air pressure tends to form a pneumatic cushion which "floats" the first card as it nears the capstan.

The capstan consists of a perforated drum which is driven continuously by a direct-coupled motor. A fixed graphite block is located inside the capstan drum, which extends over the entire length of the drum and contains a 3/8 inch cutout or opening at one side. This block is held to the inner surface of the rotating capstan by spring tension. Vacuum equal to 15 inches of mercury is applied to the graphite block element via flexible tubing. The circular capstan contains a total of 1080 holes of 1/16 inch diameter and are located such that vacuum is always applied to the solid portions of the card (areas between horizontal rows of punched holes).

When the first card moves into position, the capstan exerts a pulling force of approximately 1/2 pound on the forward end of the card, and the card reaches capstan velocity (130 inches per second) within 2 milliseconds. Picking action of the capstan is asynchronous; i.e., there is no "pick cycle" or waiting period between card selections. Rather, picking action is continuous as long as the brake unit permits the card to pass through the input throat. When initiating the card transport operation (first card of group), approximately 40 milliseconds are required between receipt of the pick card command and reading of the first card column. Following transport of the first card, this interval is reduced.

Card Input Throat -- The capstan forms one half of the throat; a fixed member forms the other half. The front edge of the throat contains a slight bevel which assists the card in being pulled into the narrow opening (0.0095 to 0.0115 inch). The thickness of a single card is approximately 0.007 inch, hence the throat permits the passage of only a single card at a time. The left wall of the supply tray, through which the slotted capstan protrudes, tends to peel the card from the capstan as the vacuum force pulls the card into the throat.

The throat gap extends over the entire 3 1/4-inch vertical dimension of the card. Upper and lower corners of the throat are beveled such that frayed or bent card corners cannot jam or hang up as they enter the narrow opening. Vacuum is applied to the capstan continuously; therefore, when one card passes through the throat, the next card is immediately pulled from the supply stack and advanced behind the previous card.

Brake Unit -- An electromagnetic card brake assembly is located just inside of the input throat and acts to control the passage of cards through the transport channel. The brake magnet contains a U-shaped core with coils mounted on each leg. A hinged armature is driven by a relatively heavy spring which provides the necessary card-braking force. Hence, when the magnet coils are de-energized, the braking shoe extends into the transport channel to prevent card movement. When the coils are energized, the brake shoe retracts to allow cards to pass through the machine. Since the card braking operation is not dependent upon current flow through the magnet coils, a card "jam" condition is avoided in the case of power failure.

The brake is approximately 1/4 inch wide, 2 3/4 inches long and fabricated from hard-coated aluminum. The shoe is fixed to a flat spring plate which, in turn, is mounted on the main transport casting.

Initially, when cards have been loaded in the supply tray and the capstan energized, the first card is picked, inserted into the throat, and has passed approximately one-third of its length into the throat when it strikes the brake shoe. The card remains in this position, the capstan slipping on the card, until the card transport operation is initiated. If braking force is applied while cards are being transported, the card motion is arrested by pinching action between the brake shoe and the transport channel wall. The brake shoe is grooved such that braking force applied to the moving card is always applied to the solid areas between card rows.