CONTROL DATA® STAR PERIPHERAL STATIONS

PAGING (DRUM) STATION

HIGH CAPACITY DISK STATION

SERVICE STATION

844 STORAGE STATION

MAGNETIC TAPE STATION

UNIT RECORD STATION

DISPLAY/EDIT STATION

STAR-1B SERVICE STATION

STAR-100 SERVICE STATION

STORAGE (MEDIA) STATION

STAR-100 MAINTENANCE CONTROL UNIT

STAR-65 MAINTENANCE CONTROL UNIT

# HARDWARE REFERENCE MANUAL

### NOTICE

ALL REFERENCES IN THIS MANUAL TO CAPABILITIES/PERFORMANCE OF THE STAR STATIONS AND ASSOCIATED PERIPHERAL DEVICES ARE NOMINAL VALUES AND MAY IN SOME CASES BE THE MAXIMUM CAPABILITIES OF THE DEVICES. THE ACTUAL CAPABILITIES ENCOUNTERED IN A SYSTEM ARE DEPENDENT ON THE PARTICULAR HARDWARE AND SOFTWARE CONFIGURATION USED.

|                | REVISION RECORD                                                                               |

|----------------|-----------------------------------------------------------------------------------------------|

| REVISION       | DESCRIPTION                                                                                   |

| 01             | Preliminary issue.                                                                            |

| (6-01-73)      |                                                                                               |

| 02             | Preliminary issue. Revised to incorporate technical review comments where available.          |

| (7-18-73)      |                                                                                               |

| 03             | Revised preliminary issue. Pages changed; v, 2-117, 2-119, 2-123, 2-136, 2-141, 2-144,        |

| (9-14-73)      | 2-148, 2-150, 2-154, 2-161, 2-168, 2-171, 2-176, 3-58 through 3-69, 3-71 through 3-74,        |

|                | 3-76 through 3-80, A-1, A-3, A-4, A-7, A-13, A-26, A-31, A-53 through A-59.                   |

|                | Pages added: iv, ix, xiv, 1-1 through 1-55, 3-64.1, 3-80.1 through 3-80.4, A-18.1 through     |

|                | A-18.6, C-1 through C-15.                                                                     |

| 04             | Revision packet issued. Pages changed: cover (note), iii, vi, ix, xii, xiii, xvi, 1-1 through |

| (10-26-73)     | 1-5, 1-7 through 1-11, 1-18, 1-20 through 1-23, 1-25, 1-28 through 1-37, 1-39 through 1-41    |

| -              | 1-45, 1-47, 1-48, 1-51 through 1-54, 2-11, 2-11.1, 2-13, 2-16 through 2-18, 2-23 through      |

|                | 2-25, 2-86, 2-117, 2-157, 3-10, 3-37, A-1 through A-59 (revised and renumbered), C-3, C-4     |

|                | C-6 through C-10, C-12 through C-15, Pages added: iv, xiii, xvi, 3-81 through 3-114,          |

|                | 4-1 through 4-31, 5-1 through 5-9, B-0 through B-8.                                           |

| A              | Manual released                                                                               |

| (1-07-74)      |                                                                                               |

| D              | Manuel mariands includes ECO 024702 (multipation change only). Dance changed mariain          |

| (4-1-74)       | Manual revised; includes ECO 034793 (publication change only). Pages changed: revision        |

| (4-1-14)       | record, iii through xii, 1-1 through 1-54, 2-1 through 2-6, 2-9, 2-10, 2-12, 2-14, 2-19,      |

|                | 2-21, 2-22, 2-25, 2-31, 2-32, 2-35, 2-40, 2-42 through 2-49, 2-52, 2-53, 2-55, 2-65,          |

|                | 2-67, 2-68, 2-70, 2-71 through 2-74, 2-82, 2-84, 2-85, 2-87, 2-88, 2-89, 2-91 through         |

|                | 2-106, 2-108, 2-109, 2-110, 2-112, 2-113, 2-114, 2-120, 2-128, 2-135, 2-136, 2-137,           |

| ·              | 2-146, 2-147, 2-152, 2-155, 2-156, 2-157, 2-165, 3-1, 3-3, 3-8, 3-9, 3-10, 3-13, 3-17,        |

|                | 3-19, 3-20, 3-21, 3-28, 3-29, 3-31, 3-33, 3-34, 3-35, 3-38, 3-40, 3-46, 3-48, 3-51            |

|                | through 3-56, 3-60, 3-62, 3-68, 3-69, 3-79, 3-94 through 3-100, 3-103, 3-104, 3-105,          |

|                | 4-1, 4-15, 5-1, 5-6, 5-8, A-1 through A-9, A-11, A-14 through A-19, A-22, A-23, A-24,         |

|                | A-27, A-30 A-31, A-32, A-34, A-46 through A-51, A-54, A-55, A-57, A-63 through A-66,          |

|                | A-70 through A-79, B-2 through B-9, C-1 through C-4, C-9 through C-15. Add the follow-        |

|                | ing pages: 1-55 through 1-59, 2-94.1 through 2-94.3, 3-106 through 3-109, 5-9 through 5-21    |

|                | A-81 through A-90.                                                                            |

| C              | Manual revised; includes ECO 035000, Pages changed; cover, title page, iii through            |

| (12-2-74)      | xii, 1-1, 1-2, 1-5, 1-7, 1-18, 1-19, 1-21, 1-29, 1-30, 1-46, 1-57, 1-58, 2-1, 2-4, 2-9, 2-10, |

|                | 2-15, 2-16, 2-17, 2-20 through 2-23, 2-32, 2-39, 2-40, 2-43 through 2-48, 2-52, 2-63          |

|                | through 2-68, 2-70, 2-74, 2-80, 2-81, 2-90 through 2-94.3, 2-97, 2-104, 2-105, 2-119,         |

|                | 2-120, 2-122 through 2-128, 2-145 through 2-151, 2-155 through 2-165, 3-4, 3-7, 3-18,         |

| ublication No. |                                                                                               |

| 60405000       |                                                                                               |

Address comments concerning this manual to:

Control Data Corporation Technical Publications Department 4201 North Lexington Avenue Arden Hills, Minnesota 55112

or use Comment Sheet in the back of this manual.

|          | RECORD of REVISIONS (CONT'D)                                                                                                                                           |  |  |  |  |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| REVISIÓN | NOTES                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|          | 3-20, 3-24 through 3-28, 3-31, 3-32, 3-33, 3-37, 3-40, 3-42 through 3-47, 3-51, 3-60 through                                                                           |  |  |  |  |  |  |  |  |

|          | 3-63, 3-68, 3-72, 3-74 through 3-82, 3-84, 3-86, 3-95, 3-107, 4-19, 4-22, 4-24, 4-25, 4-26,                                                                            |  |  |  |  |  |  |  |  |

|          | A-1, A-3, A-9, A-13 through A-19, A-24, A-26, A-32, A-33, A-42, A-43, A-49, A-57, A-71, A-74, B-2 through B-5, B-7, and B-9. Add the following pages: 2-94.4, 2-104.1, |  |  |  |  |  |  |  |  |

|          | A-42.1, A-42.2. Delete the following pages: 1-59, Appendix C (C-1 through C-15).                                                                                       |  |  |  |  |  |  |  |  |

|          | 11 42.1, 11 42.2. Belete the following pages. I be, appendix e (e i through e 10).                                                                                     |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| -        |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|          |                                                                                                                                                                        |  |  |  |  |  |  |  |  |

### **PREFACE**

This manual contains reference information for the system functions of the CONTROL DATA® STAR Peripheral Stations, descriptions of the station hardware, and some typical procedures necessary to exercise the programmable elements. The STAR stations are a set of peripheral equipment designed for use with a CDC® STAR 100 Computer, and as such, are implemented to some degree by common hardware and software. Other stations may be used in a STAR peripheral system; manuals providing information on this equipment are listed in this preface.

#### NOTE

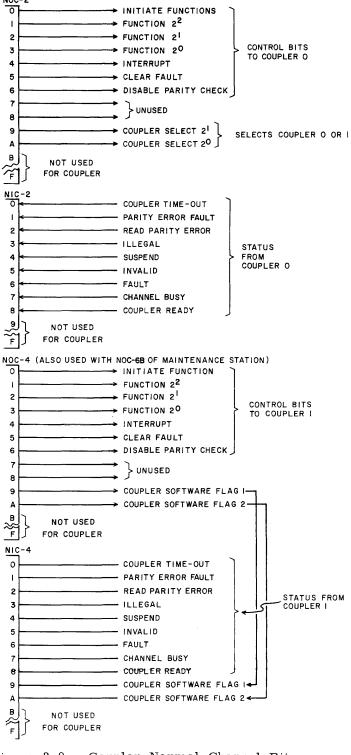

Throughout this manual, the abbreviations NOC and NIC denote normal output channel and normal input channel, respectively. As an example of its use in text, the notation NOC-5 indicates normal output channel 5.

| Control Data Publications                                                                                                                    | Publication No.          |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| †STAR-100 Computer Reference Manual                                                                                                          | 60256000                 |

| †STAR-100 Computer Hardware Maintenance Manuals: General Description, Operation, Theory of Operation, Installation and Checkout, Maintenance | 60256100                 |

| Control Data Large and Medium Scale Computer Systems Site<br>Preparation Manual Section 1 - General Information                              | 60275100                 |

| Control Data STAR-100 Computer System Site Preparation Manual Section 2 - System Data                                                        | 60381600                 |

| †STAR-100 Computer Refrigeration System Customer Engineering Manual                                                                          | 60329800                 |

| †STAR-100 Peripheral Stations Customer Engineering Manual (Maintenance)                                                                      | 60325300                 |

| STAR-100 Peripheral Stations Customer Engineering Diagrams Manu                                                                              | als                      |

| †Station Buffer Unit Core Control                                                                                                            | 60382000 and<br>60406700 |

| †Station Buffer Unit Interfaces                                                                                                              | 60382100 and<br>60406800 |

| †Station Control Unit                                                                                                                        | 60362900                 |

| †Station Display Unit                                                                                                                        | 60382500                 |

<sup>†</sup>This manual is available on a controlled distribution basis only from:

Control Data Corporation

STAR-100 Continuation Dept.

4201 No. Lexington Ave.

Arden Hills, Minn. 55112

All manuals not having the dagger are available from:

Literature and Distribution Services

8100 34th Ave. So., P.O. Box O

Minneapolis, Minn. 55440

60405000 C

| Control Data Publication                                                         | Publication No. |

|----------------------------------------------------------------------------------|-----------------|

| FR101B Buffer Controller Reference Manual                                        | 60275000        |

| 3000 Series Computer Systems I/O Specifications Manual                           | 60048800        |

| 7600/CYBER 70 Model 76 Computer Systems I/O Specifications                       | 60408700        |

| Buffer Controller Maintenance Console Customer Engineering Manual (TF201-A03)    | 58032700        |

| Buffer Controller Maintenance Console II Customer Engineering Manual (TF204-A01) | 59344000        |

| CC102-A Display Station Reference/Customer Engineering Manual                    | 82160600        |

| CC601-A/B Display Station Reference/Customer Engineering Manua                   | al 82134300     |

| CA115-A Entry Keyboard Reference/Customer Engineering Manual                     | 82160700        |

| 405 Card Reader Reference/Customer Engineering Manual                            | 40809300        |

| 3649-A Card Reader Controller Reference/Instruction Manual                       | 60097900        |

| 415 Card Punch Maintenance Manual                                                | 40819600        |

| 512-1 Line Printer Reference/Customer Engineering Manual                         | 44980100        |

| 3555-1 Line Printer Controller Reference Manual                                  | 60231300        |

| HR-600 Line Printer Customer Engineering Manual                                  | 44983100        |

| 657-1, 2, 3, 4 Magnetic Tape Transports Reference/Customer Engineering Manual    | 70600200        |

| 659-1, 2, 3, 4 Magnetic Tape Transports Reference/Customer Engineering Manual    | 70601000        |

| 841 Multiple Disk Drive Maintenance Manuals                                      | 41243500        |

| 844 Disk Storage Unit Customer Engineering Manual                                | 70629500        |

| 854 Disk Storage Drive Maintenance Manual                                        | 41245800        |

| 865 Drum Storage Unit Customer Engineering Manual (Modified 86                   | 5) 60320900     |

| High Capacity Disk Subsystem                                                     | 60428700        |

| 3446-A/B Card Punch Controller Reference Manual                                  | 60332100        |

| 3447-A Card Reader Controller Reference Manual                                   | 60332300        |

| 3528 Magnetic Tape Controller Reference Manual                                   | 60287600        |

|                                                                                  |                 |

iv 60405000 C

# **CONTENTS**

| 1.   | GENERAL DESCRIPTION                            |              | 844 Disk Storage Unit                      | 1-57  |

|------|------------------------------------------------|--------------|--------------------------------------------|-------|

| Gen  | eral                                           | 1-1          | 854 Disk Storage Drive                     | 1-57  |

|      | ipheral Station/Computer                       |              | 865 Drum Storage Unit                      | 1-57  |

|      | tem Overview                                   | 1-1          | High Capacity Disk (HCD) File              | 4 5 5 |

| Stat | ion Organization                               | 1-3          | Subsystem                                  | 1-57  |

| Stat | ion Configurations                             | 1-5          |                                            |       |

| Stat | ion Descriptions                               | 1-5          |                                            |       |

|      | Station Buffer Unit                            | 1-19         | 2. STATION BUFFER UNIT INTER               | FACES |

|      | Station Control Unit                           | 1-22         | General                                    | 2-1   |

|      | Portable Maintenance Console                   | 1-25         | SBU Overview                               | 2-1   |

|      | Paging (Drum) Station                          | 1-27         | Organization of SBU Memory                 | 2-3   |

|      | High Capacity Disk Station                     | 1-29         | SBU I/O Interfaces                         | 2-4   |

|      | 844 Service Station                            | 1-31         | Functions Performed by SBU                 |       |

|      | STAR-100 Service Station                       | 1-35         | Interfaces                                 | 2-5   |

|      | STAR-1B Service Station                        | 1-36         | SCU Control of SBU Interfaces              | 2-6   |

|      | 844 Storage and Magnetic                       |              | Selection of Interfaces by SCU             | 2-7   |

|      | Tape Stations                                  | 1-38         | SBU Interface Status Information           | 2-7   |

|      | Unit Record Station                            | 1-40         | Memory Priorities                          | 2-8   |

|      | Display/Edit Station                           | 1-41         | SBU Peripheral A Interface                 | 2-12  |

|      | Storage (Media) Station                        | 1-43         | Data Transfer Operations                   | 2-13  |

|      | STAR-100 Maintenance<br>Control Unit           | 1-45         | Normal Channel Control of the A Interfaces | 2-14  |

|      |                                                |              | Function Codes                             | 2-14  |

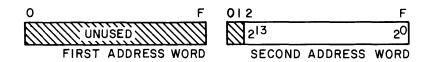

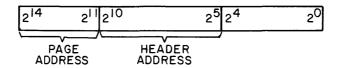

|      |                                                |              | Starting Address Format                    | 2-17  |

| Har  | dware Element Descriptions Station Buffer Unit | 1-47<br>1-47 | STAR Channel Transmission Sequence         | 2-18  |

|      | Station Control Unit                           | 1-48         | Parity Checking                            | 2-19  |

|      | Portable Maintenance Consoles                  | 1-53         | SBU Memory Parity Check                    | 2-19  |

|      |                                                |              | · · · · · · · · · · · · · · · · · · ·      | 2-19  |

|      | Station Display Unit                           | 1-53         | Interrupting the A Interface               | 2-19  |

|      | 405 Card Reader                                | 1-53         | Normal Channel Control and<br>Status Bits  | 2-20  |

|      | 415 Card Punch                                 | 1-54         | Programming Sequences                      | 2-24  |

|      | 512-1 Line Printer                             | 1-55         | SCU Coupler Interface (STAR A Data         |       |

|      | 657 and 659 Magnetic Tape<br>Transports        | 1-55         | Channel Interface)                         | 2-25  |

|      | 841 Multiple Disk Drive (Modified)             | 1-55         | Data Transfer Operations                   | 2-25  |

60405000 C

|        | Normal Channel Control of the SCU Coupler     | 2-27         | SCU Control of In<br>Logic     | idex Compare     | 2-98   |

|--------|-----------------------------------------------|--------------|--------------------------------|------------------|--------|

|        | Starting Address Format                       | 2-29         | Programming Se                 | quences          | 2-106  |

|        | STAR Channel Transmission                     |              | 344 Interface                  |                  | 2-108  |

|        | Sequence                                      | 2-29         | 844 Disk Storage               | Unit             |        |

|        | Parity Checking                               | 2-30         | Description                    |                  | 2-110  |

|        | SBU Memory Parity Check                       | 2-31         | 844 Sector Recor               | •                | 2-112  |

|        | Normal Channel Status Bits                    | 2-31         | Data Transfer O <sub>l</sub>   | •                | 2-115  |

|        | AR B Data Channel Interface<br>C Coupler)     | 2-33         | SBU Memory Add                 | dressing         | 2-119  |

| (622   | SBU/HLP Data Transfer                         | 2 00         | Parity                         |                  | 2-121  |

|        | Operations                                    | 2-35         | 844 Interface No.<br>Signals   | rmal Channel     | 2-121  |

|        | SCU/HLP Data Transfer                         | 2 22         | Address and Con                | trol Bus         | 2-129  |

|        | Operations                                    | 2-36         | Programming Se                 |                  | 2-130  |

|        | Function Codes                                | 2-37         | Multiple Disk Drive (          | -                | 2-132  |

|        | Parity Checking                               | 2-40         | MDD Description                |                  | 2-134  |

|        | SBU Memory Parity Check                       | 2-40         | MDD Sector Reco                |                  | 2-135  |

|        | Status                                        | 2-41         | Data Transfer O                | J                | 2-138  |

|        | Terminating Conditions                        | 2-42         | SBU Memory Ado                 |                  | 2-142  |

|        | Interrupting the HLP                          | 2-42         | Parity                         | ~1 000111g       | 2-143  |

|        | SCU Control of the SAC Coupler                | 2-43         | MDD Interface N                | ormal Channel    | - 110  |

|        | Programming Sequences                         | 2-48         | Signals                        | ormar chamici    | 2-144  |

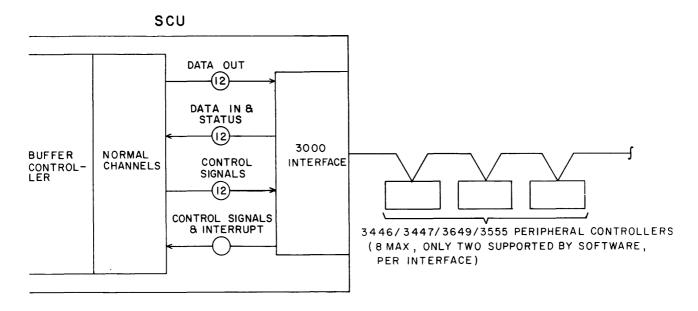

| 300    | 0 I/O Channel Interface                       | 2-52         | Address and Con                | trol Bus         | 2-152  |

|        | Main Functions                                | 2-53         | Programming Se                 | quences          | 2-153  |

|        | Data Transfer Operations                      | 2-54         | Network Trunk Interf           | ace              | 2-155  |

|        | Code Conversion Tables                        | 2-58         | ADCCP Message                  | Formats          | 2-156  |

|        | Address Formats                               | 2-61         | NTI Message Sec                | luences          | 2-158  |

|        | Multipage Data Transfer<br>Operations         | 2-62         | NTI Responses                  |                  | 2-163  |

|        | Terminating Conditions                        | 2-63         | Cyclic Redundan                | cy Check         | 2-165  |

|        | SCU Control of 3000 Interface                 | 2-63         |                                |                  |        |

|        | Scanner Status Bits                           | 2-03         | 3. STATION CONTE               | ROL UNIT INTEF   | RFACES |

|        |                                               | 2-74         | General                        |                  | 3-1    |

| 700    | Programming Sequences 0 I/O Channel Interface | 2-75         | senerar<br>Microdrum Subsyster | m and CDT        | 3-1    |

| 100    | Main Functions                                | 2-80         | Display                        | ii aiiu Civi     | 3-1    |

|        | Data Transfers                                |              | Organization of I              | Data on          |        |

|        | Address Formats                               | 2-82<br>2-84 | Microdrum                      |                  | 3-1    |

|        |                                               |              | CRT Display/Ke                 | yboard Interface | 3-9    |

|        | SCU Control of 7000 Interface<br>Status       | 2-85<br>2-89 | Display Operatio               |                  | 3-9    |

|        |                                               |              | Typical Program                | iming Sequences  | 3-13   |

| I m al | Programming Sequences<br>ex Compare Logic     | 2-94<br>2-96 | Entry Keyboard                 |                  | 3-17   |

| HILL   | EX COMPATE LOGIC                              | 4-30         |                                |                  |        |

vi 60405000 C

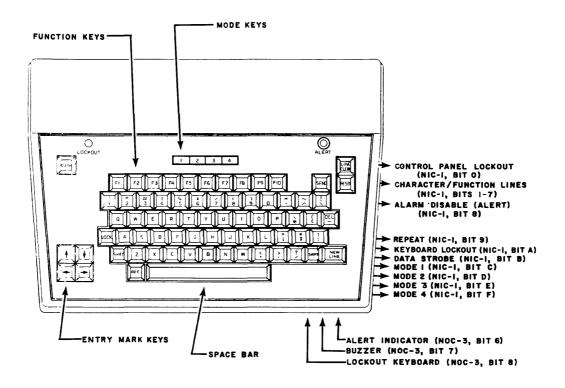

|     | Keyboard Control Keys                            | 3-17  | HR600 Printer Interface                                                   | 3-104    |

|-----|--------------------------------------------------|-------|---------------------------------------------------------------------------|----------|

|     | Keyboard Interface Signals                       |       | General                                                                   | 3-104    |

|     | (To NIC)                                         | 3-17  | Normal Channel Switch                                                     | 3-104    |

|     | Keyboard Interface Signals (From NIC)            | 3-21  | Programming Sequences                                                     | 3-108    |

| SCU | J B Coupler Interface                            | 3-22  | STAR-65 Maintenance Interface                                             | 3-109    |

|     | Data Transfer Operations                         | 3-24  |                                                                           |          |

|     | Function Codes                                   | 3-25  | 4. STATION DISPLAY UNIT AND SI                                            | U        |

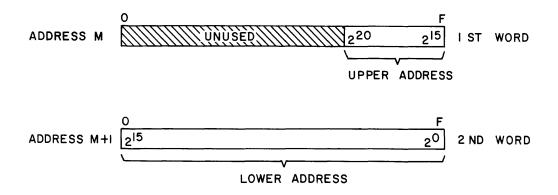

|     | Starting Address Format                          | 3-28  | COUPLER                                                                   |          |

|     | Parity Checking                                  | 3-29  | General Description                                                       | 4-1      |

|     | Terminating Conditions                           | 3-30  | SDU Coupler                                                               | 4-4      |

|     | Interrupting the A Interface                     | 3-30  | Keyboard                                                                  | 4-11     |

|     | SCU Control of the B Coupler                     | 3-31  | Memory Map                                                                | 4-20     |

|     | Programming Sequences                            | 3-35  | Normal Channel Control Bits                                               | 4-21     |

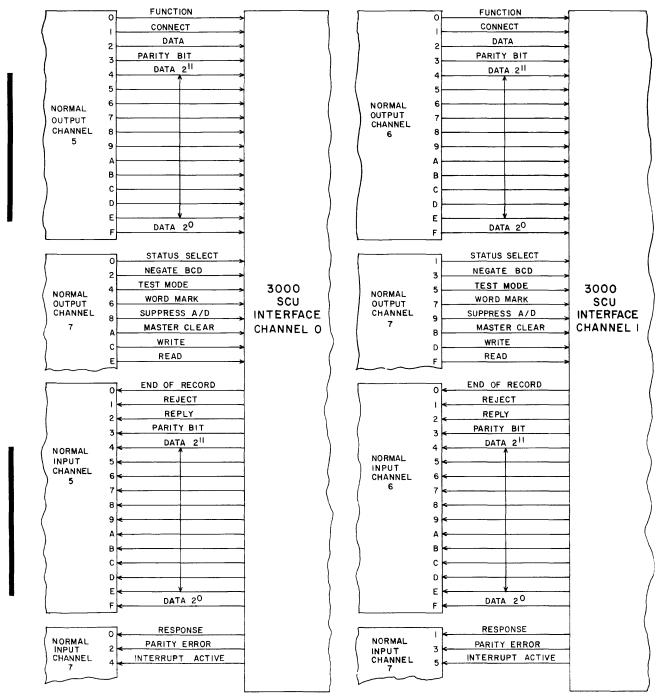

| 300 | 0 SCU Interface                                  | 3-37  | Programming Sequences                                                     | 4-28     |

|     | 3000 Interface Operations                        | 3-38  |                                                                           |          |

|     | 3000 Interface Normal Channel                    |       | 5. OPERATION                                                              |          |

|     | Signals                                          | 3-40  | General                                                                   | 5-1      |

|     | Programming Sequences                            | 3-47  | Station Control Unit Switches and                                         |          |

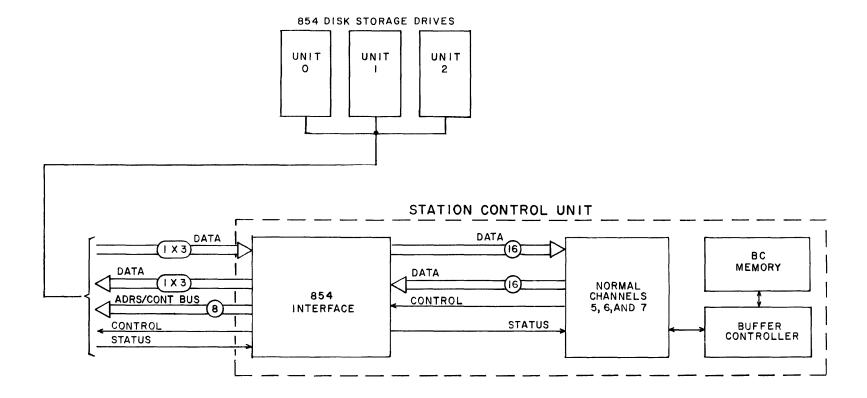

| 854 | Interface                                        | 3-51  | Indicators                                                                | 5-1      |

|     | Disk Storage Drive Description                   | 3-51  | Power Sequence                                                            | 5-1      |

|     | 854 Sector Recording                             | 3-53  | Temperature Warning Indicator                                             | 5-1      |

|     | Write Tags Operation                             | 3-56  | SCU Control Panel                                                         | 5-2      |

|     | Data Transfer Operations                         | 3-57  | Portable Maintenance Console<br>Control Panels                            | 5-6      |

|     | 854 Interface Normal Channel<br>Signals          | 3-60  | Control 1 anets                                                           | 3-0      |

|     | Address and Control Bus                          | 3-64  | APPENDIX A. STATION NORMAL                                                |          |

|     | Programming Sequences                            | 3-65  | CHANNEL BIT ASSIGNMENTS                                                   | A-1      |

| STA | AR-100 Maintenance Interface                     | 3-68  |                                                                           | -        |

|     | Maintenance Interface<br>Monitoring Activities   | 3-86  | APPENDIX B. INTERFACE NORMA:<br>CHANNEL BIT ASSIGNMENTS                   | L<br>B-1 |

| STA | AR-100 Control Interface                         | 3-94  |                                                                           |          |

|     | Control Interface to A Coupler<br>Function Codes | 3-95  | APPENDIX C. STAR DATA CHANNEL CHARACTERISTICS (Deleted; refer to Pub. No. |          |

|     | Microcode Write Switches                         | 3-97  | (Defeted; refer to Pub. No. 60429400)                                     |          |

|     | Microcode Status                                 | 3-98  |                                                                           |          |

|     | Programming Sequences                            | 3-99  |                                                                           |          |

| SDU | J Coupler Interface                              | 3-103 |                                                                           |          |

60405000 C vii

### FIGURES

| 1-1  | Typical System Configuration, STAR Peripheral Stations      | 1-2   | 2-3      | Peripheral A Interface System<br>Relationship                | 2-12 |

|------|-------------------------------------------------------------|-------|----------|--------------------------------------------------------------|------|

| 1-2  | Typical SCU/SBU Station                                     | 1-4   | 2-4      | STAR Channel Starting                                        | 0.45 |

| 1-3  | Typical SCU-Only Station                                    | 1-4   | <b>=</b> | Address Format                                               | 2-17 |

| 1-4  | Paging (Drum) Station, Typical                              |       | 2-5      | (Deleted)                                                    |      |

| 1-5  | Configuration (Deleted)                                     | 1-6   | 2-6      | SCU Coupler System<br>Relationship                           | 2-26 |

| 1-6  | 844 Service Station, Typical Configuration                  | 1-8   | 2-7      | SAC Coupler System<br>Relationship                           | 2-34 |

| 1-7  | STAR-100 Service Station,<br>Typical Configuration          | 1-9   | 2-8      | 3000 I/O Channel Interface<br>System Relationship            | 2-52 |

| 1-8  | STAR-1B Service Station, Typical Configuration              | 1-10  | 2-9      | Memory Word Assembly,<br>Read Binary                         | 2-55 |

| 1-9  | 844 Storage Station, Typical Configuration                  | 1-11  | 2-10     | Memory Word Disassembly,<br>Write Binary                     | 2-55 |

| 1-10 | -                                                           |       | 2-11     | Read Code Conversion                                         | 2-56 |

|      | Typical Configuration                                       | 1-12  | 2-12     | Write Code Conversion                                        | 2-57 |

| 1-11 | Unit Record Station, Typical                                | 1 10  | 2-13     | Read Conversion Table                                        | 2-59 |

| 1 10 | Configuration                                               | 1-13  | 2-14     | Write Conversion Table                                       | 2-60 |

|      | Display/Edit Station, Typical Configuration                 | 1-14  | 2-15     | Normal Output Channel 5 Control Information, 3000 Interface  | 2-65 |

| 1-13 | Storage (Media) Station,<br>Typical Configuration           | 1-15  | 2-16     | 7000 I/O Channel Interface<br>System Relationship            | 2-81 |

| 1-14 | STAR-100 Maintenance Control<br>Unit, Typical Configuration | 1-16  | 2-17     | Input Operation, 12- to 16-bit Assembly                      | 2-83 |

| 1-15 | STAR-65 Maintenance Control<br>Unit, Typical Configuration  | 1-17  | 2-18     | Output Operation, 16- to 12-bit Disassembly                  | 2-83 |

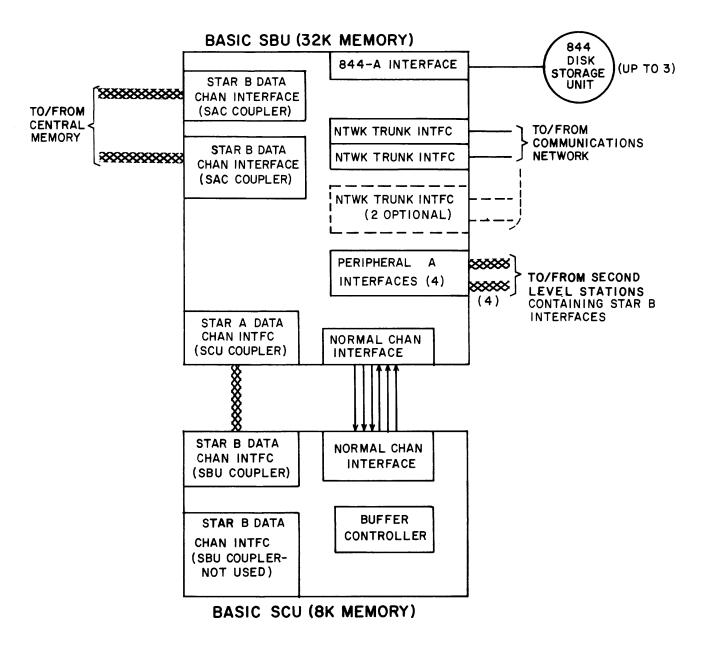

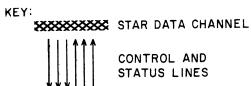

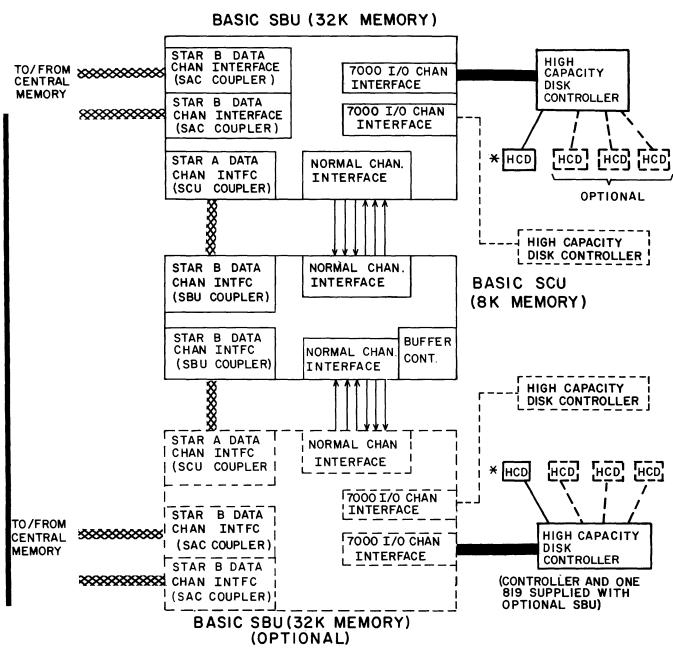

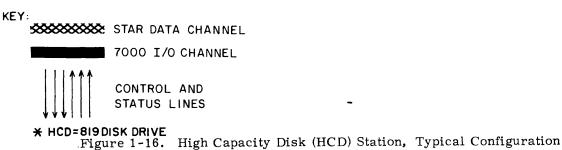

| 1-16 | High Capacity Disk (HCD)<br>Station, Typical Configuration  | 1-18  | 2-19     | Output Channel 5 Control<br>Information, 7000 Interface      | 2-87 |

| 1-17 | Station Buffer Unit Functional<br>Block Diagram             | 1-20  | 2-20     | SCU/7000 Interface Function<br>Code Formats                  | 2-88 |

| 1-18 | Station Control Unit Functional<br>Block Diagram            | 1-22. | 2-20.    | 1 Typical Register Configura-<br>tion For a Data Transfer to | - 00 |

| 1-19 | Station Buffer Unit Component Locations                     | 1-48  | 9_91     | the Drum Index Compare System                                | 2-94 |

| 1-20 | Station Control Unit Component Locations                    | 1-49  |          | Relationship                                                 | 2-96 |

| 1-21 | Diddle Pattern                                              | 1-52  | 4-22     | Normal Channel Bit Assign-<br>ments, Index Compare Inter-    |      |

|      | Station Display Unit Component                              |       |          | face (Drum Station)                                          | 2-97 |

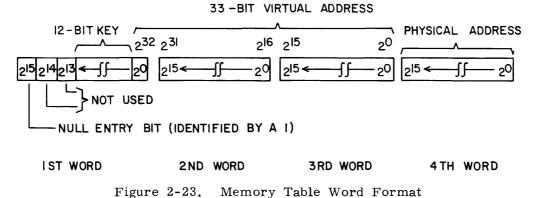

|      | Locations                                                   | 1-54  | 2-23     | Memory Table Word Format                                     | 2-98 |

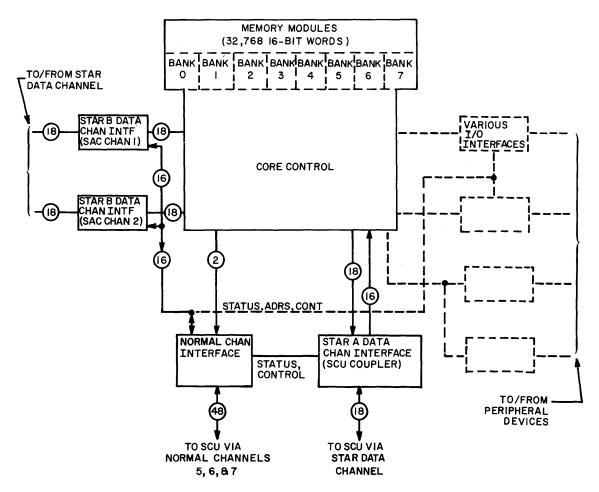

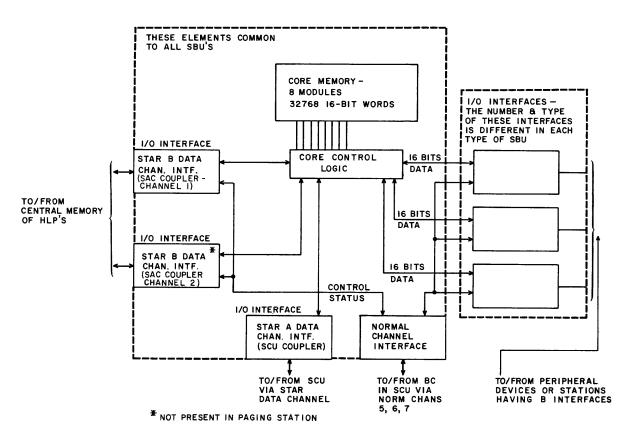

| 2-1  | SBU Block Diagram                                           | 2-2   | 2-24     | Typical SCU Request Word                                     | 0.00 |

| 2-2  | Overlapped Memory References                                | 2-3   |          | Formats                                                      | 2-99 |

viii 60405000 C

# FIGURES

| 2-25  | Request Register Loading                        | 2-100 | 3-12 | 854 Interface System                                     |       |

|-------|-------------------------------------------------|-------|------|----------------------------------------------------------|-------|

| 2-26  | 844 Interface System                            |       |      | Relationship                                             | 3-52  |

|       | Relationship                                    | 2-109 |      | 854 Sector Recording                                     | 3-53  |

| 2-27  | Read/Write Heads and Disk<br>Recording Surfaces | 2-111 | 3-14 | Address Tag Word                                         | 3-55  |

| 990   | 844 Sector Recording                            | 2-111 | 3-15 | Maintenance Control Unit/                                |       |

|       | <b>G</b>                                        |       |      | STAR-100 Computer System<br>Relationship                 | 3-69  |

|       | Address Tag Word Full Banks Address Format,     | 2-114 | 3-16 | Microcode Write Switch                                   | 0.05  |

|       | 844 Interface                                   | 2-120 |      | Control Word                                             | 3-97  |

| 2-31  | Half Banks Address Format,<br>844 Interface     | 2-120 | 3-17 | Microcode Memory Status<br>Words                         | 3-99  |

| 2-32  | MDD Interface System<br>Relationship            | 2-133 | 3-18 | Normal Channel Switch/Normal<br>Channel 6 Relationship   | 3-107 |

| 2-33  | MDD Sector Recording                            | 2-135 | 4-1  | Typical SCU/SDU System<br>Communication Paths            | 4-2   |

| 2-34  | MDD Address Tag Word                            | 2-136 | 4-2  | CRT Display Formats                                      | 4-3   |

| 2-35  | Full Banks Address Format,<br>MDD Interface     | 2-143 | 4-3  | SDU Coupler System<br>Relationship                       | 4-5   |

| 2-36  | Half Banks Address Format,                      | 0 140 | 4-4  | ASCII Data Format                                        | 4-6   |

| 0 0 7 | MDD Interface                                   | 2-143 | 4-5  | Cursor Address Format                                    | 4-8   |

| 2-37  | Network Trunk Interface<br>System Relationship  | 2-155 | 4-6  | Write-Offset                                             | 4-10  |

| 2-38  | Message Frame For-                              |       | 4-7  | Read-Offset                                              | 4-10  |

|       | mats                                            | 2-156 | 4-8  | Keyboard Layout                                          | 4-12  |

| 3-1   | Microdrum Subsystem<br>System Relationship      | 3-2   | 4-9  | Keyboard/Normal Channel<br>Signals                       | 4-13  |

| 3-2   | Work Formats Between the BC                     |       | 4-10 | Keyboard Indicator Control                               | 4-17  |

|       | and Microdrum Subsystem and Keyboards           | 3-4   |      | SDU Memory Map                                           | 4-20  |

| 3-3   | Keyboard/BC Word Formats                        | 3-10  |      | SDU and SDU Coupler Normal                               |       |

| 3-4   | SCU Keyboard and I/O Signals                    | 3-18  |      | Channel Bits                                             | 4-21  |

| 3-5   | SCU B Coupler System                            |       | 4-13 | Address Format                                           | 4-22  |

|       | Relationship                                    | 3-22  | 4-14 | Compare Character Format                                 | 4-23  |

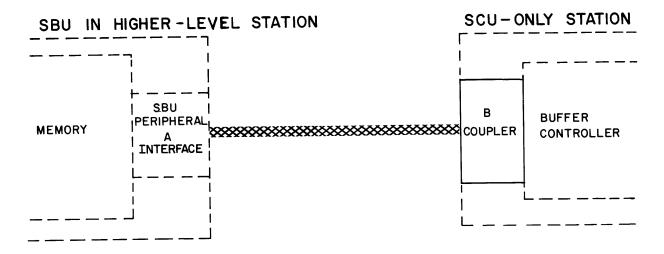

| 3-6   | B Coupler Used in SCU-Only<br>Station           | 3-23  | 5-1  | Station Control Unit Control<br>Panel                    | 5-2   |

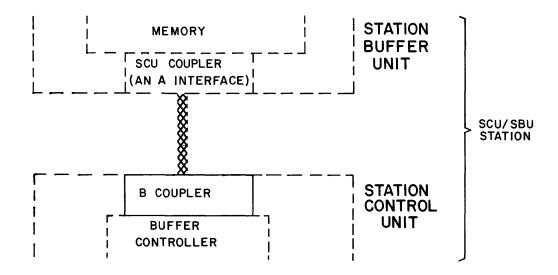

| 3-7   | B Coupler Used in SCU/SBU<br>Station            | 3-24  | 5-2  | Portable Maintenance Console<br>Control Panel (TF201)    | 5-7   |

| 3-8   | B Coupler Starting Address<br>Word Formats      | 3-28  | 5-3  | Portable Maintenance Console<br>II Control Panel (TF204) | 5-15  |

| 3-9   | Coupler Normal Channel Bits                     | 3-31  |      |                                                          |       |

| 3-10  | 3000 SCU Interface System<br>Relationship       | 3-38  |      |                                                          |       |

| 3-11  | 3000 SCU Normal Channel<br>Signals              | 3-40  |      |                                                          |       |

60405000 C ix

# TABLES

| 1-1   | Physical and Functional Properties of Magnetic Tape Transports      |              | 2-20 | Bit Descriptions For Index<br>Compare/NOC-6 and -7 | 0 104 |

|-------|---------------------------------------------------------------------|--------------|------|----------------------------------------------------|-------|

| 1-2   | Peripheral Storage Unit<br>Characteristics                          | 1-58         | 2-21 | (Drum Station) Bit Descriptions For Index          | 2-104 |

| 2-1   | SBU Connect Codes                                                   | 2-9          |      | Compare/NIC-5, -6, and -7                          | 2-105 |

| 2-2   | SBU Memory Priorities                                               | 2-10         | 2-22 | NIC-6 and -7 Bit Descriptions<br>For 844 Interface | 2-122 |

| 2-3   | Operation Function Codes                                            | 2-15         | 2-23 | NOC-6 and -7 Bit Descriptions                      | 2 122 |

| 2-4   | System Control Function Codes                                       | 2-16         | 2 20 | For 844 Interface                                  | 2-125 |

| 2-5   | Normal Channel Bit Definitions<br>For Peripheral A Interface        | 2-22         | 2-24 | Address and Control Bus<br>Functions               | 2-129 |

| 2-6   | SCU Coupler Operation Function Codes                                | 2-28         | 2-25 | NIC-6 and -7 Bit Descriptions<br>For MDD Interface | 2-145 |

| 2-7   | Normal Channel Bit Descriptions<br>For SCU Coupler Interface        | 2-32         | 2-26 | NOC -5 and -6 Bit Descriptions For MDD Interface   | 2-148 |

| 2-8   | SAC Coupler Operation Function Codes                                | 2-37         | 2-27 | Address and Control Bus<br>Functions               | 2-152 |

| 2-9   | SAC Coupler System Control<br>Codes                                 | 2-39         | 2-28 | Remote Terminal Read<br>Request Message Sequence   | 2-159 |

| 2-10  | Bit Descriptions For SAC Coupler/NOC-5, -6, and -7                  |              | 2-29 | Read Data Message Response<br>Sequence             | 2-159 |

| 2-11  | Interfaces (HCD Station) Bit Descriptions For SAC                   | 2-43         | 2-30 | Remote Terminal Write<br>Request Message Sequence  | 2-161 |

|       | Coupler/NIC-5, -6, and -7 Interfaces                                | 2-46         | 2-31 | NTI Response Sequence To<br>Write Request Message  | 2-161 |

|       | NOC-6 Bit Descriptions For 3000 Interface                           | 2-68         | 2-32 | Remote Terminal Reset<br>Message Sequence          | 2-162 |

|       | (Deleted)                                                           |              | 2-33 | NTI Reset Acknowledge<br>Message Sequence          | 2-162 |

| 2-14  | NIC-5 Status Word Bit Descriptions For 3000 Interface               | 2-71         | 2-34 | NTI Error Conditions                               | 2-164 |

| 2-15  | NIC-6 Status Word Bit Descrip-                                      |              | 3-1  | ASCII Coding Set For Keyboard                      | 3-19  |

|       | tions For 3000 Interface 3000 Interface Scanner Status              | 2-73         | 3-2  | Keyboard Control Key Function Codes                | 3-20  |

|       | Bits                                                                | 2-74         | 3-3  | B Coupler Operation Function Codes                 | 3-26  |

|       | Bit Descriptions For 7000 Interface/NIC-5 and -6 (Drum Station)     | 2-91         | 3-4  | B Coupler System Control<br>Codes                  | 3-27  |

| 2-18  | Bit Descriptions For 7000 Interface/NIC-5, -6, and -7 (HCD Station) | 2-92         | 3-5  | Normal Channel Bit Descriptions, SCU B Coupler     | 3-32  |

| 2-19  | Bit Descriptions For 7000 Interface NOC-5 and -6 (Drum              | 2-93         | 3-6  | Normal Channel Bit Definitions, 3000 SCU Interface | 3-41  |

| 2-19. | Station)  1 Bit Descriptions For 7000  Interface /NOC 5 6 and 7     | 4 <b>-93</b> | 3-7  | NIC-6A, -7 Bit Descriptions<br>For 854 Interface   | 3-60  |

|       | Interface/NOC-5, -6, and -7 (HCD Station)                           | 2-94.1       |      |                                                    |       |

x 60405000 C

### TABLES

| 3-8         | NOC-5, -6A, -7 Bit Descriptions For 854 Interface                     | 3-62  | 4-1 | ASCII Coding Set For SDU CRT Display                | 4-15 |

|-------------|-----------------------------------------------------------------------|-------|-----|-----------------------------------------------------|------|

| <b>3-</b> 9 | Address and Control Bus                                               |       | 4-2 | Keyboard Function Codes                             | 4-16 |

| 0 10        | Functions                                                             | 3-64  | 4-3 | NOC-5 Keyboard Indicator Selec                      |      |

| 3-10        | NIC-8 Through NIC-F Bit                                               |       |     | Bits for SDU Coupler Interface                      | 4-19 |

|             | Descriptions For Maintenance<br>Interface                             | 3-70  | 4-4 | NOC-6 Bit Descriptions For<br>SDU Coupler Interface | 4-24 |

| 3-11        | NOC-8 Through NOC-F Bit<br>Descriptions For Maintenance               |       | 4-5 | NIC-5, -6, and -7 Bit                               |      |

|             | Interface                                                             | 3-72  |     | Descriptions For SDU Coupler Interface              | 4-26 |

| 3-12        | Maintenance Interface Select<br>Codes                                 | 3-86  | 5-1 | Paper Tape Console Control Panel Controls           | 5-8  |

| 3-13        | Maintenance Interface Event<br>Select Codes                           | 3-89  | 5-2 | Cassette Console Control Panel Controls             | 5-16 |

| 3-14        | Function Codes For Control<br>Interface/Microcode Memory<br>Interface | 3-96  |     |                                                     |      |

| 3-15        | Bit Descriptions For Printer/<br>Normal Channel Interface             | 3-105 |     |                                                     |      |

60405000 C xi

### STAR PERIPHERAL STATION INTERFACE CONFIGURATION CHART

|                   | Station Type of Interface                       | Paging<br>(Drum)<br>Station | Storage<br>(Media)<br>Station | 844 Storage/<br>Magnetic Tape<br>Station | 844<br>Service<br>Station | STAR 100<br>Service<br>Station | STAR 1B<br>Service<br>Station | HCD<br>Station | Unit<br>Record<br>Station | Display/<br>Edit<br>Station | STAR 100<br>Maintenance<br>Control Unit | STAR 65<br>Maintenance<br>Control Unit |

|-------------------|-------------------------------------------------|-----------------------------|-------------------------------|------------------------------------------|---------------------------|--------------------------------|-------------------------------|----------------|---------------------------|-----------------------------|-----------------------------------------|----------------------------------------|

|                   | Microdrum<br>Keyboard                           | 1 1                         | 1 1                           | 1<br>1                                   | 1<br>1                    | 1<br>1                         | 1<br>1                        | 1<br>1         | 1<br>1                    | 1<br>1                      | 1<br>1                                  | 1                                      |

|                   | CRT<br>SBU Coupler                              | 1 1                         | 1<br>1                        | 1<br>1                                   | 1<br>1                    | 1<br>1                         | 1<br>1                        | 1<br>1         | 1<br>1                    | 1<br>1                      | 1<br>2                                  | 1<br>2                                 |

| SCU<br>Interfaces | Normal Channels<br>SCU Gate                     | 1                           | 1<br>1                        | 1<br>1                                   | 1<br>1                    | 1<br>1                         | 1<br>1                        | 1<br>1         | 1                         | 1<br>1                      | 1 1                                     | 1                                      |

| Interfaces        | SDU Coupler<br>3000 SCU                         |                             |                               |                                          |                           |                                |                               |                | 2                         | 1                           | 1                                       | 1                                      |

|                   | 854 SCU<br>HR 600                               |                             |                               |                                          |                           |                                |                               |                |                           |                             | 1 1                                     | 1                                      |

|                   | Normal Channel<br>Switch<br>STAR-100            |                             |                               |                                          |                           |                                |                               |                |                           |                             | 1                                       | 1                                      |

|                   | STAR-65                                         |                             |                               | _                                        |                           |                                |                               |                |                           |                             |                                         | 1                                      |

|                   | 3000 I/O<br>7000 I/O                            | 2                           | 2                             | 2                                        |                           | 1                              |                               | 2              |                           |                             |                                         |                                        |

| SBU               | 841 MDD<br>844 DSD                              |                             | 2                             | 2                                        | 1                         |                                | 2                             |                |                           |                             |                                         |                                        |

| Interfaces        | STAR A Data Char<br>SAC Coupler                 | 1                           | 2                             | 2                                        | 4<br>2                    | 8<br>2                         | 6<br>2                        | 2              |                           |                             |                                         |                                        |

|                   | Communication<br>Network Trunk<br>Index Compare | 1                           |                               |                                          | 2                         |                                | 1                             |                |                           |                             |                                         |                                        |

|                   |                                                 |                             |                               |                                          |                           |                                |                               |                |                           |                             |                                         |                                        |

### GENERAL

Section 1 contains an introduction to the CDC STAR Peripheral Stations. It includes a description of each station and its function, a brief description of each functional element within the station, and a physical description of the station hardware.

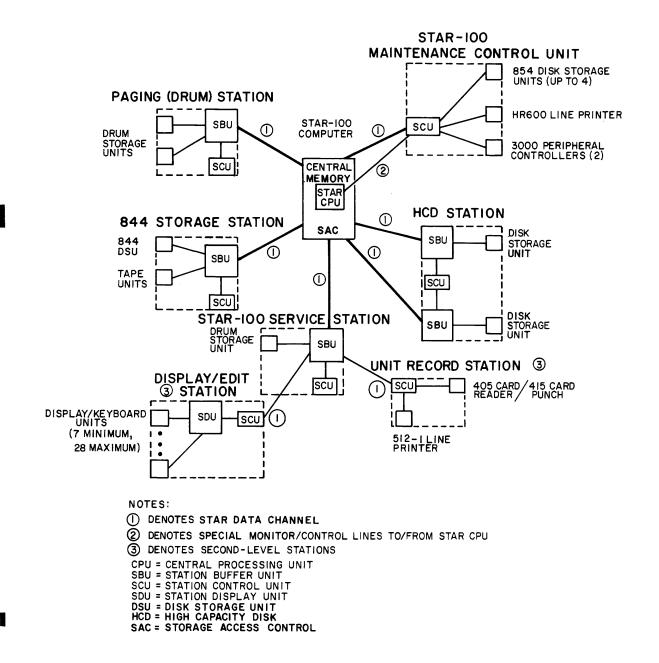

# PERIPHERAL STATION/COMPUTER SYSTEM OVERVIEW

Peripheral stations perform such tasks as detailed control of peripheral equipment, recovery and retransmission of corrected data, manipulation of records and messages as to timing and routing, and the general management of available peripheral resources.

The standard peripheral stations available to handle I/O tasks in STAR computer systems are:

- Paging (Drum) Station

- High Capacity Disk (HCD) Station

- 844 Service Station

- STAR-100 Service Station

- STAR-1B Service Station

- 844 Storage Station

- Magnetic Tape Station

- Unit Record Station

- Display/Edit Station

- Storage (Media) Station

- STAR-100 Maintenance Control Unit

- STAR-65 Maintenance Control Unit

Figure 1-1 illustrates the relationships of some of these standard stations to the central processor and the memory of a STAR-100 Computer.

Peripheral stations are classified as first level or second-level stations according to the position they occupy in the overall system hierarchy. This hierarchy is physical as well as logical in that an I/O data stream is staged twice from second-level stations and once from first-level stations on the way into and out of the STAR central processor. This procedure is necessary since many of the I/O operations usually required of the central processor have been reassigned to one or more levels in the hierarchy. First-level stations connect directly to central memory through STAR storage access control (SAC). Second-level stations (Figure 1-1) communicate indirectly with central memory through a first-level service station. The first-level service station acts as a concen-

60405000 C

Figure 1-1. Typical System Configuration, STAR Peripheral Stations

1-2 60405000 C

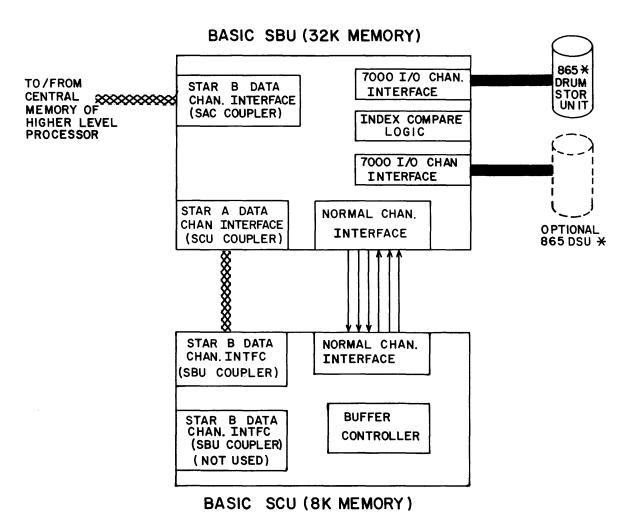

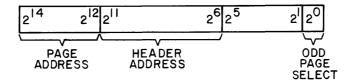

The SBU is basically a 32K- 16-bits per word-core memory with the peripheral interfaces that allow I/O devices to transfer data directly into or out of memory. Control lines from the SCU are used to activate and monitor the various peripheral interfaces. In many cases, several peripheral interfaces can transfer data concurrently. To transfer a block of data to the central processor memory from an I/O peripheral device, the data is first stored in SBU memory and then transferred to central memory via a STAR data channel. Similarly, to transfer a block of data to an I/O device, data is first stored in SBU memory and then transferred to the proper I/O device.

Differences in the varieties of SCUs and SBUs used in the various stations occur primarily in the peripheral interface areas.

### STATION CONFIGURATIONS

Figures 1-4 through 1-16 illustrate the major components in each station and methods of interconnection between peripheral equipment and SBUs.

#### NOTE

The following illustrations contain A and B data channel interfaces, which are elements associated with the STAR data channel and are explained in detail in pub. no. 60429400.

Also, the term peripheral A interface is used to differentiate the logic connected to the B interfaces of other stations from the A interface which connects to the B interface in the SCU.

### STATION DESCRIPTIONS

The following paragraphs describe the functions and logical configurations (building blocks) of the various stations and their interfaces. Most of these building blocks are used in more than one station. The Configuration Chart preceding section 1 lists the types and quantities of interfaces in each station. Figures 1-4 through 1-16 illustrate their relationship in each station.

Since the basic SBU and SCU are both common to many stations, a general discussion of each follows Figure 1-16 and precedes the station descriptions.

I

60405000 C

\* INDICATES MODIFIED UNIT

Figure 1-4. Paging (Drum) Station, Typical Configuration

(Deleted)

1-7

Figure 1-6. 844 Service Station, Typical Configuration

#### 3000 I/O CHAN STAR B DATA TO/FROM 3000 TO/FROM INTERFACE PERIPHERAL CONTROLLER(S) \* CHAN INTFC CENTRAL (SAC COUPLER) MEMORY DISK STORAGE TO/FROM 854 DISK STAR B DATA STORAGE DRIVES \* DRIVE INTFC CHAN INTFC (UP TO 4) (SAC COUPLER) LINE PRINTER TO/FROM HR 600 INTERFACE MULTIPLE LINE PRINTER \* SPECIAL **ACCESS LINES** CONTROL TO/FROM INTFC COMPUTER KEY: MAINFRAME

\*\*\*\*\*\*\*\*\* STAR DATA CHANNEL

3000 I/O CHANNEL

\* THESE ITEMS NOT SUPPLIED WITH THE BASIC SCU.

BUFFER

CONTROLLER

BASIC SCU (8K MEMORY)

Figure 1-15. STAR-65 Maintenance Control Unit, Typical Configuration

NORMAL CHAN

INTERFACE

60405000 B 1-17

#### STATION BUFFER UNIT

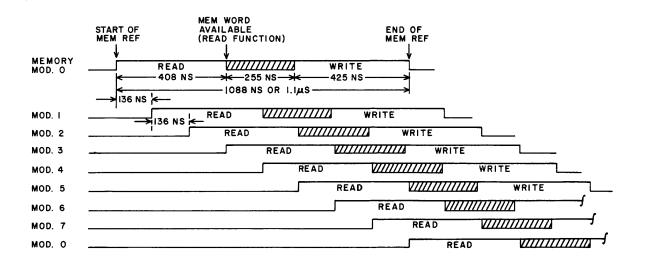

The SBU (Figure 1-17) consists primarily of core memory for intermediate storage of data between the STAR-100 CPU and peripheral devices or other peripheral stations. It also contains core control logic which provides 12 access points in and out of core memory for the various peripheral interfaces. This core memory contains 32,768 16-bit words organized into eight phased banks. The cycle time of each bank is 1.1 microseconds.

Typically, the SBU is used for transferring large amounts of data at high speeds, staging of files and jobs, temporary storage of data and messages, and expansion of the system to subordinate level stations. Therefore, the SCU is relieved of heavy data transfer tasks and is available for higher level control activities even though it controls the SBU and monitors all of its data flow. The SBU is treated as an external memory by the SCU and is not directly addressable by the BC within the SCU. Each functional section within the SBU is discussed in the order listed.

- STAR A data channel interface (SCU coupler)

- STAR B data channel interface (SAC coupler)

- Normal channel interface

- Core control

- Various I/O interfaces

#### STAR A DATA CHANNEL INTERFACE (SCU COUPLER)

The STAR A data channel interface provides a connection between an access to SBU core and an SCU via the STAR data channel. The A data channel interface is passive, with transfer, control, and initiation being directed by the STAR B data channel interface (active end).

#### STAR B DATA CHANNEL INTERFACE (SAC COUPLER)

The STAR B data channel interface provides the connection between an access to SBU core and a STAR data channel B end. The B end of the STAR data channel is the controlling end. Normally, the B end is connected to a STAR data channel provided by the SAC of a STAR computer. The B end controls transfers, specifies addresses for the A end, and handles fault conditions.

60405000 C 1-19

NOTES: INTF = INTERFACE

SAC CHAN = STORAGE ACCESS CONTROL CHANNEL

Figure 1-17. Station Buffer Unit Functional Block Diagram

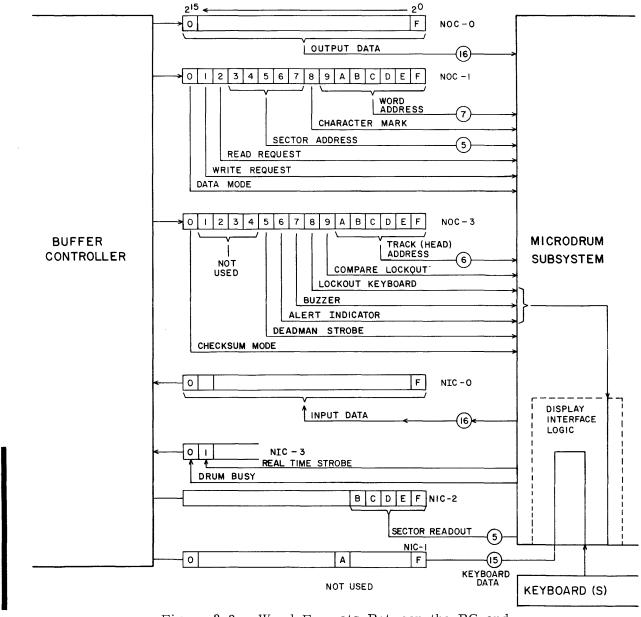

#### NORMAL CHANNEL INTERFACE

The normal channel interface logic provides a connection in the SBU between the SCU buffer controller normal channel bits and the various interface logic blocks in the SBU. The normal channel bits are used to transmit data, control information to the SBU interfaces, and read in status bits from the SBU interfaces.

This logic block interfaces six 16-bit BC normal channels, three input channels, and three output channels. It contains transmitters, receivers, data fanin and fanout logic, and a decoding section.

#### CORE CONTROL

The core control logic provides 12 access channels to eight modules of core memory having a total of 32,768 16-bit words of memory. Core memory is phased between modules, each module having independent read/write capability. The maximum memory reference rate is eight references per full memory scan of 1.1 microsecond. The core control logic determines channel priorities, increments channel addresses, checks for page boundaries, controls transfer of data and addresses to memory modules, and provides external timing signals.

### I/O INTERFACES

Various types of I/O interfaces are used to enable the transfer of data to or from peripheral devices and an HLP or between second-level stations having B interfaces and an HLP. With one exception (the network trunk interface) all I/O interfaces are controlled by the BC in the SCU and provide status conditions to the BC upon request.

60405000 C 1-21

#### STATION CONTROL UNIT

The SCU (Figure 1-18) is composed of a number of functionally related devices described in the order listed.

- Buffer controller and 1.1-microsecond memory

- Normal channels

- Normal channel interface

- SCU gate

- STAR B data channel interface (SBU coupler A/B)

- Drum/display logic, keyboard, and microdrum

#### **BUFFER CONTROLLER**

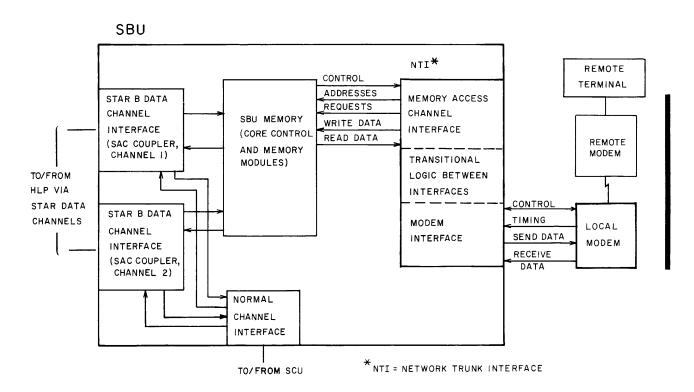

The BC is the primary control element of any station. It is an internally programmed parallel mode, digital computer having 4096 16-bit words of core memory with a cycle time of 1.1 microseconds. The core memory is expandable to 8K words. The instruction set of the BC was specifically chosen to be compatible with peripheral device-related tasks. The BC provides one 16-bit parallel block transfer channel for high speed data transfer. It also provides up to 512 individually programmed normal channel lines for lower speed data transfer and for peripheral device and station control.

An optional 8K semiconductor memory with a 200-nanosecond cycle time is available in place of the standard 1.1 microsecond core memory in the STAR station control units but is software supported only in the paging and disk stations.

#### NORMAL CHANNELS

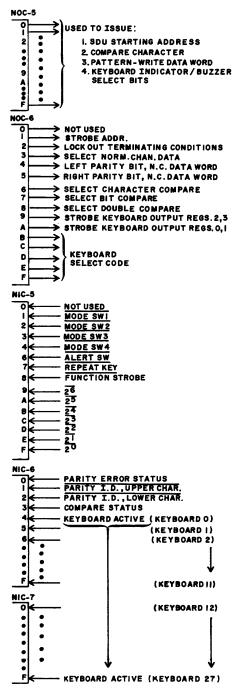

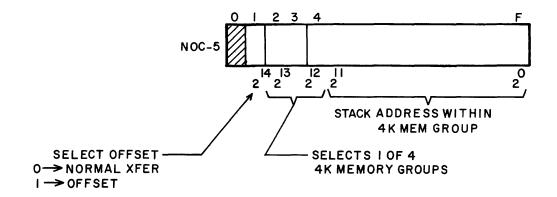

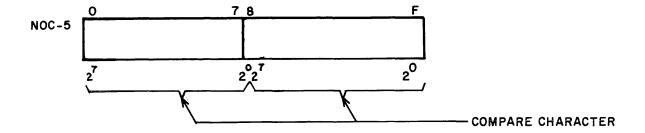

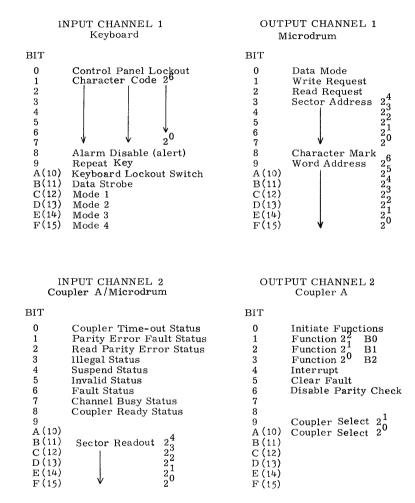

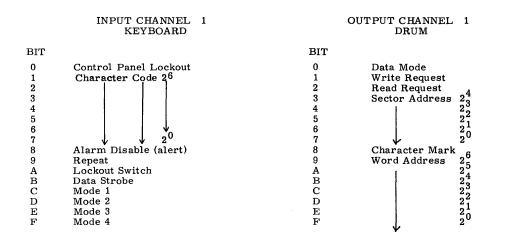

The SCU contains eight normal input channels and eight normal output channels, each of which is 16 bits wide. Channels 0 through 4 are used for the transfer of data and control functions between the programmable elements of the SBU and SCU. Channels 5 through 7 are used for similar functions (data and control) between the various I/O SBU interfaces and the SCU. All normal channel bit assignments for all channels appear in appendix A of this manual.

1-22 60405000 B

The 7000 I/O interface provides a stacking feature which allows starting and terminating addresses to be held until needed so the SCU can be free to complete more important control functions.

#### DRUM STORAGE UNIT

The DSU used in the drum station is a modified version of the CDC standard 865 DSU. The DSU provides the I/O channel with 12-head parallel format accessibility and a standard storage interface. The DSU uses 768 data tracks and four control tracks in the process of accomplishing its storage function. Two of the control tracks are used as master tracks; one is used for clock pulses and one for index marks. The remaining two are spares. The data heads are organized into 64 head groups with 12 read/write heads per group. Data bits are recorded on the drum via the phase modulation method at a clock rate of 2 megabits per second.

## HIGH CAPACITY DISK (HCD) STATION

The HCD station (Figure 1-16) provides an extension of mass memory for higher level computer storage. The SBU in this station contains 32K bits of storage. Each 7000 I/O channel interface within the SBU is connected to a separate controller. Each 7000 interface has two channels, one for transmitting function codes and receiving status and one for handling data. Up to a total of four 819 disk files are available by option for connection to a mass storage controller. A second SBU is also available by option and is connected with a disk file subsystem as illustrated in Figure 1-16. The mass storage controller and one 819 disk file are also supplied with the optional SBU.

#### STATION FUNCTIONAL OPERATION

The SBU in an HCD station receives functions from an HLP. Depending on the function, the SCU initiates operation of the STAR B interface to send or receive data from the HLP. Data is transferred in page increments, each page having 2048 hexadecimal words. As applied to STAR HCD stations, each sector of the 819 disk file contains 2064 words; the first 16 are software header and the remaining 2048 are data. After data is stored in SBU core memory, the SCU initiates operation of one of the 7000 I/O

60405000 C 1-29

interfaces to transfer a page of data to the disk itself. The disk's surface is divided into one-page increments so that one page of data from memory may be stored on a one-page sector on the disk. When the HLP requests data, the SCU commands the disk to send data to SBU memory via a 7000 I/O interface. Once data is in SBU memory, the SCU initiates an operation to transfer the data from SBU memory to the HLP via a STAR B interface. The normal channel interface in the SBU provides the path used by the SCU to control the various SBU interfaces. In system configurations requiring two SBUs and one SCU, normal channels 8, 9, and A are used for the second SBU interfaces and are defined as normal channels 5, 6, and 7, respectively.

The HCD station interfaces one or two disk file subsystems via 7000 I/O channel interfaces in the SBU. The description given for the SBU in the drum station also applies to the HCD station except that the HCD station does not use an index compare operation. The SCU in the HCD station performs the same general functions as the SCU in the drum station. However, the HCD station SCU uses the 200-nanosecond memory. Components of the HCD station are as follows:

SBU (optional SBU identical)

STAR A data channel interface (SCU coupler)

STAR B data channel interface (SAC coupler; channels 1 and 2)

Normal channel interface

Core control

1.1-microsecond memory (32K)

7000 I/O channel interfaces (channels 0 and 1)

### SCU

Buffer controller and 200-nanosecond memory (8K)

Normal channel interface

SCU gate

Block transfer channel

STAR B data channel interface (SBU couplers A and B)

Drum/display logic, keyboard, and microdrum

- Portable maintenance console

- 819 disk file

1-30 60405000 C

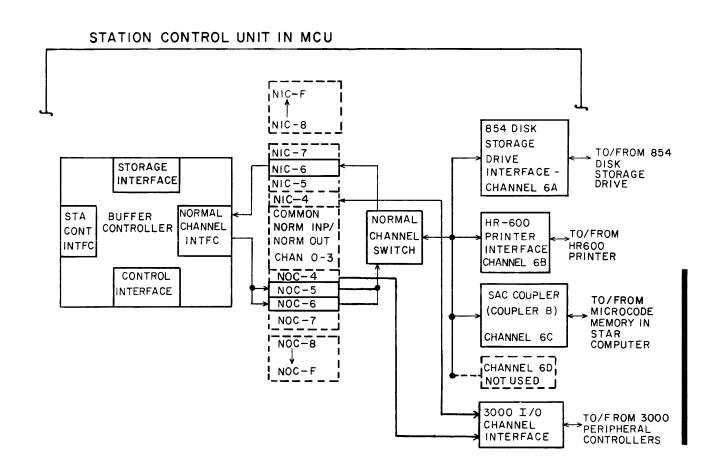

#### STAR-100 MAINTENANCE CONTROL UNIT

The STAR-100 maintenance control unit (Figure 1-14) consists primarily of the basic SCU which provides two SAC channel couplers to the central memory of a STAR-100 computer. The SCU also contains a special control interface which is connected to multiple access lines to and from the computer's mainframe. These lines serve as the means for measuring and monitoring functions of the STAR-100 Computer. The maintenance control unit also has a 3000 I/O channel interface, line printer interface, and a disk storage drive interface. A listing of the maintenance control unit's major components is as follows:

- STAR B data channel interface (SAC couplers; channels 1 and 2)

- Special control interface

- Buffer controller

- 3000 I/O channel interface

- 854 disk storage drive interface

- Line printer interface

- Normal channel interface

- Portable maintenance console (external to MCU)

### STATION FUNCTIONAL OPERATION

The two SAC coupler interfaces and the special control interface allow the maintenance control unit to regulate information flow, control pulses, and monitor performance of the STAR-100 Computer. The maintenance control unit provides system deadstart capability via the portable maintenance console and system monitoring. The three general modes of operation relative to maintenance control unit/computer program functions are:

- Operation of a computer diagnostic maintenance program used to locate faults and malfunctions within the maintenance control unit.

- Running diagnostic routines on the computer. The maintenance control unit loads diagnostics into the computer via the portable maintenance console, controls and monitors operations of the diagnostics, and indicates the results of the tests on either the line printer or other appropriate peripheral device.

60405000 B

• The maintenance control unit loads the program into the computer via the portable maintenance console and controls and monitors its operation. In this mode of operation, the maintenance control unit is responsible for autoloading the CPU and the BC of first-level stations, running on-line diagnostics, and restarting the CPU.

A special control interface connects to the microcode memory of the STAR-100 Computer. This interface provides the maintenance control unit with the ability to load and store microcode and to load microcode diagnostic routines. The interface also provides control to run the routines under maintenance control unit control.

#### PERIPHERAL EQUIPMENT

Three types of interfaces are supplied with the MCU for connecting to 3000 peripheral controllers, to a disk storage driver interface, and to a line printer interface. The 854 DSD interface accommodates up to four disk drives. The line printer interface services one line printer.

1-46 60405000 C

#### **844 DISK STORAGE UNIT**

The 844 disk storage unit, used in several of the peripheral stations, has a storage capacity of 755 million bits grouped in three sectors per track, with each disk surface having a total of 404 usable tracks. The disk rotates at 3600 rpm, and head positioning time over the recording surfaces averages between 10 and 55 milliseconds. The 844 utilizes 19 read/write heads and one track-servo head for recording on its 19 disk surfaces (top of the top disk and bottom of the bottom disk are protective nonrecording surfaces). Data recording rate is 6.8 million bits per second. The 844 uses the 881 disk pack as its recording medium.

### **854 DISK STORAGE DRIVE**

The 854 disk storage drive, used with the STAR-100 or STAR-65 maintenance control unit, has a storage capacity of  $53.4 \times 10^6$  data bits. The disk pack recording surfaces rotate at 2400 rpm. The data recording rate is  $1.25 \times 10^6$  data bits per second. Each of the ten disk recording surfaces is subdivided into 200 tracks, thereby providing a total of 2000 tracks for the unit. Head positioning time of the single access mechanism is in the range of 24 to 135 milliseconds.

### 865 DRUM STORAGE UNIT

The drum storage unit is a model 865 modified to be compatible with a 7000 I/O channel and the 7000 interfaces in the SBUs of the paging (drum) and STAR-100 service stations. It is an electromechanical recording drum having a total storage capacity of  $46.1 \times 10^6$  bits. The drum is addressable in sectors of quarter or full pages. Refer to Table 1-2 for sector data bit capacity. It rotates at 1800 rpm and uses 12 parallel heads in any one of 64 head groups to cover 768 data tracks.

### HIGH CAPACITY DISK (HCD) FILE SUBSYSTEM

The high capacity disk (819 HCD) file subsystem used with the HCD station consists of a mass controller and a high capacity disk. The controller contains the logic for controlling operations between the HCD file and a 7000 I/O channel in an SBU. The HCD file has an operational capacity of over 2.1 billion bits when used in a sectored format of 16 sectors per track, 10 head addresses per cylinder, and 404 cylinders per drive. Head positioning time is an average of 50 milliseconds and rotates at 3600 rpm. The data transfer rate is 38.7 million bits per second. Table 1-2 lists pertinent characteristics of the HCD file subsystem.

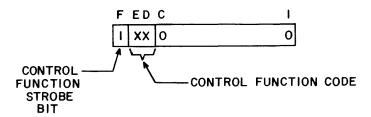

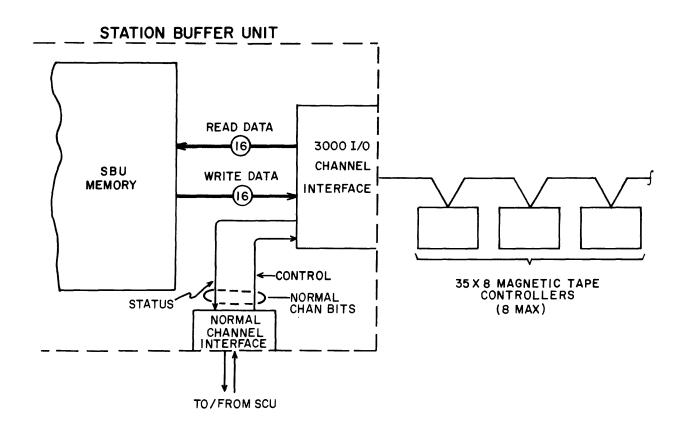

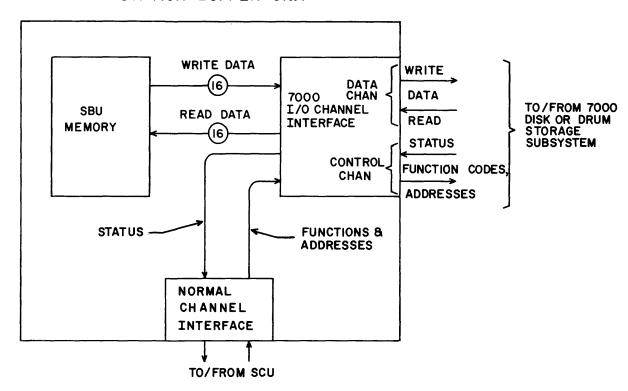

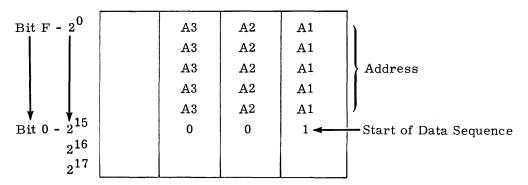

60405000 C 1-57