60256000

# CONTROL DATA® STAR-100 COMPUTER

HARDWARE REFERENCE MANUAL

#### COMPUTER INSTRUCTION INDEX

| Inst.<br>Code    | Page<br>No. | Inst.<br>Code | Page<br>No. | Inst.<br>Code   | Page<br>No.       | Inst.<br>Code | Page<br>No. | Inst.<br>Code  | Page<br>No.   |

|------------------|-------------|---------------|-------------|-----------------|-------------------|---------------|-------------|----------------|---------------|

| 00               | 6-235       | 34            | 6-31        | 67              | 6-35              | 99            | 6-70        | D <b>0</b>     | 6-102         |

| 04               | 6-231       | 35            | 6-54        | 68              | 6-34              | 9A            | 6-70        | D1             | 6-100         |

| 06               | 6-233       | 36            | 6-54        | 69              | 6-34              | 9B            | 6-75        | D4             | 6-102         |

| 08               | 6-235       | 37            | 6-188       | 6B              | 6-34              | 9C            | 6-77        | D5             | 6-100         |

| 09               | 6-55        | 38            | 6-29        | 6C              | 6-34              | †A0           | 6-89        | †† D6          | 6-158         |

| 0A               | 6-238       | <b>3</b> 9    | 6-190       | 6D              | 6-32              | †A1           | 6-89        | †††D7          | 6-166         |

| 0C               | 6-236       | 3A            | 6-190       | 6E              | 6 <del>-</del> 33 | †A2           | 6-89        | †D8            | 6-214         |

| 0D               | 6-236       | 3B            | 6-51        | 6F              | 6-34              | †A4           | 6-89        | †D9            | 6-214         |

| 0E               | 6-236       | 3C            | 6-187       | 70              | 6-35              | †A5           | 6-89        | DA             | 6-97          |

| 0F               | 6-237       | 3D            | 6-187       | 71              | 6-35              | †A6           | 6-89        | DB             | 6-98          |

| 10               | 6-39        | 3E            | 6-27        | 72              | 6-35              | †A8           | 6-91        | DC             | 6-116         |

| 11               | 6-39        | 3F            | 6-27        | 73              | 6-39              | †A9           | 6-91        | DD             | 6-205         |

| 12               | 6-188       | 40            | 6-34        | 74              | 6-44              | †AB           | 6-91        | DE             | 6-105         |

| 13               | 6-188       | 41            | 6-34        | 75              | 6-44              | †AC           | 6-91        | DF             | 6-108         |

| 14               | 6-197       | 42            | 6-34        | 76              | 6-39              | †AF           | 6-91        | E0             | 6-127         |

| 15               | 6-199       | 44            | 6-34        | 77              | 6-39              | B0            | 6-57        | E1             | 6-127         |

| 16               | 6-199       | 45            | 6-34        | 78              | 6-35              | B1            | 6-57        | E2             | 6-127         |

| 17               | 6-203       | 46            | 6-34        | 79              | 6-35              | B2            | 6-57        | E3             | 6-127         |

| 18               | 6-221       | 48            | 6-34        | 7A              | 6-35              | В3            | 6-57        | E4             | 6-147         |

| 19               | 6-224       | 49            | 6-34        | 7B              | 6-38              | В4            | 6-57        | E5             | 6-147         |

| 1A               | 6-228       | 4B            | 6-34        | 7C              | 6-39              | B5            | 6-57        | E6             | 6-143         |

| 1B               | 6-228       | 4C            | 6-34        | 7D              | 6-189             | B6            | 6-59        | E7             | 6-143         |

| 1C               | 6-228       | 4D            | 6-27        | <b>7</b> E      | 6-188             | B7            | 6-114       | E8             | 6-182         |

| 1D               | 6-228       | 4E            | 6-27        | <b>7</b> F      | 6-188             | B8            | 6-103       | E9             | 6-182         |

| 1 E              | 6-229       | 4F            | 6-34        | <del>†</del> 80 | 6-68              | B9            | 6-216       | EA             | 6-153         |

| 1 F              | 6-231       | 50            | 6-35        | <b>†</b> 81     | 6-68              | BA            | 6-111       | EB             | 6-168         |

| 20               | 6-47        | 51            | 6-35        | †82             | 6-68              | BB            | 6-190       | EC             | 6-130         |

| 21               | 6-47        | 52            | 6-35        | 83              | 6-69              | BC            | 6-191       | ED             | 6-130         |

| 22               | 6-47        | 53            | 6-39        | <b>†</b> 84     | 6-68              | BD            | 6-195       | <b>†</b> †† EE | 6-162         |

| 23               | 6-47        | 54            | 6-44        | <b>†</b> 85     | 6-68              | BE            | 6-28        | tt EF          | 6-165         |

| 24               | 6-47        | 55            | 6-44        | <u>†</u> 86     | 6-68              | BF            | 6-28        | F0             | 6-184         |

| 25               | 6-47        | 58            | 6-35        | 87              | 6-69              | C0            | 6-94        | F1             | 6-184         |

| 26               | 6-47        | 59            | 6-35        | <del>†</del> 88 | 6-68              | C1            | 6-94        | F2             | <b>6-</b> 184 |

| 27               | 6-47        | 5A            | 6-35        | <b>†</b> 89     | 6-68              | C2            | 6-94        | F3             | 6-184         |

| 28               | 6-224       | 5B            | 6-38        | <b>†</b> 8B     | 6-68              | C3            | 6-94        | F4             | 6-184         |

| <b>2</b> 9       | 6-224       | 5C            | 6-39        | †8C             | 6-68              | C4            | 6-208       | F5             | 6-184         |

| 2A               | 6-45        | 5D            | 6-39        | †8F             | 6-68              | C5            | 6-208       | F6             | 6-184         |

| $^{2\mathrm{B}}$ | 6-45        | 5E            | 6-188       | 9 <b>0</b>      | 6-70              | C6            | 6-208       | F7             | 6-184         |

| 2C               | 6-30        | 5F            | 6-188       | 91              | 6-70              | C7            | 6-208       | <u>†††</u> F8  | 6-150         |

| 2D               | 6-30        | 60            | 6-34        | 92              | 6-70              | C8            | 6-211       | <b>†††</b> F9  | 6-150         |

| 2E               | 6-30        | 61            | 6-34        | <b>†</b> 93     | 6-77              | C9            | 6-211       | FA             | 6-146         |

| 2F               | 6-48        | 62            | 6-34        | 94              | 6-81              | CA            | 6-211       | FB             | 6-132         |

| 30               | 6-30        | 63            | 6-35        | 95              | 6-81              | СВ            | 6-211       | FC             | 6-132         |

| 31               | 6-54        | 64            | 6-34        | 9 <b>6</b>      | 6-77              | CD            | 6-28        | †††FD          | 6-155         |

| 32               | 6-51        | 65            | 6-34        | 97              | 6-77              | CE            | 6-28        | <b>†</b> FE    | 6-158         |

|                  |             |               | 6-34        |                 |                   | 1             |             | 1 11 1         |               |

*†*These instructions have sign control capability.

†Automatic index incrementing takes place on these instructions. (Refer to the individual instruction descriptions.)

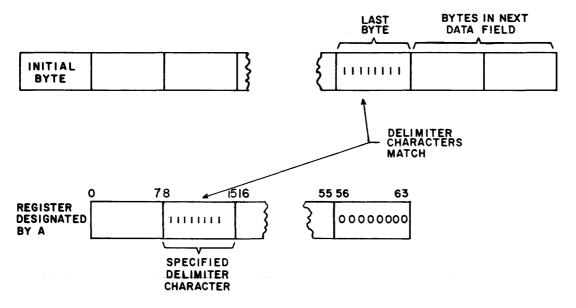

tht Delimeters may be used on these instructions, automatic index incrementing also takes place. (Refer to the individual instruction descriptions.) TITLE: STAR-100 Computer Hardware Reference Manual

PUBLICATION NO. 60256000 REVISION 09

DATE: 12-15-75

REASON FOR CHANGE:

This edition obsoletes all previous editions.

|                             | REVISION RECORD                                                                                 |

|-----------------------------|-------------------------------------------------------------------------------------------------|

| REVISION                    | DESCRIPTION                                                                                     |

| 01                          | Preliminary edition                                                                             |

| (9-2-70)                    |                                                                                                 |

| 02                          | Manual revised, pages 3-3, 3-8, 3-20, 3-21, 4-4, 4-20, 4-46, 4-59, 4-64, 4-68, 4-94, 4-95,      |

| (10-9-70)                   | 4-101, 4-176, A-9, B2 through 6, B-8, B-10 through 12, B-14 and B-18 revised.                   |

| 03                          | Manual revised. Technical and editorial corrections affecting pages: Front Cover, Title Page,   |

| (3-31-71)                   | Revision Record, iii, v, ix, 1-1 through 1-3, 2-1 through 2-4, 3-3, 3-4, 3-8, 3-14, 3-16, 3-17, |

|                             | 3-19, 3-20, 3-33, 4-1, 4-2, 4-4 through 4-6, 4-9 through 4-25, 4-28, 4-30 through 4-33, 4-37    |

|                             | through 4-44, 4-46, 4-49 through 4-52, 4-54 through 4-57, 4-59, 4-60, 4-62 through 4-67, 4-71,  |

|                             | 4-73, 4-75, 4-76, 4-77, 4-79, 4-82 through 4-89, 4-91, 4-92, 4-97, 4-98, 4-100 through 4-102,   |

|                             | 4-104, 4-106, 4-107, 4-113, 4-117, 4-119, 4-121, 4-122, 4-124 through 4-126, 4-128, 4-131       |

|                             | through 4-135, 4-139 through 4-141, 4-144, 4-145, 4-148, 4-150, 4-157, 4-159, 4-161, 4-163      |

|                             | through 4-171, 4-174, 4-177, 4-180 through 4-182, 4-191, 4-192, 4-197, 4-199, 4-202, 4-214      |

|                             | through 4-216, 4-220, 4-224 through 4-227, 4-229, 4-235 through 4-238, 6-1 through 6-4, 6-6,    |

|                             | 6-7, A-2, A-4, A-7, B-1 through B-3, B-6, B-7, B-11, B-12, B-18 and Comment Sheet.              |

| 04                          | Manual revised.                                                                                 |

| (8-31-71)                   |                                                                                                 |

| 05                          | Manual revised, This edition obsoletes all previous editions.                                   |

| (5-1-73)                    |                                                                                                 |

| 06                          | Manual revised. This edition obsoletes all previous editions.                                   |

| (10-30-73)                  |                                                                                                 |

| 07                          | Manual revised. This edition obsoletes all previous editions.                                   |

| (5-1-74)                    |                                                                                                 |

| 08                          | Manual revised. This edition obsoletes all previous editions.                                   |

| (12-15-74)                  |                                                                                                 |

| 09                          | Manual revised. This edition obsoletes all previous editions.                                   |

| (12-15-75)                  |                                                                                                 |

|                             |                                                                                                 |

|                             |                                                                                                 |

|                             |                                                                                                 |

|                             |                                                                                                 |

|                             |                                                                                                 |

|                             |                                                                                                 |

|                             |                                                                                                 |

|                             |                                                                                                 |

|                             |                                                                                                 |

|                             |                                                                                                 |

|                             |                                                                                                 |

| Publication No.<br>60256000 |                                                                                                 |

© 1970, 1971, 1973, 1974, 1975 by Control Data Corporation Printed in the United States of America Address comments concerning this manual to:

Control Data Corporation Publications and Graphics Division 4201 North Lexington Avenue St. Paul, Minnesota 55112

or use Comment Sheet in the back of this manual.

## LIST OF EFFECTIVE PAGES

New features, as well as changes, deletions, and additions to information in this manual are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

| PAGE  | SFC <sup>†</sup> | REV      | PAGE | SFC <sup>†</sup> | REV |   | PAGE | SFC <sup>†</sup> | REV        | PAGE     | SFC <sup>†</sup> | REV        |

|-------|------------------|----------|------|------------------|-----|---|------|------------------|------------|----------|------------------|------------|

| Cover |                  | -        | 3-9  |                  | 08  |   | 4-10 |                  | 08         | 5-17     |                  | 09         |

| Title |                  |          | 3-10 |                  | 08  |   | 4-11 |                  | 08         | 5-18     |                  | 09         |

| Page  |                  | -        | 3-11 |                  | 08  |   | 4-12 |                  | 08         | 5-19     |                  | 08         |

| ii    |                  | 09       | 3-12 |                  | 08  |   | 4-13 |                  | 08         | 5-20     |                  | 09         |

| iii   |                  | 09       | 3-13 |                  | 08  |   | 4-14 |                  | 08         | 5-21     |                  | 09         |

| iv    |                  | 09       | 3-14 |                  | 08  |   | 4-15 |                  | 08         | 5-22     |                  | 09         |

| v     |                  | 09       | 3-15 |                  | 08  |   | 4-16 |                  | 09         | 5-23     |                  | 08         |

| vii   |                  | 09       | 3-16 |                  | 08  |   | 4-17 |                  | 08         | 5-24     |                  | 09         |

| viii  |                  | 09       | 3-17 |                  | 08  |   | 4-18 |                  | 08         | 5-25     |                  | 08         |

| ix    |                  | 09       | 3-18 |                  | 08  |   | 4-19 |                  | 08         | 5-26     |                  | 08         |

| x     |                  | 08       | 3-19 |                  | 08  |   | 4-20 |                  | 08         | 5-27     |                  | 09         |

| xi    |                  | 08       | 3-20 |                  | 08  |   | 4-21 |                  | 08         | 5-28     | ļ                | 08         |

| xii   |                  | 09       | 3-21 |                  | 08  |   | 4-22 |                  | 08         | 5-29     |                  | 09         |

| xiii  |                  | 09       | 3-22 |                  | 08  |   | 4-23 |                  | 08         | 5-30     |                  | 09         |

| xiv   |                  | 09       | 3-23 |                  | 08  |   | 4-24 |                  | 08         | 5-31     |                  | <b>0</b> 9 |

| XV    |                  | 09       | 3-24 |                  | 08  |   | 4-25 |                  | 09         | 5-32     |                  | 08         |

| xvi   |                  | 09       | 3-25 |                  | 08  |   | 4-26 |                  | 09         | 5-33     |                  | 08         |

| xvii  |                  | 09       | 3-26 |                  | 08  |   | 4-27 |                  | 09         | 5-34     |                  | 08         |

| xviii |                  | 09       | 3-27 |                  | 08  |   | 4-28 |                  | 09         | 5-35     |                  | 08         |

| xix   |                  | 09       | 3-28 |                  | 08  |   | 4-29 |                  | 09         | 5-36     |                  | 08         |

| XX    |                  | 09       | 3-29 |                  | 08  |   | 4-30 |                  | 09         | 5-37     |                  | 08         |

| xxi   |                  | 09       | 3-30 |                  | 08  |   | 4-31 |                  | 09         | 5-38     |                  | 08         |

| 1-1   |                  | 08       | 3-31 |                  | 08  |   | 4-32 |                  | 09         | 5-39     |                  | 09         |

| 1-2   |                  | 08       | 3-32 |                  | 09  |   | 4-33 |                  | 09         | 5-40     |                  | 09         |

| 1-3   |                  | 08       | 3-33 |                  | 08  |   | 5-1  |                  | 08         | 5-41     |                  | 09         |

| 1-4   |                  | 09       | 3-34 |                  | 08  |   | 5-2  |                  | 08         | 5-42     |                  | 09 .       |

| 2-1   |                  | 08       | 3-35 |                  | 08  |   | 5-3  |                  | 08         | 5-43     |                  | 09         |

| 2-2   | ļ                | 08       | 3-36 |                  | 08  |   | 5-4  | ł                | 08         | 5-44     |                  | 09         |

| 2-3   |                  | 08       | 3-37 |                  | 09  |   | 5-5  |                  | 08         | 6-1      |                  | 08         |

| 2-4   |                  | 08       | 3-38 |                  | 08  |   | 5-6  |                  | 08         | 6-2      |                  | 09         |

| 2-5   |                  | 08       | 3-39 |                  | 08  |   | 5-7  |                  | 08         | 6-3      |                  | 08         |

| 2-6   |                  | 08       | 4-1  |                  | 08  |   | 5-8  |                  | <b>0</b> 9 | 6-4      |                  | 08         |

| 2-7   |                  | 08       | 4-2  |                  | 09  |   | 5-9  | İ                | 09         | 6-5      |                  | 09         |

| 3-1   |                  | 08       | 4-3  |                  | 08  |   | 5-10 |                  | 08         | 6-6      |                  | 09         |

| 3-2   |                  | 08       | 4-4  |                  | 08  |   | 5-11 |                  | 08         | 6-7      |                  | 09         |

| 3-3   |                  | 08<br>00 | 4-5  |                  | 08  |   | 5-12 |                  | 09         | 6-8      |                  | 09         |

| 3-4   |                  | 09       | 4-6  |                  | 08  |   | 5-13 |                  | 08         | 6-9      |                  | 08         |

| 3-5   |                  | 08       | 4-7  |                  | 08  |   | 5-14 |                  | 08         | 6-10     | e.               | 08         |

| 3-6   |                  | 08       | 4-8  |                  | 08  |   | 5-15 |                  | 09         | 6-11     |                  | 09         |

| 3-7   |                  | 09       | 4-9  |                  | 08  | ļ | 5-16 |                  | 08         | <br>6-12 |                  | 09         |

| 3-8   | L                | 09       |      |                  |     | l |      |                  |            |          |                  |            |

**†SFC** Software Feature Change

AA 5935

| PAGE | SFC <sup>†</sup> | REV        |  | PAGE | SFC <sup>†</sup> | REV        | PAGE  | SFC <sup>†</sup> | REV        | PAGE  | SFC <sup>†</sup> | REV        |

|------|------------------|------------|--|------|------------------|------------|-------|------------------|------------|-------|------------------|------------|

| 6-13 |                  | 09         |  | 6-53 |                  | 09         | 6-93  |                  | 09         | 6-133 |                  | 09         |

| 6-14 |                  | 09         |  | 6-54 |                  | 09         | 6-94  |                  | 09         | 6-134 |                  | 09         |

| 6-15 |                  | 09         |  | 6-55 |                  | 09         | 6-95  |                  | 09         | 6-135 |                  | 09         |

| 6-16 |                  | 09         |  | 6-56 |                  | 09         | 6-96  |                  | <b>0</b> 9 | 6-136 |                  | <b>0</b> 9 |

| 6-17 |                  | 09         |  | 6-57 |                  | 09         | 6-97  |                  | 09         | 6-137 |                  | 09         |

| 6-18 |                  | 09         |  | 6-58 |                  | 09         | 6-98  |                  | 09         | 6-138 |                  | 09         |

| 6-19 |                  | 09         |  | 6-59 |                  | 09         | 6-99  |                  | 09         | 6-139 |                  | 09         |

| 6-20 |                  | 09         |  | 6-60 |                  | 09         | 6-100 |                  | <b>0</b> 9 | 6-140 |                  | 09         |

| 6-21 |                  | 09         |  | 6-61 |                  | 09         | 6-101 |                  | 09         | 6-141 |                  | 09         |

| 6-22 |                  | 09         |  | 6-62 |                  | 09         | 6-102 |                  | 09         | 6-142 |                  | 09         |

| 6-23 |                  | 09         |  | 6-63 |                  | 09         | 6-103 |                  | <b>0</b> 9 | 6-143 |                  | 09         |

| 6-24 |                  | 09         |  | 6-64 |                  | <b>0</b> 9 | 6-104 |                  | 09         | 6-144 |                  | 09         |

| 6-25 |                  | 09         |  | 6-65 |                  | 09         | 6-105 |                  | 09         | 6-145 |                  | 09         |

| 6-26 |                  | 08         |  | 6-66 |                  | 09         | 6-106 |                  | 09         | 6-146 |                  | 09         |

| 6-27 |                  | 08         |  | 6-67 |                  | 09         | 6-107 |                  | 09         | 6-147 |                  | 09         |

| 6-28 |                  | 08         |  | 6-68 |                  | 09         | 6-108 |                  | 09         | 6-148 |                  | 09         |

| 6-29 |                  | 08         |  | 6-69 |                  | 09         | 6-109 |                  | 09         | 6-149 |                  | 09         |

| 6-30 |                  | 08         |  | 6-70 |                  | 09         | 6-110 |                  | 09         | 6-150 |                  | 09         |

| 6-31 |                  | 08         |  | 6-71 |                  | 09         | 6-111 |                  | 09         | 6-151 |                  | 09         |

| 6-32 |                  | 08         |  | 6-72 |                  | 09         | 6-112 |                  | 09         | 6-152 |                  | 09         |

| 6-33 |                  | 08         |  | 6-73 |                  | <b>0</b> 9 | 6-113 |                  | 09         | 6-153 |                  | 09         |

| 6-34 |                  | 09         |  | 6-74 |                  | 09         | 6-114 |                  | 09         | 6-154 |                  | 09         |

| 6-35 |                  | 08         |  | 6-75 |                  | 09         | 6-115 |                  | 09         | 6-155 |                  | 09         |

| 6-36 |                  | 08         |  | 6-76 |                  | 09         | 6-116 |                  | 09         | 6-156 |                  | 09         |

| 6-37 |                  | 08         |  | 6-77 |                  | 09         | 6-117 |                  | 09         | 6-157 |                  | <b>0</b> 9 |

| 6-38 |                  | 08         |  | 6-78 |                  | 09         | 6-118 |                  | 09         | 6-158 |                  | 09         |

| 6-39 |                  | 08         |  | 6-79 |                  | 09         | 6-119 |                  | 09         | 6-159 |                  | 09         |

| 6-40 |                  | 08         |  | 6-80 |                  | 09         | 6-120 |                  | 09         | 6-160 | ĺ                | 09         |

| 6-41 |                  | 08         |  | 6-81 |                  | 09         | 6-121 |                  | 09         | 6-161 |                  | 09         |

| 6-42 |                  | 08         |  | 6-82 |                  | 09         | 6-122 |                  | 09         | 6-162 |                  | 09         |

| 6-43 | 1                | 08         |  | 6-83 |                  | 09         | 6-123 |                  | 09         | 6-163 |                  | 09         |

| 6-44 |                  | 08         |  | 6-84 |                  | 09         | 6-124 |                  | 09         | 6-164 |                  | 09         |

| 6-45 |                  | 08         |  | 6-85 |                  | 09         | 6-125 |                  | 09         | 6-165 |                  | 09         |

| 6-46 |                  | 08         |  | 6-86 |                  | 09         | 6-126 |                  | 09         | 6-166 |                  | 09         |

| 6-47 |                  | 09         |  | 6-87 |                  | 09         | 6-127 |                  | 09         | 6-167 |                  | 09         |

| 6-48 |                  | 09         |  | 6-88 |                  | 09         | 6-128 |                  | 09         | 6-168 |                  | <b>0</b> 9 |

| 6-49 |                  | 09         |  | 6-89 |                  | 09         | 6-129 |                  | <b>0</b> 9 | 6-169 | ł                | 09         |

| 6-50 | l                | <b>0</b> 9 |  | 6-90 | ]                | 09         | 6-130 |                  | 09         | 6-170 |                  | 09         |

| 6-51 |                  | 09         |  | 6-91 |                  | 09         | 6-131 |                  | 09         | 6-171 |                  | 09         |

| 6-52 |                  | 09         |  | 6-92 |                  | 09         | 6-132 |                  | 09         | 6-172 |                  | 09         |

|      | 1                | L          |  |      | L                | L          | L     |                  |            | L     | L                |            |

**†SFC Software Feature Change**

AA 5935

| PAGE  | SFC <sup>†</sup> | REV        | PAGE  | SFC $^{\dagger}$ | REV        | PAGE | SFC <sup>†</sup> | REV | PAGE               | SFC <sup>†</sup> | REV |

|-------|------------------|------------|-------|------------------|------------|------|------------------|-----|--------------------|------------------|-----|

| 6-173 |                  | 09         | 6-213 |                  | 09         | A-15 |                  | 08  | Comment            |                  |     |

| 6-174 |                  | 09         | 6-214 |                  | 09         | A-16 |                  | 08  | Sheet              |                  | -   |

| 6-175 |                  | 09         | 6-215 |                  | 09         | A-17 |                  | 08  | Return<br>Envelope |                  |     |

| 6-176 |                  | 09         | 6-216 |                  | 09         | A-18 |                  | 08  | Back               |                  |     |

| 6-177 |                  | 09         | 6-217 |                  | 09         | A-19 |                  | 08  | Cover              |                  | -   |

| 6-178 |                  | 09         | 6-218 |                  | 09         | B-1  |                  | 08  |                    |                  |     |

| 6-179 |                  | 09         | 6-219 |                  | 09         | B-2  |                  | 08  |                    |                  |     |

| 6-180 |                  | 09         | 6-220 |                  | 09         | В-3  |                  | 08  |                    |                  |     |

| 6-181 |                  | 09         | 6-221 |                  | 09         | B-4  |                  | 08  |                    |                  |     |

| 6-182 |                  | 09         | 6-222 |                  | 09         | В-5  |                  | 08  |                    |                  |     |

| 6-183 |                  | 09         | 6-223 |                  | 09         | В-6  |                  | 09  |                    |                  |     |

| 6-184 |                  | 09         | 6-224 |                  | 09         | В-7  |                  | 09  |                    |                  |     |

| 6-185 |                  | 09         | 6-225 |                  | 09         | В-8  |                  | 09  |                    |                  |     |

| 6-186 |                  | 09         | 6-226 |                  | 09         | в-9  |                  | 09  |                    |                  |     |

| 6-187 |                  | 09         | 6-227 |                  | 09         | B-10 |                  | 09  |                    |                  |     |

| 6-188 |                  | 09         | 6-228 |                  | 09         | B-11 |                  | 09  |                    |                  |     |

| 6-189 |                  | 09         | 6-229 |                  | 09         | B-12 |                  | 09  |                    |                  |     |

| 6-190 |                  | 09         | 6-230 |                  | 09         | B-13 |                  | 09  |                    |                  |     |

| 6-191 |                  | 09         | 6-231 |                  | 09         | B-14 |                  | 09  |                    |                  |     |

| 6-192 |                  | 09         | 6-232 |                  | 09         | B-15 |                  | 09  |                    |                  |     |

| 6-193 |                  | 09         | 6-233 |                  | 09         | B-16 |                  | 09  |                    |                  |     |

| 6-194 |                  | 09         | 6-234 |                  | 09         | B-17 |                  | 09  |                    |                  |     |

| 6-195 |                  | 09         | 6-235 |                  | <b>0</b> 9 | B-18 |                  | 09  |                    |                  |     |

| 6-196 |                  | 09         | 6-236 |                  | 09         | B-19 |                  | 09  |                    |                  |     |

| 6-197 |                  | 09         | 6-237 |                  | 09         | В-20 |                  | 09  |                    |                  |     |

| 6-198 |                  | 09         | 6-238 |                  | 09         | B-21 |                  | 09  |                    |                  |     |

| 6-199 |                  | 09         | A-1   |                  | 08         | B-22 |                  | 09  |                    |                  |     |

| 6-200 |                  | 09         | A-2   |                  | 08         | В-23 |                  | 09  |                    |                  |     |

| 6-201 |                  | 09         | A-3   |                  | 08         | B-24 |                  | 09  |                    |                  |     |

| 6-202 |                  | 09         | A-4   |                  | 08         | C-1  |                  | 09  |                    |                  |     |

| 6-203 |                  | 09         | A-5   |                  | 08         | C-2  |                  | 09  |                    |                  |     |

| 6-204 |                  | 09         | A-6   |                  | 08         | C-3  |                  | 09  |                    |                  |     |

| 6-205 |                  | 09         | A-7   |                  | 08         | C-4  |                  | 09  |                    |                  |     |

| 6-206 |                  | <b>0</b> 9 | A-8   |                  | 08         | C-5  |                  | 08  |                    |                  |     |

| 6-207 |                  | 09         | A-9   |                  | 08         | C-6  |                  | 09  |                    |                  |     |

| 6-208 |                  | 09         | A-10  |                  | 08         | C-7  |                  | 09  |                    |                  |     |

| 6-209 |                  | 09         | A-11  |                  | 08         | D-1  |                  | 08  |                    |                  |     |

| 6-210 |                  | 09         | A-12  |                  | 08         | D-2  |                  | 08  |                    |                  |     |

| 6-211 |                  | 09         | A-13  |                  | 08         | D-3  |                  | 08  |                    |                  |     |

| 6-212 |                  | 09         | A-14  |                  | 08         | D-4  |                  | 08  |                    |                  |     |

*†*SFC Software Feature Change

AA 5935

This manual contains hardware reference information for the CONTROL DATA® STAR-100 Computer.

All manuals applicable to the CDC STAR-100 Computer and associated equipment include the following.

| Control Data Publication                                                                      | Publication No. |

|-----------------------------------------------------------------------------------------------|-----------------|

| STAR-100 Computer Hardware Maintenance Manuals                                                |                 |

| General Description, Operation, Theory of Operation<br>Installation and Checkout, Maintenance | 60256100        |

| Memory and Storage Access Control<br>Block Diagrams                                           | 60430100        |

| Stream<br>Block Diagrams                                                                      | 60430200        |

| Floating Point<br>Block Diagrams                                                              | 60430300        |

| Power Diagrams                                                                                | 60433200        |

| Engineering Diagram Set                                                                       |                 |

| Memory<br>Logic Diagrams                                                                      | Not applicable  |

| Logic Diagrams<br>Storage Access Control<br>LA Panel                                          | Not applicable  |

| Logic Diagrams<br>Storage Access Control<br>LB Panel                                          | Not applicable  |

| Logic Diagrams<br>Storage Access Control<br>NA Panel                                          | Not applicable  |

| Logic Diagrams<br>Storage Access Control<br>NB Panel                                          | Not applicable  |

| Logic Diagrams<br>Storage Access Control                                                      |                 |

| KA Panel                                                                                      | Not applicable  |

| Control Data Publication                             | Publication No. |

|------------------------------------------------------|-----------------|

| Logic Diagrams<br>Storage Access Control<br>KB Panel | Not applicable  |

| Logic Diagrams<br>Stream<br>FA Panel                 | Not applicable  |

| Logic Diagrams<br>Stream<br>FB Panel                 | Not applicable  |

| Logic Diagrams<br>Stream<br>GA Panel                 | Not applicable  |

| Logic Diagrams<br>Stream<br>GB Panel                 | Not applicable  |

| Logic Diagrams<br>Stream<br>HA Panel                 | Not applicable  |

| Logic Diagrams<br>Stream<br>HB Panel                 | Not applicable  |

| Logic Diagrams<br>Stream<br>JA Panel                 | Not applicable  |

| Logic Diagrams<br>Stream<br>JB Panel                 | Not applicable  |

| Logic Diagrams<br>Stream<br>PA Panel                 | Not applicable  |

| Logic Diagrams<br>Stream<br>PB Panel                 | Not applicable  |

| Logic Diagrams<br>Floating Point<br>AA Panel         | Not applicable  |

| Logic Diagrams<br>Floating Point<br>AB Panel         | Not applicable  |

| Control Data Publication                                                                                         | Publication No.          |

|------------------------------------------------------------------------------------------------------------------|--------------------------|

| Logic Diagrams<br>Floating Point<br>BA Panel                                                                     | Not applicable           |

| Logic Diagrams<br>Floating Point<br>BB Panel                                                                     | Not applicable           |

| Logic Diagrams<br>Floating Point<br>CA Panel                                                                     | Not applicable           |

| Logic Diagrams<br>Floating Point<br>CB Panel                                                                     | Not applicable           |

| Logic Diagrams<br>Floating Point<br>DA Panel                                                                     | Not applicable           |

| Logic Diagrams<br>Floating Point<br>DB Panel                                                                     | Not applicable           |

| Logic Diagrams<br>Floating Point<br>EA Panel                                                                     | Not applicable           |

| Logic Diagrams<br>Floating Point<br>EB Panel                                                                     | Not applicable           |

| Logic Diagrams<br>Floating Point<br>KA Panel                                                                     | Not applicable           |

| STAR-100 Refrigeration System Customer<br>Engineering Manual                                                     | 60329800                 |

| Control Data Intebrid Circuits Manual                                                                            | 60201000                 |

| Control Data Motor-Generator Sets<br>Electric Machinery Volumes 1 and 2                                          | 60166800<br>and 60423100 |

| Control Data Large and Medium Scale Computer<br>Systems Site Preparation Manual<br>Section 1 General Information | 60275100                 |

| Control Data STAR-100 Computer System<br>Site Preparation Manual<br>Section 2 System Data                        | 60381600                 |

| Control Data Publication                                                  | P   | ublication No. |

|---------------------------------------------------------------------------|-----|----------------|

| STAR-100 Computer Hardware Reference Manual                               |     | 60256000       |

| STAR-100 Peripheral Stations Hardware<br>Reference Manual                 |     | 60405000       |

| STAR-100 Peripheral Stations Customer Engineering<br>Manual (Maintenance) |     | 60325300       |

| STAR-100 Peripheral Stations Customer Engineering<br>Manual (Diagrams)    |     |                |

| Station Buffer Unit Core Control                                          |     | 60382000       |

|                                                                           | and | 60406700       |

| Station Buffer Unit Interfaces                                            |     | 60382100       |

|                                                                           | and | 60406800       |

| Station Control Unit                                                      |     | 60362900       |

| Station Display Unit                                                      |     | 60382500       |

#### NOTE

These manuals are available on a controlled distribution basis only from:

Control Data Corporation STAR-100 Publications Distribution STAR-100 Development Support 4201 North Lexington Aye. Arden Hills, Minnesota 55112

## CONTENTS

#### 1. GENERAL DESCRIPTION

| General                  | 1-1 |

|--------------------------|-----|

| Computer Characteristics | 1-2 |

| Central Processor        | 1-3 |

| Magnetic Core Storage    | 1-3 |

| Input/Output             | 1-3 |

|                          |     |

### 2. MAGNETIC CORE STORAGE

| Des                            | cription                            | 2-1 |  |  |  |

|--------------------------------|-------------------------------------|-----|--|--|--|

| Stor                           | age Word                            | 2-2 |  |  |  |

| MCS Access and Control Signals |                                     |     |  |  |  |

|                                | Request                             | 2-4 |  |  |  |

|                                | Address                             | 2-4 |  |  |  |

|                                | Quarter Sword Address               | 2-5 |  |  |  |

|                                | Read Data                           | 2-5 |  |  |  |

|                                | Read Parity                         | 2-5 |  |  |  |

|                                | Write Data                          | 2-5 |  |  |  |

|                                | Write Parity                        | 2-6 |  |  |  |

|                                | Write Enable                        | 2-6 |  |  |  |

|                                | Split Cycle/Clear Data Register     | 2-6 |  |  |  |

|                                | Clock                               | 2-6 |  |  |  |

|                                | Master Clear                        | 2-6 |  |  |  |

| MCS                            | 5 Degradation                       | 2-7 |  |  |  |

|                                | 524K System Degradation             |     |  |  |  |

|                                | Options                             | 2-7 |  |  |  |

|                                | 1048K System Degradation<br>Options | 2-7 |  |  |  |

| 3.                             | CENTRAL PROCESSOR UNIT              |     |  |  |  |

| Des                            | cription                            | 3-1 |  |  |  |

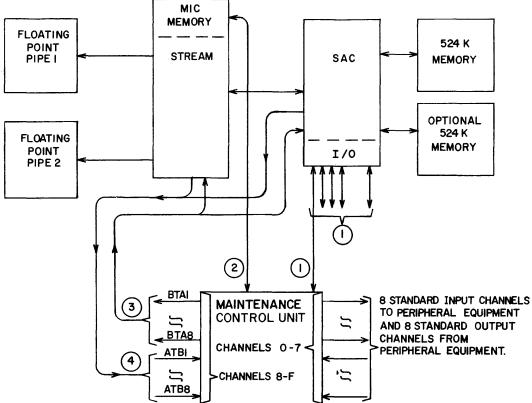

| Stor                           | age Access Control                  | 3-1 |  |  |  |

|                                | SAC Read Operations                 | 3-3 |  |  |  |

|                                | Memory Parity Fault                 | 3-3 |  |  |  |

|      | Par                | ity Fault Isolation                   | 3-5             |  |  |  |  |  |  |

|------|--------------------|---------------------------------------|-----------------|--|--|--|--|--|--|

|      | SAC Wri            | ite Operations                        | 3-5             |  |  |  |  |  |  |

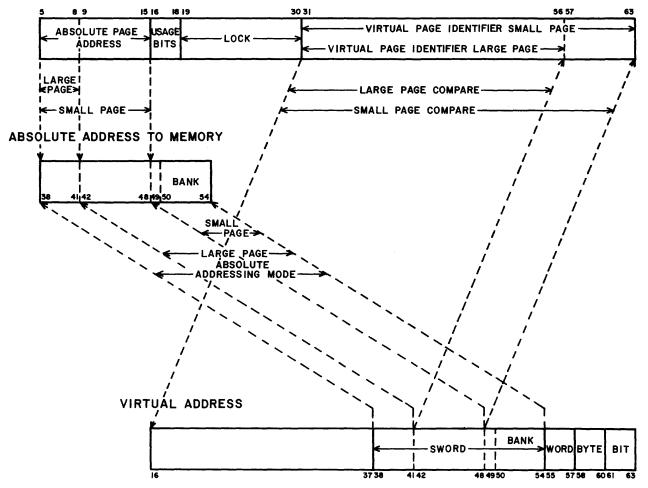

|      | Vir                | tual Address Mechanism                | 3-6             |  |  |  |  |  |  |

|      | MCS Page Sizes     |                                       |                 |  |  |  |  |  |  |

|      | Stor               | age Protect Features                  | 3-6             |  |  |  |  |  |  |

|      | Sear               | rching the Page Table                 | 3-7             |  |  |  |  |  |  |

|      |                    | Multiple-Match Fault                  | 3-11            |  |  |  |  |  |  |

|      |                    | Absolute Bounds Address               | 3-11            |  |  |  |  |  |  |

|      | Input/Ou           | itput Channels                        | 3-11            |  |  |  |  |  |  |

|      |                    | Assembly/Disassembly                  | 3-12            |  |  |  |  |  |  |

|      |                    | I/O Data                              | 3-13            |  |  |  |  |  |  |

|      |                    | I/O Addressing                        | 3-13            |  |  |  |  |  |  |

|      |                    | I/O Channel Priority                  | 3-16            |  |  |  |  |  |  |

|      |                    | I/O Channel Write<br>Lockout          | 3-17            |  |  |  |  |  |  |

|      | System             | Communication                         | 3-17            |  |  |  |  |  |  |

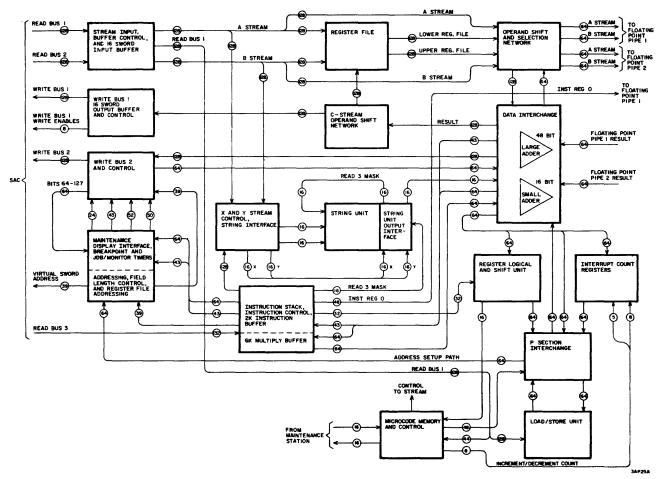

| Stre | am                 |                                       | 3-19            |  |  |  |  |  |  |

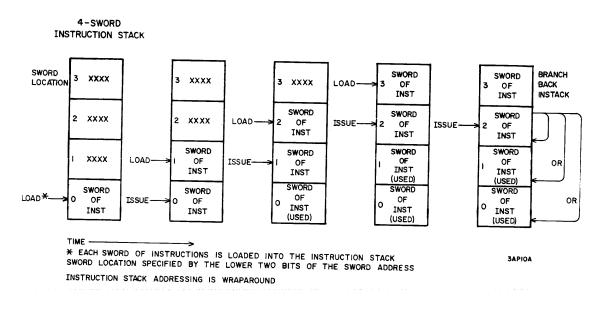

|      | Instruct           | ion Control                           | 3-19            |  |  |  |  |  |  |

|      | Address            | ing                                   | 3-22            |  |  |  |  |  |  |

|      | Stream             | Input and Buffer Control              | 3-23            |  |  |  |  |  |  |

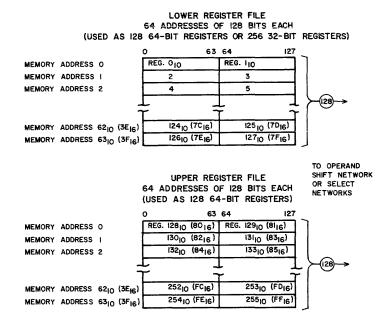

|      | Register           | r File                                | 3-23            |  |  |  |  |  |  |

|      | Operand            | Shift Network                         | 3-26            |  |  |  |  |  |  |

|      | Data Int           | erchange                              | 3-26            |  |  |  |  |  |  |

|      | C-Strea            | m Operand Shift Network               | 3-26            |  |  |  |  |  |  |

|      | Write B<br>Control | us 1 Output Buffer and                | 3-26            |  |  |  |  |  |  |

|      |                    | us 2 and Control                      | 3-26            |  |  |  |  |  |  |

|      | X-and Y-           | -Stream Control and<br>uput Interface | 3-27            |  |  |  |  |  |  |

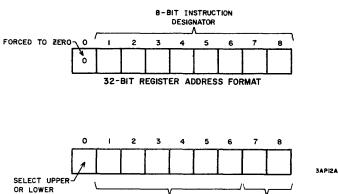

|      | String U           |                                       | 3-27            |  |  |  |  |  |  |

|      | -                  | t Control                             | 3-27            |  |  |  |  |  |  |

|      |                    | rical Instruction Control             | 3-27            |  |  |  |  |  |  |

|      | -                  | ary Arithmetic Control                | 3-27            |  |  |  |  |  |  |

|      |                    |                                       | · ·· ·· · · · · |  |  |  |  |  |  |

|             | Desired Arithmetic Control                        | 3-29         |                                                     |      |

|-------------|---------------------------------------------------|--------------|-----------------------------------------------------|------|

|             | Decimal Arithmetic Control                        | -            | Illegal Instruction in Monitor<br>Mode              | 5-2  |

|             | Miscellaneous Operations                          | 3-30<br>3-31 | Exchange from Job Mode to                           |      |

|             | Register Logical and Shift Unit                   | 3-31         | Monitor Mode                                        | 5-3  |

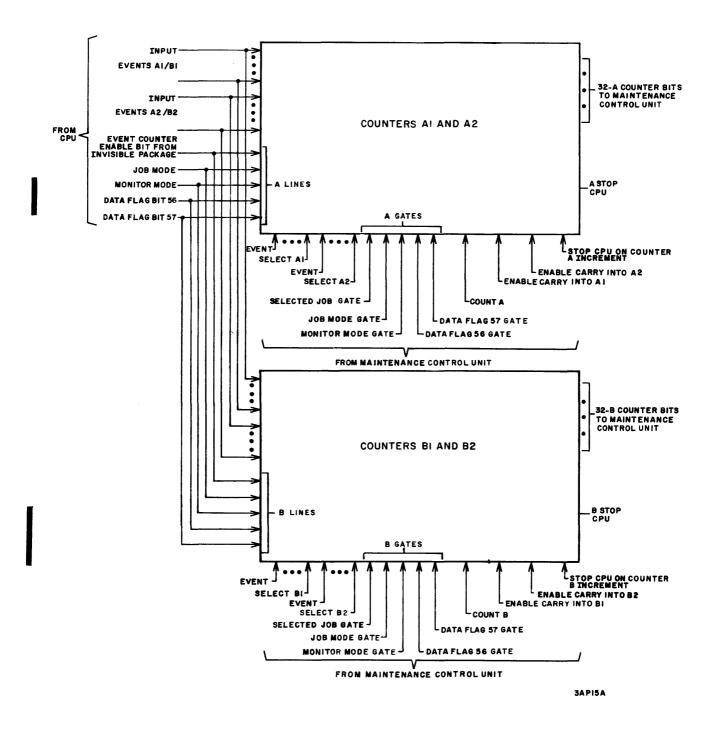

|             | Interrupt Counters                                | 3-31         | Interrupts                                          | 5-4  |

|             | P Section Interchange                             | 3-31         | Storage Access Interrupts                           | 5-4  |

|             | Load/Store Unit                                   | 3-31         | External Interrupts                                 | 5-6  |

|             | Microcode                                         | 3-32         | I/O Channel Interrupt Lines                         | 5-6  |

|             | MIC Operation                                     | 3-34         | Monitor Interval Timer Interrupt                    | 5-7  |

|             | MIC Interrupt                                     |              | Invisible Package                                   | 5-7  |

|             | MIC Parity                                        | 3-34         | Addressing Modes                                    | 5-10 |

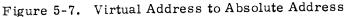

|             | Checkpoint                                        | 3-35         | Virtual Addressing                                  | 5-10 |

| -           | MIC Write Lockout                                 | 3-35         | Pages                                               | 5-10 |

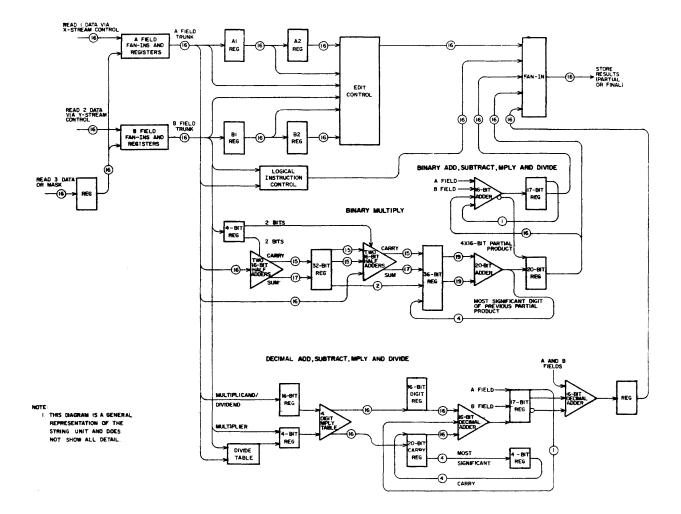

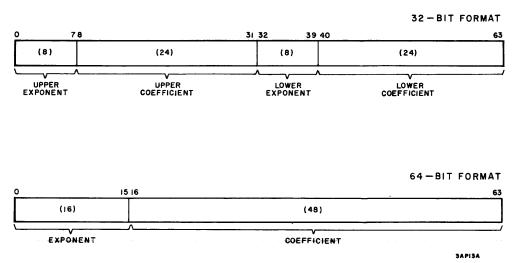

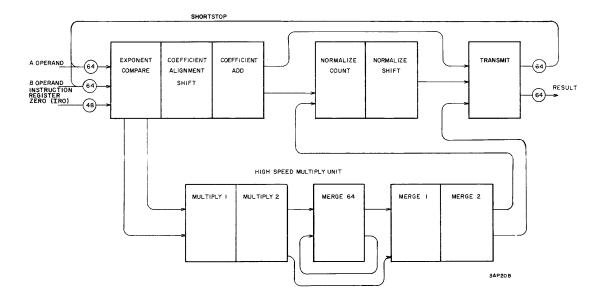

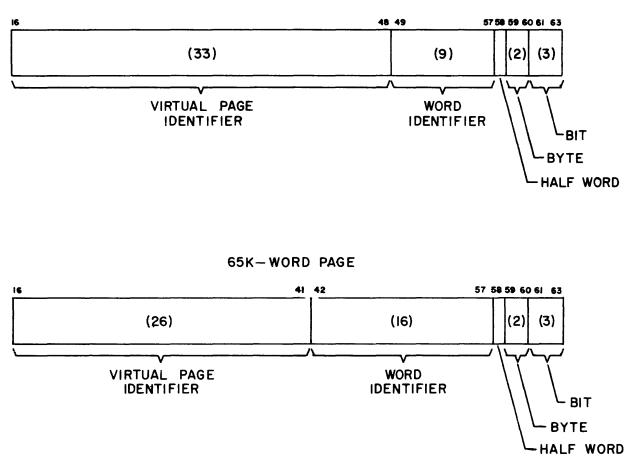

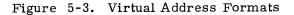

| F.10        | ating Point                                       | 3-35         | Virtual Address Format                              | 5-10 |

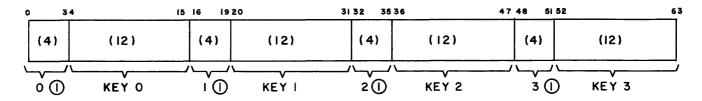

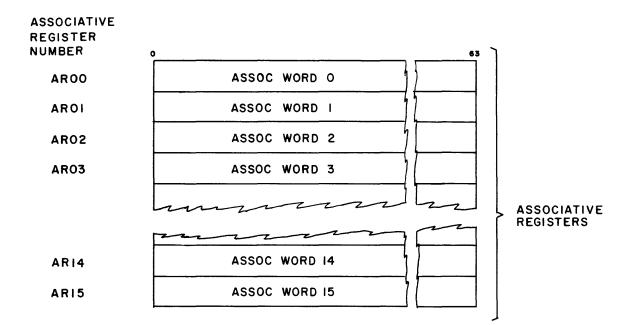

|             | Pipe 1                                            | 3-36<br>3-38 | Associative Words                                   | 5-12 |

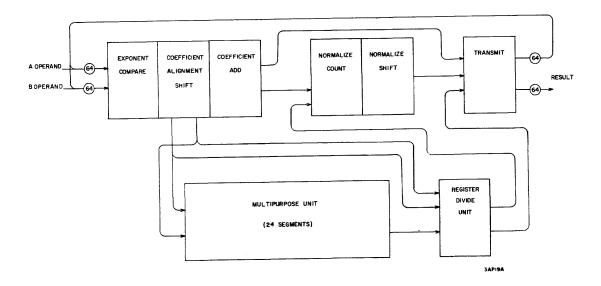

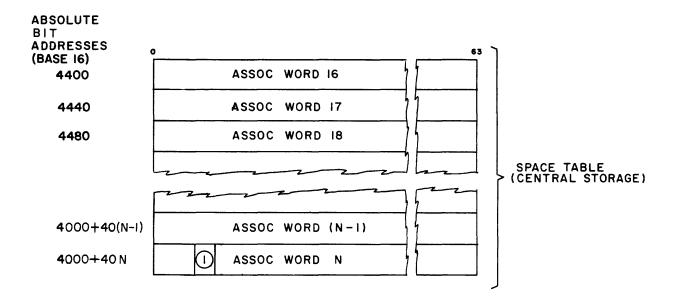

|             | Pipe 2                                            |              | Associative Registers                               | 5-14 |

|             | Register Divide                                   | 3-39         | Space Table                                         | 5-15 |

|             | Multipurpose                                      | 3-39         | Page Table                                          | 5-15 |

| 4           | MAINTENANCE CONTROL UNIT                          |              | <b>Operation of Virtual Address</b>                 | 5-17 |

| 4.          | MAINTENANCE CONTROL UNIT                          |              | Absolute Address                                    | 5-18 |

| Description |                                                   | 4-1          | <b>Real-</b> Time Counters                          | 5-19 |

| MC          | U Interfaces                                      | 4-3          | Free Running Clock Counter                          | 5-19 |

| MC          | U Monitoring                                      | 4-23         | Monitor Interval Timer                              | 5-19 |

|             | Display Registers                                 | 4-23         | Job Interval Timer                                  | 5-20 |

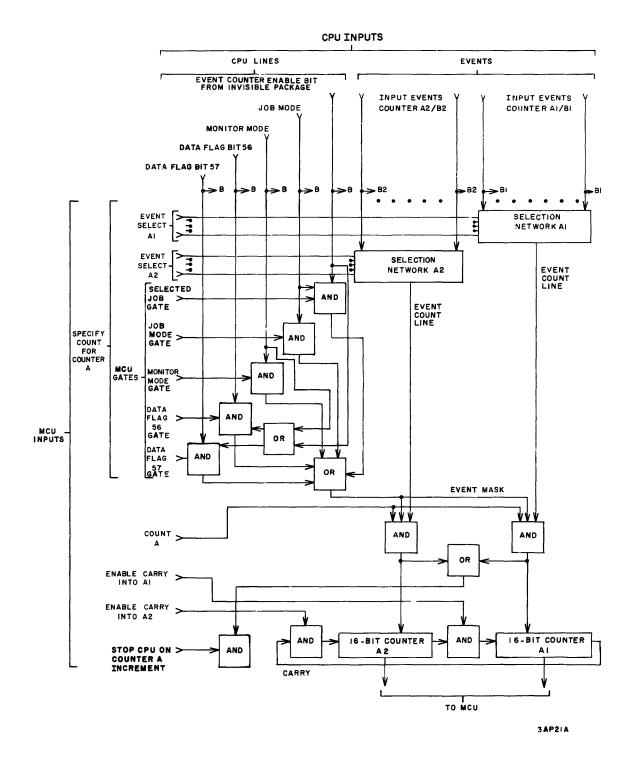

|             | Monitoring Counters                               | 4-25         | Register File                                       | 5-20 |

|             | Count Gates and CPU Lines                         | 4-30         | <b>Register File Restrictions</b>                   | 5-21 |

|             | Carry Lines                                       | 4-31         | Register 0 (Trace                                   |      |

|             | Stop Lines                                        | 4-31         | Register) Restrictions                              | 5-22 |

|             | Counter Setup                                     | 4-31         | Registers 1 and 2 (64-bit),<br>2 through 5 (32-bit) |      |

|             | Logic Fault Monitoring                            | 4-32         | Restrictions                                        | 5-29 |

|             | Temperature Pressure and Dew-<br>point Monitoring | 4-32         | Registers 0 through 7<br>(64-bit), 0 through F      |      |

|             | Power Fail Monitoring                             | 4-33         | (32-bit), Monitor Mode                              |      |

|             | Compressor Monitoring                             | 4-33         | Restrictions                                        | 5-29 |

|             | compressor monitoring                             | 1 00         | Register 1 (32-bit) Right-<br>most Half of 64-Bit   |      |

| 5.          | PROGRAMMING CONSIDERATION                         | S            | Register 0                                          | 5-29 |

| ••          |                                                   | 5            | <b>Register Restrictions for</b>                    |      |

| -           | neral                                             | 5-1          | the STAR-1B                                         | 5-29 |

| Moı         | nitor and Job Modes                               | 5-1          | Common Register File for<br>Monitor and Job Modes   | 5-29 |

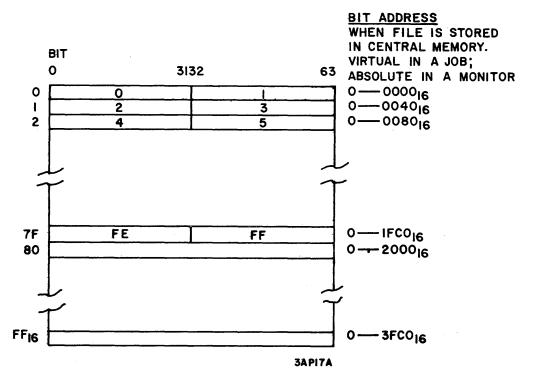

|             | Exchange from Monitor Mode<br>to Job Mode         | 5-2          | Data Flag Branch Register                           | 5-30 |

|             |                                                   |              | Data Flags                                          | 5-31 |

|             |                                                   |              | 5                                                   |      |

I

|      | Mask Bits                                  | 5-31 |

|------|--------------------------------------------|------|

|      | Product Bits                               | 5-31 |

|      | Dynamic Inclusive OR for<br>Product Bits   | 5-32 |

|      | Data Flag Branch Enable Bit                | 5-32 |

|      | Free Data Flags                            | 5-32 |

|      | Monitoring Counter Enable Flags            | 5-32 |

|      | Pipe 2 Register Instruction Flag           | 5-32 |

|      | Data Flag Branch Operation                 | 5-38 |

|      | Data Flag Branch Timing<br>Considerations  | 5-39 |

|      | eral Definitions and Program-<br>g Guides  | 5-40 |

|      | Overlap of Operand and Result<br>Fields    | 5-40 |

|      | Illegal Instructions                       | 5-40 |

|      | Instructions Which Cause                   |      |

|      | Undefined Results or<br>Operations         | 5-40 |

|      | Item Count                                 | 5-41 |

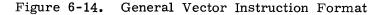

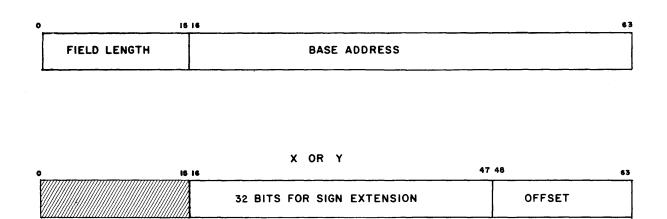

|      | Field Length and Offset                    | 5-41 |

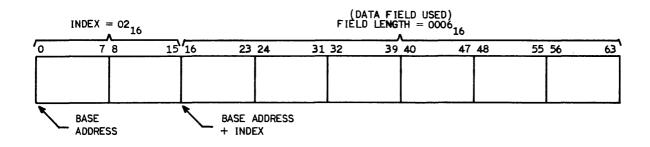

|      | Index                                      | 5-42 |

|      | Data Fault                                 | 5-42 |

|      | Operand Size Definitions                   | 5-42 |

|      | Restrictions on Self-Modifying<br>Programs | 5-43 |

|      | Result Vector 64-Sword<br>Lookahead        | 5-44 |

|      |                                            |      |

| 6.   | INSTRUCTIONS                               |      |

| Gen  | eral                                       | 6-1  |

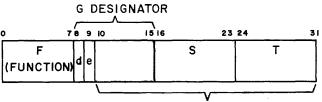

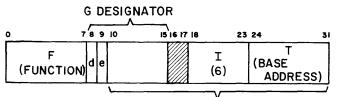

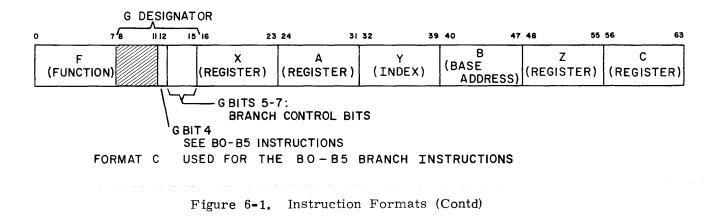

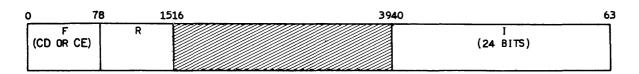

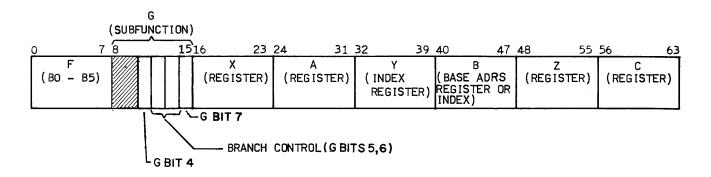

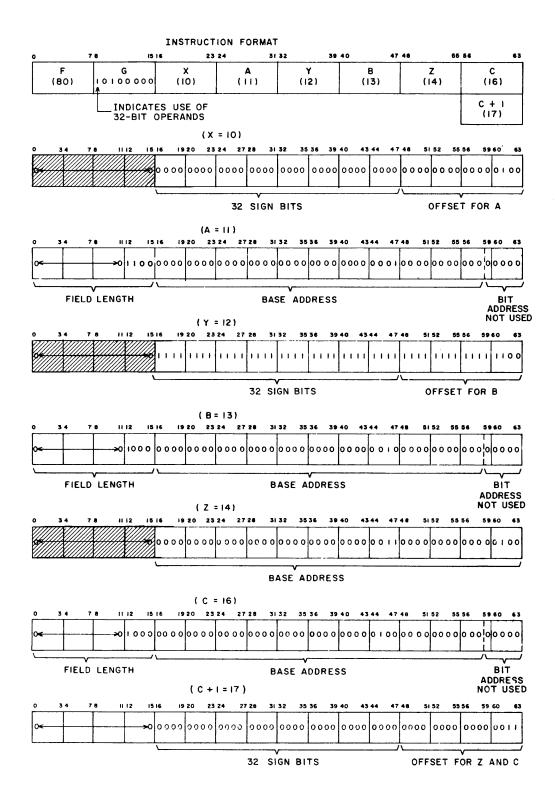

|      | Instruction Word Formats                   | 6-1  |

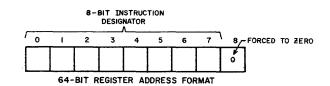

|      | Instruction Designators                    | 6-1  |

|      | Unused Bit Areas                           | 6-2  |

|      | Instruction Types                          | 6-10 |

| Inst | ruction Descriptions                       | 6-26 |

|      | Index Instructions                         | 6-27 |

|      | 3E Enter (R) with I (16 Bits)              | 6-27 |

|      | 3F Increase (R) by I (16 Bits)             | 6-27 |

|      | 4D Half Word Enter (R) with<br>I (16 Bits) | 6-27 |

| 4E Half Word Increase (R)<br>by I (16 Bits)     | 6-27          |

|-------------------------------------------------|---------------|

| CD Half Word Enter (R) with<br>I (24 Bits)      | 6-28          |

| CE Half Word Increase (R)                       | • ••          |

| with I (24 Bits)                                | 6-28          |

| BE Enter (R) with I (48 Bits)                   | 6-28          |

| BF Increase (R) by I (48 Bits)                  | 6-28          |

| 38 Transmit (R Bits 00-15) to<br>(T Bits 00-15) | 6-29          |

| Register Instructions                           | 6-29          |

| 2C Logical Exclusive OR (R),<br>(S), to (T)     | 6-30          |

| $2\mathrm{D}$ Logical and (R), (S), to (T)      | 6-30          |

| 2E Logical Inclusive OR (R),<br>(S), to (T)     | 6-30          |

| 30 Shift (R) Per S to (T)                       | 6-30          |

| 34 Shift (R) Per (S) to (T)                     | 6-31          |

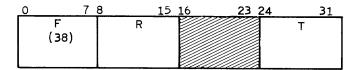

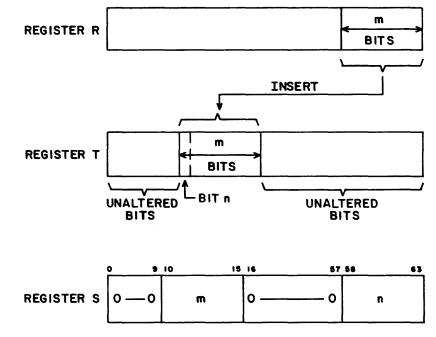

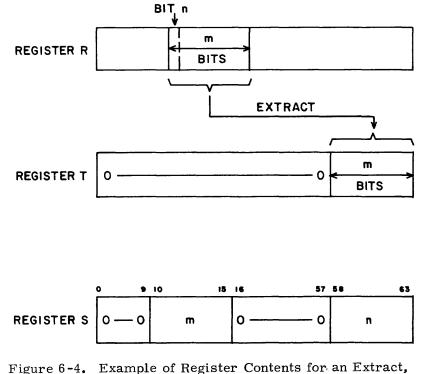

| 6D Insert Bits from (R) to (T) Per (S)          | 6-32          |

| 6E Extract Bits from (R) to (T) Per (S)         | 6-33          |

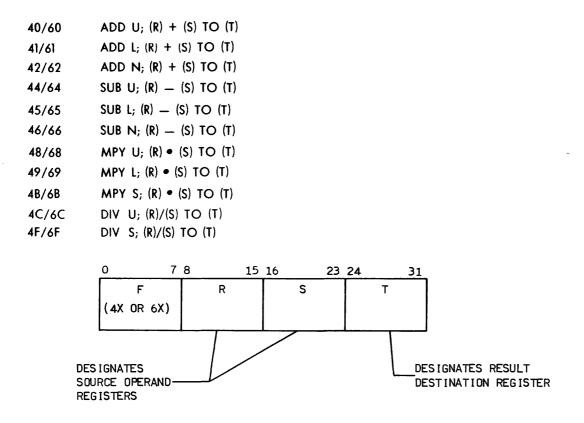

| 40/60 Add U; (R) + (S) to (T)                   | 6-34          |

| 41/61 Add L; (R) + (S) to (T)                   | 6 <b>-</b> 34 |

| 42/62 Add N; (R) + (S) to (T)                   | 6-34          |

| 44/64 Sub U; (R) - (S) to (T)                   | 6 <b>-</b> 34 |

| 45/65 Sub L; (R) - (S) to (T)                   | 6 <b>-</b> 34 |

| 46/66 Sub N; (R) - (S) to (T)                   | 6 <b>-</b> 34 |

| $48/68$ Mpy U; (R) $\bullet$ (S) to (T)         | 6-34          |

| 49/69 Mpy L; (R) $\bullet$ (S) to (T)           | 6-34          |

| $4B/6B$ Mpy S; (R) $\bullet$ (S) to (T)         | 6-34          |

| 4C/6C Div U; (R) / (S) to (T)                   | 6-34          |

| 4F/6F Div S; (R) / (S) to (T)                   | 6-34          |

| 63 Add Address (R) + (S) to (T)                 | 6-35          |

| 67  Sub Address (R) - (S) to (T)                | 6-35          |

| 58/78 Transmit (R) to (T)                       | 6-35          |

| 59/79 Absolute (R) to (T)                       | 6-35          |

| 51/71 Floor (R) to (T)                          | 6 <b>-</b> 35 |

| 52/72 Ceiling (R) to (T)                        | 6 <b>-</b> 35 |

| 5A/7A Exponent of (R) to (T)                    | 6-35          |

| 50/70 Truncate (R) to (T)                       | 6-35          |

| 5B/7B Pack (R), (S) to (T)                      | 6-38          |

,

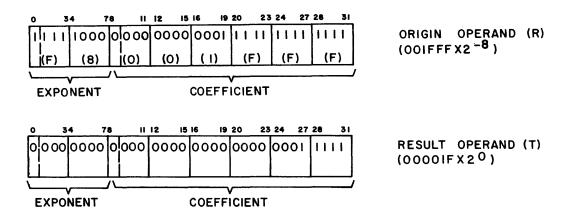

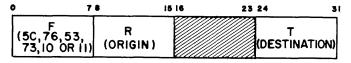

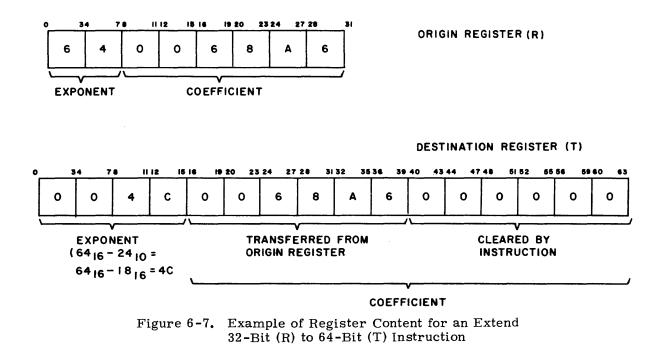

|     | 5C Extend 32 Bit (R) to<br>64 Bit (T)             | 6-39  | B0 Index, Branch if $(A) + (X) = (Z)$               | 6-57         |

|-----|---------------------------------------------------|-------|-----------------------------------------------------|--------------|

|     | 5D Index Extend 32 Bit (R) to<br>64 Bit (T)       | 6-39  | B1 Index, Branch if $(A) + (X) \neq (Z)$            | 6-57         |

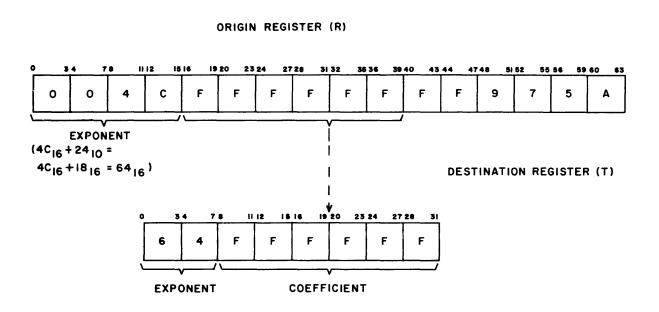

|     | 76 Contract 64 Bit (R) to<br>32 Bit (T)           | 6-39  | B2 Index, Branch if $(A) + (X) \ge (Z)$             | 6-57         |

|     | 77 Rounded Contract 64 Bit (R)<br>to 32 Bit (T)   | 6-39  | B3 Index, Branch if $(A) + (X) < (Z)$               | 6-57         |

|     | 7C Length of (R) to (T)                           | 6-39  | B4 Index, Branch if                                 | 0 5 5        |

|     | 53/73 Significant Square Root<br>of (R) to (T)    | 6-39  | (A) + (X) $\leq$ (Z)<br>B5 Index, Branch if         | 6-57         |

|     | 10 Convert BCD to Binary,                         |       | (A) + (X) > (Z)                                     | 6-57         |

|     | Fixed Length<br>11 Convert Binary to BCD,         | 6-39  | B6 Branch to Immediate<br>Address (R) + I (48 Bits) | <b>6-</b> 59 |

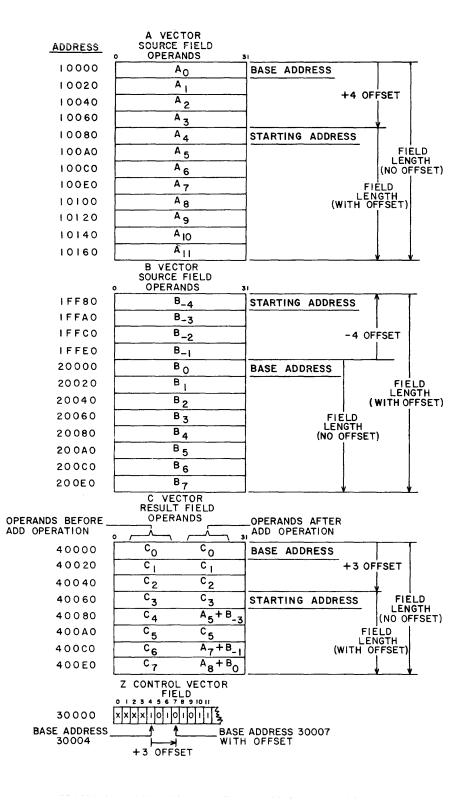

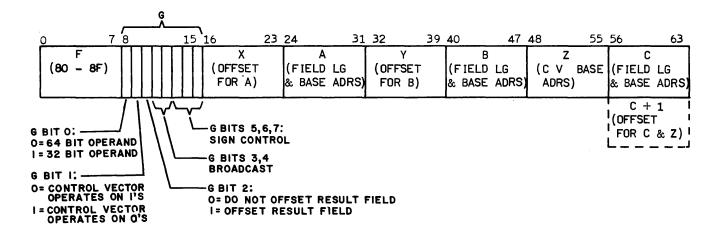

|     | Fixed Length                                      | 6-39  | Vector Instructions                                 | 6-59         |

|     | 54/74 Adjust Significance of                      |       | Instruction Formats                                 | 6-59         |

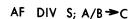

|     | (R) Per (S) to (T)                                | 6-44  | Subfunction Bits                                    | 6-60         |

|     | 55/75 Adjust Exponent of (R)<br>Per (S) to (T)    | 6-44  | Field Lengths, Base Address,<br>and Offsets         | 6-62         |

|     | 2A Enter Length of (R) with<br>I (16 Bits)        | 6-45  | Control Vector                                      | 6-63         |

|     | 2B Add to Length Field                            | 6-45  | Vector Instruction Termination                      | 6-64         |

| Bra | unch Instructions                                 | 6-47  | Example of Vector Instruction<br>Operation          | 6-65         |

|     | 20/24 Branch if (R) = (S)<br>(32/64 Bit FP)       | 6-47  | 80 Add U; $A + B \rightarrow C$                     | 6-68         |

|     | (32/34  Brt F1)<br>21/25 Branch if (R) $\neq$ (S) | 0 11  | 81 Add L; $A + B \rightarrow C$                     | 6-68         |

|     | (32/64 Bit FP)                                    | 6-47  | 82 Add N; $A + B \rightarrow C$                     | 6-68         |

|     | 22/26 Branch if (R) > (S)                         | 0 4 7 | 84 Sub U; A - $B \rightarrow C$                     | 6-68         |

|     | (32/64  Bit FP) -                                 | 6-47  | 85 Sub L; A - $B \rightarrow C$                     | 6-68         |

|     | 23/27 Branch if (R) < (S)<br>(32/64 Bit FP)       | 6-47  | 86 Sub N; A - $B \rightarrow C$                     | 6-68         |

|     | 2F Register Bit Branch                            |       | 88 Mpy U; A ● B→C                                   | 6-68         |

|     | and Alter                                         | 6-48  | 89 Mpy L; A ● B→C                                   | 6-68         |

|     | 33 Data Flag Register Bit<br>Branch and Alter     | 6 40  | 8B Mpy S; $A \bullet B \rightarrow C$               | 6-68         |

|     | 3B Data Flag Register Load/                       | 6-49  | 8C Div U; $A/B \rightarrow C$                       | 6-68         |

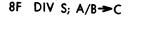

|     | Store                                             | 6-51  | 8F Div S; $A/B \rightarrow C$                       | 6-68         |

|     | 32 Bit Branch and Alter                           | 6-51  | 83 Add A; $A + B \rightarrow C$                     | 6-69         |

|     | 36 Branch and Set (R) to Next                     |       | 87 Sub A; A - $B \rightarrow C$                     | 6-69         |

|     | Instruction                                       | 6-54  | 98 Transmit $A \rightarrow C$                       | 6-70         |

|     | 31 Increase (R) and Branch if (R) $\neq$ 0        | 6-54  | 99 Absolute $A \rightarrow C$                       | 6-70         |

|     | 35 Decrease (R) and Branch                        | 0 01  | 91 Floor $A \rightarrow C$                          | 6-70         |

|     | if (R) $\neq 0$                                   | 6-54  | 92 Ceiling $A \rightarrow C$                        | 6-70         |

|     | 09 Exit Force                                     | 6-55  | 9A Exponent of $A \rightarrow C$                    | 6-70         |

|     |                                                   |       |                                                     |              |

|      | 90 Truncate A→C                                          | 6-70         | DI           |

|------|----------------------------------------------------------|--------------|--------------|

|      | 9B Pack A, B→C                                           | 6-75         | ••           |

|      | 9C Extend 32 Bit A→64 Bit C                              | 6-77         | DS           |

|      | 96 Contract 64 Bit A→32 Bit C                            | 6-77         | D]<br>/2     |

|      | 97 Rounded Contract 64 Bit A→<br>32 Bit C                | 6-77         | D(           |

|      | 93 Significant Square Root of A→C                        | 6-77         | D4<br>B8     |

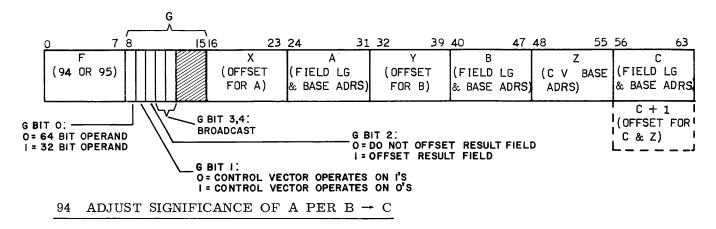

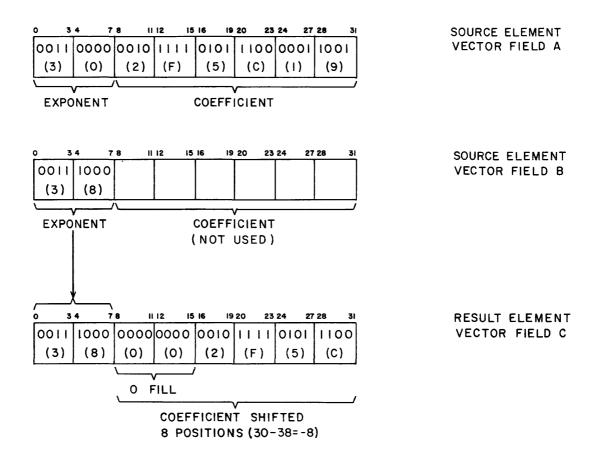

|      | 94 Adjust Significance of A Per $B \rightarrow C$        | 6-81         | DI           |

|      | 95 Adjust Exponent of A Per $B \rightarrow C$            | 6-81         | DI<br>B4     |

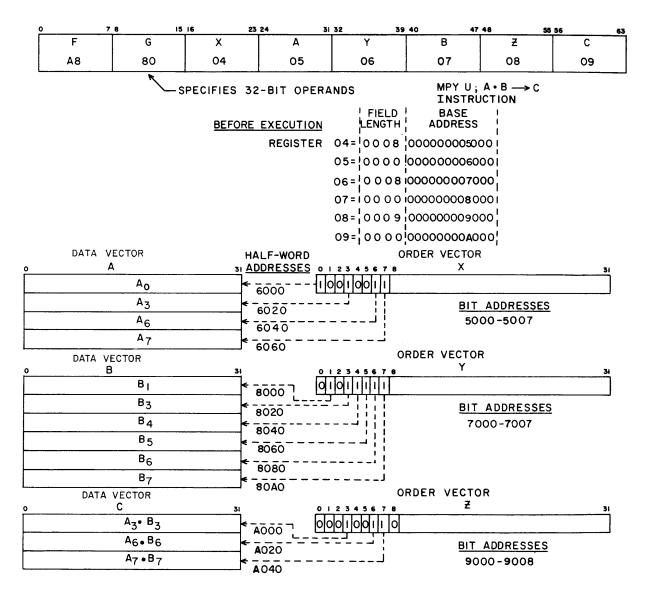

| Spai | rse Vector Instructions                                  | 6-84         | B            |

| ~ F  | Sparse Vector Instruction                                |              | D            |

|      | Format                                                   | 6-86         | (C           |

|      | Base Addresses and Field<br>Lengths                      | 6-86         | String<br>St |

|      | Sparse Vector Instruction<br>Termination                 | 6-86         | Co<br>St     |

|      | A0 Add U; A + $B \rightarrow C$                          | <b>6-</b> 89 | E            |

|      | A1 Add L; $A + B \rightarrow C$                          | 6-89         | E            |

|      | A2 Add N; $A + B \rightarrow C$                          | 6-89         | E            |

|      | A4 Sub U; A - $B \rightarrow C$                          | 6-89         | E            |

|      | A5 Sub L; A - $B \rightarrow C$                          | 6-89         | E            |

|      | A6 Sub N; A - $B \rightarrow C$                          | 6-89         | E            |

|      | A8 Mpy U; A ● B→C                                        | 6-91         | F            |

|      | A9 Mpy L; A ● B→C                                        | 6-91         | A۰           |

|      | AB Mpy S; A $\bullet$ B $\rightarrow$ C                  | 6-91         | FC<br>A·     |

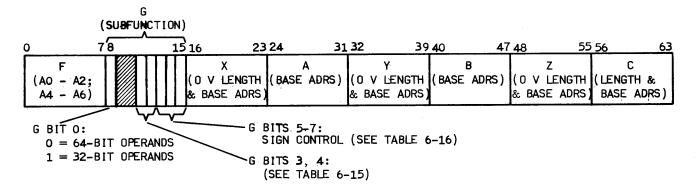

|      | AC Div U; $A/B \rightarrow C$                            | 6-91         | E4           |

|      | AF Div S; $A/B \rightarrow C$                            | 6-91         | E            |

| Vec  | tor Macro Instructions                                   | 6-94         | E6           |

|      | C0 Select EQ; A = B,<br>Item Count to (C)                | 6-94         | E'           |

|      | C1 Select NE; A <b>f</b> B <b>,</b><br>Item Count to (C) | 6-94         | F.<br>F      |

|      | C2 Select GE; $A > B$ ,<br>Item Count to (C)             | 6-94         | F9<br>Or     |

|      | C3 Select LT; A < B,<br>Item Count to (C)                | 6-94         | ${ m E}_{2}$ |

|      | DA Sum $(A0 + A1 + A2 + An)$ to (C) and (C + 1)          | 6-97         | FI<br>B      |

|      |                                                          |              |              |

|      | DB Product (A0, A1, A2,                     |       |

|------|---------------------------------------------|-------|

|      | An) to C                                    | 6-98  |

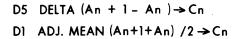

|      | D5 Delta (An+1 - An) →Cn                    | 6-100 |

|      | D1 Adj. Mean (An+1 + An)<br>/2→Cn           | 6-100 |

|      | D0 Average $(An + Bn)/2 \rightarrow Cn$     | 6-102 |

|      | D4 Ave. Diff. $(An - Bn)/2 \rightarrow Cn$  | 6-102 |

|      | B8 Transmit Reverse $A \rightarrow C$       | 6-103 |

|      | DE Polynomial Evaluation                    | 6-105 |

|      | DF Interval A Per B→C                       | 6-108 |

|      | BA Transmit Indexed $List \rightarrow C$    | 6-111 |

|      | B7 Transmit List→Indexed C                  | 6-114 |

|      | DC Vector Dot Product to<br>(C) and (C + 1) | 6-116 |

| Stri | ng Instructions                             | 6-117 |

|      | String Instruction Data                     | 0 111 |

|      | Code and Formats                            | 6-118 |

|      | String Instruction Format                   | 6-121 |

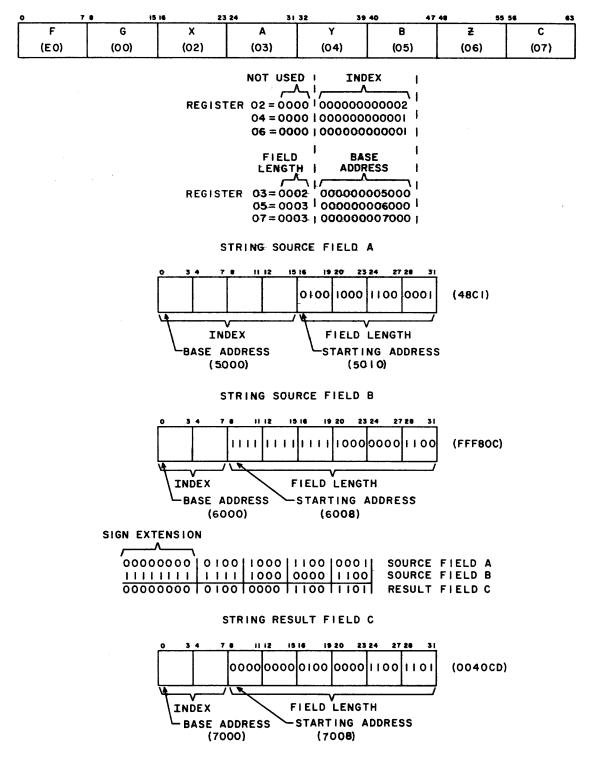

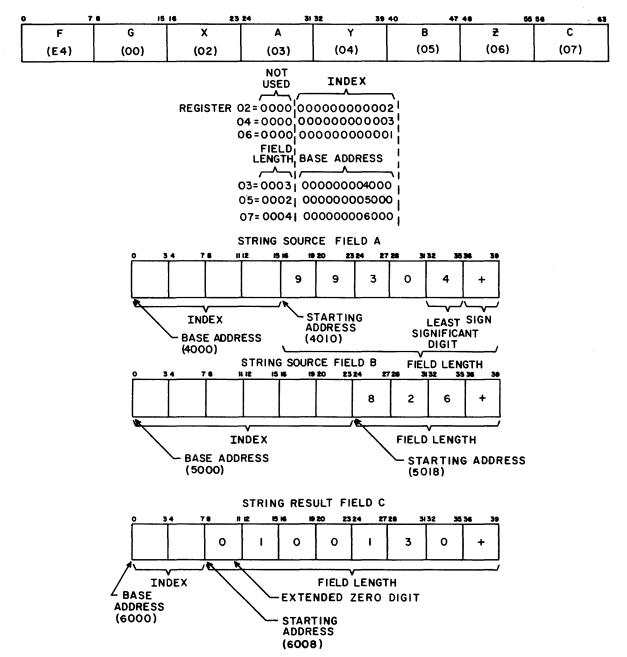

|      | E0 Binary Add; A + B $\rightarrow$ C        | 6-127 |

|      | E1 Binary Sub; A - B→C                      | 6-127 |

|      | E2 Binary Mpy; A ● B→C                      | 6-127 |

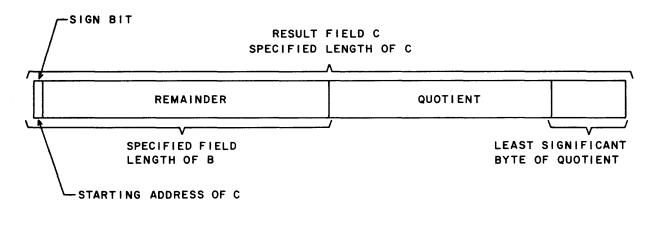

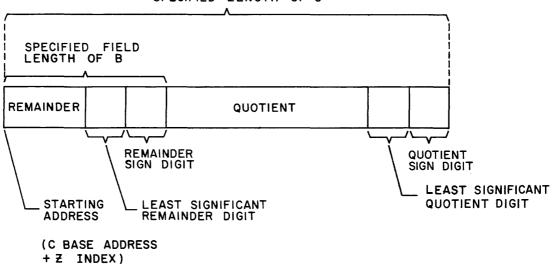

|      | E3 Binary Div; A/B→C                        | 6-127 |

|      | EC Modulo Add A + $B \rightarrow C$         | 6-130 |

|      | ED Modulo Sub A - B→C                       | 6-130 |

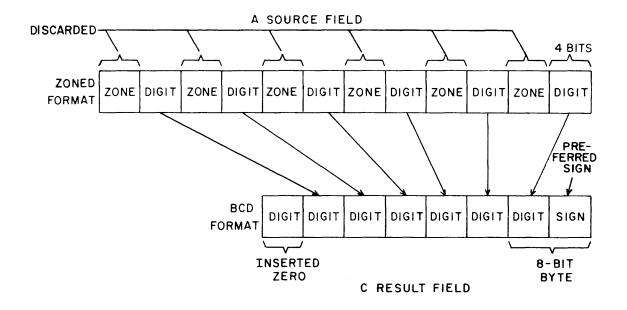

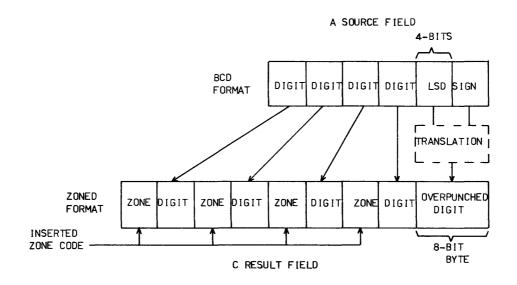

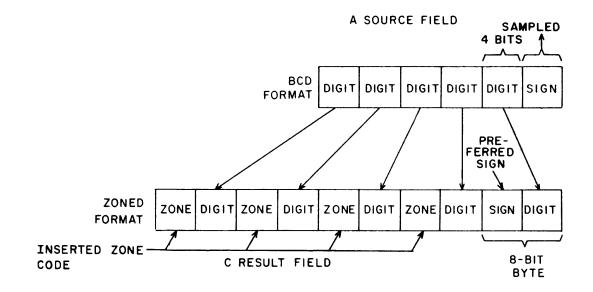

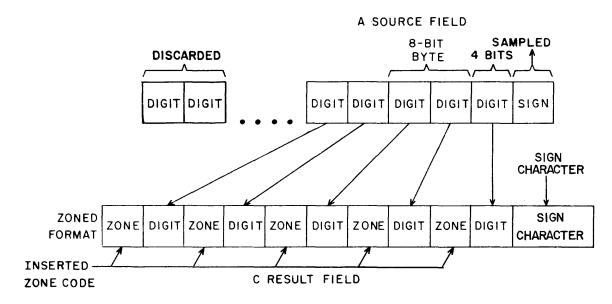

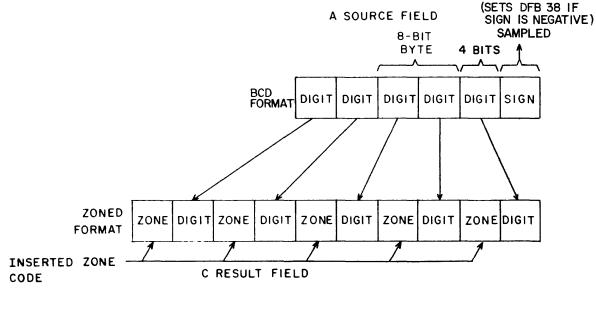

|      | FB Pack Zoned to BCD;<br>A→C                | 6-132 |

|      | FC Unpack BCD to Zoned;                     | 0 100 |

|      |                                             | 6-132 |

|      | E4 Decimal Add; $A + B \rightarrow C$       | 6-143 |

|      | E5 Decimal Sub; $A - B \rightarrow C$       | 6-143 |

|      | E6 Decimal Mpy; $A \bullet B \rightarrow C$ | 6-143 |

|      | E7 Decimal Div; $A/B \rightarrow C$         | 6-143 |

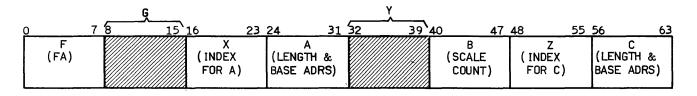

|      | FA Move and Scale; $A \rightarrow C$        | 6-146 |

|      | F8 Move Bytes Left; $A \rightarrow C$       | 6-150 |

|      | F9 Move Bytes Left,<br>Ones Comp. A→C       | 6-150 |

|      | EA Merge Per Byte Mask A<br>B Per G→C       | 6-153 |

|      | FD Compare Bytes A,<br>B Per Mask Field C   | 6-155 |

|      |                                             |       |

| FE Search for Masked                                              |         | BC Compress $A \rightarrow C$ Per Z         | 6-191          |

|-------------------------------------------------------------------|---------|---------------------------------------------|----------------|

| Key Byte; A, B Per C, G                                           | 6-158   | CF Arith. Compress $A \rightarrow C$        | 0-101          |

| FF Search for Masked Key                                          |         | Per B                                       | 6-192          |

| Word; A, B Per C, G                                               | 6-158   | BD Merge A, $B \rightarrow C$ ; Per Z       | 6-195          |

| D6 Search for Masked Key Bit;<br>A, B Per C, G                    | 6-158   | 14 Bit Compress                             | 6-197          |

| EE Translate A Per $B \rightarrow C$                              | 6-162   | 15 Bit Merge                                | 6-199          |

| EF Translate and Test Per                                         |         | 16 Bit Mask                                 | 6-199          |

| B→C                                                               | 6-165   | 17 Character String Merge                   | 6-203          |

| D7 Translate and Mark A Per<br>B→C                                | 6-166   | DD Sparse Dot Product to<br>(C) and (C + 1) | 6-205          |

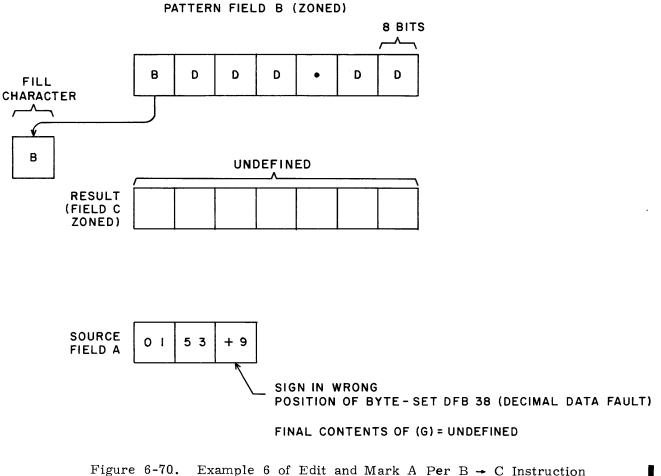

| EB Edit and Mark A Per $B \rightarrow C$                          | 6-168   | C4 Compare EQ; A = B,                       | c 900          |

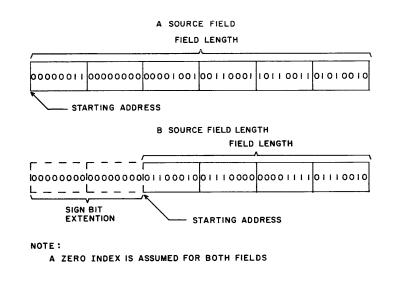

| E8 Compare Binary A, B                                            | 6-182   | Order Vector $\rightarrow Z$                | 6-208          |

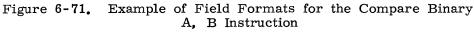

| E9 Compare Decimal A, B                                           | 6-182   | C5 Compare NE; A ≠ B,<br>Order Vector→Z     | 6-208          |

| Logical String Instructions                                       | 6-184   | C6 Compare GE; $A \ge B$ ,                  |                |

| F0 Logical Exclusive OR<br>A, $B \rightarrow C$                   | 6-184   | Order Vector $\rightarrow Z$                | 6-208          |

| F1 Logical AND A, $B \rightarrow C$                               | 6-184   | C7 Compare LT; A < B,<br>Order Vector→Z     | 6-208          |

| F2 Logical Inclusive OR                                           | • • • • | C8 Search EQ; A = B,                        |                |

| A, B→C                                                            | 6-184   | Index List $\rightarrow$ C                  | 6-211          |

| F3 Logical Stroke, A, $B \rightarrow C$                           | 6-184   | C9 Search NE; A ≠ B,<br>Index List→C        | 6-211          |

| F4 Logical Pierce A, $B \rightarrow C$                            | 6-184   | CA Search GE; A >B,                         | 0-211          |

| F5 Logical Implication A, $B \rightarrow C$                       | 6-184   | Index List $\rightarrow$ C                  | 6-211          |

| F6 Logical Inhibit A, B→C                                         | 6-184   | CB Search LT; A < B,<br>Index List→C        | 6-211          |

| F7 Logical Equivalence                                            |         | D8 Max, of A to (C)                         |                |

| A, B→C                                                            | 6-184   | Item Count to (B)                           | 6-214          |

| Nontypical Instructions                                           | 6-187   | D9 Min. of A to (C) the Count to $(B)$      | 6-214          |

| 3D Index Multiply (R) ● (S) to (T)<br>3C Half Word Index Multiply | 6-187   | Item Count to (B)<br>B9 Transpose/Move      | 6-214<br>6-216 |

| (R) $\bullet$ (S) to (T)                                          | 6-187   | 18 Move Bytes Right                         | 6-221          |

| 5E/7E Load (T) Per (S), (R)                                       | 6-188   | 19 Scan Right                               | 6-224          |

| 5F/7F Store (T) Per (S), (R)                                      | 6-188   | 28/29 Scan Equal/Unequal                    | 6-224          |

| 12/13 Load/Store Byte (T)                                         | a 100   | 1A Fill Field T with Byte R                 | 6-228          |

| Per (S), (R)                                                      | 6-188   | 1B Fill Field T with Byte (R)               | 6-228          |

| <b>37 Tran</b> smit Job Interval<br>Timer to (T)                  | 6-188   | 1C Form Repeated Bit Mask                   |                |

| 7D Swap S→T, R→S                                                  | 6-189   | with Leading Zeros                          | 6-228          |

| 39 Transmit Realtime<br>Clock to (T)                              | 6-190   | 1D Form Repeated Bit Mask with Leading Ones | 6-228          |

| 3A Transmit (R) to Job                                            |         | 1E Count Leading Equals R                   | 6-229          |

| Interval Timer                                                    | 6-190   | 1F Count Ones in Field R,                   | 6 994          |

| BB Mask A, B→C Per Z                                              | 6-190   | Count to T                                  | 6-231          |

|                                                                   |         |                                             |                |

| 04 Breakpoint - Maintenance    | 6-231 | 0D Load Associative Registers                          | 6-236  |

|--------------------------------|-------|--------------------------------------------------------|--------|

| 06 Fault Test - Maintenance    | 6-233 | 0E Translate External                                  |        |

| Monitor Instructions           | 6-235 | Interrupt                                              | :6-236 |

| 00 Idle                        | 6-235 | 0F Load Keys From (R),<br>Translate Address (S) to (T) | 6-237  |

| 08 Input/Output Per R          | 6-235 | 0A Transmit (R) to Monitor                             |        |

| 0C Store Associative Registers | 6-236 | Interval Timer                                         | 6-238  |

## **APPENDIXES**

- A. NUMBER SYSTEMS AND TABLES

- B. FLOATING POINT ARITHMETIC

- C. G BITS AND TERMINATING CONDITIONS

- D. DATA FLAG APPLICATIONS TO INSTRUCTIONS

## **FIGURES**

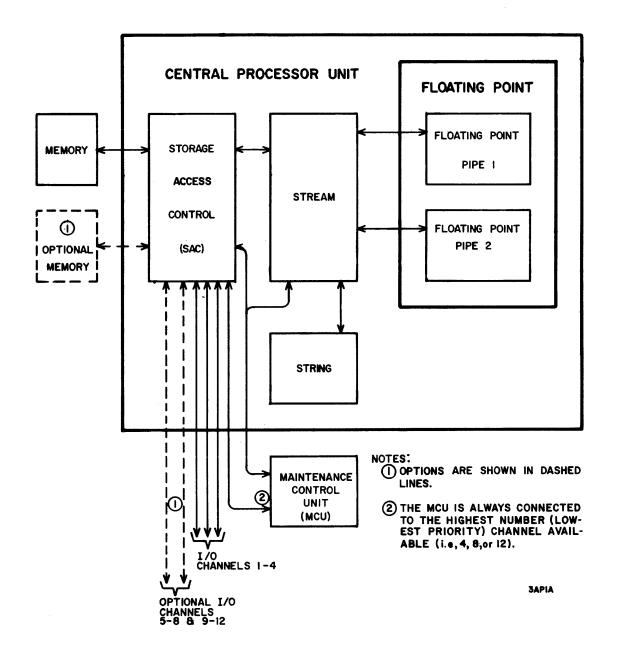

| 1-1     | Basic CDC STAR-100<br>Configuration                                         | 1-4  |

|---------|-----------------------------------------------------------------------------|------|

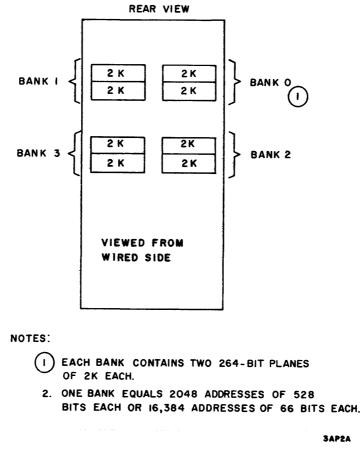

| 2-1     | One of Eight MCS Sections<br>(Cabinets)                                     | 2-1  |

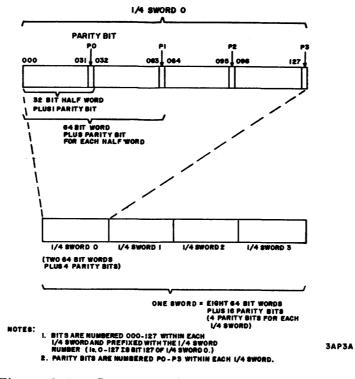

| 2-2     | Superword (Sword) Configura-<br>tion                                        | 2-2  |

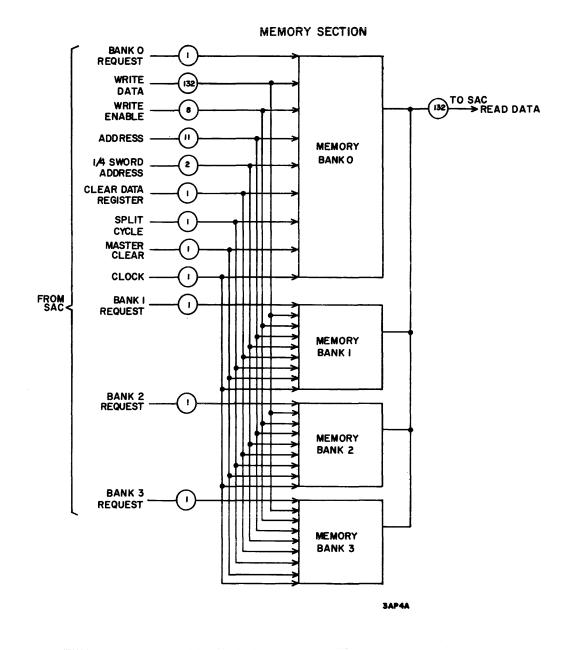

| 2-3     | SAC/Memory Connections                                                      | 2-3  |

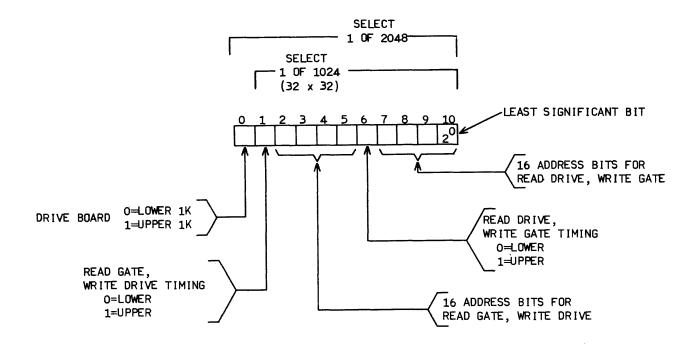

| 2-4     | MCS Address Selection                                                       | 2-4  |

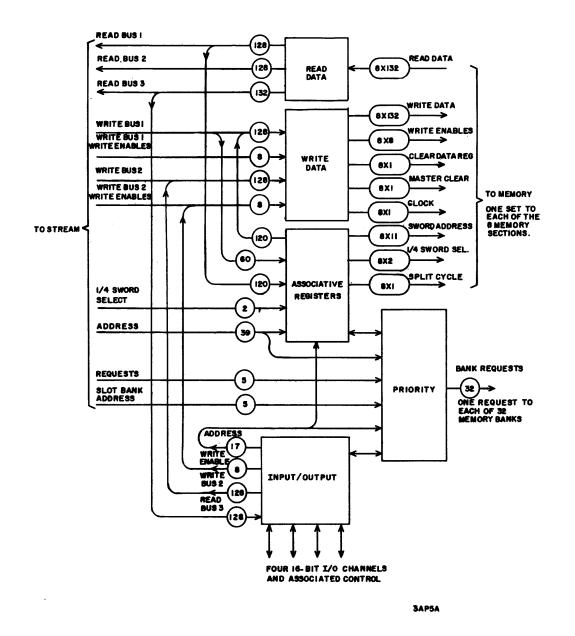

| 3-1     | Storage Access Control                                                      | 3-2  |

| 3-2     | Page Table Search Examples                                                  | 3-10 |

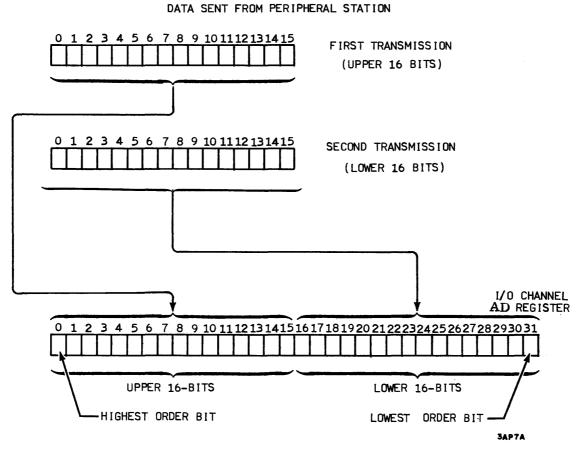

| 3-3     | I/O Data Formats                                                            | 3-14 |

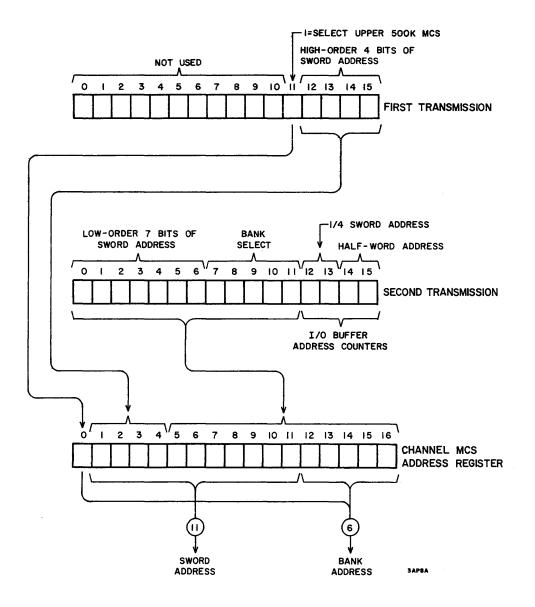

| 3-4     | I/O Address Formats                                                         | 3-15 |

| 3-5     | Basic Stream Block Diagram                                                  | 3-20 |

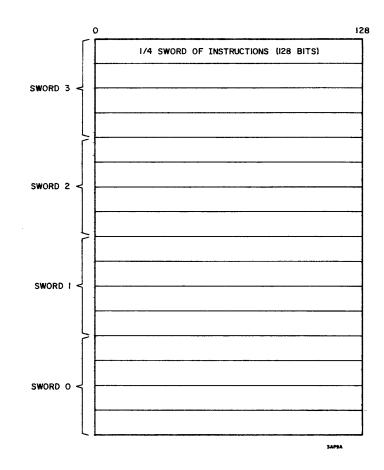

| 3-6     | Instruction Stack                                                           | 3-21 |