# OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL LIST OF EFFECTIVE PAGES

New features, as well as changes, deletions, and additions to information in this manual, are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed. The total number of pages in this document is 389

| PAGE           | REV | PAGE | REV | PAGE | REV | PAGE | REV | PAGE | REV |

|----------------|-----|------|-----|------|-----|------|-----|------|-----|

| 0              | A   |      |     |      |     |      |     |      |     |

| Cover          |     |      |     |      |     |      |     |      |     |

| i thru ili     | A   |      |     |      |     |      |     |      |     |

| iv Blank       | A   |      |     |      |     |      |     |      |     |

| 1-1 thru 1-18  | A   |      |     |      |     |      |     |      |     |

| 2-1 thru 2-20  |     |      |     |      |     |      |     |      |     |

| 3-1 thru 3-321 | A   |      |     |      |     |      |     |      |     |

| 3-322 Blank    |     |      |     |      |     |      |     |      |     |

| A-1 thru A-10  | A   |      |     |      |     |      |     |      |     |

| Comment        |     |      |     |      |     |      |     |      |     |

| Form           | A   |      |     |      |     |      |     |      |     |

| Mailer         |     | }    |     |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

| •              |     |      |     |      |     |      |     |      |     |

|                |     |      | 1   |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

|                |     |      |     |      | -   |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

|                |     |      |     |      |     |      |     |      |     |

#### Revision Letters I, O, Q & X are not used.

OPTICAL STORAGE INTERNATIONAL PROPRIETARY NOTICE

Contained herein is material which is private, Trade-Secret or otherwise proprietary to Optical Storage International and is authorized for reproduction or use only under the terms of an applicable Optical Storage International contract. Address comments concerning this manual to:

Optical Storage International Customer Documentation P. O. Box 58063 Santa Clara, Calif. 95052

or use comment sheet in the back of this manual

•

# OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL

LIST OF EFFECTIVE PAGES

75114906 A

New features, as well as changes, deletions, and additions to information in this manual, are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed. The total number of pages in this document is 389.

| PAGE                                                                                                           | REV       | PAGE | REV | PAGE | REV | PAGE | REV | PAGE | REV |

|----------------------------------------------------------------------------------------------------------------|-----------|------|-----|------|-----|------|-----|------|-----|

| er<br>ru iii<br>Blank<br>thru 1-18<br>thru 2-20<br>thru 3-321<br>22 Blank<br>thru A-10<br>nment<br>Form<br>ler | ~~~~~~~~~ |      |     |      |     |      |     |      |     |

|                                                                                                                |           |      |     |      |     |      |     |      |     |

|                                                                                                                |           |      |     |      |     |      |     |      |     |

sion Letters I, O, Q & X are not used.

ICAL STORAGE INTERNATIONAL PROPRIETARY NOTICE

tained herein is material which is private, Trade-Secret or otherwise inietary to Optical Storage International and is authorized for reproduction ise only under the terms of an applicable Optical Storage International ract. Address comments concerning this manual to:

Optical Storage International Customer Documentation P. O. Box 58063 Santa Clara, Calif. 95052

or use comment sheet in the back of this manual

ge: ii

- N

• .

## OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL PREFACE

## SCOPE

This Peripheral Equipment Reference Manual has been prepared to aid trained maintenance personnel in the service and repair of the LaserDrive 1200 Intelligent Digital Optical Disk with Small Computer System Interface (SCSI), also referred to as the LD 1200. Comments, suggestions for improvement, and corrections to this manual are solicited. Forms are provided for those purposes at the end of this document.

ORGANIZATION OF INFORMATION

Section 1 – General Description Section 2 – Operation Section 3 – Theory of Operation

RELATED PUBLICATIONS

The following documents may be used to supplement the LD 1200 Peripheral Equipment Reference Manual:

### PUBLICATION

PUBLICATION NUMBER

| LD 1200 Hardware Maintenance Manual, Volume 1        | 75114907    |

|------------------------------------------------------|-------------|

| LD 1200 Hardware Maintenance Manual, Volume 2        | 75114908    |

| LD 1200 Customer User Manual                         | 75114905    |

| LD 1200 Site Preparation Manual                      | 75114903    |

| Small Computer System Interface (SCSI) Specification | ANSĊ X3T9.2 |

| System Interface Assembly (SIA) Specification        | 75110948    |

. .

# OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL TABLE OF CONTENTS

Page: v

## Contents

| 1. | GENERAL DESCRIPTION                                                                                                                              | 1-1                          |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|    | 1.1. INTRODUCTION                                                                                                                                | 1-1                          |

|    | 1.2. PHYSICAL DESCRIPTION                                                                                                                        | 1-1                          |

|    | 1.3. LD 1200 UNIT                                                                                                                                | 1-3                          |

|    | 1.4. CARD RACK                                                                                                                                   | 1-6                          |

|    | 1.5. LD 1200 PCA DESCRIPTIONS                                                                                                                    | 1-8                          |

|    | 1.6. POWER SUPPLY                                                                                                                                | 1-12                         |

|    | 1.7. BASEPLATE                                                                                                                                   | 1-12                         |

|    | 1.8. LD 1200 FRONT PANEL                                                                                                                         | 1-18                         |

|    | 1.9. LD 1200 REAR PANEL                                                                                                                          | 1-18                         |

| 2. | OPERATION                                                                                                                                        | 2-1                          |

|    | 2.1. INTRODUCTION                                                                                                                                | 2-1                          |

|    | 2.2. CONTROLS AND INDICATORS<br>2.2.1. Operator Panel<br>2.2.2. Maintenance Panel<br>2.2.3. Power Supply                                         | 2-1<br>2-1<br>2-4<br>2-8     |

|    | 2.3. POWER ON/OFF PROCEDURES<br>2.3.1. Power-On Procedure<br>2.3.2. Power-Off Procedure                                                          | 2-8<br>2-8<br>2-8            |

|    | 2.4. DATA CARTRIDGE LOADING/UNLOADING PROCEDURES                                                                                                 | 2-8                          |

|    | 2.5. OPERATOR PANEL OPERATING PROCEDURES<br>2.5.1. Data Write Protection<br>2.5.2. Disk Spin–Up/Down<br>2.5.3. Running Operator Diagnostic Tests | 2-10<br>2-10<br>2-11<br>2-11 |

# OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL TABLE OF CONTENTS

Page: vi

75114902 B

|    | 2.6. MAINTENANCE PANEL OPERATING PROCEDURES                                          | 2-12         |

|----|--------------------------------------------------------------------------------------|--------------|

|    | 2.6.1. Diagnostic Test Operating Procedure (Performed Only by the Customer Engineer) | 2-13         |

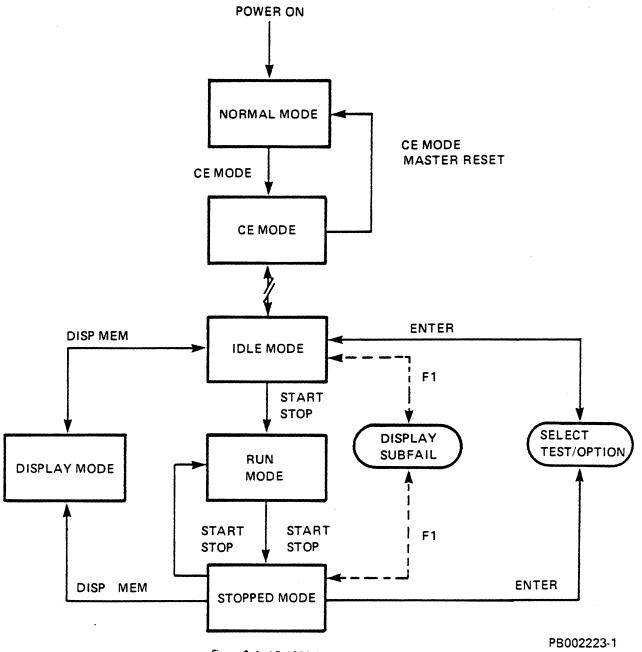

|    | 2.6.2. Firmware Overview                                                             | 2-15         |

|    | 2.6.2.1. Normal Mode                                                                 | 2-15         |

|    | 2.6.2.2. CE Mode                                                                     | 2-16         |

|    | 2.6.2.3. Stopped Mode                                                                | 2-16         |

|    | 2.6.3. Selecting a Test                                                              | 2-16         |

|    | 2.6.4. Selecting an Option                                                           | 2-16         |

|    | 2.6.5. Starting a Test or Option                                                     | 2-17         |

|    | 2.6.6. Entering Parameters                                                           | 2-17         |

|    | 2.6.7. Stopping/Resuming a Test<br>2.6.8. Displaying a Subfailure Code               | 2-18<br>2-18 |

|    | 2.6.9. Displaying a Sublative Code<br>2.6.9. Displaying/Modifying Memory             | 2-18         |

| ~  |                                                                                      |              |

| J. | THEORY OF OPERATION                                                                  | 3-1          |

|    | 3.1. INTRODUCTION                                                                    | 3-1          |

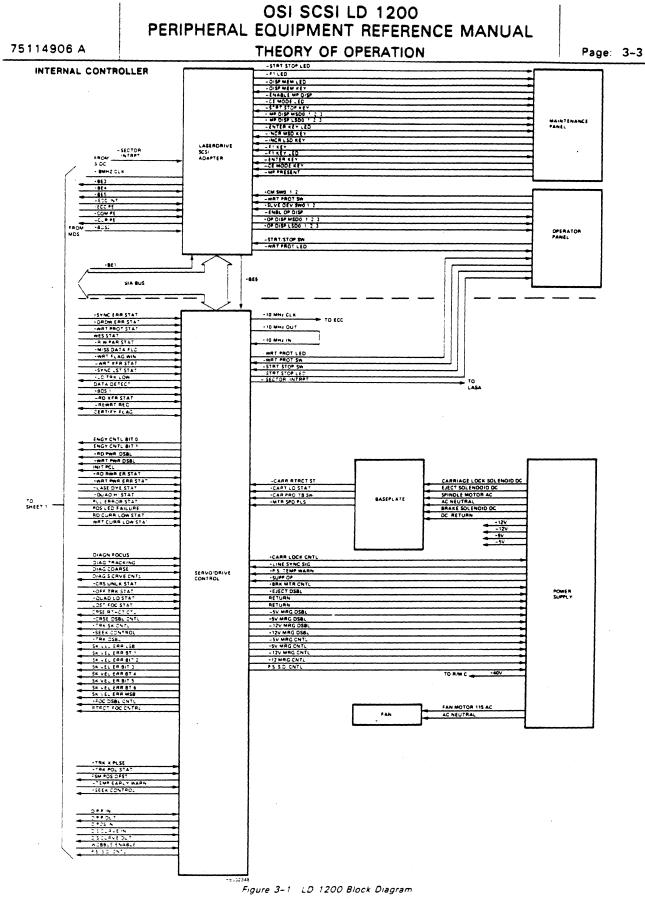

|    | 3.2. LD 1200 GENERAL BLOCK DIAGRAM                                                   | 3-1          |

|    | 3.2.1. Interfaces                                                                    | 3-4          |

|    | 3.2.2. LD 1200 SCSI Adapter PCA                                                      | 3-4          |

|    | 3.2.3. Error Correction Code and Common Memory Interface Unit PCA                    | 3-4          |

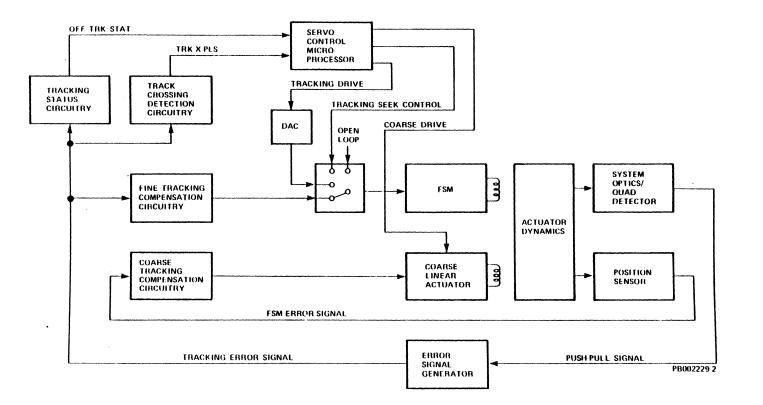

|    | 3.2.4. Servo/Drive Control PCA                                                       | 3-4          |

|    | 3.2.5. Servo Systems PCA                                                             | 3-5          |

|    | 3.2.6. Error Signal Generator PCA<br>3.2.7. Read/Write Control PCA                   | 3-5<br>3-5   |

|    | 3.2.8. Modulator Demodulator Synchronizer PCA                                        | 3-6          |

|    | 3.2.9. Carriage                                                                      | 3-6          |

|    | 3.2.10. Media                                                                        | 3-6          |

|    | 3.2.11. Baseplate                                                                    | 3-6          |

|    | 3.2.12. Power Supply                                                                 | 3-7          |

|    | 3.2.13. Operator Panel                                                               | 3-7          |

|    | 3.2.14. Maintenance Panel (Optional)                                                 | 3–7          |

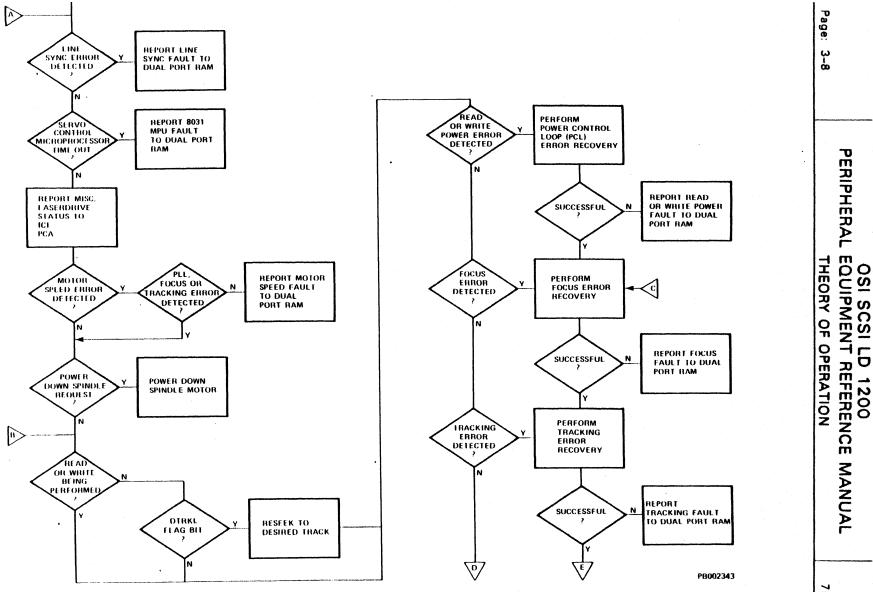

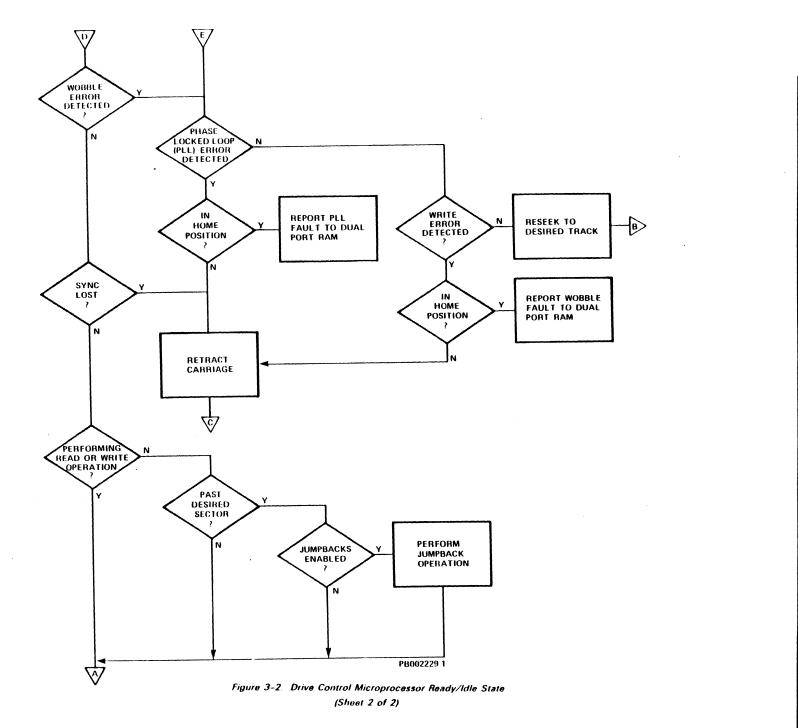

|    | 3.3. LD 1200 FUNCTIONS                                                               | 3-7          |

|    | 3.3.1. Drive Initialization and Focus                                                | 3-7          |

|    | 3.3.2. Seek                                                                          | 3-7          |

|    | 3.3.2.1. Seek Initialization                                                         | 3-10         |

|    | 3.3.2.2. Seek<br>3.3.2.3. Jumpbacks                                                  | 3-10<br>3-15 |

|    | 3.3.3. Read/Write                                                                    | 3-17         |

|    | 3.3.3.1. Initialization                                                              | 3-20         |

|    | 3.3.3.2. Synchronization and Sector Identification                                   | 3-23         |

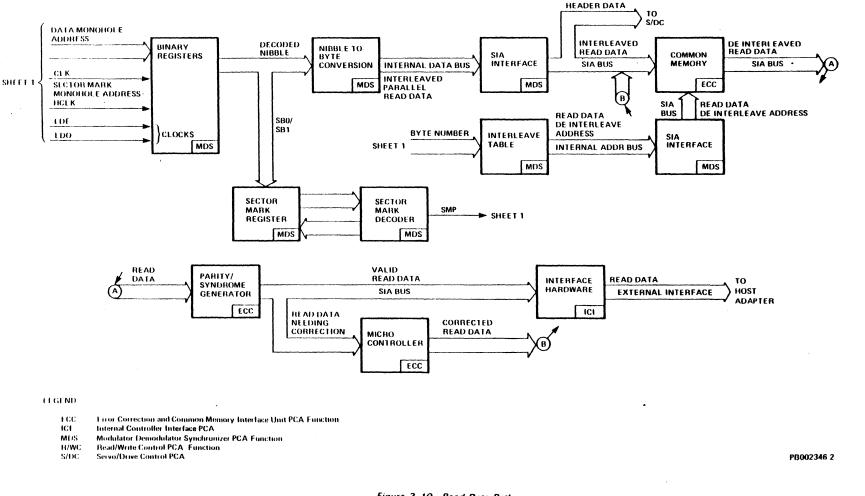

|    | 3.3.3.3. Read Data Operation                                                         | 3-27         |

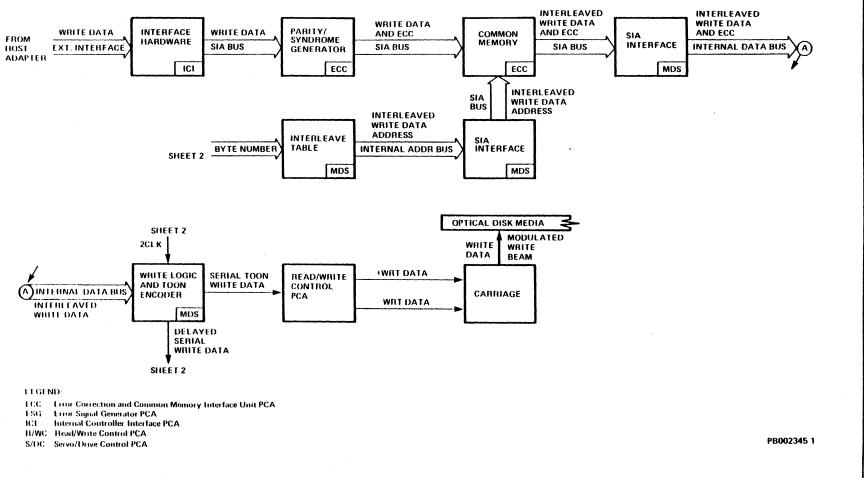

|    | 3.3.3.4. Write Data Operation                                                        | 3-27         |

|    | 3.3.4. Error/Fault Handling                                                          | 3-31         |

|    | 3.3.4.1. Direct Read During Write                                                    | 3-35         |

|    | 3.3.4.2. Track Miscompare Error                                                      | 3-35         |

|    | 3.3.4.3. Missing Data Field Error                                                    | 3-35<br>3-35 |

|    | 3.3.4.4. Power Supply Overtemperature<br>3.3.4.5. Card Rack Overtemperature          | 3-35         |

|    | 3.3.4.6. Laser Read Power Error/Fault                                                | 3-36         |

|    | 3.3.4.7. Laser Write Power Error/Fault                                               | 3-36         |

|    | 3.3.4.8. Quad Sum High Fault                                                         | 3-36         |

|    |                                                                                      |              |

OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL

Page: <sub>vii</sub>

## TABLE OF CONTENTS

| 3.3.4.9. Verify Header Error/Fault                             |   | 3-36         |

|----------------------------------------------------------------|---|--------------|

| 3.3.4.10. Motor Speed Fault                                    |   | 3-36         |

| 3.3.4.11. MPU Timeout Fault                                    |   | 3-37         |

| 3.3.4.12. MPU Self-Test Fault                                  |   | 3-37         |

| 3.3.4.13. Wobble Error/Fault                                   |   | 3-37         |

| 3.3.4.14. Phase-Locked Loop Error/Fault                        |   | 3-37         |

| 3.3.4.15. Focus Error/Fault                                    |   | 3-37         |

| 3.3.4.16. Seek Error/Fault                                     |   | 3-38         |

| 3.3.4.17. Tracking Error/Fault                                 |   | 3-38         |

| 3.3.4.18. Line Sync Fault                                      |   | 3-38         |

| 3.3.4.19. Data Synchronization Error/Fault                     |   | 3-38         |

| 3.3.4.20. Quad Sum Low Fault                                   |   | 3-39         |

| 3.3.4.21. Illegal Operation Code                               |   | 3-39         |

| 3.3.4.22. Invalid Logical Unit number                          |   | 3-39         |

| 3.3.4.23. Illegal Seek Address                                 | • | 3-39         |

| 3.3.4.24. Illegal Command Descriptor Block Parameter           |   | 3-39         |

| 3.3.4.25. End of Media Reached                                 |   | 3-39         |

| 3.3.4.26. Illegal Transfer Length                              |   | 3-39         |

| 3.3.4.27. SCSI I/O Parity Error                                |   | 3-39         |

| 3.3.4.28. Unable to Read Data Error                            |   | 3-39<br>3-40 |

| 3.3.4.29. Logical Block Address Not Found                      |   | 3-40         |

| 3.3.4.30. Unable to Write Data Error                           |   | 3-40         |

| 3.3.4.31. Internal Parity Error                                |   | 3-40         |

| 3.3.4.32. Servo/Drive Control Parity Error                     |   | 3-40         |

| 3.3.4.33. Modulator/Demodulator Synchronizer Parity Error      |   | 3-40         |

| 3.3.4.34. Error Correction Code Circuitry Fault                |   | 3-41         |

| 3.3.4.35. Voltage Fault                                        |   | 3-41         |

| 3.3.4.36. Invalid Bootstrap Load Error                         |   | 3-41         |

| 3.3.4.37. Laser Degraded                                       |   | 3-41         |

| 3.3.4.38. Power-Up Diagnostics Aborted                         |   | 3-41         |

| 3.3.4.39. Diagnostic Fault Detected                            |   | 3-41         |

| 3.3.4.40. Illegal Sequence (Device Not Ready)                  |   | 3-42         |

| 3.3.4.41. Write Protected Device Error                         |   | 3-42         |

| 3.3.4.42. Data Field Overwrite Error                           |   | 3-42         |

| 3.3.4.43. Empty Sector Detected                                |   | 3-42         |

| 3.3.4.44. Device Error                                         |   | 3-42         |

|                                                                |   |              |

| 3.4. INTERFACES                                                |   | 3-43         |

| 3.4.1. Definitions                                             |   | 3-43         |

| 3.4.2. Small Computer System Interface (SCSI)                  |   | 3-43         |

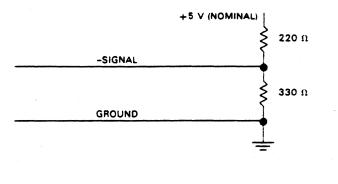

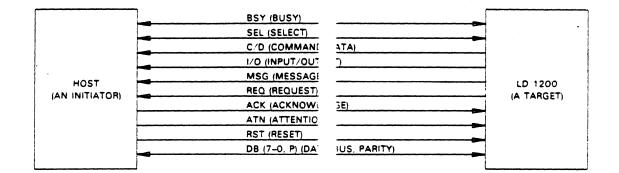

| 3.4.2.1. SCSI Hardware                                         |   | 3-43         |

| 3.4.2.2. SCSI Signal Definitions                               |   | 3-44         |

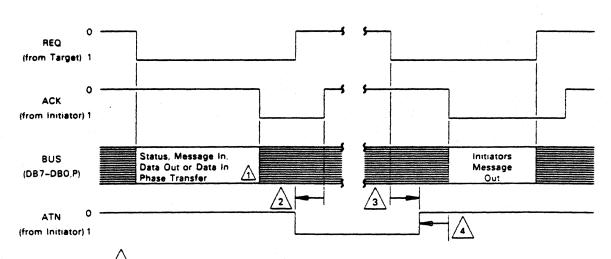

| 3.4.2.3. SCSI Bus Phases                                       |   | 3-45         |

| 3.4.2.4. SCSI Bus Conditions                                   |   | 3-50         |

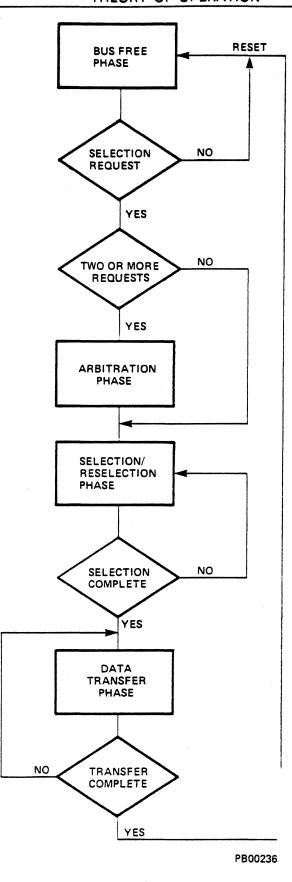

| 3.4.2.5. SCSI Bus Phase Sequences                              |   | 3-52         |

| 3.4.2.6. SCSI Pointers                                         |   | 3-55         |

| 3.4.2.7. Message System Specification                          |   | 3-55         |

| 3.4.2.8. SCSI Command Implementation                           |   | 3-58         |

| 3.4.2.9. Command Descriptor Block                              |   | 3-59         |

| 3.4.2.10. Command Examples                                     |   | 3-61         |

| 3.4.2.11. Group 0 Commands                                     |   | 3-62         |

| 3.4.2.12. Group 1 Commands                                     |   | 3-63         |

| 3.4.2.13. Completion Status Byte                               |   | 3-64         |

| 3.4.2.14. Sense Description                                    |   | 3-65         |

| 3.4.3. Internal Device Interface/System Interface Assembly Bus |   | 3-71         |

|            | OSI SCSI LD 1200                                                         |                |

|------------|--------------------------------------------------------------------------|----------------|

|            | PERIPHERAL EQUIPMENT REFERENCE MANUAL                                    |                |

| <b>D</b>   |                                                                          | 75114000 0     |

| Page: viii | TABLE OF CONTENTS                                                        | 75114902 B     |

|            |                                                                          |                |

|            |                                                                          |                |

|            | 3.4.3.1. SIA Bus Line Descriptions                                       | 3-73           |

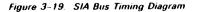

|            | 3.4.3.2. SIA Bus Timing                                                  | 3-74           |

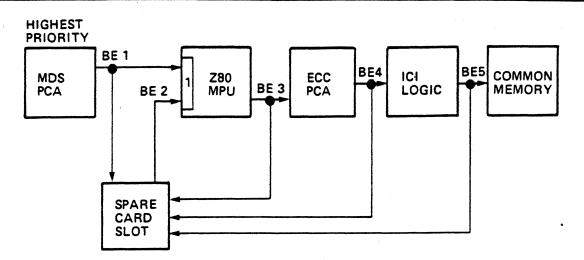

|            | 3.4.3.3. Bus Module Priority System                                      | 3-74           |

|            | 3.4.3.4. IDI Sequences                                                   | 3-76           |

|            | 3.4.3.5. Track and Sector Identification Registers                       | 3-84           |

|            | 3.4.3.6. Read/Write Command Registers                                    | 3-84           |

|            | 3.4.3.7. Drive Status and Control Registers                              | 3-85           |

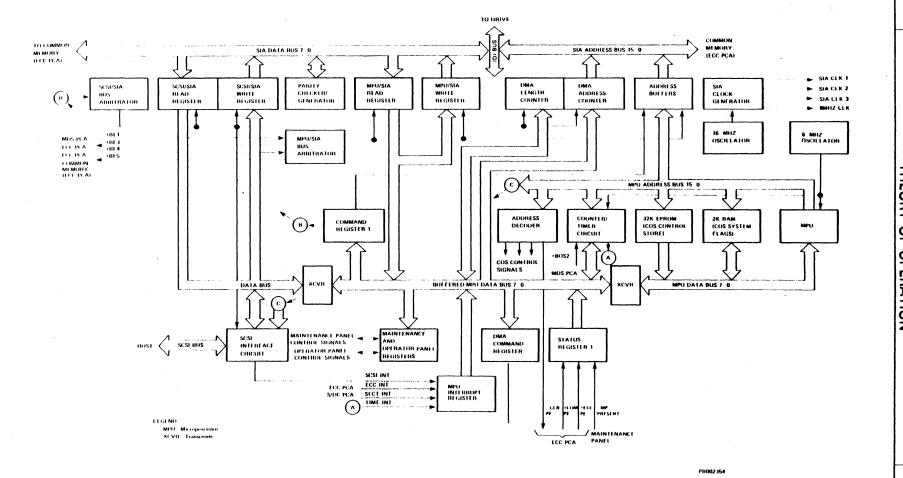

|            | 3.5. LD 1200 ADAPTER PCA                                                 | 3-92           |

|            | 3.5.1. Interface Signals                                                 | 3-95           |

|            | 3.5.2. I/O Ports                                                         | 3-97           |

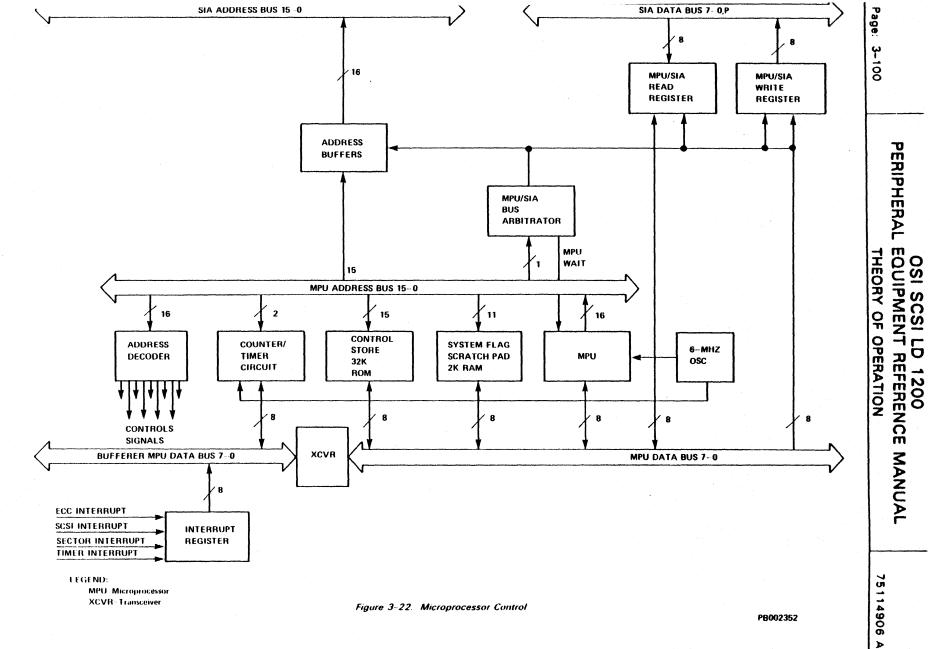

|            | 3.5.3. Microprocessor Control                                            | 3-99           |

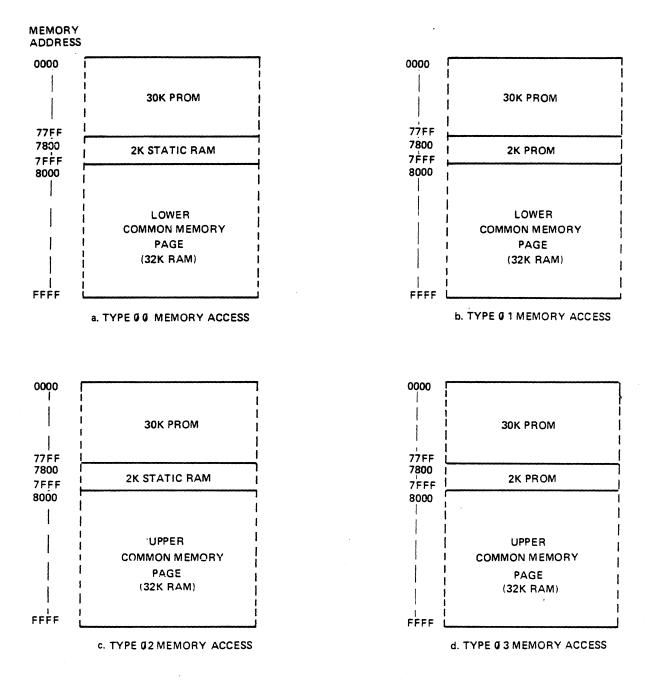

|            | 3.5.3.1. MPU Memory Control System                                       | 3-101          |

|            | 3.5.3.2. MPU/SIA Address Buses                                           | 3-102          |

|            | 3.5.3.3. Address Decoder                                                 | 3-102          |

|            | 3.5.3.4. MPU Timing Control                                              | 3-103          |

|            | 3.5.3.5. MPU Interrupt Register                                          | 3-103          |

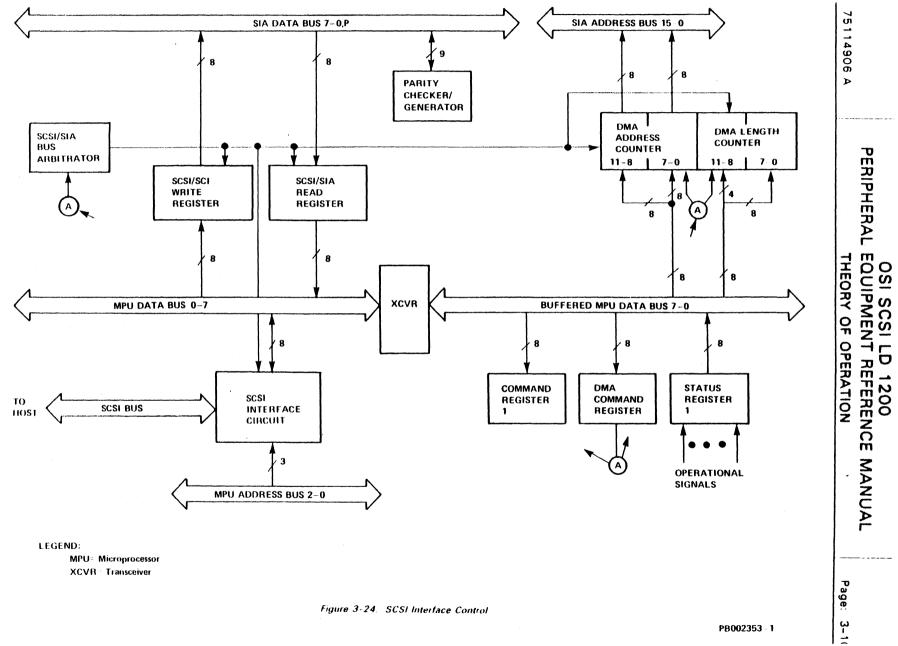

|            | 3.5.4. SCSI Interface Control                                            | 3-104          |

|            | 3.5.4.1. SCSI Interface Circuit                                          | 3-106          |

|            | 3.5.4.2. SCSI/SIA Write and Read Registers                               | 3-115          |

|            | 3.5.4.3. SCSI/Common Memory Direct Memory Access                         | 3-115          |

|            | 3.5.4.4. SCSI/SIA Bus Arbitrator                                         | 3-116          |

|            | 3.5.4.5. Parity Checker/Generator                                        | 3-117          |

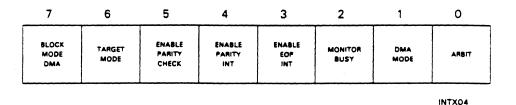

|            | 3.5.4.6. Command Register 1 (Port Write-97 hex)                          | 3-117          |

|            | 3.5.4.7. Status Register 1 (Port Read-94 hex)                            | 3-118          |

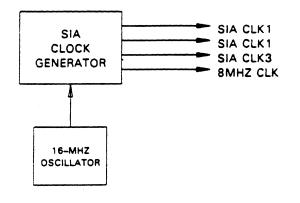

|            | 3.5.5. SIA Clock Generator                                               | 3-118          |

|            | 3.5.6. Operator and Maintenance Panel External Registers                 | 3-119          |

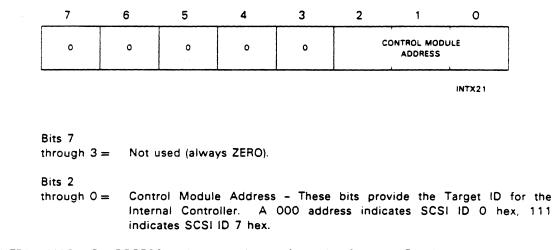

|            | 3.5.6.1. Device Address Switch Register (Port Read-95 hex)               | 3-121          |

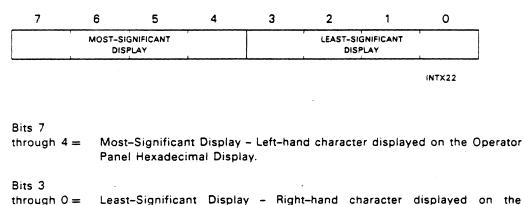

|            | 3.5.6.2. Operator Panel Hexadecimal Display Register (Port Write-94 hex) | 3-121          |

|            | 3.5.6.3. Maintenance Panel LED Register (Port Write-95 hex)              | 3-122          |

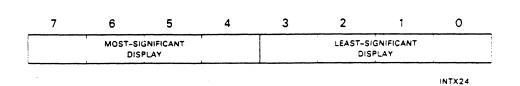

|            | 3.5.6.4. Maintenance Panel Hexadecimal Display Register (Port Write-96   | 3-122          |

|            | hex)<br>3.5.6.5. Maintenance Panel Keyboard Register (Port Read–97 hex)  | 3-123          |

|            | 5.5.0.5. Maintenance ranei Reyboard negister (ron nead-57 nex)           | 3-123          |

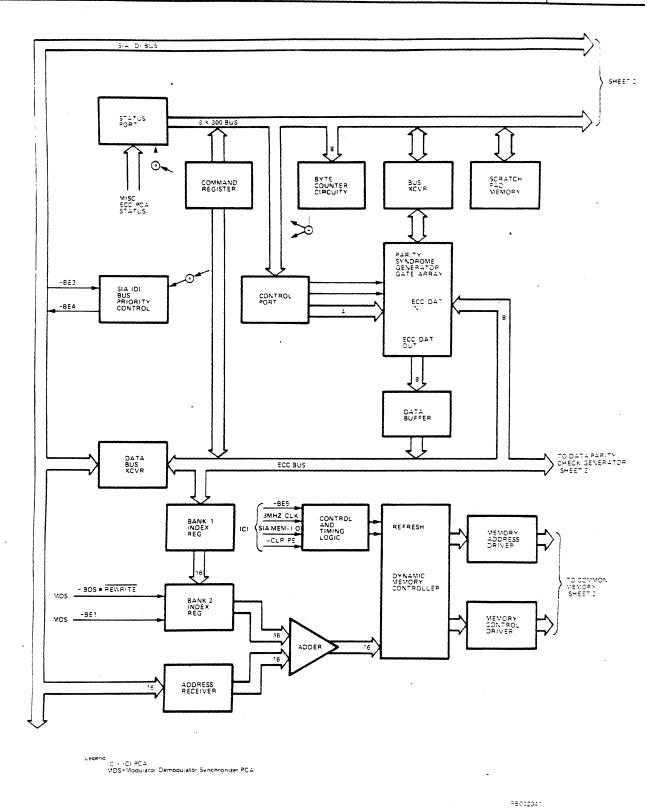

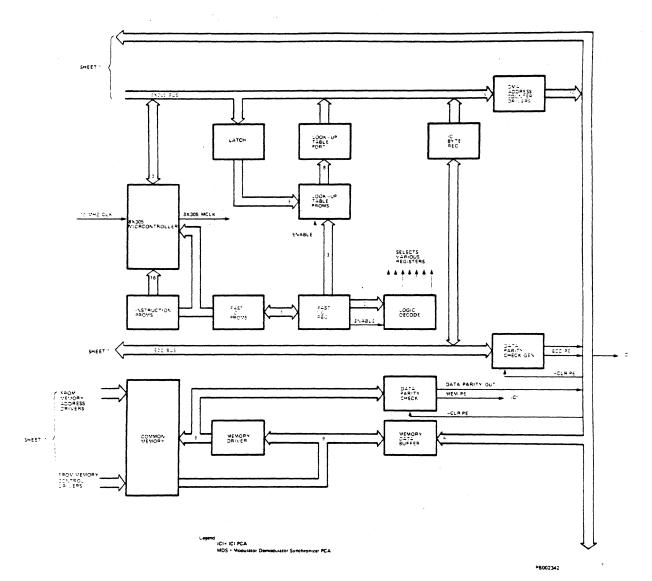

|            | 3.6. ERROR CORRECTION AND COMMON MEMORY INTERFACE UNIT<br>PCA            | 3-124          |

|            | 3.6.1. Signal Interface Descriptions                                     | 3-127          |

|            | 3.6.2. SIA/IDI Bus                                                       | 3-128          |

|            | 3.6.2.1. SIA/IDI Address Bus                                             | 3-128          |

|            | 3.6.2.2. SIA/IDI Data Bus                                                | 3-128          |

|            | 3.6.2.3. SIA/IDI Bus Control Signals                                     | 3-128          |

|            | 3.6.2.4. SIA/IDI Bus Clock Signals                                       | 3-128          |

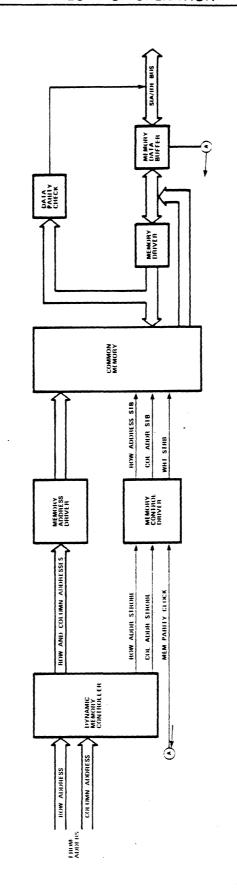

|            | 3.6.3. Common Memory Interface                                           | 3-129          |

|            | 3.6.3.1. Address Receivers                                               | 3-129          |

|            | 3.6.3.2. Data Bus Transceiver                                            | 3-130          |

|            | 3.6.3.3. Bank 1 Index Registers                                          | 3-130          |

|            | 3.6.3.4. Bank 2 Index Registers                                          | 3-130          |

|            | 3.6.3.5. Adders                                                          | 3-130          |

|            | 3.6.3.6. Control and Timing Logic                                        | 3-130          |

|            | 3.6.3.7. Dynamic Memory Controller                                       | 3-130          |

|            | 3.6.3.8. Memory Address Driver                                           | 3-132          |

|            | 3.6.3.9. Memory Control Driver                                           | 3-132<br>3-132 |

|            | 3.6.3.10. Common Memory<br>3.6.3.11. Memory Data Buffer                  | 3-132<br>3-133 |

|            | 3.6.3.12. Memory Data buffer                                             | 3-133          |

|            |                                                                          |                |

OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL

#### 'age: x

# TABLE OF CONTENTS

75114902 B

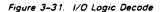

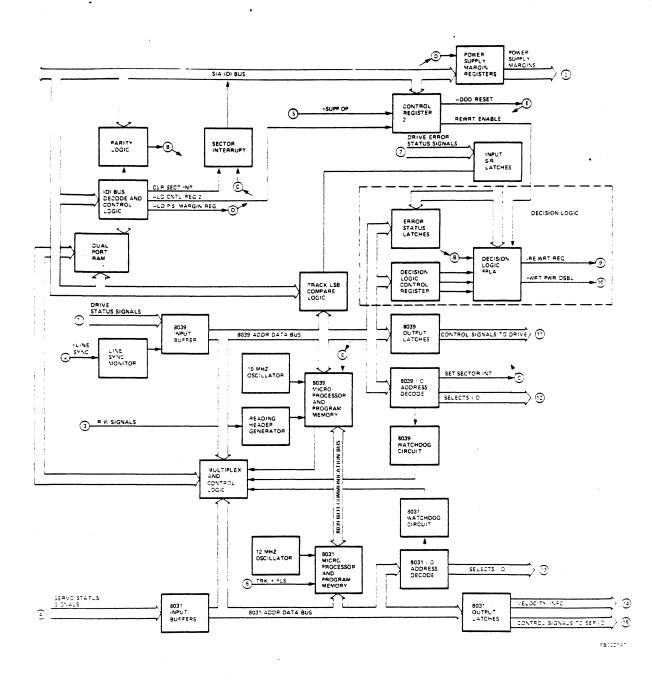

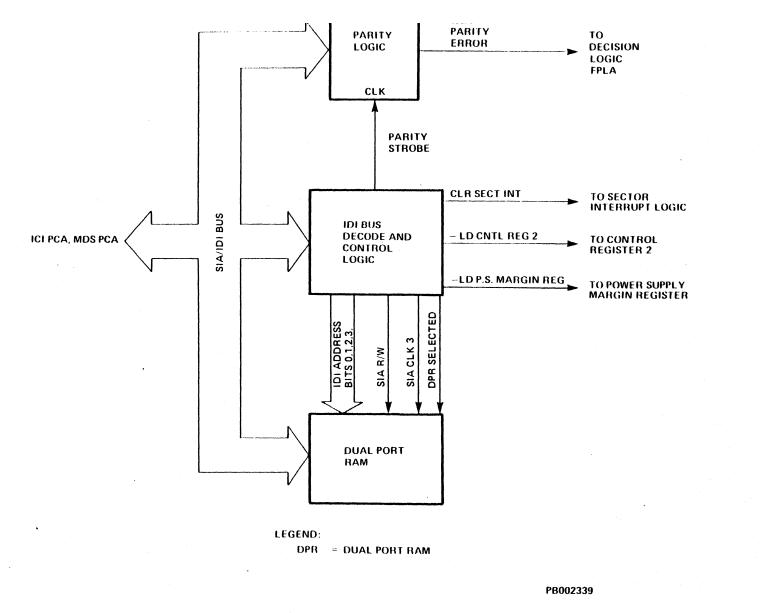

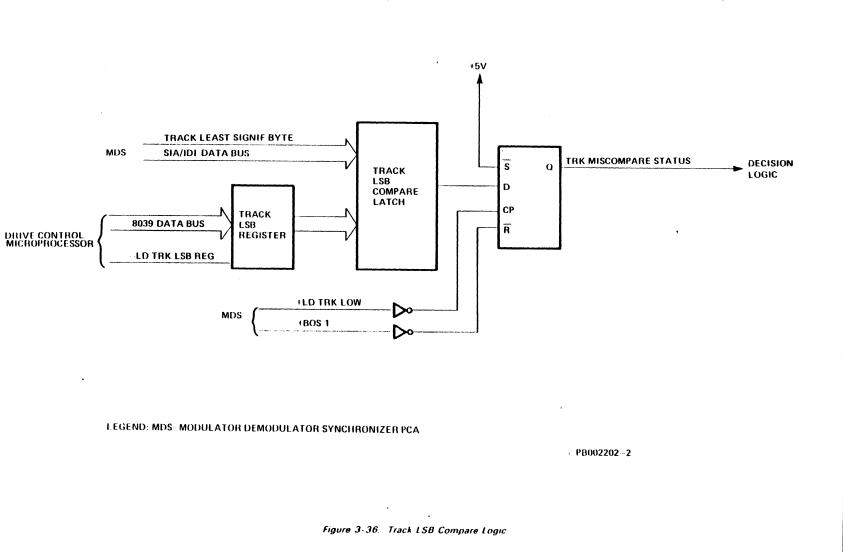

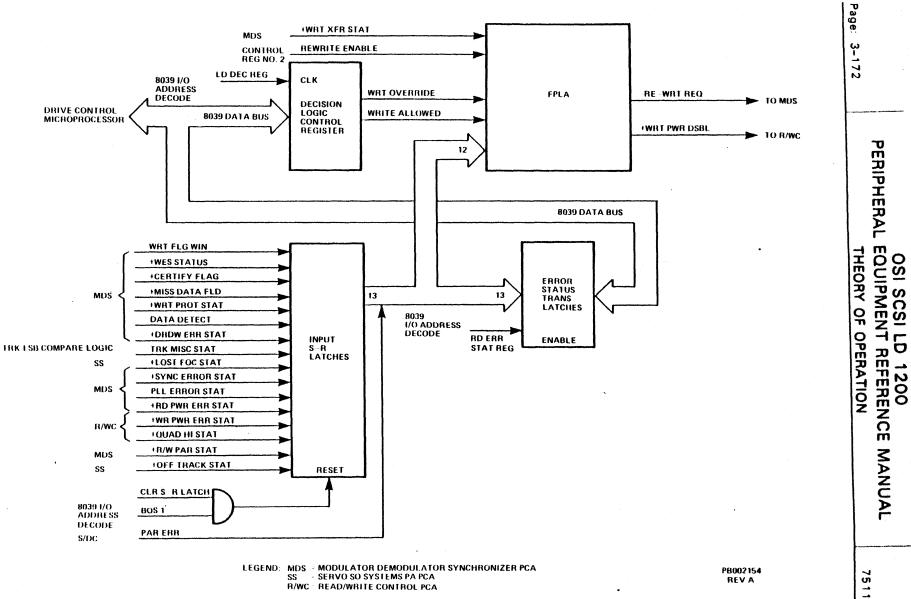

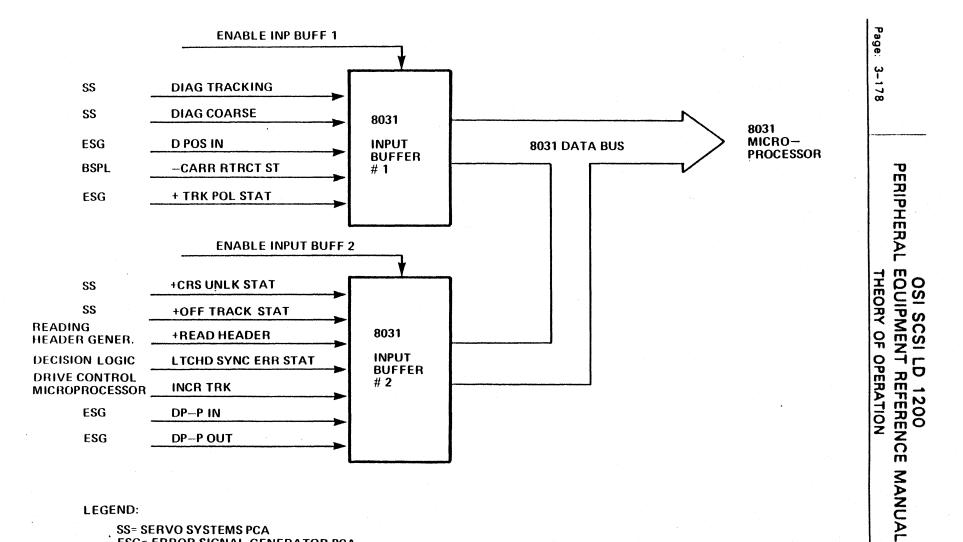

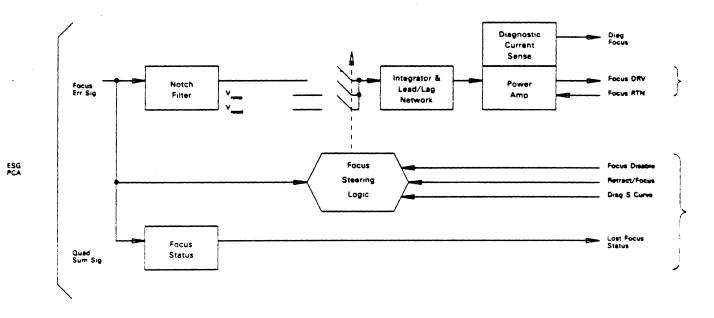

3.7.14. 8039 Output Latches 3-165 3.7.15. 8039 I/O Address Decode 3-168 3.7.16. Sector Interrupt 3-169 3.7.17. 8039 Watchdog Circuit 3.7.18. Track LSB Compare Logic 3-170 3-170 3.7.19. Decision Logic 3-170 3.7.19.1. Decision Logic Interface Signals 3-170 3.7.19.2. Input S-R Latches 3-176 3.7.19.3. Error Status Transfer Latch 3-176 3.7.19.4. Decision Logic Control Register 3-177 3.7.19.5. Field Programmable Logic Array (FPLA) 3-177 3.7.20. 8031 Input Buffers 3-177 3.7.21. 12-MHz Oscillator 3-180 3.7.22. 8031 Microprocessor and Program Memory 3-180 3.7.23. 8031 Output Latches 3-180 3.7.24. 8031 I/O Address Decode 3-183 3.7.25. 8031 Watchdog Circuit 3-184 3.8. SERVO SYSTEMS PCA 3-184 3.8.1. Signal Descriptions 3-184 3.8.2. Focus Servo Loop 3-189 3.8.2.1. Focus Servo Error Recovery 3-191 3.8.3. Fine Tracking Servo Loop 3-193 3.8.3.1. Tracking Servo Loop Error Recovery 3-196 3.8.4. Coarse Tracking Servo Loop 3-198 3.8.4.1. Coarse Tracking Loop Error Recovery 3-200 3.9. ERROR SIGNAL GENERATOR PCA 3-202 3.9.1. Interface Signal Descriptions 3-203 3.9.2. Focus and Tracking AGCs 3-206 3.9.2.1. Focus AGC 3-206 3.9.2.2. AGC Reference 3-206 3.9.2.3. Tracking AGC 3.9.2.4. High-Pass Filter 3-206 3-206 3.9.3. Tracking Wobble Circuitry 3-208 3.9.3.1. Wobble Sample and Hold 3-208 3.9.3.2. Low-Pass Filter 3-208 3.9.4. Summing Amplifier and Low Pass Filter 3-208 3.9.5. Track Crossing Circuitry 3-210 3.9.6. FSM Position Offset Circuitry 3-210 3.9.7. Overtemperature Circuitry 3-210 3.9.8. Diagnostics 3-211 3.9.8.1. D S-Curve In 3-211 3.9.8.2. D S-Curve Out 3-211 3.9.8.3. D P-P In 3-212 3.9.8.4. D P-P Out 3-212 3.9.8.5. D POS IN 3-21.2 3.10. READ/WRITE CONTROL PCA 3-213 3.10.1. Interface Signals 3-217 3.10.2. Initialization Circuit 3-223 3.10.3. Initialization Switch 3-223 3.10.4. Laser Power Check Circuit 3-223 3.10.5. Read Power Control Disable 3-224 3.10.6. Read Power Control Circuit 3-224

. •

OSI SCSI LD 1200

|    |   |   |   | - | - | - | - |  |

|----|---|---|---|---|---|---|---|--|

| 75 | 1 | 1 | 4 | 9 | 0 | 2 | 8 |  |

# PERIPHERAL EQUIPMENT REFERENCE MANUAL TABLE OF CONTENTS

Page: xi

1

| 3.10.7. Read Power Switch                                  | 3-224 |

|------------------------------------------------------------|-------|

| 3.10.8. Read Power Current Source                          | 3-225 |

| 3.10.9. Read Current Detection                             | 3-225 |

| 3.10.10. Write Power Control Disable                       | 3-225 |

| 3.10.11. Write Power Control Circuit                       | 3-226 |

| 3.10.12. Write Power Switch                                | 3-226 |

| 3.10.13. Write Power Current Source                        | 3-226 |

| 3.10.14. Write Current Detection                           | 3-226 |

| 3.10.15. Dying Status Circuit                              | 3-227 |

| 3.10.16. Quad Sum Too High Detection                       | 3-227 |

| 3.10.17. Logic                                             | 3-227 |

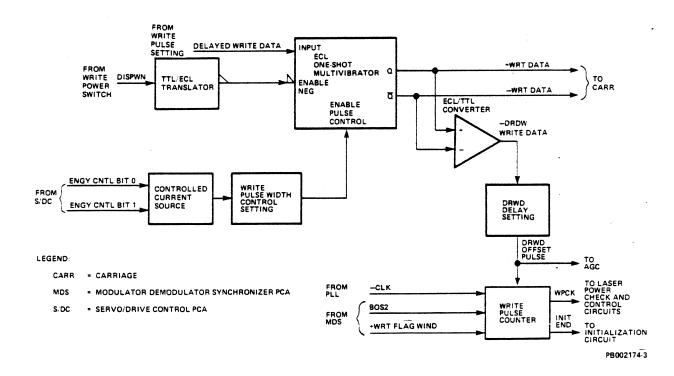

| 3.10.18. Write Pulse Delay Setting                         | 3-227 |

| 3.10.19. Write Pulse Width Setting                         | 3-228 |

| 3.10.20. DRDW Delay Setting                                | 3-229 |

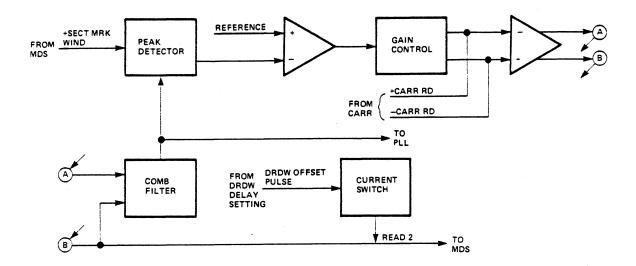

| 3.10.21. Automatic Gain Control                            | 3-229 |

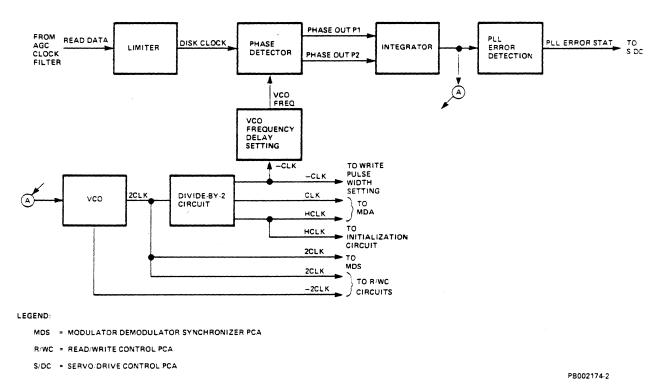

| 3.10.22. Phase-Locked Loop and VCO Frequency Delay Setting | 3-230 |

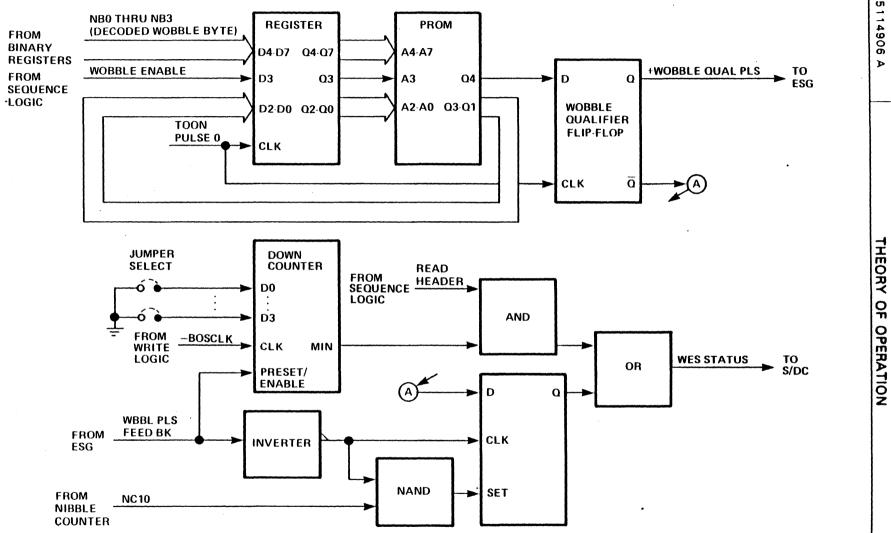

| 3.10.23. Wobble Detection                                  | 3-232 |

| 3.10.24. Carriage Power Supply Interconnect                | 3-232 |

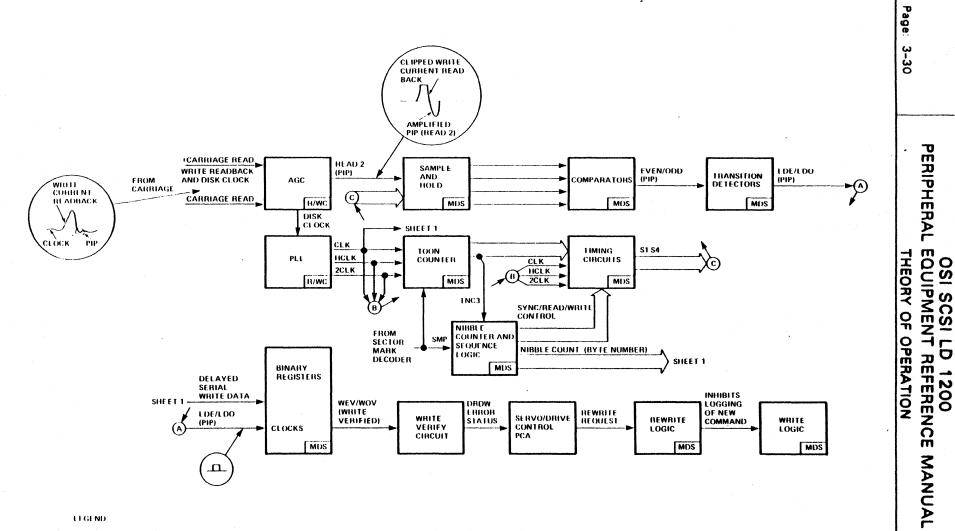

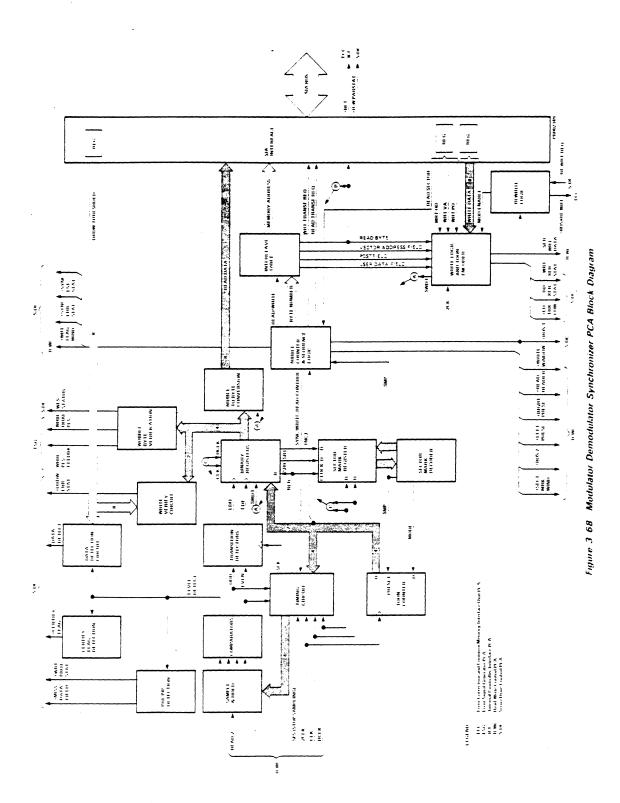

| 3.11. MODULATOR DEMODULATOR SYNCHRONIZER PCA               | 3-233 |

| 3.11.1. Interface Signals                                  | 3-236 |

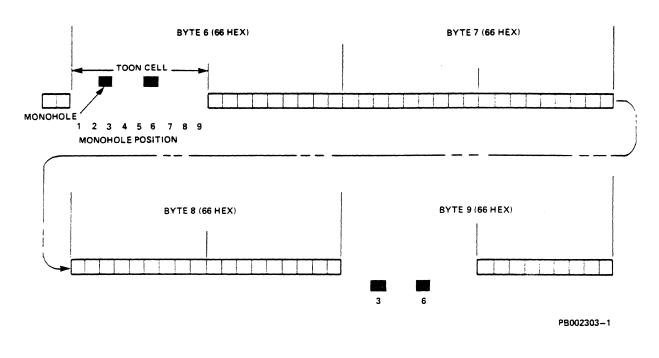

| 3.11.2. TOON Counter                                       | 3-241 |

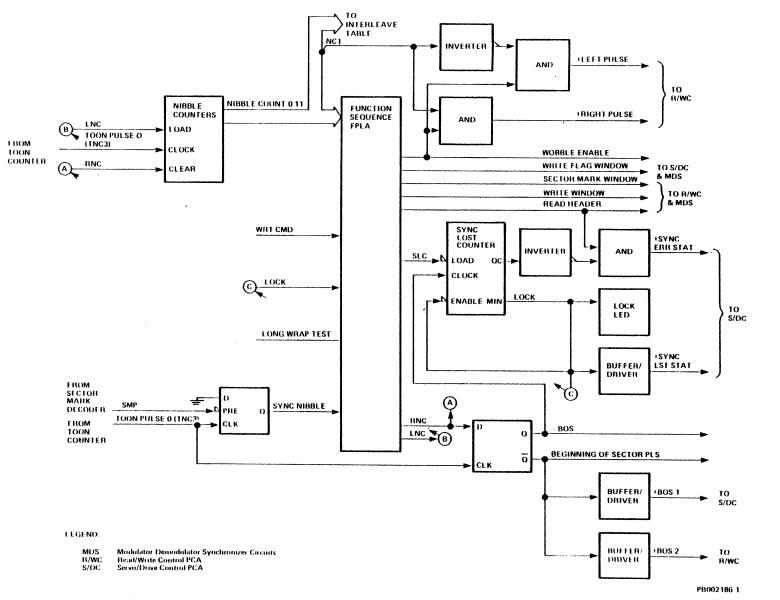

| 3.11.3. Nibble Counter and Sequence Logic                  | 3-241 |

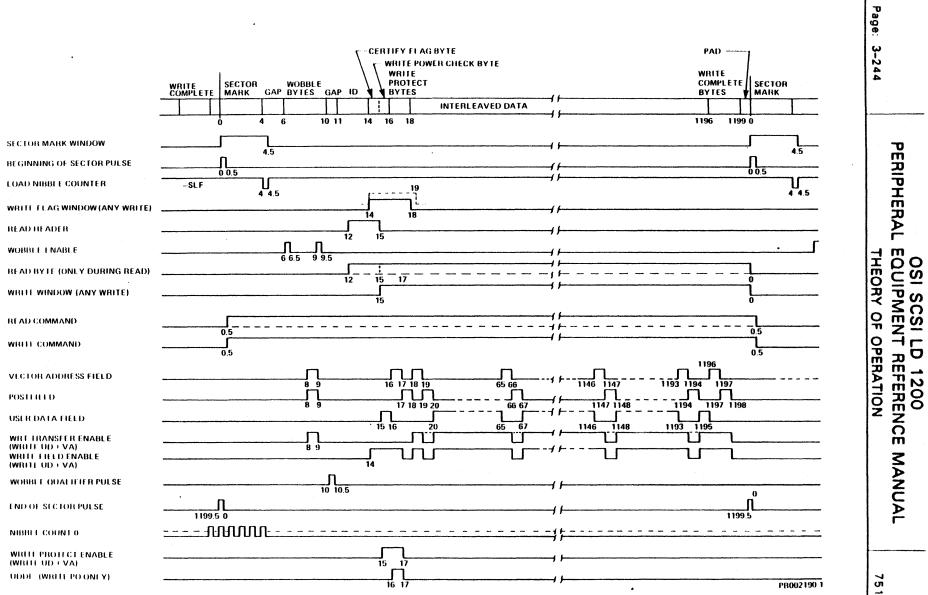

| 3.11.4. Timing Circuit                                     | 3-246 |

| 3.11.4.1. Sector Mark Detection Timing                     | 3-246 |

| 3.11.4.2. Data Read Timing                                 | 3-247 |

| 3.11.4.3. Write Verify Timing                              | 3-249 |

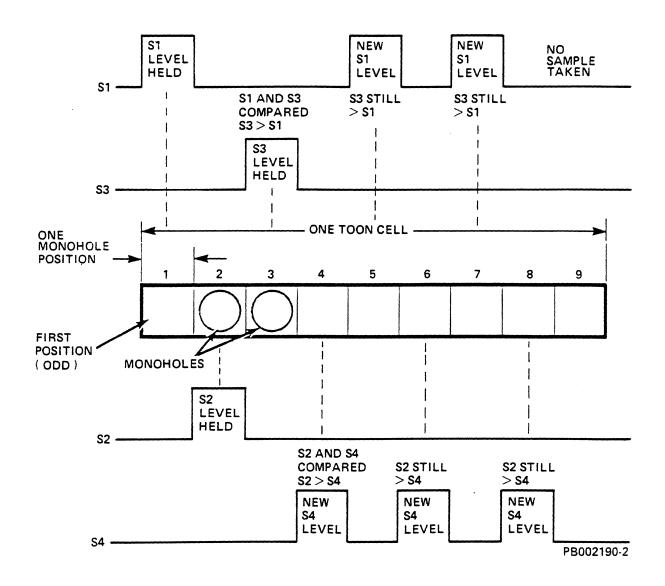

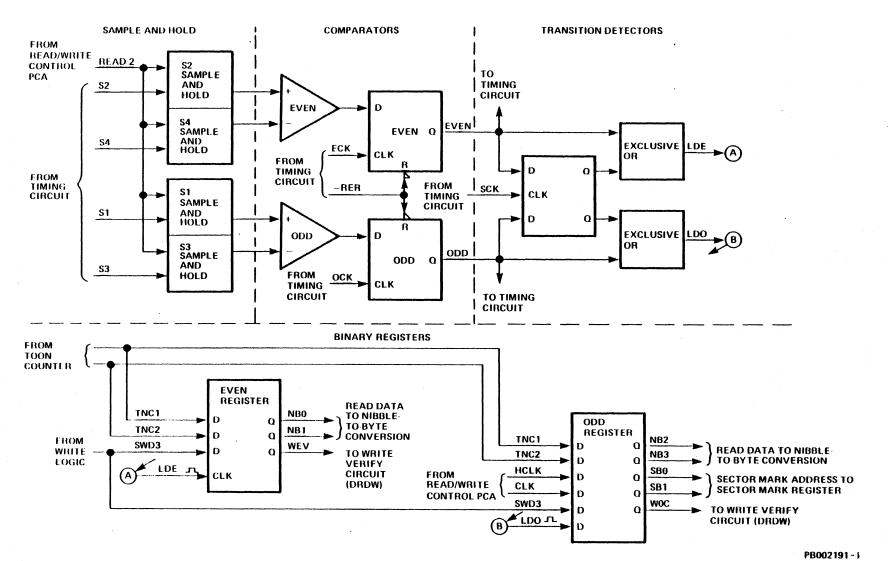

| 3.11.5. Sample and Hold                                    | 3-250 |

| 3.11.6. Comparators                                        | 3-250 |

| 3.11.7. Transition Detectors                               | 3-253 |

| 3.11.8. Binary Registers                                   | 3-253 |

| 3.11.8.1. Sector Mark Search Mode                          | 3-253 |

| 3.11.8.2. Data Read Mode                                   | 3-253 |

| 3.11.8.3. Write Verify Mode                                | 3-254 |

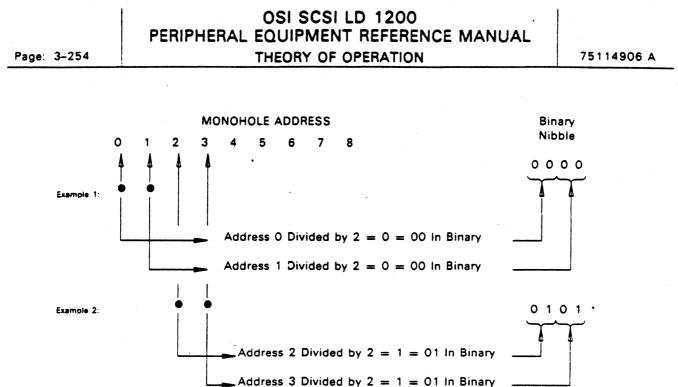

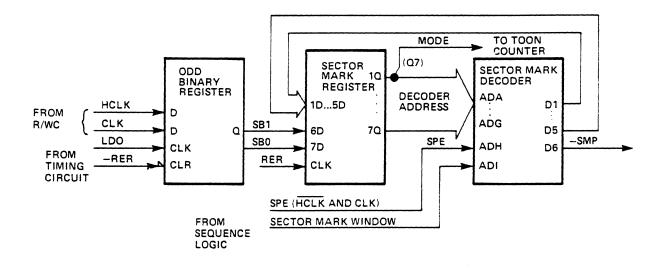

| 3.11.9. Sector Mark Register and Decoder                   | 3-254 |

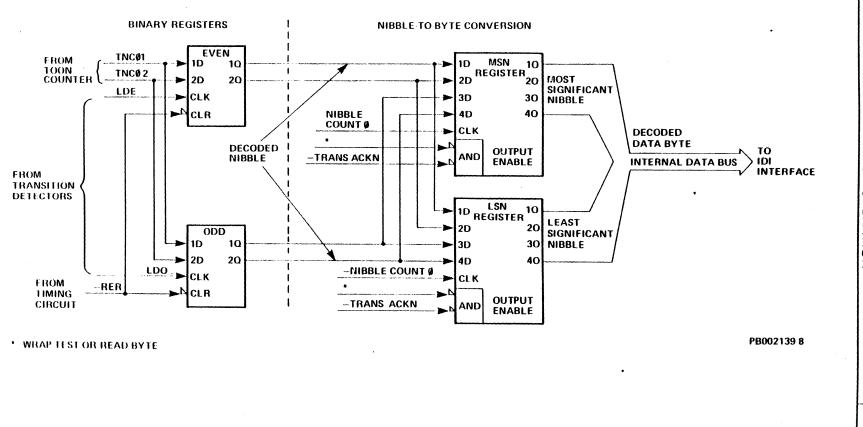

| 3.11.10. Nibble-to-Byte Conversion                         | 3-256 |

| 3.11.11. Interleave Table                                  | 3-258 |

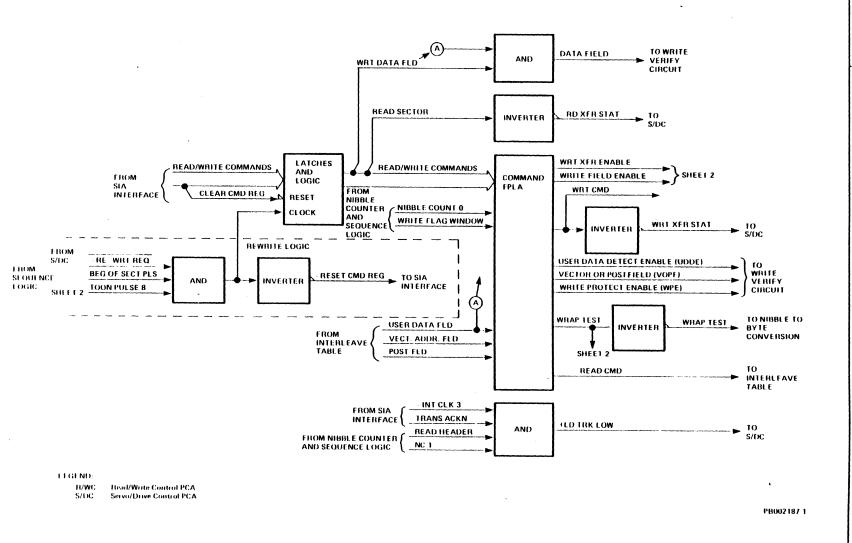

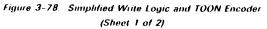

| 3.11.12. Write Logic and TOON Encoder                      | 3-264 |

| 3.11.13. Rewrite Logic                                     | 3-267 |

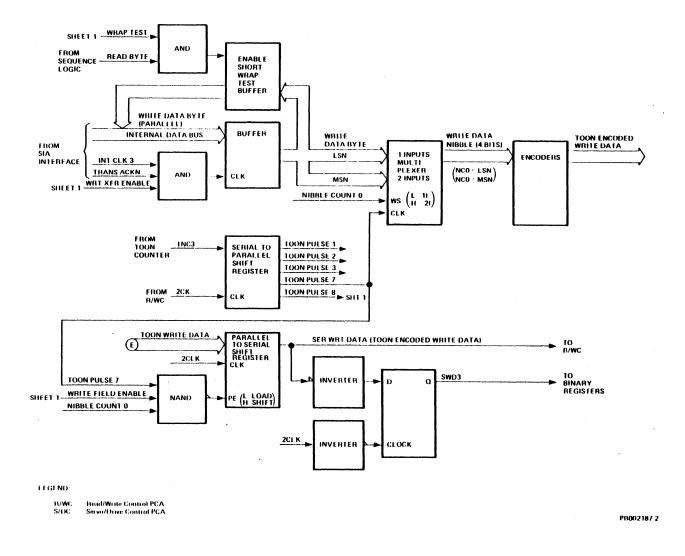

| 3.11.14. SIA Interface                                     | 3-267 |

| 3.11.15. Pre-PIP Detection                                 | 3-272 |

| 3.11.16. Certify Flag Detection                            | 3-273 |

| 3.11.17. Data Detection Circuit                            | 3-273 |

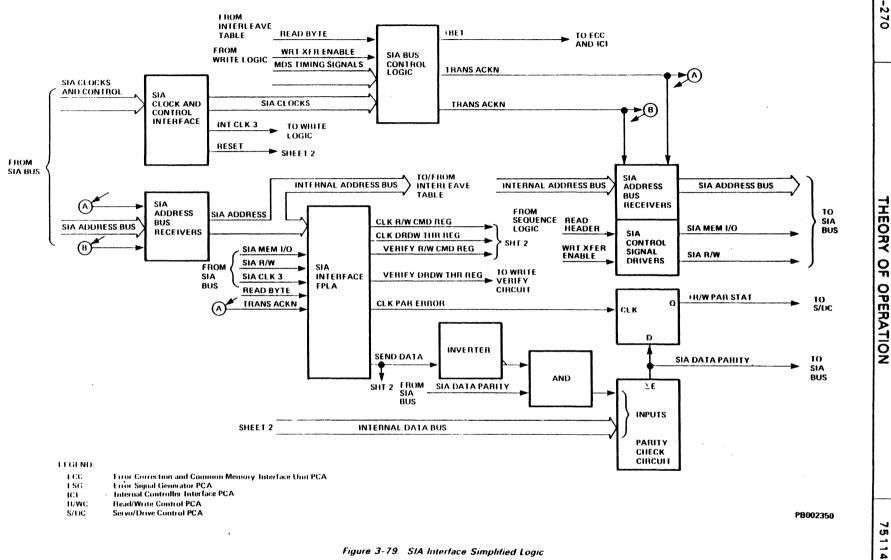

| 3.11.18. Write Verify Circuit                              | 3-273 |

| 3.11.19. Wobble Byte Verification                          | 3-276 |

| 3.12. CARRIAGE                                             | 3-278 |

| 3.12.1. Interface Signals                                  | 3-280 |

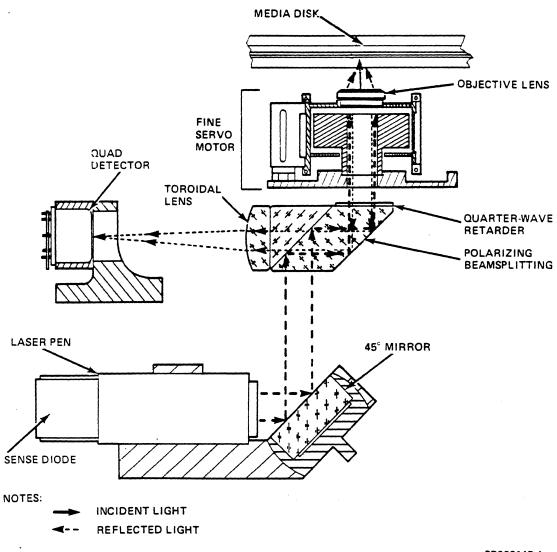

| 3.12.2. Optical System                                     | 3-282 |

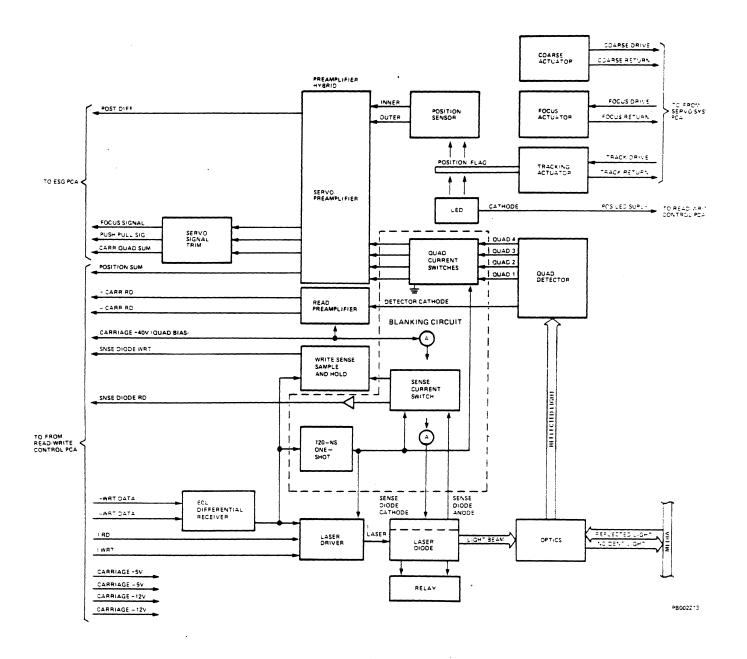

| 3.12.3. Electronics System                                 | 3-284 |

| 3.12.3.1. ECL Differential Receiver                        | 3-284 |

| 3.12.3.2. Laser Driver                                     | 3-284 |

| 3.12.3.3. Laser Diode                                      | 3-285 |

| 3.12.3.4. Sense Diode                                      | 3-285 |

| 3.12.3.5. Relay                                            | 3-235 |

|            | OSI SCSI LD 1200    |        |

|------------|---------------------|--------|

| PERIPHERAL | EQUIPMENT REFERENCE | MANUAL |

TABLE OF CONTENTS

75114902 B

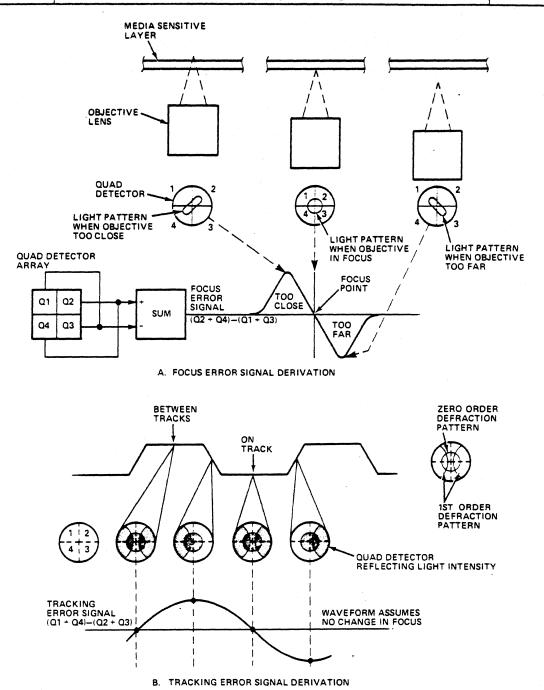

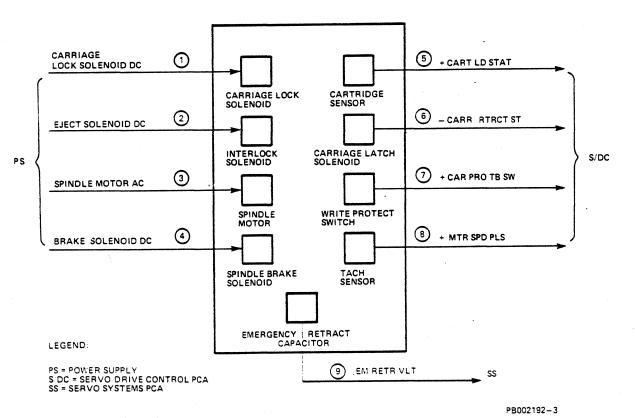

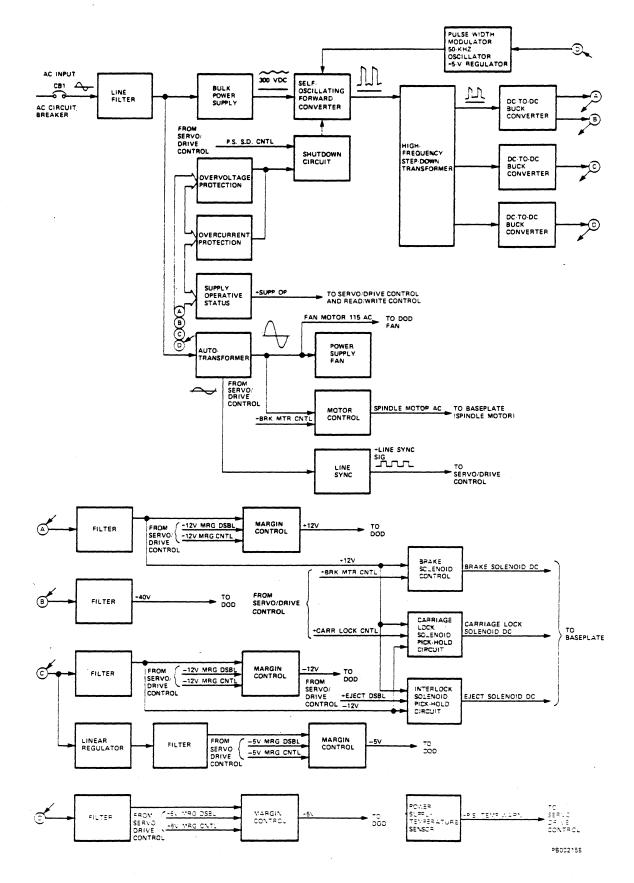

3.12.3.6. Blanking Circuit 3-285 3.12.3.7. Quad Detector 3-286 3.12.3.8. Write Sense Sample and Hold 3-287 3.12.3.9. Position Sensor, Position Flag, and LED 3-287 3.12.3.10. Servo Preamplifier 3.12.3.11. Servo Signal Trim 3.12.3.12. Read Preamplifier 3-287 3-287 3-289 3.12.4. Electromechanical System 3-289 3.13. MEDIA 3-290 3.13.1. Surface Format 3-291 3.13.2. Data Recording Format 3-297 3.14. BASEPLATE 3-301 3.14.1. Signal Descriptions 3-301 3.14.2. Functional Description 3-303 3.15. POWER SUPPLY 3-304 3.15.1. Input Specifications 3-305 3.15.2. Output Specifications 3.15.3. Interface Signals 3-305 3-305 3.15.4. Block Diagram Description 3-311 3.15.4.1. AC Circuit Breaker 3-311 3.15.4.2. Line Filter 3-311 3.15.4.3. Bulk Power Supply 3-311 3.15.4.4. Self-Oscillating Forward Converter 3-312 3.15.4.5. Pulse Width Modulator, 50-kHz Oscillator, +5V Regulator 3-312 3.15.4.6: High-Frequency Step-Down Transformer 3-312 3.15.4.7. DC-to-DC Buck Converters 3-312 3.15.4.8. Filters 3-312 3.15.4.9. Linear Regulator 3-312 3.15.4.10. Margin Controls 3-313 3.15.4.11. Overvoltage Protection 3-313 3.15.4.12. Undervoltage Protection 3-313 3.15.4.13. Shutdown Circuit 3.15.4.14. Supply Operative Status 3-313 3-313 3.15.4.15. Autotransformer 3-313 3.15.4.16. Power Supply Fan 3-314 3.15.4.17. Motor Control 3-314 3.15.4.18. Line Sync 3-314 3.15.4.19. Brake Solenoid Control 3-314 3.15.4.20. Carriage Lock Solenoid Pick-Hold Circuit 3-314 3.15.4.21. Interlock Solenoid Pick-Hold Circuit 3-314 3.15.4.22. Power Supply Temperature Sensor 3-314 3.16. OPERATOR PANEL 3-315 3.17. MAINTENANCE PANEL 3-318 APPENDIX A. GLOSSARY A-1

Page: xii

OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL TABLE OF CONTENTS

## 75114902 B

# Figures

| -                                                                                           |              |

|---------------------------------------------------------------------------------------------|--------------|

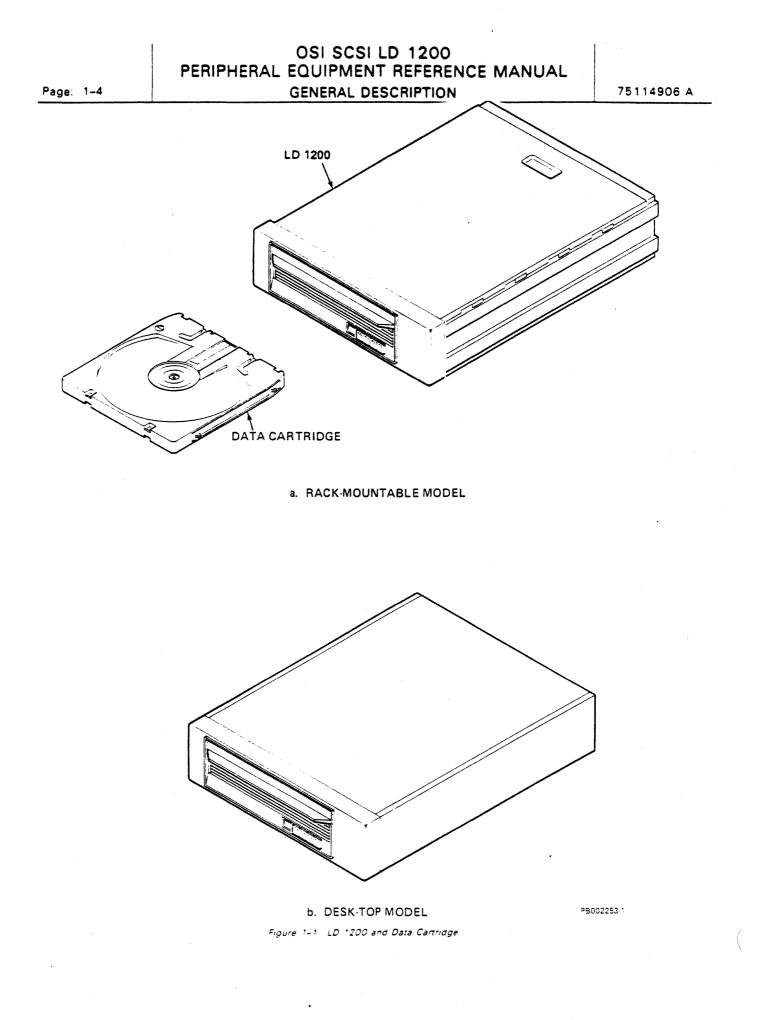

| Figure 1–1. LD 1200 and Data Cartridge                                                      | 1-4          |

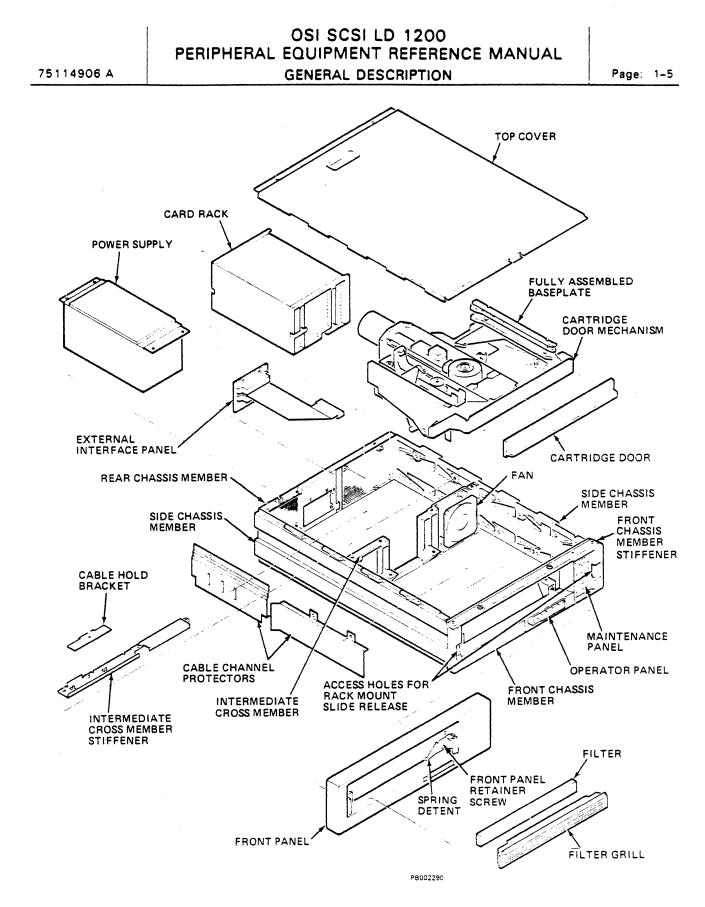

| Figure 1-2. LD 1200 Major Assemblies                                                        | 1-5          |

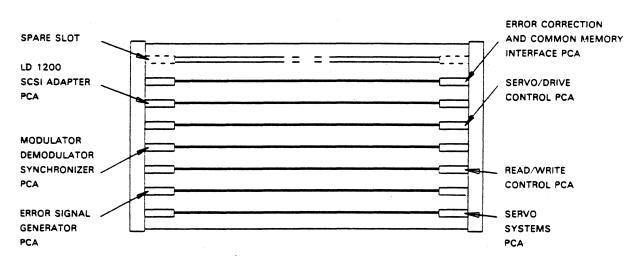

| Figure 1–3. Card Cage, Front View                                                           | 1-6          |

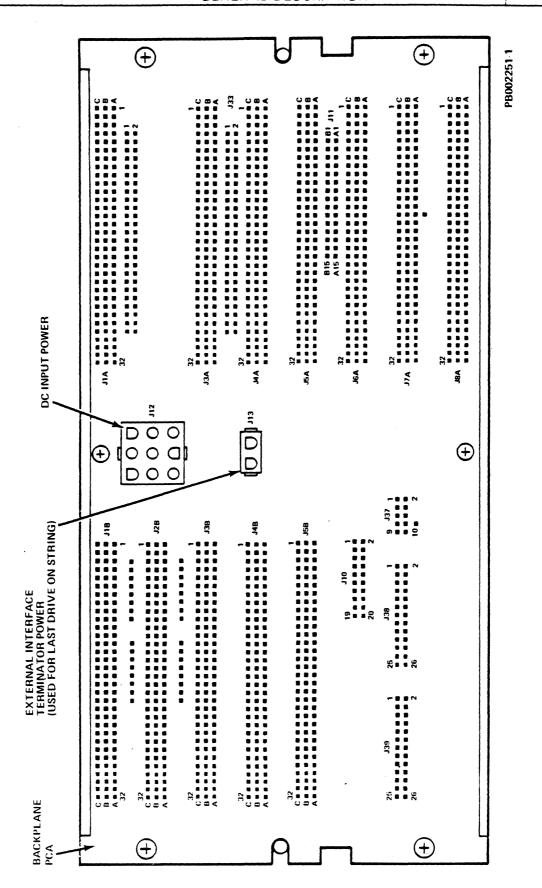

| Figure 1–4. Card Rack, Rear View                                                            | 1-7          |

| Figure 1-5. LD 1200 SCSI Adapter PCA, Component Side                                        | 1-9          |

| Figure 1–6. Modulator Demodulator Synchronizer PCA, Component Side                          | 1-10         |

| Figure 1-7. Read/Write Control PCA, Component Side                                          | 1-11         |

| Figure 1–8. Power Supply Cable Connections                                                  | 1-14         |

| Figure 1–9. Baseplate, Top View                                                             | 1-15         |

| Figure 1–10. Baseplate, Bottom View                                                         | 1-17         |

| Figure 1-11. LD 1200 Rear Panel                                                             | 1-18         |

| Figure 2-1. LD 1200 Controls/Indicators and Cartridge Loading                               | 2-2          |

| Figure 2-2. Data Cartridge Write Protection                                                 | 2-10         |

| Figure 2-3. LD 1200 Maintenance Panel Access                                                | 2-14         |

| Figure 2-4. LD 1200 Diagnostic Modes of Operation                                           | 2-15         |

| Figure 2-5. Memory Access Maps                                                              | 2-19         |

| Figure 3-1. LD 1200 Block Diagram                                                           | 3-2          |

| Figure 3-2. Drive Control Microprocessor Ready/Idle State                                   | 3-8          |

| Figure 3-3. Error Signal Generator Circuitry                                                | 3-11         |

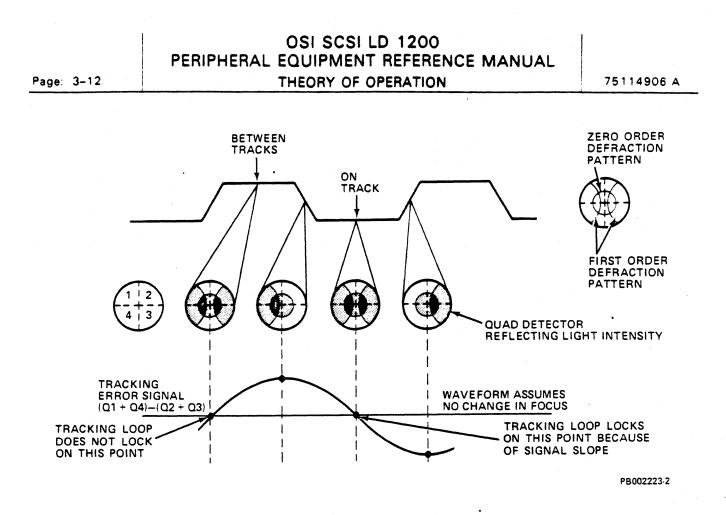

| Figure 3-4. Quad Detector Tracking Signal                                                   | 3-12         |

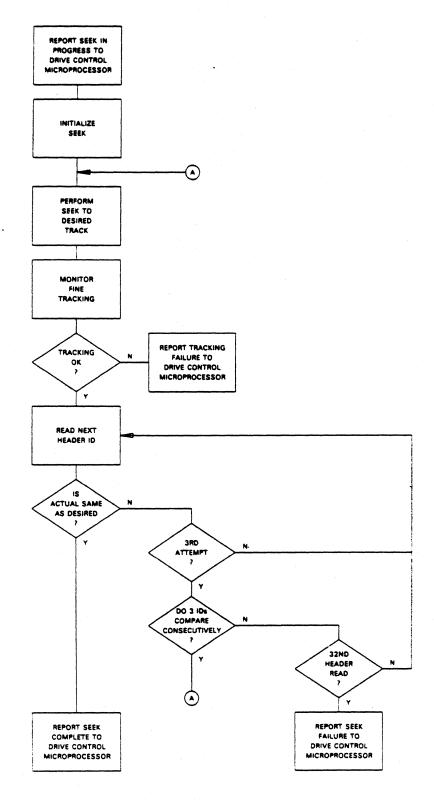

| Figure 3-5. Servo Microprocessor Seek Flow Chart                                            | 3-14         |

| Figure 3–6. Jumpback Operation                                                              | 3-16         |

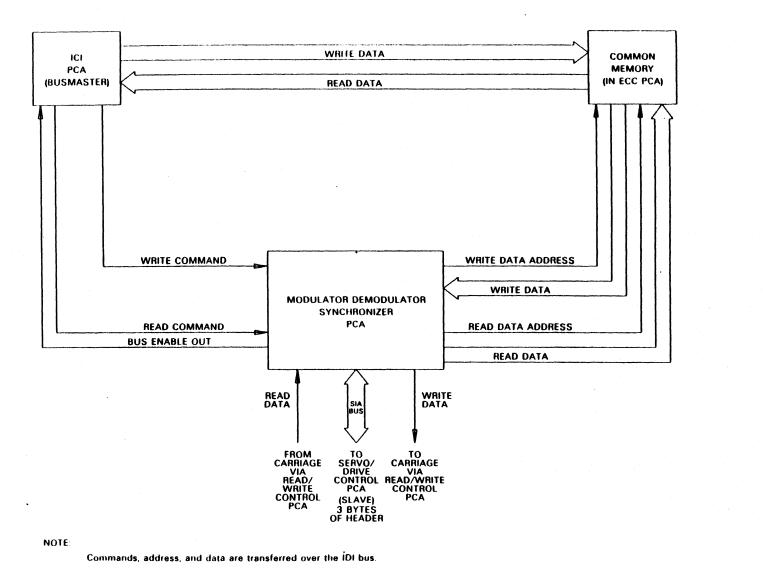

| Figure 3-7. Read and Write Protocol Paths                                                   | 3-18         |

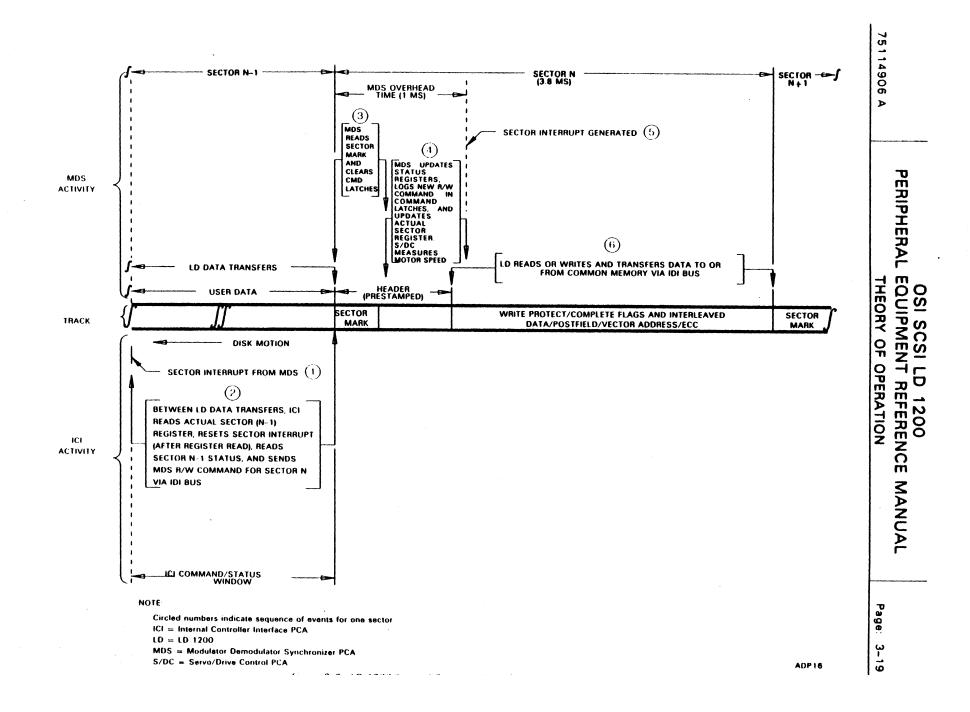

| Figure 3-8. LD 1200/Internal Controller Read/Write Sequence                                 | 3-19         |

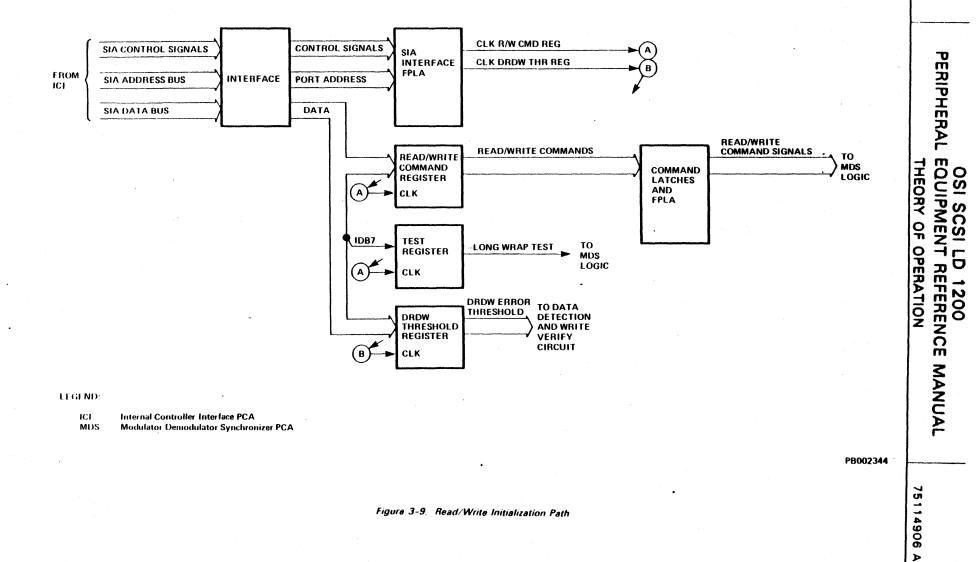

| Figure 3-9. Read/Write Initialization Path                                                  | 3-22         |

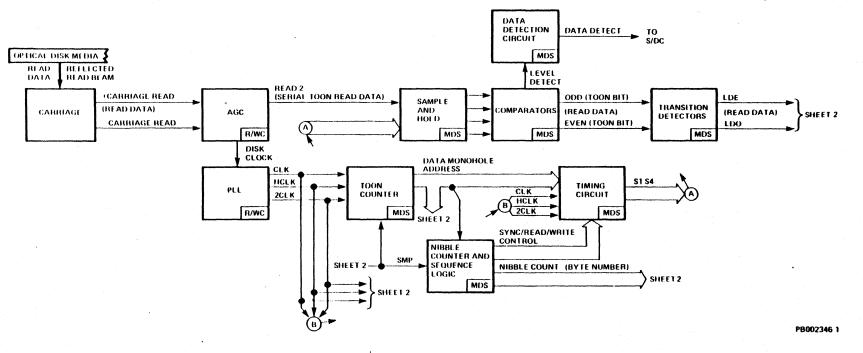

| Figure 3-10. Read Data Path                                                                 | 3-24         |

| Figure 3-11. Write Data Path                                                                | 3-29         |

| Figure 3-12. Termination for Single-Ended Devices                                           | 3-44         |

| Figure 3-13. SCSI Interface Signals                                                         | 3-45         |

| Figure 3-14. Attention Condition Sequence                                                   | 3-52         |

| Figure 3-15. Phase Sequence with Arbitration                                                | 3-54<br>3-55 |

| Figure 3-16. Simplified SCSI System                                                         | 3-55         |

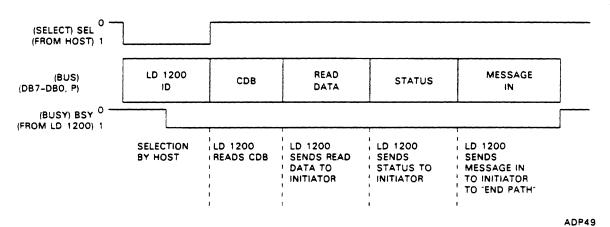

| Figure 3–17. Single Command Example with Data Transfer to the Host                          | 3-01         |

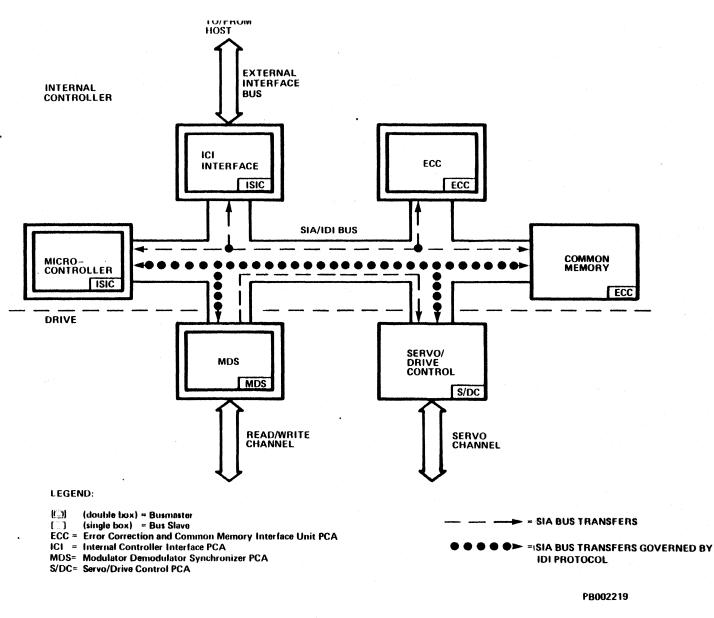

| Figure 3–18. LD 1200 SIA/IDI Bus Configuration                                              | 3-72         |

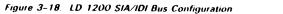

| Figure 3–19. SIA Bus Timing Diagram<br>Figure 3–20. LD 1200 SIA Bus Priority                | 3-75         |

| Figure 3-20. LD 1200 STA bus Friding<br>Figure 3-21. LD 1200 SCSI Adapter PCA Block Diagram | 3-94         |

| Figure 3–21. Microprocessor Control                                                         | 3-94         |

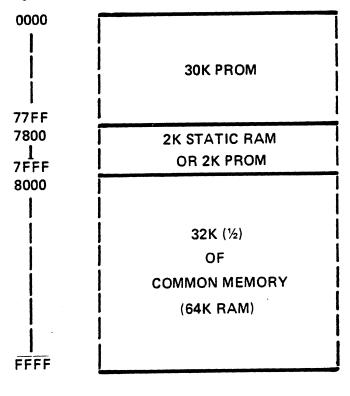

| Figure 3–23. MPU Memory Map                                                                 | 3-101        |

| Figure 3–24. SCSI Interface Control                                                         | 3-105        |

| Figure 3–24. SCSI interface Control<br>Figure 3–25. SIA Clock Generator                     | 3-119        |

| Figure 3–26. Operator and Maintenance Panel External Registers                              | 3-120        |

| Figure 3–27. Error Correction and Common Memory Interface Unit PCA Block                    | 3-125        |

| Diagram                                                                                     | 0 120        |

| Figure 3–28. Common Memory                                                                  | 3-131        |

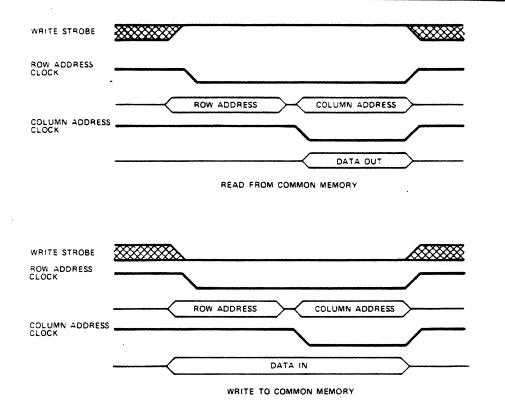

| Figure 3–29. Read or Write to Common Memory                                                 | 3-133        |

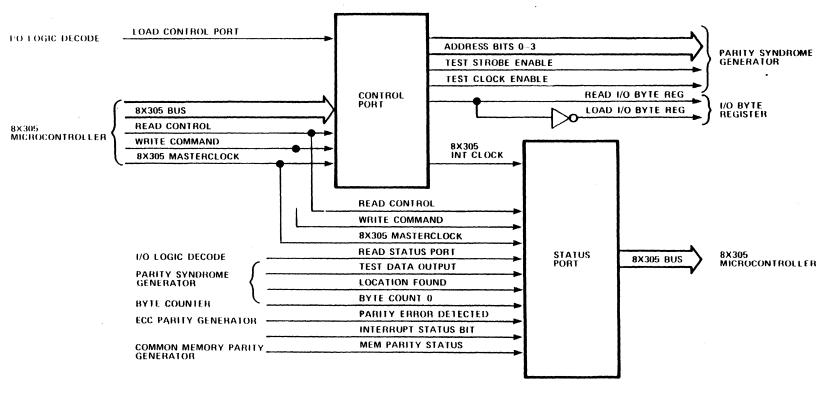

| Figure 3–30. Control and Status Ports                                                       | 3-135        |

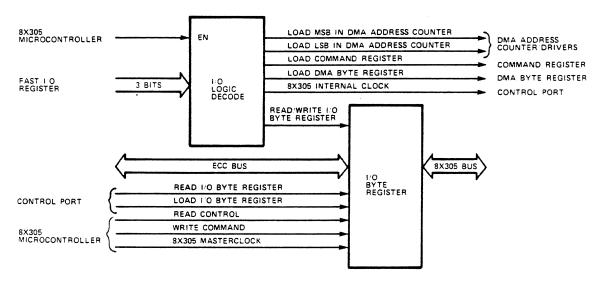

| Figure 3–31. I/O Logic Decode                                                               | 3-139        |

| Figure 3-32. Servo/Drive Control PCA Block Diagram                                          | 3-142        |

| Figure 3-33. IDI Bus Decode and Control Logic                                               | 3-148        |

| Figure 3-34. 8039 Input Buffers                                                             | 3-160        |

| Figure 3-35: 8039 Output Buffers                                                            | 3-166        |

| Figure 3–36. Track LSB Compare Logic                                                        | 3-171        |

|                                                                                             |              |

Page, xiii

# OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL

Page: xiv

TABLE OF CONTENTS

75114902 B

| Figure 3-37. | Decision Logic                                       | 3-172 |

|--------------|------------------------------------------------------|-------|

|              | 8031 Input Buffers                                   | 3-178 |

| Figure 3-39. | 8031 Output Latches                                  | 3-182 |

| Figure 3-40. | Servo Systems PCA Block Diagram                      | 3-188 |

| Figure 3-41. | Focus Loop Block Diagram                             | 3-189 |

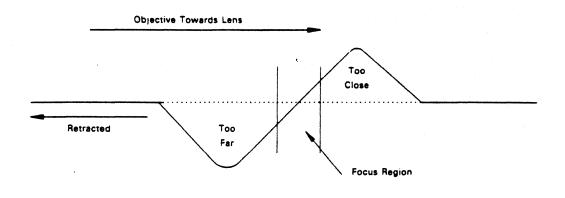

| Figure 3-42. | Focus "S" Curve                                      | 3-190 |

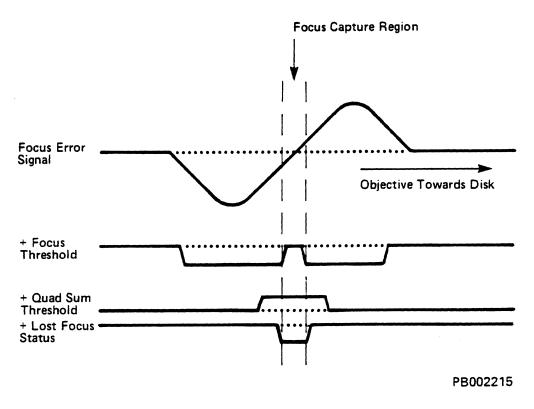

| Figure 3-43. | Focus Status Timing Diagram                          | 3-191 |

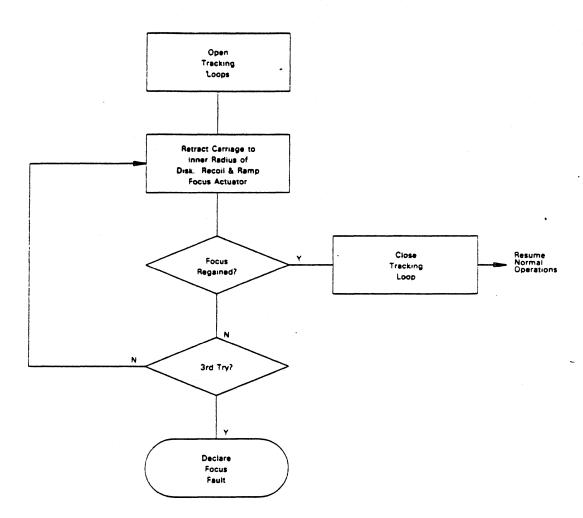

|              | Focus Error Recovery Functional Flow Chart           | 3-192 |

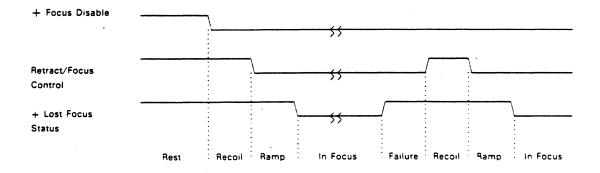

|              | Focus Failure Timing Diagram                         | 3-192 |

| Figure 3-46. | Initialization Failure During Focus                  | 3-193 |

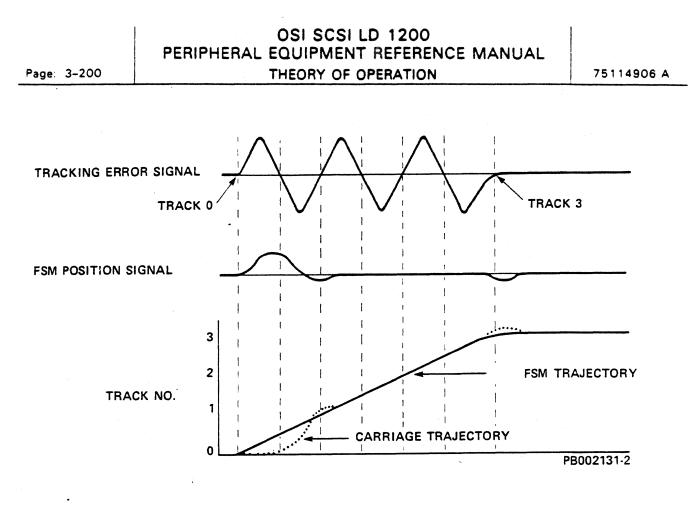

| Figure 3-47  | Tracking Block Diagram                               | 3-194 |

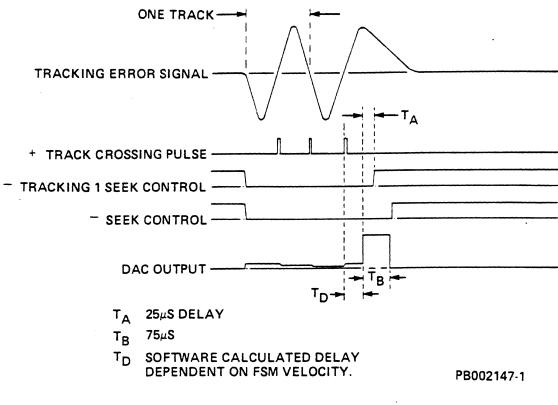

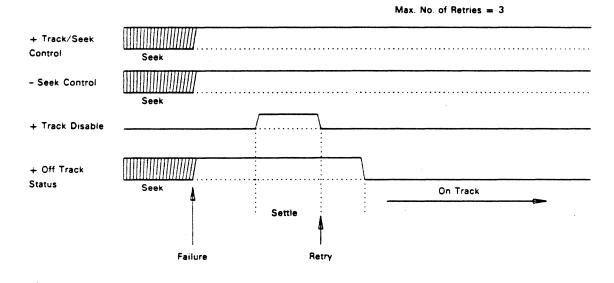

| Figure 3-48. | Seek Arrival Mode Timing Diagram                     | 3-195 |

| Figure 3-49. | Tracking Initialization Timing Diagram               | 3-196 |

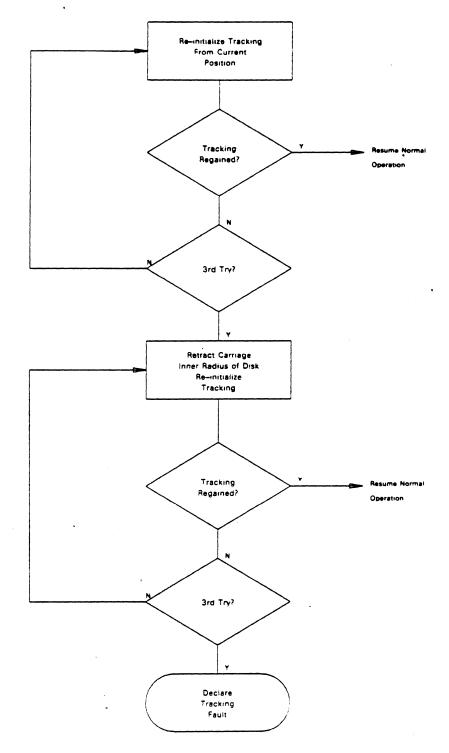

| Figure 3-50. | Tracking Error Recovery Functional Flow Chart        | 3-197 |

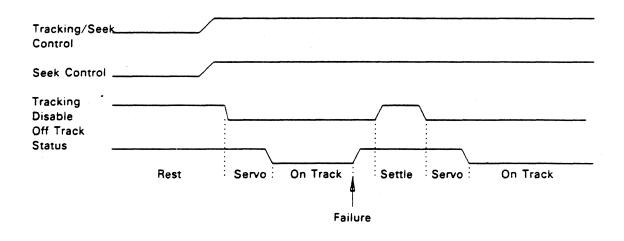

| Figure 3-51. | Initialization Failure Timing Diagram                | 3-198 |

| Figure 3-52. | Tracking Failure Timing Diagram                      | 3-198 |

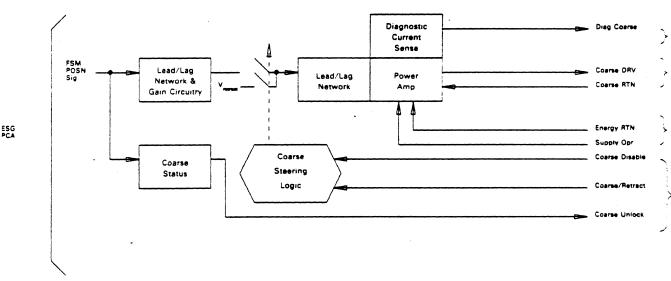

| Figure 3-53. | Coarse Loop Block Diagram                            | 3-199 |

| Figure 3-54. | Seek Profile                                         | 3-200 |

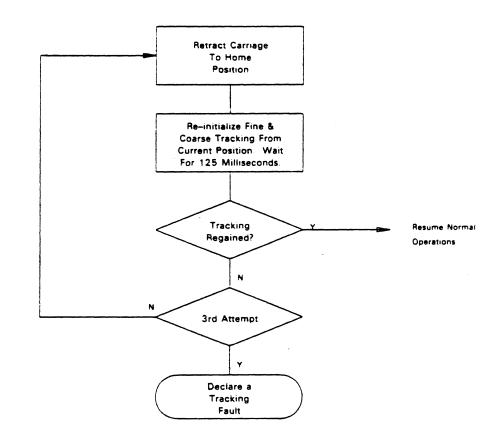

| Figure 3-55. | Coarse Loop Error Recovery Functional Flow Chart     | 3-201 |

| Figure 3-56. | Track Following or Seek Failure Timing Diagram       | 3-202 |

| Figure 3-57. | Error Signal Generator PCA Block Diagram             | 3-204 |

| Figure 3-58. | Focus Error and Tracking Signal Circuit              | 3-207 |

| Figure 3-59. | Wobble Circuitry                                     | 3-209 |

| Figure 3-60. | Track Crossing Circuitry                             | 3-210 |

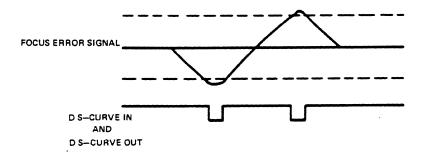

| Figure 3-61. | Diagnostic S Curve                                   | 3-211 |

| Figure 3-62. | Diagnostic Push-Pull Curve                           | 3-212 |

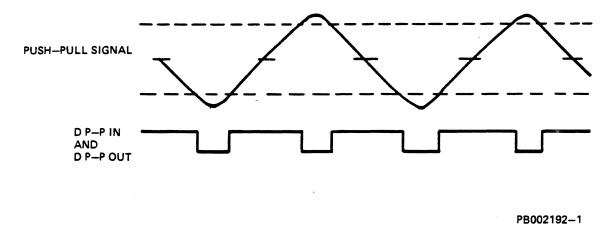

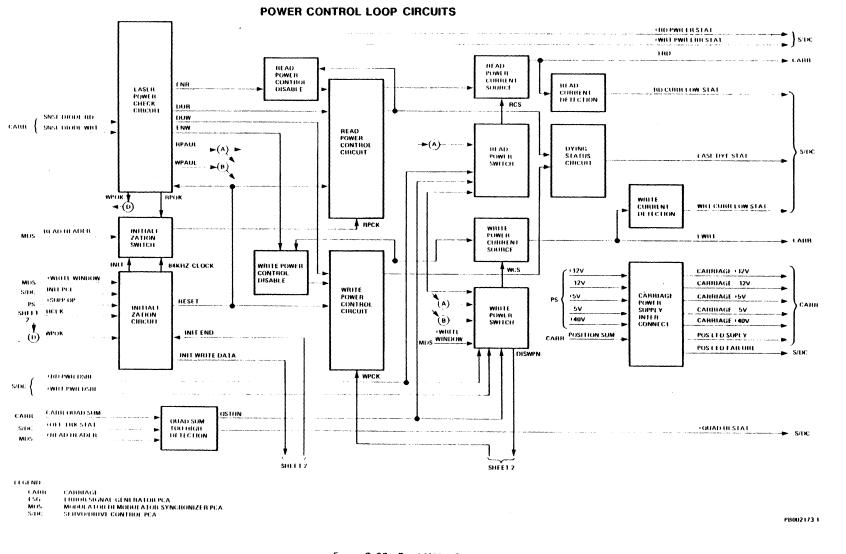

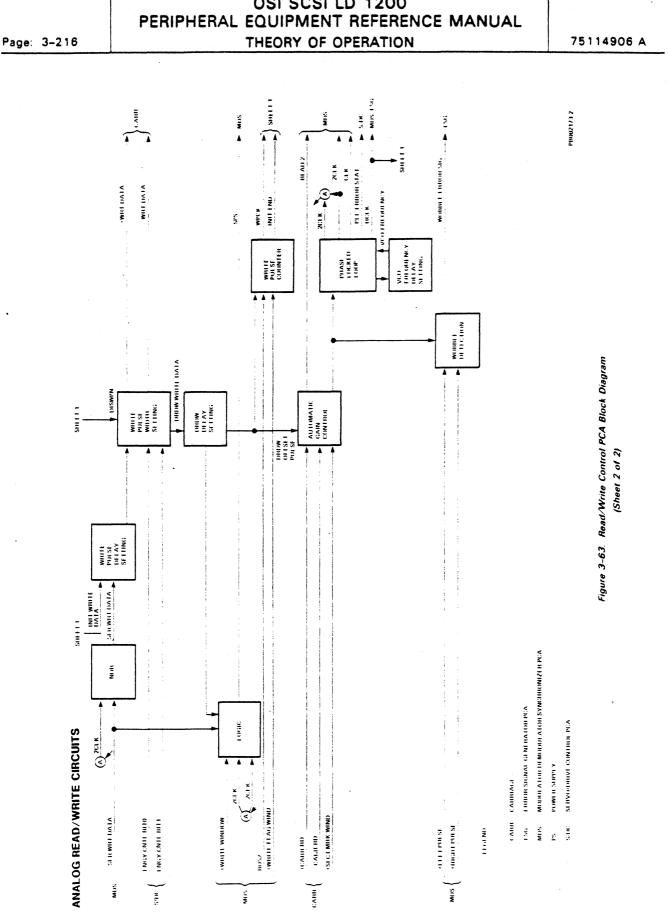

| Figure 3-63. | Read/Write Control PCA Block Diagram                 | 3-215 |

| Figure 3-64. | Write Pulse Width Setting Block Diagram              | 3-228 |

| Figure 3-65. | Automatic Gain Control Block Diagram                 | 3-230 |

|              | PLL and VCO Frequency Delay Setting Block Diagram    | 3-231 |

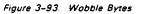

| Figure 3-67. | Wobble Bytes                                         | 3-233 |

| Figure 3-68. | Modulator Demodulator Synchronizer PCA Block Diagram | 3-235 |

| Figure 3-69. | Simplified Nibble Counter and Sequence Logic         | 3-243 |

| Figure 3-70. | Sequence Signal Timing                               | 3-244 |

|              | Sample and Hold Timing Sequence Example              | 3-249 |

|              | Data Path Simplified Logic                           | 3-252 |

| Figure 3-73. | Sector Mark Decode Simplified Logic                  | 3-255 |

|              | TOON Decode Simplified Logic                         | 3-257 |

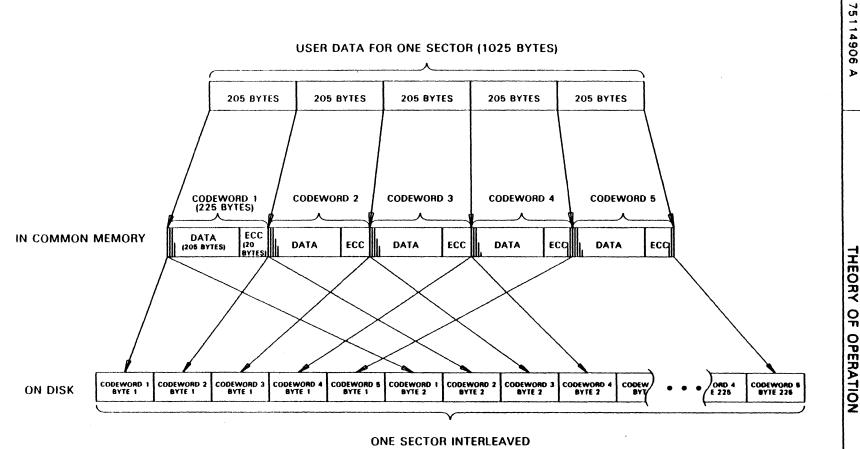

|              | Interleave Theory                                    | 3-261 |

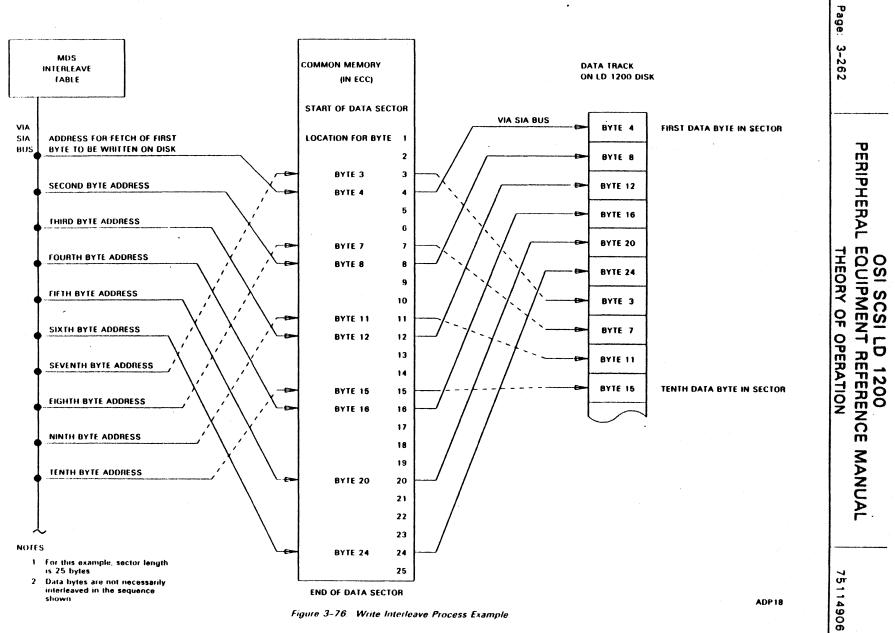

| Figure 3-76. | Write Interleave Process Example                     | 3-262 |

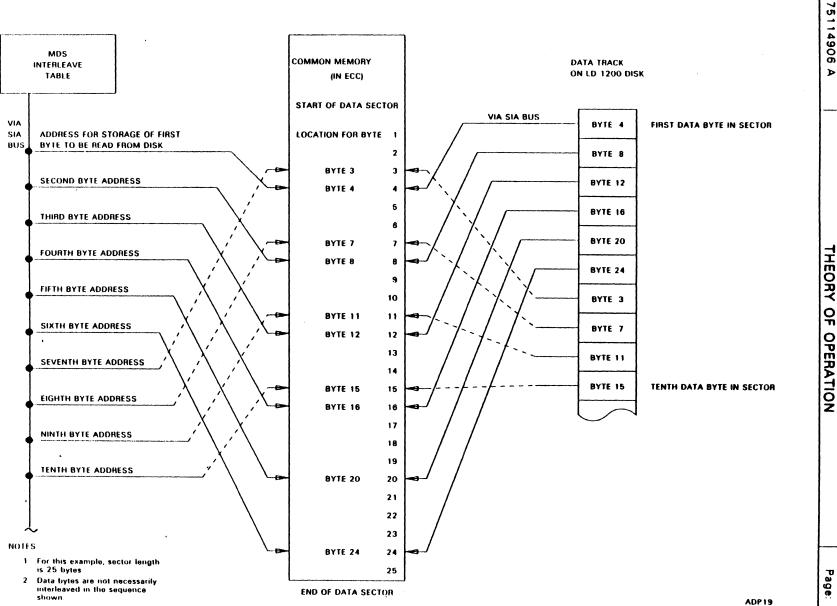

|              | Read Interleave Process Example                      | 3-263 |

| Figure 3-78. | Simplified Write Logic and TOON Encoder              | 3-265 |

| Figure 3-79. | SIA Interface Simplified Logic                       | 3-270 |

|              | Write Verify Circuit Simplified Logic                | 3-275 |

| Figure 3-81. | Wobble Byte Verification Simplified Logic            | 3-277 |

|              | Carriage Block Diagram                               | 3-279 |

|              | Carriage Optical System                              | 3-283 |

|              | Quad Detector Signals                                | 3-288 |

|              | Electromechanical System Model                       | 3-289 |

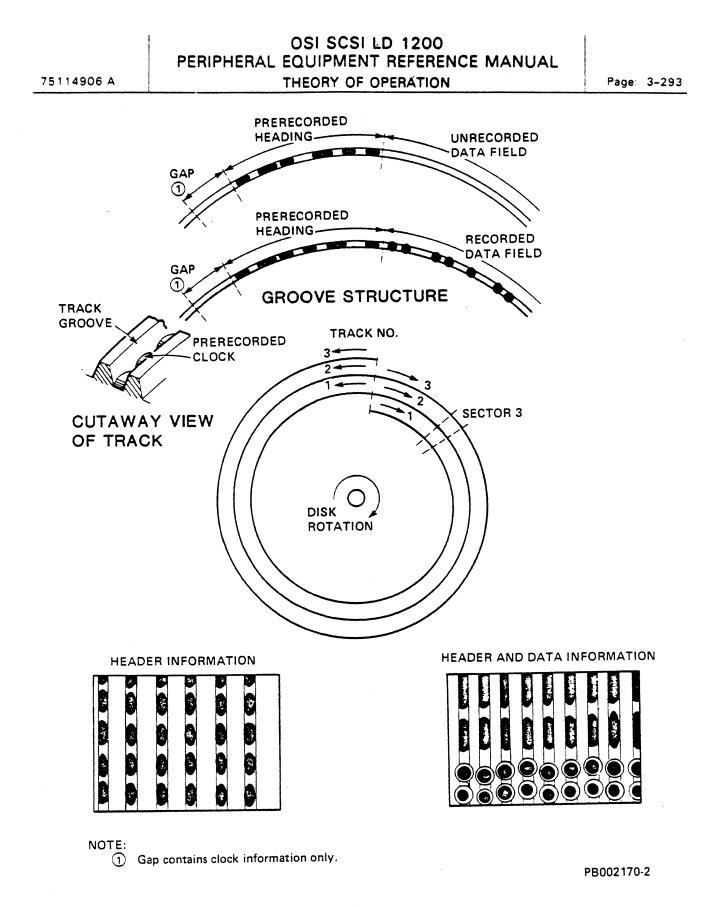

|              | LD 1200 Data Cartridge                               | 3-291 |

|              | Disk Construction                                    | 3-292 |

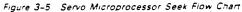

|              | Recording Surface Format                             | 3-293 |

|              | Media Track Structure                                | 3-295 |

|              | Data Representation in the Media                     | 3-296 |

| Figure 3-91  | LD 1200 Sector Format (One Sector)                   | 3-298 |

|              |                                                      |       |

# OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL

75114902 B

## TABLE OF CONTENTS

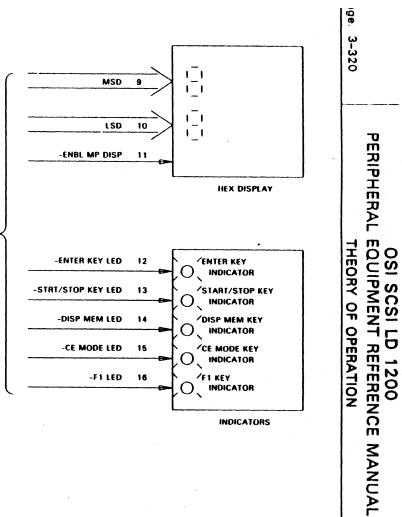

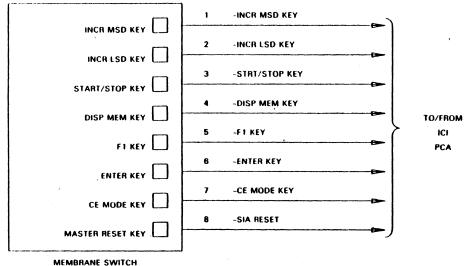

| Figure 3-92. Sector Mark Code Definition<br>Figure 3-93. Wobble Bytes<br>Figure 3-94. Baseplate Block Diagram<br>Figure 3-95. Power Supply Block Diagram<br>Figure 3-96. Operator Panel Block Diagram<br>Figure 3-97. Maintenance Panel Block Diagram | 3-299<br>3-299<br>3-302<br>3-307<br>3-317<br>3-320 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Tables                                                                                                                                                                                                                                                |                                                    |

| Table 1–1. LD 1200 Mechanical and Electrical Characteristics                                                                                                                                                                                          | 1-2                                                |

| Table 2-1. Operator Panel Controls and Indicators                                                                                                                                                                                                     | 2-3                                                |

| Table 2–2. Maintenance Panel Controls and Indicators                                                                                                                                                                                                  | 2-5                                                |

| Table 3–1. Reported LD 1200 Errors and Faults                                                                                                                                                                                                         | 3-34                                               |

| Table 3–2. Information Transfer Phases                                                                                                                                                                                                                | 3-48                                               |

| Table 3–3. Operation Code                                                                                                                                                                                                                             | 3-59                                               |

| Table 3-4. Typical Group 0 Command Descriptor Block for Six-Byte Commands                                                                                                                                                                             | 3-59                                               |

| Table 3-5. Typical Group 1 Command Descriptor Block for Ten-Byte Commands                                                                                                                                                                             | 3-60                                               |

| Table 3-6. Status Byte                                                                                                                                                                                                                                | 3-64                                               |

| Table 3–7. Status Byte Code Bit Values                                                                                                                                                                                                                | 3-65                                               |

| Table 3–8. Status Categories                                                                                                                                                                                                                          | 3-78                                               |

| Table 3–9. Error Action Overview                                                                                                                                                                                                                      | 3-80                                               |

| Table 3–10. Write Error Categories                                                                                                                                                                                                                    | 3-81                                               |

| Table 3-11. Control Bit Categories                                                                                                                                                                                                                    | 3-82                                               |

| Table 3-12. SCSI I/O Port Definitions                                                                                                                                                                                                                 | 3-98                                               |

| Table 3–13. Command Byte                                                                                                                                                                                                                              | 3-136                                              |

| Table 3–14. IDI Bus Address Decode                                                                                                                                                                                                                    | 3-149                                              |

| Table 3-15. 8039 Address Decode                                                                                                                                                                                                                       | 3-169                                              |

| Table 3–16. 8031 Address Decode                                                                                                                                                                                                                       | 3-183                                              |

| Table 3-17. Common Memory Data Buffer Format (One Sector)                                                                                                                                                                                             | 3-258                                              |

| Table 3–18. TOON Code Definition                                                                                                                                                                                                                      | 3-301                                              |

Page: xv

• . • • . • • •

## OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL GENERAL DESCRIPTION

## **1. GENERAL DESCRIPTION**

## 1.1. INTRODUCTION

The purpose of this section is to familiarize the user or Customer Engineer (CE) with the SCSI LaserDrive 1200 Intelligent Digital Optical Disk (LD 1200) and its field replaceable units (FRUs). This section includes an illustrated physical description of the overall unit and its FRUs.

## **1.2. PHYSICAL DESCRIPTION**

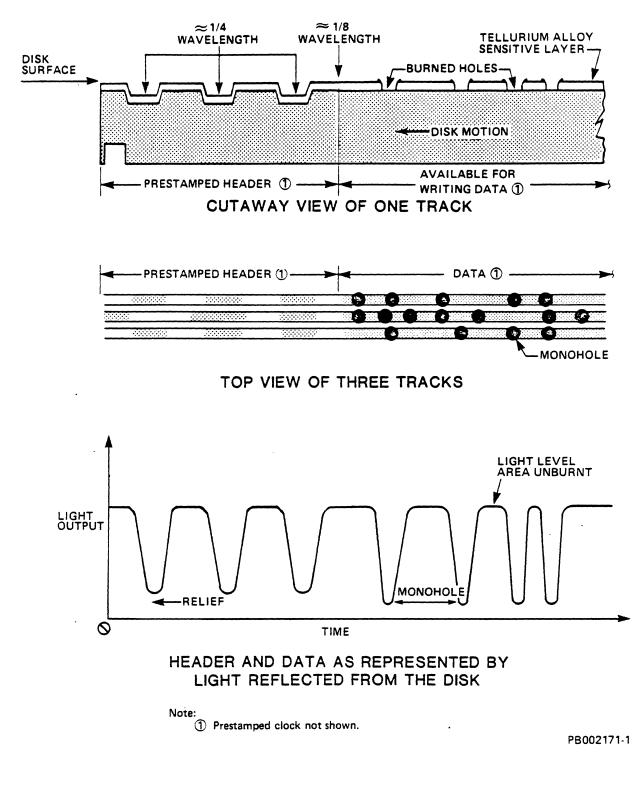

The LD 1200 is a random-access, optical disk drive with removable Media and a Small Computer System Interface (SCSI). It stores up to two gigabytes of data on a disk that can be written on once and read multiple times.

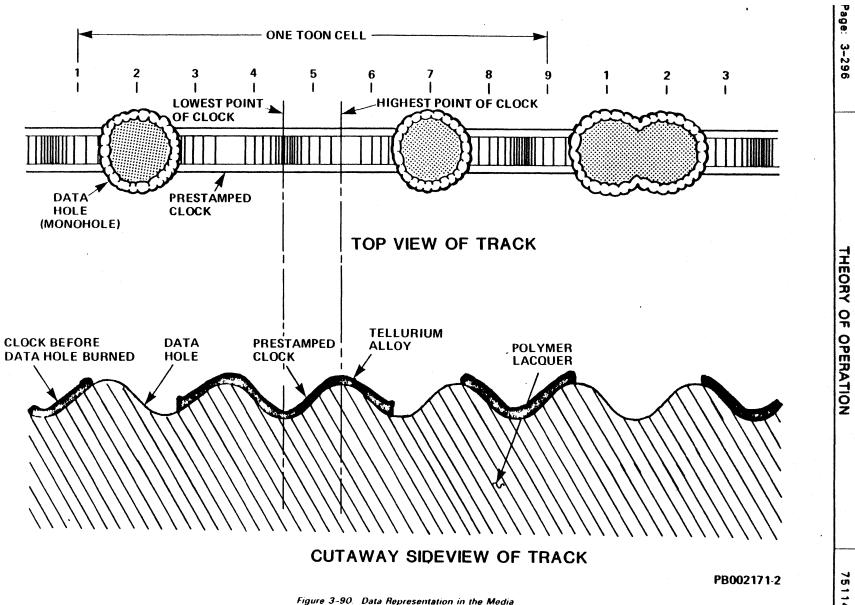

The write process consists of melting holes into the Media by means of a laser beam. The read process consists of sensing the change in light reflected from the Media by means of photodetectors. This information is sent to the logic. A hole reflects very little light and represents a binary ONE. The absence of a hole reflects most of the laser beam and represents a binary ZERO.

Table 1-1 provides a list of the mechanical and electrical characteristics of the LD 1200.

## Page: 1-2

# OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL

GENERAL DESCRIPTION

75114906 A

l

### Table 1-1. LD 1200 Mechanical and Electrical Characteristics

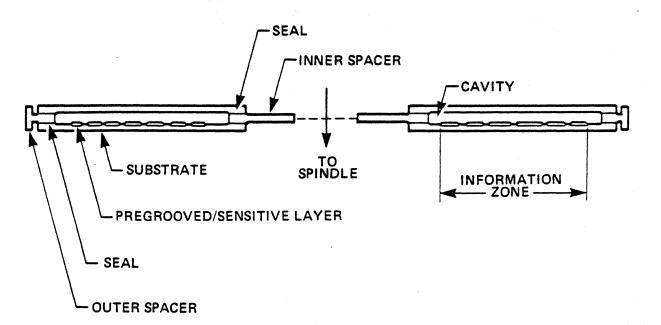

| Minimum Usable Data Cartridge Capacity           | Single-sided Media: 1 gigabyte: Double-sided Media: 2 gigabytes. |

|--------------------------------------------------|------------------------------------------------------------------|

| Number of Disks                                  | 1                                                                |

| Disk Construction                                | Pregrooved, glass sandwich                                       |

| Disk Diameter                                    | 12 in (306 mm)                                                   |

| Data Surfaces                                    | Single-sided Media: 1; Double-sided Media: 2                     |

| Recording:                                       |                                                                  |

| Tracks per Disk                                  | Single-sided Media: 32,000; Double-sided                         |

|                                                  | Media: 64,000.                                                   |

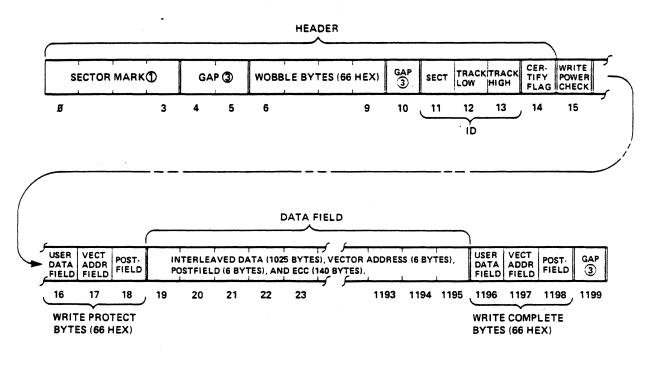

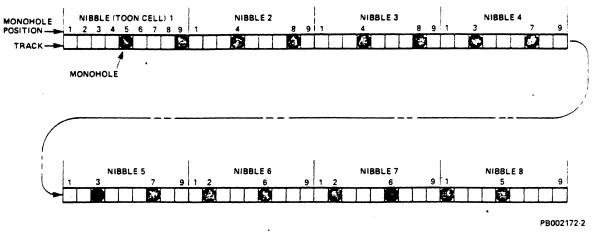

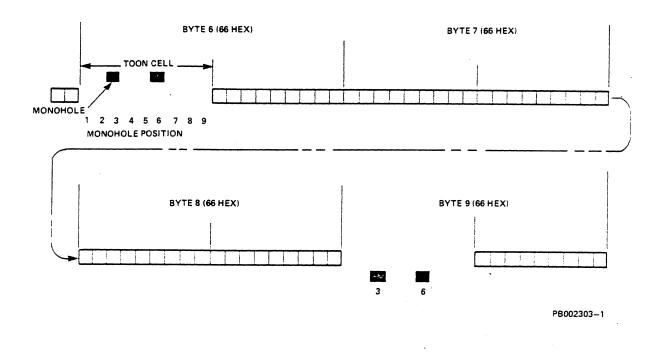

| Sector Size                                      | 1,025 user bytes                                                 |

| Sectors per Track                                | 32                                                               |

| Interface                                        | Small Computer System Interface                                  |

| Maximum Host Transfer Rate                       | Write: 2 MB/s; Read: 1.33 MB/s                                   |

| Average Data Transfer Rate                       | 262 kB/s                                                         |

| Average Access Time                              | 150 ms                                                           |

| Average Rotational Latency                       | 62.5 ms                                                          |

| Spindle Speed                                    | 480 +4.8/-9.6 rpm                                                |

| Spindle Power Up/Down Time                       | Up: 8 sec maximum                                                |

|                                                  | Down: 3 sec maximum                                              |

| Data Reliability Error Rate with (ECC)           | 10 <sup>-12</sup> during 10 years                                |

| Drive Reliability Mean Time                      | 12,000 hours                                                     |

| Between Failures (MTBF)                          |                                                                  |

| Media Life - Total Storage Time                  | 10 years                                                         |

| Power Options                                    | 100V, 50/60 Hz                                                   |

|                                                  | 110V, 50/60 Hz                                                   |

|                                                  | 120V, 60 Hz                                                      |

|                                                  | 200V, 50 Hz                                                      |

|                                                  | 220V, 50 Hz                                                      |

| •                                                | 240V, 50 Hz                                                      |

| Power Dissipation                                | 250W average (217 kcal/hr; 860 BTU/hr)                           |

|                                                  | 400W maximum (347 kcal/hr; 1376 BTU/hr)                          |

| Environmental:                                   |                                                                  |

| Operating Temperature                            | 10 to 40°C (50 to 104°F)                                         |

| Nonoperating Temperature                         | -40 to 60°C (-40 to 140°F)                                       |

| Operating Humidity                               | 20 to 80% relative humidity (no condensation allowed)            |

| Nonoperating Humidity                            | 10 to 90% relative humidity (no condensation allowed)            |

| Operating Altitude                               | -983 to 8200 ft                                                  |

|                                                  | (-300 to 2500 m)                                                 |

| FCC Rating                                       | Class B                                                          |

| Physical Characteristics: (Rack-Mountable Model) |                                                                  |

| Height                                           | 5.25 in. (13.3 cm)                                               |

| Width                                            | 19 in. (48.3 cm)                                                 |

| Depth                                            | 25.6 in. (65 cm)                                                 |

| Weight                                           | 55 lbs (25 kg)                                                   |

| Physical Characteristics: (Desk-Top Model):      |                                                                  |

| Height                                           | 5.25 in. (13.3 cm)                                               |

| Width                                            | 18.5 in (46.9 cm)                                                |

| Depth                                            | 25.88 in. (65.7 cm)                                              |

| Weight                                           | 55 lbs (25 kg)                                                   |

The LD 1200 is either a rack-mountable or desk-top unit with an internal power supply. Spindle Motor, logic chassis (card rack), and an optical Read/Write head (Carriage).

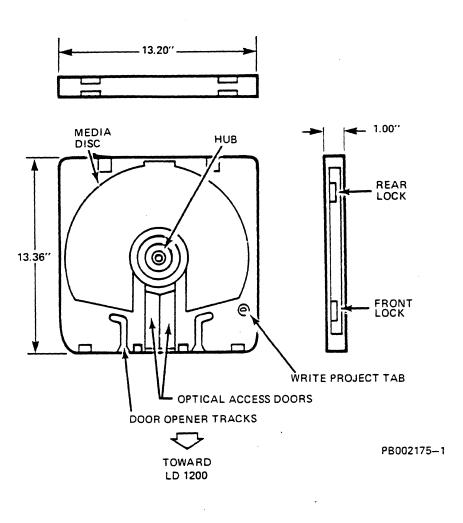

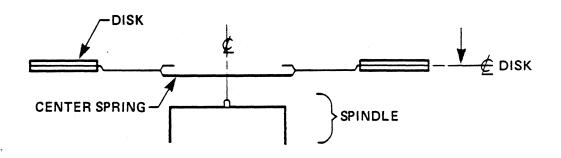

Data is stored on a 12-inch diameter disk. The Media consists of a sandwich of two glass disks, coated internally with a metallic layer on which the data is written. This Media is contained in a plastic Data Cartridge (cassette type).

The Data Cartridge is provided with optical access doors that open when the cartridge is inserted into the unit, exposing the Media to the laser beam. Safety interlocks protect the user from exposure to the laser beam. The unit does not operate unless the Data Cartridge is properly inserted and seated, and the disk is spinning at the proper speed.

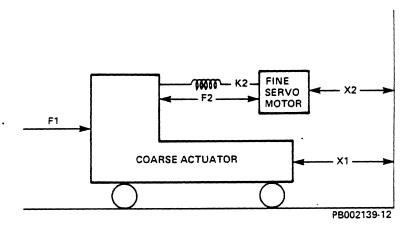

The Carriage Assembly, in the LD 1200, contains a laser pen. This pen emits a light beam that is routed through an objective lens, mounted in the Fine Servo Motor, to the Media. The Fine Servo Motor focuses the laser beam on the Media and keeps it in the center of the data track. The Coarse Actuator moves the Carriage Assembly underneath the disk surface for Seek operations.

## 1.3. LD 1200 UNIT

Figure 1-1 illustrates the LD 1200 Unit and Data Cartridge. A general physical and functional description of the LD 1200 unit and Data Cartridge is given in the Physical Description subsection.

The major assemblies of the LD 1200 are shown in figure 1-2. These assemblies are described in the following subsections.

Figure 1-2. LD 1200 Major Assemblies

## 1.4. CARD RACK

The Card Rack is located in the right, rear corner of the LD 1200. It contains seven printed circuit assemblies (PCAs) and the logic interconnect board into which the PCAs are connected (the Backplane PCA). These seven PCAs are as follows:

- Error Correction and Common Memory Interface Unit (ECC) PCA.

- LD 1200 SCSI Adapter (SCSI) PCA (also known as Internal Controller Interface PCA or ICI PCA)

- LD 1200 SCSI Adapter PCA (SCSI PCA), also known as the Internal Controller Interface PCA or ICI PCA.

- Modulator Demodulator Synchronizer (MDS) PCA

- Read/Write Control (R/WC) PCA

- Error Signal Generator (ESG) PCA

- Servo Systems (SS) PCA

The Card Rack and PCAs are shown in figure 1–3. The Backplane PCA is shown in figure 1–4.

Figure 1-3. Card Cage, Front View

ADP38

75114906 A

## OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL GENERAL DESCRIPTION

Page: 1-7

Figure 1-4. Card Rack, Rear View

•

## 1.5. LD 1200 PCA DESCRIPTIONS

The following is a brief description of the major LD 1200 PCAs and the Backplane PCA contained in the Card Rack:

- Error Correction and Common Memory Interface Unit PCA This PCA generates error correction characters which are loaded into Common Memory with write data and performs error detection and correction on read data. It also provides Common Memory to buffer data and status transfers between the LD 1200 and the Host Adapter.

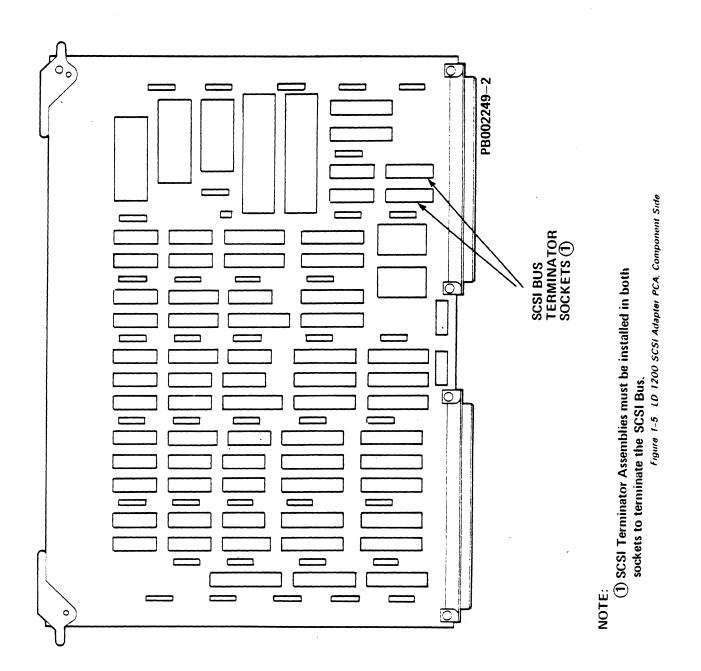

- LD 1200 SCSI Adapter PCA This PCA contains the majority of the Internal Controller logic, enabling the LD 1200 to communicate with a Host over an SCSI interface. It interfaces with the Host Adapter, ECC, MDS, and Servo/Drive Control PCAs, the Operator Panel, and (when installed) the Optional Maintenance Panel. This PCA also provides for termination of the external (SCSI) interface (refer to figure 1–5).

- Servo/Drive Control PCA This PCA provides the logic for the servo and drive functions, controlling laser power and Carriage movement.

- Modulator Demodulator Synchronizer PCA This PCA performs the basic data manipulation functions of the LD 1200.

The following jumpers are located on this PCA (refer to figure 1-6 for jumpers locations).

- (H147,G643) Wobble Formatting Jumper Allows the selection of different wobble formats when using a Media also provided with this option.

- (F553) Continuous Rewrite Jumper Used during testing only, this jumper allows the Rewrite function to continue beyond one sector.

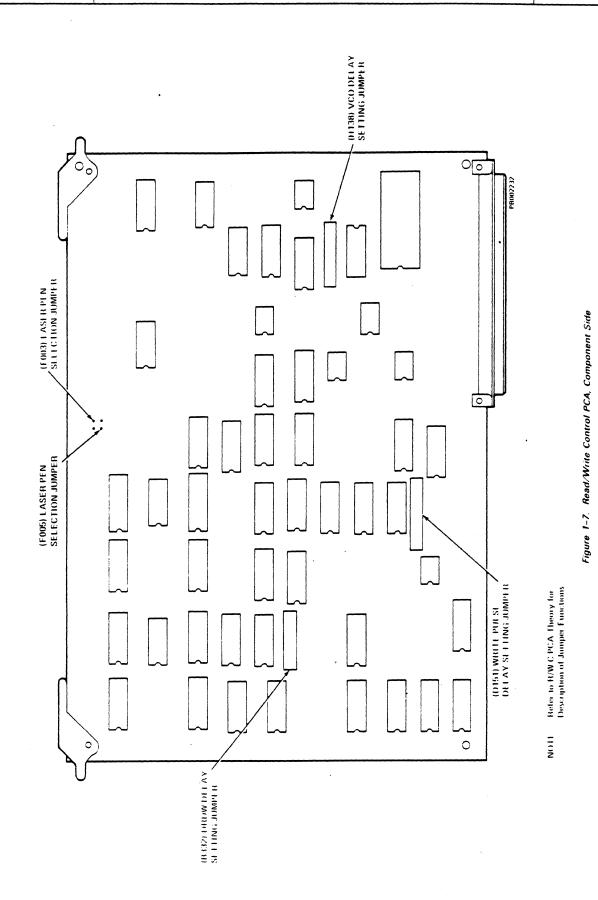

- Read/Write Control PCA This PCA controls Read and Write laser power, provides automatic gain control of read data, and provides timing signals for the Read/Write channel.

The following jumpers are located on this PCA (refer to figure 1-7 for jumper locations).

- (F003, F005) Laser Pen Selection Jumper Provides compatability between the characteristics of different Laser Pens supplied by different manufacturers.

- (H138) VCO Delay Setting Jumper Provides selected time delay allowing adjustment of the phase of the internal clocks with relation to the disk clock.

- (D151) Write Pulse Delay Setting Jumper Allows an adjustable time delay to be produced between the receipt of 2CLK and the output of write data to the Carriage.

- (B332) DRDW Delay Setting Jumper Allows an adjustable time delay to be produced between the output of the Modulator Demodulator Synchronizer PCA and the input to the Automatic Gain Control.

- Error Signal Generator PCA This PCA generates and amplifies the servo error signals that are used by the Servo Systems PCA to control Carriage movement.

- Servo Systems PCA This PCA controls the Carriage servo functions.

- Backplane PCA This PCA interconnects the major LD 1200 PCAs.

OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL GENERAL DESCRIPTION

75114906 A

Page: 1-9

Page: 1-10

# OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL GENERAL DESCRIPTION

(G643) WOBBLE FORMATTING JUMPER (H147) WOBBLE FORMATTING JUMPER 0) PB002249 5 ς 5 ς Figure 1-6. Modulator Demodulator Synchronizer PCA, Component Side Ó (F553) CONTINUOUS REWRITE JUMPER 0 Ş 5 0 IC

75114906 A

# OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL GENERAL DESCRIPTION

Page: 1-11

•

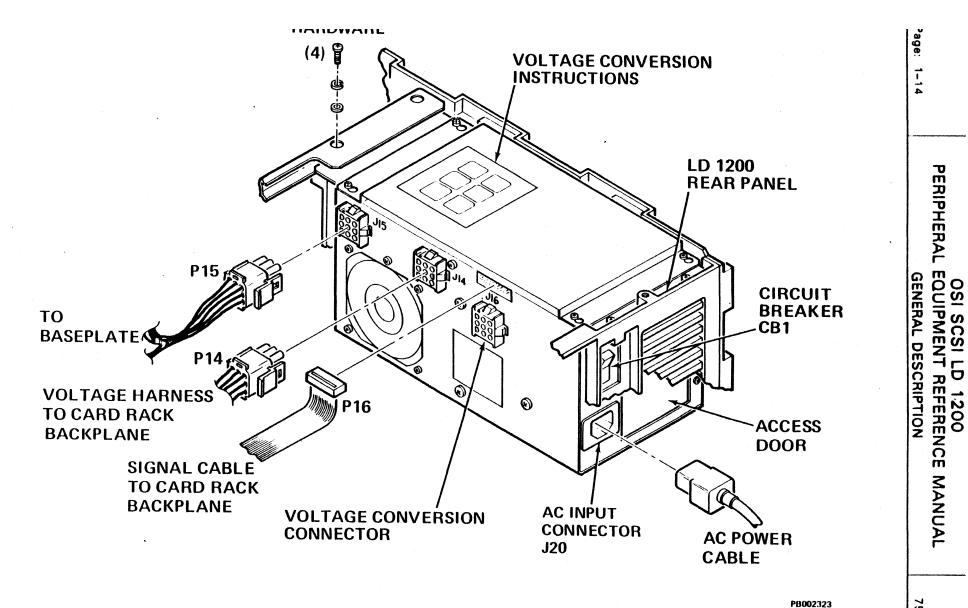

## 1.6. POWER SUPPLY

The LD 1200 Power Supply is located in the left, rear corner of the unit. It is a switching type of supply, accepting ac input of 100 V, 50/60 Hz; 110 V, 50/60 Hz; 120 V, 60 Hz; 200 V, 50 Hz; 220 V, 50 Hz; or 240 V, 50 Hz. It supplies dc output voltages of  $\pm 5$ ,  $\pm 5$ ,  $\pm 12$ ,  $\pm 12$ , and  $\pm 40$  Vdc, and an ac output voltage of 115 Vac.

The Power Supply is shown in figure 1-2. Power Supply cable connections are shown in figure 1-8.

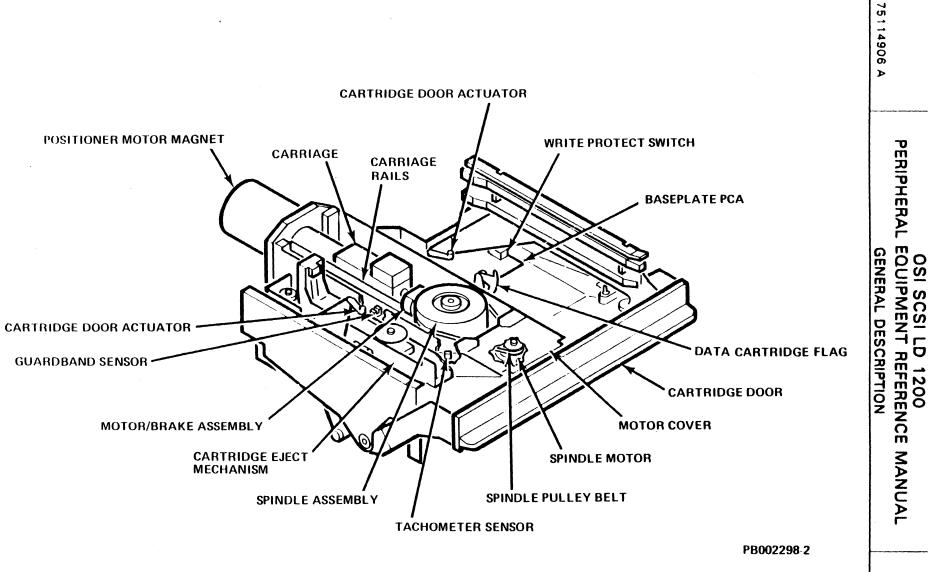

## 1.7. BASEPLATE

The Baseplate provides the main supporting structure and mounts for the critical mechanical, electromechanical, and optomechanical assemblies in the LD 1200. It is designed as a stable and rigid reference to aid in ease of assembly and alignment of interrelated subassemblies.

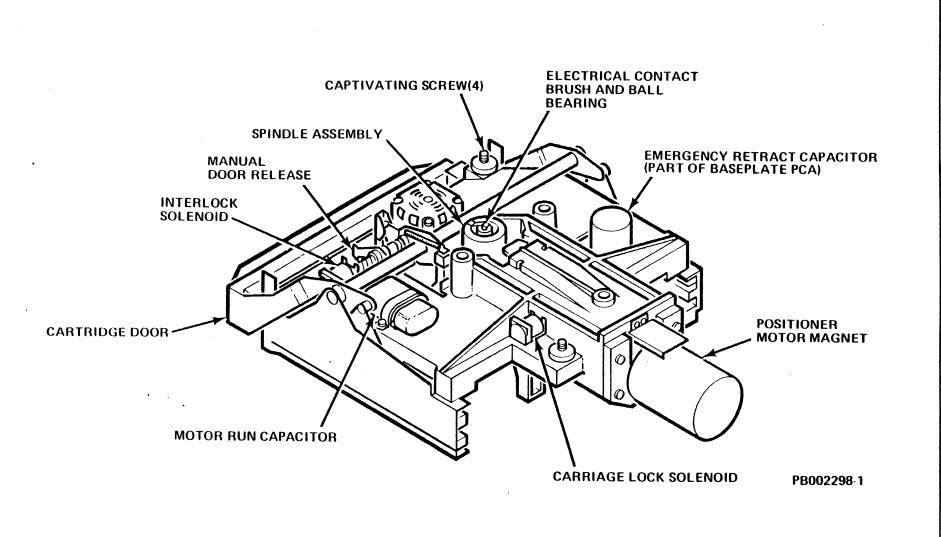

The FRUs located on the top of the Baseplate are shown in figure 1–9. A brief description of these FRUs follows:

- Motor Cover Covers the top of the Spindle Motor.

- Spindle Pulley Belt Wraps around the Spindle Motor Pulley and the Spindle. When the motor is running, the belt rotates the Spindle.

- Spindle Motor Rotates the Spindle by means of the Spindle Pulley Belt.

- Tachometer Sensor Senses the speed of the Spindle Motor.

- Spindle Assembly Provides the means for securing and rotating the Media.

- Motor/Brake Assembly Used to brake the Spindle Assembly to a stop.

- Guardband Sensor Indicates when the Carriage is retracted to the guardband area of the Media.

- Carriage Provides the Read/Write/Servo head for the LD 1200. The Carriage moves between different areas of the Media when a Seek function is performed.

- Positioner Motor Magnet Interacts with the Carriage to form a voice coil motor, which moves the Carriage during Seek operations.

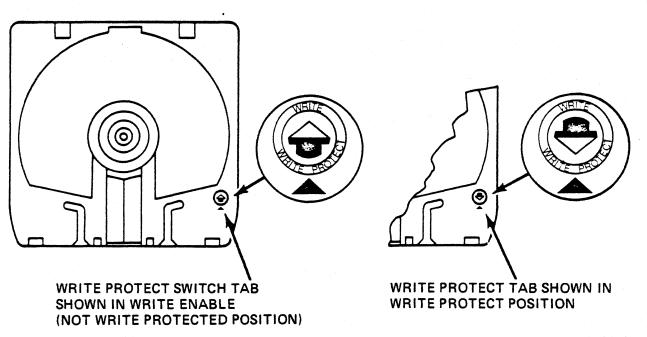

- Write Protect Switch When the Write Protect Tab on the Data Cartridge is set to the write protect position, this switch is activated, indicating to the logic that the write protect function has been activated.

- Baseplate Terminator PCA (known as Baseplate PCA) Distributes logic signals from the Baseplate to the Card Rack. This PCA includes the Emergency Retract Capacitor, Write Protect Switch, and Data Cartridge Flag.

- Data Cartridge Flag Indicates to the logic when the Data Cartridge is inserted.

- Cartridge Door Opens to allow insertion of the Data Cartridge into the LD 1200. The guide rails in the door mechanism position the Data Cartridge over the Spindle Assembly and separate the cartridge halves, freeing the Media, when the door is closed.

- Cartridge Door Actuators Open the optical access doors in the Data Cartridge when it is inserted into the LD 1200, allowing the laser beam direct access to the Media.

- Cartridge Eject Mechanism Ejects the Data Cartridge approximately one inch when the Cartridge Door is opened.

Figure 1-8. Power Supply Cable Connections

75114906 A

#### Figure 1-9 Baseplate, Top View

Page: 1-15

The FRUs located on the bottom of the Baseplate are shown in figure 1-10. A brief description of these items follows:

- Carriage Lock Solenoid Locks the Carriage in the Home position after a power failure or normal shut down.

- Interlock Solenoid Prevents removal of the Data Cartridge when the Spindle is spinning.

- Manual Door Release Provides a manual means for opening the Cartridge Door in case of a power failure.

- Emergency Retract Capacitor Fully retracts the Carriage when a power failure occurs.

- Motor Run Capacitor Enables the Spindle Motor to spin up the Spindle smoothly.

- Electrical Contact Brush Protects the Spindle from electrostatic buildup and discharge.

- Ball Bearing The replaceable rotating contact point on the Spindle for the Contact Brush.

- Captivating Screws Secure the Baseplate to the LD 1200 chassis.

Figure 1-10. Baseplate, Bottom View

OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL GENERAL DESCRIPTION

75114906 A

Page: 1-17

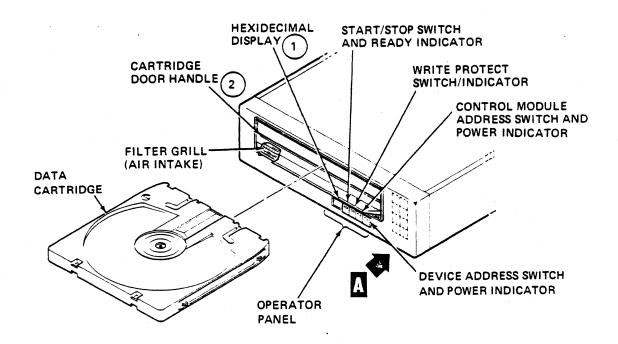

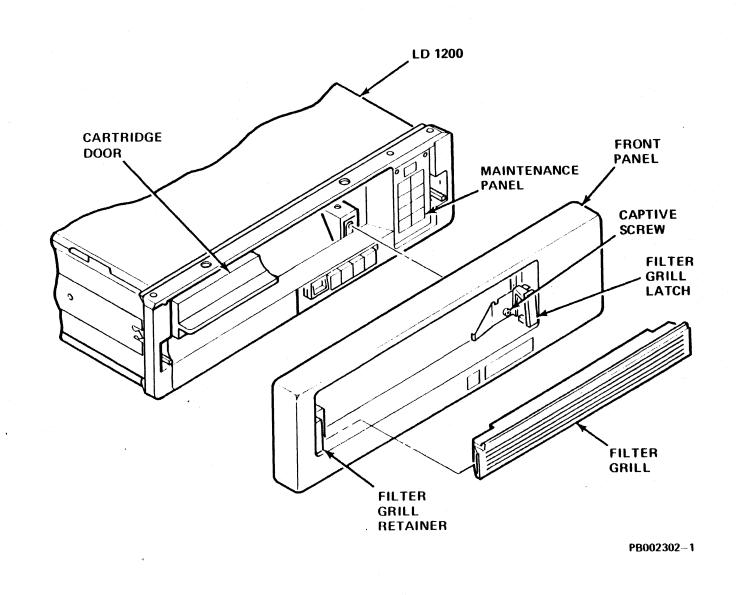

## 1.8. LD 1200 FRONT PANEL

The front panel of the LD 1200 includes the Operator Panel, opening for the Cartridge Door, Filter Grill, and Air Filter (refer to figure 1-2). The Operator Panel provides the user/machine interface necessary to operate the LD 1200. The Filter Grill contains the Air Filter which provides primary air filtration for the LD 1200.

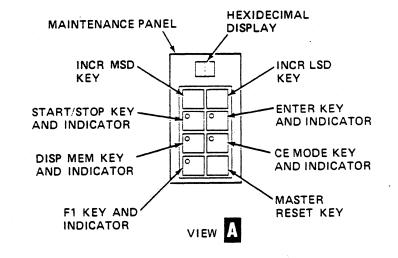

Behind the front panel is located the optional Maintenance Panel (refer to figure 1-2). The Maintenance Panel enables the Customer Engineer (CE) to run diagnostic tests to troubleshoot the LD 1200.

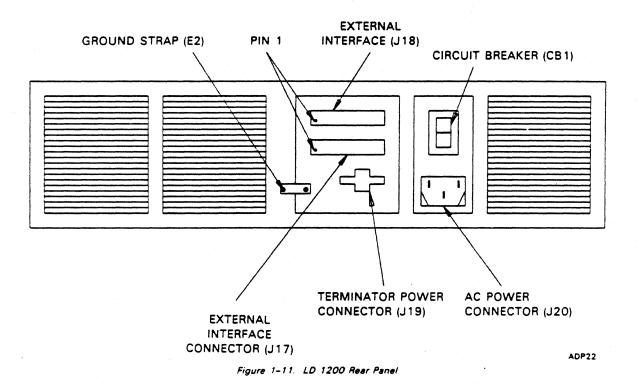

### 1.9. LD 1200 REAR PANEL

The LD 1200 rear panel includes the Air Filter Grill, the Ground Strap (E2), external interface Connectors (J17 and J18), Circuit Breaker (CB1), AC Power Connector (J20), and Terminator Power Connector (J19). The rear panel is shown in figure 1–11.

75114906 A

## 2. OPERATION

#### 2.1. INTRODUCTION

This section describes the controls and indicators for the Operator Panel, the Maintenance Panel, and the Power Supply. It also includes the procedures for SCSI LaserDrive 1200 Intelligent Digital Optical Disk (LD 1200) Power-On and Power-Off, and Data Cartridge loading and unloading.

#### NOTE

The Maintenance Panel controls and indicators may be used ONLY by trained service personnel.

### 2.2. CONTROLS AND INDICATORS

#### 2.2.1. Operator Panel

The Operator Panel is located on the front of the LD 1200. It contains a hexadecimal display, controls, and indicators as described in table 2-1 (see figure 2-1):

Page: 2-1

.

## NOTES:

1 ) 2 Display of 0 0 indicates successful test completion.

Pull down to open.

PB002209

75114906 A

.

.

OSI SCSI LD 1200 PERIPHERAL EQUIPMENT REFERENCE MANUAL OPERATION

Page: 2-3

## Table 2-1. Operator Panel Controls and Indicators

| CONTROL/INDICATOR       | DESCRIPTION                  | PURPOSE                                                                                                                                                                                                                                       | COMMENT                                                                                                                                                                                                                                             |

|-------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hexadecimal Display     | Two-character LED<br>display | Displays failure and<br>subfailure codes and<br>the state of normal<br>machine operation.                                                                                                                                                     | When a failure is<br>detected, the failure<br>code remains on the<br>display until the<br>beginning of a<br>diagnostic test.                                                                                                                        |

| START/STOP Switch       | Alternate Action             | Powers-up the<br>Spindle Motor when<br>depressed and locked<br>into position.                                                                                                                                                                 | Used after the Data<br>Cartridge is inserted<br>into the LD 1200.                                                                                                                                                                                   |

|                         |                              | Powers-down the<br>Spindle Motor when<br>depressed and<br>released from the<br>locked position.                                                                                                                                               | The Host can also<br>control the Spindle<br>Motor.                                                                                                                                                                                                  |

| READY Indicator         | Green LED                    | Flashes during Spindle<br>Motor power-up or<br>power-down. When<br>Spindle Motor is up to<br>speed and the LD<br>1200 is ready, the<br>indicator remains<br>illuminated. When the<br>Spindle Motor is<br>powered down, it is<br>extinguished. | Located within the<br>START/STOP switch.                                                                                                                                                                                                            |

|                         |                              |                                                                                                                                                                                                                                               | Also extinguishes<br>when a device fault<br>occurs.                                                                                                                                                                                                 |

| WRITE PROTECT<br>Switch | Alternate Action             | Provides media write<br>protection when<br>depressed and locked<br>into position.                                                                                                                                                             | Write protection can<br>also be achieved by<br>Host interface<br>commands and by<br>rotating the Write<br>Protect Tab on the<br>Data Cartridge<br>counter-clockwise<br>(see Data Cartridge<br>Write Protection<br>illustration in this<br>section). |

|                         |                              |                                                                                                                                                                                                                                               | Any one, two, or three<br>of the methods can be<br>used at the same                                                                                                                                                                                 |