# CDC<sup>®</sup> STORAGE MODULE DRIVE BK4XX BK5XX

GENERAL DESCRIPTION OPERATION THEORY OF OPERATION DISCRETE COMPONENT CIRCUITS

HARDWARE REFERENCE MANUAL

# CDC<sup>®</sup> STORAGE MODULE DRIVE BK4XX BK5XX

GENERAL DESCRIPTION OPERATION THEORY OF OPERATION DISCRETE COMPONENT CIRCUITS

HARDWARE REFERENCE MANUAL

|            | REVISION RECORD                                                                |

|------------|--------------------------------------------------------------------------------|

| REVISION   | DESCRIPTION                                                                    |

| A          | Manual released including ECOs 48092, 48113C, 48151, 48155, 48196A, 48200,     |

| (3-1-77)   | 48210, 48211, 48240B, 48242, 48256, 48351.                                     |

| В          | Technical and editorial changes.                                               |

| (5-16-77)  |                                                                                |

| с          | Technical and editorial changes.                                               |

| (11-15-77) |                                                                                |

| D          | Manual updated to include ECOs 55157, 48941 (Release BK5B5J/K), 55087 (Release |

| (6-26-78)  | BK4AlD and BK5AlD), and 55116A (Release BK4B7A/B). Update also includes othe   |

|            | technical and editorial changes.                                               |

| E          | Manual updated with ECO 55280. Update includes technical and editorial         |

| (10-4-78)  | changes.                                                                       |

| F          | Manual updated with ECOs 55122, 55113, 55248A, 55325A, 55351, 55395, 55416A,   |

| (1-19-79)  | plus additional technical and editorial changes.                               |

| G          | Manual updated with ECOs 55438, 55663, 55476A, 55682, 55697A, 55743, 55742,    |

| (5-29-79)  | 55633A, 55728, 55658, and additional technical and editorial changes.          |

| Н          | Manual updated with ECOs 55785, 55804, 55821, 55810, 55835, plus additional    |

| (10-18-79) | editorial changes.                                                             |

| J          | Manual updated with ECOs 55854, 55898, plus additional editorial changes.      |

| (10-24-79) |                                                                                |

| K          | Manual updated with ECOs 55923, 55909, 55912, 55982, 55980, 55898, 55887B,     |

| (11-21-79) | plus additional technical and editorial changes.                               |

| L          | Manual updated with ECOs 55992, 55956, 60031, 55844B, 60032, plus additional   |

| (2-8-80)   | technical and editorial changes.                                               |

| M          | Manual updated with technical and editorial changes.                           |

| (6-27-80)  |                                                                                |

|            |                                                                                |

|            |                                                                                |

|            |                                                                                |

|            |                                                                                |

|            |                                                                                |

|            |                                                                                |

|            |                                                                                |

|            |                                                                                |

|            |                                                                                |

|            |                                                                                |

|            |                                                                                |

| ,          |                                                                                |

|            |                                                                                |

|            |                                                                                |

KØR 0639

REVISION LETTERS I, O, Q AND X ARE NOT USED

© 1977, 1978, 1979, 1980 by Control Data Corporation Printed in the United States of America Address comments concerning this manual to:

Control Data Corporation Technical Publications Dept. 7801 Computer Avenue Minneapolis, Mn. 55435

or use Comment Sheet in the back of this manual.

# Sheet\_1\_ of \_1\_

New features, as well as changes, deletions, and additions to information in this manual are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

| PAGE    | REV | PAGE   | REV    | PAGE    | RE∨ | PAGE    | REV | PAGI | REV |

|---------|-----|--------|--------|---------|-----|---------|-----|------|-----|

|         |     | 3-13   | A      | 3-59    | A   | Cmt Sht | -   |      |     |

| Cover   | -   | 3-14   |        | 3-60    | A   | Rtn Env |     |      |     |

| Blank   | -   |        | L      | 3-61    | A   | Blank   | - 1 |      |     |

| Title P | -   | 3-15   | L      | 3-62    | D   | Cover   |     |      |     |

| ii 🔰    | М   | 3-16   | A      |         | 1 1 | COVET   |     | 4    | 1   |

| iii     | М   | 3-17   | L      | 3-63    | A   |         |     |      |     |

| Blank   | -   | 3-18   | A      | 3-64    | A   |         |     |      |     |

| v       | м   | 3-19   | D      | 3-65    | А   |         |     |      |     |

| Blank   | -   | 3-20   | F      | 3-66    | A   |         |     |      |     |

| vii     | с   | 3-21   | F      | 3-67    | L   |         |     |      |     |

| viii    |     | 3-22   | A      | 3-68    | A   |         |     |      | 1 . |

|         | D   | 3-23   | A      | 3-69    | G   |         |     |      |     |

| ix      | D   | 3-24   | F      | 3-70    | G   |         |     |      | 1   |

| x       | D   |        | D      | 3-71    | A ^ |         |     |      |     |

| xi      | М   | 3-25   | F      | 3-72    | 1 1 |         |     |      | 1   |

| Blank   | -   | 3-26   |        |         | A   |         |     |      |     |

| S-1 Div | -   | 3-27   | F      | 3-73    | A   |         |     |      |     |

| Blank   | -   | 3-28   | D      | 3-74    | A   |         |     |      |     |

| 1-1     | Е   | 3-29   | D      | 3-75    | A   |         |     |      |     |

| 1-2     | A   | 3-30   | D      | 3-76    | A   |         |     |      |     |

| 1-3     | A   | 3-30.7 | D      | 3-77    | A   |         |     |      |     |

|         | D   | Blank  |        | 3-78    | A   |         |     |      |     |

| 1-4     |     | 3-31   | 1 1    | S-4 Div |     |         |     |      |     |

| 1-5     | G   |        | A<br>D | Blank   |     |         |     |      |     |

| 1-6     | А   | 3-32   |        | 4-1     | A   |         |     |      |     |

| 1-7     | А   | 3-33   | A      | 4-2     | E   |         |     |      |     |

| 1-8     | G   | 3-34   | A      |         |     |         |     |      |     |

| 1-9     | М   | 3-35   | A      | 4-3     | A   |         |     |      |     |

| 1-10    | М   | 3-36   | A      | 4-4     | A   |         |     |      |     |

| S-2 Div | -   | 3-37   | A      | 4-5     | A   |         |     |      |     |

| Blank   | -   | 3-38   | A      | 4-6     | A   |         |     |      |     |

| 2-1     | Е   | 3-39   | L      | 4-7     | A   |         |     |      |     |

| 2-2     | A   | 3-40   | Ā      | 4-8     | A   |         |     |      |     |

|         | M   | 3-41   | A      | 4-9     | A   |         |     |      |     |

| 2-3     |     |        | D      | 4-10    | A   |         |     |      |     |

| 2-4     | D   | 3-42   | D      | 4-11    | A   |         |     |      |     |

| 2-5     | н   | 3-43   |        | 4-12    | E   |         |     |      |     |

| Blank   | -   | 3-44   | D      |         |     |         | 1 1 |      |     |

| S-3 Div | -   | 3-45   | L      | 4-13    | A   |         | 1 1 |      |     |

| Blank   | -   | 3-46   | D      | 4-14    | A   |         |     |      |     |

| 3-1     | A   | 3-47   | L      | 4-15    | A   |         |     |      |     |

| 3-2     | A   | 3-48   | L      | 4-16    | A   |         |     |      |     |

| 3-3     | A   | 3-49   | L      | 4-17    | A   |         |     |      |     |

| 3-4     | A   | 3-50   | A      | 4-18    | A   |         |     |      |     |

|         | A   | 3-51   | A      | 4-19    | A   |         |     |      | 1   |

| 3-5     | 1 1 |        | 1      | 4-20    | A   |         |     |      | 1   |

| 3-6     | A   | 3-52   | A      | 4-21    | A   |         |     |      |     |

| 3-7     | A   | 3-53   | A      | 4-22    |     |         |     |      |     |

| 3-8     | G   | 3-54   | A      |         | A   |         |     |      |     |

| 3-9     | A   | 3-55   | A      | 4-23    | A   |         |     |      |     |

| 3-10    | L   | 3-56   | A      | Blank   | -   |         |     |      |     |

| 3-11    | Е   | 3-57   | A      |         |     |         |     |      |     |

| 3-12    | Ā   | 3-58   | A      |         |     |         |     |      |     |

|         |     |        |        |         |     |         |     |      |     |

|         |     |        |        |         |     |         |     |      |     |

|         |     |        |        |         |     | 1       |     | 1    |     |

|         |     |        |        |         |     |         |     |      |     |

|         | 1   | - I.   | 1 1    |         |     | 1       | 1   | 1    | 1   |

# PREFACE

This manual contains information applicable to all the Storage Module Drives (SMDs) listed in the configuration charts (found following the table of contents). The configuration charts define each of the equipments covered by this manual in terms of cabinet mounting styles, cabinet colors, and the various electronic features provided. Since this manual covers all the various configurations available on the SMD, it is necessary to understand exactly which configuration you have, in order to know which procedures in this manual are applicable to your drive.

This manual has been prepared for customer engineers and other technical personnel directly involved with maintaining the SMD.

Reference information is provided in four sections in this manual:

- Section 1 General Description

- Section 2 Operation

- Section 3 Theory of Operation

- Section 4 Discrete Component Circuits

Other manuals, also applicable to the SMD's covered in this manual, are as follows:

| P | ub         | 1 | i | С | a | t | i | o | n | NC | ۰. |  |

|---|------------|---|---|---|---|---|---|---|---|----|----|--|

| - | <b>u</b> 2 | - | - | ~ | ~ | - | - | - |   |    |    |  |

Title

83322150 Hardware Maintenance Manual Volume 1; Installation and Checkout, Maintenance, Parts Data

83322250 Hardware Maintenance Manual Volume 2; Diagrams and Wire Lists. Applicable to BK4XX

83322240 Hardware Maintenance Manual Volume 2; Diagrams and Wire Lists. Applicable to BK5XX

83322440 Normandale Circuits Manual; General Theory, Logic Symbology, Data Sheets.

A guide for the Disk Drive Operator, publication number 83323770, is also available. The guide may be ordered through Literature Distribution Services at the following address:

> Control Data Corporation Literature Distribution Services 308 North Dale St. St. Paul, MN 55103

# CONTENTS

| 1. GENERAL DESCRIPTION                |      |

|---------------------------------------|------|

| Introduction                          | 1-1  |

| Data Storage Medium                   | 1-3  |

| Drive Functional Description          | 1-3  |

| Drive Physical Description            | 1-4  |

| General                               | 1-4  |

| Mounting Configuration Description    | 1-4  |

| Drive Electronics Package Description | 1-6  |

| Equipment Configuration               | 1-9  |

| General                               | 1-9  |

| Equipment Identification Plate        | 1-9  |

| General                               | 1-9  |

| Equipment Identification Number       | 1-9  |

| Series Code                           | 1-10 |

| Part Number                           | 1-10 |

| Serial Number                         | 1-10 |

| FCO Log                               | 1-10 |

| Manual To Equipment Correlation       | 1-10 |

| 2. OPERATION                          |      |

| Introduction                          | 2-1  |

| Controls and Indicators               | 2-1  |

| General                               | 2-1  |

| Control Panel                         | 2-1  |

| Power Control Panel                   | 2-1  |

| Operating Instructions                | 2-1  |

| General                               | 2-1  |

| Disk Pack                             | 2-1  |

| General                               | 2-1  |

| Disk Pack Storage                     | 2-4  |

| Disk Pack Handling                    | 2-4  |

| Disk Pack Installation                | 2-4  |

| Disk Pack Removal                        | 2-5  |

|------------------------------------------|------|

| Power Application                        | 2-5  |

| General                                  | 2-5  |

| Power On Procedure                       | 2-5  |

| Power Off Procedure                      | 2-5  |

| 3. THEORY OF OPERATION                   |      |

| Introduction                             | 3-1  |

| Power System Functions                   | 3-2  |

| General                                  | 3-2  |

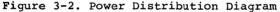

| Power Distribution                       | 3-2  |

| Power Sequencing                         | 3-2  |

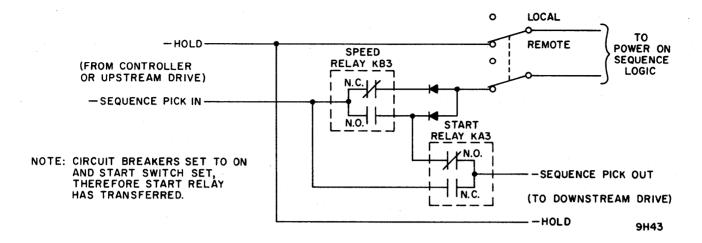

| Power On Sequence                        | 3-4  |

| Power Off Sequence                       | 3-6  |

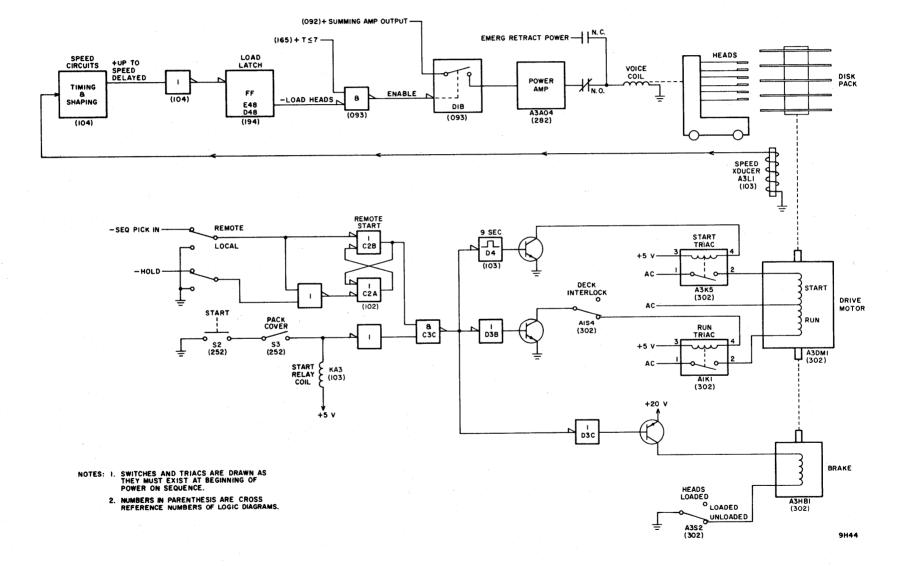

| Emergency Retract                        | 3-6  |

| Electromechanical Functions              | 3-7  |

| General                                  | 3-7  |

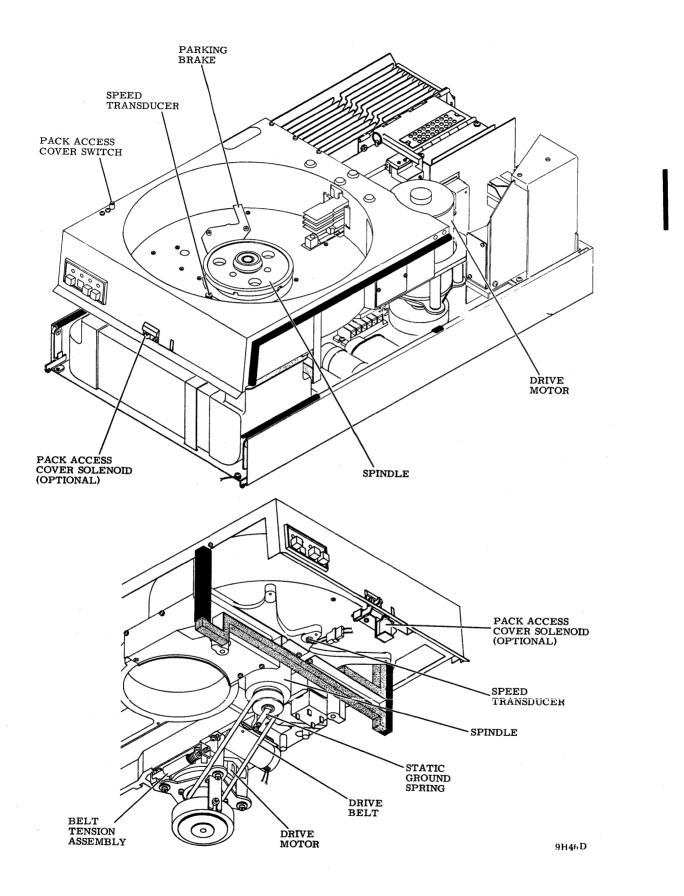

| Disk Pack Rotation                       | 3-7  |

| General                                  | 3-7  |

| Drive Motor                              | 3-9  |

| Spindle                                  | 3-9  |

| Parking Brake                            | 3-9  |

| Speed Transducer                         | 3-9  |

| Pack Access Cover Switch                 | 3-10 |

| Pack Access Cover Solenoid<br>(Optional) | 3-10 |

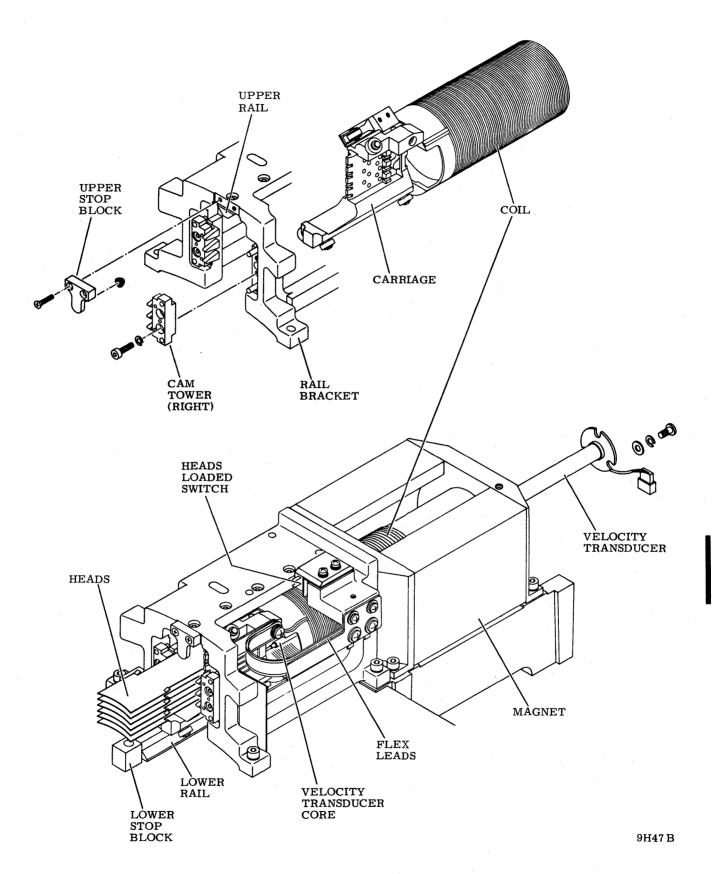

| Head Positioning                         | 3-10 |

| General                                  | 3-10 |

| Actuator Physical Description            | 3-10 |

| Actuator Functional Description          | 3-10 |

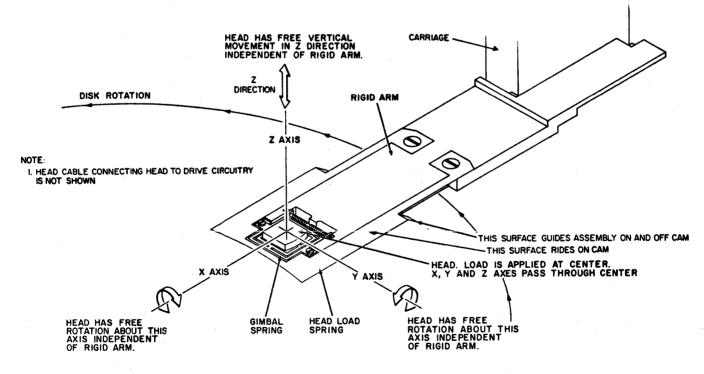

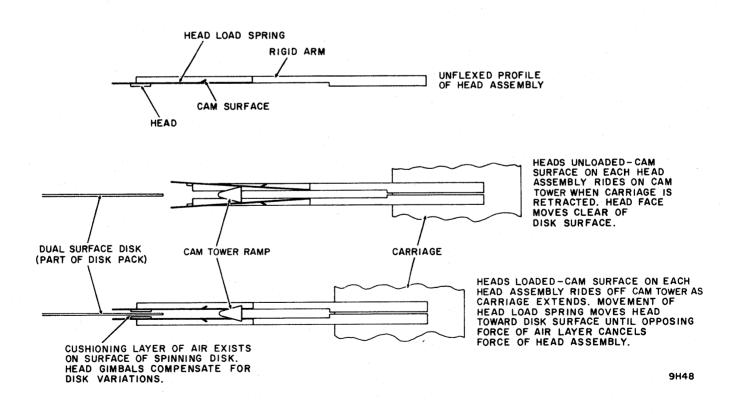

| Head Description                         | 3-12 |

| Air Flow System                          | 3-14 |

vii

| Interface Functions              | 3-14   | Direct Seek Position Control         | 3-41 |

|----------------------------------|--------|--------------------------------------|------|

| General                          | 3-14   |                                      | 3-41 |

|                                  |        | General                              |      |

| I/O Cables                       | 3-14   | Direct Seek Coarse Control           | 3-41 |

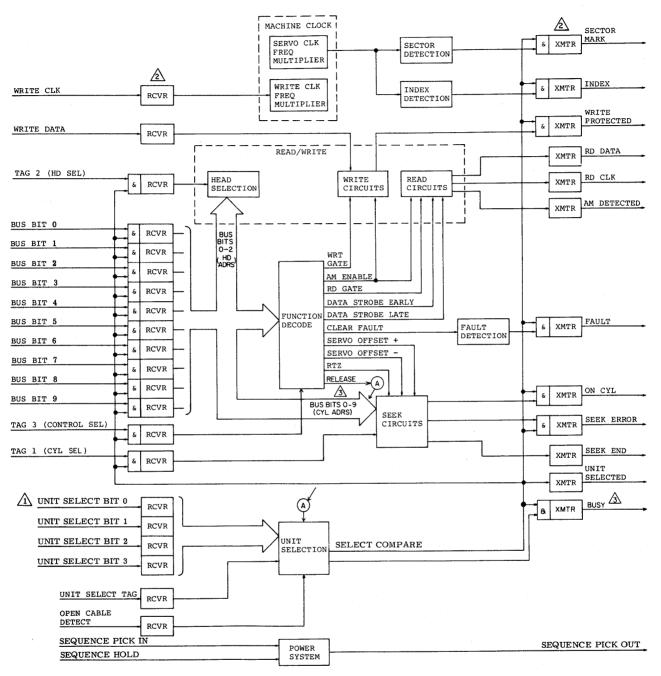

| I/O Signal Processing            | 3-14   | Direct Seek Fine Control             | 3-45 |

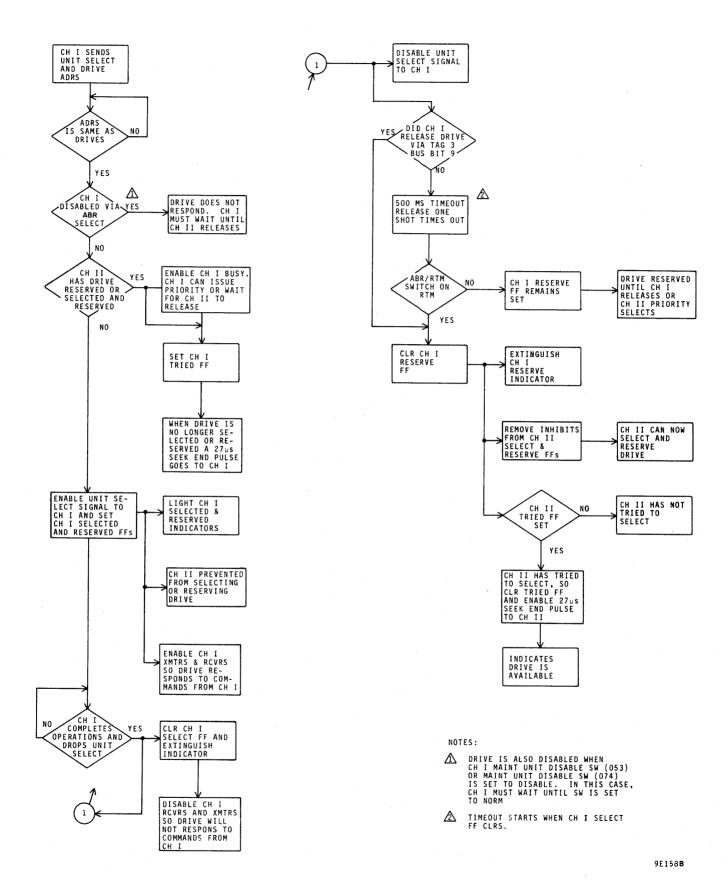

| Unit Selection                   | 3-22   | Load Seek Position Control           | 3-49 |

| General                          | 3-22   | General                              | 3-49 |

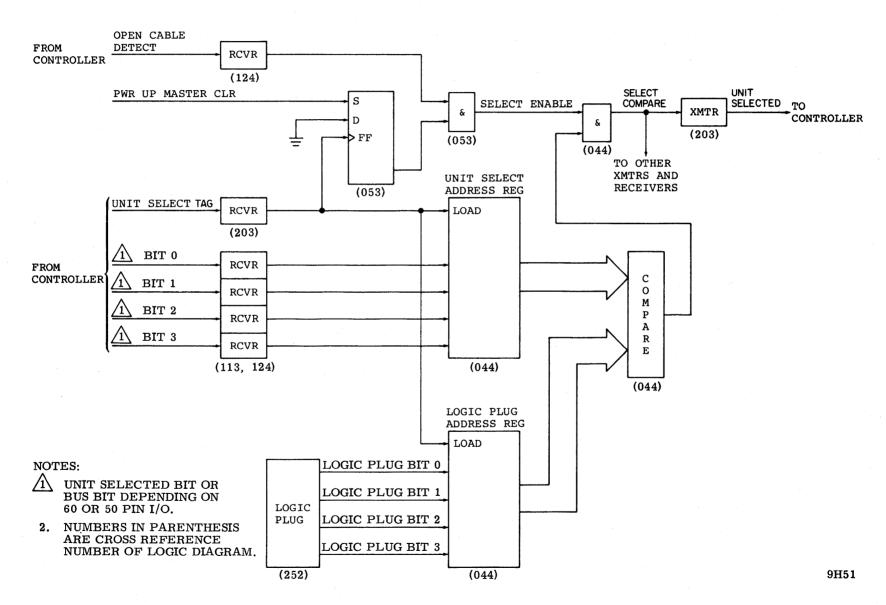

| Single Channel Unit Selection    | 3-22   | Load Seek Coarse Control             | 3-49 |

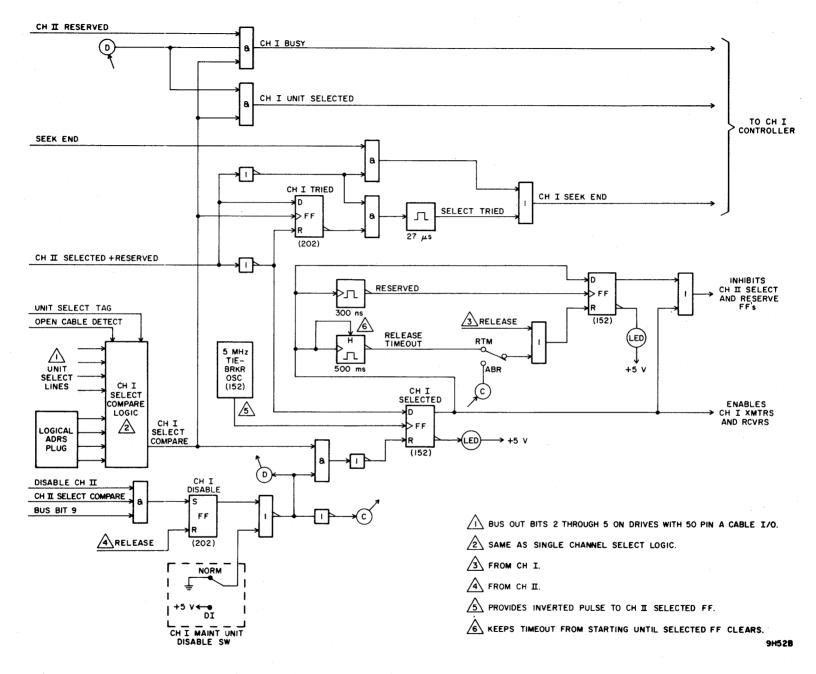

| Dual Channel Unit Selection      | 3-22   | Load Seek Fine Control               | 3-51 |

| General                          | 3-22   | Return to Zero Seek Position Control | 3-52 |

| Select and Reserve Function      | 3-22   | Unload Seek Position Control         | 3-52 |

| Release Function                 | 3-27   | Seek End and Error Detection         | 3-52 |

| Priority Select Function         | 3-27   | General                              | 3-52 |

| Maintenance Disable Function     | 3-27   | Timeout Error                        | 3-54 |

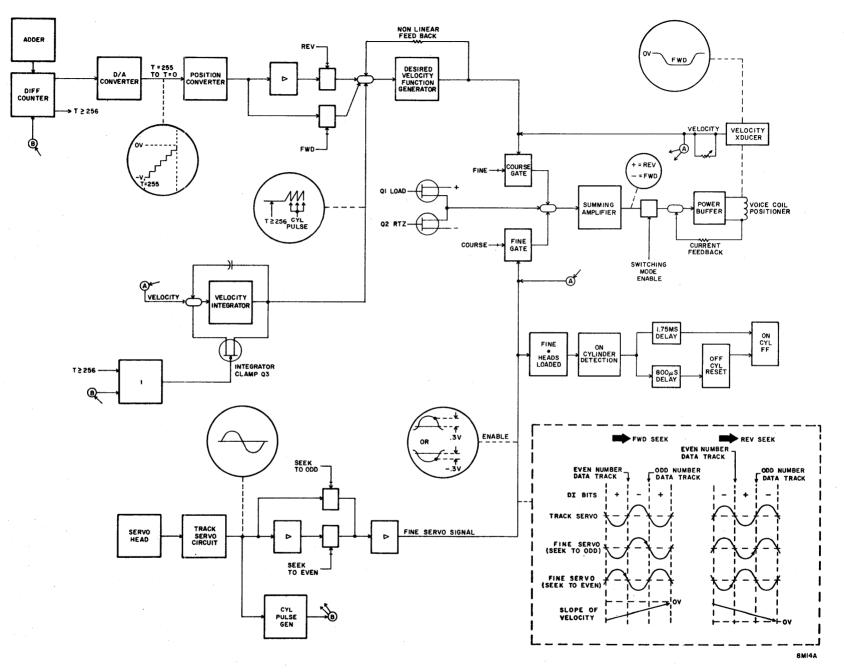

| Seek Functions                   | 3-27   | Maximum Address Fault                | 3-54 |

| General                          | 3-27   | End of Travel Errors                 | 3-54 |

|                                  |        | Machine Clock                        | 3-55 |

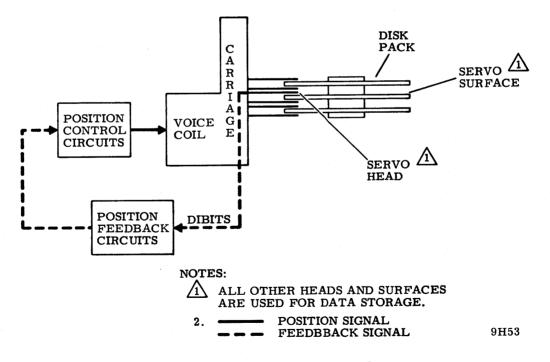

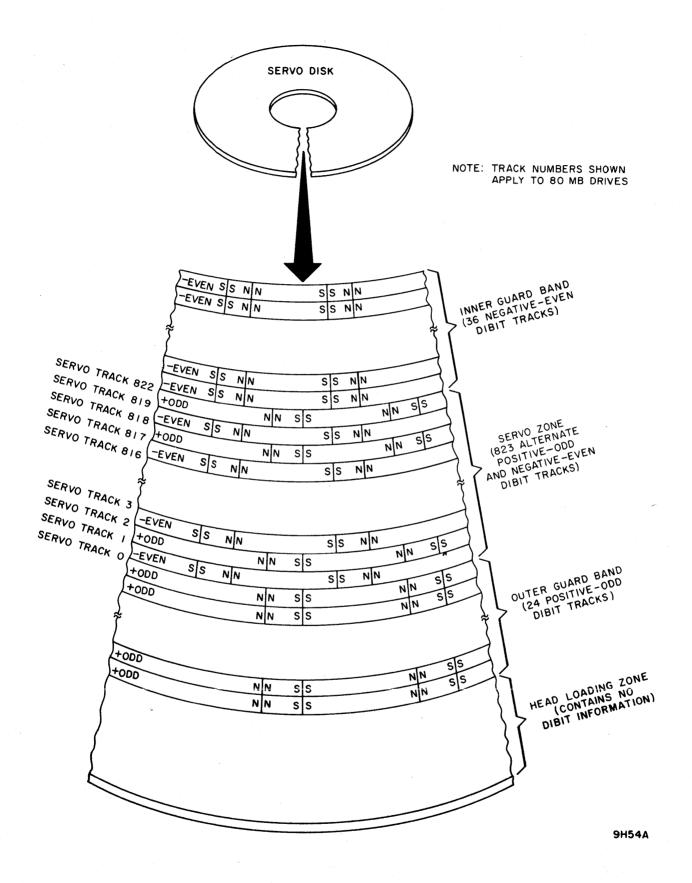

| Servo Disk Information           | 3-30.1 | General                              | 3-55 |

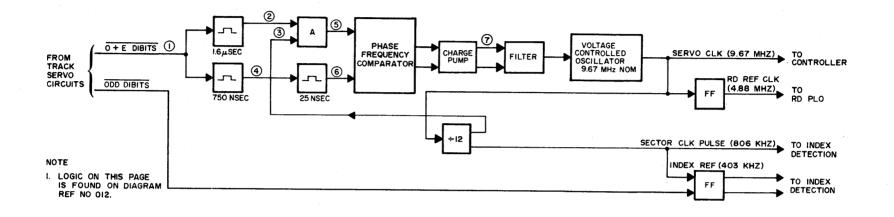

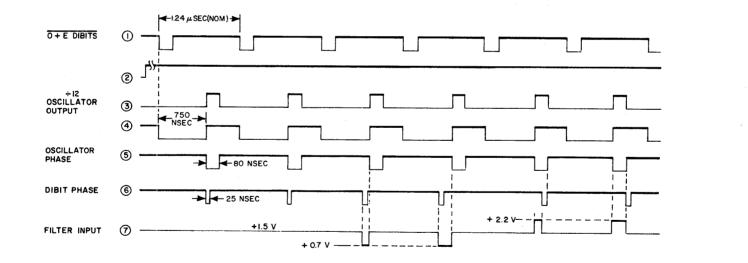

| General                          | 3-30.1 | Servo Clock Multiplier               | 3-55 |

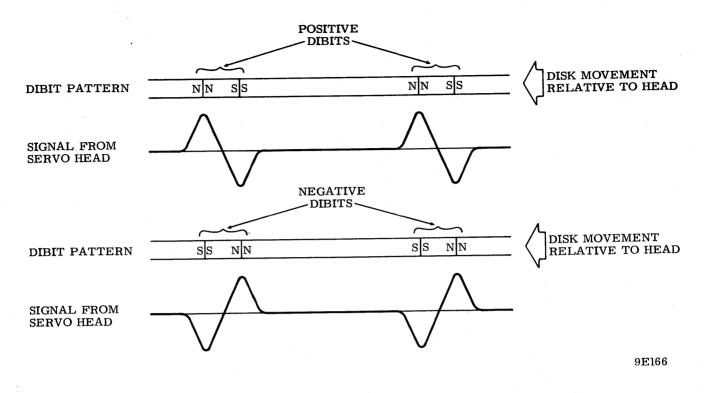

| Dibits                           | 3-30,1 | Write Clock Frequency Multiplier     | 3-55 |

| Dibit Tracks                     | 3-30.1 | Head Operation and Selection         | 3-57 |

| Outer and Inner Guard Bands      | 3-31   | General                              | 3-57 |

| Servo Zone                       | 3-31   | Head Functional Description          | 3-57 |

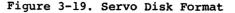

| Cylinder Concept                 | 3-31   | Head Selection                       | 3-58 |

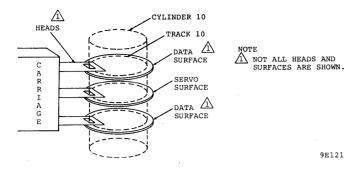

| Position Feedback Generation     | 3-31   | Track Orientation                    | 3-59 |

| General                          | 3-31   | General                              | 3-59 |

| Track Servo Preamp               | 3-33   | Index Detection                      | 3-59 |

| Dibit Sensing                    | 3-33   | Sector Detection                     | 3-61 |

| Automatic Gain Control (AGC)     | 3-33   | Read-Write Functions                 | 3-62 |

| Track Servo Signal Amplification | 3-35   | General                              | 3-62 |

| Odd/Even Dibits Clock Generation | 3-37   | Write Operations                     | 3-62 |

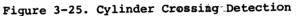

| Cylinder Crossing Detection      | 3-37   | General                              | 3-62 |

| End of Travel Detection          | 3-37   | Principles of MFM Recording          | 3-62 |

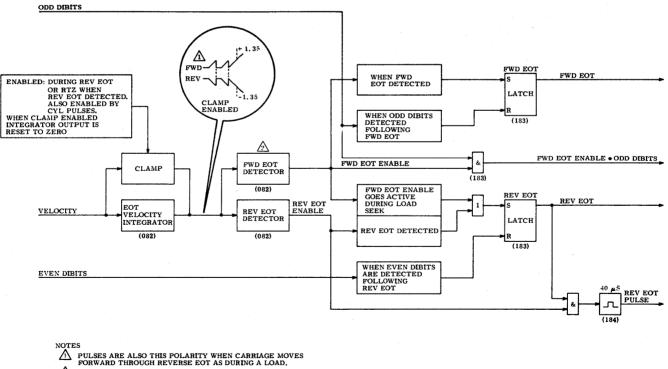

| Velocity Feedback Generation     | 3-40   | NRZ to MFM Converter/Write           |      |

| Position Signal Amplification    | 3-41   | Compensation Circuits                | 3-62 |

| , <u>r</u>                       |        |                                      |      |

| 3-66 | General                                                                                      | 3-76                                                                                                                                                                                                                                                                                                                         |

|------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-66 | Write Fault                                                                                  | 3-76                                                                                                                                                                                                                                                                                                                         |

| 3-67 | Head Select Fault                                                                            | 3-76                                                                                                                                                                                                                                                                                                                         |

| 3-67 | Read and Write Fault                                                                         | 3-76                                                                                                                                                                                                                                                                                                                         |

| 3-68 | (Read or Write) and Off Cylinder<br>Fault                                                    | 3-76                                                                                                                                                                                                                                                                                                                         |

| 3-68 | Voltage Fault                                                                                | 3-76                                                                                                                                                                                                                                                                                                                         |

| 3-69 | Errors Not Indicated by Fault Latch                                                          | 3-76                                                                                                                                                                                                                                                                                                                         |

| 3-69 | General                                                                                      | 3-76                                                                                                                                                                                                                                                                                                                         |

| 3-69 | Low Speed or Voltage                                                                         | 3-76                                                                                                                                                                                                                                                                                                                         |

|      | No Servo Tracks Fault                                                                        | 3-78                                                                                                                                                                                                                                                                                                                         |

|      | Seek Error                                                                                   | 3-78                                                                                                                                                                                                                                                                                                                         |

| 3-76 | 4. DISCRETE COMPONENT CIRCUITS                                                               |                                                                                                                                                                                                                                                                                                                              |

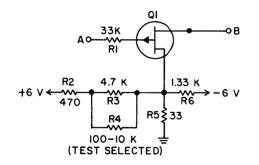

| 3-76 | Introduction                                                                                 | 4-1                                                                                                                                                                                                                                                                                                                          |

| 3-76 | Data Sheets                                                                                  | 4-1                                                                                                                                                                                                                                                                                                                          |

|      | 3-66<br>3-67<br>3-67<br>3-68<br>3-68<br>3-69<br>3-69<br>3-69<br>3-69<br>3-70<br>3-76<br>3-76 | <pre>3-66 Write Fault 3-67 Head Select Fault 3-67 Read and Write Fault 3-68 (Read or Write) and Off Cylinder Fault 3-68 Voltage Fault 3-69 Errors Not Indicated by Fault Latch 3-69 General Low Speed or Voltage 3-69 No Servo Tracks Fault 3-70 Seek Error 3-76 4. DISCRETE COMPONENT CIRCUITS 3-76 Introduction 3-76</pre> |

# FIGURES

| 1-1 | Disk Pack                                      | 1-3  |

|-----|------------------------------------------------|------|

| 1-2 | Drive Functional Blocks                        | 1-4  |

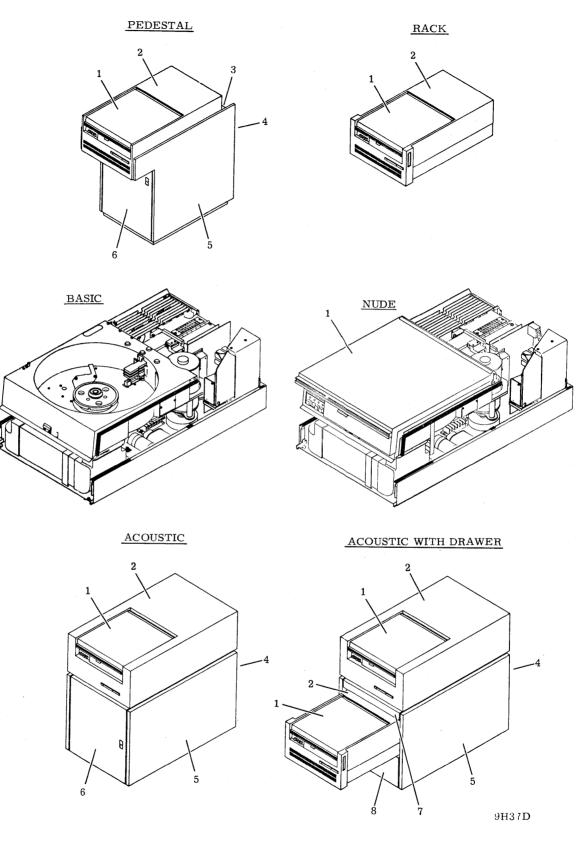

| 1-3 | Drive Mounting Configurations                  | 1-5  |

| 1-4 | Drive Electronic Package                       | 1-8  |

| 1-5 | Equipment Identification Plate                 | 1-9  |

| 2-1 | Control Panel Switches and<br>Indicators       | 2-1  |

| 2-2 | Power Control Panel Switches<br>and Indicators | 2-3  |

| 3-1 | Drive Functional Block Diagram                 | 3-1  |

| 3-2 | Power Distribution Diagram                     | 3-3  |

| 3-3 | Power Sequencing Circuits                      | 3-4  |

| 3-4 | Power On Sequence - Simplified<br>Logic        | 3-5  |

| 3-5 | Emergency Retract Circuits                     | 3-6  |

| 3-6 | Electromechanical Functions -<br>Block Diagram | 3-7  |

| 3-7 | Disk Pack Rotation Mechanisms                  | 3-8  |

| 3-8 | Actuator Components                            | 3-11 |

| 3-9  | Head Arm Assembly                                 | 3-12   |

|------|---------------------------------------------------|--------|

| 3-10 | Head Loading                                      | 3-13   |

| 3-11 | I/O Cables                                        | 3-15   |

| 3-12 | I/O Signal Processing                             | 3-21   |

| 3-13 | Single Channel Unit Select Logic                  | 3-23   |

| 3-14 | Channel I Dual Channel Select<br>Logic Flow Chart | 3-24   |

| 3-15 | Dual Channel Select and Reserve<br>Flow Chart     | 3-25   |

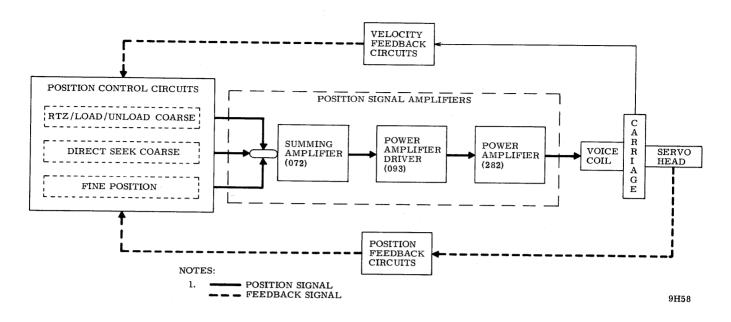

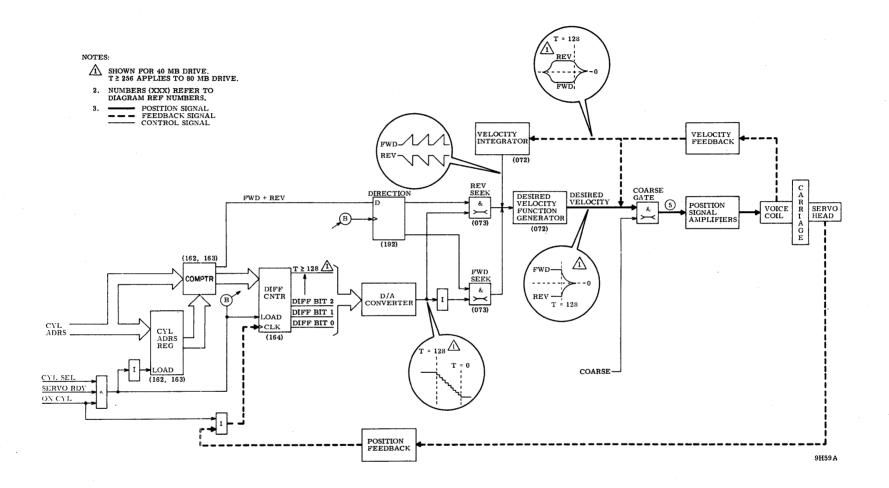

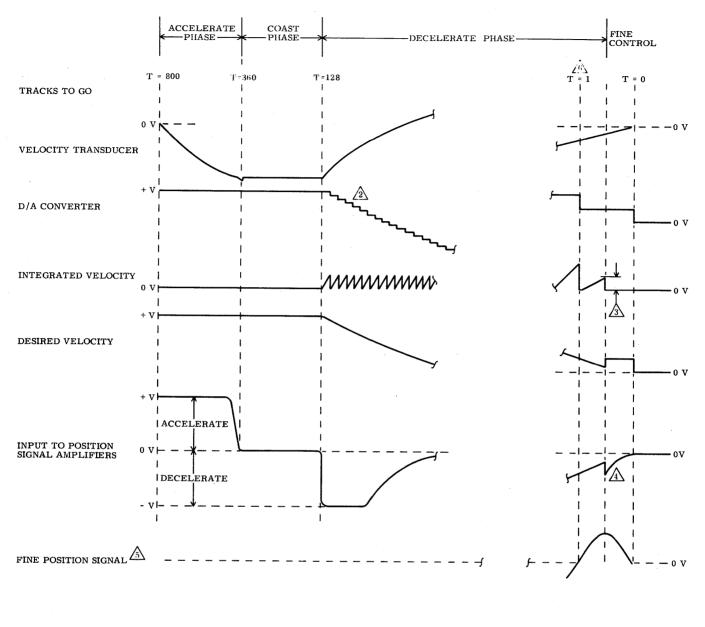

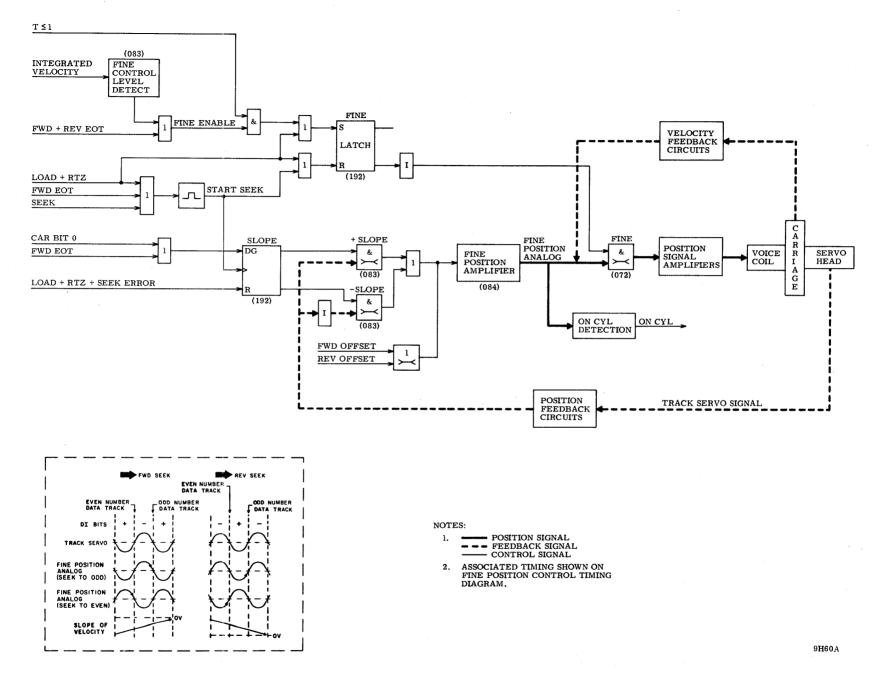

| 3-16 | Servo System Functional Block<br>Diagram          | 3-28   |

| 3-17 | Servo Head and Surface                            | 3-30.3 |

| 3-18 | Positive and Negative Dibit<br>Pattern            | 3-31   |

| 3-19 | Servo Disk Format                                 | 3-32   |

| 3-20 | Cylinder Concept                                  | 3-33   |

| 3-21 | Position Feedback Circuit -<br>Block Diagram      | 3-34   |

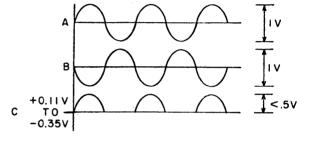

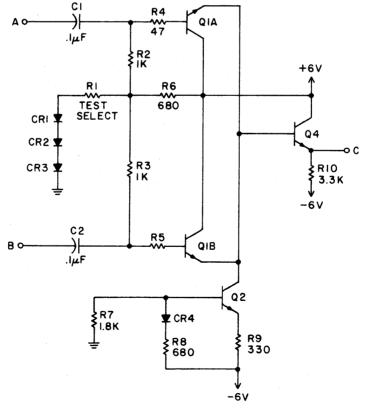

| 3-22 | Servo Preamp Output                               | 3-35   |

| 3-23 | Track Servo Amplifier Circuit and Signals       | 3-36 | 3-42         | Reading Data                                                | 3-58 |

|------|-------------------------------------------------|------|--------------|-------------------------------------------------------------|------|

|      |                                                 |      | 3-43         | Head Select Circuits                                        | 3-59 |

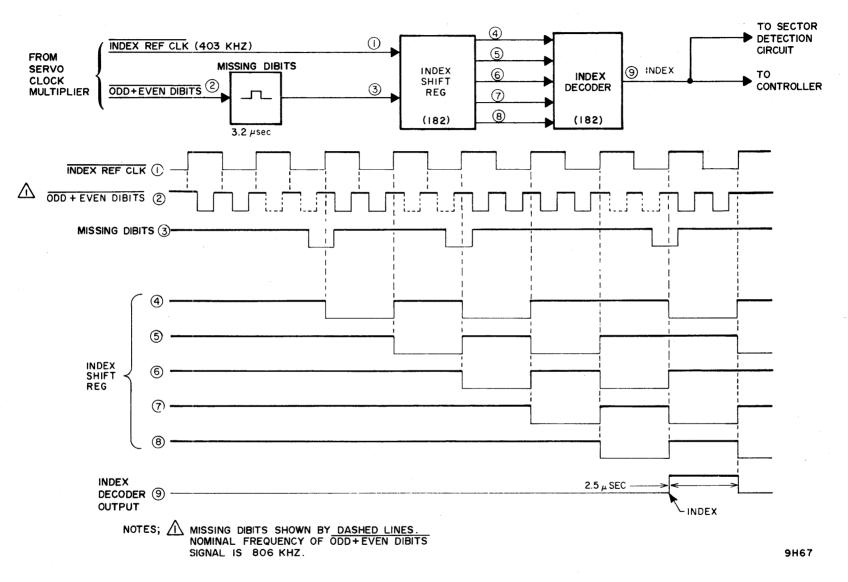

| 3-24 | Odd/Even Dibit Clock - Logic and<br>Timing      | 3-38 | 3-44         | Index Detection - Logic and<br>Timing                       | 3-60 |

| 3-25 | Cylinder Crossing Detection                     | 3-39 |              |                                                             | 5 00 |

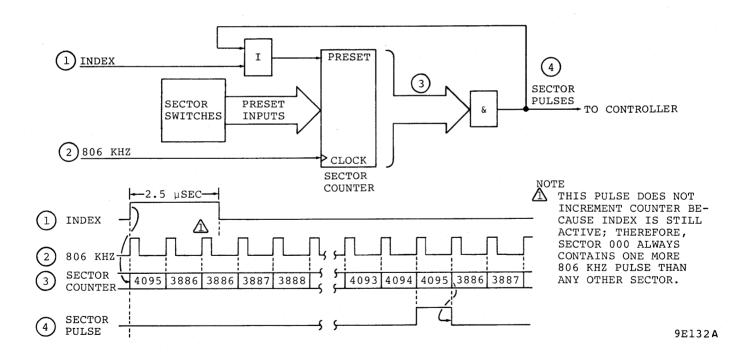

| 3-26 | End of Travel Detection Circuits                | 3-39 | 3-45         | Sector Detection - Logic and<br>Timing                      | 3-61 |

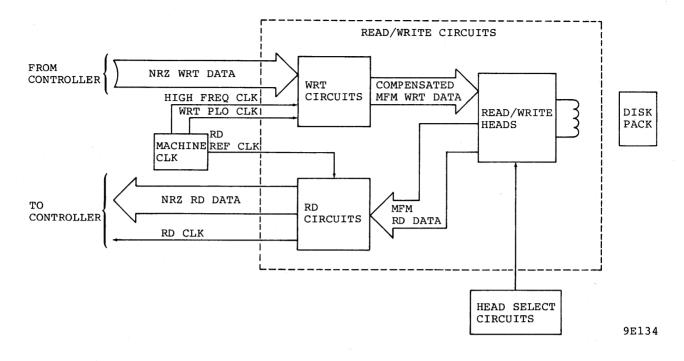

| 3-27 | Velocity Feedback Circuits                      | 3-40 | 3-46         | Read-Write Circuits - Block<br>Diagram                      | 3-63 |

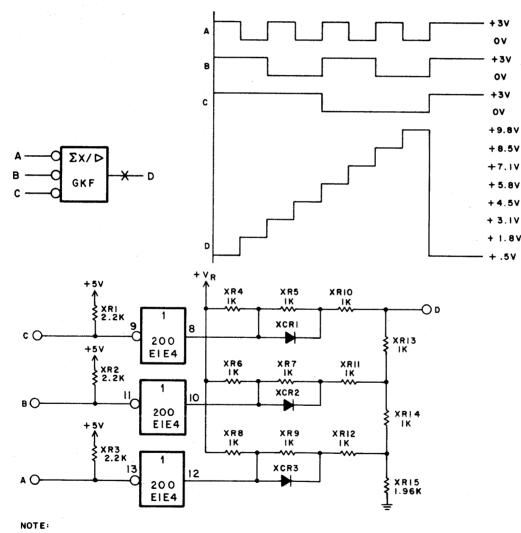

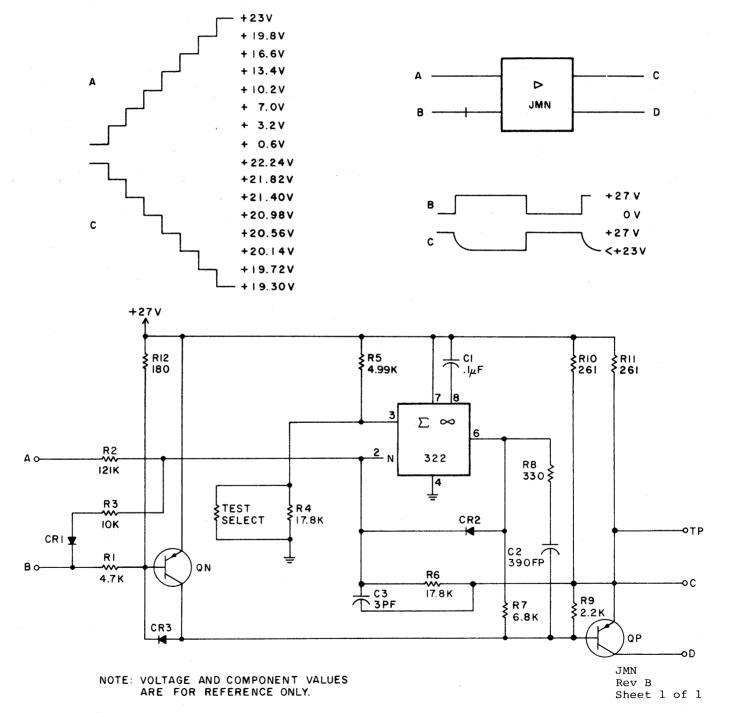

| 3-28 | Position Signal Amplifier<br>Circuits           |      | 3-47         | Write Circuits - Block Diagram                              | 3-63 |

| 3-29 | Direct Seek Coarse Position<br>Control Circuits | 3-42 | 3-48         | MFM Recording - Waveforms and<br>Timing                     | 3-64 |

| 3-30 | Direct Seek Coarse Position<br>Control Signals  | 3-44 | 3-49         | NRZ to MFM Converter/Write<br>Compensation Circuit          | 3-65 |

| 3-31 | Fine Position Control Circuits                  | 3-46 | 3-50         | Write Compensation Timing                                   | 3-65 |

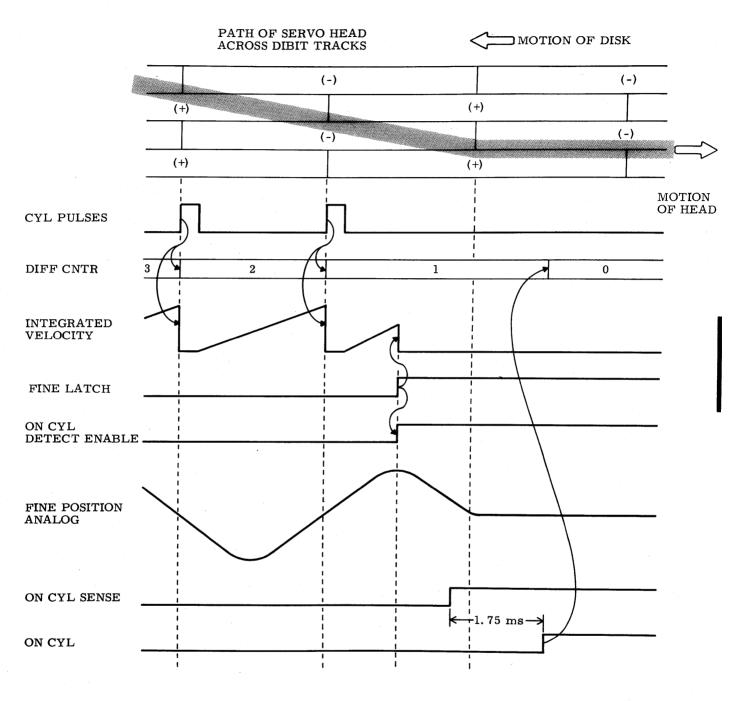

| 3-32 | Fine Position Control Timing                    | 3-47 | 3-51         | Write Driver Circuit and Timing                             | 3-67 |

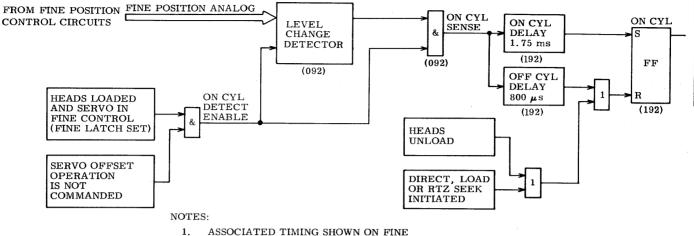

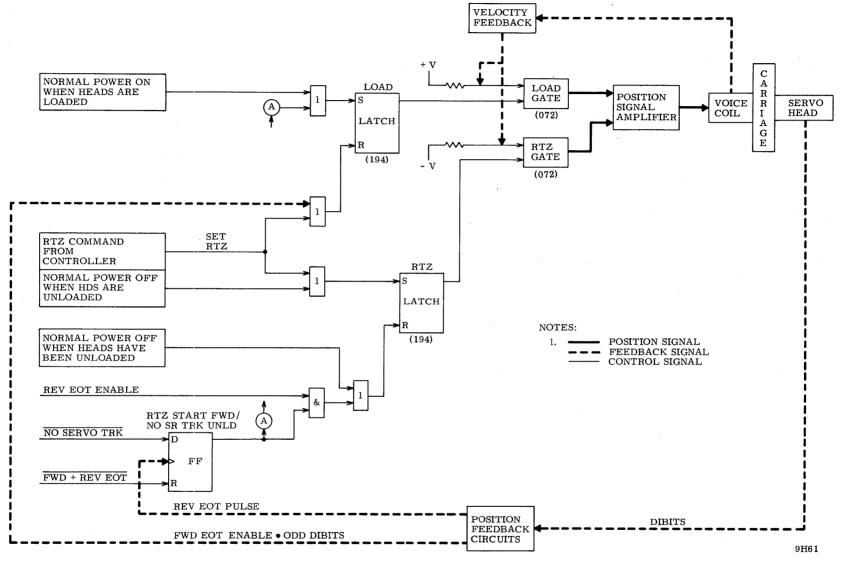

| 3-33 | On Cylinder Detection Logic                     | 3-49 | 3-52         | Read Circuits - Block Diagram                               | 3-68 |

| 3-34 | RTZ/Load/Unload Coarse Position<br>Control Loop | 3-50 | 3-53         | Analog Read Data Detection<br>Circuits                      | 3-69 |

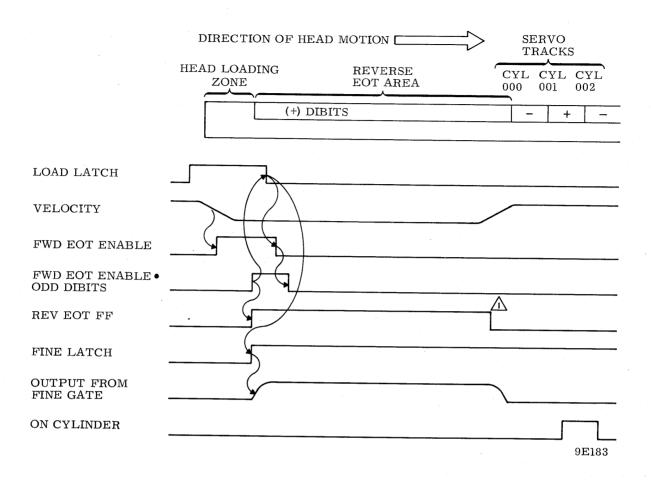

| 3-35 | Load Seek Timing                                | 3-51 | 3-54         | Read Analog to Digital Converter<br>- Logic and Timing      | 3-70 |

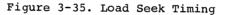

| 3-36 | Return to Zero Seek Timing                      | 3-53 |              | 5                                                           |      |

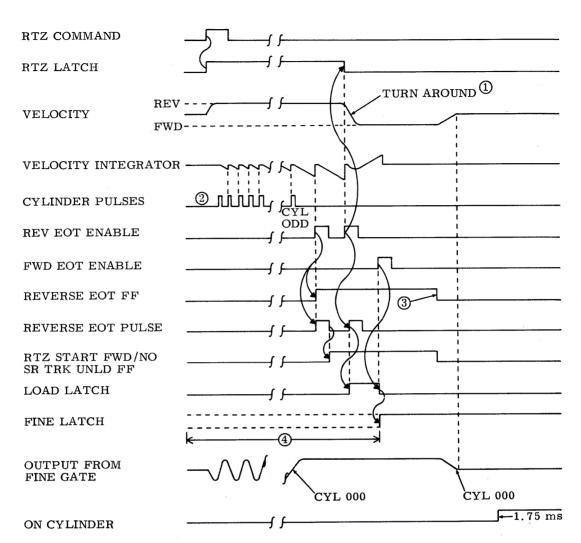

| 3-37 | Seek End and Seek Error<br>Detection            | 3-54 | 3-55         | Lock to Data/Address Mark Detec-<br>tion - Logic and Timing | 3-71 |

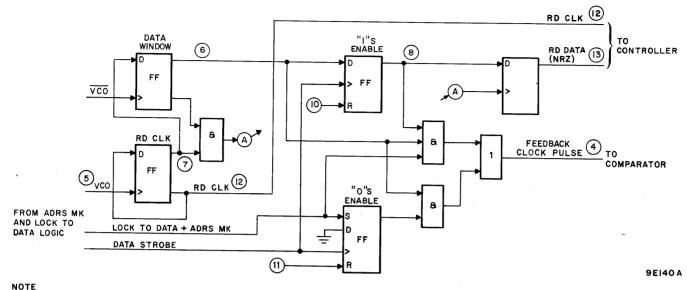

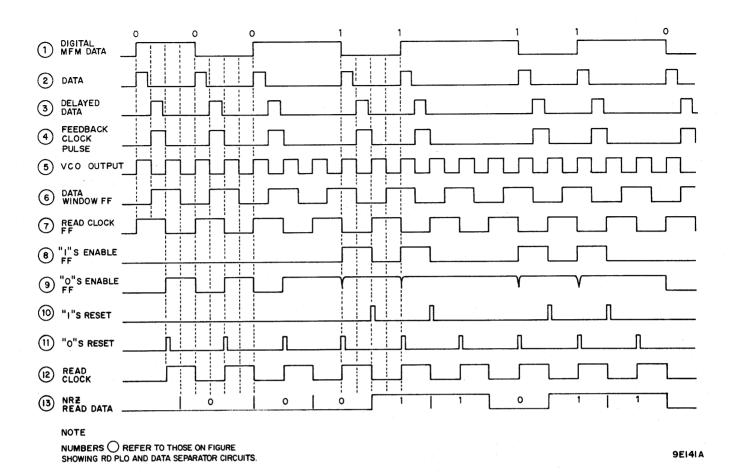

| 3-38 | Servo Clock Multiplier                          | 3-56 | 3-56         | Read PLO and Data Separator<br>Circuits                     | 3-72 |

| 3-39 | Write Clock Multiplier                          | 3-57 | <b>3-</b> 57 | Data Separator Logic                                        | 3-74 |

| 3-40 | Read-Write Heads                                | 3-57 | 3-58         | Read PLO and Data Separator<br>Timing                       | 3-75 |

| 3-41 | Writing Data                                    | 3-58 |              | 1 TWT118                                                    |      |

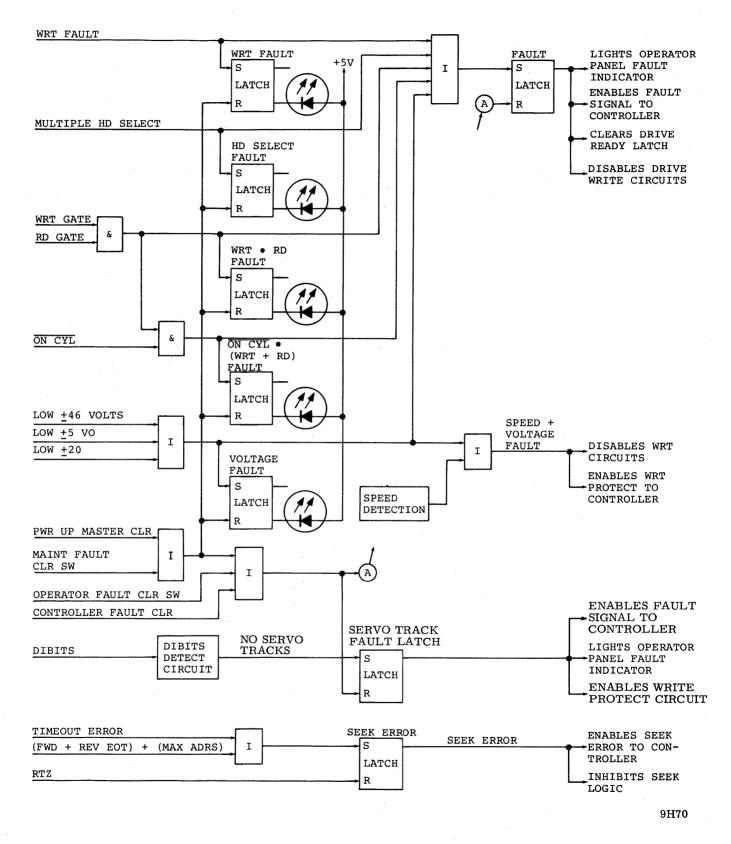

|      |                                                 |      | 3-59         | Fault and Error Detection                                   | 3-77 |

# TABLES

| 1-1 | Equipment Specifications                | 1-1  | 3-2 | Drive to Controller Signal Line<br>Functions | 3-20 |

|-----|-----------------------------------------|------|-----|----------------------------------------------|------|

| 1-2 | Mounting Configuration Assemblies       | 1-4  | 3-3 | Dual Channel Unit Select Circuit             |      |

| 1-3 | Drive Electronics Package<br>Assemblies | 1-6  |     | Functions                                    | 3-26 |

|     |                                         |      |     | Servo Circuit Functions                      | 3-29 |

| 2-1 | Control Panel Functions                 | 2-2  | 3-4 | Write Circuit Functions                      | 3-64 |

| 2-2 | Power Control Panel Functions           | 2-2  | 3-5 | Write Current Zones                          | 3-66 |

| 3-1 | Controller to Drive Signal Line         |      |     |                                              |      |

|     | Functions                               | 3-18 | 3-6 | Read Circuit Functions                       | 3-68 |

# **ABBREVIATIONS**

| ABR          | Absolute Reserve              | MULT        | Multiple                          |

|--------------|-------------------------------|-------------|-----------------------------------|

| ABV          | Above                         | NC          | No Connection                     |

| ADDR         | Address                       | NEG         | Negative                          |

| ADRS         | Address                       | NFR         | Not Field Replaceable             |

| AGC          | Automatic Gain Control        | NO          | Number                            |

| AM           | Address Mark                  | NOM         | Nominal                           |

| AMPL         | Amplifier                     | NORM        | Normal                            |

| BLK          | Black                         | NRM         | Normal                            |

| BLW          | Below                         | NRZ         | Nonreturn To Zero                 |

| CAR          | Cylinder Address Register     | PC PT       | Piece Part                        |

| СН           | Channel                       | PLO         | Phase Lock Oscillator             |

| CHAN         | Channel                       | PN          | Part Number                       |

| CNTLGL       | Centrifugal                   | POS         | Positive                          |

| CNTR         | Counter                       | PWR         | Power                             |

| COMP         | Compensation                  | RCVRS       | Receivers                         |

| COMPTR       | Comparitor                    | RD          | Read                              |

| CONFIG       | Configuration                 | RDY         | Ready                             |

|              | Continued                     | REC         | Receiver                          |

| CONT         | Cross Reference               | REF         | Reference                         |

| CR REF       |                               | REG         | Register                          |

| CYL          | Cylinder                      | REV         | 5                                 |

| D/A          | Digital To Analog             |             | Reverse                           |

| DCDR         | Decoder                       | RGTR<br>RTM | Register                          |

| DIFF         | Difference                    |             | Reserve Timer                     |

| DLY          | Delay                         | RTZ         | Return To Zero                    |

| DRVR         | Driver                        | S&IOABC     | Sector and Index On A and B Cable |

| DSBL         | Disable                       | S&IOBC      | Sector and Index On B Cable       |

| ECL          | Emitter Coupled Logic         | s/c         | Series Code                       |

| ECO          | Engineering Change Order      | SEC         | Second                            |

| EMER         | Emergency                     | SEL         | Select                            |

| EN           | Enable                        | SEQ         | Sequence                          |

| EOT          | End Of Travel                 | SER         | Servo                             |

| EQUIP        | Equipment                     | SH          | Sheet                             |

| EQUIV        | Equivalent                    | SOL         | Solenoid                          |

| FCO          | Field Change Order            | SR          | Servo                             |

| FF           | Flip Flop                     | SW          | Switch                            |

| FIG          | Figure                        | Т           | Track                             |

| FLT          | Fault                         | TBS         | To Be Supplied                    |

| FREQ         | Frequency                     | TLA         | Top Level Assembly                |

| FTU          | Field Test Unit               | TP          | Test Point                        |

| FWD          | Forward                       | TRK         | Track                             |

| GND          | Ground                        | TTL         | Transistor Transistor Logic       |

| HD           | Head                          | UNREG       | Unregulated                       |

| I/0          | Input-Output                  | VCO         | Voltage Controlled Oscillator     |

| INTLK        | Interlock                     | VCO<br>₩+R  | Write Or Read                     |

| LAP          | Logical Address Plug          | W•R         | Write and Read                    |

| LD           | Load                          |             |                                   |

| MAINT        | Maintenance                   | W/          | With                              |

| MAINI<br>MAX | Maximum                       | W/O         | Without                           |

|              | Maximum<br>Megabyte           | WRT         | Write                             |

| MB           | Modified Frequency Modulation | WT          | White                             |

| MFM          | 1 1                           | XDUCER      | Transducer                        |

| MK           | Mark                          | XMTR        | Transmitter                       |

**SECTION 1**

**GENERAL DESCRIPTION**

# INTRODUCTION

The Control Data BK4XX and BK5XX Storage Module Drives (SMD's) are high speed, random access digital data storage devices that connect to a central processor through a controller. The major difference between the drives is their storage capacity. The total data storage capacity of the BK4XX is 40 megabytes, and the BK5XX is 80 megabytes. All the equipment specifications for each drive are listed in table 1-1.

The remainder of this section provides a general description of the drives and is divided into the following areas:

- Data Storage Medium Describes the disk pack which is the medium used to store the data.

- Drive Functional Description Explains the basic function of the drive.

- Drive Physical Description Provides a basic description of the drives physical characteristics.

- Equipment Configuration Describes the various drive configurations and how to identify them.

| Specification                                                                                                                                             | Value                                                                                                                                                                                                   |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <u>Size</u>                                                                                                                                               | Refer to Space and Clearance paragraph in<br>Installation and Checkout section of maintenance<br>manual volume 1.                                                                                       |  |

| Weight<br>Pedestal Cabinet<br>Acoustic Cabinet<br>Acoustic Cabinet With Drawer<br>Rack Mount (both 30 and 36 in)<br>Basic<br>Nude                         | 243 lbs. (110 kg)<br>340 lbs. (155 kg)<br>567 lbs. (258 kg)<br>160 lbs. (73 kg)<br>135 lbs. (61 kg)<br>140 lbs. (62 kg)                                                                                 |  |

| Temperature<br>Operating<br>Operating Change/Hr<br>Transit (packed for shipment)<br>Non-Operating Change/Hr                                               | 590 F (15.5° C) to 90° F (32.2°C)<br>12° F (6.6° C) per hr<br>-40° F (-40.4° C) to 158° F (70.0° C)<br>36° F (20° C) per hr                                                                             |  |

| Relative Humidity<br>Operating<br>Transit (packed for shipment)                                                                                           | 20% to 80% ) No Condensation<br>5% to 95% )                                                                                                                                                             |  |

| Altitude<br>Operating<br>Transit (packed for shipment)                                                                                                    | -1000 ft (305 m) to 6500 ft (2000 m)<br>-1000 ft (305 m) to 15,000 ft (4572 m)                                                                                                                          |  |

| Disk Pack<br>Type<br>Disks/Pack<br>Data Surfaces<br>Servo Surfaces<br>Usable Tracks/Surface<br>Tracks/Inch<br>Track Spacing (center to center)<br>Coating | 40 MB - 876 80 MB - 877<br>3 (Top and bottom disks are for protection only.)<br>5<br>1<br>40 MB - 411 80 MB - 823<br>40 MB - 192 80 MB - 384<br>40 MB0052 (.13 mm) 80 MB0026 (.66 mm)<br>Magnetic Oxide |  |

| Table continued on next page                                                                                                                              |                                                                                                                                                                                                         |  |

#### TABLE 1-1. EQUIPMENT SPECIFICATIONS

# TABLE 1-1. EQUIPMENT SPECIFICATIONS (Contd)

| Specification                                                                                                      | Value                                                                                                                                                                              |  |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Data Capacity*<br>Bytes/Track<br>Bytes/Cylinder<br>Bytes/Spindle<br>Cylinders/Spindle                              | $\begin{array}{ccccccc} 40 & \text{MB} & & & \frac{80 & \text{MB}}{20 & 160} \\ 100 & 800 & & & 100 & 800 \\ 41 & 428 & 800 & & 82 & 958 & 400 \\ & & & 411 & & & 823 \end{array}$ |  |

| Recording Characteristics<br>Mode<br>Density (nominal)<br>Outer Track<br>Inner Track<br>Rate (nominal)             | Modified Frequency Modulation (MFM)<br>4038 bits/in (1590 bits/cm)<br>6038 bits/in (2377 bits/cm)<br>9.67 MHz (1 209 600 bytes/sec)                                                |  |

| <u>Heads</u><br>Read/Write<br>Servo<br>Read/Write Width                                                            | 5<br>1<br>40 MB - 0.004 in (0.102 mm)<br>80 MB - 0.002 in (0.051 mm)                                                                                                               |  |

| Seek Characteristics<br>Mechanism<br>Max Seek Time (411 or 823 Tracks)<br>Max Track Seek Time<br>Average Seek Time | Voice Coil, Driven By Servo Loop<br>55 ms<br>6 ms<br>30 ms                                                                                                                         |  |

| Latency**<br>Average<br>Maximum                                                                                    | 8.33 ms (at 3600 r/min)<br>17.3 ms (at 3474 r/min)                                                                                                                                 |  |

| Spindle Speed                                                                                                      | 3600 r/min                                                                                                                                                                         |  |

| Controllers Per Drive                                                                                              | l or 2 - Refer to channel access column on configuration chart in front matter of manual.                                                                                          |  |

| Drives Per Controller                                                                                              | 16 maximum                                                                                                                                                                         |  |

| Power Requirements                                                                                                 | Refer to configuration chart in front matter of<br>manual. Also, refer to Installation and Checkou<br>section of maintenance manual volume 1.                                      |  |

| * Based on 8 bit bytes and not allow<br>** Latency is time required to reach<br>cylinder.                          | wing for sectoring tolerance gaps.<br>specific track location after drive is on                                                                                                    |  |

# DATA STORAGE MEDIUM

The data storage medium for the drive is a disk pack, consisting of five 14-inch disks, center mounted on a hub (see figure 1-1). The disk pack is portable and interchangeable between equivalent drives. The packs are not interchangeable, however, between the 40 and 80 megabyte drives.

The disk pack has a total of six usable surfaces, each coated with a layer of magnetic oxide and related binders and adhesives. One of these surfaces, referred to as the servo surface, contains information prerecorded at the factory. This surface is used by the drive to generate position information and various timing signals. The remaining five surfaces can be used by the system for data storage and are referred to as data surfaces.

Figure 1-1. Disk Pack

# **DRIVE FUNCTIONAL DESCRIPTION**

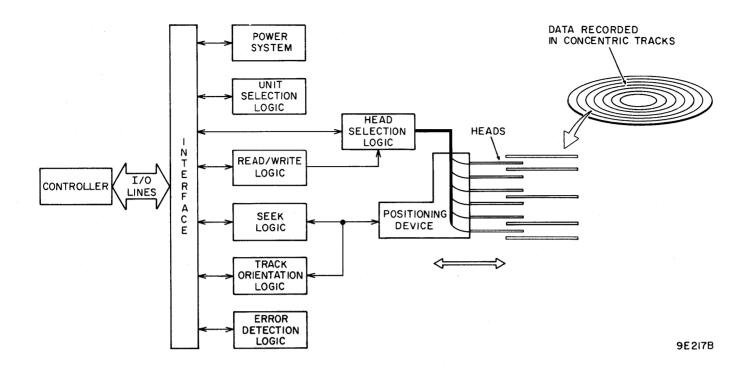

The drive contains all the circuits and mechanical devices necessary to record data on and recover it from the disk pack (see figure 1-2). The necessary power for this is provided by the drives power supply, which receives its input power from the site main power source.

All functions performed by the drive are done under direction of the controller. The controller communicates with the drive via the interface which consists of a number of I/O lines carrying the necessary signals to and from the drive.

Some interface lines, including those that carry commands to the drive, are not enabled unless the drive is selected by the controller. Unit selection allows the controller, which can be connected to more than one drive, to initiate and direct an operation on a specific unit.

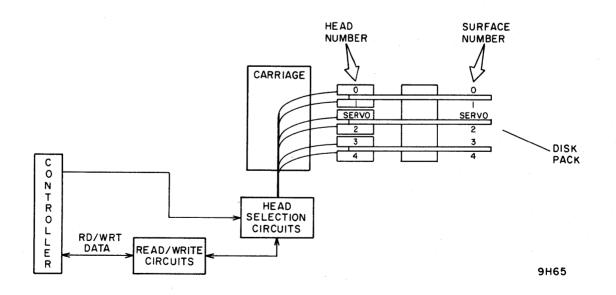

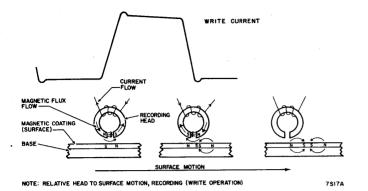

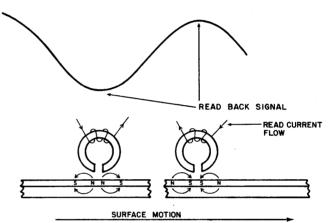

All operations performed by the drive are related to data storage and recovery (normally referred to as writing and reading). The actual reading and writing is performed by electromagnetic devices called heads that are positioned over the recording surfaces of the rotating disk pack. There is a separate head for each surface in the pack and the heads are positioned in such a way that data is written in concentric tracks around the disk surfaces (see figure 1-2).

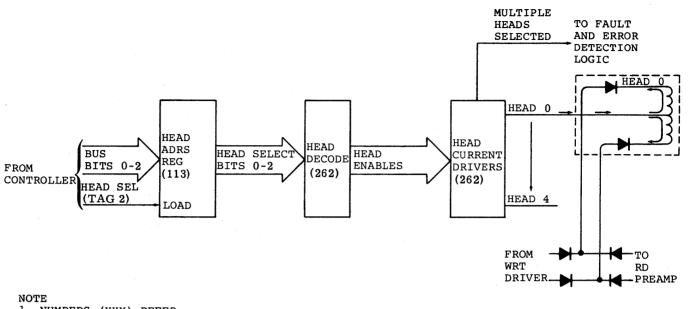

Before any read or write operation can be performed the controller must instruct the drive to position the heads over the desired track (called seeking) and also to use the head located over the surface (head selection) where the operation is to be performed.

After selecting a head and arriving at the data track, the controller still must locate that portion of the track on which the data is to be written or read. This is called track orientation and is done by using the Index and Sector signals generated by the drive. The Index signal indicates the logical beginning of each track and the Sector signals are used by the controller to determine the position of the head on the track with respect to Index.

When the desired location is reached the controller commands the drive to actually read or write the data. During a read operation the drive recovers data from the pack, and transmits it to the controller. During a write operation, the drive receives data from the controller, processes it and writes it on the disk pack.

Figure 1-2. Drive Functional Blocks

The drive is also capable of recognizing certain errors that may occur during its operation. When an error is detected, it is indicated either by a signal to the controller or by a maintenance indicator on the drive itself.

#### are mounted on slide rails, others are mounted in cabinets, and the naked unit is available as a desk top unit or can be mounted in a user supplied cabinet. Table 1-2 lists the names of the various mounting configuration assemblies.

# DRIVE PHYSICAL DESCRIPTION

#### GENERAL

The physical description of the drive is divided into two areas: 1) Mounting Configuration Description, and 2) Drive Electronics Package Description. The mounting configuration description deals with the various cabinet styles in which the SMD is available. The drive electronics package description deals with the functional electronics of the SMD.

#### MOUNTING CONFIGURATION DESCRIPTION

The SMD is available in a number of mounting configurations (see figure 1-3). The mounting configurations provides a means of enclosing the drive electronics package and preventing dust and dirt from entering the pack area. In addition, some of the mounting configurations provide acoustic isolation. Some units (rack and drawer mounted)

# TABLE 1-2. MOUNTING CONFIGURATION ASSEMBLIES

| Index Number | Assembly Name       |

|--------------|---------------------|

| 1            | Pack Access Cover   |

| 2            | Case Assembly       |

| 3            | Top Panel           |

| 4            | Rear Door Assembly  |

| 5            | Side Panel Assembly |

| 6            | Front Door Assembly |

| 7            | Top Filler Panel    |

| 8            | Bottom Filler Panel |

Figure 1-3. Drive Mounting Configurations

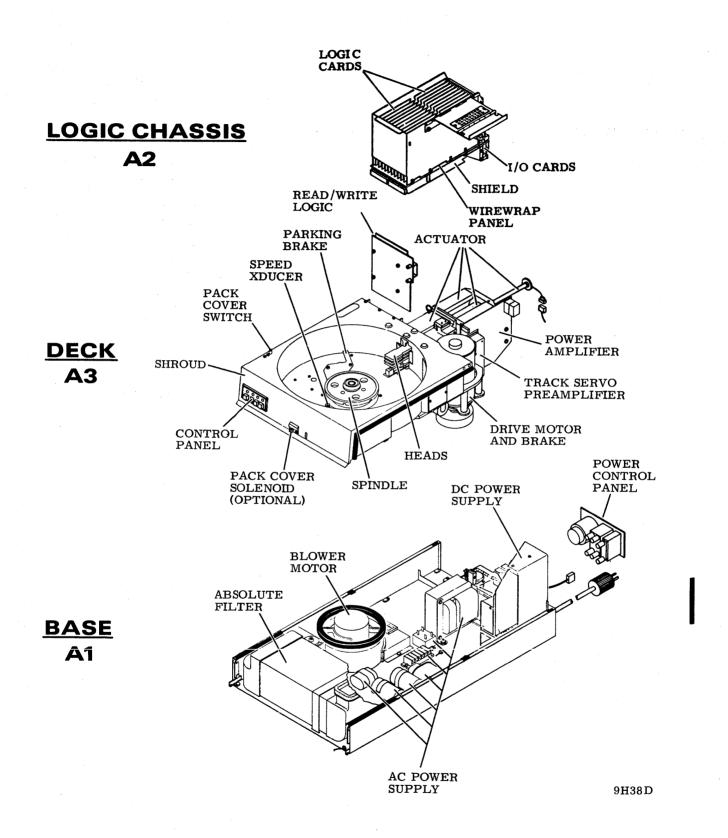

#### DRIVE ELECTRONICS PACKAGE DESCRIPTION

The drive electronics package contains three major assemblies: 1) the base assembly, 2) the logic chassis assembly, and 3) the deck assembly. Figure 1-4 illustrates these major assemblies as well as the subassemblies contained within each of them. Table 1-3 defines each of the subassemblies. The base assembly provides a means of mounting the drive electronics package to the mounting

configuration used. It also contains the hinge plate to which the deck is attached. The deck can then be raised and lowered to provide maintenance access to the various elements contained within the base or on the underside of the deck. The logic chassis is attached to the deck by a hinged bracket on the top of the magnet assembly. In this way, the logic chassis can be raised or lowered to provide access to the wirewrap panel for maintenance purposes.

| Assembly      | Subassembly                  | Purpose                                                                                                                                                                        |  |  |

|---------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Base          | Absolute Filter              | Removes contaminants from air before it is forced into pack area.                                                                                                              |  |  |

|               | AC Power Supply              | Filters and controls ac power and provides power to drive and blower motors and to dc power supply.                                                                            |  |  |

|               | Blower Motor                 | Blows clean air into pack area and cooling air into logic chassis.                                                                                                             |  |  |

|               | DC Power Supply              | Rectifies ac power and provides seven<br>dc output voltages as well as emergency<br>retrack control.                                                                           |  |  |

|               | Power Control                | Controls application of ac and dc power.<br>Panel contains an elapsed time meter and<br>circuit breakers.                                                                      |  |  |

| Logic Chassis | I/O Cards                    | Interfaces I/O cable with backpanel.                                                                                                                                           |  |  |

|               | Logic Cards                  | Contain the majority of the integrated<br>and discrete circuitry which makeup<br>functional logic on machine.                                                                  |  |  |

|               | Terminator Cards             | (Used only on last drive in a daisy<br>chain string and on all star configura-<br>tion drives.) Contain termination<br>resistors for receivers and trans-<br>mitters.          |  |  |

|               | Wirewrap Panel               | Contains all wiring which interconnects<br>logic cards, I/O cards, Terminator<br>cards, and miscellaneous cables attached<br>to logic chassis.                                 |  |  |

| Deck          | Actuator                     | Used to position servo and read/write<br>heads. Made up of rail bracket, rails,<br>carriage and coil assembly, magnet as-<br>sembly, and also contains velocity<br>transducer. |  |  |

|               | Control Panel                | Used by operator to control operation<br>of drive. Contains three switches and<br>indicators and the logical address<br>plug.                                                  |  |  |

|               | Table continued on next page |                                                                                                                                                                                |  |  |

#### TABLE 1-3. DRIVE ELECTRONICS PACKAGE ASSEMBLIES

| Assembly     | Subassembly              | Purpose                                                                                                                                                                        |

|--------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deck (Contd) | Drive Motor and Brake    | Drive motor drives spindle which in<br>turn drives disk pack. Brake is used<br>to decelerate pack after drive motor<br>is turned off.                                          |

|              | Heads                    | Servo head reads data from disk pack<br>servo surface to control actuator<br>positioning. Read/write heads used<br>to record and read back data on disk<br>pack data surfaces. |

|              | Pack Cover Solenoid      | This optional feature locks pack access<br>cover closed whenever disks are turning<br>or power is removed from drive.                                                          |

|              | Pack Cover Switch        | Prevents drive motor start sequence<br>from being initiated when pack access<br>cover is opened.                                                                               |

|              | Parking Brake            | Prevents spindle from turning while pack is being installed or removed.                                                                                                        |

|              | Power Amplifier          | Provides final amplification of servo<br>positioning signal before it is applied<br>to voice coil.                                                                             |

|              | Read/Write Logic         | Contains the logic associated with head<br>selection, read amplification, and write<br>data signal shaping.                                                                    |

|              | Shroud                   | Provides protection and ventilation for disk pack.                                                                                                                             |

|              | Speed Transducer         | Magnetic pickup which provides informa-<br>tion to logic on relative speed of disk<br>pack.                                                                                    |

|              | Spindle                  | Provides surface to secure disk pack<br>and means of transmitting drive motor<br>rotational motion to pack.                                                                    |

|              | Track Servo Preamplifier | Provides first stage of amplification<br>for track servo signal which is read<br>from disk pack by servo head.                                                                 |

# TABLE 1-3. DRIVE ELECTRONICS PACKAGE ASSEMBLIES (Contd)

Figure 1-4. Drive Electronics Package

# EQUIPMENT CONFIGURATION

### GENERAL

The equipment configuration is identified by the equipment identification plate and by the FCO log. It is necessary to identify the equipment configuration to determine if the manuals being used are applicable to the equipment. The following describes the cabinet identification plate, FCO log and manual to equipment correlation.

#### EQUIPMENT IDENTIFICATION PLATE

#### General

This plate is attached to the front of the shroud on the drive (refer to figure 1-5). This plate identifies the drives basic mechanical and logical configuration at the time it leaves the factory. The information contained on this plate is defined in the following.

| STO             | DRAGE       | MODUL | E DRI      | VE    |              |

|-----------------|-------------|-------|------------|-------|--------------|

| EQUAP IDENT NO  | SERIES CODE | R     | ART NUMBER | s     | RIAL NUMBER  |

| BK5XXX          | 02          | 774   | 56104      |       | 147          |

| VOLTS           | Hz          | Ð     | A/8        | WATTS | WIRE - GI    |

|                 |             |       |            |       |              |

|                 |             |       |            |       |              |

| OURPMENT LIDENT |             |       |            |       | MADE IN U.S. |

9H 39B

## Figure 1-5. Equipment Identification Plate

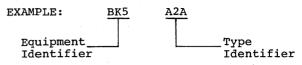

#### **Equipment Identification Number**

This number is divided into the two parts shown in the example:

The equipment identifier indicates the basic functional capabilities of the drive. This number will be either BK4 or BK5. The differences between these units can be determined by referring to the configuration chart in front matter of this manual.

The type identifier indicates differences between drives that have the same equipment number. These differences are necessary to adapt a drive to specific system requirements. However, they do not change the overall capabilities of the drive as defined in the configuration chart.

Different type identifiers are assigned to define differences in input power, data capacity, channel access capabilities, A cable configurations, pack interlock solenoid (presence or absence), equipment colors, and equipment mounting styles. The configuration chart defines each of these catagories for every equipment identification number. Most of the catagories are self-explanatory. The following provides a further explanation of some of the areas.

- Channel Access The drives are available in either single channel access (capable of being connected to one controller) or dual channel access (capable of being connected to two controllers at the same time).

- A Cable Configuration The numerous A Cable configurations fall into three basic categories.

60-Pin Configurations

The standard configuration uses a 60pin, flat cable and includes the Sector and Index signals. The configuration chart notation for these units is "60pin". This same cable may be used with a B Cable that also includes Sector and Index signals. These units are designated by the abbreviation S&IOABC. A third possibility is a 60-pin, flat cable with the Sector and Index signals moved to the B Cable. The abbreviation for these units is S&IOBC.

### 50-Pin Configuration

The standard configuration uses a 50pin, flat cable and includes the Sector and Index signals. The configuration chart notation for these units is "50pin".

#### 75-Pin Configuraiton

Some unique units have a flat-to-round, 60-75 pin A Cable configuration. These units are covered in separate manual supplements and are noted in the configuration chart as "75-pin".

#### Series Code

The series code represents a time period within which a unit is built. While all units are interchangeable at the system level, regardless of series code; parts differences may exist within units built in different series codes. When a parts difference exists, that difference is noted in the parts data section of maintenance manual volume 1.

#### Part Number

This number indicates the top level assembly number of the equipment and is for factory use only.

#### Serial Number

Each drive has a unique serial number assigned to it. Serial numbers are assigned sequentially within a family of drives. Therefore, no two equipments will have the same serial number.

#### FCO LOG

Field Change Orders (FCOs) are generated whenever a condition exists which requires that a machine(s) in the field be changed. It is important that FCOs be installed in the units in a timely manner because, once the FCO is released, the related manuals are changed to show only the post FCO condition. It is also important that the FCO log located on side of logic chassis be kept up to date. Without an accurate record of the changes which have been installed in the unit it would be impossible to relate the machine configuration to the manual.

#### MANUAL TO EQUIPMENT CORRELATION

Throughout the life cycle of a machine, changes are made, either in the factory build (a series code change) or by FCOs installed in the field. All of these changes are also reflected in changes to the manual package. In order to assure that the manual correlates with the machine, refer to the Manual To Equipment Level Correlation sheet located in the front matter of maintenance manual volume 1. This sheet records all the FCOs which are reflected in the manual. It should correlate with the machine FCO log if all the FCOs have been installed in the machine.

SECTION 2

OPERATION

# **OPERATION**

# INTRODUCTION

This section provides the information and instructions necessary for operating the drive and is divided into the following areas:

- Controls and Indicators Locates and describes various controls and indicators related to operation of the drive.

- Operating Instructions Describes procedures for operating the drive.

# CONTROLS AND INDICATORS

#### GENERAL

The drive has two basic types of operator controls and indicators. These are (1) Operator control panel (2) power control panel. These are shown on figure 2-1 and explained in the following.

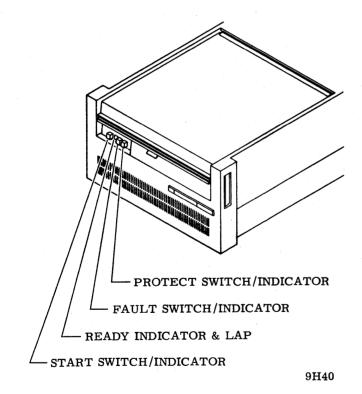

Figure 2-1. Control Panel Switches and Indicators

#### NOTE

Additional controls and indicators contained on cards in Logic Chassis, and used for maintenance purposes, are described in hardware maintenance manual.

2

#### CONTROL PANEL

The control panel is located on the front of the shroud, just below the edge of the pack access cover. The panel contains the switches and indicators required to control and monitor the basic operation of the drive. Figure 2-1 shows these controls and indicators and table 2-1 explains their functions.

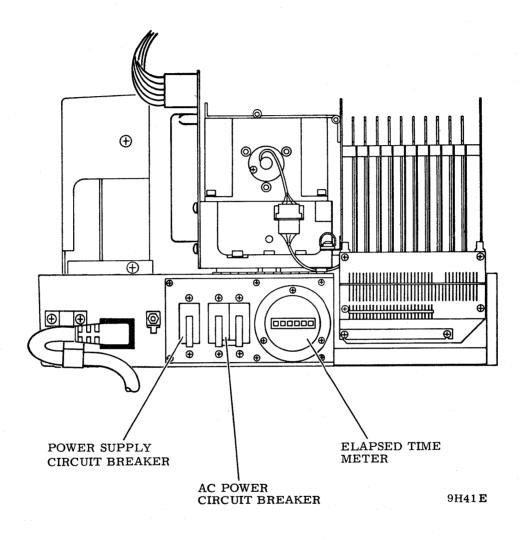

#### POWER CONTROL PANEL

The power control panel is located at the rear of the base assembly. Depending on the mounting configuration of the drive, it may be necessary to open cabinetry in order to gain access to the panel. The panel contains an elapsed time meter and the power control circuit breakers. Figure 2-2 shows the power control panel components and table 2-2 explains their functions.

## **OPERATING INSTRUCTIONS**

#### GENERAL

This discussion describes the procedures that are performed during normal operation of the drive. These procedures concern the disk pack and power application.

#### **DISK PACK**

#### General

There are two different types of disk packs applicable to the 40 and 80 megabyte drives. These packs are constructed so that they cannot be released from their storage cannister unless they are being installed on the correct drive. Be certain that the disk pack being installed is the proper type for the drive on which it is being installed.

Disk pack information is divided into storage and handling procedures and installation and removal procedures. Be thoroughly familiar with these procedures before attempting them on a drive.

| TABLE | 2-1. | CONTROL | PANEL | FUNCTIONS |

|-------|------|---------|-------|-----------|

|       |      |         |       |           |

| Switch Indicator                    | Function                                                                                                                                                                  |  |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| START Switch/Indicator              | Pressing switch when drive is in power off condition (disk<br>pack not spinning) lights indicator and starts power on<br>sequence, provided following conditions are met. |  |

|                                     | • Disk pack is installed                                                                                                                                                  |  |

|                                     | • Pack access cover is closed                                                                                                                                             |  |

|                                     | • All power supply circuit breakers are on                                                                                                                                |  |

| READY Indicator                     | Lights when unit is up to speed, heads are loaded, and no fault condition exists.                                                                                         |  |

| Logical Address Plug                | Determines logical address of drive. Address can be set to<br>any number from 0 to 15 by installing proper plug. If no<br>plug is installed, address is 15.               |  |

| FAULT Switch/Indicator              | Lights if a fault condition exists within drive. It is extinguished by any of the following:                                                                              |  |

|                                     | <ul> <li>Pressing FAULT switch on operator control panel</li> </ul>                                                                                                       |  |

|                                     | • Fault Clear signal from controller                                                                                                                                      |  |

|                                     | <ul> <li>Maintenance Fault Clear switch on fault card in logic<br/>chassis location A04.</li> </ul>                                                                       |  |

|                                     | Conditions causing fault are described in discussion on Fault<br>Detection in section 3 of this manual.                                                                   |  |

| WRITE (Protect)<br>Switch/Indicator | Pressing switch to light indicator, disables drives write circuits and prevents it from writing data on pack.                                                             |  |

|                                     | Pressing switch to extinguish indicator, removes disable from write circuits.                                                                                             |  |

TABLE 2-2. POWER CONTROL PANEL FUNCTIONS

| Control/Indicator               | Function                                                                                                                                                                                                                                                                               |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLY<br>Circuit Breaker | Applies ac power to transformer<br>which in turn enables dc power<br>supplied.                                                                                                                                                                                                         |

| AC POWER<br>Circuit Breaker     | Applies ac power to POWER SUPPLY<br>circuit breaker, blower motor,<br>and to rear door fans used on<br>acoustic mounting configuration<br>only). Also provides power for<br>drive motor; however, control<br>panel START switch must be pressed<br>to enable start sequence for motor. |

| Elapsed Time Meter              | Records accumulated ac power-on<br>time. Meter starts when AC POWER<br>circuit breaker is set to ON.                                                                                                                                                                                   |

Figure 2-2. Power Control Panel Switches and Indicators

#### **Disk Pack Storage**

To ensure maximum disk pack life and reliability, observe the following precautions:

- Store disk packs in machine-room atmosphere (refer to environmental specifications table in maintenance manual volume 1).

- If disk pack must be stored in different environment, allow two hours for adjustment to computer environment before use.

- Never store disk pack in direct sunlight or in dirty environment.

- Store disk packs flat, not on edge. They may be stacked with similar packs when stored.

- Always be sure that both top and bottom of storage cannister are on disk pack and locked together whenever it is not actually installed in a drive.

- When marking packs, use pen or felt tip marker that does not produce loose residue. Never use a lead pencil. Write label before it is applied to disk pack canister.

- Do not attach any label to the disk pack itself. Labels will not remain attached when the pack is spinning and catastrophic head crashes may result.

All labels should be placed on the pack canister if required.

- Cleaning of disk surfaces is not recommended. If disks must be cleaned, the cleaning must be done by trained service personnel.

# **Disk Pack Handling**

Because it is possible for a damaged disk pack to cause damage to the heads of a drive, or to have damaged heads cause damage to a disk pack, it is important that the following be observed.

- Be aware of a sudden increase in error rate related to a specific drive or pack.

- Be aware of any unusual noise such as screeching or pinging while heads are loaded on a pack.

- Be aware of a burning odor coming from a drive.

- Be alert to the possibility of contamination such as dust, dirt, grease, oil, or smoke which could accumulate on the pack or heads.

If any of these conditions exist, or there is any doubt about the pack or drive's functional condition, call in trained service personnel.

# CAUTION

Do not attempt to operate a suspect disk pack on another drive or operate a new disk pack on a drive with suspect heads. To do so may cause further damage.

#### **Disk Pack Installation**

The disk pack must be installed prior to performing any drive operation. Disk pack installation consists of setting the pack on the drive's spindle and locking the pack in place. The following describes the procedure.

### CAUTION

Failure to ensure cleanliness of pack or shroud area, or failure to purge blower system may cause damage to pack or heads.

- 1. Set AC POWER circuit breaker to ON and allow blower to operate for two minutes minimum (to purge blower and shroud) before installing pack.

- Disengage bottom dust cover from pack canister by holding bottom cover and turning canister handle counterclockwise.

#### CAUTION

Non-fully retracted heads indicate a problem in the drive's servo, and may result in damage to the pack or heads during pack installation or removal. If heads are not fully retracted, contact maintenance personnel. DO NOT push on heads.

- 3. Raise pack access cover and ensure that heads are fully retracted.

- 4. Carefully set disk pack on spindle, avoiding abusive contact between pack and spindle. Rotate storage canister handle clockwise until it stops turning. Then, give gentle snugging twist to handle and lift storage canister off pack.

- 5. Set storage canister into bottom dust cover and set aside for later use.

- 6. Close pack access cover to prevent entry of dust and contamination.

#### **Disk Pack Removal**

Disk pack removal consists of replacing the storage canister and lifting pack off spindle. The following describes the procedure.

1. Press START switch to stop drive motor and unload heads.

# CAUTION

Non-fully retracted heads indicate a problem in the drive's servo, and may result in damage to the pack or heads during pack installation or removal. If heads are not fully retracted, contact maintenance personnel. DO NOT push on heads.

- 2. When disk pack has stopped turning, open pack access cover and ensure that heads are fully retracted.

- 3. Place storage canister over disk pack so post protruding from center of disk pack is received into storage canister handle.

- Rotate storage canister handle counterclockwise until pack is free of spindle.

### CAUTION

Avoid abusive contact between disk pack and spindle or one or the other may be damaged.

5. Lift disk pack out of drive by canister handle and close pack access cover.

### CAUTION

Excessive force in tightening bottom dust cover will damage cover.

Install bottom dust cover on pack canister by holding dust cover and turning pack canister handle clockwise.

#### POWER APPLICATION

#### General

Power application is divided into two areas: Power On Procedure, and Power Off Procedure. These procedures assume that the drive is connected to an ac power source as defined in the installation section of the maintenance manual. They also assume that the LOCAL/REMOTE switch and MAINT UNIT DISABLE switch(es), located on cards in the logic chassis, are set to REMOTE and NORM respectively.

#### **Power On Procedure**

The following procedure describes applying power to the drive:

1. Gain access to power control panel and set AC POWER and POWER SUPPLY circuit breakers to ON. Ensure that blower starts to operate. Allow blower to operate for two minutes minimum before proceeding.

# CAUTION

Failure to allow blower to operate for two minute period before installing disk pack will not allow sufficient purge time and may cause damage to disk pack or heads.

- 2. Install disk pack in accordance with Disk Pack Installation procedure.

- 3. Press START switch on control panel and ensure that START indicator lights. Drive starts as soon as Sequence Pick and Sequence Hold signals are available from controller. Within 30 seconds of the time the sequence signals are available, the READY indicator should light. Drive is then ready for operation.

#### **Power Off Procedure**

The following procedure describes removing power from the drive:

- 1. Press START switch on control panel to turn off START indicator. Ensure that heads unload and that drive motor stops.

- 2. Remove disk pack in accordance with Disk Pack Removal procedure.

- 3. Gain access to power control panel and set AC POWER and POWER SUPPLY circuit breakers to OFF.

.

SECTION 3

# THEORY OF OPERATION

· -, ŋ

# INTRODUCTION

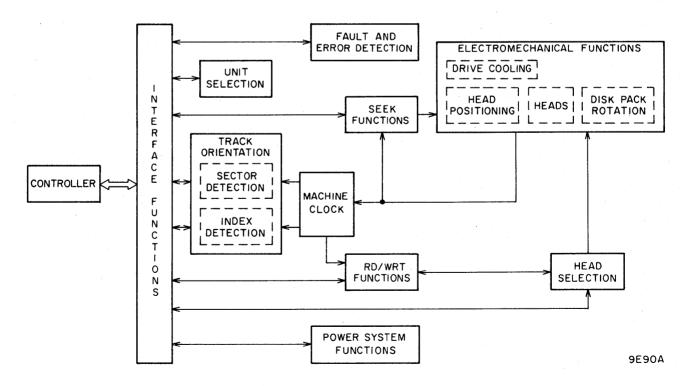

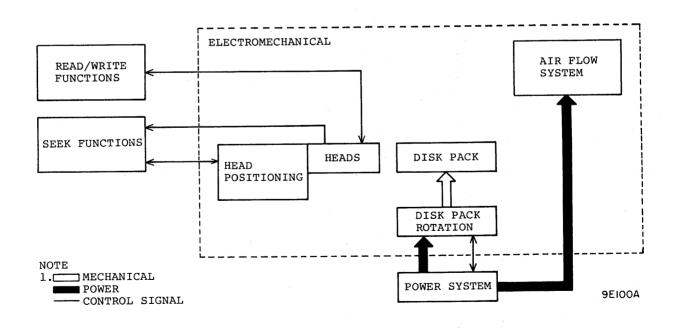

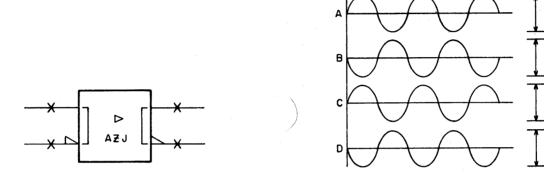

The theory of operation section describes drive functions and the hardware used in performing them. It is divided into the following major areas (refer to figure 3-1):

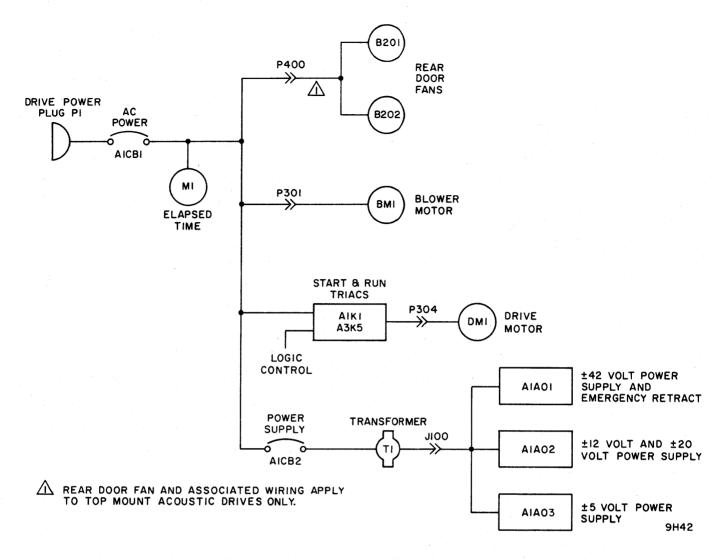

- Power System Functions Describes how the drive provides the voltages necessary for drive operation.

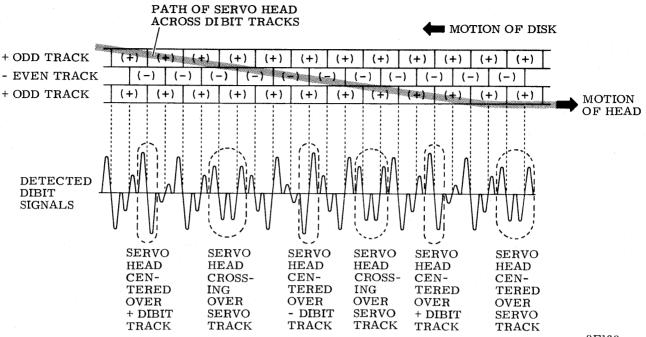

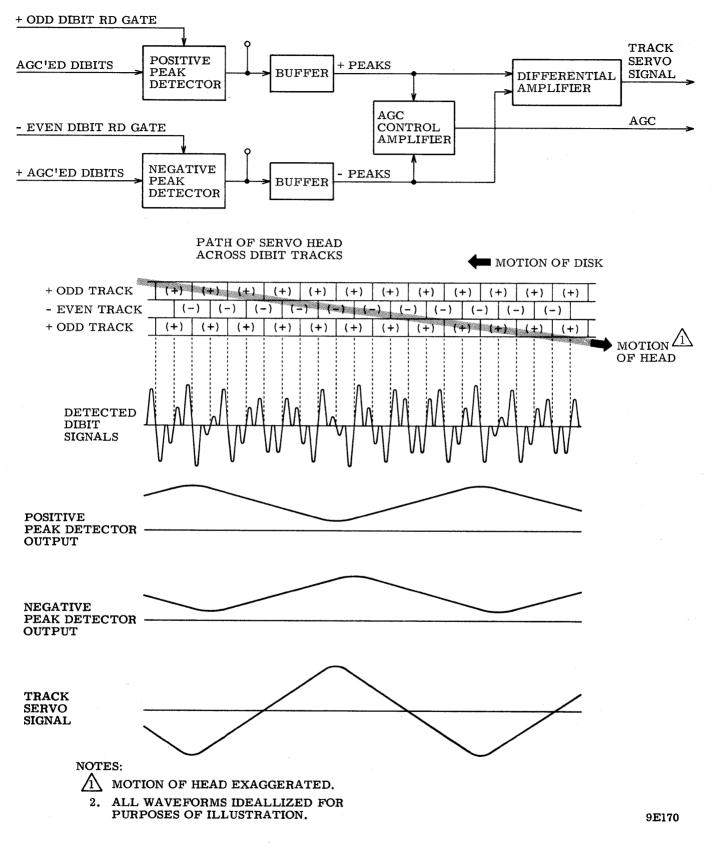

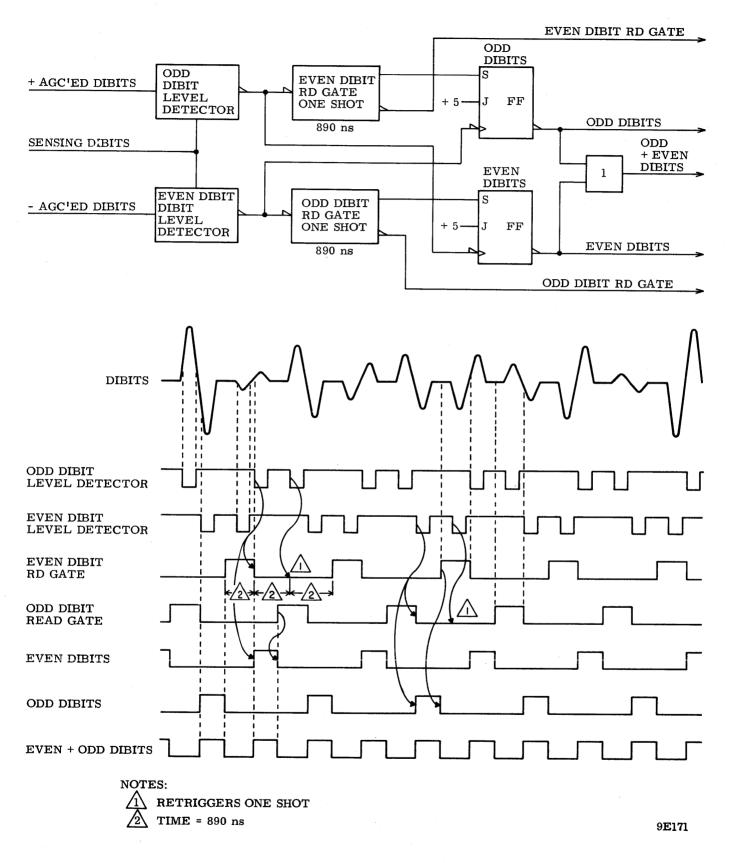

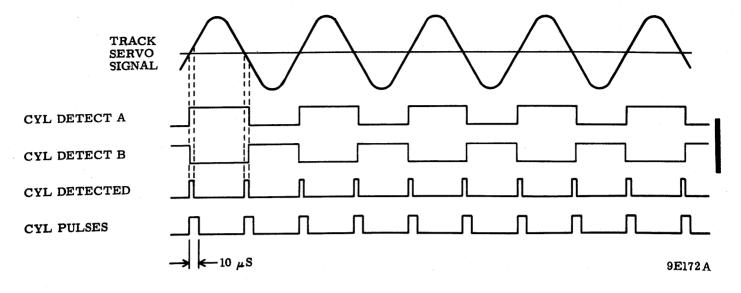

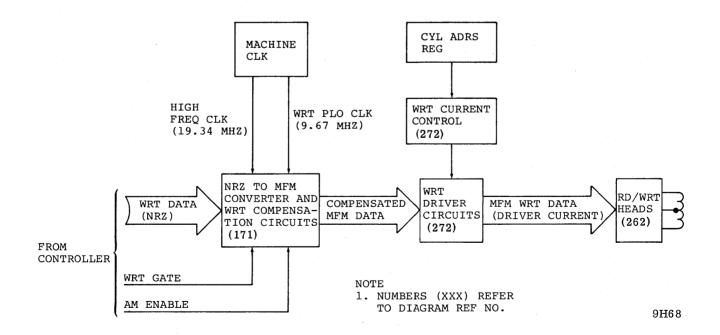

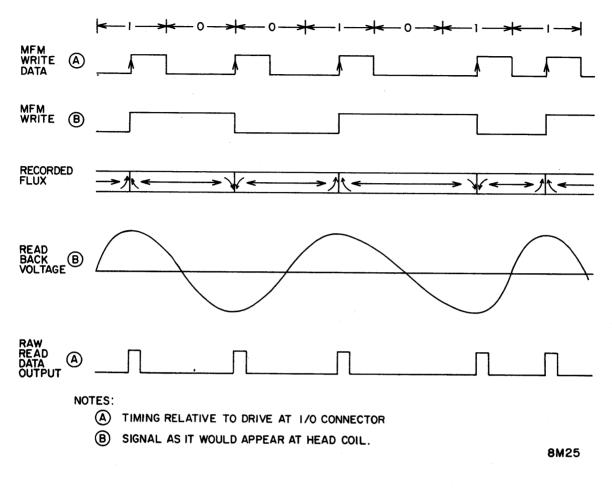

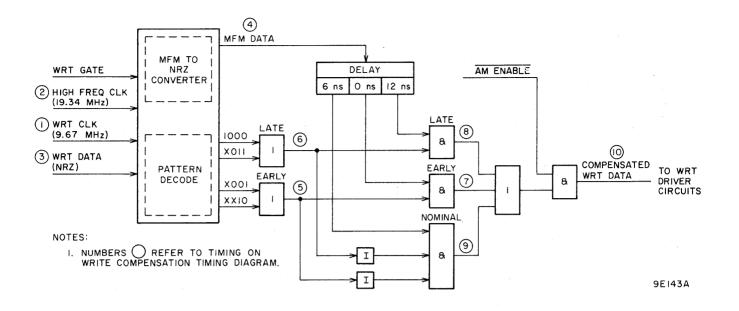

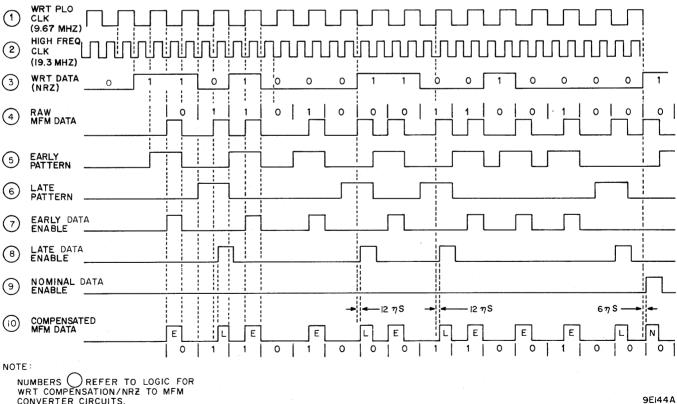

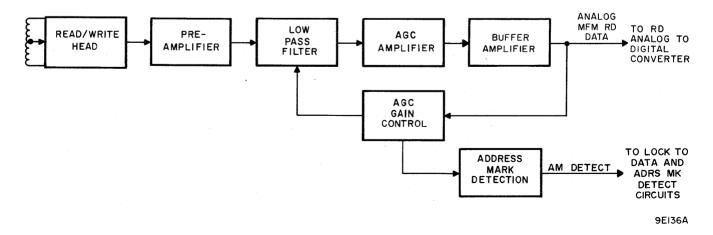

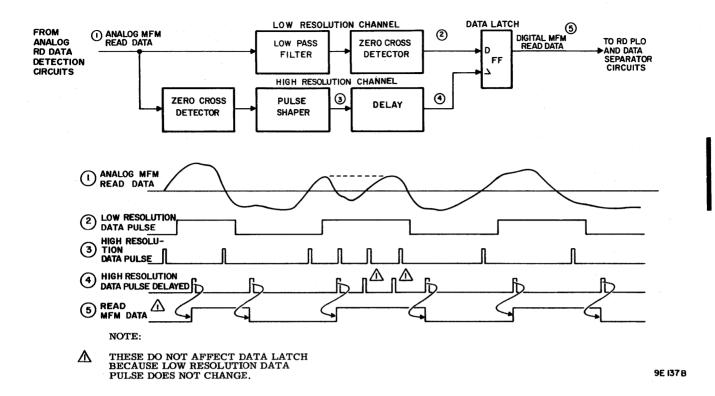

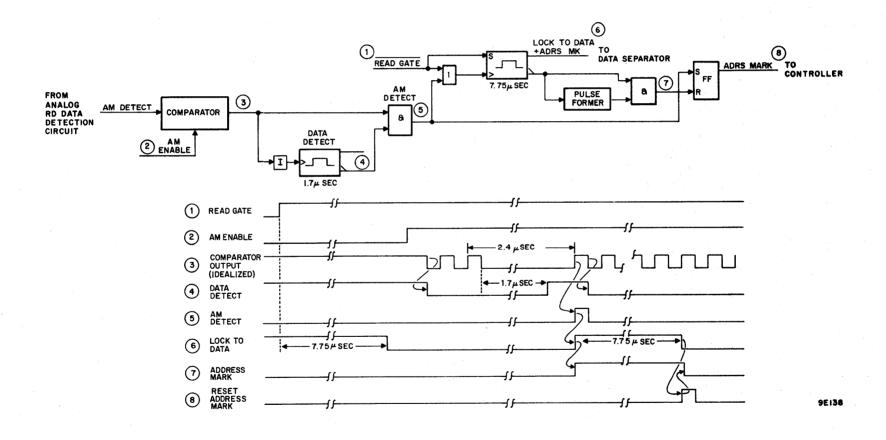

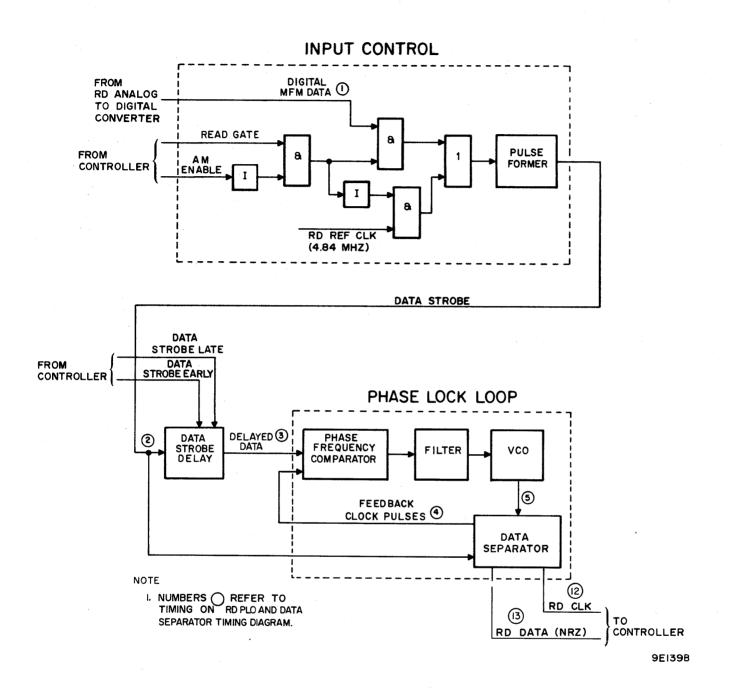

- Electromechanical Functions Provides a physical and functional description of the mechanical and electromechanical systems (disk pack rotation, head positioning, and air flow).