SPEC 77653331 CD 7 REV A Issue DATE October, 1980 PAGE 1 of 54

# PRODUCT SPECIFICATION FOR FINCH DISK DRIVE MODEL 9410-1F

MAGNETIC PERIPHERALS INC.

|        | •            |                       |                                       |                     |                                       |           |        |

|--------|--------------|-----------------------|---------------------------------------|---------------------|---------------------------------------|-----------|--------|

|        |              |                       | [                                     | PC                  | SPEC. NO.                             | SHEE      | TREV   |

|        |              | a ta<br>Angara ang sa |                                       | Α                   | 77653331                              | 2         | A      |

|        | UCT S        | PECIFICATIO           | DN - MODEL 9410 FINCI                 |                     | IVE                                   | nga sa ka |        |

| 1 1100 | 001 0        |                       |                                       |                     |                                       |           |        |

| 1.0    | SCOI         | PE                    | TABLE OF CON                          |                     |                                       |           | 5      |

| 2.0    | Δ ΡΡΙ        | LICABLE DOC           | UMENTS                                |                     |                                       |           | 5      |

| 2.0    | 2.1          |                       | S                                     |                     |                                       |           | 5      |

|        | 2.2          | DOCUMENT              |                                       |                     |                                       | ••••      | 6      |

| 3.0    | GENI         | ERAL DESCR            | IPTION                                |                     |                                       |           | 6      |

|        |              |                       |                                       |                     |                                       |           |        |

| 4.0    |              | CURES                 | ••••••••••••••••••                    |                     |                                       |           | 8      |

|        | $4.1 \\ 4.2$ |                       | FEATURES<br>CONFIGURATION             |                     | • • • • • • • • • • • • • • • • • • • |           | 8<br>8 |

| 5.0    |              | ESSORIES              |                                       |                     |                                       |           | 8      |

|        |              |                       |                                       |                     |                                       |           | 0      |

| 6.0    | PERI         |                       | HARACTERISTICS                        |                     |                                       |           | 9      |

|        | 6.1          |                       | ) DATA CHARACTERIS                    |                     |                                       |           |        |

|        |              |                       | sitioning Timing                      |                     |                                       |           |        |

|        |              | 6.1.3 Rea             | ad to Write Recovery Ti               | ime                 |                                       | 1         | .0     |

|        | 6.2          |                       | ACITY                                 |                     |                                       |           |        |

|        | 6.3          |                       | A TRANSFER RATE                       |                     |                                       |           |        |

|        | 6.4          | START/ST              | OP TIME                               | • • • • • • • • • • | • • • • • • • • • • • • • • • • •     |           | .0     |

| 7.0    | RELI         | ABILITY SPI           | ECIFICATIONS                          | ••••                | • • • • • • • • • • • • • • • • •     | 1         | .1     |

|        | 7.1          | ERROR RA              | LLD                                   | ••••                |                                       |           | .1     |

|        |              |                       | ad Errors                             |                     |                                       |           |        |

|        |              |                       | vironmental Interferenc<br>ite Errors |                     |                                       |           |        |

|        |              |                       | ek Errors                             |                     |                                       |           |        |

|        | 7.2          |                       |                                       |                     |                                       |           |        |

|        |              | 7.2.1 Mea             | an Time Between Failur                |                     |                                       |           |        |

|        |              |                       | eventive Maintenance .                |                     |                                       |           |        |

|        |              |                       | vice Life                             |                     |                                       |           |        |

|        |              |                       | vice Philosophy                       |                     |                                       |           |        |

|        |              |                       | stallation                            |                     |                                       |           |        |

| 0.0    | DUI          |                       |                                       |                     |                                       |           |        |

| 8.0    |              | -                     | RICAL SPECIFICATIO                    |                     |                                       |           |        |

|        | 8.1<br>8.2   |                       | REQUIREMENTS<br>REQUIREMENTS          |                     |                                       |           |        |

|        | 8.2<br>8.3   |                       | ER DISSIPATION                        |                     |                                       |           |        |

|        | 8.4          |                       | ENTAL LIMITS                          |                     |                                       |           | 16     |

|   | PC | SPEC. NO. | SHEET | REV. |

|---|----|-----------|-------|------|

|   | А  | 77653331  | 3     | Α    |

| · |    |           |       |      |

# TABLE OF CONTENTS (contd.)

|      | 8.5                    | <ul> <li>8.4.1 Temperature</li> <li>8.4.2 Relative Humidity</li> <li>8.4.3 Effective Altitude (Sea Level Reference)</li> <li>8.4.4 Vibration and Shock</li> <li>8.4.5 Air Cleanliness</li> <li>MECHANICAL SPECIFICATIONS</li> <li>8.5.1 Drive Orientation</li> </ul>                                                                                                                                                         | 16<br>16<br>17<br>17<br>19<br>20<br>21                               |

|------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 9.0  | MEDI                   | A CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                            | 21                                                                   |

|      | 9.1                    | MEDIA DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                            | 21                                                                   |

| 10.0 | ERRO                   | R RECOVERY CONSIDERATIONS FOR THE HOST SYSTEM                                                                                                                                                                                                                                                                                                                                                                                | 22                                                                   |

|      | 10.1                   | EARLY/LATE STROBE                                                                                                                                                                                                                                                                                                                                                                                                            | 23<br>23<br>23                                                       |

| 11.0 | TRAC                   | K OR SECTOR REALLOCATION                                                                                                                                                                                                                                                                                                                                                                                                     | 23                                                                   |

|      | 11.1                   | ERROR DETECTION                                                                                                                                                                                                                                                                                                                                                                                                              | 24                                                                   |

| 12.0 | INTE                   | RFACE CABLING REQUIREMENTS/OPTIONS                                                                                                                                                                                                                                                                                                                                                                                           | 24                                                                   |

|      | $12.1 \\ 12.2 \\ 12.3$ | DC CABLE AND CONNECTOR<br>COMMAND AND DATA CABLES AND CONNECTORS<br>INTERFACE DRIVERS/RECEIVERS<br>12.3.1 Single-Ended Drivers/Receivers<br>12.3.2 Balanced Differential Drivers/Receivers                                                                                                                                                                                                                                   | 26<br>27<br>27<br>27<br>30                                           |

| 13.0 | DIGI                   | TAL-INTERFACE SIGNAL DEFINITIONS                                                                                                                                                                                                                                                                                                                                                                                             | 31                                                                   |

| 14.0 | INTE                   | RFACE SIGNAL DEFINITIONS                                                                                                                                                                                                                                                                                                                                                                                                     | 31                                                                   |

|      | 14.1                   | INPUT SIGNAL LINES         14.1.1       Unit Select (1-2-3-4)         14.1.2       Direction         14.1.3       Step         14.1.4       Head Select 20, 21         14.1.5       Fault Reset         14.1.6       Return to Zero         14.1.7       Read Enable         14.1.8       Write Enable         14.1.9       Write Data "+" and "-"         14.1.10       Write Clock "+" and "-"         OUTPUT SIGNAL LINES | 31<br>34<br>36<br>37<br>37<br>37<br>38<br>38<br>38<br>38<br>38<br>38 |

|      |                        | 14.2.1       Unit Read -1, -2, -3, -4         14.2.2       Index         14.2.3       Byte Clock         14.2.4       Write Fault                                                                                                                                                                                                                                                                                            | 38<br>38<br>40<br>40                                                 |

|  | РС | SPEC. NO. | SHEET | REV. |

|--|----|-----------|-------|------|

|  | A  | 77653331  | 4     |      |

# TABLE OF CONTENTS (-contd.)

|      | 14.2.5       Disk Capacity         14.2.6       Unit Selected         14.2.7       Servo/Read Clock "+" and "-"         14.2.8       Read "+" and "⊥"         14.3       RESERVED SIGNAL LINES                                                                                                        | 41<br>41<br>41             |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 15.0 | DATA FORMAT AND DATA CONTROL TIMING                                                                                                                                                                                                                                                                   | 43                         |

|      | <ul> <li>15.1 FORMAT DEFINITION <ul> <li>15.1.1 Intersector Gap</li> <li>15.1.2 Address Area.</li> <li>15.1.3 Data Area</li> </ul> </li> <li>15.2 WRITE-FORMAT PROCEDURE <ul> <li>15.3 READ/WRITE CONTROL TIMING</li> <li>15.3.1 Read Function</li> <li>15.3.2 Write Function.</li> </ul> </li> </ul> | 44<br>45<br>46<br>47<br>47 |

|  | РС | SPEC. NO. | SHEET | REV. |

|--|----|-----------|-------|------|

|  | Α  | 77653331  | 5     | A    |

#### 1.0 SCOPE

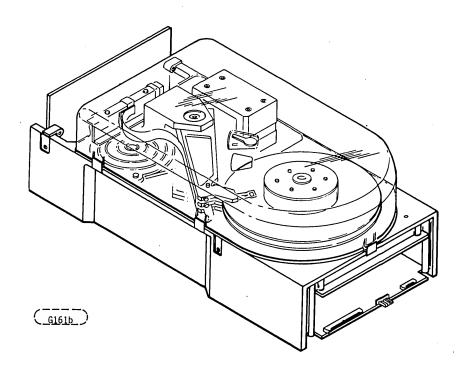

This specification describes the Control Data Corporation Model 9410 FINCH Disk Drive. This 8-inch member of the rigid disk family utilizes a digital interface and is available in 8 and 24 megabyte unformatted capacities. The basic configurations are: 9410-8-1F and 9410-24-1F

# 2.0 APPLICABLE DOCUMENTS

#### 2.1 STANDARDS

The 9410 (FINCH) shall comply with CDC standards as noted in the appropriate sections of this specification.

In addition to the corporate standards, the FINCH shall comply with the requirements of UL 478 and CSA Standard C22.2 No. 154-1975.

|  | PC | SPEC. NO. | SHEET | REV. |

|--|----|-----------|-------|------|

|  | Α  | 77653331  | 6     | Α    |

#### 2.2 DOCUMENTATION

3.0

The following documentation is available for field support of the FINCH.

TBD Hardware Maintenance Manual, Level 2

77653374 Application Note, Diagnostics for Model 9410 FINCH Disk Drive

TBD Power Supply Product Specification

TBD Operator and Installation Guide

GENERAL DESCRIPTION

The 9410 FINCH is a member of a family of low-cost, high-performance, highly reliable, random access storage devices designed to meet the needs of the OEM marketplace.

The FINCH is designed to record and recover data on up to two eight-inch fixed disk media; it does not contain any removable media capability.

The FINCH digital interface is intended to utilize a single controller design capable of controlling both a 9410 and a Flexible Disk Drive (FDD).

The 9410 digital electrical interface consists of a 50-pin command interface and a 20-pin data interface. The 50-pin command interface is designed to allow daisy-chained or radial connections to 9410's and 9406 FDD's. Thus, the 50pin 9410 command interface contains functional and electrically compatible signals to a 9406; however, due to different step rates, access time, and data transfer rates, the timing relationships of the individual signals may vary. The 20-pin radial data interface is unique to the 9410 and is based on differential NRZ data plus clocks to meet electrical requirements for a 6.45 MHz data rate.

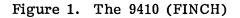

The disk and actuator chamber is environmentally sealed. No outside air is drawn into the unit. Air is recirculated within the disk/actuator chamber and passes through a nonreplaceable absolute filter to ensure the maintenance of a contamination free disk/actuator environment.

Refer to Figure 2 for an exploded view of the FINCH. <u>NEVER</u> disassemble the FINCH. This exploded view is for information only. Servicing items in the upper sealed environmental enclosure (heads, media, actuator, etc.) requires special facilities. Only the printed circuit boards external to the sealed area can be replaced with no special facilities.

|  | PC | SPEC. NO. | SHEET | REV. |

|--|----|-----------|-------|------|

|  | A  | 77653331  | 7     | A    |

Figure 2. FINCH

| <br> |           |       | OFV  |   |

|------|-----------|-------|------|---|

| PC   | SPEC. NO. | SHEET | HEV. | ĺ |

| A    | 77653331  | 8     | Α    |   |

|      |           |       |      | 1 |

#### 4.0 FEATURES

# 4.1 STANDARD FEATURES

The FINCH has the following standard features:

- Full data recovery circuitry

- Sealed disk, head, and actuator chamber

- No preventive maintenance required

- LSI circuitry for high reliability

- Low audible noise for office environments

- Vertical (side) or horizontal (bottom) mounting

- Low power consumption

- Rotary voice coil actuator

- Operator and Installation Guide

- Terminators

# 4.2 OPTIONAL CONFIGURATION (FACTORY INSTALLED ONLY)

The following optional features are available for the FINCH:

8 or 24 megabyte capacity

# 5.0 ACCESSORIES

The following accessories are available for the FINCH and must be ordered and shipped separately:

- Shock mounts (horizontal)

- Front panel

- Power supply includes 5-foot power cable

- Hardware Maintenance Manual, Level 2

- Diagnostic Application Note

| • • • • • • • • • • • • • • • • • • • | PC | SPEC. NO. | SHEET | REV |

|---------------------------------------|----|-----------|-------|-----|

|                                       | A  | 77653331  | 9     | Α   |

6.0 PERFORMANCE CHARACTERISTICS Data Capacity (Unformatted)

> Bytes per Track 13,440 bytes Bytes per Surface 8,010,240 bytes Single Disk 8,010,240 bytes Note 1 Double Disk 24,030,720 bytes Track Format User Defined Variable Number of Byte Clocks Per Revolution 13,440 Recording Mode Interface NRZ Disks MFM Data Transfer Rate 6.45 Mb/s (806 KB/s) Data Interface NRZ DATA + CLOCK **Rotational Speed** 3600 r/min ±1.5% Average Latency 8.33 ms Tracks Per Surface 605 (Note 2) 50 kHz ±20% Step Pulse Rate (20 µs between Step pulses) Single Track Seek Time 10 ms Max. Average Seek Time 50 ms (Step Pulse Rate of 50 kHz  $\pm 20\%$ ) Maximum Seek Time (605 Tracks) (Step Pulse 100 ms Rate of 50 kHz ±20%) Head Change to Read Gate Delay 15 µs Max.

Note 1: Based on 596 primary cylinders. Does not include spare tracks.

Note 2: See Media Characteristics, paragraph 9.0.

| · · · · · · · · · · · · · · · · · · · | PC | SPEC. NO. | SHEET | REV. |

|---------------------------------------|----|-----------|-------|------|

|                                       | A  | 77653331  | 10    | Α    |

# 6.1 ACCESS TO DATA CHARACTERISTICS

#### 6.1.1 Positioning Time

Positioning time is defined as the time required from the receipt of a seek or position command by the FINCH until the drive signals the controller that it is ready to perform another seek or read/write function on the new cylinder. Average seek time is determined by dividing the sum of the time for all possible movements by the total number of movements.

#### 6.1.2 Spindle Speed and Latency

The spindle speed is  $3600 \pm 1.5\%$  r/min. The speed tolerance includes motor performance and motor control circuit tolerances, but does not include other variables which affect data transfer rates as seen at the interface.

The average latency time is 8.33 milliseconds, based on a nominal disk speed of 3600 r/min. The maximum latency time is 16.75 milliseconds based on a minimum disk speed of 3546 r/min.

# 6.1.3 Read to Write Recovery Time

Assuming a read operation is in progress, the required minimum time interval between the end of read gate and the initiation of write gate is 0.3 microseconds.

#### 6.2 DATA CAPACITY

The total unformatted data capacity of the 9410 is 8,010,240 bytes per data surface. This capacity does not include the spare data tracks.

#### 6.3 READ DATA TRANSFER RATE

The nominal read serial data transfer rate is 6.45 Mbits per second. The range of transfer rate variations on a bit per second basis for read/write operations is 3% of the nominal. This range includes the effects of all factors including spindle speed variations and dynamic jitter on a byte to byte basis. Data on the interface is NRZ plus clock.

#### 6.4 START/STOP TIME

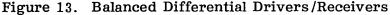

The FINCH will become ready less than 60 seconds after application of DC power. Stop time will be less than two minutes after removal of DC power.

There is no power control switch or indicator on the drive.

|  | PC | SPEC. NO. | SHEET | REV. |

|--|----|-----------|-------|------|

|  | Α  | 77653331  | 11    | Α    |

|  |    |           |       |      |

# 7.0 RELIABILITY SPECIFICATIONS

The following reliability specifications assume correct host/drive operational interface has been implemented, including all interface timings, power supply voltages, environmental conditions, and appropriate data-handling circuits in the host system.

Error Rates

| Soft Read Errors<br>(Recoverable)   | Less than 1 in $10^{10}$ bits transferred                                                                                         |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Hard Read Errors<br>(Unrecoverable) | Less than 1 in $10^{12}$ bits transferred                                                                                         |

| Seek Errors                         | Less than 1 in 10 <sup>6</sup> seeks                                                                                              |

| MTBF                                | First Year Production - 5000 hours minimum<br>Second Year Production - 7500 hours minimum<br>Third Year On - 10,000 hours minimum |

| Service Life                        | 5 years or 30,000 hours                                                                                                           |

| Preventive Maintenance              | None required                                                                                                                     |

# 7.1 ERROR RATES

The error rates stated in this specification assume the following:

- a. That the 9410 is operated per this specification utilizing the CDC provided accessory power supply or its equivalent.

- b. That a data format is employed fulfilling the requirements of the 9410 as outlined in Section 15.0.

- c. That errors caused by media defects or host system failures are excluded from error rate computations. Refer to paragraph 9.0, Media Defect Recognition.

- d. That power requirements as specified in paragraph 8.2 and system grounding requirements indicated in the installation instructions are met.

- e. That all read/write operations are accomplished with the same physical orientation of the drive. (Refer to paragraph 8.5.1.)

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| А  | 77653331  | 12    | A    |

# 7.1.1 Read Errors

Prior to the determination or measurement of read error rates:

- a. The data which is to be used for a measurement of read error rates must be verified as being written correctly on the media.

- b. All media defect induced errors must be excluded from error rate calculations.

A recoverable read error is one that can be reread correctly in 2 sets of 10 retries. After 10 retries, a recalibrate (RTZ) and seek to desired address must be accomplished. The soft read error rate for any read operation shall be less than one error in  $10^{10}$  bits read.

An unrecoverable read error is one that cannot be read correctly after 2 sets of 10 retries. The hard read error rate for any read operation shall be less than one bit in  $10^{12}$  bits read.

# 7.1.2 Environmental Interference

When operating at low effective data transfer rate, (that is, random access of single short records) the effective error rate may be expected to exceed the specified limits due to environmental interference. Excluding environmental interference, the recoverable read error rate shall be no more than one error in eight hours of operation.

# 7.1.3 Write Errors

Write errors can occur as a result of the following: write data not being presented correctly, media defects, environmental interference, or equipment malfunction. As such, write errors are not predictable as a function of the number of bits passed.

If an unrecoverable write error occurs because of a FINCH equipment malfunction, the error is classified as a failure affecting MTBF. Unrecoverable write errors are those which cannot be corrected within four attempts at writing the record with a write verify after each attempt.

## 7.1.4 Seek Errors

A seek error is defined as a condition where the drive fails to position the heads to the addressed track provided the correct stepping information has been presented to the FINCH. There shall be no more than one recoverable seek error in  $10^6$  physical seek operations. Unrecoverable seek errors are classified as failures for MTBF calculations.

| 2 | PC | SPEC. NO. | SHEET | REV. |

|---|----|-----------|-------|------|

|   | Α  | 77653331  | 13    | Α    |

# 7.2 RELIABILITY AND SERVICE

# 7.2.1 Mean Time Between Failure

Following an initial period of 200 hours, the Mean Time Between Failure shall exceed 5000 hours for units manufactured in the first year of production and 7500 hours for units manufactured in the second year. For units manufactured after the second year, the MTBF shall exceed 10,000 hours. The following equation defines MTBF:

MTBF = Operating Hours No. of Equipment Failures

"Operating Hours" means total power on hours less any maintenance time. "Equipment Failure" means any stoppage or substandard performance of the equipment because of equipment malfunction, excluding stoppages or substandard performance caused by operator error, adverse environment, power failure, controller failure, cable failure, or other failure not caused by equipment. To establish a meaningful MTBF, operation hours must be greater than an average of 5200 hours per drive and shall include field performance data from all field sites.

The term equipment failure implies that emergency maintenance is required because of a hardware failure.

#### 7.2.2 Preventive Maintenance

No routine scheduled preventive maintenance shall be required. Service will be performed only at an approved service depot (7.2.4).

# 7.2.3 Service Life

The FINCH shall have a useful service life of five years or 30,000 hours, whichever occurs first, before requiring factory overhaul. Depot repair or replacement of major parts will be permitted during the lifetime (7.2.4).

### 7.2.4 Service Philosophy

Due to the sophisticated design and special equipment required to repair the 9410, most repairs may only be effected at a properly equipped and staffed depot service and repair facility. These repair facilities will be capable of performing all warranty and routine repair activities in a timely manner.

Further details will be provided at a later date.

| PC | С | SPEC. NO. | SHEET | REV. |

|----|---|-----------|-------|------|

| A  | A | 77653331  | 14    | A    |

### 7.2.5 Installation

The FINCH is designed, manufactured, and tested with a "Plug-in and Play" installation philosophy. Basically, this philosophy minimizes the requirements for a highly trained personnel to integrate a FINCH into the OEM's system, whether in a factory or field environment. An Operator and Installation Guide is provided with each drive.

# 7.2.6 Service Tools

No special tools are required for site installation or site maintenance. Refer to paragraph 7.2.4.

#### 8.0 PHYSICAL/ELECTRICAL SPECIFICATIONS

8.1 AC POWER REQUIREMENTS

None

#### 8.2 DC POWER REQUIREMENTS

The voltage and current requirements for a single FINCH are shown in the following table. Values indicated apply at the drive power connector.

| Voltage                                                              | +5 VDC   | -5.2 VDC | +24 VDC |

|----------------------------------------------------------------------|----------|----------|---------|

| Regulation                                                           | ±2%      | ±2%      | ±10%    |

| Ripple                                                               | 50 mV    | 50 mV    | 500 mV  |

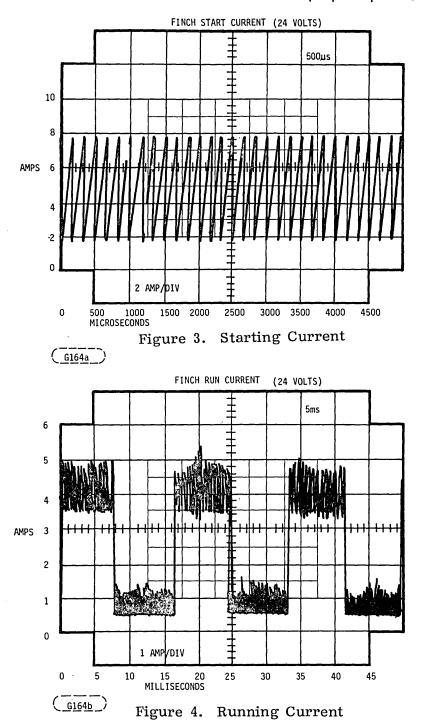

| Average Operating Current<br>(Worst Case)                            | 1.5 A    | 2.4 A    | 3.3 A   |

| Operating Current (Typical)                                          | 1.1 A    | 2.0 A    | 2.8 A   |

| Operating Current (Peak)                                             |          |          | 4.5 A   |

| Absolute Maximum Voltage<br>Without Physical Damage<br>to Disk Drive | +6.8 VDC | -6.8 VDC | +30 VDC |

Table 1. DC Power Requirements

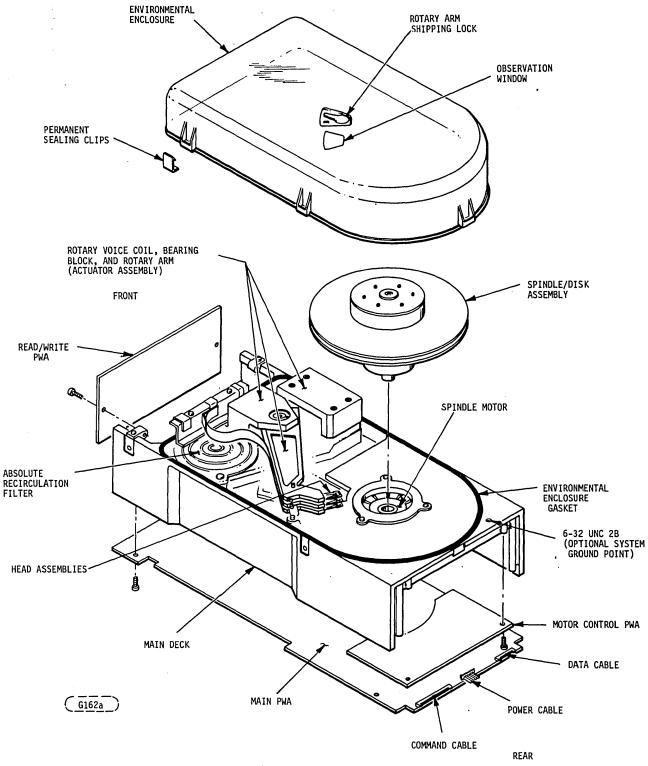

- NOTE 1: At power-up, the motor current regulator will limit the 24-volt current to an average of less than 4.2 amps with 8 amp peaks. (See typical running and starting current waveforms, Figures 3 and 4.)

- NOTE 2: Minimum current loading for each supply voltage is not less than 30% of the worst case average shown in the table. The 24 volt supply can have instantaneous minimum current 0.7 amp.

- NOTE 3: The +5 and -5.2 volt supplies may share a common DC return. The 24 volt supply shall have a separate return.

|    | Τ | PC | SPEC. NO. | SHEET | REV. |

|----|---|----|-----------|-------|------|

| ÷. |   | Α  | 77653331  | 15    | A    |

# 8.2 -contd.

NOTE 4: Where power is provided to multiple drives from a common supply, worst case average and peak current loading powerup must be considered. The average current noted must be available to each drive to ensure proper spindle acceleration.

| P | РС | SPEC. NO. | SHEET | REV. |

|---|----|-----------|-------|------|

|   | A  | 77653331  | 16    | A    |

# 8.3 HEAT/POWER DISSIPATION

Each FINCH will dissipate no more than 100 watts of power or dissipate more than 350 BTU's per hour. Typical power dissipation under nominal conditions is 85 watts.

# 8.4 ENVIRONMENTAL LIMITS

Temperatures and humidity specifications preclude condensation on any drive part. Altitude and atmospheric pressure specifications are referenced to a standard day at  $58.7^{\circ}$ F (14.8°C).

## 8.4.1 Temperature

# a. Operating

50° to 104°F (10° to 40°C) with a maximum gradient of 18°F (10°C) per hour. Above 983 feet (300 meters) altitude the maximum temperature is derated linearly to 95°F (35°C) at 6562 feet (2000 meters). Cabinet packaging designs should provide ample air circulation around the FINCH to ensure environmental limits are not exceeded as a result of heat transfer from other system components.

#### b. Transit

$-40^{\circ}$  to  $158^{\circ}$ F ( $-40^{\circ}$  to  $70^{\circ}$ C) with a maximum gradient of  $36^{\circ}$ F ( $20^{\circ}$ C) per hour. This specification assumes that the drive is packaged in the shipping container designed by CDC for use with the FINCH.

c. Storage

14° to 122°F (-10° to 50°C) with a maximum gradient of 27°F (15°C) per hour.

# 8.4.2 Relative Humidity

a. Operating

20% to 80% relative humidity with a maximum gradient of 10% per hour.

b. Transit

5% to 95% relative humidity.

c. Storage

10% to 90% relative humidity.

|  | PC | SPEC. NO. | SHEET | REV. |

|--|----|-----------|-------|------|

|  | A  | 77653331  | 17    | A    |

8.4.3 Effective Altitude (Sea Level Reference)

a. Operating

-983 to +6562 feet (-300 to +2000 meters)

b. Transit

-983 to +9830 feet (-300 to +3000 meters)

c. Storage

-983 to +8200 feet (-300 to +2500 meters)

8.4.4 Vibration and Shock

The FINCH is designed to withstand the vibration and shock conditions specified below without damage to its function, physical structure, or external appearance.

#### NOTE

Shock and vibration limits are assumed to be measured directly on the drive casting. If the equipment is installed in an enclosure to which the stated shock/vibration criteria is applied, resonances may occur internally to the enclosure resulting in vibrations in excess of these limits. In this case, it may be necessary to add shock absorbers to the enclosure.

a. Operating

Equipment, as normally installed and positioned, shall meet the full specified performance while subject to the following conditions injected from the floor in a vertical direction.

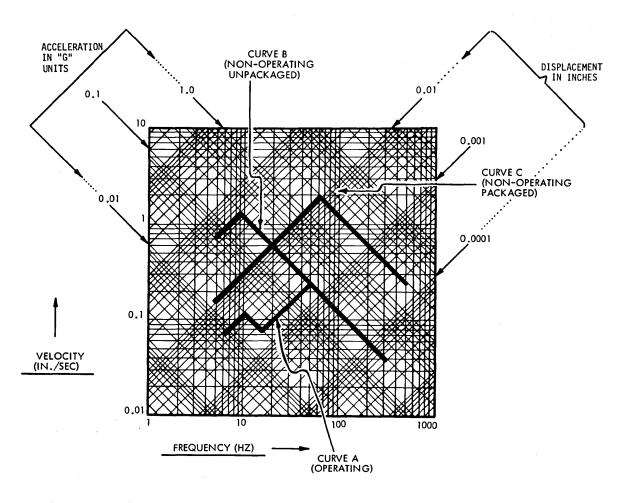

- 1. Continuous vibration as indicated in Figure 5, Curve A (Operating).

- 2. Intermittent shocks of up to 2 g and not exceeding 10 milliseconds in duration. No shock is to be repeated more often than two per second.

- b. Transit

Equipment in its normal upright position shall withstand the conditions of vibration and shock injected from the floor in the three major mutually perpendicular axes.

- 1. Vibration as shown in Figure 5, Curve C (Non-Operating Packaged).

- 2. Shocks of up to 5 g, not exceeding 10 milliseconds in duration. The time between consecutive shocks cannot be less than five seconds.

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| А  | 77653331  | 18    | A    |

(Z097b)

Figure 5. Vibration Levels

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| А  | 77653331  | 19    | A    |

# 8.4.4 -contd

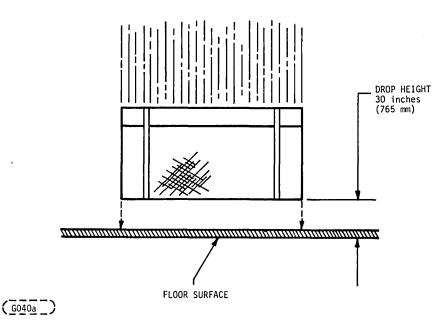

The FINCH is packaged by CDC for van or air freight shipment, shall withstand drop tests from 30 inches (765 mm) on all surfaces, three edges and one corner, against a concrete floor or equivalent. See Figure 6.

Figure 6. Flat Drop Test

# 8.4.5 Air Cleanliness

The FINCH is designed to operate in what CDC considers to be an office environment with minimum or no environmental control. Heating is provided, but artificial cooling may not exist for the equipment. Natural or forced air ventilation may be used to limit the maximum temperature. This range is considered the minimum acceptable environment for human comfort. In this environment, the FINCH will operate with the following levels of contamination:

- a. Particle sizes greater than 1.0 micron-concentration of  $4 \ge 10^7$  particles per cubic meter.

- b. Particle sizes greater than 1.5 microns-concentration of  $4 \ge 10^6$  particles per cubic meter.

- c. Particle sizes greater than 5.0 microns-concentration of  $4 \ge 10^5$  particles per cubic meter.

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| А  | 77653331  | 20    | Α    |

#### 8.5 MECHANICAL SPECIFICATIONS

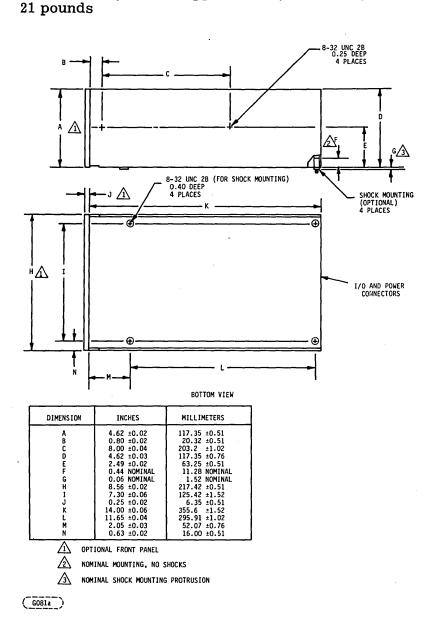

The following dimensions are exclusive of the decorative front panel accessory. Refer to Figure 7 for detailed mounting configuration dimensions. The illustration and dimensions are preliminary and subject to revision.

Height: 4.62 inches Width: 8.56 inches Depth: 14.00 inches Weight: Approximately

s 117.4 millimeters s 217.42 millimeters s 354.6 millimeters tely Approximately 9.53 kilograms

Figure 7. Mounting Configuration Dimensions

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| Α  | 77653331  | 21    | Α    |

|    |           |       |      |

#### 8.5.1 Drive Orientation

The FINCH can be mounted in either of two positions:

- 1. When viewing from the rear (I/O connectors visible), with its right side facing

- down and its left side up. (The machine label is located on the left side.)

- 2. On its baseplate with the environmental enclosure facing up.

Further details on mounting will be included in the Operator and Installation Guide.

#### 9.0 MEDIA CHARACTERISTICS

#### 9.1 MEDIA DESCRIPTION

The media used on the FINCH has a diameter of approximately 8.0 inches. The aluminum substrate is coated with ferrous oxide with lubrication to permit the heads to contact the surface when starting and stopping.

Each data surface has total of 605 tracks and is capable of recording 8,010,240 bytes of unformatted data on 596 tracks. Two error-free spare tracks are provided for track reallocation due to possible media flaws.

Media defects are characterized as being either correctable or uncorrectable as a function of the type and magnitude of the media flaw. Various error correction codes may be implemented to correct errors in the data read from the disk. However, the code chosen should be consistent with the media manufacturers media testing and certification methods. In the FINCH media certification is performed using the following standards:

- an error burst of 11 bits or less is a correctable error

- an uncorrectable error is one greater than 11 bits in length

Host systems utilizing the FINCH should have, as a minimum, resident capabilities to recognize and map defective tracks and perform track reallocation routines.

At the time of shipment from the point of manufacture, the FINCH recording surfaces will meet the following requirements.

- a. 605 total tracks per data surface

- b. 596 primary tracks plus two error-free spare tracks for future use

- c. up to seven additional tracks may contain defects

- d. tracks 0 and 604 to be error free

- e. an area equal to 60 bytes in length immediately after Index to be defect free on each track

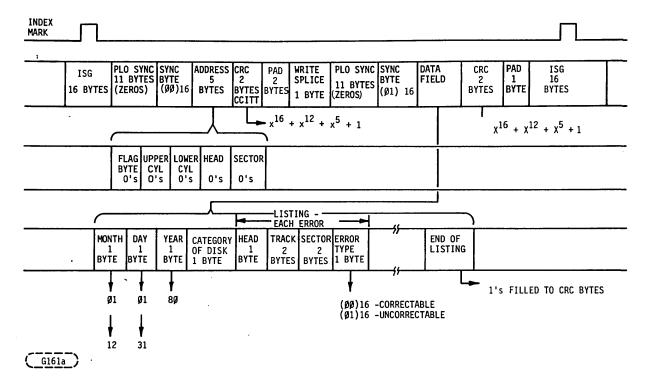

At the time of manufacture, media defect information is recorded in surface 0, track 0, and sector 0 (see Figure 8). This identifies flagged track data for those customers who wish to use it as part of a system initialization and track deallocation routine without recertification. If the customer wishes to use this data, it is imperative not to write on this area of the disk until the information has been recovered.

|  | РС | SPEC. NO. | SHEET | REV. |

|--|----|-----------|-------|------|

|  | Α  | 77653331  | 22    | A    |

Figure 8. Format for Surface 0, Track 0, Sector 0--Factory Flagged Track Data Track

#### **10.0 ERROR RECOVERY CONSIDERATIONS FOR THE HOST SYSTEM**

The FINCH has a minimum of  $t_{WO}$  error free spare tracks per surface available for alternate track assignments. Eight megabytes of unformatted information may be stored in the 596 data recording tracks per surface.

Appropriate rewrite and reread procedures must be executed in a manner similar to that described in paragraph 7.1 through 7.1.4 to determine the recoverability of data should an error occur. Reallocation is required to ensure data storage capacity is maintained should defects develop during field operations.

The more sophisticated error recovery and reallocation programs should be strongly considered during subsystem and software development. Sector reallocations permit continued use of the major portion of a track when a defect is found.

|  | PC | SPEC. NO. | SHEET | REV. |

|--|----|-----------|-------|------|

|  | A  | 77653331  | 23    | A    |

10.0 -contd.

Error correction codes (ECC) and algorithmic programs also should be considered. ECC may permit "bad spots" to be reliably used for data retention if the defect does not exceed a specified quantity of bits (typically 11 bits).

- **10.1** EARLY/LATE STROBE

- 10.1.1 Early Strobe

When this line is true, the device PLO data separator will strobe data at a time earlier than nominal. Normal strobe timeing will be returned when both strobe enable lines are false.

10.1.2 Late Strobe

When this line is true, the device PLO data separator will strobe data at a time later than nominal. Normal strobe timing will be returned when both strobe enable lines are false.

#### NOTE

The use of early and late strobes is for the purpose of recovering marginal data.

# 11.0 TRACK OR SECTOR REALLOCATION

To maximize the available storage capacity, a bad track reallocation customer-designed program is required and a bad sector reallocation or sector skip program is recommended.

Under typical bad track reallocation, the defective track is reallocated to one of the spare tracks provided. Bad track (or sector) location information is normally recorded on track 0 and read into the customer's operating program during program initilization.

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| А  | 77653331  | 24    | Α    |

# 11.0 -contd.

The size of the typical defect found on the disk is less than 11 bits. Obviously, this would affect at least one sector. Flagging and reallocating this one sector may allow the remainder of the track to be used for data storage.

In a sector skip program, one or two spare sectors are allocated at the end of each track. As an example, in a 30 plus 2 scheme, there are 30 data sectors plus 2 spare sectors per track. The defective sector is flagged, then shifted to the following sector when performing an actual operation. Or, a defective sector can be flagged and reallocated to a spare sector at the end of its track.

Defective byte location information will be provided on track 0, head 0 of the disk at the time of shipping from the point of manufacture.

# **11.1** ERROR DETECTION

Because no fault indication or operator/drive interaction is required, software must adequately inform the operator if any technical difficulties arise. In multi-unit installations, logical and physical identification are necessary for the operator to identify a defective unit. For further information refer to Application Note for Diagnostics, 77653374.

#### **12.0** INTERFACE CABLING REQUIREMENTS/OPTIONS

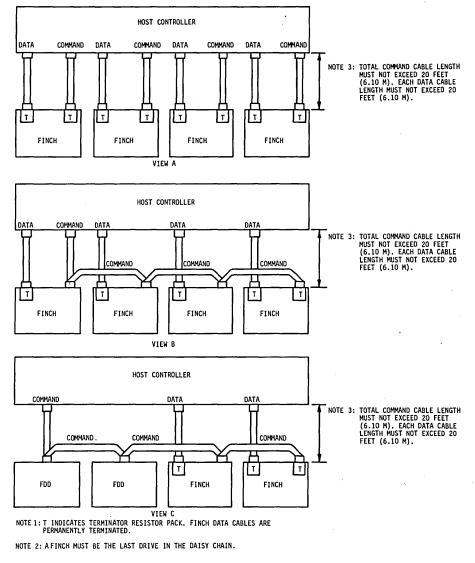

Interface cabling options for the FINCH are shown in Figure 9. View A of Figure 9 shows each drive interfaced to its own command cable, which, in turn, allows interfacing of more than four drives and a variety of system operational techniques. Each drive has its data cable and command cable radially connected to the host controller. The length of each individual cable must not exceed 20 feet (6.1 meters). Terminator resistors must be installed in the host controller for each data cable and for each command cable. If instead of all FINCH's there are FDD's plus FINCH's, then a terminator resistor pack also would be installed in each FDD for its data/command cable.

A daisy chain configuration incorporates parallel interfacing of the disk drives on a common command cable. A maximum of four drives may be daisy chained on the command cable. Only the drive which is selected by the host system has its control and data signals enabled through this common interface. View B of Figure 9 consists only of FINCH's. A terminator resistor is required in the host controller for each data cable. Only the last FINCH in the daisy chain requires a terminator resistor pack for the command cable. Terminator resistor packs for the command cable of other drives would be removed. The total combined command cable length (from the controller to the first drive, to the second and subsequent drives) must not be more than 20 feet (6.1 meters). A FINCH must be the last drive in the daisy chain; this is to ensure FINCH-unique lines are terminated.

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| A  | 77653331  | 25    | А    |

# 12.0 -contd.

View C of Figure 9 consists of a common controller for both FINCH's and FDD's. A maximum of four drives (any combination of FDD's plus FINCH's) may be daisy chained on the command cable. Terminator resistors are required in the controller and in the last drive in the daisy chain for the command cable. Terminator resistor packs for the command cable of other drives would be removed. A terminator resistor is required in the controller for each data cable. The total combined command cable length (from the controller to the first drive, to the second and subsequent drives) must not be more than 20 feet (6.1 meters).

## CAUTION

A FINCH must be the last drive in the daisy chain.

Refer to paragraph 14.1.1 for logical unit selection.

# Figure 9. Interface Cabling Options.

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| А  | 77653331  | 26    | A    |

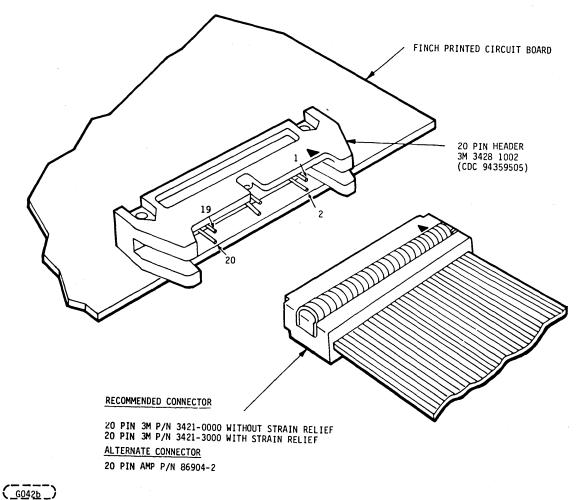

# 12.1 DC CABLE AND CONNECTOR

The FINCH receives DC power through a 7-position connector which plugs into either two right-angled headers or one 7-pin header mounted on the printed circuit board assembly. The 2-pin and 4-pin headers are mounted such that they form a composite 7-pin header with the fifth pin missing (see Figure 10). The plug-in connector consists of a locking clip housing with the fifth position molded shut for keying; this housing uses locking clip contacts. If locking clip contacts are not desired, a housing using high pressure contacts and a nylon keying post to be plugged into the fifth position can be used.

(G040b )

Figure 10. DC Cable Connector

#### FUNCTION

#### AMP PART NUMBER\*

7-Position Plug-in Connector:

| With Locking Clip Housing<br>Locking Clip Contacts<br>Crimping Tool for Locking Clips | 1-87270-1<br>87278-2<br>90308 |

|---------------------------------------------------------------------------------------|-------------------------------|

| Without Locking Clip Housing                                                          | 3-87025-3                     |

| High Pressure Contacts<br>Nylon Keying Post                                           | 87024-3                       |

| Nyion Reying Post                                                                     | 87116-1                       |

\*Equivalent parts may be used.

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| A  | 77653331  | 27    | А    |

# 12.2 COMMAND AND DATA CABLES AND CONNECTORS

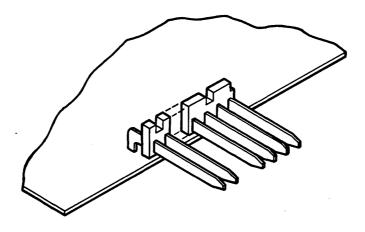

Refer to Figure 11 for a pictorial representation of the Data cable interface.

| FUNCTION                                     | CDC NO.    | *RECOMMENDED<br>PART NO. |

|----------------------------------------------|------------|--------------------------|

| 50-Pin Command Cable<br>Connector            |            |                          |

| With Strain Relief                           | 75810305-5 | 3M-3425-3000             |

| Without Strain Relief                        | 95880003-9 | 3M-3425-0000             |

| 20-Pin Data Cable Connector                  |            |                          |

| With Strain Relief                           |            | 3M-3421-3000             |

| Without Strain Relief                        |            | 3M-3421-0000             |

| 50-Conductor Cable<br>Type (Stranded AWG 28) |            | 3M-3365-50               |

| 20-Conductor Cable<br>Type (Stranded AWG 28) |            | 3M-3365-20               |

# 12.3 INTERFACE DRIVERS/RECEIVERS

The FINCH utilizes two types of signals -- single-ended and balanced differential. The data and clock signals utilize balanced differential drivers and receivers. All other signals utilize single-ended drivers and receivers.

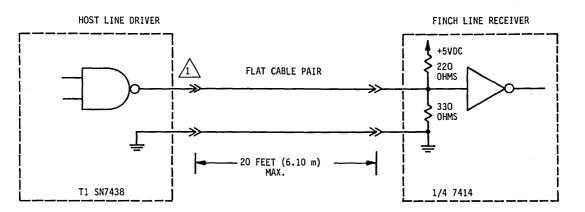

12.3.1 Single-Ended Drivers/Receivers

# 12.3.1.1 Transmitter Characteristics

The FINCH uses the 7438 quad-2-input driver (or equivalent) to transmit status and data to the host. This driver is capable of sinking a current of 48 mA with a low-level output voltage of 0.4 volt (see Figure 12).

\*Equivalent parts may be used.

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| А  | 77653331  | 28    | A    |

Figure 11. Data Cable Interface

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| А  | 77653331  | 29    | A    |

# 12.3.1.2 Receiver Characteristics

The FINCH uses the 7414 Hex Inverter with hysteresis gate (or equivalent) as a line receiver. The input of each receiver is terminated in 132 ohms via a 220-ohm/330-ohm resistor combination as shown in Figure 12.

INTERFACE SIGNAL LEVELS AND LOGICAL SENSE AT THE FINCH I/O CONNECTOR ARE DEFINED AS FOLLOWS:

IF FINCH IS TO BE LOCATED EXTERNAL TO HOST CABINETRY, APPROPRIATE I/O CABLE SHIELDING AND SHIELD TERMINATION MAY BE REQUIRED TO MEET RADIATED EMISSIONS STANDARDS.

| LOGIC LEVEL                 |     | FROM FINCH    | TO FINCH      |

|-----------------------------|-----|---------------|---------------|

| HIGH (FALSE OR DEACTIVATED) | (0) | ≥2.4 V;≤5.0 V | ≥2.0 V;≤5.0 V |

| LOW (TRUE OR ACTIVATED)     | (1) | ≤0.4 V;≥0.0 V | ≤0.8 V;≥0.0 V |

THE DIFFERENCE IN THE VOLTAGES BETWEEN INPUT AND OUTPUT SIGNALS IS DUE TO THE LOSSES IN THE CABLE.

(<u>\_\_\_\_\_\_\_</u>\_\_)

Figure 12. Single-Ended Transmitters and Receivers

| A |    |           |       |      |   |

|---|----|-----------|-------|------|---|

|   | PC | SPEC. NO. | SHEET | HEV. | l |

|   | A  | 77653331  | 30    | A    |   |

#### 12.3.1.3 Terminator Characteristics

The terminators consist of a DIP resistor module which plugs into a DIP socket in the last unit in a daisy chain. Each drive is furnished with terminators. Terminators must be removed from all except the last drive on the cable prior to daisy-chain operation. An equivalent terminator must be provided in the controller on each input signal line from the FINCH to the controller. Refer to Figure 12. Only the Command cable DIP resistor module is removable.

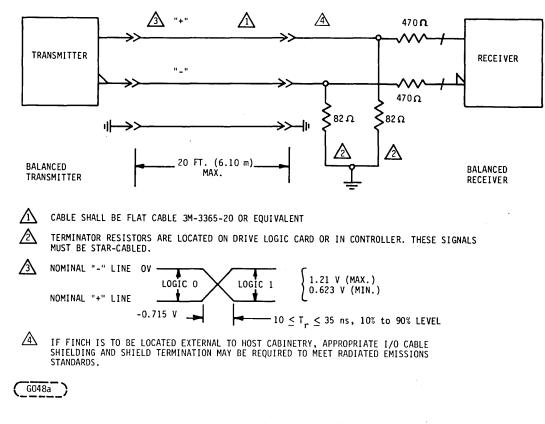

12.3.2 Balanced Differential Drivers/Receivers

## 12.3.2.1 Transmitter Characteristics

The FINCH uses 75110A-type balanced differential drivers terminated per Figure 13. Logic 1 on the interface is defined when the "+" output is more positive than the "-" output.

| ſ | ····· | PC | SPEC. NO. | SHEET | REV. | ł |

|---|-------|----|-----------|-------|------|---|

|   |       | Α  | 77653331  | 31    | Α    |   |

#### 12.3.2.2 Receiver Characteristics

The FINCH uses the 75107A-type balanced differential receiver terminated per Figure 13. Logic 1 on the interface is defined when the "+" input is more positive than the "-" input.

#### 12.3.2.3 Terminator Requirements

Each differential receiver in the drive is terminated with 470-ohm and 82-ohm resistors per Figure 13. An equivalent terminator must be provided in the controller on each input signal line from the FINCH to the controller.

## 13.0 DIGITAL-INTERFACE SIGNAL DEFINITIONS

The FINCH utilizes two digital interface cables (Command and Data) for information transfer between it and the controller/host system. The connector pin assignment for the Command cable is shown in Figure 14. The connector pin assignment for the Data cable is shown in Figure 15. The signal direction, as well as type is also shown on these figures. (All single-ended signals are true when the interface voltage level is less than 0.4 volts.)

## 14.0 INTERFACE SIGNAL DEFINITIONS

This section lists and defines standard input and output signals. All nonreserved signal leads not used by the controller must be either terminated or set to a logic 0 state. Reserved interface leads are discussed in paragraph 14.3. All timing diagrams for single-ended signals are drawn with the true or logic 1 state signalled by the low voltage level.

All information in this section assumes valid drive operating conditions have been accommodated. Refer to Figures 13 and 14.

#### 14.1 INPUT SIGNAL LINES

#### 14.1.1 Unit Select (1-2-3-4)

These input lines are used to activate a device's drivers and receivers for up to four drives in a daisy-chained operation.

Unit Select must remain active during any communication with the host controller.

All signals from the drive in the radial data cable are available to the controller regardless of the state of the Unit Select lines.

Logical unit designation is accomplished at the time of installation by setting the DIP switches located on the base board assembly.

|  | PC | SPEC. NO. | SHEET | REV. | l |

|--|----|-----------|-------|------|---|

|  | А  | 77653331  | 32    | Α    | ĺ |

|  |    |           |       |      | I |

# "DASH 1" INTERFACE

|                     | SIGNAL DIRECTION           | SIGNAL DIRECTION | SIGNAL<br>PIN NO.    | GROUND<br>PIN NO. |

|---------------------|----------------------------|------------------|----------------------|-------------------|

|                     | NA                         |                  | 2                    | 1                 |

|                     | RETURN TO ZERO (RTZ)       |                  | 4                    | 3                 |

|                     | NA                         | -                | 6                    | 5                 |

|                     | INDEX                      |                  | 8                    | 7                 |

|                     | NA                         |                  | 10                   | 9                 |

| CONTROLLER/<br>HOST | STEP                       |                  | 12                   | 11                |

| INTERFACE           | DIRECTION                  |                  | 14                   | 13                |

|                     | WRITE ENABLE               |                  | 16                   | 15                |

|                     | NA                         |                  | 18                   | 17                |

|                     | UNIT SELECT -1             |                  | 20                   | 19                |

|                     | UNIT SELECT -2             |                  | 22                   | 21                |

|                     | UNIT SELECT -3             |                  | 24                   | 23                |

|                     | UNIT SELECT -4             | <b>_</b>         | 26                   | 25                |

|                     | UNIT READY -1              |                  | 28                   | 27                |

|                     | UNIT READY -2              |                  | 30                   | 29                |

|                     | UNIT READY -3              |                  | 32                   | 31                |

|                     | UNIT READY -4              |                  | 34                   | 33                |

|                     | NA                         |                  | 36                   | 35                |

|                     | READ ENABLE                |                  | 38                   | 37                |

|                     | HEAD SELECT 2 <sup>0</sup> |                  | 40                   | 39                |

|                     | HEAD SELECT 2 <sup>1</sup> |                  | 42                   | 41                |

|                     | RESERVED FOR FACTORY USE   |                  | 43                   |                   |

|                     | WRITE FAULT                | -                | 44                   |                   |

|                     | NA                         |                  | 45                   |                   |

|                     | FAULT RESET                |                  | 46                   |                   |

|                     | NA                         |                  | 47                   |                   |

|                     | BYTE CLOCK                 |                  | 48                   |                   |

|                     | DISK TYPE                  |                  | 50                   | 49                |

|                     | -                          |                  | FINCH CO<br>CONNECTO | MMAND<br>R*       |

NA -- NOT APPLICABLE TO THE FINCH BUT IS USED BY THE FDD.

★ -- ALL SIGNALS IN THE COMMAND CABLE ARE SINGLE-ENDED SIGNALS.

(\_\_\_\_\_\_\_)

Figure 14. Command Cable Interface

|  |    |           |                                                                                                                 | i nevr | 4 |

|--|----|-----------|-----------------------------------------------------------------------------------------------------------------|--------|---|

|  | PC | SPEC. NO. | SHEET                                                                                                           | REV.   |   |

|  | A  | 77653331  | 33                                                                                                              | Α      |   |

|  | I  |           | the second se |        | • |

| ······································ | SIGNAL DIRECTION         | SIGNAL DIRECTION | PIN NO.           | TYPE* |

|----------------------------------------|--------------------------|------------------|-------------------|-------|

|                                        | INDEX                    |                  | 1                 | SE    |

|                                        | GROUND                   |                  | 2                 |       |

|                                        | BYTE CLOCK               |                  | 3                 | SE    |

| CONTROLLER/<br>HOST                    | GROUND                   |                  | 4                 |       |

| INTERFACE                              | EARLY DATA STROBE ENABLE |                  | 5                 | SE    |

|                                        | LATE DATA STROBE ENABLE  |                  | 6                 | SE    |

|                                        | UNIT SELECTED            | _                | 7                 | SE    |

|                                        | GROUND                   |                  | 8                 |       |

|                                        | WRITE DATA "+"           |                  | 9                 | DIFF  |

|                                        | WRITE DATA "-"           |                  | 10                | DIFF  |

|                                        | GROUND                   |                  | 11                |       |

|                                        | WRITE CLOCK "+"          |                  | 12                | DIFF  |

|                                        | WRITE CLOCK "-"          |                  | 13                | DIFF  |

|                                        | GROUND                   |                  | 14.               |       |

|                                        | SERVO/READ CLOCK "+"     |                  | 15                | DIFF  |

|                                        | SERVO/READ CLOCK "-"     |                  | 16                | DIFF  |

|                                        | GROUND                   | ,                | 17                |       |

|                                        | READ DATA "+"            |                  | 18                | DIFF  |

|                                        | READ DATA "-"            |                  | 19                | DIFF  |

|                                        | GROUND                   |                  | 20                |       |

|                                        |                          | <u></u>          | FINCH I<br>CONNEC |       |

# "DASH 1" INTERFACE

DIFF = DIFFERENTIAL SIGNAL

(G046a)

Figure 15. Data Cable Interface

| Т | PC | Ċ | SPEC. NO. | SHEET | REV |

|---|----|---|-----------|-------|-----|

|   | A  | A | 77653331  | 34    | A   |

|   |    |   |           |       |     |

# 14.1.1 -contd.

The Unit Ready lines are the only command cable lines not gated with Unit Select. No data cable signal lines are gated with Unit Select.

The 9410 should not be selected until the Ready input is received after AC and DC power have been applied (Figure 16). The 9410 will be selected within 1 microsecond after the activation of Unit Select and deselected within 1 microsecond after the deactivation of Unit Select. Unit Select must be valid 1 microsecond before the first step pulse is received and 1 microsecond after the last step pulse is received.

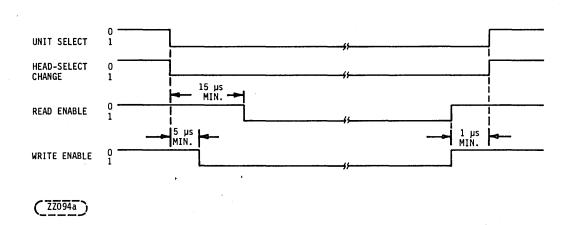

At the completion of a write operation, Unit Select must remain active for 1 microsecond (Figure 18). The activation of Unit Select enables the Head Select logic. When a drive is deselected, no head is selected within the drive. When the Select line is activated, a head change will occur, thus requiring a delay before a read or write operation can be initiated.

Figure 16. Power Turn On and Unit Selection

# 14.1.2 Direction

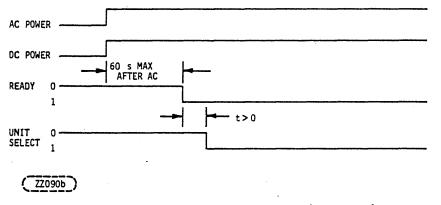

Direction determines the course of movement of the head carriage: a logic 1 on this line signifies head-carriage movement toward the higher-numbered cylinders; a logic 0 on this line signifies head-carriage movement toward the low-numbered cylinders.

Direction must stabilize a minimum of 1 microsecond before each Step pulse and 1 microsecond after the last Step pulse (see Figure 17).

| Г | PC | SPEC. NO. | SHEET | REV. |

|---|----|-----------|-------|------|

|   | А  | 77653331  | 35    | Α    |

-- 10 ms FOR A SINGLE TRACK SEEK (I.E., 1 STEP PULSE

-- DEPENDENT ON STEP RATE INPUT

Figure 17. Track-Access Timing

| P | PC | SPEC. NO. | SHEET | REV. |

|---|----|-----------|-------|------|

| A | A  | 77653331  | 36    | Α    |

14.1.3 Step

Step is used with Direction to cause head-carriage movement. Each pulse on the Step line causes the head carriage to be moved one cylinder in the direction determined by the state of the Direction line.

Step pulses must be a minimum of 0.5 microsecond at the logic 1 or logic 0 level (see Figure 17). The minimum time between Step pulses is 16 microseconds. (To meet the 9410 seek performance characteristics, the maximum time between Step pulses is 25 microseconds.)

The 9410 operates in a semibuffered Step mode. The R/W heads will start to move when the first Step pulse is received. The rate of head movement is determined by the rate of the incoming Step pulses; however, the Step pulse rate may exceed the head movement rate. The Ready line is used to indicate that a seek is in progress (see Figure 17). The Ready line will be deactivated within 100 microseconds after the leading edge of the first Step pulse and will be activated when the seek function is successfully completed.

After the last Step pulse has been sent to the 9410, the Drive Select line may be deactivated and a different drive selected. The minimum time after the last Step pulse before the Drive Select or Direction line can be deactivated is 1 microsecond.

The first Step pulse to initiate a seek should not be sent to the 9410 unless the Ready line is true.

The Drive will always attempt to maintain the heads over the recording zone of the media (between tracks 0 and 604). Head positioning movement will normally terminate at the boundary (track 0 or 604) in the direction of movement; however, if a hardware fault existed within the drive such that the head was driven outside of the recording zone, the head will automatically be repositioned over track 0 if possible. If the head can be positioned within the recording zone successfully, no fault will be signified and the Ready line will be activated after successfully positioning the head. It is the controller's responsibility to verify the correct head position after a seek function.

|  | PC | SPEC. NO. | SHEET | REV. |  |

|--|----|-----------|-------|------|--|

|  | А  | 77653331  | .37   | A    |  |

# 14.1.4 Head Select 2<sup>0</sup>, 2<sup>1</sup>

These lines are used to select the proper media and head for data transfer as follows:

| Head<br>2 <sup>1</sup> | $\frac{\text{Select}}{2^0}$ | Head<br>No. |                        | Media<br>Selected |

|------------------------|-----------------------------|-------------|------------------------|-------------------|

| 0                      | 0                           | 0           | Top Head               | Basic Media       |

| 1                      | 1                           | 3           | Invalid Head<br>Select |                   |

| 1                      | 0                           | 2           | Top Head               | Optional Media    |

| 0                      | 1                           | 1           | Bottom Head            | Optional Media    |

Head Selection may be changed at any time following activation of Unit Select, but must occur a minimum of 15 microseconds prior to a read operation or 5 microseconds prior to a write operation. Read Enable or Write Enable must be deactivated a minimum of 1 microsecond prior to a head change (Figure 18).

The Ready line will not change as a result of head change.

#### 14.1.5 Fault Reset

Fault Reset is used to reset the Write Fault latch if the fault no longer exists. A minimum 1 microsecond pulse to the logic 1 level is required to reset the Write Fault latch.

#### 14.1.6 Return to Zero

RTZ causes the actuator to return to track 0 and reset a seek error indication. This seek is significantly longer than a seek to track 0 and should only be used for recalibration and not data acquisition.

The RTZ function will be initiated by a logic 1 pulse (0.5 to 25 microseconds). The Unit Ready input will be deactivated within 100 microseconds after reception of an RTZ command. The successful completion of an RTZ will be signified by the activation of Unit Ready.

|  | PC | SPEC. NO. | SHEET | REV. |

|--|----|-----------|-------|------|

|  | Α  | 77653331  | 38    | А    |

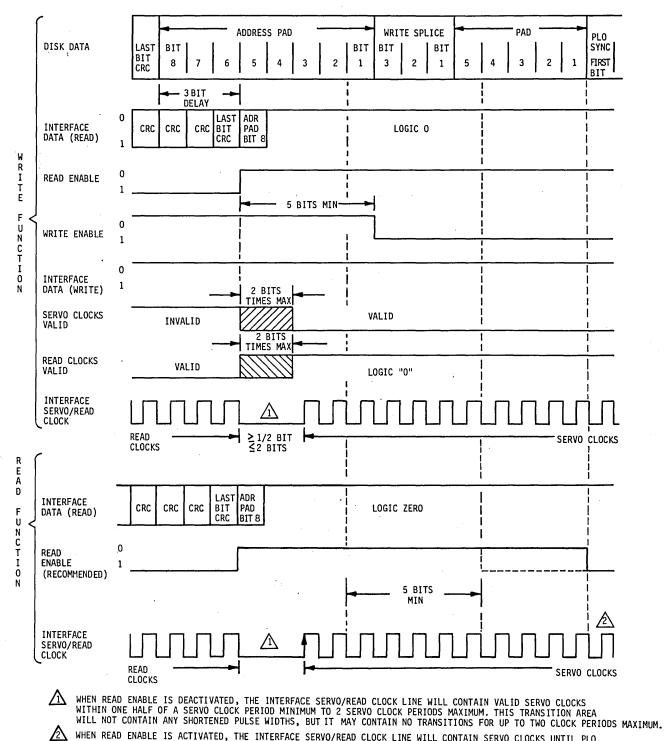

# 14.1.7 Read Enable

Activation (logic 1) of the Read Enable signal enables digital read data on the Read Data lines and enables Read Clock on the Read/Servo clock lines. The leading edge of Read Enable triggers the read chain to synchronize the internal phase-locked oscillator to a media-recorded PLO synchronization field (refer to Section 15.0).

# 14.1.8 Write Enable

Activation (logic 1) of the Write Enable signal enables the write drive and initiates recording of the contents of the Write Data lines onto the media. (Refer to Section 15.0 for timing.)

#### 14.1.9 Write Data "+" and "-"

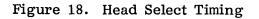

Data to be recorded on the media is supplied on these balanced differential lines. These lines carry NRZ data which is in phase sync with the Write Clock lines. (See Figure 19.)

#### 14.1.10 Write Clock "+" and "-"

These lines carry the balanced differential Write Clock signal which must be synchronized with the NRZ Write Data as illustrated in Figure 19. The Write Clock is the Servo Clock retransmitted to the drive during a Write operation. The Write Clock need not be transmitted continuously but must be transmitted at least 2 1/2 servo clock periods prior to Write Enable.

#### 14.2 OUTPUT SIGNAL LINES

#### 14.2.1 Unit Ready -1, -2, -3, -4

A logic 1 on these lines indicates that the disk is up-to-speed, the heads are over the recording zone, the drive is on cylinder and not executing a seek function, and no write fault conditions exist. These lines are not gated with Unit Select and an individual line is provided for each drive in a daisy-chain configuration.

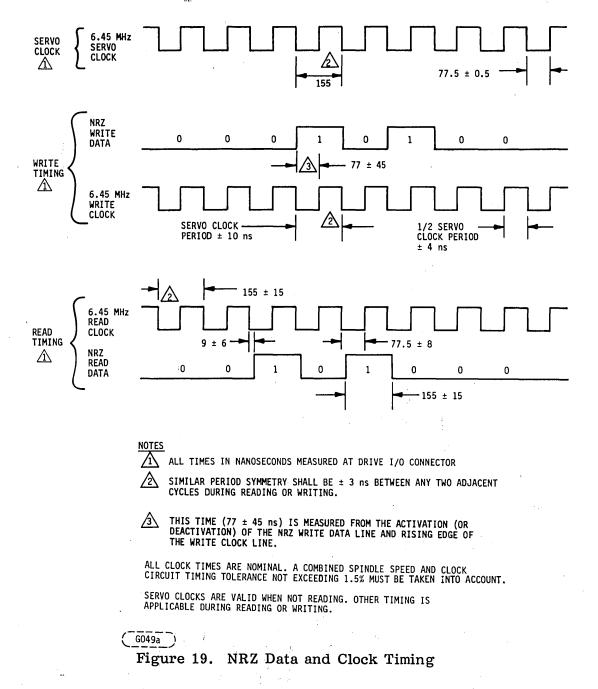

#### 14.2.2 Index

Index, which occurs once per revolution, indicates the physical beginning of the cylinders. Index is true for 1.24 microseconds nominal per revolution (see Figure 20). This signal is contained in the Command cable and gated with Unit Select: it is also available in the Data cable, not gated with Unit Select.

|  | PC | SPEC. NO. | SHEET | REV. |

|--|----|-----------|-------|------|

|  | А  | 77653331  | 39    | A    |

|  |    |           |       |      |

|  | PC | SPEC. NO. | SHEET     | REV. |

|--|----|-----------|-----------|------|

|  | A  | 77653331  | 40        | Α    |

|  |    |           | · · · · · |      |

(ZZ092b)

#### Figure 20. Index and Byte Clock Relationship

# 14.2.3 Byte Clock

Byte Clock occurs once per eight Servo Clock periods. There are 13,440 byte clocks per disk revolution at a nominal rate of 806 kHz. The controller is responsible for counting the byte clocks to determine the sector size and location. The interrelationship of Index and the Byte Clock is shown in Figure 20. This signal is continuously transmitted if the disk is up to speed and the heads are positioned over the recording zone of the disk.

This signal is contained in the Command cable and gated with Unit Select: it is also available in the Data cable not gated with Unit Select.

#### 14.2.4 Write Fault

Write Fault conditions detected by the FINCH will activate the Write Fault signal. The Write Fault signal will remain activated until it is deactivated by the Fault Reset lead or by power sequencing the FINCH. The Write Fault lead will be deactivated within 0.5 microsecond from the leading edge of the Fault Reset line. Reading or writing of the disk will be inhibited if the Fault lead is activated.

A Write Fault condition will occur if Write Enable is true and either write current is absent, write data is absent, the FINCH is not ready, an invalid head or internal multiple heads are selected, or Read Enable is true. A Write Fault condition will also occur if Write Enable is false and write current is present.

|  | PC | SPEC. NO. | SHEET | REV. | ł |

|--|----|-----------|-------|------|---|

|  | Α  | 77653331  | 41    | Α    |   |

#### 14.2.5 Disk Capacity

This output signal, when true, indicates the presence of basic and optional media. When false, this signal indicates the presence of the basic media (8 megabytes) only.

#### 14.2.6 Unit Selected

This output signal, when true, provides positive feedback to the controller that the unit is selected. The individual lines from each 9410 may be checked by the controller to verify that only one drive at a time is selected. This signal will become activated within 1 microsecond after a unit is selected. This signal will be deactivated within 1 microsecond after a unit is deselected.

#### 14.2.7 Servo/Read Clock "+" and "-"

These balanced differential lines contain the drive-generated Read Clocks if the Read Enable signal is true or the drive-generated Servo Clocks if the Read Enable signal is false. This signal is located in the Data cable and is not gated with Unit Select.

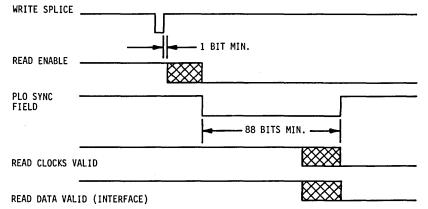

The Read Clock defines the beginning of a data cell and, when valid, is in phase and frequency synchronization with the Read Data as specified in Figure 19. The Read clocks will be valid within 88 Read Clock periods from the concurrence of Read Enable and a PLO synchronization field (refer to Section 15.0 for interface timing).

The Servo Clock is an internally generated phase-locked clock (6.45 MHz nominal) which should be used by the controller to generate Write Clocks (see Figure 19). This clock is phase and frequency locked to the disk rotational speed. Servo Clocks will be valid within two Servo Clock periods after the Read Enable signal is switched from the true to the false condition.

(Phase/Frequency discontinuities may exist, by no clock transitions, in the Servo/Read Clock signal when the Read Enable signal is being switched between the true and false conditions. Refer to Figure 24).

14.2.8 Read Data "+" and "-"

> These balanced differential lines transmit the recovered media data in the NRZ form from the FINCH to the controller. This data is in frequency and phase synchronization with the Read Clocks as specified in Figure 19. The Read Data lines are valid within 88 Read Clock periods from the concurrence of Read Enable and PLO synchronization. Refer to Figure 21 for detailed timing and Section 15.0 for recommended format timings. The Read Data lines are located in the data cables and will be a logic 0 until PLO synchronization is established with a Read function.

| PC | SPEC. NO. | SHEET | REV. |

|----|-----------|-------|------|

| А  | 77653331  | 42    | A    |

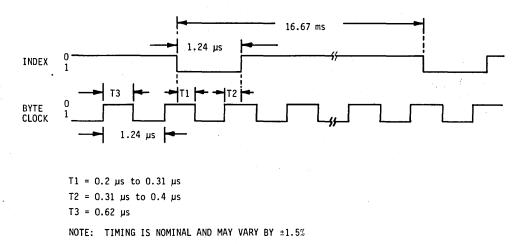

READ ENABLE MUST BE DEACTIVATED PRIOR TO THE WRITE SPLICE. READ ENABLE MAY BE REINITIATED AT LEAST ONE BIT AFTER THE WRITE SPLICE AND WITH AT LEAST 11 BYTES OF PLO SYNC REMAINING IN THE SYNC FIELD.

(\_<u>6162b</u>)

Figure 21. Read Timing

| Ţ | PC | SPEC. NO. | SHEET | REV |

|---|----|-----------|-------|-----|

|   | А  | 77653331  | 43    | Α   |

#### 14.3 RESERVED SIGNAL LINES

Reserved signal lines are provided for potential future enhancements or for test purposes within CDC. These leads should be left as an open circuit by the controller or supplied with a logic 0 input.

These reserved signal lines are as follows:

Command Connector, Pin 43 Data Connector, Pin 5 and Pin 6

### 15.0 DATA FORMAT AND DATA CONTROL TIMING

#### 15.1 FORMAT DEFINITION

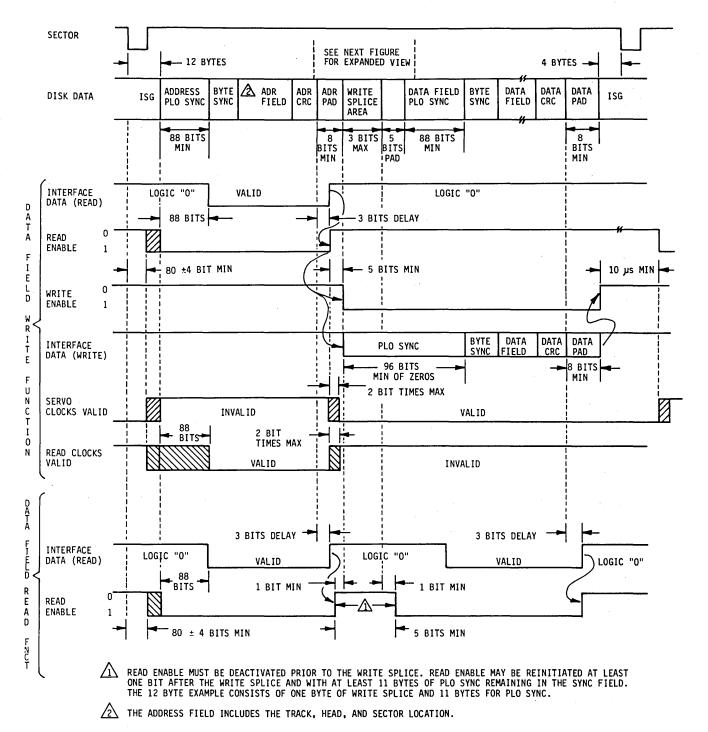

G042a

The record format on the disk is under control of the controller. The Index pulse and byte clocks are available for use by the controller to indicate the beginning of a track and allow the controller to define the beginning of a sector. A suggested format for fixed-length data records is shown in Figure 22.

The format presented in Figure 22 consists of three functional areas: Intersector Gap, Address, and Data. The Data area is used to record the system's data files. The Address area is used to locate and verify the track and sector location on the disk where the Data areas are to be recorded. This section refers to a Sector pulse which is generated internal to the controller from the Byte clock to ease the format description.

| DEX/SECTOR      |                         |                                   |                             | FIXED                 | SECTOR:              | "N" IDENT                 | ICAL SECTOR             | RS                                |               |                        |                       | SEC             |

|-----------------|-------------------------|-----------------------------------|-----------------------------|-----------------------|----------------------|---------------------------|-------------------------|-----------------------------------|---------------|------------------------|-----------------------|-----------------|

| 12 BYTE         | \$ <b></b>              | ADI                               | DRESS ARE                   | <i>م</i>              |                      | •                         |                         | DATA A                            | REA           |                        |                       | 4 BYTES         |

| ISG<br>16 BYTES | PLO<br>SYNC<br>11 BYTES | BYTE<br>SYNC<br>PATTERN<br>1 BYTE | ADDRESS<br>FIELD<br>5 BYTES | ADR<br>CRC<br>2 BYTES | ADR<br>PAD<br>1 BYTE | WRITE<br>SPLICE<br>1 BYTE | PLO<br>SYNC<br>11 BYTES | BYTE<br>SYNC<br>PATTERN<br>1 BYTE | DATA<br>FIELD | DATA<br>CRC<br>2 BYTES | DATA<br>PAD<br>1 BYTE | ISG<br>16 BYTES |

|                 |                         | 7                                 |                             |                       |                      |                           | -                       |                                   |               |                        |                       |                 |