# **SYSTEMS**

## **ETA10 System Reference Manual**

## **ETA10** Computer System

## **ETA10 System Reference Manual**

PUB-1005 Revision A December 4, 1987 The items listed below are referenced in this document and are names, products, or trademarks associated with the following companies:

Apollo is a trademark of Apollo Computer Corporation.

DOMAIN is a trademark of Apollo Computer Corporation.

CDC is a trademark of Control Data Corporation.

CYBER 180 is a product of Control Data Corporation.

CYBER 205 is a product of Control Data Corporation.

ETA is a trademark of ETA Systems, Incorporated.

ETHERNET is a trademark of Xerox Corporation.

Loosely Coupled Network (LCN) is a product of Control Data Corporated.

Network Access Device (NAD) is a product of Control Data Corporated.

Network Access Device (NAD) is a product of ETA Systems, Incorporated.

VAX is a trademark of Digital Equipment Corporation.

#### Disclaimer:

ETA<sup>TM</sup> Systems, Incorporated reserves the right to make changes in specifications and other information contained in this publication without prior notice, and the reader should consult ETA Systems to determine whether any such changes have been made. (At non-U.S. installations, the reader should consult the local marketing representative). This manual may not be reproduced and is intended for the exclusive use of ETA Systems' customers.

The terms and conditions governing the sale of ETA Systems hardware products and the licensing and use of ETA Systems software consist solely of those set forth in the written contracts between ETA Systems and its customers. No statement contained in this publication, including statements regarding capacity, suitability for use, or performance of products, shall be considered a warranty by ETA Systems for any purpose or give rise to any liability of ETA Systems.

In no event will ETA Systems be liable for any incidental, indirect, special, or consequential damages (including lost profits) arising out of or relating to this publication or the information contained in it, even if ETA Systems has been advised, knew, or should have known of the possibility of such damages.

The copyright laws prohibit the copying of this manual without the written consent of ETA Systems. Copying, under the law, includes translating into another language or format.

Prepared by: ETA Systems, Incorporated Technical Communication Dept. 1450 Energy Park Drive St. Paul, MN 55108

© Copyright 1987 by ETA Systems, Inc. All rights reserved.

Documents that have a numeric revision code, such as 01 or 03, are still in the draft stage. They are not yet approved for release. Documents carrying an alphabetic code, such as A or C, are complete, finished documents. They are approved for release.

| Document<br>Revision | Software<br>Version | Date             |

|----------------------|---------------------|------------------|

| Revision A           | Rel. 1, Vers. 1.0   | December 4, 1987 |

#### **Changes in This Revision**

Compared to draft versions previously distributed, this revision of the *ETA10 System Reference Manual* includes new material on the operating system kernel in chapter 4, revisions of chapters 7 and 8, a glossary, and an index. It is meant to accompany Release 1, Version 1.0 of EOS, the ETA10 operating system.

•.

## **Table of Contents**

| About | This | Document | <br>xi |

|-------|------|----------|--------|

|       |      |          |        |

#### System Architecture

#### Chapter 1

| Overview of the  | System Components       Section 1         Guide to the Chapter Contents in This Manual       1-2         Super-cooled Systems       1-3         Air-cooled Systems       1-3         Operating Software       1-4 |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Architect | ure                                                                                                                                                                                                               |

| -                | Architectural Overview                                                                                                                                                                                            |

|                  | Hardware and Software Integration                                                                                                                                                                                 |

|                  | Computational Architecture                                                                                                                                                                                        |

|                  | Memory Architecture                                                                                                                                                                                               |

|                  | Input/Output Architecture 1-9                                                                                                                                                                                     |

|                  | Network Architecture                                                                                                                                                                                              |

| The ETA10 Mod    | lel Range                                                                                                                                                                                                         |

|                  | Cooling Options                                                                                                                                                                                                   |

|                  | Redundancy Options 1-12                                                                                                                                                                                           |

#### The User Environment

#### Chapter 2

| The Environment Model            | 2–2  |

|----------------------------------|------|

| Overview of the VSOS Environment | 2-14 |

| Functional Description of VSOS   | 2-30 |

| The VSOS Command Shell           | 2–44 |

#### **Resource Management**

| ETA10 | Resource Management                    | ion 1 |

|-------|----------------------------------------|-------|

|       | Management of the System Memories      | -5    |

|       | Central Processor Memory Management    | -6    |

|       | Shared Memory Management 3-            | -9    |

|       | Communication Buffer Memory Management | -11   |

|       | Management of Processors               | -13   |

| Management of the Input/Output Subsystem | 3–14      |

|------------------------------------------|-----------|

| Management of the System Configuration   | 3–15      |

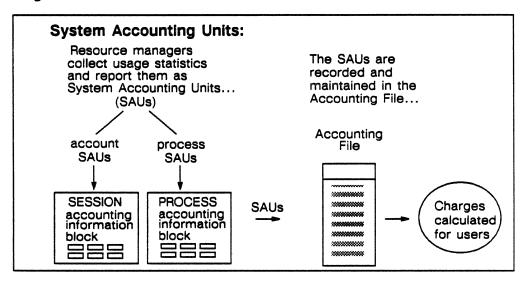

| Resource Allocation and Accounting       | Section 2 |

| Accounting System                        | 3–18      |

| Tracking Resource Usage                  | 3–20      |

| The User Registry                        | 3–22      |

| The Account and Project Registry         |           |

#### The Operating System Kernel

| Introduction     | Section                                        | 1 |

|------------------|------------------------------------------------|---|

|                  | Distribution of Kernel Features                |   |

|                  | The Kernel Operating System Feature Groups 4-6 |   |

| Underlying Opera | tions                                          | 2 |

|                  | CPU Monitor                                    |   |

|                  | Process Queues                                 |   |

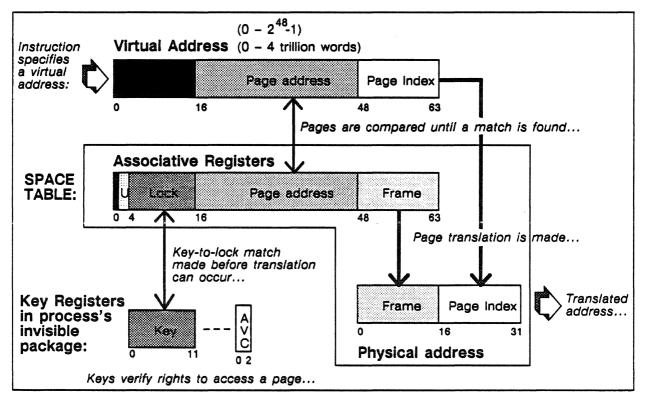

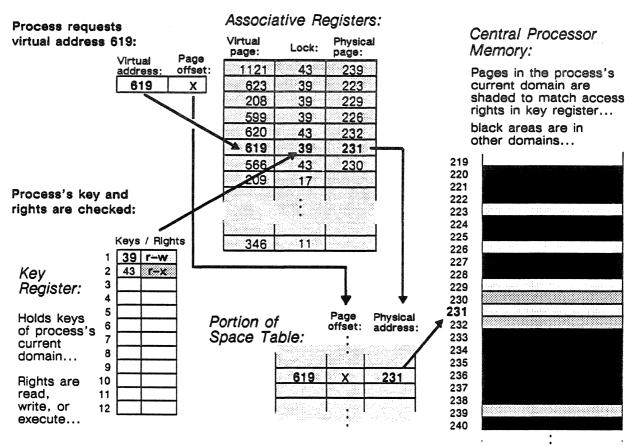

|                  | Virtual Address Mechanism 4-16                 |   |

|                  | Locked-Down Process Objects 4–18               |   |

|                  | Mode Exchanges 4–21                            |   |

|                  | Domain Change                                  |   |

|                  | Critical System Servers                        |   |

| Processes on the | ETA10                                          | 3 |

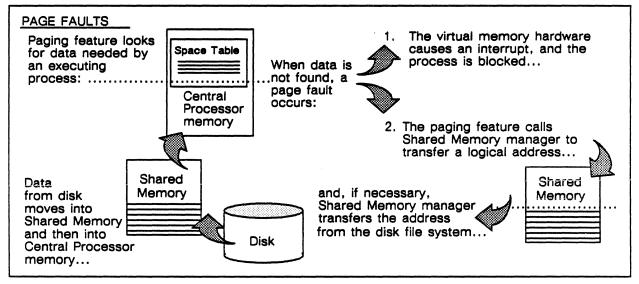

|                  | Page Fault Processing 4-37                     |   |

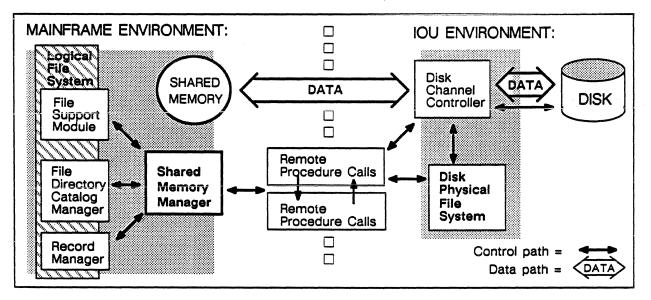

| The Logical-File | System                                         | 4 |

| U                | File Directory/Catalog Manager                 |   |

|                  | File Support Module                            |   |

|                  | Record Manager                                 |   |

| The Memory Mar   | agers                                          | 5 |

|                  | Central Processor Memory Manager 4-101         |   |

|                  | Shared Memory Manager 4-117                    |   |

|                  | Communication Buffer Management 4-123          |   |

| The Process Man  | agers                                          | 6 |

|                  | The Global Scheduler                           |   |

|                  | Process Management                             |   |

|                  | Remote Procedure Calls 4-166                   |   |

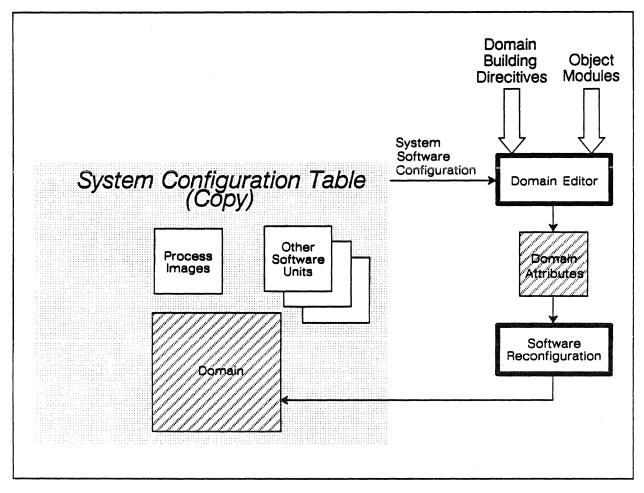

| Domain Managen  | nent                               |

|-----------------|------------------------------------|

| -               | Domain Management 4-177            |

| The System Mana | agers                              |

| •               | System Configuration Control 4-205 |

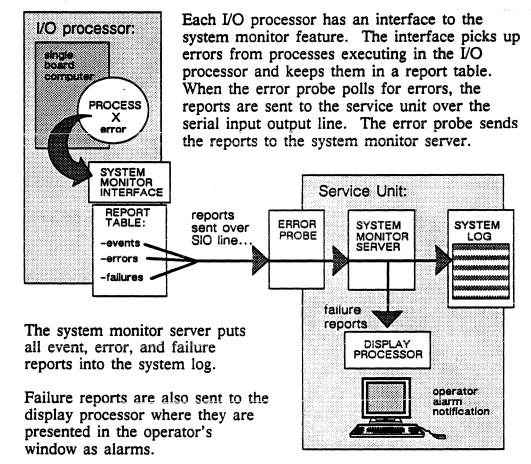

|                 | System Monitor                     |

|                 | System Logging and Analysis 4-238  |

| System Entry    | Section 9                          |

|                 | User Management                    |

#### Mainframe Components

| Overview of the I | ETA10 Mainframe                             | Section 1 |

|-------------------|---------------------------------------------|-----------|

| •                 | Mainframe Components                        |           |

|                   | Overview of the ETA10 Hardware System       |           |

| Central Processor | r Architecture                              | Section 2 |

|                   | Central Processor Operations                | 5–14      |

|                   | Monitor Mode and Job Mode                   |           |

|                   | Scalar Processor and Its Operations         | 5–19      |

|                   | Vector Unit Operations                      |           |

|                   | The Register File                           | 5–33      |

|                   | Data Flag Branch Register                   |           |

|                   | Central Processor Interrupt Register        |           |

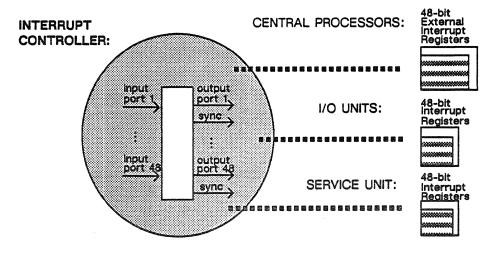

|                   | Interrupt Network                           |           |

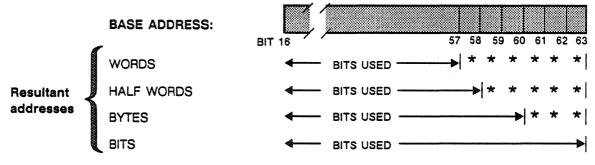

|                   | Machine Addressing                          |           |

|                   | Using Floating Point Numbers and Arithmetic |           |

|                   | Error Management in the Central Processor   |           |

|                   | Master Clock                                |           |

|                   | Timers and Counters                         |           |

|                   | Instrumentation Counters                    | 5–55      |

| System Memories   | · · · · · · · · · · · · · · · · · · ·       | Section 3 |

| -                 | Central Processor Memory                    | 5–58      |

|                   | Virtual-to-Physical Addressing              |           |

|                   | Central Processor Memory Protection         |           |

|                   | Central Processor Memory Interface          | 5–71      |

|                   | Shared Memory                               |           |

|                   | Shared Memory Interface                     |           |

|                   | Communication Buffer                        |           |

|                   | Communication Buffer Interface              |           |

| The ETA10 Instru  | uction Set                                  | Section 4 |

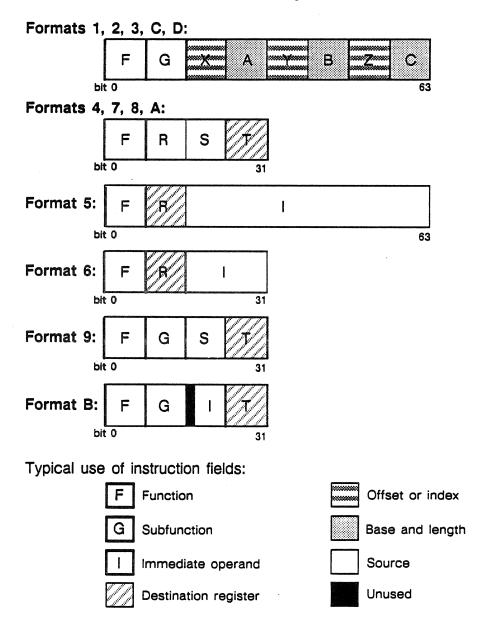

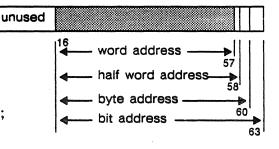

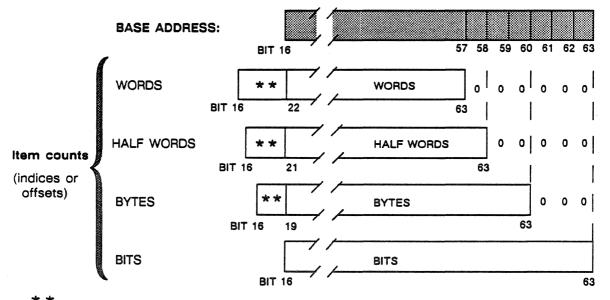

|                   | Instruction Formats                         | 5–93      |

| Addressing                            | 5–95  |

|---------------------------------------|-------|

| Illegal Instructions                  | 5–98  |

| Scalar Instructions                   | 5-100 |

| Vector Instructions                   | 5-101 |

| Sparse Vector Instructions            | 5-103 |

| Functional Categories of Instructions | 5-104 |

#### The I/O Subsystem

#### Chapter 6

|              | Ubsystem       Section 1         cture       6-6 |

|--------------|--------------------------------------------------|

| I/O Software |                                                  |

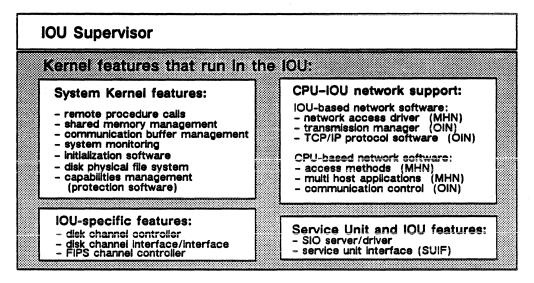

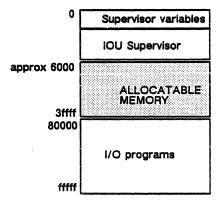

| IOU Supervi  | sor                                              |

| Operating Sy | ystem Kernel Features                            |

| I/O Channel  | Software                                         |

| Disk Channe  | el Software                                      |

| FIPS 60-2 C  | hannel Software                                  |

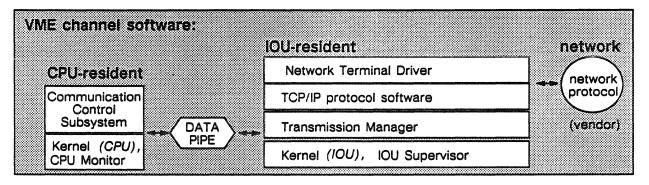

| VME Chann    | el Software                                      |

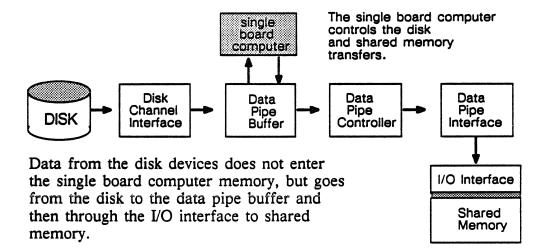

| Disk Input/C | Output                                           |

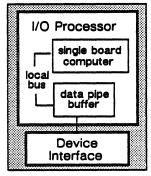

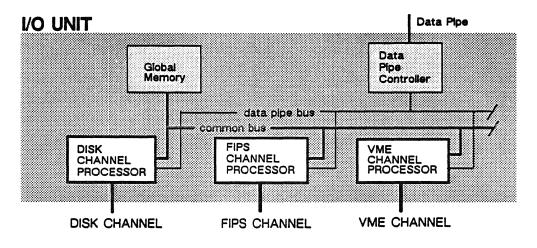

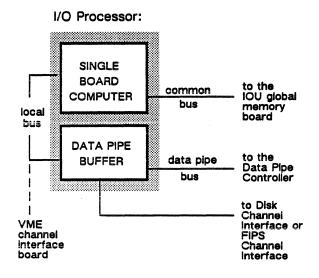

| I/O Hardware | Section 3                                        |

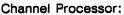

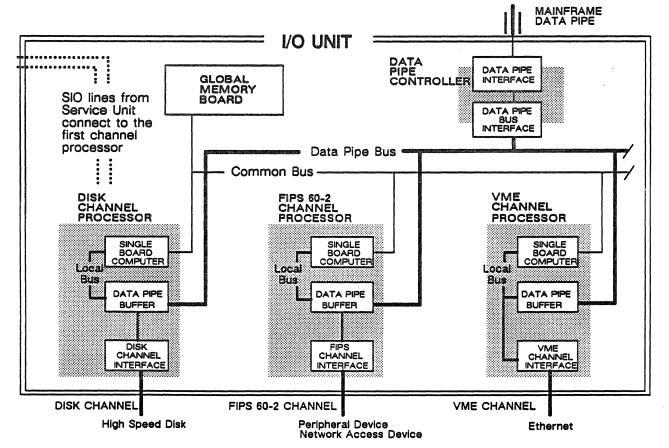

| I/O Processo | r Components                                     |

| The IOU Co   | nnection to the Data Pipe 6-36                   |

| The I/O Inte | rface to Shared Memory 6-39                      |

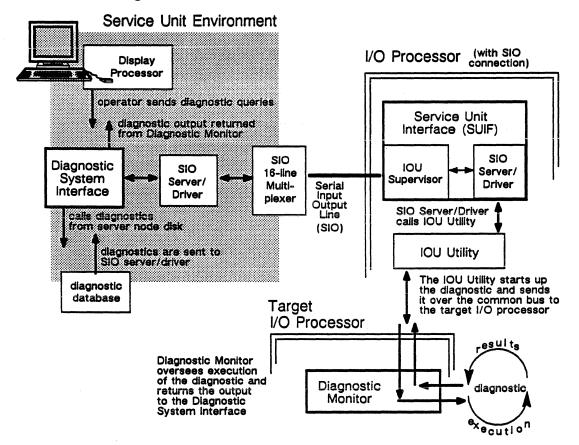

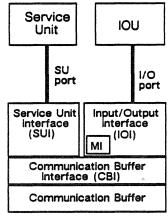

| IOU Connec   | tions to the Service Unit                        |

| IOU Bus Are  | chitecture                                       |

| The IOU Ch   | assis                                            |

#### Networks

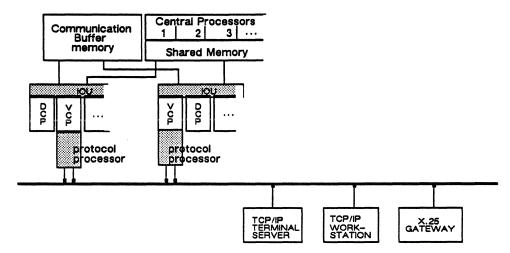

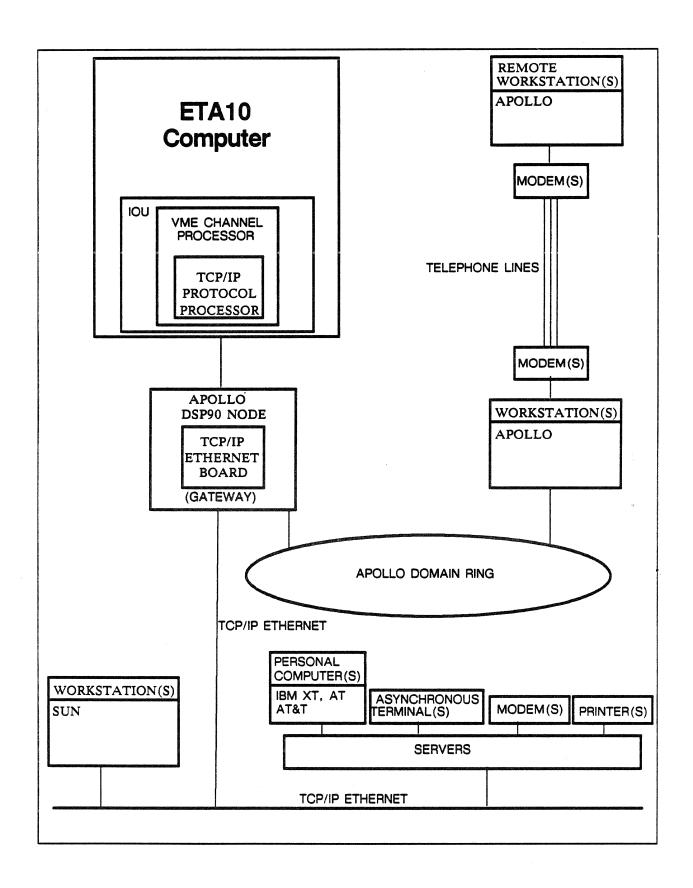

| The | Open Interconnection Network Section 1            |

|-----|---------------------------------------------------|

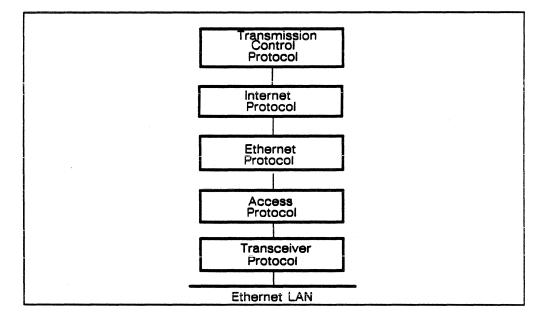

|     | TCP/IP and CSMA/CD Communication Protocols        |

|     | Typical ETA10 OIN Configuration                   |

|     | The OIN Hardware Components                       |

|     | How the VME Channel Processor Controls the OIN    |

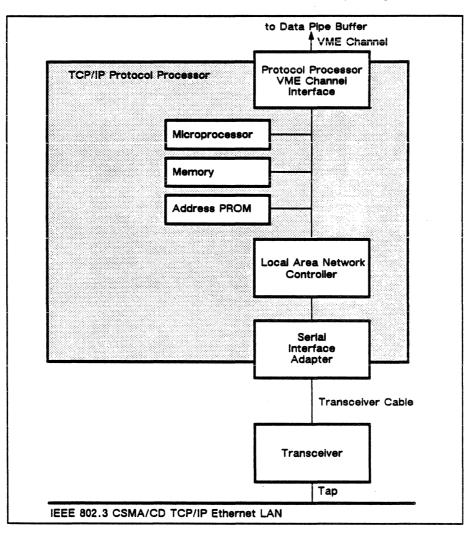

|     | TCP/IP Protocol Processor Components              |

|     | Five Levels of OIN Communication Protocols        |

|     | How Users Access the ETA10 through the OIN        |

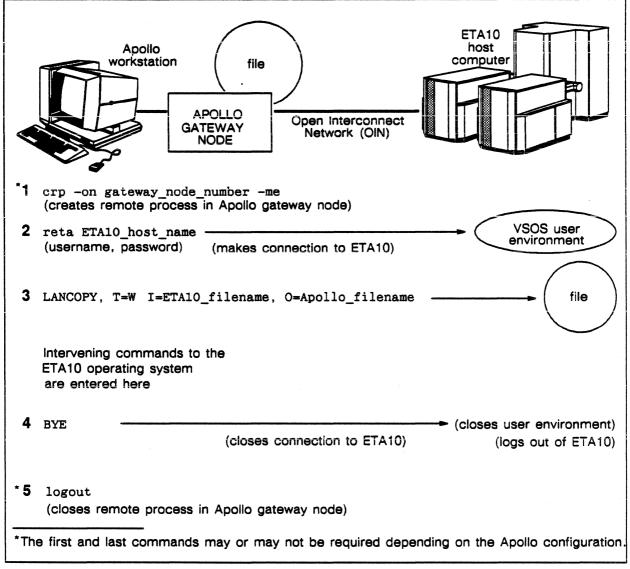

|     | Five Commands from an Apollo Workstation          |

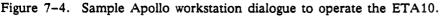

|     | ETA10 Software for the OIN                        |

|     | Transmission Manager and TCP/IP Protocol Software |

|     | The OIN-Related Software Residing in the CPU      |

|     |                                                   |

| Management of OIN Equipment                            | 7–19      |

|--------------------------------------------------------|-----------|

| Reliability of ETA10 Network Services                  | 7–20      |

| The Loosely Coupled Network                            | Section 2 |

| Computers and Software that Connect to the LCN         | 7–22      |

| How the Remote Host Facility Is Used to Transfer Files | 7–24      |

| Using the MFLINK Command                               | 7–25      |

| ETA10 Process Flow for the Loosely Coupled Network     | 7–26      |

| Five Levels of LCN Communication Protocols             | 7–27      |

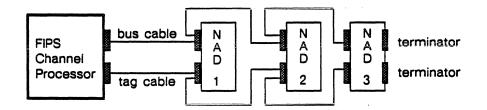

| NADs Connect LCN Hosts to Network Trunk Cables         | 7–28      |

| How the FIPS Channel Processor Controls the LCN        | 7–31      |

| The Hardware Components of the LCN Trunk               | 7–31      |

| ETA10 Software for the Loosely Coupled Network         | 7–33      |

| ETA10 Software for the LCN that Resides on the CPU     | 7–35      |

| Additional ETA10 Software for the LCN                  | 7–39      |

| Management of LCN Equipment                            | 7–41      |

#### Peripherals: Disk Drives

#### Chapter 8

Chapter 9

Chapter 10

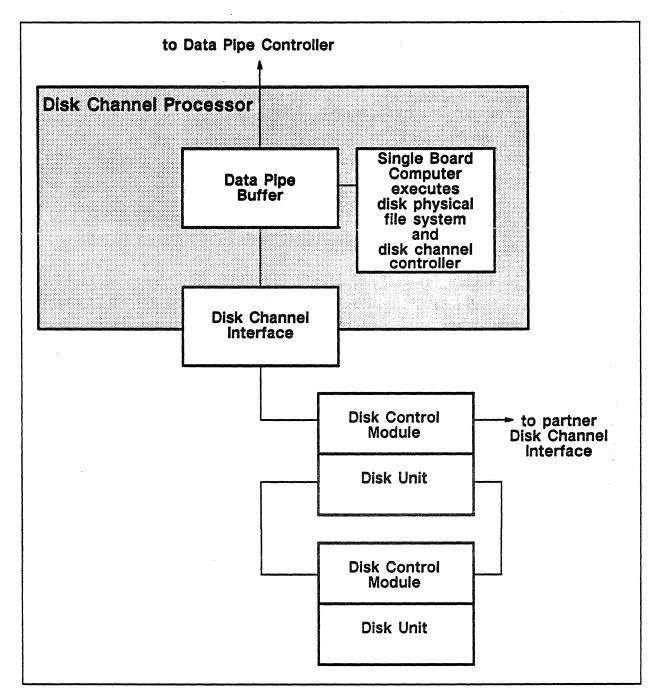

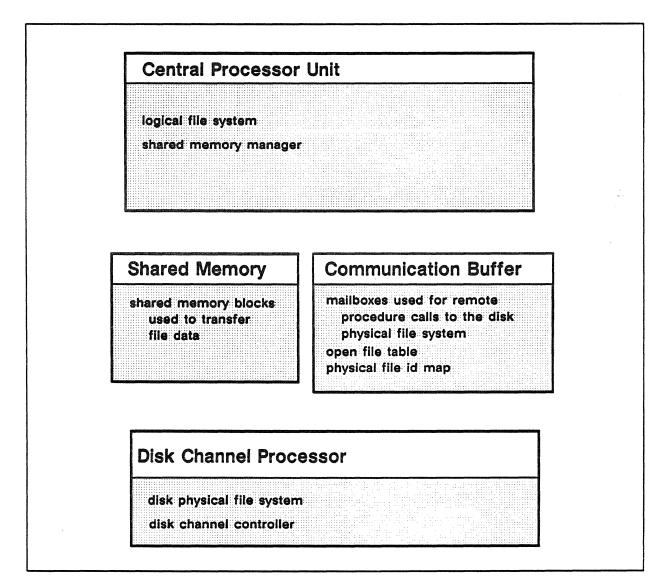

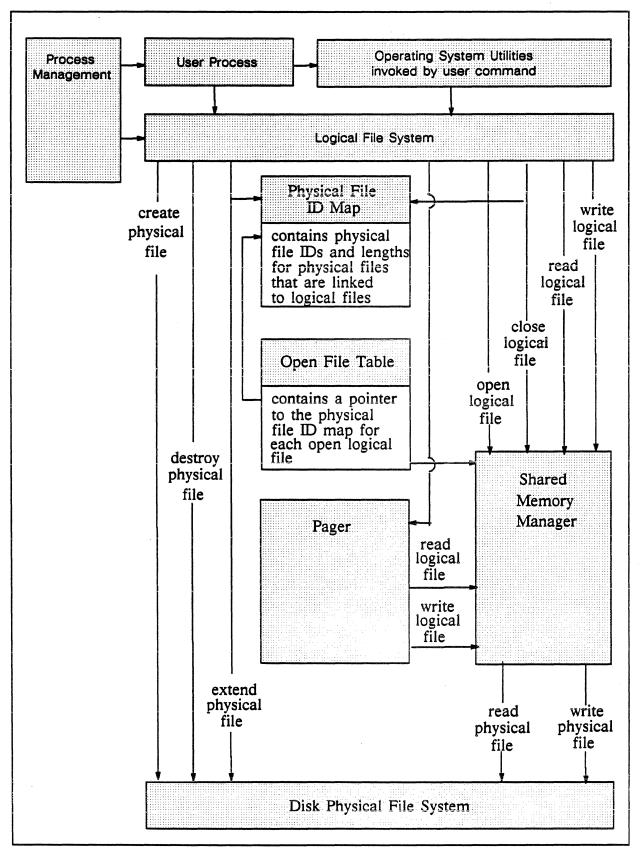

| Disk Physical File Structure            | 8–2  |

|-----------------------------------------|------|

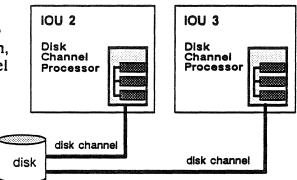

| Hardware Components and the Disk System | 8-4  |

| Interface to the Disk System            | 8–9  |

| Disk System Performance                 | 8–15 |

| Disk System Management                  | 8–16 |

#### Service Unit Features and Functions

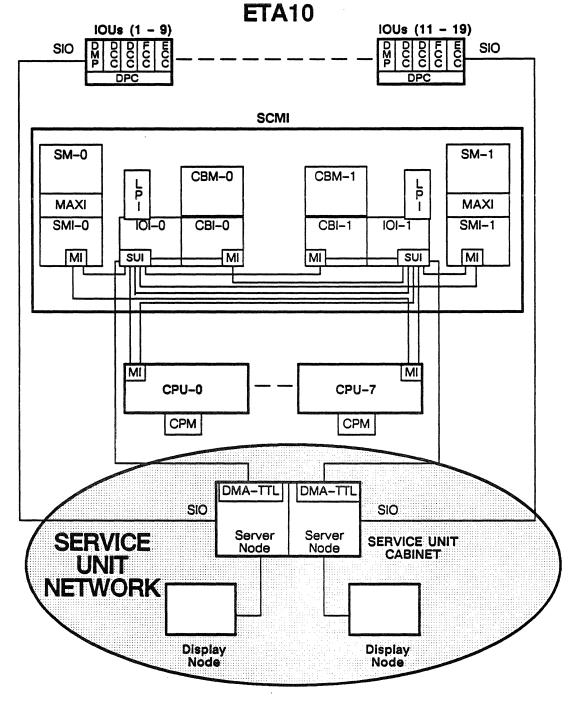

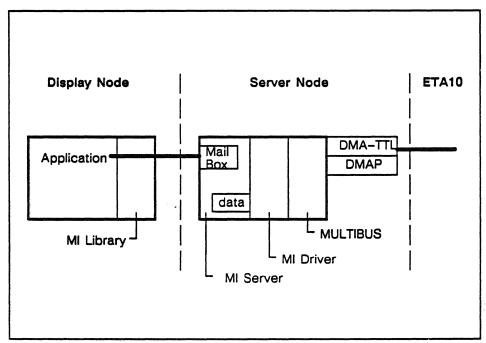

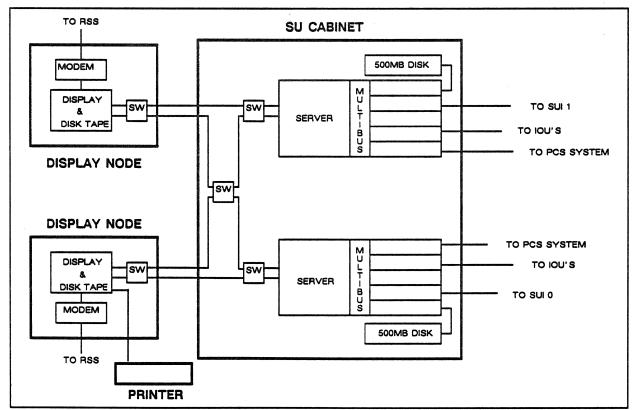

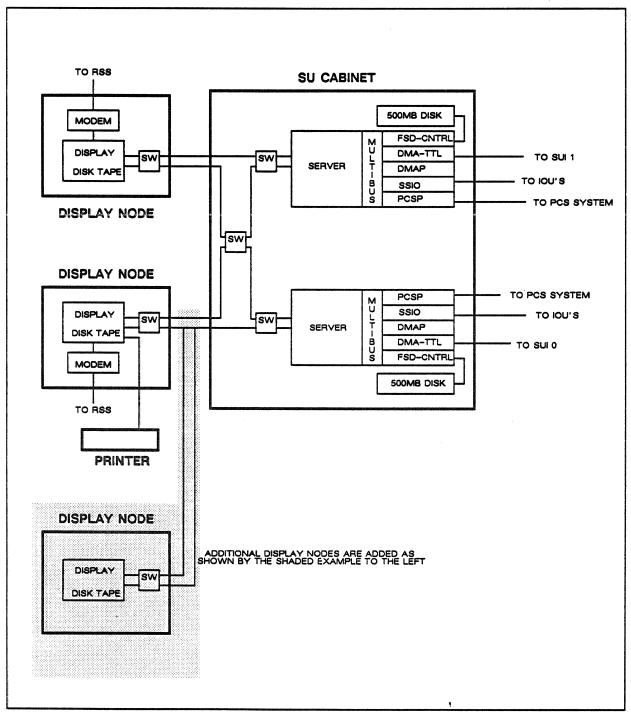

| The SU Network – An Overview          | 9–2  |

|---------------------------------------|------|

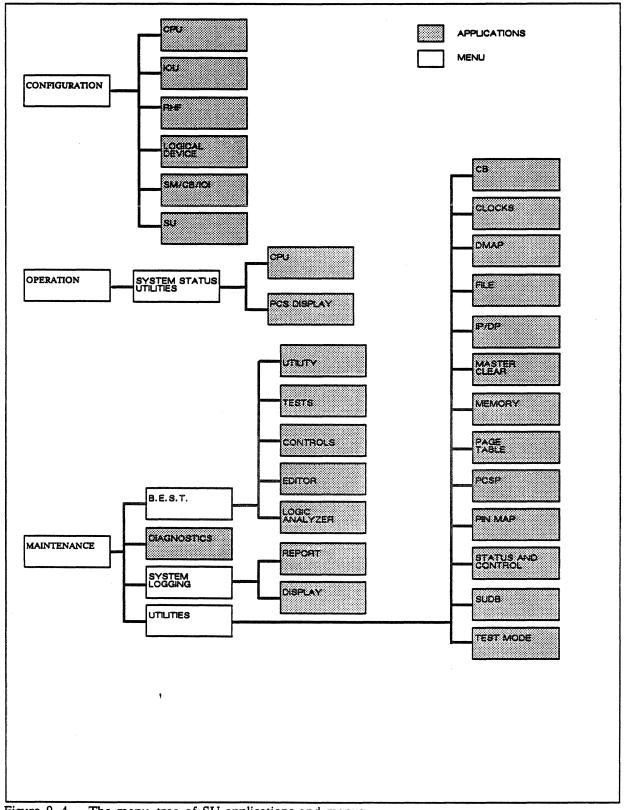

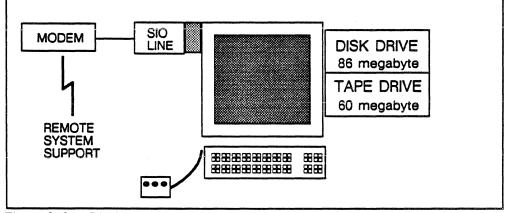

| The Service Unit Operator Environment | 9–6  |

| SU Hardware Components                | 9–9  |

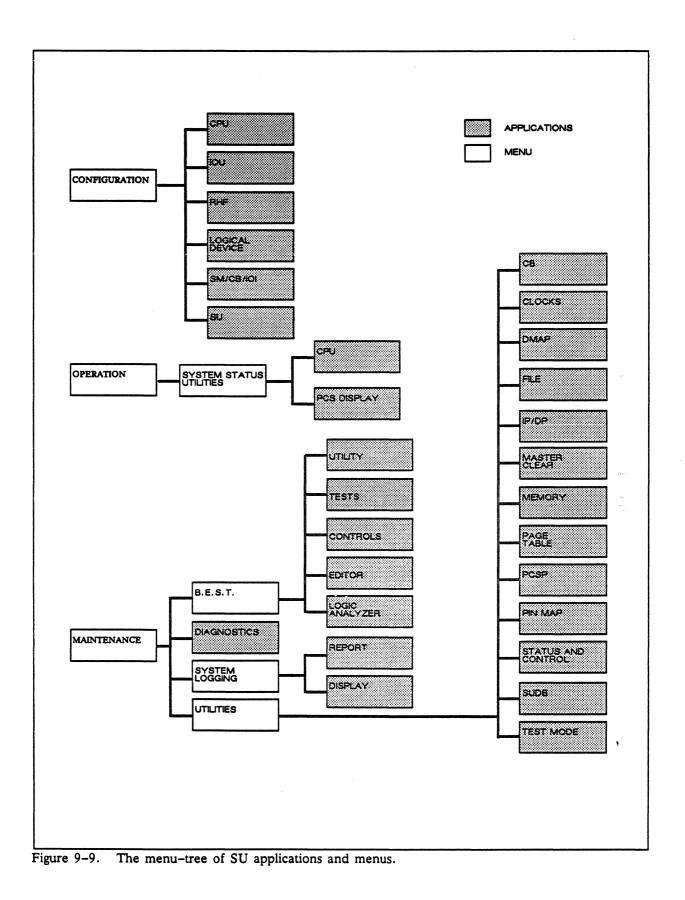

| Service Unit Applications             |      |

| The SU Support Processes              | 9–41 |

#### Power and Cooling Systems

| The Cryogenic System             | 10-2  |

|----------------------------------|-------|

| Refrigeration System             | 10-12 |

| Power Distribution System        | 10-14 |

| The Power and Cooling Supervisor | 10-18 |

| Glossary                  | Glossary-1 |

|---------------------------|------------|

| Referenced Documents List | Ref.Doc1   |

| Index                     | Index–1    |

#### Purpose

The ETA10 System Reference Manual is a detailed overview of the ETA10's architecture and major features. It is not meant to repeat specific, operations-oriented information from other ETA Systems reference documents. The level of complexity is appropriate for system analysts who want comprehensive descriptions of hardware components and operating system functions. It is suitable for training courses providing general orientation on the ETA10 system. Readers wanting support for hands-on use of the system should refer to "Related Documents" later in this section.

This edition (Revision A) describes Release 1, Version 1.0 of EOS, the ETA10 operating system, and its VSOS user environment.

#### **Intended Audience**

This manual is intended for system analysts and experienced users as well as for administrators, trainers, students, and system evaluators.

#### How This Document Is Arranged

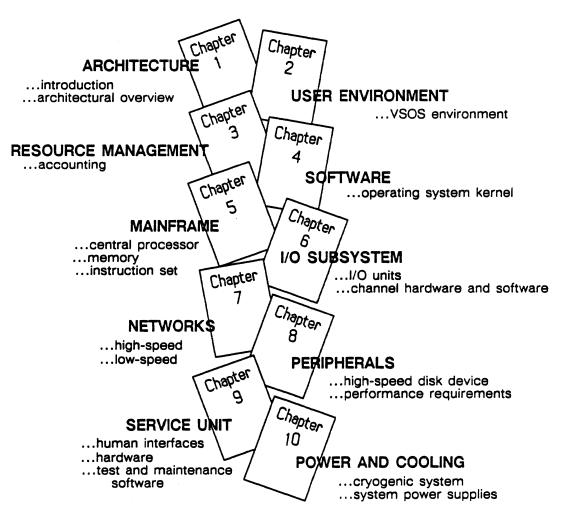

This document contains ten chapters, a glossary, and an index. A general table of contents at the beginning of the manual is augmented by detailed tables of contents at the start of each chapter.

Chapter 1: Introduction to System Architecture provides a brief overview of the ETA10 computer system: its architecture, hardware and software components, and model range. The reader is directed to more detailed discussions of each subject later in the manual.

Chapter 2: The User Environment describes VSOS, programming environment of the ETA10 operating system EOS.

Chapter 3: Resource Management describes system configuration, resource allocation, and management of users and user sessions.

**Chapter 4: Operating System Kernel** the monitor, and supervisors, distributed collection of features that make up the kernel of EOS Release 1, Version 1.0.

Chapter 5: The Mainframe Components describes the ETA10's CPU architecture and instruction set, system memories, interfaces, and transfer mechanisms.

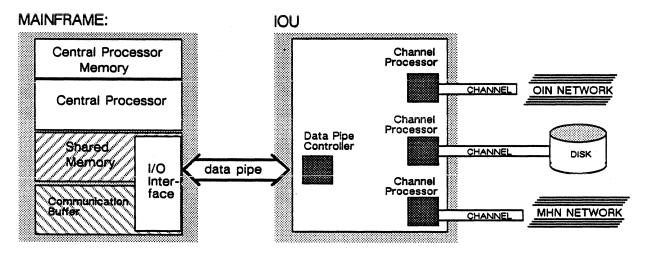

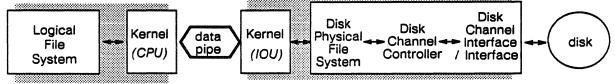

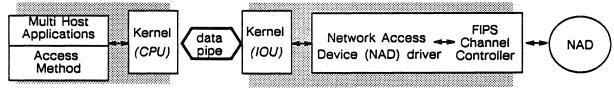

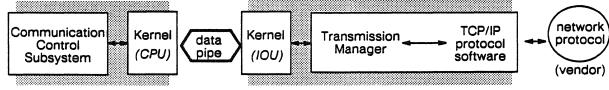

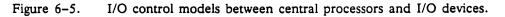

Chapter 6: The Input/Output Subsystem describes I/O interface architecture, I/O unit (IOU) hardware and software, as well as the disk storage system, channels, and interfaces.

**Chapter 7: Networks** describes two networks supported by the ETA10: a local area network and a network supporting communications with remote hosts.

Chapter 8: System Peripherals describes the ETA10's disk storage peripherals.

Chapter 9: Service Unit Features and Functions describes the hardware components, support software, applications, file system, network, and operator environment of the service unit (SU).

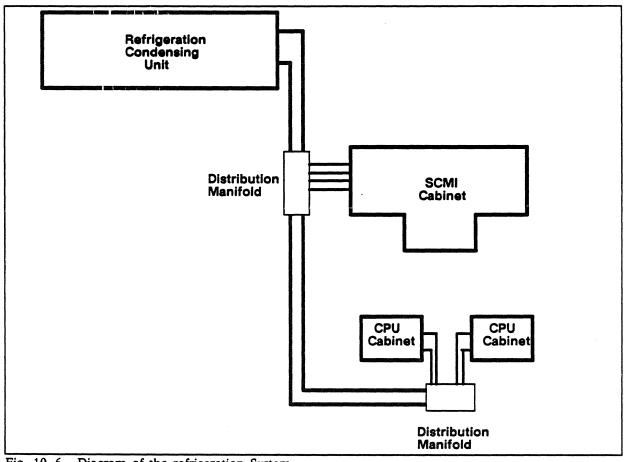

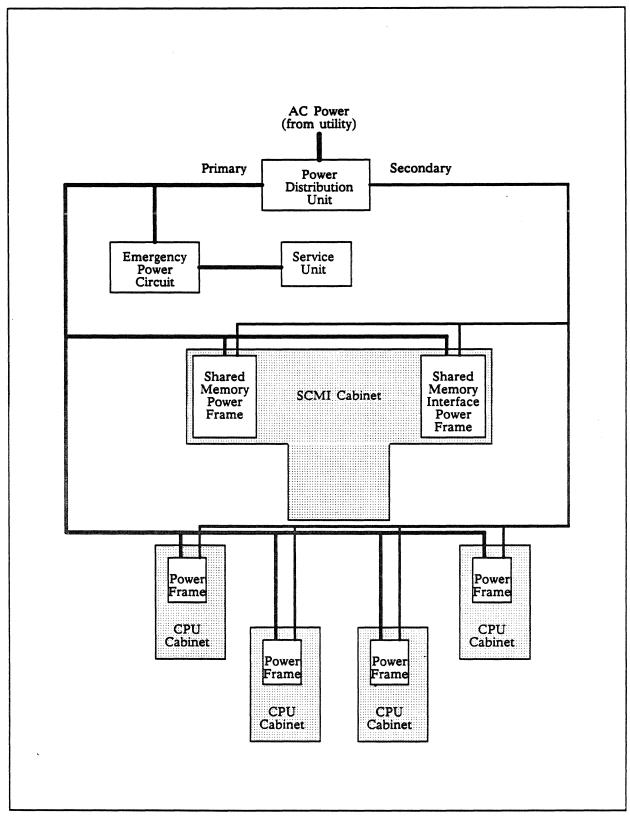

Chapter 10: Power and Cooling Systems describes the cryogenic, refrigeration, and power systems.

The final component of the manual includes a glossary, a bibliography, and an index.

#### How to Use This Document

The general table of contents covers major subjects. More detailed tables of contents at the beginning of each chapter include lists of figures and tables. A glossary and an index appear at the end of the manual.

#### **Conventions Used in This Document**

An attempt has been made in this manual to expand the acronyms used in developmental documentation; e.g., "CPM" becomes "CP memory" or "central processor memory", "IOU" becomes "I/O unit", and so on. However, developers' acronyms are retained in diagrams and descriptions where they are most suitable.

#### **Related Documents**

The following ETA Systems publications are useful supplements to the System Reference Manual. The System Overview is a good introduction, and the manuals on VSOS and support tools give information (especially command and parameter descriptions) in greater detail than in this manual, which is meant as a conceptual rather than a hands-on guide.

- PUB-1006 ETA-10 System Overview

- PUB-1118 Support Tools: Utilities, Debugger, B.E.S.T.

- PUB-1119 Support Tools: Diagnostics

- PUB-1051 VSOS Environment Reference Manual: Concepts and Commands

- PUB-1084 VSOS Environment Reference Manual: System Interface Library Calls

.

.

## Chapter

## **Introduction to the System Architecture**

#### **Chapter Contents**

| Overview of the System Components            | Section 1 |

|----------------------------------------------|-----------|

| Guide to the Chapter Contents in this Manual | 1–2       |

| Super-cooled Systems                         | 1–3       |

| Air-cooled Systems                           | 1–3       |

| Operating Software                           | 1–4       |

| Processor-Specific Monitor and Supervisors   |           |

| EOS Kernel                                   | 1–4       |

| Applications Software                        | 1–5       |

| System Architecture                          |           |

| Architectural Overview                       | 1–6       |

| Hardware and Software Integration            | 1–7       |

| Computational Architecture                   | 1–7       |

| Machine Arithmetic                           | 1–8       |

| The Instruction Set                          | 1-8       |

| Memory Architecture                          | 1–8       |

| Memory Hierarchy                             | 1–9       |

| Shared Memory                                | 1–9       |

| Input/Output Architecture                    | 1–9       |

| Network Architecture                         | 1–10      |

| Low-Speed Network                            | 1–10      |

| High-Speed Network                           | 1–10      |

| The ETA10 Model Range                        |           |

| Cooling Options                              | 1–11      |

| Redundancy Options                           | 1–12      |

| Multiple Components                          | 1–13      |

| Redundant Components                         | 1–13      |

| Redundant Connections                        | 1–13      |

## Chapter

### **Introduction to the System Architecture**

#### In This Chapter . . .

Chapter 1 serves as the introductory chapter in this reference manual for the ETA10 supercomputer. As a system reference, the manual provides a functional description of the system, describing the hardware and software both as discrete components and as parts of an integrated system.

Section 1 introduces the two basic models of the ETA10 system and their major components. Section 2 is an architectural overview of the components, and a guide to the chapters that describe them. Section 3 discusses the range of ETA10 models and their cooling and redundancy options.

Section 1: Overview of the System Components

- Guide to chapter contents

- Introduction to super-cooled and air-cooled systems

- Section 2: System Architecture

- Overview of computational, memory, I/O, and network architectures

- References to chapter contents

#### Section 3: ETA10 Model Range

- Cooling options for model range

- Redundancy options for model range

## Section 1: Overview of the System Components

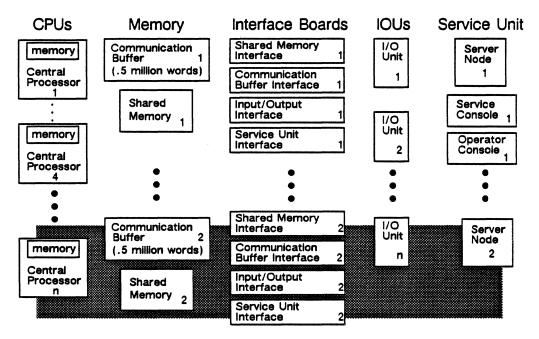

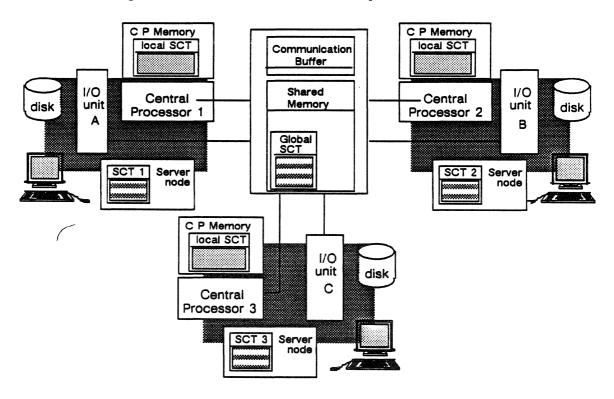

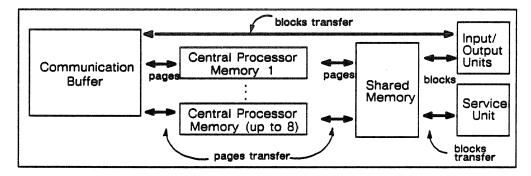

An ETA10 system is comprised of the following components:

- one to eight central processing units

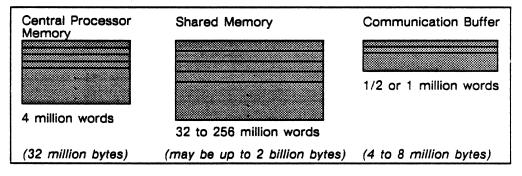

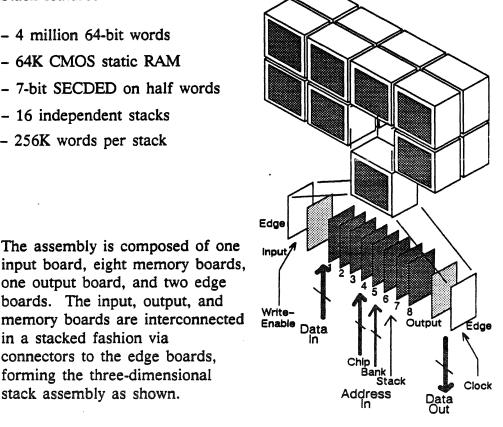

- 4-million word central processor memories, a large shared memory, and a communication buffer

- one to eighteen input/output units

- service unit for system maintenance and control

- power and cooling support appropriate for model

- distributed set of operating software

- set of user environment and application software

#### Guide to the Chapter Contents in this Manual...

#### Super-cooled Systems

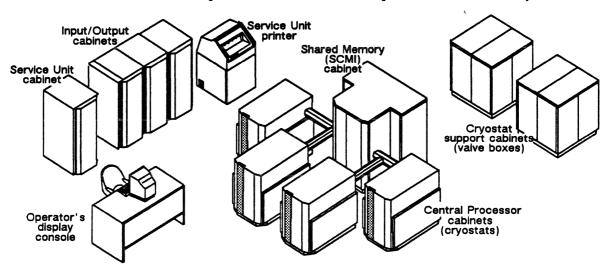

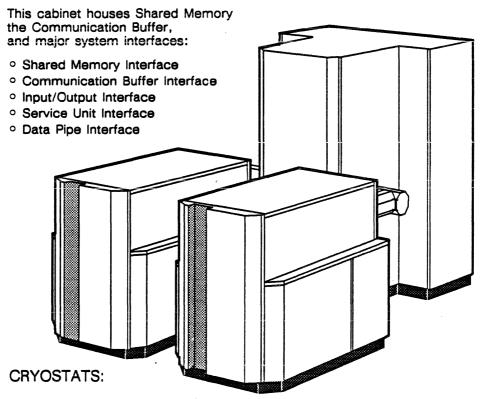

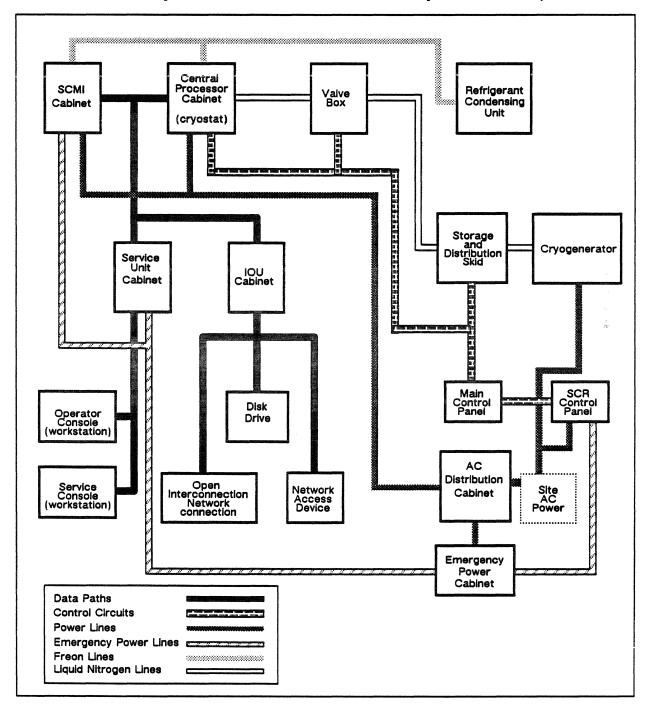

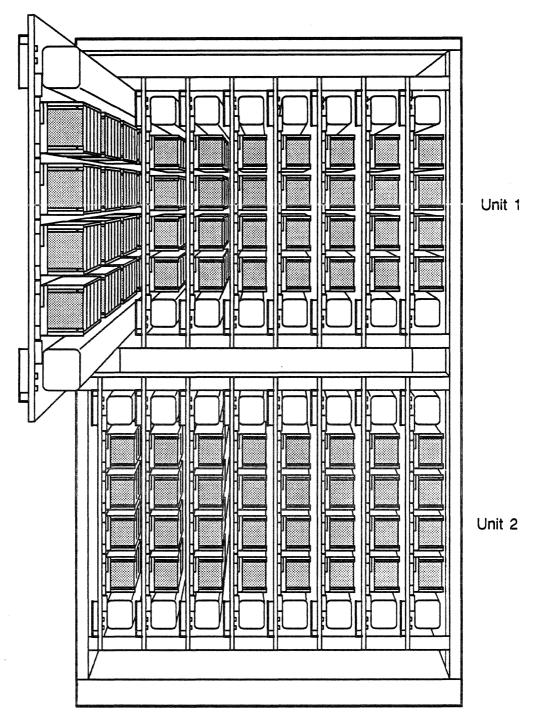

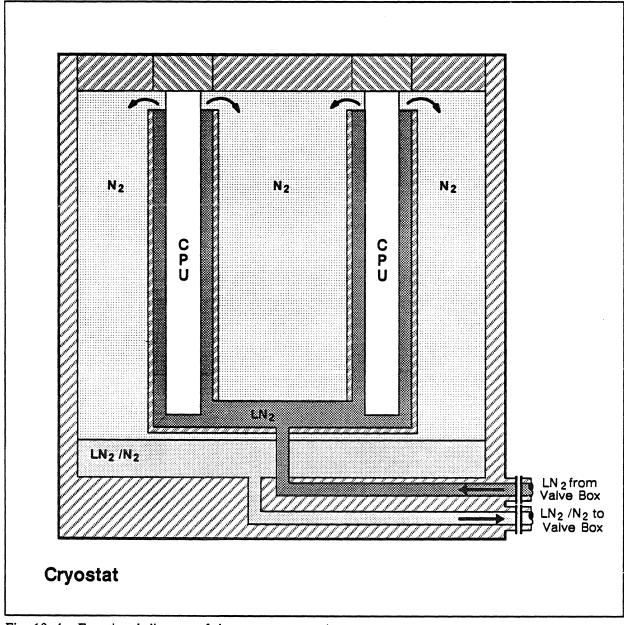

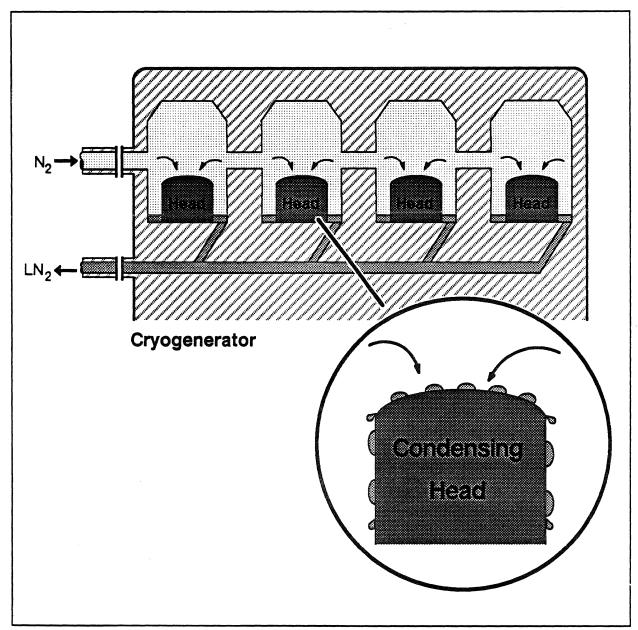

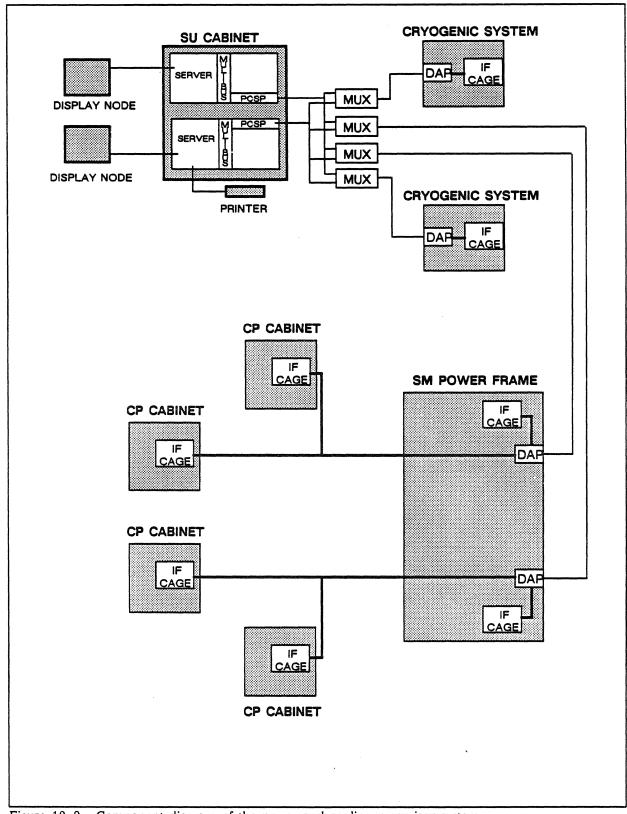

Here is a computer-room view of a super-cooled ETA10 system:

Figure 1-1. Computer-room view of super-cooled ETA10 system with four to eight processors.

In the center are the super-cooled central processors in their cryogenic housings, the cryostats. Since one or two processors may be contained in each cryostat, this can be a four-to-eight processor system. The central processing units directly access the shared memory housed in the tall cabinet behind and connected to the cryostats.

Cryogenic support cabinets provide mechanical controls for the cryostats, and are installed nearby. The I/O units and the service unit components are individually housed in identical cabinets. Also shown is an operator console with its display workstation; there may be several of these workstations networked with the service unit.

### Input/Output cabinets Service Unit cabinet Operator display consol ETA10 Cabinet Printer

**Air-cooled Systems**

In contrast, the computer room-view of an air-cooled ETA10 is markedly different. One or two air-cooled central procesors, the memory, and the system interfaces are all packaged within a single cabinet.

I/O units, the service unit cabinet, printer, and an operator's console with its display workstation are shown here with the air-cooled ETA10 cabinet.

Figure 1–2. Computer-room view of a single processor air-cooled ETA10 system.

PUB-1005 Rev. A Although the models differ externally, internal views of both air-cooled and super-cooled ETA10 systems are identical. The architectures are the same: fast central processors, a large virtually addressed local memory, large second-level shared memory, wide bandwidth I/O transfers, and a distributed operating system. This manual describes the super-cooled ETA10 models.

#### **Operating Software**

The ETA10 operating system, EOS, has three components:

- processor-specific core software

- system-wide kernel features

- applications software supported by the first two categories

#### **Processor-Specific Monitor and Supervisors**

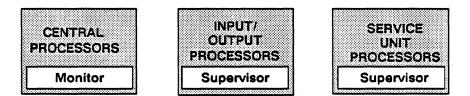

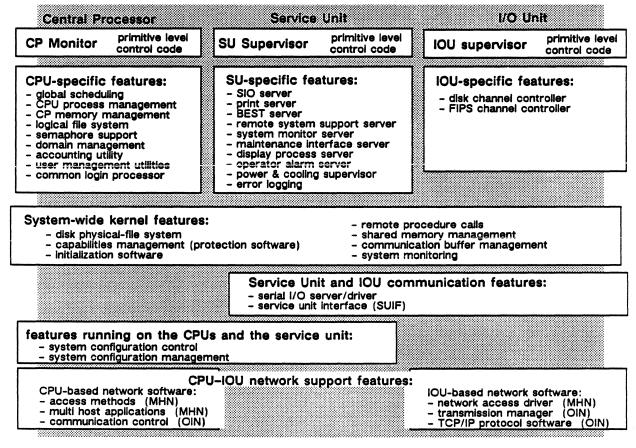

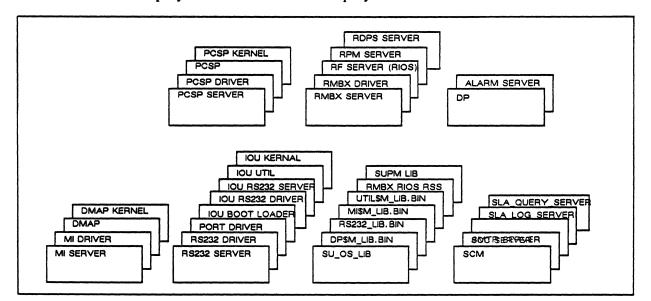

Each type of system processor has its own software to provide its basic, low-level functions: the mainframe central processor has monitor software that runs in monitor mode. The 68020 processors in both the service unit and the I/O processors have individualized supervisor software that runs in supervisor mode.

#### **EOS Kernel**

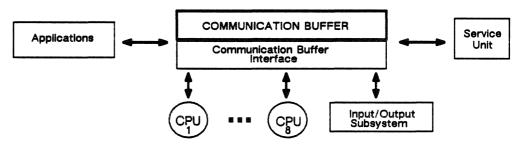

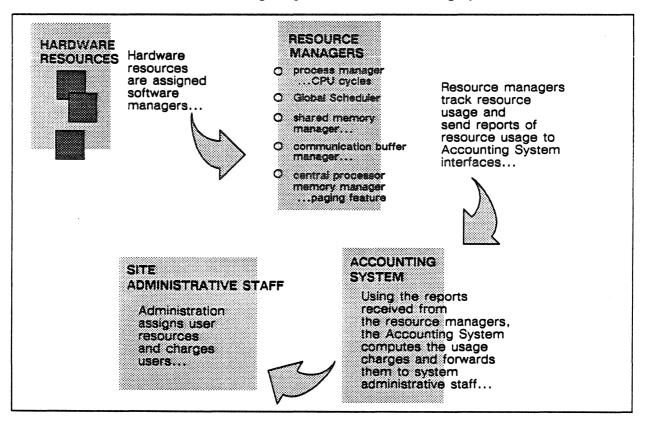

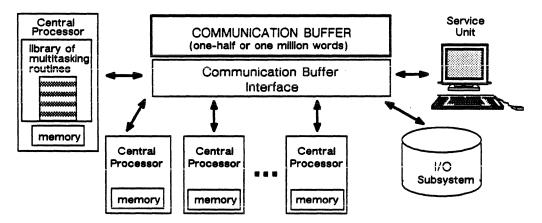

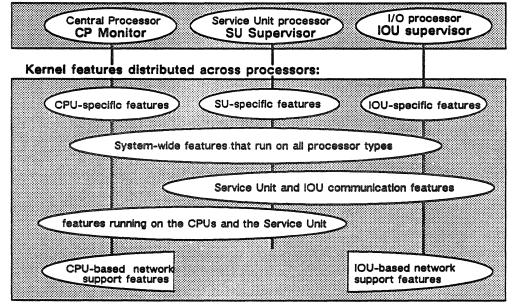

The kernel level of EOS is distributed across the entire hardware system. Portions of the kernel coordinate activities among system processors, and manage the memory hierarchy to balance demands of the computational engine with wide bandwidth I/O from peripheral disk and network systems. Kernel features coordinate among processors to manage memories, I/O capabilities, and system maintenance/communication functions.

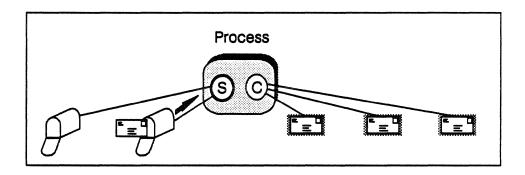

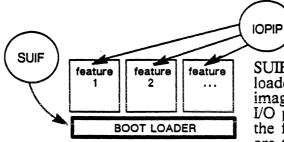

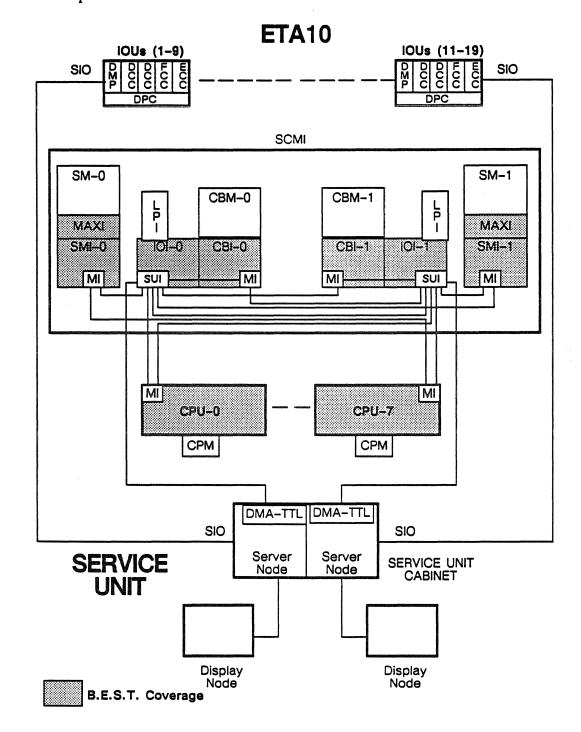

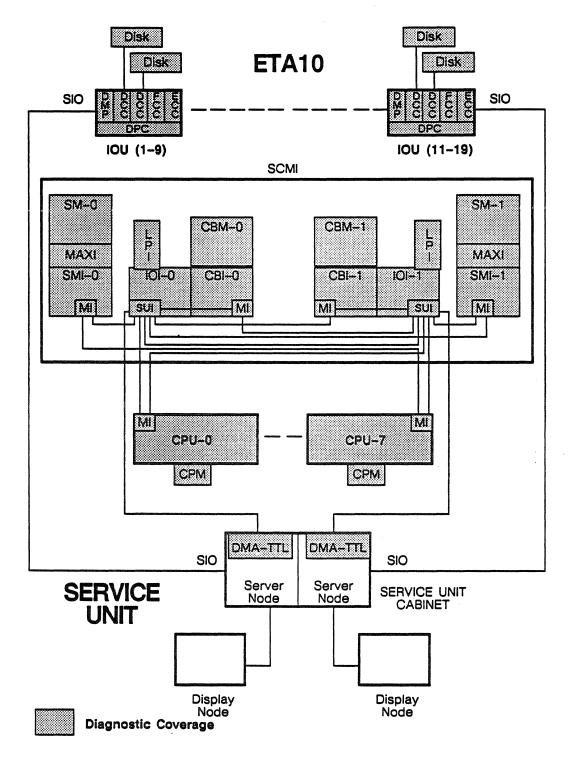

Figure 1-3. The EOS kernel is distributed across system hardware.

Kernel features perform a wide range of functions. The logical file system provides implicit and explicit I/O. Process management controls the multitude of processes active on each central processor. Domain management software provides efficient access to system operating code and routines without resorting to process switching. Interprocess communication uses the communication buffer to create and control semaphores that coordinate activities among central processors. Remote procedure calls enable the three types of system processors to communicate with each other. Memory managers coordinate the multi-level hierarchy of system memories. Another set of features provide system scheduling, monitoring, accounting, and control functions.

#### **Applications Software**

The applications software is supported by the first two categories. It includes the VSOS user environment, system and special libraries, compilers and debuggers, system utilities, and development and vectorizing tools.

## Section 2: System Architecture

The ETA10 implements a balanced architecture characterized by parallelism throughout its high-speed processing, addressing, and data transfer operations. The multi-pipelined computational engine is balanced by extremely fast I/O, and by a nearly unlimited virtual memory space to support the multitude of requests coming from high-speed disks and multi-user local area networks.

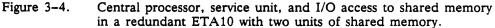

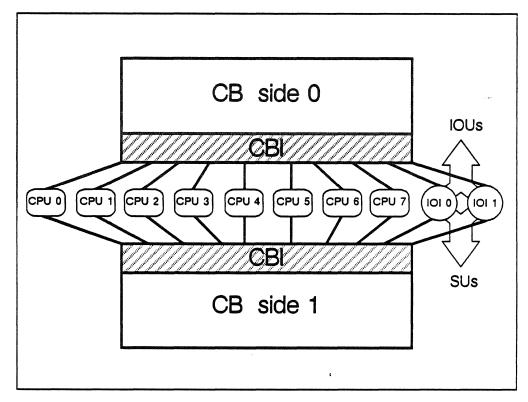

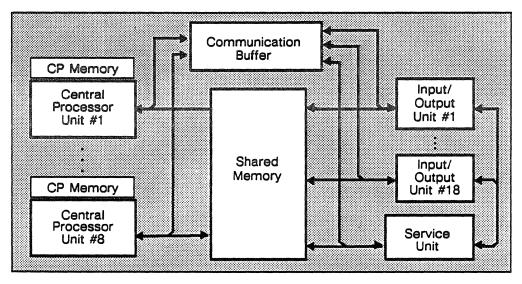

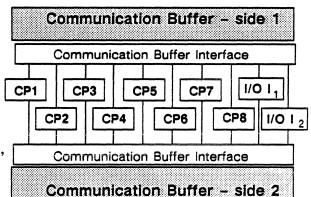

The ETA10 is a fully distributed processing machine; work is spread throughout the system in such a way that central processors execute, I/O processors move data, the service unit monitors performance, all done simultaneously. Central processors dedicated to execution are balanced by independent I/O and service unit processors that perform other necessary but non-computational system work. The addition of the communication buffer enables the central processors to efficiently share and multiprocess data as well as to manage complex system resources.

#### Architectural Overview

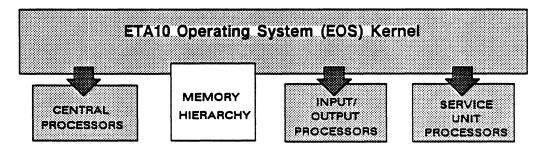

At the heart of the ETA10 system is a high bandwidth shared memory that satisfies the data demands of vector processors and high-speed I/O transfers to disks and networks.

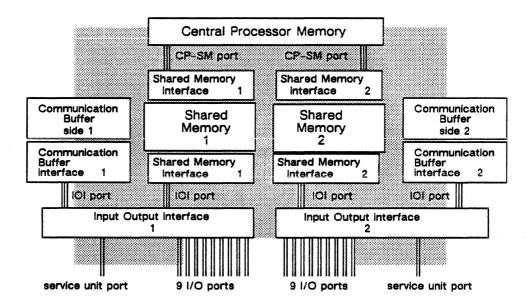

Figure 1-4. System components of the ETA10.

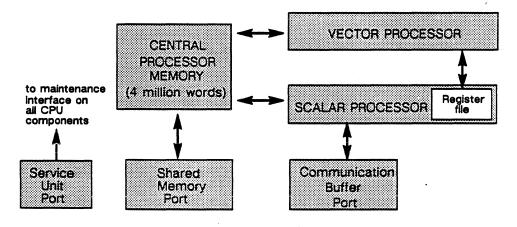

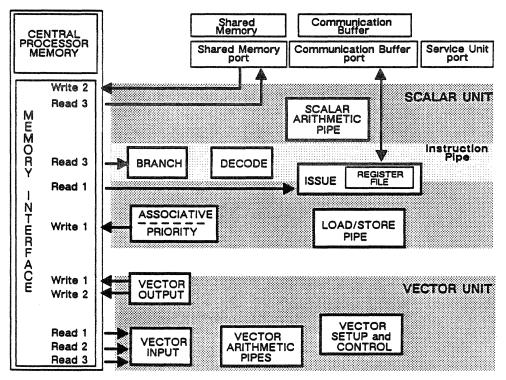

Each central processor has both a scalar unit and a double-pipelined vector unit that supply the computational power in the system. The data needs of these very fast processors are met by four million words of virtually addressed memory and ample system bandwidths. Shared memory makes direct transfer to the local central processor memory. The shared memory allows large blocks of data to be moved efficiently to central processor memories. I/O bandwidths allow data transfers to/from peripherals at high rates.

#### Hardware and Software Integration

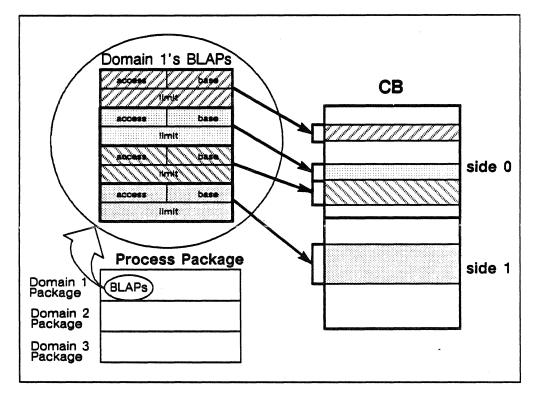

Within the ETA10, hardware and operating system components execute programs concurrently, supported by large memory bandwidths and parallel processing capabilities. Software maximizes hardware resources by keeping several user programs in shared memory at the same time, rapidly switching the processors between programs as priority and data availability dictate. Hardware and software combine to provide parallel protection schemes: protection between programs, protection between processes, and protection within processes.

The operating system plays a major role in managing memory and controlling memory contention. The operating system must distribute data over the large shared memory so as to make the data quickly and readily accessible when requested.

Chapter 2 describes the VSOS user environment. Chapter 4 covers the main part – the kernel – of EOS (the ETA10 Operating System). System resource management is discussed in Chapter 3.

#### **Computational Architecture**

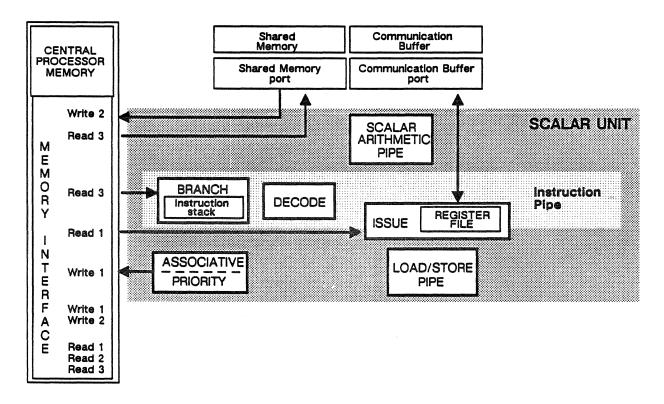

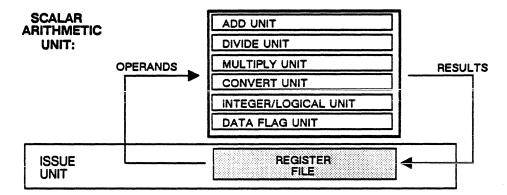

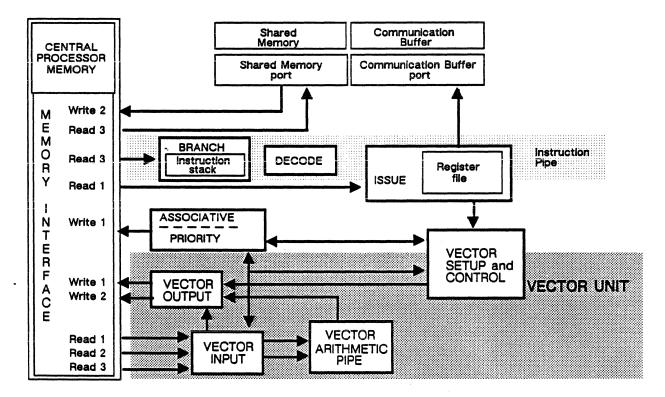

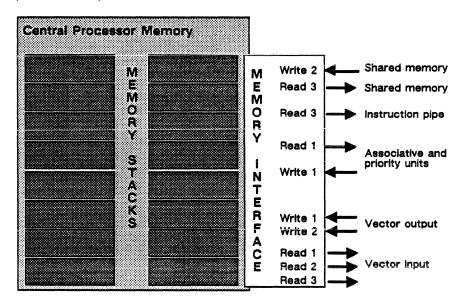

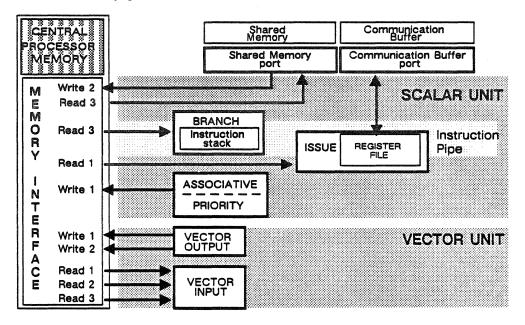

Central processor operations overlap with shared memory data transfers. Once the transfers from shared memory are started, data moves to the processor at one 64-bit word per clock cycle. Transfers can be made at this rate per cycle to five processors at once or, in redundant systems, to all eight processors.

Central processor memory moves eight 64-bit words per clock into the processor. The central processor has a scalar unit and twin vector pipelines that operate totally in parallel, the scalar unit producing one result per clock cycle, the vector unit producing two 64-bit results or four 32-bit results per cycle.

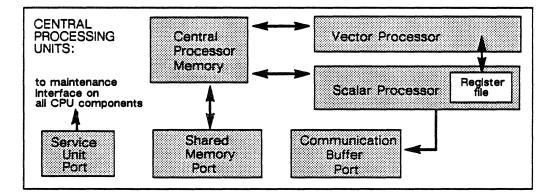

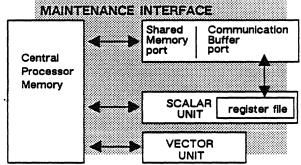

Figure 1-5. Components in the ETA10 central processing unit.

Vector operations can be overlapped, allowing a vector operation to be starting while another is completing. This overlap improves the performance of short vector operations.

#### **Machine Arithmetic**

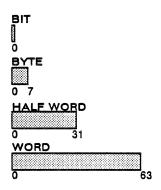

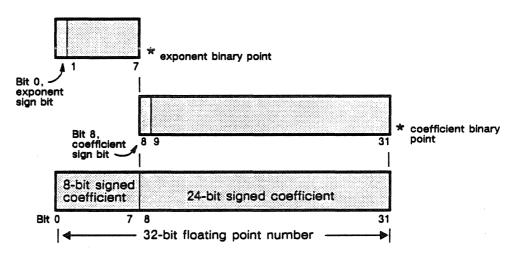

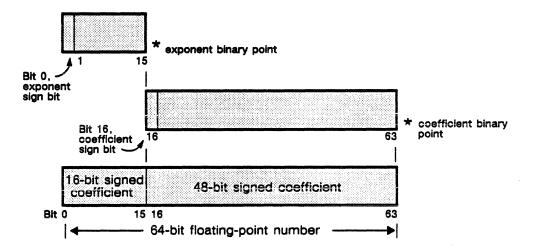

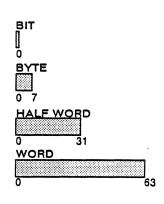

A twos complement binary number system is used in ETA10 arithmetic operations. Floating point operations use twos complement arithmetic in formats for both full and half words. Full words have 64 bits, half words have 32. The benefit of using 32-bit words is that two pieces of data can be put in the same space; also, a vector processor processes twice as many 32-bit operands in the same amount of time. In the 48-bit coefficient of a full 64-bit word, numbers are precise to 14 decimal digits; in the 24-bit coefficient of a 32-bit half word, numbers are precise to about 7 decimal digits.

Machine arithmetic is described in Chapter 5, in the "Central Processor Architecture" section.

#### The Instruction Set

The ETA10 architecture uses a large instruction set designed primarily for vector operations. Both the ETA10 instruction set and processor hardware are vector-based; they are not merely extended to provide vector operations. The ETA10 instruction set derives historically from Iverson's *A Programming Language* (APL). The significance of APL is that vectors are inherent to the language rather than additions to it.

The ETA10 instruction set is model independent, and is compatible with Control Data Corporation's CYBER 205 instruction set. It has 256 function codes, 40 of which are unused. The richness of this set is extended by sub-functions that give an instruction additional refinement. Special shared memory instructions manage the queues used in memory-to-memory transfers between central processor memory and shared memory. A group of communication buffer instructions enable the central processors to communicate and share data.

The instruction set is described in Chapter 5, in the "ETA10 Instruction Set" section.

#### **Memory Architecture**

The ETA10 central processor supports a virtual memory system with virtual address space of 2 trillion words. In this system, users request memory rather than manage it; large jobs can be staged without loss in throughput and without involving the user. The system includes very large hierarchical memories. Fewer memory conflicts occur with a hierarchical structure than with systems depending upon a central memory. A hierarchical structure supports large numbers of small jobs as well as very large jobs. Explicit file I/O is also available.

Memory management software is described in Chapter 4, "Operating System Kernel". Memory hardware is described in Chapter 5, in the "System Memories" section.

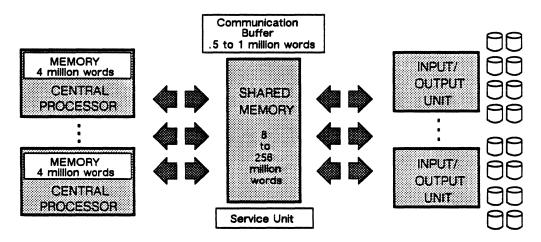

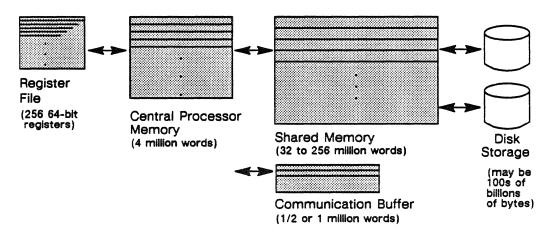

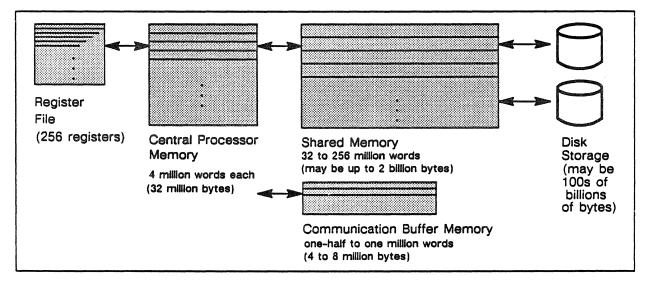

#### **Memory Hierarchy**

At the top end of the hierarchy, speed and ease of memory access are greatest while memory size is smallest. The central processor has a 10 nanosecond access time for the register file; a central processor waits one second for data to be transferred in from an I/O unit. Although memory size increases at the other end of the hierarchy, access time also increases.

Figure 1-6. The ETA10 memory hierarchy.

#### Shared Memory

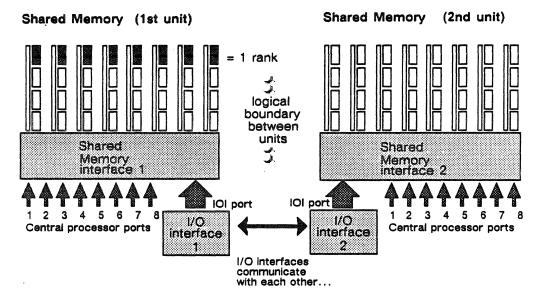

All system processors have access to shared memory. Shared memory serves as the repository for work as it comes into the system, executes, and leaves the system. When programs are multiprocessed, different pages of data are moved from shared memory and sent to different processors. The central processors communicate between themselves using shared memory and the communication buffer to pass messages back and forth to coordinate program execution. The I/O subsystem accesses shared memory to send or receive requests that bring work into the system and that move data out to the disks or networks.

#### **Input/Output Architecture**

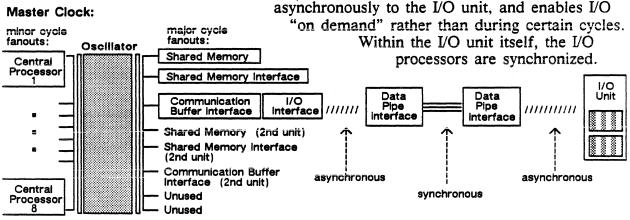

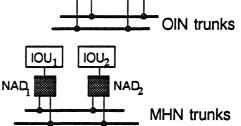

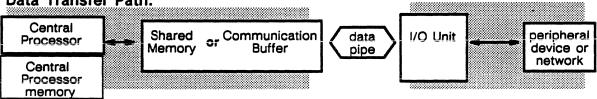

An I/O unit functions in the system as a set of independent, multifunctional channels, able to access both shared memory and the communication buffer. Within each I/O unit, several types of channels interleave high speed transmissions from disk drives and network interfaces. The software architecture distributes most of the I/O functionality within I/O processor-based code. Memory management software resident on the central processors makes and confirms I/O requests. Software required to interface network user programs for processing also resides on the central processors; other network protocol and message packaging software resides on the I/O processors.

I/O hardware and software are described in Chapter 6, "I/O Subsystem". Disk characteristics and requirements are described in Chapter 8, "Peripherals".

#### **Network Architecture**

Both a high-speed and a low-speed network are implemented in the ETA10 system architecture.

#### Low-Speed Network

The first network is workstation-based, and reflects the growing trend for supercomputing "on demand." This is the Open Interconnection Network, a local area network that serves to connect users into the system via a standard mode of access. This network allows users to take advantage of the ETA10's ability to efficiently handle a great many small, interactive sessions. The ETA10 interface to this network provides system access for a large number of network users and ensures reasonable performance and response time. The peak transfer rate across the Ethernet exceeds 1 million bits per second.

#### **High-Speed** Network

The second network is mainframe-based, and reflects the typical use of supercomputers for processing huge amounts of data stored on large systems. This is the Multi-Host Network, a loosely coupled network that connects mainframes rather than users to the ETA10. High-performance mainframes and peripherals are connected to the system over a trunk that achieves a peak transfer rate of approximately 6 million bits per second. The higher performance is required because the work processed via this type of network is large-batch oriented.

Chapter 7, "Networks", describes both types of networks and their interfaces to the ETA10 system.

## Section 3: The ETA10 Model Range

The ETA10 series of supercomputers include two air-cooled models and two super-cooled models. The P and Q series are air-cooled and achieve peak 32-bit performance ranges of 375 to 950 MFLOPS. The E and G series are super-cooled and achieve peak 32-bit performance ranges of 850 to 10,200 MFLOPS. (Peak 64-bit performance is one half the 32-bit performance.)

All ETA10 models are architecturally identical. All models use the same central processor, instruction set, and primary hardware components; all models run under the same operating software and applications set. Performance increments are gained by adding central processors and pluggable memory cards, and by super-cooling central processors.

| This chart compares characteristics of the ETA10 models: | is chart compares characteristics of the | ETA10 models: |

|----------------------------------------------------------|------------------------------------------|---------------|

|----------------------------------------------------------|------------------------------------------|---------------|

| ETA10<br>Model:   | Number<br>of CPUs: | Cycle<br>Time:<br>(ns) | Million Words<br>of Shared<br>Memory:                           | Cooling<br>Method: |

|-------------------|--------------------|------------------------|-----------------------------------------------------------------|--------------------|

| 0.0.000 <u>A.</u> | 4                  | <b>~</b> 4             | 6 61                                                            |                    |

| P                 | 1-2                | 24                     | 8–64                                                            | AIR                |

| P<br>Q            | 1-2<br>1-2         | 24<br>19               | 8-64<br>8-64                                                    | AIR                |

| P<br>Q<br>E       |                    |                        | Contractor (Contractor) → T = T = T = T = T = T = T = T = T = T |                    |

Although ETA10 models are architecturally identical, cooling and redundancy options provide ranges of system performance and availability during failure and maintenance.

#### **Cooling Options**

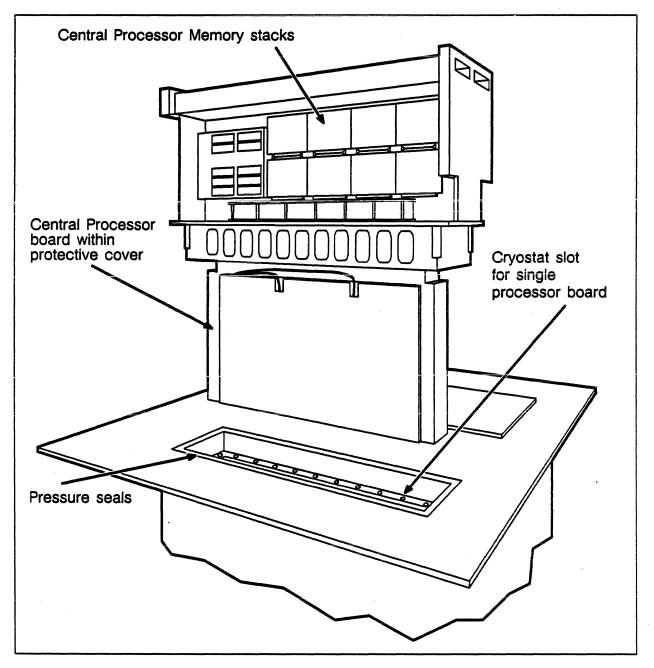

Cooling options provide significant performance enhancements for the central processor boards. CMOS semiconductor technology is used in the high density chips that populate the central processor boards. Because CMOS chips use relatively little power and dissipate very little heat, they need only be cooled with ambient air to function normally. The ETA10 P and Q models are cooled in this manner.

However, by substantially lowering the environmental temperature, logic gate delays are greatly reduced and double the processing capability of the board. Central processor boards in ETA10 G and E models are housed in cryostats where they are super-cooled in baths of liquid nitrogen. Super-cooled systems offer very exceptional levels of performance; air-cooled systems offer efficiency in installation and lower costs of operation.

#### **Redundancy Options**

System redundancy ensures the system is available during component failure or maintenance. Availability is used as a measure of the system's ability to function and to perform during failure or maintenance.

Redundancy means that the user sees no change in the system during instances of failure or maintenance. Redundant design in the ETA10 is apparent in several ways:

- multiple components that can independently perform the same function. Normally these components extend system capability; but they can substitute for other components as needed. For example, the multiple central processors.

- redundant components that are included as insurance; they may or may not extend system capability. For example, the parallel power supplies.

- redundant connections between components that are another form of system insurance

The upper portion of this diagram shows the number of components in each category included in a typical non-redundant model E system. The numbers refer to how many of the components are in the system.

Figure 1-7. Redundancy options in the ETA10 super-cooled systems.

The components within the shaded area at the bottom are those added in each category to provide redundancy in a model E system.

#### **Multiple Components**

Both redundant and non-redundant models have multiple central processors and I/O units: these units function independently and readily substitute for a like unit removed from the system configuration. Multiple processors are required to meet system performance needs, but they also serve to ensure system availability.

#### **Redundant Components**

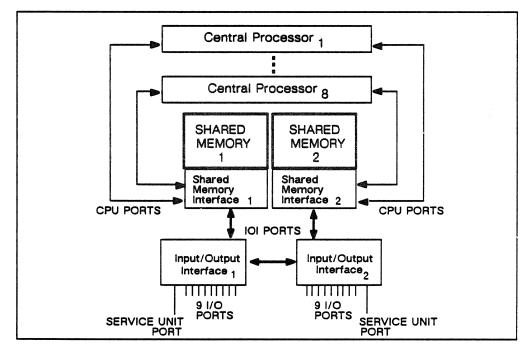

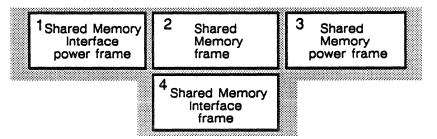

The diagram above shows the components required to make the system redundant, absolutely ensuring system availability. Required components are a shared memory, a communication buffer, a set of the major system interface boards, and a second service unit server node.

When there are two units of shared memory and communication buffer, each fully functions as a component "half". For example, IOUs that port into one unit of the shared memory are also fully able to access the second or redundant unit of shared memory. Redundant interface boards may enhance system performance as well as provide system insurance. A second I/O interface board doubles the number of I/O ports into shared memory; a second shared memory interface board doubles the number of central processor access slots to shared memory. A redundant system includes a second server node in the service unit to maintain parallel connections to the system maintenance interface.

#### **Redundant** Connections

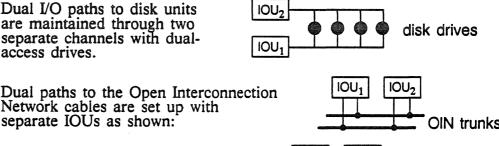

Some components are dually connected. Each IOU is connected by a pair of serial input/output lines to each service unit server node. Peripheral devices and networks are usually dually connected to two IOUs to maintain connections even in the event of failures.

PUB-1005 Rev. A

## Chapter 2

## The User Environment

#### **Chapter Contents**

| The Environment Model                         | 2–2  |

|-----------------------------------------------|------|

| Introductory Description                      | 2–2  |

| The VSOS User Environment                     |      |

| Calling a Kernel Function from an Environment | 2-4  |

| Elements in the Environment                   | 2-5  |

| Environment-independent components            | 2-5  |

| Environment-dependent components              | 2-6  |

| Management of users and user sessions         | 2-7  |

| User access to the system                     | 2-7  |

| Environment Processes                         | 2–8  |

| User sessions                                 | 2-10 |

| Batch sessions and Interactive sessions       | 2-10 |

| Session start-up                              | 2–12 |

| Session execution and completion              | 2-12 |

| The Login Process                             | 2-13 |

| Overview of the VSOS Environment              | 2-14 |

| Files                                         | 2-14 |

| Libraries                                     | 2-18 |

| Language Processors                           | 2-18 |

| Utilities                                     | 2–18 |

| System Interface Library (SIL)                | 2-18 |

| Command Shell                                 | 2-19 |

| The Open Interconnection Network (OIN)        | 2–19 |

| VSOS/Kernel Interfaces                        | 2–20 |

| How ETA VSOS differs from CDC VSOS            | 2-25 |

| File Concept Differences                      | 2–26 |

| Device Characteristics                        | 2–26 |

| Process Management                            | 2–27 |

| User Interface Differences                    |      |

|                                               | 2-27 |

### **Contents** (continued)

| The VSOS File System                | -30 |

|-------------------------------------|-----|

| The VSOS Tables                     | -34 |

| The File Information Table          | -34 |

| The Command Shell                   | -34 |

| Communicating with the User         | -34 |

| Managing Processes                  | -35 |

| Establishing the VSOS Environment   | -36 |

| Security and Protection             | -42 |

| The VSOS Command Shell              | -44 |

| Shell Initialization                | -46 |

| Command Processing                  | -48 |

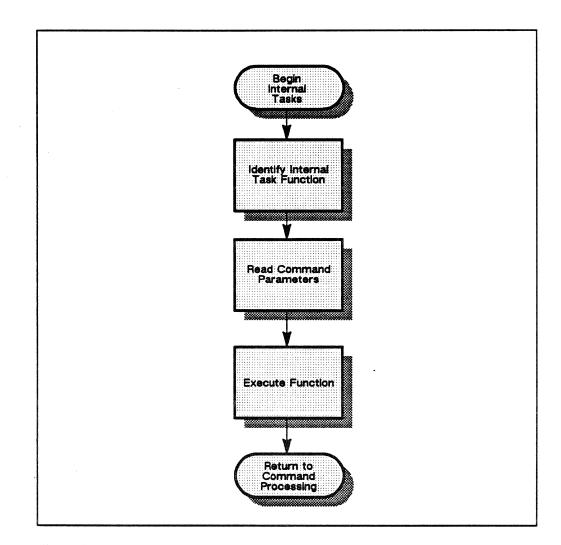

| Internal Tasks                      | -50 |

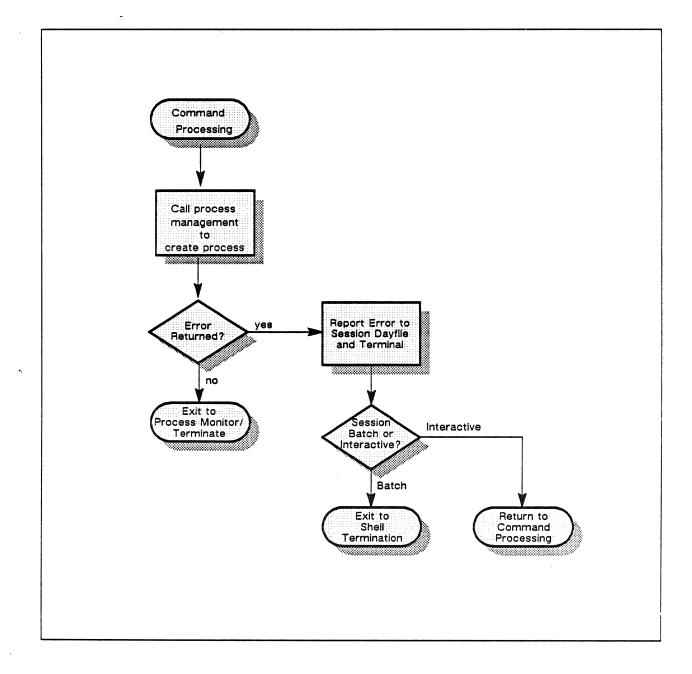

| Process Create                      | -52 |

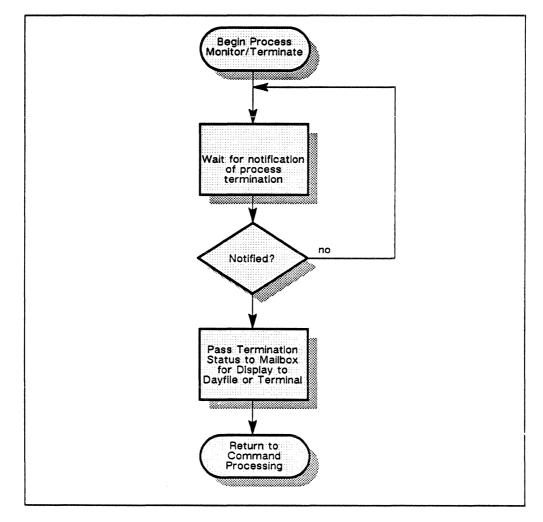

| Process Monitor / Process Terminate | -54 |

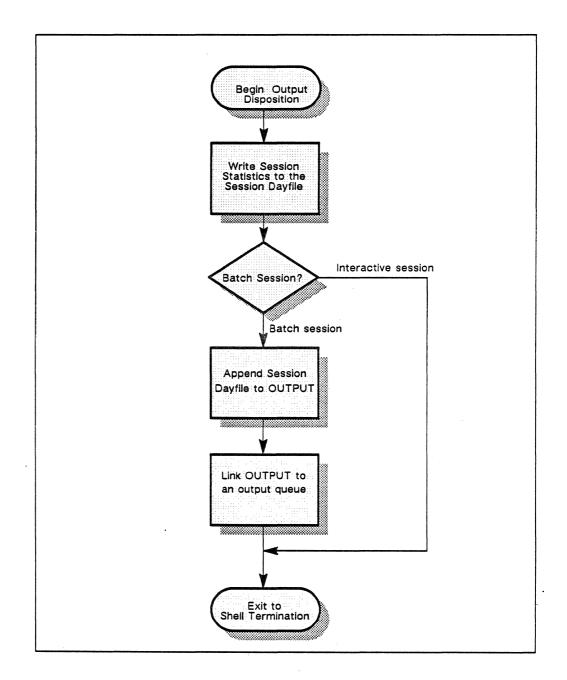

| Output Disposition                  | -55 |

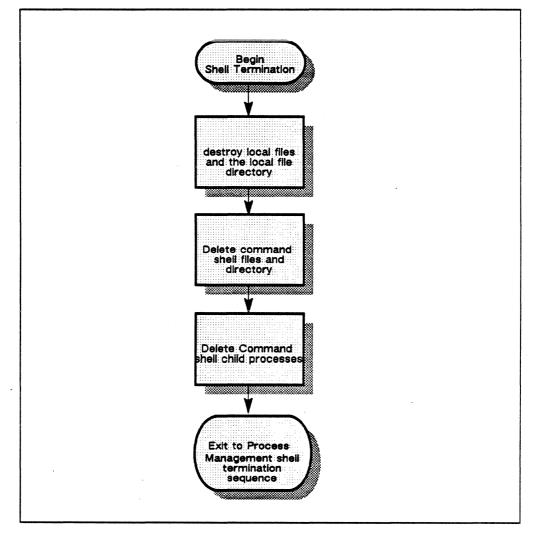

| Shell Termination                   | -56 |

|                                     |     |

#### List of Figures

| Fig <b>ur</b> e | Title                                                        | Page   |

|-----------------|--------------------------------------------------------------|--------|

| 2-1             | The environment model                                        | 2-3    |

| 2-2             | Calling a kernel function from an environment                |        |

| 2-3             | Spawning of processes in the VSOS environment                | . 2–9  |

| 2-4             | Comparison of interactive and batch sessions                 |        |

| 2-5             | System entry of batch and interactive sessions               |        |

| 2-6             | Interactive login process involving the common login feature |        |

|                 | and Global Scheduler                                         | 2-13   |

| 2-7             | File Directory/Catalog manager file system                   |        |

| 2-8             | The VSOS environment directories                             |        |

| 2-9             | The user interfaces to the operating system                  |        |

| 2-10            | Directories for newly created users                          |        |

| 2-11            | VSOS File Management                                         |        |

| 2-12            | Pathways to the $VSOS$ environment                           |        |

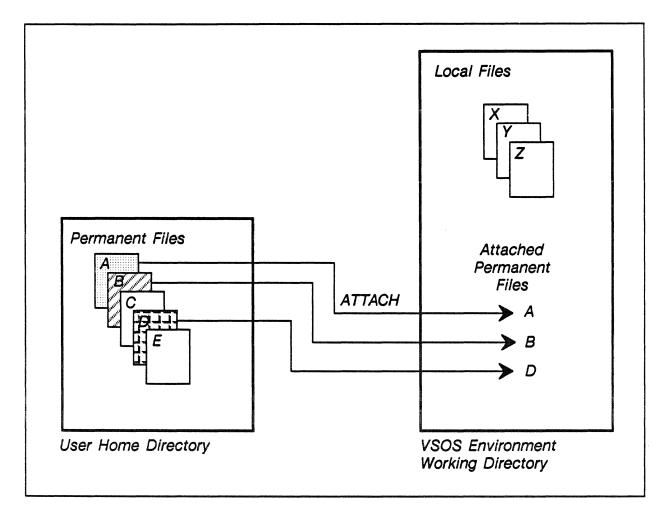

| 2-13            | VSOS environment working directory with links to the         |        |

|                 | user's home directory                                        | 2-37   |

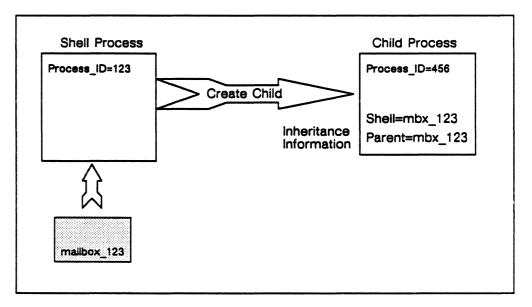

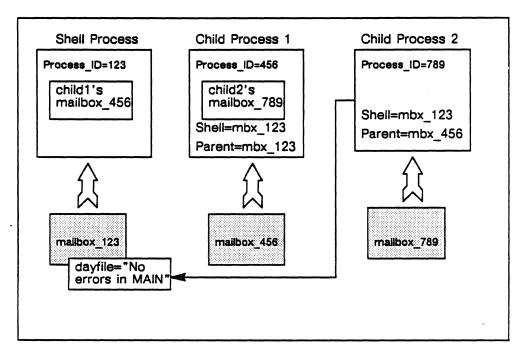

| 2-14            | The shell creates (exports) a mailbox                        | 2-38   |

| 2-15            | The shell creates a process, passing inheritance information |        |

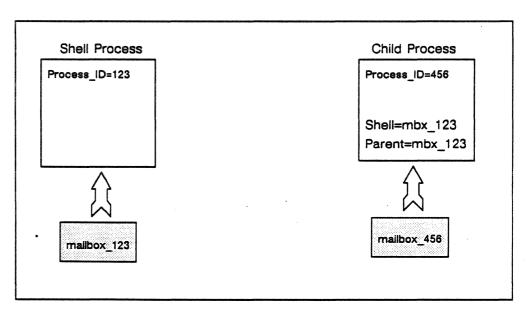

| 2-16            | The newly created process exports (creates) its own mailbox  | . 2-39 |

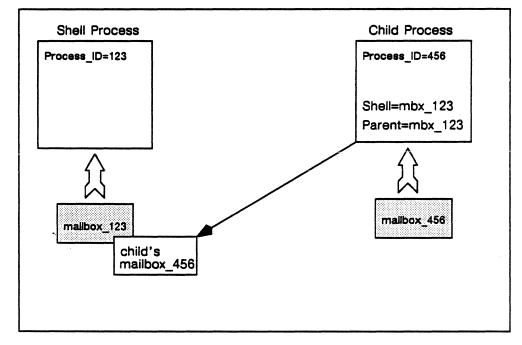

| 2-17            | The shell is informed of the mailbox ID of the new process   |        |

| 2-18            | A process sends a dayfile message to the shell               |        |

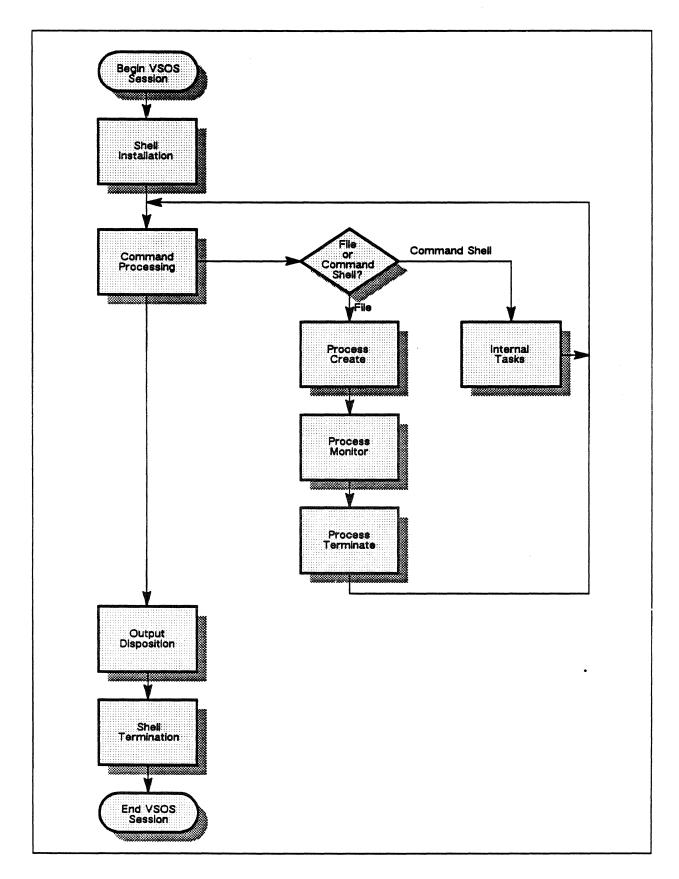

| 2-19            | Processing of a VSOS environment session                     |        |

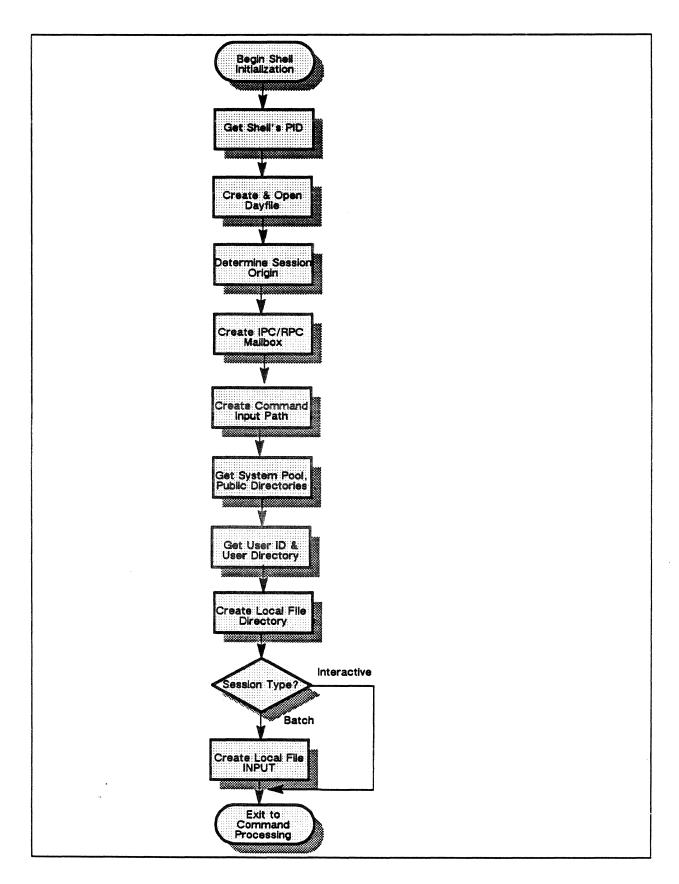

| 2-20            | Shell initialization flow chart                              |        |

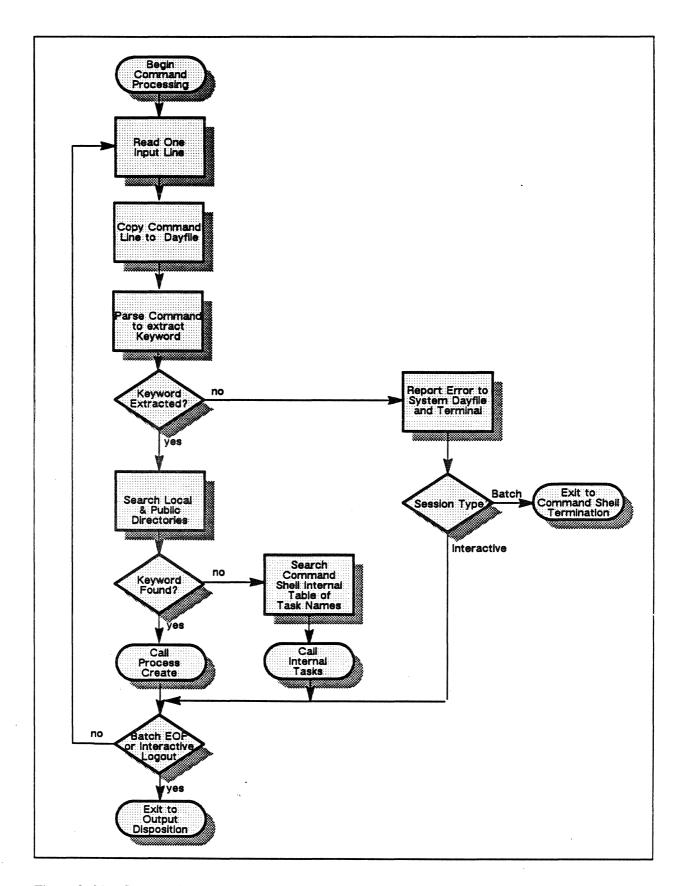

| 2-21            | Command processing flow chart                                |        |

| 2-22            | Internal tasks flow chart                                    |        |

| 2-23            | Process create flow chart                                    |        |

| 2-24            | Process monitor/terminate flow chart                         | . 2–54 |

| 2-25 | Output disposition  | <br>5 |

|------|---------------------|-------|

| 2-26 | Shell Termination . | <br>6 |

#### List of Tables

| Table | Title                | Page |

|-------|----------------------|------|

| 2-1   | VSOS command summary | 2–22 |

| 2-2   | SIL non-I/O routines | 2–23 |

| 2-3   | SIL I/O routines     | 2–24 |

1

PUB-1005 Rev. A

# Chapter 2

# The User Environment

# In This Chapter

Chapter 2 introduces you to the Virtual Storage Operating System (VSOS) environment available on the ETA system.

- The Environment Model

- Overview of the ETA VSOS Environment

- Functional Description of VSOS

- The VSOS Command Shell

## The Environment Model

#### **Introductory Description**

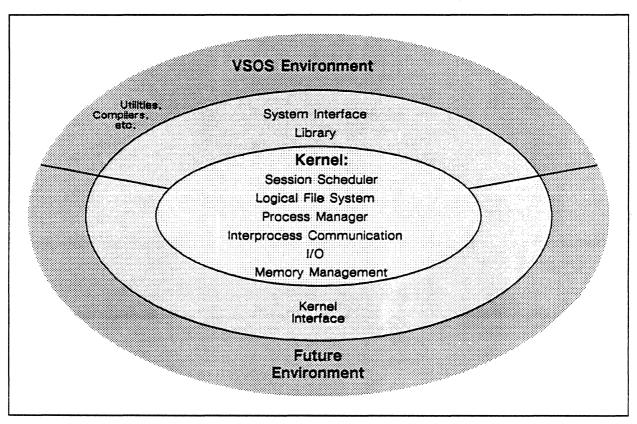

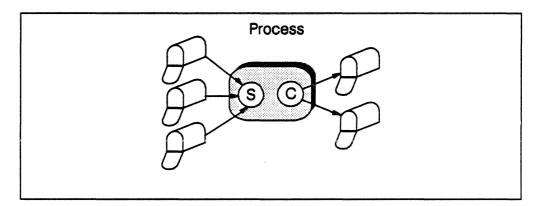

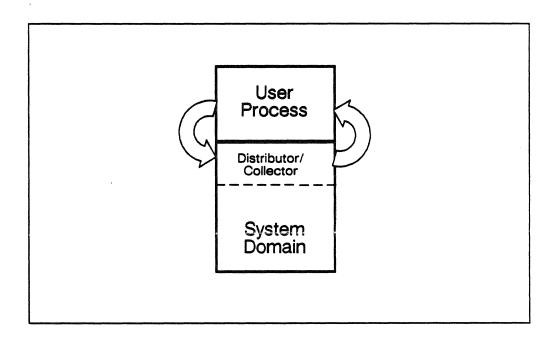

EOS is a general purpose operating system that is designed to support multiple views or presentations of its functions. EOS comprises a kernel, a set of interface libraries, a programming environment, and support tools. The kernel provides basic system functions to the user: file management, I/O, memory management, and process control. It manages system resources, and controls system hardware and software.

User applications running on the ETA10 make use of kernel functions by means of a programming environment that maps on to the underlying operating system transparently to the user. The programming environment, a layer of software built on top of the kernel, handles the necessary interaction between the user and the kernel's services. The environment enables you to take advantage of the machine's capabilities using a language and context that is familiar.

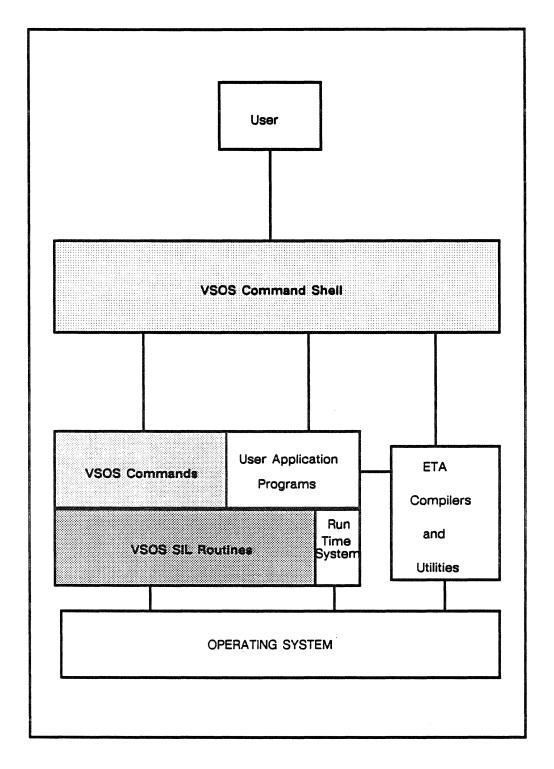

Figure 2-1 shows the layers of software on the ETA10: the basic kernel functions, an interface allowing access to these functions, and the ETA10 user environment, which accesses the functions by way of the interface.

All the necessary pieces for program development and execution – libraries, editors, compilers, debuggers and other tools, are accessible from the programming environment. Users have access to a common set of languages and tools, such as FORTRAN 200, ETA Debug, and the loader. These products are defined independently of the environment, but use some of the environmental support for context. For example, ETA Debug uses the file search algorithm of the active environment to locate files.

Figure 2-1. The environment model.

An environment provides basic features to its users. A command language allows you to initiate utility programs, compilers, user applications, and to specify parameters controlling their execution. The command shell interprets the command language and causes the appropriate commands to be executed in a session. Libraries provide the interfaces between a user program and the operating system, allowing programs to communicate with the kernel using subroutines or system calls. ETA Systems provides application packages for many subject areas, including biotechnology, computational fluid dynamics, and structural analysis.

#### The VSOS User Environment

ETA Systems supports the Virtual Storage Operating System (VSOS) command set, the user interface of the CYBER 205, as its first programming environment. There are some differences in the ETA10 version. CYBER 205 features which have no analogue in ETA computer systems have been deleted. Some utilities have been replaced by new ones with equivalent or new functionality. New features have been added. Richer interactive abilities are provided and the user interface has been made more powerful. The main differences between CYBER 205 VSOS and the ETA10 system are discussed later in this chapter.

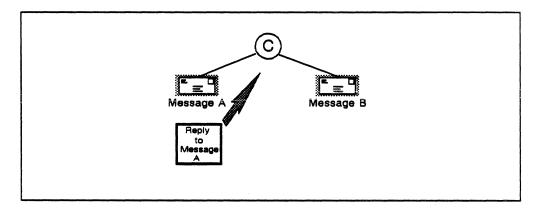

#### Calling a kernel function from an environment

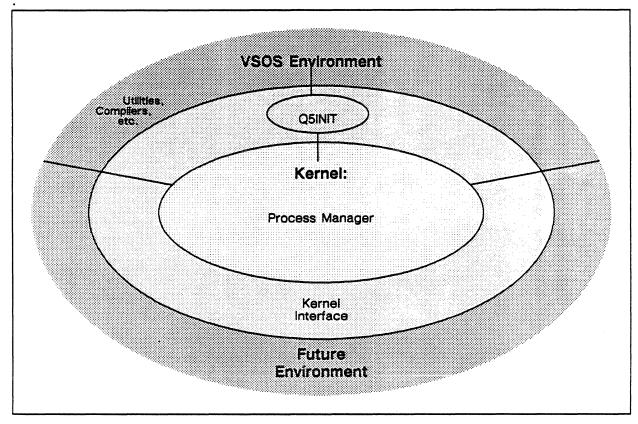

Applications running in an environment call the kernel through an interface which is a collection of routines. For example, VSOS applications call **System Interface Library** (SIL) routines, which communicate with the kernel to complete both I/O and non-I/O functions. The interface used by an environment is specific to that environment.

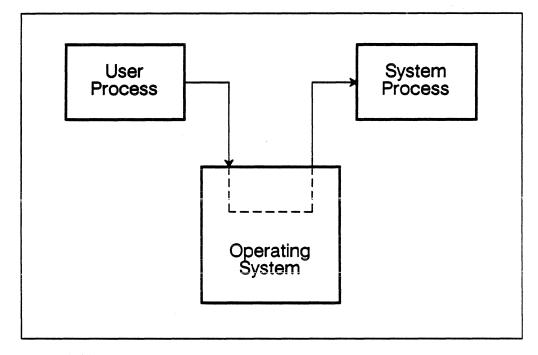

Figure 2-2 shows a request to the operating system from an application running in the VSOS Environment. The request is to prepare a new process for execution. The application issues a SIL subroutine call, Q5INIT (initialize a controllee), to a process management function in the kernel, requesting that it run a process, and passing information about the process that is to run.

Figure 2-2. Calling a kernel function from an environment.

#### **Elements in the Environment**

Operating system components fall into two groups in relation to user environments: those dependent on an environment, and those independent of it. Environment-independent tools serve as common resources.

#### **Environment-independent** components

*Kernel functions.* These are accessed by user environments, but their structure is not dependent on an environment's functional requirements.

A common set of languages and tools. These include the FORTRAN 200 compiler, ETA Debug, and the loader.

The object text and executable file formats.

File representation and file limits. These include the maximum number of records in a file, length of records, the maximum number of file objects, the length of the data that can be transmitted during I/O, the maximum number of outstanding I/O operations allowed, and the maximum number of files that can be open at the same time. File access permissions. The ETA file system allows access to a file based on a state ID, which contains the user name, the user's group ID, and the domain name. The state ID is checked against valid permission types for that state to decide if the user can perform file operations. The access types exposed depend on the environment.

User validation and privileges, including system security, access to the system and user objects, and validation during the user login procedure. These are controlled by the kernel features.

*File attributes*. Intrinsic attributes necessary to define a file include the physical file identifier, the owner user name, and the file's device class identifier. Record management attributes define such elements as record type, maximum record length, and padding characters. Accounting and statistical attributes describe the file's creation date and time, the account ID, information about when the file was last modified, and so on. Resource limitation attributes include the file's device class and the current file length.

#### **Environment-dependent** components

The interface to kernel functions. In the VSOS environment, these consist of subroutine calls that request activity and return results.

Libraries containing routines tailored to a particular environment, such as the System Interface Library for VSOS.

Utilities.

#### The command processor and command formats.

*User validation.* This is conducted at login time to determine a user's access rights to the selected environment. A default environment is activated for the user who does not select an environment at login time.

The process management model. Processes in a session run under the control of the environment in which they are activated. Inheritance information is passed on to new processes in the session. This contains data about directories known to the user environment, as well as other needed information.

File permissions, which allow users to reference files. An environmentally determined access state allows users to access a file. A state ID, containing the user name, the user's group ID, and the domain name, is checked against the type of file operation requested by the user and access permission granted accordingly. File attributes which are dependent on the user's environment include the type of file access – sequential or direct. Although the system does not define a file type as having sequential or direct access, a user environment does make that distinction.

*File system model.* The environment presents a view of the underlying file system that is tailored to its user.

#### Management of Users and User Sessions

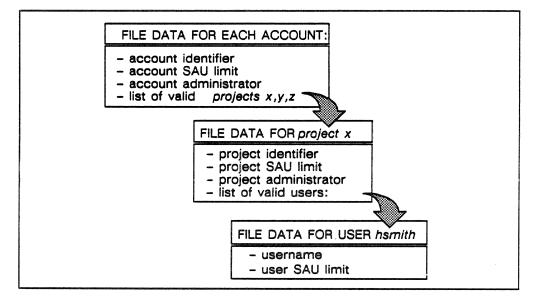

Anyone privileged to log in to the system is a user, but users differ in the extent to which they are privileged to access files, system resources, and other users. At the top of the pyramid is the system administrator, who has almost unlimited access to the system. The system administrator grants system access to other users and oversees their privileges. Depending on the site, there may be additional site administrators under the authority of the system administrator. A project administrator manages privileges for all the users on a project, while an account administrator does the same for the users associated with his/her accounts. System, project, and account administrators are all users in the sense that they have user IDs and passwords; in addition, however, they have special privileges that allow them to fulfill their roles in site administration. An ordinary user may be privileged only to log in and run a specific program, and may make changes only under his own user ID.

#### User Access to the System

Site administration controls user access through the *user registry*, the interface through which users are identified to the system. If the system cannot identify the user ID or password of someone logging in, the login is rejected.

The user registry is the record of all system users and privileges granted to them. Examples of these privileges include the permission to submit batch sessions and the permission to charge resource usage to a particular project and account. The user registry is covered in greater detail in chapter 3 in "The User Registry" section. The set of privileges for a user is called the *user profile*.

A user profile is a list of those system privileges and features available to a certain user; it is a subset of the user registry. The system administrator sets up user IDs, supplies them to the user registry, and creates the individual profiles that define user access to a subset of the available system features.

Each user profile contains a set of default session parameters which include default accounting information and default working-directory parameters that execute automatically when the user logs on or off.

#### **Environment Processes**

In an ETA10 environment, a process is the execution of the smallest unit of work that can be executed. An executing program is a process. Tasks in the VSOS environment map to the processes that the kernel works with on the ETA10 system. A series of processes constitutes a session. Processes run under both batch and interactive sessions, and are monitored and controlled on a session basis. Once a process is activated, it runs in its user's environment for the duration of the session. Users cannot switch environments in mid-session. For a discussion of VSOS task execution, refer to the VSOS Environment Reference Manual: Concepts and Commands, PUB-1051.

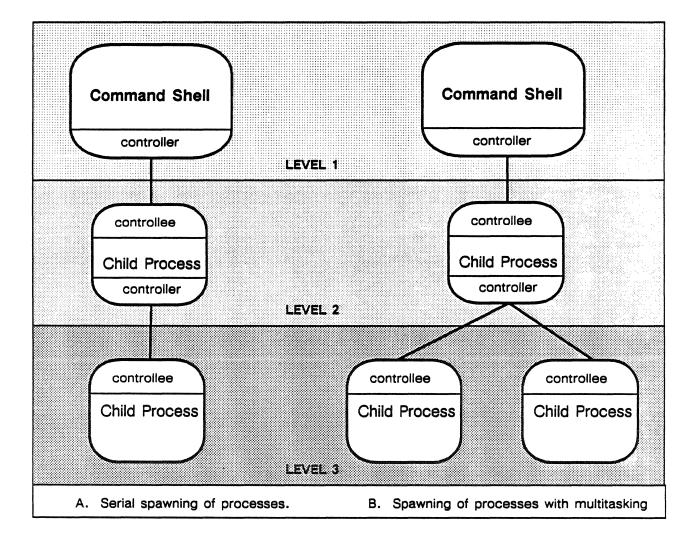

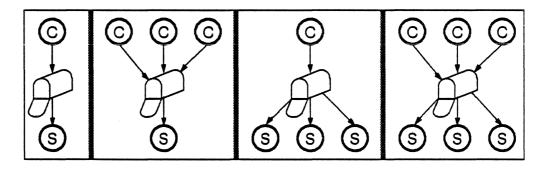

Each process is spawned serially. A spawned process can start other processes – one at a time. The starting process is the controller, the process it starts is its controllee. A series of two or more controllers and controllees forms a controllee chain. The command shell is the first process born in a session and is always a controller, at level 1. It may start a new process, or controllee, at level 2, which, acting as a controller, can spawn a controllee at level 3, and so on. After a process is spawned, the shell continually checks process management for the status of the spawned process, until the spawned process terminates. When the process has completed, the shell spawns the next process to execute.

The VSOS environment always spawns processes in hierarchical fashion. It never has multiple child processes running at the same time. However, use of a library of multitasking routines available in future releases makes a difference in the way child processes are spawned, as shown in figure 2–3. Multitasking allows a user's program, not the command shell, to spawn processes horizontally, producing multiple child processes running at the same level.

Figure 2-3. Spawning of processes in the VSOS environment.

#### **User Sessions**

On the ETA10, jobs and sessions are the same work unit, and the system manages batch jobs and interactive sessions in exactly the same way. ETA Systems uses the term *session* to refer to this work unit on the system.

Every session is the execution of a set of processes, whether the process name arrives at the command shell from a batch input file or directly from a user's keyboard.

- Every session runs under the control of the user environment. A user logged into a VSOS session remains in that environment till logging out; the user session runs under control of the VSOS shell that enables the user to enter commands and do work.

- Every session has a unique name, so that a user or operator can refer to all of the work being performed in it as a single unit.

- The operating system uses the session as an accounting and control envelope for a set of process executions.

#### **Batch Sessions and Interactive Sessions**

Although the ETA10 treats batch sessions and interactive sessions in the same way, there are some differences between these types of user sessions, as shown in figure 2-4. An interactive session usually involves a two-way exchange of prompts and responses. As an example, a user logs in, issues a command or commands, receives a response, and the user logs out. In a batch session, a file of commands is entered into the input queue and executed later. In the VSOS environment, a batch session can be submitted to the input queue from an interactive session. The input and output from batch sessions are associated with files; the input and output from interactive sessions are associated with terminals. Local batch sessions terminate after the output file is transferred to the user's home directory, and interactive sessions terminate when the user logs off.

| INTERACTIVE<br>SESSIONS                                                                 | BATCH<br>SESSIONS – 2 START OPTIONS                                                              |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| START-UP:                                                                               | START-UP:                                                                                        |

| <ul> <li>USER logs in,<br/>connection is<br/>established by<br/>Common Login</li> </ul> | 1. ENQUEUE command (local batch)<br>via an interactive session                                   |

| Processor                                                                               | 2. ENQUEUE command (local batch)<br>via a batch session                                          |

| <ul> <li>User session is<br/>queued as an<br/>interactive login</li> </ul>              | <ul> <li>Session is created and queued to input queue</li> </ul>                                 |

| <ul> <li>User environment<br/>and command<br/>shell established</li> </ul>              | <ul> <li>When session is selected to execute, the<br/>user environment is established</li> </ul> |

| EXECUTION:                                                                              | EXECUTION:                                                                                       |

| <ul> <li>User processes execute<br/>and complete</li> </ul>                             | • User commands are executed from file                                                           |

| COMPLETION:                                                                             | COMPLETION:                                                                                      |

| <ul> <li>User logs out</li> </ul>                                                       | <ul> <li>Output is returned to specified file</li> </ul>                                         |

| • Session terminates                                                                    | • Session terminates                                                                             |

Figure 2-4. Comparison of interactive and batch sessions.

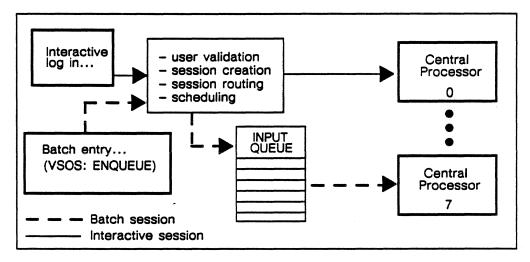

#### Session Start-Up

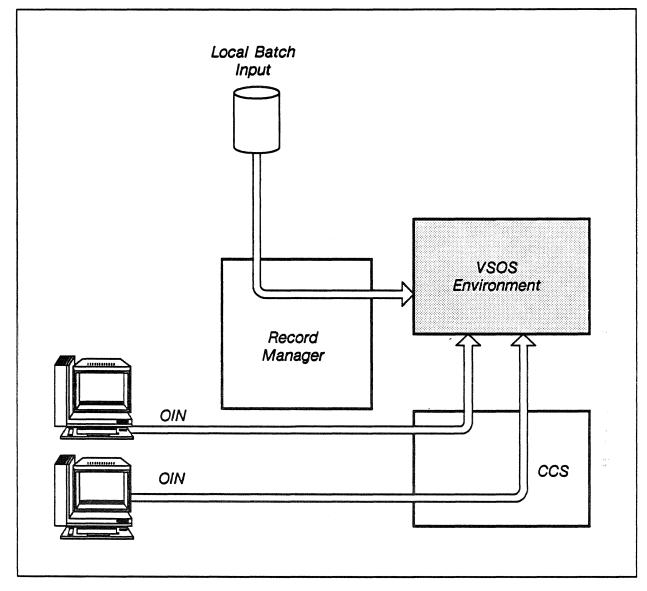

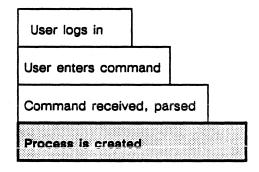

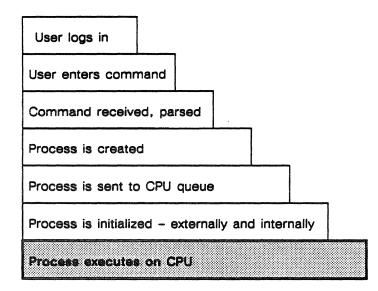

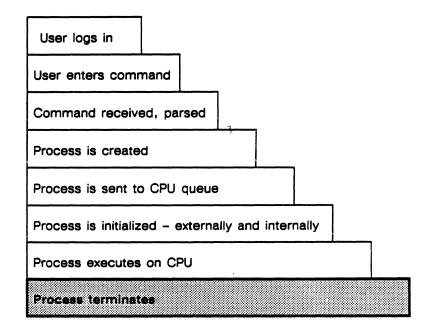

Although batch and interactive sessions arrive on the system in different ways, the two kinds of sessions are validated in the same way (figure 2-5). The user management feature continually runs on the system, managing system use and access. It prompts for the username and password on the login line, then user management turns the session over to global scheduler.

Figure 2–5. System entry of batch and interactive sessions.

#### Session Execution and Completion

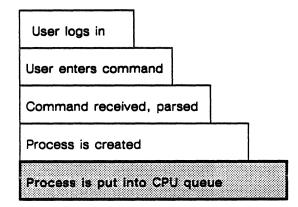

Global scheduler stores the information about the session and the processes included in it, and creates the session shell – a process that starts and runs the session. Then Global scheduler moves the session into the session input queue. When it finds a central processor with enough memory available to start a new process, Global scheduler sends the processor one of the session's processes for execution. Associated with each process is a process table that includes the names of the executable files, the name of the shell, for example, as well as other information needed by processes making up the session.

When the last process has completed, the environment command shell sends a report to the system dayfile. If it is a batch session, the processes have written to the indicated output file or files.

#### The Login Process

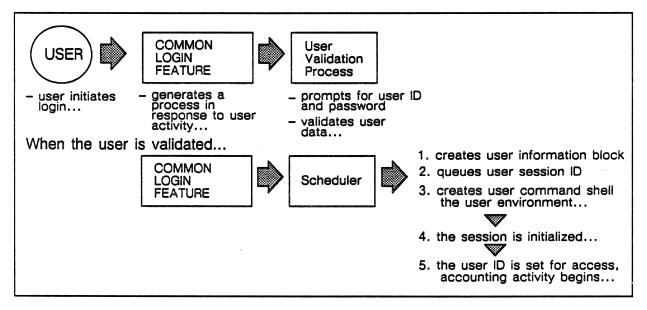

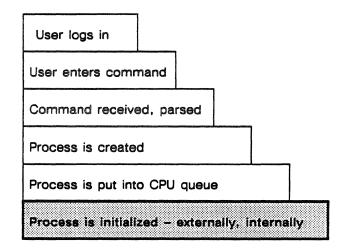

The common login feature validates user logins; it is initialized during system start-up and runs continuously on the system. It has two functions: the first is to respond to users logging in and to interactively prompt for user ID and password, and the second is to validate the user ID, password, and privilege to log in and, when those items are valid, to create the appropriate session.

When the user has been validated, the common login feature calls global scheduler, which initiates the session by setting up the user environment. When the session is initialized, the first process may be started. Information from the user data block is used to manage the session, to send data to the accounting system, for example. Figure 2-6 illustrates the interactive login procedure.

A local batch session may be started during an interactive or batch session using the ENQUEUE command.

Figure 2-6. Interactive login process involving the common login feature and global scheduler.

# **Overview of the VSOS Environment**

The VSOS Environment consists of a number of components:

- Files

- Libraries

- Language processors

- Utilities

- The System Interface Library

- The command shell

#### Files

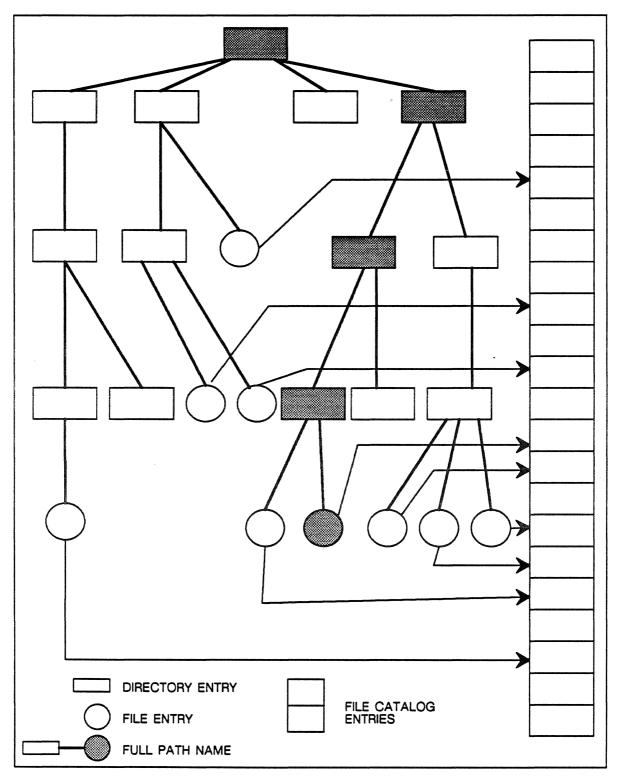

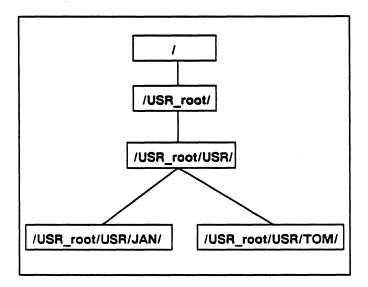

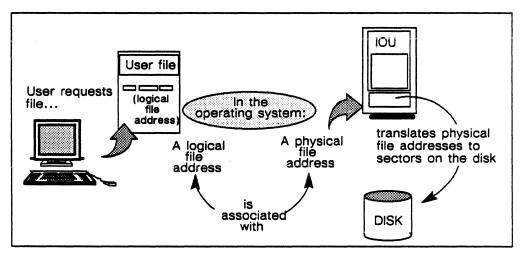

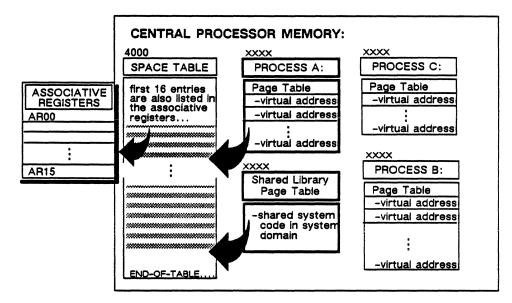

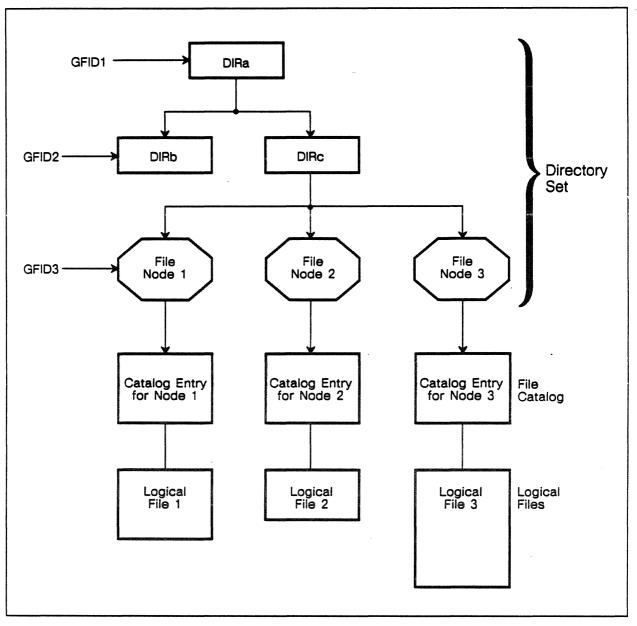

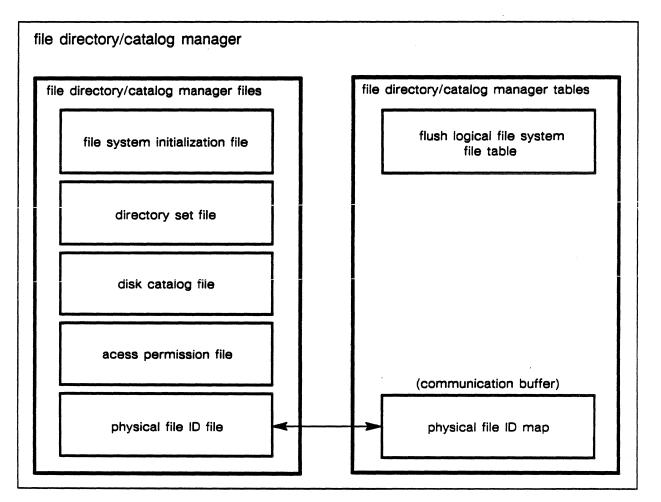

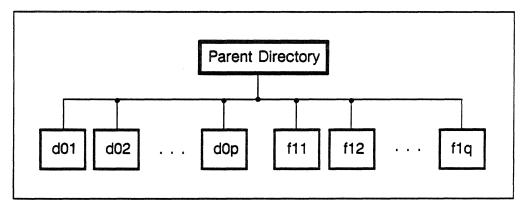

In the VSOS Environment, a file is a data structure accessible to users and the system by name. The VSOS file system has a flat structure, meaning that you have only one directory containing all your permanent disk files. In the underlying system kernel, files are arranged in a hierarchical tree structure, where files are linked to the leaf nodes of a naming tree. The tree is defined and maintained using directories. Files are grouped by being linked to directories. Information about files, such as their attributes, is stored in the file catalog.

Figure 2-7 describes the ETA10 file directory system. Access is via a pathname, consisting of an ordered list of directory names, down to the file name. The kernel's file system structure (called the logical file system) is generalized enough to support the environment's file and I/O models. The VSOS environment automatically performs the necessary mapping of your files into the logical file system's tree structure.

Three data structures are supported by the ETA system:

- Records

- Groups

- Files

Within this logical file structure, a byte is the smallest unit of data managed by the system. A collection of bytes forms a record. A group, which is a collection of records, is the next higher structure, and a file is the highest level. These logical groups of data are also referred to as partitions. Data can be accessed by referencing partitions, using the partition number.

Figure 2-7. File directory/catalog manager file system.

File formats define the logical record structure of a file to the ETA kernel. The logical file system defines the logical structure of files according to four user-selectable record formats:

- ANSI fixed length (F) records with a fixed, specifiable number of bytes that is set as a file attribute.

- Record mark delimited (R) records of variable length delimited by a byte at the end of each.

- Undefined (U) no records; the file is considered one continuous string of bytes.

- Control word delimited (V) variable length records delimited by control words which mark record, group and file partitions. VSOS type (W) records are mapped to the file system's type (V) records.

File Attributes describe the characteristics of a file, such as its name, access permissions, and its device class. Attributes are set by the VSOS Environment when the file is created. You can assign the file attributes, or the system can assign default values. The attributes remain in effect for the life of the file, or until the user changes them explicitly.

File Types determine the way the system uses the files. A controllee file, also referred to as a virtual or virtual code file, is an executable file generated by LOAD. A process is the execution of a controllee file. Data files are any non-controllee files. Output files, which contain data to be processed by an output device, and object, or binary files, which provide the input to LOAD to generate executable controllee files are data files.

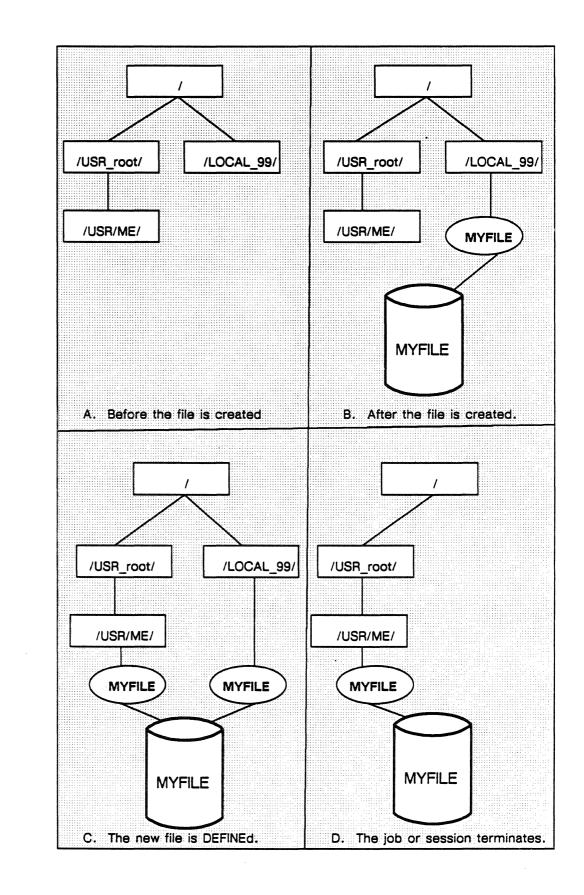

File Duration, the length of a file's existence on the system, depends on the file type. Temporary files exist only as long as the session continues. Permanent files are stored until explicitly deleted. Local files, which can be temporary or permanent, are immediately available to a task.

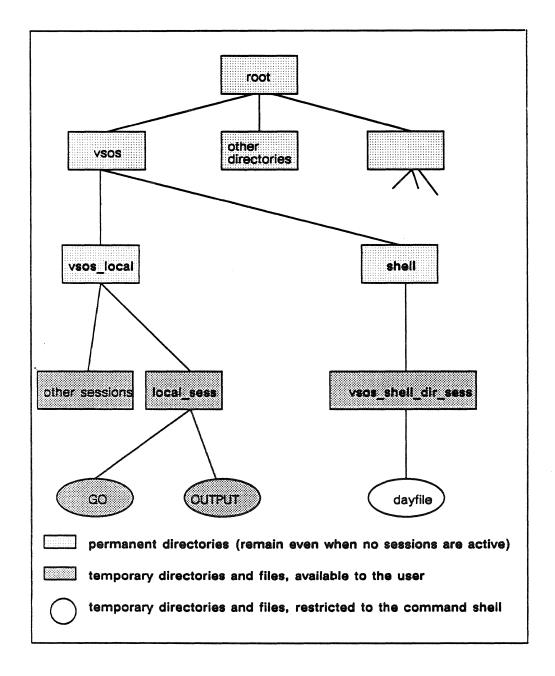

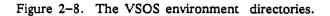

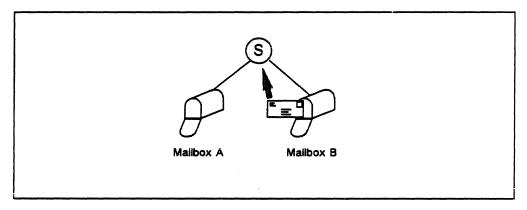

Figure 2-8 shows a portion of the logical file system tree pertinent to a single session. Because the kernel operating system supports only permanent files, the command shell creates the directory needed to simulate the behavior of local files (local\_sess). Sess is the unique session ID. The local\_sess directory is unique to a session. It contains files or links to files which behave as local files to the session, and becomes the working directory for all processes in the environment. Files in this directory can be attached, defined and returned. The shell also creates a directory (vsos\_shell\_dir\_sess) to store its own files such as the dayfile, which are unique to the session and inaccessible to the user. Both directories are destroyed at the end of the session.

File Ownership may be by the VSOS environment (public), or by a user name (private). Utilities, commands, compilers, and general purpose routines are public files.

For more detailed information about VSOS environment file concepts, refer to the VSOS Environment Reference Manual: Concepts and Commands, PUB-1051.

#### Libraries

System libraries are available to you as an environment user. Some libraries contain routines that are specific to an environment, such as the VSOS SIL routines.

Other libraries are available to users in any environment. A library of multitasking routines available in future releases provides you with tools to perform multitasking operations such as task initialization, synchronization, and data sharing.

Standard libraries for language compilers are also available. In addition, you can create your own libraries within your environment. However, unlike system libraries, which are stored in system file space, user-created libraries are stored in the user's file space.

#### Language Processors

FORTRAN 200 is compatible with the FORTRAN CYBER 205 compiler, making it convenient to transport existing FORTRAN programs from the CYBER to the ETA10. ETA VAST is a vectorizing pre-compiler for the ETA10, intended for use in conjunction with the FORTRAN compiler.

#### Utilities

Several system utilities are available to the environment user. OLE, the object library editor, performs maintenance of object files. The LOAD utility links object files and libraries, and generates an executable file, also known as a controllee file. You can debug your programs interactively using ETA Debug, the symbolic debugger, which allows you to troubleshoot programs written in ETA product languages.

#### System Interface Library (SIL)

SIL consists of a number of subroutines that provide access to basic operating system features:

- File management

- Record I/O

- Message transmission

- Task initiation

- Task monitoring

- Task termination

Transparent routines translate a variable format SIL call into a fixed format acceptable to the CYBER Implementation Language (CYBIL), the language used for the development of the operating system software. Each library routine then:

- Parses the actual parameters

- Verifies parameter legality

- Makes the kernel calls necessary to accomplish the requested action.

Results from the kernel are translated into terms that a VSOS user is accustomed to and passed back to the calling application.

The SIL subroutine calls are detailed in the VSOS Environment Reference Manual: Concepts and Commands (PUB-1084).

#### **Command Shell**

The VSOS environment command shell serves three purposes:

- 1. It communicates with you, accepting your VSOS environment commands as input and returning responses as output. This communication may be interactive, or the command shell may be reading and writing disk files without your direct involvement.

- 2. It manages the processes of a batch or interactive session. It controls the initiation and sequencing of processes within a session.

- 3. It establishes those characteristics which cause a session to resemble a VSOS job, including the:

Establishment of a VSOS-like file system

Management of a session dayfile

Disposition of specially named files

#### The Open Interconnection Network (OIN)

The Open Interconnection Network (OIN) is a local area network based on the Ethernet protocol. Users on the OIN can interface to the VSOS environment through the communications control system (CCS) to log in, enter commands, and transfer files.

#### **VSOS/Kernel Interfaces**

VSOS Environment users interact with operating system functions using *commands* and *System Interface Library (SIL) routines* to perform such activities as:

- Session and process management

- Memory management

- Handling of file system and I/O

- Program development and code file management

- Inter-process communication

- Retrieval of information about the system

Figure 2-9 illustrates the VSOS user interface to the kernel functions.

Figure 2-9. The user interfaces to the operating system.

The user issues commands through the command shell, either batch or interactively. Refer to the VSOS Environment Reference Manual: Concepts and Commands, PUB-1051, for detailed information about VSOS commands. Table 2-1 lists the VSOS environment commands.

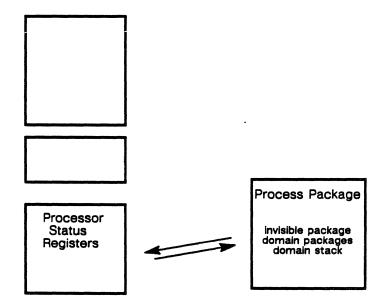

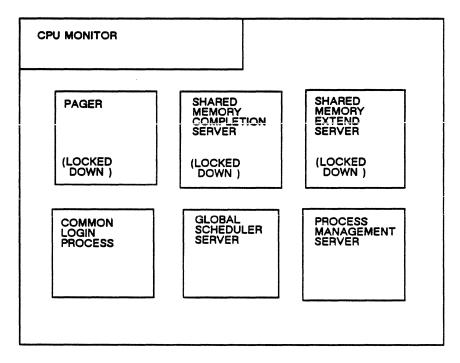

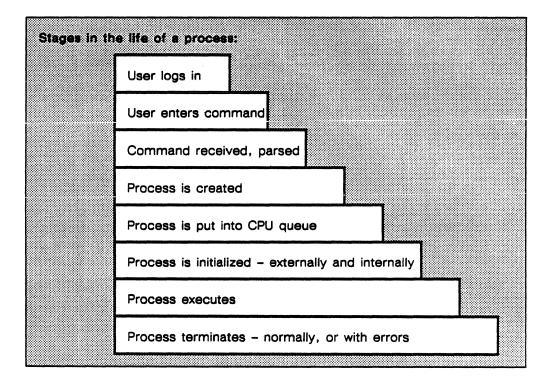

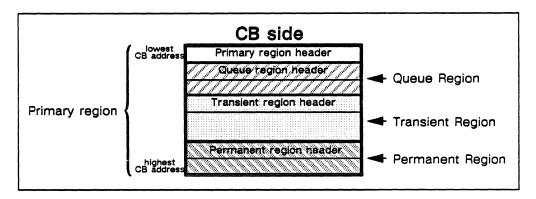

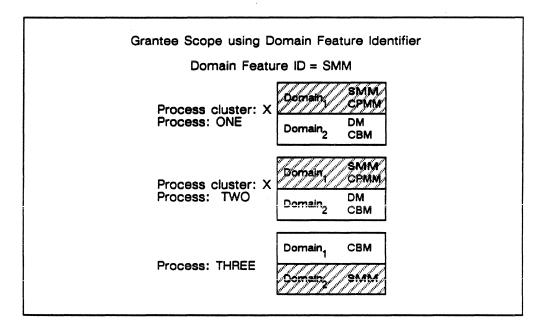

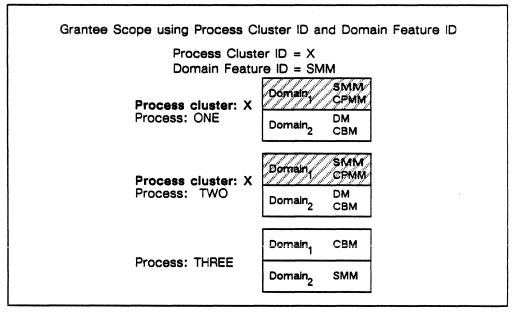

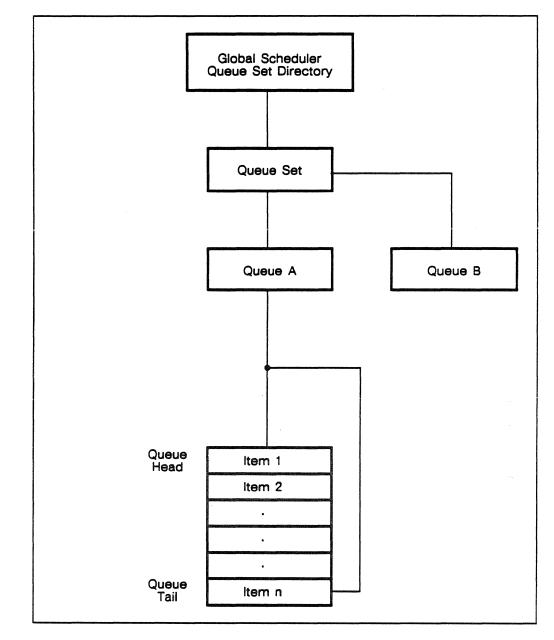

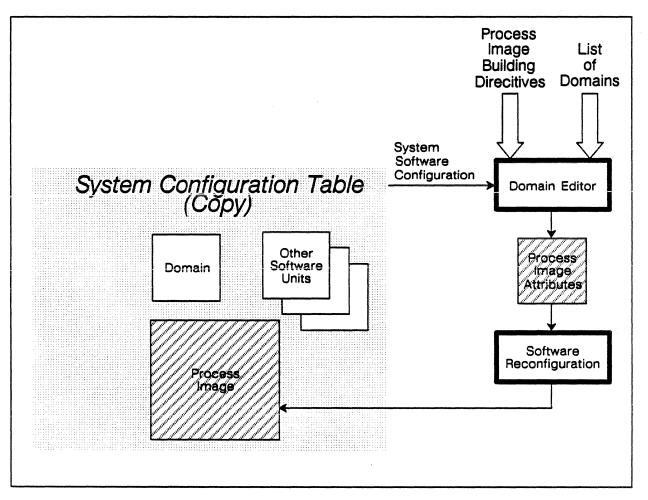

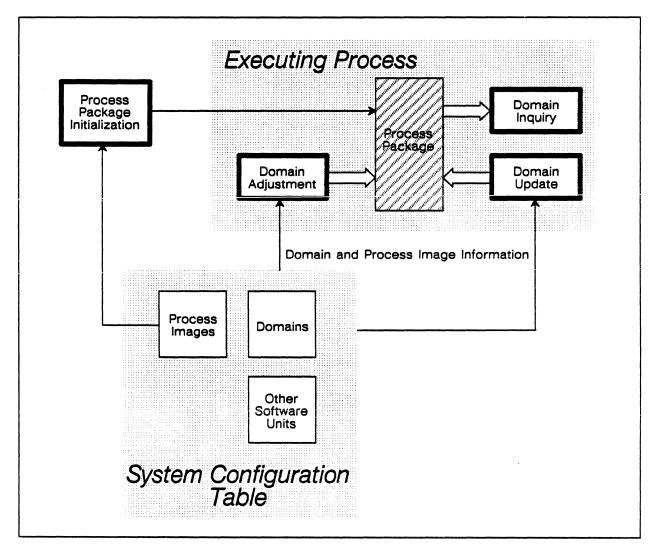

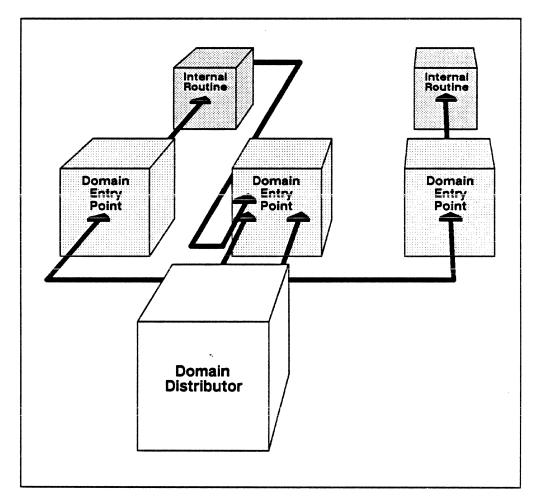

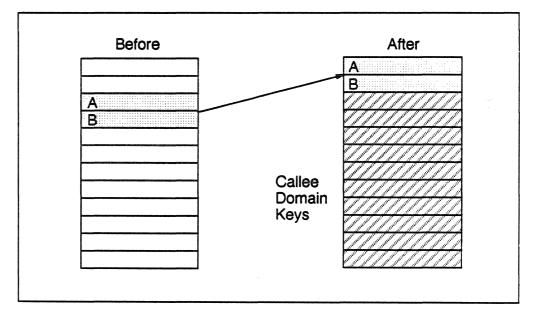

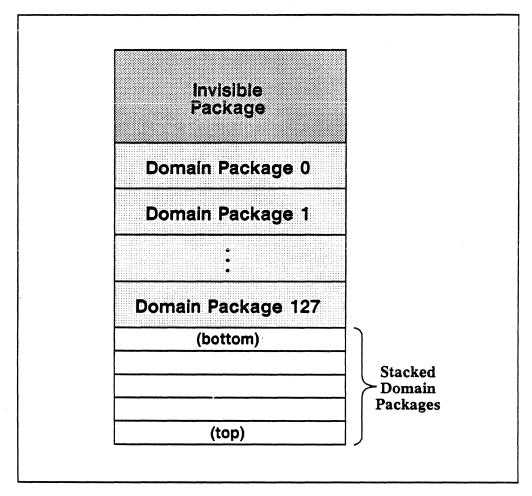

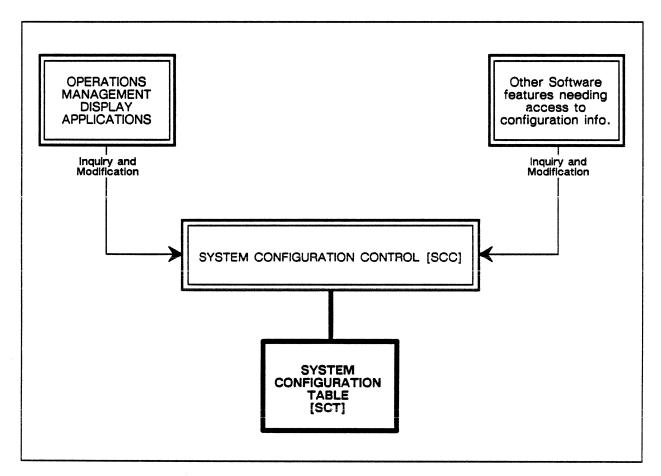

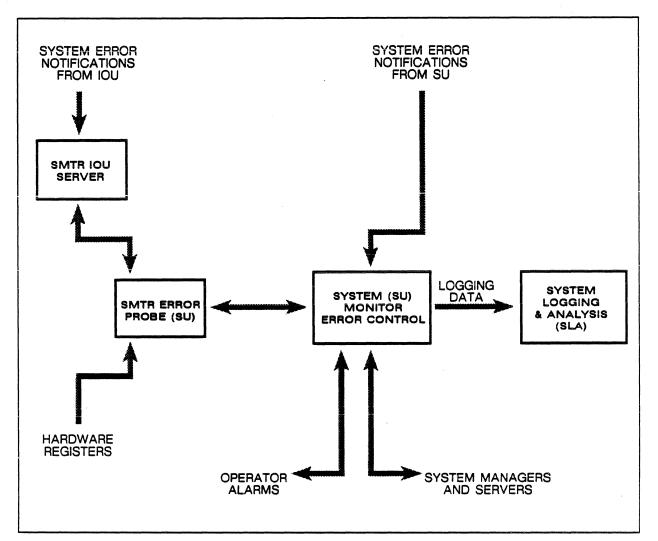

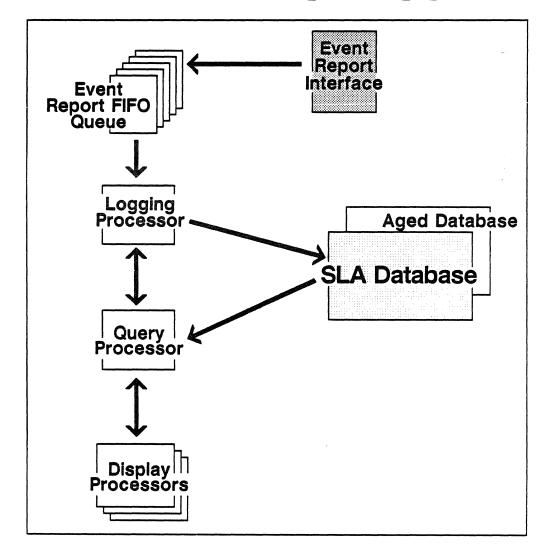

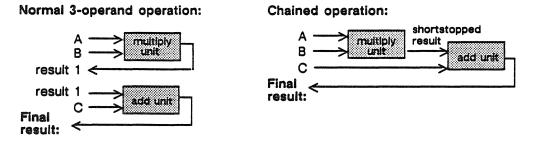

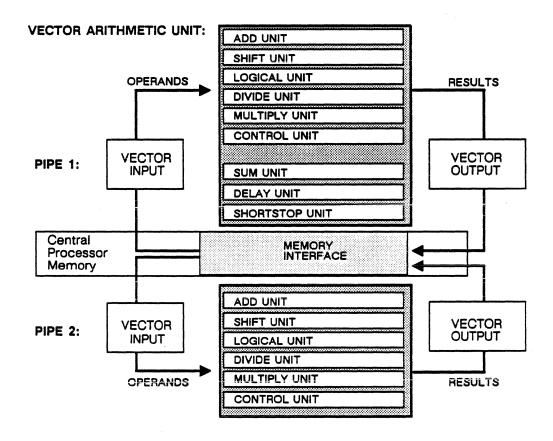

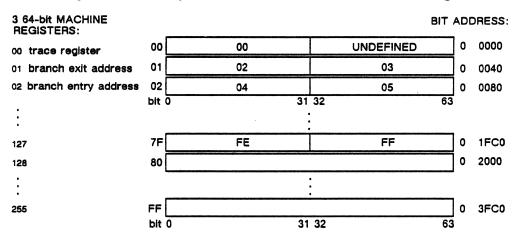

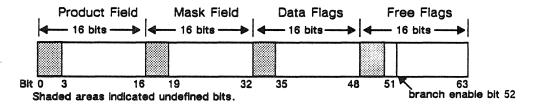

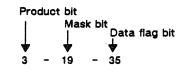

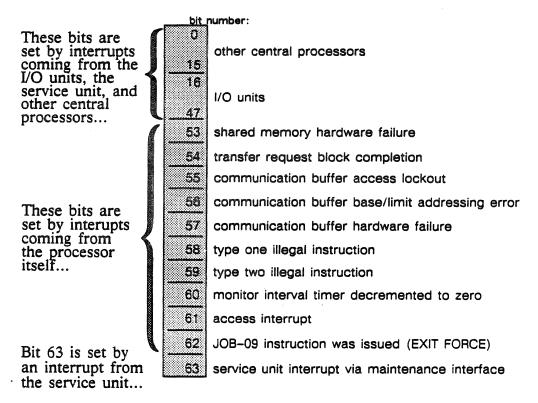

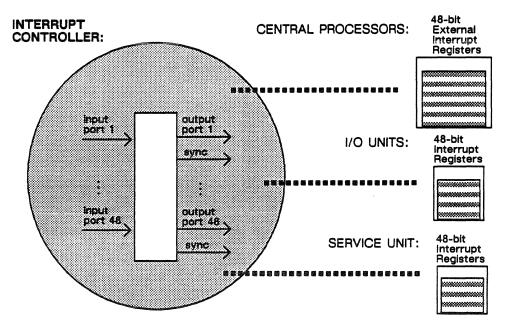

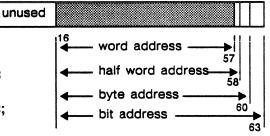

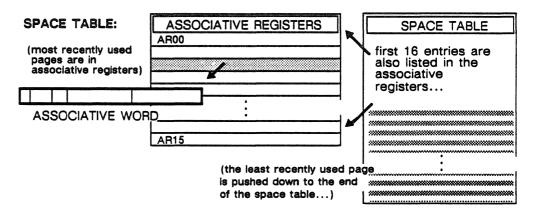

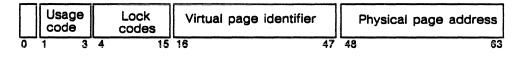

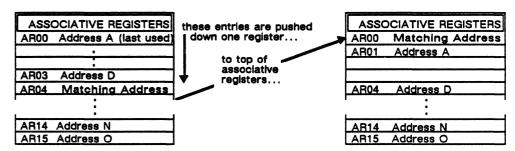

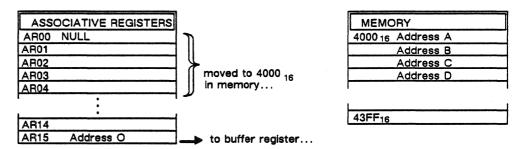

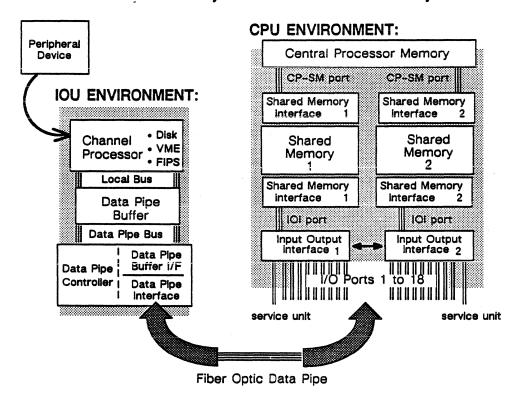

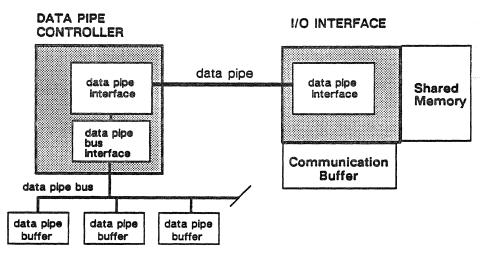

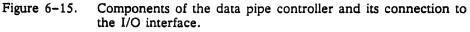

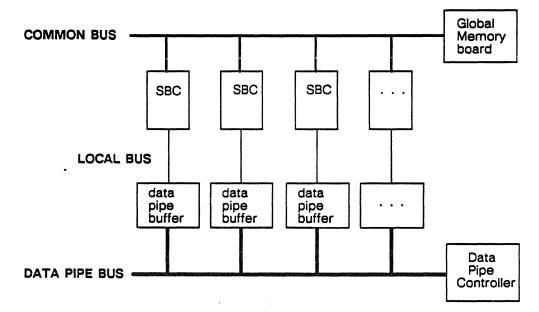

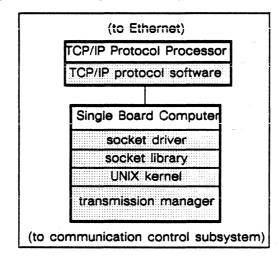

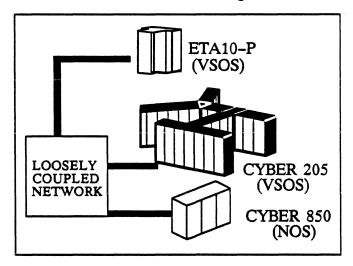

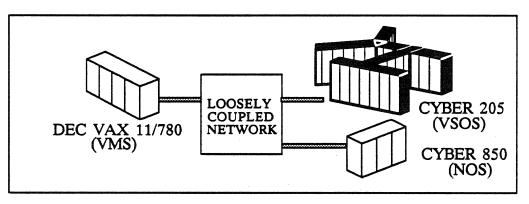

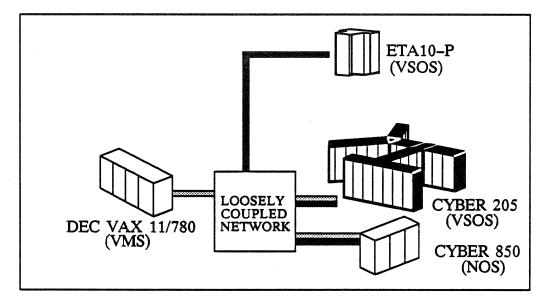

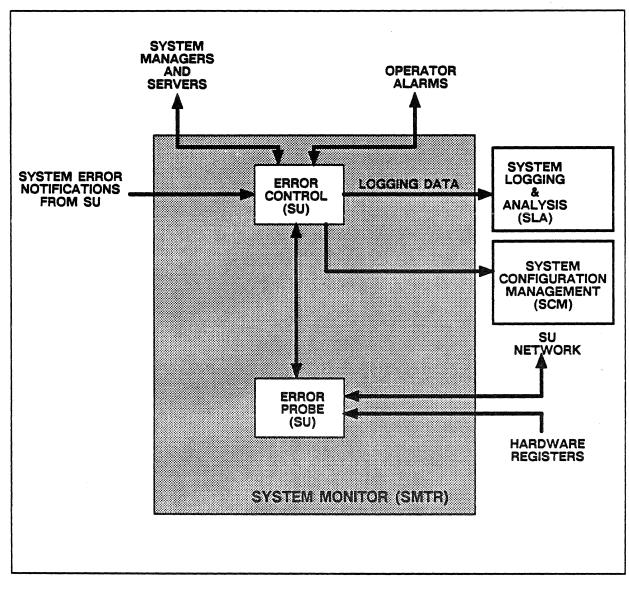

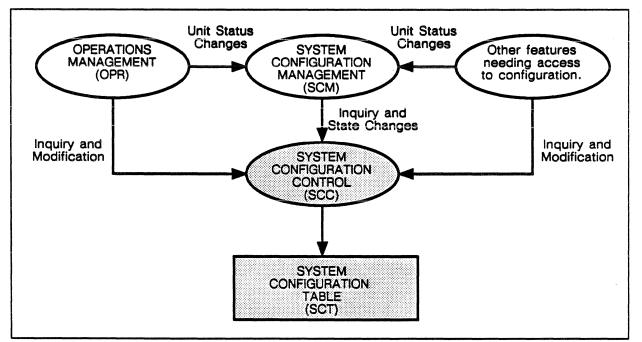

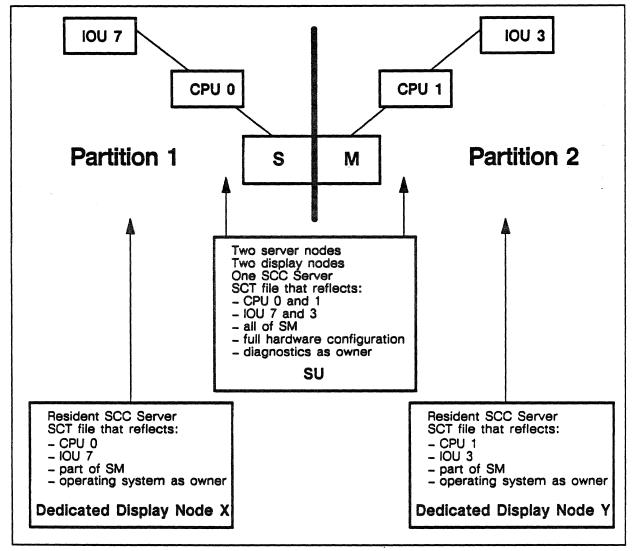

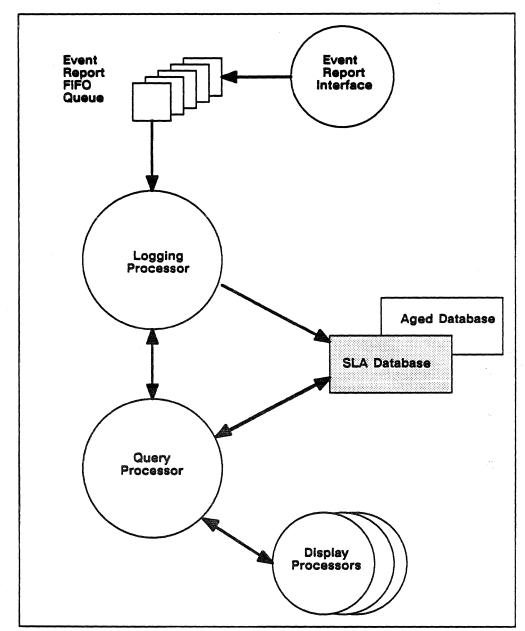

Table 2–1. VSOS Command Summary.