# **GD** CONTROL DATA

CDC® CYBER 170

COMPUTER SYSTEMS

MODELS 815, 825, 835, 845, AND 855

CDC® CYBER 180

COMPUTER SYSTEMS

MODELS 810, 830, 835, 840, 845, 850, 855, 860, AND 990

# **VIRTUAL STATE**

VOLUME II INSTRUCTION DESCRIPTIONS PROGRAMMING INFORMATION

## **REVISION RECORD**

| REVISION         | DESCRIPTION                                                                                                                                                                                                                                                              |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01<br>(06-06-83) | Manual released.                                                                                                                                                                                                                                                         |

| A<br>(04-15-84)  | Manual updated to add support of CYBER 170 Model 845 and CYBER 180 Models 810, 830, 835, 845, 855, and 990. Due to extensive changes, revision bars and dots are not used and all pages reflect the latest revision level. This edition obsoletes all previous editions. |

| B<br>(11-02-84)  | Manual updated to add support of CYBER 180 Models 840, 850, and 860.                                                                                                                                                                                                     |

| C<br>(05-03-85)  | Manual revised; includes Engineering Change Order 46891. Front Cover through 5, 7/8, 14, 16, II-1-30, II-2-1, II-2-78, II-2-127, II-2-129, II-2-130, II-2-134, II-2-136 through II-2-138, and II-2-145 through II-2-147 are revised. Page II-2-149 is added.             |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

| •                |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

|                  |                                                                                                                                                                                                                                                                          |

REVISION LETTERS I, O, Q, S, X AND Z ARE NOT USED.

© 1983, 1984, 1985 by Control Data Corporation All rights reserved Printed in the United States of America Address comments concerning this manual to:

Control Data Corporation Publications and Graphics Division 4201 North Lexington Avenue St. Paul, Minnesota 55112

or use Comment Sheet in the back of this manual.

# LIST OF EFFECTIVE PAGES

New features, as well as changes, deletions, and additions to information in this manual, are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

| PAGE               | REV    | PAGE               | REV | PAGE                 | REV    | PAGE               | REV    | PAGE                   | REV |

|--------------------|--------|--------------------|-----|----------------------|--------|--------------------|--------|------------------------|-----|

| Front Cover        | _      | II-1-42            | Α   | 11-1-101             | A      | 11-2-23            | A      | II-2-82                | A   |

| Title Page         | -      | II-1-43            | A   | II-1-102             | A      | 11-2-24            | A      | 11-2-83                | A   |

| 2                  | C      | II-1-44            | A   | II-1-103             | A      | II-2-25            | A      | II-2-84                | A   |

| 3                  | c      | II-1-45            | A   | II-1-104             | A      | II-2-26            | A      | II-2-85                | - A |

| 4                  | C      | II-1-46            | A   | II-1-105             | A      | 11-2-27            | A      | 11-2-86                | Α - |

| 5                  | C      | II-1-47            | A   | II-1-106             | A      | 11-2-28            | A      | II-2-87                | A   |

| 6                  | A      | II-1-48            | A   | II-1-107             | A      | II-2-29            | A      | 11-2-88                | A   |

| 7/8                | C      | II-1-49            | A   | II-1-108             | A      | II-2-30            | A      | 11-2-89                | A   |

| 9                  | В      | II-1-50            | A   | II-1-109             | A      | II-2-31            | A      | II-2-90                | A   |

| 10                 | A      | II-1-51            | A   | II-1-110             | A      | II-2-32            | A      | II-2-91                | A   |

| 11                 | A      | II-1-52            | A   | II-1-111             | A      | II-2-33            | A      | 11-2-92                | A   |

| 12                 | A      | II-1-53            | A   | II-1-112             | A      | 11-2-34            | A      | 11-2-93                | A   |

| 13                 | В      | II-1-54            | A   | II-1-113             | A      | II-2-35            | A      | II-2-94                | A   |

| 14                 | C      | II-1-55            | A   | II-1-114             | A      | 11-2-36            | A      | II-2-95                | A   |

| 15                 | В      | II-1-56            | A   | II-1-115             | A      | II-2-37            | A      | 11-2-96                | A   |

| 16                 | C      | II-1-57            | A   | II-1-116             | A      | II-2-38            | A      | II-2-97                | A   |

| II-1-1             | A      | II-1-58            | В   | II-1-117             | A      | II-2-39            | A      | 11-2-98                | A   |

| II-1-2             | A      | II-1-59            | A   | II-1-118             | A      | 11-2-40            | A      | 11-2-99                | A   |

| II-1-3             | A      | 11-1-60            | A   | II-1-119             | A      | 11-2-41            | A      | 11-2-100               | A   |

| II-1-4             | A      | II-1-61            | A   | II-1-120             | A      | II-2-42            | A      | II-2-101               | A   |

| II-1-5             | В      | II-1-62            | A   | II-1-121             | A      | 11-2-43            | A      | II-2-102               | A   |

| II-1-6             | A      | II-1-63            | В   | II-1-122             | A      | 11-2-44            | A      | 11-2-103               | В   |

| II-1-7             | A      | II-1-64            | A   | II-1-123             | A      | 11-2-45            | A      | 11-2-104               | A   |

| II-1-8             | A      | II-1-65            | A   | II-1-124             | A      | 11-2-46            | A      | II-2-105               | A   |

| II-1-9             | В      | II-1-66            | A   | II-1-125             | A      | II-2-47            | A      | 11-2-106               | A   |

| II-1-10            | В      | II-1-67            | A   | II-1-126             | A.     | 11-2-48            | A      | 11-2-107               | A   |

| II-1-11            | A      | 11-1-68            | A   | II-1-127             | A      | 11-2-49            | A      | 11-2-108               | Α.  |

| II-1-12            | A      | 11-1-69            | A   | 11-1-128             | A      | II-2-50            | A      | II-2-109<br>  II-2-110 | A   |

| II-1-13            | A      | 11-1-70            | A   | II-1-129             | A      | II-2-51            | A      |                        | A   |

| II-1-14            | A      | II-1-71            | A   | II-1-130<br>II-1-131 | A      | II-2-52            | A      | II-2-111               | A   |

| II-1-15<br>II-1-16 | A      | II-1-72<br>II-1-73 | A   | 11-1-131             | A<br>A | II-2-53            | A      | II-2-112<br>II-2-113   | A   |

| II-1-16<br>II-1-17 | A<br>A | II-1-74            | A   | 11-1-132             | A      | II-2-54<br>II-2-55 | A<br>A | II-2-113               | A   |

| II-1-17<br>II-1-18 | A      | II-1-75            | A   | II-1-134             | A      | II-2-56            | A      | II-2-114<br>II-2-115   | В   |

| II-1-18<br>II-1-19 | A      | II-1-76            | A   | 11-1-135             | A      | II-2-57            | A      | 11-2-115               | A   |

| II-1-19<br>II-1-20 | Â      | II-1-77            | A   | II-1-136             | A      | II-2-58            | A      | II-2-110<br>II-2-117   | A   |

| II-1-21            | A      | 11-1-78            | A   | 11-1-137             | A      | 11-2-59            | A      | 11-2-118               | Â   |

| 11-1-22            | В      | 11-1-79            | Â   | 11-2-1               | c      | 11-2-60            | Â      | 11-2-119               | A   |

| 11-1-23            | В      | 11-1-80            | Â   | 11-2-2               | Ă      | 11-2-61            | Â      | 11-2-120               | A   |

| II-1-24            | В      | II-1-81            | A   | II-2-3               | A      | 11-2-62            | A      | II-2-121               | В   |

| II-1-25            | В      | II-1-82            | A   | 11-2-4               | Ā      | 11-2-63            | A      | II-2-122               | A   |

| II-1-26            | В      | II-1-83            | A   | II-2-5               | A      | 11-2-64            | A      | II-2-123               | A   |

| II-1-26.1/         |        | II-1-84            | A   | 11-2-6               | A      | II-2-65            | A      | II-2-124               | A   |

| II-1-26.2          | В      | II-1-85            | A   | II-2-7               | A      | II-2-66            | Ā      | II-2-125               | Α   |

| II-1-27            | A      | 11-1-86            | A   | 11-2-8               | A      | II-2-67            | A      | 11-2-126               | A   |

| II-1-28            | A      | II-1-87            | A   | 11-2-9               | A      | 11-2-68            | A      | II-2-127               | C   |

| II-1-29            | A      | II-1-88            | A   | II-2-10              | A      | II-2-69            | A      | 11-2-128               | A   |

| II-1-30            | c      | II-1-89            | A   | II-2-11              | A      | II-2-70            | A      | II-2-129               | c   |

| II-1-31            | A      | II-1-90            | В   | 11-2-12              | A      | II-2-71            | A      | 11-2-130               | C   |

| II-1-32            | A      | II-1-91            | A   | II-2-13              | A      | II-2-72            | A      | 11-2-131               | Α   |

| II-1-33            | A      | II-1-92            | A   | 11-2-14              | В      | II-2-73            | A      | 11-2-132               | A   |

| II-1-34            | A      | II-1-93            | A   | II-2-15              | A      | II-2-74            | A      | II-2-133               | A   |

| II-1-35            | A      | II-1-94            | A   | II-2-16              | A      | II-2-75            | A      | II-2-134               | С   |

| II-1-36            | A      | II-1-95            | A   | II-2-17              | A      | 11-2-76            | A      | II-2-135               | A   |

| II-1-37            | A      | 11-1-96            | A   | II-2-18              | A      | II-2-77            | A      | II-2-136               | С   |

| II-1-38            | A      | II-1-97            | A   | 11-2-19              | A      | II-2-78            | c      | II-2-137               | C   |

| II-1-39            | A      | II-1-98            | A   | 11-2-20              | A      | 11-2-79            | A      | II-2-138               | С   |

| II-1-40            | A      | II-1-99            | A   | II-2-21              | A      | 11-2-80            | A      | II-2-139               | A   |

| II-1-41            | A      | II-1-100           | A   | 11-2-22              | A      | II-2-81            | A      | II-2-140               | A   |

| PAGE                 | REV    | PAGE       | REV | PAGE | REV | PAGE | REV      | PAGE | REV   |

|----------------------|--------|------------|-----|------|-----|------|----------|------|-------|

| II-2-141             | A      |            |     |      |     |      |          |      |       |

| 11-2-142             | A      |            |     |      |     |      |          |      |       |

| 11-2-143             | A      |            |     |      |     |      |          | ,    |       |

| 11-2-144             | A      |            |     |      | 1 1 |      |          |      |       |

| 11-2-145             | C      |            |     |      |     |      |          |      |       |

| 11-2-146             | C      |            |     |      |     |      |          |      |       |

| II-2-147<br>II-2-148 | C      | , i        |     |      | ŀ   | •    |          | 4    |       |

| II-2-149             | C      |            | 1   |      |     |      |          |      |       |

| II-A-1               | Ă      |            |     |      |     |      |          |      |       |

| II-A-2               | A      |            |     |      | l 1 |      |          |      | 1     |

| II-A-3               | A      |            |     |      | ] I |      |          |      |       |

| II-B-1               | A      |            | 1   |      | 1 1 |      |          |      |       |

| II-B-2               | A      |            |     |      |     |      |          |      | ŀ     |

| II-B-3<br>II-B-4     | A<br>A |            |     |      |     |      | İ        |      |       |

| II-B-4<br>II-B-5     | A      |            |     |      |     |      |          |      |       |

| II-C-1               | В      |            |     |      |     |      |          |      |       |

| II-C-2               | Ā      |            |     |      |     |      |          |      | 1     |

| II-C-3               | A      | 1          |     |      |     |      |          |      |       |

| II-C-4               | A      |            |     |      |     |      |          |      |       |

| II-C-5               | A      |            |     |      |     |      |          | 1    |       |

| II-C-6<br>II-C-7     | A      |            |     |      |     |      |          |      |       |

| II-C-7               | A      |            |     |      |     |      |          |      |       |

| II-C-9               | A      |            |     |      |     |      |          | '    |       |

| II-C-10              | A      |            |     |      |     |      | <b>!</b> |      |       |

| II-C-11              | A      |            |     |      |     |      |          |      |       |

| II-D-1               | A      |            |     |      |     |      | 1 1      | ł    |       |

| II-D-2               | A      |            |     |      |     |      |          |      | 1     |

| II-D-3               | В      |            |     |      | 1 1 |      | 1 1      |      |       |

| II-D-4<br>II-D-5     | B<br>B |            |     |      |     |      |          |      |       |

| 11-D-6               | A      |            |     |      |     |      |          |      |       |

| II-D-7               | В      |            |     |      |     |      |          |      |       |

| II-D-8               | A      |            | ŀ   |      |     |      |          |      |       |

| II-D-9               | A      |            |     |      |     |      |          |      |       |

| II-D-10              | A      |            |     |      |     |      |          |      |       |

| II-D-11              | A      |            |     |      |     |      | i i      |      | ] [   |

| II-D-12<br>II-D-13   | A<br>A |            |     |      |     |      |          |      |       |

| II-D-13<br>II-D-14   | A      |            |     |      |     |      |          |      |       |

| II-D-15              | A      |            | . [ |      |     |      | 1        |      |       |

| II-D-16              | A      |            |     | •    |     |      |          | 1    |       |

| Index-1              | В      |            | Ė   |      |     |      |          |      |       |

| Index-2              | В      | .          | .[  |      | 1   |      | 1        |      |       |

| Index-3              | В      |            |     |      |     |      | 1        |      |       |

| Index-4              | B<br>B |            |     | 1    |     |      |          |      |       |

| Index-5<br>Index-6   | В      |            |     |      |     |      |          | 1    |       |

| Index-7              | В      |            |     |      |     |      |          | * .  |       |

| Comment Sheet        | C      |            |     |      |     |      |          |      |       |

| Back Cover           | -      |            |     |      |     |      |          |      | 1 1   |

|                      | 1      |            |     |      |     |      | [        |      |       |

|                      | 1      |            |     |      |     |      |          |      |       |

|                      |        |            |     |      |     |      |          |      |       |

|                      |        |            |     |      |     |      |          |      |       |

|                      | 1      |            |     |      |     |      | .        |      |       |

| 1                    | ł      | <b>   </b> |     |      |     |      |          |      |       |

| 1                    |        |            |     |      |     |      |          |      | Į . I |

|                      |        |            |     |      |     | .    |          |      |       |

|                      |        |            |     |      |     |      |          |      |       |

|                      |        |            | '   |      |     | ` ·  |          |      |       |

|                      |        |            |     |      |     |      |          |      |       |

| 1                    | l:     |            | 1   |      | 1   |      |          |      |       |

|                      | 1      |            |     |      |     |      |          |      |       |

| 1                    | 1      |            |     |      |     |      |          |      | ļ     |

| 1                    |        |            |     |      |     |      |          | 4 4  |       |

|                      | I      |            |     |      |     |      |          |      |       |

|                      | 1      | ; <u> </u> |     | l    |     |      |          |      |       |

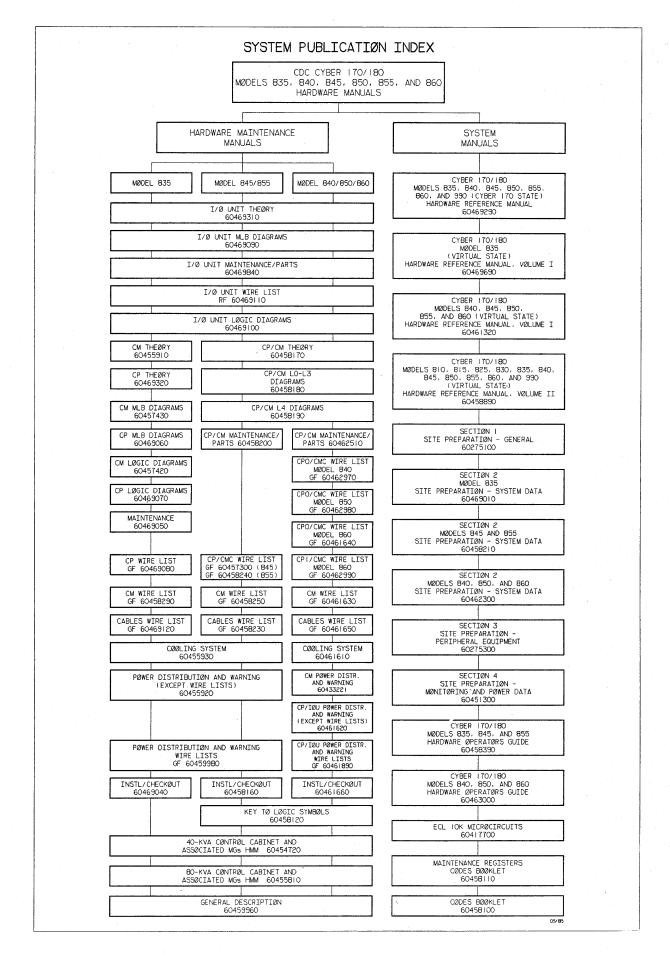

## PREFACE

This manual contains hardware reference information for the CDC® CYBER 170 Models 815, 825, 835, 845, and 855 computer systems, and the CYBER 180 Models 810, 830, 835, 840, 845, 850, 855, 860, and 990 computer systems, in their Virtual State of operation.

This manual provides model-independent instruction descriptions and programming information relative to the computer systems hardware. Additional hardware reference information regarding operation of the computer systems in both their CYBER 170 State and Virtual State environments is available in manuals listed in the system publications index on the following page.

## **AUDIENCE**

This manual is for use by programming and engineering services personnel who operate, program, and maintain the computer systems.

Other manuals applicable to the CYBER 170 and CYBER 180 computer systems are:

| Control Data Publication                                        | Publication Number |

|-----------------------------------------------------------------|--------------------|

| NOS Version 2 Operator/Analyst Handbook                         | 60459310           |

| NOS Version 2 Systems Programmer's Instant                      | 60459370           |

| NOS Version 1 Operator's Guide                                  | 60457700           |

| NOS Version 1 Systems Programmer's Instant                      | 60457790           |

| NOS/BE Version 1 Operator's Guide                               | 60457380           |

| NOS/BE Version 1 System Programmer's Reference Manual, Volume 1 | 60458480           |

| NOS/BE Version 1 System Programmer's Reference Manual, Volume 2 | 60458490           |

| NOS/VE Analysis Usage                                           | 60463915           |

| NOS/VE Operations Usage                                         | 60463914           |

| Codes Booklet                                                   | 60458100           |

| Maintenance Register Codes Booklet                              | 60458110           |

| CDC® 721 Enhanced Display Terminal (CC634B) HRM                 | 62950102           |

|                                                                 |                    |

Publication ordering information and latest revision levels are available from the Literature Distribution and Services catalog, publication number 90310500.

60458890 C

## WARNING

This equipment generates, uses and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. As temporarily permitted by regulation, it has not been tested for compliance with the limits for Class A computing device pursuant to Subpart J of Part 15 of the FCC Rules which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

# **CONTENTS**

| 1.  | INSTRUCTION DESCRIPTIONS               | II-1-1           | E-1 V1/V0 T 12                    |         |

|-----|----------------------------------------|------------------|-----------------------------------|---------|

| 1.  | INSTRUCTION DESCRIPTIONS               | 11-1-1           | Enter X1/X0, Immediate<br>Logical | 11-1-24 |

| Vir | tual State CP Instructions             | II-1-1           | Enter X1/X0, Signed               | 11 1 27 |

|     | Instruction Formats                    | II-1-1           | Immediate                         | II-1-25 |

|     | struction Description Nomenclature     |                  | Enter, Signed Immediate           | II-1-25 |

|     | errupts                                | II-1-3           | CP Shift Instructions             | II-1-25 |

|     | General Instructions                   | II-1-4           |                                   |         |

|     | CP Load and Store Instructions         | II-1-5           | Shift Word, Circular              | II-1-26 |

|     | Load/Store Multiple                    | II-1-6           | Shift End-Off, Word/Half-<br>Word | TT 1.07 |

|     | Load/Store Word                        | II-1-7           | CP Logical Instructions           | II-1-27 |

|     | Load/Store Word, Indexed               | II-1-7           |                                   | II-1-27 |

|     | Load/Store Address                     | II-1-8           | Logical Sum/Difference/           | TT 1 00 |

|     | Load/Store Address, Indexed            | II-1-8           | Product                           | II-1-28 |

|     | Load/Store Bytes                       | II-1-0<br>II-1-9 | Logical Complement                | II-1-28 |

|     | Load/Store Bytes, Immediate            | II-1-9           | Logical Inhibit                   | 11-1-29 |

|     |                                        | II-1-9           | CP Register Bit String            |         |

|     | Load Bytes, Relative<br>Load/Store Bit |                  | Instructions                      | 11-1-29 |

|     | · · · · · · · · · · · · · · · · · · ·  | II-1-10          | Bit String Descriptor             | 11-1-29 |

|     | CP Integer Arithmetic                  |                  | Isolate Bit Mask                  | II-1-30 |

|     | Instructions                           | II-1-11          | Isolate                           | II-1-30 |

|     | Half-Word Integer Sum                  | II-1-12          | Insert                            | II-1-30 |

|     | Integer Sum                            | II-1-13          | CP Mark to Boolean                |         |

|     | Half-Word Integer Difference           | II-1-14          | Instruction                       | II-1-30 |

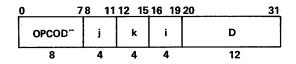

|     | Integer Difference                     | II-1-14          | BDP Instruction Descriptions      | II-1-31 |

|     | Half-Word Integer Product              | II-1-14          | BDP Nomenclature                  | II-1-32 |

|     | Integer Product                        | II-1-15          | BDP Numeric Instructions          | II-1-32 |

|     | Half-Word Integer Quotient             | II-1-15          | Decimal Arithmetic                | II-1-34 |

|     | Integer Quotient                       | II-1-16          | Decimal Compare                   | II-1-35 |

|     | Half-Word Integer/Integer              |                  | Numeric Move                      | II-1-36 |

|     | Compare                                | II-1-16          | Decimal Scale                     | II-1-37 |

|     | CP Branch Instructions                 | II-1-17          | BDP Byte Instructions             | II-1-38 |

|     | Branch Relative                        | II-1-17          | Byte Compare                      | II-1-39 |

|     | Branch Intersegment                    | II-1-18          | Byte Translate                    | II-1-40 |

|     | Branch on Half-Word                    | II-1-18          | Move Bytes                        | II-1-40 |

|     | Branch                                 | II-1-19          | Edit                              | II-1-41 |

|     | Branch and Increment                   | II-1-19          | Edit Mask                         | II-1-42 |

|     | Branch on Segments Unequal             | 11-1-20          | Edit Operation                    | II-1-42 |

|     | CP Copy Instructions                   | II-1-20          | MOP Description                   |         |

|     | Copy Address                           | II-1-21          | Nomenclature                      | II-1-42 |

|     | Copy Half Word                         | II-1-21          | End Suppression Toggle            | II-1-43 |

|     | Copy Full Word                         | II-1-22          | Special Characters Table          |         |

|     | CP Address Arithmetic                  |                  | Symbol                            | II-1-43 |

|     | Instructions                           | II-1-22          | Negative Sign Toggle              | II-1-43 |

|     | Address Increment, Indexed             | II-1-22          |                                   |         |

|     | Address Increment, Signed              | 11 1 22          | Zero Field Toggle                 | II-1-43 |

|     | Immediate                              | TT_1_22          | Skipping of Signs                 | II-1-44 |

|     | Address Relative                       | II-1-23          | Microoperation 0                  | II-1-44 |

|     |                                        | II-1-23          | Microoperation 1                  | II-1-44 |

|     | Address Increment, Modulo              | II-1-23          | Microoperation 2, 3               | II-1-44 |

|     | CP Enter Instructions                  | II-1-23          | Microoperation 4                  | II-1-44 |

|     | Enter Zeros/Ones/Signs                 | II-1-24          | Microoperation 5                  | II-1-44 |

|     | Enter, Immediate Positive/             |                  | Microoperation 6                  | II-1-45 |

|     | Negative                               | II-1-24          | Microoperation 7                  | II-1-45 |

60458890 B

| Microoperation 8                  | II-1-45            | Return                                        | II-1-74            |

|-----------------------------------|--------------------|-----------------------------------------------|--------------------|

| Microoperation 9 Microoperation A | II-1-45            | Pop                                           | II-1-75            |

| Microoperation B                  | II-1-46<br>II-1-46 | Copy Free Running Counter                     | II-1-76            |

| Microoperation C                  | II-1-46            | Test and Set Bit Test and Set Page            | II-1-77<br>II-1-77 |

| Microoperation D                  | II-1-46            | · · · · · · · · · · · · · · · · · · ·         | II-1-78            |

| Microoperation E                  | II-1-47            | Call Relative                                 | II-1-78            |

| Microoperation F                  | II-1-47            | Compare Swap<br>Call Indirect                 | II-1-81            |

| Edit Function NUMERIC             | II-1-47            |                                               | II-1-83            |

| Termination of the                | 11-1-47            | Reserved Operation Codes<br>Execute Algorithm | II-1-83            |

| Edit Instruction                  | II-1-47            | Local Privileged System                       | 11-1-05            |

| Byte Scan While Nonmember         | II-1-48            | Instructions                                  | II-1-83            |

| BDP Subscript and Immediate       | 11 1 40            | Load Page Table Index                         | II-1-84            |

| Data Instructions                 | II-1-48            | Global Privileged System                      | 11 1 04            |

| Calculate Subscript and Add       | II-1-49            | Instruction                                   | II-1-84            |

| Move Immediate Data               | 11-1-50            | Processor Interrupt                           | II-1-84            |

| Compare Immediate Data            | 11-1-51            | Monitor Mode Instructions                     | II-1-85            |

| Add Immediate Data                | 11-1-52            | Mixed-Mode Instructions                       | II-1-86            |

| Floating-Point Instruction        | 11 1 32            | Purge Buffer                                  | II-1-86            |

| Descriptions                      | II-1-52            | Copy to/from State Buffer                     | II-1-87            |

| Double-Precision Register         |                    | Branch on Condition Register                  | II-1-88            |

| Designators                       | II-1-53            | Peripheral Processor Instruction              | 11 1 00            |

| Floating-Point Conversion         |                    | Descriptions                                  | II-1-90            |

| Instructions                      | II-1-53            | PP Instruction Formats                        | II-1-90            |

| Convert From Integer to FP        | II-1-53            | PP Data Format                                | 11-1-90            |

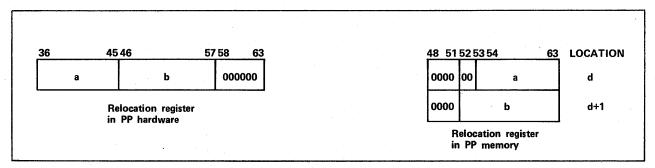

| Convert From FP to Integer        | II-1-53            | PP Relocation Register Format                 | II-1-91            |

| Floating-Point Arithmetic         |                    | PP Load and Store Instructions                | II-1-93            |

| Instructions                      | II-1-54            | PP Arithmetic Instructions                    | II-1-97            |

| Floating-Point Sum/               |                    | PP Logical Instructions                       | II-1-103           |

| Difference                        | II-1-55            | PP Replace Instructions                       | II-1-108           |

| Floating-Point Product            | II-1-56            | PP Branch Instructions                        | II-1-113           |

| Floating-Point Quotient           | II-1-57            | PP Central Memory Access                      |                    |

| Floating-Point Branch             | II-1-58            | Instructions                                  | II-1-116           |

| Normal Exit                       | II-1-58            | PP Input/Output Instructions                  | II-1-124           |

| Branch Exit                       | II-1-58            | Other IOU Instructions                        | II-1-135           |

| Group Interrupt Conditions        | II-1-58            | Exchange Jumps                                | II-1-136           |

| Floating-Point Branch on          |                    | Dicharge damps                                | 11 1 13            |

| Comparison                        | II-1-59            |                                               |                    |

| Floating-Point Branch on          | 22 2 37            | 2. PROGRAMMING INFORMATION                    | 11-2-1             |

| Condition                         | II-1-59            | 2. Involution Information                     |                    |

| Floating-Point Compare            | II-1-60            | CP Exchange Operations                        | II-2-1             |

| Vector Instruction Descriptions   | II-1-60            | Virtual State Job-to-Monitor                  |                    |

| Vector Instruction Format         | II-1-61            | Exchange Operations                           | II-2-3             |

| Integer Vector Arithmetic         | II-1-63            | Virtual State Monitor-to-Job                  | ,                  |

| Integer Vector Compare            | II-1-63            | Exchange Operations                           | II-2-3             |

| Logical Vector Arithmetic         | II-1-64            | Exchange Packages                             | II-2-3             |

| Integer/Floating-Point            |                    | CP Registers                                  | II-2-6             |

| Vector Conversion                 | II-1-64            | Process State Registers                       | II-2-6             |

| Floating-Point Vector             |                    | CP Base Constant (BC)                         | 11 2 0             |

| Arithmetic                        | II-1-64            | Register                                      | II-2-6             |

| Special Purpose Vector            | 0.                 | CP Debug Index (DI) Register                  |                    |

| Instructions                      | II-1-65            | CP Debug List Pointer (DLP)                   |                    |

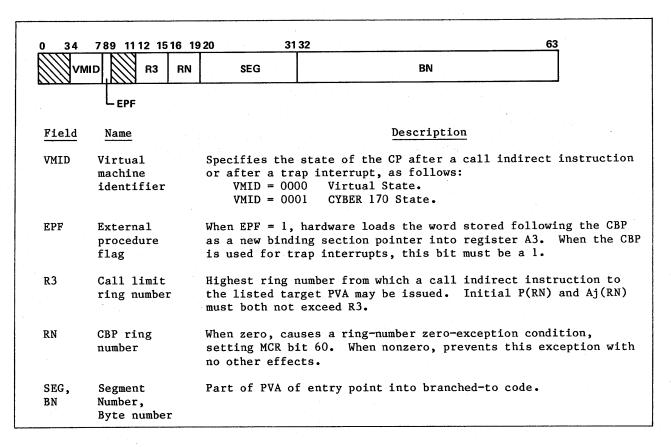

| System Instruction Descriptions   | II-1-71            | Register                                      | II-2-6             |

| Nonprivileged System              |                    | CP Debug Mask Register (DM)                   |                    |

| Instructions                      | II-1-72            | Register (MI)                                 | 11-2-7             |

| Program Error                     | II-1-72            | CP Flag Register                              | II-2-8             |

| Scope Loop Sync                   | II-1-73            | Critical Frame Flag                           |                    |

| Exchange                          | II-1-73            | (CFF)                                         | II-2-8             |

|    | On-Condition Flag (OCF)               | II-2-8          | CP Job Process State (JPS)       | 11-2-14      |

|----|---------------------------------------|-----------------|----------------------------------|--------------|

|    | Process-Not-Damaged                   | 0 0             | Register                         |              |

|    | (PND) Flag                            | 11-2-8          | CP Model Dependent Word (MDW)    |              |

|    | CP Largest Ring Number (LRN)          |                 | Register                         | 11-2-14      |

|    | Register                              | II-2-8          | CP_Monitor Process (MPS)         | 0 15         |

|    | CP Last Processor                     |                 | Register                         | 11-2-15      |

|    | Identification (LPID)                 |                 | CP System Interval Timer         | *            |

|    | Register                              | II-2-8          | (SIT) Register                   | II-2-15      |

|    | CP Monitor Condition Registe          | r               | CP Virtual Machine               |              |

|    | (MCR)                                 | II-2-8          | Capability List (VMCL)           | II-2-15      |

|    | CP Monitor Mask Register              | 11-2-8          | CM Registers                     | 11-2-16      |

|    | Operand X Registers                   | 11-2-9          | CM Corrected Error Log (CEL)     |              |

|    | CP Process Interval Timer             |                 | Register                         | 11-2-16      |

|    | (PIT)                                 | 11-2-9          | CM Element Identifier (EID)      |              |

|    | · · · · · · · · · · · · · · · · · · · |                 |                                  | II-2-17      |

|    | CP Program Address (P)                | TT 2 0          | Register                         | 11 2 17      |

|    | Register                              | II-2 <b>-</b> 9 | CM Environment Control (EC)      | II-2-17      |

|    | CP Segment Table Address              | 0 10            | Register                         |              |

|    | (STA) Register                        | 11-2-10         | CM Free-Running Counter Register | 11-2-17      |

|    | CP Segment Table Length               |                 | CM Options Installed (01)        | 0 1 <b>-</b> |

|    | (STL) Register                        | II-2-10         | Register                         | II-2-17      |

|    | CP Top-of-Stack (TOS)                 |                 | CM Port Bounds Register          | 11-2-17      |

|    | Pointer Register                      | 11-2-10         | CM Status Summary Register       | II-2-17      |

|    | CP Trap Enable (TE) Register          | II-2-10         | CM Uncorrectable Error Log       |              |

|    | CP Trap Pointer (TP)                  |                 | (UEL) Register                   | II-2-18      |

|    | Register                              | II-2-10         | IOU Registers                    | II-2-18      |

|    | CP Untranslatable Pointer             |                 | IOU Element Identifier (EID)     |              |

|    | (UTP) Register                        | II-2-11         | Register                         | II-2-19      |

|    | CP Untranslatable Virtual             |                 | IOU Environment Control (EC)     |              |

|    | Machine Identifier                    |                 | Register                         | II-2-19      |

|    | (UVMID) Register                      | 11-2-11         | IOU Fault Status (FS) Registers  | II-2-19      |

|    |                                       | 11 2 11         | IOU Fault Status Mask Register   | II-2-19      |

|    | CP User Condition Register            | 11-2-11         |                                  |              |

|    | (UCR)                                 |                 | IOU Options Installed (OI)       | 11-2-19      |

|    | CP User Mask Register (UMR)           | 11-2-11         | Register                         | 11-2-19      |

|    | CP Virtual Machine                    | TT 0 10         | IOU OS Bounds Register           | II-2-19      |

|    | Identifier (VMID) Register            |                 | IOU Status Summary Register      |              |

| CP | Processor State Registers             | 11-2-12         | IOU Test Mode (TM) Register      | 11-2-20      |

|    | CP Options Installed (OI)             |                 | CP Condition and Mask Registers  | 11-2-20      |

|    | Register                              | II-2-13         | CP Condition Register Bit        | 0 00         |

|    | CP Page Size Mask (PSM)               |                 | Grouping                         | 11-2-23      |

|    | Register                              | II-2-13         | CP Interrupts                    | II-2-25      |

|    | CP Page Table Address                 |                 | Exchange Interrupts              | 11-2-25      |

|    | (PTA) Register                        | II-2-13         | Trap Interrupts                  | II-2-25      |

|    | CP Page Table Length (PTL)            |                 | Interrupt Conditions             | 11-2-26      |

|    | Register                              | II-2-13         | Access Violation (MCR 54)        | II-2-26      |

|    | CP Processor Fault Status             |                 | Address Specification            |              |

|    | (PFS) Registers                       | II-2-13         | Error (MCR 52)                   | II-2-27      |

|    | CP Processor Identifier               | 11 2 15         | Arithmetic Loss-of-              |              |

|    |                                       | 11-2-13         | Significance (UCR 62)            | II-2-27      |

|    | (PID) Register                        | 11 2 15         | Arithmetic Overflow (UCR 57)     |              |

|    | CP Processor Test Mode (PTM)          | TT 0 10         | Code of Energy Elec (UCB 53)     | TT-2-29      |

|    | Register                              | II-2-13         | Critical Frame Flag (UCR 53)     |              |

|    | CP Status Summary (SS)                |                 | Debug (UCR 56)                   | II-2-28      |

|    | Register                              | 11-2-13         | Divide Fault (UCR 55)            | 11-2-28      |

|    | CP Cache/Map Corrected                |                 | Environment Specification        |              |

|    | Error Log (CCEL/MCEL)                 |                 | Error (MCR 55)                   | II-2-28      |

|    | Register                              | II-2-14         | Exponent Overflow (UCR 58)       | 11-2-29      |

|    | CP Dependent Environment              |                 | Exponent Underflow (UCR 59)      | II-2-29      |

|    | Control (DEC) Register                | 11-2-14         | External Interrupt (MCR 56)      | II-2-29      |

|    | CP Element Identifier (EID)           |                 | Floating-Point Indefinite        |              |

|    | Register                              | II-2-14         | (UCR 61)                         | II-2-29      |

|    | <del>-</del>                          |                 |                                  |              |

| Floating-Point Loss-of-         |         | Data Type 1: Packed         |         |

|---------------------------------|---------|-----------------------------|---------|

| Significance (UCR 60)           | 11-2-30 | Decimal, Unsigned Slack     |         |

| Free Flag (UCR 50)              | 11-2-30 | Digit                       | II-2-42 |

| Instruction Specification       |         | Data Type 2: Packed         |         |

| Error (MCR 51)                  | 11-2-30 | Decimal, Signed             | 11-2-43 |

| Inter-Ring Pop (UCR 52)         | 11-2-31 | Data Type 3: Packed         |         |

| Invalid BDP Data (UCR 63)       | 11-2-31 | Decimal, Signed, Slack      |         |

| Invalid Segment/Ring            |         | Digit                       | 11-2-43 |

| Number Zero (MCR 60)            | II-2-31 | Data Type 4: Unpacked       |         |

| Not Assigned (MCR 49)           | II-2-31 | Decimal, Unsigned           | II-2-43 |

| Outward Call/Inward Return      |         | Data Type 5: Unpacked       |         |

| (MCR 61)                        | II-2-31 | Decimal, Trailing Sign      |         |

| Page Table Search               |         | Combined Hollerith          | II-2-44 |

| Without Find (MCR 57)           | 11-2-32 | Data Type 6: Unpacked       |         |

| Privileged Instruction          |         | Decimal, Trailing Sign      |         |

| Fault (UCR 48)                  | II-2-32 | Separate                    | II-2-44 |

| Process Interval Timer          |         | Data Type 7: Unpacked       |         |

| (UCR 51)                        | II-2-32 | Decimal, Leading Sign       |         |

| Detected Uncorrectable          |         | Combined Hollerith          | II-2-44 |

| Error (MCR 48)                  | 11-2-32 | Data Type 8: Unpacked       |         |

| CYBER 170 State Exchange        | 11 2 32 | Decimal, Leading Sign       |         |

| Request (MCR 53)                | 11-2-32 | Separate                    | II-2-44 |

| Short Warning (MCR 50)          | 11-2-32 | Data Type 9: Alphanumeric   | 11-2-45 |

| Soft Error Log (MCR 62)         | 11-2-33 | Data Type 10: Binary,       | 11-2-4. |

| System Interval Timer           | 11-2-33 | * * ·                       | 11-2-45 |

|                                 | TT 2 22 | Unsigned                    | 11-2-4. |

| (MCR 59)                        | II-2-33 | Data Type 11: Binary,       | TT 2 /  |

| Trap Exception (MCR 63)         | 11-2-33 | Signed                      | II-2-45 |

| Unimplemented Instruction       | ~~ 0 00 | Slack Digit                 | 11-2-45 |

| (UCR 49)                        | II-2-33 | Undefined Results           | 11-2-45 |

| Multiple Interrupt Conditions   | 11-2-33 | Overlap                     | 11-2-45 |

| Flags                           | II-2-35 | Invalid Data                | II-2-45 |

| Stack Manipulating Operations   | II-2-36 | Vector Programming          | 11-2-46 |

| Stack Frames and Save Areas     | 11-2-36 | Vector Length (Number of    |         |

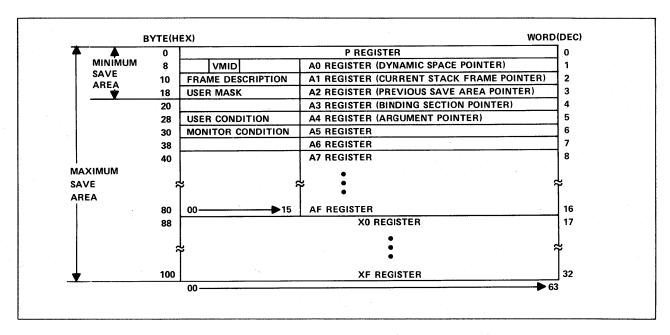

| Stack Frame Save Area Format    | II-2-36 | Operations)                 | 11-2-47 |

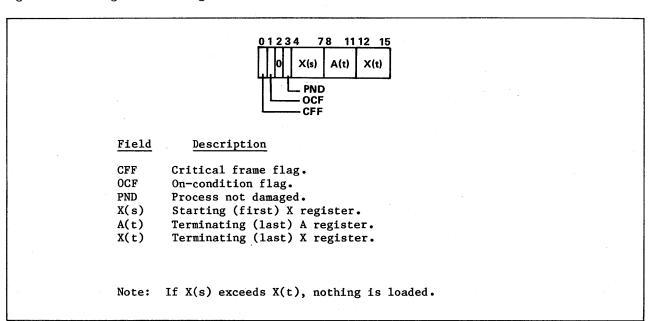

| Stack Frame Save Area           |         | Vector Page Size            | II-2-48 |

| Descriptor Field                | II-2-37 | Vector Broadcast            | II-2-48 |

| Virtual Machine Identifier      |         | Vector Interrupts           | II-2-48 |

| (VMID) Field                    | 11-2-38 | Vector Overlap              | II-2-48 |

| User Mask/Condition and         |         | Floating-Point Programming  | II-2-48 |

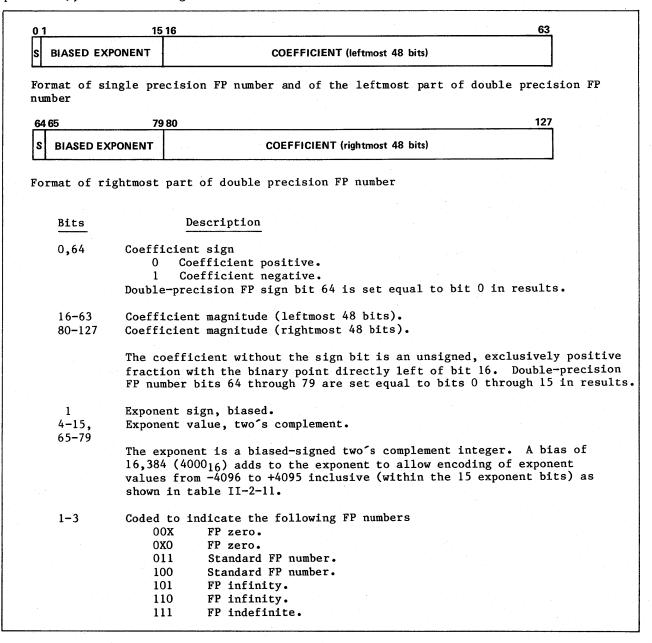

| Monitor Condition Fields        | II-2-39 | Floating-Point Data Formats | II-2-49 |

| Assigned Registers During Stack |         | Standard and Nonstandard FP |         |

| Operation                       | II-2-39 | Numbers                     | II-2-51 |

| Top-of-Stack Pointers           | II-2-39 | Floating-Point Zero         | 11-2-51 |

| Dynamic Space Pointer (A0)      | 11-2-39 | Floating-Point Nonzero      | II-2-51 |

| Current Stack Frame Pointer     |         | Floating-Point Infinite     | 11-2-51 |

| (A1)                            | II-2-39 | Floating-Point Indefinite   | 11-2-52 |

| Previous Save Area Pointer      | 11 2 37 | Double-Precision Non-       | 11 2 32 |

| (A2)                            | 11-2-39 | standard FP Numbers         | 11-2-52 |

| Binding Section Pointer         | 11 2 37 |                             | 11-2-52 |

| (A3)                            | 11-2-40 | Exponent Arithmetic         |         |

|                                 | II-2-40 | Normalization               | 11-2-52 |

| Argument Pointer (A4)           | 11-2-40 | Floating-Point Sum and      | TT 0 50 |

| Exceptions During Stack         | TT 2 40 | Difference                  | II-2-52 |

| Operations                      | 11-2-40 | Floating-Point Multiply     | II-2-53 |

| Business Data Processing        | TT 0 /0 | Floating-Point Divide       | II-2-53 |

| Programming                     | II-2-40 | Floating-Point End Cases    | II-2-54 |

| BDP Data Descriptors            | 11-2-40 | Program Monitoring          | II-2-64 |

| BDP Data Types                  | 11-2-41 | Debug                       | 11-2-64 |

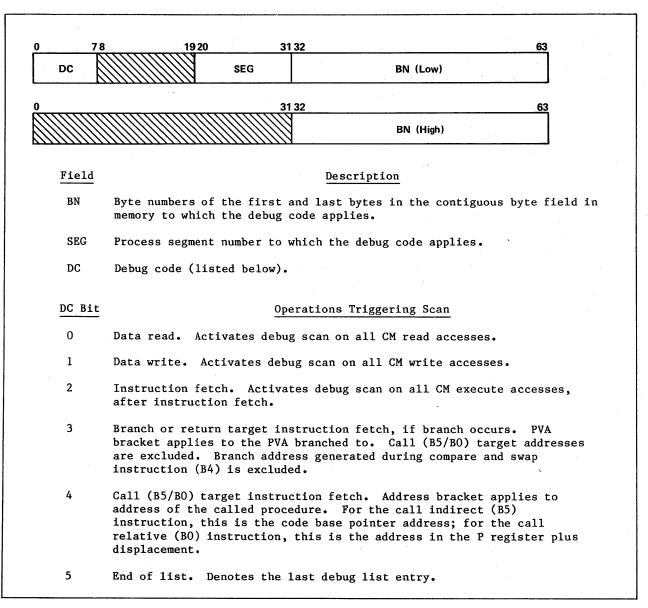

| Data Type 0: Packed             | 0       | Debug List                  | II-2-64 |

| Decimal, Unsigned               | 11-2-42 | Debug List Pointer Register | II-2-65 |

|                                 |         |                             |         |

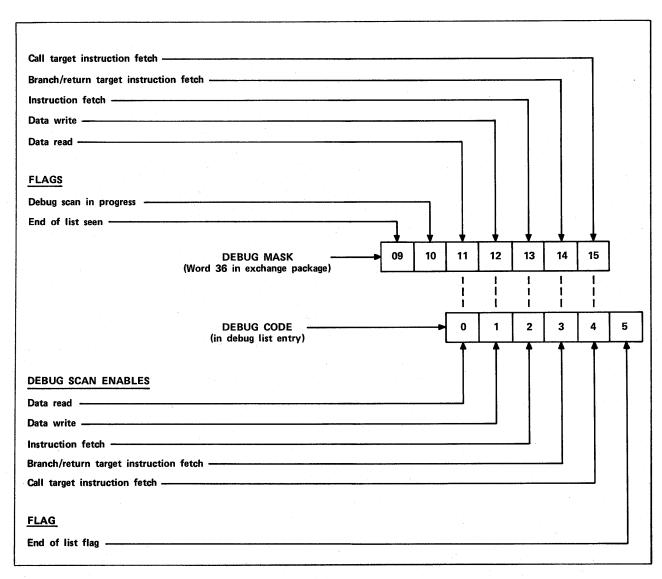

| Debug Index Register              | 11-2-65              | Return from Virtual State                                    |           |

|-----------------------------------|----------------------|--------------------------------------------------------------|-----------|

| Debug Mask Register               | 11-2-66              | <del></del>                                                  | II-2-105  |

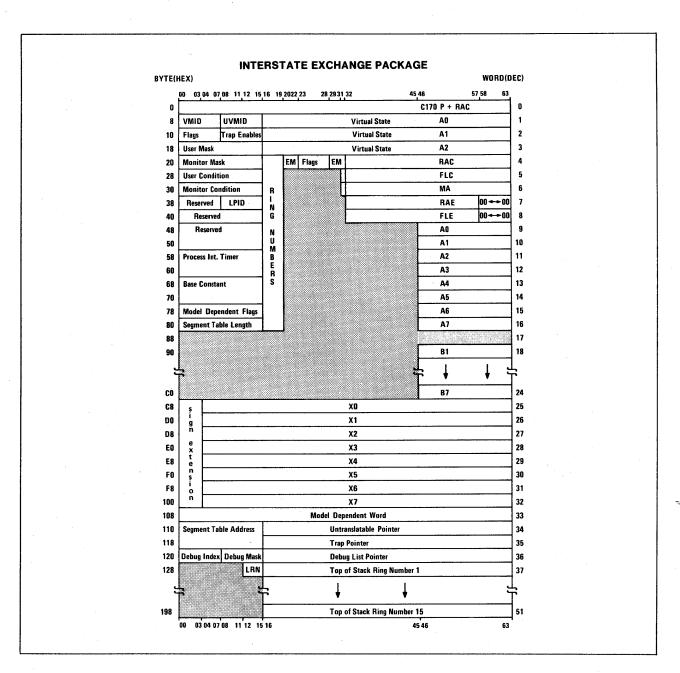

| Enabling Debug                    | II <b>-</b> 2-68     | Exchange Packages used in                                    | _         |

| Debug Scan Operation              | 11-2-68              | CYBER 170 State                                              | II-2-107  |

| Interrupts During Debug Scan      | 11-2-69              |                                                              | 11-2-107  |

| Debug-Software Interaction,       |                      | Program Address (P)                                          |           |

| Debug Enabled                     | 11-2-70              | Register                                                     | II-2-109  |

| Debug-Software Interaction,       |                      | Stack Pointers                                               | II-2-109  |

| Debug Disabled                    | II-2-70              | EM Register                                                  | 11-2-109  |

| Virtual and Central Memory        |                      | Flags                                                        | 11-2-110  |

| Programming                       | II-2-77              | Unified Extended Memory                                      |           |

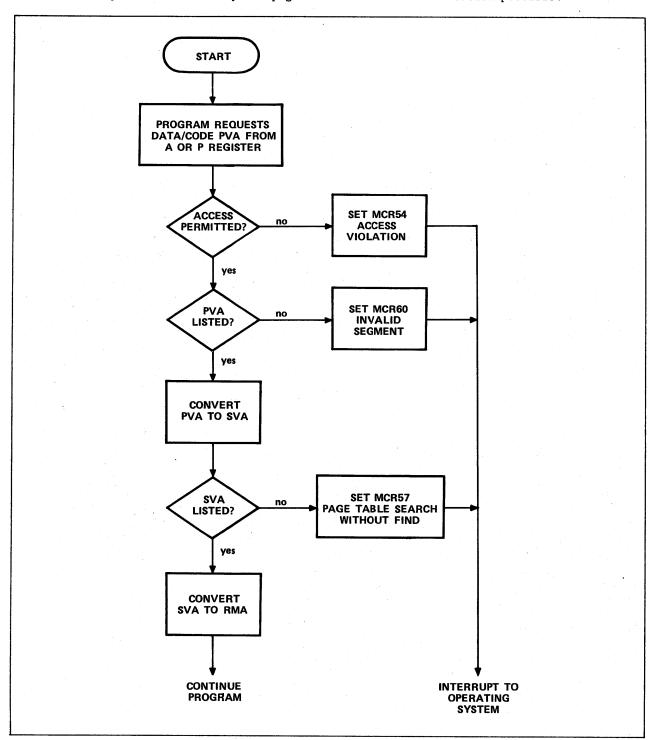

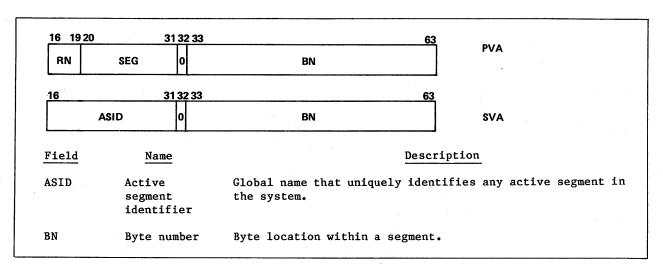

| Process Virtual Memory            | 11-2-78              | (UEM) Enable Flag                                            | 11-2-110  |

| System Virtual Memory             | 11-2-78              | Expanded Addressing                                          |           |

| Real Memory                       | II-2-79              | Select Flag                                                  | 11-2-110  |

| Address Tables                    | 11-2-83              | Enhanced Block Copy Flag                                     | II-2-110  |

| Segment Descriptor Table          | II-2-84              | Software Flag (Word 4,                                       |           |

| System Page Table                 | II-2 <b>-</b> 86     | Bit 28)                                                      | 11-2-110  |

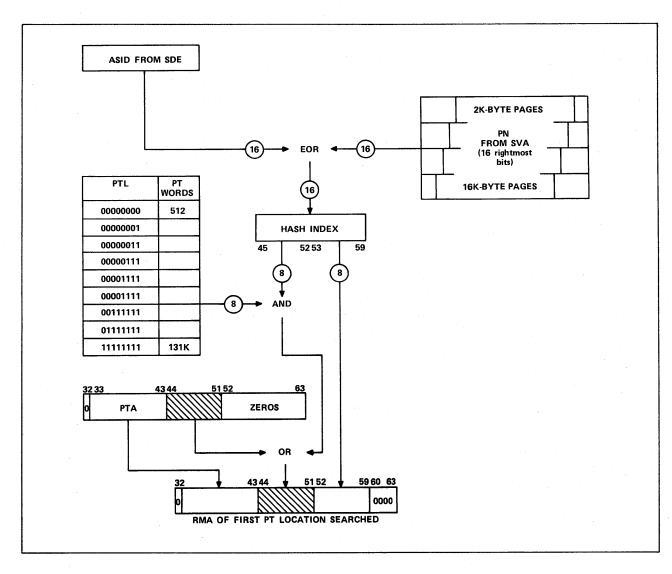

| Page Table Search                 | 11-2-86              | Instruction Stack Purge                                      |           |

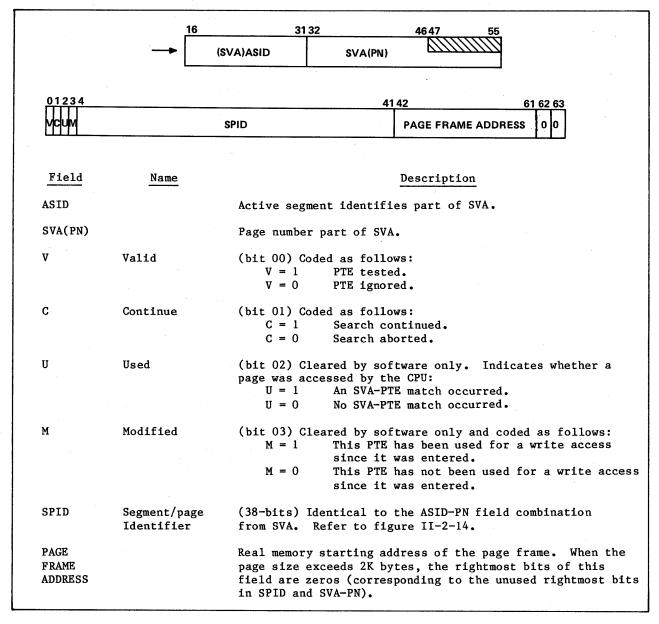

| Page Table Entries                | 11-2-87              | Flag                                                         | II-2-111  |

| PTE Control Fields                | 11-2-88              | Software Flag (Word 4,                                       |           |

| PTE Segment/Page                  |                      | Bit 26)                                                      | II-2-111  |

| Identifier Field                  | II-2-88              | CYBER 170 State Monitor                                      |           |

| PTE Page Frame KMA Field          | II-2-89              | Flag                                                         | II-2-111  |

| Listing of Pages in               |                      | Exit Mode Halt Flag                                          | 11-2-111  |

| Page Table                        | 11-2-90              | RAC Register                                                 | II-2-111  |

| Process Binding Section           | II-2-90              | FLC Register                                                 | II-2-111  |

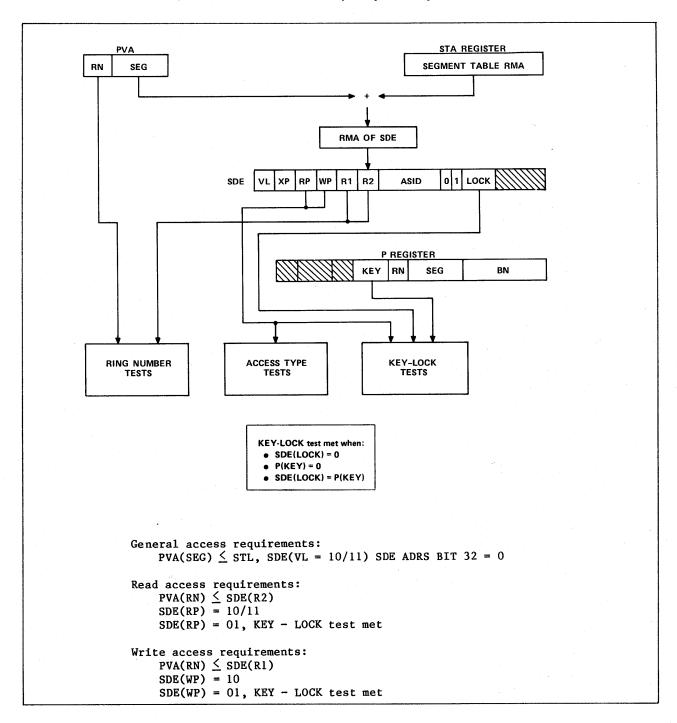

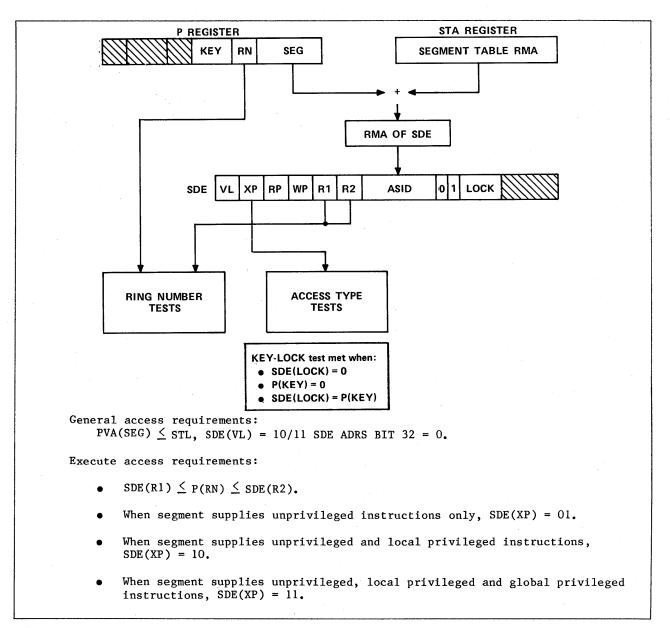

| Access Protection                 | 11-2-91              | Monitor Address (MA)                                         |           |

| Ring Structure                    | 11-2-95              | Register                                                     | II-2-111  |

| Ring Voting                       | 11-2-95              | Address (A) Registers                                        | II-2-112  |

| Effect of RN = 0                  | II-2-96              | RAE Register                                                 | II-2-112  |

| RN for Read/Write Access          |                      | FLE Register                                                 | II-2-112  |

| RN for Execute Access             | 11-2-96              | Virtual State Ring                                           |           |

| RN Effect on Pop                  | 11-2-90              | Numbers                                                      | II-2-112  |

| Instruction                       | 11-2-97              | Index (B) Registers                                          | II-2-112  |

| Effect of RN Violations           | II-2-98              | Operand (X) Registers                                        | 11-2-112  |

| _                                 | 11-2-90              | CYBER 170 State Exchange Package                             |           |

| Execute Access Privilege/<br>Mode | 11-2-98              | Interstate Stack Frame Save Area                             |           |

|                                   | 11-2-99              | Code Modification in CYBER 170                               | 11 2 113  |

| Keys/Locks                        | II-2-102             | State                                                        | II-2-115  |

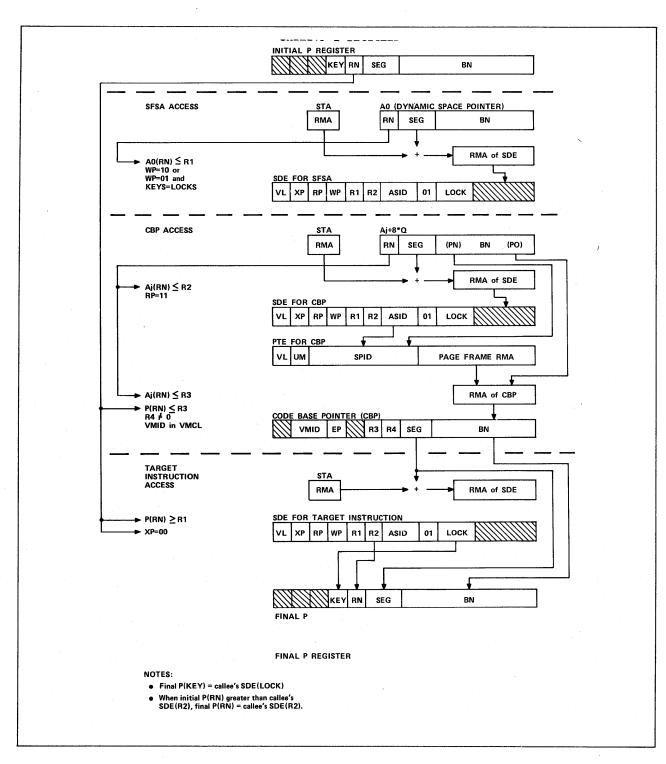

| Interstate Programming            | II-2-102<br>II-2-102 |                                                              | II-2-115  |

| Operation in CYBER 170 State      | 11-2-102             | Debug/Performance Monitoring Exception Handling in CYBER 170 | 11-2 113  |

| Memory Addressing in CYBER 170    | TT 0 100             |                                                              | 11-2-115  |

| State                             | 11-2-103             | State                                                        | II-2-115  |

| Cache Invalidation in CYBER 170   |                      | Software Exception Conditions                                | II-2-119  |

| State (Models 835 through         | TT 0 100             | Address Errors                                               | II-2-119  |

| 860 Only)                         | II-2-103             | Illegal Instructions                                         | 11-2-120  |

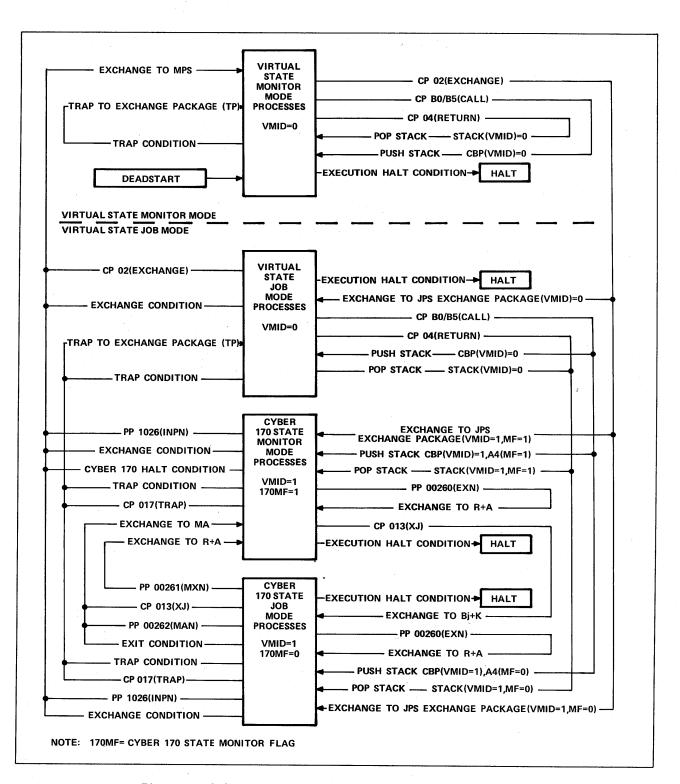

| State-Switching Operations        | 11-2-104             | Extended Memory Transfer                                     | II-2-120  |

| Virtual State Monitor Mode-       |                      | Exceptions                                                   | 11-2-120  |

| to-CYBER 170 State                | 0 10/                | Hardware Exceptions in                                       | TT 0 101  |

| Exchange                          | 11-2-104             | CYBER 170 State                                              | 11-2-121  |

| CYBER 170 State-to-               |                      | 10U Peripheral Processor                                     | TT 0 101  |

| Virtual State Monitor             |                      | Programming                                                  | II-2-121  |

| Mode Exchange                     | 11-2-104             | Central Memory Addressing by                                 | TT. 0 101 |

| Exchanges Within CYBER 170        |                      | PPs                                                          | 11-2-121  |

| State                             | II-2-104             | Absolute and Relocation                                      |           |

| Call from Virtual State           |                      | Addressing                                                   | 11-2-121  |

| to CYBER 170 State                | 11-2-105             | OS Bounds Test                                               | 11-2-122  |

| Trap Interrupt from               |                      | PP Central Memory Read                                       | 11-2-122  |

| CYBER 170 State to                |                      | PP Central Memory Write                                      | 11-2-122  |

| Virtual State                     | II-2-105             | PP Memory Addressing by PPs                                  | II-2-123  |

13

| Direct 6-Bit Operand            | 11-2-123 | IOU Dedicated Channels           | II-2-136   |

|---------------------------------|----------|----------------------------------|------------|

| Direct 18-Bit Operand           | 11-2-123 | Two-Port Multiplexer Programming | 11-2-138   |

| Direct 6-Bit Address            | 11-2-123 | Function Words                   | 11-2-139   |

| Direct 12-Bit Address           | 11-2-123 | Terminal Select (7XXX)           | 11-2-139   |

| Indexed 12-Bit Address          | 11-2-123 | Terminal Deselect (6XXX)         | II-2-139   |

| Indirect 6-Bit Address          | 11-2-123 | Calendar Clock/Auto Dial-        |            |

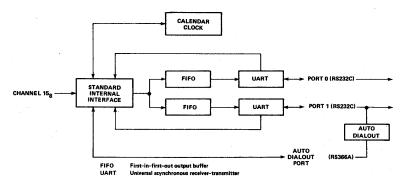

| Channel Input/Output Operations | 11-2-124 | Out (1XXX)                       | 11-2-140   |

| Channel Flags                   | II-2-124 | Read Summary Status (00XX)       | II-2-141   |

| Channel Active Flag             | II-2-124 | PP Terminal Data (OlXX)          | 11-2-141   |

| Register-Full Flag              | II-2-124 | PP Write Output Buffer           |            |

| Channel (Marker) Flag           | 11-2-125 | (02XX)                           | II-2-142   |

| Error Flag                      | II-2-125 | Set Operation Mode to            |            |

| Programming for Channel Input/  |          | Terminal (03XX)                  | II-2-142   |

| Output                          | II-2-125 | Set/Clear Data Terminal          |            |

| Inter-PP Communications         | II-2-126 | Ready (DTR) (04XX)               | II-2-143   |

| PP Program Timing Consideration | II-2-127 | Set/Clear Request to Send        |            |

| Cache Invalidation              | II-2-127 | (RTS) (05XX)                     | II-2-143   |

| Error Detection and Recovery    | II-2-128 | Master Clear (07XX)              | II-2-143   |

| PP Hardware Errors              | II-2-128 | Programming Considerations       | II-2-143   |

| Channel Parity Errors           | II-2-128 | Data Output                      | II-2-143   |

| Parity Errors on Output         |          | Data Input                       | II-2-144   |

| Data                            | 11-2-128 | Maintenance Channel Programming  | II-2-144   |

| Parity Errors on Input          |          | MCH Function Words               | II-2-144   |

| Data                            | 11-2-129 | MCH Control Words                | II-2-145   |

| Timeout                         | II-2-129 | MCH Programming for Halt/        |            |

| Initialization                  | II-2-129 | Start (Opcode $0/1$ )            | II-2-145 💂 |

| Display Station Programming     |          | MCH Clear LED (Opcode 3)         | II-2-145   |

| (Channel 10 <sub>8</sub> )      | 11-2-130 | MCH Programming for Read/        | _          |

| Keyboard                        | 11-2-130 | Write (Opcode 4/5)               | II-2-146   |

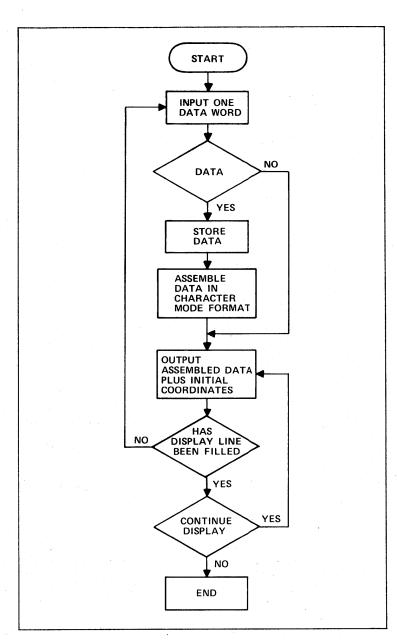

| Data Display                    | II-2-130 | MCH Programming for Master       |            |

| Character Mode                  | II-2-130 | Clear/Clear Errors               |            |

| Dot Mode                        | II-2-130 | (Opcode 6/7)                     | II-2-147   |

| Codes                           | II-2-133 | MCH Echo (Opcode 8)              | II-2-147   |

| Programming Example             | 11-2-134 | MCH Programming for Read         | -          |

| Program Timing Consideration    | 11-2-134 | IOU Summary Status               |            |

| Real-Time Clock Programming     | 11-2-136 | (Opcode C, IOU Only)             | II-2-147   |

|                                 |          |                                  |            |

|                                 |          |                                  |            |

## **APPENDIXES**

| A. GLOSSARY              | II-A-1 | Twelve-Bit Channel         |        |

|--------------------------|--------|----------------------------|--------|

|                          | ,      | Control Signals            | II-C-2 |

|                          |        | Maintenance Channel        |        |

| B. EDIT EXAMPLES         | II-B-1 | Signals                    | II-C-3 |

|                          |        | Control Signals            | II-C-3 |

|                          |        | Signals and Cables         | II-C-3 |

| C. INTERFACE INFORMATION | II-C-1 | Data Signals               | II-C-5 |

|                          |        | PP and Channel Interaction | II-C-5 |

| Interfaces               | II-C-1 | Active Flag                | II-C-5 |

| Twelve-Bit External      |        | Full Flag                  | II-C-5 |

| Interface                | II-C-1 | Function Instructions      | II-C-5 |

| Maintenance Channel      |        | External Channel Input/    |        |

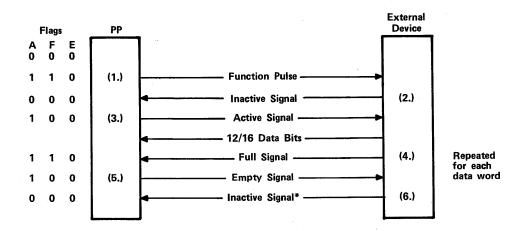

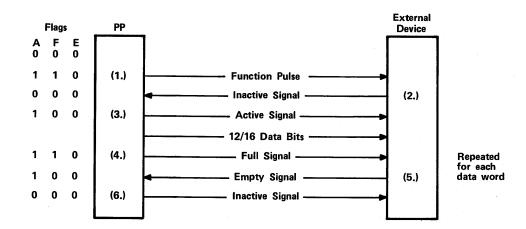

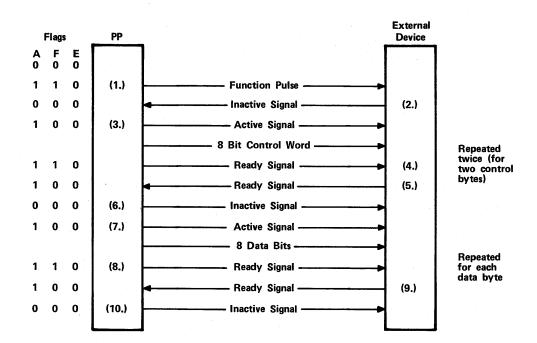

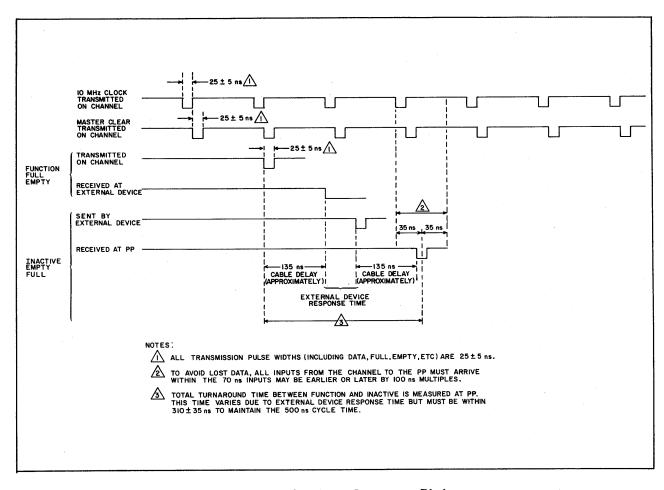

| Interface                | II-C-1 | Output Sequences           | II-C-5 |

| Two-Port Multiplexer     |        |                            |        |

| Interface                | II-C-1 |                            |        |

| Signals                  | II-C-2 | D. INSTRUCTION INDEX       | II-D-1 |

## **INDEX**

# **FIGURES**

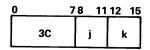

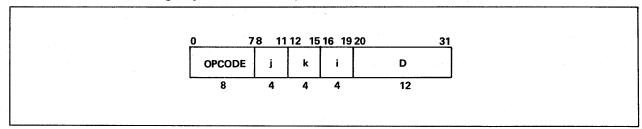

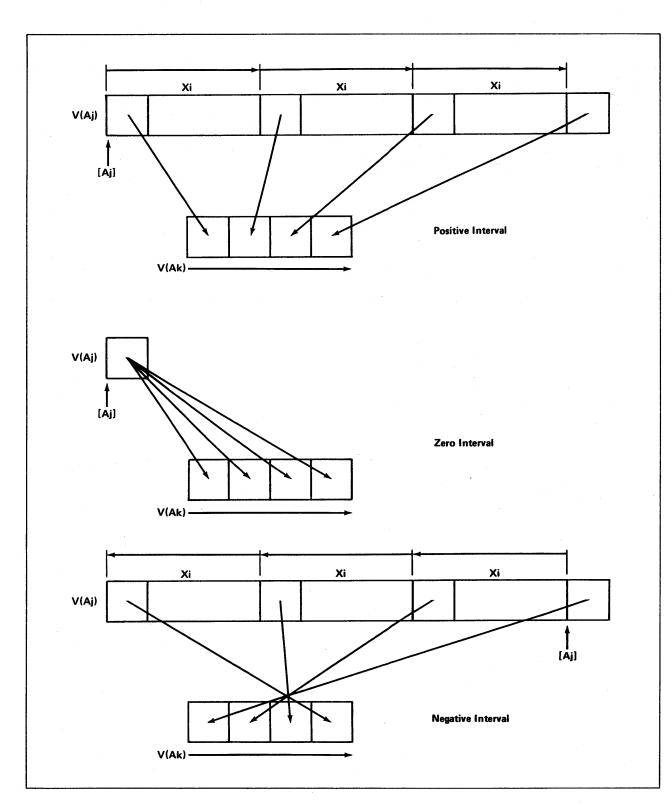

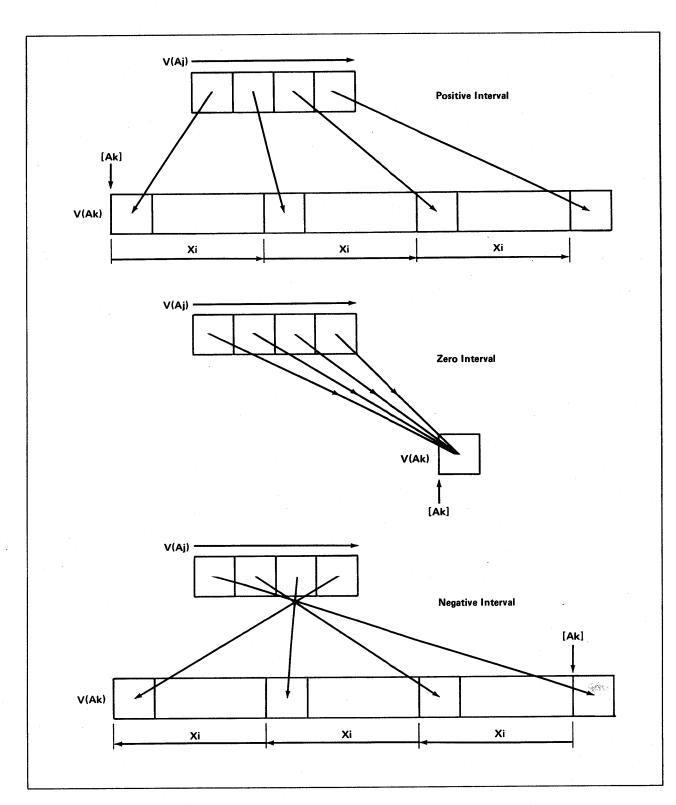

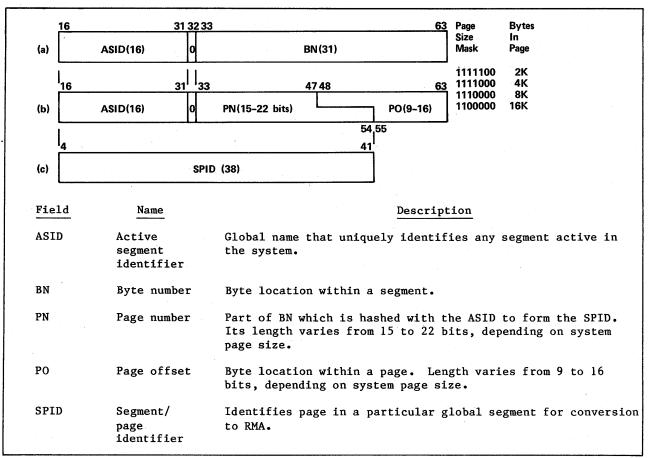

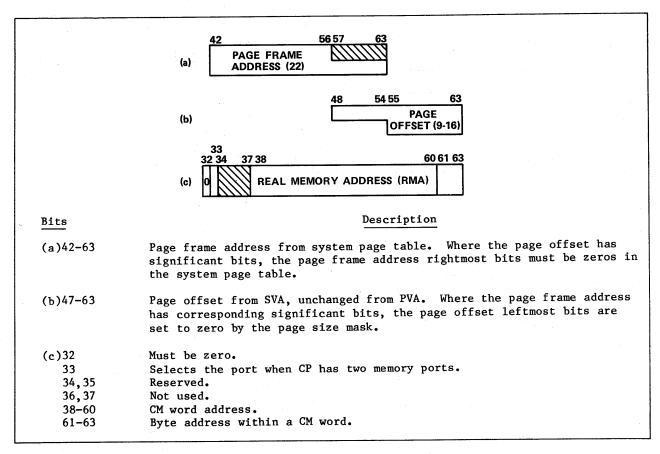

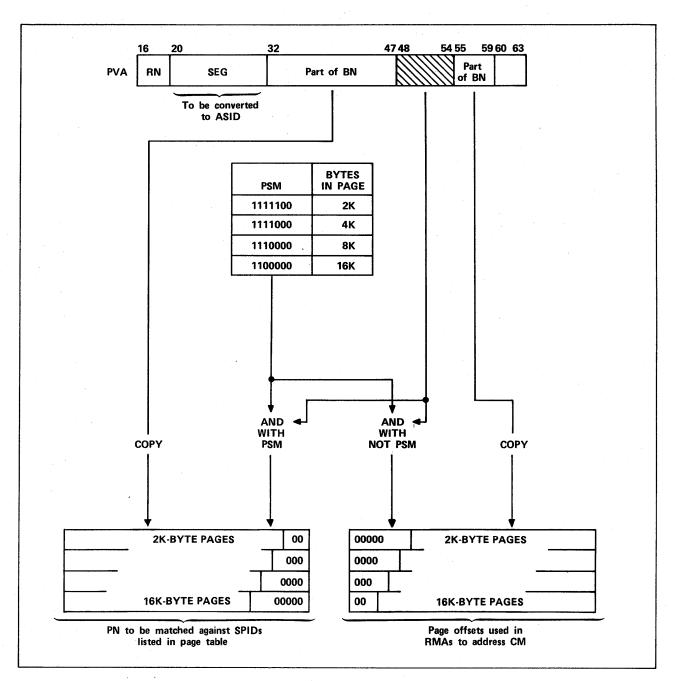

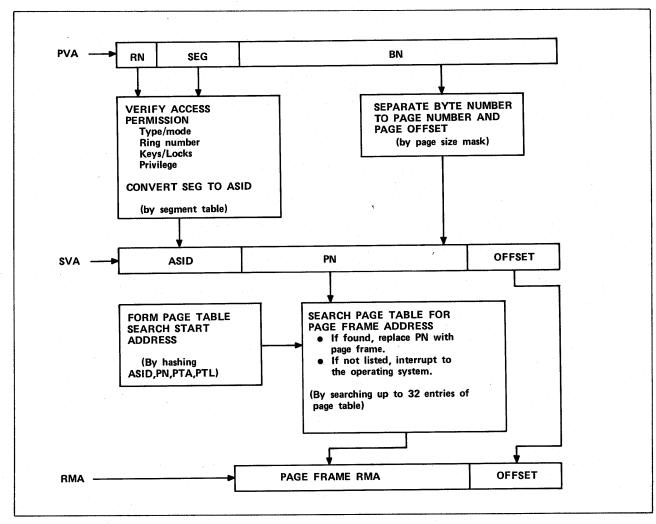

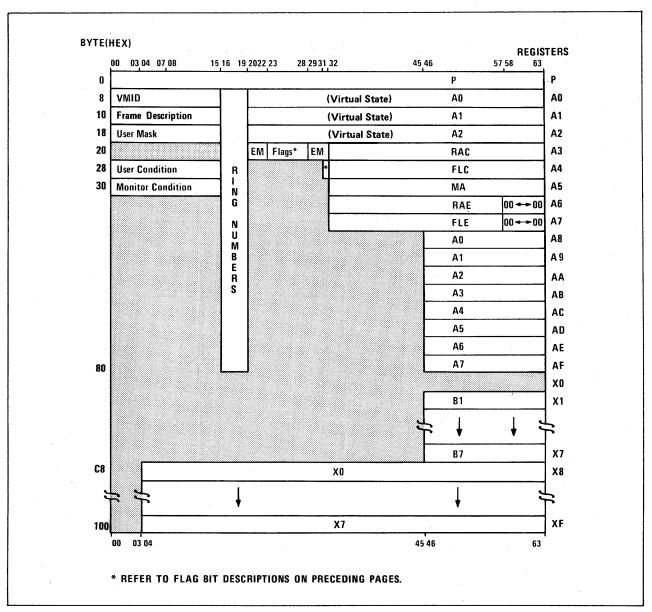

| II-1-1           | Vector Instruction Format             | II-1-61              | II-2-16            | Virtual BN-to-Page Number/  | 0 00               |

|------------------|---------------------------------------|----------------------|--------------------|-----------------------------|--------------------|

| II-1-2           | Gather Instruction                    | II-1-67              |                    | Page Offset Conversion      | 11-2-82            |

| II-1-3           | Scatter Instruction                   | II-1-69              | II-2-17            | PVA-to-RMA Conversion       | 11-2-83            |

| II-1-4           | PP Instruction Formats                |                      | 11-2-18            | Segment Descriptor Table    |                    |

|                  | and Nomenclature                      | II-1-91              |                    | Entry Format                | II-2-85            |

| II-1-5           | PP Data Format                        | II-1-92              | II-2-19            | Page Table Search, Start    |                    |

| II-1-6           | PP Relocation Register                |                      |                    | RMA Formation               | 11-2-87            |

|                  | Format                                | II-1-92              | II-2-20            | Page Table Entry Format     | 11-2-89            |

| II-1-7           | Relocation and Address                |                      | 11-2-21            | Code Base Pointer Format    | 11-2-91            |

|                  | Formation                             | II-1-117             | II-2-22            | PVA-to-SVA Conversion,      |                    |

| II-2-1           | CP Calls, Returns and                 |                      |                    | Read/Write                  | II-2-93            |

|                  | Interrupts                            | II-2-2               | II-2-23            | PVA-to-SVA Conversion,      |                    |

| II-2-2           | Virtual State Exchange                |                      |                    | Execute                     | II-2-94            |

|                  | Package                               | II-2-5               | II-2-24            | Call Indirect Access        |                    |

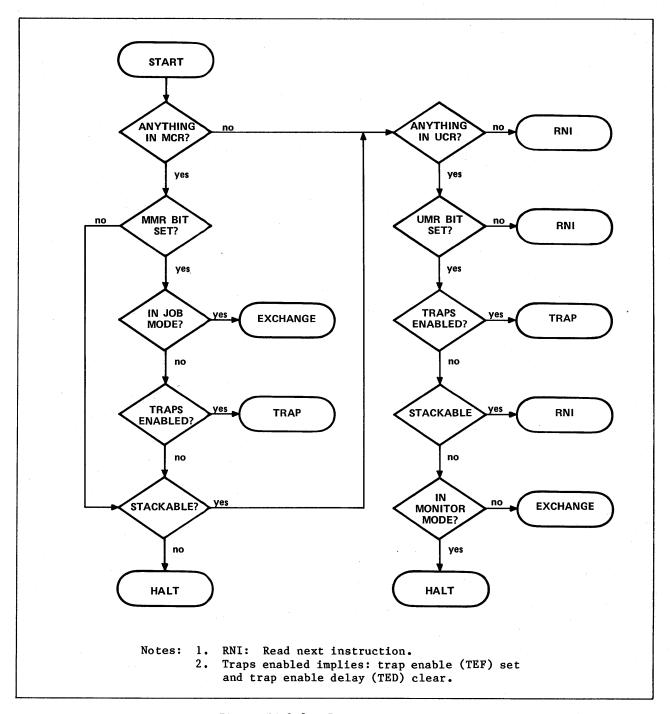

| II-2-3           | Interrupt Flowchart                   | II-2-34              |                    | Requirements                | II-2-101           |

| II-2-4           | Format of XO for Call                 |                      | 11-2-25            | Interstate Calls, Returns   |                    |

|                  | Instructions                          | II-2-37              |                    | and Interrupts              | II-2-106           |

| II-2-5           | Virtual State Stack Frame             | 11 2 3,              | 11-2-26            | Interstate Exchange         |                    |

| 11 2 3           | Save Area                             | 11-2-37              | 11 2 20            | Package                     | 11-2-108           |

| II-2-6           | Stack Frame Save Area                 | 11 2 37              | 11-2-27            | CYBER 170 State Exchange    | 11 1 100           |

| 11-2-0           | Descriptor                            | 11-2-38              | 11-2-21            | Package                     | 11-2-113           |

| II-2-7           | •                                     | II-2-41              | II-2-28            | Interstate Stack Frame      | 11 2 113           |

|                  | BDP Data Descriptor Format            | 11-2-41              | 11-2-20            |                             | 11-2-114           |

| II-2-8           | Floating-Point Data                   | TT 0 40              | TT 0 00            | Save Area                   | 11-2-114           |

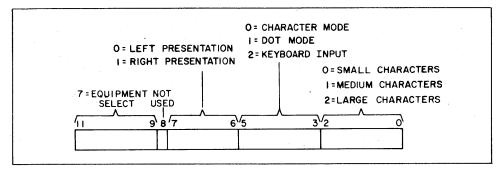

| TT 0 0           | Formats                               | 11-2-49              | II-2-29            | Display Station Output      | TT 0 100           |

| II-2-9           | Debug List Entry                      | II-2-67              |                    | Function Code               | II-2-133           |

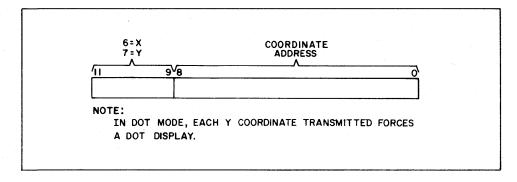

| II-2-10          | Debug Condition Select                | II-2-66              | II-2-30            | Coordinate Data Word        | II-2-133           |

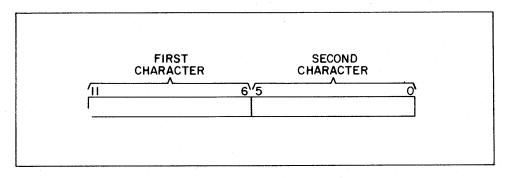

| II-2-11          | Central Memory Addressing             |                      | 11-2-31            | Character Data Word         | 11-2-133           |

|                  | from CP                               | II-2-77              | II-2-32            | Receive and Display         |                    |

| II-2-12          | Process Virtual Address               |                      |                    | Program Flowchart           | 11-2-135           |

|                  | (PVA) Format                          | II-2-78              | II-2-33            | IOU Dedicated Channels,     |                    |

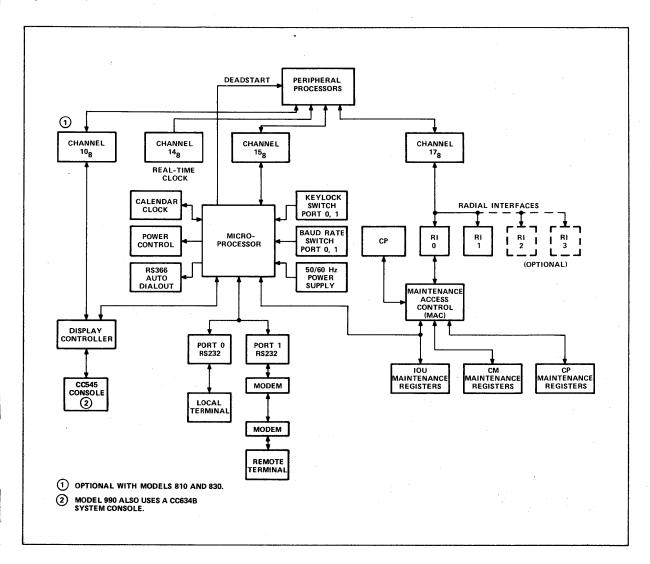

| II-2-13          | System Virtual Address                |                      |                    | Models 810, 815, 825,       |                    |

|                  | (SVA) Format                          | II <del>-</del> 2-79 |                    | and 830                     | 11-2-136           |

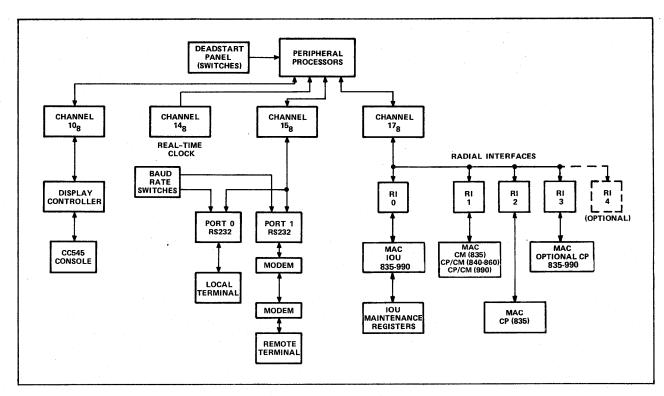

| II-2-14          | Segment/Page Identifier               |                      | 11-2-34            | IOU Dedicated Channels,     |                    |

|                  | (SPID) Format                         | 11-2-80              |                    | Models 835, 840, 845,       |                    |

| II-2-15          | Real Memory Address (RMA)             |                      |                    | 850, 855, 860, and 990      | 11-2-137           |

|                  | Format                                | II-2-81              | II-C-1             | Data Sequences Timing       | II-C-11            |

|                  |                                       |                      | -                  |                             |                    |

|                  |                                       |                      |                    |                             |                    |

|                  |                                       |                      |                    |                             |                    |

|                  |                                       | TABL                 | ES                 |                             |                    |

|                  |                                       |                      |                    |                             |                    |

| II-1-1           | CP Load and Store                     |                      | 11-1-11            | BDP Numeric Instructions    | II-1-32            |

|                  | Instructions                          | II-1-5               | II-1-12            | BDP Divide Fault            | II-1-35            |

| II-1-2           | CP Integer Arithmetic                 |                      | II-1-13            | BDP Byte Instructions       | 11-1-38            |

|                  | Instructions                          | II-1-11              |                    | BDP Subscript and           |                    |

| II-1-3           | CP Branch Instructions                | II-1-17              |                    | Immediate Data              |                    |

| II-1-4           | CP Copy Instructions                  | II-1-20              |                    | Instructions                | II-1-48            |

| II-1-5           | CP Address Arithmetic                 |                      | II-1-15            | Floating-Point Conversion   |                    |

| 11 1 3           | Instructions                          | II-1-22              |                    | Instructions                | II-1-53            |

| II-1-6           | CP Enter Instructions                 | II-1-23              | 11-1-16            | Floating-Point Arithmetic   |                    |

| II-1-7           | CP Shift Instructions                 | II-1-25              | 11 1 10            | Instructions                | II-1-54            |

| II-1-8           |                                       | II-1-27              | II-1-17            | Floating-Point Branch       | 11 1 31            |

| II-1-6<br>II-1-9 | CP Pogical Instructions               | 11-1-71              | TT - 1-1/          | Instructions                | 11-1-58            |

| TT-1-2           | CP Register Bit String Instructions   | II-1-29              | II-1-18            | Vector Instructions         | II-1-62            |

| II-1-10          |                                       | 11-1-72              | II-1-10<br>II-1-19 | Nonprivileged Instructions  | II-1-02<br>II-1-72 |

| 11-1-10          | Compare j Field and X1 Bits 32 and 33 | 11-1-31              | 11-1-13            | moubiliviteded instructions | 11-1-12            |

|                  | DILS JE AUG JJ                        | 11-111               |                    |                             |                    |