CDC° CYBER 170 MODELS 175, 740, 750, 760, 865, 875 FUNCTIONAL UNITS

THEORY OF OPERATION DIAGRAMS

HARDWARE MAINTENANCE MANUAL

| REVISION | DESCRIPTION                                                                                          |

|----------|------------------------------------------------------------------------------------------------------|

| 01       | Preliminary edition.                                                                                 |

| (12-74)  |                                                                                                      |

| 02       | Updated diagrams to reflect ECO 36000. This edition obsoletes previous edition.                      |

| (2-75)   |                                                                                                      |

| 03       | Updated diagrams to reflect ECOs 35738, 35539, 35693, and 36121. This edition obsoletes pre-         |

| (5-75)   | vious editions.                                                                                      |

| A        | Manual released. This edition obsoletes all previous editions.                                       |

| (7-75)   |                                                                                                      |

| В        | No change to this manual (ECO 36403).                                                                |

| (9-75)   |                                                                                                      |

| С        | Updated manual to reflect ECO 36429.                                                                 |

| (9-75)   |                                                                                                      |

| D        | Updated manual to reflect ECO 36183.                                                                 |

| (9-75)   |                                                                                                      |

| E        | Updated manual to reflect ECO 36724. (ECO PD1346 did not list this manual.)                          |

| (9-75)   |                                                                                                      |

| F        | Updated manual to reflect ECO/FCO 36194.                                                             |

| (9-75)   |                                                                                                      |

| G        | Updated manual to reflect ECO/FCO 36699.                                                             |

| 10-75)   |                                                                                                      |

| н        | Updated manual to reflect ECO 36185.                                                                 |

| (11-75)  |                                                                                                      |

| J        | Updated manual to reflect ECO 36849.                                                                 |

| (12-75)  |                                                                                                      |

| к        | Updated manual to reflect ECO/FCO 36197. Added secondary block and ESE diagrams. This                |

| (2-76)   | edition obsoletes all previous editions.                                                             |

| L        | Manual revised; includes Field Change Order 37147. Pages vi, 5-1-4, 5-1-5 in volume 1, vi, viii,     |

| (12-76)  | 5-11-11, 5-11-13, 5-11-29, 5-11-33, 5-11-34.8, 5-11-35, 5-11-53, 5-11-71, 5-11-147, 5-12-3, 5-12-17, |

|          | 5-12-25, 5-12-47, 5-12-49, 5-12-65, and 5-14-3 in volume 2 are revised.                              |

| М        | Manual revised; includes Engineering Change Order 37731. Page 5-1-5 in volume 1 and pages 5-12-3,    |

| (8-77)   | 5-12-5, 5-12-6.1, 5-12-6.3, 5-12-6.4, 5-12-7, 5-12-12.2, 5-12-13, and 5-14-1 in volume 2 are revised |

| N        | Manual revised; includes Field Change Order 37843 (ECO 37767). Pages vi, x, 5-1-5, 5-4-5, 5-5-1,     |

| (8-77)   | 5-7-5, 5-7-15, 5-10-9, and 5-10-13 in volume 1 and pages vi, ix, 5-11-5, 5-11-13, 5-11-17, 5-11-19,  |

|          | 5-11-29, 5-11-33, 5-11-35, 5-11-93, 5-11-153, 5-12-1, 5-12-3, 5-12-5, 5-12-7, 5-12-9, 5-12-10.2,     |

|          | 5-12-11, 5-12-13, 5-12-15, 5-12-17, 5-12-25, 5-12-43, 5-12-63, 5-12-65, 5-12-69, 5-12-71, 5-12-78.5, |

|          | Part 13 divider, 5-13-1, and 5-13-9 in volume 2 are revised. Page 5-12-73.1 is added in volume 2.    |

## REVISION LETTERS I, O, Q, S, X AND Z ARE NOT USED.

Address comments concerning this manual to: Control Data Corporation Publications and Graphics Division 4201 North Lexington Avenue St. Paul, Minnesota 55112

© 1974, 1975, 1976, 1977, 1978, 1979, 1981, 1983

by Control Data Corporation All rights reserved Printed in the United States of America

or use Comment Sheet in the back of this manual.

| REVISION   | DESCRIPTION                                                                                         |

|------------|-----------------------------------------------------------------------------------------------------|

| Р          | Manual revised; includes Engineering Change Order 37722. Removes volume 2 and adds model C          |

| (10-77)    | information. Front cover, title page and pages iv, v, vi, vii, x, 5-1-2, 5-1-4, and 5-1-5 are       |

|            | revised.                                                                                            |

| R          | Manual revised; includes Engineering Change Order 38980. Pages iii, iv, v, vi, 5-1-4, 5-1-5,        |

| (04-10-78) | 5-2-15, 5-3-15, 5-4-23, 5-5-41, 5-6-11, 5-7-81, 5-8-45, 5-8-53, 5-9-11, 5-10-17, 5-10-19, and       |

|            | 5-10-21 are revised. Page iv-a/iv-b is added. Pages 5-1-7, 5-2-9, 5-2-11, 5-2-13, 5-4-3, 5-4-9,     |

|            | 5-4-11, 5-5-1, 5-5-31, 5-6-7, 5-7-17, 5-7-19, 5-7-25, 5-7-29, 5-7-31, 5-7-33, 5-7-35, 5-7-37,       |

|            | 5-7-39, 5-7-41, 5-7-43, 5-7-49, 5-7-51, 5-7-55, 5-7-67, 5-7-69, 5-7-83, 5-8-23, 5-8-27, 5-8-29,     |

|            | 5-8-43, and 5-10-15 are reprinted for purposes of clarity.                                          |

| S          | Manual revised; includes Engineering Change Order 39978. Front cover, title page and pages          |

| (05-10-79) | iv-a/iv-b, v, vii, viii, ix, x, xi, 5-1-2, 5-1-9, 5-1-11, 5-1-13, 5-8-1, 5-8-3, 5-8-5, 5-8-7,       |

|            | 5-8-19, 5-8-47, and 5-8-49 are revised. Pages 5-1-15 and 5-1-17 are added.                          |

| Т          | Engineering Change Order 39735. No change to this manual.                                           |

| (07-05-79) |                                                                                                     |

| U          | Manual revised; includes Engineering Change Order 40383, publications change only. Pages ii-a/ii-b, |

| (07-6-79)  | iv-a, and v are revised. Page iv-b is added.                                                        |

| v          | Manual revised; includes Engineering Change Order 40489. Pages ii-a/ii-b, iv-a/iv-b, vii, xi,       |

| (11-26-79) | 5-1-1, 5-1-2, 5-1-4, 5-1-5, and 5-1-6 are revised.                                                  |

| W          | Manual revised; includes Engineering Change Order 41276. Grid locators 52B2, 52B4, 52B6, 52B7, 52B8 |

| (03-16-81) | 52B9, 52B10, 52B12, 52B13, 52E3/E4, and 52E7/E8 are revised.                                        |

| Y          | Manual revised to include Engineering Change Order 44495 which adds support for models 865 and 875. |

| (05-30-83) | This edition obsoletes the microfiche edition.                                                      |

| AA         | Manual revised; includes Engineering Change Order 44802. Pages iii through iv-c and viii are        |

| (08-05-83) | revised. Pages iv-d and iv-e are added.                                                             |

|            |                                                                                                     |

|            |                                                                                                     |

|            |                                                                                                     |

|            |                                                                                                     |

|            |                                                                                                     |

|            |                                                                                                     |

|            |                                                                                                     |

|            |                                                                                                     |

|            |                                                                                                     |

|            | · · · · · · · · · · · · · · · · · · ·                                                               |

|            |                                                                                                     |

|            |                                                                                                     |

|            |                                                                                                     |

|            |                                                                                                     |

|            |                                                                                                     |

|            |                                                                                                     |

|            |                                                                                                     |

|            |                                                                                                     |

|            |                                                                                                     |

|            |                                                                                                     |

|            |                                                                                                     |

, . .

• •

·

# MANUAL TO EQUIPMENT LEVEL CORRELATION SHEET

This manual reflects the equipment configurations listed below.

EXPLANATION: Locate the equipment type and series number, as shown on the equipment FCO log, in the list below. Immediately to the right of the series number is an FCO number. If that number and all of the numbers underneath it match all of the numbers on the equipment FCO log, then this manual accurately reflects the equipment.

| EQUIPMENT TYPE | SERIES     | WITH FCOs              | COMMENTS |

|----------------|------------|------------------------|----------|

| AA 120         | A01        | ×.                     | Released |

| AA120          | A01<br>A02 | EC035091               | Released |

|                | A03        | EC035467               |          |

|                | A04        | EC036623               |          |

|                | A05        | EC036634               |          |

|                | A06        | EC036637               |          |

|                | A06        | EC036403               |          |

|                | A06        | EC036429               |          |

|                | A06        | EC036183               |          |

|                | A06        | EC036724               |          |

|                | A07        | FC036579               |          |

|                | A08        | FC036699               |          |

|                | A09        | FC036194               |          |

|                | A09        | EC036185               |          |

|                | A09        | EC036849               |          |

|                | A10        | FCOPD1407              |          |

|                | A11        | FCOPD1377              |          |

|                | A12        | FCOPD1408              |          |

|                | A13        | FC036199               |          |

|                | A14        | FCOPD1511              |          |

|                | A15<br>A16 | FCOPD1456<br>FCOPD1392 |          |

|                | A17        | FCOPD1454              |          |

|                | A17<br>A18 | FCOPD1597              |          |

|                | A19        | FCOPD1562              |          |

|                | A20        | FC036197               |          |

|                | A21        | FCOPD938               |          |

|                | A21        | Included               |          |

|                | A22        | FC036639               |          |

|                | A23        | FC036647               |          |

|                | A24        | FC036624               |          |

|                | A25        | FC036641               |          |

|                | A26        | FC036999               |          |

|                | A27        | FC036646               |          |

|                | A28        | FC036645               |          |

|                | A29        | FC036642               |          |

|                | A30        | FC036681               |          |

|                | A31        | FC036644               |          |

|                | A32<br>A33 | FC036656               |          |

|                | A33<br>A34 | FC036654<br>FC036630   |          |

|                | A34<br>A35 | FC036630               | l        |

|                | A36        | FC037054               |          |

|                | A37        | FC036631               |          |

|                | A38        | FC036653               |          |

|                | A39        | FC036651               |          |

|                | A40        | FC036652               |          |

|                | A41        | FC036875               |          |

|                | A42        | FC036626               |          |

|                | A43        | FC036192               |          |

|                |            |                        |          |

| EQUIPMENT TYPE | SERIES       | WITH FCOs             | COMMENTS |

|----------------|--------------|-----------------------|----------|

|                | A44          | FC036854              |          |

|                | A45          | FC037362              |          |

|                | A46<br>A47   | FC037530<br>FC037147  |          |

|                | A47<br>A48   | FC036643              |          |

|                | A52          | EC037731              |          |

|                | A53          | FC037843              |          |

|                | A53          | FC037949              |          |

|                | A54          | FC038031              |          |

|                | A55<br>A56   | FC038236<br>FC038135  |          |

|                | A50          | FC037840              |          |

|                | A58          | FC038252              |          |

|                | A59          | FC038308              |          |

|                | A60          | FC038171              |          |

|                | A60          | FC038022<br>EC037722  |          |

|                | A60<br>A61   | FC037722              |          |

|                | A62          | FC038338              |          |

| ]              | A63          | FC038386              |          |

|                | A63          | FC038712              |          |

|                | A64          | FC038418              |          |

|                | A64<br>A64   | EC038980<br>EC038856  |          |

|                | A64          | EC038858              |          |

|                | A65          | EC038897              |          |

|                | A65          | EC039044              |          |

|                | A66          | EC038584              |          |

|                | A66<br>A67   | EC038670<br>EC038764  |          |

|                | A67          | EC039041              |          |

|                | A67          | EC038781              |          |

|                | A67          | EC038871              |          |

|                | A68          | EC038941              |          |

|                | A68<br>A69   | ECO39411<br>ECO39368  |          |

|                | A69          | EC039319              |          |

|                | A70          | EC038867              |          |

|                | A70          | EC039978              |          |

|                | A70          | EC039735              |          |

|                | A70<br>A71   | EC040383<br>FC039396  |          |

|                | A71          | FC039678              |          |

|                | A72          | FC039800/             | <u>.</u> |

|                |              | FC039778              | 1        |

|                | A73          | FC039590/<br>FC039773 |          |

|                | A74          | FC039732              |          |

|                | A74          | FC039726              |          |

|                | A74          | EC040489              |          |

|                | A75          | FC040748/             |          |

|                | A75          | FCO40843<br>FCO40479  |          |

|                | A75<br>A75   | EC041276              |          |

|                | 701          | Tasludel              |          |

|                | B01<br>B01   | Included<br>FC036639  |          |

|                | B01          | FC036647              |          |

|                | B01          | FC036624              |          |

|                | B01          | FC036641              |          |

|                | - B01<br>B01 | FC036999<br>FC036646  | j        |

|                | B01<br>B01   | FC036645              |          |

|                | B01          | FC036642              |          |

|                | B01          | FC036681              |          |

|                | B01          | FC036644              |          |

|                | BO1          | FC036656              |          |

|                | B01          | FC036654              |          |

| EQUIPMENT TYPE | SERIES     | WITH FCOs             | COMMENTS |

|----------------|------------|-----------------------|----------|

|                | B01        | FC036630              |          |

|                | B01        | FC037073              |          |

|                | B01<br>B01 | FC037054<br>FC036631  |          |

|                | B01        | FC036653              |          |

|                | B01        | FC036651              |          |

|                | B01        | FC036652              |          |

|                | B01        | FC036875              |          |

|                | B01        | FC036626              |          |

|                | B01<br>B01 | FC036192<br>FC036854  |          |

|                | B01<br>B02 | FC037362              |          |

|                | B02        | FC037530              |          |

|                | B02.       | FCO37147              |          |

|                | B02        | FC036643              |          |

|                | B05        | EC037731              |          |

|                | B06<br>B06 | FCO37843<br>FCO37949  |          |

|                | B06<br>B07 | FC037949<br>FC038031  |          |

|                | B08        | FC038236              |          |

|                | B09        | FC038135              |          |

|                | B10        | FC037840              |          |

|                | B11<br>B11 | FC038252              |          |

|                | B11<br>B12 | FC038308<br>FC038171  |          |

|                | B13        | FC038022              |          |

|                | B13        | EC037722              |          |

|                | B14        | FC037813              |          |

|                | B15        | FC038338              |          |

|                | B16<br>B17 | FC038386<br>FC038712  |          |

|                | B18        | FC038418              |          |

|                | B18        | EC038980              |          |

|                | B18        | EC038856              |          |

|                | B18<br>B18 | ECO38858<br>ECO38897  |          |

|                | B19        | EC038097              |          |

|                | B20        | EC038584              |          |

|                | в20        | EC038670              |          |

|                | B21        | EC038764              |          |

|                | B22<br>B22 | ECO39041<br>ECO38781  |          |

|                | B22<br>B22 | EC038871              |          |

|                | B23        | EC038941              |          |

|                | B24        | EC039411              |          |

|                | B25        | EC039368              |          |

|                | B25<br>B26 | ECO39319<br>ECO38867  |          |

| ×              | B26        | EC0389978             |          |

|                | B26        | EC039735              |          |

|                | B26        | EC040383              |          |

|                | B27        | FC039396              |          |

|                | В27<br>В28 | FCO39678<br>FCO39800/ |          |

|                | 520        | FC039778              |          |

|                | в29        | FC039590/             |          |

|                |            | FC039773              |          |

|                | B29        | FC039732              |          |

|                | B30<br>B30 | FCO39726<br>ECO40489  |          |

|                | B30<br>B31 | FC040748/             |          |

| · · · · · ·    |            | FC040843              |          |

|                | B31        | FC040479              |          |

|                | B31        | ECO41276              |          |

|                | C02        | FC038135              |          |

|                | C02        | FC037840              |          |

|                | C02        | FC038252              |          |

|   | C02<br>C03 | FC0.28.200            | COMMENTS |

|---|------------|-----------------------|----------|

|   |            | FC028208              |          |

|   | I C03      | FC038308              |          |

|   |            | FC038171              |          |

|   | C03<br>C03 | FC038022<br>EC037722  |          |

|   | C03        | FC037813              |          |

|   | C04        | FC038338              |          |

|   | C04        | FC038386              |          |

|   | C05        | FC038712              |          |

|   | C06        | FC038418              |          |

|   | ' C06      | EC038980              |          |

|   | C07<br>C08 | EC038856              |          |

|   | C08        | EC038858<br>EC038897  |          |

|   | C09        | EC039044              |          |

|   | C10        | EC038584              |          |

|   | C11        | EC038670              |          |

|   | C11        | EC038764              |          |

|   | C12        | EC039041              |          |

|   | C13<br>C14 | EC038781              |          |

|   | C14<br>C15 | EC038871<br>EC038941  |          |

|   | C15<br>C16 | EC038941<br>EC039411  |          |

|   | C17        | EC039368              |          |

|   | C18        | EC039319              |          |

|   | C18        | EC038867              |          |

|   | C18        | EC039978              |          |

|   | C18        | EC039735              |          |

|   | C18<br>C19 | ECO40383<br>FCO39396  |          |

|   | C19        | FC039678              |          |

|   | C19        | FC039800/             | -        |

|   |            | FC039778              |          |

|   | C20        | FC039590/             |          |

|   |            | FC039773              |          |

|   | C20        | FC039732              |          |

|   | C21<br>C21 | FC039726<br>EC040489  |          |

|   | C21<br>C21 | FC040748/             |          |

|   | 021        | FC040843              |          |

|   | C22        | FC040479              |          |

|   | C22        | EC041276              |          |

|   | D01        | EC039978              |          |

|   | D01        | EC039735              |          |

|   | D01        | ECO40383              |          |

|   | D01        | FC039396              |          |

|   | D01        | FC039678              |          |

|   | D01        | FC039800/<br>FC039778 |          |

|   | D01        | FC039590/             |          |

|   | 201        | FC039773              |          |

|   | D01        | FC039732              |          |

|   | D01        | FC039726              |          |

|   | D01        | EC040489              |          |

|   | D01        | FC040748/             |          |

|   | D01        | FC040843<br>FC040479  |          |

|   | D01        | EC041276              |          |

|   | D01        |                       | Released |

|   | D02        | FC039944              |          |

|   | - D03      | FC040112              |          |

|   | D04        | FC040106              |          |

| : | D05        | FC039936/             |          |

|   | D06        | FC040225<br>FC040205  |          |

|   | D08<br>D07 | FC040205<br>FC040221  |          |

|   | D08        | FC040432              |          |

|   |            |                       |          |

| EQUIPMENT TYPE | SERIES     | WITH FCOs             | COMMENTS |

|----------------|------------|-----------------------|----------|

|                | D09        | ECO39947/             |          |

|                |            | FC040364              |          |

|                | D10        | FC040379              |          |

|                | D11        | FC039945              |          |

|                | D12        | FC040607              |          |

|                | D13        | FC040658<br>FC040030  |          |

|                | D14<br>D15 | FC040030<br>FC040583  |          |

|                | D15<br>D16 | FC040585              |          |

|                | D10<br>D17 | FC040740              |          |

|                | D18        | FC040857              |          |

|                | D19        | FC040830              |          |

|                | D20        | FC040827              |          |

|                | D21        | FCO40915              |          |

|                | D22        | FCO40904              |          |

|                | D23        | FC041012              |          |

| · ·            | D24        | FC041021              |          |

|                | D25        | FC041043              |          |

|                | D26        | EC041358              |          |

|                | D27        | FC041346              |          |

|                | D28<br>D29 | ECO41363<br>FCO41359  |          |

|                | D29<br>D30 | FC041339              |          |

|                | D30        | EC041632              |          |

| · · ·          | D32        | EC041639              |          |

|                | D33        | FC041636              |          |

|                | D34        | EC041790              |          |

|                | D35        | FC042000              |          |

|                | D36        | EC041372              |          |

|                | D37        | FC042050              |          |

|                | D38        | FCO41736              |          |

|                | D39        | FC042323              |          |

|                | D40        | FC042348              |          |

|                | D41        | FC042913              |          |

|                | E01        | ECO44495              |          |

| AT 364         | A01        | EC038980              |          |

|                | A01        | EC038856              |          |

|                | A01        | EC038858              |          |

|                | A01        | EC038897              |          |

|                | A01        | EC039044              |          |

|                | A01        | EC038584              |          |

|                | A01<br>A01 | EC038670              |          |

|                | A01<br>A01 | EC038764<br>EC039041  |          |

|                | A01<br>A01 | EC039041<br>EC038781  |          |

|                | A01        | EC038871              |          |

|                | A01        | EC038941              |          |

|                | A01        | EC039411              |          |

|                | A01        | EC039368              |          |

|                | A01        | EC039319              |          |

|                | A01        | ECO38867              |          |

|                | A01        | EC039978              |          |

|                | A01        | EC039735              |          |

|                | A01        | EC040383              |          |

|                | A01        | FC039396              |          |

|                | A01<br>A01 | FC039678<br>FC039800/ |          |

|                |            | FC039778              |          |

|                | A01        | FC039590/             |          |

|                | A01        | FC039773<br>FC039732  |          |

|                | A01<br>A01 | FC039726              |          |

|                | A01        | EC040489              |          |

|                | A01        | FC040748/             |          |

|                |            | FC040843              |          |

|                | A01        | FC040479              |          |

¢

| EQUIPMENT TYPE | SERIES     | WITH FCOs             | COMMENTS |

|----------------|------------|-----------------------|----------|

|                | A01        | EC041276              | •        |

|                | A01        | F00200//              | Released |

|                | A01<br>A01 | FCO39944<br>FCO40112  |          |

|                | A01        | FC040112<br>FC040106  |          |

|                | A01        | FC039936/             |          |

|                |            | FC040225              |          |

|                | A01        | FC040205              |          |

|                | A01        | FCO40221              |          |

|                | A01        | FC040432              |          |

|                | A01        | EC039947/             |          |

|                | A01        | FCO40364<br>FCO40379  |          |

|                | A01        | FC039945              |          |

|                | A01        | FC040607              |          |

|                | A01        | FC040658              |          |

|                | A01        | FC040030              |          |

|                | A01        | F6040583              |          |

|                | A01        | FC040589A             |          |

|                | A01<br>A01 | FC040740<br>FC040857  |          |

|                | A01        | FC040830              |          |

|                | A01        | FC040827              |          |

|                | A01        | FC040915              |          |

|                | A01        | FC040904              |          |

|                | A01        | FC041012              |          |

|                | A01        | FC041021              |          |

|                | A01<br>A01 | FC041043<br>EC041358  |          |

|                | A01        | FC041346              |          |

|                | A01        | EC041363              |          |

|                | A01        | FC041359              | · · ·    |

|                | A01        | FC041833              |          |

|                | A01        | EC041632              |          |

|                | A01<br>A01 | EC041639<br>FC041636  |          |

|                | A01        | EC041790              |          |

|                | A01        | FC042000              |          |

|                | A01        | ECO41372              |          |

|                | A01        | FC042050              |          |

|                | A01        | FC041736              |          |

|                | A01<br>A01 | FC042323<br>FC042348  |          |

|                | A01        | FC042913              |          |

|                | B01        | ECO39978              |          |

|                | B01        | EC039735              |          |

|                | B01        | EC040383              |          |

|                | B01        | FC039396              |          |

|                | B01        | FC039678              |          |

|                | B01        | FC039800/<br>FC039778 |          |

|                | B01        | FC039590/             |          |

|                |            | FC039773              |          |

|                | B01        | FC039732              |          |

|                | B01        | FC039726              |          |

|                | B01        | EC040489              |          |

|                | B01        | FC040748/<br>FC040843 |          |

|                | B01        | FC040845              |          |

|                | · B01      | EC041276              |          |

|                | B01        |                       | Released |

|                | B01        | FC039944              |          |

|                | B01<br>B01 | FC040112<br>FC040106  |          |

|                | B01<br>B01 | FC039936/             |          |

|                | 201        | FC040225              |          |

|                | B01        | FC040205              |          |

)

| B01     FC040221       B01     FC040432       B01     EC039947/       FC040364       B01     FC040379       B01     FC040607       B01     FC040688       B01     FC040030       B01     FC040583       B01     FC040589A                                                                | B01   FC040432     B01   EC039947/     FC040379     B01   FC040379     B01   FC040607     B01   FC040658     B01   FC040583     B01   FC040583     B01   FC040583     B01   FC040587     B01   FC040857     B01   FC040827     B01   FC040915     B01   FC041012     B01   FC041021     B01   FC041033     B01   FC041033     B01   FC041033     B01   FC041033     B01   FC041034     B01   FC0410358     B01   FC041358     B01   FC041363     B01   FC041632  < |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| B01   FC040857     B01   FC040830     B01   FC040827     B01   FC040915     B01   FC040915     B01   FC040904     B01   FC041012     B01   FC041021     B01   FC041043     B01   EC041358     B01   FC041346     B01   EC041363     B01   FC041833     B01   FC041833     B01   EC041632 | B01   EC041790     B01   FC042000     B01   EC041372     B01   FC042050     B01   FC041736     B01   FC042323     B01   FC042348     B01   FC042913     AT402   A01   EC040383     A01   EC040489                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

PREFACE

This manual contains theory of operation and diagrams for the functional unit portion of the CONTROL DATA® AA120-A/B/C/D/E Central Computer and the AA131-D Central Computer with an AT402-A Upgrade Option installed. Also included is information about the AT364-A/B Central Processor Enhancement which is used with the AA120-C/D Central Computer.

Models 740, 750, and 760 are defined as 7X0. Models 865 and 875 are defined as 8X5.

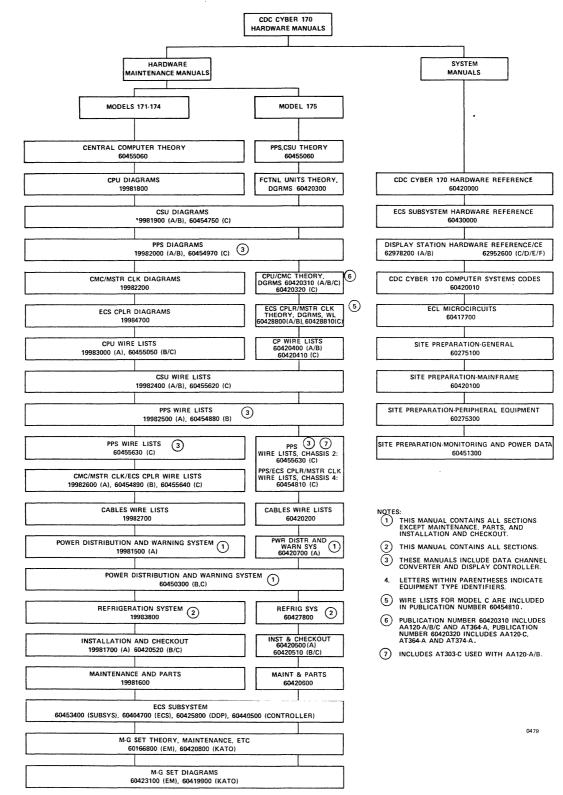

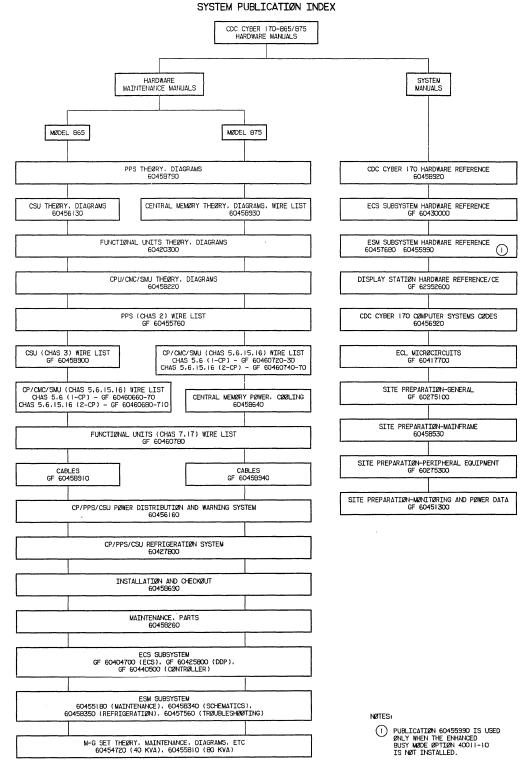

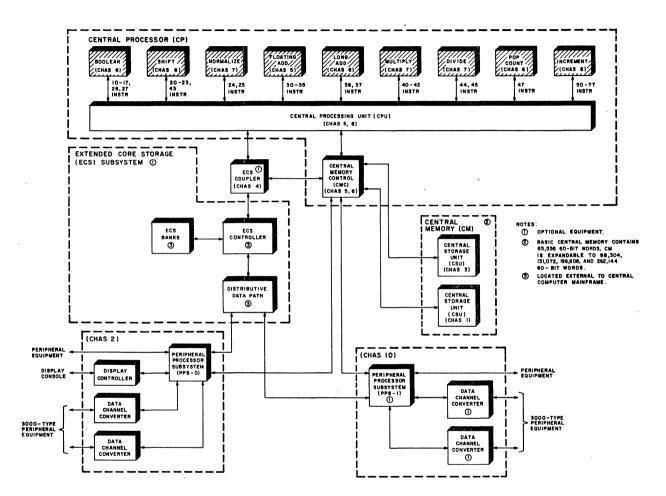

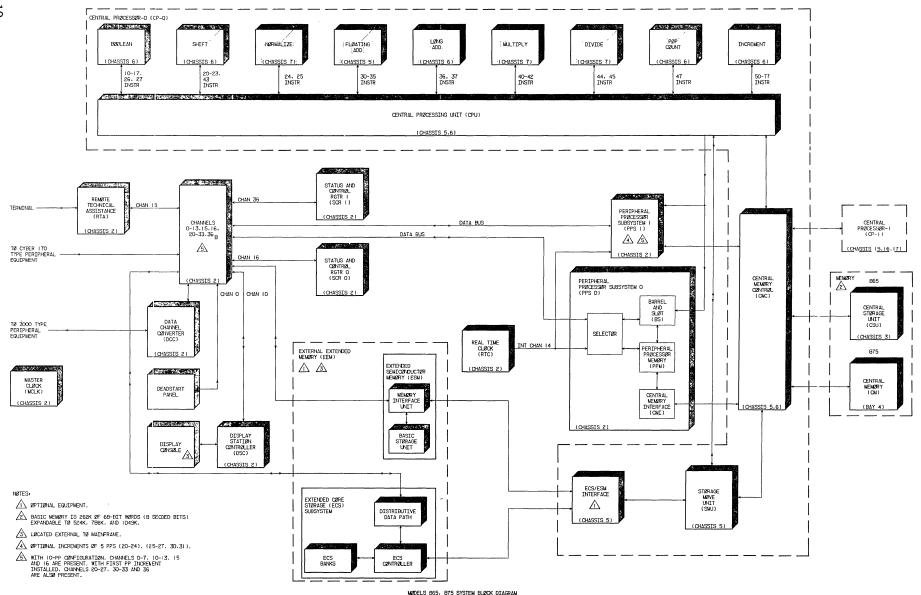

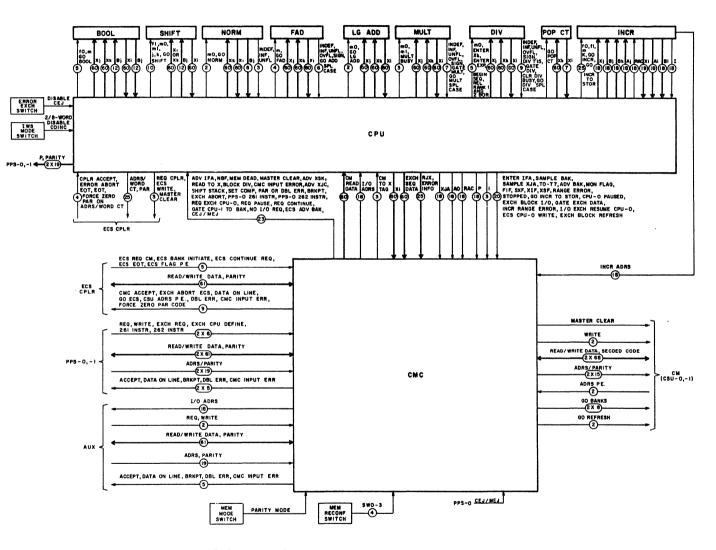

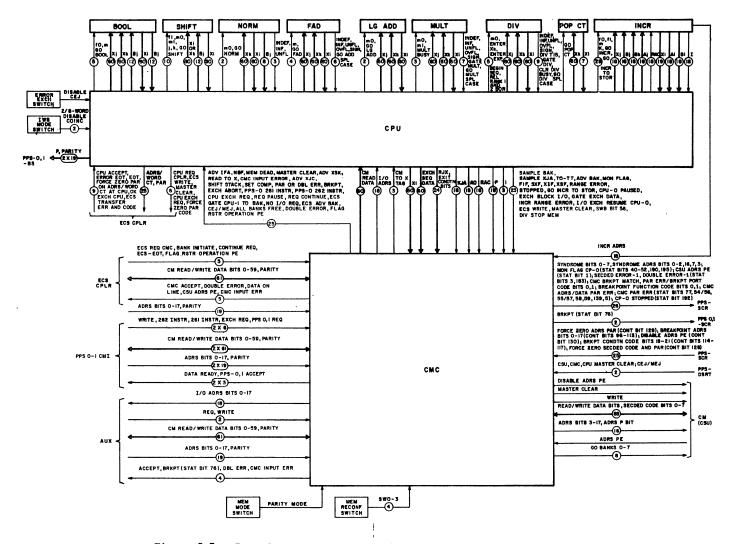

Comparable information on the central processing unit (CPU), central memory control (CMC), central storage unit (CSU), peripheral processor subsystem (PPS), and extended core storage (ECS) coupler is contained in other manuals. The system publication indexes on the following pages graphically list the related publications. Refer to the Literature and Distribution Services catalog for the latest revision of each manual.

This manual contains a manual to equipment level correlation sheet. The last line of this sheet indicates the latest equipment level (series code) that the manual covers. All manuals for the central computer indicate the latest series code even if the particular manual is not affected by the field change order.

v

60420300 Y

#### SYSTEM PUBLICATION INDEX

60420300 S

### SYSTEM PUBLICATION INDEX

|                                                                           | CDC CYBER 170<br>HARDWARE MAN                                      | JALS                                                                                                                                          |

|---------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| MODELS 720, 730                                                           | RE<br>MANUALS<br>MODELS 740, 750, 760                              | SYSTEM<br>MANUALS                                                                                                                             |

| PPS THEORY<br>GF 604                                                      |                                                                    | CDC CYBER 170 HARDWARE REFERENCE<br>GF 60456100                                                                                               |

| CSU THEORY<br>GF 6045                                                     | 5130                                                               | ECS SUBSYSTEM HARDWARE REFERENCE<br>GF 60430000                                                                                               |

| CPU THEORY, DIAGRAMS<br>GF 60456170                                       | FUNCTIONAL UNITS THEORY, DIAGRAMS<br>GF 60420300                   | ESM SUBSYSTEM HARDWARE REFERENCE<br>60457680, 60455990, 60458600, 60458590                                                                    |

| CMC THEORY, DIAGRAMS<br>GF 60456180                                       | CPU/CMC THEORY, DIAGRAMS<br>GF 60456260                            | DISPLAY STATION HARDWARE REFERENCE/CE<br>GF 62952600                                                                                          |

| ECS CPLR THEOR<br>GF 6045                                                 | Y, DIAGRAMS<br>6190                                                | CDC CYBER 170 COMPUTER SYSTEMS CODES<br>60456920                                                                                              |

| PPS (CHAS 2) V<br>GF 6045                                                 | VIRE LIST<br>6140                                                  | ECL MICROCIRCUITS<br>GF 60417700                                                                                                              |

| CSU (CHAS 3)<br>GF 6045                                                   | WIRE LIST<br>5150                                                  | SITE PREPARATION GENERAL<br>GF 60275100                                                                                                       |

| CPU/CMC (CHAS 1) WIRE LIST<br>GF 60456200                                 | CP (CHAS 5-7) WIRE LIST<br>GF 60456220, 30, 40                     | SITE PREPARATION-MAINFRAME<br>GF 60456890                                                                                                     |

| CPU/ECS CPLR (CHAS 4) WIRE LIST<br>GF 60456210()                          | ECS CPLR (CHAS 4) WIRE LIST<br>GF 60456250                         | SITE PREPARATION-PERIPHERAL EQUIPMENT<br>GF 60275300                                                                                          |

| CABLES<br>GF 60457530                                                     | CABLES<br>GF 60457540                                              | SITE PREPARATION MONITORING AND POWER DATA<br>GF 60451300                                                                                     |

| POWER DISTRIBUTION /<br>GF 604                                            |                                                                    |                                                                                                                                               |

| REFRIGERATION SYSTEM<br>GF 19983800                                       | REFRIGERATION SYSTEM<br>GF 60427800                                | NOTES:                                                                                                                                        |

| GF 60420520<br>MAINTENAN<br>GF 6045                                       | GF 60420510                                                        | GF 60456250<br>(2) PUBLICATIONS 60455990 AND<br>60458590 ARE USED ONLY<br>WHEN THE ENHANCED BUSY<br>MODE OPTION 40011-10 IS<br>NOT INSTALLED. |

| GF 60404700 (ECS), GF 60425800 (DD                                        | YSTEM<br>PP), GF 60440500 (CONTROLLER)                             | (3) PUBLICATIONS 60458600,<br>60458590, AND 60458580<br>APPLY TO ESM II ONLY.                                                                 |

| ESM SUBS<br>60458580, 60455180 (MAINTENAN<br>60458350 (REFRIGERATION), 60 | YSTEM<br>CE), 60458340 (SCHEMATICS),<br>157560 (TROUBLESHOOTING) ③ |                                                                                                                                               |

| M-G SET THEORY, MA<br>60166800 (EM), 604                                  | INTENANCE, ETC<br>20800 (KATO)                                     |                                                                                                                                               |

| M-G SET DIA<br>60423100 (EM), 6041                                        | GRAMS<br>9900 (KATO)                                               | 1182D                                                                                                                                         |

| 25.kVa FREQUENCY CONVERTER<br>THEORY MAINTENANCE DIAGRANIS<br>GF 60456520 |                                                                    |                                                                                                                                               |

1

5

10629 (06/22/83) Ţ

CONTENTS

| 4. THEORY OF OPERATION<br>(included in section 5)                                                                               |                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 5. DIAGRAMS                                                                                                                     |                                                                                                |

| Part 1. Introduction                                                                                                            |                                                                                                |

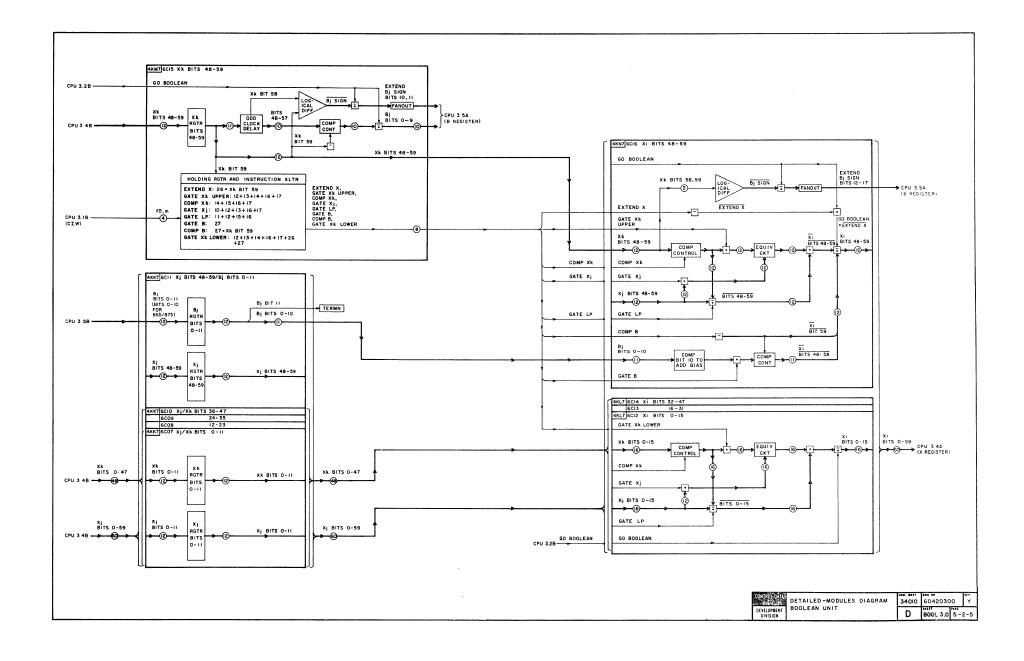

| Part 2. Boolean Unit                                                                                                            |                                                                                                |

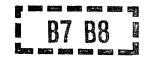

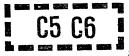

| Primary Block Diagram (BOOL 1.0)<br>Secondary Block Diagram (BOOL 2.0)<br>Detailed-Modules Diagram (BOOL 3.0)<br>Logic Diagrams | 5-2-1<br>5-2-3<br>5-2-5                                                                        |

| 4KK7<br>4KL7<br>4KN7<br>Timing Diagram, Boolean Instruction                                                                     | 5-2-7<br>5-2-9<br>5-2-11<br>5-2-15                                                             |

| Timing Diagram, Boorean Instruction                                                                                             | J-2-1J                                                                                         |

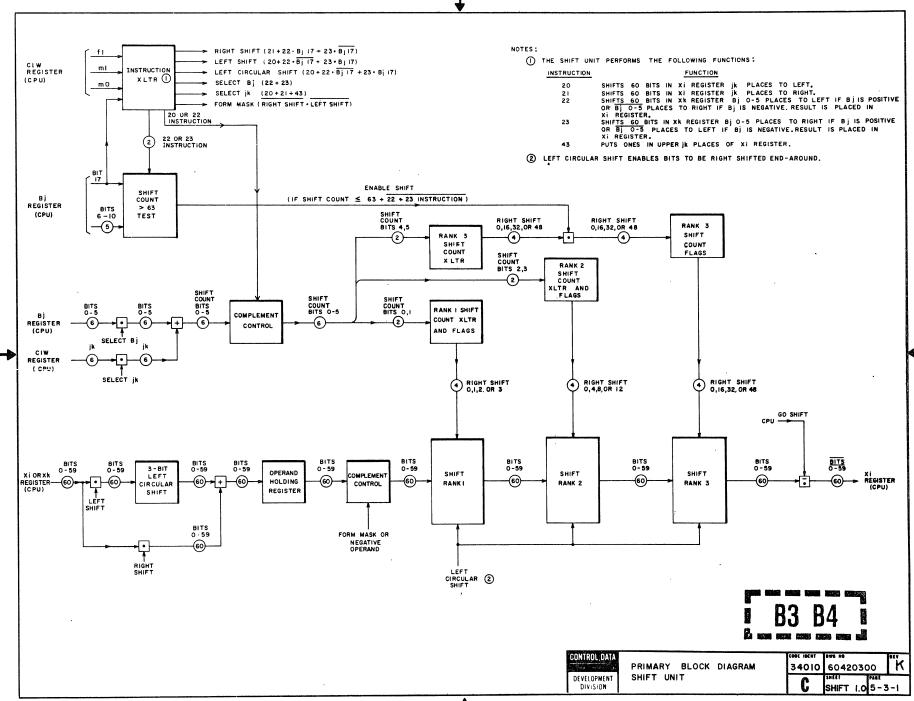

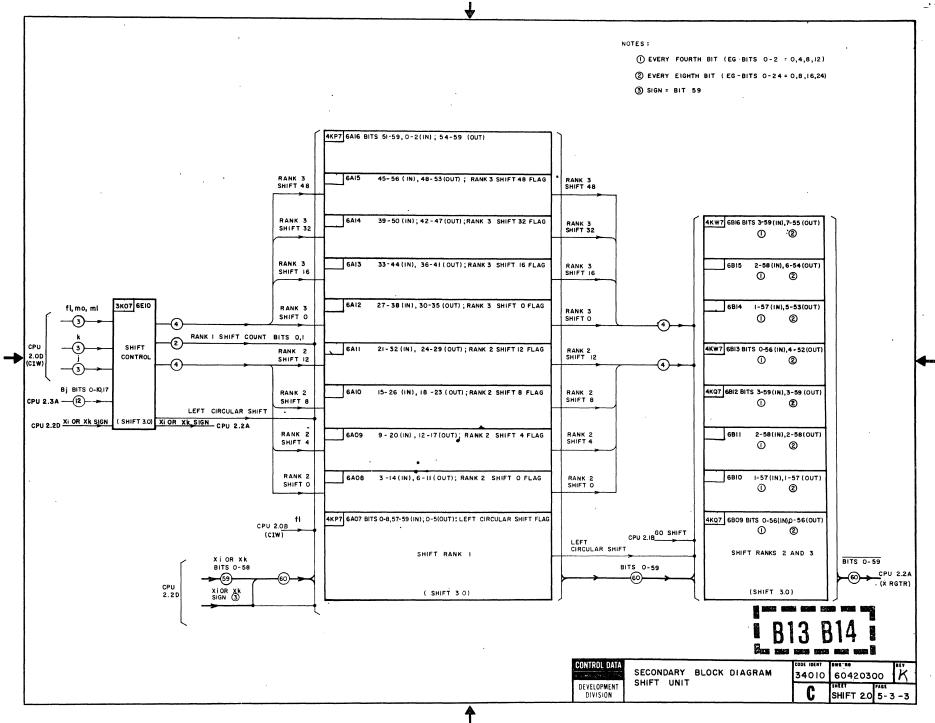

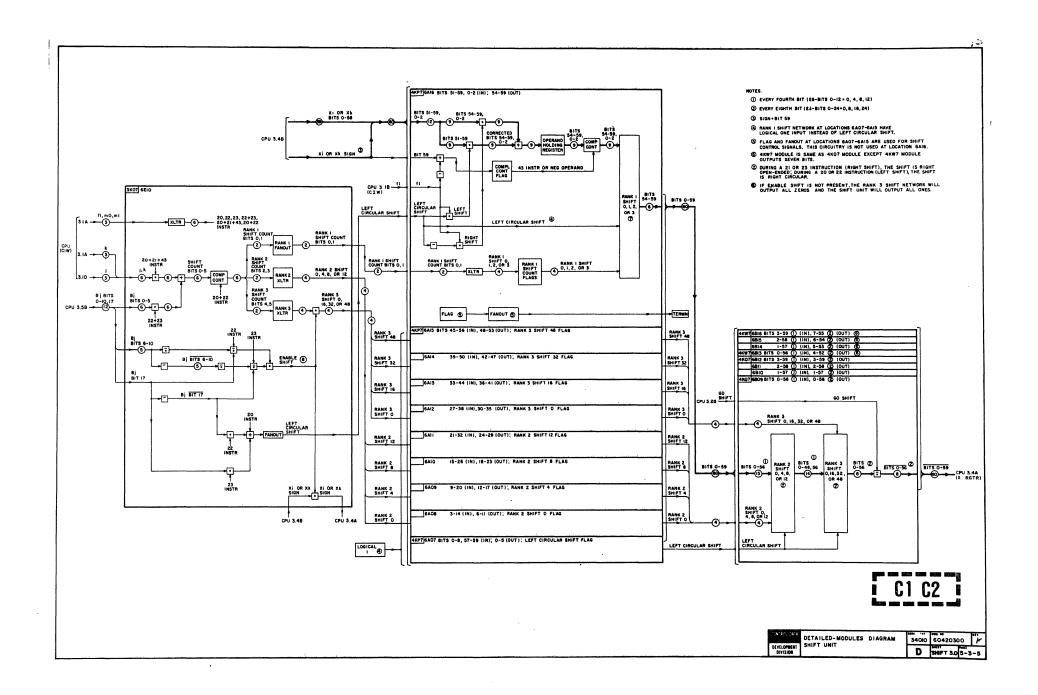

| Part 3. Shift Unit                                                                                                              |                                                                                                |

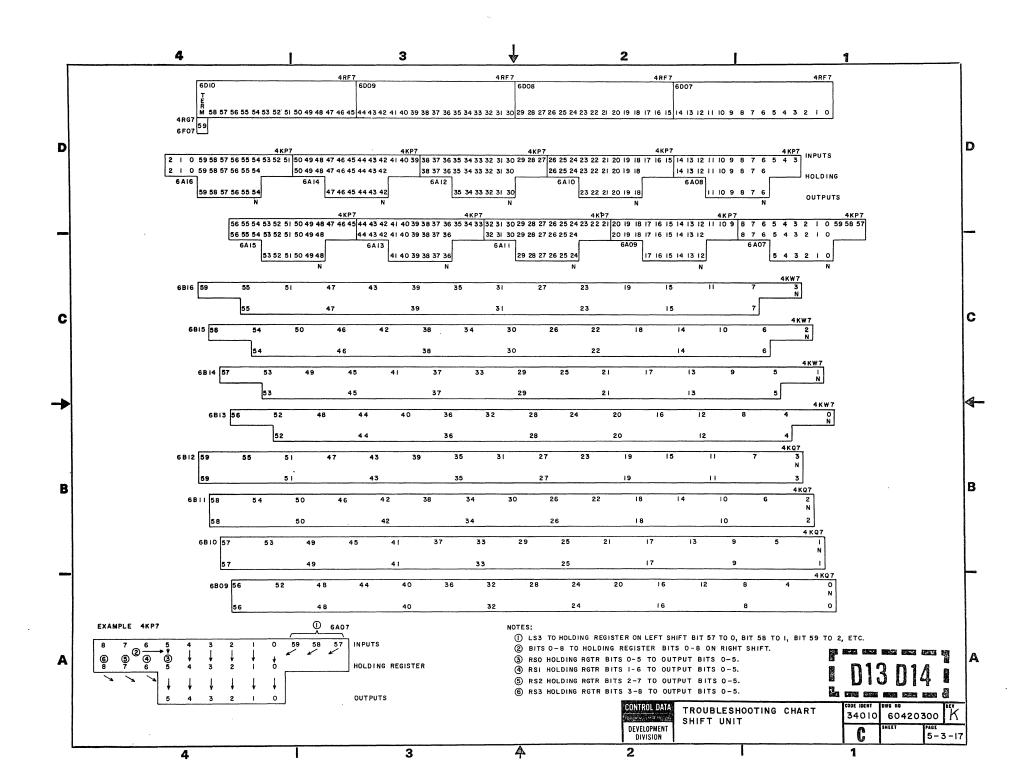

| Primary Block Diagram (SHIFT 1.0)<br>Secondary Block Diagram (SHIFT 2.0)<br>Detailed-Modules Diagram (SHIFT 3.0)                | 5-3-1<br>5-3-3<br>5-3-5                                                                        |

| Logic Diagrams<br>3K07<br>4KP7<br>4KQ7<br>4KW7                                                                                  | 5-3-7<br>5-3-9<br>5-3-11<br>5-3-13                                                             |

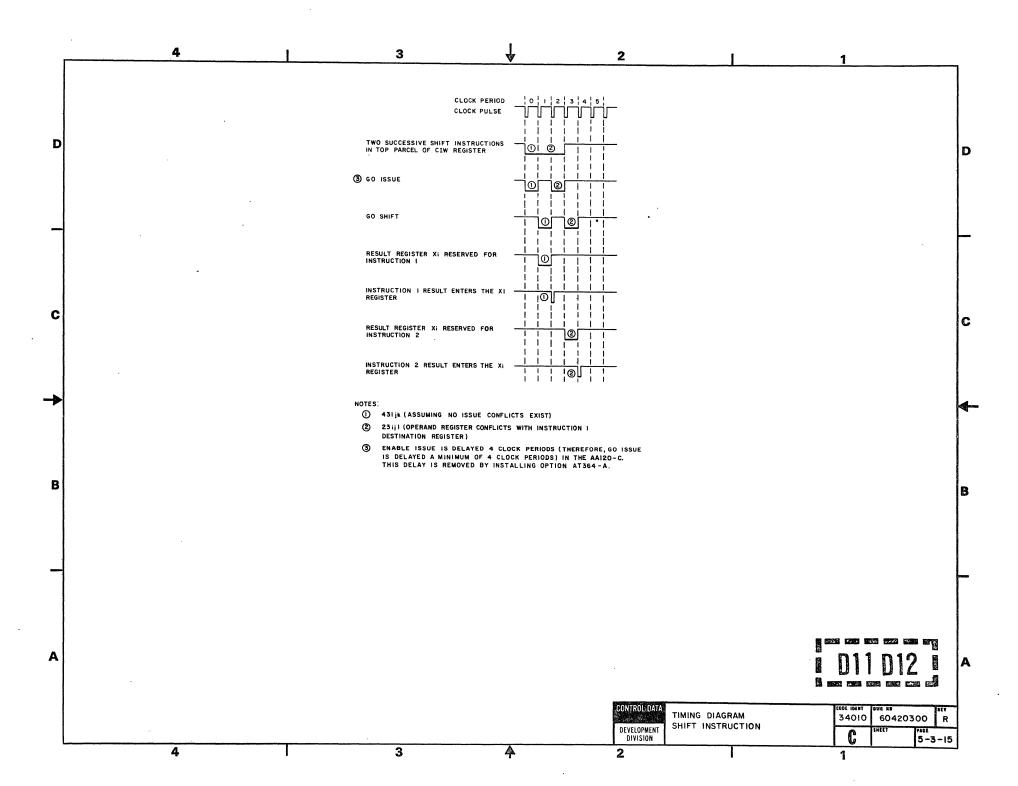

| Timing Diagram, Shift Instruction<br>Troubleshooting Chart, Shift Unit                                                          | 5-3-15<br>5-3-17                                                                               |

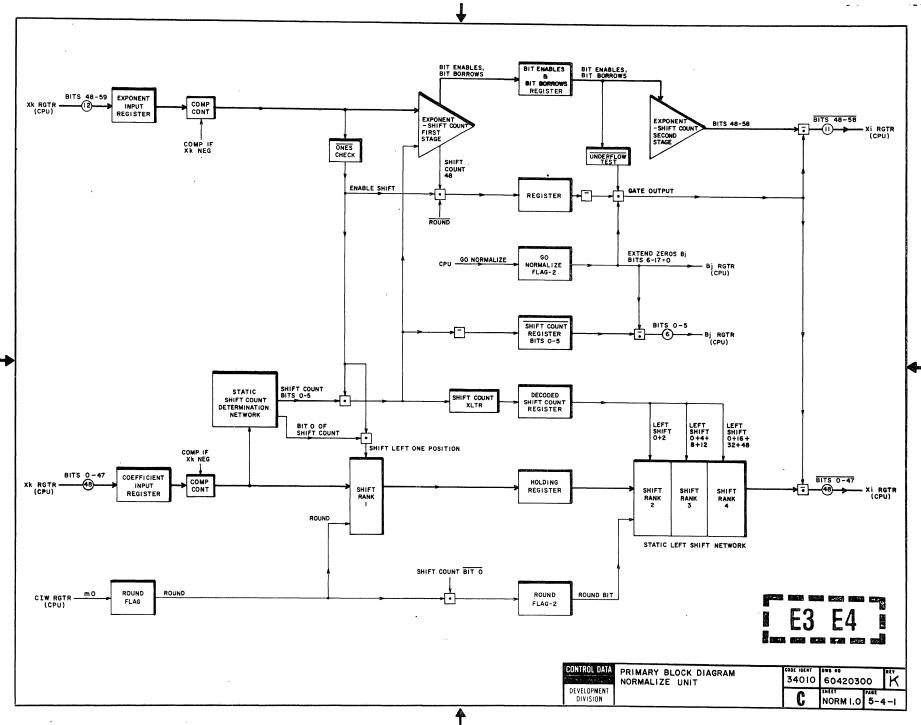

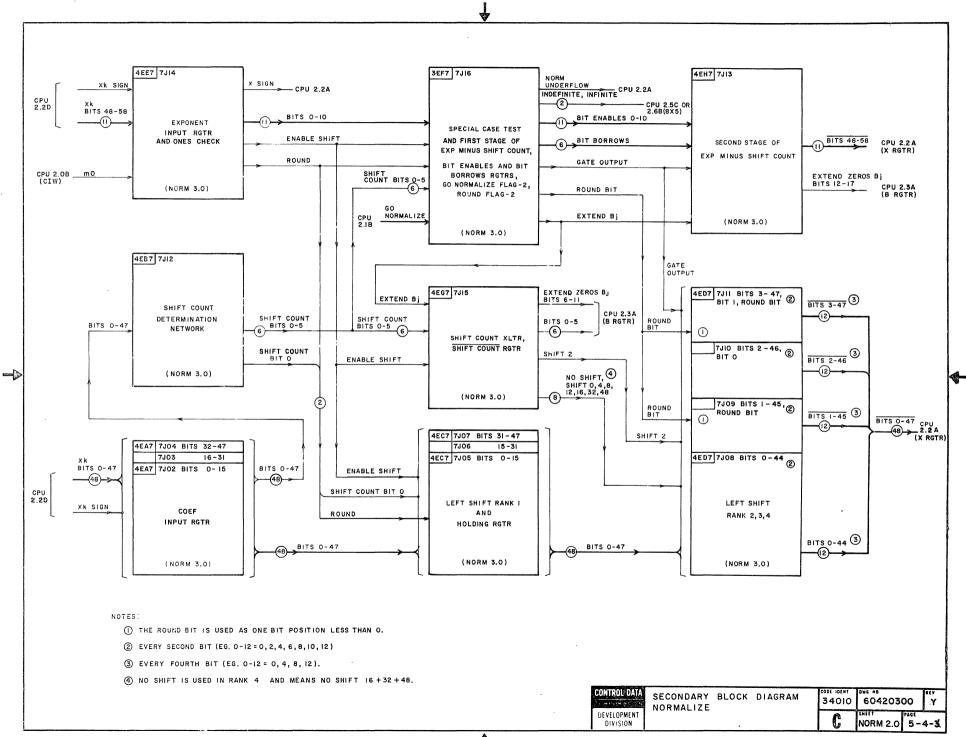

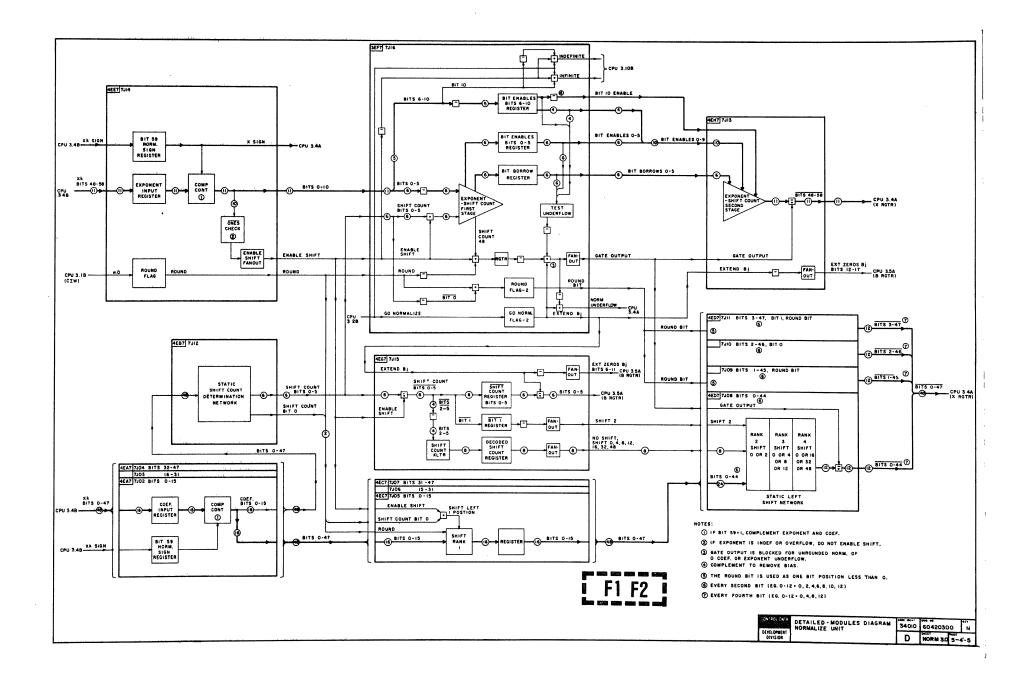

| Part 4. Normalize Unit                                                                                                          |                                                                                                |

| Primary Block Diagram (NORM 1.0)<br>Secondary Block Diagram (NORM 2.0)<br>Detailed-Modules Diagram (NORM 3.0)<br>Logic Diagrams | 5-4-1<br>5-4-3<br>5-4-5                                                                        |

| 4EA7<br>4EA7<br>4EB7<br>4EC7<br>4ED7<br>4EE7<br>4EF7<br>4EG7<br>4EH7<br>Timing Diagram, Normalize Instruction                   | 5-4-7<br>5-4-9<br>5-4-11<br>5-4-13<br>5-4-15<br>5-4-15<br>5-4-17<br>5-4-19<br>5-4-21<br>5-4-23 |

|                                                                                                                                 |                                                                                                |

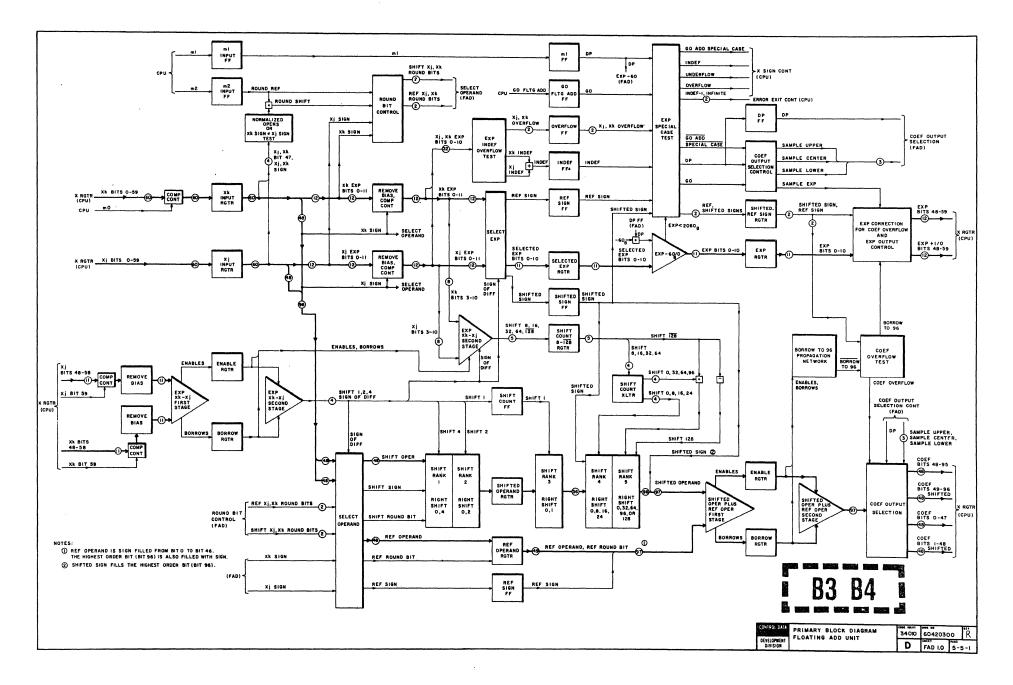

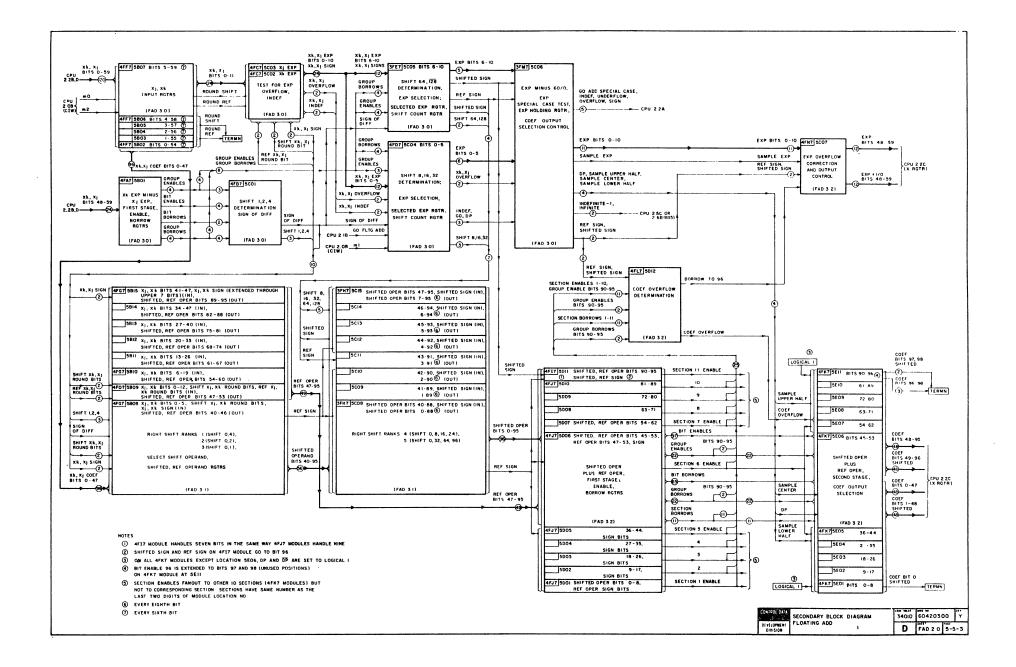

| Part 5. Floating Add Unit                                                                                                      |                |

|--------------------------------------------------------------------------------------------------------------------------------|----------------|

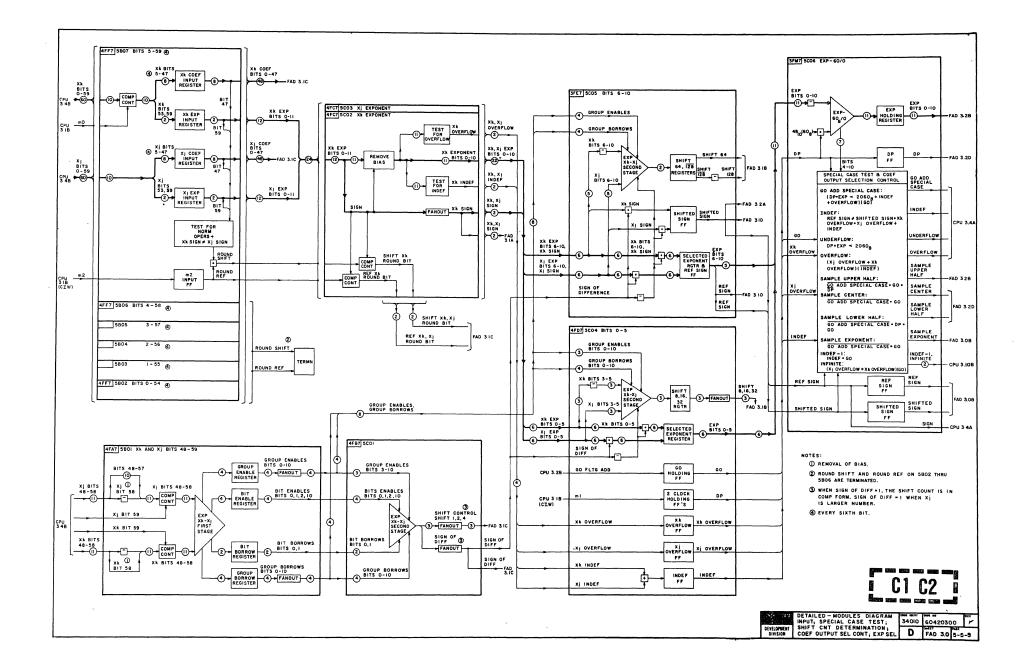

| Primary Block Diagram (FAD 1.0)<br>Secondary Block Diagram (FAD 2.0)<br>Detailed-Modules Diagrams<br>Input, Special Case Test: | 5-5-1<br>5-5-3 |

| Shift Count Determination; Coeffi-<br>cient Output Selection Control                                                           |                |

| Exponent Selection (FAD 3.0)                                                                                                   | 5-5-5          |

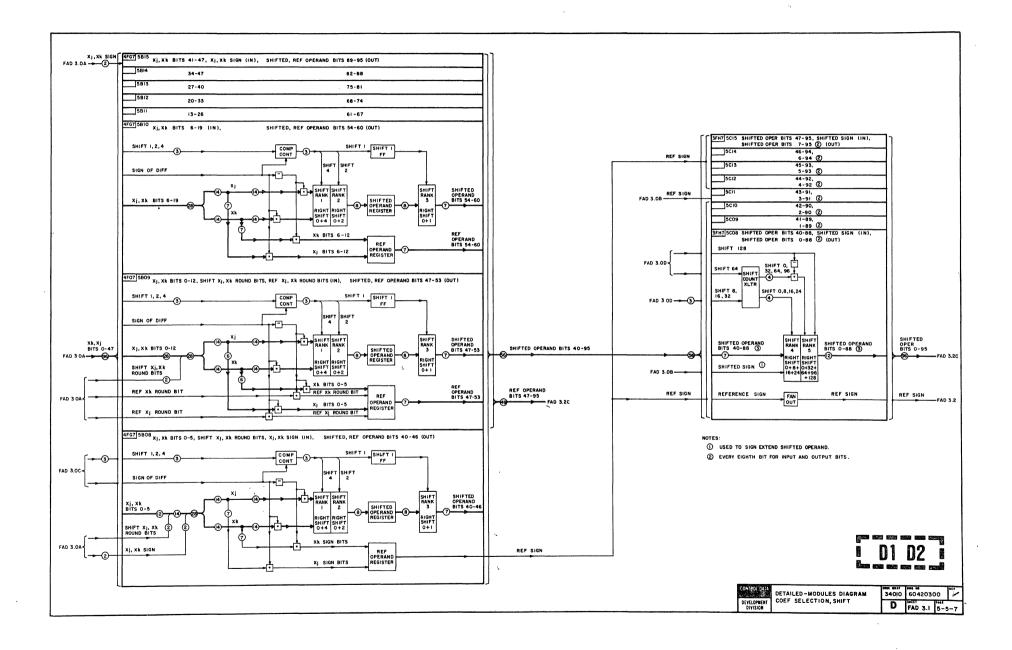

| Coefficient Selection, Shift (FAD 3.1)                                                                                         | 5-5-7          |

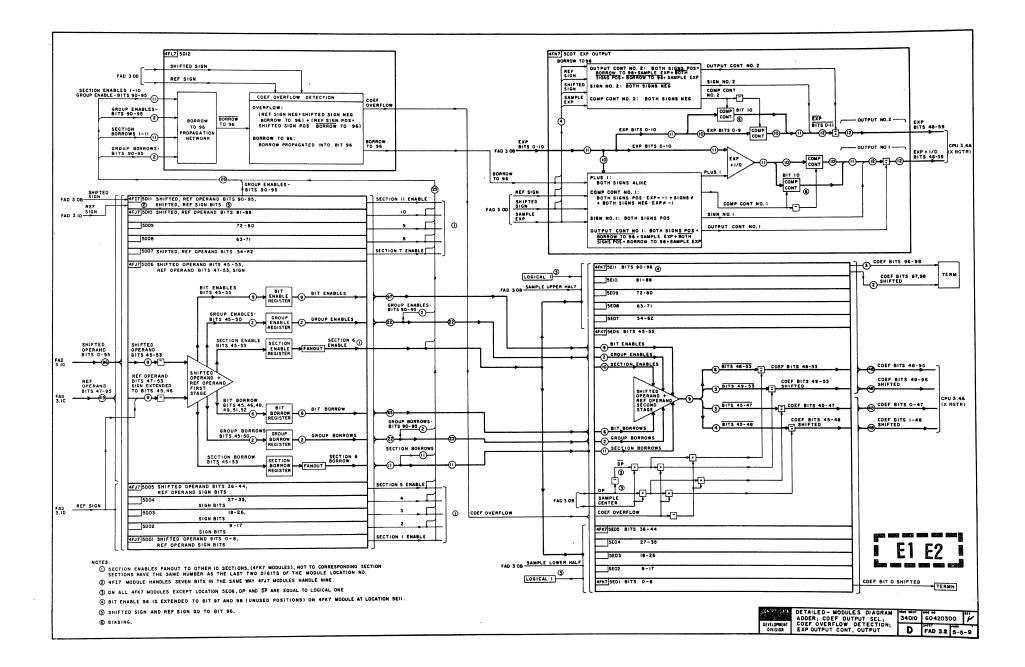

| Adder; Coefficient Output Selection,                                                                                           |                |

| Coefficient Overflow Detection;                                                                                                |                |

| Exponent Output Control; Output                                                                                                |                |

| (FAD 3.2)                                                                                                                      | 5-5-9          |

| Logic Diagrams                                                                                                                 |                |

| 4FA7                                                                                                                           | 5-5-11         |

| 4FB7                                                                                                                           | 5-5-13         |

| 4FC7                                                                                                                           | 5-5-15         |

| 4FD7                                                                                                                           | 5-5-17         |

| 3FE7                                                                                                                           | 5-5-19         |

| 4FF7                                                                                                                           | 5-5-21         |

| 4FG7                                                                                                                           | 5-5-23         |

| 3FH7                                                                                                                           | 5-5-25         |

| 4F17                                                                                                                           | 5-5-27         |

| 4FJ7                                                                                                                           | 5-5-29         |

| 4FK7                                                                                                                           | 5-5-31         |

| 4FL7                                                                                                                           | 5-5-33         |

| 3FM7                                                                                                                           | 5-5-35         |

| 4FN7                                                                                                                           | 5-5-37         |

| 4F07                                                                                                                           | 5-5-39         |

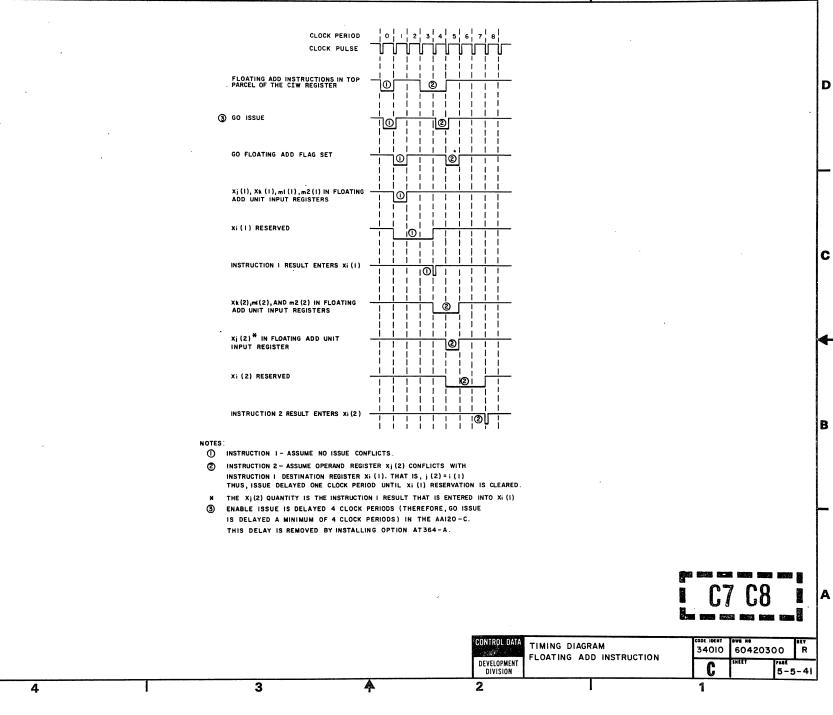

| Timing Diagram, Floating Add                                                                                                   |                |

| Instruction                                                                                                                    | 5-5-41         |

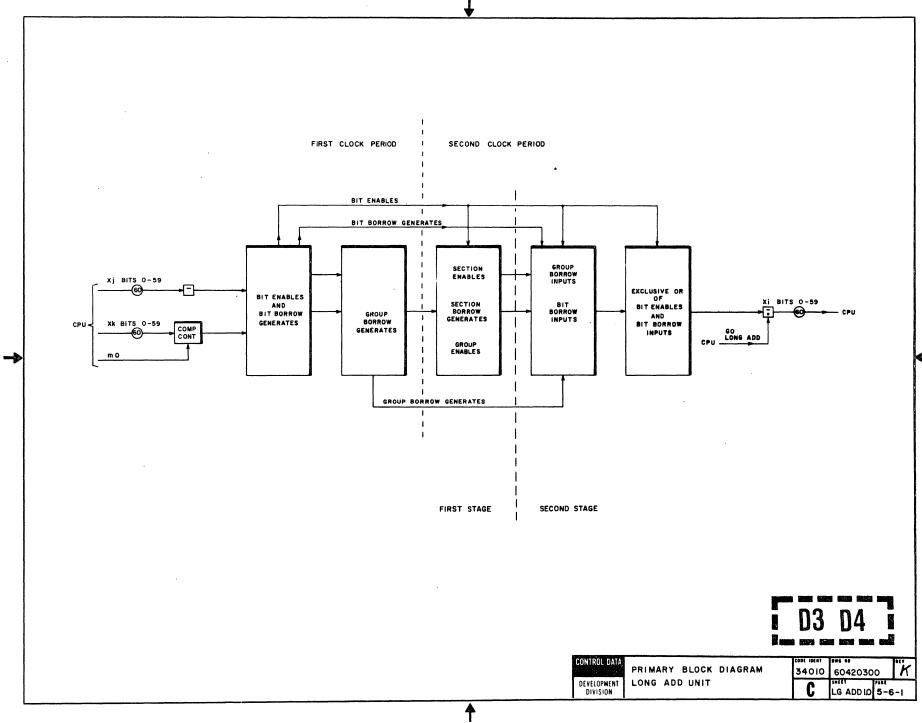

| Part 6. Long Add Unit                                                                                                          |                |

| Primary Block Diagram (LG ADD 1.0)                                                                                             | 5-6-1          |

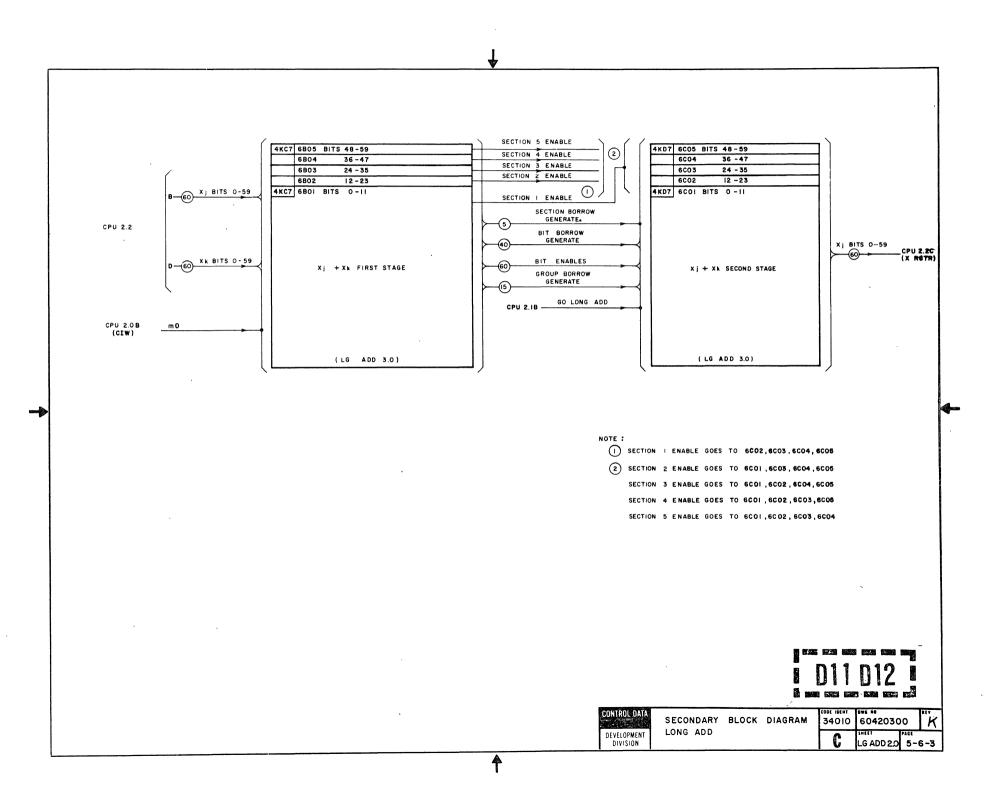

| Secondary Block Diagram (LG ADD 2.0)                                                                                           | 5-6-3          |

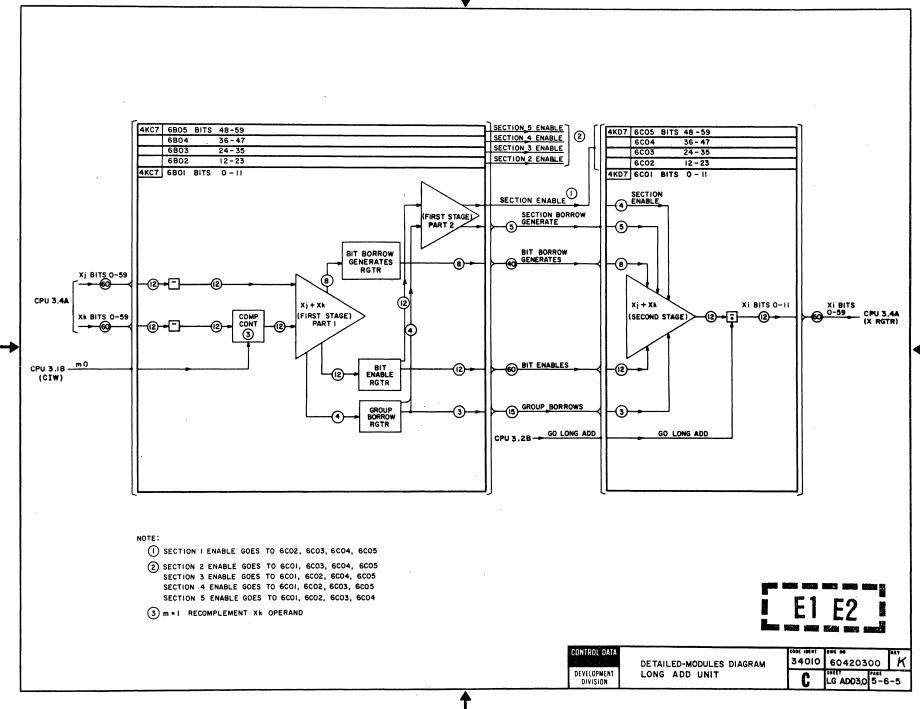

| Detailed-Modules Diagram (LG ADD 3.0)                                                                                          | 5-6-5          |

| Logic Diagrams                                                                                                                 | 7-0-7          |

| 4KC7                                                                                                                           | 5-6-7          |

|                                                                                                                                | 5-6-9          |

| 4KD7                                                                                                                           |                |

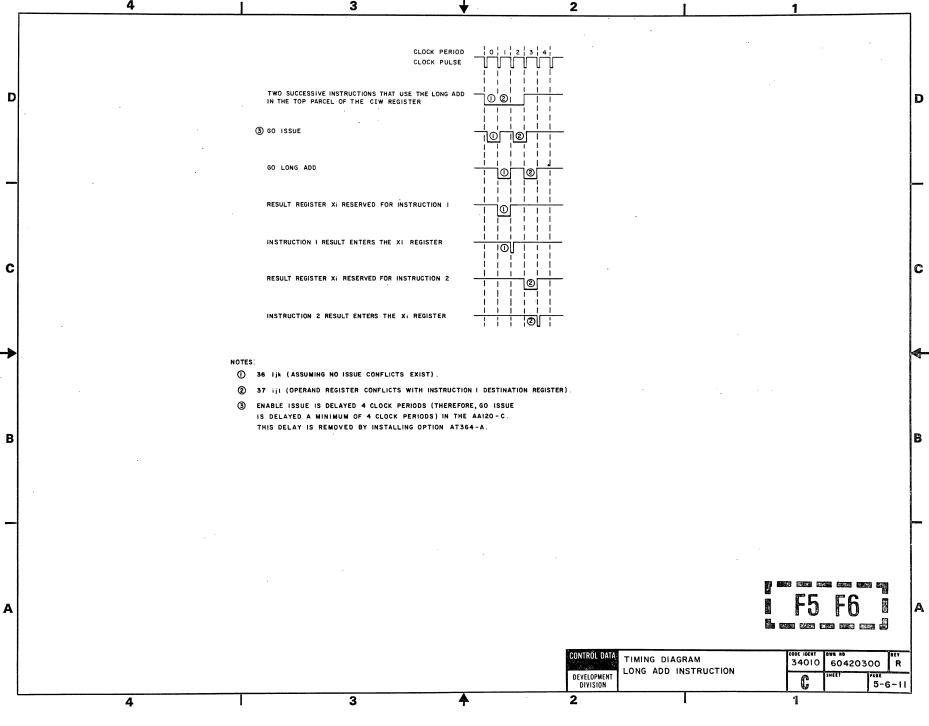

| Timing Diagram, Long Add Instruction                                                                                           | 5-6-11         |

| Part 7. Multiply Unit                                                                                                          |                |

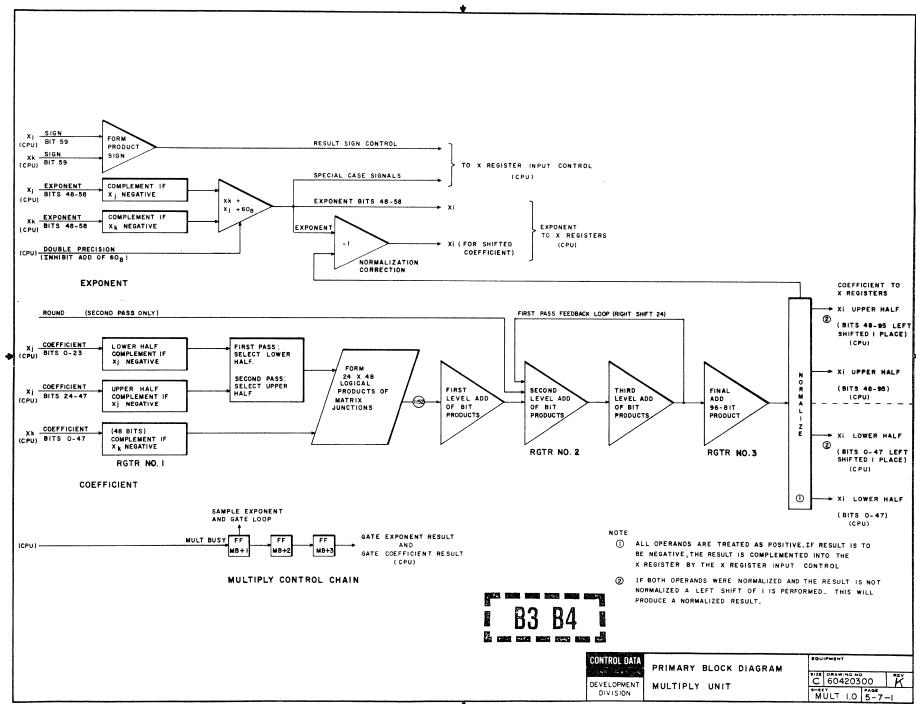

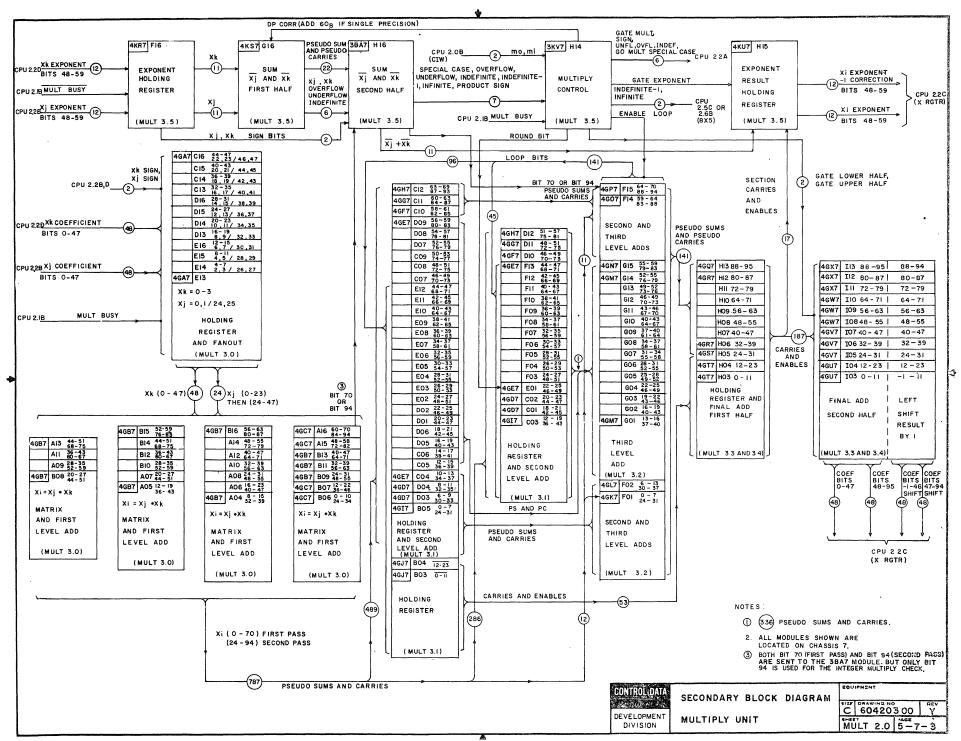

| Primary Block Diagram (MULT 1.0)                                                                                               | 5-7-1          |

| Secondary Block Diagram (MULT 2.0)                                                                                             | 5-7-3          |

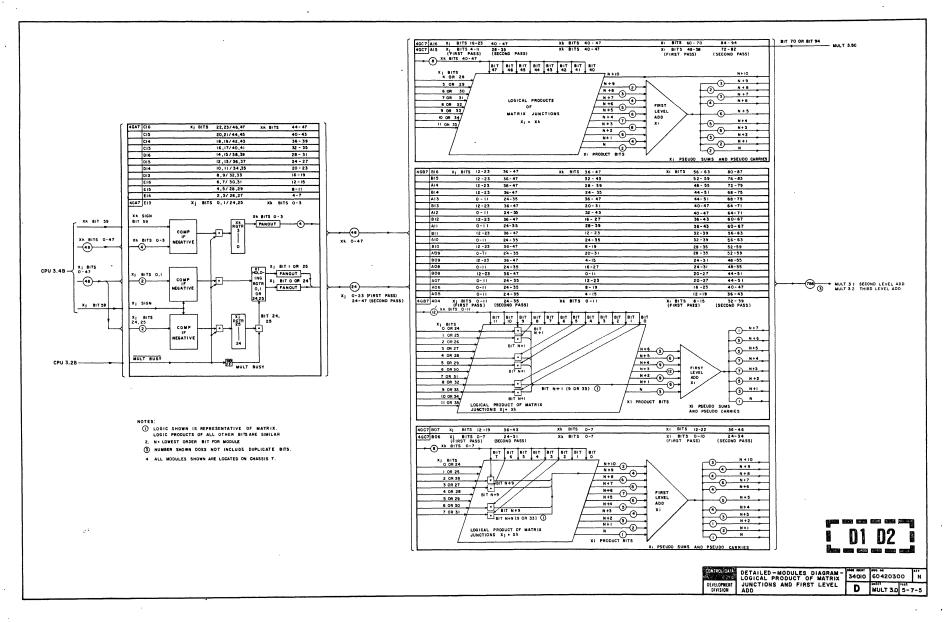

| Detailed-Modules Diagrams                                                                                                      |                |

| Logical Product o Matrix Junctions                                                                                             |                |

| and First Level Add (MULT 3.0)                                                                                                 | 5-7-5          |

60420300 Y

•

.

ix 🛛

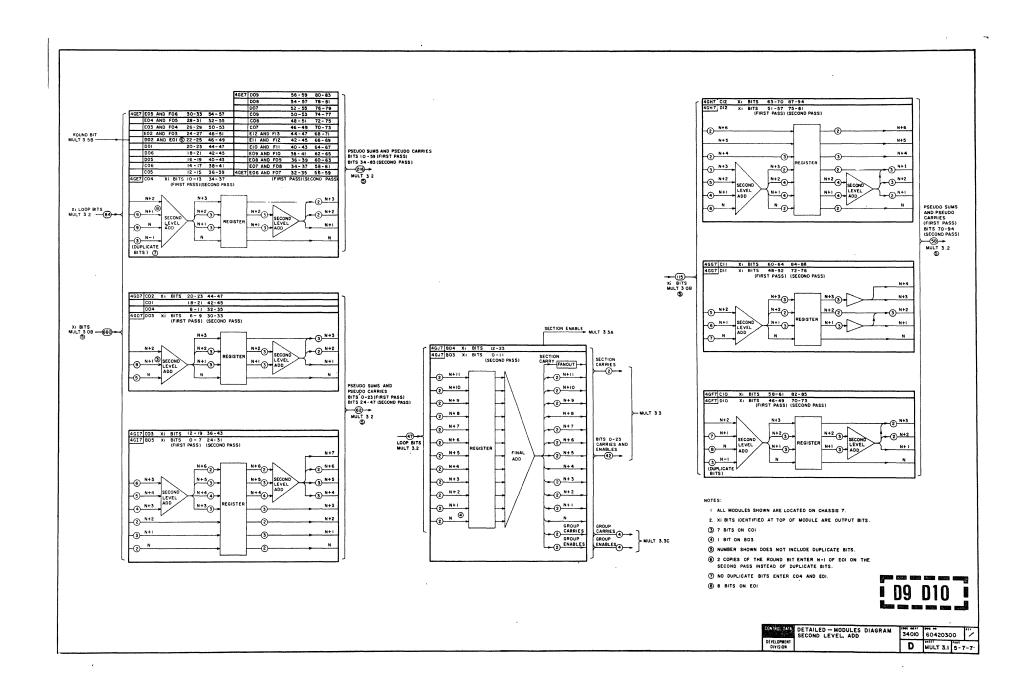

| Second Level Add (MULT 3.1)          | 5-7-7  | 4DC7                                 | 5-8-17  |

|--------------------------------------|--------|--------------------------------------|---------|

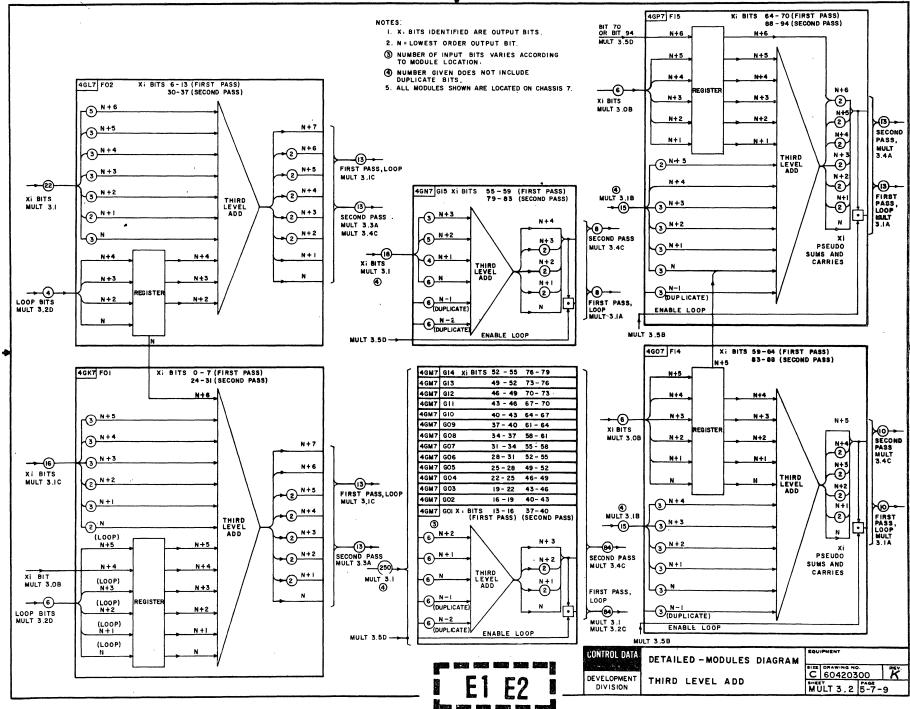

| Third Level Add (MULT 3.2)           | 5-7-9  | 4DD7                                 | 5-8-19  |

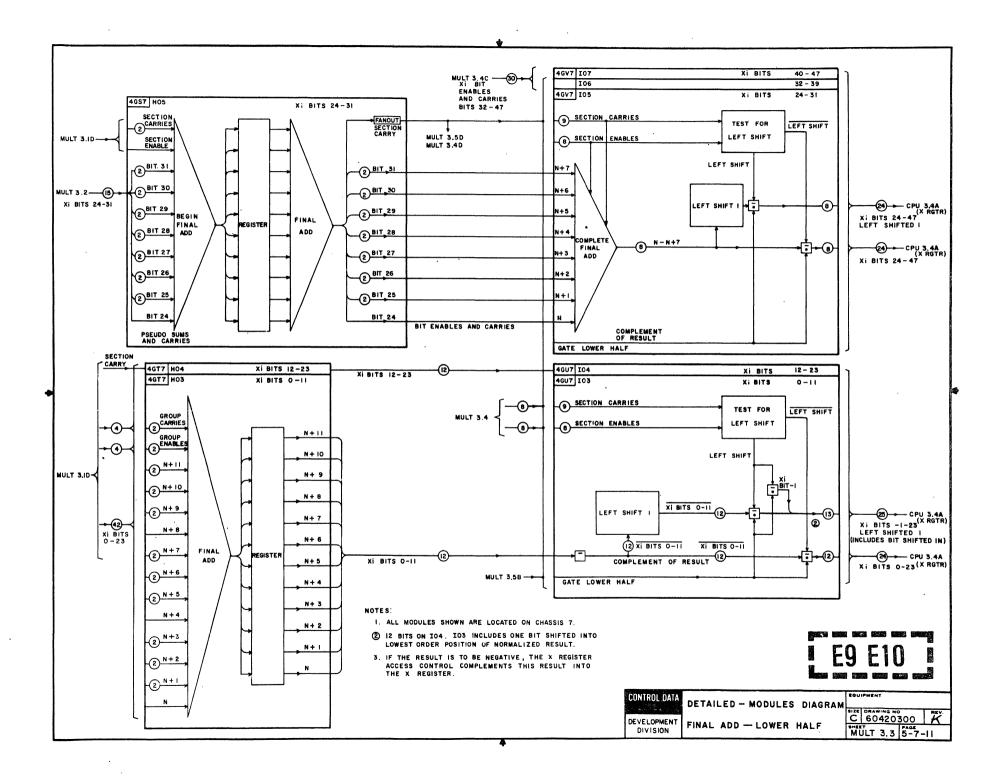

| Final Add - Lower Half (MULT 3.3)    | 5-7-11 | 4DE7                                 | 5-8-21  |

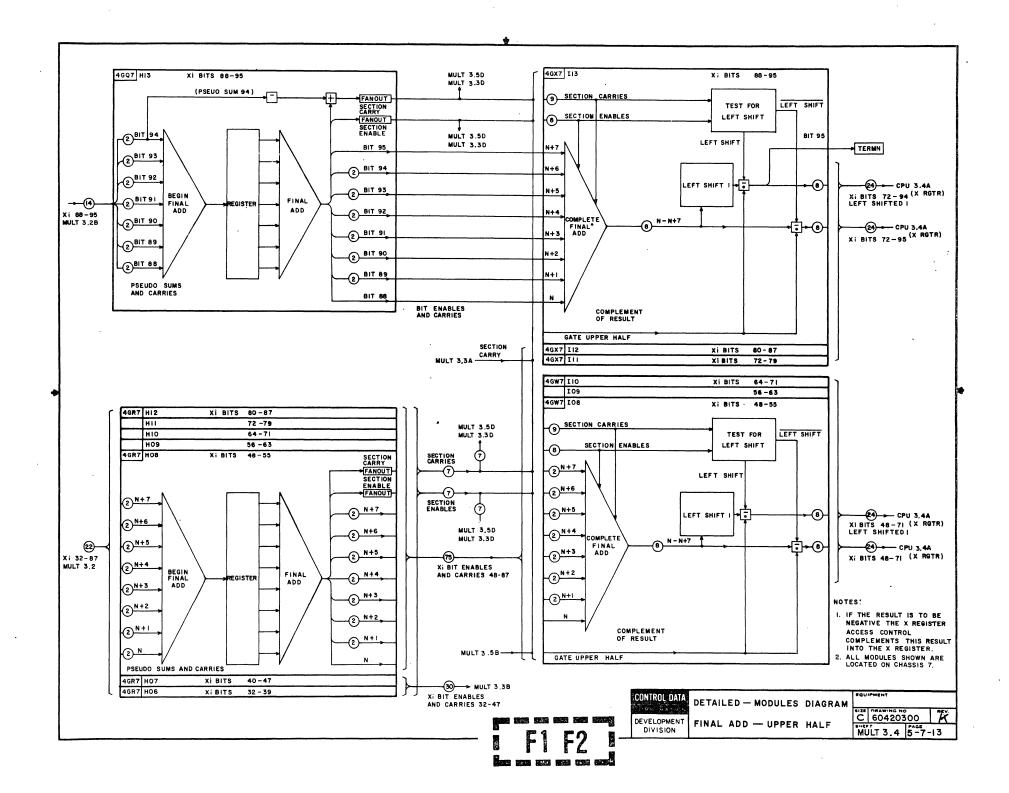

| Final Add - Upper Half (MULT 3.4)    | 5-7-13 | 4DF7                                 | 5-8-23  |

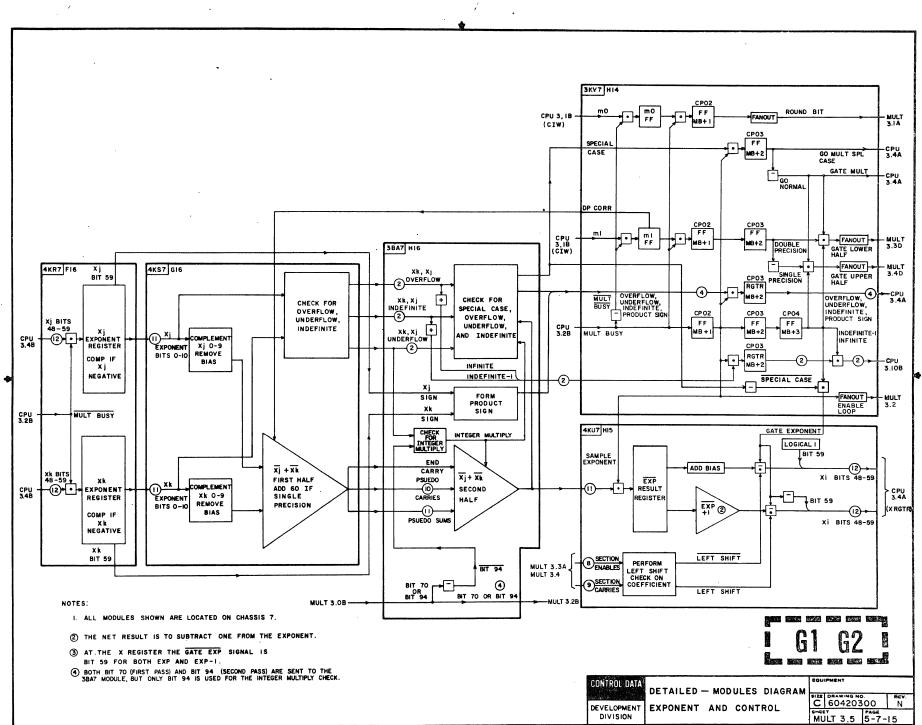

| Exponent and Control (MULT 3.5)      | 5-7-15 | 4DG7                                 | 5-8-25  |

|                                      | 5 1 15 | 4DH7                                 | 5-8-27  |

| Logic Diagrams                       | F 7 17 |                                      |         |

| 3BA7                                 | 5-7-17 | 4D17                                 | 5-8-29  |

| 4GA7                                 | 5-7-19 | 4DJ7                                 | 5-8-31  |

| 4GB7                                 | 5-7-21 | 4DK7                                 | 5-8-33  |

| 4GB7                                 | 5-7-23 | 4DL7                                 | 5-8-35  |

| 4GC7                                 | 5-7-25 | 4DM7                                 | 5-8-37  |

| 4GC7                                 | 5-7-27 | 4DN7                                 | 5-8-39  |

| 4GD7                                 | 5-7-29 | 4D07                                 | 5-8-41  |

| 4GE7                                 | 5-7-31 | 3DP7                                 | 5-8-43  |

|                                      |        |                                      |         |

| 4GF7                                 | 5-7-33 | 4DR7                                 | 5-8-47  |

| 4GG7                                 | 5-7-35 | 4DS7                                 | 5-8-49  |

| 4GH7                                 | 5-7-37 | 4KR7                                 | 5-8-51  |

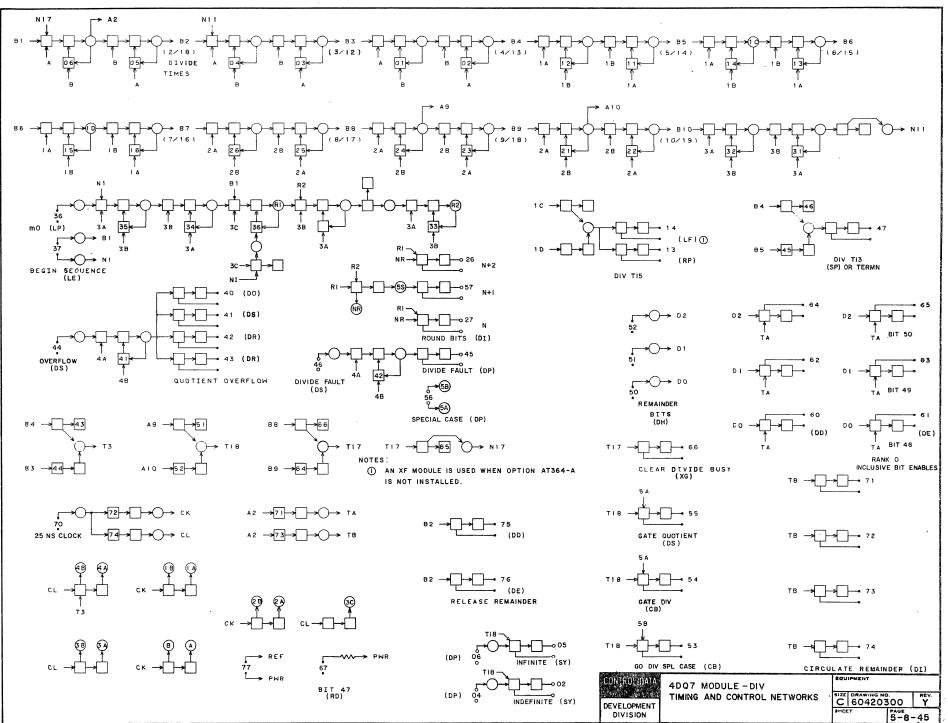

| 4G17                                 | 5-7-39 | Timing Diagram, Divide Instruction   | 5-8-53  |

| 4GJ7                                 | 5-7-41 |                                      |         |

| 4GK7                                 | 5-7-43 | Part 9. Population Count Unit        |         |

| 4GL7                                 | 5-7-45 |                                      |         |

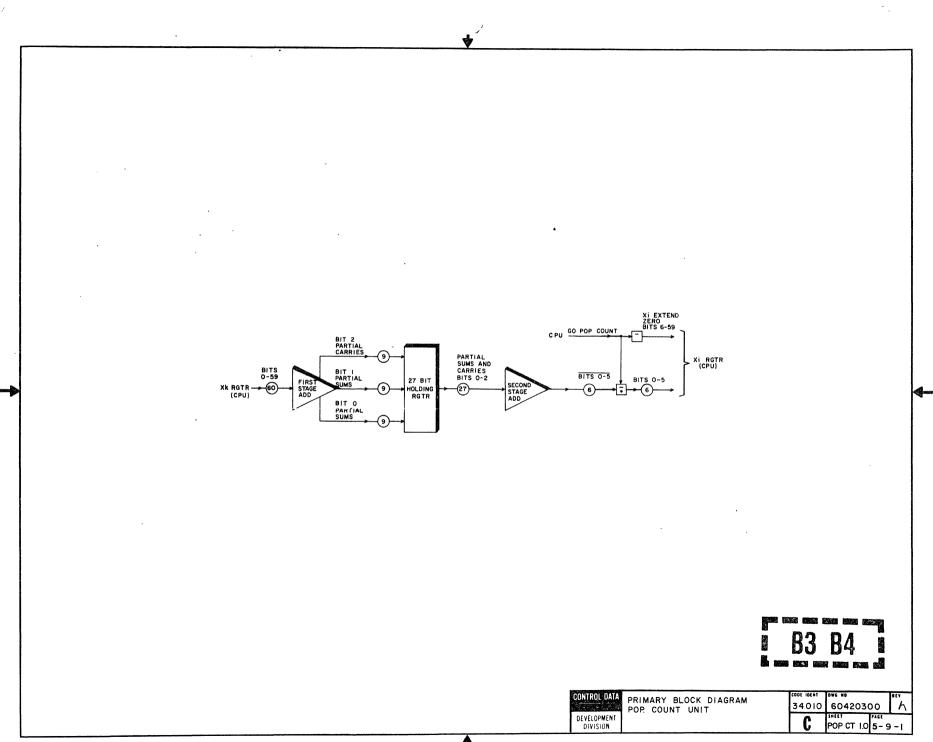

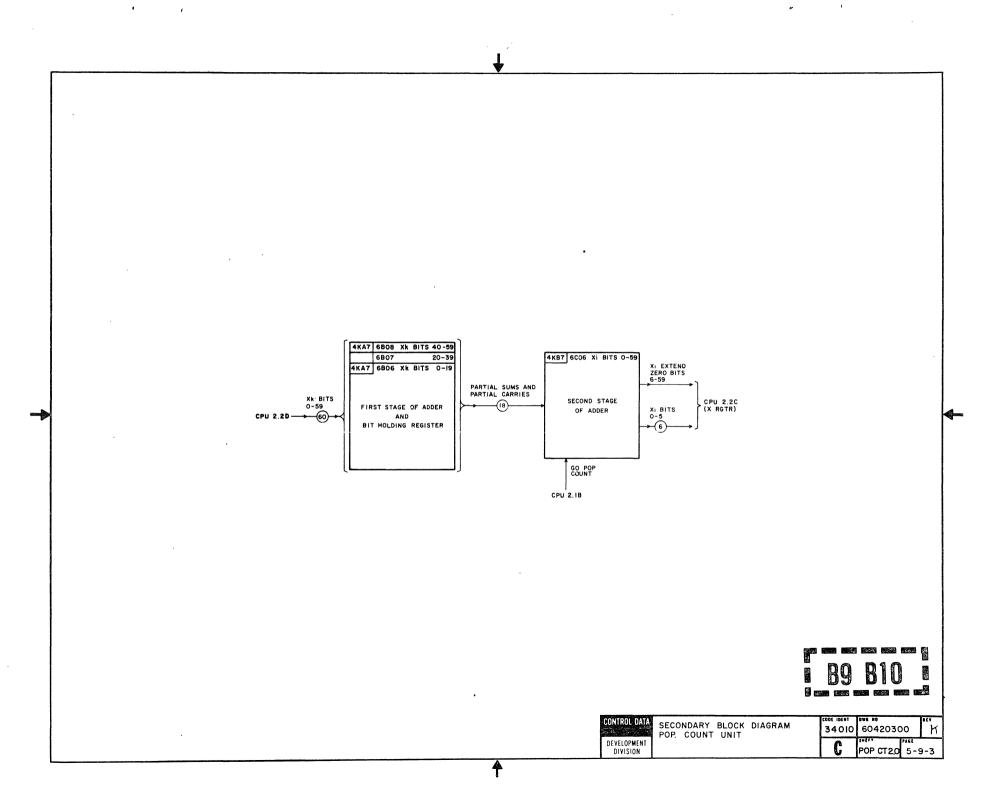

| 4GM7                                 | 5-7-47 | Primary Block Diagram (POP CT 1.0)   | 5-9-1   |

| 4GN7                                 | 5-7-49 |                                      |         |

|                                      |        | Secondary Block Diagram (POP CT 2.0) | 5-9-5   |

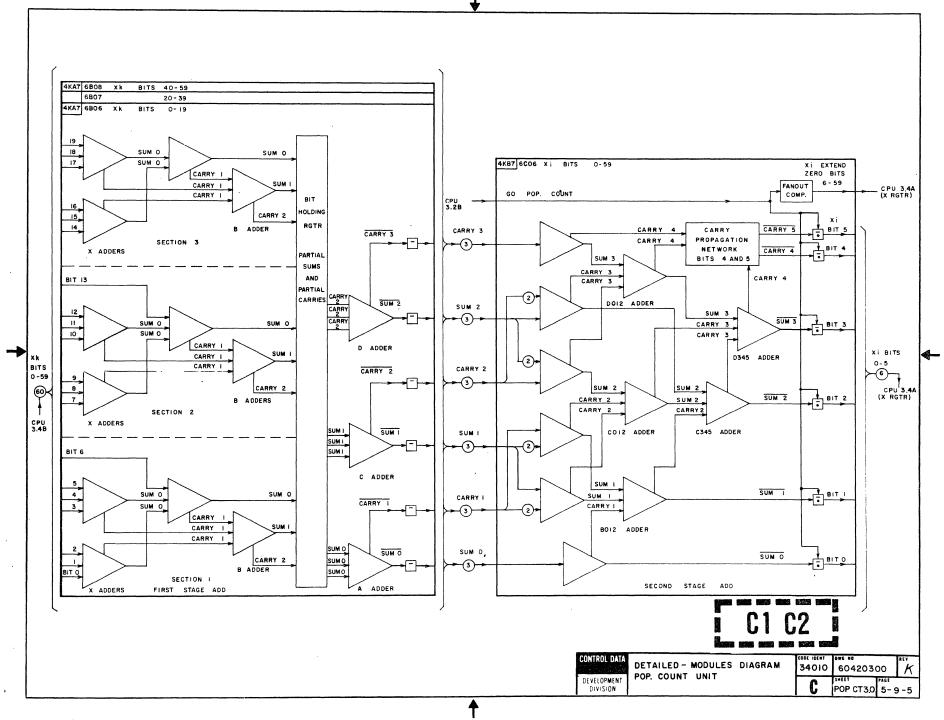

| 4G07                                 | 5-7-51 | Detailed-Modules Diagram (POP        |         |

| 4GP7                                 | 5-7-53 | CT 3.0)                              | 5-9-5   |

| 4CQ7                                 | 5-7-55 | Logic Diagrams                       |         |

| 4GR7                                 | 5-7-57 | 4KA7                                 | 5-9-7   |

| 4GS7                                 | 5-7-59 | 4KB7                                 | 5-9-9   |

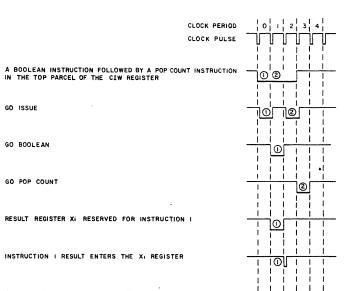

| 4GT7                                 | 5-7-61 | Timing Diagram, Population Count     |         |

| 4GU7                                 | 5-7-63 | Instruction                          | 5-9-11  |

| 4GV7                                 | 5-7-65 |                                      |         |

| 4GW7                                 | 5-7-67 | Part 10. Increment Unit              |         |

| 4GX7                                 | 5-7-69 |                                      |         |

| 4KR7                                 | 5-7-71 | Part 10A. Increment Unit Block       |         |

|                                      | 5-7-73 |                                      |         |

| 4KS7                                 |        | Diagrams (Models 175, 740, 750,      |         |

| 4KU7                                 | 5-7-75 | 760)                                 |         |

| 3KV7                                 | 5-7-77 |                                      |         |

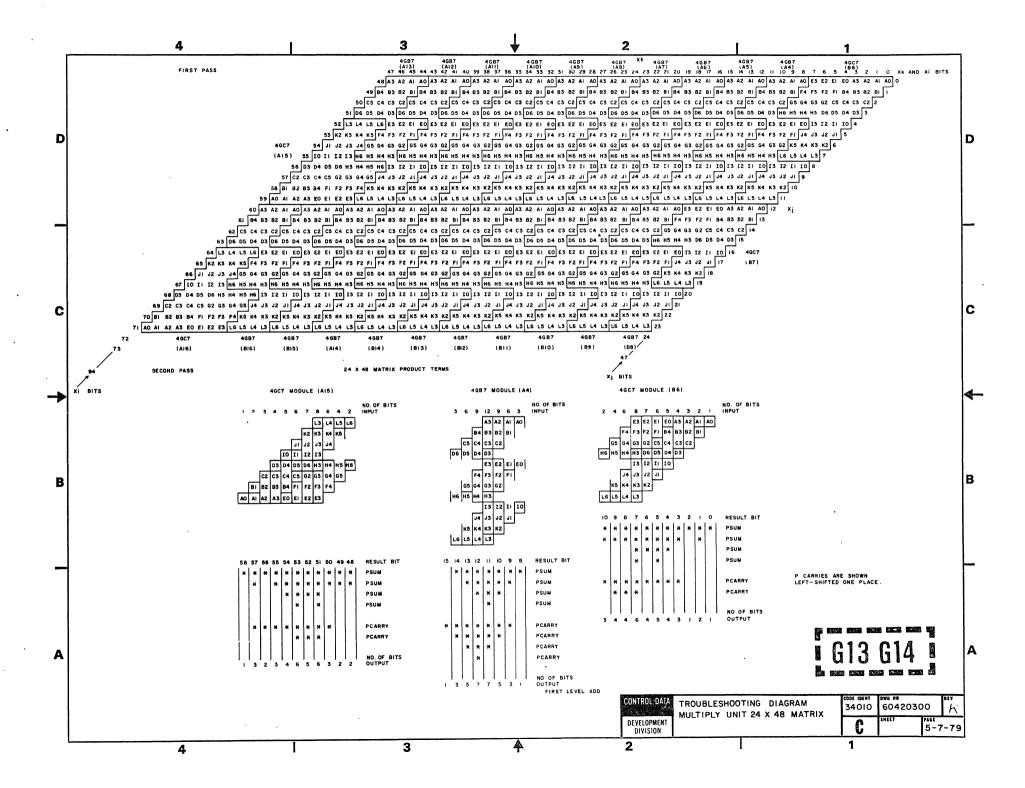

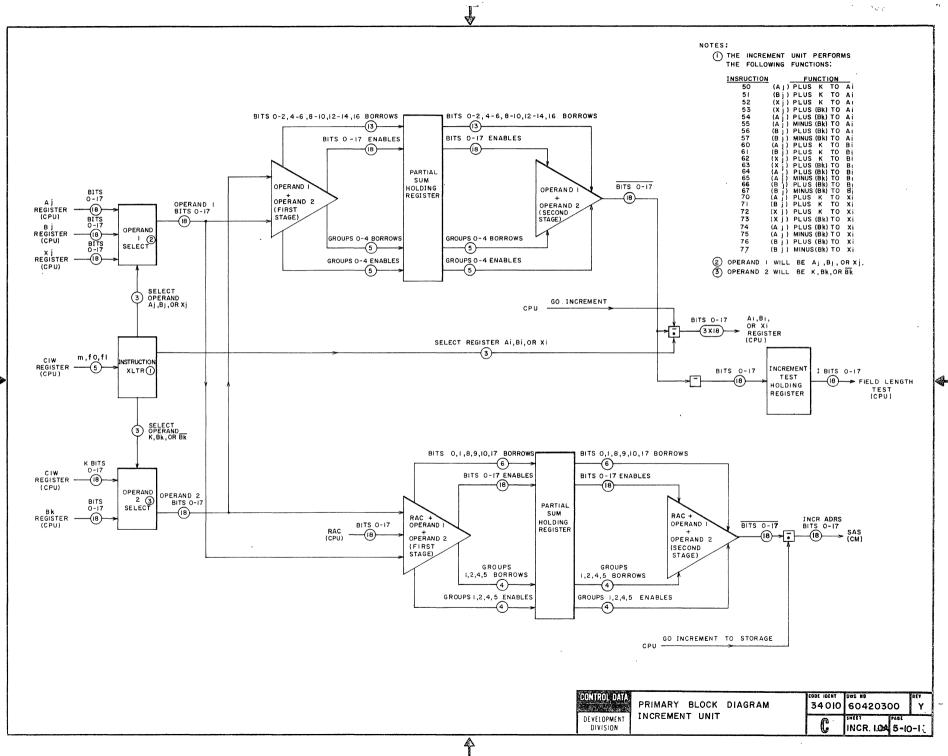

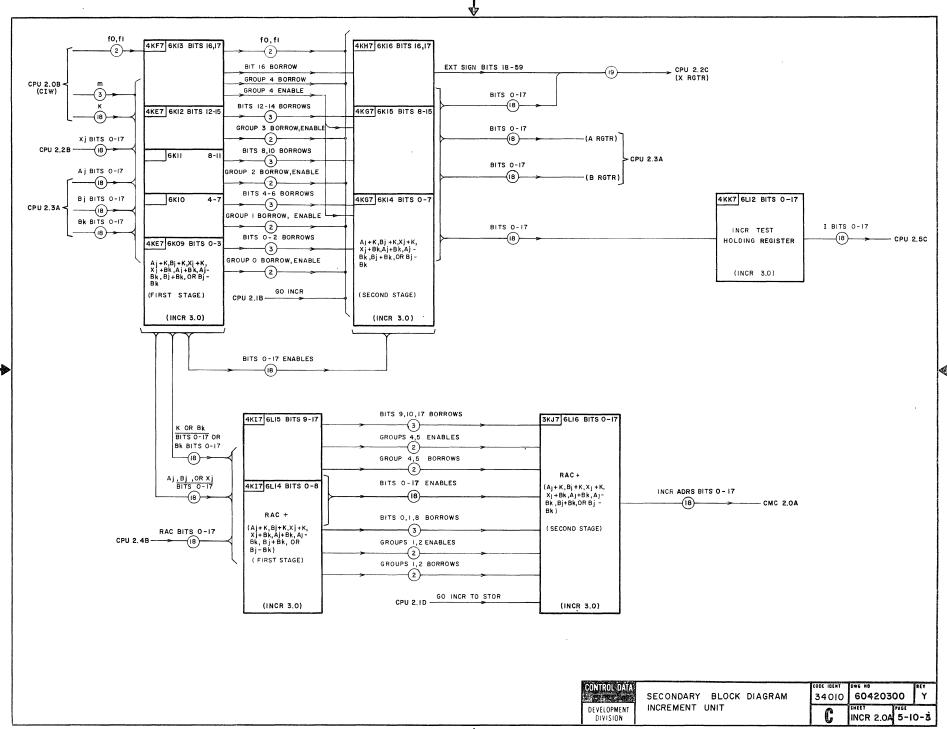

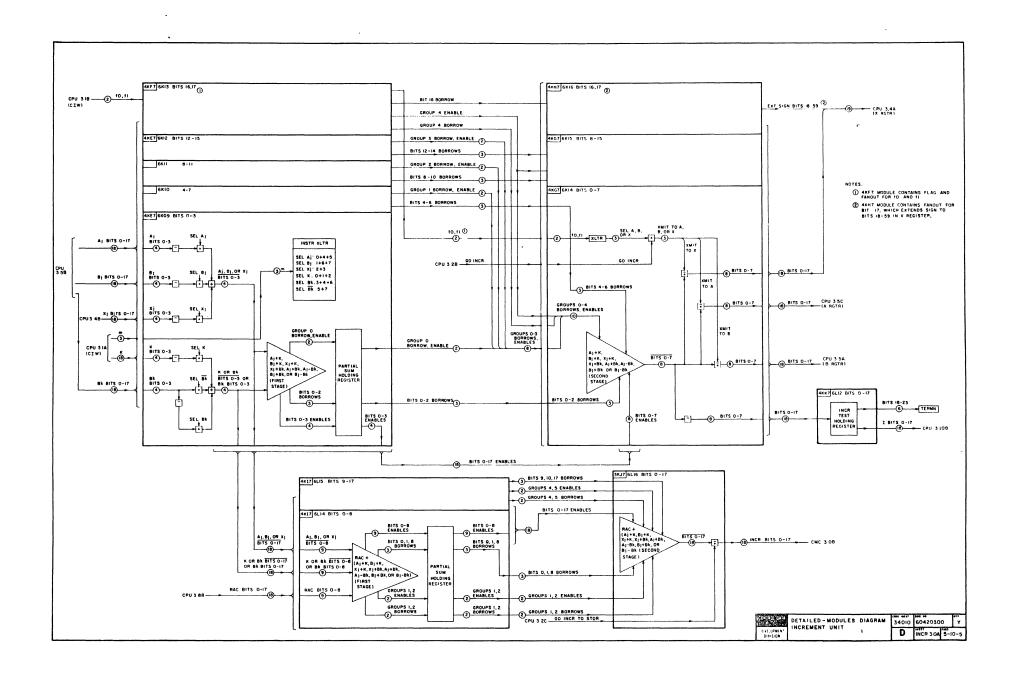

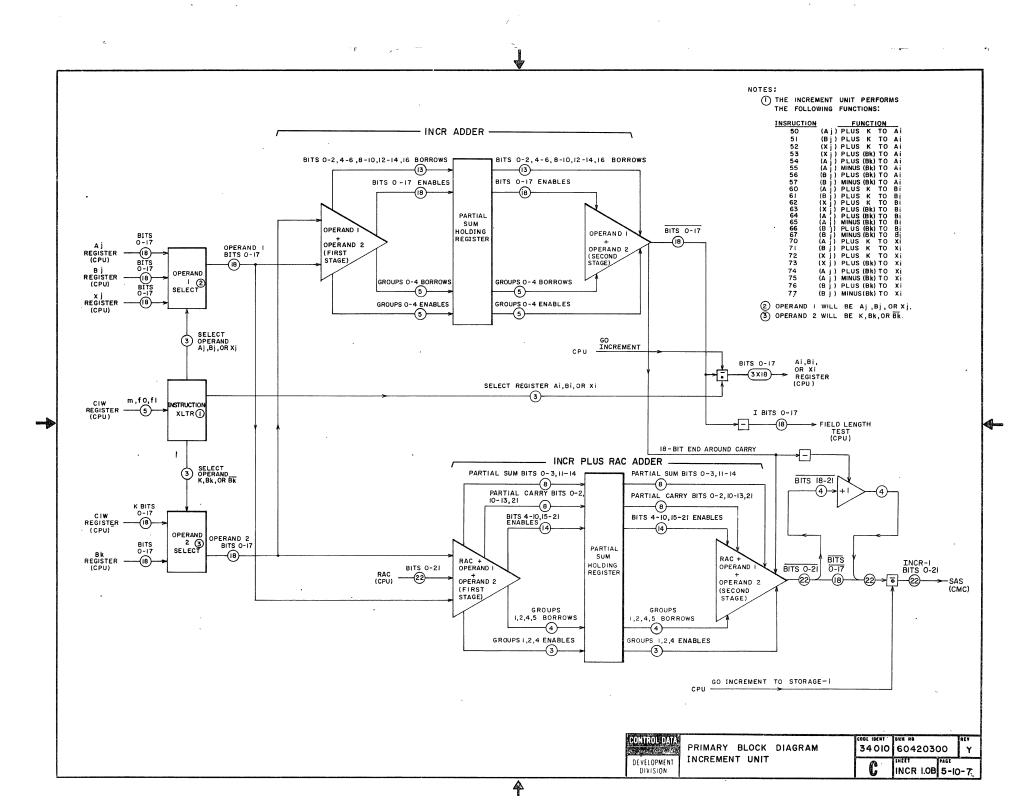

| Troubleshooting Diagram, Multiply    |        | Primary Block Diagram (INCR 1.0A)    | 5-10-1  |

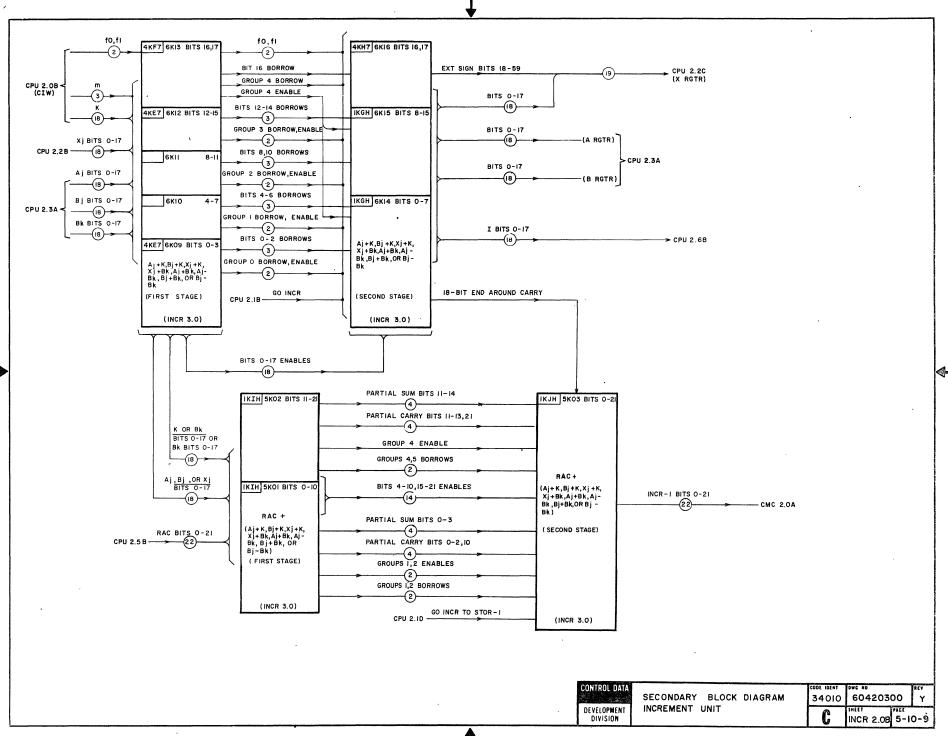

| Unit 24 x 48 Matrix                  | 5-7-79 | Secondary Block Diagram (INCR 2.0A)  | 5-10-3  |

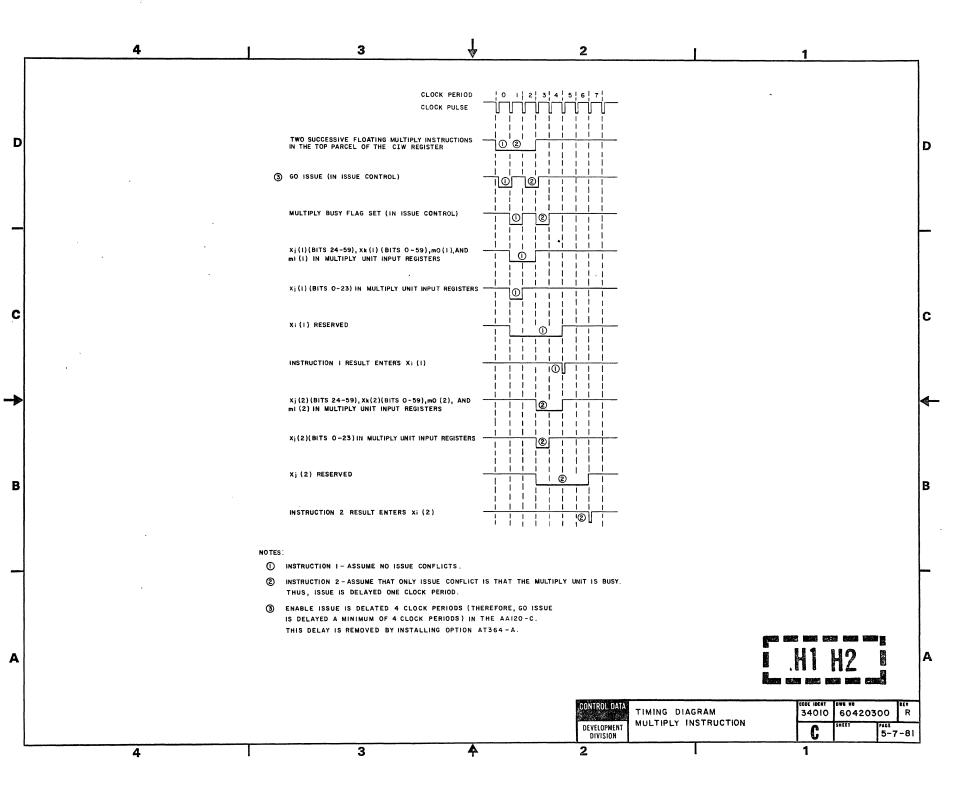

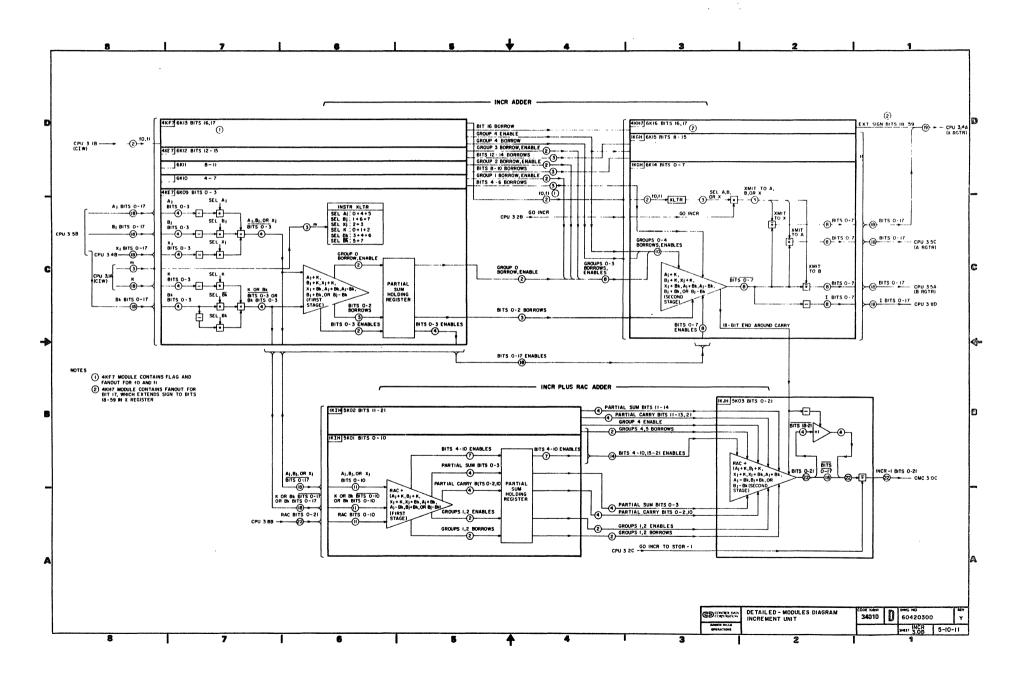

| Timing Diagram, Multiply Instruction | 5-7-81 | Detailed-Modules Diagram (INCR 3.0A) | 5-10-5  |

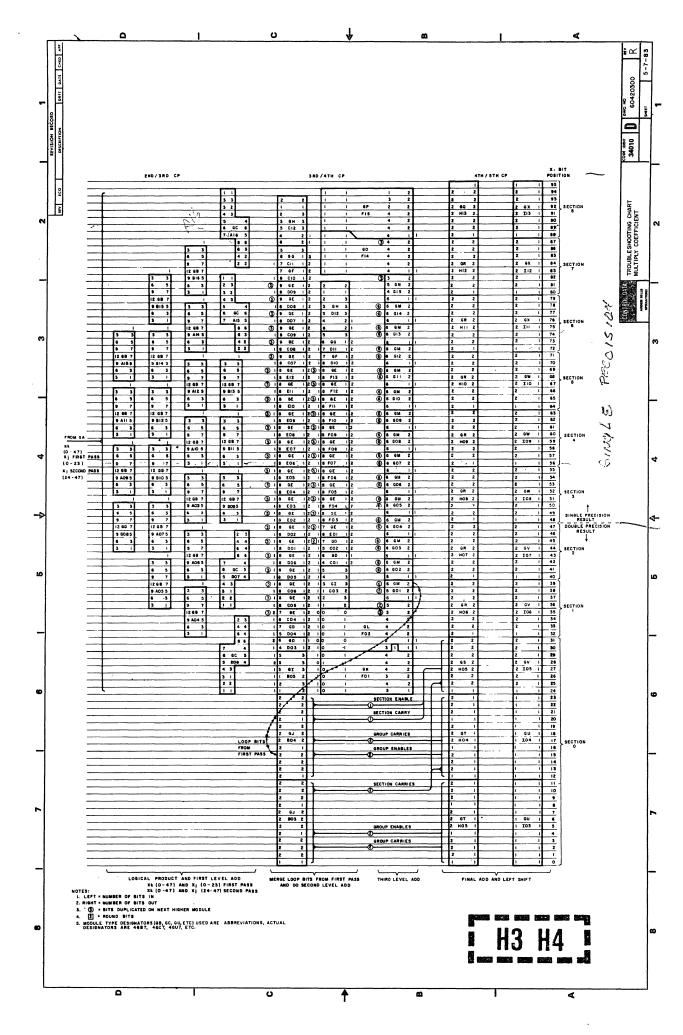

| Troubleshooting Chart, Multiply      |        | <b>3 1</b> <i>1</i>                  |         |

| Coefficient                          | 5-7-83 | Part 10B. Increment Unit Block       |         |

|                                      |        | Diagrams (Models 865, 875)           |         |

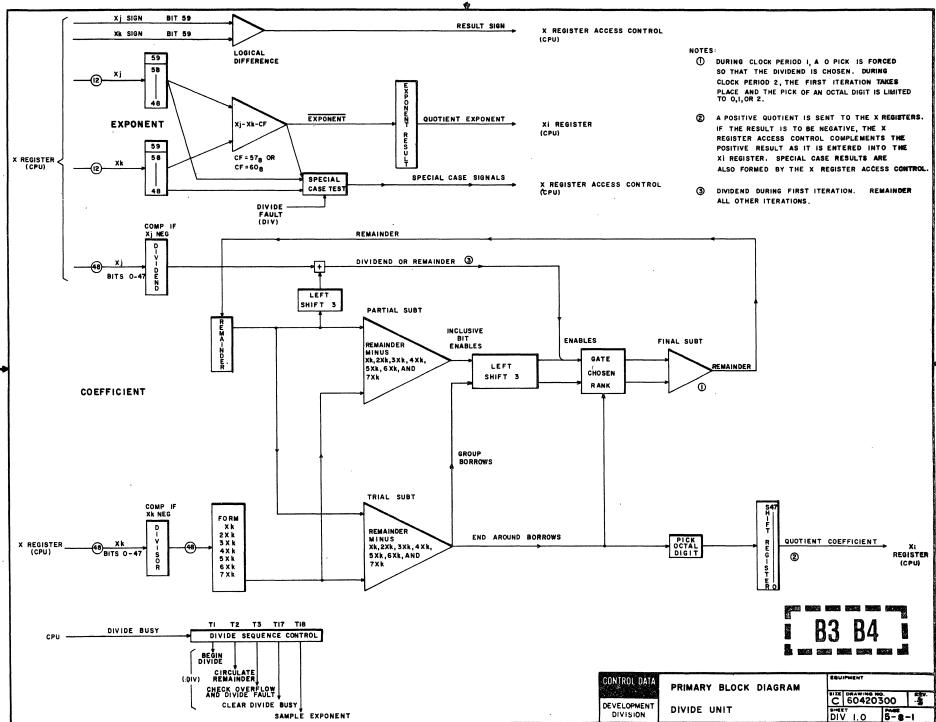

| Part 8. Divide Unit                  |        | Diagrams (models 000, 070)           |         |

| Tart 0. Divide onit                  |        | Brinsmy Block Diserver (INCB 1 OB)   | 5 10 7  |

|                                      | F 0 1  | Primary Block Diagram (INCR 1.0B)    | 5-10-7  |

| Primary Block Diagram (DIV 1.0)      | 5-8-1  | Secondary Block Diagram (INCR 2.0B)  | 5-10-9  |

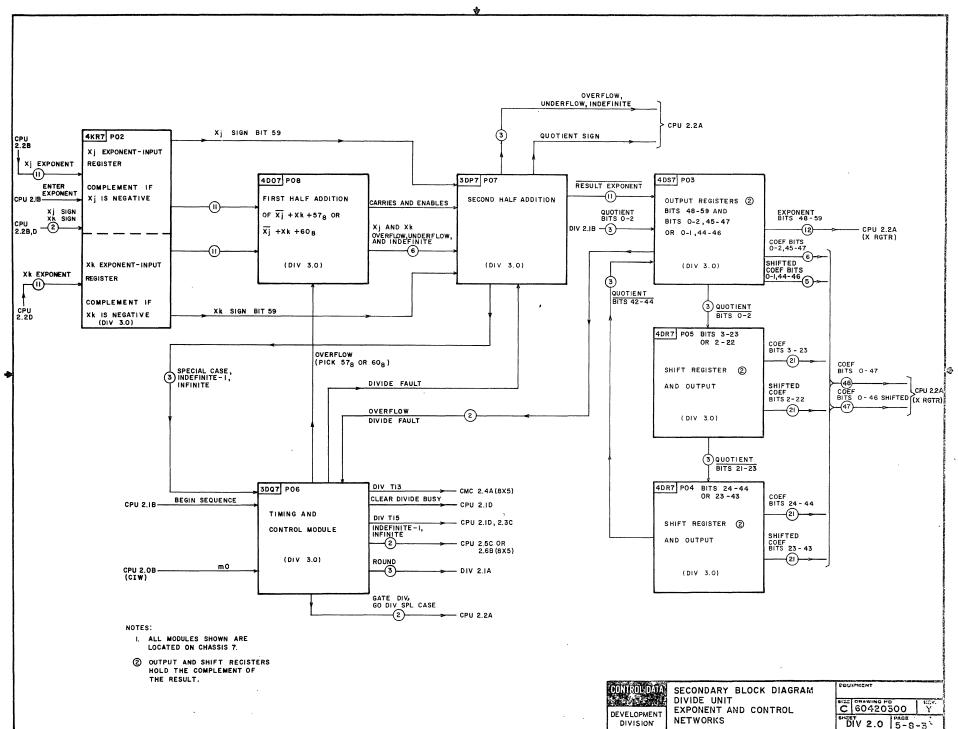

| Secondary Block Diagrams             |        | Detailed Modules Diagram (INCR 3.0B) | 5-10-11 |

| Exponent and Control Networks        |        |                                      |         |

| (DIV 2.0)                            | 5-8-3  | Part 10C. Logic and Timing Diagrams  |         |

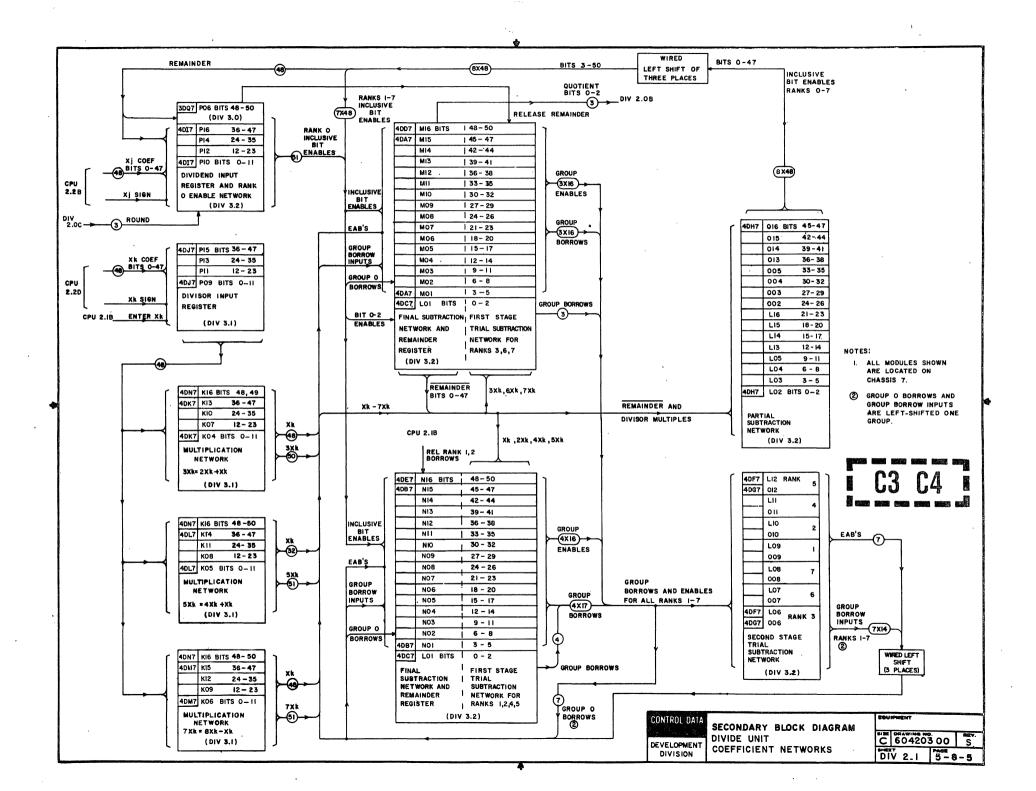

| Coefficient Networks (DIV 2.1)       | 5-8-5  |                                      |         |

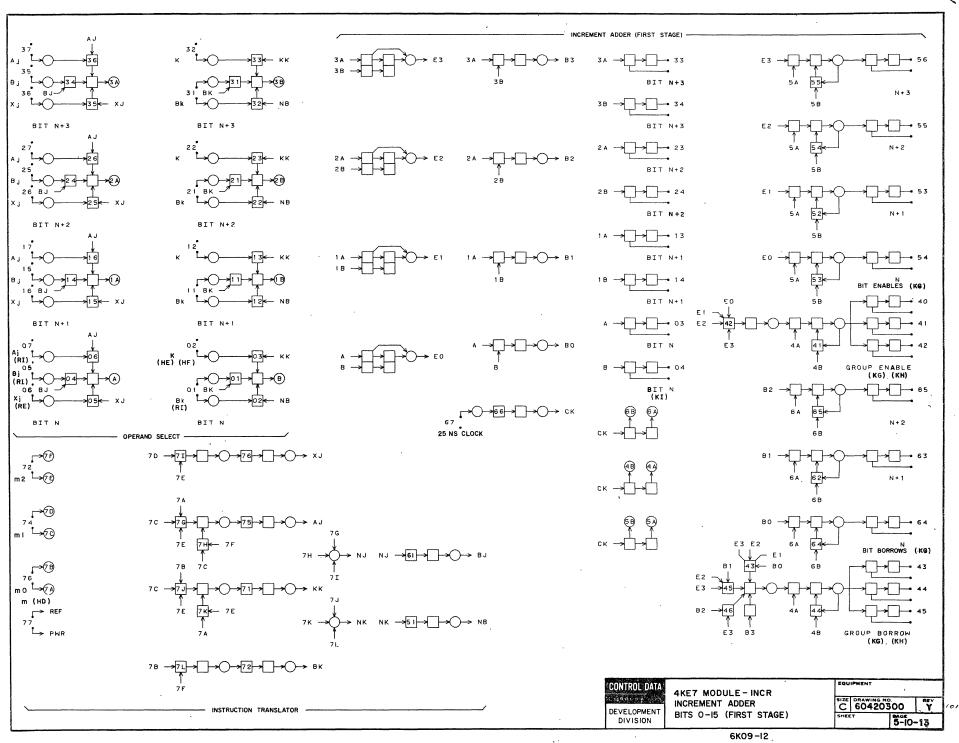

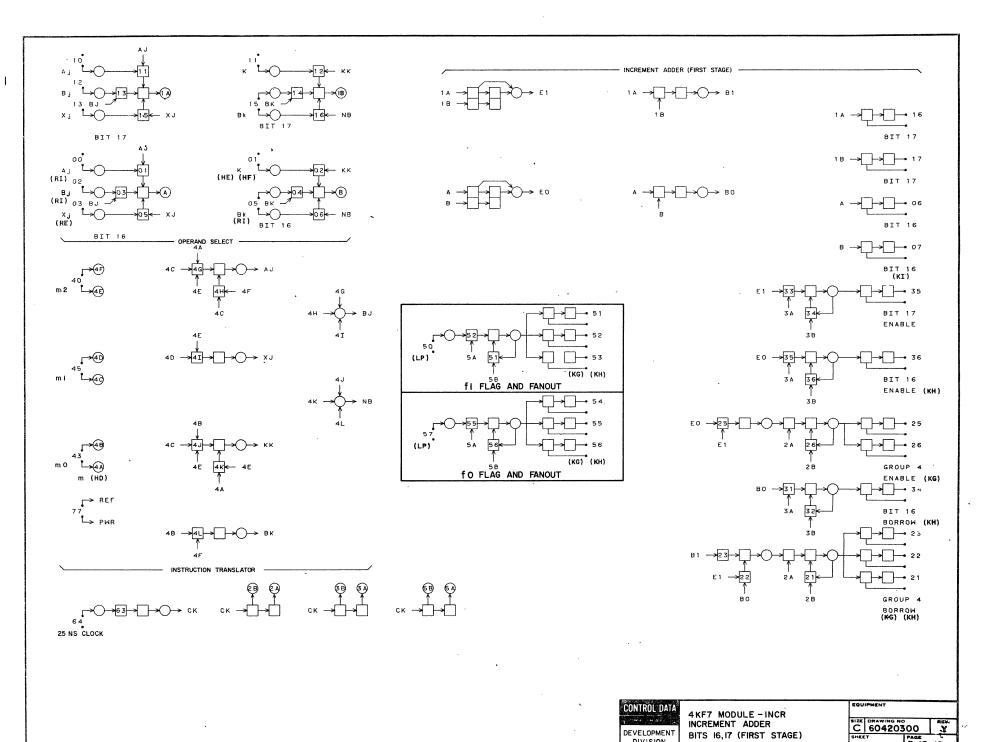

| Detailed-Modules Diagrams            |        | 4KE7                                 | 5-10-13 |

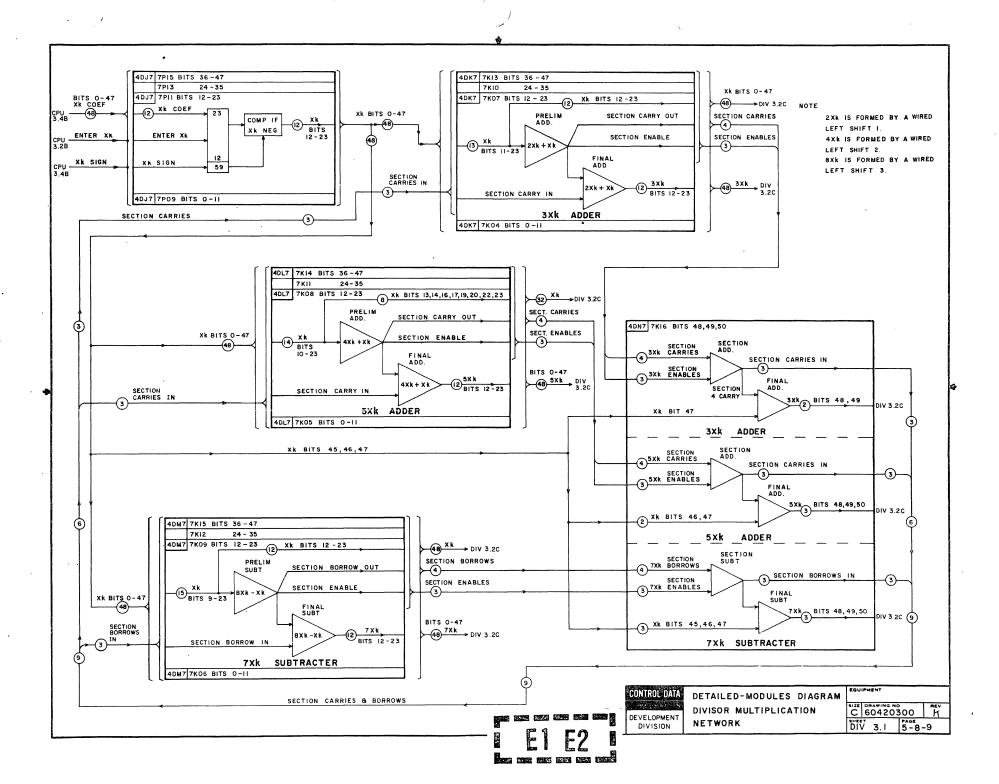

| Divisor Multiplication Network       |        | 4KF7                                 | 5-10-15 |

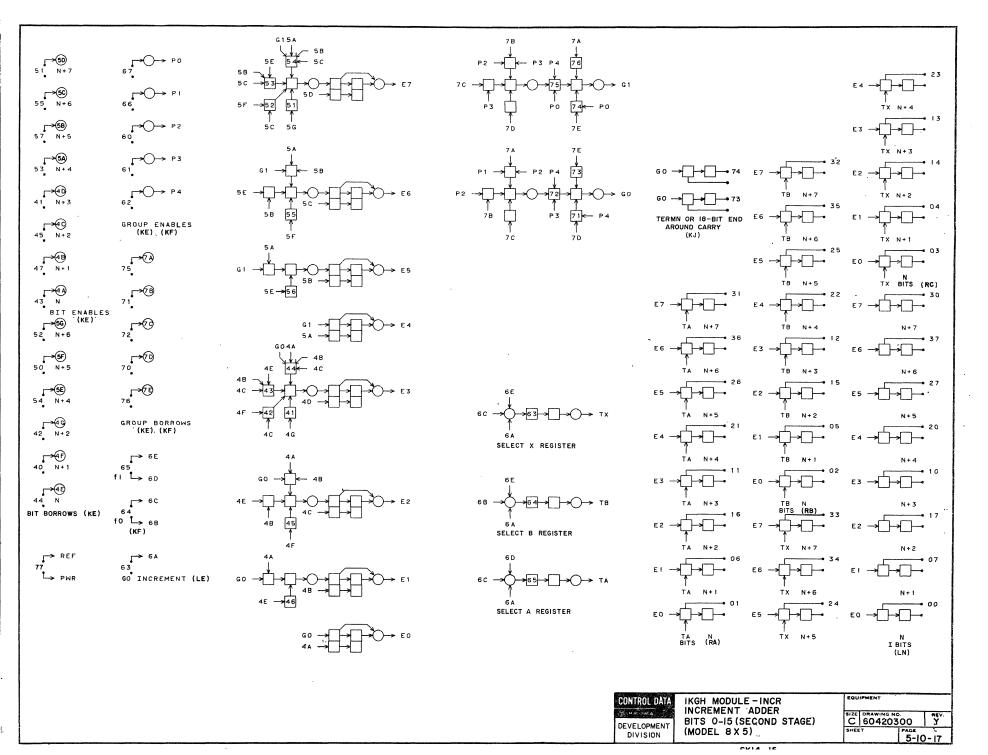

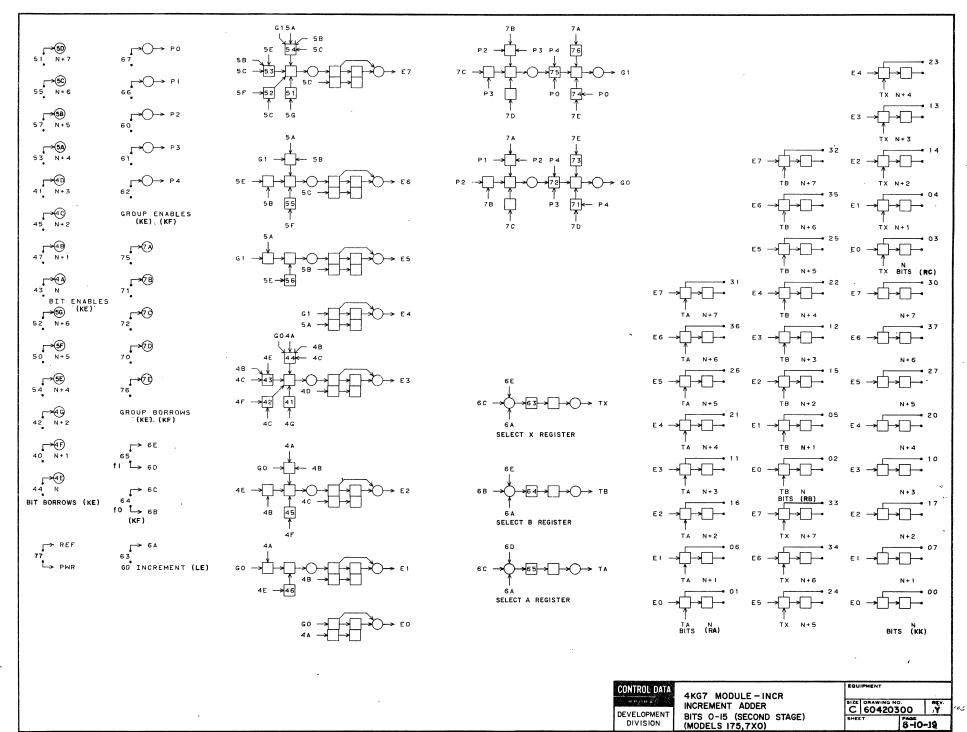

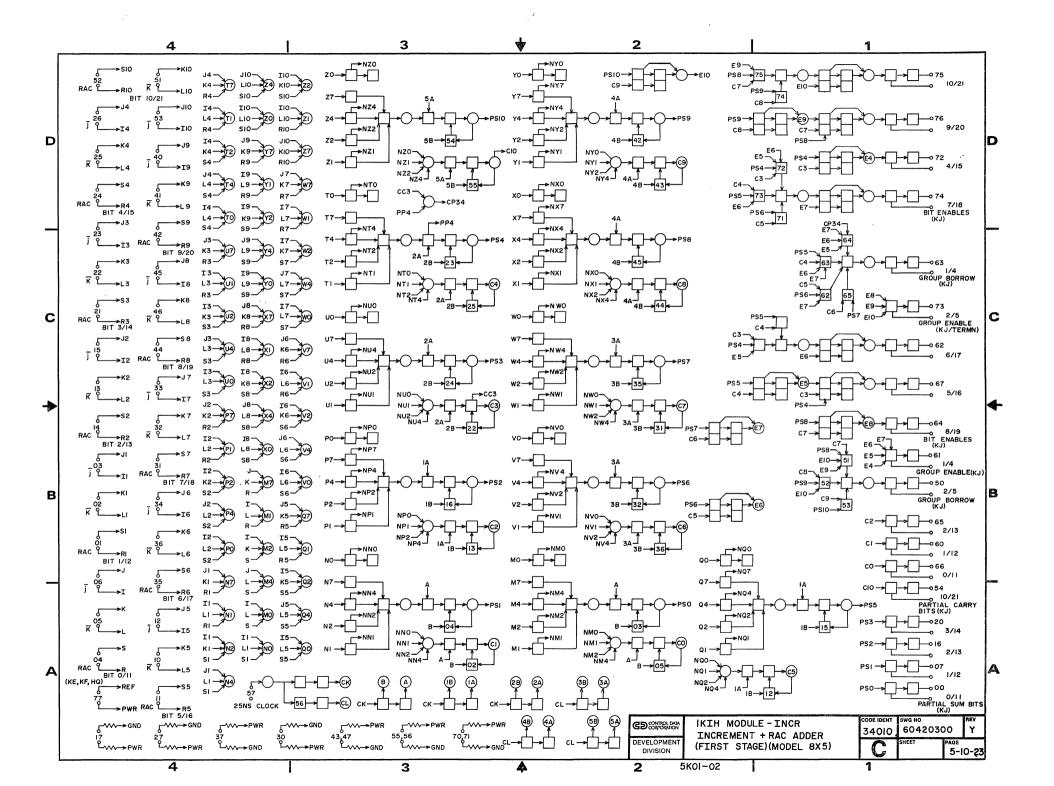

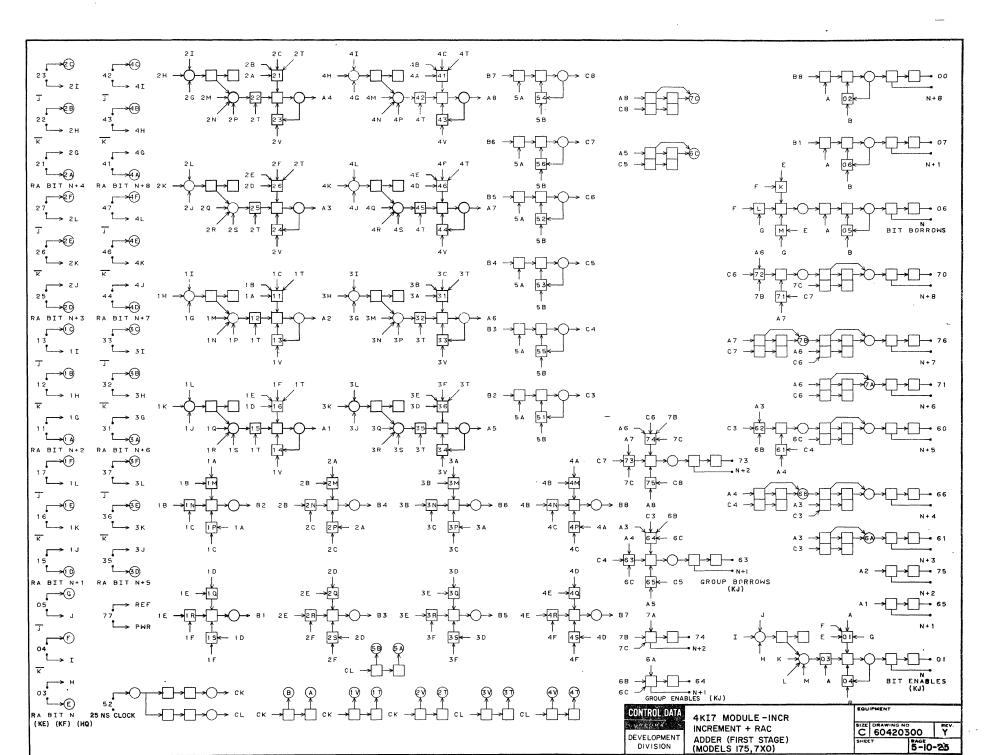

| (DIV 3.1)                            | 5-8-9  | IKGH (8X5)                           | 5-10-17 |

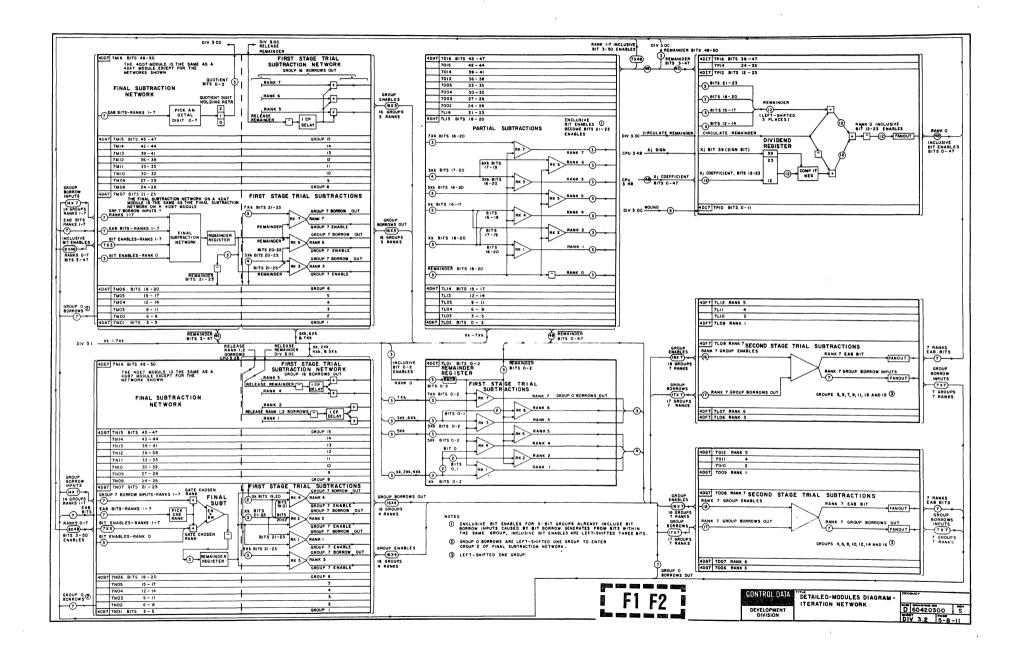

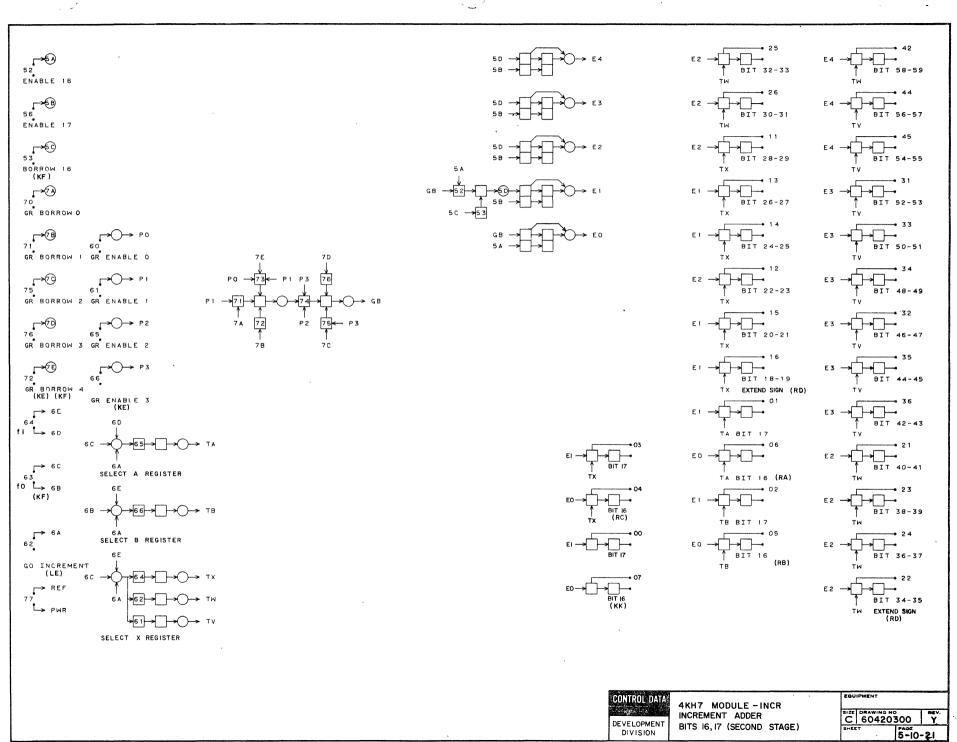

| Iteration Network (DIV 3.2)          | 5-8-11 | 4KG7 (175, 7X0)                      | 5-10-19 |

|                                      | J-0-11 | · · ·                                |         |

| Logic Diagrams<br>4DA7               | E 0 13 | 4KH7                                 | 5-10-21 |

|                                      | 5-8-13 | Logic Diagrams                       | F 10 00 |

| 4DB7                                 | 5-8-15 | 1KIH (8X5)                           | 5-10-23 |

|                                      |        |                                      |         |

**e** x

•

60420300 Y

.

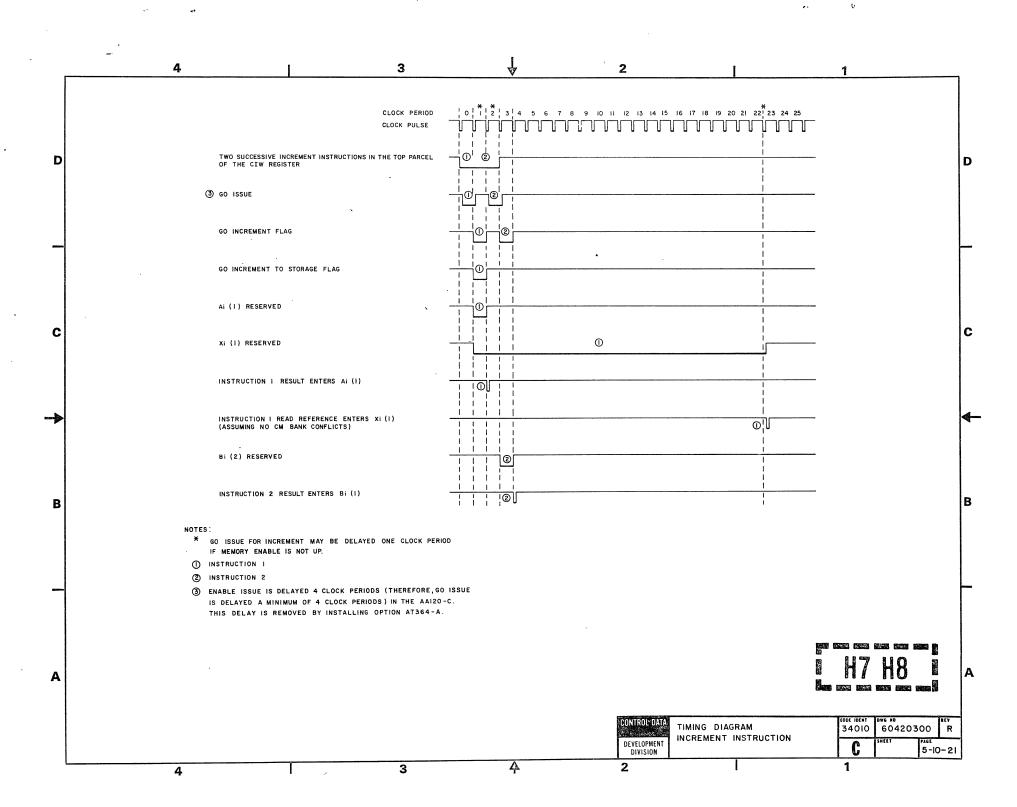

| 4KI7 (175, 7XO) | 5-10-25 | Timing Diagram, Increment Instruc- |         |

|-----------------|---------|------------------------------------|---------|

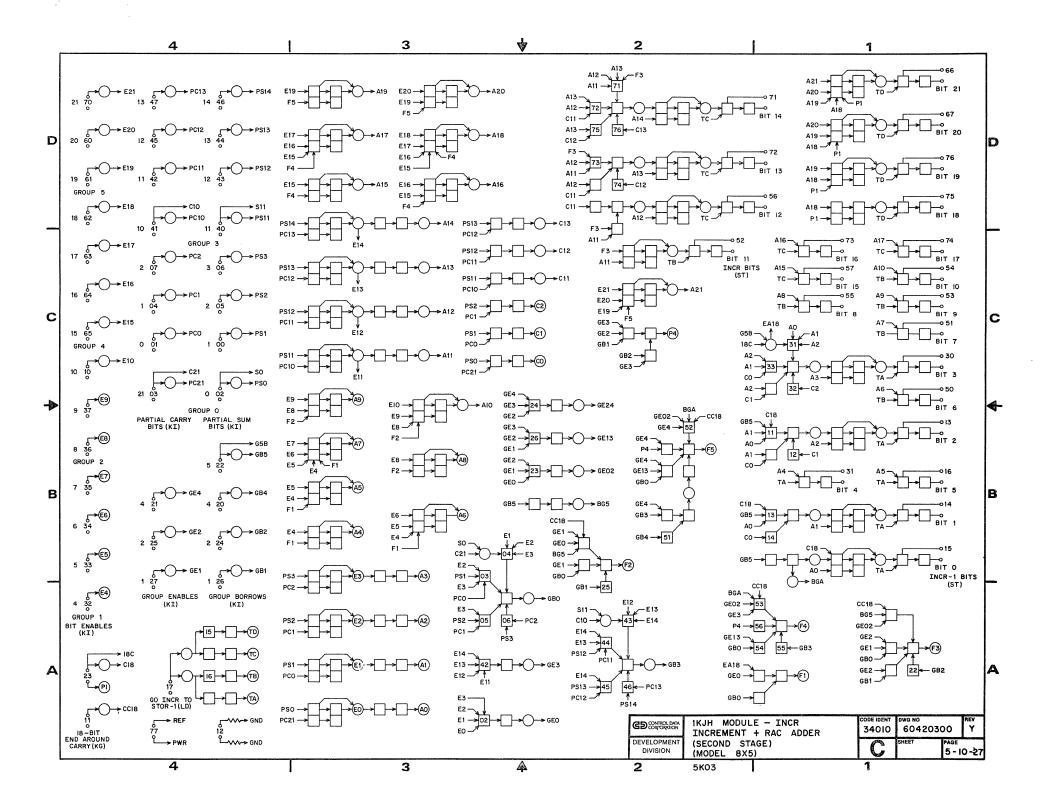

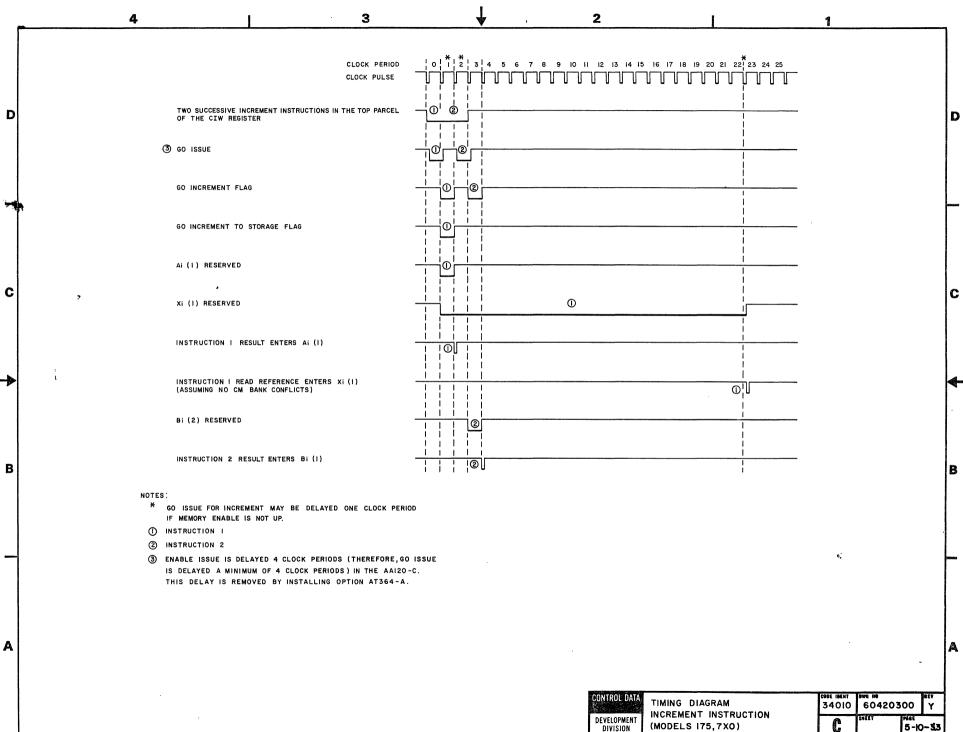

| IKJH (8X5)      | 5-10-27 | tion (175,7X0)                     | 5-10-33 |

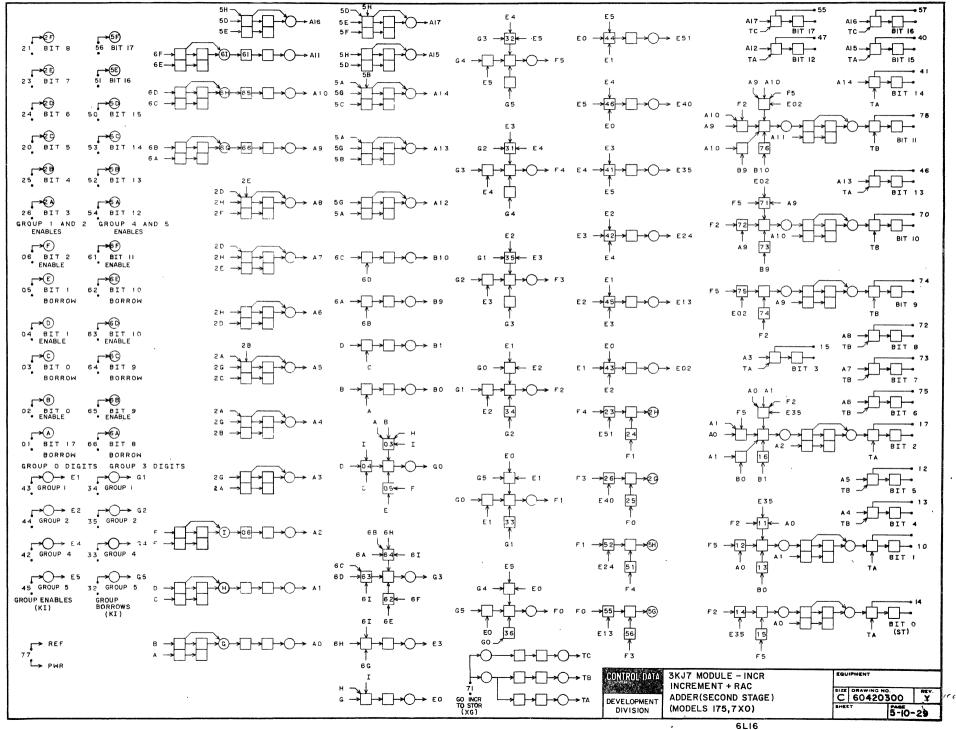

| 3KJ7 (175, 7X0) | 5-10-29 | Timing Diagram, Increment Instruc- |         |

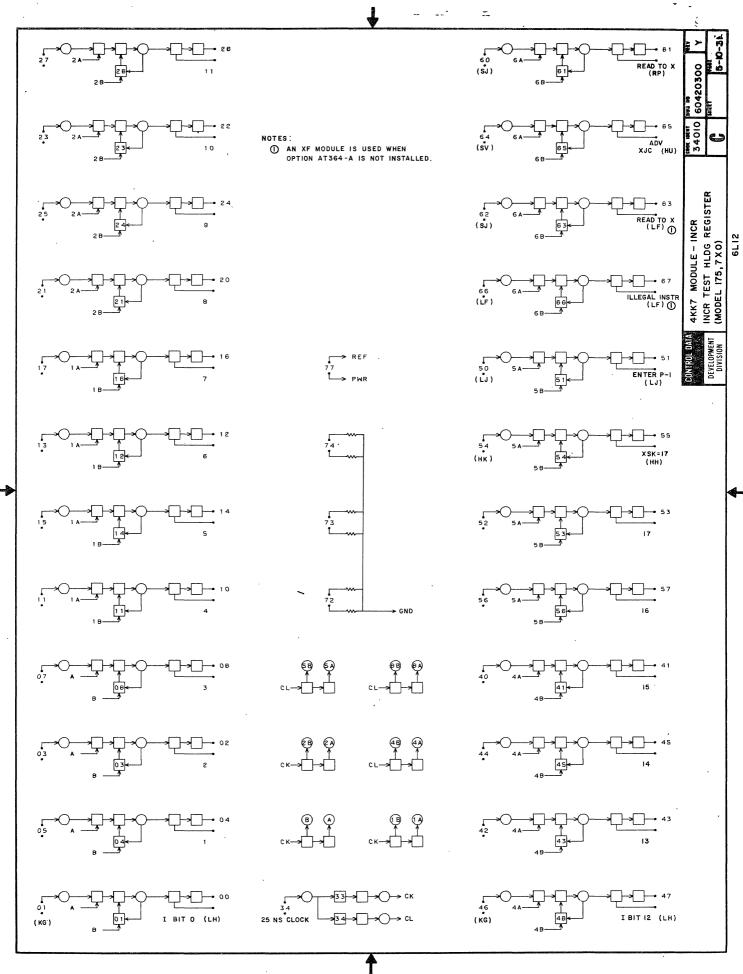

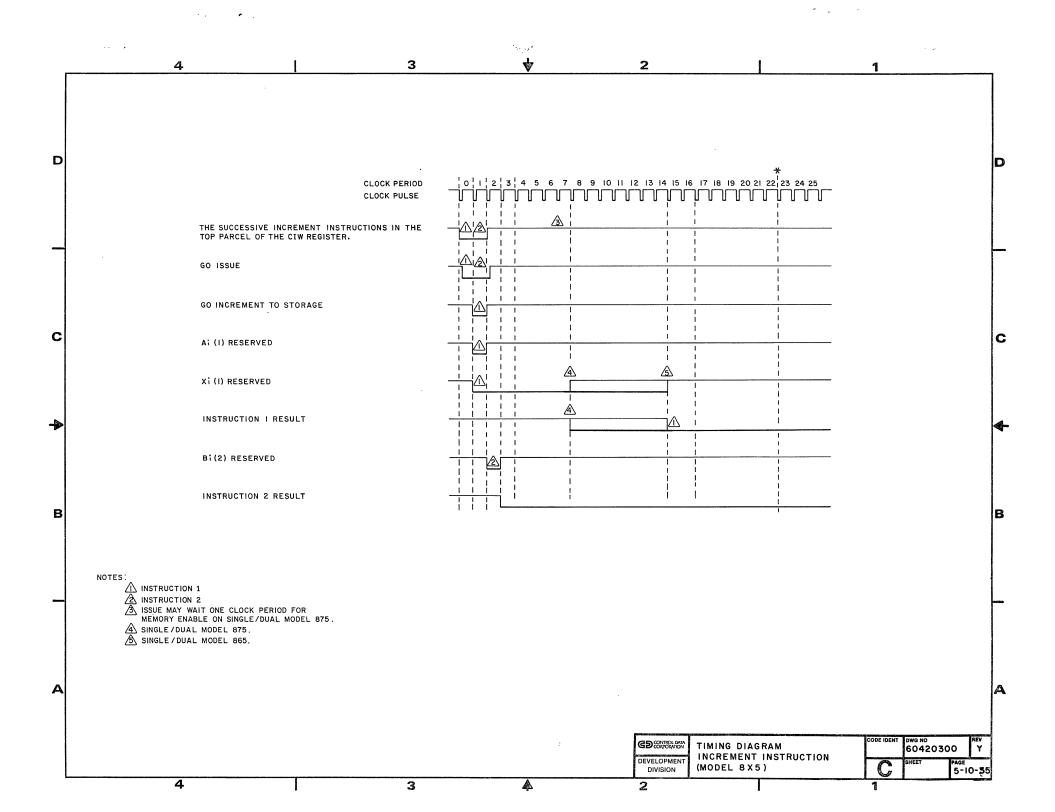

| 4KK7 (175, 7X0) | 5-10-31 | tion (8X5)                         | 5-10-35 |

## FIGURES

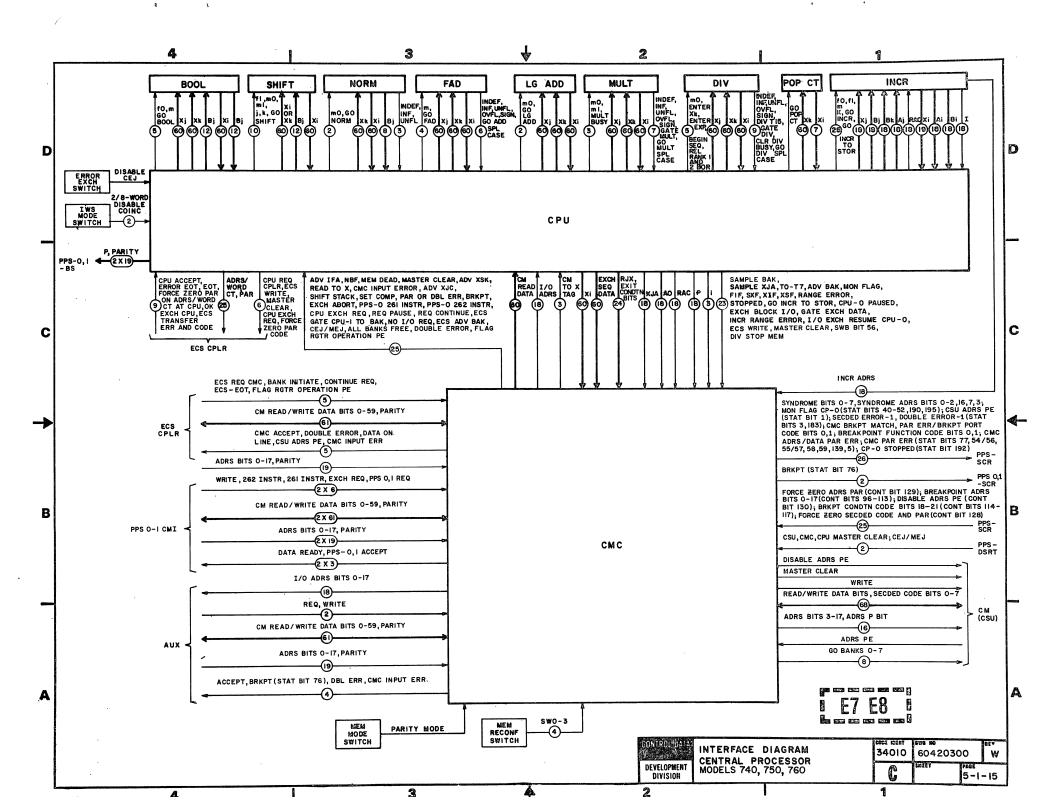

| 5-1 | Key to Diagram Symbols          | 5-1-6  | 5-6 | Interface Diagram, Central  |        |

|-----|---------------------------------|--------|-----|-----------------------------|--------|

| 5-2 | Key to Logic Symbols            | 5-1-7  |     | Processor, Model 175        | 5-1-11 |

| 5-3 | System Block Diagram, Model 175 | 5-1-8  | 5-7 | Interface Diagram, Central  |        |

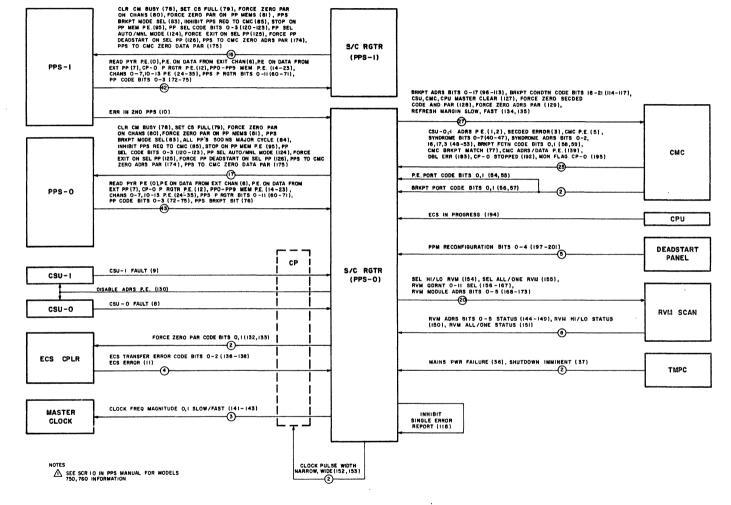

| 5-4 | System Block Diagrams, Models   |        |     | Processor, Models 740, 750, |        |

|     | 740, 750, 760                   | 5-1-9  |     | 760                         | 5-1-12 |

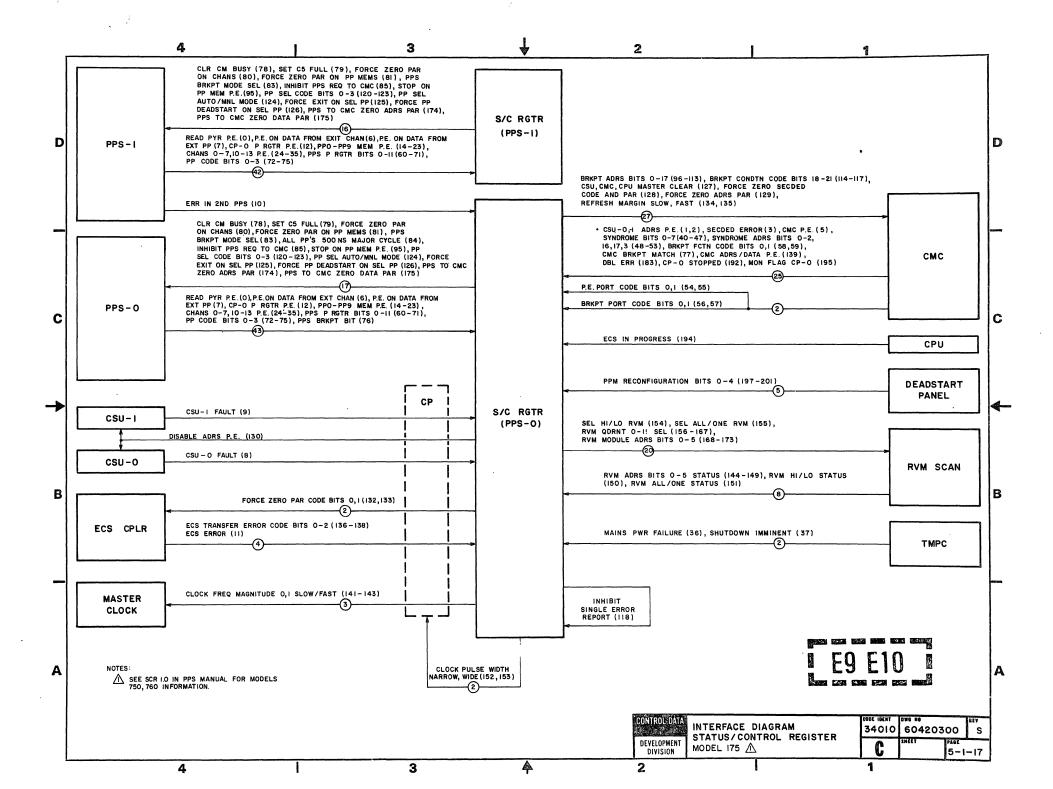

| 5-5 | System Block Diagram, Models    |        | 5-8 | Interface Diagram, Status/  |        |

|     | 865, 875                        | 5-1-10 |     | Control Register, Model 175 | 5-1-13 |

|     |                                 |        |     |                             |        |

### TABLE

5-1-4

5-1 Module-to-Diagrams Cross-References

60420300 Y

.

.

.

xi o

### SECTION 1

### GENERAL DESCRIPTION

### SECTION 2

#### OPERATION

(Information for sections 1 and 2 is contained in the CDC CYBER 170 Hardware Reference Manual.)

### SECTION 3

### INSTALLATION AND CHECKOUT

(Information for section 3 is contained in the CDC CYBER 170 Installation and Checkout Manual.)

### SECTION 4

#### THEORY OF OPERATION

(Information for section 4 is combined with the diagrams in section 5 of this manual.)

|                                              | Page   | Fiche/Grid |

|----------------------------------------------|--------|------------|

| Logic Diagrams                               |        |            |

|                                              | 5-7-17 | 58B2       |

| 4GA7                                         | 5-7-19 | 58B4       |

| 4GB7                                         | 5-7-21 | 58B10      |

| 4GB7                                         | 5-7-23 | 58B14      |

| 4GC7                                         | 5-7-25 | 58C2       |

| 4GC7                                         | 5-7-27 | 58C6       |

| 4GD7                                         | 5-7-29 | 58C10      |

| 4GE7                                         | 5-7-31 | 58C12      |

| 4GF7                                         | 5-7-33 | 58D2       |

| 4GG7                                         | 5-7-35 | 58D4       |

| 4GH7                                         | 5-7-37 | 58D6       |

| 4GI7                                         | 5-7-39 | 58D8       |

| 4GJ7                                         | 5-7-41 | 58D10      |

| 4GK7                                         | 5-7-43 | 58D12      |

| 4GL7                                         | 5-7-45 | 58D14      |

| 4GM7                                         | 5-7-47 | 58E2       |

|                                              | 5-7-49 | 58E6       |

|                                              | 5-7-51 | 58E8       |

| 4GP7                                         | 5-7-53 | 58E10      |

| 4CQ7                                         | 5-7-55 | 58E12      |

| 4GR7                                         | 5-7-57 | 58F2       |

| 4GS7                                         | 5-7-59 | 58F4       |

| 4GT7                                         | 5-7-61 | 58F6       |

| 4GU7                                         | 5-7-63 | 58F8       |

| 4GV7                                         | 5-7-65 | 58F10      |

| 4GW7                                         | 5-7-67 | 58F12      |

| 4GX7                                         | 5-7-69 | 58F14      |

| 4kr7                                         | 5-7-71 | 58G2       |

| 4KS7                                         | 5-7-73 | 58G4       |

| 4KU7                                         | 5-7-75 | 58G8       |

| 3KV7                                         | 5-7-77 | 58G12      |

| Troubleshooting Diagram, Multiply Unit       |        |            |

| 24 x 48 Matrix                               | 5-7-79 | 58G14      |

| Timing Diagram, Multiply Instruction         | 5-7-81 | 58H2       |

| Troubleshooting Chart, Multiply Coefficient. |        | 58H4       |

| Part 8. Divide Unit                          |        |            |

|                                              |        |            |

| Primary Block Diagram (DIV 1.0)              | 5-8-1  | 59B4       |

| Secondary Block Diagrams                     |        |            |

| Exponent and Control Networks (DIV 2.0).     | 5-8-3  | 59C2       |

| Coefficient Networks (DIV 2.1)               |        | 59C4       |

| Detailed-Modules Diagrams                    |        |            |

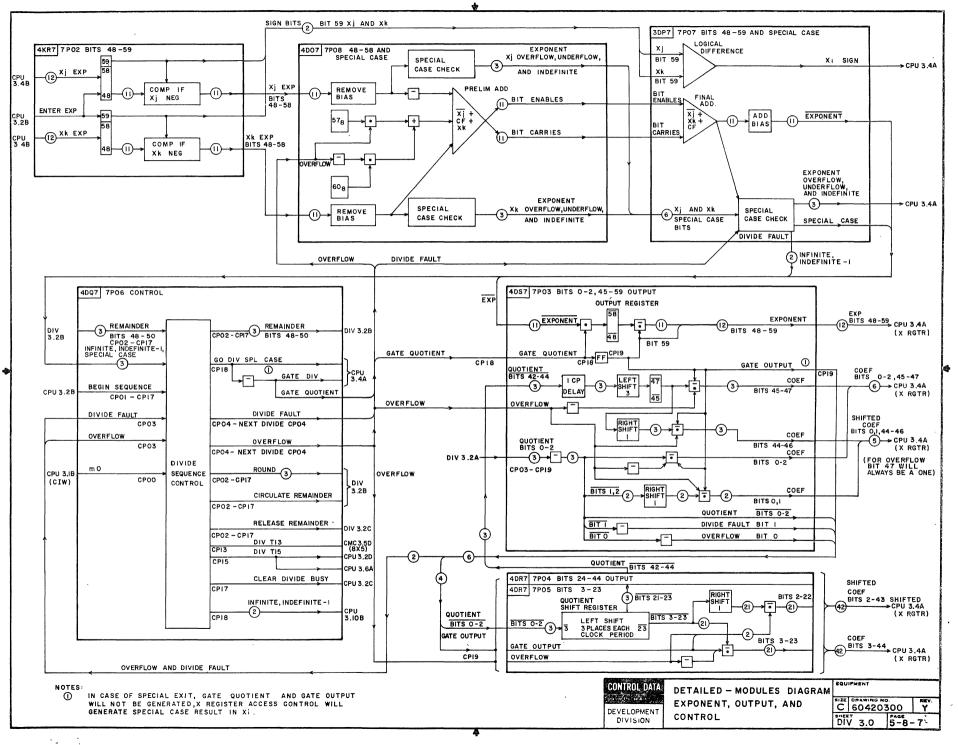

| Exponent, Output, and Control (DIV 3.0).     | 5-8-7  | 59D2       |

| Divisor Multiplication Network (DIV 3.1)     |        | 59E2       |

| Iteration Network (DIV 3.2)                  |        | 59F2       |

| Logic Diagrams                               |        |            |

| 4 DA7                                        | 5-8-13 | 60 B2      |

| 4DB7                                         | 5-8-15 | 60B6       |

| 4 DC7                                        | 5-8-17 | -60B8      |

|                                              | 5-8-19 | 60B12      |

| 4 DF7                                        | 5-0-21 | 60.02      |

63

4DE7 .

4DF7 .

4DG7 .

4 DH7 .

. .

.

. .

.

. .

.

.

xi

60C2

60C6

60 C8 60 C10

5-8-21

5-8-23

5-8-27

. 5-8-25

.

.

.

. . .

. .

,

. .

.

. •

•

•

.

•

# TABLE OF CONTENTS (Continued)

| · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                                                                                                                 | Fiche/Grid                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 4DK7   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   .   . | 5-8-29<br>5-8-31<br>5-8-33<br>5-8-37<br>5-8-37<br>5-8-41<br>5-8-43<br>5-8-45<br>5-8-47<br>5-8-49<br>5-8-51<br>5-8-53 | 60Cl2<br>60Cl4<br>60D2<br>60D4<br>60D6<br>60D8<br>60Dl0<br>60Dl2<br>60E2<br>60E2<br>60E6<br>60E8<br>60E10<br>60El2 |

| Part 9. Population Count Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                      |                                                                                                                    |

| Primary Block Diagram (POP CT 1.0)<br>Secondary Block Diagram (POP CT 2.0)<br>Detailed-Modules Diagram (POP CT 3.0)<br>Logic Diagrams                                                                                                                                                                                                                                                                                                                                                        | 5-9-1<br>5-9-3<br>5-9-5                                                                                              | 610B4<br>610B10<br>610C2                                                                                           |

| 4KA7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5-9-7<br>5-9-9<br>5-9-11                                                                                             | 610D2<br>610D6<br>610D10                                                                                           |

| Part 10. Increment Un t                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                      |                                                                                                                    |

| Primary Block Diagram (INCR 1.0) Secondary Block Diagram (INCR 2.0) Detailed-Module Diagram (INCR 3.0) Logic Diagrams                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                      | 610E4<br>610E10<br>610D2                                                                                           |

| 4KE7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5-10-7<br>5-10-9<br>5-10-11<br>5-10-13<br>5-10-15<br>5-10-17<br>5-10-19<br>5-10-21                                   | 610G2<br>610G4<br>610G6<br>610G8<br>610G10<br>610H2<br>610H5<br>610H8                                              |

# FIGURES

| 5-1 | Key to Diagram Symbols 5-1-6 | 52D12 |

|-----|------------------------------|-------|

|     | Key to Logic Symbols 5-1-7   | 52Dl4 |

## TABLE

~

5-1 Module-to-Diagrams Cross-References. . 5-1-4

52 D8

# SECTION 1

# GENERAL DESCRIPTION

# SECTION 2

# OPERATION

(Information for sections 1 and 2 is contained in the CDC CYBER 170 Hardware Reference Manual, publication number 60420000.)

# SECTION 3

# INSTALLATION AND CHECKOUT

(Information for section 3 is contained in the CDC CYBER 170 Model 175 Installation and Checkout Manual, publication number 60420500.)

## SECTION 4

# THEORY OF OPERATION

(Information for section 4 is combined with the diagrams in section 5 of this manual.)

SECTION 5

DIAGRAMS

PART 1

# INTRODUCTION

### INTRODUCTION

### GLOSSARY

The glossary is a list of terms, mnemonics, and abbreviations used on the diagrams.

#### MODULE-TO-DIAGRAMS CROSS-REFERENCES

#### GENERAL

Table 5-1 provides a list of functional unit module types along with the following information on each type.

- Quantity Number of modules of this type located on the mainframe

- Location All physical locations at which this module type can be found

- Diagram Secondary block and detailed-modules diagrams on which this module type is depicted.

#### USES

Table 5-1 can be used to locate a particular module logic diagram in the manual without knowing the functional entity to which it pertains. Another use is to determine the availability and the location of a substitute module during maintenance. The table also helps to locate all modules of the same type without having to scan all module placement diagrams.

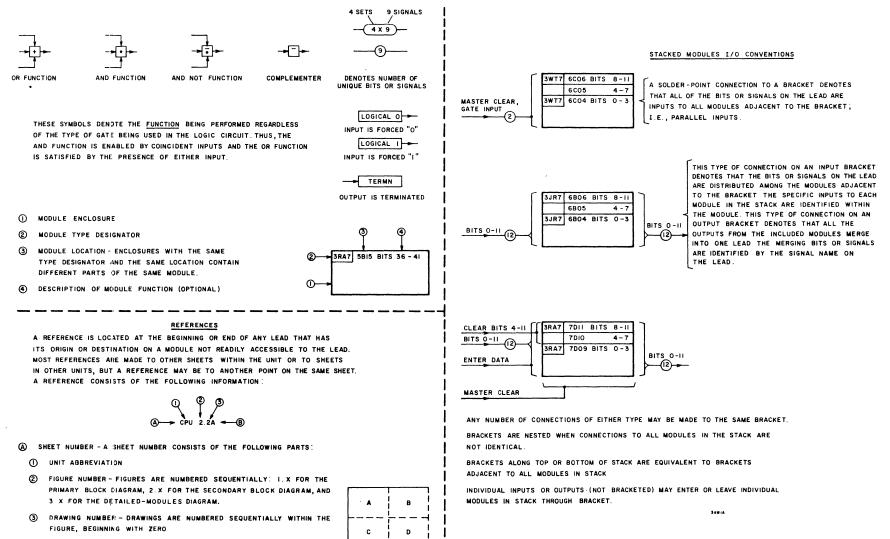

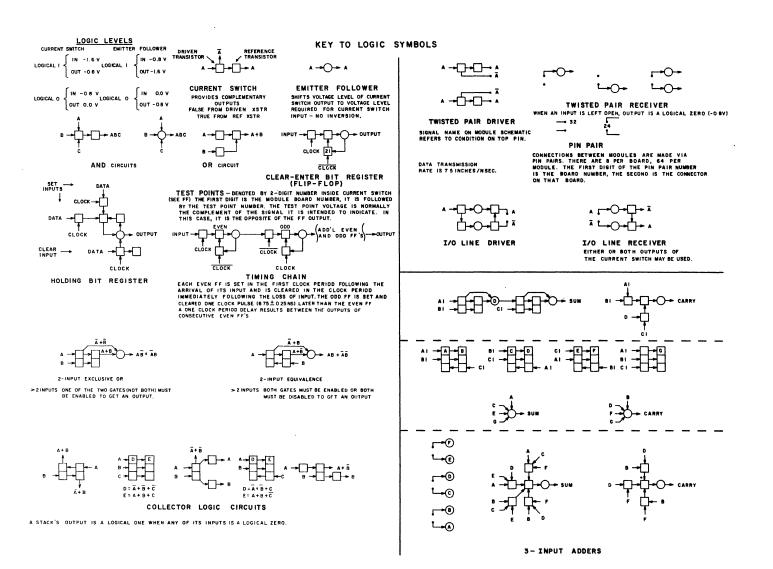

#### KEY TO SYMBOLS (Figures 5-1 and 5-2)

The number of unfamiliar symbols on the block and detailed-modules diagrams has been kept to a minimum. The symbology has been chosen because it simplifies or clarifies and is therefore essential to the use and understanding of the diagrams. Time spent familiarizing oneself with these conventions is not wasted. Note particularly that the AND and OR symbols define functions, not gates. In some cases, hardware constraints caused the use of AND gates to perform OR functions. Therefore, the block and detailed-modules diagrams depict the OR function, not the AND hardware.

60420300 V

5-1-1

#### SYSTEM BLOCK AND INTERFACE DIAGRAMS

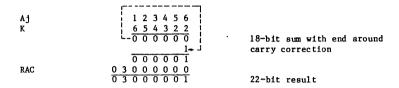

The system block diagrams (figures 5-3, 5-4, 5-5) provide a comprehensive view of the central computer. In addition to aiding one's understanding of the system, it relates physical to electrical data (for example, multiply functional unit located on chassis 7) and defines the boundaries of the central processor diagrams in the various parts of this section.