# **CONTROL DATA** 8092 TeleProgrammer

REFERENCE MANUAL

|                                       |                    | RECORD          | OF CH    | ANGE NOTICES |

|---------------------------------------|--------------------|-----------------|----------|--------------|

| C. N. NO.                             | DATE<br>ORIGINATED | DATE<br>ENTERED | INITIALS | REMARKS      |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 | <u> </u> |              |

|                                       |                    |                 |          |              |

| <del></del>                           |                    |                 |          |              |

| <del>_</del>                          |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       | <u> </u>           |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

| · · · · · · · · · · · · · · · · · · · |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

|                                       |                    |                 |          |              |

Address comments concerning this manual to:

Control Data Corporation IDP Publications 9549 Penn Avenue South Minneapolis 31, Minnesota

© 1964, Control Data Corporation Printed in the United States of America

#### CONTENTS

#### CHAPTER ONE - DESCRIPTION

| Description Summary of Characteristics Description of Registers                                                                                                                                                                     | 1-1<br>1-3<br>1-4                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Operational Registers Transient Registers Addressing Modes Input/Output Instruction Repertoire                                                                                                                                      | 1-5<br>1-5<br>1-6<br>1-6<br>1-8                              |

| List of Instruction (numerical listing) External Function Codes and Status Responses                                                                                                                                                | 1-9<br>1-16                                                  |

| CHAPTER TWO - OPERATION                                                                                                                                                                                                             |                                                              |

| Operation Operator's Panel Switches Displays Status Indicators Starting the TeleProgrammer Loading a Program or Data Entering Data from the TeleProgrammer Panel Examining the Storage Contents                                     | 2-1<br>2-1<br>2-2<br>2-4<br>2-5<br>2-7<br>2-7<br>2-7<br>2-8  |

| CHAPTER THREE - PRINCIPLES OF OPERATION                                                                                                                                                                                             |                                                              |

| CONTROL Section Registers Master Clock Main Timing Chain Storage Reference Cycle Function Translator Operating Controls Non-Volatile Storage                                                                                        | 3-2<br>3-8<br>3-9<br>3-12<br>3-14<br>3-18                    |

| STORAGE Section Properties of the Magnetic Core Storage Control Storage Reference Cycle Storage Reference Control Storage Sequence Control Address Selection Storage Address Register R/W Driver Selection Inhibit Driver Selection | 3-20<br>3-22<br>3-24<br>3-27<br>3-28<br>3-32<br>3-33<br>3-35 |

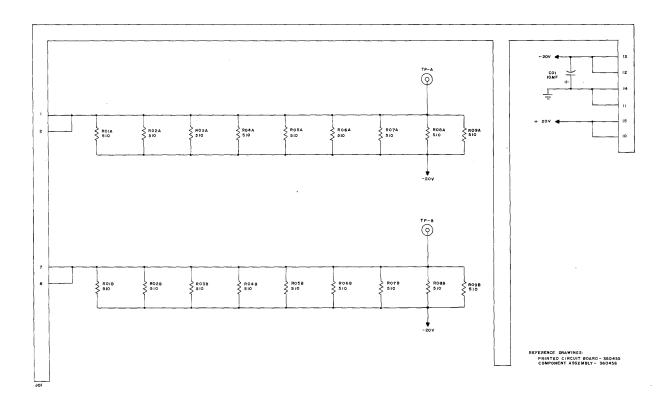

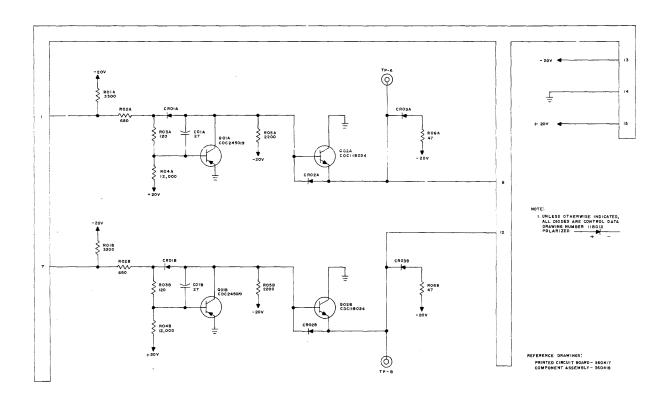

| Electronic Theory of Memory Circuits | 3-37 |

|--------------------------------------|------|

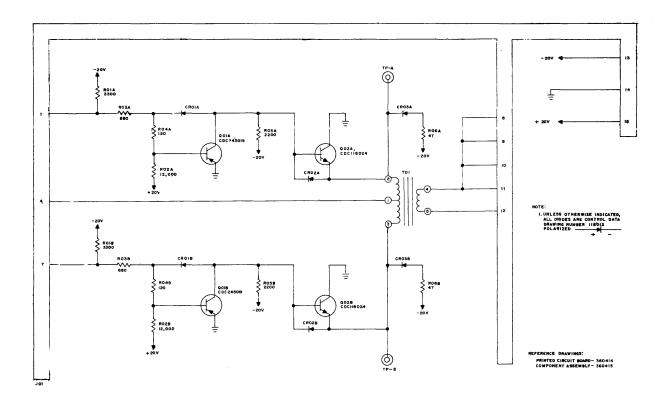

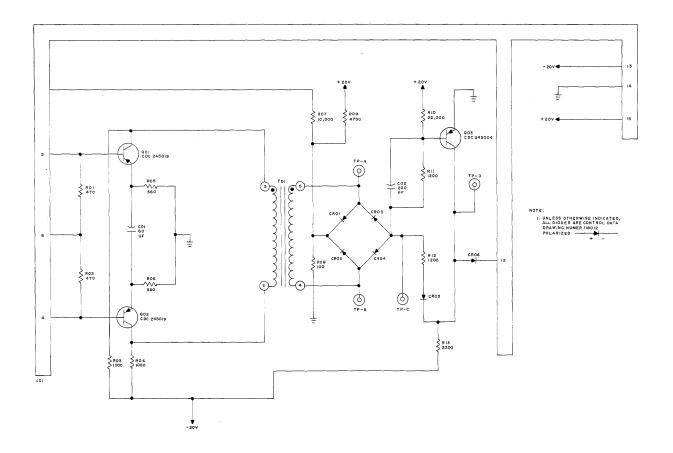

| Drive Generator (G10)                | 3-37 |

| Diverter (52A)                       | 3-39 |

| Selector (53)                        | 3-40 |

| Current Source (12 & 13)             | 3-41 |

| Inhibit Generator (G11)              | 3-42 |

| Sense Amplifier (G14)                | 3-43 |

| Arithmetic Section                   | 3-44 |

| Binary Arithmetic                    | 3-44 |

| Arithmetic Operations                | 3-46 |

| Theory of the Adder                  | 3-47 |

| Adder Operation                      | 3-50 |

| Shifting                             | 3-57 |

| Input/Output Section                 | 3-58 |

| Information Cables                   | 3-58 |

| Input/Output Cable Lines             | 3-60 |

| Equipment Selection                  | 3-61 |

| Status Request Responses             | 3-61 |

| Input/Output Control                 | 3-62 |

| Input Data Transmission              | 3–68 |

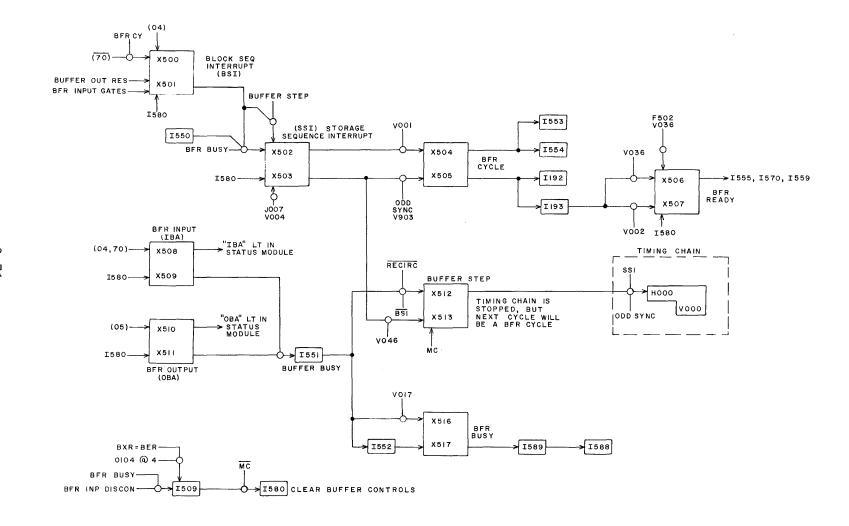

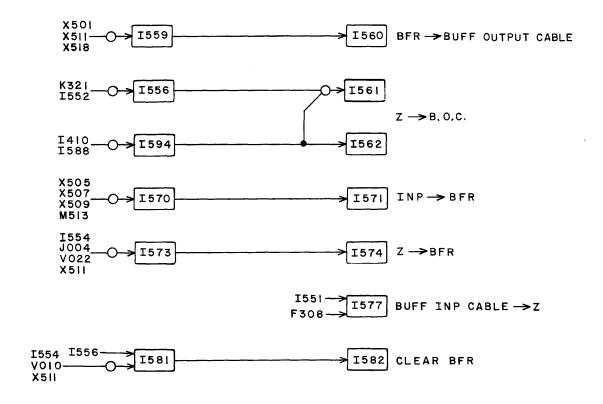

| Buffer Operations                    | 3-69 |

| Buffer Control                       | 3-69 |

| Transmission Control                 | 3-72 |

| Buffer I/O Cables                    | 3-73 |

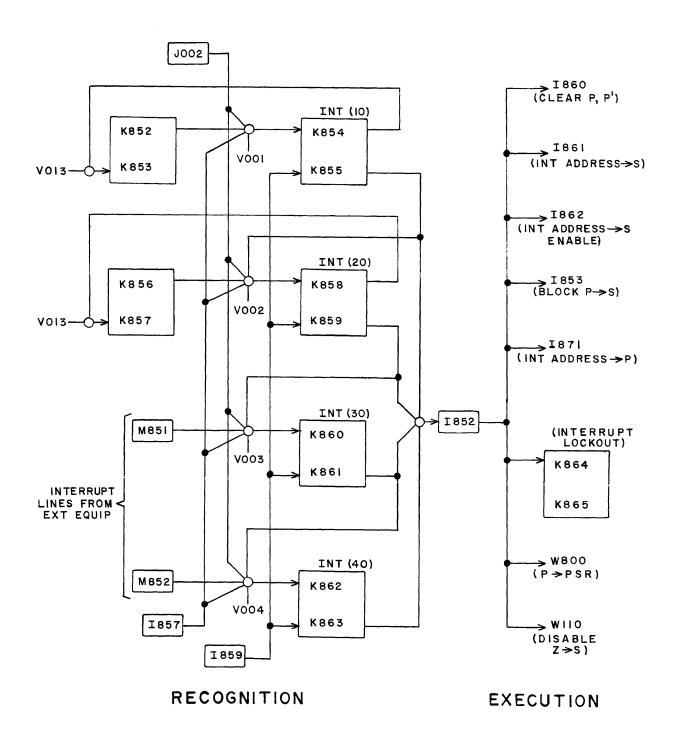

| Interrupt                            | 3-73 |

| Recognition                          | 3-75 |

| Interrupt 10                         | 3-75 |

| Interrupt 20                         | 3-75 |

| Interrupt 30 and 40                  | 3-75 |

| Priority of Recognition              | 3-75 |

| Execution                            | 3-76 |

| Interrupt Lockout                    | 3-76 |

| Master Clear                         | 3-76 |

Glossary

#### FIGURES

| 2-1  | Operator's Panel                      | 2-1  |

|------|---------------------------------------|------|

| 3-1  | Block Diagram of the TeleProgrammer   | 3-3  |

| 3-2  | Master Clock Oscillator Waveforms     | 3-8  |

| 3-3  | Main Timing Control                   | 3-10 |

| 3-4  | Main Timing                           | 3-11 |

| 3-5  | Typical Function Translation          | 3-13 |

| 3-6  | Run/Step Controls                     | 3-15 |

| 3-7  | Load/Clear, Enter/Sweep Controls      | 3-17 |

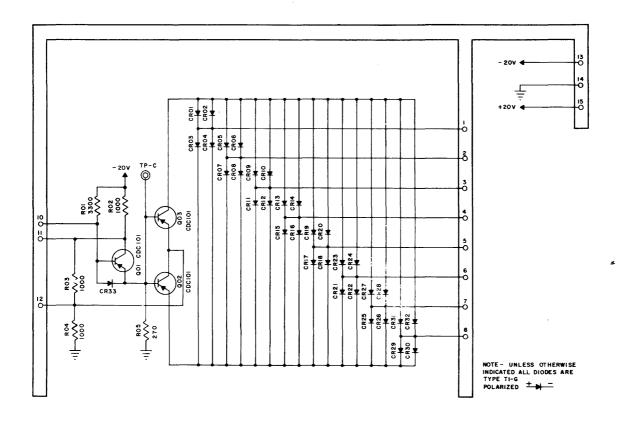

| 3-8  | Non-Volatile Storage Circuits         | 3-19 |

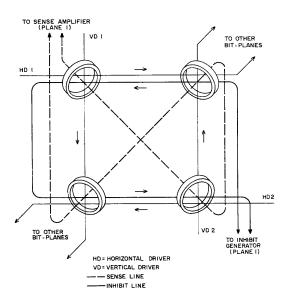

| 3-9  | 4-Bit Magnetic Core Matrix            | 3-21 |

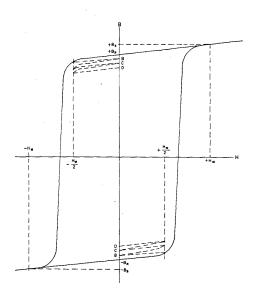

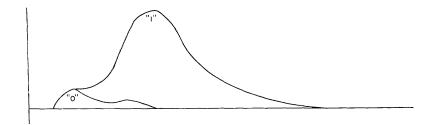

| 3-10 | Hysteresis Diagram                    | 3-23 |

| 3-11 | Storage Reference Control             | 3-27 |

| 3-12 | Storage Sequence Control              | 3-30 |

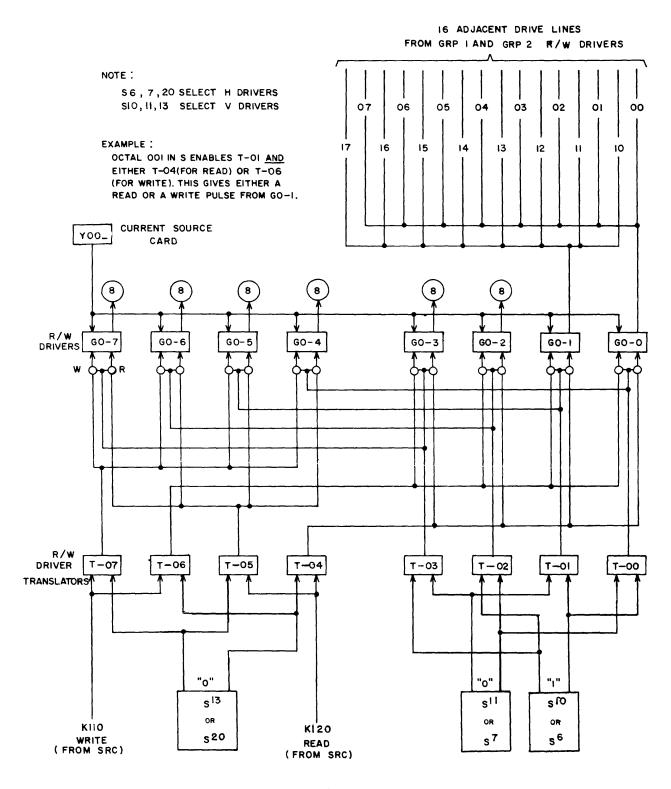

| 3-13 | Read/Writer Selection                 | 3-13 |

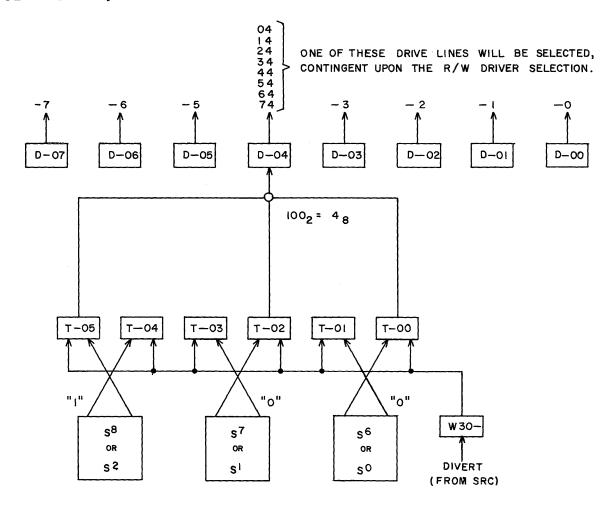

| 3-14 | Diverter Selection                    | 3-35 |

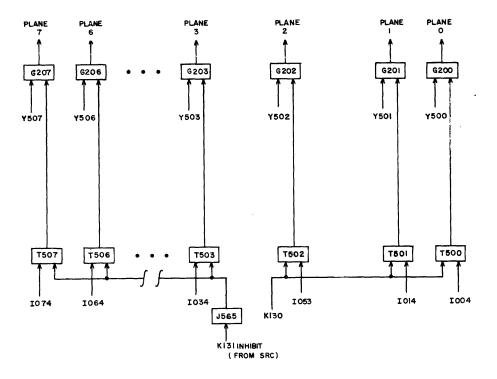

| 3-15 | Inhibit Driver Selection              | 3-36 |

| 3-16 | Drive Generator (G10)                 | 3-38 |

| 3-17 | Diverter (52A)                        | 3-39 |

| 3-18 | Selector (53)                         | 3-40 |

| 3-19 | Current Source (G12)                  | 3-41 |

| 3-20 | Inhibit Generator (G11)               | 3-42 |

| 3-21 | Sense Amplifier (G14)                 | 3-43 |

| 3-22 | Operation of Adder                    | 3-54 |

| 3-23 | Adder Structure                       | 3-55 |

| 3-24 | Adder Input (R & Q Inverters)         | 3-56 |

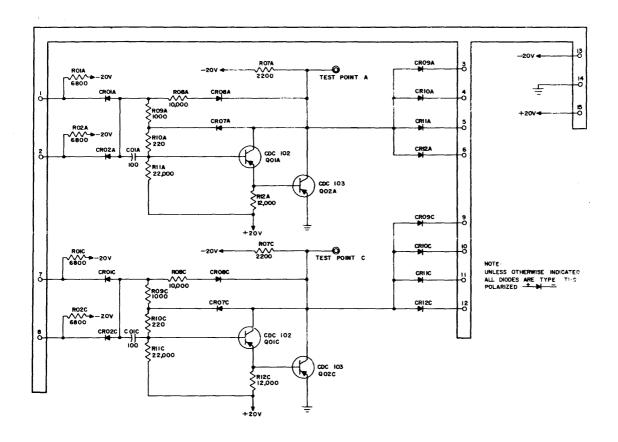

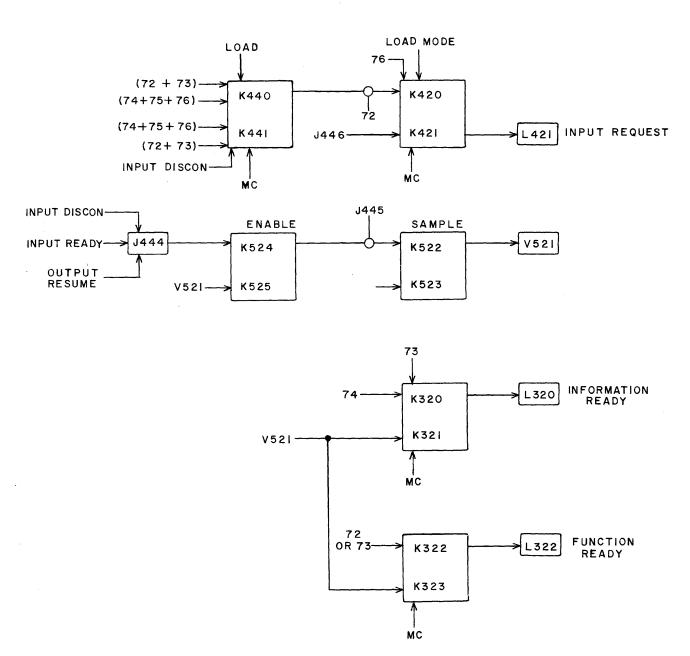

| 3-25 | Input/Output Controls                 | 3-63 |

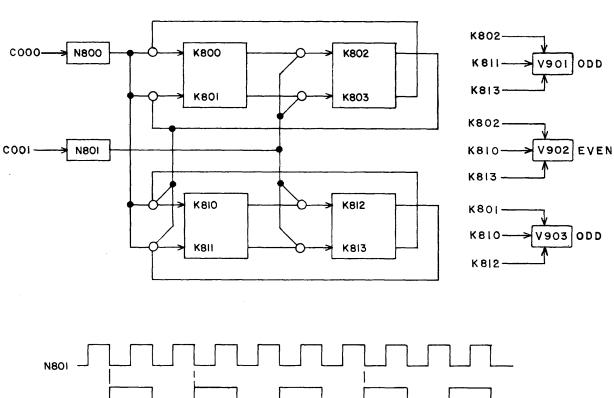

| 3-26 | Resynchronizing Network               | 3-64 |

| 3-27 | Resync Circuit                        | 3-66 |

| 3-28 | Buffer Controls (Tipin)               | 3-71 |

| 3-29 | Buffer Registers Transmission Control | 3-72 |

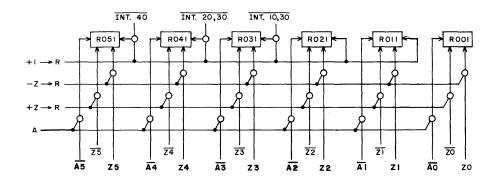

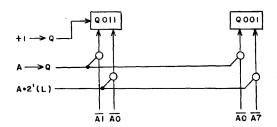

| 3-30 | Interrupt Circuit                     | 3-74 |

|      | TABLES                                |      |

| 1-1  | Instruction Repertoire                | 1-8  |

| 1-2  | List of Instructions (Numerical)      | 1-9  |

| 1-3  | External Function Codes               | 1-16 |

| 3-1  | Decimal and Binary Equivalents        | 3-45 |

| 3-2  | Adder Commands                        | 3-55 |

| 3-3  | Pin Assignments I/O Cables            | 3-59 |

| 3-4  | Input and Output Call Lines           | 3-60 |

Control Data Corporation 8092 TeleProgrammer

# CHAPTER ONE DESCRIPTION

The CONTROL DATA\* 8092 TeleProgrammer is a highly flexible, multipurpose, stored program data processor and converter. It employs high speed

(3 megacycle clock frequency) transistor amplifier circuits, diode logic, and an

extremely fast magnetic core matrix memory. Word construction is 8 binary

digits, parallel throughout, programmable to multiple-precision and to alphanumeric and binary-coded decimal.

The basic memory of the CONTROL DATA 8092 TeleProgrammer consists of magnetic core storage with a basic capacity of 2048 8-bit words and an optional 4096 8-bit word memory with a storage cycle time of 4.0 usec. The internal program can directly address all 4096 words by the use of three 4-bit Tag registers. The TeleProgrammer has a total of 42 instructions, executed in one to four storage cycles; the time varies between 4.0 and 16.0 usec. The average program execution time for an instruction is approximately 10.0 usec.

<sup>\*</sup> Registered Trademark.

A general purpose input channel and output channel system is provided for attaching a variety of input/output devices. Input and output transmissions are by 8-bit characters. Standard input/output is by optional punched papertape read and punch units. Optionally, other input/output devices, such as on-line typewriter, magnetic tape handlers, punched card units, digital communication units, analog-to-digital converters, or similar equipment may be added.

A buffer input/output channel permits the TeleProgrammer to continue high-speed computation while communicating with external equipment. Any peripheral unit connected to the buffer channel may also be addressed using the normal input/output channel.

Four interrupt lines, including a manual interrupt, allow more effective use of computer time through sophisticated programming.

Operation of the 8092 TeleProgrammer is sequenced by an internally stored program. This program, as well as the data being processed, is contained in the high-speed, random-access storage. An instruction is an 8-bit word comprising a 6-bit function code, F, and a 2-bit code Tag register reference, T. Program modifications are accomplished and operands are manipulated by memory or indirect addressing through use of T.

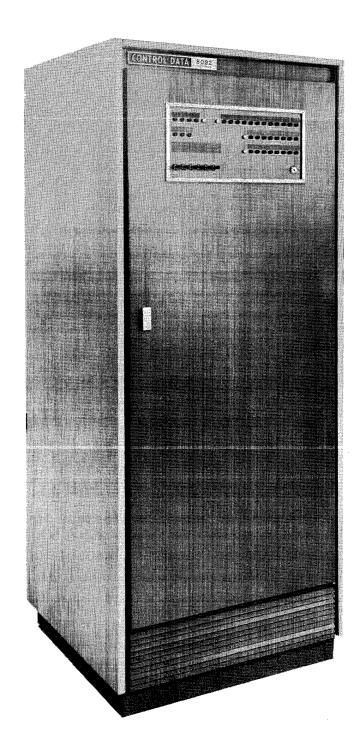

The 8092 is constructed in a stand-up cabinet 68 3/4 inches high. Operating requirements are a maximum of 850 watts of 110 volt, 60 cycle power, and a normal room temperature not exceeding 100 degrees F.

#### SUMMARY OF CHARACTERISTICS

Type of Machine

Digital, stored program

Mode of Operation

Parallel

Word Length

8 bits

Memory

2048 8-bit words expandable to

4096 8-bit words.

Type of Instruction

Single address

Address Features

No address, memory and indirect

addressing.

Instruction Word

8-bit word (6-function code, F;

2-bit Tag reference, T).

Input/Output

Interrupt feature on all input/output

channels Normal and Buffered

input/output channels.

Instruction Repertoire

42 instructions for arithmetic and

manipulative operations.

Type of Arithmetic

Binary; one's complement.

Control Provisions

Complete manual control from

control panel.

Assembler

The ability to use the OSAS or OSAS-A assembler for those who

have a 160 or 160-A computer.

#### DESCRIPTION OF REGISTERS

The CONTROL DATA 8092 TeleProgrammer uses six operational and eight transient registers. Operational registers are referred to implicitly in the individual program steps, and may be modified by manually inserting quantities into them. The transient registers, important only to the internal operation of the machine, are not available for modification from the control panel.

#### OPERATIONAL REGISTERS

| A Register | Α | is | the | principal | arithmetic | register | for | most |

|------------|---|----|-----|-----------|------------|----------|-----|------|

|------------|---|----|-----|-----------|------------|----------|-----|------|

arithmetic operations. A operates as a subtractive accumulator. The quantity zero is

represented by all zeros.

Z Register As a buffer register, Z receives the word

read out of storage and holds the word to be written into storage. For addition and subtraction, the contents of Z are added to or

subtracted from the contents of A.

P Register P, the Program Address register, contains

the address of the current instruction. At the beginning of each instruction the contents of P are increased by one to provide the address of the instruction; if a jump is called for, a jump address is entered in P. For certain instructions, the contents of P are

advanced by 2.

T Registers The T registers hold the upper 4 bits of the

12-bit storage address used in direct or

indirect addressing.

#### TRANSIENT REGISTERS

During a buffer operation the Buffer Data **BFR**

> register holds the word of information being transferred to or from storage.

During a buffer operation the Buffer Entrance BER

register holds the address to or from which information is being transferred. It is advanced by one with each data-word transfer.

BXR The Buffer Exit register contains the terminat-

> ing address (LWA + 1) for the current buffer operation. After each data-word transfer, a comparison is made between BER and BXR to determine whether another word should be

transferred.

A' Register A! is an auxiliary arithmetic register.

> results of arithmetic operations are first formed in A' and then transmitted to the A, Z, S, or P registers.

S Register S functions as the Storage Address register.

> Prior to any storage reference, the address word is entered in S, and the contents of S are used to select the storage location involved

in the reference.

F Register F holds the lower 6 bits and f' the upper 2

> bits (Tag register reference) of an instruction word (the function code) throughout the execution of the instruction. The execution of an

instruction is under control of the quantity if F.

**PSR** The P Storage register is used in interrupt

> operations. During such operations, the address in P is transferred to PSR, thereby releasing P and enabling the TeleProgrammer to jump to the interrupt address specified by the interrupt level. PSR is then transferred

to P at the end of the interrupt routine.

O Register The O register holds the upper 6 bits of a

12-bit external function code used for control-

ling external equipment.

All registers, but PSR, S, F, A' and O may be displayed by setting lever switches on the panel.

#### ADDRESSING MODES

Maximum flexibility of the 6-bit address is provided by three addressing modes:

No Address - N

Using the memory location immediately following the instruction as an 8-bit operand permits the performance of arithmetic and logical operations with an 8-bit constant associated with the instruction. This eliminates the need for entering many constants into memory.

Memory Address - D

Refers to an 8-bit operand in any storage location addressed by the memory location immediately following the instruction and the Tag register referenced by T.

Indirect Address - 1

Provides for operand references. Instructions employing indirect addressing use the memory location immediately following the instruction to refer to one of the first 256 storage locations. The contents of this address are used along with the Tag register (referenced by T) as the address of the operand.

#### INPUT/OUTPUT

Seven instructions deal with input/output operations. Instructions 70 and 72 initiate input. Output data is sent by instructions 71 and 73. External function codes for directing the operation of the input/output equipment are sent by instruction 75. Instruction 76 provides an 8-bit input to A, and 74, an 8-bit output from the memory location immediately following the 74 instruction.

Communication with external equipment, effected in the same manner for either normal or buffer input/output channels, is accomplished by first executing instruction 75; the operand obtained is the external function code.

This code selects the particular equipment and specifies the operation mode.

Only one input or one output equipment is active at a given time on the normal input/output channel.

The input or output sequence of transmission is as follows: The address designated by the instruction (immediately following instruction) is placed in the A register and used for storing the input word or for reading a word for output. After each transmission the address in A is advanced by one and compared with the contents of the address immediately following the starting address. If the comparison shows inequality, another transmission of a data word is initiated. If the comparison shows equality, the program continues with the instruction at the address following the ending address. The 74 instruction initiates a single output operation with the 8-bit quantity from the memory location immediately following the 74 instruction being placed in the output channel.

The 70 and 71 initiate buffer input and buffer output, respectively. Prior to executing these, however, the buffer entrance and exit registers must be set and a device on the buffer channel selected by a 75 instruction. A complete list of instructions arranged in order of instruction codes is shown in Table 1-2. External Function codes and Status Responses for TeleProgrammer peripheral equipment are shown in Table 1-3.

#### TABLE 1-1 THE 8092 TeleProgrammer INSTRUCTION REPERTOIRE

| Functions                                                                                                   | Rel.<br>Code                                  | Octal<br>Code                          | Cycle<br>Time<br>*              | Functions                                                                                                                            | Rel.<br>Code                                         | Octal<br>Code                                | Cycle<br>Time<br>*                   |

|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------|--------------------------------------|

| LOADS:  Load A (No.) Load A (Mem.) Load A (Ind.) Load Comp. (Mem.) Load Comp. (Ind.) Tag Reg. to A BER to A | LDN<br>LDM<br>LDI<br>LCM<br>LCI<br>TTA<br>BER | 20<br>21<br>22<br>25<br>26<br>03<br>06 | 2<br>3<br>4<br>3<br>4<br>1<br>1 | ARITHMETICS:  Add (No Adr.) Add (Mem.) Add (Indirect) Subtract (No) Subtract (Mem.) Subtract (Ind.) Replace Add (Mem.) Replace Add 1 | ADN<br>ADM<br>ADI<br>SBN<br>SBM<br>SBI<br>RAM<br>RAO | 30<br>31<br>32<br>34<br>35<br>36<br>51<br>55 | 2<br>3<br>4<br>2<br>3<br>4<br>4<br>4 |

| STORES:  Store A (Mem.) Store A (Ind.) A to Tag Reg. A to BER A to BXR                                      | STM<br>STI<br>ATT<br>ABR<br>ABX               | 41<br>42<br>02<br>04<br>05             | 3<br>4<br>1<br>1                | LOGICALS:  Log. Prod.(No) Log. Prod.(Mem.) Log. Prod.(Ind.) Log. Sum (No) Log. Sum (Mem.) Log. Sum (Ind.)                            | LPN<br>LPM<br>LPI<br>LSN<br>LSM<br>LSI               | 10<br>11<br>12<br>14<br>15<br>16             | 2<br>3<br>4<br>2<br>3<br>4           |

| JUMPS:***  If A = 0  If A ≠ 0  If A ≥ 0  If A < 0  Unconditional                                            | ZJP<br>NZP<br>PJP<br>NJP<br>UJP               | 60<br>61<br>62<br>63<br>64             | 2<br>2<br>2<br>2<br>2           | IN-OUT:  Input Normal Output Normal Input Buffer Output Buffer Input to A Output No. Adr.                                            | INN<br>OUT<br>IBI<br>IBO<br>INA<br>OTN               | 72<br>73<br>70<br>71<br>76<br>74             | **<br>**<br>2<br>2<br>2<br>2         |

| SHIFTS: A left 1 bit                                                                                        | SHA                                           | 01                                     | 1                               | CONTROLS:  Ext. Function Clear Interrupt Clear Buffer Error Stop Halt                                                                | EXF<br>CIL<br>CBC<br>ERR<br>HLT                      | 75<br>13<br>07<br>00<br>77                   | 3<br>1<br>1<br>-<br>1                |

<sup>\*</sup> Cycle Times; each cycle = 4 microseconds.

<sup>\*\*</sup> 3 + 2(X + 1) + terminate time. Where X = No. of words.

<sup>\*\*\* (</sup>Jump cycle times above are 1 less cycle if jump is not made.)

## TABLE 1-2 LIST OF INSTRUCTIONS Numerical Listing with Comments

| Octal<br><u>Code</u> | Mnemonic<br>Code |                                     |                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00(X)*               | ERR              | Error Stop                          | This is an illegal instruction as such, it can be used as an Error Stop.                                                                                                                                                                                                                                                                                                                                     |

| 01(X)                | SHA              | Shift A Left<br>One Bit             | Shift the contents of A left end around 1 bit position. Bits coming off the left end of the A register go to lowest bit position on the right end of the register.                                                                                                                                                                                                                                           |

| 02(Y)                | ATT              | A to Tag<br>Register                | Transfer the lower 4 bits of the A register into the designated Auxiliary Tag register.                                                                                                                                                                                                                                                                                                                      |

| 04(Y)                | ABR              | A to Buffer<br>Entrance             | Transfer the contents of A to the lower positions of the Buffer Entrance register. The lower 2 bits of Tag register 3 become bits 8 and 9 of BER. If the buffer is busy a jump occurs to the combined address contained in the designated Tag register of the first word and the contents of the second word of the instruction set. If not busy, control continues to the next instruction set in sequence. |

| 05(Y)                | ABX              | A to Buffer Exit<br>Register        | Transfer the contents of A to the lower 8 bits of the Buffer Exit register (BXR). If the buffer is busy a jump occurs to the combined address contained in the designated Tag register of the first word and the contents of the second word of the instruction set. If not busy, control continues to the next instruction set in sequence.                                                                 |

| 06(X)                | BER              | Buffer to Entrance<br>Register to A | Load the A register with the lower 8 bits of the Buffer Entrance register.                                                                                                                                                                                                                                                                                                                                   |

| Octal<br><u>Code</u> | Mnemonic<br>Code |                                       |                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------|------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07(X)                | CBC              | Clear Buffer<br>Controls              | This instruction has the effect of sending a zero to buffer control and thus putting that device in a "ready state". If this instruction is used <u>during</u> a buffer operation, it will stop the buffer.                                                                                                                                                                         |

| 10(X)                | LPN              | Logical Product<br>(No Address)       | Form in A the Logical Product of the contents of A and the contents of the second word of the instruction set.                                                                                                                                                                                                                                                                      |

| 11(Y)                | LPM              | Logical Product<br>(Memory Address)   | Form in A, the Logical Product of the contents of A and the contents of the memory location whose address is the combined contents of the designated Tag register, and the second word of the instruction set. The initial contents of the memory location remains unchanged.                                                                                                       |

| 12(Y)                | LPI              | Logical Product<br>(Indirect Address) | Form in A the Logical Product of the contents of A and the contents of the memory location whose address is the combined contents of the designated Tag register and the contents of one of the first 256 decimal locations. The address of this decimal location is given in the second word of the instruction set. The initial contents of the memory location remain unchanged. |

| 13(X)                | CIL              | Clear Interrupt<br>Lockout            | This instruction clears the interrupt lockout flip flop and it must be programmed at the end of every routine which is initiated by the interrupt. To return to main program after clearing interrupt lockout, the Tag designation must be 1. If zero, control continues in sequence.                                                                                               |

| 14(X)                | LSN              | Logical Sum<br>(No Address)           | Form in A the Logical Sum of the contents of A and the second word of the instruction set.                                                                                                                                                                                                                                                                                          |

| 15(Y)                | LSM              | Logical Sum<br>(Memory Address)       | Form in A the Logical Sum of the contents of A and the contents of the memory location whose combined address is given in the designated Tag register and the second word of the instruction set.                                                                                                                                                                                   |

| Octal<br><u>Code</u> | Mnemonic<br>Code |                                    |                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16(Y)                | LSI              | Logical Sum<br>(Indirect Address)  | Form in A the Logical Sum of the contents of A and the contents of the designated Tag register and one of the first 256 (decimal) locations. The location of one of these 256 locations is given in the second word of the instruction set.                                                                                                                              |

| 20(X)                | LDN              | Load A<br>(No Address)             | Load the A register with the contents of the second word of the instructional set. A quantity of 8 bits can be entered into A by this instruction.                                                                                                                                                                                                                       |

| 21(Y)                | LDM              | Load A (Memory Address)            | Load the A register with the contents of<br>the of the memory address whose lower<br>8 bit digits are given in the second<br>instruction word and whose upper 4 bits<br>are contained in the designated Auxiliary<br>Tag register.                                                                                                                                       |

| 22(Y)                | LDI              | Load A<br>(Indirect)               | Load A with the contents of the address whose lower 8 bits are contained in one of the first 256 (decimal) addresses, and whose upper 4 bits are contained in a designated Auxiliary Tag register. The location in the core (one of the first 256 decimal addresses) is given in the second instruction word. The Auxiliary Tag register is indicated in the first word. |

| 25(Y)                | LCM              | Load Complement<br>to A (Memory)   | Load the A register with the <u>complement</u> of the contents of the memory address whose lower 8 bits are given in the second instruction word and whose upper 4 bits digits are contained in the designated Auxiliary Tag register.                                                                                                                                   |

| 26(Y)                | LCI              | Load Complement<br>to A (Indirect) | Load A with the complement of the contents of the address whose lower 8 bits are contained in one of the first 256 (decimal) addresses and whose upper 4 bits digits are contained in the designated Auxiliary Tag register. The location in the core is given in the second instruction word. The Auxiliary Tag register is indicated in the first word.                |

| Octal<br><u>Code</u> | Mnemonic<br><u>Code</u> |                                |                                                                                                                                                                                                                                                          |

|----------------------|-------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30(X)                | ADN                     | Add (No<br>Address)            | Add to the A register the 8-bit number given in the second word of the instruction set. The sum is left in A.                                                                                                                                            |

| 31(Y)                | ADM                     | Add (Memory<br>Address)        | Add to A the contents of the combined address given in the designated Tag register and the second word of the instruction set.                                                                                                                           |

| 32(Y)                | ADI                     | Add (Indirect<br>Address)      | Add to A the contents of the combined address contained in the designated Tag register and one of the first 256 decimal locations indicated in the second word of the instruction set.                                                                   |

| 34(X)                | SBN                     | Subtract (No<br>Address)       | Subtract from the A register the number contained in the second word of the instruction set. The difference is left in A register.                                                                                                                       |

| 35(Y)                | SBM                     | Subtract<br>(Memory Address)   | Subtract from the contents of A, the contents of the combined address contained in the designated Tag register and the second word of the instruction set.                                                                                               |

| 36(Y)                | SBI                     | Subtract<br>(Indirect Address) | Subtract from the contents of A, the contents of the combined address contained in the designated Tag register and the location of one of the first 256 decimal registers, indicated by the second word of the instruction set.                          |

| 41(Y)                | STM                     | Store A<br>(Memory Mode)       | Store the contents of the A register whose address is equivalent to the combined contents of the designated Tag register and the second word of the instruction set.                                                                                     |

| 42(Y)                | STI                     | Store A<br>(Indirect Mode)     | Store the contents of the A register whose address is equivalent to the combined contents of the designated Tag register and the contents of one of the first 256 decimal core registers. The location of which is given in the second instruction word. |

| Octal<br><u>Code</u> | Mnemonic<br>Code |                                 |                                                                                                                                                                                                                                                                        |

|----------------------|------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 51(Y)                | RAM              | Replace Add<br>(Memory Address) | Add the contents of the A register to the contents of the memory address formed by the contents of the designated Tag register and the second word of the instruction set. The sum thus formed, remains in A, and replaces the initial contents of the memory address. |

| 55(Y)                | RAO              | Replace Add One                 | Add 1 to the contents of the memory address indicated by the combined contents of the designated Tag register and the second word of the instruction set. This sum is performed in A and remains in A at the end of the instruction.                                   |

| 60(Y)                | ZJP              | Zero Jump                       | If the contents of A equals zero, jump to the <u>combined</u> address contained in the designated Tag register and the second word of the instruction set. If the contents of A are not zero, continue in sequence with next <u>set</u> of instructions.               |

| 61(Y)                | NZP              | Not Zero Jump                   | If contents of A are not zero, jump to the <u>combined</u> address contained in the designated Tag register and the second word of the instruction set. If the contents of A are zero, continue in sequence with the next <u>set</u> of instructions.                  |

| 62(Y)                | PJP              | Positive Jump                   | If the contents of A are positive (equal or greater than zero), jump to the combined address contained in the designated Tag register and the second word of the instruction set. If the contents of A are not positive, continue in sequence.                         |

| 63(Y)                | NJP              | Negative Jump                   | If the contents of A are negative, jump to the combined address contained in the designated Tag register and the second word of the instruction set. If the contents of A are not negative, continue in sequence with the next set of instructions.                    |

| Octal<br><u>Code</u> | Mnemoni<br><u>Code</u> | c<br>_                    |                                                                                                                                                                                                                                                                                                                                                                |

|----------------------|------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 64(Y)                | UJP                    | Unconditional<br>Jump     | Jump to the combined <u>address</u> contained in the designated Tag register and the second word of the instruction set.                                                                                                                                                                                                                                       |

| 70(Y)                | IBI                    | Initiate Buffer<br>Input  | This instruction initiates an input buffer cycle. If the buffer channel is not busy, control goes to the next instruction following the second word of the instruction set. If the buffer channel is busy, a jump occurs to the memory location whose combined address is contained in the designated Tag register and the second word of the instruction set. |

| 71(Y)                | IBO                    | Initiate Buffer<br>Output | This instruction initiates the output buffer cycle. If the buffer channel is busy, a jump occurs to the combined memory address given in the designated Tag register and the second word of the instruction set. If the buffer channel is not busy, control goes to the next sequential instruction following the instruction set.                             |

| 72(Y)                | INN                    | Input Normal              | Input a number of words to memory starting at the memory address contained in the designated Tag register and the second word of the instruction. Last word address +1 is contained in the 3rd word of instruction set.                                                                                                                                        |

| 73 (Y)               | out                    | Output Normal             | Output a number of words to memory starting at the memory address contained in the designated Tag register and the second word of the instruction set. Last word address +1 is contained in the 3rd word of instruction set.                                                                                                                                   |

| 74(X)                | OTN                    | Output No<br>Address      | The instruction <u>outputs</u> <u>one</u> word. This word is the second word of the instruction set.                                                                                                                                                                                                                                                           |

| 75(X)                | EXF                    | External<br>Function      | This instruction is used to <u>select</u> an external input or output device to communicate with the 8092 TeleProgrammer.                                                                                                                                                                                                                                      |

| Octal<br><u>Code</u> | Mnemonic<br>Code |              |                                                                                                           |

|----------------------|------------------|--------------|-----------------------------------------------------------------------------------------------------------|

| 76(X)                | INA              | Input to A   | This instruction <u>inputs</u> <u>one</u> word from a previously selected input device to the A register. |

| 77(X)                | HLT              | Program Stop | This instruction is used to bring the program to a halt.                                                  |

#### NOTE:

<sup>\*(</sup>X)-instructions followed by X means that this instruction ignores the upper two bits and the operand is in the next sequential memory location following the instruction or the operation is performed in 1 cycle.

<sup>\*(</sup>Y)-instruction followed by Y means that this instruction uses the upper two bits to reference one of three 4-bit registers to establish a twelve bit address made up of 4 bits from the Tag register and 8 bits from memory.

#### TABLE 1-3

### EXTERNAL FUNCTION CODES AND STATUS RESPONSES FOR PERIPHERAL EQUIPMENT

All External Function Codes and Status Responses are given in octal code.

#### 1. 8098 TALLY READER

A. External Function Codes

4102 Select Reader

B. No Status codes

#### 2. 8096 TELETYPE MODEL 33 PAGE PRINTER

A. External Function Codes

4211 Select Input 4221 Select Output

B. No Status codes

#### 3. 8099 350 PAPER TAPE READER

A. External Function Codes

4102 Select Reader

B. No Status codes

#### 4. 8091 BRPE-11 PAPER TAPE PUNCH

A. External Function Codes

4104 Select Paper Tape Punch

B. No Status codes

#### 5. 161 INPUT/OUTPUT TYPEWRITER

#### A. External Function Codes

4210 Select Typewriter Output

4220 Select Typewriter Input

4240 Request Typewriter Status

#### B. Status Response Codes

0000 Typewriter Ready

0004 Typewriter Power Off

0010 Typewriter not in Computer Status

0020 Input Character Ready

0040 Output in Use

NOTE: If a second typewriter is added, the master octal bits will be 43.

#### 6. 8093 MAGNETIC TAPE SYNCHRONIZER

#### A. Function Codes

(X) is designated by Unit Select Switch on top of 603 Tape Handler Cabinet. Operator shall use positions 0 through 3.

"Binary" means odd parity is generated and checked on tape. "Coded" means even parity is generated and checked on tape.

1X02 Status Request 1

1X03 Status Request 2

1X04 Set Interrupt Lockout

1X05 Clear Interrupt Lockout

1X07 Programmed Clear

1X10 Write, Binary, Low Density

1X11 Write, Binary, High Density

1X12 Write, Coded, Low Density

1X13 Write, Coded, High Density

1X14 Write File Mark

1X20 Search Forward to File Mark

1X21 Search Backward to File Mark

1X22 Rewind to Load Point

1X24 Search Forward One Record

1X25 Search Backward One Record

1X26 Rewind Unload

1X30 Read, Binary, Low Density

1X31 Read, Binary, High Density

1X32 Read, Coded, Low Density

1X33 Read, Coded, High Density

1X34 Read

#### B. Status Responses

#### Status Request 1

| Bit<br><u>Location</u> | <u>Octal</u> | Description                                  |

|------------------------|--------------|----------------------------------------------|

| 0                      | 001          | Coded (Even Parity, no Odd Parity)           |

| 1                      | 002          | Transport Not Ready                          |

| 2                      | 004          | Parity Error                                 |

| 3                      | 010          | Program Error                                |

| 4                      | 020          | End of File                                  |

| 5                      | 040          | Tape Mark (Load Point or End of Tape)        |

| 6                      | 100          | High Density (Not Low Density)               |

| 7                      | 200          | Busy (Tape Motion)                           |

| Note:                  | Illegal BCD  | will bring bits 0, 2, and 3 (Octal Code 015) |

#### Status Request 2

| Bit<br><u>Location</u> | Octal | Description             |

|------------------------|-------|-------------------------|

| 0                      | 001   | High Density            |

| 1                      | 002   | Even Parity             |

| 2                      | 004   | End of File             |

| 3                      | 010   | Load Point              |

| 4                      | 020   | Write Not Ready         |

| 5                      | 040   | Searching for File Mark |

| 6                      | 100   | Writing File Mark       |

|                        |       |                         |

#### 7. 162 MAGNETIC TAPE SYNCHRONIZER

A. External Function Codes (6-bit mode, X = 1) (12 bit mode, X = 2)

| X110<br>thru<br>X117 | Write if OUT is given.<br>Write End-of-File Mark if no OUT is given.                            |

|----------------------|-------------------------------------------------------------------------------------------------|

| X120<br>thru<br>X127 | Backspace one record if INA is given.<br>Seach backward to End-of-File Mark if no INA is given. |

| X120<br>thru<br>X137 | Read forward if INPUT is given.<br>Search forward to End-of-File Mark if no INPUT is given.     |

| X140<br>thru<br>X147 | Request Status                                                                                  |

X150 Rewind Unload thru X157 X160 Rewind Load thru X167 X171 Set tapes to odd parity X172 Set tapes to even parity 2100 High density thru 2107 1100 thru Low density 1107

#### B. Status Response Codes

0000 Odd parity selected - no errors 0001 Even parity selected - no errors 0002 Tape X not ready 0004 Parity error 0015 Illegal BCD detected on Write 0020 End-of-File Mark read End-of-Tape or Load Point sensed 0040 0100 High density 0200 Tape X busy

NOTE: The last octal bit designates one of the four (eight) 60X's. The master octal bits 12, 13, 22, and 23 are used for second and third tape control. If the tape transport is a 606, a 6-bit high density selection is illegal (a programmer consideration).

#### 6. 166-2 LINE PRINTER

#### A. External Function Codes

0700 Asynchronous print 0710 Synchronous print 0740 Check status 072X Advance forms

#### B. Status Response Codes

0000 166-2 ready 0001 Buffer busy 0002 Out of paper 0004 Paper moving 0010 Drum stationary

0020 Off-line

#### 9. 167-2 CARD READER (Hollerith Facility)

#### A. External Function Codes

4500 EF clear 4501 Free run read 4502 Single cycle read 4504 Negate translate, H BCD 4505 FRR, H BCD and pack 4506 SCR, H BCD and pack 4540 Check status

#### Status Response Codes

В.

0000 Card reader ready 0001 Hopper empty 0002 Stacker full 0004 Feed failure 0010 Program error 0020 Amplifier failure 0040 Motor power off

#### 10. 170 CARD PUNCH CONTROL UNIT

#### A. External Function Codes

3002 Punch 3040 Check Status

#### B. Status Response Codes

0000 170 ready 0200 MS in 1604 position 2000 Punch not ready

#### 11. 177 CARD READER

#### A. External Function Codes

```

EF clear

4500

4501

Free run read

4502

Single cycle read

4505

Negate translate, H

BCD, free run read

BCD, single cycle read

Negate translate, H

4506

Gate card

4510

4540

Status request

```

#### B. Status Response Codes

```

0001

Input tray empty

0002

Primary or secondary stacker full

0004

Feed failure

0010

Late input request

Pre-read error

0020

Manual on or motor power off

0040

0100

Read comparison error

0200

End of file

0400

Ready

```

### 12. <u>8094 PERIPHERAL ADAPTOR</u>(Required when 12-bit interface is needed for peripheral equipment)

#### A. External Functions

```

6301 Select

6302 De-Select

```

B. No Status Codes

#### 13. 8060 SERIES DIGITAL COMMUNICATIONS TERMINALS

#### A. External Function Codes

```

36X0 Select stop send

36X1 Select send

36X2 Select data input

36X3 Select status input

36X4 Select

```

#### B. Status Response

0000 Computer has cleared to send 0002 Carrier is on and computer sending

#### 14. 8095 RECORD TRANSMISSION CONTROL PANEL

#### A. EXF Codes

35XX Select to input data 3501 Status Request 1 3502 Status Request 2

#### B. Status Responses #1

The Control Panel will respond with the status responses when the TeleProgrammer sends a 3501 external function. These status responses are, in effect, the way in which the terminal operator communicates with the TeleProgrammer.

| Octal<br>Response | Meaning                         |

|-------------------|---------------------------------|

| 001               | Send End of Message             |

| 002               | Send Come to Phone              |

| 004               | End of Message Not Acknowledged |

| 010               | Come to Phone Not Acknowledged  |

| 020               | Stop (Not Ready)                |

| 040               |                                 |

| 100               | Translate                       |

| 200               | Send Mode (Not Receive)         |

|                   |                                 |

#### Response #2

The Control Panel responds with the status responses shown in Table 3 when the TeleProgrammer sends a 3502 external function. This status response indicates to the TeleProgrammer which peripheral device to select for the input (send) or output (receive) operation it is to perform.

| Select<br>Send<br>Switch<br>Position | Octal<br><u>Response</u>                      | <u>Select</u>                                              | <u>For</u>           |

|--------------------------------------|-----------------------------------------------|------------------------------------------------------------|----------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7      | 0X0<br>0X1<br>0X2<br>0X4<br>1X1<br>1X2<br>1X4 | Magnetic Tape<br>Punched Cards<br>Paper Tape<br>I/O Writer | Sending<br>Equipment |

| Select<br>Send<br>Switch<br>Position | Octal<br>Response | <u>Select</u>                      | <u>For</u> |

|--------------------------------------|-------------------|------------------------------------|------------|

| 1                                    | 00X               | Receive Device as<br>Called for in |            |

|                                      | 0.4.5.0           | Header                             | Receiving  |

| 2                                    | 01X               | Magnetic Tape                      |            |

| 3                                    | 02X               | Punched Cards                      | Equipment  |

| 4                                    | 04X               | Line Printer                       |            |

| 5                                    | 21X               | Paper Tape                         |            |

| 6                                    | 22X               | I/O Writer                         |            |

| 7                                    | 24X               |                                    |            |

# CHAPTER TWO CPERATION

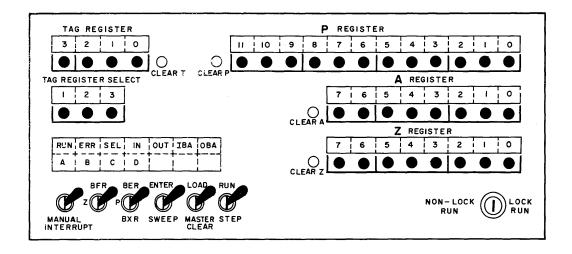

Figure 2-1 8092 Operator's Panel

#### TeleProgrammer OPERATOR's Panel

The 8092 TeleProgrammer Operator's Panel consists of several displays and switches necessary for the operation of the TeleProgrammer. The panel (see figure 2-1) contains six display windows, six switches, and a lock switch. Four of the display windows can display in binary the contents of nine 8092 registers. Buttons beneath these displays clear and enter data into the P, A, Z, and Tag registers (the only registers into which data may be entered or cleared). A fifth window contains information as to which Tag register has been selected. The sixth window contains the operating lights which indicate the status of operation

of the TeleProgrammer. At the bottom of the panel are located all the operating and mode switches. The operation of these switches is explained below:

#### **SWITCHES**

Manual Interrupt

-Momentary depression causes the Teleprogrammer to enter an interrupt routine to determine the nature of the interrupt.

-This 3-position switch chooses the register that is to be displayed in the

8-bit Z register display.

Up - Displays the last word processed during the last buffer operation (BFR register).

Center - Shows the current contents of the Z register (Z register).

Down - Not assigned.

-This 3-position switch chooses the register to be displayed in the 12-bit P register display.

Up - Displays the address of the last word transferred out, the next word to be transferred in on the buffer channel (BER register).

BFR,Z

BER, P, BXR

<u>Center</u> - Displays the address of the current instruction (P register).

<u>Down</u> - Displays the LWA + 1 of the last buffer operation (BXR register).

#### ENTER/SWEEP

-Sweep is used to display the contents of core storage locations. Enter is used for entering information into core storage from the console.

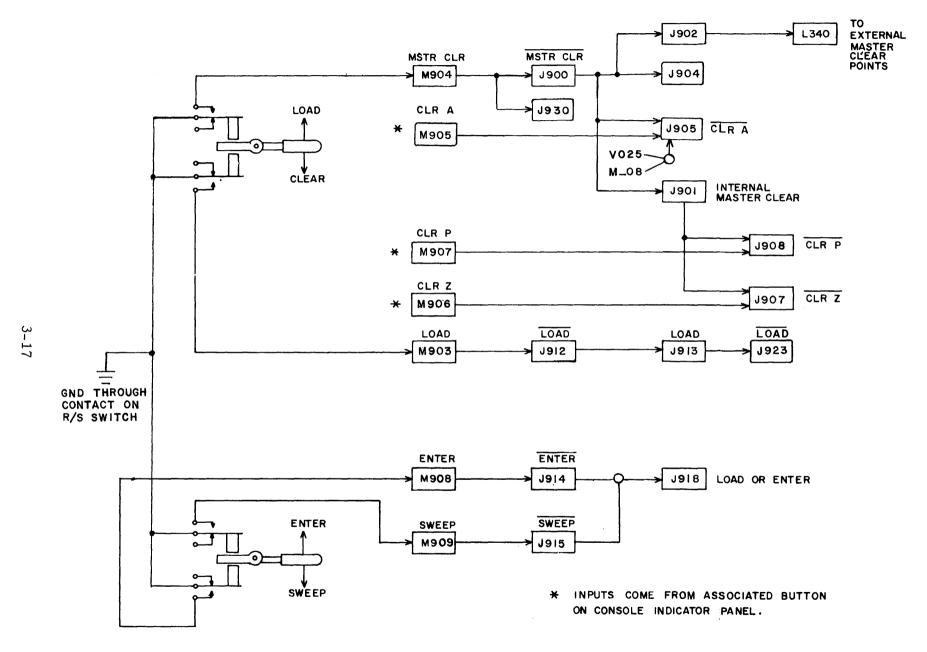

#### LOAD/MASTER CLEAR

- LOAD position allows specially prepared paper tapes to be read into storage by the paper tape reader.

Master CLEAR performs a TeleProgrammer master clear which

- a. Clears the registers

- b. Clears the control flip flops

- c. Clears all waiting interrupts and removes interrupt lockout.

Note: The master clear does not alter core storage.

#### RUN/STEP

Up - In RUN position a program is executed at high speed starting at the location specified by the P register.

Center - Center position stops the computer program. If the switch is in RUN and an ERR or HLT instruction is executed, the switch must be returned to neutral and then placed in RUN to continue computation.

Down - In STEP position, one storage cycle of an instruction is executed each time the switch is set; a program may be executed one instruction at a time for debugging.

#### NON-RUN LOCK RUN LOCK

In the Lock position all other switches are disabled and the TeleProgrammer is locked in the RUN position.

In the non-lock position, the console switches are enabled and the TeleProgrammer programs can be operated and modified from the console.

#### DISPLAYS

Z REGISTER

-This display known as the Z register group displays the Z and BFR registers in accordance with the setting of the BFR, Z switch.

#### A Register

-Displays the current contents of the A register.

P Register

-This display known as the P register group displays the BER, P, and BXR registers in accordance with the setting of the BER, P, BXR switch.

TAG REGISTER

-This display indicates the Tag register currently being referenced by an instruction. The contents of any Tag register may be displayed by depressing one of the buttons directly below the select indicators. Depressing one of the select buttons also enables the Tag registers to be manually set or cleared.

#### STATUS INDICATORS

<u>SEL</u>

RUN -Indicates that the TeleProgrammer is in

RUN status. This does not necessarily

indicate that instructions are being executed.

ERR -Indicates that a timing fault has occurred.

-Displayed each time an EXF instruction

is executed; remains until selection is

completed. A constant display of SEL

with no apparent input/output action usually

indicates the TeleProgrammer has attempted

an illegal selection.

2-5

<u>IN</u>

<u>out</u>

<u>IBA</u>

<u>OBA</u>

A, B, C, or D

-Displayed during all normal input operations. A constant display of IN with no apparent input action usually indicates that input was attempted without proper unit selection. IN is also displayed when the TeleProgrammer is waiting for an external device to supply data.

Displayed during all normal output operations. A constant display of OUT with no apparent output action usually indicates that output was attempted without proper unit selection.

Displayed during all buffer input operations.

Displayed during all buffer output operations.

Indicates which storage reference cycle will

be executed at the next operation of the

Run/Step switch. When a master clear

is performed, D is displayed indicating

that the next operation to be executed,

when the Run/Step switch is operated,

will be to fetch the instruction from memory

at the address indicated by the P register.

### STARTING THE 8092 TeleProgrammer

- 1) Be sure the TeleProgrammer is plugged into proper power source and room temperature is within the prescribed limits.

- 2) Turn Power switch on power supply to ON.

- Master clear by momentarily pressing Load/Clear switch to Clear.

- 4) When the ERR light goes out, the TeleProgrammer is ready to operate. If repeated master clears do not turn the Red ERR light off, turn off the 8092 and call maintenance.

#### LOADING A PROGRAM OR DATA

### Paper Tape Load Format

- 1) Master Clear

- 2) Turn on reader

- 3) Insert paper tape in reader

- 4) Set P to starting location

- 5) Set Load/Clear switch to LOAD

- 6) Set Run/Step switch to RUN. Paper tape will load and TeleProgrammer will stop.

### ENTERING DATA FROM THE TeleProgrammer Panel

- 1) Master clear. Set Enter/Sweep switch to ENTER

- 2) Set P to location into which data is to be entered.

- 3) Enter one word of data into the A register.

- 4) Set Run/Step switch to STEP, once. At this point A is clear and the data word is in storage and in Z.

- 5) If data is to be entered into consecutive locations, go to step 3 and P will be advanced by one on step 4. If data is to be entered into non-consecutive locations, clear P. Go to step 2.

# EXAMINING THE STORAGE CONTENTS

- 1) Master clear. Set Enter/Sweep switch on SWEEP

- 2) Set P to location to be examined.

- 3) Press Run/Step switch to STEP, once. The contents of the location specified by P will appear in Z.

- 4) To examine consecutive locations, go to step 3 and P will be advanced by one on step 3. To examine non-consecutive location, clear P, go to step 2.

# CHAPTER THREE PRINCIPLES OF OPERATIONS

The Principles of Operation section emphasizes circuit logic rather than electrical operation. The TeleProgrammer is constructed from a great many circuits and stages which are electrically similar. The functions of the circuits are described in this chapter.

The TeleProgrammer may be explained conveniently by discussing it in four major categories:

Control Section

Determines how the TeleProgrammer is to respond to a stored program and implements the necessary action.

Storage Section

Holds the pertinent program steps and operands used in problem solving.

Arithmetic Section

Performs the arithmetic processes.

Input/Output

The means by which information is usually entered into the TeleProgrammer, and the only method of communication to peripheral units for storage of processed data on magnetic tape, paper tape, or typewriter copy.

The functional descriptions contained herein are supplemented by:

Logic Diagrams

A graphic presentation of the logical relationships.

File of Equations

The complete and ultimate source of all information concern-

ing the logic of the computer.

The information in these two volumes is so necessary for a complete understanding of the logic circuits that they are not called out during every functional description; rather, it is assumed that the reader will automatically refer to them.

Three additional sources will be found useful from time to time:

Appendix A Instruction timing charts pinpointing the steps involved in

execution of each instruction.

Appendix C Information for installing the TeleProgrammer; includes

weights, power consumption, and so forth.

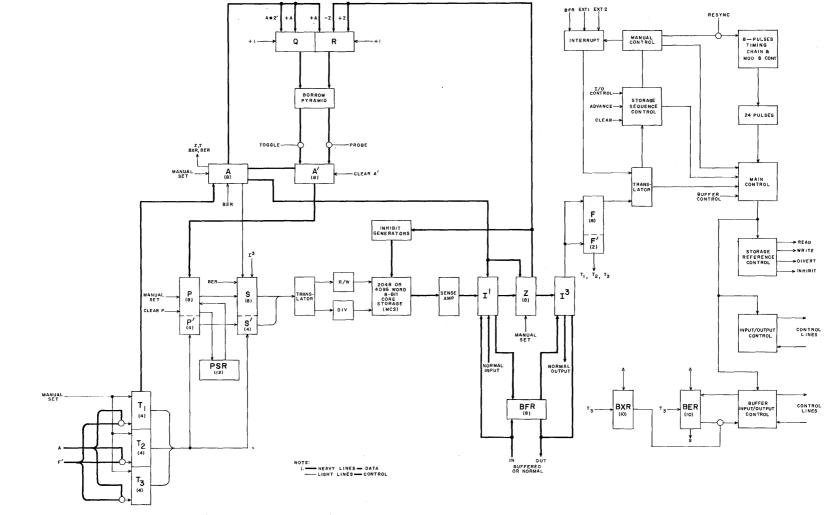

A block diagram of the TeleProgrummer is shown in figure 3-1.

# CONTROL SECTION

All TeleProgrammer logic, that is, the transfer of information from one logic element to another, is performed at a rate determined by a series of oscillator cards. Initiation and control of the logical operations or commands necessary for the execution of an instruction, however, are governed by a main timing chain. In the following paragraphs, each of the components in the basic control mechanism is discussed.

### REGISTERS

The TeleProgrammer has fourteen registers. Six of these, A, P, Z,  $T_1$ ,  $T_2$ , and  $T_3$ , are operational in that their contents may be modified by manipulation of the associated bit-stage push buttons. The eight transient registers A', S, F, PSR, BFR, BER, BXR and O are important only to the internal operation of the TeleProgrammer. The contents of all registers but PSR, A', S, F and O may be displayed on the console.

### A Register (8 Bits)

The A register is the principal arithmetic register. For most arithmetic operations, A, together with the adder, operates as a 8-bit subtractive accumulator.

Figure 3-1. Block Diagram of TeleProgrammer

The arithmetic processes of addition and subtraction are performed modulus  $2^8-1$ . The quantity zero is represented by all zeros.

Each stage of A incorporates a flip-flop (FF) with inputs from the corresponding stage of the A' register. The set side of the FF has an input from the bit-stage push button on the console control panel; the clear side has an input from the Clear A function. Additional forced (set/clear) inputs come from the Buffer Entrance register and Tag registers.

Outputs from A go to the adder through R and Q inverters, and to second-level control for sensing A = 0. The final stage in A sends its output to the function translator for determining, under certain conditions, whether the quantity in A is positive ( $A^{11} = "0"$ ) or negative ( $A^{11} = "1"$ ). Outputs from A also go to Z, BER, BXR, S,  $T_1$ ,  $T_2$  and  $T_3$ .

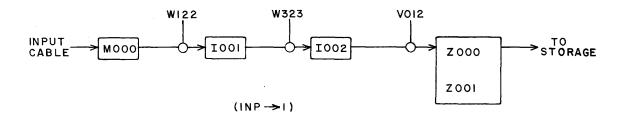

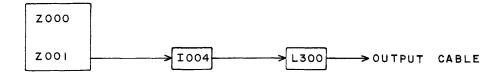

### Z Register (8 bits)

The Z register performs a variety of functions. It acts as a storage restoration register for non-buffered data read-out of memory, and it holds one of the operands in arithmetic operations. It communicates with external equipment via the input/output channels, and is one of the two means of communication with core storage.

Because the number of transmission paths through Z exceeds the input and output pin capacity of any one FF card, each stage of Z has four inverters. Two inverters lead to the set input, and the other two come from the clear and set outputs of the Z stage FF.

### P Register (12 bits)

The Program Address register, P, holds the address of the current instruction and is a double-rank counter. At the beginning of each instruction, P is increased by one to provide the address for that instruction. If a jump instruction is called for, P is forced to the jump address. In addition to the manual set and clear inputs, P has one set input from the PSR register, and a forced input from A' and the three Tag registers to provide the jump address. The output from P goes directly to the S register.

# A' Register (8 bits)

The results of all operations involving the adder are formed in the auxiliary arithmetic register, A'. The contents of A' move under program control to A, or P. The state of each stage of A' during adder operations is determined by one or more levels with the adder. Functions controlling A', labeled Clear, Toggle, and Probe, are explained in the Arithmetic Section.

### S Register (12 bits)

The Storage Address register, S, holds the address for any ensuing storage reference for an operand, another address, or an instruction word. Each stage of S is a single FF with inputs from A, Z, P, BER,  $T_1$ ,  $T_2$ , and  $T_3$ . Outputs go to the storage translators for implementing the actual address selection.

### F Register (8 bits)

The Function register holds the upper 6 bits of the instruction word in its lower 6 bits throughout the execution of that instruction. The 2 bits of the Tag register reference are held in the upper 2-bit positions. The inputs to F come from

Z via the 1<sup>3</sup> inverters. Outputs from F go to the Function Translator. Outputs from F' go to the Tag register select circuits

# PSR Register (12 bits)

The 12-bit P Storage register is temporary storage for the address at which the TeleProgrammer was interrupted. On recognition of an interrupt, information in P is forced into PSR. Each stage of the PSR consists of one FF which has inputs from each corresponding stage of the P register. Outputs from PSR go to corresponding stages in the P register.

# $T_1$ , $T_2$ , $T_3$ Registers (4 bits)

The three 4-bit T registers hold the upper four bits of a 12-bit address. These are referenced or selected by the upper two bits of the instruction word. Inputs to the Tag registers are from an inverter selection matrix which is fed from the lower 4 bits of the A register. Manual inputs also come through this inverter matrix. Outputs from the Tag registers go to an inverter selection matrix that selects which Tag register content is to be transferred to the upper 4 bits of the P or S register.

### O Register (6-bits)

The 6-bit O register is temporary storage for the upper 6 bits of a 12-bit External Function code. Inputs to O are from the lower 6 bits of the Z register. Outputs feed the line driver output cards.

### BFR

The Buffer Data register holds the word of information being transferred to or from storage during a buffer operation.

Each stage of BFR consists of one FF. During a buffer input cycle, BFR receives data from the buffer input cable and sends an output to the IO-4 inverters for writing the input word into storage. For buffer output, BFR receives the buffer output word from the IO-2 inverters and puts it on the buffer output cable.

#### BER

The Buffer Entrance register holds the storage address to which, or from which, the current data word is to be transferred during a buffer input/output operation. Each BER stage has a forced input from the corresponding stage of the A register.

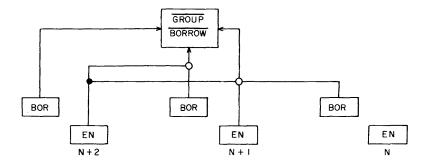

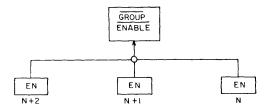

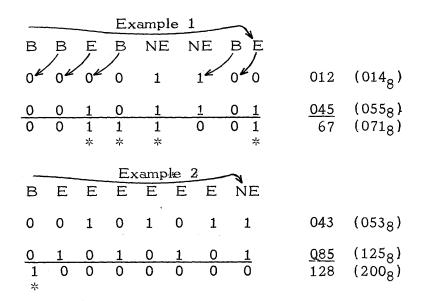

The contents of BER are incremented by 1 during each buffer cycle except the first, since for this case the first word address (FWA) has already been entered into BER by an ABR (X04) instruction. Outputs from BER go to a network for comparing the current buffer word address with the last word address held in the Buffer Exit register, and also to the S register.

### <u>BXR</u>

The Buffer Exit register holds the terminating address (LWA + 1). Forced inputs to each single FF stage of BXR come from the A register during the ABX (X05) instruction which precedes each buffer I/O operation. The output from BXR goes to a network for comparing BER with BXR during each buffer cycle.

### MASTER CLOCK

The master clock which provides the timing pulses used throughout the TP consists of four interconnected oscillators, each of which is contained on a type 02A card. Each oscillator operates at 3.0 megacycles and produces two sine waves, even and odd, 180 degrees out of phase with one another. Each oscillator card has two logic symbols. For example, C--0 could represent the even phase, and C--1, the odd phase. The odd phase is always the higher order symbol.

One pin on each of the four oscillator cards connects all even phases together. The odd phases are similarly connected, thereby assuring that the oscillators are synchronized. Five even and five odd output pins are available on each 02A card. Since these outputs draw some current, each oscillator is loaded as symmetrically as possible.

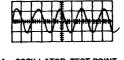

A. OSCILLATOR TEST POINT (VERTICAL: 5v/cm; SWEEP: 0.2 psec/cm)

B. OSCILLATOR OUTPUT PIN (VERTICAL: 5v/cm.; SWEEP: 0.2 psec/cm)

C. COMPARISON OF PHASES AT THE OUTPUT OF SLAVE INVERTER (VERTICAL: 2 v/cm.; SWEEP: 0.2 µsec/cm)

Figure 3-2. Master Clock Oscillator Waveforms

Figure 3-2 shows the waveforms of the oscillator card and the square wave produced after that wave passes through one inverter. The asymmetrical shape of the wave at the oscillator output pin is due to the bias used in clipping the sine wave peaks. Only the negative (top) portion of the wave is used in gating. Therefore, the clock pulses in the TeleProgrammer are 0.167 in duration.

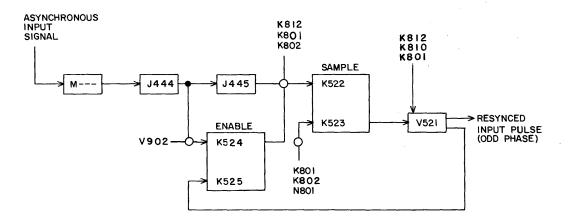

Two oscillators drive a resynchronizing system which times asynchronous signals, such as those developed by manual switches and external equipment communication lines, to the TeleProgrammer. This system is discussed in the section dealing with input/output control.

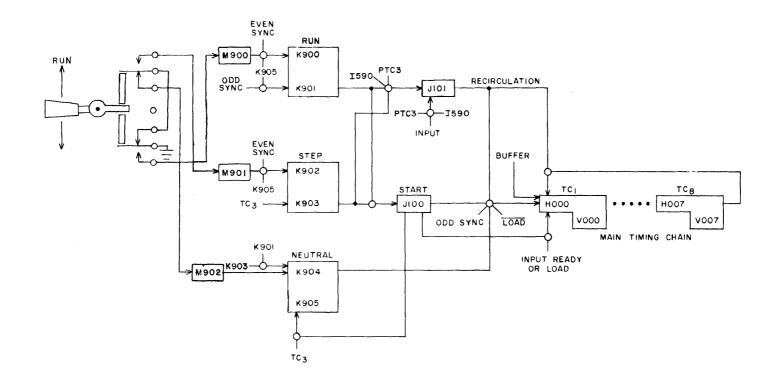

### MAIN TIMING CHAIN

The main timing chain is the ultimate source of control for all arithmetic, transfer and housekeeping functions. The timing chain is inactive during normal input/output operations since the external equipment is asynchronous with the computer. However, any operation using these devices must be initiated by the timing chain.

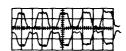

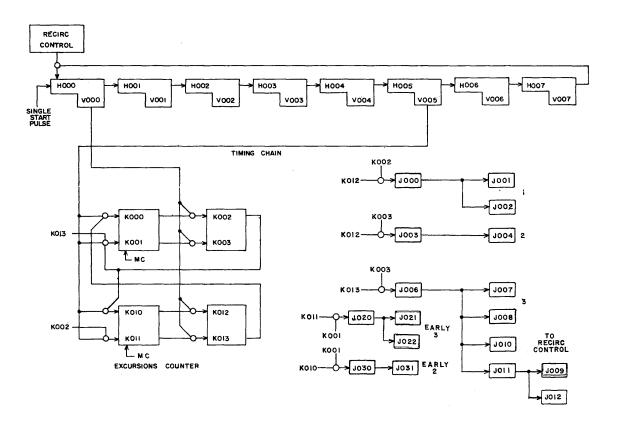

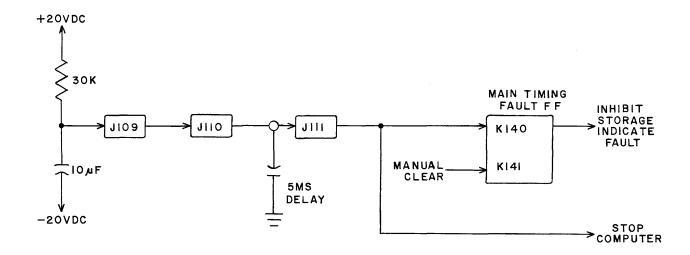

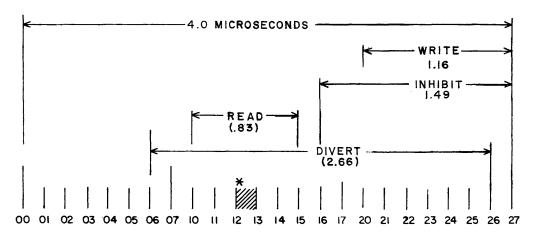

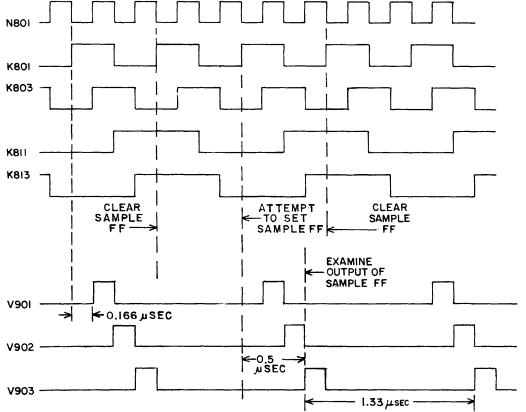

The chain consists of eight control delays (top of figure 3-3). For each input (start) pulse, the chain emits eight pulses (as evidenced by V00-outputs), spaced 0.167 usec apart. A recirculation control allows the V007 pulse to re-enter H000, thereby extending the number of timed pulses emitted. A string of 24 pulses (three passes through the timing chain) is produced for each start pulse. Such a train of pulses is called a storage reference cycle, and is the basic timing unit within the TeleProgrammer.

### Timing Chain Excursions Counter

A record of the number of times a given pulse has traversed the timing chain is kept by the excursions counter. This is a two-stage, double-rank, reflected binary counter (figure 3-3 lower left). Excursions counter outputs go to the primary timing control.

# Primary Timing Control

The primary timing control translators reflect the state of the excursions counter. The three passes of each storage reference cycle are decoded by the inverters in Figure 3-3, lower right). The passes are designated 1, 2, 3, early 2nd or early 3rd. The early quarter begins at time 5(V005) on the previous pass (figure 3-4). The part these cards play in TeleProgrammer timing is described more complete in the section on storage control.

Figure 3-3. Main Timing Controls

Figure 3-4. Main Timing

# STORAGE REFERENCE CYCLE

The storage reference (SR) cycle is the basic timing unit for the TeleProgrammer; all operations depend upon the execution of at least one such cycle.

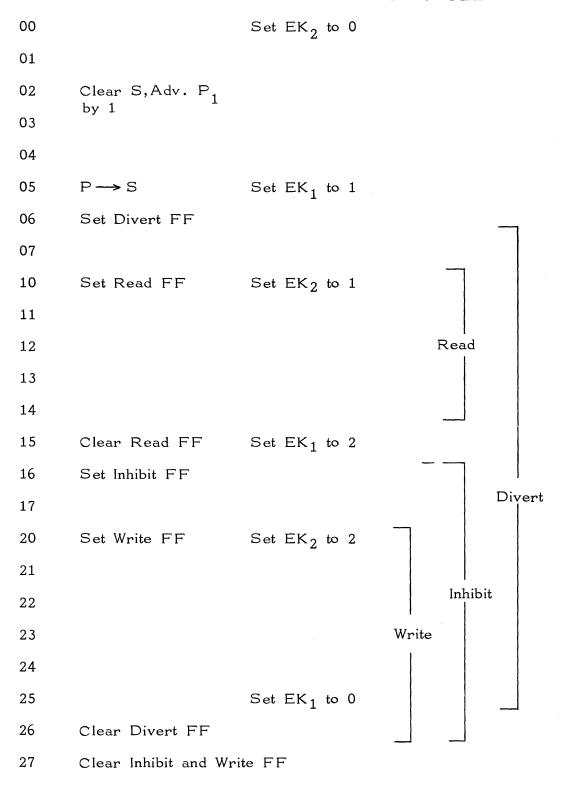

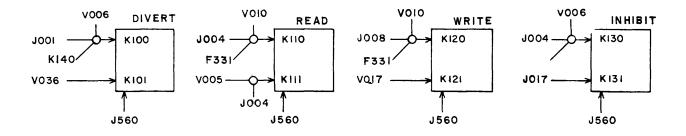

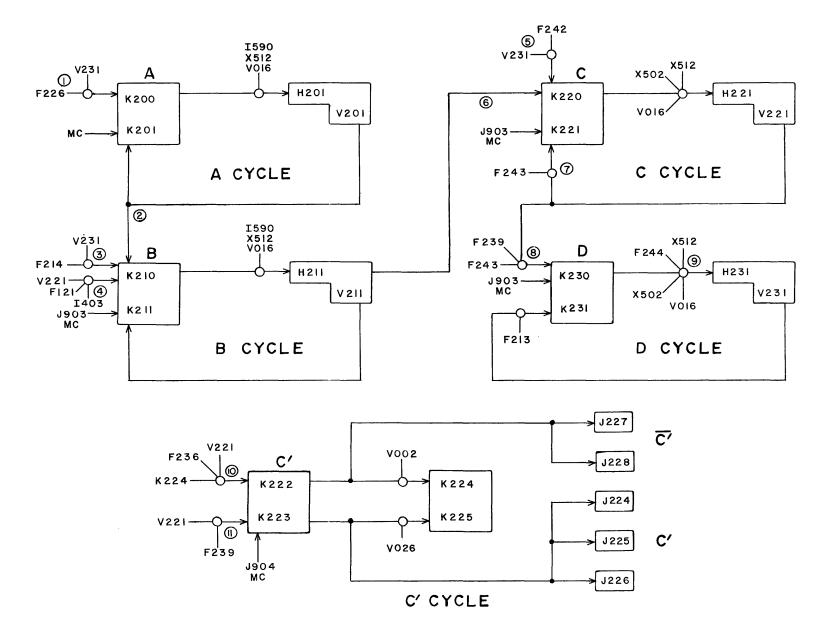

The storage reference cycle consists of four phases: divert, read, write, inhibit (described in the storage section). At the bottom of figure 3-4 is shown the timing of the four Storage Reference Control FFs which regulate the duration of each of the SR phases. These FFs will be energized during each SR cycle, whether it be A, B, C or D. The decision as to which type of SR cycle is to be executed is the province of the Storage Sequence Control.

#### FUNCTION TRANSLATOR

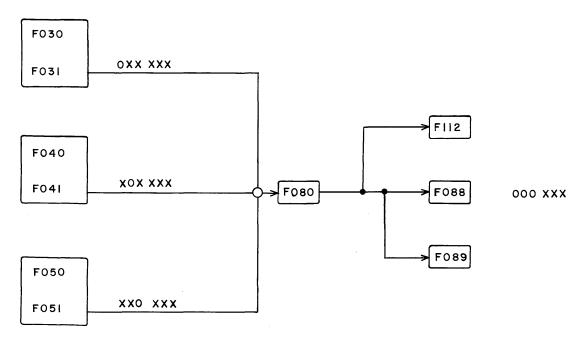

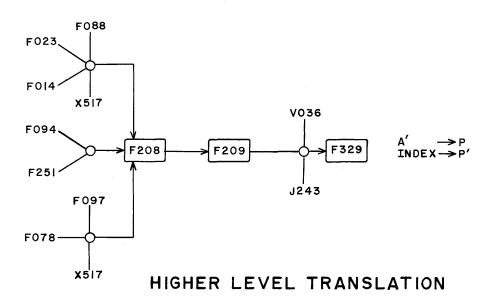

The function translator performs several levels of translations upon the operation code held in the F register in order to determine what machine commands must be fulfilled during that instruction. A typical translation is shown in figure 3-5.

Other translations may involve fewer elements.

The first-level translators consist of two 3-bit groups which translate the F register into octal notation. As an example consider the element F080. F080 has inputs from the upper 3-bit group of F030 through F051 and has a normal "1" output except when those three contain zeros. F080 is thus energized when a code 000XXX is in the F register (i.e., an octal 0X where X denotes insignificant digits). In other words, F080 translates 0X octal. From these first level translations, higher level translations are performed which, then combined with primary timing elements, control the actions and reactions of the TeleProgrammer to various instructions. An example of higher level translation

IST LEVEL FUNCTION TRANSLATION

Figure 3-5. Typical Function Translation

is F208 and F209. Here if any one of the AND inputs is satisfied F208 will be energized and F209 will go to a "1", which in turn satisfied the AND to F329 thereby accomplishing the A'->P function.

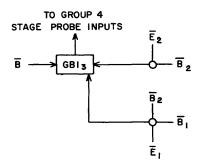

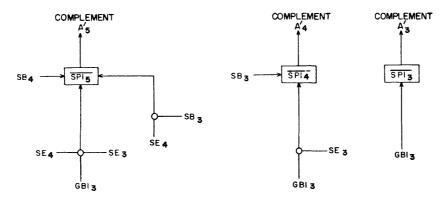

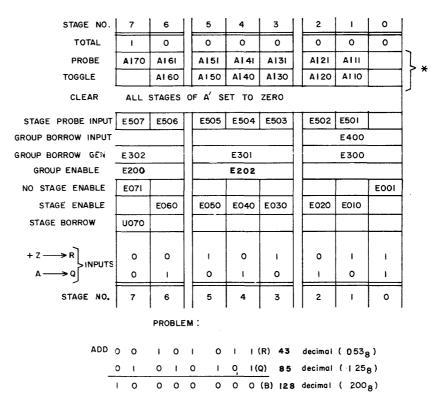

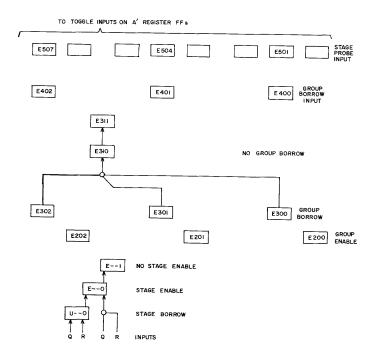

### F' Register