# CONTROL DATA® 3000 SERIES COMPUTER SYSTEMS

INPUT/OUTPUT SPECIFICATION MANUAL

|                                       | RECORD of REVISIONS                                                                                 |

|---------------------------------------|-----------------------------------------------------------------------------------------------------|

| REVISION                              | NOTES                                                                                               |

| А                                     | Pages 2, 3, 12, 21, 22, and 24 revised; page 12A added.                                             |

| В                                     | Title changes from 3200, 3400, and 3600 to 3000 series.                                             |

| С                                     | Complete revision; data on circuits and connectors added as appendixes.                             |

| D                                     | Pages 11, 16, 17, 18. 0, 20 and 22 revised. New pages 18. 1 and 18. 2 added.                        |

| (6-4-65)                              |                                                                                                     |

| Е                                     | Appendix C - Dwg No. 17684000 (was Dwg. No. 2231214), pages 18.0 and 23 revised.                    |

| (8-3-65)                              |                                                                                                     |

| F                                     | Publication Change Order 11859 - Page 18, 1 and 18, 2 revised.                                      |

| (11-2-65)                             |                                                                                                     |

| G                                     | Publication Change Order 14083 - Pages iii and 22 revised. Pages 27, 28, 29, 30, 31, 33, 35, 37 and |

| (7-19-66)                             | 39 added.                                                                                           |

| н                                     | Change Order 14575, pages 7, 13, 16, 37 and 39 revised.                                             |

| (6-27-67)                             |                                                                                                     |

| J                                     | Manual revised; Engineering Change Order 20640, publication change only. Pages 7, B-3, B-7, B-8     |

| (10-14-68)                            | B-9. 1, B-9. 2 and B-10 revised.                                                                    |

| K                                     | Field Change Order 21538. Page 17 revised.                                                          |

| (10-17-69)                            |                                                                                                     |

| L                                     | Engineering Change Order 23515, publication change only. Page 11 revised.                           |

| (10-17-69)                            |                                                                                                     |

| М                                     | Manual Revised. Engineering Change Order 26090, publication change only. Pages 32, 32, 1, 32, 2,    |

| (9-2-70)                              | and 40 added.                                                                                       |

|                                       |                                                                                                     |

|                                       |                                                                                                     |

|                                       |                                                                                                     |

|                                       |                                                                                                     |

|                                       |                                                                                                     |

| · · · · · · · · · · · · · · · · · · · |                                                                                                     |

|                                       |                                                                                                     |

|                                       |                                                                                                     |

|                                       |                                                                                                     |

|                                       |                                                                                                     |

|                                       |                                                                                                     |

|                                       |                                                                                                     |

|                                       |                                                                                                     |

|                                       |                                                                                                     |

|                                       |                                                                                                     |

|                                       |                                                                                                     |

|                                       |                                                                                                     |

|                                       |                                                                                                     |

Address comments concerning this manual to:

Control Data Corporation Technical Publications Department 4201 North Lexington Avenue St. Paul, Minnesota 55112

or use Comment Sheet in the back of this manual.

.

Pub No. 60048800 © 1965, 1966, 1967, 1968, 1969, 1970 by Control Data Corporation

**Printed** in United States of America

# CONTENTS

| Scope and Purpose                    | 1  |

|--------------------------------------|----|

| Contents                             | 1  |

| Appendixes                           | 1  |

| Data Channel Interfaces              | 1  |

| Operations                           | 2  |

| Connect                              | 2  |

| Function                             | 2  |

| Read                                 | 2  |

| Write                                | 2  |

| All Operations                       | 4  |

| Data Transfer Rates                  | 27 |

| Definitions                          | 27 |

| Data Flow Analysis                   | 27 |

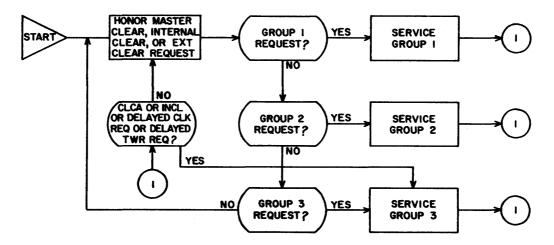

| 3100 Computer Block Control Priority | 28 |

| 3200 Computer Block Control Priority | 29 |

| 3300 Computer Block Control Priority | 30 |

| 3500 Computer Block Control Priority | 32 |

| I/O Transfer Rate Test Results       | 33 |

| APPENDIXES                           |    |

| A Signal Cable and Connector         |    |

B Transmitter, Receiver, Transmission Line

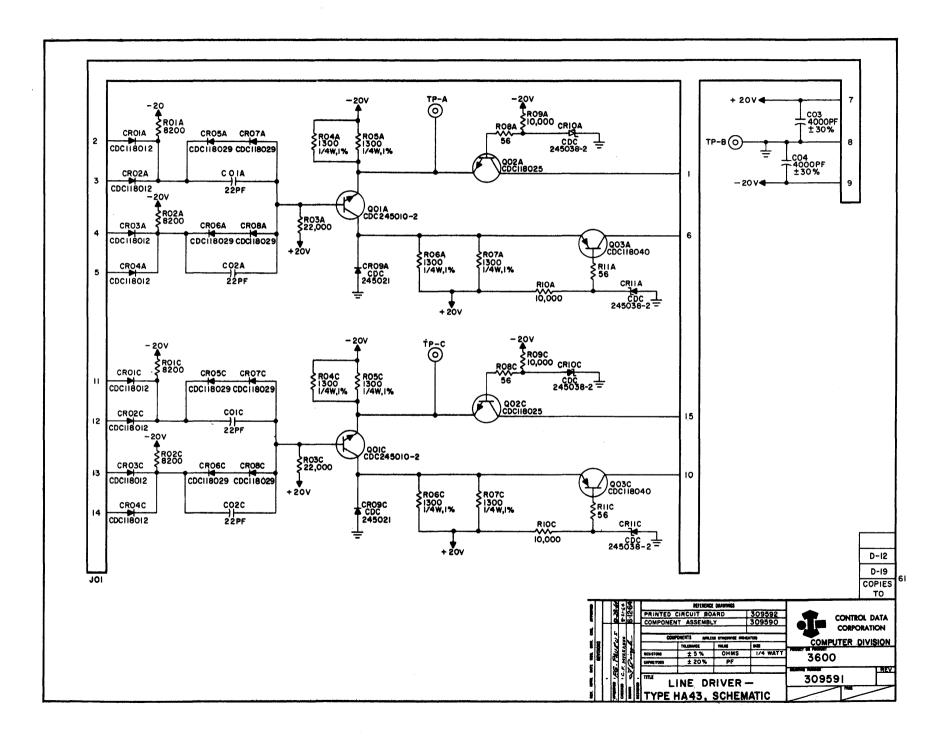

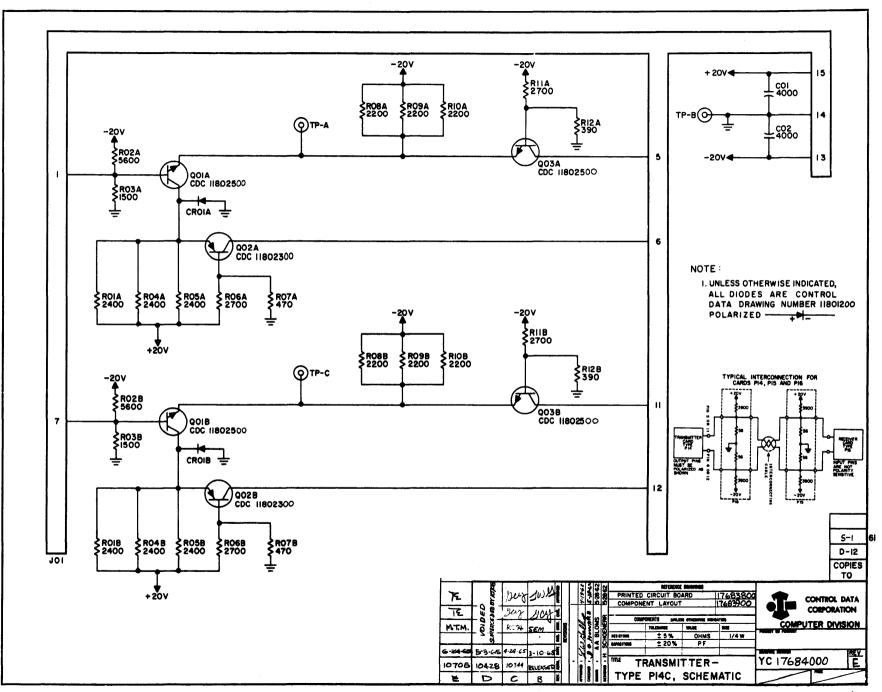

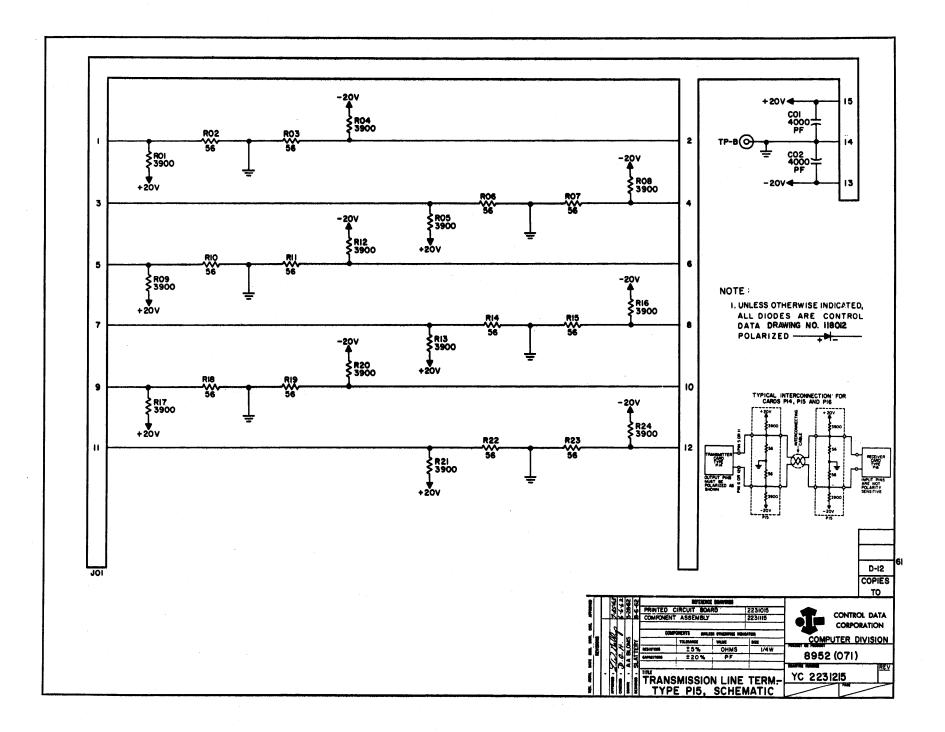

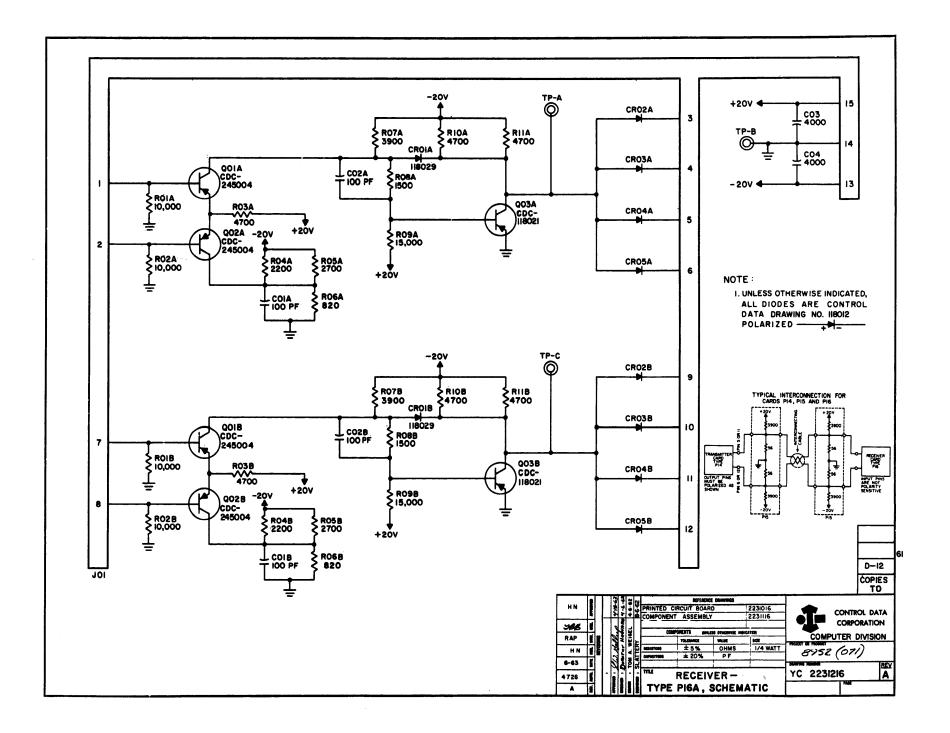

C Schematic Diagrams

# **FIGURES**

| 1. | Signal Timing                                 | 3    |

|----|-----------------------------------------------|------|

| 2. | Block Control Priority Scheme (3500 Computer) | 32.1 |

# TABLES

| 1. | Bidirectional Signals                           | 5    |

|----|-------------------------------------------------|------|

| 2. | Signals from Data Channel to External Equipment | 6    |

| 3. | Signals from External Equipment to Data Channel | 12   |

| 4. | Standard 12-bit Channel Interface               | 19   |

| 5. | Special 24-bit Channel Interface                | 21   |

| 6. | Special 48-bit Channel Interface                | 24   |

| 7. | Buffer Groups (3500 Block Control Priority)     | 32.1 |

|    |                                                 |      |

# **SCOPE AND PURPOSE**

This specification applies to all devices used as external equipments with the 3000 series of computing systems. The purpose of this specification is to describe a uniform set of operating characteristics, consistent with accepted engineering practices and moderate hardware requirements, which will apply to all equipments.

# CONTENTS

This specification contains brief descriptions of the data channel interfaces and the basic operations. Tables 1, 2, and 3 define in detail the transmitted signals and their relation to the operations. Tables 4, 5, and 6 list signal and pin assignments in the cables.

### APPENDIXES

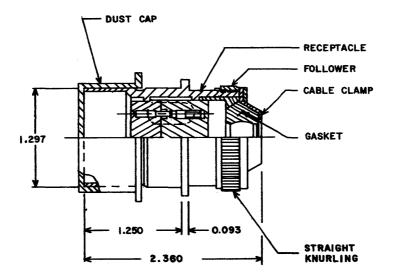

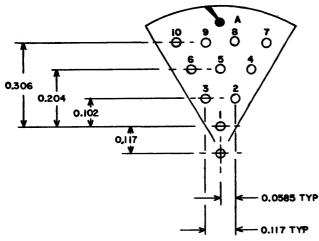

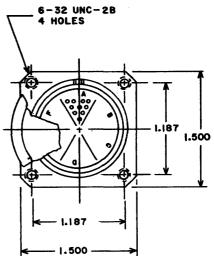

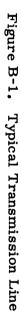

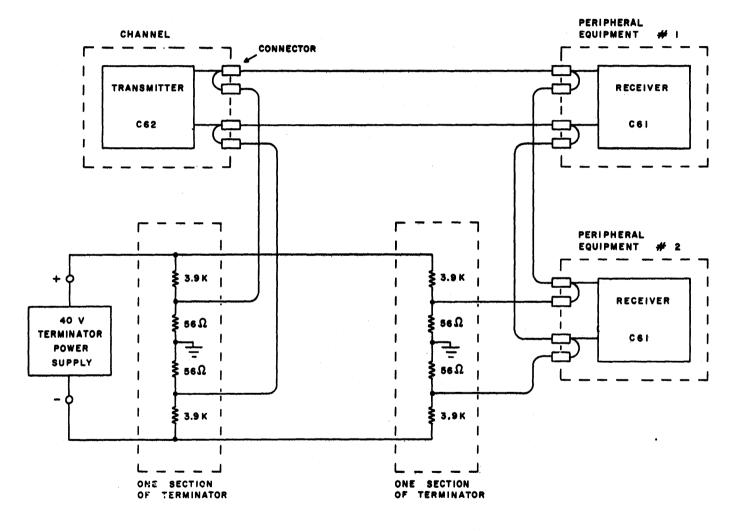

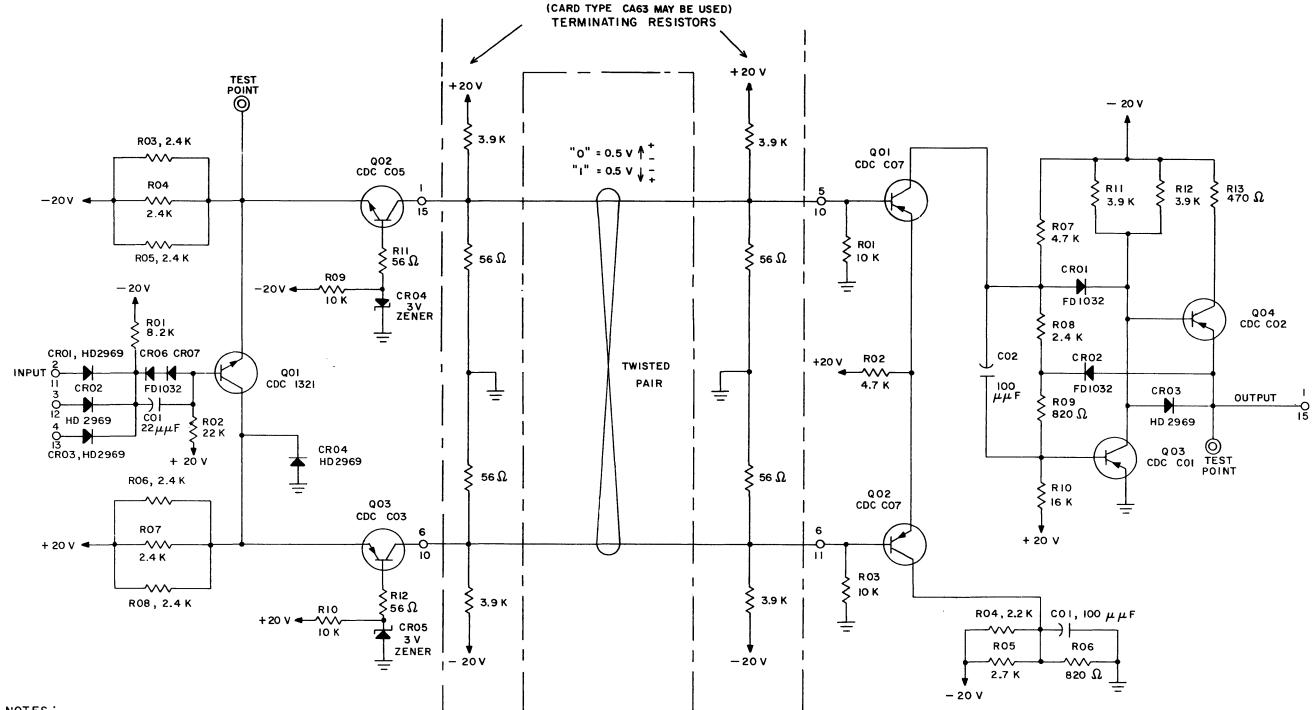

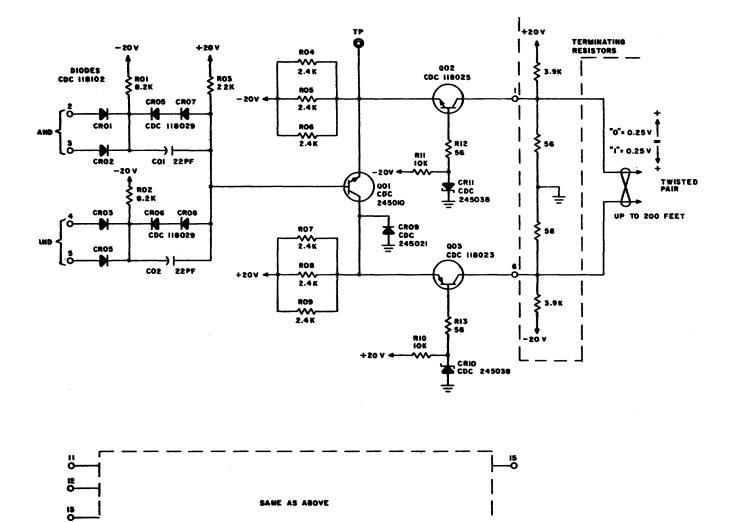

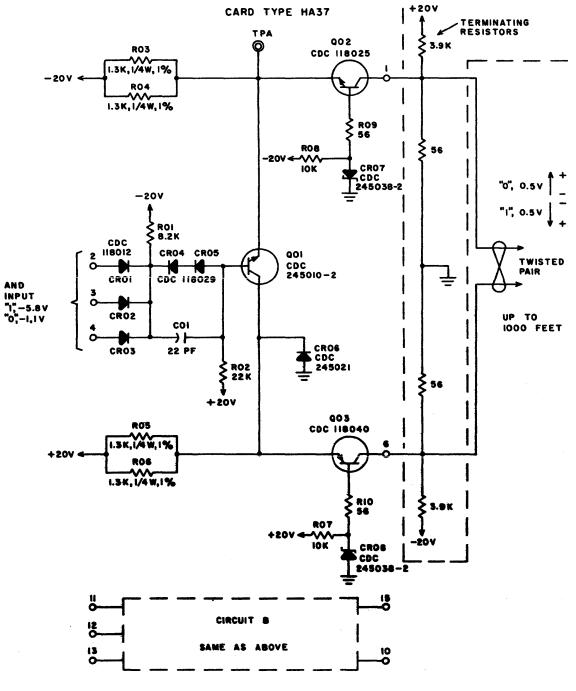

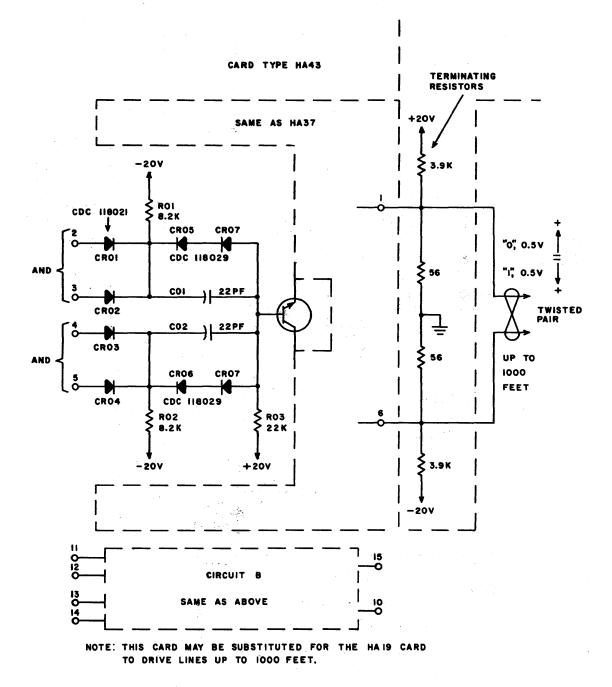

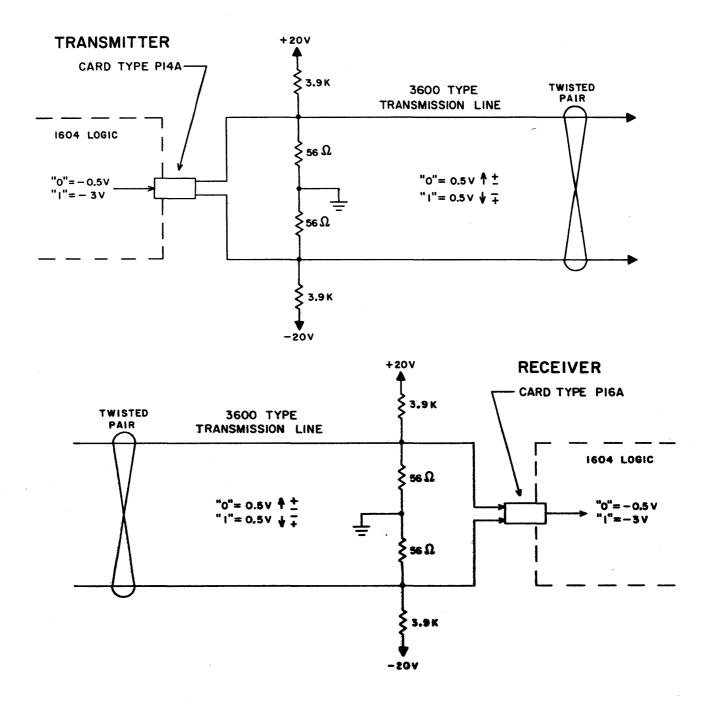

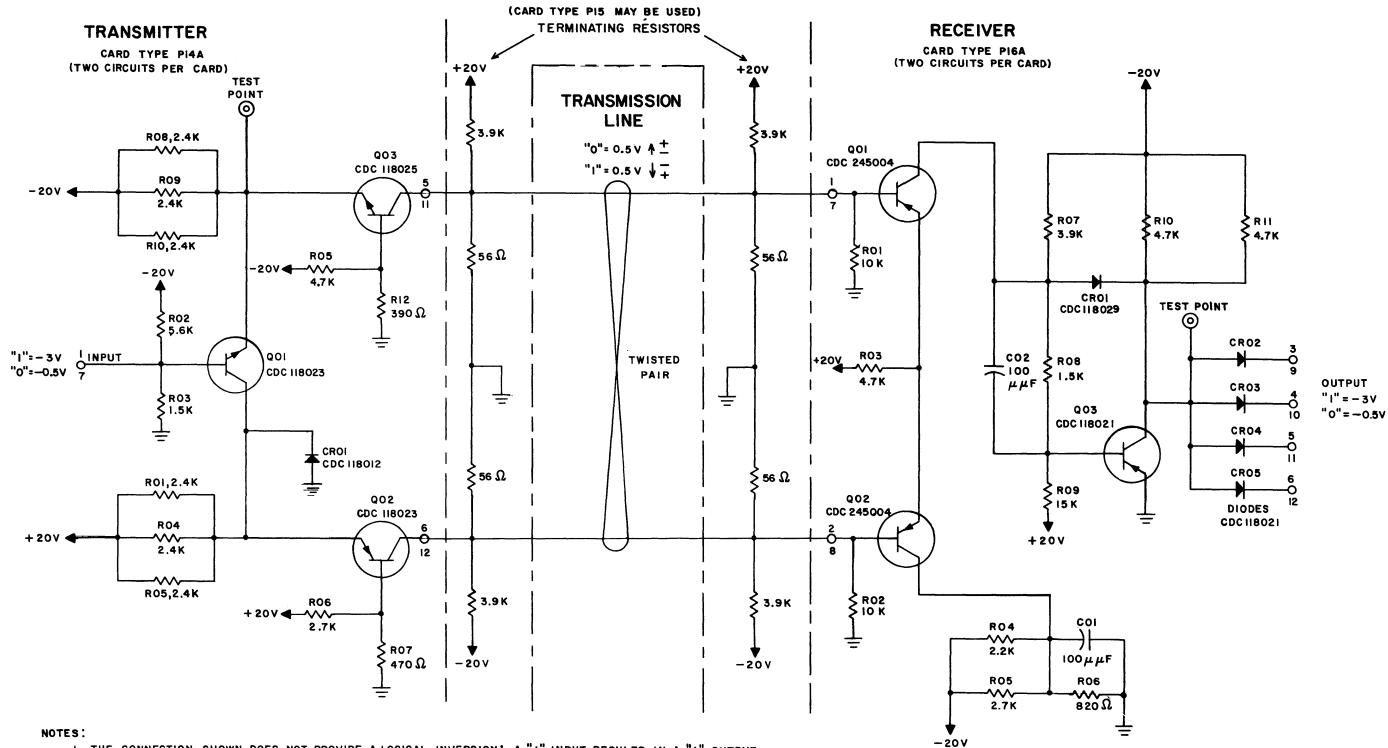

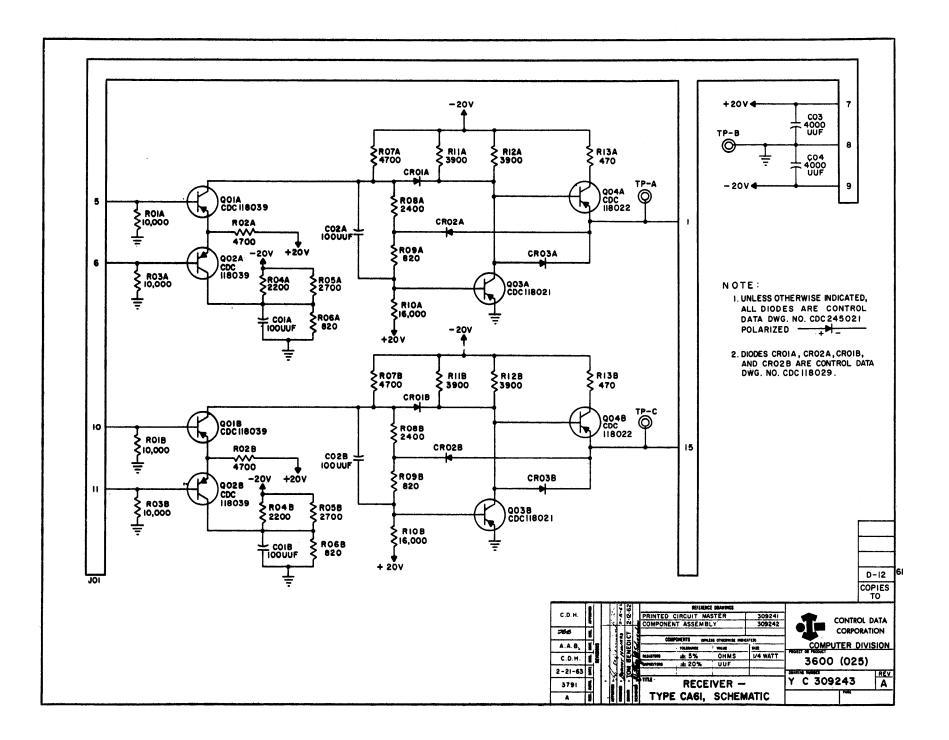

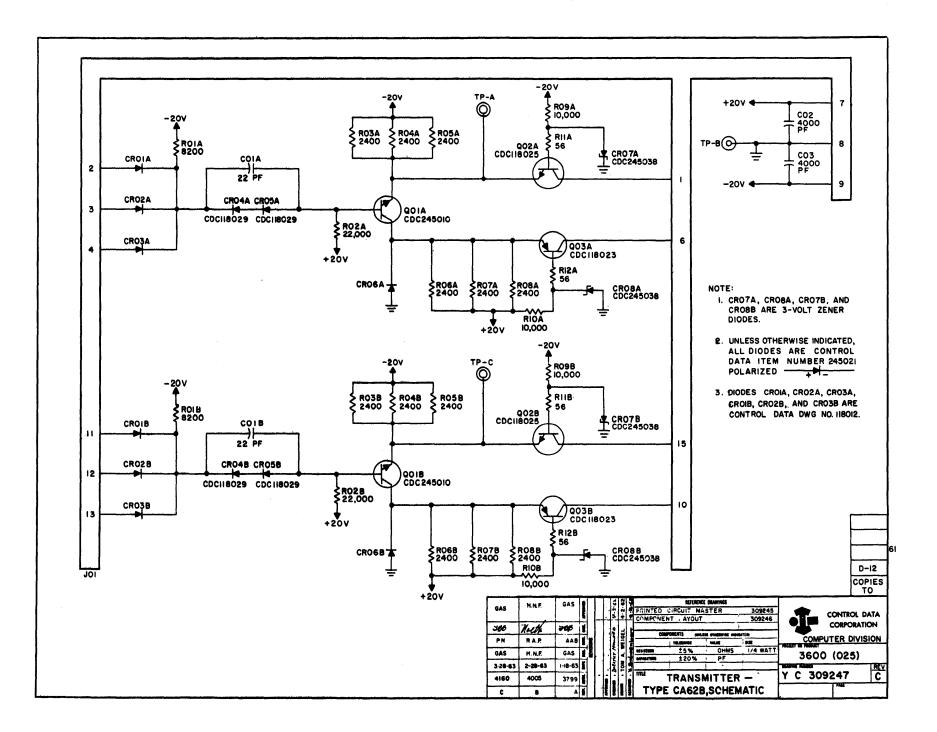

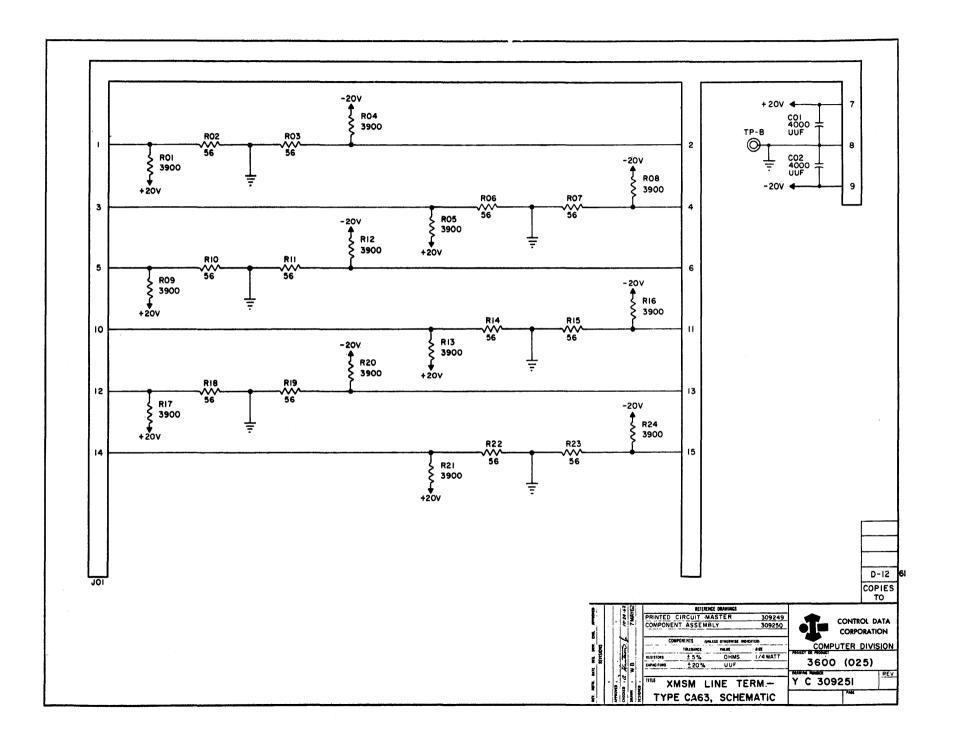

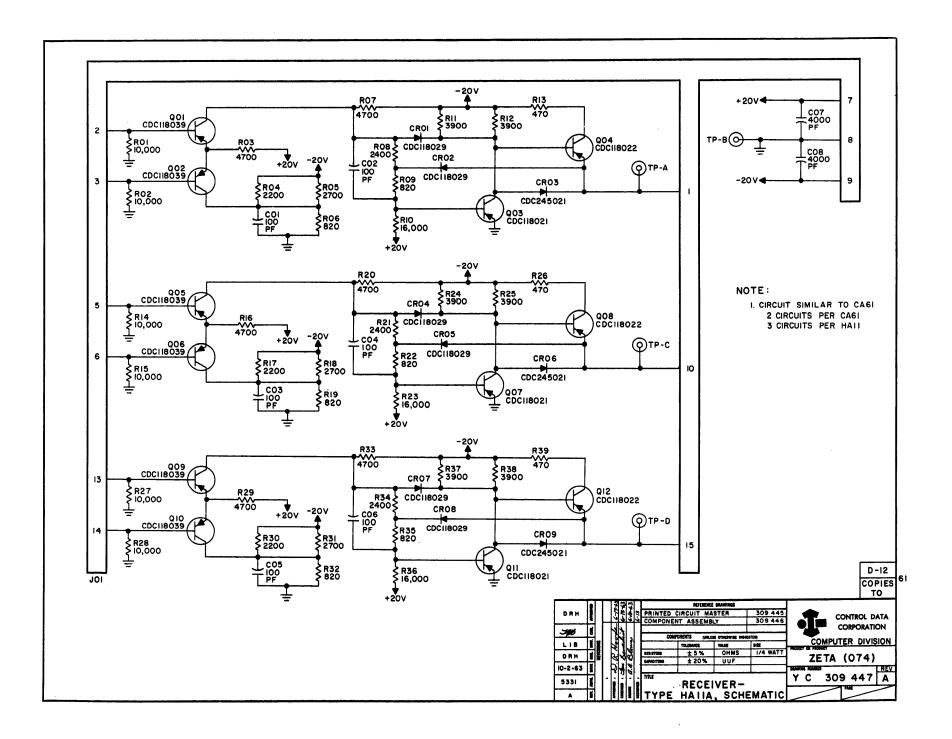

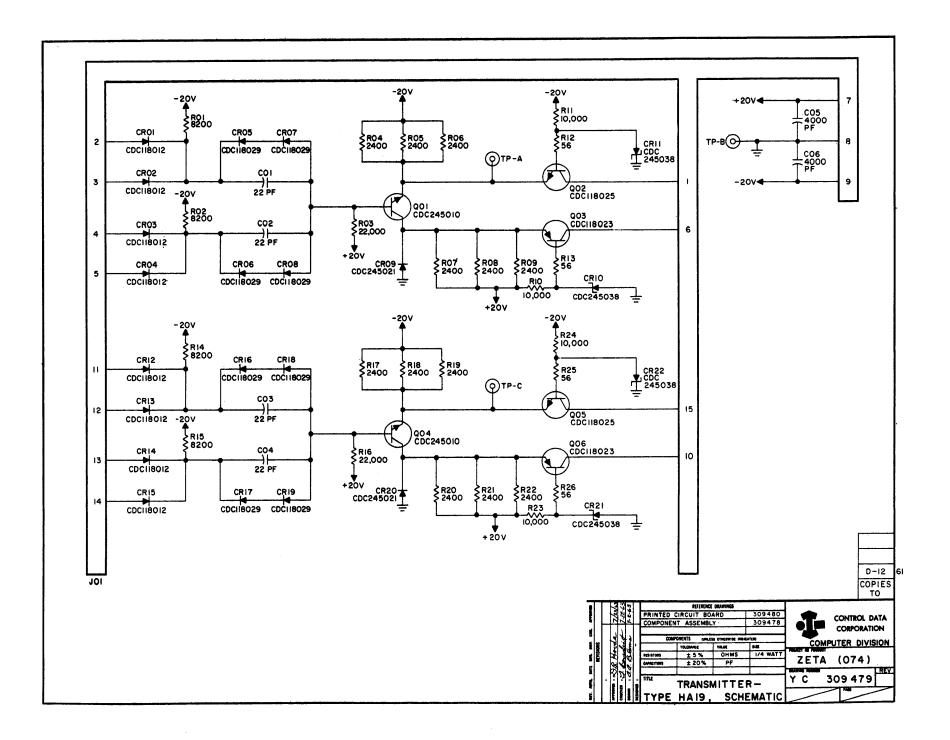

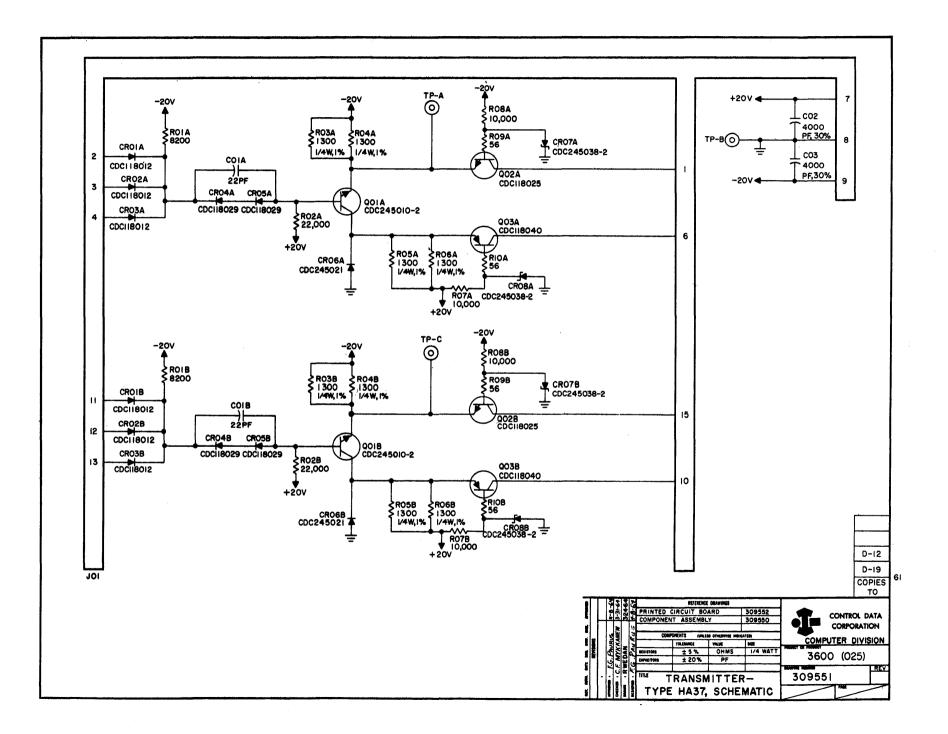

Appendix A discusses the physical characteristics and dimensions of the 29-pair signal cable and the 61-pin connector. Appendix B describes the electronic characteristics and operation of transmitter and receiver circuits and the twistedpair transmission line. Appendix C contains schematic diagrams of the various types of transmitters and receivers currently in use.

> NOTE: The items presented in the appendix section are subject to change by Engineering Change Order. The information given was valid and accurate as of revision C of this manual.

# DATA CHANNEL INTERFACES

A 3000 series computing system communicates with external equipment via bidirectional data channels. The standard 12-bit data channel transmits and receives information in the form of 12-bit bytes. The data channel contains assembly/ disassembly logic as required. The special 24-bit and 48-bit channels communicate in 24-bit and 48-bit bytes, respectively.

### **OPERATIONS**

### CONNECT

A data channel may have eight possible equipments attached to its set of I/O cables. These are selected individually by means of the Connect instruction. A 12-bit connect code is transmitted; the upper 3 bits select one of the eight equipments and the lower 9 bits select the unit (if any) of that equipment. This is accomplished by a Connect signal (delayed 0.2 usec) directing all eight equipments to examine the code. The selected equipment returns a Reply or Reject, according to whether it is available for connection.

### FUNCTION

Various operating modes and conditions (such as Interrupt) are specified using the Function instruction. The 12-bit function code is placed on the data lines and a Function signal (delayed 0.2 usec) is sent. The connected external equipment responds by returning the Reply or the Reject signal. If the connected equipment is capable of executing the specified function at the time it receives the signal, it initiates the function and returns the Reply signal. If the connected equipment is not capable of performing the specified function at this time, it returns the Reject signal.

### READ

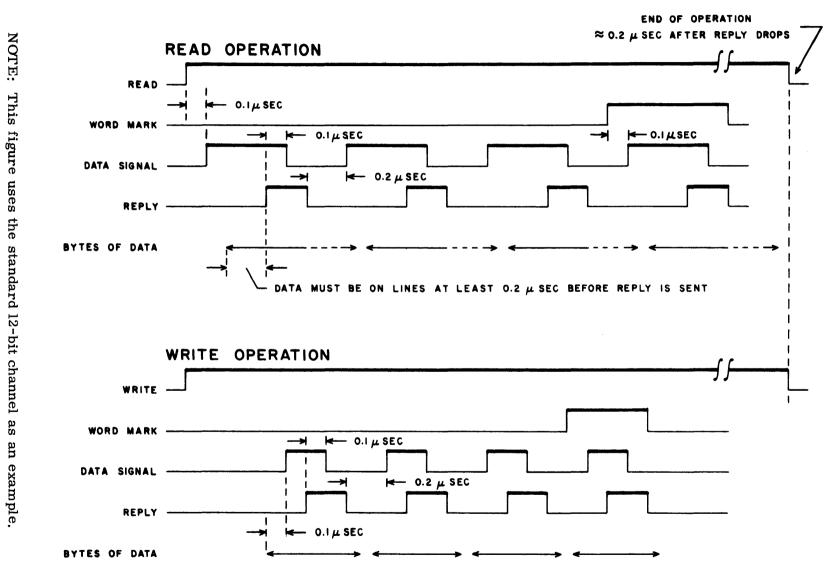

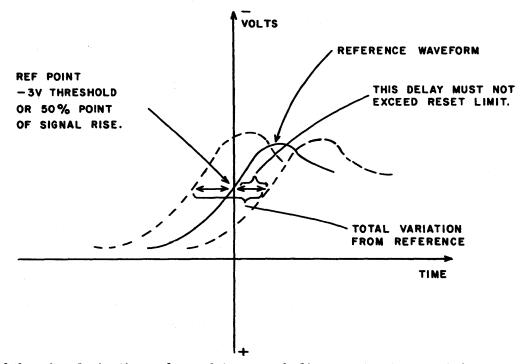

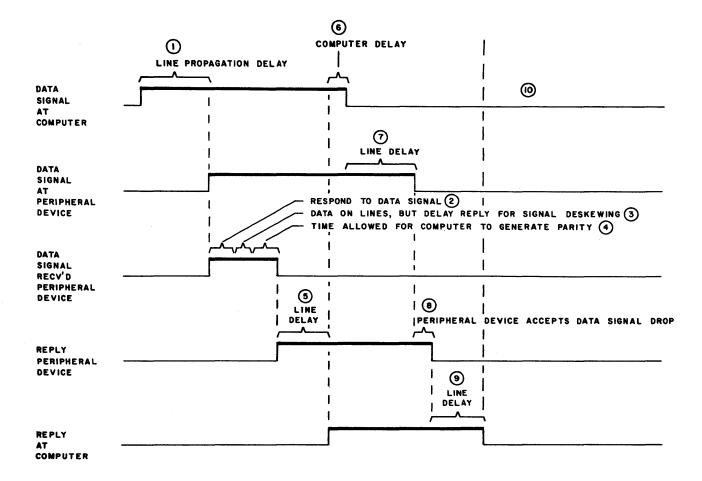

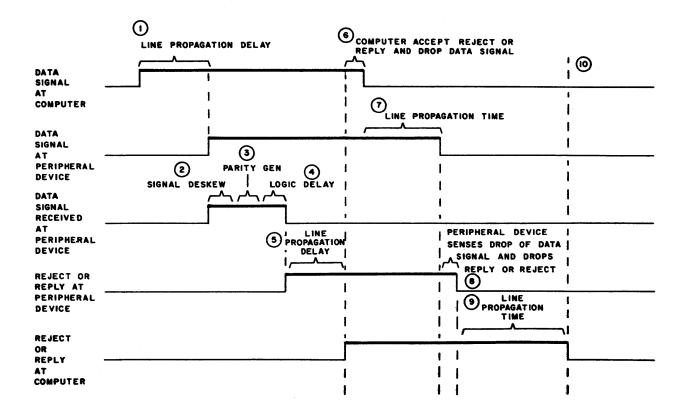

The signals transmitted during a read operation are as follows, and the timing sequence is shown in figure 1.

The read line comes up at the beginning of a read operation and remains up during the entire time of the operation. The Data signal is brought up when the channel is ready to accept data from the external equipment. When the external equipment has a word ready, it puts it on the data lines and sends the Reply signal. If the external equipment has reached an end of record condition, it sends the End of Record signal instead of the Reply, causing the read line to drop. The channel brings up the word mark line coincident with the Data signal during the transfer of the final byte.

#### WRITE

The signals transmitted during a write operation are as follows, and the timing sequence is shown in figure 1.

2

Figure l.

Signal Timing

ω

The write line comes up at the beginning of a write operation and remains up during the entire time of the operation. The Data signal is brought up when the channel has placed data on the data lines. When the external equipment has sampled the data lines, it returns a Reply signal. The channel brings up the word mark line coincident with the Data signal during the final byte.

#### ALL OPERATIONS

In response to a Connect, Function, or Data signal, the external equipment returns a Reply, Reject, or End of Record. The channel then acknowledges the Reply, Reject, or End of Record by dropping the Connect, Function or Data signal. This in turn causes the external equipment to drop its Reply, Reject or End of Record.

# TABLE 1

# **Bidirectional Signals**

| Signal     | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Bits  | <ul> <li>The lines which carry data are bidirectional and perform as follows:</li> <li>1. During a read (input) operation, data is transmitted from the external equipment to the channel.</li> <li>2. During a write (output) operation, data is transmitted from the channel to the external equipment.</li> <li>3. The connect code and function code are transmitted from the channel to the external equipment via the 12 data lines. In 24-bit and 48-bit interfaces, these codes are carried by the lower 12 lines (numbers 00 through 11).</li> </ul> |

| Parity Bit | A parity bit accompanies each 12 bits transmitted between<br>the channel and external equipment. Odd parity is used; thus<br>the total number of "1's" transmitted is always an odd number.<br>Parity bits accompany the connect code, the function code,<br>and each 12 bits of data.                                                                                                                                                                                                                                                                        |

### TABLE 2

# Signals from Data Channel to External Equipment

| Signal  | Definition                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connect | "1" signal sent to external equipment when 12-bit connect code<br>is available on data lines. If the equipment is available, it<br>connects and returns the Reply signal. If it is not available, it<br>returns the Reject signal. The Connect signal and code drop<br>when the external equipment returns the Reply or Reject.                                                                                         |

|         | A data channel may have a maximum of eight external equipments<br>attached to its set of I/O cables. The 12-bit connect code and the<br>Connect signal are received by all eight equipments, but only one<br>equipment (the equipment number switch setting of which matches<br>the upper 3 bits of the connect code) will respond. (The other<br>equipments do not return Reject signals.)                             |

|         | No response is returned by any of the equipments if a parity<br>error exists on the connect code; however, the Transmission<br>Parity Error indicators on all equipments will light. After a<br>delay of 100 microseconds, the computation module generates its<br>own internal Reject.                                                                                                                                 |

|         | A connect code does not initiate any action, but merely selects an<br>external equipment. The upper 3 bits of the connect code select<br>one of the eight possible equipments attached to the data channel,<br>and the lower 9 bits specify the unit (if any) of that equipment                                                                                                                                         |

|         | A connect code matching its equipment number switch setting will<br>be accepted by the equipment if it is available, although it may be<br>in the Not Ready condition. The connect code will be Rejected<br>only if the equipment is already connected to or reserved by<br>another data channel, or is otherwise not available. The equipment<br>will, however, enable its status lines to the channel which attempted |

| Signal              | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connect<br>(Cont'd) | to connect, so that the reason for the Reject may be determined<br>using the Copy Status instruction. The status lines remain<br>enabled to that channel until it transmits another connect code to<br>any of its external equipments.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                     | Once an equipment is connected to a data channel, it remains<br>connected until the channel initiates a disconnect. Any connect code<br>which does not match its equipment number switch setting will<br>disconnect the equipment, including its status lines. The equip-<br>ment must be capable of recognizing the code and disconnecting<br>within 1 microsecond after receiving the Connect signal. When<br>being selected, the equipment must not return a Reply or Reject<br>earlier that 2 microseconds after receiving the Connect signal.<br>NOTE<br>In equipment designed after May 1, 1966, the lead-<br>ing edge of a Connect signal will simultaneously<br>clear all Transmission Parity Error conditions<br>existing in equipment attached to the data channel.<br>Parity is checked after the clear on the current |

|                     | connect code. This clearing has no affect on other<br>conditions, e.g. Interrupt in any equipment. Refer<br>to the appropriate Reference Manual for information<br>on specific peripheral equipment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Function            | "1" signal sent to external equipment when 12-bit function code<br>is available on data lines. If the connected equipment is capable<br>of executing the specified function at the time that it receives the<br>Function signal, it initiates the function and returns the Reply<br>signal. If the equipment cannot perform the function, it returns<br>the Reject signal. The Function signal and code drop when the<br>external equipment returns the Reply or Reject.<br>The 12-bit function code and Function signal are received by all the<br>equipments attached to the data channel, but only the connected                                                                                                                                                                                                               |

|                     | equipment will respond. If no equipment is connected, the Function<br>signal and code will be completely ignored. After a delay of 100<br>microseconds, the computation module generates its own internal<br>Reject.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# Signals from Data Channel to External Equipment

| Signal               | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function<br>(Cont'd) | The specified function will not be performed if a parity error<br>exists on the function code; however, a Parity Error signal is<br>returned by the connected equipment. Also, the Transmission<br>Parity Error indicator on the connected equipment will light.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      | Once a function code is accepted, all other function codes will be<br>locked out until the first one is acted upon. An equipment does<br>not hold or stack up the function codes; a Reply or Reject is<br>returned immediately. If a second function code is received<br>which specifies the same function as the previous function code,<br>the second function code will be rejected unless the function can<br>immediately be performed a second time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Channel<br>Busy      | Static "1" signal sent to external equipment while data channel<br>is active during a read or write operation. The Channel Busy<br>signal becomes "1" immediately when the computation module<br>initiates the read or write operation and remains up until the<br>operation is finished and no further chaining is specified. It does<br>not drop between blocks of data in a chain, nor does it drop when an<br>End of Record signal is received unless the End of Record<br>actually terminates the operation.<br>The connected equipment immediately becomes Busy (status<br>response bit 01) when the channel busy line goes to "1", unless<br>it is already Busy or is Not Ready. If the equipment is already<br>Busy finishing a previous operation, it remains Busy and begins<br>the new operation as soon as possible. The equipment does not<br>become Busy if it is Not Ready; however, if the equipment be-<br>comes Ready while the Channel Busy signal is up, the equipment<br>will become Busy. |

| Signal              | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read                | Static "1" signal directing the connected equipment to begin<br>reading information from its storage medium, and to continue<br>as long as the Read signal is present. The read operation always<br>starts at the beginning of a record. If the Read signal drops<br>before the complete record is read, data transmission stops but<br>the external equipment continues its action until the end of re-<br>cord is reached. If the Read signal drops and comes back up<br>within a record, data transmission stops and does not begin<br>again until the beginning of the next record |

| Write               | Static "1" signal directing the connected equipment to begin<br>writing information into its storage medium, and to continue as<br>long as the Write signal is present. The write operation always<br>starts at the beginning of a record. Each time the Write signal<br>drops, the external equipment automatically ends the record.                                                                                                                                                                                                                                                  |

| Master<br>Clear     | "1" signal from computation module which returns data channel<br>and external equipment to zero initial conditions and disconnects<br>external equipment.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Data<br>Signal      | "1" signal used during read and write operations. Data signal<br>drops when Reply (or End of Record) is received from external<br>equipment. 1) During a read operation, the Data signal indicates<br>that the channel is ready to accept data from the external equip-<br>ment. 2) During a write operation, the Data signal indicates<br>that the channel has placed output data on the data lines.                                                                                                                                                                                  |

| Computer<br>Running | Static "1" when computer is operating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Signal                               | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Negate BCD<br>Conversion             | Static "1" signal which indicates that the computation module<br>is operating in the 1604 mode. 1) During a read operation,<br>this signal directs the external equipment to not convert BCD<br>codes from external to internal. 2) During a write operation,<br>this signal directs the external equipment to not convert BCD<br>codes from internal to external.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Suppress<br>Assembly/<br>Disassembly | Many peripheral equipments handle data in the form of 6-bit<br>bytes. These equipments and their controllers contain assembly/<br>disassembly logic as required to convert between the 12-bit<br>word length of the standard data channel and the 6-bit capabil-<br>ity of the equipment. Normally, during a Read (input) opera-<br>tion, two 6-bit bytes are assembled into a 12-bit word; during<br>a Write (output) operation, the opposite occurs.<br>A "1" signal on the Suppress Assembly/Disassembly line<br>prevents this conversion from occurring. This signal directs<br>the equipment to utilize only the lower 6 bits (bits 00 - 05) of<br>the 12-bit word. During a Read operation, bits 06-11 will be<br>"0's"; during a Write operation, any data in bits 06-11 will<br>not be used.<br>Any equipment or controller which does not normally perform<br>12-bit/6-bit assembly and disassembly will ignore the Suppress<br>Assembly/Disassembly signal.<br>The Suppress Assembly/Disassembly signal comes up simul-<br>taneously with the Read or Write signal and drops when the<br>Read or Write signal drops. |

| Signal                                               | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sample<br>Status Time<br>(A special<br>signal)*      | A "1" signal sent to the external equipment when the status sense<br>lines have been enabled. The signal is used by the external<br>equipment to clear specific status FF's. **                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Word<br>Mark                                         | <ul> <li>A "1" signal sent to external equipment together with certain of the Data Signals on both Read and Write operations. The Word Mark signal comes up 0.1 microsecond in advance of the Data Signal, and remains up for the duration of the Data Signal.</li> <li>The Word Mark signal identifies the low-order byte of every addressed word, as follows: <ol> <li>If the I/O operation is computer word addressed, the Word Mark will accompany the Data Signal for the final byte (bits 11 - 00) of the computer word.</li> </ol> </li> <li>If the I/O operation is byte addressed or character addressed, the Word Mark will accompany every Data Signal because every Data Signal controls the transmission of an entire addressed word.</li> </ul> |

| Clear<br>External<br>Interrupt,<br>Special<br>Signal | A "1" signal sent to the source of an Interrupt external to the<br>computer system, directing that external source to drop its<br>Interrupt signal. This condition does not apply to standard<br>peripheral equipments, but has application on special real-time<br>devices. (This signal can be generated only by the 3100 and 3200<br>computers.)                                                                                                                                                                                                                                                                                                                                                                                                           |

\* Generated by 3100, 3200, 3300 and 3500 Computer Systems only.

\*\* Not used by all peripherals; refer to individual equipments to determine if the signal is used, and which status FF's are affected.

# TABLE 3

| Signal           | Definition                                                                                                                                                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reply            | "1" signal produced by external equipment in response to a Connect,<br>Function, or Data signal. Signal drops when Connect, Function, or<br>Data signal drops.                                                                              |

|                  | 1. If connection can be made when Connect signal is received, external equipment connects and returns a Reply.                                                                                                                              |

| 4                | 2. If specified function can be performed when Function signal<br>is received, external equipment initiates function and<br>returns a Reply.                                                                                                |

|                  | 3. During a read operation, external equipment sends a Reply<br>as soon as it has placed data on the data lines in response to<br>the Data signal.                                                                                          |

|                  | During a write operation, external equipment sends a Reply<br>as soon as it samples the data lines in response to the Data<br>signal.                                                                                                       |

|                  | (If end of record is reached during a read operation, the Reply is<br>not returned in response to the Data signal. Instead, the external<br>equipment transmits the End of Record signal.)                                                  |

| Reject           | "1" signal produced by external equipment in response to a<br>Connect or Function signal if the connection cannot be made or the<br>function cannot be performed at the time that the external equipment<br>receives the respective signal. |

| End of<br>Record | "1" signal produced (instead of Reply) in response to the next<br>Data signal following the end of every record during a read<br>operation. The End of Record signal drops when the Data signal<br>drops.                                   |

# TABLE 3 (Cont'd)Signals from External Equipment to Data Channel

| Signal                       | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| End of<br>Record<br>(Cont'd) | If the Read signal drops before the end of record is reached, th<br>End of Record signal is not sent because none of the remaining<br>data in the record is transmitted, although the external equip-<br>ment continues its action until the end of record is reached.<br>(This applies even though the Read signal may have dropped and<br>come back up again within a record. See definition for Read signal<br>Records of data written on magnetic tape are separated by blan<br>spaces called inter-record gaps. In the case of punched cards,                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                              | each card is a record.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Parity<br>Error              | <ul> <li>each card is a record.</li> <li>"1" signal produced if data channel does not send an odd number of "1's" in 12 bits plus parity bit. (A parity bit accompanies each 12 bits; the 24-bit channel sends 2 parity bits and the 48-bit channel sends 4 parity bits. The external equipment checks each 12-bit portion separately and if there are any errors, it sends th Parity Error signal.) A transmission Parity Error condition can be cleared by a Master Clear signal.</li> <li>NOTE In equipment designed after May 1, 1966, a Transmission Parity Error condition can be cleared by a Connect operation. (See definition of Connect signal.) The following events occur when a parity error is detected. 1. Parity Error on Connect Code a. No equipment will connect. b. Any connected equipment will disconnect. c. No equipment returns a Reply or Reject.</li></ul> |  |  |  |

|                              | <ul> <li>d. No equipment returns a Parity Error signal.</li> <li>e. The Transmission Parity Error indicators on all<br/>equipments attached to the data channel will light.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                              | <ul> <li>2. Parity Error on Function Code <ul> <li>a. Nothing happens if no equipment is connected.</li> <li>b. If an equipment is connected, the following occurs: <ol> <li>1) It returns a Parity Error signal.</li> <li>2) Its Transmission Parity Error indicator will light.</li> </ol> </li> </ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

.

| Signal                      | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parity<br>Error<br>(Cont'd) | <ul> <li>3) It does not return a Reply or Reject.</li> <li>4) It does not perform the function.</li> <li>2 Parity Error on Data during Write Operation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                             | <ul> <li>3. Parity Error on Data during Write Operation <ul> <li>a. Nothing happens if no equipment is connected</li> <li>b. If an equipment is connected, the following occurs: <ol> <li>1) It returns a Parity Error signal.</li> <li>2) Its Transmission Parity Error indicator will light.</li> <li>3) It uses the data.</li> <li>4) It returns a Reply.</li> </ol> </li> </ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Status<br>Bits              | 4) It returns a Reply. The external equipment indicates its operating conditions by placing information on the 12 status lines. Each equipment has its own particular set of status response codes, some of which are unique to that equipment. Several status indications are normally common to all equipments, however, and occupy the same bit positions in the status response codes for all equipments. These are: <u>Ready</u> , Bit 00 = "1" An equipment is Ready if, when properly connected, a Read or Write signal can initiate a read or write operation. An equipment is Not Ready if, when properly connected, a Read or Write signal can initiate a read or write operation. Once Ready, an equipment remains continually Ready until operation is no longer possible; it then becomes Not Ready. An equipment cannot become Not Ready while it is actually transferring information; information transfer must first be halted. |  |  |

### TABLE 3 (Cont'd) Signals from External Equipment to Data Channel

Signals

(Cont'd)

Definition Status Bits Any equipment which requires manual intervention in its normal operation (such as loading tape, cards, paper, etc.) is provided

with switches to put it in either a manual mode or a computer controlled mode. When in the manual mode, the equipment is Not Ready. An equipment that has become Not Ready because of the need for manual intervention automatically goes into the manual mode. It becomes Ready again only after it has been attended to and manually switched back into the computer controlled mode. Busy, Bit 01 = "1" An equipment is Busy when it is in operation. The equipment becomes Busy immediately upon initiation of the read or write operation. Normally, an equipment remains Busy until it has finished all activity and is ready to perform another operation; it then becomes Not Busy. However, an equipment will become Not Busy if a condition arises due to which the equipment can no longer continue the operation. (An example of such a condition is becoming Not Ready because of running out of cards, paper, etc. An equipment cannot be Busy if it is Not Ready.) Error, Bit 10 = "1" This signal indicates information errors produced and detected

by the external equipment. It does not indicate parity errors on information received from the data channel; the parity error line is reserved for this. It is not an indication of malfunction such as paper tearing or printed circuit card failure.

If a read or write operation includes more than one record, the error bit is not cleared between records, but will indicate an error anywhere in the operation.

| Signal                  | Definition                                                           |

|-------------------------|----------------------------------------------------------------------|

| Status Bits<br>(Cont'd) | The error indication is cleared by beginning a new operation.        |

|                         | Reserved, Bit 11 = "1"                                               |

|                         | This bit is used by multi-channel peripheral equipment to            |

|                         | indicate that the equipment is reserved by one of the data           |

|                         | channels to which it is attached. Once a multi-channel equip-        |

|                         | ment has been connected by a data channel, it remains reserved       |

|                         | by that channel even though the operation may terminate, the         |

|                         | equipment may become Not Busy, and/or the channel may connect        |

|                         | another equipment. No other data channel can communicate with        |

|                         | the equipment until the first data channel releases the reservation. |

|                         | This may be done using the Master Clear facility, the Clear          |

|                         | Channel instruction, or by issuing the appropriate function code.    |

| Status Bits             | All equipment other than Magnetic Tape Controllers use status bits   |

| 7,8,&9                  | 7, 8, and 9 to indicate that the equipment has reached a certain     |

|                         | pre-selected Interrupt condition and is producing an Interrupt       |

|                         | signal because of it. Magnetic Tape Controllers, however, use        |

|                         | status bits 7, 8, and 9 for other purposes. See below.               |

|                         | All Equipment (except Magnetic Tape Controllers):                    |

|                         | Bit 07 = "1"                                                         |

|                         | Equipment has Interrupted on Ready and Not Busy.                     |

|                         | Bit 08 = "1"                                                         |

|                         | Equipment has Interrupted on End of Operation                        |

|                         | Bit 09 = "1"                                                         |

|                         | Equipment has Interrupted on Abnormal End of Operation               |

|                         | Magnetic Tape Controllers, only:                                     |

|                         | 800 BPI, Bit 07 = "1"                                                |

|                         | The equipment is set to operate at a density of 800 bits per inch.   |

| Signal                               | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status Bits<br>7, 8, & 9<br>(Cont'd) | Lost Data, Bit 08 = "1"<br>This condition occurs if the Data signal from the data channel<br>is not present when the equipment is ready to send data during<br>a Read operation or to receive data during a Write operation.<br>On a Read operation, reading continues to the end of the record;<br>on a Write operation, tape motion stops immediately. Further<br>Read or Write operations are impossible until the Lost Data<br>condition is cleared by a new function. Any legal<br>function code will clear the Lost Data condition. (The Lost Data<br>condition can be cleared by a Master Clear, but this also dis-<br>connects the equipment.)<br>End of Operation, Bit 09 = "1"<br>This bit goes to a "0" whenever tape motion (except rewind) is<br>initiated. It changes from "0" to "1" when an end of record is<br>detected. Errors may be checked as soon as End of Operation<br>status exists after Read, Write, Write File Mark, or Skip Bad<br>Spot operations, even though tape is still in motion.<br>During non-stop Read or Write data operations, new Read or Write<br>operations may be initiated whenever End of Operation status<br>exists from the previous Read or Write operation. Although errors<br>may be checked when End of Operation occurs after Skip Bad Spot<br>or Write File Mark operations, no new operation may be initiated<br>until Not Busy status exists.<br>During the execution of all select function instructions (except<br>Write File Mark or Skip Bad Spot), End of Operation status is<br>meaningless. |

| Signal             | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt<br>Lines | A "1" signal on an interrupt line indicates that an external<br>equipment has reached a predetermined condition. A data<br>channel may communicate with a maximum of eight equipments,<br>and each equipment uses one interrupt line. An interrupt signal<br>may be dropped by reselecting the same selection, or by clearing<br>the selection.                                                                                                                                                                                                                                                                           |

|                    | Each equipment has a set of conditions upon which it will interrupt,<br>if selected. Some of the interruptable conditions are common to<br>all equipment and are described below.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                    | Interrupt on End of Operation<br>With this selected, Interrupt will occur the next time an operation<br>ends. The operation may be in progress at the time of the<br>selection or it may be initiated later. Interrupt will not occur<br>from an operation which has ended before the selection is made.<br>Interrupt on end of operation can occur both at the end of an<br>I/O read or write operation, and at the end of an operation<br>specified by a function code. If a function code is accepted to<br>initiate an operation that is already completed, an end of operation<br>Interrupt will occur, if selected. |

|                    | Normally, the end of operation Interrupt for a read or write<br>operation will occur when all data has been transferred, the<br>Channel Busy signal has dropped, reading or writing of the<br>current record is completed, and all error checking is com-<br>pleted. In some cases, this Interrupt may occur before the<br>equipment becomes Not Busy. If for any reason (such as be-<br>coming Not Ready) the equipment is unable to continue the<br>activity, the equipment will end its operation and Interrupt will<br>occur.                                                                                         |

# TABLE 3 (Cont'd)Signals from External Equipment to Data Channel

# Signals Definition Interrupt Lines Interrupt on Abnormal End of Operation This directs the external equipment to Interrupt if an operation (Cont'd) ends under circumstances other than normal, such as becoming Not Ready or detecting an error. The operation may be in progress at the time of the selection or it may be initiated later. Interrupt will not occur from an operation which has ended before the selection is made, even though it may have ended under abnormal circumstances. If the equipment has become Not Ready before the Interrupt is selected, however, an attempt to initiate another operation after the selection is made will cause the equipment to Interrupt immediately. The equipment does not send the Interrupt signal while information is being transferred. All activity and information transfers are stopped at the most consistent point (such as at the end of the current record); then the Interrupt occurs. Automatic stopping on an error takes place only when this Interrupt is selected. Interrupt on Ready, or Interrupt on Ready and Not Busy The purpose of this Interrupt is to indicate that the external equipment is ready to start a new operation. It is often used to indicate the completion of any manual intervention. The Negate Channel Interrupt Lockout is a signal produced by an Negate Channel equipment to accompany its Interrupt signal if the Interrupt has Interrupt occurred because of an Abnormal End of Operation which prevented Lockout the equipment from completing a Read or Write operation. The Channel Interrupt Lockout condition is established by the computer to block the receipt of Interrupt signals from the equipments cabled to that data channel. The Negate Channel Interrupt Lockout signal, when generated by an external equipment to accompany its

# TABLE 3 (Cont'd)Signal from External Equipment to Data Channel

| Signal                                                | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Negate<br>Channel<br>Interrupt<br>Lockout<br>(Cont'd) | Interrupt signal, will override the Lockout condition and will allow<br>the channel to notify the computer that an Interrupt exists. All<br>Interrupts present at the channel are then processed; the order of<br>processing is not necessarily dependent upon the order received<br>but may be determined by things such as program priority or a<br>fixed-cycle scanner. The Negate Channel Interrupt Lockout signa<br>drops when the Interrupt which it accompanied is processed; the<br>channel then reverts back to the Interrupt Lockout condition.<br>The purpose of the Negate Channel Interrupt Lockout signal is to<br>prevent a possible "hang up" by the data channel if the computer<br>had previously placed the channel in the Lockout condition and was<br>waiting for the completion of the Read or Write operation. In this<br>state, the channel could not accept the Interrupt on Abnormal End<br>of Operation signal from the equipment, but neither could it com-<br>plete the Read or Write operation. |  |  |  |

| Reverse<br>Assembly                                   | This signal directs the data channel to reverse the order of bytepositions when assembling a 48-bit word from data received fromthe equipment. The bytes are assembled as follows, using thestandard 12-bit channel as an example:NormalReverseByte 1Bits 47 - 36Byte 2Bits 35 - 24Byte 3Bits 23 - 12Byte 4Bits 11 - 00Bits 47 - 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 24-Bit<br>Device<br>Present &<br>Connected            | Certain 3100, 3200, and 3300 computer data channels can com-<br>municate with both 12-bit and 24-bit I/O devices. The channels<br>provide 3 receptacles for the 3 cables used by 24-bit devices; and<br>a 12-bit device on this type of channel does not use the third cable.<br>The 24-Bit Device Present & Connected is a signal produced by<br>24-bit equipment enabling the data channel to check parity on the<br>upper 12 bits which are on the third cable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

A 3606 type 12-bit channel communicates with external equipment using 2 bidirectional 29-pair cables. Each 48-bit word is transmitted in the form of four 12-bit bytes, each of which is accompanied by a parity bit. The sequence of operation is shown in figure 1. The Word Mark signal accompanies the final 12-bit byte.

### TABLE 4

### Standard 12-bit Channel Interface

### CABLE A

### Data I/O Cable, Signal and Pin Assignments

| Pin (two used)        | Signal            |

|-----------------------|-------------------|

| A1-2                  | Data Bit 00       |

| A3-4                  | Data Bit 01       |

| A5-6                  | Data Bit 02       |

| A7-8                  | Data Bit 03       |

| A9-10                 | Data Bit 04       |

| B1-2                  | Data Bit 05       |

| B3-4                  | Data Bit 06       |

| B5-6                  | Data Bit 07       |

| B7-8                  | Data Bit 08       |

| B9-10                 | Data Bit 09       |

| C1-2                  | Data Bit 10       |

| C3-4                  | Data Bit 11       |

| C5-6                  | Parity Bit        |

| C7-8                  | Channel Busy      |

| C9-10                 | Reverse Assembly  |

| D1-2                  | Read              |

| D3-4                  | Write             |

| D5-6                  | Connect           |

| D7-8                  | Function          |

| D9-10                 | Data Signal       |

| E1-2                  | Reply             |

| E3-4                  | Reject            |

| E5-6                  | End of Record     |

| E7-8                  | Parity Error      |

| E9-10                 | (Unused)          |

| F1-2                  | Word Mark         |

| F3-4                  | Master Clear      |

| F5-6                  | (Unused)          |

| F7-8                  | (Unused)          |

| *F9-10 (not in cable) | Termination Power |

\*NOTE: The 29-pair cables terminate in 61-pin connectors. Pins F9-10 of each connector are used to provide power to the terminator assembly and do not connect to lines in the I/O cable.

### Standard 12-bit Channel Interface

### CABLE B

### Control I/O Cable, Signal and Pin Assignments

| Pin (two used)        | Signal                           |

|-----------------------|----------------------------------|

| A1-2                  | Status Bit 00                    |

| A3-4                  | Status Bit 01                    |

| A5-6                  | Status Bit 02                    |

| A7-8                  | Status Bit 03                    |

| A9-10                 | Status Bit 04                    |

| B1-2                  | Status Bit 05                    |

| B3-4                  | Status Bit 06                    |

| B5-6                  | Status Bit 07                    |

| B7-8                  | Status Bit 08                    |