CONTROL DATA

.

# CONTROL DATA® 3276-A communication terminal controller

**REFERENCE MANUAL**

March &, 1966 Ed Salter K. M. Lampert

3276 Manuals

Reference manuals for the 3276 Multiplexor are in short supply: single copies have been mailed to you and to John Henderson. IDP is in the process of revising this publication and is reluctant to print additional copies of the present version.

Users of this manual are sometimes confused by a barrage of equipment numbers which are not related to pricing manual numbers and descriptions. The 3276 is composed of the following units:

- 1 8165 Master Multiplexor {MUX}

- 2 Albb Input Slave MUX

- 2 8167 Output Slave MUX

The 321 Teletype Terminal Unit {TTU} is composed of the following units:

1 85X8 Low Speed Input Unit {LSIU}

ASX9 Low Speed Output Unit (LSOU)

The input/output units are selected to match the terminal equipment: ASDA LSIU's and ASDA LSOU's are used with five level teletype and ASDA LSIU's and ASDA LSOU's are used with eight level teletypes. Other terminal units are used with higher speed equipment.

K. M. Lampert

/dd

cc: John Henderson – File

CONTROL DATA

# **CONTROL DATA® 3276-A** communication terminal controller

**REFERENCE MANUAL**

Pub. No. 368 161 00

| Record of Revisions |                                       |  |  |  |

|---------------------|---------------------------------------|--|--|--|

| REVISION            | NOTES                                 |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     | · · · · · · · · · · · · · · · · · · · |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

|                     |                                       |  |  |  |

Address comments concerning this manual to:

Control Data Corporation Industrial Data Processing Div Technical Publications Section 9549 Penn Avenue So. Minneapolis, Minnesota 55431

# CONTENTS

### 3276-A COMMUNICATION TERMINAL CONTROLLER

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1 (3276-A)                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Controller Description<br>Performance<br>Physical Composition                                                                                                                                                                                                                                                                                                                                                                                      | 1 (3276-A)<br>1 (3276-A)<br>2 (3276-A)                                                                                                                                             |

| Individual Controller Units<br>8165-C Master MUX with Read Scanner<br>8165-B Master MUX<br>8166-E Input Slave Multiplexer (Input MUX)<br>8167-B Output Slave Multiplexer (Output MUX)<br>8167-C Output Slave Multiplexer (Output MUX)<br>8508-B and 8518 LSIUs<br>8509-B and 8519 LSOUs<br>IDP-111 Data Set Adapter<br>IDP-112 Data Set Adapter<br>IDP-113 Data Set Adapter<br>IDP-114 Data Set Adapter<br>I/O Cables<br>Three-Digit Model Numbers | 2 (3276-A)<br>2 (3276-A)<br>4 (3276-A)<br>5 (3276-A)<br>5 (3276-A)<br>5 (3276-A)<br>5 (3276-A)<br>6 (3276-A)<br>6 (3276-A)<br>6 (3276-A)<br>7 (3276-A)<br>7 (3276-A)<br>7 (3276-A) |

| FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                    |

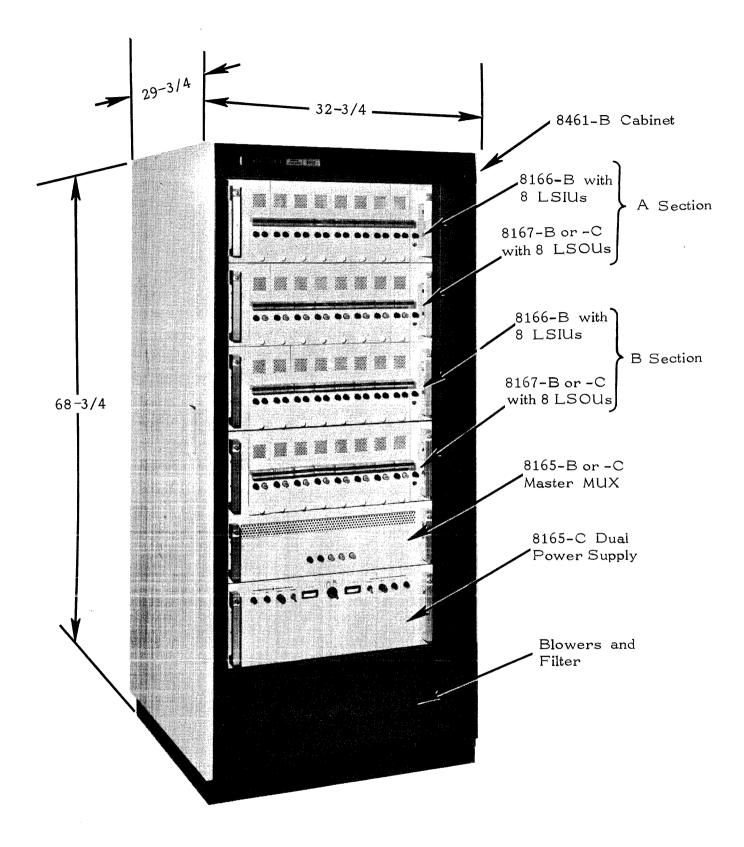

| 1 3276-A Communication Terminal Controller                                                                                                                                                                                                                                                                                                                                                                                                         | ii (3276-A)                                                                                                                                                                        |

| 2 Composition of 3276 Controller (typical example)                                                                                                                                                                                                                                                                                                                                                                                                 | 2 (3276-A)                                                                                                                                                                         |

| 3 I/O Signal Sequence - Computer Interface                                                                                                                                                                                                                                                                                                                                                                                                         | 9 (3276-A)                                                                                                                                                                         |

| TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                    |

| 1 3276-A Controller Components                                                                                                                                                                                                                                                                                                                                                                                                                     | 4 (3276-A)                                                                                                                                                                         |

| 2 Interface with 3000 Series Computer                                                                                                                                                                                                                                                                                                                                                                                                              | 10 (3276-A)                                                                                                                                                                        |

| 3 Computation Module of 3000 Series Computer<br>Control I/O Cable                                                                                                                                                                                                                                                                                                                                                                                  | 10 (3276-A)                                                                                                                                                                        |

| 4 I/O Interface Signals between Computer and MUX                                                                                                                                                                                                                                                                                                                                                                                                   | 11 (3276-A)                                                                                                                                                                        |

ii (3276-A)

#### 3276-A COMMUNICATION TERMINAL CONTROLLER

#### INTRODUCTION

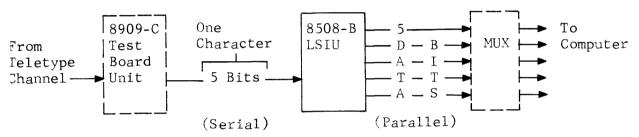

The role of the CONTROL DATA 3276-A Communication Terminal Controller (see figure 1) is that of a channelizing or circuit selector for the processing element of the CONTROL DATA 8050 System. It is a selector switch which connects, one at a time, all of the subscriber (remote, local, message assembly and off-line crypto) circuits terminated to the 8050 System. It interfaces the processor to each Teletype circuit on either a simplex, half-duplex or a full-duplex basis (whichever is required). Speed conversion from computer speeds to Teletype speeds is performed. The required serial-to-parallel conversion is provided by the Controller (serial on the lines parallel to the processor) and the required parallel-to-serial conversion (parallel from the processor, serial to the lines).

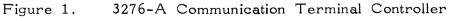

Each Controller can handle up to eight full-duplex DATA-PHONE lines or 16 full-duplex Teletype channels. For more than 16 channels more Controllers can be added to the system. More than one Teletype unit at different remote and/or local stations can be placed on each channel; thus, the system is flexible and expandable.

#### CONTROLLER DESCRIPTION

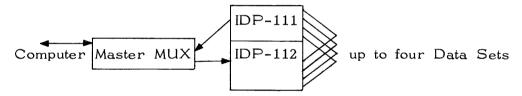

The Controller is a solid-state electronic device which regulates data transmission between a Control Data computation module and several communication channels. The Controller's position between the computation module and the communication channels is illustrated below.

The Controller is highly flexible and can handle up to 16 full-duplex Teletype lines or up to eight full-duplex, high-speed, voice-grade lines.

#### PERFORMANCE

The 3276-A Communication Terminal Controller:

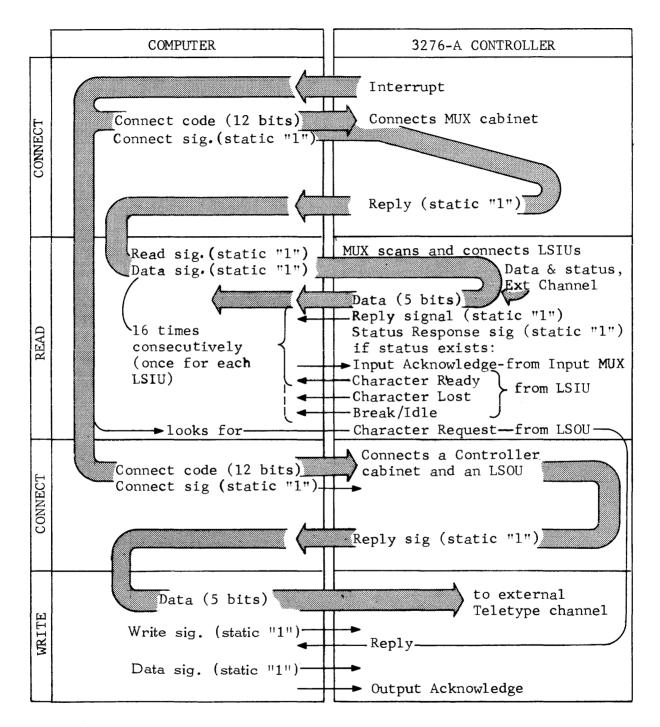

1. Interrupts the computer periodically to ask the computer to enter a Read/Write subroutine with the multiplexer (MUX).

- 2. Decodes the connect codes sent by the computer to the individual input/ output (I/O) units. For the Read Connect code the MUX scans the low-speed input units (LSIUs).

- 3. Converts the input serial characters (one bit at a time) to parallel characters (up to eight bits at a time) for the computer to read.

- 4. Serializes the parallel characters sent by the computer and transmits them, one bit at a time, to the external communication channels.

- 5. Connects the computer to external channels of various speeds.

- 6. Sends status response codes such as Character Ready, Character Request, Character Lost, Idle, or Break to the computer.

- 7. Distributes Read/Write data between the computer and the external communication lines.

#### PHYSICAL COMPOSITION

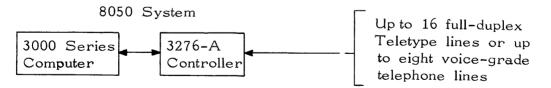

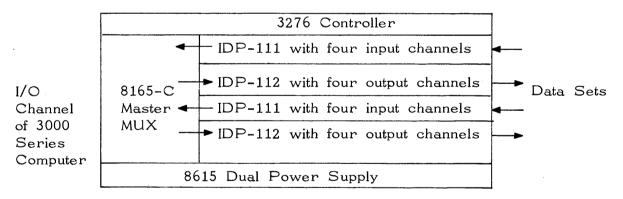

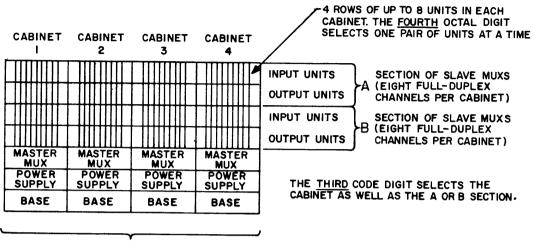

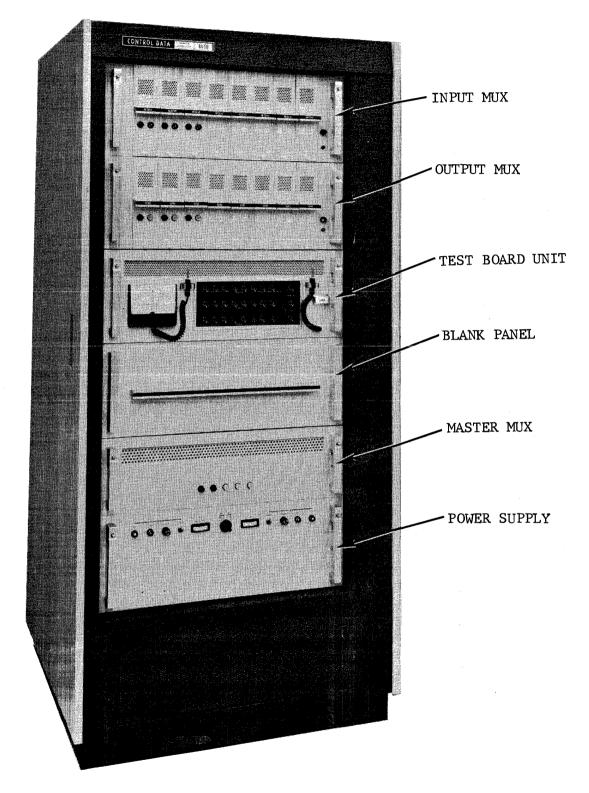

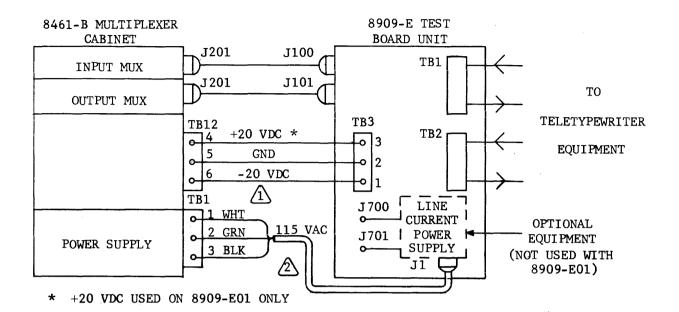

The 3276 Controller is modular in construction. The Master MUX, Slave MUXs, I/O units and power supply are drawer-type modules. The composition of the Controller is variable, due to the flexible arrangement of the modules (see figure 2).

#### INDIVIDUAL CONTROLLER UNITS

Table 1 lists the units which are modular parts of the Controller.

#### 8165-C MASTER MUX WITH READ SCANNER

The 8165-C Master MUX matches the interface of the computer, two slave input MUXs and two slave output MUXs. It generates and sends the channel Interrupt signal to the computer. The 8165-C decodes the connect code to select the A or B section slave MUX as well as each I/O unit. It also regulates the connect code and Read and Write Data signals all of which use the same lines. It sends a Reply signal to the computer when data or code is on the channel. It passes status response codes to the computer.

When the MUX is connected and a Read signal is present, the MUX automatically scans all 16 LSIUs for information. When a Write signal is present, the LSOUs are selected individually under computer control.

#### 2 (3276-A)

For Communication between Computer and Teletype Lines (five-level)

NOTE: For eight-level lines substitute these model numbers for the LSOUs and LSIUs; 8518 and 8519 . Future high-speed I/O units will fit into the 8166 and 8167 slaves MUXs.

For Communication between Computer and Voice-Grade Lines

NOTE: Other high-speed units can be substituted.

Figure 2. Composition of 3276-A Controller (typical examples)

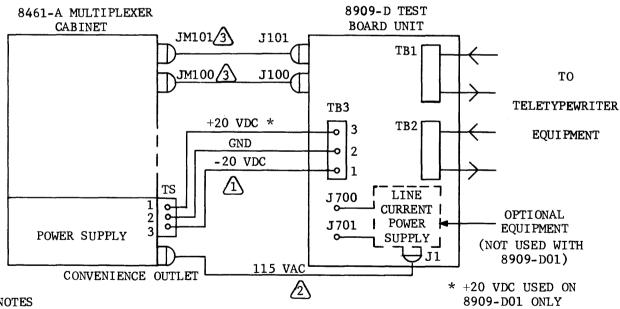

TABLE 1. 3276-A CONTROLLER COMPONENTS

| Cabinet<br>MUX<br>Drawers                                   | 8461-B Cabinet (including blower and wiring)<br>8165-B Master MUX (without read scanner)<br>8165-C Master MUX (with read scanner)<br>8166-B Input Slave MUX<br>8167-B Output Slave MUX<br>8167-C Output Slave MUX with start-motor delay |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low-Speed<br>Teletype<br>Terminals<br>used in<br>Slave MUXs | 8508-B LSIU (five bits)<br>8509-B LSOU (five bits)<br>8518 LSIU (up to eight bits)<br>8519 LSOU (up to eight bits)                                                                                                                       |

| High – Speed<br>Input/Output<br>Units used in<br>Slave MUXs | 8536 HSIU (up to eight bits)<br>8537 HSOU (up to eight bits)                                                                                                                                                                             |

| High-Speed<br>Communication<br>Adapters<br>(Drawers)        | IDP-111 Data Set Adapter (receive)<br>IDP-112 Data Set Adapter (send)<br>IDP-113 Data Set Adapter (receive)<br>IDP-114 Data Set Adapter (send)                                                                                           |

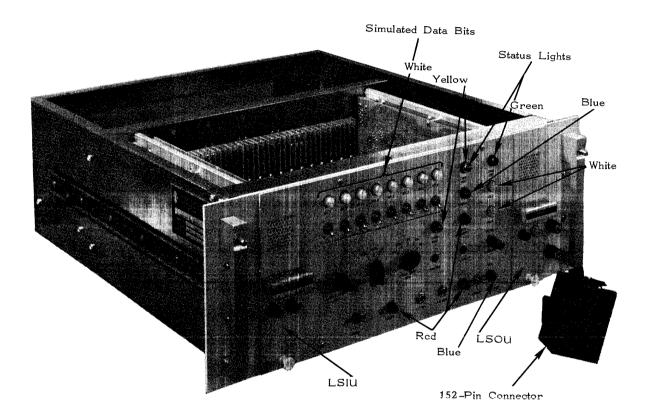

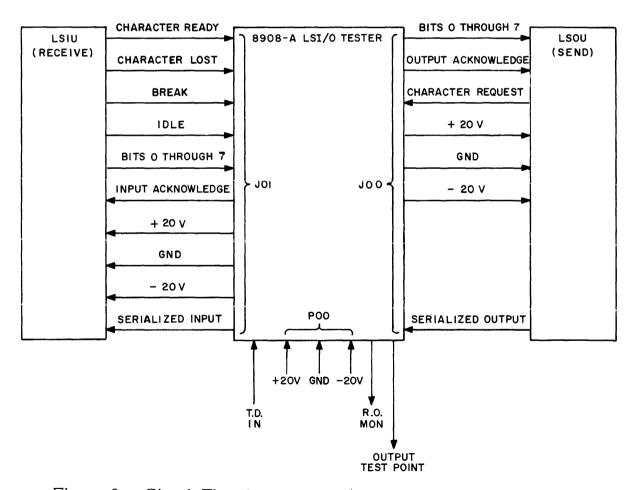

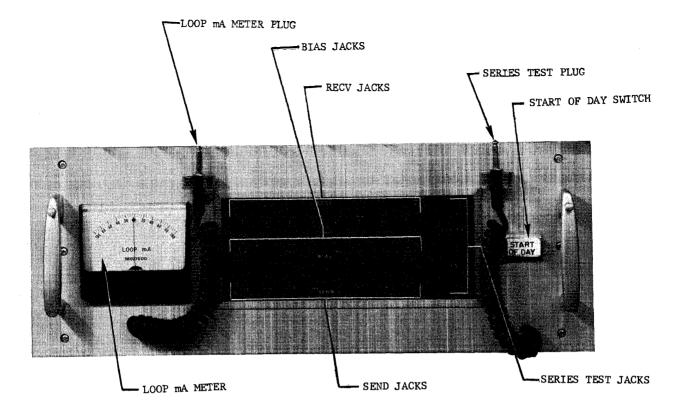

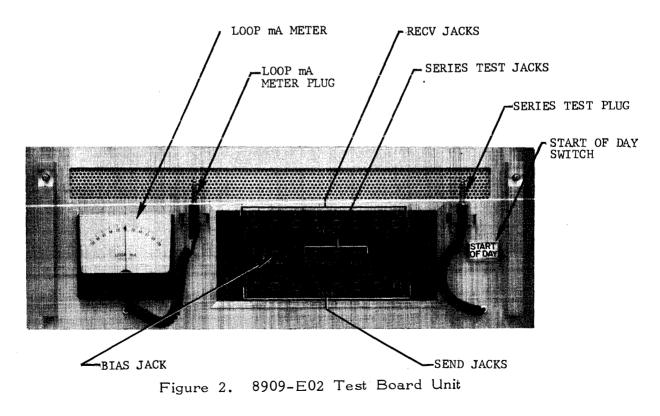

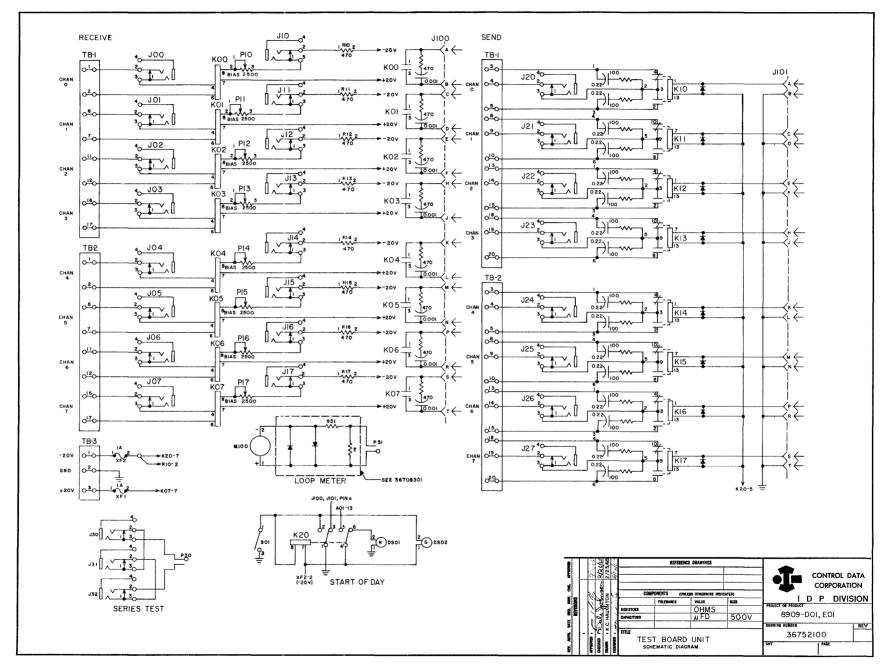

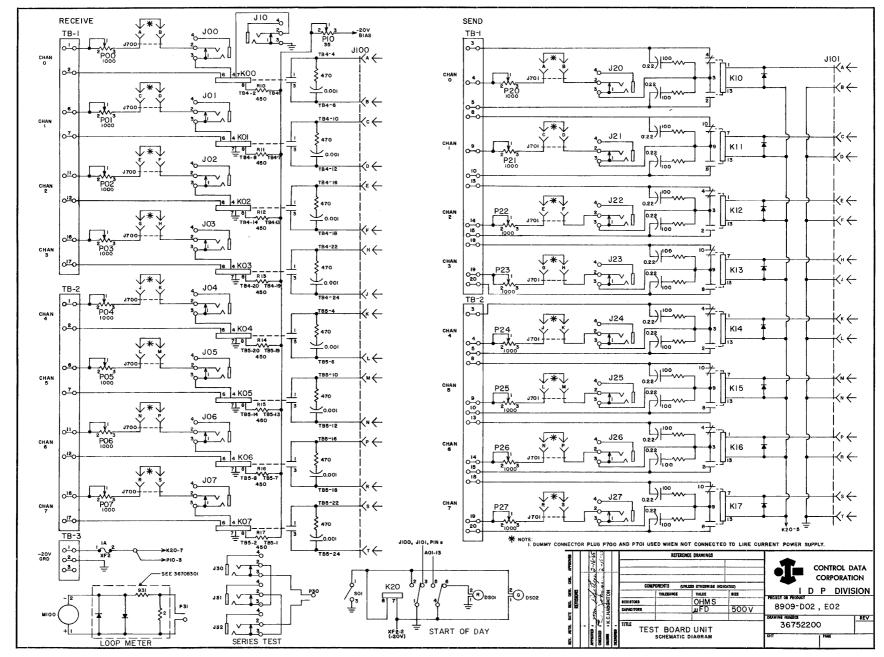

| Other<br>Drawer<br>Modules                                  | 8615-C Dual Power Supply (separate manual)<br>8908-E LSI/O Unit Tester<br>8909-E Test Board Unit                                                                                                                                         |

#### 8165-B MASTER MUX

The 8165-B Master MUX is similar to the 8165-C except that it does not initiate scanning of the input units. Scanning is accomplished by the computer or a separate scanning device. The MUX arrangement in the Controller is as follows:

|                     |                  | Section<br>A | 8166<br>MUX | ] <b></b> Up | to | eight | 8508 |  | LSIUs<br>HSIUs |

|---------------------|------------------|--------------|-------------|--------------|----|-------|------|--|----------------|

| Computer<br>Channel | 8165-B<br>Master |              | 8167<br>MUX | <b>↓</b> Up  | to | eight | 8509 |  | LSOUs<br>HSOUs |

|                     | мих              | Section<br>B | 8166<br>MUX | JeUp         | to | eight | 8508 |  | LSIUs<br>HSIUs |

|                     |                  |              | 8167<br>MUX | └──► Up      | to | eight | 8509 |  | LSOUs<br>HSOUs |

#### 8166-B INPUT SLAVE MULTIPLEXER (INPUT MUX)

The 8166-B Input MUX matches the interface of the 8165 (-B or -C) Master MUX and also of the 8508-B or 8518 LSIU. The 8166-B is basically a fanin unit which receives the decoded connect code from the 8165 Master MUX and selects the proper LSIU. It receives data from the connected LSIU and sends it to the computer via the 8165 Master MUX. There is space for two 8166-Bs in each Controller cabinet; one in section A, and one in section B. Each 8166-B can hold up to eight LSIUs.

#### 8167-B OUTPUT SLAVE MULTIPLEXER (OUTPUT MUX)

The 8167-B Output MUX matches the interface of the 8165 (-B or -C) Master MUX and also of the 8509-B or 8519 LSOU. It receives the decoded connect code from the 8165 Master MUX and selects the proper LSOU. The 8167 enables data to enter the connected LSOU. There is space for two 8167s in each 3276-A MUX cabinet; one in section A, and one in section B.

#### 8167-C OUTPUT SLAVE MULTIPLEXER (OUTPUT MUX)

The 8167-C Output MUX is similar to the 8167-B except that it contains a 4second motor-start delay circuit for each channel. This circuit allows remote teletypewriter motors to reach operating speed before receiving transmission.

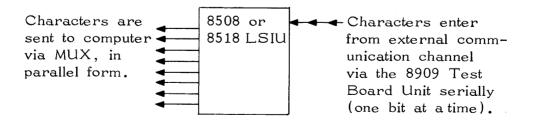

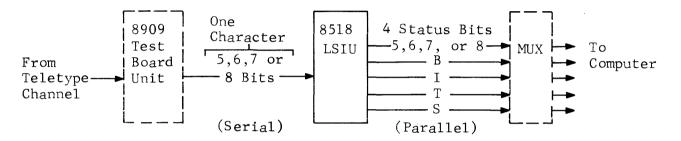

#### 8508-B AND 8518 LSIU(S)

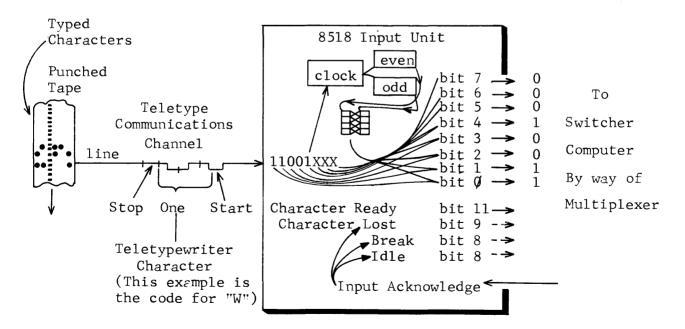

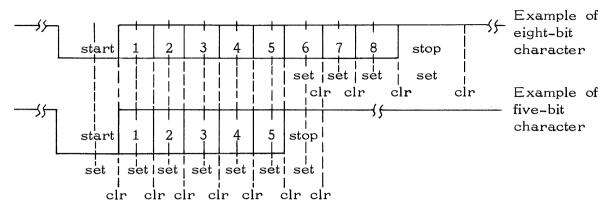

The 8508-B five-bit LSIU converts the incoming serial Teletype characters to parallel form for the computer to read (see the example following this paragraph). The 8518 LSIU differs from the 8508-B in that it can be adjusted to handle up to eight-bit characters.

5 (3276-A)

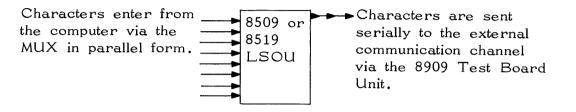

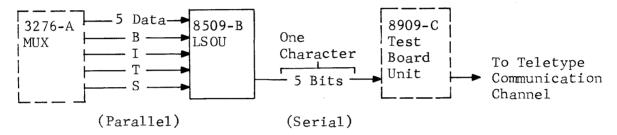

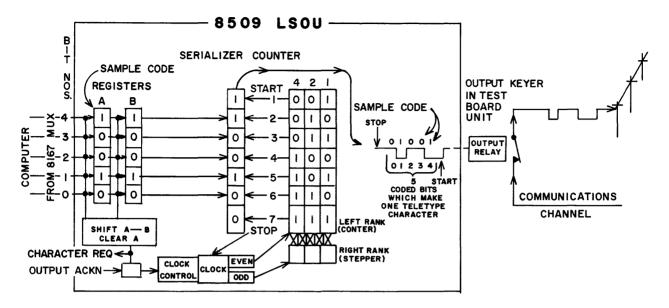

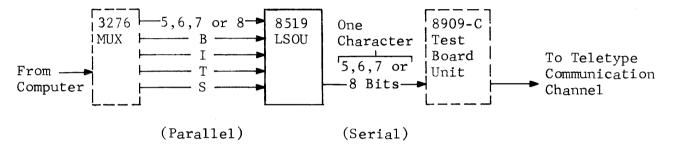

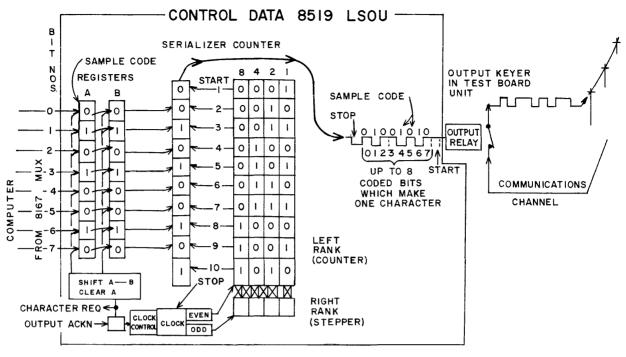

8509-B AND 8519 LSOU(S)

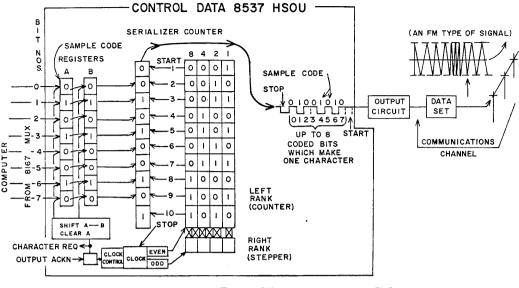

The 8509-B five-bit LSOU serializes the characters which come from the computer in parallel form. The 8519 LSOU can assemble up to eight-bit characters. The LSOUs function as shown in the following example:

#### IDP-111 DATA SET ADAPTER

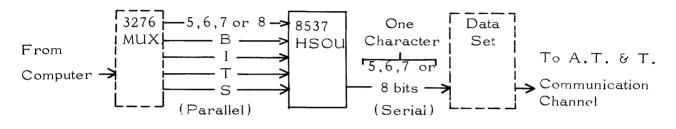

The IDP-111 Data Set Adapter is a high-speed input multiplexing unit which matches the interface of the computer (via the Master MUX) with that of up to four 202-C1 Data Sets as shown in the example.

IDP-112 DATA SET ADAPTER

The IDP-112 Data Set Adapter is a high-speed output multiplexing unit which matches the interface of the computer (via the Master MUX) with that of up to four data sets for communication on voice-grade lines.

#### IDP-113 DATA SET ADAPTER

The IDP-113 Data Set Adapter is a high-speed input multiplexing unit which matches the interface of the computer (via the Master MUX) with that of up to four data sets. Its main purpose is to facilitate communication between an 8050 System and certain IBM devices. The IDP-113 converts characters from serial to parallel form as shown in the example.

Remote Data Set - IBM equipment

6 (3276-A)

#### IDP-114 DATA SET ADAPTER

The IDP-114 Data Set Adapter is a high-speed output multiplexing unit which matches four data sets to the computer interface. The IDP-114 facilitates communication to IBM devices from the 8050 System. It converts characters from parallel to serial form.

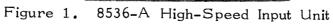

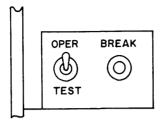

#### 8536-A HIGH-SPEED INPUT UNIT

The 8536-A High-Speed Input Unit (HSIU) is similar to the 8518 LSIU except that it is adaptable to higher communication speeds (up to 1200 words per minute). The 8536-A HSIU receives data serially, assembles each character, and sends it in parallel form to one of eight channels in an 8166 IMUX.

#### 8537-A HIGH-SPEED OUTPUT UNIT

The 8537-A High-Speed Output Unit (HSOU) is similar to the 8519 LSOU except that it is adaptable to higher communication speeds (up to 1200 words per minute). The 8537-A HSOU receives parallel-bit characters from the MUX, and sends the bits serially to the data set.

#### I/O CABLES

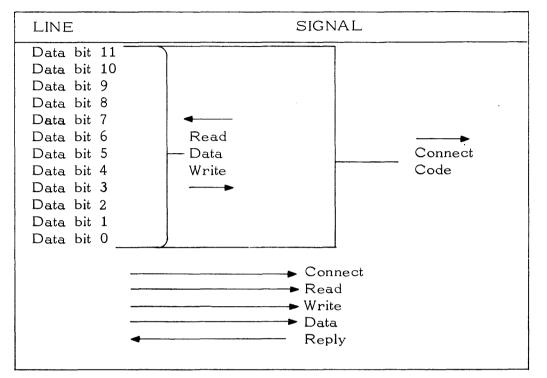

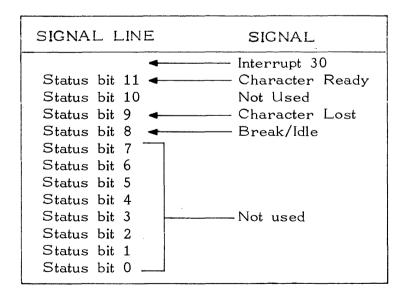

The computation module of the computer communicates with the 3276 Controller through a standard 12-bit channel interface on two bidirectional cables. Each cable contains 29 transmission lines. Each transmission line consists of two twisted pairs of 24-gauge conductors.

#### Data I/O Cable

The data I/O cable (see table 2) uses its 12 data lines to carry the 12-bit connect code as well as data (both Read and Write). This cable also carries signals such as Connect, Data, Read, Write and Reply.

#### Status I/O Cable

The status I/O cable (see table 3) uses three status response lines and one interrupt line. Figure 3 describes each signal sent between the computer and the MUX. Table 4 shows graphically the sequence of signals between the computer and the MUX.

#### THREE-DIGIT MODEL NUMBERS

The three-digit numbers listed in the table below represent combinations and choices of input/output units that fit into the slave-MUX drawers of the 3276 Communication Terminal Controller.

7 (3276–A)

At the time of this printing only the 321 and 323 Units are available. The other units will be covered in supplements to this manual whenever the units become available.

| 3-DIGIT<br>NUMBER                  | MODEL CONFIGURATION                                                                                                                           | COMPATIBLE<br>DATA SET |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 311<br>312                         | 8546 + 8547 High–Speed I/O Units*<br>311 + Automatic Dialer                                                                                   | 201<br>201 + 801       |

| 313                                | 8536 + 8537 High-Speed I/O Units**                                                                                                            | 103                    |

| 314                                | + 8538 + 8539 Data Set Control Units<br>313 + Automatic Dialer                                                                                | 103 + 801              |

| 315<br>316                         | High-Speed Data (750 wpm) Output Unit<br>High-Speed Data (750 wpm) Input Unit                                                                 | 402C<br>402D           |

| 317                                | 8536 + 8537 High-Speed I/O Units**                                                                                                            | 202                    |

| 318                                | + 8538 + 8539 Data Set Control Units<br>317 + Automatic Dialer                                                                                | 202 + 801              |

| TELETYPE<br>WRITER LIN<br>TERMINAL |                                                                                                                                               |                        |

| 321<br>323                         | 8508 + 8509 or 8518 + 8519 LSI/Os<br>8508 or 8509 or 8518 or 8519 LSI/Os                                                                      |                        |

| TELEX LIN<br>TERMINALS             |                                                                                                                                               |                        |

| 324<br>325                         | 8548 + 8549 or 8558 + 8559***<br>8548 or 8549 or 8558 or 8559                                                                                 |                        |

| * 8547 (+ 81                       | .66 MUX is similar in operation to interim 1<br>.67 OMUX) is similar in operation to interin<br>538 + 8166) is similar in operation to interi | n model IDP 114        |

| ** 8537 (+ 85<br>*** 8548 is sir   | 539 + 8167) is similar in operation to interi<br>nilar in operation to an 8508 + Telex senso<br>nilar in operation to an 8509 + Telex senso   | m model IDP 112<br>pr  |

| *** 8558 is sir                    | nilar in operation to an 8518 + Telex sense                                                                                                   |                        |

8559 is similar in operation to an 8519 + Telex sensor

\*\*\*

8 (3276-A)

Figure 3. I/O Signal Sequence - Computer Interface

TABLE 2. INTERFACE WITH 3000 SERIES COMPUTER

TABLE 3. COMPUTATION MODULE OF 3000 SERIES COMPUTER CONTROL I/O CABLE

10 (3276-A)

# TABLE 4. I/O INTERFACE SIGNALS BETWEEN COMPUTER AND MUX

|                         | Bidirectional Signals                                                                                                                                                                        |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Data Lines              | s The 12 lines which carry data are bidirectional, and perform as follows:                                                                                                                   |  |  |  |  |

|                         | 1. In a Read (input) operation, data is transmitted from MUX to the computer.                                                                                                                |  |  |  |  |

|                         | 2. In a Write (output) operation, data is transmitted from the computer to the MUX.                                                                                                          |  |  |  |  |

|                         | 3. The connect code is transmitted from the computer to the MUX via the 12 data lines.                                                                                                       |  |  |  |  |

|                         | Computer to MUX Signals                                                                                                                                                                      |  |  |  |  |

| Connect                 | Status "1" signal sent to the MUX when 12-bit connect code is available on data lines. Signal drops when MUX returns Reply.                                                                  |  |  |  |  |

| Read                    | Static "1" signal produced by computer during a Read operation.                                                                                                                              |  |  |  |  |

| Write                   | Static "1" signal produced by computer during a Write operation.                                                                                                                             |  |  |  |  |

| Data<br>Signal          | Static "1" signal sent to external equipment during both Read<br>and Write operations. Signal drops conditionally when Reply is<br>received from the MUX.                                    |  |  |  |  |

|                         | 1. In a Read operation, Data signal indicates that the computer is read to accept a 12-bit word from the MUX. Only a maximum of eight of the 12 lines are used for data bits.                |  |  |  |  |

|                         | 2. In a Write operation, Data signal indicates the computer has placed a 12-bit word on the data lines.                                                                                      |  |  |  |  |

| MUX to Computer Signals |                                                                                                                                                                                              |  |  |  |  |

| Interrupt               | A "1" signal which periodically asks the computer to go into an I/O subroutine with the MUX. The period is adjustable (by logic-card substitution) to either high-or low-speed transmission. |  |  |  |  |

-

### TABLE 4. I/O INTERFACE SIGNALS BETWEEN COMPUTER AND MUX (CONT)

| Reply       | Static "1" signal produced by the MUX in response to a Connect<br>or Data signal. Signal drops when Connect or Data signal drops.                                                                      |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | <ol> <li>If connection can be made when Connect Signal is received,<br/>an LSI/O unit connects and returns a Reply.</li> </ol>                                                                         |

|             | 2. In a Read operation the MUX sends a Reply as soon as it<br>has placed a 12-bit word on data lines in response to the<br>Data signal. Note that a data character uses only the eight<br>lowest bits. |

|             | 3. In a Write operation, the MUX sends a Reply as soon as it samples the data lines in response to the Data signal.                                                                                    |

| Status Bits | Static "1" signal is produced by a connected LSIU and sent to<br>the computer only if one of the five following conditions exists:                                                                     |

|             | 1. Character Ready                                                                                                                                                                                     |

|             | 2. Character Lost                                                                                                                                                                                      |

|             | 3. Break                                                                                                                                                                                               |

|             | 4. Idle                                                                                                                                                                                                |

|             | 5. Character Request is produced by an LSOU but is sensed<br>by the computer along with LSIU Status Response signals.                                                                                  |

CONTROL DATA

# CONTROL DATA 8165 MASTER MULTIPLEXER

Pub. No. 368 161 00 (02)

# 8165 MASTER MULTIPLEXER

### CONTENTS

| Description                                        | 1 (8165-B/C                               | ) |

|----------------------------------------------------|-------------------------------------------|---|

| Operation<br>Panel<br>Lamps                        | 1 (8165-B/C<br>2 (8165-B/C<br>2 (8165-B/C | ) |

| Write Logic<br>Channel Interrupt<br>Connect Signal | 2 (8165-B/C<br>2 (8165-B/C<br>2 (8165-B/C | ) |

| Read Logic<br>Character Ready                      | 2 (8165-B/C<br>3 (8165-B/C                |   |

| 3000 Series Computer Interface<br>Interrupt        | 3 (8165-B/C<br>3 (8165-B/C                |   |

| Connect Code                                       | 4 (8165-B/C                               | ) |

#### FIGURES

| 1 | 8165 Master Multiplexer    | ii | (8165-B/C) |

|---|----------------------------|----|------------|

| 2 | MUX Word                   | 4  | (8165-B/C) |

| 3 | Connect Code Configuration | 6  | (8165-B/C) |

## TABLES

| 1 Connect Code Deciphering 6 (8 | 8165-B/C) |

|---------------------------------|-----------|

|---------------------------------|-----------|

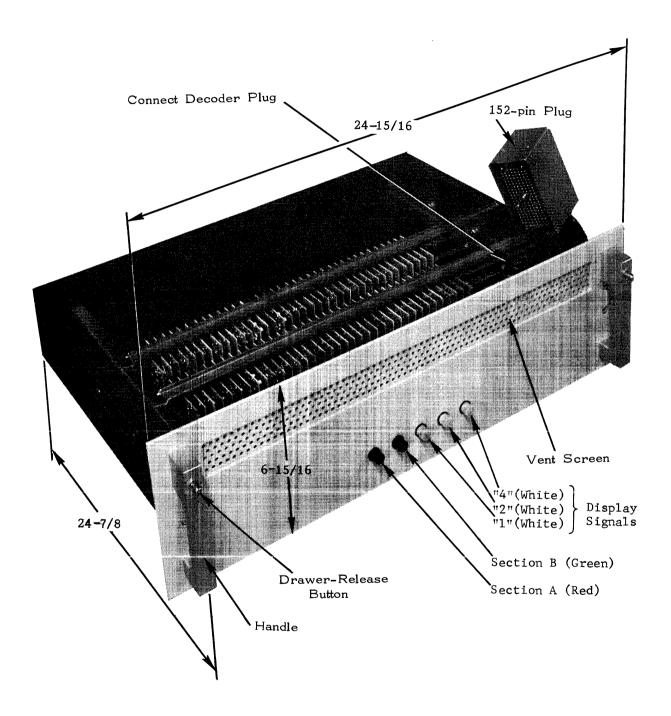

Figure 1. 8165 Master Multiplexer

ii (8165-B/C)

#### 8165 MASTER MULTIPLEXER

#### DESCRIPTION

The CONTROL DATA 8165 Master Multiplexer (Master MUX), figure 1, is a high-speed data switch that distributes messages between a computer in a CONTROL DATA 8050 System and two pairs of input/output slave MUXs. It interrupts a computer channel periodically for input/output (I/O) operations. It decodes connect codes for the 32 I/O units in the cabinet. Physically the 8165 Master MUX is a drawer (containing logic cards, controls and wiring) that fits into the 3276-A Communication Terminal Controller cabinet assembly. The 8165-A interfaces the CONTROL DATA 160-A or 8090 Computer. The 8165-B and 8165-C models interface the 3000 series Computers.

This manual covers both the 8165-B and 8165-C Master MUXs which are alike except for read scanning. The 8165-B does not have a read scanner. Therefore, the computer or an external scanner sends connect codes to all the input units in sequence. The 8165-B Master MUX decodes the connect code for each unit.

The 8165-C has a read scanner. The computer sends only one connect code per cabinet. The 8165-C Master MUX in any controller cabinet decodes the connect code and scans all the input units.

#### OPERATION

The 8165 Master MUX performs the following operations:

- 1. Initiates the channel Interrupt signal which periodically asks the computer to enter an I/O routine with the MUX.

- 2. Decodes its own connect code.

- 3. Scans all input units (8165-C).

- 4. Decodes connect codes to input units (8165-B).

- 5. Sends any data which is available from a low-speed input unit (LSIU) to the computer.

- 6. Decodes connect codes to output units.

- 7. Replies to Connect, Read or Write signal from the computer.

- 8. Sends the computer the status code indicating Character Ready, Character Lost, Break or Idle received from the LSIUs.

#### PANEL

The 8165 Master MUX panel serves as a display board for the A and B sections and LSI/O unit connect decoders.

#### LAMPS

There are five indicator lamps in a horizontal row on the panel. They display the decoder connect code. The left two lamps indicate which section (A or B) is communicating with the computer. The first lamp (red) designates the A section. The second lamp (green) indicates the B section. The right three lamps (white) indicate in octal code which of eight pairs of LSI/O units in the module is selected. The lamps are lighted by the connect code from the computer. They go off when the connect code and Connect signal stop.

#### WRITE LOGIC

#### CHANNEL INTERRUPT

The MUX operates on a computer-interrupt basis (see diagrams 364561500 and 36461600 in pub. no. 368 165 00). The interrupt clock in the Master MUX is a free-running multivibrator. It sets the interval between interrupts at slightly less than the mimimum character interval. For example, with a Teletype (TTY) rate of 100 words per minute where the character interval is 100 ms, the interrupt clock is set to cycle once every 90 ms. Once each cycle, the clock sets the Interrupt flip-flop (FF), which notifies the computer that an Interrupt is generated. The computer enters the interrupt routine.

#### CONNECT SIGNAL

The computer sends out a Connect signal along with a connect code. The Connect signal is used throughout the 8165 circuit to enable and/or disable decoding. The programmed connect code selects the assigned output section (A or B) and output unit (one of eight).

#### READ LOGIC

The 8165 read logic has a threefold purpose; it is a channel for parallel-bit transmission of each input character from an 8508-B Low-Speed Input Unit to the computer. When alarm status signals, such as Character Lost or Break/Idle, are generated in an input unit they pass through the Master MUX to the computer.

#### CHARACTER READY

When an input unit sends a Character Ready bit through the 8165 to the computer, the computer returns a Read signal via the 8165 to the read unit.

The Read signal enables the Reply signal to return to the computer if data is ready. This allows a character to leave an LSIU and enter the computer. In the 8165-C, the Read signal starts the counter which scans all input units for any available Read data.

#### 3000 SERIES COMPUTER INTERFACE

The I/O section of the computer provides the methods for data exchange and for control of information transmission between the computer and the various external equipments. All information from the externally located peripheral equipments must enter or leave the computer through these cables.

Information passes between the computer and the external equipment as a block of information at a word-by-word rate or as a single word input or output. The speed of the particular equipment in communication with the computer determines the data exchange rate.

#### INTERRUPT

#### Description

An Interrupt signal jumps the computer main program and initiates an interrupt subroutine. At the completion of the interrupt subroutine the main program can be resumed. Each Interrupt signal transfers computer control to a distinct location in memory (refer to Execution paragraph).

To use the interrupt feature, every connect command must be followed by a Clear Interrupt Lockout (CIL) command, but not until the completion of any I/O sequence related to that connect command.

The interrupt clock in the 8165 Master MUX is set at a cycle time just under the character rate. The clock is adjustable from low Teletype speed (60 to 100 words per minute) to high telephone speed (1050 words per minute) by replacing the type CC82-5 card in location B20 with a type CC82-4 card, and readjusting the delay in location B21 to the desired time.

#### Recognition

Interrupt FFs are activated by an internal 8165 Master MUX clock. The routine must branch to an interrupt subroutine. The Interrupt signal is removed from the line by the external equipment.

#### Execution

During the execution portion of the interrupt, the computer stores the contents of P at location 00004, and then takes its next instruction from 00005 to enter the subroutine.

The Master MUX is connected to the computer's data and control I/O cables. Cables with 152-pin plugs are used to connect the slave MUX and the Master MUX to common cabinet wiring and receptacles.

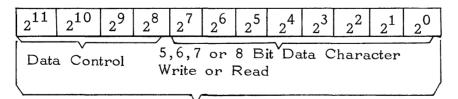

The MUX word is 12 bits long of which up to eight bits are communications data (see figure 2).

#### CONNECT CODE

The connect codes 00XX, 01XX and 02XX are reserved for addressing as high as a 12-cabinet MUX system. Each octal digit represents three bits. MUX systems can be addressed in groups of four 8165 Master MUXs.

In the read mode the computer connects an 8165-C Master MUX which in turn scans eight LSIUs in each section (A and B), and each LSOU for Character Request. In the write mode the computer connects each LSOU for which there is data.

The first and second digits of the code (00, 01 or 02) direct the computer communication to one of the three groups of 8155 cabinets (four cabinets maximum to a group).

Used for Connect Code

Figure 2. MUX Word

The third octal digit chooses not only a cabinet but also a section (A or B) within the cabinet (see figure 3). The first two bits select a cabinet (the binary count limit of two bits is four). The third bit selects the A or B section.

The fourth octal digit of this code selects one of eight pairs (one input and one output) of LSI/O units by octal numbers 0 through 7.

To show the exact selection, divide the octal code into its binary equivalent as shown in table 1.

Example: The computer has a character ready to send to a teletypewriter way station which is connected to LSOU no. 5 in section B in the second cabinet. What is the connect code to address this LSOU?

Solution: The first and second octal digits (01) are give. The bits of the third octal digit (01XX) are "01" for the second cabinet and "1" for section B. The fourth octal digit is composed of bits 101 representing unit no. 5, thus:

Binary

000 001 011 101

Octal

0135 = connect code

The decoder plug is a 24-pin twist-lock cylinder which is wired to decode the first three octal digits of the connect code. It plugs into the panel of each 8165 Master MUX, and is wired to select the correct cabinet and section, for example 010X.

011X

The 8165 decodes the third digit as to odd or even (0 or 1). The fourth digit is decoded in the internal logic of the MUX to select one of eight of LSOUs units in a section.

THE FIRST AND SECOND CODE DIGITS (00,01 OR 02) SELECTS WHICH GROUP OF 4 CABINETS TO "TALK TO".

Figure 3. Connect Code Configuration

| Octal  | 0                                                 | 0,1, or 2                                       | х                                                                                                               | Х                                                     |

|--------|---------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

|        | (2 <sup>11</sup> 2 <sup>10</sup> 2 <sup>9</sup> ) | (2 <sup>8</sup> 2 <sup>7</sup> 2 <sup>6</sup> ) | $(2^{5}2^{4}2^{3})$                                                                                             | $(2^{2}2^{1}2^{0})$ LSI/O<br>unit no.                 |

| Binary | 000                                               | 001,000,010                                     |                                                                                                                 | 000 0                                                 |

|        | MUX system                                        | Groups of<br>4 cabinets                         | Section                                                                                                         |                                                       |

|        | -                                                 | Cabinet 1—                                      | _       .                                                                                                       | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

|        |                                                   | Cabinet 2—                                      | $\begin{bmatrix} 0 & 1 & 0 \\ 0 & 1 & 1 \end{bmatrix} = \begin{bmatrix} 0 & 1 & 0 \\ B \end{bmatrix}$           | 0 1 1                                                 |

|        |                                                   | Cabinet 3—                                      | $-\begin{bmatrix} 1 & 0 & 0 \\ 1 & 0 & 1 \end{bmatrix} = \begin{bmatrix} -1 & 0 & 0 \\ 0 & 0 & 0 \end{bmatrix}$ | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

|        |                                                   | Cabinet 4—                                      |                                                                                                                 | 1 1 0 6                                               |

|        |                                                   |                                                 |                                                                                                                 | 1 1 1 7                                               |

TABLE 1. CONNECT CODE DECIPHERING

# CONTROL DATA 8166-B INPUT SLAVE MULTIPLEXER

# 8166-B INPUT SLAVE MULTIPLEXER

### CONTENTS

| Introduction                                                       | 1 (8166-B)                                                                       |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Description                                                        | 1 (8166-B)                                                                       |

| Logic Cards                                                        | 1 (8166-B)                                                                       |

| LSIUs                                                              | 1 (8166-B)                                                                       |

| Status Codes<br>Character Ready<br>Character Lost<br>Break<br>Idle | 1 (8166-B)<br>2 (8166-B)<br>2 (8166-B)<br>2 (8166-B)<br>2 (8166-B)<br>2 (8166-B) |

| Logic                                                              | 3 (8166-B)                                                                       |

| LSIU Interface                                                     | 3 (8166-B)                                                                       |

| Fan In                                                             | 3 (8166-B)                                                                       |

#### FIGURES

Figure 1. 8166-B Input Slave Multiplexer

ii(8166-B)

#### 8166-B INPUT SLAVE MULTIPLEXER

#### INTRODUCTION

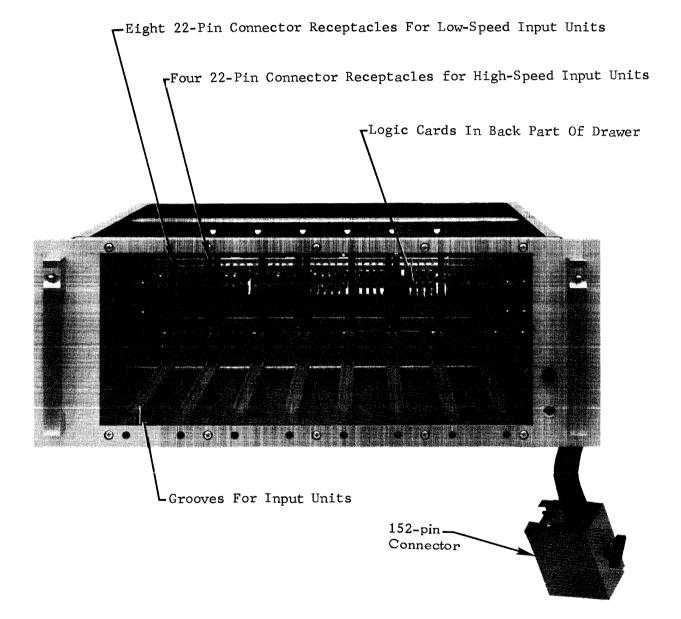

The CONTROL DATA 8166-B Input Slave Multiplexer (Input MUX), figure 1, is a data handling device which collects data from each of its eight connected low-speed input units (LSIUs) and fans in the data to the computer by way of the Master MUX.

#### DESCRIPTION

The 8166-B is a drawer-type module which fits into the 3276-A cabinet. It slides out on telescoping channels, and locks in either the extended or closed position. Before the drawer can be opened, the 152-pin plug must be disconnected, and the release buttons on the two pull handles must be pressed. The plug is disconnected simply by unscrewing the wing screw until it is free, and pulling the plug out.

#### LOGIC CARDS

The back part of the modules contains two rows, of logic cards, the eight 22conductor receptacles for the LSIUs, and four receptacles for high-speed input units.

#### LSIU(S)

Eight 8508-B or 8518 LSIUs slide into channels in the front of the 8166-B like books on a shelf. When the LSIUs are pushed all the way in, they mate with the matching receptacles. An LSIU is locked in with a plastic button which snaps in.

#### STATUS CODES

The following four status bits enter the 8166-B from its LSIUs. Each status bit is fanned in from eight LSIUs to a single signal line. The fan-in takes place in the 8166-B.

Character Ready Character Lost Break Idle

#### CHARACTER READY

The Character Ready is a "1" signal which accompanies a parallel-bit character from an LSIU. The computer selects each LSIU individually (8165-B) or by means of a read scanner in the 8165-C. When the computer enables an LSIU which has a Character Ready signal, it receives the signal on bit 11 and accepts the character.

#### NOTE

Input Acknowledge is a short pulse generated in the 8166-B after the computer accepts the character. The Input Acknowledge signal is sent to the selected LSIU to clear the Character Ready, Character Lòst, and Break status flip-flops.

#### CHARACTER LOST

The Character Lost is a "1" signal sent from a connected LSIU through the 8166-B fan-in to the computer. If the computer fails to accept a character from the LSIU before the next character arrives, the Character Lost signal is sent to the computer.

#### BREAK

The Break is a "1" signal which indicates to the LSIU that there is a broken Teletype circuit. When a connected input unit has a Break signal set, it sends the signal to the computer and the operator is alerted. The Break signal is accompanied by a data character of all zeros.

#### IDLE

The Idle signal is sent by an LSIU when an idle line is detected. If the telegraph channel remains marking for 5 seconds, a thermal delay relay in the LSIU sends the Idle signal to the computer. The Idle and Break signals are joined in the 8166-B Input MUX as one signal, which can be logically separated by the computer. The Idle signal is accompanied by a continuous repetition of the last previous character in the holding register.

### 2 (8166-B)

#### LOGIC

#### LSIU INTERFACE \*

Each 3276 MUX cabinet can contain two 8166s, each of which can hold up to eight LSIUs (see logic diagram 36449500 in pub. no. 368 165 00). Each LSIU plugs into a separate 22-conductor receptacle. This is the LSIU interface. Through this connection pass the data bits, the four status signals, the dc electric power, the teletypewriter signals, signal-monitor line, and the Input Acknowledge. All these signals, except Input Acknowledge, travel from the LSIU into the 8166-B. The Input Acknowledge is generated within the 8166-B and sent to the LSIU to clear the status flip-flops.

#### FAN IN

The 8166-B lnput MUX takes the data-bit signals and the status-bit signals from all eight of its LSIUs and fans them into a common signal channel. Thus, data from any of the eight LSIUs is sent to the computer over a single group of wires. LSIUs are connected consecutively. Each LSIU sends its signals to the computer separately as it is connected in its turn.

<sup>\*</sup> The 8536 High-Speed Input Unit (HSIU) is so similar to the 8518 LSIU that references to LSIU also apply to the 8536 HSIUs.

# **CONTROL DATA 8167** OUTPUT SLAVE MULTIPLEXER

# 8167 OUTPUT SLAVE MULTIPLEXER

#### CONTENTS

| Description                                                                                             | 1           | (8167-B/C)                                                         |

|---------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------|

| 8167-B Output MUX                                                                                       | 1           | (8167-B/C)                                                         |

| 8167-C Output MUX                                                                                       | 1           | (8167-B/C)                                                         |

| Physical Description                                                                                    | 1           | (8167-B/C)                                                         |

| Output Logic<br>Character Request<br>Output Acknowledge<br>Select Output<br>Connect LSOU (bits 0, 1, 2) | 2<br>2<br>2 | (8167-B/C)<br>(8167-B/C)<br>(8167-B/C)<br>(8167-B/C)<br>(8167-B/C) |

| Reset Timer                                                                                             | 3           | (8167-B/C)                                                         |

FIGURES

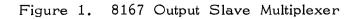

| 1 | 8167 Output Slave Multiplexer | ii (8167-B/C) |

|---|-------------------------------|---------------|

|---|-------------------------------|---------------|

ii (8167-B/C)

## 8167 OUTPUT SLAVE MULTIPLEXER

## DESCRIPTION

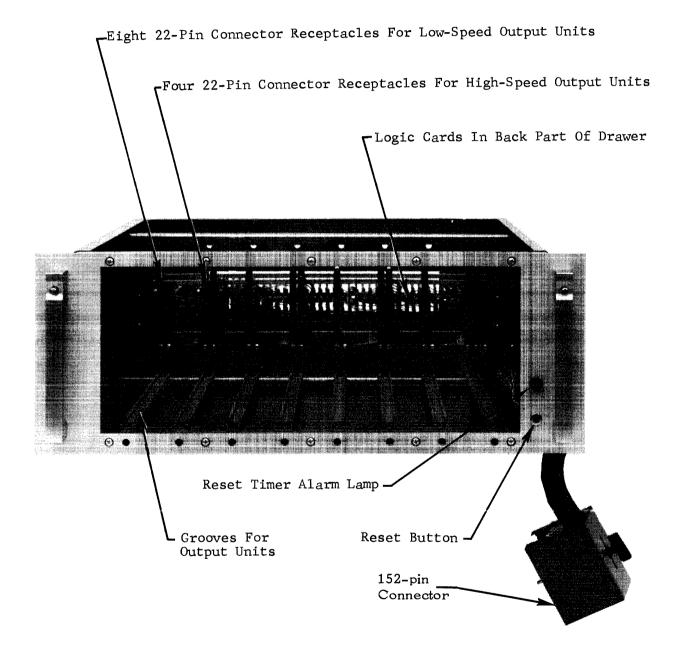

The CONTROL DATA 8167 Output Slave Multiplexer (Output MUX), figure 1, is a drawer-type modular part of the 3276 Controller. It matches the interfaces of the 8165 Master MUX and eight low-speed output units (LSOUs). This manual covers both the 8167-B and the 8167-C Output MUX models.

## 8167-B OUTPUT MUX

The 8167-B Output MUX performs as follows:

- 1. It directs the connect code to the proper LSOU to enable data to enter the LSOU.

- 2. It distributes the Start-of-Day signal to all eight of its LSOUs.

- 3. It fans in the Character Request signals from the LSOUs (up to 16 in a cabinet) to one signal line to Master MUX.

- 4. It sends an alarm if the computer fails to periodically service the MUX.

# 8167-C OUTPUT MUX

The 8167-C operates in the same manner as the 8167-B with the following exception. The 8167-C has additional logic circuitry to provide a 4-second delay. This delay holds back transmission until the motors in the receiving Teletype units have had time to accelerate to operating speed.

# PHYSICAL DESCRIPTION

The 8167 chassis is in drawer form and fits into the 3276 cabinet. The entire 8167 module slides out on telescoping channels and locks in either the extended or the closed position. Before the drawer can be opened, the 152-pin plug must be disconnected, and the release buttons on the two pull handles must be pressed. The plug is disconnected simply by unscrewing the wing screw, and pulling out the plug. The back of the module contains the logic cards, and the 22-conductor LSOU receptacles.

Eight LSOUs slide into channels in the front portion of the 8167 like books on a shelf. When the LSOUs are pushed all the way in they plug into the matching sockets. Each LSOU is locked in with a plastic button.

# OUTPUT LOGIC

An 8167 Output MUX directs the outgoing communication from the 8165 Master MUX to the eight LSOUs one at a time (see diagram no. 36448700 and 36713000 in pub. no. 368 165 00).

# CHARACTER REQUEST

Each channel which is ready to accept data from the MUX, sends a Character Request signal to the 8167. All of these signals (up to eight) are fanned in to a single Character Request signal and sent to the 8165. If the computer has an output message ready to send, it sends a data character along with Write and Data signals to the 8165. These signals combine with Character Request in the 8165 to form an Output Ready. This signal has two main purposes:

- 1. To enable the data character to move on through the connected 8167 to (but not into) all eight LSOUs.

- 2. To send an Output Acknowledge signal to each connected output unit, enabling the data character enter the output unit.

# OUTPUT ACKNOWLEDGE

This signal enters the 8167 Output MUX from the 8165 Master MUX indicating that the computer has sent a character. The Output Acknowledge combines with the Select Output signal and the selected LSOU address to direct the Output Acknowledge to the specific LSOU which has been addressed by the computer.

SELECT OUTPUT

The computer program directs the 8165 Master MUX to select one of the two 8167 Output MUXs. Both 8167 modules receive the data, the LSOU connect

2 (8167-B/C)

code and Output Acknowledge. Only the connected 8167 receives a Select Output function code. Select Output plays the important dual role of enabling the Output Acknowledge to the selected LSOU and enabling any existing Character Request in the selected 8167 module.

CONNECT LSOU (BITS 0, 1, 2)\*

The LSOU connect code is sent from the computer, decoded in the Master MUX, and sent to the 8167 in three parallel bits. These three bits are coded (0 through 7) to represent the octal number of the selected LSOU. The three bits and their complements are multiplexed for two purposes:

- 1. To enable a Character Request coming from any individual LSOU before it is fanned in to a single combined signal from all LSOUs in the module.

- 2. To address only the connected LSOU by allowing the Output Acknowledge signal to reach only the one LSOU.

When the Output Acknowledge enters the selected LSOU it enables the data character to enter the LSOU transfer register and starts the character clock.

The LSOU converts the character from parallel to serial form and sends it out on the teletypewriter communication line. The LSOU transfer register is cleared. The LSOU sends back another Character Request to the 8167. This enables the output cycle to continue.

# RESET TIMER

The reset timer section of the logic in the 8167 is a delayed-alarm device which is periodically reset by the computer. If the computer fails or detects a failure in the 8050 System the computer will not reset the timer. If a reset signal is not received for 227 ms, the reset timer lights the alarm lamp and sends an Alarm signal to the console. The alarm lamp (red) is located on the right hand side of the 8167 Output MUX front panel. The reset button is below the alarm lamp.

<sup>\*</sup> The 8537 High-Speed Output Unit (HSOU) is so similar to the 8519 LSOU that reference to LSOUs also applies to the 8537 HSOU.

.

# CONTROL DATA 8508 LOW-SPEED INPUT UNIT

Pub. No. 368 161 00 (05)

# 8508-B LOW-SPEED INPUT UNIT

CONTENTS

| Introduction<br>Panel             | 1 | (0000 -) |

|-----------------------------------|---|----------|

| Behind Panel                      | 1 | (8508-B) |

| Logic Cards                       | 2 | (8508-B) |

| Characteristics                   | 3 | (8508-B) |

| General Description               | 4 | (8508-B) |

| Status Codes                      | 4 | (8508-B) |

| Logic Description                 | 5 | (8508-B) |

| Clock                             | 5 | (8508-B) |

| Counter                           | 6 | (8508-B) |

| Register A (Staticizer)           | 6 | (8508_B) |

| Stop Pulse                        | 6 | (8508-B) |

| Status Codes in the Logic Diagram | 6 | (8508-B) |

# FIGURES

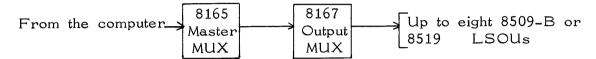

| 1 | 8508-B Low-Speed Input Unit (5 bits) | ii (8508-B) |

|---|--------------------------------------|-------------|

| 2 | Switches Behind Panel                | 2 (8508-B)  |

| 3 | Data Path through an LSIU            | 3 (8508-B)  |

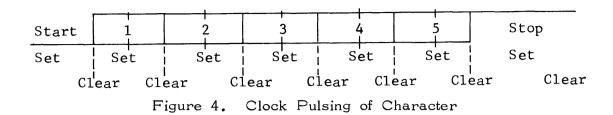

| 4 | Clock Pulsing of Character           | 5 (8508-B)  |

ii (8508-B)

## 8508-B LOW-SPEED INPUT UNIT

## INTRODUCTION

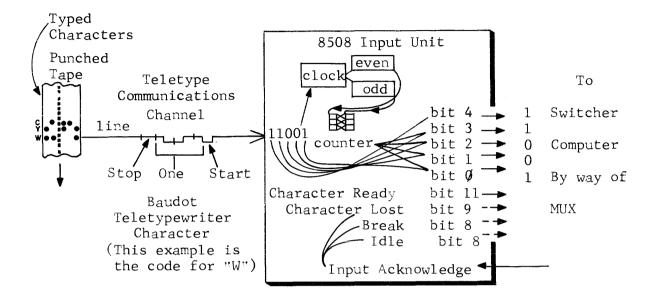

The CONTROL DATA 8508-B Low-Speed Input Unit (LSIU), figure 1, is a signal coverter interposed between a teletypewriter communication channel and one input channel of an 8166-B Input Slave Multiplexer (Input MUX). The LSIU receives a message serially (one teletypewriter bit at a time), assembles each character, and sends it in parallel form to the MUX (see example). It notifies the operator in case of a broken or inactive teletypewriter line, or of a lost character.

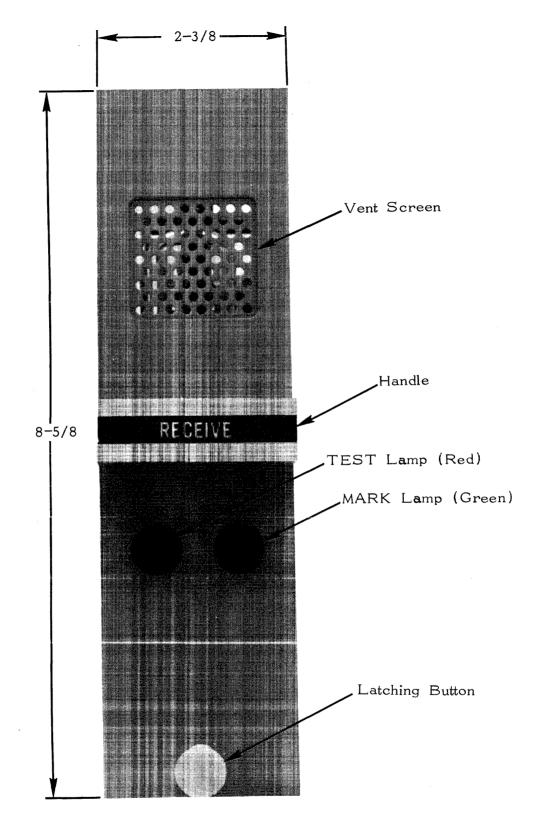

#### PANEL

The 8508-B LSIU display panel (see figure 1) is actually the front surface of the 8166-B Input MUX. It contains the following lamps and switches.

#### MARK Lamp

This green lamp flickers while the LSIU is receiving a message. It lights every time a marking pulse is received. A steady green light indicates a marking current (no Teletype characters are being received, although the LSIU and sending teletypewriter are connected and turned on).

#### TEST Lamp

This red lamp lights when the OPER/TEST toggle switch is at TEST. It warns the operator that the LSIU is in test condition and is inoperative.

#### BEHIND PANEL

Behind the panel are the following switches (see figure 2):

Figure 2. Switches Behind Panel

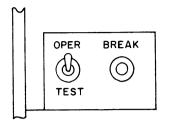

# OPER/TEST Toggle Switch

This switch must be at OPER during the normal receiving operation of the LSIU. The TEST position of the switch lights the red TEST panel lamp.

This switch is used during maintenance checks or tests within the machine. Setting the switch at TEST starts the LSIU clock and counter. It may or may not set the registers, depending on whether the BREAK button is pressed.

# BREAK Push-Button Switch

Pressing this button sets all registers to 1. Conversely, if this button is not pressed all registers remain cleared. However, if the LSIU is not in the mark-ing condition this button is ineffective.

# LOGIC CARDS

Each LSIU fits into an 8166-B Input MUX like one of eight books on a shelf. The LSIU contains three parallel printed-circuit cards.

$\underline{Card A}$  contains the inverters, flip-flops (FFs) and other components of the clock and counter.

<u>Card B</u> contains the components that clear or shift the registers, plus the Character Lost, Break FFs, and Idle relays.

$\underline{Card \ C}$  contains the components of the clock control and the A and B registers as well as data output circuits.

The two outer cards are hinged at the rear for easy access.

All logic signals, power, and telegraph circuits enter through the 22-pin connector on the rear of the LSIU.

Figure 3. Data Path through an LSIU

# CHARACTERISTICS

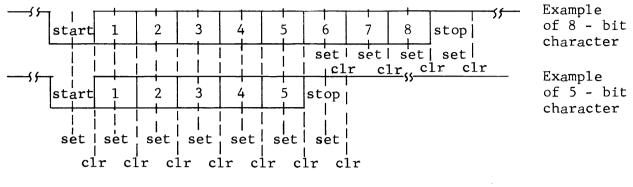

The LSIU performs the following functions (see figure 3):

- 1. It receives teletypewriter characters in a 7.42-unit, start-stop, Baudot code, serially, one bit at a time.

- 2. It drops the Start (1 bit) and Stop (1.42 bits) leaving just five data bits.

- 3. It distributes the five data bits of each character into the intermediate assembly register A.

- 4. It informs the computer through the 8166-B Input MUX that a five-bit character is ready in parallel form.

- 5. It reports a Character Lost in bit-9 position if the condition exists.

- 6. It reports a line break as well as an idle line or noncycling status. This status is inserted into bit-8 position by means of the 8166-B Input MUX.

## GENERAL DESCRIPTION

An LSIU is an electronic receiving device compatible with teletypewriter communication channels, codes, and speeds. It accepts Start/Stop signals as serial-bit pulses derived from a channel with a line relay. These pulses are strobed to convert each incoming character to parallel data bits. The bits are stored in a transfer register for a maximum of one character period, awaiting withdrawal by the computer, by way of the MUX.

An LSIU is adjustable to accommodate teletypewriter speeds of 60, 66, 75, or 100 words per minute.

Like a teletypewriter printer, an LSIU responds to a start pulse. Whenever a start pulse is recognized, the internal clock executes the timing function for the serial-to-parallel conversion, stopping at the predicted end of character to await the next start pulse.

The LSIU passes electrical signals to the computer through the MUX. These signals are of two kinds: status codes and data characters.

## STATUS CODES

The LSIU generates input status codes which are sent on signal lines to the computer through the 8166-B Input MUX and the Master MUX.

## Character Ready

The Character Ready signal tells the computer that a character has been assembled in the holding register and is ready to be withdrawn. The Character Ready is generated by the stop pulse after the last character bit enters the B register. The signal is sent to the 8165 Master MUX through the 8166-B Input MUX<sup>\*</sup>

#### Character Lost

The Character Lost signal is sent to the computer if the computer does not pick up a character before the next character arrives at the holding register. The second character will destroy the previous character.

## Break Signal

The Break signal indicates a break in line current from a remote station. It is sent to the computer if there is no Stop signal at the end of a character, but just one continuous space (absence of marking current). A Break signal is generated also if a remote station activates a break key. A Break signal is accompanied by an all-zero-bit character.

## Idle Signal

The Idle signal is generated by R<sup>203</sup> thermal relay. If the teletypewriter circuit is apparently intact, and no character is received for a specified period (5 to 10 seconds for example), the thermal relay sets the idle bit in the LSIU. See paragraph on "Status Codes in the Logic Diagram" in this book.

Whenever the computer accepts a data/status word from the LSIU, it acknowledges the event with an Input Acknowledge signal that clears the LSIU's status bits. Thus, subsequent interrogations of the LSIU result in no new information until the next event (character arrival) occurs.

# LOGIC DESCRIPTION

The LSIU receives a teletypewriter character in a 7.42-unit start-stop code (see logic drawing no. 36461700 in pub. no. 368 165 00). The message comes in serially one bit at a time. A start pulse, or line-logic "0" causes the input relay R200 to be de-energized, and the normally open contacts are opened. The resultant logic"1" activates the internal circuit of the LSIU. After a halfstart-pulse delay, a "1" signal sets the clock-control FF. The clock control sends out a "1" which starts the clock.

# CLOCK

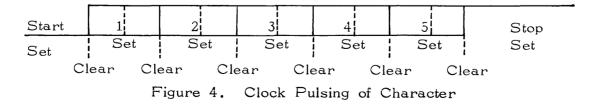

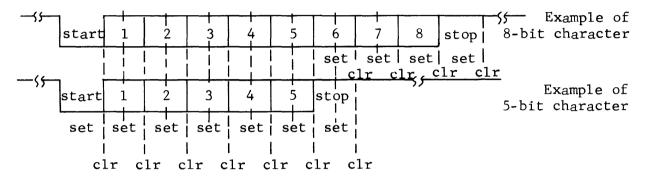

The clock of the LSIU is a free running multivibrator. As it cycles it sends out even and odd pulses. When the Clock FF is set, it sends out a short pulse through the even-clock circuit. When the clock is cleared it sends a short pulse ("1") to the odd-clock circuit ( $N^{205}$  and  $N^{207}$ ). The clock-produced even and odd pulses are clearly separated in time. The clock cycles seven times for each character. Then it is turned off by the stop pulse (coded 7 count). See figure 4.

## Even Clock and Odd Clock

The alternating pulses from the even and odd clocks feed into the counter. The even clock enables the left rank FFs of the counter to be set or cleared if other AND conditions are met. The odd clock transfers the count from left to right FFs.

## COUNTER

The left rank of the counter counts in binary. The right rank accepts the count and gates the advance. The even/odd pulses alternate back and forth between the left and right ranks advancing the count by one for each cycle. The seven count and the even-clock pulse clear the clock control, and the clock.

## REGISTER A (STATICIZER)

The register A is loaded with five data bits corresponding to a Baudot character. The counter establishes the sequence of loading the Register FFs. The clock provides the register-loading pulse. The output of diode card  $Z^{200}$  provides the identity ("1" or "0") of each bit of each character.

## STOP PULSE

The stop pulse is energized by the even clock and by the counter at the count of seven. It performs the following functions:

- 1. After 120 usec, it shifts the data from register A to register B.

- 2. It clears or turns off the clock control.

- 3. It clears or stops the clock.

- 4. It clears the counter.

- 5. It gates the Character Lost and Break alarm signal FFs.

- 6. After another 26 usec, a 19-usec pulse clears register A, and sets the Character Ready FF.

## STATUS CODES IN THE LOGIC DIAGRAM

The Input Acknowledge signal from the computer clears the Character Ready, Character Lost and Break FFs. However, if the computer fails to acknowledge the character from register B before the next character arrives, the Character Ready FF will not be cleared. The Character Lost FF then will be set when the next character is assembled in the LSIU.

If the Teletype circuit is disrupted and all the bits in register A are"1"s, the Break FF is set. The Break signal is sent by way of the MUX to the computer.

If one character is not followed by another within an interval controlled by thermal relay  $R^{203}$ , the relay will send an Idle signal. The time delay which sets off the thermal relay is set at a length of time just longer than one character cycle.

The Break and Idle outputs are combined in the MUX. To test for Break or Idle, examine the input data. If the bits are not all "0"s, the condition is idle. When all bits are "0"s the condition is Break.

# CONTROL DATA 8509 LOW-SPEED OUTPUT UNIT

# 8509-B LOW-SPEED OUTPUT UNIT

# CONTENTS

| Introduction                                                                                                                                                               | 1                     | (8509-B)                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------|

| Panel<br>SPACE Lamp<br>TEST Lamp                                                                                                                                           | 1                     | (8509-B)<br>(8509-B)<br>(8509-B)                                                             |

| Behind Panel<br>OPER/TEST Switch<br>BREAK Push-Button Switch                                                                                                               | 2                     | (8509-B)<br>(8509-B)<br>(8509-B)                                                             |

| Logic Cards                                                                                                                                                                | 2                     | (8509-B)                                                                                     |

| Characteristics                                                                                                                                                            | 2                     | (8509-B)                                                                                     |

| General Description                                                                                                                                                        | 3                     | (8509-B)                                                                                     |

| Logic Description<br>Output Acknowledge Signal<br>Clock Control (Starts and Stops Clock)<br>Register Control<br>Clock<br>Even Clock and Odd Clock<br>Counter<br>Serializer | 5<br>5<br>5<br>6<br>6 | (8509-B)<br>(8509-B)<br>(8509-B)<br>(8509-B)<br>(8509-B)<br>(8509-B)<br>(8509-B)<br>(8509-B) |

# FIGURES

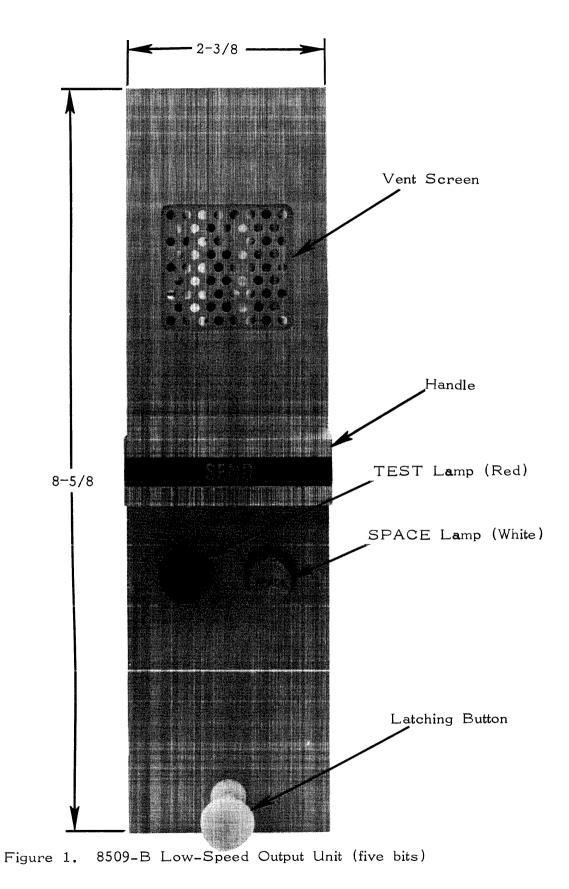

| 1 | 8509-B Low-Speed Output Unit | ii (8509–B) |

|---|------------------------------|-------------|

| 2 | Switched behind the Panel    | 2 (8509-B)  |

| 3 | Data Path through an LSOU    | 4 (8509-B)  |

| 4 | Clock Pulsing of Character   | 6 (8509_B)  |

# TABLES

| 1 | Order of | Serialized | Bits | (five-level) | 6 (8509-B) |

|---|----------|------------|------|--------------|------------|

|---|----------|------------|------|--------------|------------|

ii (8509-B)

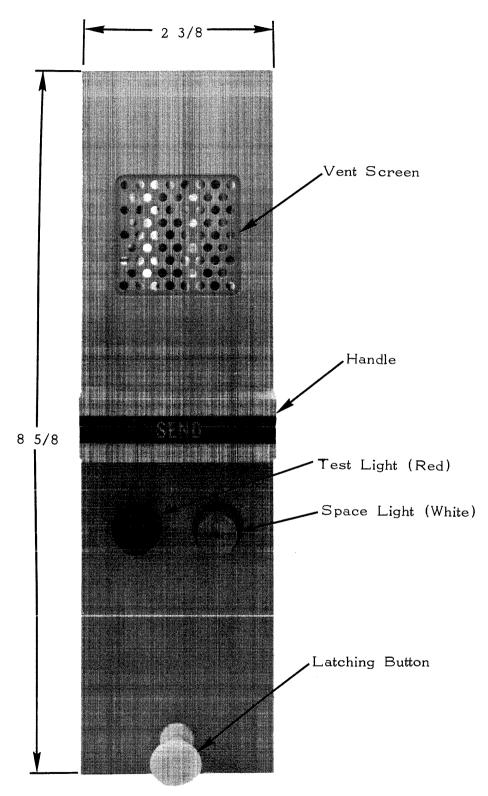

## 8509-B LOW-SPEED OUTPUT UNIT

## INTRODUCTION

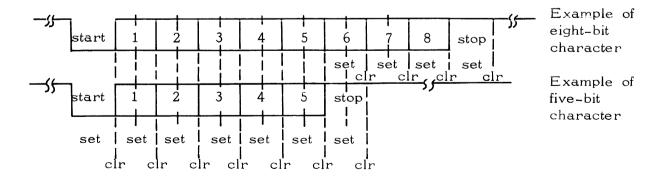

The CONTROL DATA 8509-B Low-Speed Ouput Unit (LSOU), figure 1, is a signal converter interposed between one output point on an 8167 Output Slave Multiplexer (Output MUX) and a teletypewriter communication channel. The LSOU receives parallel-bit characters from the MUX. By means of a clock and counter, the LSOU sends the bits serially to the telegraph circuit in the 7.5-unit startstop teletypewriter code.

#### PANEL

The 8509-B LSOU control panel (see figure 1) mounts flush against the front surface of the 8167 Output MUX. It contains the following labeled lamps and switches:

#### SPACE LAMP

This white lampflickers while the LSOU is sending a message. It lights every time there is a break or space pulse in the teletypewriter communications line.

#### TEST LAMP

This red lamp lights when the OPER/TEST toggle switch (behind panel) is at TEST. The lighted lamp warns the operator that the LSOU is in test condition and therefore inoperative.

## BEHIND PANEL

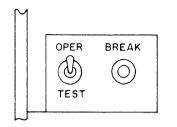

Behind the panel on the right side are the following switches (see figure 2):

Figure 2. Switches behind the Panel

# OPER/TEST TOGGLE SWITCH

This switch must be at OPER during the normal operation of the LSOU. The TEST position lights the red TEST lamp (on the panel front). It sets the clock control which in turn starts the clock. This switch can be used during maintenance checks and tests.

# BREAK PUSH-BUTTON SWITCH

When this push button is pressed it actuates relay  $R^{100}$  which cuts the teletype-writer circuit. It also lights the SPACE lamp.

# LOGIC CARDS

Each LSOU fits into an 8167-B Output MUX like one of eight books on a shelf. The LSOU consists of three printed-circuit cards. The two outer cards are hinged at the rear for easy access.

<u>Card A</u> contains (Transfer) register A and (Holding) register B as well as the status code flip-flop (FF).

<u>Card B</u> contains the character serializer.

<u>Card C</u> contains the clock and counter.

Since the 8509-A LSOU is a pluggable unit, all logic signals, power, and telegraph circuits enter through the 22-pin connector on the rear of the LSOU.

# CHARACTERISTICS

The LSOU performs as follows when it is connected to send a character:

2 (8509-B)

- 1. It receives five parallel data bits from the computer by way of the MUX.

- 2. Simultaneously it receives an Output Acknowledge signal. This enables the five-bit character to enter register A.

- 3. It shifts the character from register A to B (if the clock is stopped) and clears register A.

- 4. It requests the next five-bit character by generating a Character Request signal.

- 5. It starts the multivibrator clock.

- 6. The clock counter sends one bit at a time in sequence and adds start and stop units.

- 7. The serializer "ands" the counter and bit register sequentially, thus regulating the consecutive order of the bits.

- 8. It sends the 7.5-unit code to the output keyer in the test board unit.

Each character in a 100-wpm (for example) system has a duration of 100 ms including start and stop pulses.

## GENERAL DESCRIPTION

An LSOU is an electronic parallel-to-serial converter that is compatible with teletypewriter communication channels, codes, and speeds (see figure 3). The 8509-B LSOU accepts one five-bit character at a time by way of the MUX. Each character is stored in a register before it is "clocked out". A series of pulses is produced which contains the data bits and the start and stop pulses required by the teletypewriter circuit driven by the LSOU. An 8509-B LSOU can generate 7.42- or 7.5-unit characters with five information pulses. The clock is adjustable to provide output rates within the range of 60 to 100 wpm.

An internal five-bit register stores one five-bit character in addition to the character undergoing parallel-to-serial conversion. For this reason, the computer has the time of one character cycle to respond to a Character Request from the LSOU while maintaining the maximum output rate.

Figure 3. Data Path through an LSOU

An LSOU generates only one status code, Character Request. When the computer responds with Information Ready, the MUX enables the data character and Output Acknowledge to be sent to the LSOU. This event causes the Request to drop and the serializing function to start in the LSOU. If no character is transferred with the acknowledgement, a blank character is generated and sent by the LSOU. Failure of the computer to acknowledge a Request merely extends the stop pulse.

# LOGIC DESCRIPTION

When the LSOU is not sending data, the relay puller P100 is de-energized (see logic diagram no. 36461800 in pub. no. 368 165 00). The telegraph communication channel is a closed circuit. A marking line current passes through the circuit. This holds true until the start pulse of a character reaches the relay puller P100 which energizes the output keyer in the test board unit.

When a five-bit character passes through the LSOU, the five bits reach the LSOU in parallel in external voltage levels ("1" = -0.5v, "0" = -16v). Each bit passes through an M card and is converted to internal voltage levels ("1" = 3.5v, "0" = nominal 0v).

## OUTPUT ACKNOWLEDGE SIGNAL

Whenever an 8509-B LSOU receives a five-bit character from the computer, it also receives an Output Acknowledge signal. The Output Acknowledge is a logic "1" signal which has the following functions within the LSOU:

- 1. It enables the data character to enter register A.

- 2. It sets a FF  $A^{110}/A^{111}$  which in turn gates the clock control  $K^{100}/K^{101}$ .

CLOCK CONTROL (STARTS AND STOPS CLOCK)

With the clock stopped between data characters, the outputs of inverter  $I^{104}$  and N103 are "1"s. These "1"s are gated with the "1" from A<sup>111</sup> to set the the clock Control FF K<sup>100</sup>/K<sup>101</sup>. When the clock control is set it does the following: