# 3600 SYSTEM Design Handbook

-

-----

CORPORATION

**COMPUTER DIVISION**

September 25, 1962

TO: Bob Hesslund

EDZ:fb

This Design Handbook is the result of the efforts of many individuals in the Computer Division. It has been prepared for the purpose of disseminating technical information concerning circuits and logic to the other groups within the corporation and to provide a ready reference source for the useage of 3600 building blocks.

I would like to call your attention to the paragraph on the cover sheet concerning the confidential nature of the information in this Handbook. Your attention is also called to the registration number which is assigned to each individual copy. You will be held responsible for this particular copy, and further additions and deletions will be sent to you.

Any comments concerning the use, improvement, and criticism of the Handbook would be appreciated and should be addressed to the undersigned.

i

immer

E.D. Zimmer Director of Engineering

COMPUTER DIVISION

CDC # 8

**Registration Number**

#### 3600 DESIGN HANDBOOK

Recognition is given to the following engineers for their part in the development of the circuits contained in this manual:

> Bollesen, V Gallup, L. Kammann, C. McCann, R. Schoenherr, H. Schrieber, G. Slattery, L.

#### NOTE

THE IDEAS AND DESIGNS SET FORTH IN THIS DESIGN HANDBOOK ARE THE PROPERTY OF CONTROL DATA CORPORATION AND ARE NOT TO BE DISSEMINATED, DISTRIBUTED, OR OTHERWISE CONVEYED TO THIRD PERSONS WITHOUT THE EXPRESS WRITTEN PERMISSION OF THE CONTROL DATA CORPORATION LEGAL DEPARTMENT.

> Control Data Corporation Computer Division 501 Park Avenue Minneapolis, Minnesota

> > October 1, 1962

Publ. 135

## CONTENTS

| Chapter | 1 | ••• ` | Component | Specifications |

|---------|---|-------|-----------|----------------|

|---------|---|-------|-----------|----------------|

| Diodes                 | 1-2  |

|------------------------|------|

| Zener Diodes           | 1-3  |

| Tunnel Diodes          | 1-4  |

| Type C01 Transistor    | 1-5  |

| Type C02 Transistor    | 1-6  |

| Type C03 Transistor    | 1-7  |

| Type C04 Transistor    | 1-8  |

| Type C05 Transistor    | 1-9  |

| Type C07 Transistor    | 1-10 |

| Type 2N404 Transistor  | 1-11 |

| Type 2N1760 Transistor | 1-12 |

# Chapter 2 - Logic Card Types

# Chapter 3 - Circuit Descriptions

| Odd Plane Inhibit Generator   | 3-2  |

|-------------------------------|------|

| Clock Oscillator - Amplifier  | 3-5  |

| Clamp                         | 3-11 |

| Transformer Driver            | 3-14 |

| Even Plane Inhibit Generator  | 3-17 |

| Gate                          | 3-20 |

| Sense Amplifier               | 3-24 |

| Emitter Follower              | 3-29 |

| Delay Line Driver             | 3-31 |

| Dummy Inhibit Generator       | 3-33 |

| Driver Transformer            | 3-36 |

| Basic Inverter Circuit        | 3-39 |

| Transmitter and Receiver      | 3-49 |

| Resync Circuit                | 3-56 |

| Capacitive Delay              | 3-63 |

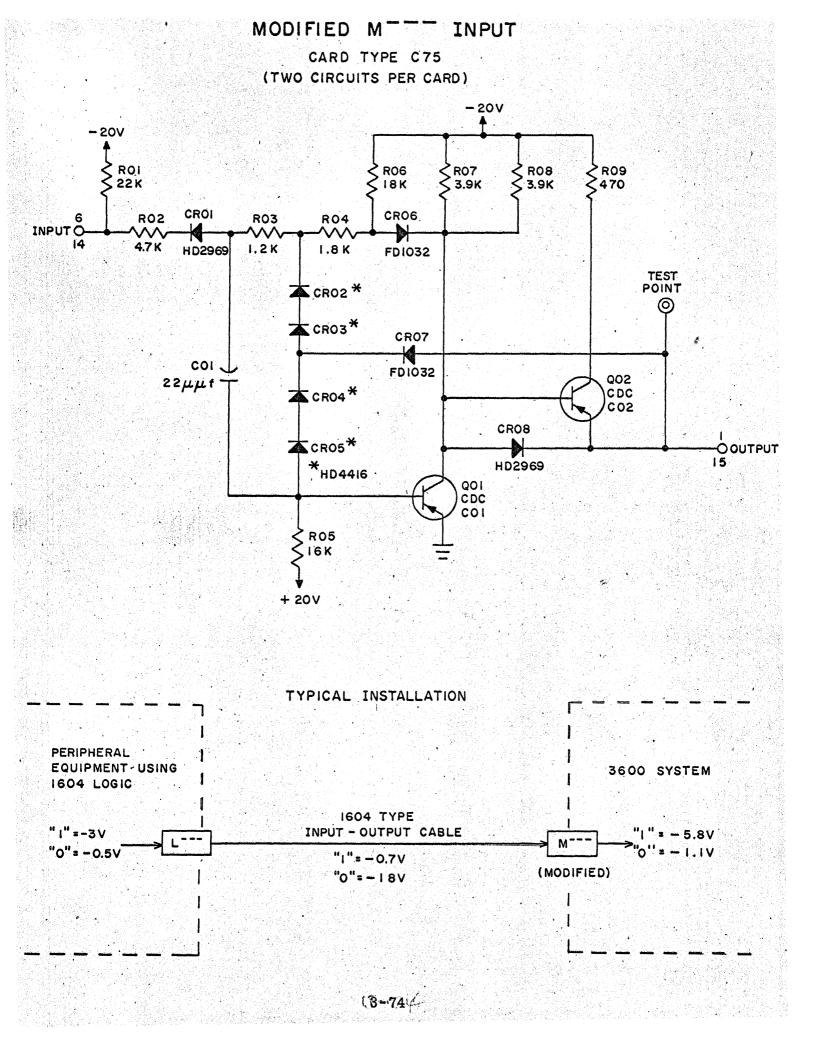

| Modified M <sup></sup> Input  | 3-73 |

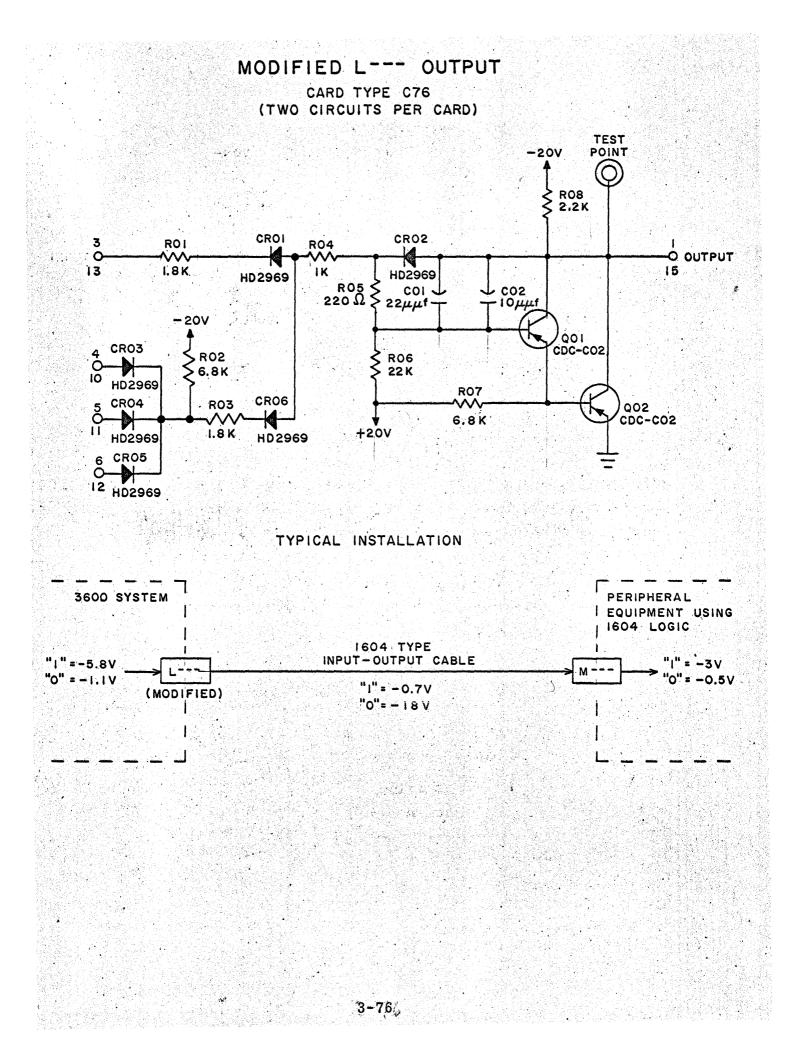

| Modified L <sup></sup> Output | 3-75 |

|                               |      |

# CONTENTS (CONT'D)

# Chapter 3 - (Cont'd)

| Priority Circuit '     | 3-78  |

|------------------------|-------|

| Delay Line, 1 usec     | 3-88  |

| Crystal Oscillator     | 3-90  |

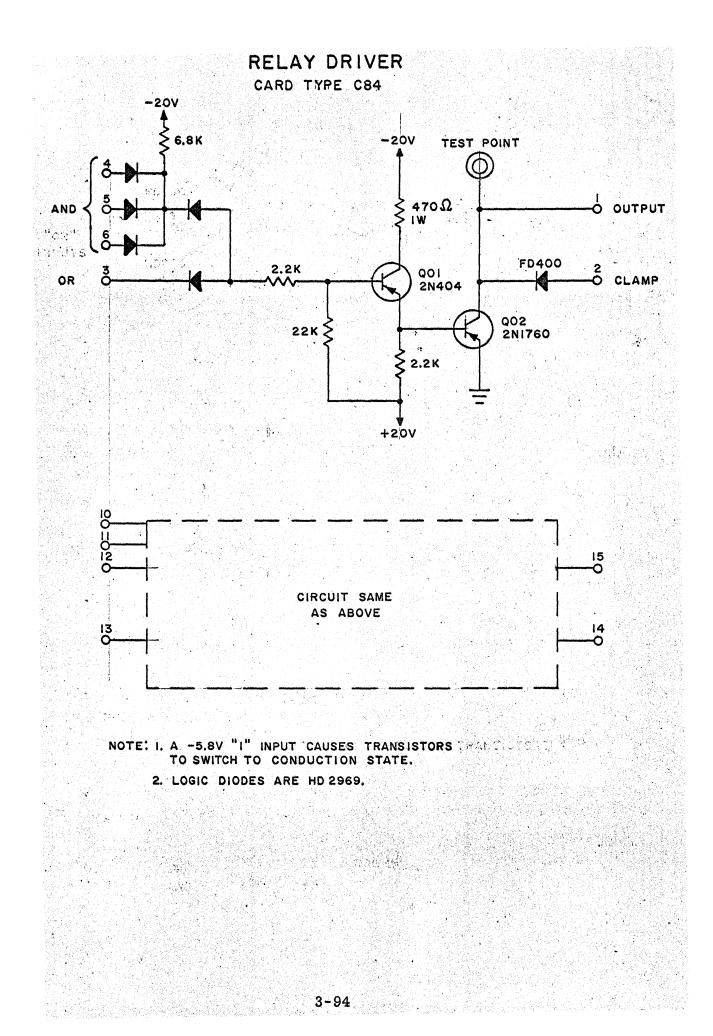

| Relay Driver           | 3-93  |

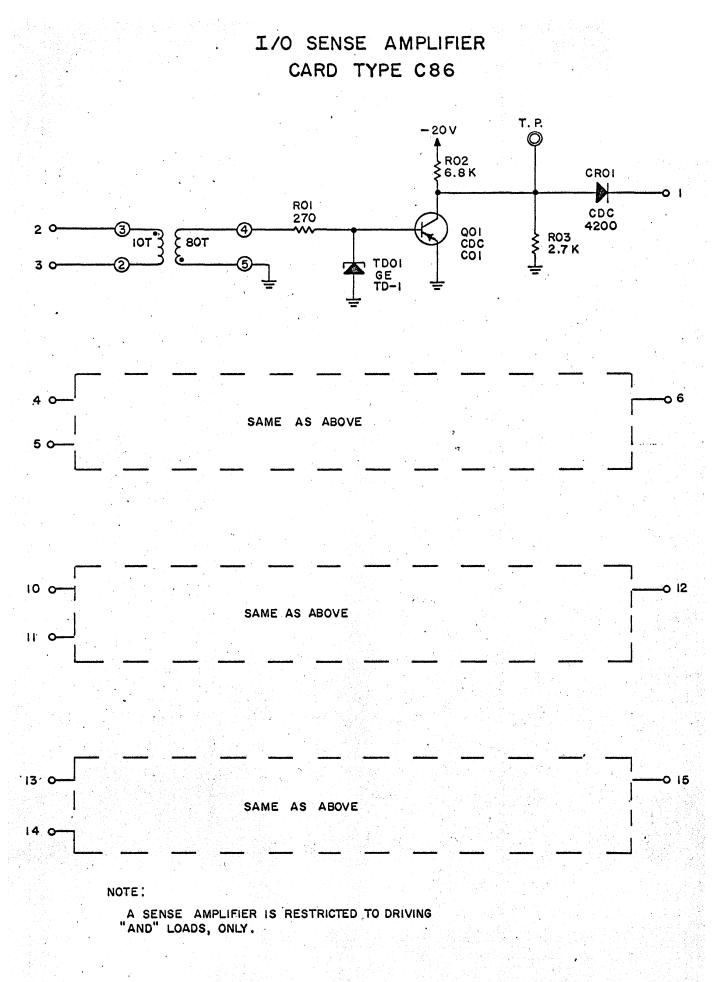

| I/O Sense Amplifier    | 3-96  |

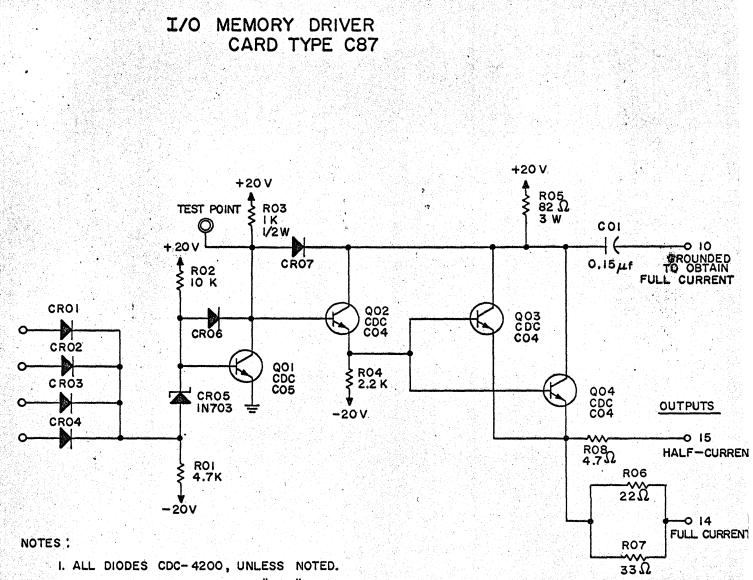

| I/O Memory Driver      | 3-99  |

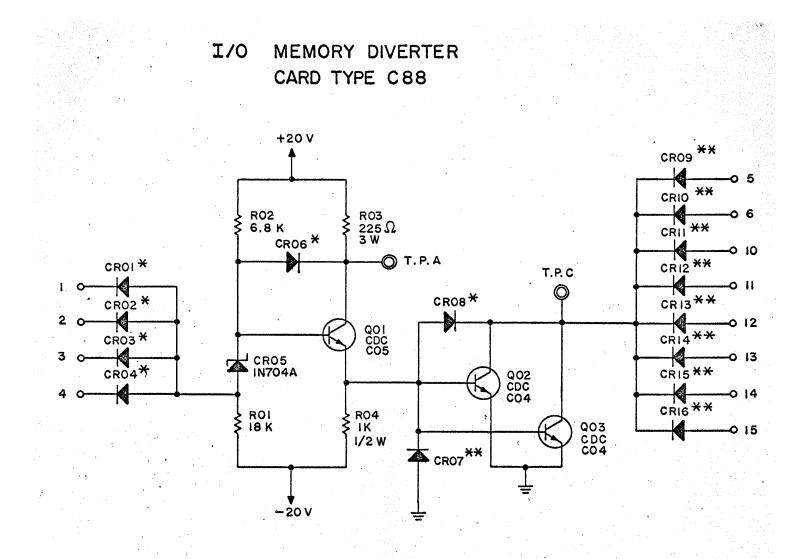

| I/O Memory Diverter    | 3-102 |

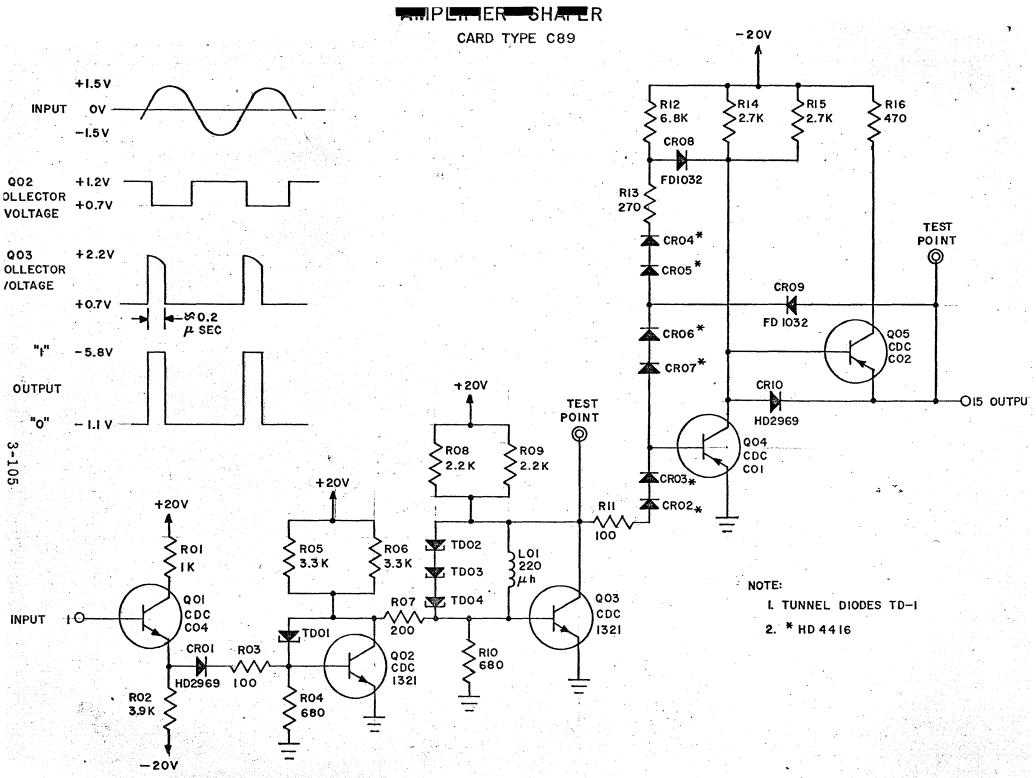

| Amplifier-Shaper       | 3-104 |

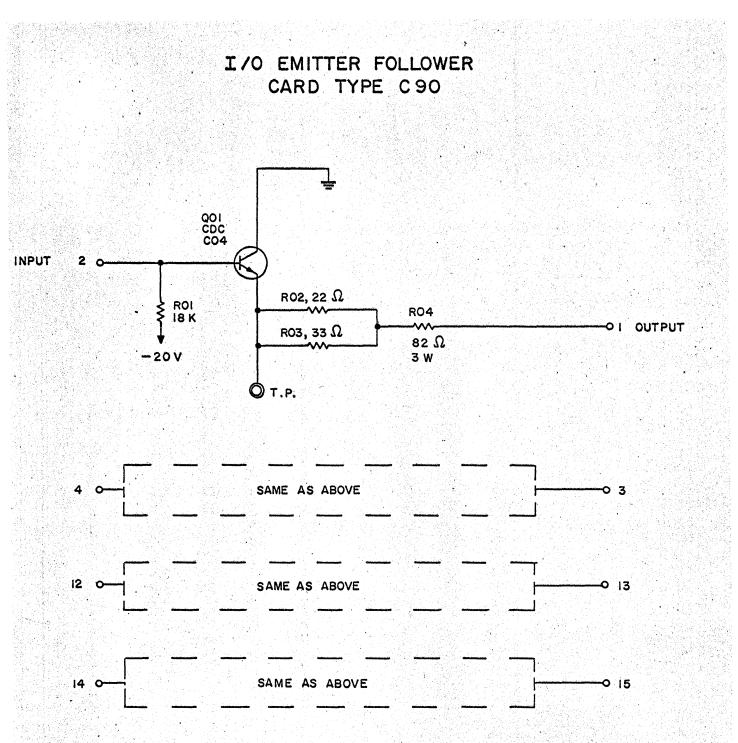

| I/O Emitter Follower   | 3-107 |

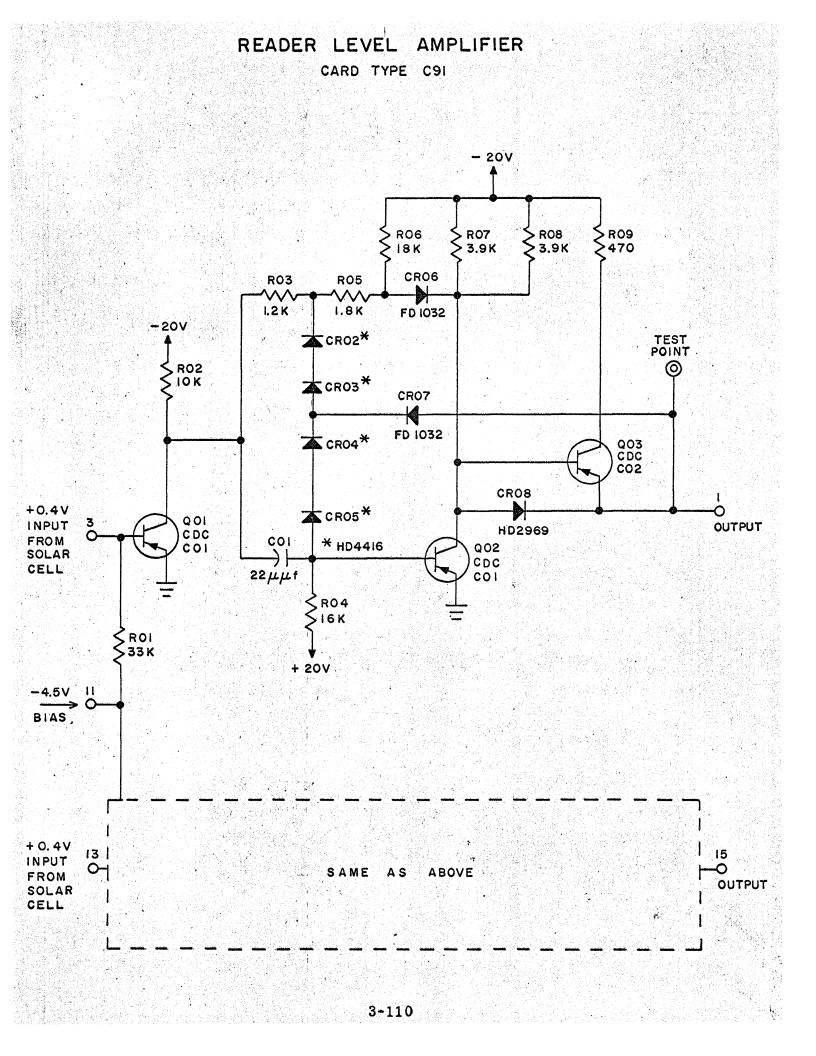

| Reader Level Amplifier | 3-109 |

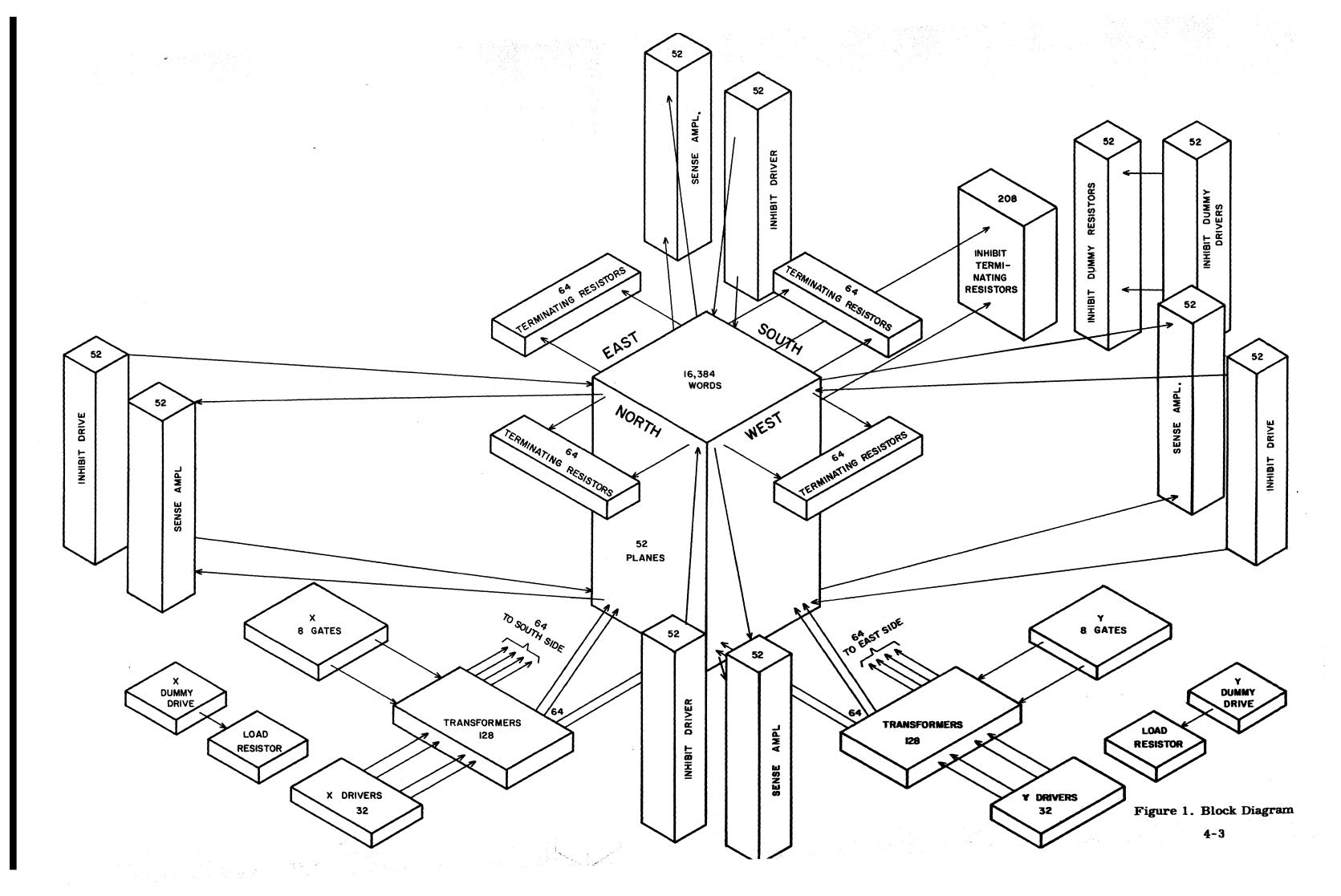

# Chapter 4 - Magnetic Core Memory

| General                      | 4-1  |

|------------------------------|------|

| Magnetic                     | 4-1  |

| Memory Plane                 | 4-9  |

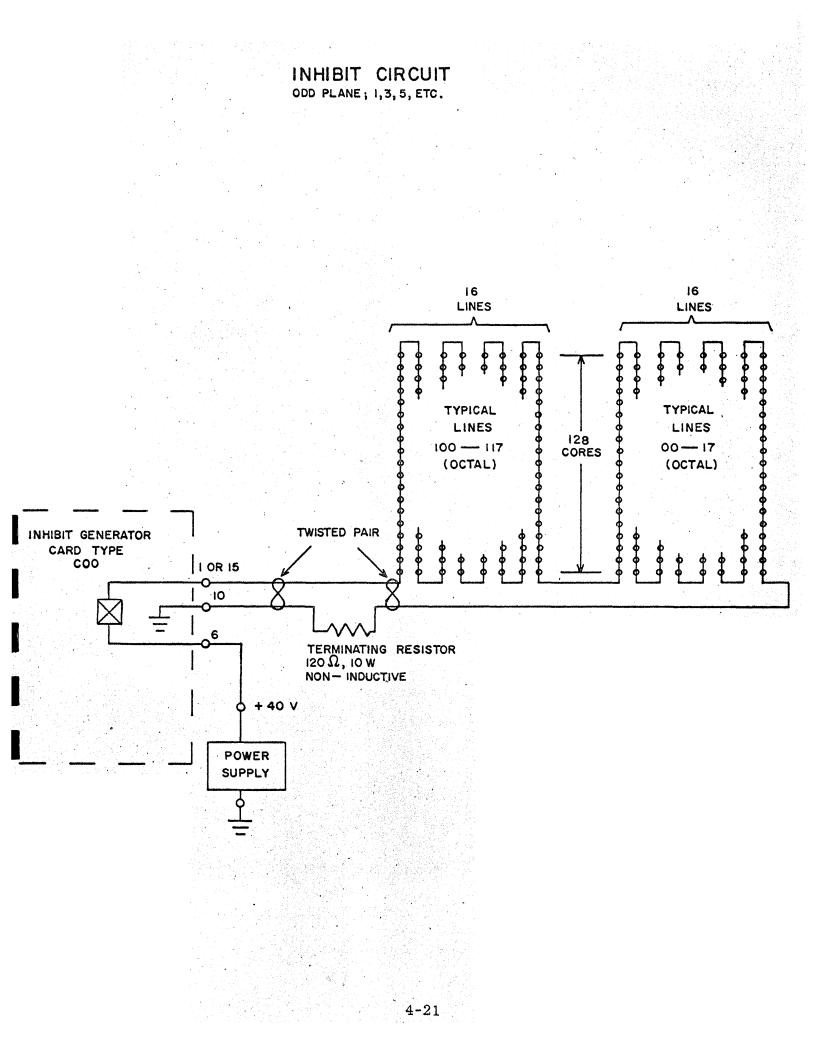

| Memory Stack                 | 4-9  |

| Windings                     | 4-14 |

| Sense Line                   | 4-17 |

| Inhibit Line                 | 4-17 |

| Drive Lines                  | 4-23 |

| Dummy Drive and Inhibit      | 4-26 |

| Transposition of Drive Lines | 4-26 |

| F | I | G | τ | J | R | E | S |  |

|---|---|---|---|---|---|---|---|--|

|---|---|---|---|---|---|---|---|--|

| FIGURES                                       | - 174<br> |

|-----------------------------------------------|-----------|

| Chapter 1 - Component Specifications          |           |

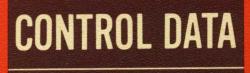

| Coil, Clock Oscillator-Amplifier              | 1-13      |

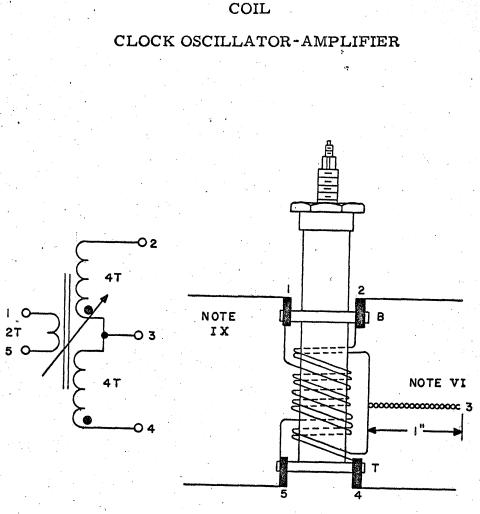

| Transformer, Pulse                            | 1-14      |

|                                               |           |

| Chapter 2 - Logic Card Types                  |           |

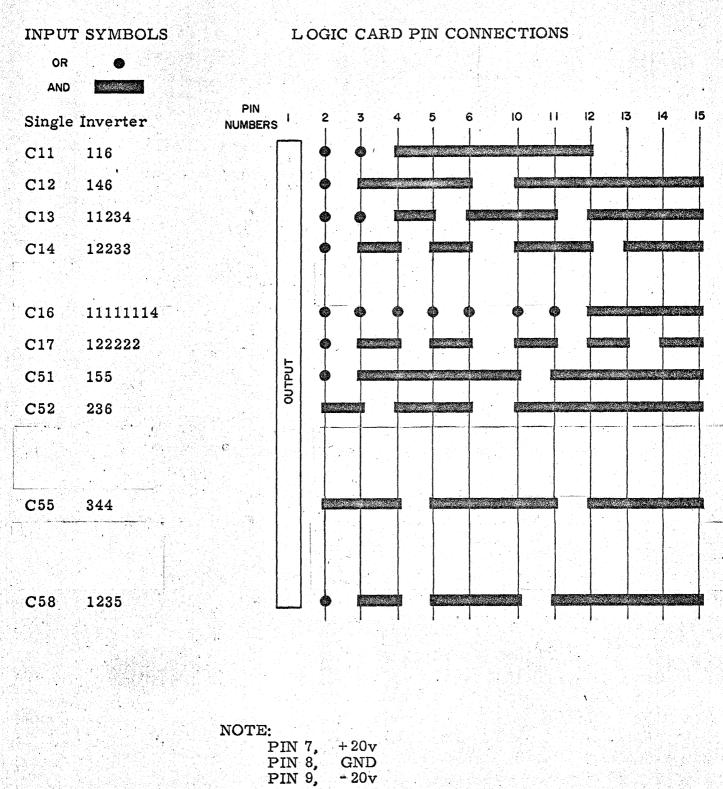

| Single Inverter Pin Connections               | 2-2       |

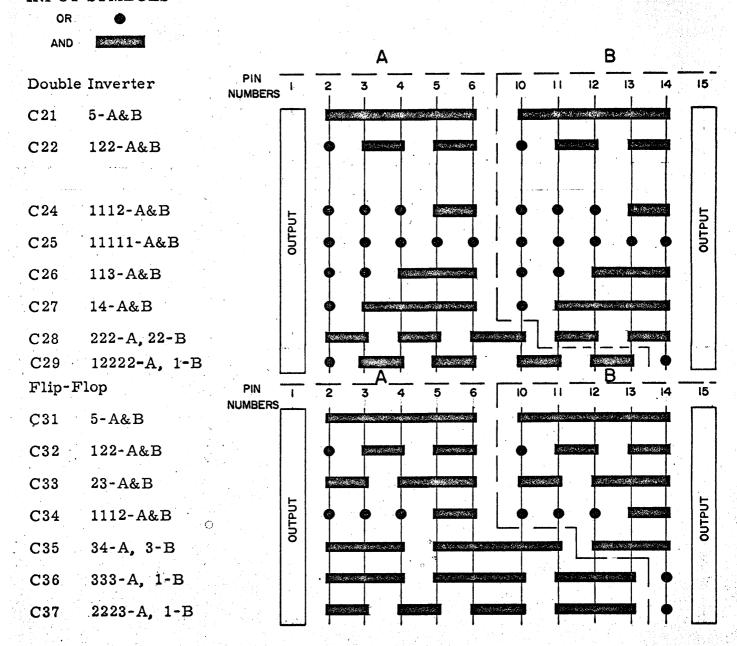

| Double Inverter and Flip-Flop Pin Connections | 2-3       |

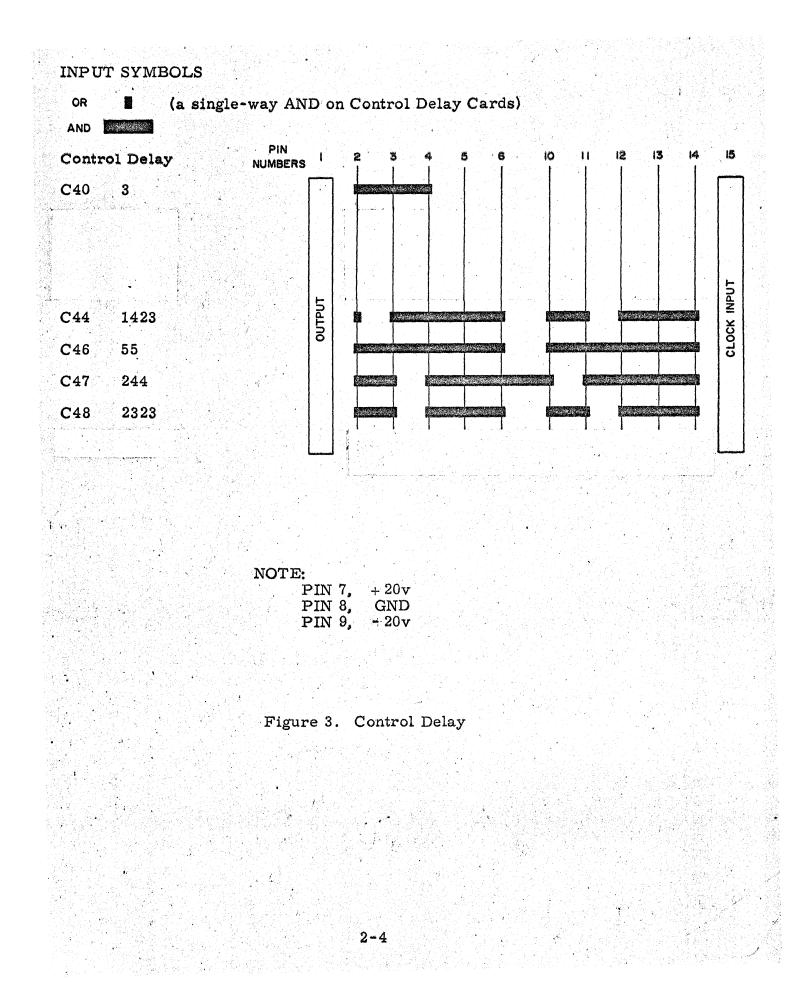

| Control Delay Pin Connections                 | 2-4       |

| Chapter 3 - Circuit Descriptions              | 4<br>     |

|                                               | 3-3       |

| Inhibit Generator, Odd Plane                  | 3-3       |

| Clock Oscillator-Amplifier<br>Clock Pyramid   | 3-7       |

| Clamp                                         | 3-13      |

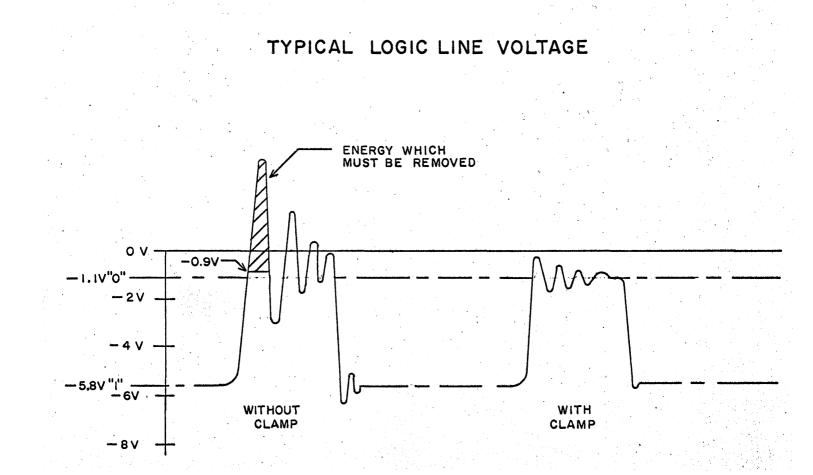

| Typical Logic Line Voltage                    | 3-13      |

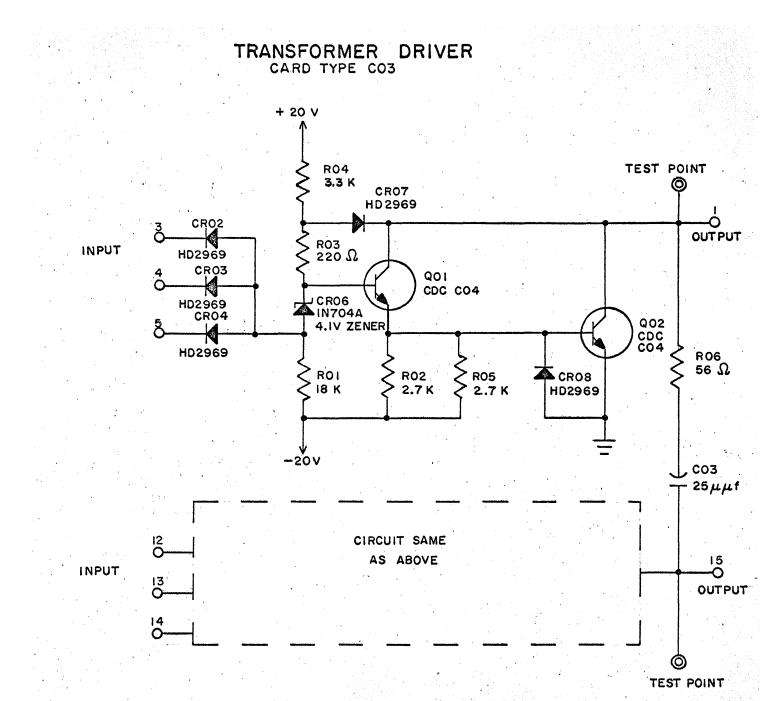

| Transformer Driver                            | 3-15      |

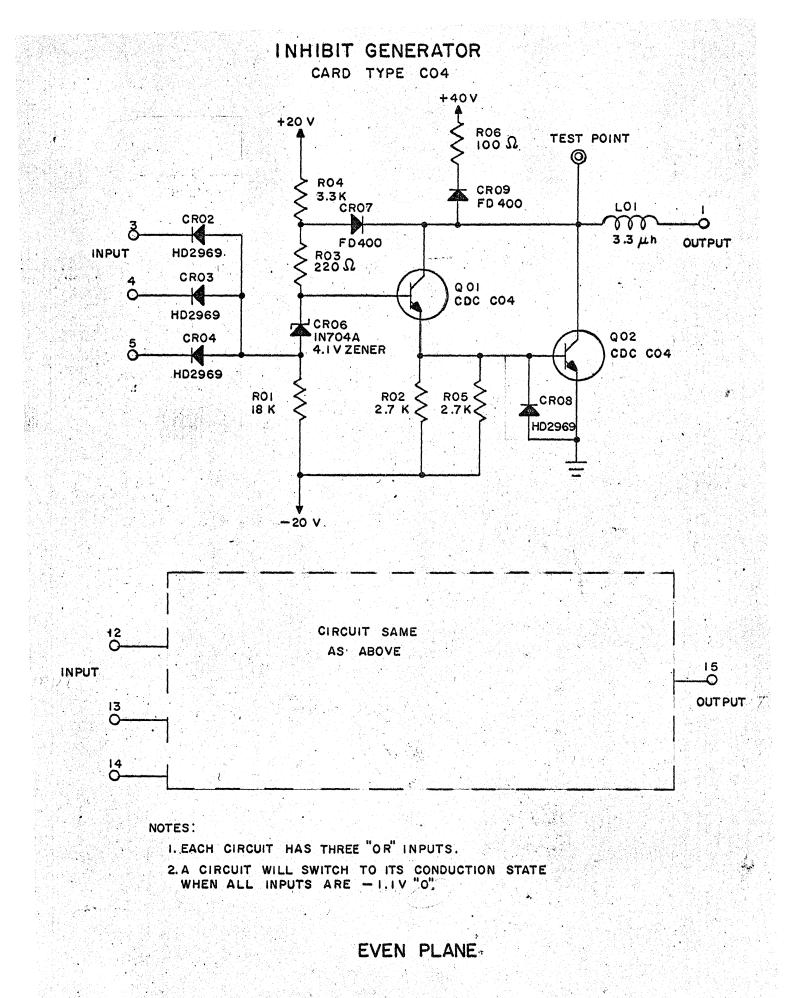

| Inhibit Generator, Even Plane                 | 3-18      |

| Gate                                          | 3-21      |

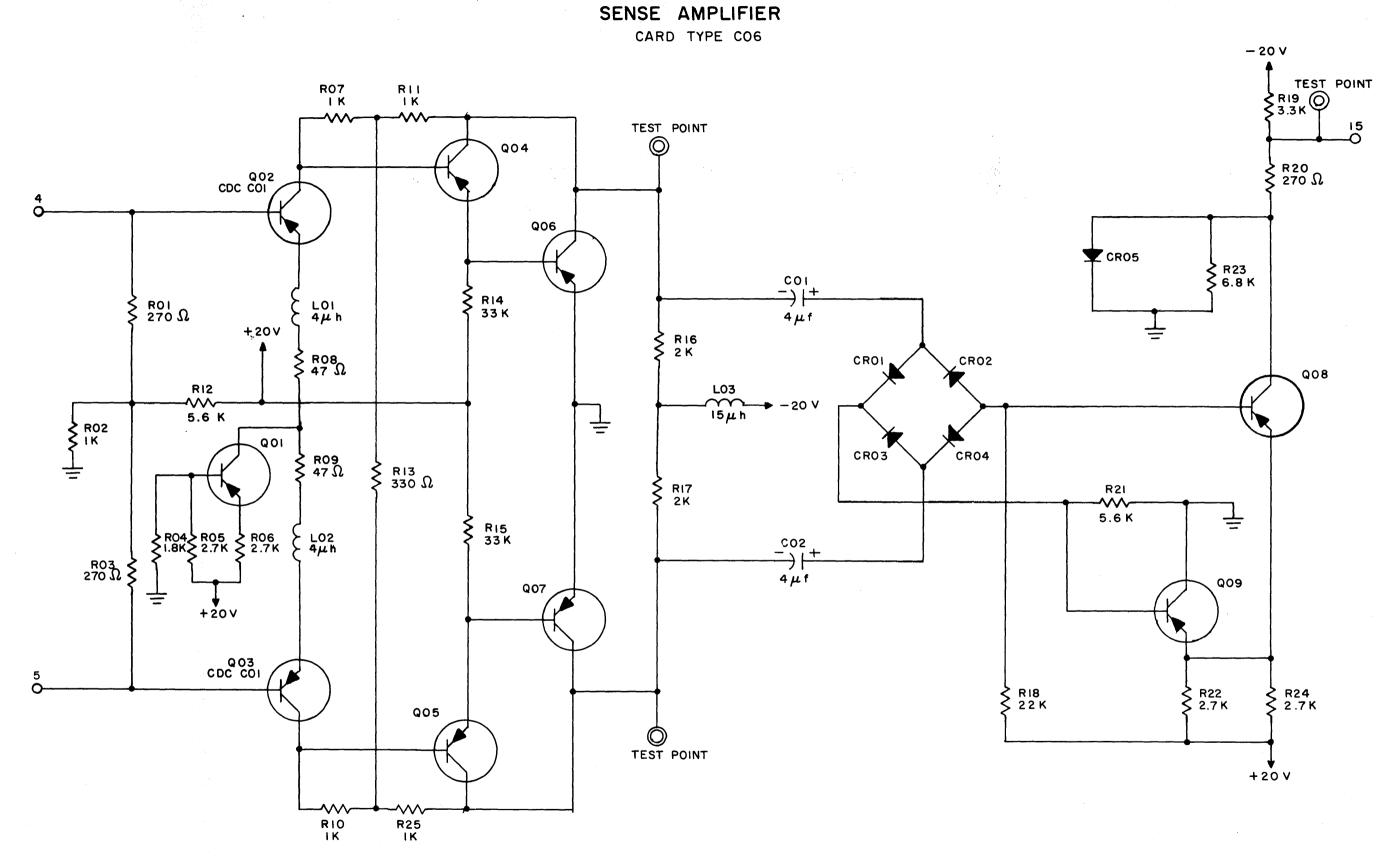

| Sense Amplifier                               | 3-25      |

| Emitter Follower                              | 3-30      |

| Delay Line Driver                             | 3-32      |

| Dummy Inhibit Generator                       | 3-34      |

| Memory Driver Transformer                     | 3-37      |

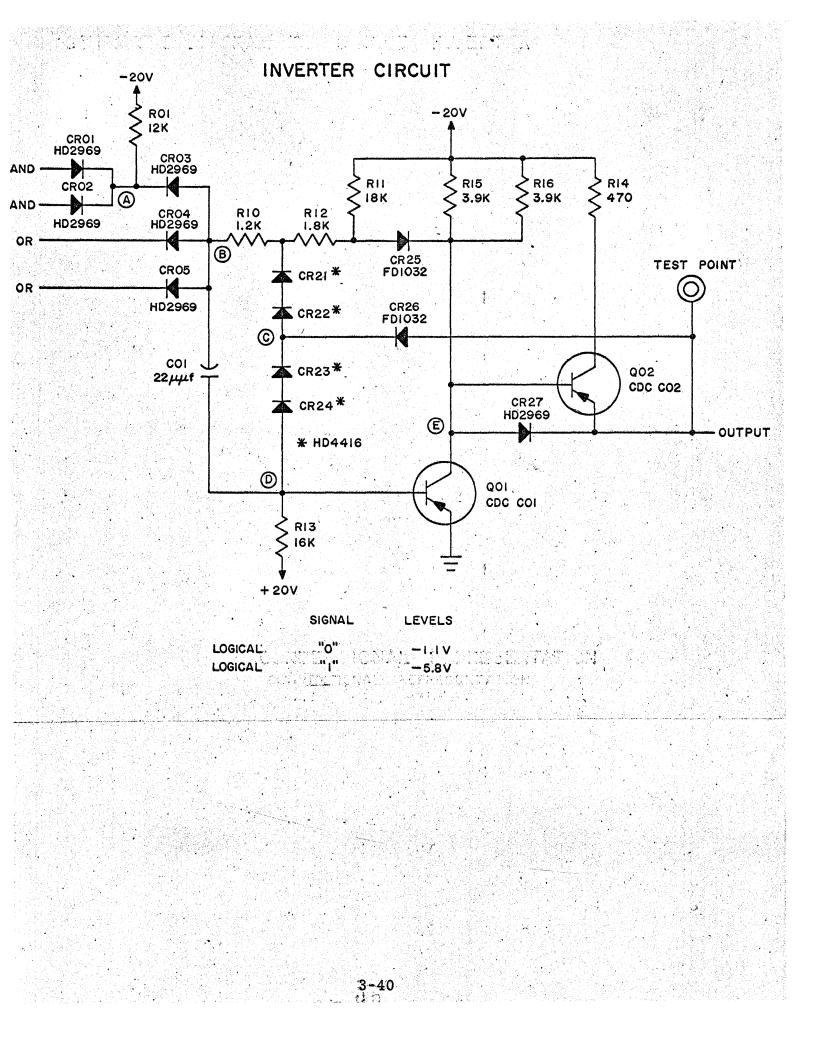

| Inverter Circuit                              | 3-40      |

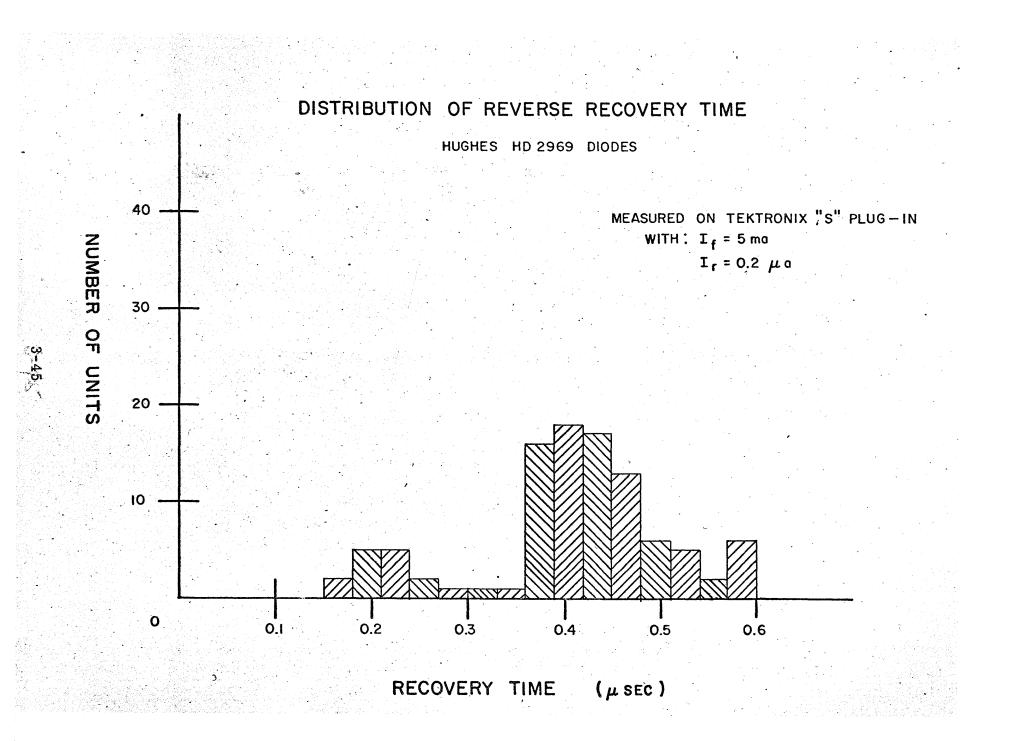

| Distribution of Reverse Recovery Time         | 3-45      |

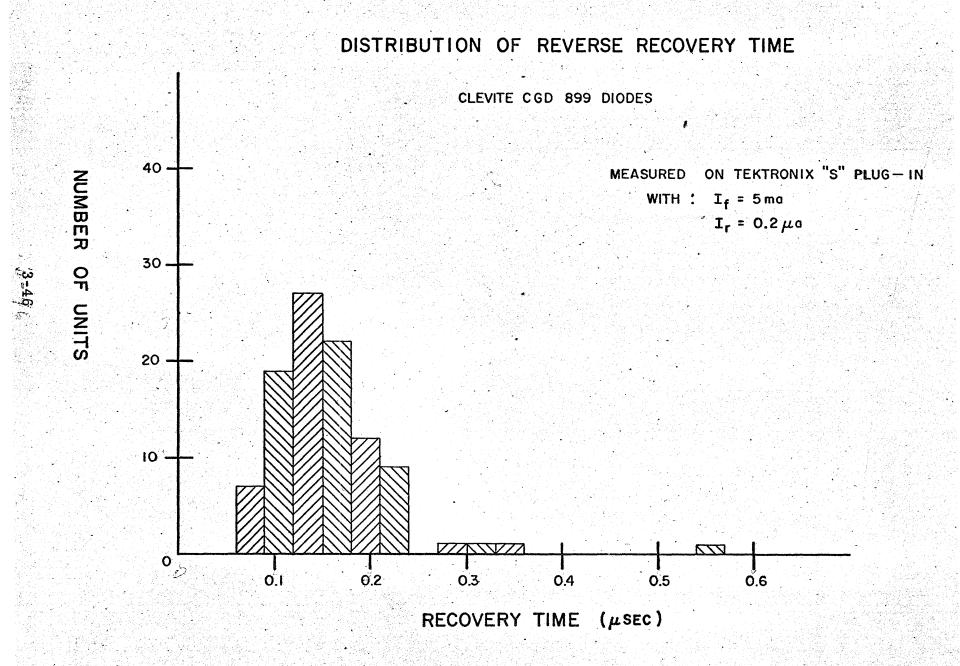

| Distribution of Reverse Recovery Time         | 3-46      |

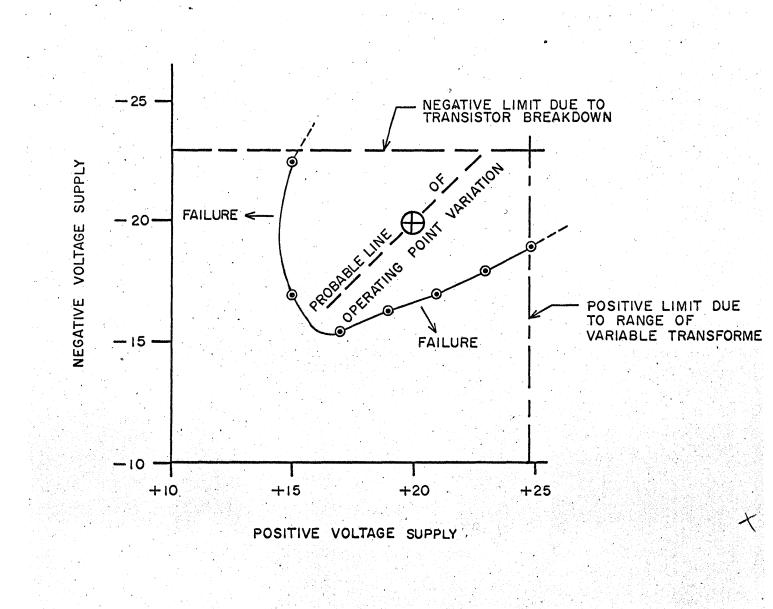

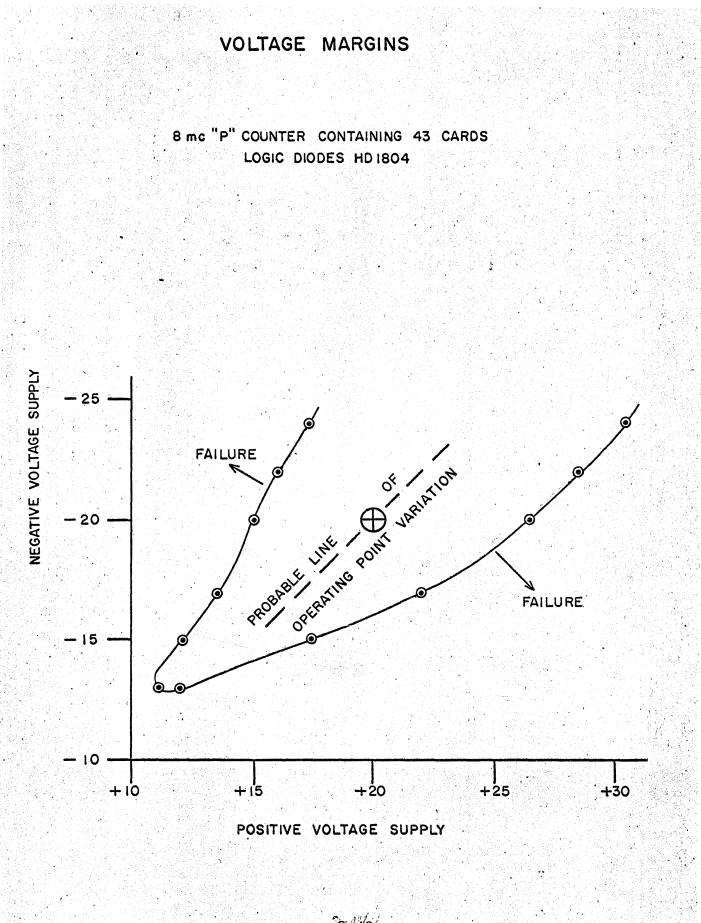

| Voltage Margins                               | 3-47      |

| Voltage Margins                               | 3-48      |

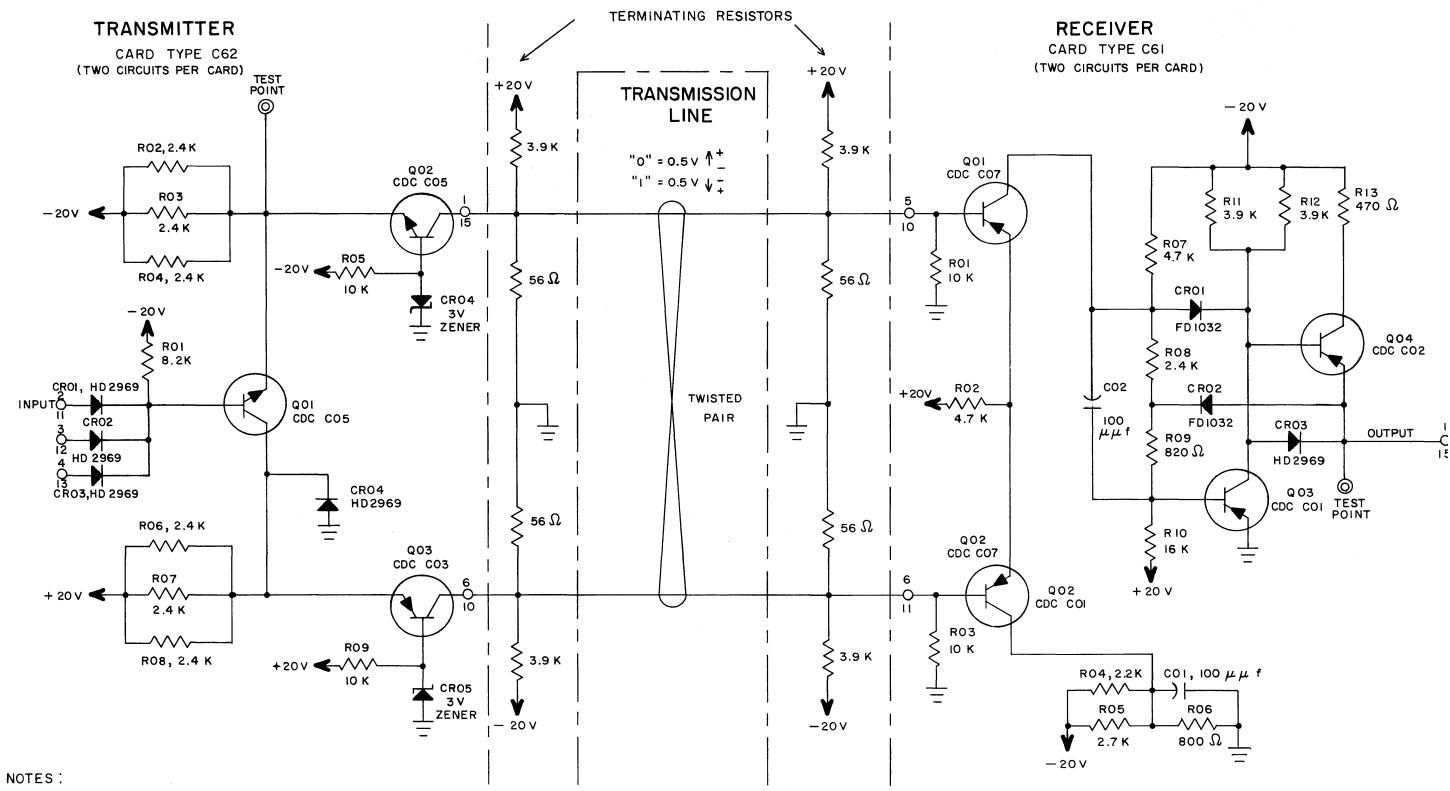

| Receiver                                      | 3-51      |

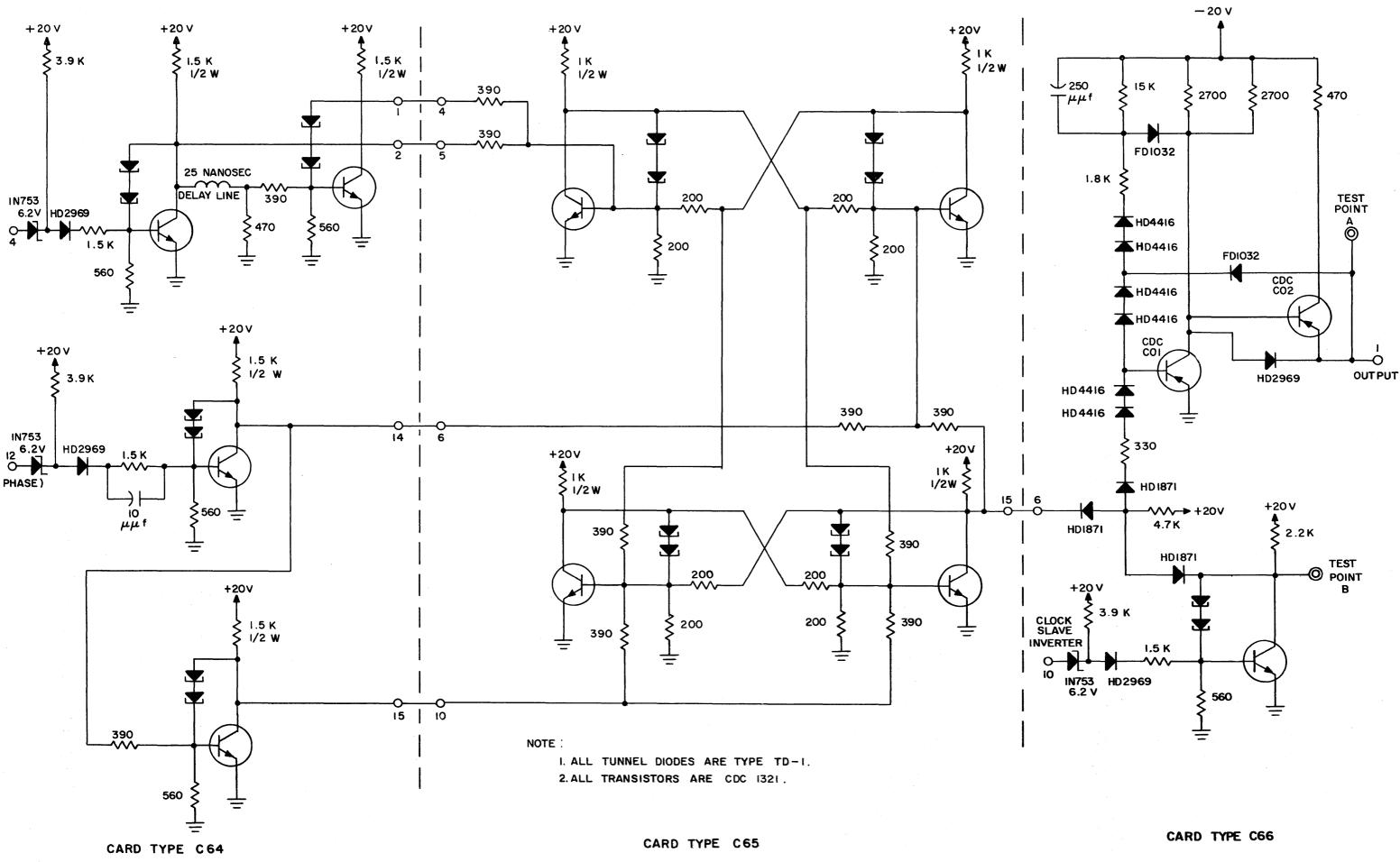

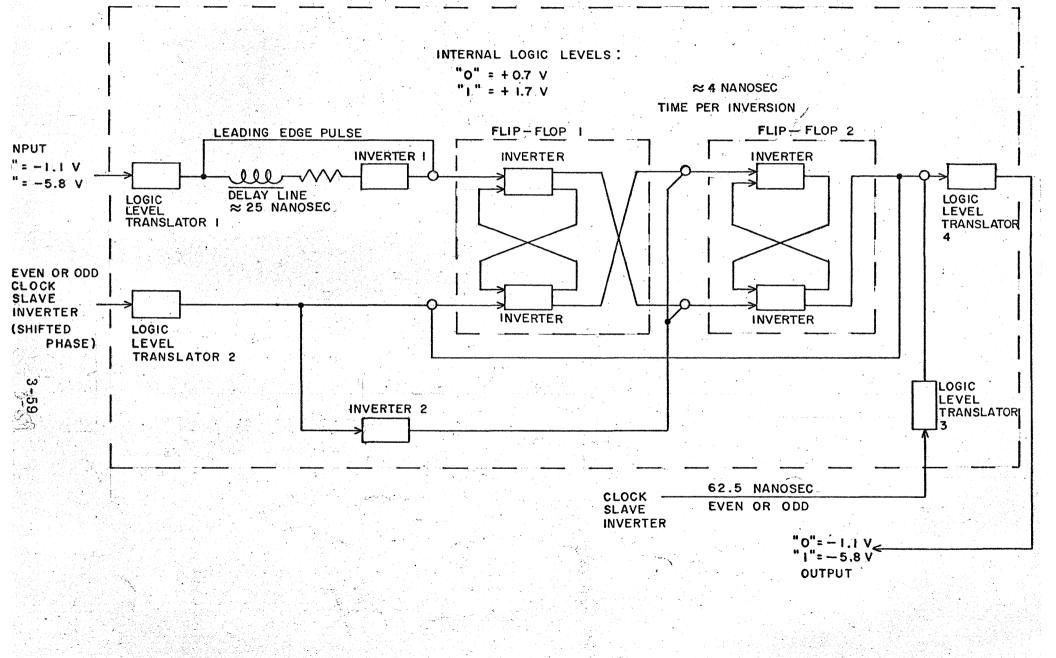

| Resync Circuit                                | 3-57      |

| Resync Circuit                                | 3-59      |

| Resync Circuit Timing Diagram                 | 3-60      |

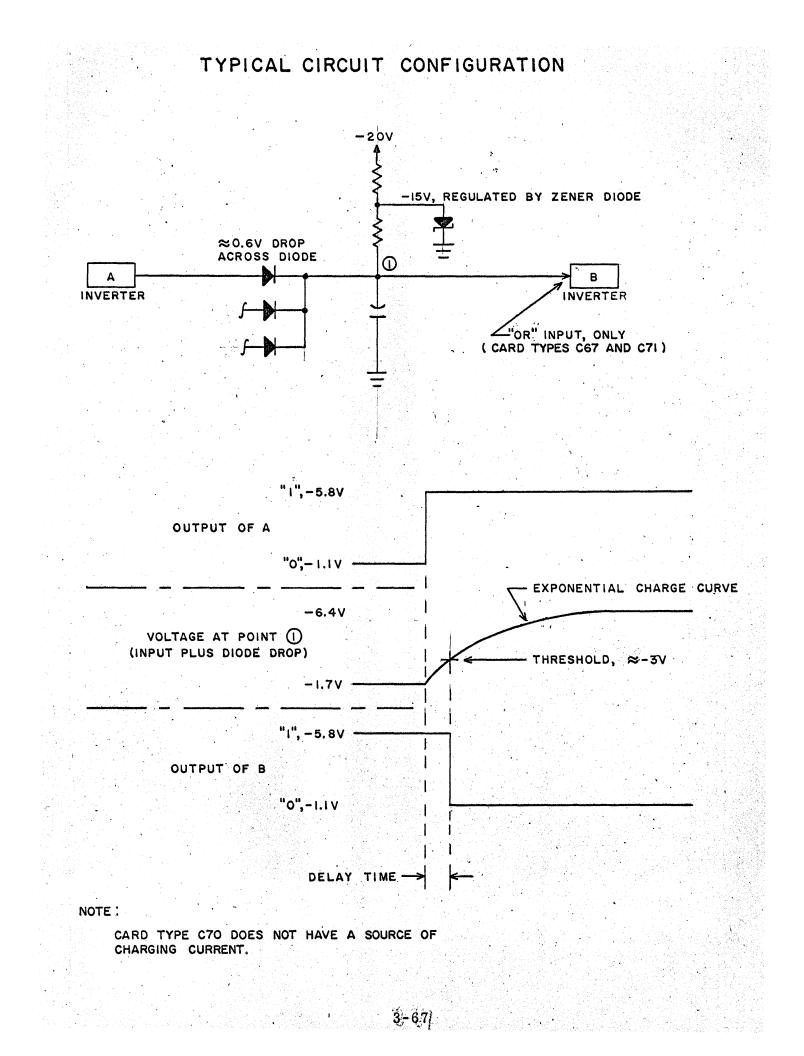

| Typical Circuit Configuration                 | 3-67      |

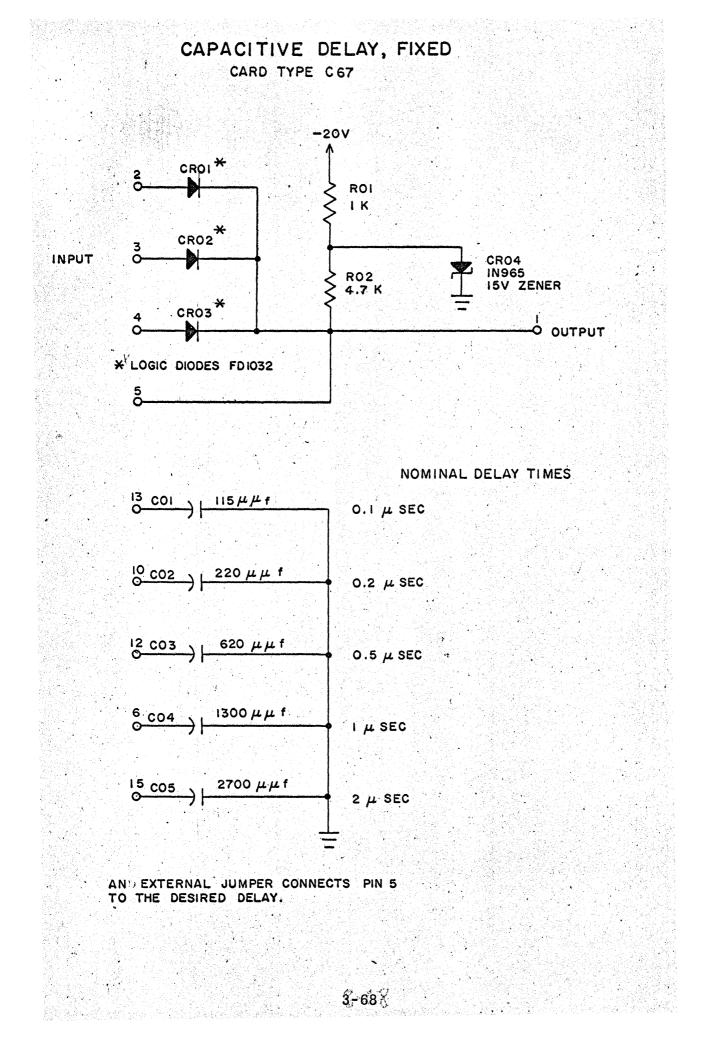

| Capacitive Delay, Fixed                       | 3-68      |

| vii                                           |           |

| -  | - C |          |   | 1.1 |    |   | - |          |       | * | -            |   |    | ÷. | 2 | - 24 | ÷ |

|----|-----|----------|---|-----|----|---|---|----------|-------|---|--------------|---|----|----|---|------|---|

|    | h   | <b>~</b> | * | +   | er | • | 2 | 3 ° 🛶    | 6 - E | L | $\mathbf{c}$ | ~ | n  | 4  | L | 4    | ١ |

| خب |     | a.       | J | •   | сī |   | v | <u> </u> | ÷.,   | Ľ | Ŵ            | U | 11 | •  |   | u    | 1 |

|    |     |          |   |     |    |   |   |          |       |   |              |   |    |    |   |      |   |

| 한 가지 않는 것이 있는 것이 있는 것이 있는 것이 있는 것이 있는 것은 것은 것을 가지 않는 것이 있다. 가지 않는 것은 |    |

|----------------------------------------------------------------------------------------------------------|----|

| Chapter 3 - (Cont'd)                                                                                     |    |

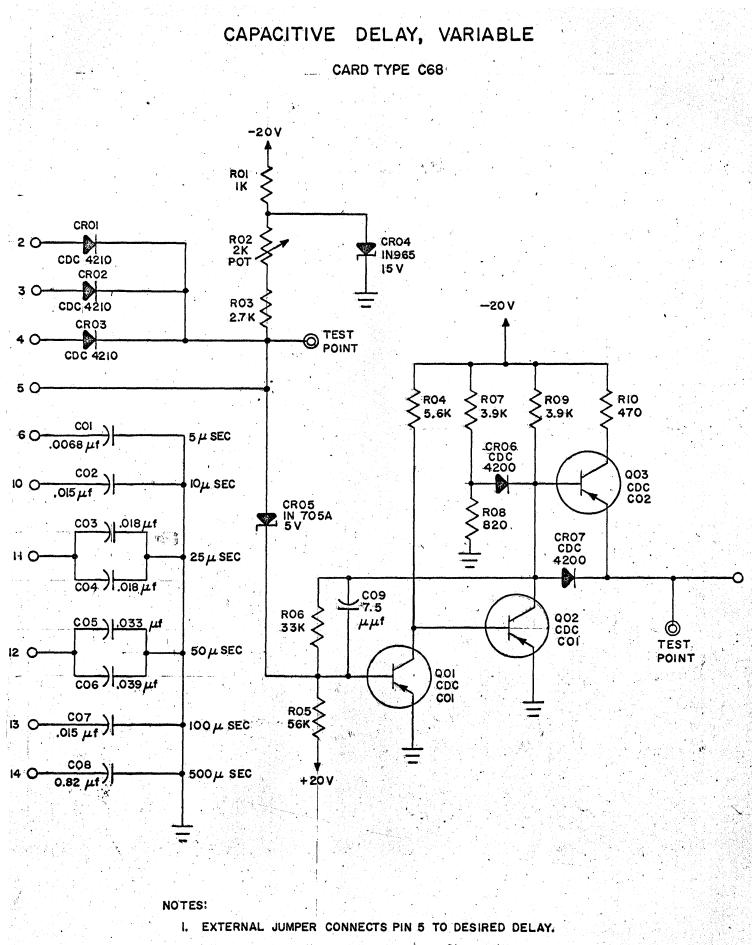

| Capacitive Delay, Variable                                                                               | 3- |

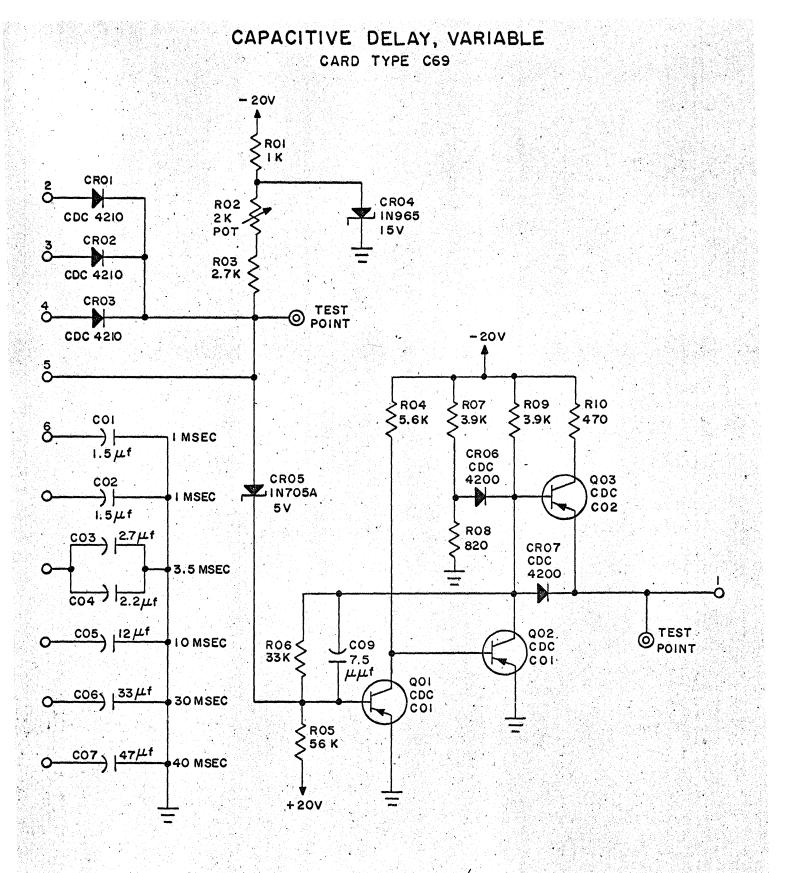

| Capacitive Delay, Variable                                                                               | 3- |

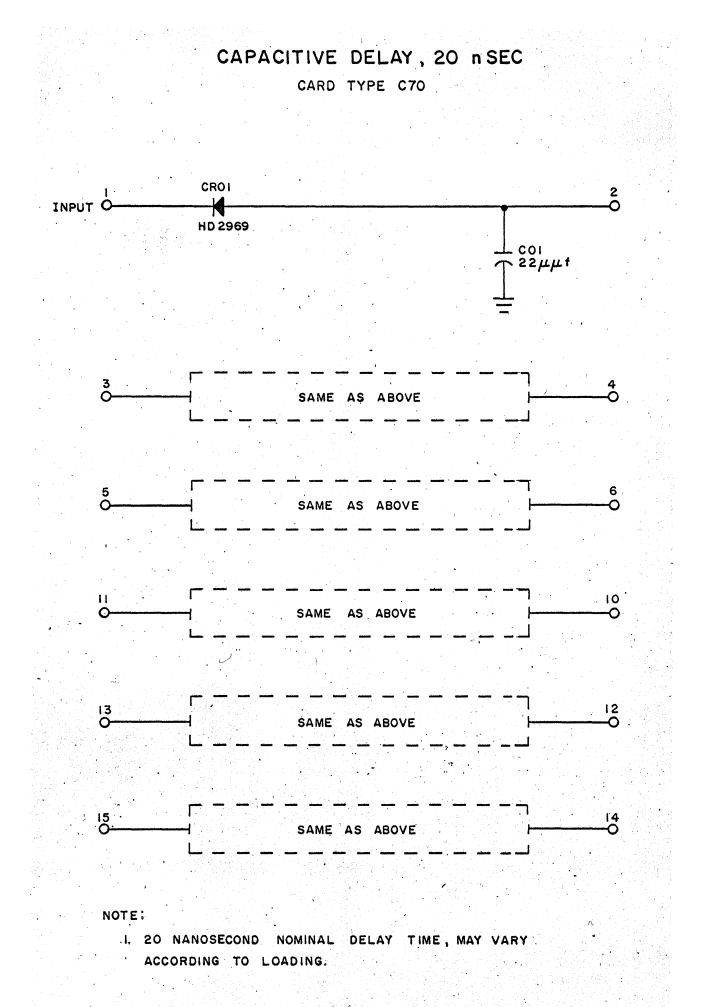

| Capacitive Delay, 20 nsec                                                                                | 3- |

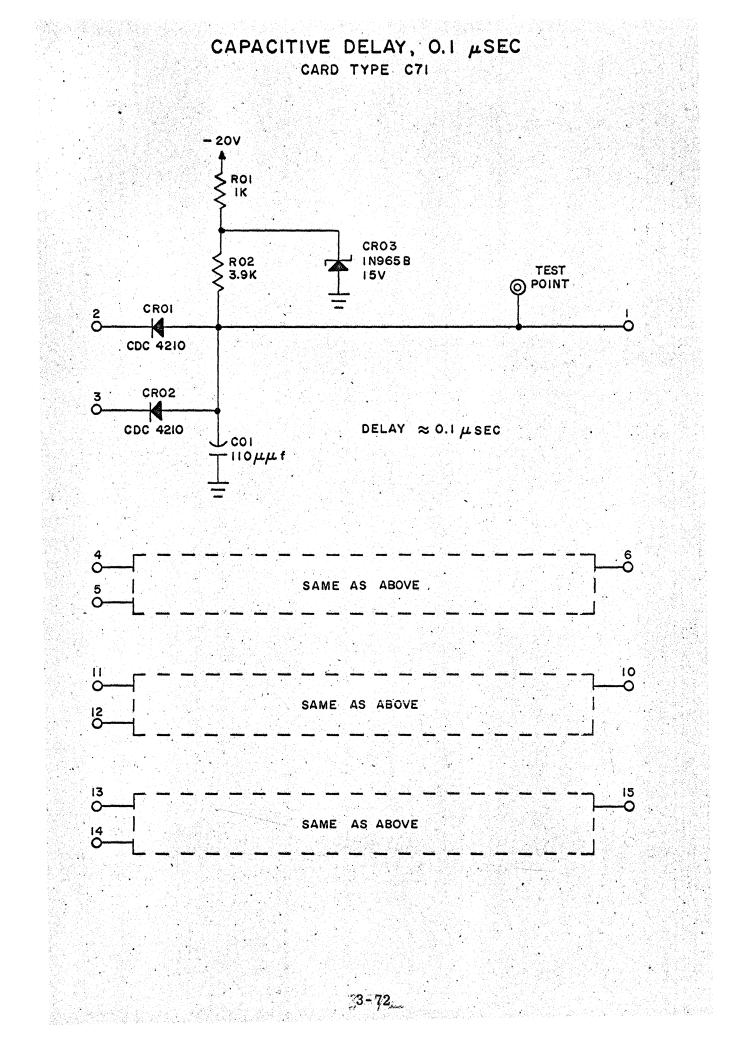

| Capacitive Delay, 0.1 usec                                                                               | 3- |

| Modified M <sup></sup> Input                                                                             | 3- |

| Modified L <sup></sup> Output                                                                            | 3- |

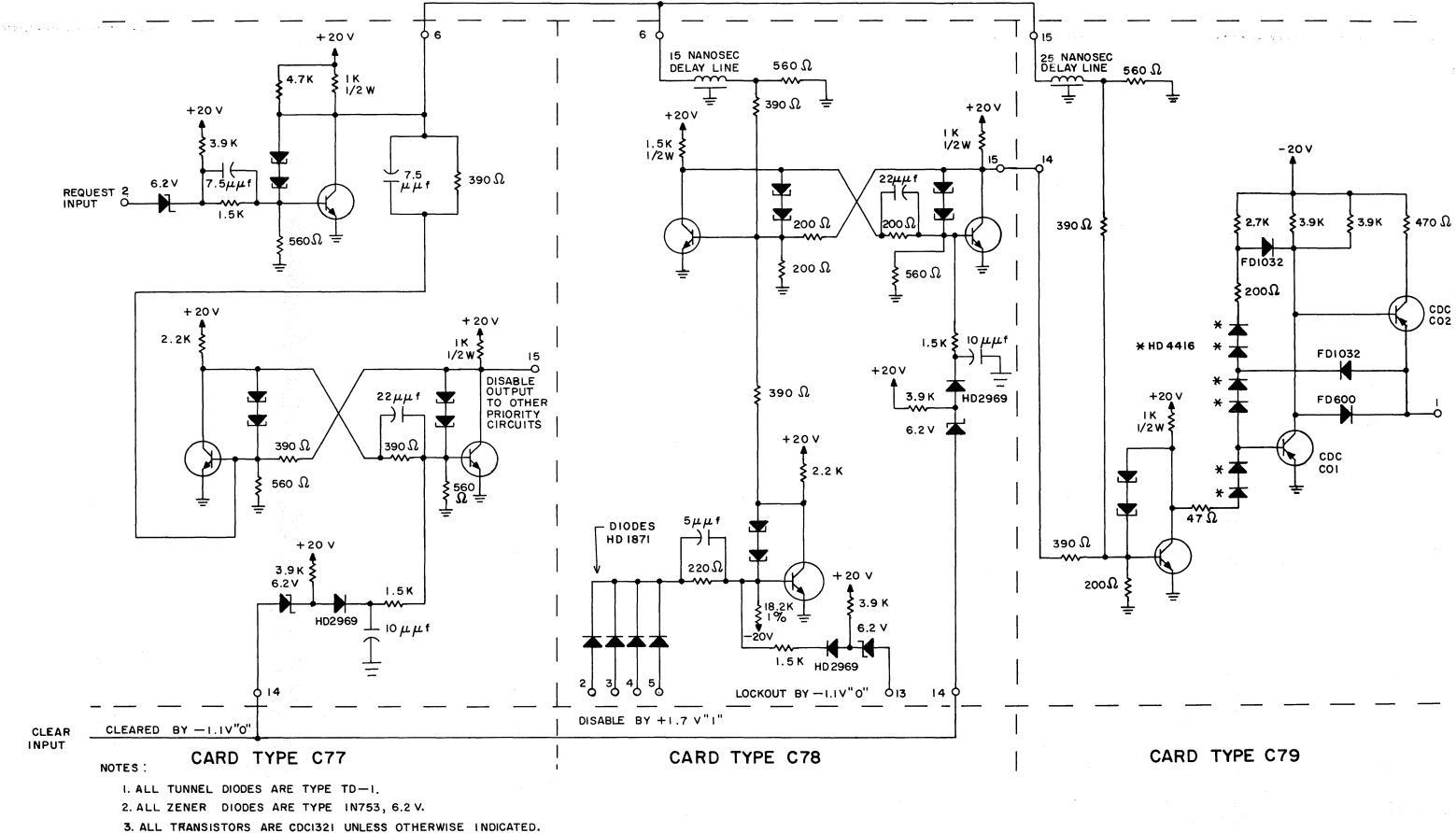

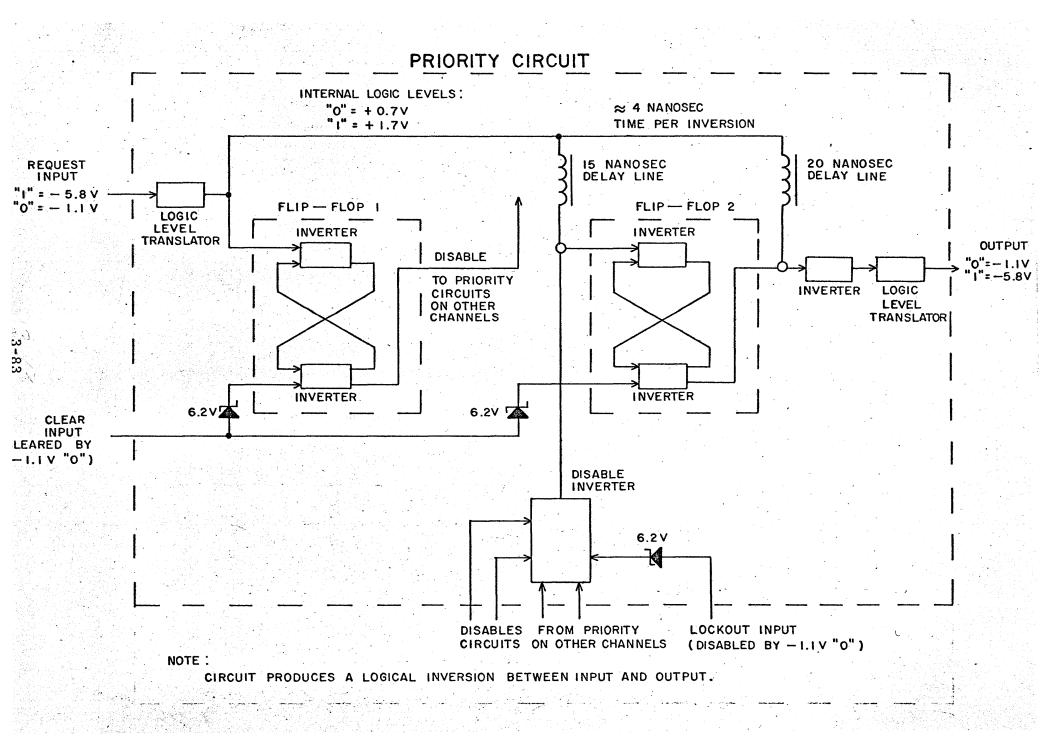

| Priority Circuit                                                                                         | 3- |

| Priority Circuit                                                                                         | 3- |

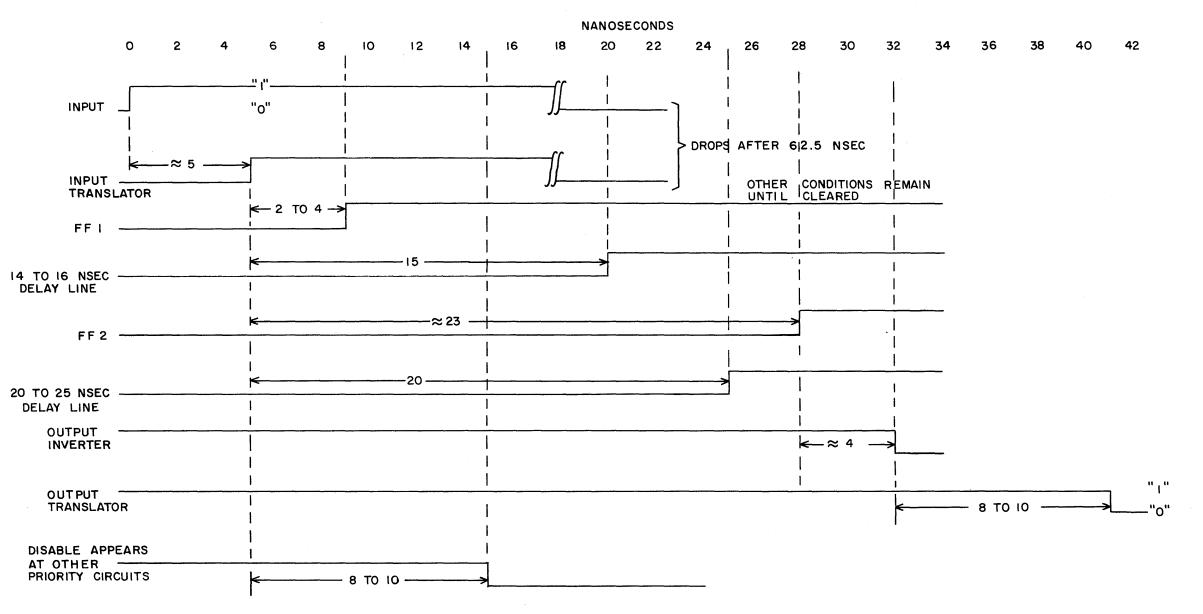

| Priority Circuit Timing Diagram                                                                          | 3- |

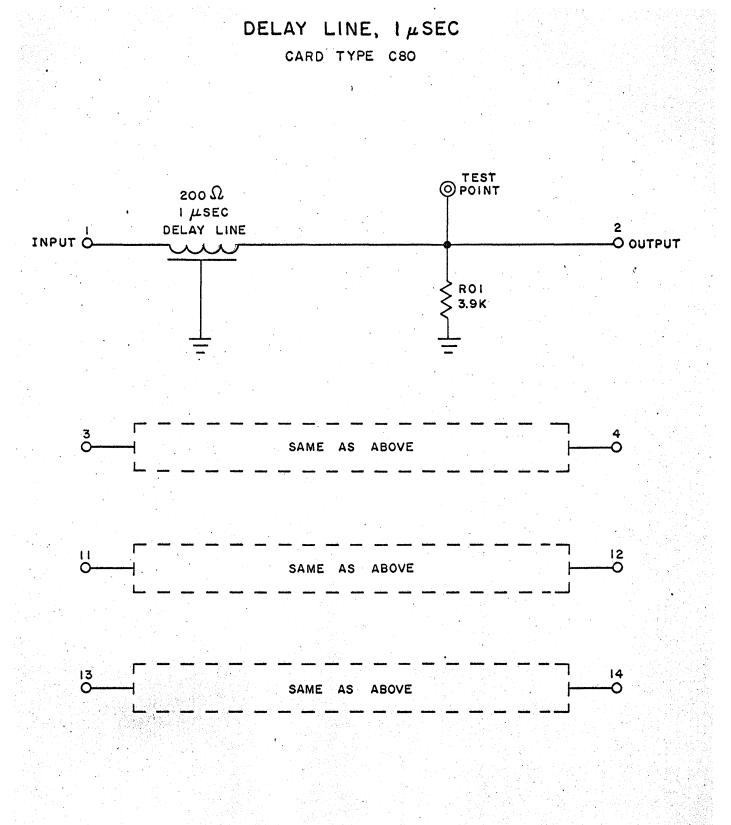

| Delay Line, 1 usec                                                                                       | 3- |

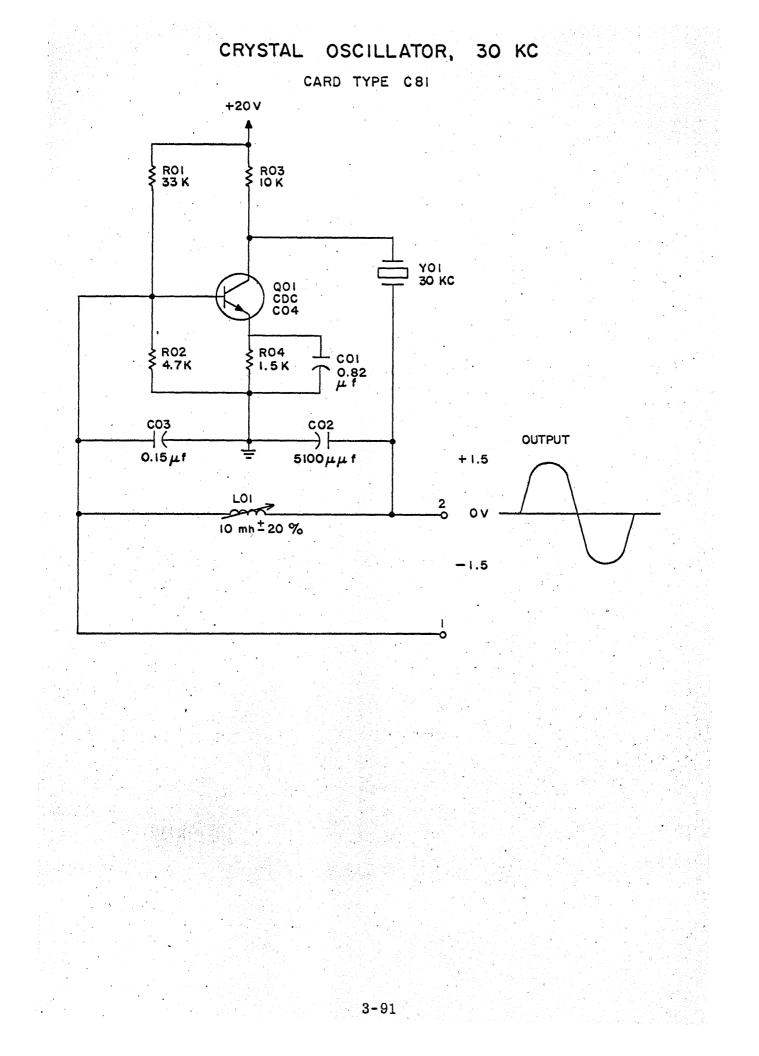

| Crystal Oscillator, 30 KC                                                                                | 3- |

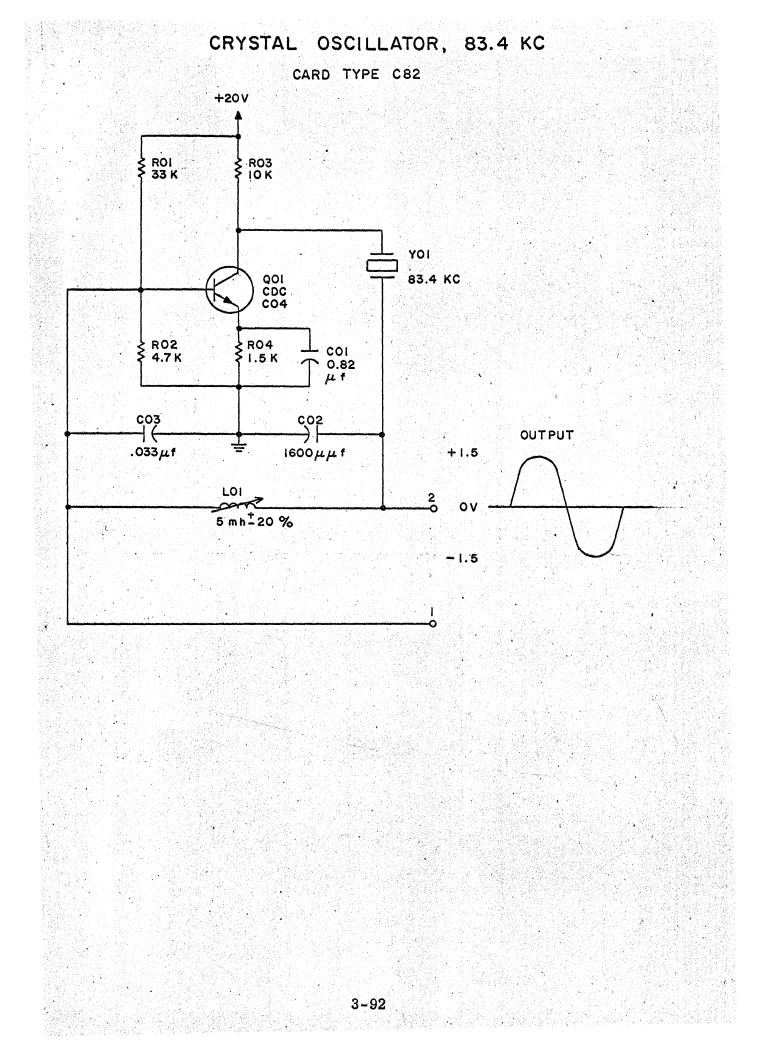

| Crystal Oscillator, 83.4 KC                                                                              | 3- |

| Relay Driver                                                                                             | 3- |

| I/O Sense Amplifier                                                                                      | 3- |

| I/O Memory Driver                                                                                        | 3- |

| I/O Memory Diverter                                                                                      | 3- |

| Amplifier-Shaper                                                                                         | 3- |

| I/O Emitter Follower                                                                                     | 3- |

| Reader Level Amplifier                                                                                   | 3- |

| Chapter 4 - Magnetic Core Memory                                                                         |    |

| Block Diagram                                                                                            | 4- |

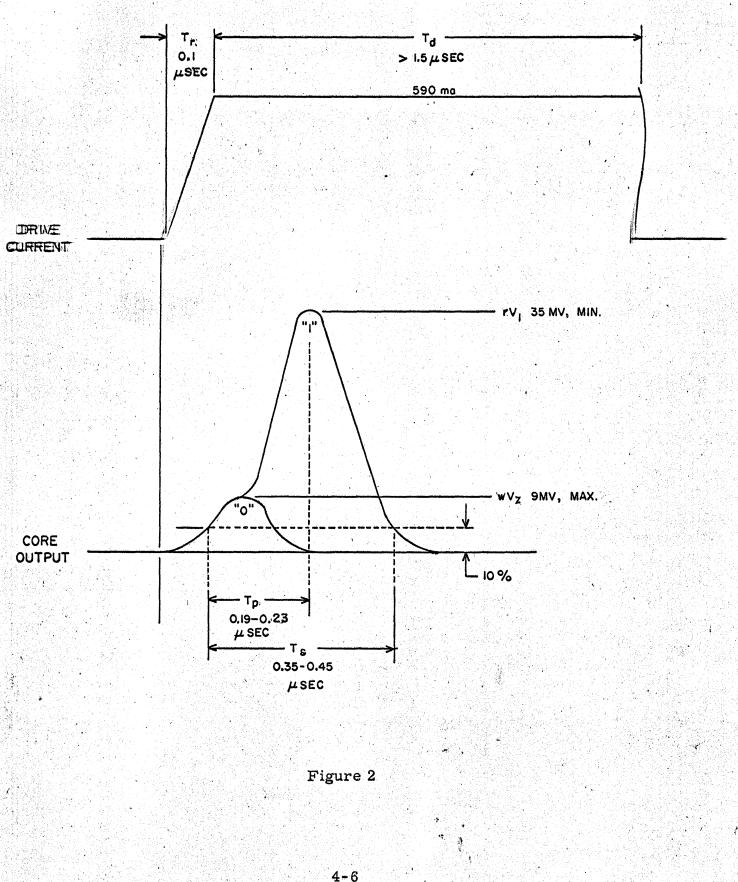

| Representative Core Test Waveforms                                                                       | 4- |

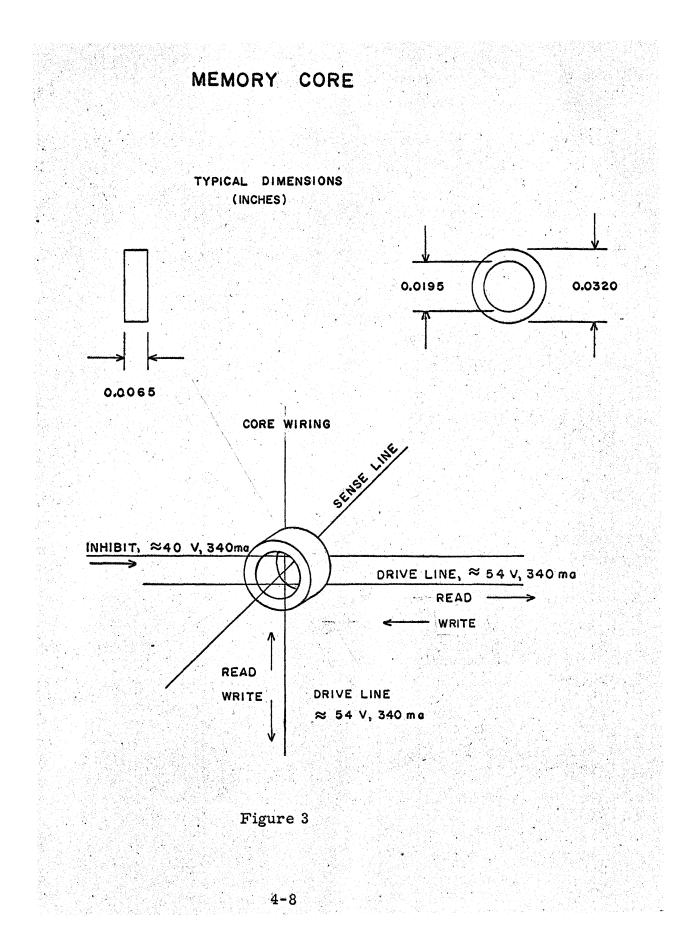

| Memory Core                                                                                              | 4- |

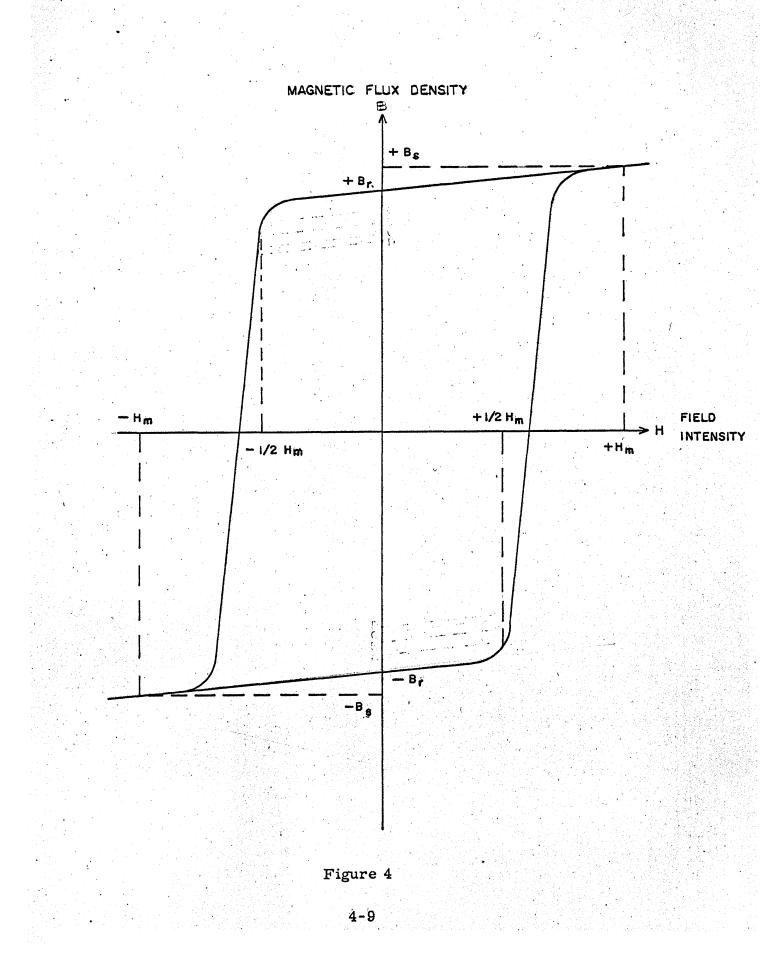

| Core Hysteresis Curve                                                                                    | 4- |

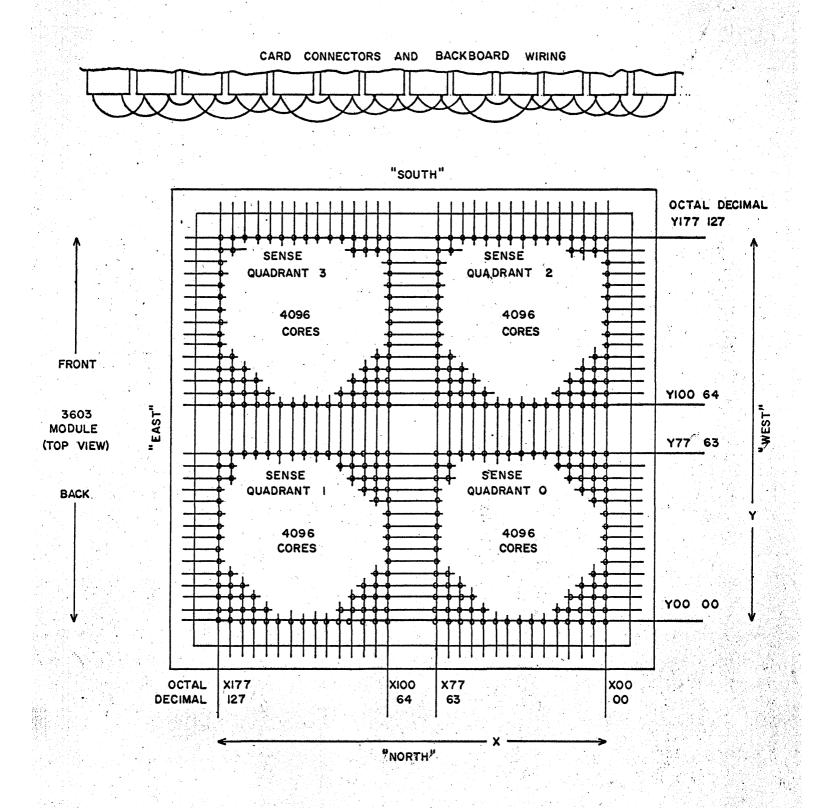

| Memory Plane Orientation                                                                                 | 4- |

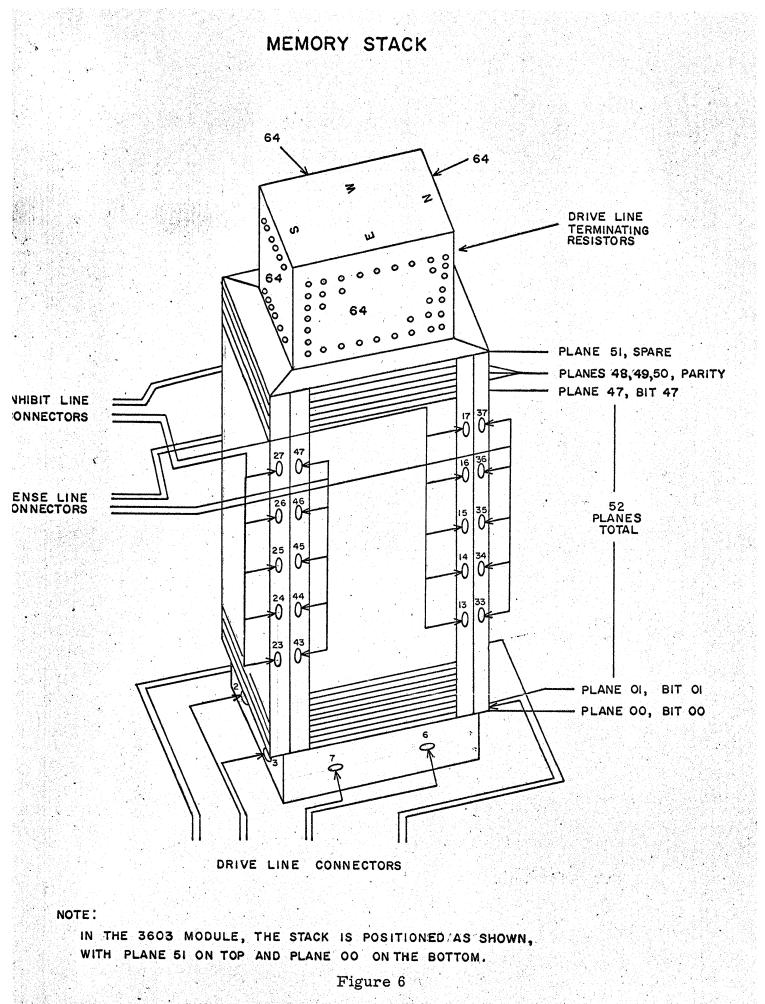

| Memory Stack ("Southeast" view)                                                                          | 4- |

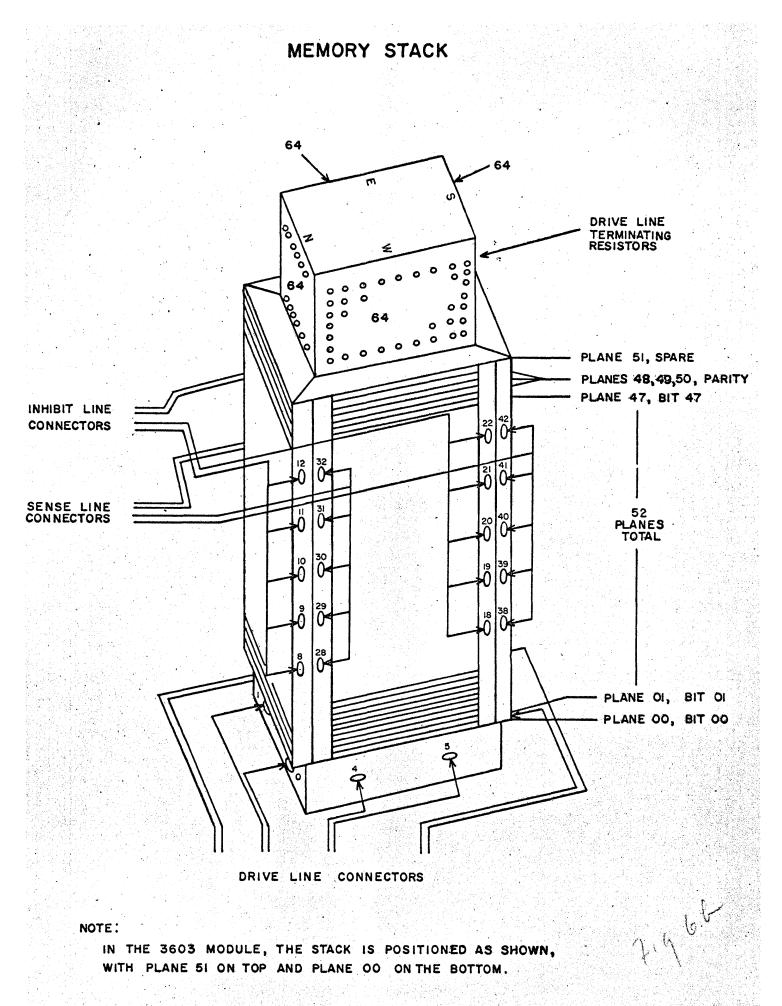

| Memory Stack ("Northwest" view)                                                                          | 4- |

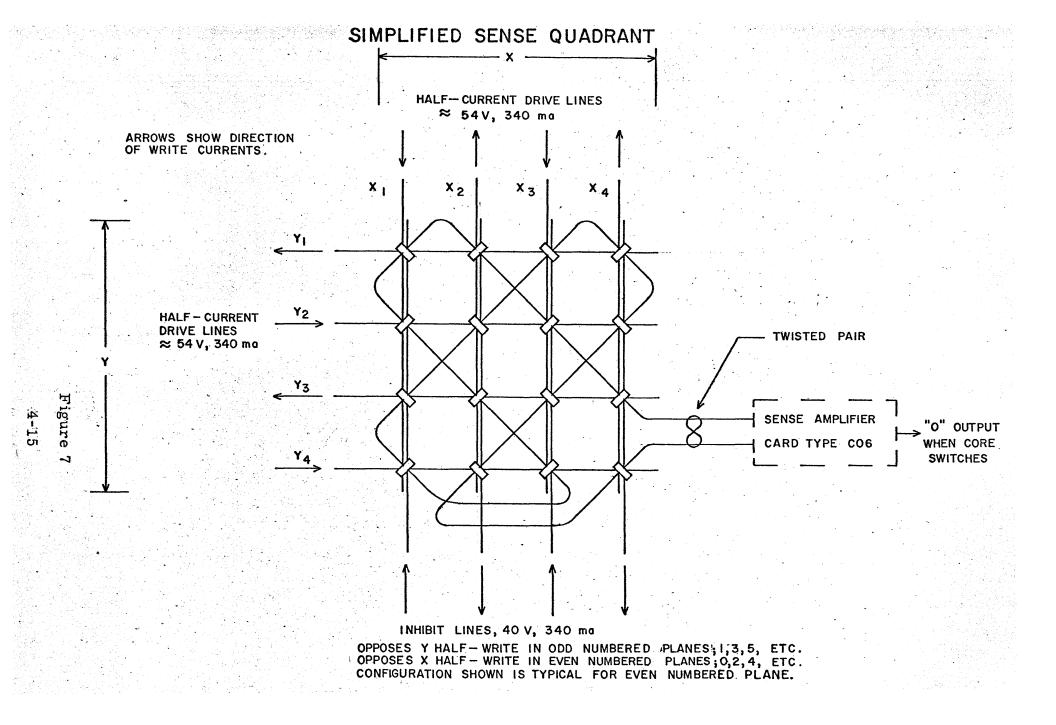

| Simplified Sense Quadrant                                                                                | 4- |

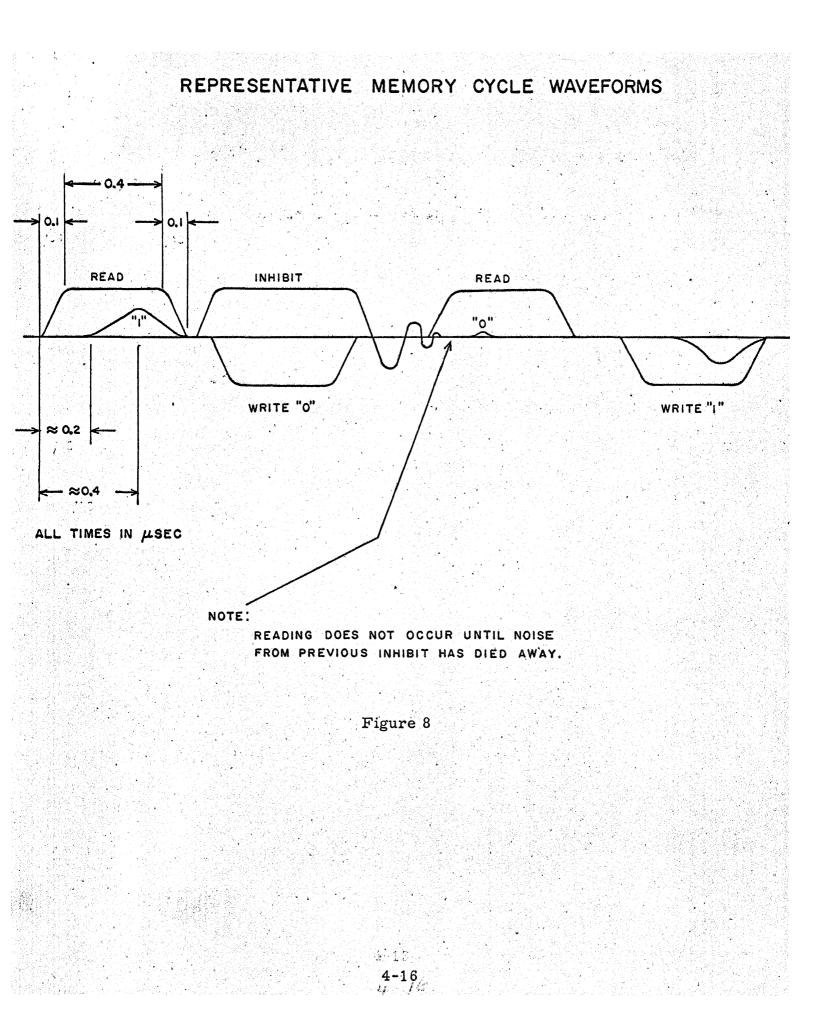

| Representative Memory Cycle Waveforms                                                                    | 4- |

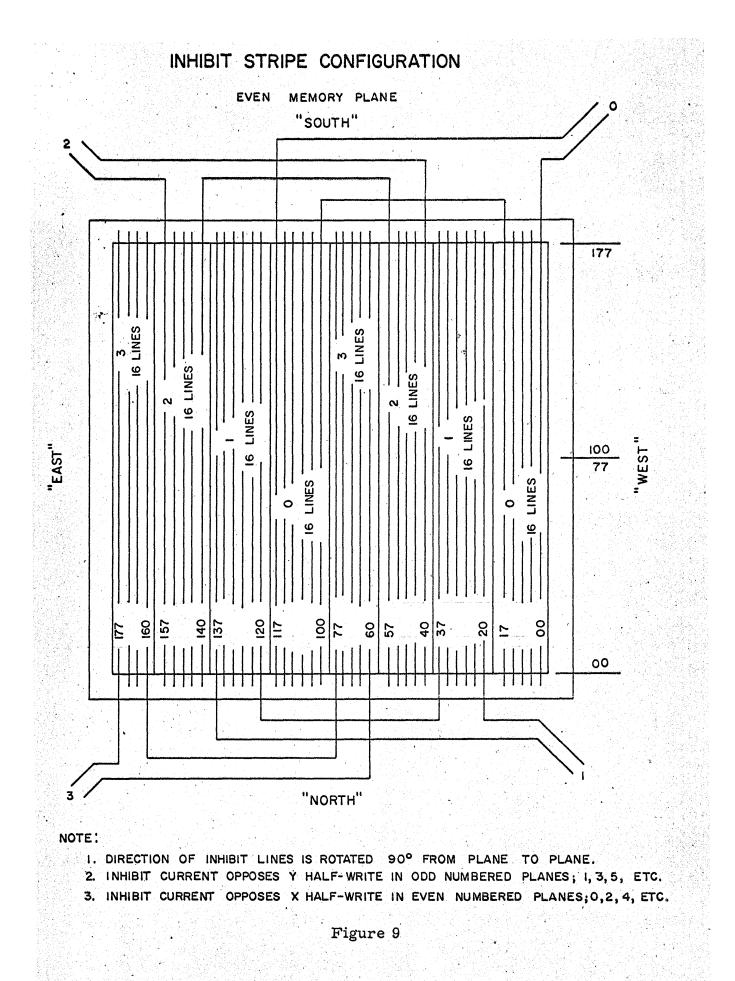

| Inhibit Stripe Configuration (Even Plane)                                                                | 4- |

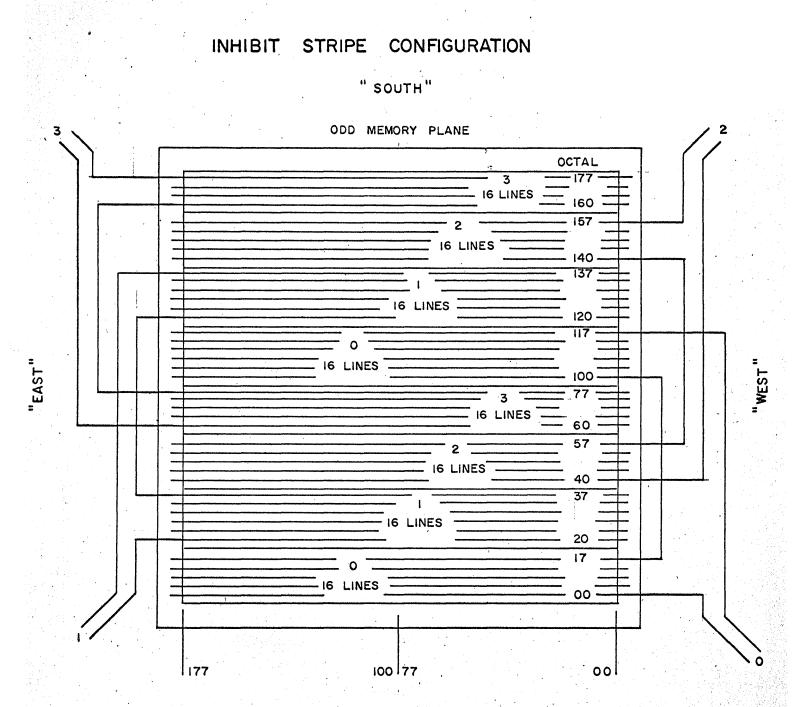

| Inhibit Stripe Configuration (Odd Plane)                                                                 | 4- |

| 에는 것은                                                                |    |

# FIGURES (CONT'D)

# Chapter 4 - (Cont'd)

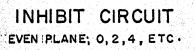

| Inhibit Circuit (Even Plane)      | 4-20             |

|-----------------------------------|------------------|

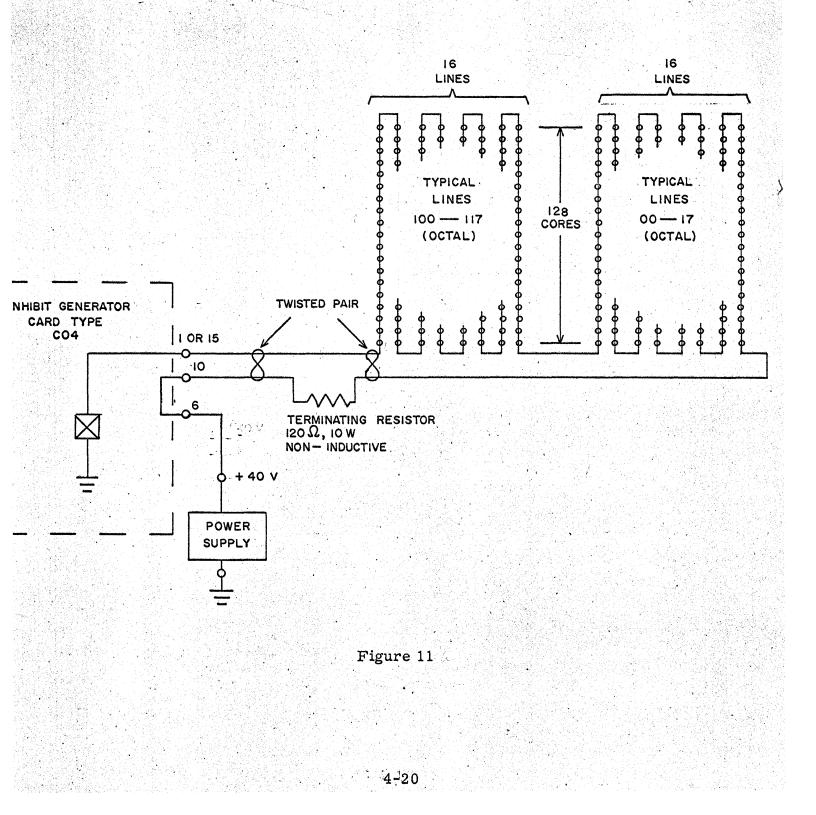

| Inhibit Circuit (Odd Plane)       | 4-21             |

| X and Y Drive Lines               | 4-24             |

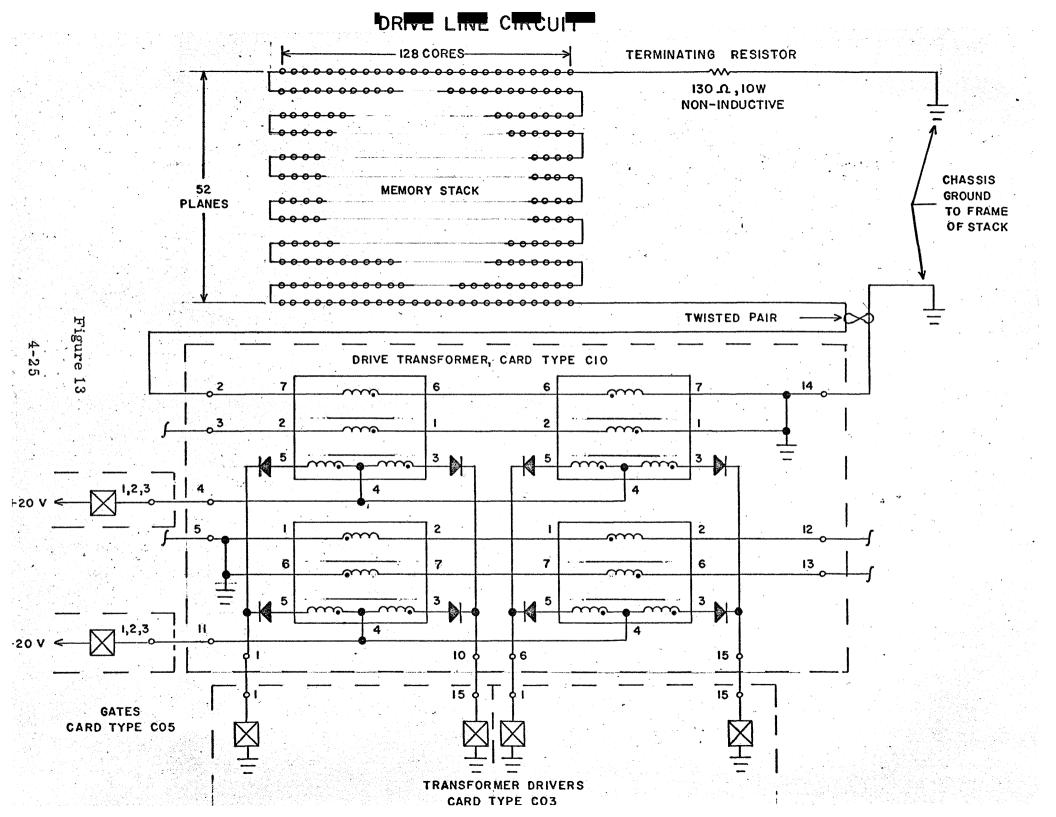

| Drive Line Circuit                | 4-25             |

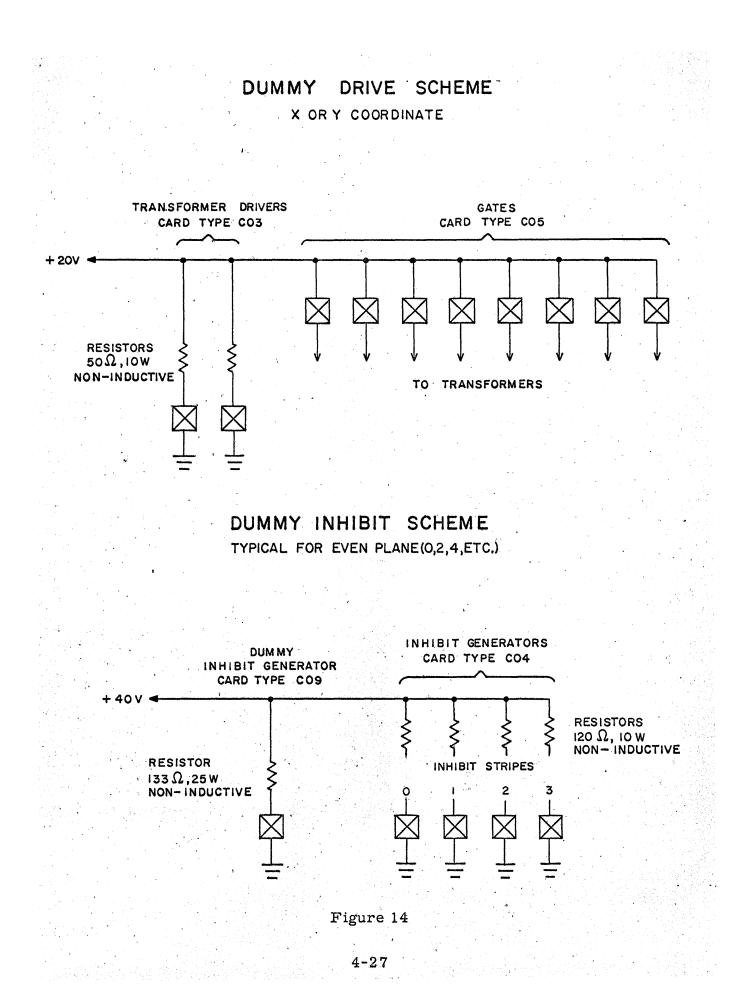

| Dummy Drive Scheme                | <b>4-26</b> ≥ () |

| Dummy Inhibit Scheme (Even Plane) | 4-27             |

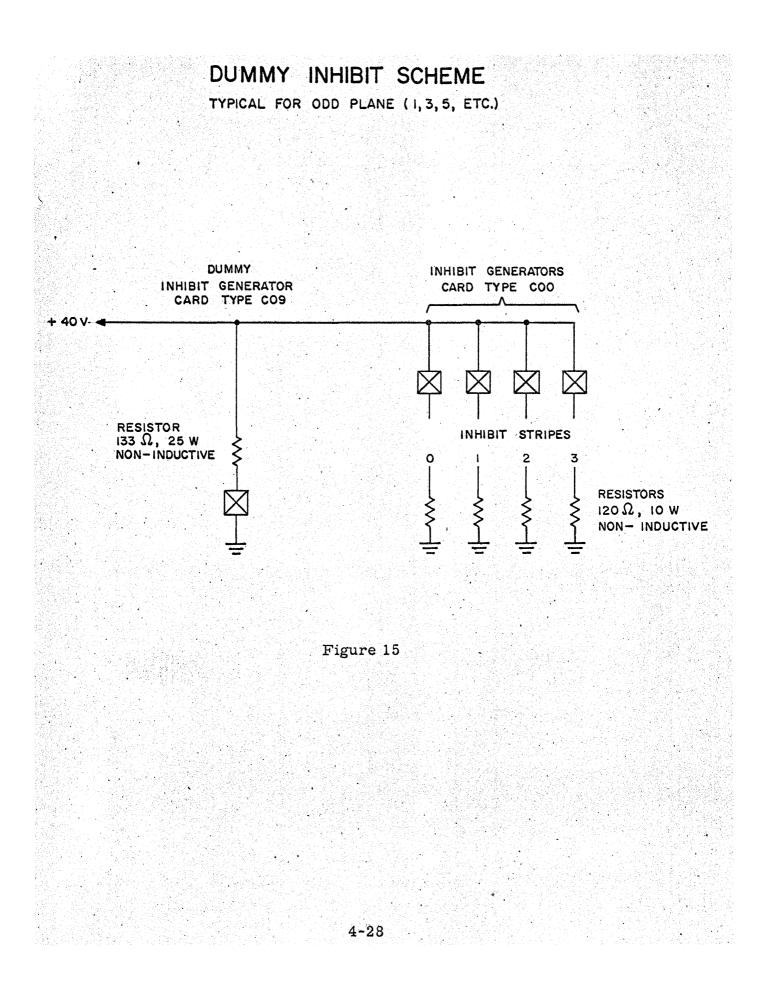

| Dummy Inhibit Scheme (Odd Plane)  | 4-28             |

|                                   | • •              |

#### TABLES

# Chapter 4 - Magnetic Core Memory

| 1   | Core Specifications                      | 4-5  |

|-----|------------------------------------------|------|

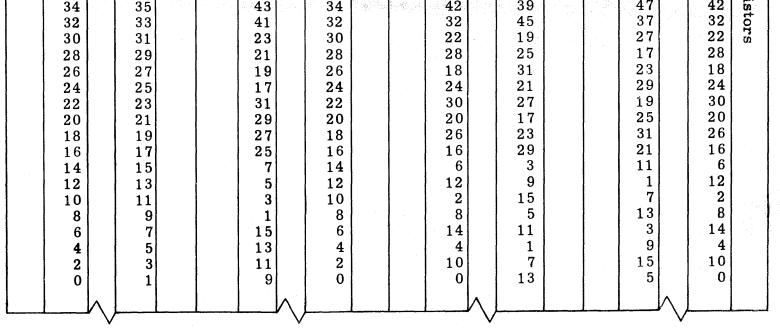

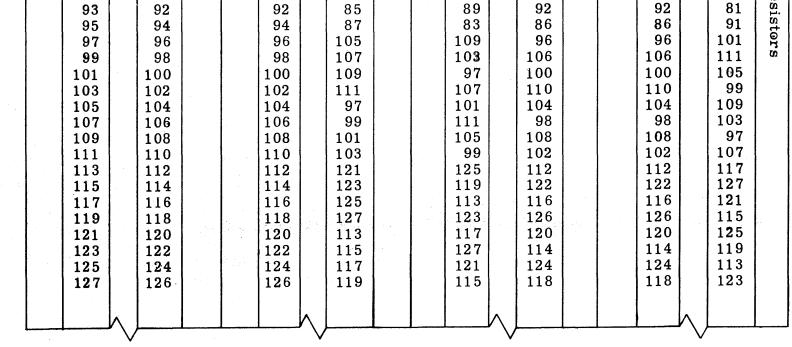

| · 2 | Drive Line Transpositions ("North" View) | 4-31 |

| 3   | Drive Line Transpositions ("South" View) | 4-33 |

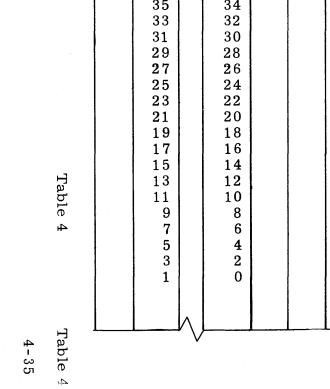

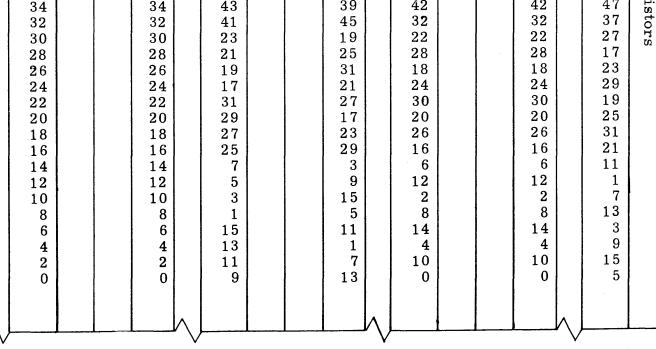

| 4   | Drive Line Transpositions ("East" View)  | 4-35 |

| 5   | Drive Line Transpositions ("West" View)  | 4-37 |

#### CHAPTER 1

#### COMPONENT SPECIFICATIONS

The following pages list significant characteristics of electronic components used in 3600 system printed circuit development.

|                                        | Parameter                                                                                                                            | Condition                                                                                             | Limit                                            | CDC<br>Item No |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------|

| HD4416<br>Hughes<br>Silicon            | Forward Voltage V <sub>f</sub><br>Dynamic Impedance Z <sub>D</sub>                                                                   | I <sub>f</sub> = 2 ma<br>I <sub>f</sub> = 2 ma<br>f = 1000 cps                                        | 0.67v ± 50 mv<br>< 100 ohms                      | 4203           |

| FD 1032<br>Fairchild<br>Silicon<br>(O  | Forward Current I <sub>f</sub><br>Reverse Current I <sub>r</sub><br>ther characteristics similar                                     | $V_{f} = 1 v$ $V_{r} = 40 v$ $to FD 100)$                                                             | >10 ma<br>< 0.1 ua                               | 4210           |

| HD 2969<br>Hughes<br>Germanium<br>(C   | Forward Voltage V <sub>f</sub><br>Working Inverse<br>Voltage WIV<br>Recovery Time T <sub>rr</sub><br>overed by Control Data Corr     | $I_f = 3 \text{ ma}$<br>Switching from<br>$I_f = 3 \text{ ma}$<br>to $V_r = 5v$<br>poration spec. 118 | 0.35v max.<br>40v min.<br>0.6 usec max.<br>-012) | 4200           |

| FDS 2055<br>Fairchild<br>Silicon<br>(O | Forward Current I <sub>f</sub><br>Forward Voltage V <sub>f</sub><br>Breakdown Voltage B <sub>v</sub><br>ther characteristics similar | I <sub>f</sub> = 150 ma<br>I <sub>r</sub> = 100 ua<br>• to FD 400)                                    | 400 ma max.<br>< 1.0v<br>> 75v                   | 4211           |

| HD 1871<br>Hughes<br>Germanium         | Forward Voltage V <sub>f</sub><br>Breakdown Voltage B <sub>v</sub><br>Recovery Time T <sub>rr</sub>                                  | I <sub>f</sub> = 10 ma<br>Switching from<br>I <sub>f</sub> = 10 ma<br>to V <sub>r</sub> = 6v          | 0.42v max.<br>10v min.<br>0.35 usec max.         |                |

|                               | ZENER DI                                                                       | ODES                               |                            |

|-------------------------------|--------------------------------------------------------------------------------|------------------------------------|----------------------------|

|                               | Zener Breakdown<br>Voltage<br>V <sub>z</sub> at 25 <sup>0</sup> C<br>Min. Max. | Dynamic<br>Impedance<br>ZD<br>Max. | Reverse<br>Current<br>Max. |

| 1N703<br>Hughes<br>Silicon    | 3.0v 3.9v<br>at 5ma                                                            | 55Ω at 10ma                        |                            |

| 1N704A<br>Hughes<br>Silicon   | 3.9v 4.3v<br>at 5ma                                                            | 45Ω at 10ma                        | 5ua at -1v                 |

| 1N965B<br>Motorola<br>Silicon | 14.25v 15.75v<br>at 8.5ma                                                      | 16Ω at 8.5ma                       |                            |

| 1N753<br>Motorola<br>Silicon  | 5.6v 6.8v<br>at 20ma                                                           |                                    |                            |

| 1N705A<br>Hughes<br>Silicon   | 4.6v 5.1v<br>at 5ma                                                            | 35î at 10ma                        | 5ua at -1.5v               |

|     |                                                 |                     | TUN                     | INEL DIODES                              |                                              |                           |                                           |

|-----|-------------------------------------------------|---------------------|-------------------------|------------------------------------------|----------------------------------------------|---------------------------|-------------------------------------------|

|     |                                                 | Q<br>Peak<br>I<br>p | Current<br>Valley<br>Iv | Peak-to-Valley<br>Current Ratio<br>I /Iv | Voltage<br>Peak Valley<br>V <sub>p</sub> V.v | Forward<br>Voltage<br>Vfp | Valley-to-Peak<br>Voltage Ratio<br>Vv/V p |

| 1-4 | TD-1 Maxim<br>G.E. Typica<br>Germanium Minim    | 1 1.0m              | a 0.12ma                |                                          | 65mv 350mv                                   | 500mv-                    |                                           |

|     | IN2931 Maxim<br>Hoffman Typica<br>Silicon Minim | .1 10ma             |                         | 3, 5                                     | 65mv 470mv                                   | 790mv                     | 6.8                                       |

# TYPE C01 TRANSISTOR (PNP GERMANIUM)

| PARAMETER                  | CONDITION              | LIMIT    |

|----------------------------|------------------------|----------|

| Breakdown Voltage<br>BVCEO | IC = 10 ma             | > 7v     |

| Breakdown Voltage<br>BVEBO | IE = 100 μa            | > 1v     |

| Current Gain<br>hFE        | IC = 20 ma<br>VCE = 1v | > 40     |

| Gain Bandwidth<br>ft       | IC = 20 ma<br>VCE = 1v | > 300 mc |

- I. Basic transistor similar to a 2N964

- II. Case size to conform to T0-18 outline

- III. Case to be marked C01

# TYPE C02 TRANSISTOR (PNP GERMANIUM)

| PARAMETER                                                                                                       | CONDITION              | LIMIT                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------|

| Breakdown Voltage<br>BVCBO                                                                                      | IC = 100 µa            | > 25v                                                                                                          |

| Breakdown Voltage<br>BVEBO                                                                                      | IE = 100 μa            | > 1v                                                                                                           |

| Current Gain<br>hFE                                                                                             | IC = 10 ma<br>VCE = 5v | > 20                                                                                                           |

| Gain Bandwidth<br>ft                                                                                            | IC = 10 ma<br>VCE = 5v | > 300 mc                                                                                                       |

| والمرجوع والمرجوع أبرار والمتعارين والمتحاط والمرجوع والمتحر والمتحرين والمحاوي فالمتحاد والمتحاط والمتحاط والم |                        | and a second |

- I. Basic transistor similar to a 2N960

- II. Case size to conform to T0-18 outline

- III. Case to be marked C02

# TYPE C03 TRANSISTOR (PNP GERMANIUM)

| PARAMETER                  | CONDITION                | LIMIT   |

|----------------------------|--------------------------|---------|

| Breakdown Voltage<br>BVCBO | IC = 100 μa              | >10v    |

| Breakdown Voltage<br>BVEBO | IE = 100 μa              | >4v     |

| Current Gain-<br>hFE       | IC = 10 ma<br>VCE = 0.3v | > 20    |

| Gain Bandwidth<br>ft       | IE = 20 ma<br>VCB = 1v   | >200 mc |

- I. Basic transistor similar to a 2N705 or 2N960 through 2N966.

- II. Case size to conform to T0-18 outline

- III. Case to be marked C03

# TYPE C04 TRANSISTOR (NPN SILICON)

| PARAMETER                         | CONDITION                 | LIMIT    |

|-----------------------------------|---------------------------|----------|

| Breakdown Voltage<br>BVCBO        | IC = 10 µa                | > 90v    |

| Breakdown Voltage<br>BVBEO        | IE = 10 µa                | > 5 v    |

| Saturation Voltage<br>VCE (Sat.)  | IC = 400 ma<br>IB = 40 ma | <1.25v   |

| Saturation Voltage<br>VBE (Sat. ) | IC = 400 ma<br>IB = 40 ma | < 2v     |

| Current Gain<br>hFE               | IC = 400 ma<br>VCE = 10v  | > 25     |

| Gain Bandwidth<br>ft              | IC = 20 ma<br>VCE = 20v   | > 300 mc |

| Collector Capacitance<br>COB      | VCB = 10v $IE = 0$        | < 8 uuf  |

NOTE:

- I. Basic transistor similar to a 2N22181a

- II. Case size to conform to T0-5 outline

III. Case to be marked C04

1-8

# TYPE C05 TRANSISTOR (NPN SILICON)

| PARAMETER                        | CONDITION                 | LIMIT   |

|----------------------------------|---------------------------|---------|

| Breakdown Voltage<br>BVCBO       | $IC = 10 \ \mu a$         | >50v    |

| Breakdown Voltage<br>BVEBO       | IE = $10 \mu a$           | >5v     |

| Saturation Voltage<br>VCE (Sat.) | IC = 150 ma<br>IB = 15 ma | <0.4v   |

| Saturation Voltage<br>VBE (Sat.) | IC = 150 ma<br>IB = 15 ma | <1.3v   |

| Current Gain<br>hFE              | IC = 10 ma<br>VCE = 10v   | > 35    |

| Gain Bandwidth<br>ft             | IC = 20 ma<br>VCE = 20v   | >250 mc |

- I. Basic transistor similar to a 2N2218la

- II. Case size to conform to T0-5 outline

- III. Case to be marked C05

# TYPE C07 TRANSISTOR (PNP GERMANIUM)

| CONDITION                | LIMIT                                                                                                                                               |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| IC = 1 ma                | >15v                                                                                                                                                |

| IC = 100 ua              | > 20v                                                                                                                                               |

| IE = 1 ma                | >2v                                                                                                                                                 |

| VCB = 5v                 | < 5 ua                                                                                                                                              |

| IC = 10 ma<br>VCE = 0.5v | > 30                                                                                                                                                |

| IC = 10 ma<br>IB = 1 ma  | <0.4v                                                                                                                                               |

| IC = 5 ma<br>VCE = 3v    | >100 mc                                                                                                                                             |

| VCB = 6v<br>f = 4 mc     | < 3 uuf                                                                                                                                             |

|                          | IC = 1 ma<br>IC = 100 ua<br>IE = 1 ma<br>VCB = 5v<br>IC = 10 ma<br>VCE = $0.5v$<br>IC = 10 ma<br>IB = 1 ma<br>IC = 5 ma<br>VCE = $3v$<br>VCB = $6v$ |

### NOTE:

- I. Basic transistor similar to a 2N980.

- II. Case size to conform to TO-18 outline. III. Case to be marked C07.

# TYPE 2N404 TRANSISTOR (PNP GERMANIUM)

| ,                                            | · · · · · ·                                       |                          |

|----------------------------------------------|---------------------------------------------------|--------------------------|

| PARAMETER                                    | CONDITION                                         | LIMIT                    |

| Breakdown Voltage<br><sup>BV</sup> CBO       | I <sub>C</sub> = 20μa                             | > 25v                    |

| Breakdown Voltage<br><sup>BV</sup> EBO       | I <sub>E</sub> = 20μa                             | > 12v                    |

| Saturation Voltage<br><sup>V</sup> CE (Sat.) | I <sub>C</sub> = 12 ma<br>I <sub>B</sub> = 0.4 ma | < 0.35v                  |

| Current Gain<br><sup>h</sup> FE              | I <sub>C</sub> = 12 ma<br>V <sub>CE</sub> = 0.15v | > 30<br>50, typical      |

| Alpha-Cutoff Frequency<br><sup>f</sup> αb    | $V_{CB} = 6v$<br>$I_{C} = 1 ma$                   | > 4 mc<br>13 mc, typical |

NOTE:

1. Other characteristics covered by 2N404 specification.

II. Case size to conform to TO-5 outline.

| TRA                                          | 2N1760<br>ANSISTOR<br>ERMANIUM)                     |                      |

|----------------------------------------------|-----------------------------------------------------|----------------------|

| PARAMETER                                    | CONDITION                                           | LIMIT                |

| Breakdown Voltage<br><sup>BV</sup> CBO       | I <sub>C</sub> = 3.0 ma                             | > 60v                |

| Breakdown Voltage<br><sup>BV</sup> BEO       | I <sub>E</sub> = 3.0 ma                             | > 30v                |

| Saturation Voltage<br><sup>V</sup> CE (Sat.) | I <sub>C</sub> = 3.0 amp<br>I <sub>B</sub> = 200 ma | < 0.7v               |

| Current Gain<br><sup>h</sup> FE              | I <sub>C</sub> = 0.5 amp<br>V <sub>CE</sub> = 2v    | > 60<br>100, typical |

15

÷

NOTE:

1

| I. | Basic | trans  | istor | similar | to | Clevite |

|----|-------|--------|-------|---------|----|---------|

|    | CTP1  | 736 01 | · 2N1 | 760.    |    |         |

$\dot{\gamma}$

• 7

II. Other characteristics covered by Clevite Bulletin TB226-2.

× 4.

, **\***.

#### NOTES:

- I. Coil form similar to Cambridge Thermionic Corp. PLST-2C4L/H.

- II. Coil to be wound single layer with no spacing between turns.

- III. Coil to be wound bifilar with #32 enameled copper wire.

- IV. Coil to be adjacent to "T" collar with "B" collar to be moved to support winding.

- V. Center tap (#3) to be brought out twisted with a minimum length of 1 inch from collar edge.

- VI. Last 1/2 inch of twisted center tap lead to be tinned.

- VII. Solder lugs to be formed parallel to length of coil form.

- VIII. Tuning slug to be type 20063-H.

- IX. Tinned leads to be brought out 1 inch on terminals 1, 2, 4 and 5.

Figure 1

- 1. Workmanship shall be consistent with best commercial practices. Part shall conform to dimensions and tolerances on drawing.

- 2. Material and Finish:

Core: General ceramics, Ferramic CF-102, type H.

Winding: Phelps - Dodge #34 heavy Nyleze.

Terminals: Brass. Copper preplate .00005 thick. Gold plate .00005 thick.

- Base and Cover: Mineral filled Phenolic type CFG per MIL-M-14F, color black, (Durez 11540) or equivalent pending approval by Control Data Corp.

- 3. Cement base to cover using Minnesota Mining and Manufacturing cement #505.

- 4. Wind the two 60-turn secondaries bifilar for 15 turns. Continue fourfilar for 45 turns. Connect the two 45 turn windings together to make the 90-turn center tap primary.

- 5. Mark terminals in approximate position as shown.

- 6. Mark part "300010" and revision letter to which part is manufactured, manufacturer's name or symbol, in approximate position as shown.

Figure 2

#### CHAPTER 2

#### LOGIC CARD TYPES

| NAME            | CIRCUIT                                                   | NUMBER                  |

|-----------------|-----------------------------------------------------------|-------------------------|

| Single Inverter | One inverter circuit                                      | C11-C17, and<br>C51-C58 |

| Double Inverter | Two separate inverter circuits                            | C21-C28                 |

| Flip-Flop       | Two inverter circuits having cross-coupled feed back      | C31-C37                 |

| Control Delay   | Flip-flop having its feedback<br>ANDed with a clock phase | C40-C49                 |

Logic circuits are constructed with two types of inputs, logical AND and logical OR. All of the various logic cards and their respective input configurations are presented in the tables on the following pages.

The input configuration of a circuit is also represented by a number. For instance, card type C11 is a single inverter 116. This means that the circuit has two OR inputs and a six-way AND input.

Double inverter and flip-flop cards contain two circuits designated A and B. Each has separate inputs and the configurations are not necessarily symmetrical.

Control delay cards also contain two circuits designated A and B. All logic inputs pertain to circuit A, and all OR inputs are effectively single-way ANDs and must be grounded if not used.

- 20v

Figure 1. Single Inverter

2-2

INPUT SYMBOLS

| NOTI | <b>E:</b> |    |      |   |

|------|-----------|----|------|---|

|      | PIN'      | 7, | + 20 | V |

|      | PIN       | 8, | GN   | D |

|      | PIN       | 9, | - 20 | v |

Figure 2. Double Inverter and Flip-Flop

#### CHAPTER 3

#### CIRCUIT DESCRIPTIONS

The following pages contain descriptions and schematic diagrams of type "C" printed circuit cards developed for the 3600 system. These prototype cards are designated by a two-digit number preceded by the letter C; for example, C65.

The following descriptions are presented in numerical order.

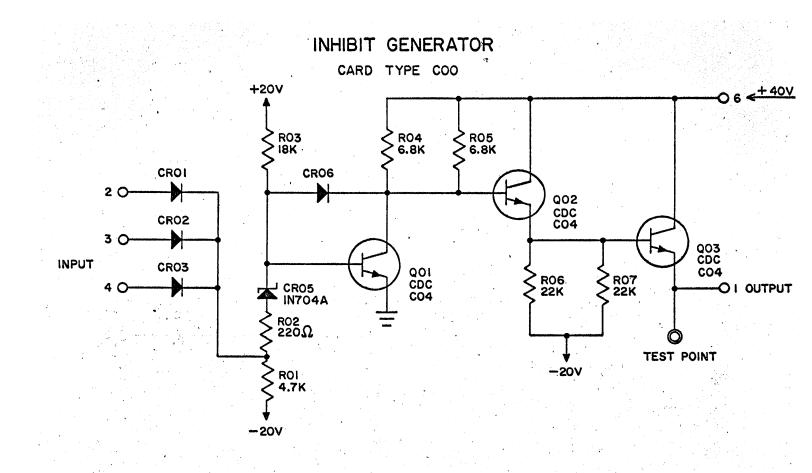

ODD PLANE INHIBIT GENERATOR Card Type C00

#### FUNCTION

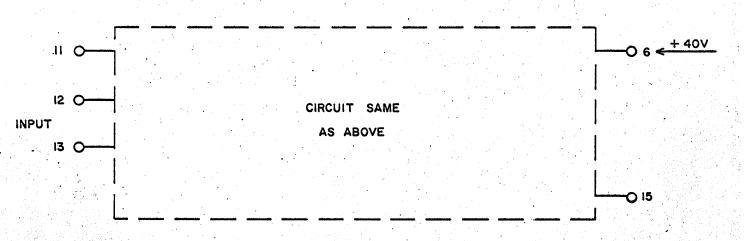

The function of the circuits on this card is to allow a 340 ma inhibit current to flow from the +40v source at pin 6 to the inhibit winding at pin 1 or pin 15. This occurs whenever all inputs to the respective circuit are at the logical "1" level of -5.8v. The inhibit circuit contains a series 120-ohm resistor so that the resulting current is approximately 340 ma.

#### OPERATION

Each circuit has a three-way logical AND input, meaning that all inputs must be at the -5. 8v''1'' level in order for an input to be sensed. A -1. 1v''0'' signal on any input will disable the AND. An unused input acts as a steady "1" if left open, or as a steady "0" if grounded.

A level-shifting action is provided to the base of Q01 by resistors R01, R02, R03, and the 4. 1v zener diode CR05. The zener diode CR05 is reverse-biased so that its operating point is beyond the knee of the breakdown region; thus the cathode remains approximately 4. 1v positive with respect to the anode, regardless of current fluctuations.

When a -1. 1v "0" signal appears at an input, the zener diode CR05 places a forward bias on the base of Q01. Transistor Q01 then switches to a state of heavy conduction. It is held out of saturation by the feedback diode CR06 and its collector voltage is approximately +0. 4v. The low collector voltage of Q01 is also the base voltage of Q02, which is connected as an emitter follower. The emitter voltage of Q02 is equal to its +0. 4v base voltage minus its base-emitter junction drop, and is approximately -0. 3v. This provides sufficient forward bias so that a minimum conduction is maintained through Q02. Transistor Q03 is connected as an emitter follower with the inhibit winding load in series with the emitter. The emitter of Q03 is connected to ground through

### ODD PLANE

3-3

3. ALL DIODES ARE HD2969 UNLESS OTHERWISE INDICATED.

2. TRANSISTORS QO2 & QO3 CONDUCT WHEN ALL INPUTS ARE -5.8V "I".

I. EACH CIRCUIT HAS THREE "AND" INPUTS.

the inhibit line. The base-emitter junction is therefore reverse-biased by the -0. 3v input, so that Q03 is cut off. This disables the current path from the +40v supply to the inhibit winding.

With the AND input satisfied by -5.8v "1" signals, the base of Q01 is biased at approximately -1.5v and Q01 is cut off. The collector voltage of Q01 rises to approximately +38.5v (40v minus the IR drop across R03 and R04). This provides drive to the base-emitter junction of Q02. Transistor Q02 is connected as an emitter follower; thus its emitter voltage becomes approximately +38v. This provides a strong forward bias to the base of Q03, causing Q03 to conduct heavily. The voltage applied to the inhibit line is the emitter voltage of Q03 and is approximately +37.5v. The 340 ma inhibit current is also the emitter current of Q03, and is allowed to flow when Q03 switches to the conduction state.

000

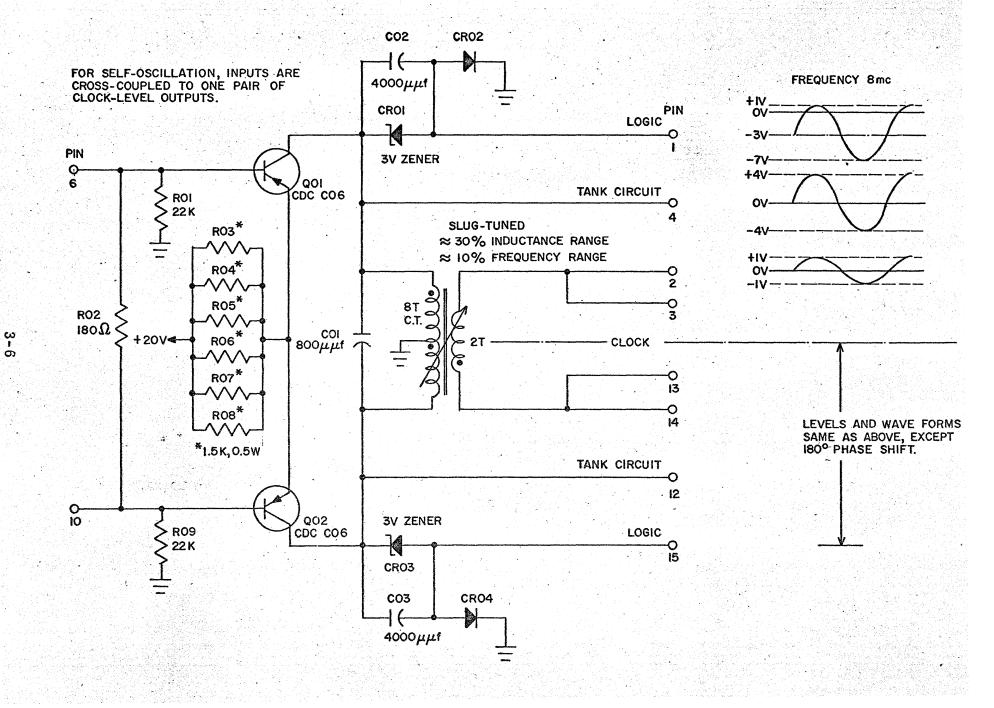

#### CLOCK OSCILLATOR-AMPLIFIER Card Type C01

#### General

The clock oscillator-amplifier shown in figure 1 is essentially a tank circuit which may be tuned through a small range around 8 megacycles, with drive provided to the tank by two transistor amplifiers. The transistors are connected in a push-pull configuration, with the two circuit inputs directly connected to their bases. When the transistor inputs are provided with cross-coupled feedback from the oscillator transformer secondary, a continuous self-oscillation is maintained.

The circuit is designed so that, if external drive is provided to the inputs, the two transistors will operate as sine wave amplifiers, providing a two-phase output at the tank frequency.

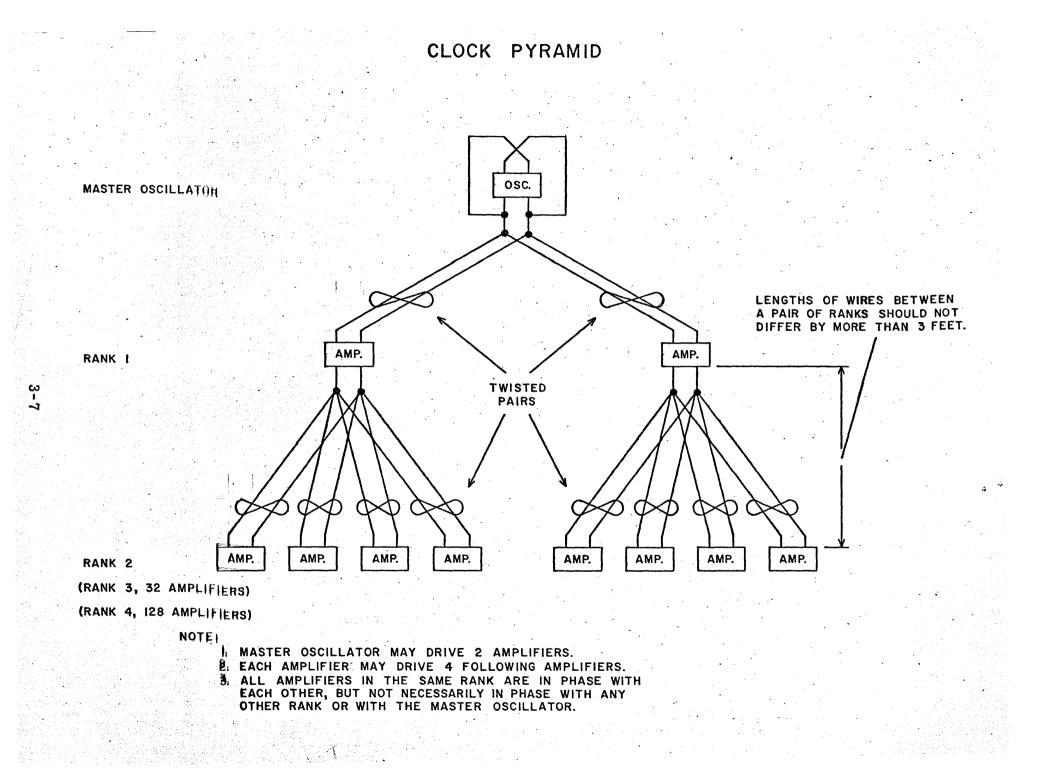

#### Pyramid Connection

The computer timing configuration for which this circuit is designed is an oscillatoramplifier pyramid, as shown in figure 2. The master oscillator is a clock circuit connected as a feedback oscillator. To avoid undue loading effects, the master oscillator is permitted to drive only 2 amplifiers.

The ranks of amplifiers are clock circuits which receive external inputs and function as push-pull sine wave amplifiers. Each amplifier is capable of driving 4 others; thus, the pyramid effect is produced. Each amplifier in a rank must be in phase with every other amplifier in that same rank, although it is not necessary for the ranks to be in phase with each other or with the master oscillator. Outputs to the logic are taken only from the final rank of amplifiers.

#### **Circuit** Operation

The driving transistors Q01 and Q02 are CDC C06<sup>t</sup>s and are connected in a pushpull configuration. Only one transistor would be necessary to sustain oscillation; however, two transistors greatly increase the ability of the circuit to drive an unsymmetrical load.

#### CLOCK OSCILLATOR - AMPLIFIER

Clock amplifier logic outputs are restricted to driving AND loads, only. By means of jumpered connections, an amplifier may drive up to 10 loads. Ideally, this would be distributed with 5 loads on each output phase; however, the loading may be unbalanced to 8 and 2, if necessary.

The characteristics of transistors Q01 and Q02 are presented in the component section of this report; however, these transistors have a power handling capability of 150 mw at  $25^{\circ}$  C ambient. The average transistor dissipation in an oscillator circuit is of the order of 60 mw.

An 800  $\mu\mu$ f silver-mica capacitor C01 having a low temperature coefficient and good stability with life is used in the tank circuit to resonate with the transformer inductance at a center frequency of 8 megacycles. The transformer inductance may be tuned through a range of approximately 30% by means of a low permeability ferrite slug. This has the effect of shifting the tank frequency through a range of approximately 10%.

The peak-to-peak signal developed across the tank is restricted to approximately 8v by the clamp diodes CR01 and CR04. The printed circuit card provides outputs at pins 4 and 12 at which this sine wave appears. All of the tanks in a rank of amplifiers may be locked in phase with one another by connecting these outputs in parallel, in case this is ever necessary.

A logic-level signal is a sine wave about -3v, with peaks at +1v and -7v. It is produced by using a zener diode to shift the d-c reference level of the tank output. Logic-level outputs are taken only from the last rank of the clock pyramid, and are available at pins 1 and 15.

The circuit in figure 1 provides a clock-level output at pins 2, 3, 13, and 14, which is taken from the secondary of the tank transformer. The secondary winding consists of 2 turns, while the primary winding is 8 turns, center-tapped; therefore the clock-level output is a sine wave about ground with a peak-to-peak amplitude of approximately 2v.

3-8

The clock-level signals are used as drive signals throughout the clock pyramid, as shown in figure 2. All wires used to transmit clock-level signals must be twisted pair, and the distance over which the signal is transmitted should be less than 15 feet. In addition, there should be less than a 3 foot variation in the lengths of wires used to transmit drive signals between a given pair of ranks.

### Ground Rules

- A. Clock-level outputs.

- 1. The oscillator may drive 2 amplifiers, in addition to providing its own feedback.

- 2. Each amplifier may drive 4 other amplifiers.

- 3. Interconnecting wires between ranks of amplifiers and from the master oscillator to rank 1 must be twisted pair.

- 4. Signals may be transmitted up to 15 feet.

- 5. There should be no more than a 3-foot difference in the lengths of interconnecting wires between a given pair of ranks.

- B. Tank circuit output.

- 1. This is used only to phase-lock the tanks within a single rank of amplifiers, if necessary.

- C. Logic-level outputs.

- 1. Clock outputs must always connect to logic card AND inputs.

- 2. A maximum of 10 loads may be driven.

- 3. A maximum of 8 loads may be driven by any single output; with

- 8 loads on one output, the opposite-phase output of that amplifier may drive only 2 loads, so that the total number does not exceed 10.

### Procedure for Tuning a Clock Pyramid

A scope equipped with a differential or dual-trace preamplifier, such as a Tektronix type CA, may be used for tuning the pyramid. The probe leads should be of equal length and must be grounded at the cards. The scope should be externally synchronized during step 3, and it is convenient to use the master oscillator for this.

Step 1.

Adjust the transformer of the master oscillator to the correct computer frequency. This may be done by setting the horizontal sweep at 0.1  $\mu$ sec/ cm and adjusting until 8 peaks are seen across the 10 cm scope grid, if the desired frequency is 8 megacycles.

#### Step 2.

With the scope on a sensitive range, adjust one of the amplifiers in Rank 1 for maximum amplitude.

Step 3.

Using external sync, adjust the remaining amplifiers in Rank 1 to be in phase with the reference amplifier tuned in step 2. With a differential preamplifier, this may be done by inverting one signal and adding algebraically, and adjusting for minimum deflection with the scope on a sensitive range.

Other ranks are tuned according to steps 2 and 3.

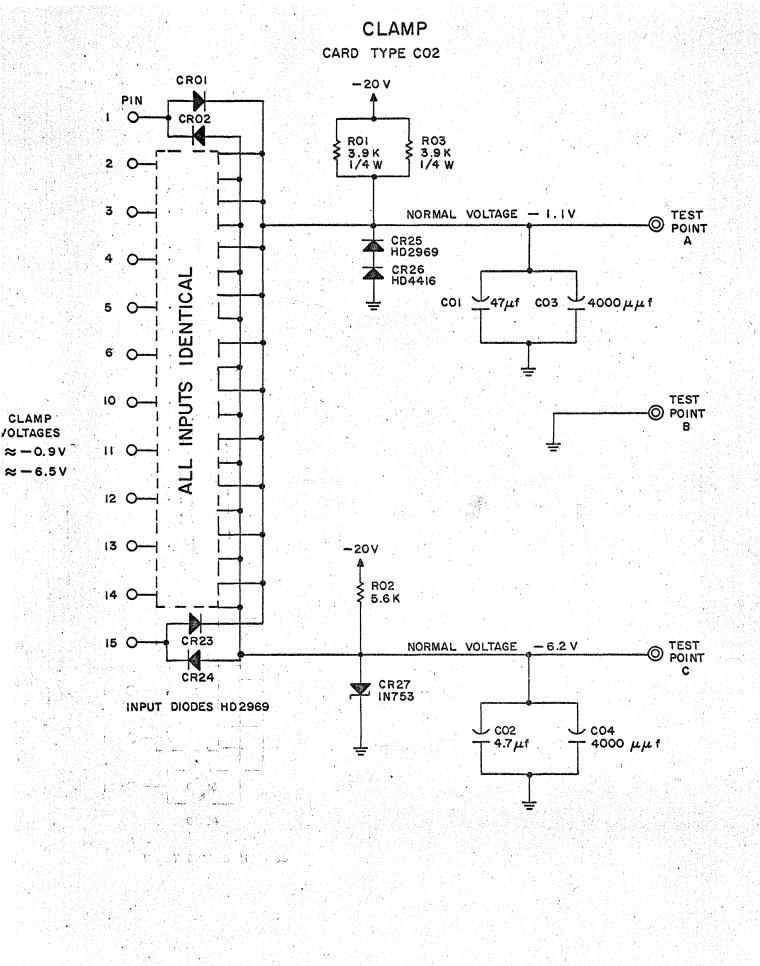

#### CLAMP

#### Card Type C02

This circuit provides a clamp for logic circuit connecting lines, so that ringing will be minimized. If sufficient energy is removed from the first overshoot, the remainder of the ringing will have an amplitude less than the logic circuit threshold. A schematic of the clamp circuit is presented in figure 1, with typical waveforms showing its effect on a line having excessive ringing.

The clamp voltage in the positive direction is the sum of the forward drops across diodes CR25 and CR26, less the drop across the input diodes, and is approximately -0.9v.

The clamp voltage in the negative direction is the sum of the drop across zener diode CR27 plus the drop across the input diodes, and is approximately -6.5v.

Filtering is provided by capacitors C01, C02, C03, and C04. Due to their large areas, C01 and C02 present an appreciable amount of inductive reactance. It is therefore necessary to include the small capacitors C03 and C04 in order to filter out high-frequency spikes.

- Williams

## TRANSFORMER DRIVER Card Type C03

## FUNCTION

The function of the circuits on this card is to enable 450 ma of positive current to flow from the output pins 1 or 15 to ground, whenever all inputs to the respective circuit are at the logical "0" level of -1.1v. Pins 1 and 15 connect to the two ends of the primary windings of eight memory driver transformers. During the memory cycle, one transformer will be centertapped to +20v; thus current flow in either direction may be obtained by selecting one of the circuits on the C03 card.

The output pins 1 and 15 are connected as shown in figure 1 by capacitor C03 and resistor R06, which form a series differentiating network. This connection will transmit only those signals having a high rate of change, such as a sharp noise spike, and will block entirely a steady d-c voltage. Thus, a noise spike appearing at pin 1 will also appear at pin 15, and their total effect will be to cancel each other. However, the d-c levels of pins 1 and 15 will be completely separated if either circuit switches to the conduction state while the other remains cut off.

### OPERATION

The two circuits on the card are identical and are labeled A and B. The following discussion of operation applies to either circuit, however, the component numbers mentioned are those appearing in circuit A.

A level-shifting action is provided to the base and emitter of Q01 by resistors R01, R03, R04, and the 4.1v zener diode CR06. The zener diode CR06 is reverse-biased so that its operating point is beyond the knee of the breakdown region; thus the cathode remains approximately 4.1v positive with respect to the anode, regardless of current fluctuations.

NOTES:

S. See 2

I.EACH CIRCUIT HAS 3 OR INPUTS. 2.TRANSISTORS SWITCH TO CONDUCTION STATE WHEN ALL INPUTS ARE - 1.1 V "0"... Each circuit has three logical OR inputs, meaning that a -5.8v "1" signal on any input will be sensed, although a -1.1v "0" signal may be present simultaneously at another input. Any unused input acts as a steady "0", regardless of whether it is grounded or left open.

When a -5.8v"'1" signal appears at an input, the base of Q01 will be biased at about -1v and it will be cut off. The base of Q02 will be held at approximately -0.3v by the forward drop of diode CR08, and Q02 will likewise be cut off. Thus, except for negligible leakage effects, pin 1 is completely isolated from ground and will rise to a high positive voltage. Diode CR07 therefore provides a blocking action, preventing current from flowing through the transformer primary into pin 1.

If all of the circuit inputs are at the -1.1v "0" level, zener diode CR06 holds the base of Q01 at a positive voltage. This forward bias is sufficient so that Q01 conducts heavily, but it is held out of deep saturation by diode CR07 and resistor R03. Transistor Q01 in its conduction state allows the +20v source, which connects to pin 1 through the transformer primary, to bias the base of Q02 at a positive potential. Thus transistor Q02 also conducts heavily, and positive current is allowed to flow from pin 1 to ground with only a drop of approximately 1v across Q02.

Transistor Q02 is a grounded emitter stage driven by the emitter follower stage Q01. The base drive for Q02 is taken directly from the emitter of Q01; thus the input to Q02 follows the input to Q01 and is increased by the gain of Q01. When Q01 switches on, it attempts to bias the base of Q02 well into the positive voltage domain, so that Q02 also switches on and conducts heavily. Likewise, when Q01 switches off, Q02 also switches off, and the voltage drop across diode CR08 applies a reverse bias of approximately 0.3v to the base emitter junction of Q02 so that it is well into the cut off region.

# EVEN PLANE INHIBIT GENERATOR Card Type C04

### FUNCTION

The function of the circuits on this card is to allow a 340 ma inhibit current to flow from pin 1 or 15 to ground, whenever all inputs to the respective circuit are at the logical "0" level of -1. 1v. The inhibit wires are energized by a source of +40v, and each inhibit circuit contains a series 120-ohm resistor so that the resulting current is approximately 340 ma. The even plane inhibit wires terminate at either pin 1 or pin 15 of a C04 card, and the path will be completed to ground allowing current to flow, if the respective inhibit generator circuit switches to its conduction state.

### OPERATION

The two circuits contained on the card are identical and are labeled A and B. The following discussion of operation applies to either circuit but the component numbers mentioned are those appearing in circuit A.

A level-shifting action is provided to the base and emitter of Q01 by resistors R01, R03, R04, and the 4.1v zener diode CR06. The zener diode CR06 is reverse-biased so that its operating point is beyond the knee of the breakdown region; thus the cathode remains approximately 4.1v positive with respect to the anode, regardless of current fluctuations.

Each circuit has three logical OR inputs, meaning that a -5. 8v "1" signal on any input will be sensed, although a -1. 1v "0" signal may be present simultaneously at another input. Any unused input acts as a steady "0", regardless of whether it is grounded or left open.

When a -5.8v "1" signal appears at an input, the base of Q01 is biased at about -1v and Q01 is cut off. The base of Q02 will be held at approximately -0.3v by the forward drop of diode CR08, and Q02 will also be cut off. Thus, except for

negligible leakage effects, pin 1 is completely isolated from ground and will rise to a high positive voltage. Diode CR07 therefore provides a blocking action, preventing current from flowing through the inhibit wire into pin 1.

If all of the circuit inputs are at the -1. 1v "0" level, zener diode CR06 holds the base of Q01 at a sufficiently positive voltage so that Q01 conducts heavily. In this state, diode CR07 holds Q01 out of saturation. Transistor Q01 in its conduction state allows the +40v source, which connects through the inhibit wire to pin 1, to bias the base of Q02 at a positive level. Thus transistor Q02 also conducts heavily, and positive current is allowed to flow from pin 1 to ground with only a drop of approximately 1v across Q02.

Transistor Q02 is a grounded emitter stage driven by the emitter follower stage Q01. The base drive for Q02 is taken directly from the emitter of Q01; thus the input to Q02 follows the input to Q01 and is increased by the gain of Q01. When Q01 switches on, it attempts to bias the base of Q02 well into the positive voltage domain, so that Q02 also switches on and conducts heavily. Likewise, when Q01 switches off, Q02 also switches off, and the voltage drop across diode CR08 applies a reverse bias of approximately 0.3v to the baseemitter junction of Q02 so that it is well into the cut off region.

The connection of diode CR07, the 100-ohm resistor R06, and the +40v source provides a clamp for the collector voltage of the transistors. When the transistors switch to the non-conducting state, the inductance of the inhibit wire will tend to induce high-voltage transients; however, these inductive transients are clamped at  $\pm 40v$  plus the drop across the silicon diode.

The 3.3 microhenry inductor in series with the output pin is for the purpose of reducing ringing on the inhibit wire. The inductor increases the current rise time and hence reduces the overshoot.

## GATE Card Type C05

### FUNCTION

The function of the Gate circuit is to enable a current path from a +20v source through which current of the order of 900 ma flows to the primary windings of two memory driver transformers. Pin 4 connects to +20v and pins 1, 2, and 3 provide the output. The path from pin 4 to the output is enabled only when all inputs to the Gate circuit are at the logical "0" level of -1.1v.

The function of the Discharger circuit is to ground the primary windings of the two memory driver transformers which were previously energized. This removes stored charge from the windings and neutralizes the transformers. The Discharger circuit is enabled by a -1.1v "0" input.

### OPERATION

Pins 10 through 13 provide four logical OR inputs to the Gate circuit, and pin 6 provides an OR input to the Discharger. An unused input is interpreted as a steady "0", regardless of whether it is grounded or left open.

A level-shifting action for the Gate inputs is performed by resistors R01, R03, R05, and the 4.1v zener diode CR06. The zener diode CR06 is reverse-biased so that its operating point is beyond the knee of the breakdown region; thus the cathode remains approximately 4.1v positive with respect to the anode, regardless of current fluctuations. Resistors R02, R06, and zener diode CR08 perform the levelshifting action for the Discharger.

With open circuits or logical "0" signals on all Gate inputs, the base of Q01 will be at a potential of around +0.7v. It is prevented from going further positive by the low forward base-emitter impedance of Q01. During this time, Q01 will be in the conduction state. However, if any input receives a -5.8v "1", the zener diode CR06 will hold the base of Q01 at approximately -1.7v and Q01 will be cut off.

During the time that Q01 is cut off by a "1" signal, its collector potential will be raised to a high positive value by the +20v source attached to pin 4. Since no appreciable current now flows through the 82-ohm resistor and tunnel diode between base and emitter of Q03, it is also essentially cut off.

When Q01 switches to its conducting state, current is allowed to flow from the +20v source at pin 4 through the tunnel diode and 82-ohm resistor between emitter and base of Q03, through the three parallel 2.7k resistors, and through Q01 to ground. A threshold level is provided by the tunnel diode, since in its low-voltage state, it does not allow Q03 to conduct. However, when current through the tunnel diode increases to 10 ma, it switches to its high-voltage state. This places approximately 0.8v forward potential on the base of Q03 causing it to switch to its conduction state. This enables the series circuit from +20v at pin 4 through Q03 and through the three parallel 2.7k resistors to -20v. The base drive for Q04 and Q05 is taken from the collector of Q03, and when Q03 conducts, turn-on current is provided for Q04 and Q05 so that they switch to the conduction state. Thus the circuit is completed, allowing positive current to flow from pin 4 to the output. When Q03 switches off, the voltage drop across diode CR10 applies a reverse bias of approximately 0.6v to the base-emitter junctions of Q04 and Q05, cutting them off.

Transistors Q04 and Q05 control a current of the order of 900 ma flowing in a highly inductive load. Diode CR09 is therefore provided so that when Q04 and Q05 interrupt the current, the induced high-voltage transient will be dissipated harmlessly.

Diode CR11 acts as a clamp against positive voltage surges at the collectors of Q04 and Q05 when current is interrupted. Pin 5 connects to a separate +20v buss and prevents pin 4 from becoming more positive than +20.6v, taking into account the 0.6v drop across the silicon diode.

Capacitors C02 and C03 provide a smoothing filter for spikes and ripple in the +20v sources at pins 4 and 5. The 8 microfarad capacitor C02 is sufficient for ripple and low frequency fluctuations; however, it exhibits a certain amount of inductive reactance due to its large area. For this reason, it is necessary to include C03 which has negligible inductive reactance and is therefore effective in filtering high frequency spikes.

The Discharger circuit is enabled by a -1.1v "0" input on pin 6. This causes zener diode CR08 to apply sufficient forward bias to the base of Q02 so that Q02 switches to its maximum conduction state. Transistor Q02 thus provides a low impedance path to ground for any stored charge remaining in the primary windings of the two memory driver transformers.

# SENSE AMPLIFIER Card Type C06

This card amplifies and detects the pulses induced in a sense winding when a magnetic memory core switches polarity. The two ends of the sense winding are connected to pins 4 and 5, and when a core switches its magnetic state, the circuit produces a logical "0" output on pin 15.

The circuit may be conveniently divided into two sections: a differential voltage amplifier having a gain of approximately 100, and a discriminator having an output of approximately -13. 6v representing a logical "1" which changes to a logical "0" when a memory core switches its magnetic state. The following logic card will interpret any signal more positive than -3v as being a logical "0", however the discriminator output approaches -1.6v when a core switches.

#### AMPLIFIER

The differential voltage amplifier is the symmetrical portion of the circuit to the left of the diode bridge, as shown in the accompanying diagram. Input signals from the sense winding are received on pins 4 and 5. The ends of the sense winding are connected to these two pins, forming a series loop which threads all of the memory cores in a plane quadrant. The only ground reference to this loop is through the 1000-ohm resistor R02, thus the nominal 30 mv potential induced in the sense winding by the switching of a core is applied equally and oppositely to both input pins. This is amplified into a 3v signal which appears across the diode bridge.

The amplifier circuit is sensitive only to the <u>difference</u> in potential between pins 4 and 5, which is produced by the application of a double-ended signal from the sense winding. A simultaneous shift of the d-c reference level of <u>both</u> input pins produces only a negligible effect. It is possible for both inputs to fluctuate simultaneously by as much as 2v without producing more than 0.2v fluctuation at the diode bridge.

NOTE :

I. ALL DIODES FD 1032.

2. ALL TRANSISTORS CDC CO2, UNLESS OTHERWISE INDICATED.

3-25

The degree of sensitivity exhibited by a differential amplifier to potential differences between its inputs as opposed to simultaneous shifts of both inputs in the common mode is often represented by a number called the "common mode rejection ratio", which figure for this circuit is of the order of 40,000.

Resistors R01 and R03 are connected in series across the two inputs, as shown. This relatively low resistance is in parallel with the input impedance of the amplifier, so that the total terminating impedance across the sense line is reduced. This has the effect of making the amplifier less sensitive to noise induced by the flow of inhibit current.

The 4 uh inductors in the emitter circuits of Q02 and Q03 determine the high frequency roll-off of the amplifier. This inductance reduces the gain at high frequencies, and prevents the amplifier from responding to noise spikes.

The signals produced by the memory cores are received and amplified in the double-ended fashion. As an example of operation, assume that the 30 mv potential from the memory core is of a direction such that pin 4 shifts negative 15 mv and pin 5 shifts positive 15 mv from the rest state. These potentials are applied to the bases of Q02 and Q03, causing Q02 to conduct more heavily while conduction through Q03 decreases. This action is further regulated by the constant-current source through Q01, so that an emitter current increase in Q02 must be accompanied by a corresponding decrease in Q03.

The results of the preceding action are such that the collector of Q02 becomes more positive and the collector of Q03 becomes more negative. This, in turn, causes transistors Q04 and Q06 to conduct less heavily while conduction through Q05 and Q07 increases. The collectors of Q04 and Q06 therefore shift approximately 1.5v in the negative direction and the collectors of Q05 and Q07 shift a similar amount in the positive direction, so that a potential difference of 3v exists across the diode bridge.

The signals from the collectors of Q02 and Q03 are amplified by a factor of 100 by Q04 and Q06, and by Q05 and Q07, respectively, which are connected as an emitter follower and a grounded emitter amplifier. Depending upon their particular characteristics, the two transistors are capable of providing a maximum available gain of the order of 1000. To insure stable operation, this is reduced to around 30 by the negative feedback connection of the two 1000-ohm resistors from collector to base. A portion of this negative feedback, however, is nullified by the 330-ohm resistor connected between the two feedback lines, so that the over-all voltage gain of each of the stages is approximately 100.

### DISCRIMINATOR

The discriminator is the portion of the circuit to the right of the diode bridge, whose function is to provide outputs at voltage levels suitable for use by logic circuits. The output of the discriminator is taken from pin 15, and is at approximately -13.6v during the rest state. However, when a voltage appears across the diode bridge, the output at pin 15 approaches -1.6v which is interpreted as a logical "0".

The diodes used in the bridge are high speed silicon devices having a forward voltage drop of the order of 0.6v. Therefore, during the rest state a voltagedividing action is provided from +20v to ground through the 22,000-ohm resistor R18, the diode bridge, and the 5600-ohm resistor R21. Due to the forward drop of the diodes, the base of Q08 is held at around 1.2v higher positive potential than the base of Q09. Transistor Q09 thus conducts quite heavily while Q08 conducts very little. Under these conditions the output at pin 15 is around -13.6v, due to the voltage dividing action of R19, R20, and R23. Transistor Q09 provides a low impedance path to ground, so that the emitter of Q08 cannot rise to a high positive potential when it is in a state of low conduction.

The diode bridge rectifies the potential across it, so that an input of either polarity results in a negative input to the base of Q08 and a positive input to the base of Q09. This has the effect of causing Q08 to conduct heavily while Q09, in turn, conducts very little. Transistor Q08 thus enables a low impedance path from +20v to ground through diode CR05, which is a silicon diode having a forward drop of approximately 0.6v. The anode of CR05 is therefore at approximately +0.6v, so that pin 15 is biased at approximately -1.6v by resistors R20, R19, and the +20v source. This output voltage level is interpreted as a logical "0".

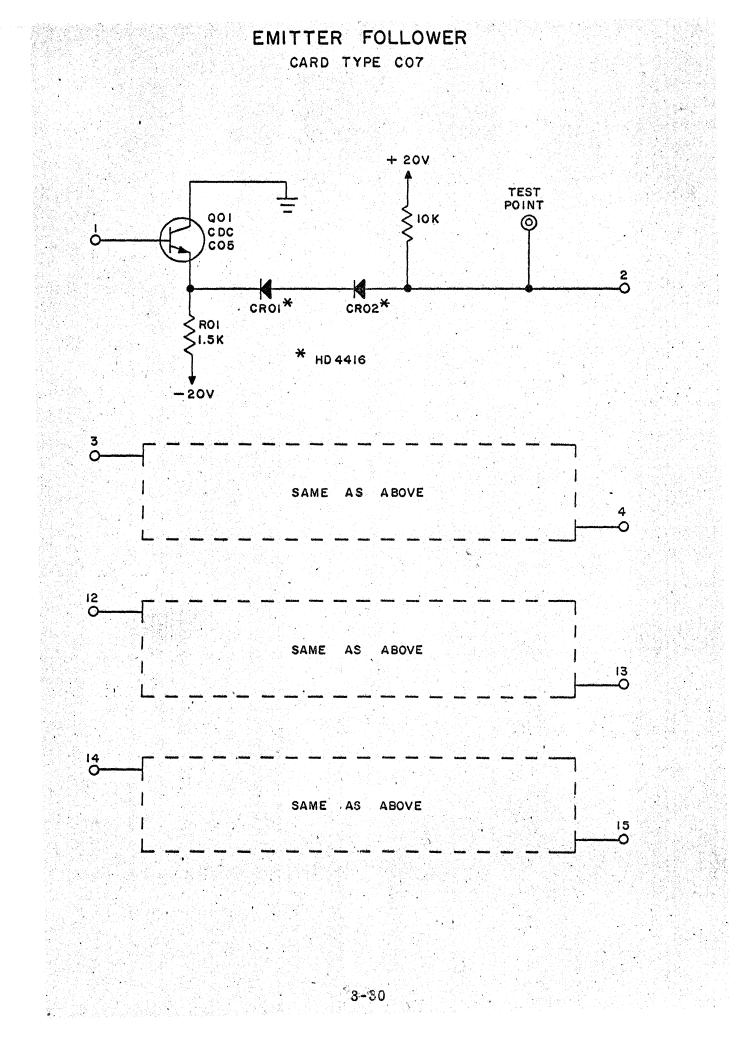

## EMITTER FOLLOWER Card Type C07

### FUNCTION

The function of this circuit is to convert inputs received from a terminated 200-ohm delay line into outputs suitable for driving a logic card load. This circuit is designed to provide a high impedance load for the delay line, avoiding excessive current drain which will affect its operating characteristics.

### OPERATION

The delay line is driven by the circuit contained on card type C08; thus its input signal levels are approximately -0.3v and -10v. However, due to integrating characteristics and attenuation, the peak voltage levels tend to diminish slightly as the signal travels down the delay line. The input signal levels of the emitter follower circuit are therefore of the order of -0.3v and -10v, depending upon the point of the delay line from which the signal is taken.

A -0.3v input results in an output near ground which is interpreted as a logical "0". A -10v input results in an output of approximately -9.3v which is interpreted as a logical "1".

Transistor Q01 is an NPN silicon type CDC C05. It is connected as an emitter follower; thus its emitter voltage is always approximately 0.7v more negative than the circuit input.

CR01 and CR02 are silicon diodes having a forward voltage drop of approximately 0.7v. The series connection of these two diodes holds the circuit output 1.4v more positive than the emitter of Q01.

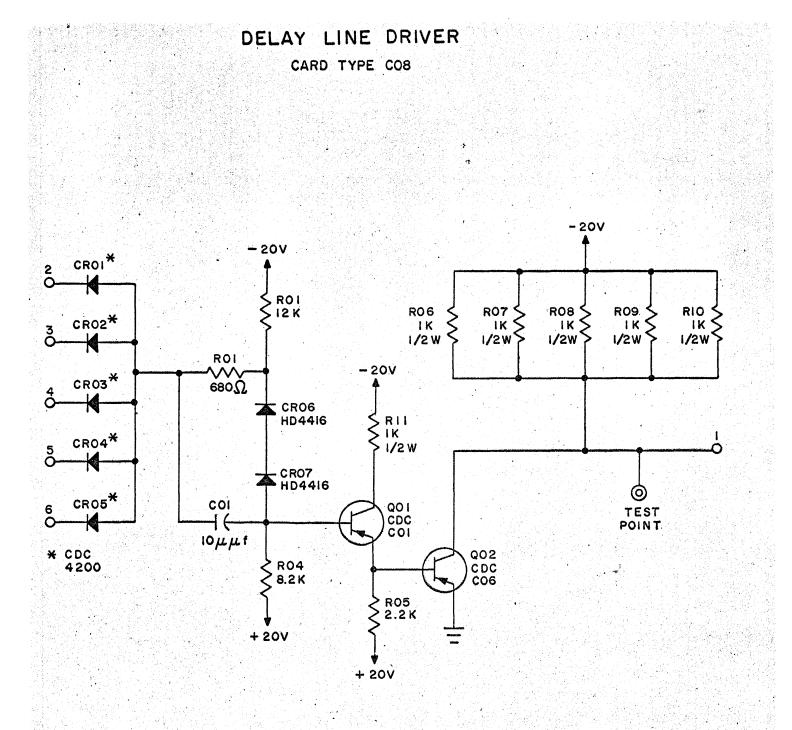

## DELAY LINE DRIVER Card Type C08

### FUNCTION

The function of this circuit is to provide an output suitable for driving a terminated 200-ohm delay line. With a 200-ohm load at pin 1 and the circuit in its quiescent state, the output voltage level is approximately -10v. Upon receipt of a -5.8v "1" input, both transistors switch to a state of heavy conduction and the output voltage becomes approximately -0.3v.

#### **OPERATION**

The circuit has 5 logical OR inputs; thus a -5.8v "1" on any input will activate the circuit. An unused input is effectively a steady "0", regardless of whether it is grounded or left open.

An input level-shifting action is provided by the two forward-drop diodes CR06 and CR07. These are silicon diodes having a forward voltage drop of approximately 0.7v. The two diodes in series provide a voltage shift of +1.4v from the cathode of CR06 to the anode of CR07.

With -1.1v "0" inputs, the base of Q01 is held at approximately +1.3v by the level-shifting diodes. Transistor Q01 is connected as an emitter follower; thus its emitter voltage is equal to the base voltage plus the base-emitter junction drop, and is approximately +1.6v. This provides sufficient forward bias so that minimum conduction is maintained through Q01. The emitter voltage of Q01 drives the base of Q02, which is a grounded emitter stage. The base-emitter junction of Q02 is therefore back-biased by the +1.6v input, and Q02 is cut off.

A -5.8v "1" input holds the base of Q01 at approximately -0.6v causing Q01 to conduct heavily. The emitter voltage of Q01 goes to approximately -0.3v, which causes Q02 to switch on and conduct heavily. In this state, the circuit output is equal to the drop across Q02, and approaches -0.3v.

With Q02 in the cut off state, its collector voltage tends to rise toward -20v. However, the 200-ohm load acts as a voltage divider with the equivalent 200-ohm resistance of the five 1000-ohm resistors, and the output stabilizes at -10v.

#### NOTES:

- I. CIRCUIT HAS 5 "OR" INPUTS.

- 2. A -5.8V "I" INPUT CAUSES TRANSISTORS TO CONDUCT.

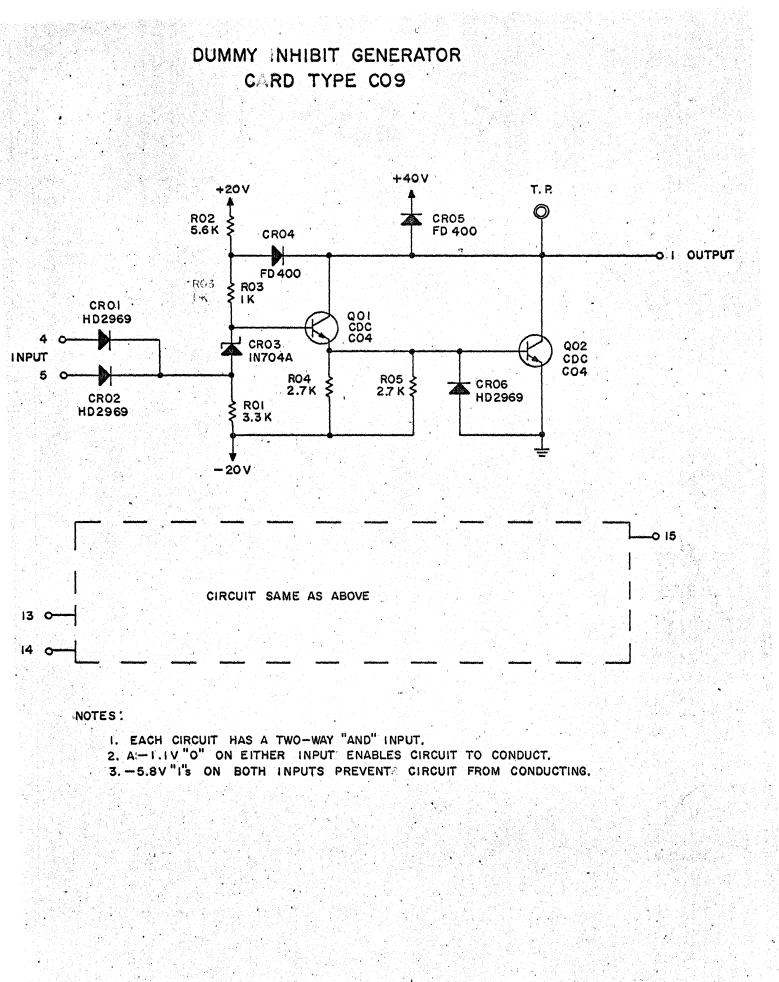

### DUMMY INHIBIT GENERATOR

Card Type C09

### FUNCTION

The function of the circuits on this card is to enable a 340 ma current to flow from pin 1 or 15 to ground, whenever at least one input to the respective circuit is a -1.1v "0". The dummy inhibit circuits are energized by a +40v supply, and each circuit contains a series 133-ohm resistor external to the circuit on the card. Each dummy inhibit circuit terminates at either pin 1 or pin 15 of a C09 card, and the path will be completed to ground allowing current to flow if the respective dummy inhibit generator switches to its conduction state.

### OPERATION

Each circuit has a two-way logical AND input, meaning that both inputs must be at the -5. v''' level in order for an input to be sensed. A -1. v''' signal on either input will disable the AND. An unused input acts as a steady "1" if left open, or as a steady "0" if grounded.

The transistors are disabled if the AND is satisfied by two -5.8v "1" inputs, preventing dummy inhibit current from flowing. If either input receives a -1.1v "0", the transistors switch to the conduction state and current is allowed to flow from the output pin to ground.

A level-shifting action is provided by the 4.1v zener diode CR03. This diode is reverse-biased so that its operating point is beyond the knee of the breakdown region; thus the cathode remains approximately 4.1v positive with respect to the anode, regardless of current fluctuations.

When the AND is satisfied by -5.8v "1" inputs, this voltage level plus the forward drop of diodes CR01 and CR02 holds the anode of CR03 at approximately -6.1v. The base of Q01 is therefore at approximately -2v. The emitter of Q01 is held at approximately -0.3v by the forward drop of CR06. This places a reverse bias of 1.7v across the base-emitter junction of Q01, so that it is well into the cut off region. In addition, the 0.3v drop of CR06 reverse-biases the base-emitter

junction of Q02, so that it is also cut off. Thus, except for negligible leakage effects, the output pin is completely isolated from ground.

When either input receives a -1.1v "0", the anode of CR03 is held at approximately -1.4v. The 4.1v voltage differential across the zener diode CR03 attempts to hold the base of Q01 at approximately +2.7v. This causes Q01 to switch on and conduct heavily, but it is clamped out of saturation by CR04. The emitter voltage of Q01 rises to approximately +2.2v, providing drive to the base of Q02. Transistor Q02 thus switches to the conduction state, allowing current to flow from the output pin to ground.

The connection of diode CR05 and the +40v supply provides a clamp for the collector voltage of the transistors. When the transistors switch to the non-conducting state, the inductance of the dummy inhibit line will tend to induce high-voltage transients; however, these inductive transients are clamped at +40v plus the drop across the silicon diode CR05.

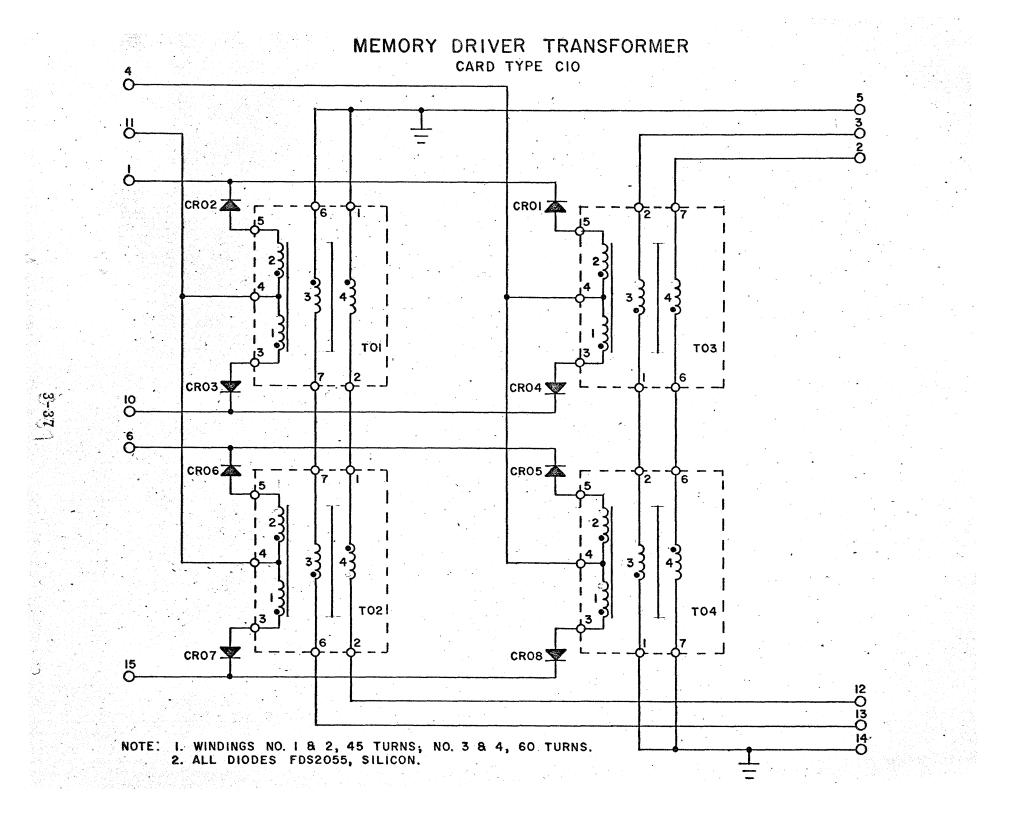

# DRIVER TRANSFORMER Card Type C10

### FUNCTION

The function of this card is to provide half-currents of 340 ma at approximately 44v to the memory stack when supplied with primary power at the +20v level. The card contains four 6:4.5 voltage step-up transformers, each having two secondary windings of 60 turns and a center-tapped primary of 90 turns. The transformers are connected so that two operate simultaneously with their primary windings energized in parallel from +20v and their secondaries connected in series. The output voltages are therefore additive, resulting in levels of approximately 44v.

This card operates in conjunction with three other cards; a gate card which switches a source of +20v into the center taps of the transformer primaries, and with two transformer driver cards which allow current to flow from one of the primary windings to ground.

#### **OPERATION**

A schematic of the circuit contained on card type C10 is presented in the accompanying diagram, with the transformers indicated by dashed outlines. The transformers are identical, each having four windings and seven connecting pins as shown. Silicon diodes at transformer pins 3 and 5 provide isolation so that current cannot flow through a primary winding in the wrong direction, and prevent interaction between transformers.

The dots on the transformer windings indicate the <u>direction</u> of <u>current flow</u>. For example, if current flows into the dotted end of the primary winding, current will also flow into the dotted end of the secondary winding. There will consequently be a voltage reversal between the dotted ends of the primary and secondary windings.

As an example of operation, assume that card pin 11 is energized from a source of +20v. This is fed to the center tap of the primary windings of transformers T01 and T02. Then, by connecting card pins 1 or 10, and 6 or 15 to ground, it is possible to produce either +44v or -44v at either pin 12 or pin 13 while the

$\mathbf{A}^{(1)}$

other pin remains at essentially zero potential. The positive and negative potentials correspond to the memory cycle, in which a current of one polarity is used to "read" and the other to "write".

To produce -44v at pin 12, the external circuitry would connect card pins 10 and 15 to ground, allowing 450 ma to flow through windings #1 of T01 and T02. The primary voltage is of the order of +18v, due to the drop across the silicon diode and external circuitry; however, the 6:4.5 transformer step-up produces a secondary voltage of approximately +22v.

It is seen that windings #4 of T01 and T02 are connected in series so that the voltages are additive, resulting in -44v at pin 12. It is further seen that windings #3 are connected oppositely, so that the voltages cancel and only a negligible effect is produced at pin 13. However, -44v will appear at pin 13 with negligible voltage at pin 12 if the external circuitry grounds pin 6 instead of pin 15.

If it is desired to produce +44v at pin 12, then pins 1 and 6 will be grounded; and if the +44v is to appear at pin 13, pins 1 and 15 will be grounded.

Under the preceding sets of conditions, the voltages appearing on pins 12 and 13 will appear on pins 2 and 3, if the source of +20v is gated into pin 4 instead of pin 11.

The various outputs available at pins 2, 3, 12, and 13 and the conditions necessary to produce them, are listed below. Pin 5 provides a common return for pins 12 and 13, and pin 14 provides a common return for pins 2 and 3.

| Gate +20v<br>into: | Enable Ground<br>Connection From: | Resulting Voltages at:<br>Pin 2 Pin 3 Pin 12 Pin 13 |

|--------------------|-----------------------------------|-----------------------------------------------------|

| Pin 4              | Pins 6 & 10                       | -44v                                                |

| Pin 4              | Pins 1 & 15                       | · +44v                                              |

| Pin 4              | Pin's 10 & 15                     | -44v'                                               |

| Pin 4              | Pins 1 & 6                        | +44 <b>v</b>                                        |

| Pin 11             | Pins 10 & 15                      | -44v                                                |

| Pin 11 -           | Pins 1 & 6                        | +44v                                                |

| Pin 11             | Pins 6 & 10                       | -44v                                                |

| Pin 11             | Pins 1 & 15                       | +44v                                                |

### BASIC INVERTER CIRCUIT

The basic inverter circuit consists of two transistor stages, as shown in figure 1. Transistor Q01 is a grounded emitter stage which supplies AND current to the load, and transistor Q02 is an emitter follower stage which supplies OR current to the load.

The input to the circuit consists of two levels of diode logic. The maximum number of inputs is limited by the number of available input pins on a circuit card; however, the maximum number of individual inputs to any single AND cannot exceed 6. The number of OR inputs has no similar restriction, and is limited only by the number of input pins.

The input logic diodes are Hughes HD2969, which are medium speed germanium devices. A set of graphs is included in this report which shows the comparative recovery time of these diodes.

The response of an AND input is a function of the time constant of the AND resistor R01, shunt circuit capacitance at point (A), and the recovery speed of the input diodes. Because additional AND diode inputs increase the shunt capacitance, it is necessary to decrease the size of the AND resistor a proportionate amount as the number of inputs to the AND increases beyond 3. Since the OR inputs are not affected by this time constant, the output of an inverter circuit has better switching characteristics with an OR input than with AND inputs.

The transition speed of the AND circuit varies inversely with the recovery speed of the AND diodes. Slow diodes allow additional recovery current to be drawn, which in effect, allows a larger turn-on current in the first transistor stage.

The input resistor and diode network of transistor Q01 establishes the clamping levels for the output signal. This network also provides feedback to the base of Q01 which stabilizes the two quiescent values of the output voltage.

The input network establishes an input threshold level of approximately -3 volts. Thus, the input signal must be more negative than -3 volts before transistor Q01 turn-on current is allowed to flow. Silicon forward drop diodes CR21 through CR24 are used in the input network to obtain a constant d-c level for signal threshold. These diodes also have a low dynamic impedance which causes little attenuation of the input signal current.

The 22 uuf speed-up capacitor C01 on the input of the first stage bypasses the 1.2 k resistor R10 and the diode network during the initial rise or fall of the input signal. This provides additional drive to the base of Q01 during the input signal transition, thereby speeding the switching of this stage.

Feedback is accomplished through two high speed silicon diodes CR25 and CR26, which have very low stored charge characteristics. If these diodes were capable of storing excessive charge, there would be additional delay in switching. By using diodes with very low storage, the initial switching speed is greatly improved.

When the grounded emitter stage Q01 is turned on, collector current flows out of the circuit through the series diode CR27. In this state, Q01 can supply current to 8 AND loads. Transistor Q01 is clamped out of saturation by the silicon feedback diode CR26, and the output voltage settles at a nominal value of -1.1 volt. The voltage drop across diode CR27 insures a back bias being applied to the base-emitter junction of Q02, thereby keeping this stage turned off.

When Q01 turns off, the collector voltage starts to rise toward -20 volts. Since the voltage across the load cannot change as quickly as the collector voltage of Q01, the series output diode CR27 is back-biased and the output emitter follower stage Q02 is turned on.

The turn-on current is applied to the base of Q02 at the rate at which Q01 turns off. The turn-on current is the current that is drawn through the first stage collector resistors R15 and R16, and this current is available to turn on the output stage only as fast as it is turned off in the first stage.

Transistor Q02 in the on state proceeds to drive the output voltage negative. At about -5.8 volts, the output is fed back to the input of the first stage by diode CR25 to start the clamping action. Since this process has delay associated with it, the output signal overshoots the -5.8 volt mark and may carry as far as -8 volts. The circuit then settles the voltage back to the -5.8 volt level. During this time, transistor Q02 can pass the current of 8 OR loads through to the -20 volt supply.

The switching speed of the circuit is slightly faster when driving OR loads instead of AND loads. With full AND loading, the turn-on and turn-off transition times are less than 30 nanoseconds. The transition time to the -3 volt threshold is approximately 10 to 15 nanoseconds. This accounts for the majority of the inverter circuit delay, which is less than 20 nanoseconds.

In the case of driving 8 OR loads, the transitions are faster. This is because transistor Q02 is being driven by Q01 and the gain of both transistors is effective in switching the load. This additional gain causes the output load to be driven harder and therefore switches it faster.

42

### Ground Rules

- 1. An inverter may simultaneously drive 8 AND loads, 8 OR loads, or any combination up to 8 loads total.

- 2. A flip-flop or a control delay may drive only 7 loads, because it is required to provide its own feedback which constitutes 1 load.

- The switching time for a circuit output to change from a -5.8v "1" to a -1.1v "0", or vice versa, is approximately 30 nanoseconds.

- 4. The delay time required for a circuit output to reach the -3v threshold is approximately 10 to 20 nanoseconds and is dependent upon the loading.

- 5. A circuit having an OR input will switch faster than a circuit having an AND input; thus the delay time is reduced with an OR input.

- 6. Generally, two electronic inversions and a total of 60 inches of lead length are allowed between successive clock phases. This rule may be violated in cases where the logic circuits are very lightly loaded, but all such cases must be individually inspected to certify satisfactory operation.

- 7. Any interconnecting lead more than 80 inches long must be clamped by means of the circuit on card type C02.

- 8. All drive lines from H<sup>--</sup> terms to N<sup>--</sup>, V<sup>--</sup>, or Y<sup>--</sup> terms must be clamped, regardless of length.

- 9. N<sup>--</sup>, V<sup>--</sup>, and Y<sup>--</sup> terms having a clock signal on an AND input must use one of the special card types numbered C72, C73, and C74. The clock input must be on the following pins:

Card Type Inverter A Inverter B

| C72     |                 | 5 01          | • 6                                      | 13 or | 14 |

|---------|-----------------|---------------|------------------------------------------|-------|----|

| C73     | р.<br>С. р.     | 2 01          | • 3                                      | 10 or | 11 |

| C74     |                 | 5 01          | • 6                                      | 13 or | 14 |

| an dara | t ki çer de beş | 영국의 관계에 관망했다. | 방송 전 전 전 전 전 전 전 전 전 전 전 전 전 전 전 전 전 전 전 |       |    |

- 10. In case an entire AND input group is unused, at least one of the inputs must be grounded.