# CONTROL DATA® SYSTEM 17

1784 COMPUTER INPUT/OUTPUT SPECIFICATIONS

**PRELIMINARY**

|                            | REVISION RECORD                                                     |  |  |  |

|----------------------------|---------------------------------------------------------------------|--|--|--|

| REVISION DESCRIPTION       |                                                                     |  |  |  |

| 01                         | Preliminary edition released Class B, ECO CK1015, October 24, 1974. |  |  |  |

|                            |                                                                     |  |  |  |

|                            |                                                                     |  |  |  |

|                            |                                                                     |  |  |  |

|                            |                                                                     |  |  |  |

|                            |                                                                     |  |  |  |

|                            |                                                                     |  |  |  |

|                            |                                                                     |  |  |  |

|                            |                                                                     |  |  |  |

|                            |                                                                     |  |  |  |

|                            |                                                                     |  |  |  |

|                            |                                                                     |  |  |  |

|                            |                                                                     |  |  |  |

|                            |                                                                     |  |  |  |

|                            |                                                                     |  |  |  |

|                            |                                                                     |  |  |  |

|                            |                                                                     |  |  |  |

| ublication No.<br>89673100 |                                                                     |  |  |  |

© 1974

by Control Data Corporation

Printed in the United States of America

Address comments concerning this manual to:

Control Data Corporation

Small Computer Development Division

4455 Eastgate Mall

La Jolla, California 92037

or use Comment Sheet in the back of this manual.

# **PREFACE**

This specification manual provides the channel operating characteristics for the engineer concerned with the peripheral interface on the CONTROL DATA  $^{\bigcirc R}$  1784 Computer.

The following publications may be found useful:

| Control Data Publication                            | <u>Pub. No.</u> |

|-----------------------------------------------------|-----------------|

|                                                     |                 |

| 1784 Computer System Reference Manual               | 89633400        |

| 1784 Computer, Customer Engineering Manual          | 89633300        |

| TTL A/Q DSA Bus Expander, Hardware Reference Manual | 89758600        |

In addition, the 1784 Computer System Peripheral Equipment Customer Engineering and Reference Manuals should be consulted.

# CONTENTS

|    |                                            | Page |

|----|--------------------------------------------|------|

| 1. | INTRODUCTION                               |      |

|    | Scope and Purpose                          | 1-1  |

|    | General Discussion                         |      |

|    | The Two Access Channels                    | 1-2  |

|    | Channel Access                             | 1-3  |

| 2. | MECHANICAL SPECIFICATIONS                  |      |

|    | Introduction                               | 2-1  |

|    | Specifications for Printed Wiring Assembly |      |

|    | Dimensions and Standard Hole Locations     | 2-1  |

|    | Material                                   | 2-4  |

|    | Card Stiffener                             | 2-4  |

|    | Component Protusion from Board             | 2-4  |

|    | Connector                                  | 2-4  |

|    | Connector Nomenclature                     | 2-7  |

|    | Pin Assignments                            | 2-7  |

|    | Test Points                                | 2-8  |

|    | Back-Plane Interconnections                | 2-8  |

| 3. | ELECTRICAL SPECIFICATIONS                  |      |

|    | Introduction                               | 3-1  |

|    | Specifications                             |      |

|    | Supply Voltages                            | 3-1  |

|    | Supply Drain                               | 3-1  |

|    | Power Dissipation                          | 3-2  |

|    | Voltage Brought into Back-Plane            | 3-2  |

|    | Pin Assignment                             | 3-2  |

|    | Channel Loading                            | 3-2  |

|    | Peripheral Equipment Connections           | 3-2  |

# C O N T E N T S (Cont'd.)

|    |                              | Page |

|----|------------------------------|------|

| 4. | A/Q CHANNEL                  |      |

|    | Input, Output on A/Q Channel | 4-1  |

|    | Control Signals              | 4-3  |

|    | Read                         | 4-3  |

|    | Write                        | 4-3  |

|    | Reply                        | 4-3  |

|    | Reject                       | 4-4  |

|    | Program Protect              | 4-4  |

|    | Character Input              | 4-4  |

|    | Continue Bit                 | 4-6  |

|    | Addressing                   |      |

|    | Converter                    | 4-6  |

|    | WEZ                          | 4-6  |

|    | Equipment                    | 4-7  |

|    | Command Code                 | 4-7  |

|    | Unit (Channel)               | 4-7  |

|    | I/O Operations               | 4-8  |

|    | Director                     | 4-8  |

|    | Data Transfer                | 4-8  |

|    | Functions                    | 4-9  |

|    | Status                       | 4-9  |

|    | A/Q Channel Timing           | 4-9  |

|    | A/Q Channel Access           | 4-11 |

|    | Signal Definitions           | 4-12 |

89673100 01 .v

# CONTENTS (Cont'd.)

|    |                                              | Page |

|----|----------------------------------------------|------|

| 5. | DIRECT STORAGE ACCESS CHANNEL                |      |

|    | Input, Output on DSA Channel                 | 5-1  |

|    | Control Signals                              | 5-2  |

|    | Request                                      | 5-2  |

|    | Write Enable                                 | 5-3  |

|    | Resume                                       | 5-3  |

|    | Program Protect, Protect Fault               | 5-3  |

|    | Storage Parity, Parity Fault                 | 5-4  |

|    | Addressing                                   | 5-4  |

|    | I/O Operations                               | 5-4  |

|    | Data Transfer                                | 5-4  |

|    | DSA Priority                                 | 5-5  |

|    | DSA Channel Timing                           | 5-6  |

|    | Timing Considerations for Two Bank Operation | 5-10 |

|    | DSA Channel Access                           | 5-10 |

|    | Distributed Scanner                          | 5-15 |

|    | Scanner Operation                            | 5-15 |

|    | Scanner Connections                          | 5-15 |

|    | Special Connections                          | 5-18 |

# C O N T E N T S (Cont'd.)

|    |                               | Page |

|----|-------------------------------|------|

| 5. | INTERRUPTS                    |      |

|    | Internal Interrupt            | 6-1  |

|    | Interrupt Signals             | 6-1  |

|    | Interrupt on Data             | 6-1  |

|    | Interrupt on End-of-Operation | 6-2  |

|    | Interrupt on Alarm            | 6-2  |

|    | Interrupt Hardware            | 6-2  |

|    | Interrupt Priorities          | 6-2  |

|    | Protected Program             | 6-4  |

89673100 01 vii

# CONTENTS (Cont'd.)

|             |                                   | Page |

|-------------|-----------------------------------|------|

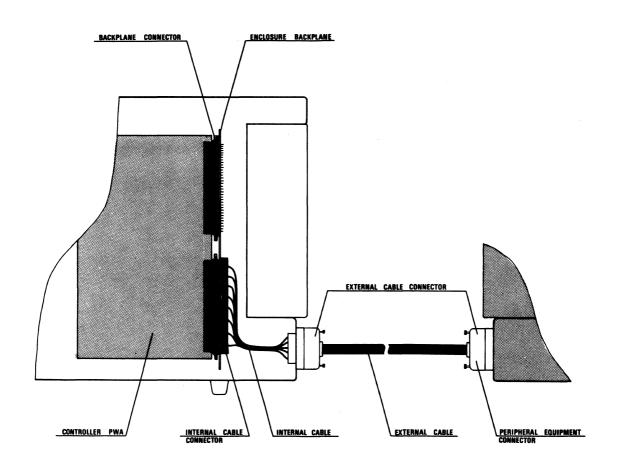

| APPENDIX A. | Peripheral Cables                 | A-1  |

| APPENDIX B. | Design Aids                       |      |

|             | Introduction                      | B-1  |

|             | Artwork for the Printed Wiring    | B-1  |

|             | Layout Grid and References        | B-1  |

|             | Artwork for Printed Conductors    | B-5  |

|             | High Speed Signal Lines           | B-6  |

|             | Parallel Signal Lines             | B-6  |

|             | Processing for Printed Conductors | B-7  |

|             | Layout Rules for TTL PWA Design   | B-8  |

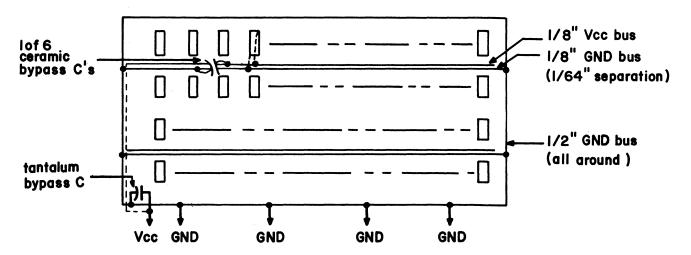

|             | Supplies and Filtering            | B-8  |

|             | Unused Elements                   | B-9  |

|             | Layout Procedure                  | B-10 |

|             | Ground System                     | B-10 |

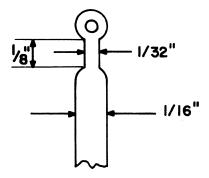

|             | Printed Wiring Patterns           | B-11 |

|             | Electrical                        | B-13 |

|             | Terminations                      | B-13 |

# LIST OF FIGURES

| Figure |                                                                    | Page |

|--------|--------------------------------------------------------------------|------|

| 1-1    | Typical Configuration of 1784 Computer System                      | 1-5  |

| 1-2    | Card Placement Slot Assignment                                     | 1-6  |

| 2-1    | 50-PAK Printed Wiring Board Dimensions and Standard Hole Locations | 2-2  |

| 2-2    | 50-PAK Connector Pin Configuration                                 | 2-5  |

| 2-3    | Card Stiffener on the 50-PAK PWB                                   | 2-6  |

| 3-1    | A/Q Channel Input/Output Lines                                     | 3-3  |

| 4-1    | Input-Output Timing Diagram                                        | 4-5  |

| 4-2    | A/Q Input/Output Timing                                            | 4-10 |

| 5-1    | DSA Channel Timing                                                 | 5-7  |

| 5-2    | Scanner Wiring Connections                                         | 5-17 |

| 5-3    | Typical Scanner Timing                                             | 5-19 |

| A-1 | Arrangement of Internal and External Cables                 | A-2  |

|-----|-------------------------------------------------------------|------|

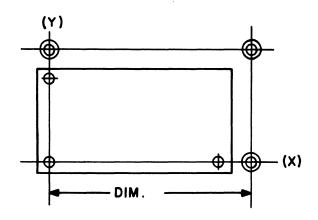

| B-1 | Printed Wiring Board Dimensions and Standard Hole Locations | B-3  |

| B-2 | Dimensioning and Alignment                                  | B-4  |

| B-3 | Etched Circuit Patterns for Solder Areas                    | B-11 |

| B-4 | Recommended Ground and Logic Voltage Connection             | B-12 |

| B-5 | Signal Line Terminations                                    | B-13 |

89673100 01 ix

# LIST OF TABLES

| Table | Title                                        | Page |

|-------|----------------------------------------------|------|

| 4-1   | Use of Director                              | 4-8  |

| 4-2   | A/Q Channel Pin Assignments                  | 4-11 |

| 4-3   | Signal Definitions for A/Q Channel           | 4-12 |

| 5-1   | DSA Channel Pin Assignments                  | 5-11 |

| 5-2   | Signal Definitions for                       | 5-12 |

|       | Direct Storage Access (DSA) Channel          | 5-12 |

| 6-1   | Interrupt Access Pin Assignment on A/Q Slots | 6-3  |

SECTION 1

INTRODUCTION

#### INTRODUCTION

#### SCOPE AND PURPOSE

This specification manual applies to all external equipment used with the CONTROL DATA  $^{\bigcirc}$  1784 Computer. The purpose of the manual is to describe the operating characteristics which apply to all peripherals connected on the computer A/Q Data Channel or on the Direct Storage Access (DSA) Channel.

The manual is written for the engineer concerned with the peripheral The general discussion of the computer input/output access is followed by the mechanical and electrical specifications for all interface assemblies. Descriptions and specifications for the two access channels as well as for the interrupt system are given in Section 4. More detailed discussion of the logic design of the computer system are found in the applicable manuals written for customer engineers (for a partial list refer to the Preface for this manual). Use the 1784 Reference Manual, publication number 89633400 and the software documentation for applications and programming. Refer to Appendix A of this manual for a description of data transmissions techniques, including the interface required between the TTL\_components of the 1784 and the input/output equipment of the CONTROL DATA(R) 1700 system peripherals (3000 series current logic).

89673100 01 1-1

#### GENERAL DISCUSSION

#### The Two Access Channels

Communication between the 1784 computer and its external peripherals takes place through two data channels:

Direct Storage Access (DSA) Channel: provides fast buffered bi-directional data transfer with direct access to the memory.

#### 2. A/Q Channel:

provides non-buffered bi-directional data transfer, utilizing the A and Q registers of the Computer. The A register holds the data and the function codes, it also accepts the status replies from peripheral equipment; the Q register holds the address of the peripheral equipment.

The A and Q registers are also used to initiate and monitor data transfer through the DSA Channel.

Rate of data transfer depend on the computer mode of operation. Exact timing specifications are given in later sections; the following table summarizes approximate rates in terms of 16-bit words-per-second. Note that the two versions of the computer differ in their memory cycle times as follows:

1784-1: memory cycle time 600 nsec 1784-2: memory cycle time 900 nsec

#### APPROXIMATE DATA TRANSFER RATES

| Channe1 |                                                                 | RATE (16-bit words/second) for equipment     |                              |

|---------|-----------------------------------------------------------------|----------------------------------------------|------------------------------|

|         | 1784-1                                                          | 1784-2                                       |                              |

| DSA     | $\begin{cases} 1.1 \times 10^6 \\ >0.7 \times 10^6 \end{cases}$ | 1.6 x 10 <sup>6</sup> >0.5 x 10 <sup>6</sup> | with priority<br>no priority |

| A/Q     | 110 x 10 <sup>3</sup>                                           | 160 x 10 <sup>3</sup>                        | -                            |

#### Channel Access

Peripheral equipments communicate with the appropriate channel through peripheral controllers and adaptors. A data bus provides the connection between the peripheral controllers and each input/output channel (A/Q, DSA). The peripherals connected to a bus, time-share the access to the corresponding channel.

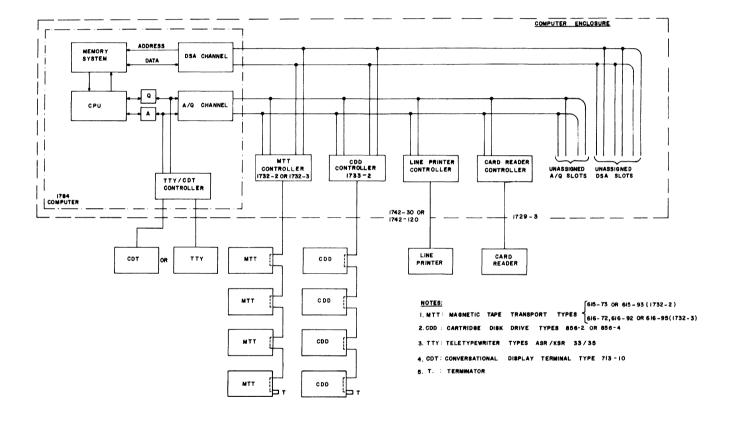

The access priority is controlled by the computer interrupt system (refer to Section 6). Access connections to each channel bus are available on identical pins of preassigned slots in the computer enclosure. Each slot can accommodate a peripheral controller. Connections to each channel may be made on a random basis provided bus loading conditions are observed (refer to Sections 4,5). The logic signal levels are those of TTL integrated circuits. A typical configuration of the 1784 Computer with peripheral devices is shown in Figure 1-1.

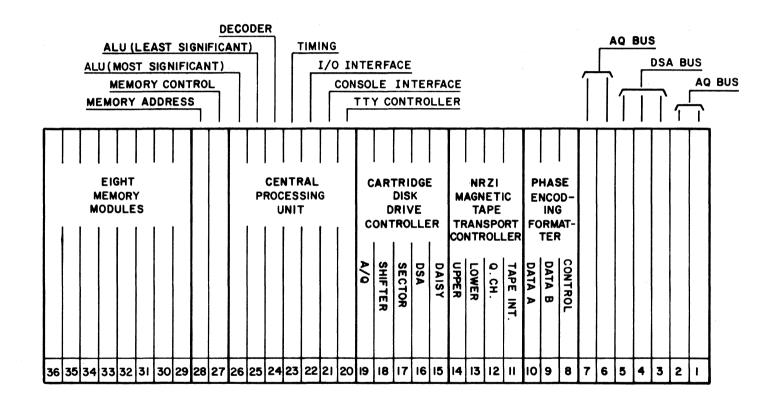

The slot assignment for peripheral controller and adaptor assembly placements in the computer enclosures is shown in Figure 1-2 (DSA Bus, A/Q Bus). Preassigned slots provide access to both the A/Q and the DSA channel for the following equipments, through their respective controllers:

| Peripheral Equipment                            |                                                            |    | Controller         |

|-------------------------------------------------|------------------------------------------------------------|----|--------------------|

| 856-2, 856-4                                    | Cartridge Disk Drive (CDD)                                 |    | 1733-2             |

| 615-73 or 615-93<br>616-72,<br>616-92 or 616-95 | Magnetic Tape Transport (MTT) Magneti Tape Transport (MTT) |    | 1732-2<br>1732-3   |

|                                                 | Phase-Encoding Formatter (PE) option                       | or | 10300-1<br>10300-2 |

89673100 01 1-3

Note that the 1784 computer equipment includes the TTY Controller to communicate with a Teletypewriter (TTY) or a Conversational Display Terminal (CDT) through the A/Q channel; refer to the 1784 CE manual, publication number 89633300 and 1784 Reference manual, publication number 89633400.

The mechanical and electrical specifications of the printed wiring assemblies which can be accommodated in the enclosure slots are given in Sections 2 and 3, and the signal and timing specifications on the two channels in Sections 4 and 5.

1-4 89673100 01

Figure 1-1. Typical Configuration of 1784 Computer System

Figure 1-2.

а •

Main

Computer

Enclosure

Card Placement Slot Assignment

89673100 01

Figure 1-2.

Card Placement Slot Assignment

DSA BUS DSA BUS DSA BUS DSA BUS MEMORY CONTROL MEMORY ADDRESS AQ BUS <u></u> EIGHT MEMORY OPEN OPEN AQ OPEN AQ AQ BUS BUS BUS Expansion Enclosure MODULES [8] 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 7 6 5 4 3 2 10 9

|  |  | 1 |

|--|--|---|

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

# SECTION 2

MECHANICAL SPECIFICATIONS

#### MECHANICAL SPECIFICATIONS

#### INTRODUCTION

All peripheral controllers and adaptors accommodated within the computer enclosures must conform to the mechanical constraints imposed by these enclosures. Thus the circuitry has to be accommodated on one or more printed wiring assemblies. These must conform to CDC 50-PAK specifications as well as other dimensional and heat-dissipation constraints.

This section gives the applicable specifications. Guide lines to aid in the mechanical design and layout of the printed wiring assembly are given in Appendix B.

#### SPECIFICATIONS FOR PRINTED WIRING ASSEMBLY

This specification gives the mechanical requirements for Printed Wiring Assemblies (PWA) designed to be accommodated in the 1784 Computer enclosures. The PWA is built on a double sided Printed Wiring Board (PWB).

#### Dimensions and Standard Hole Locations

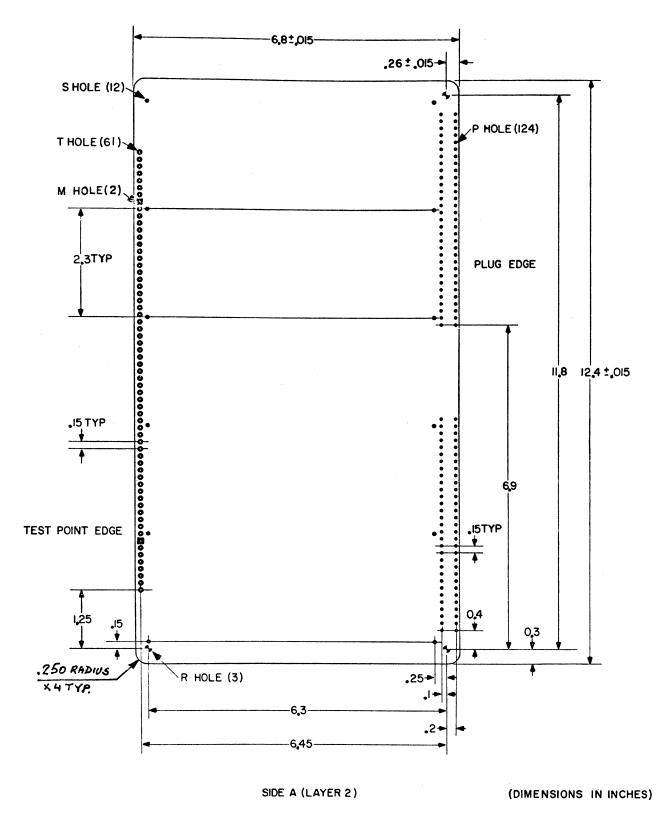

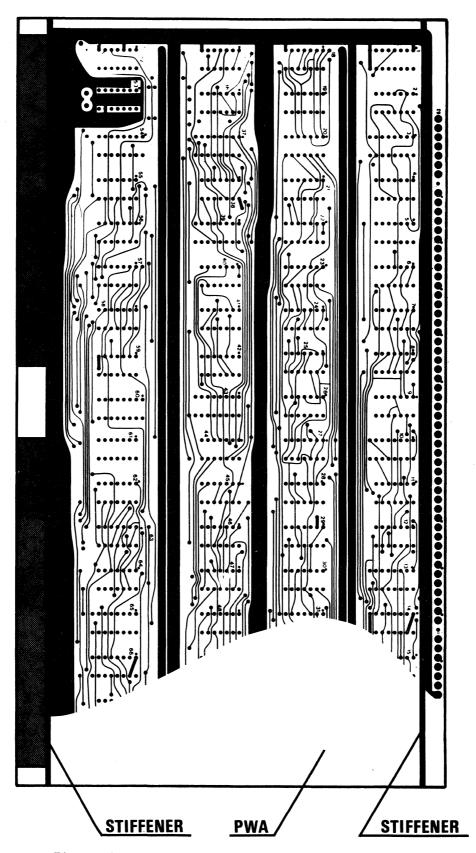

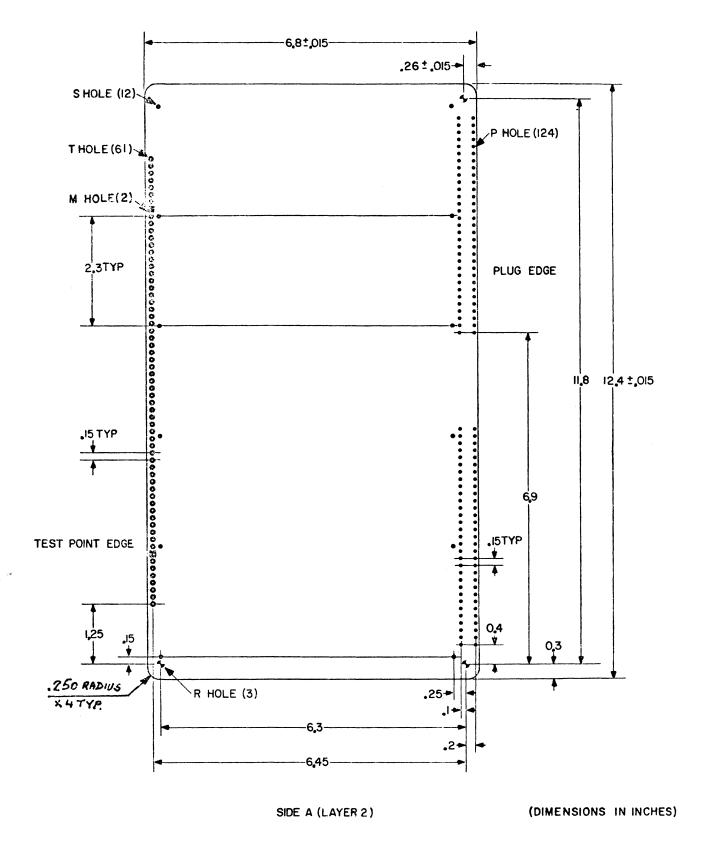

For dimensions of the CDC 50-PAK Printed Wiring Board (PWB) and hole locations for the connector and test points refer to Figure 2-1.

89673100 01 2-1

Figure 2-1. 50-PAK Printed Wiring Board Dimensions and Standard Hole Locations

#### Notes for Figure 2-1

- 1. All dimensions are in inches.

- 2. Unless otherwise specified, all hole centers must be located within 0.004 of the intersections of a 0.05 square grid. (All holes must be located 0.008 diameter to a 0.025 BSC grid at maximum material condition).

- 3. Any unmarked hole electrically isolated from all other copper on the board is Class B.

#### 4. Hole legend:

| SYMBOL                            | DIAMETER                             | TOLERANCE                                                   | CLASS                 |

|-----------------------------------|--------------------------------------|-------------------------------------------------------------|-----------------------|

| T<br>P<br>S<br>R<br>M<br>Unmarked | .073<br>.039<br>.090<br>.125<br>.090 | ±.005<br>±.003<br>±.005<br>±.005<br>±.005<br>( +.003<br>000 | A<br>A<br>B<br>B<br>B |

|                                   |                                      |                                                             |                       |

5. Clearances of components and foil from board edges:

|            | TEST<br>POINT<br>EDGE | PLUG<br>EDGE | SHORT<br>EDGES |

|------------|-----------------------|--------------|----------------|

| Components | 0.4                   | 0.65         | 0.15           |

| Foil       | 0.1                   | 0.1          | 0.15           |

89673100 01 2-3

#### Material

The base material for the PWB is 0.062 fiber glass according to CDC specification 52338700.

#### Card Stiffener

A card stiffener must be used along both long edges of the PWB (plug edge and test point edge, refer to Figure 2-1). The recommended card stiffener is shown in Figure 2-3.

#### Component Protrusion from Board

Component side (side A) 0.27" max

Soldering side (side B) 0.09" max

#### Connector

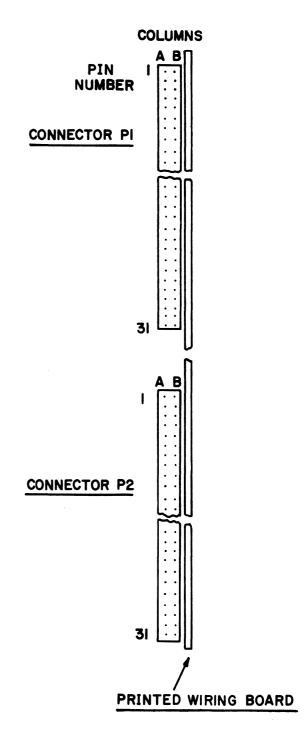

Each PWA plugs into two female connectors on the back-plane of the computer enclosure. Two matching male connectors (CDC P/N 94243400) are mounted on the PWB in the standard holes (refer to Figure 2-1), on the left hand side of the PWB when viewed from the connector end (refer to Figure 2-2).

2-4 89673100 01

#### Notes:

- 1. View from connector end of printed wiring board.

- 2. Connector pin designation is illustrated in the following example:

P1B03 is pin number 3 in column B of connector P1.

Figure 2-2. 50-PAK Connector Pin Configuration

Figure 2-3. Card Stiffener on the 50-PAK PWB

# Connector Nomenclature

When the PWA is viewed from the connector end (refer to Figure 2-2) the following designations apply:

- Connector P1 and connector P2 are in top-to-bottom order

- Column A and column B of connector pins are in left-right order

- Pins 1 to 31 are numbered from top-to-bottom.

# Pin Assignments

The following connector pins are assigned permanently:

| Connector<br>Pin                 | Assigned to                                    | Remarks                                                                                       |

|----------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------|

| P2A31<br>P1A01                   | V <sub>cc</sub> (+5V)<br>V <sub>EE</sub> (-5V) | Main logic voltage                                                                            |

| P1B11<br>P1A29<br>P2A03<br>P2A21 | Logic ground                                   | At best four pins are assigned for logic ground                                               |

| P2B31 )<br>P1B01 }               | Logic ground<br>(optional                      | If there are free pins available, these two should be grounded (order of preference as given) |

#### Test Points

The column of holes on the left hand side of the PWB are designated test points (PWB viewed from component side, connectors to the fight, - refer to Figure 2-1). The Test Points (TP) are numbered consecutively from top to bottom. Test point 1 is reserved for logic ground, 63 for  $V_{\rm CC}$ .

#### Back-Plane Interconnections

The layout of interconnected Printed Wiring Assemblies (PWA's) must be coordinated so that back-plane wiring is as short and direct as possible. To implement this, the designer must specify approximately the plug and pin number for each signal.

2-8 89673100 01

# SECTION 3

**ELECTRICAL SPECIFICATIONS**

#### ELECTRICAL SPECIFICATIONS

#### INTRODUCTION

This section gives the electrical constraints applicable to the peripheral controllers and adaptors accommodated on Printed Wiring Assemblies (PWA's) within the 1784 Computer enclosures.

#### SPECIFICATIONS

#### Supply Voltages

The power supply voltage normally available at the peripheral controller slots is the enclosure main logic voltage ( $V_{\rm CC}$  = +5V) and logic ground.

Other supplies are available within the enclosures, refer to Table 4-6 of the 1784 Computer CE Manual, publication number 89633300.

#### Supply Drain

The PWA may draw current from the enclosure power supply subject to the following limitations:

- the overall current drain allowed is 30A for <u>all</u> controllers in each enclosure (refer to 1784 Computer CE Manual, publication number 89633300).

- current allowed per connector contact is 3A maximum.

- power dissipation (see below).

89673100 01 3-1

#### Power Dissipation

Power dissipation from PWA's accommodated within the computer enclosure is restricted as follows:

Maximum from any one PWA:

15 watts

Average from three or more adjacent PWA's:

10 watts each PWA

Power concentrations substantially higher than average may need special provisions.

#### Voltage Brought into Back-Plane

If a voltage other than that available in the enclosure, is supplied through the back-plane, it shall be 0 to +7V max if unprotected, or  $\pm30V$  max if isolated to prevent unintentional shorts to adjacent back-plane pins.

#### Pin Assignment

Refer to Section 2 of this manual.

#### Channel Loading

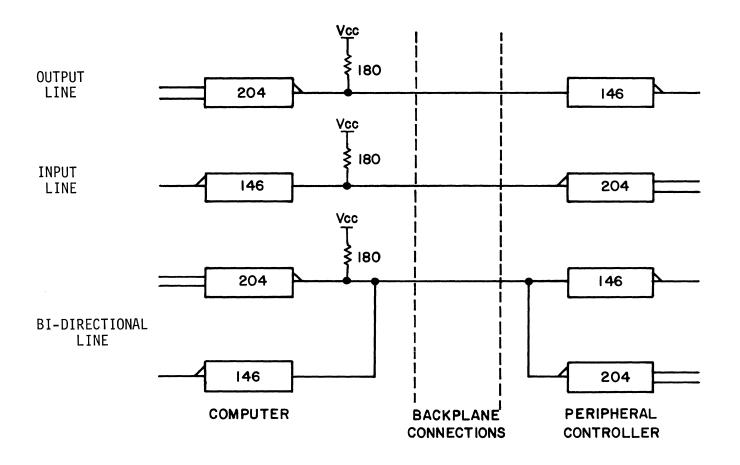

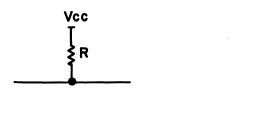

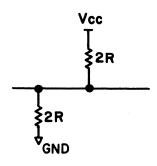

Each signal (data or control) transmitted from a peripheral controller to the CPU in the A/Q channel must be driven by an open-collector NAND buffer (IC Type 7438, CDC P/N 62031200 or equivalent). Each input line is terminated at the input to the CPU by a 180 ohm pull-up resistor (to  $V_{\rm CC}$ ). The input loads the line with 20 TTL loading units.

Each device on the A/Q channel is allowed to load any line from the CPU by one TTL load unit. The data bus (A register) is bi-directional. Figure 3-1 gives examples of typical input, output and bi-directional lines.

### Peripheral Equipment Connections

For connections between a peripheral equipment and its controller consult the relevant customer engineering manual.

NOTE: 146 can be replaced by any TTL logic circuit gate providing that the line is loaded by only one load unit.

Figure 3-1. A/Q Channel Input/Output Lines

|  | - |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

SECTION 4

THE A/Q CHANNEL

|  |   |  | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

|--|---|--|-----------------------------------------|

|  |   |  | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

|  |   |  | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1    |

|  |   |  |                                         |

|  |   |  |                                         |

|  |   |  |                                         |

|  |   |  |                                         |

|  |   |  |                                         |

|  | , |  |                                         |

#### THE A/Q CHANNEL

The A/Q channel provides non-buffered bi-directional access to the computer memory and controls the program interrupt system. It transfers data, a word at a time, through the A register using the Q register to hold the address of the peripheral system. The A and Q registers also initiate and monitor the DSA Channel operation. They perform a number of other internal, computer functions as well.

# INPUT, OUTPUT ON A/Q CHANNEL

A single 16-bit word is input to or output from the A register when an input or output command is executed by the computer. The data transfer is performed on an asynchronous bidirectional (hand-shaking) basis.

The computer initiates the instruction by generating a command signal as follows:

| Operation                              | Signal        |

|----------------------------------------|---------------|

| Input to computer Output from computer | READ<br>WRITE |

The address of the peripheral system selected for the current operation is always available in the equipment (E) field of the Q register. The peripheral controller whose equipment number corresponds to this address responds with a Reply or Reject signal to the command, provided the whole of the Q register content has the correct format (see Address Format below).

<u>Data is transferred</u> on the 16 line bi-directional A register bus when the peripheral controller responds with a <u>Reply</u> signal. The Reply is generated, provided -

- the peripheral system has been addressed correctly

- the peripheral system is in a state to accept the data on the A-register bus (output operation) or it has made the data available on the A-register bus (input operation

If the peripheral system addressed cannot accept data in input operation or has not made data available in output operation, it normally responds with a Reject signal within 4.0 microsecona of the command (Read or Write).

If the computer does not receive any response within 4.0 microseconds (AB107) it generates an Internal Reject signal which resets the correct instruction. The computer proceeds to the <u>next command</u> after execution of the current command. The address location of the next command, relative to the current command address (P) is given in the following table:

| Response                         | Location of<br>Next Command |

|----------------------------------|-----------------------------|

| Reply                            | P + 1                       |

| Reject                           | P + ] + A                   |

| No response<br>(Internal Reject) | P + Δ                       |

Here  $\Delta$  is the field consisting of the lowest 8 bits of the input command, the highest bit of  $\Delta$  being a sign bit. P is the contents of the P (Program) register.

#### CONTROL SIGNALS

The operation of the computer and its peripherals is coordinated by a number of control signals.

**READ**

Input command signal

The Read signal of the computer indicates a request for an input operation from the peripheral equipment addressed. If data is available at the peripheral, its controller returns a Reply within 4.0 microseconds in response to the Read signal. If no data is available, or the peripheral is otherwise not ready, a Reject signal should be returned from the peripheral controller within 4.0 microseconds.

WRITE

Output command signal

The Write signal of the computer indicates the request for an output operation from the computer to the peripheral equipment addressed. If the peripheral can use the data, its controller responds to the Write signal with a Reply within 4.0 microseconds. If the peripheral cannot use the data, its controller responds with a Reject signal within 4.0 microseconds.

<u>Note</u> that in some cases the peripheral addressed does not respond to a Read or Write signal within the specified microseconds. In this case an Internal Reject signal is generated within the computer to terminate the operation.

REPLY

Positive response from controller

In response to the computer Read or Write signal going active the peripheral controller addressed checks conditions within its own system. If it has data available for transmission on the A-register bus (input operation) or it can accept data from the A-bus (output operation), the controller stores the data in its own register and sends

89673100 01 4-3

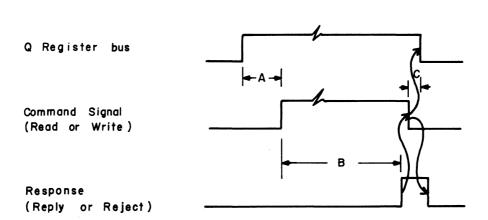

a Reply signal to the computer. This resets the Write signal to inactive which in turn resets the controller Reply and the A-register data lines. Figure 4-1 is the timing diagram of this sequence.

#### REJECT

Negative response from controller

If the peripheral system addressed cannot perform the computer command, it responds to the Read or Write signal with a Reject within 4.0 microseconds (see Figure 4-1).

# PROGRAM PROTECT

The Program Protect signal is present if the I/O instruction requires access to a protected equipment. If this signal is not present and the equipment addressed is protected, it returns a Reject signal for all access attempts excluding status requests. Conversely, an unprotected equipment will accept both protected and unprotected commands.

The protected status of an equipment is normally determined by the setting of a switch or jumper plug on its controller.

# CHARACTER INPUT

This signal is generated by the peripheral equipment if the data transfer is an 8-bit character or less in the low-order bit positions. Equipments which never exceed an 8-bit transfer may have this line active continuously during data transfer.

### Notes:

A: 100 nsec maximum B: 4  $\mu$ sec maximum C: 100 nsec maximum

Figure 4-1. Input-Output Timing Diagram

CONTINUE BIT

Bit 15 of the Q register is the Continue bit and can be used to speed up the operation of peripheral systems which require continuous random addressing. This mode operates as follows:

- The peripheral device is addressed with Q15 = 1 and the remainder of Q set to the desired address. This connects the peripheral.

- 2) All succeeding addresses with Q15 = 1 will be recognized by this device. Thus 15 bits of address are available to the selected peripheral for internal use.

- 3) The next address with Q15 = 0 will disconnect the peripheral unless the address of the peripheral is zero (field E all zeros).

#### ADDRESSING

The Q register of the 1784 computer is used to hold the address codes of the peripheral equipments being accessed. The format of the Q register content is shown below.

| _ | 15 11 | 10 07 | 06 00   | _          |

|---|-------|-------|---------|------------|

|   | W     | Е     | COMMAND | Q REGISTER |

CONVERTER

The W field (Q11 ÷ Q15) must be zero for all standard peripheral controllers.

WEZ

Only the zero state of the W field is of interest for the operation of peripheral equipments. The signal WEZ (W equals Zero) indicates this state on a single line allowing the lines Q11 ÷ Q15 not to be connected.

#### **EQUIPMENT**

Address bits Q07  $\div$  Q10 (field E) contain the equipment number of the peripheral system connected to the channel (0 through  $F_{16}$ ). The controller of the peripheral system responds when the setting of the Equipment Number and the code in field E match. The Equipment Number is normally set on the controller PWA by means of switches or jumper plugs.

## COMMAND CODE

Bits  $Q00 \div Q07$  are not preassigned and are therefore available to meet specific requirements of the station and unit. These bits control and direct information on the A/Q channel in the following ways:

- Specify the data transfer

- Direct the control functions and function level

- Direct the status and status level

- Address the line to specific stations under one equipment having multiplexing capabilities.

The Command code is divided into two sections: "S" contains the Station code and "D" contains the Director. The Station code is located in bit 06 and adjacent lower order bits as required. The Director is located in bit 00 and adjacent higher order bits as required. They cannot overlap; all bits in the Command code are not necessarily used.

| 15 | 11 | 10          | 07 | 06 |                       | 00 |            |

|----|----|-------------|----|----|-----------------------|----|------------|

| W  |    | !           | E  |    | $S \leftrightarrow D$ |    | Q REGISTER |

| L  |    | <del></del> |    |    | COMMAND               |    |            |

#### UNIT (CHANNEL)

Units (or channels) within a peripheral system are controlled by a higher-level controller in that system and respond only to that controller. A function code directs the controller to recognize the information on the A-register bus as the address of the desired unit.

#### I/O OPERATIONS

DIRECTOR

All input/output operations in the 1784 Computer System are initiated by the Read (Input to A) and Write (Output from A) commands. The 16 bits of register A and the associated bus contain the information of the channel. The meaning of this information during input and output operations is determined by the Director (bits 00 and upward of the Q register). Bit 00 of the Director determines whether the contents of A is data, a function code, or status. The use of the remainder of the Director bits (if any) is detailed in the reference information for each equipment.

TABLE 4-1. USE OF DIRECTOR

| DIRECTOR<br>BIT 00<br>ACTIVE | 1784 INSTRUCTION | PERIPHERAL OPERATION                      |

|------------------------------|------------------|-------------------------------------------|

| low                          | Output from A    | Write Data                                |

| low                          | Input to A       | Read Data                                 |

| high                         | Output from A    | Function code sent to peripheral          |

| high                         | Input to A       | Status of peripheral sent to the computer |

DATA TRANSFER

To transfer data, all bits of the Director must be low. A Read or a Write command specifies the direction of the data flow. If the peripheral system can receive data from or send data to the channel, it will respond with a Reply. If the peripheral system is unable to receive or send data, it will normally respond with a Reject. A read or Write signal will always be rejected during data transfers if the device is not Ready.

**FUNCTIONS**

Refer to Section 5 of 1784 Reference Manual,

publication number 89633400.

STATUS

Refer to Section 5 of 1784 Reference Manual, publication number 89633400.

A/Q CHANNEL

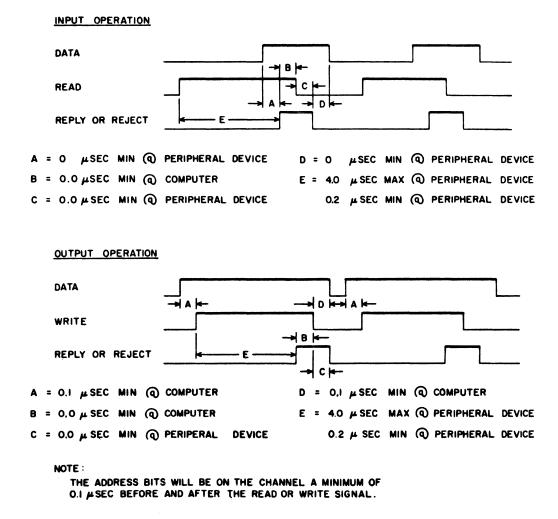

TIMING

Input and output signal timing restrictions are shown in Figure 4-2. In addition to the signals shown, a timing pulse is generated 135  $\mu sec$  (±40  $\mu sec$ ) before a Read or Write signal can appear on the A/Q channel. This timing pulse is active for 75  $\mu$ sec (±20  $\mu$ sec).

4-9 89673100 01

Figure 4-2. A/Q Input/Output Timing

#### A/Q CHANNEL ACCESS

Access to the A/Q channel is available on identical pin locations on the enclosure back plane. The pin locations correspond to prewired slots allocated for the A/Q channel (refer to Figure 1-2). Each slot accommodates the two 62-pin connectors of the 50-PAK printed wiring assembly. Table 4-2 lists pin assignments for the various signals.

TABLE 4-2. A/Q CHANNEL PIN ASSIGNMENTS

|                                                                  | P <sub>1</sub>                                                                                                                             | LL 4-2. A/Q 0                                                                                      | LE THE ASSIGNMENTS | P <sub>2</sub>                                                                                                                             |     |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| А                                                                |                                                                                                                                            | В                                                                                                  | А                  |                                                                                                                                            | В   |

| A05<br>A06<br>A00<br>A12<br>A11<br>A03<br>A04                    | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10                                                                                            | A01<br>A02<br>A07<br>A08<br>A09<br>A10<br>CMI                                                      | GND                | 1<br>2<br>3<br>4<br>5<br>6<br>7                                                                                                            |     |

| TP  A15 Q00 Q02 Q04 Q06 Q08 Q10 Q12 Q14 WEZ READ REPLY PRTM  GND | 8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31 | A13<br>A14<br>GND<br>Q01<br>Q03<br>Q05<br>Q07<br>Q09<br>Q11<br>Q13<br>Q15<br>WRITE<br>REJECT<br>MC | V <sub>cc</sub>    | 8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31 | GND |

Notes:

- 1) Q00 : Q15 active high; all other signals active low.

- 2)  $V_{CC} = +5V$ . Total usage of all A/Q and DSA controllers should not exceed 30 amps.

- 3) GND = logic ground.

4-11

## SIGNAL DEFINITIONS

TABLE 4-3. SIGNAL DEFINITIONS FOR A/Q CHANNEL

| SIGNAL/LINE     | DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A00 ÷ A15       | A 16-line bi-directional bus carrying data or status information between register A of the computer and all associated input/output (I/O) system controllers. It is termed the A-bus and is part of the A/Q channel of the computer. Each of the 16 lines of each I/O system is wire-ORed to the A-bus. The direction of flow of the information (to/from the computer) is determined by the input/output commands (READ, WRITE). The signals transmitted from the computer are active low on lines held normally by pull-up resistors within the computer The line drivers for signals transmitted to the computer on the peripheral controllers are open collector output gates. For typical connection refer to Figure 3-1. |

| Q00 ÷ Q15       | 16 lines from the computer which specify the address of the peripheral equipment for data transfer. The 9 highest order bits uniquely specify the device. The lower 7 bits can specify functions of lower level devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Converter (WEZ) | The W field of the Q register (bits Q11 : Q15) is zero during input/output operations. WEZ indicates this.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| READ            | Control signal from the computer to the peripheral equipment, initiates one input transfer operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| WRITE           | Control signal from the computer to the peripheral equipment, initiates one output transfer operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Continued on next page

### SIGNAL DEFINITIONS (Cont'd.)

TABLE 4-3. SIGNAL DEFINITIONS FOR A/Q CHANNEL (Cont'd.)

| SIGNAL/LINE               | DEFINITION                                                                                                                                                                                                                                                                                                                            |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REPLY                     | Positive response originating in the peripheral equipment or its controller in response to a signal on the Read or Write line. The Reply is reset when the Read or Write signal goes inactive.                                                                                                                                        |

| REJECT                    | Negative response originating in the peripheral equipment in response to Read or Write signal indicating that the operation cannot be performed. The Reject is reset when the Read or Write signal goes inactive.                                                                                                                     |

| Master Clear (MC)         | General reset signal sent by the computer. It clears the I/O channels and the peripheral system.                                                                                                                                                                                                                                      |

| Program Protect<br>(PRTM) | Signal transmitted by the computer. It indicates that the operation was initiated by an I/O instruction whose program protect bit is set. It permits buffered I/O devices to write via direct access to protected computer storage locations. When Programmer's Console Protect switch is not set, the Program Protect bit is active. |

| Character Input<br>(CHI)  | Signal transmitted to the computer during input operations. When this signal is present during an input to register A, the lower 8-bits of the word are loaded into the lower 8 bits of A without disturbing the upper 8 bits of A.                                                                                                   |

| Timing Pulse (TP)         | The Timing Pulse is a 75 nsec ( $\pm 20$ nsec) pulse. It occurs once during each storage cycle. It begins 135 nsec ( $\pm 40$ nsec) before a Read or Write signal can appear on the A/Q channel. This timing applies to the A/Q channel only.                                                                                         |

INTERRUPT SIGNALS Refer to Section 6.

## SECTION 5

DIRECT STORAGE ACCESS CHANNEL

#### DIRECT STORAGE ACCESS CHANNEL

The Direct Storage Access (DSA) Channel provides fast external access to the 1784 Computer memory. It transfers data direct between the memory and buffered controllers of bulk storage or other peripherals. The transfer takes place independently of the internal operations of the computer, though it is initiated and monitored by the A and Q registers. Peripherals working through the DSA channel may have priority over others by means of the interrupt system. This allows continuous, fast bulk data transfer.

#### INPUT, OUTPUT ON DSA CHANNEL

During a DSA input or output command a single 16-bit word is transferred between a buffered peripheral controller and the computer memory.

A peripheral controller on the DSA channel initiates the transfer cycle by means of the Request  $(\overline{SRQ})$  signal after obtaining use of the channel through the Scanner.

The direction of data transfer is determined by the Write Enable signal: in its presence (the signal active) data is transferred from the peripheral controller to the memory; in its absence data transfer is in the opposite direction.

The Scanner gives each peripheral controller connected to the DSA channel access to the channel on a first-come-first-served basis, and allows a number of peripherals to time-share the channel. The principles of the scanner operation are described later in this section.

89673100 01 5-1

INPUT, OUTPUT ON DSA CHANNEL (Cont'd.)

Priority access for the fast transfer of bulk data can be obtained by each peripheral controller on the DSA channel by means of the DSA PRIORITY interrupt signal. This signal, when active, ensures that the CPU does not access the memory and therefore gives the peripheral on the DSA channel uninterrupted access. In this case the data flow to or from the memory is interrupted only by the memory refresh cycles (refer to Memory System, 1784 Computer CE Manual, publication number 89633300).

<u>The address</u> of the memory location for data transfer must be available at the peripheral controller immediately after the access Request signal (refer to Figure 5-1, DSA Timing Diagram)

<u>Data is transferred</u> when the memory responds to the access Request (refer to Figure 5-1, DSA Timing Diagram).

<u>Error signals</u> (Parity Error, Protect Fault) available from the memory have to be checked in the peripheral controller and appropriate action taken.

#### CONTROL SIGNALS

The operation of the computer memory and the peripheral controller on the DSA channel accessing it is coordinated by a number of control signals. These are described below. Note that a peripheral controller on the DSA channel obtains access to the channel through the scanner which is described later in this section. The timing diagram of the control signals is given in Figure 5-1.

#### REQUEST (SRO)

The memory access Request signal is generated immediately after the peripheral controller obtained access to the DSA channel through the scanner. It indicates a request to transfer data to/from the memory location specified by the 16 address bits of the peripheral controller (ADOO ÷ AD15).

Write Enable (SWRITE)

The Write Enable signal of the peripheral controller specifies the direction of data transfer as shown in the following table:

| Write Enable | Operation | Data Transfer           |

|--------------|-----------|-------------------------|

| Active       | Write     | Memory to<br>Peripheral |

| Inactive     | Read      | Peripheral<br>to Memory |

Resume (SRSM)

The computer response to access request by the peripheral controller is the Resume signal. This signal resets the Request signal and the address bits of the peripheral controller and initiates data transfer. When the Resume signal becomes inactive, the memory parity error and protect fault lines should be checked and appropriate action taken in the peripheral controller.

Program Protect Protect Fault

The Program Protect signal corresponds to the memory word protect bit (bit 17: SD17). If an attempt is made to write into a protected memory location when an unprotected instruction was the ultimate source of this attempt, a protect violation occurs and the Protect Fault line  $(\overline{\text{SVFO}})$  is activated; it is available to the peripheral controller to stop data transfer or to take other appropriate action.

#### Storage Parity Parity Fault

A storage parity bit is entered as bit 16 (SD16) with every word written into memory. It is generated in the memory system. Storage parity is checked (and consequently a Parity fault may occur) in two cases:

- 1. when a word is read from memory;

- when a word is written into a memory location, and the word already in that location is read and its parity checked.

The Parity Fault line  $(\overline{PEL})$  is available to the peripheral controller to stop data transfer or to take other appropriate action.

#### ADDRESSING

The address of the memory location to be accessed (16 address bits SA00:SA15) must be available at the address bus terminals immediately after the access request signal becomes active. Note that the 16 bits can address any location within the full 64 kiloword memory.

#### I/O OPERATIONS

#### DATA TRANSFÉR

Data is transferred a word at a time during each memory access cycle. For data transfer from the memory to the peripheral the Write Enable (SWRITE) must be active high; the data (Data Out: SD00÷SD15), is active high. Data transfer from a peripheral to the memory takes place with the Write Enable signal inactive (low); the data (Data In: SD00÷SD15) is active low. Refer to Figure 5-1. If a DSA cycle is followed by another one within the maximum delay specified after the start of Resume (SRSM) (see Figure 5-1), and the CPU is waiting to reference the

#### I/O OPERATIONS

DATA TRANSFER (Cont'd.)

memory, then the second DSA request will be taken and the CPU forced to wait. This is because the memory system gives the DSA priority over the CPU. Thus the DSA can obtain continuous memory cycles and block CPU memory accesses by sending memory requests at a high enough rate. This does not apply in two bank operation because the CPU can access the upper bank while the DSA sends a request to the lower bank. If the DSA then tries to access the upper bank it has to wait until the CPU access ends.

Note that once a DSA memory cycle has been initiated, the CPU is free to continue the main program while the input/output operation is handled by the appropriate peripheral controller.

# DSA PRIORITY (SS)

Peripherals that require particularly fast access to computer memory may generate a Priority signal to block access from the CPU. Peripherals that require continuous memory access may halt the scanner for the duration of the access.

A peripheral controller on the DSA channel can thus unconditionally block all CPU memory accesses with this signal. This allows it to access both banks at maximum speed, although it has to wait for refresh cycles.

#### WARNING

Care should be taken in halting the scanner for more than one storage cycle as this may interfere with the operation of other non-buffered devices concurrently operating on the DSA channel.

89673100 01 5-5

### DSA CHANNEL TIMING

The timing of data and control signals is shown in Figure 5-1. Note that the timing is different for computers with different memory cycle times. The relationship between cycle times and equipments is given here:

| Computer | Memory<br>Cycle Time<br>(nanoseconds) |

|----------|---------------------------------------|

| 1784-1   | 900                                   |

| 1784-2   | 600                                   |

Note also that the transfer timing depends on DSA priority assignments and the need to interpose memory refresh cycles.

Refer to the notes to Figure 5-1 and to the explanation on operation with two memory banks at the end of this section.

5-6 89673100 01

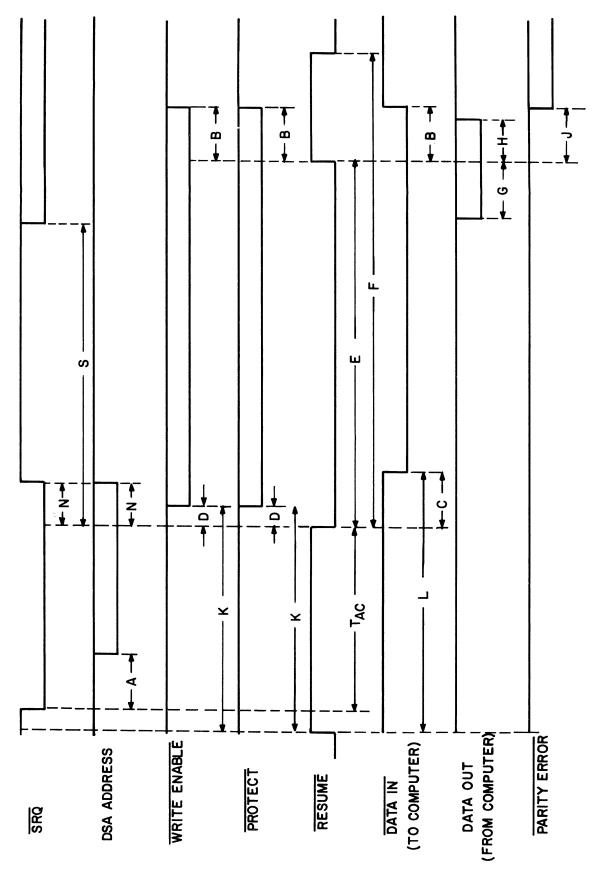

Figure 5-1. DSA Channel Timing

## NOTES (to Figure 5-1):

#### 1. Nomenclature:

TAC : DSA Access Time PEL : Parity Error

SRQ : Memory Access Request from DSA channel SA00:SA15 DSA Address

Data In SD00:SD15

SWRITE: Write enable Data Out : SD00:SD15

SPI : Protect

### 2. Timing

|                | 1                 | 784-1             |                          | 1 7               | 8 4 - 2           |                         | Remarks                                         |

|----------------|-------------------|-------------------|--------------------------|-------------------|-------------------|-------------------------|-------------------------------------------------|

|                | minimum<br>(nsec) | typical<br>(nsec) | maximum<br>(nsec)        | minimum<br>(nsec) | typical<br>(nsec) | maximum<br>(nsec)       |                                                 |

| A.<br>B.<br>C. | -<br>50<br>-      | -                 | 70<br>175<br>120<br>60   | -<br>50<br>-      | -                 | 110<br>200<br>245<br>60 |                                                 |

| E.<br>F.       | 390<br>-          | 440<br>600        | 490<br>-                 | 605               | 655<br>900        | 705<br>-                |                                                 |

| G.<br>H.       | 110<br>70         | <b>-</b>          | -                        | 190<br>120        | -<br>-            | -<br>-                  |                                                 |

| J.<br>K.       | 0                 | -<br>-            | 10<br>-                  | - 0               | -<br>-            | 10<br>-                 |                                                 |

| L.<br>N.       | 150<br>0          | -                 | 215                      | 210<br>0          | -                 | 320                     |                                                 |

| s.             | -                 | -                 | 285                      | <del>-</del>      | -                 | 470                     | at maximum<br>DSA access<br>rate                |

| TAC            | 220               | -                 | 800 <sub>.</sub><br>1400 | 330               | -                 | 1160<br>2060            | with DSA<br>Priority<br>without DSA<br>Priority |

#### NOTES (to Figure 5-1) (Cont'd.):

#### 3. Refresh cycle time:

490 nsec once every 32 microseconds (600 nsec Memory) 735 nsec once every 48 microseconds (900 nsec Memory)

#### 4. Modes of Operation

Worst Case

The maximum DSA access time  $(T_{AC})$  occurs when the memory system performs CPU access cycles and successive Refresh cycles.

DSA Priority signal active

The memory system cannot perform CPU cycles. The DSA access time  $(T_{AC})$  is minimum; it is increased by the regular occurrence of Refresh cycles.

#### Successive DSA requests

The memory system cannot perform CPU cycles on the memory bank addressed by the equipment on the DSA channel. The DSA cycle time is equal to the memory cycle time (600 nsec or 900 nsec). The DSA cycle time will be increased by the Refresh cycles. Note that on single-bank operation (32KW active) no CPU access can occur if the DSA requests are generated fast enough.

89673100 01 5-9

TIMING CONSIDERATIONS FOR TWO BANK OPERATION

The computer can have one or two memory banks (refer to 1784 Computer CE Manual, publication number 89633300), each with a maximum of 32 kilowords. The two banks work independently. Any memory request using an address of  $7FFF_{16}$  or less will access the lower bank. Any memory request using an address  $8000_{16}$  or above will access the upper bank.

If the CPU accesses one bank, the DSA can simultaneously access the other bank. In this case, the CPU and DSA can work at maximum speed subject to refresh cycle requirements.

If the CPU and DSA access the same bank, then memory cycles are shared between them. If the CPU requests a memory access while a DSA cycle is in progress, it must wait until the DSA cycle is finished. If a refresh cycle is pending when the DSA cycle ends, the CPU must also wait for that refresh cycle to be completed.

Similarly, if the DSA requests access while a CPU cycle is in progress, it must wait until the CPU cycle is finished. If a refresh cycle is pending when the CPU cycle ends, the DSA must also wait for that refresh cycle to be completed.

# DSA CHANNEL ACCESS

Access to the DSA channel is available on identical pin locations on the back plane of the main computer enclosure. The pin locations correspond to prewired slots allocated for the DSA channel (refer to Figure 1-2). Each slot accommodates a standard 50-PAK PWB - refer to Section 2.

Table 5-1 lists pin assignments for the various signals.

TABLE 5-1. DSA CHANNEL PIN ASSIGNMENTS

|                                                                                | P <sub>1</sub>                                                                                                                |                                                                                                       |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| А                                                                              |                                                                                                                               | В                                                                                                     |

| SD05 SD06 SD00 SD12 SD11 SD03 SD04  MC SD15  SRSM  SRQ  PEL SD16 SF1 SD17 32KW | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>22 | SD01 SD02 SD07 SD08 SD09 SD10  SD13 SD14 GND SS  SPI SRI SCRØM (SRØ) SVIO AUTOLOAD SCFØM (SFØ) SWRITE |

| SAO8<br>SAO9<br>SA10<br>SA11<br>SA12                                           | 22<br>23<br>24<br>25<br>26<br>27                                                                                              | SA00<br>SA01<br>SA02<br>SA03<br>SA04                                                                  |

| SA13<br>GND<br>SA14<br>SA15                                                    | 28<br>29<br>30<br>31                                                                                                          | SA05<br>SA06<br>SA07                                                                                  |

| P <sub>2</sub>         |                                                                                 |     |  |

|------------------------|---------------------------------------------------------------------------------|-----|--|

| Α                      |                                                                                 | В   |  |

| GND<br>V <sub>CC</sub> | 1 2 3 4 5 6 7 8 9 10 11 2 13 14 15 16 17 18 19 20 21 22 24 25 26 27 28 29 30 31 | GND |  |

#### NOTES:

- 1. Signal polarity

- Address bits (SA00:SA15) are active high.

Data bits (SD00:SD15) are active high for DSA transfers from the computer (Write).

Data bits (SD00:SD15) are active low for DSA transfers to the computer (Read).

All other signals on the DSA bus are as indicated (overlined: active low).

- Power Supply

$V_{CC} = +5V$ .

Total usage of all controllers on A/Q and DSA buses should not exceed 30 amperes.

3. GND = logic ground.

# SIGNAL DEFINITIONS

TABLE 5-2. SIGNAL DEFINITIONS FOR DIRECT STORAGE ACCESS (DSA) CHANNEL

| SIGNAL/LINE          | DEFINITION                                                                                                                                                                                                               |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data (SD00:SD15)     | A 16 line bidirectional bus which carries data as follows:                                                                                                                                                               |

| ,                    | <ol> <li>In a DSA Read operation, a 16-bit data word is<br/>written directly into the memory locations defined<br/>by the address bits of the peripheral controller<br/>(active high data).</li> </ol>                   |

|                      | 2. In a DSA Write operation, a 16-bit data word is transferred from a memory location to the appropriate register and then to the peripheral controller on the DSA channel (active low data).                            |

| Protect Bit (SD17)   | Signal line showing the state of the Program protect bit of the storage location currently being addressed.  It is active low when the storage location is protected.                                                    |

| Parity Bit (SD16)    | Signal line for the parity signal of the 18-bit memory word. It is active low when the total number of high signals on the 18 lines (16 data lines, protect bit and parity bit lines) is odd (odd parity).               |

| Parity Error (PEL)   | Signal transmitted from the computer. It is active low when the storage parity error flip-flop is set.                                                                                                                   |

| Protect Fault (SVIO) | Signal transmitted from the computer. It is active low when an unprotected peripheral equipment tries to write into a protected memory location via the DSA channel while the front panel Program Protect switch is set. |

# $\frac{\texttt{SIGNAL}}{\underline{\texttt{DEFINITIONS}}} \; (\texttt{Cont'd.})$

TABLE 5-2. SIGNAL DEFINITIONS FOR DIRECT STORAGE ACCESS (DSA) CHANNEL (cont'd)

| SIGNAL/LINE           | DEFINITION                                                                                                                                                                                                                                                                                                                      |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address (SA00÷SA15)   | A 16 line bus which transmits the address of the storage location to be accessed from the peripheral controller. When the storage cycle starts, the address is placed in the appropriate computer register.                                                                                                                     |

| Request (SRQ)         | Signal transmitted to the computer requesting access to storage. The signal becomes inactive after the computer responds by the Resume signal.                                                                                                                                                                                  |

| Resume (SRSM)         | Computer response to Request. Starts DSA data transfer, resets Request signal and address bits, indicates timing for checking Parity Error and Protect Fault lines.                                                                                                                                                             |

| Write Enable (SWRITE) | Control signal in peripheral controller for directing data transfer. When the signal is active low, data is transferred from the computer memory location addressed to the peripheral controller (Write cycle). When it is active high, data is transferred from the peripheral controller to the memory location (Read cycle). |

| Protect (SPI)         | Signal transmitted to the computer. When active low it allows data from a peripheral system to be written into a protected storage location.                                                                                                                                                                                    |

| Master Clear (MC)     | General reset signal transmitted from the computer. When active low it clears the peripheral system.                                                                                                                                                                                                                            |

89673100 01 5-13

# SIGNAL DEFINITIONS (Cont'd.)

TABLE 5-2. SIGNAL DEFINITIONS FOR DIRECT STORAGE ACCESS (DSA) CHANNEL (cont'd).

| SIGNAL/LINE                                                                               | DEFINITION                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Priority (SS)                                                                             | DSA priority signal transmitted to the computer. When active low, it prevents the CPU from accessing the memory. This increases the DSA data transfer rate because data transfer from a peripheral equipment on the DSA channel will not be interrupted by the CPU. Note that the data flow is interrupted by refresh cycles even if the DSA priority is set. |

| AUTOLOAD                                                                                  | Active low signal transmitted from the computer when the AUTOLOAD pushbutton on the Programmer's Console is pressed.                                                                                                                                                                                                                                          |

| Scan Forward In (SFI) Scan Referse In (SRI) Scan Forward Out (SFØ) Scan Reverse Out (SRØ) | Four lines connecting the peripheral controller with the distributed scanner (see Scanner Connections).                                                                                                                                                                                                                                                       |

| 32KW                                                                                      | Signal transmitted from the computer. It is active low when the computer is set to operate with two memory banks (65 Kilowords) by the 32K/65K mode switch on the Programmer's Console. It is active high for one memory bank operation (32K).                                                                                                                |

|                                                                                           |                                                                                                                                                                                                                                                                                                                                                               |

5-14

# DISTRIBUTED SCANNER

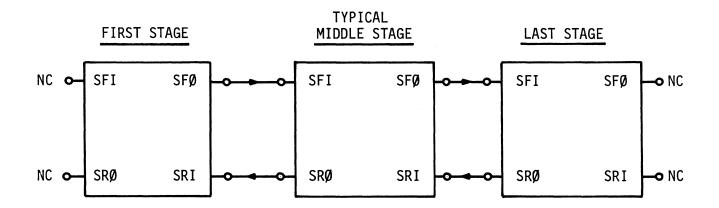

To give each peripheral controller connected on the DSA channel access to it, each controller must carry a flip-flop and control circuit as part of its logic circuit. The flip-flops, one on each controller, are connected as a ring-counter-oscillator forming the distributed scanner. This scans the indicating lines from the controllers requesting channel access (NEED); a controller requests access to the channel by halting the scanner. The various scanner stages (one in each device) are connected through the enclosure back plane wiring. This connection has to be done at the time of system installation. The following paragraphs will aid in understanding the setting up of the distributed scanner.

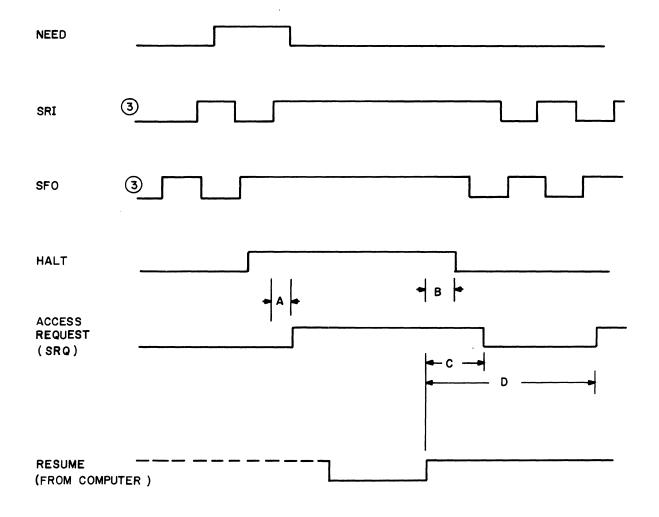

#### SCANNER OPERATION

When a peripheral equipment controller connected to the DSA requires access to computer storage, it generates the Need signal. This causes the scanner to halt at the stage in this controller; at the same time the Request  $(\overline{SRQ})$  signal is activated to obtain memory access for the controller. Typical timing is shown in Figure 5-3

#### SCANNER CONNECTIONS

Any scanner stage flip-flop transmits an active high signal when set and a low signal when cleared. A stage receiving an active high signal will set, while a stage receiving an active low will attempt to reset. The stages must be connected to form an oscillating ring by appropriate signal reversals in the chain and by connecting the output of the last stage to the input of the first one.

89673100 01 5-15

The position of the controller in the scanner chain depends on the particular system. Three positions can be distinguished, each having a specific polarity, as follows:

| CONTROLLER | SIGNAL POLARITY |             |  |

|------------|-----------------|-------------|--|

| POSITION   | RECEIVED        | TRANSMITTED |  |

| First      | High            | Low         |  |

|            | Low             | High        |  |

| Middle     | Hi gh           | High        |  |

|            | Low             | Low         |  |

| Last       | High            | High        |  |

|            | Low             | Low         |  |

|            |                 |             |  |

To aid in the connection, inputs and outputs for forward and reverse scan are distinguished on each scanner stage, as follows:

|              | Input                 | Output                 |

|--------------|-----------------------|------------------------|

| Forward scan | Scan Forward In (SFI) | Scan Forward Out (SFØ) |

| Reverse scan | Scan Reverse In (SRI) | Scan Reverse Out (SRØ) |

Figure 5-2 illustrates the connection of three stages in an oscillating ring. Note that there may be several middle stages.

#### Notes:

- 1. NC: Terminal not connected

- 2. All connections are on the enclosure backplane. In interconnection diagrams the following changes in nomenclature may occur:

SCFØM for SFØ, SCRØM for SRØ.

Figure 5-2. Scanner Wiring Connections

89673100 01

## SPECIAL CONNECTIONS

When only two peripheral controllers are connected to the DSA channel, the first and last stages will be connected directly as follows:

| First St | age_ | <u>Last Stage</u> |

|----------|------|-------------------|

| SFØ      |      | SFI               |

| SRI      | 4    | SRØ               |

2. When only one peripheral controller is connected to the DSA channel, it will be connected to be self-oscillating as follows:

Single Stage