# CONTROL DATA<sup>®</sup> LINE PRINTER CONTROLLER FF524-A

GENERAL DESCRIPTION OPERATION AND PROGRAMMING INSTALLATION AND CHECKOUT THEORY OF OPERATION DIAGRAMS MAINTENANCE PARTS DATA WIRE LIST

HARDWARE MAINTENANCE MANUAL

|                 | REVISION RECORD                                                                                   |  |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| REVISION        | DESCRIPTION                                                                                       |  |  |  |  |  |  |

| 01              | Released Class B. ECO CK387.                                                                      |  |  |  |  |  |  |

| (12/73)         |                                                                                                   |  |  |  |  |  |  |

| 02              | Revised. ECO CK524. Publications change only.                                                     |  |  |  |  |  |  |

| (5/74)          |                                                                                                   |  |  |  |  |  |  |

| 03              | Revised. ECO CK937. Publications change only.                                                     |  |  |  |  |  |  |

| (9/74)          |                                                                                                   |  |  |  |  |  |  |

| .04             | Revised. ECO CK1046. Publications change only.                                                    |  |  |  |  |  |  |

| (11/74)         |                                                                                                   |  |  |  |  |  |  |

| A               | Released. ECO CK1229. Publications change only.                                                   |  |  |  |  |  |  |

| (6/75)          |                                                                                                   |  |  |  |  |  |  |

| B               | ECO CK1445.Revised pages: iii, vii, viii, 2-3, 3-1, 3-3, 5-13, 5-15, 5-19, 7-1, 8-2 thru 8-9, 2-7 |  |  |  |  |  |  |

| (9/76)          |                                                                                                   |  |  |  |  |  |  |

|                 | -                                                                                                 |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 | ·                                                                                                 |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 | •                                                                                                 |  |  |  |  |  |  |

| ł               |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

| ~               |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

|                 |                                                                                                   |  |  |  |  |  |  |

| Publication No. |                                                                                                   |  |  |  |  |  |  |

| 89637300        |                                                                                                   |  |  |  |  |  |  |

Address comments concerning this manual to: Control Data Corporation Publications & Graphics Div. 4455 Eastgate Mall La Jolla, California 92037

or use Comment Sheet in the back of this manual.

• 1974, 1975, 1976 by Control Data Corporation Printed in the United States of America

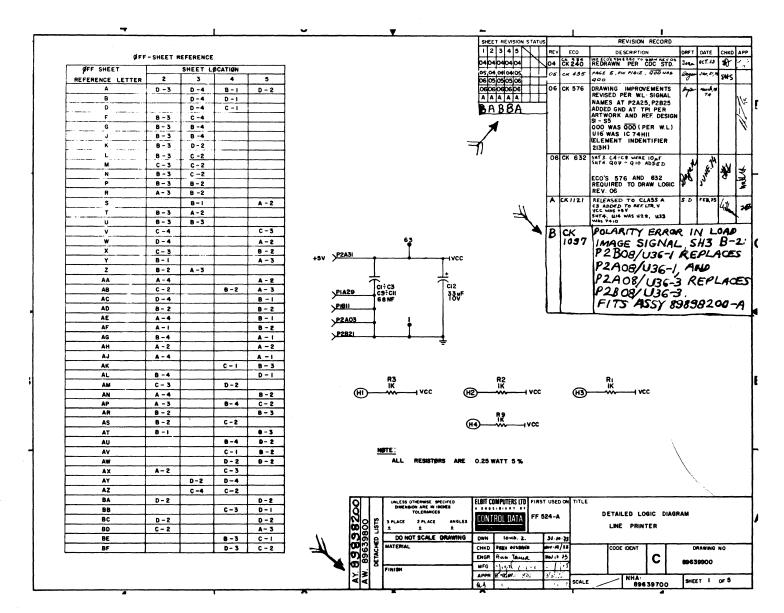

| SHEET 1       | OF <u>1</u> |                   | EQ                   | UIPME                        | NTS |   |  |

|---------------|-------------|-------------------|----------------------|------------------------------|-----|---|--|

| MANUAL<br>REV | FCO OR ECO  | SERIES<br>FF524-A | S/N                  | LOGIC<br>DIAGRAM<br>89639900 |     |   |  |

|               |             | 01                | 01                   | 02                           |     |   |  |

| 01            | ECO CK085   | 02                | 51, 103<br>104 & 110 | 04                           |     |   |  |

| 02            | ECO CK485   | 03                | 101                  | 06                           |     |   |  |

| 03            | ECO CK937   | 03                | -                    | -                            |     |   |  |

| 04            | ECO CK1046  | 03                | -                    | -                            |     | u |  |

| A             | EC0 CK1229  | 03                | -                    | A                            |     |   |  |

| В             | ECO CK1097  | 04                | 401                  | В                            |     |   |  |

| В             | ECO CK1311  | 05                | 501                  | В                            |     |   |  |

| В             | ECO CK1502  | 06                | 537                  | В                            |     |   |  |

|               |             |                   |                      |                              |     |   |  |

# MANUAL TO EQUIPMENT LEVEL CORRELATION SHEET

\*,

# PREFACE

This manual supplies reference information for the CONTROL DATA® FF524-A Line Printer Controller. This equipment is used with the AB107-A/AB108-A Computer to control the CL408-A/B or CL409-A/B Line Printers. A knowledge of the computer and line printer is required before using this line printer controller.

The following Control Data publications may be useful as references:

1

| Title                                                   | Publication No. |

|---------------------------------------------------------|-----------------|

| 1742 Line Printer Controller Reference<br>Manual        | 89637200        |

| 1784 Computer Reference Manual                          | 89633400        |

| AB107-A/AB108-A Computer Customer<br>Engineering Manual |                 |

| I/O Specification Manual                                | 89673100        |

×.

# CONTENTS

6

7

8

### PREFACE

| 1 | GENERAL DESCRIPTION                       |     |

|---|-------------------------------------------|-----|

|   | Introduction                              | 1-1 |

|   | Interface Connectors and Cables           | 1-1 |

|   | Data Transfer                             | 1-1 |

|   |                                           |     |

| 2 | PROGRAMMING AND OPERATION                 |     |

|   | Programming                               | 2-1 |

|   | Codes                                     | 2-3 |

|   | Converter                                 | 2-3 |

|   | Equipment                                 | 2-3 |

|   | Command                                   | 2-3 |

|   | Director Status                           | 2-5 |

|   | Control Characters                        | 2-8 |

| 3 | INSTALLATION AND CHECKOUT                 |     |

|   | Installation                              | 3-1 |

|   | Unpacking                                 | 3-1 |

|   | Physical Limitations                      | 3-1 |

|   | Power Requirements                        | 3-1 |

|   | Cabling and Connectors                    | 3-1 |

|   | <b>Cooling Requirements</b>               | 3-2 |

|   | <b>Environmental Considerations</b>       | 3-2 |

|   | Preparation and Installation              | 3-2 |

|   | Checkout                                  | 3-7 |

| 4 | THEORY OF OPERATION                       |     |

|   | General                                   | 4-1 |

|   | A/Q Receivers/Transmitters                | 4-2 |

|   | Protection Logic                          | 4-2 |

|   | Equipment and Operation Decoder           | 4-2 |

|   | Data Transfer                             | 4-3 |

|   | Director Function                         | 4-3 |

|   | Interrupt Logic                           | 4-5 |

|   | <b>Clock Generator and Timing Counter</b> | 4-5 |

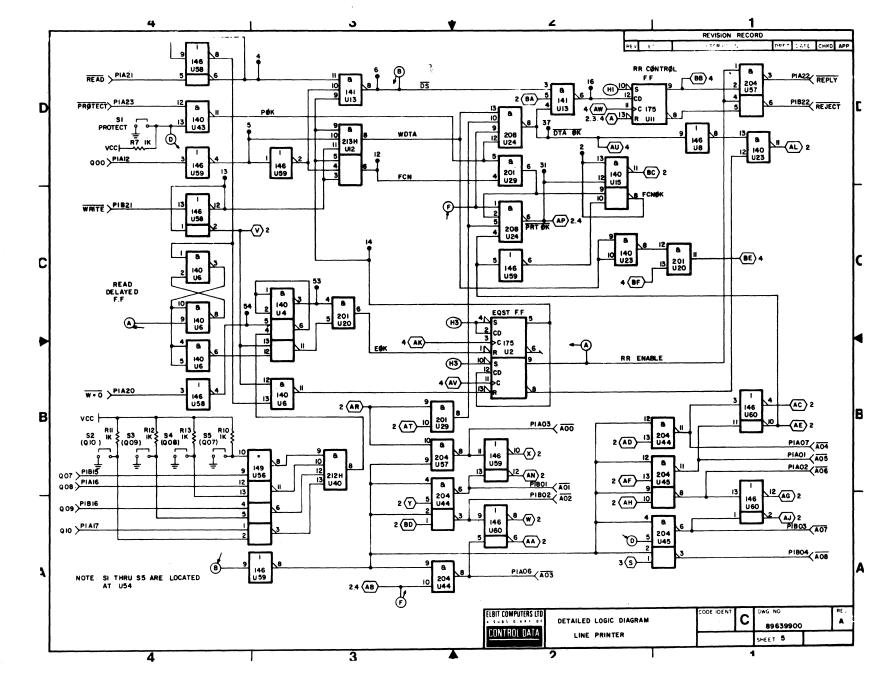

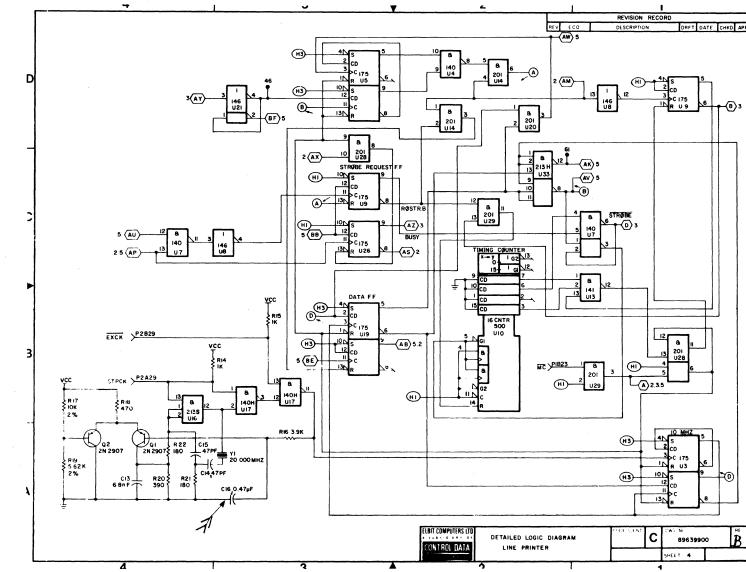

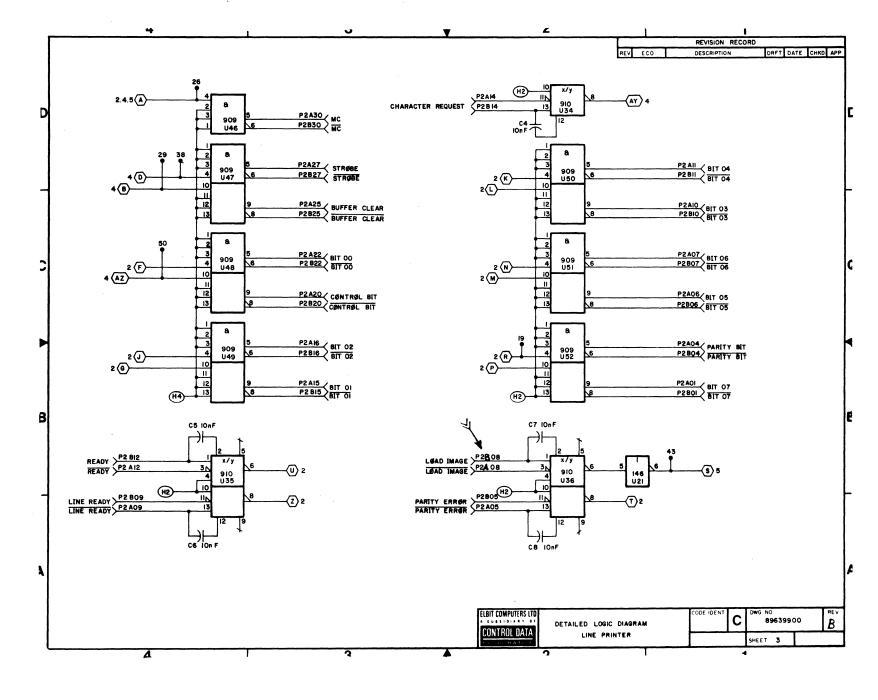

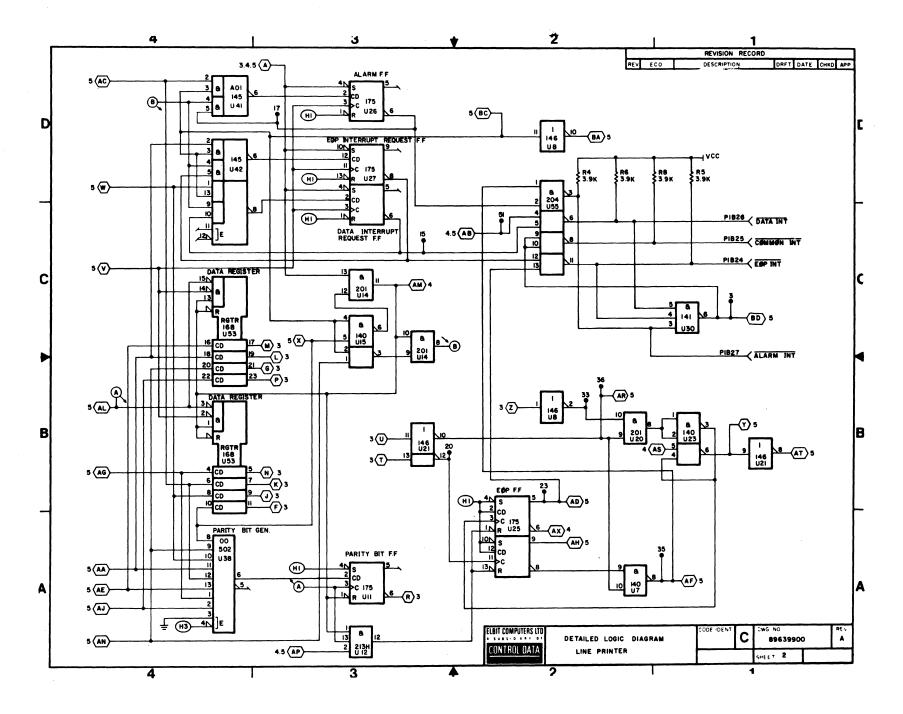

## 5 DIAGRAMS

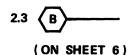

| Key to Logic Symbols               | 5-1  |

|------------------------------------|------|

| Signal Flow                        | 5-1  |

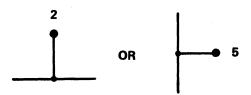

| Test Points                        | 5-2  |

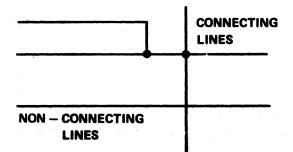

| Connecting and Non-Connectir       | ıg   |

| Lines                              | 5-2  |

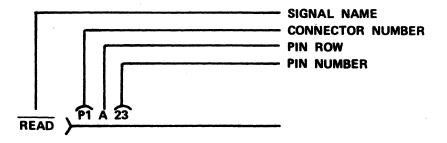

| Connectors                         | 5-6  |

| Equipment and Operation Decoder    | 5-7  |

| Equipment Number Decoder           | 5-7  |

| Protect Logic                      | 5-7  |

| Write Operation                    | 5-7  |

| Write Data                         | 5-8  |

| Director Function                  | 5-8  |

| Read Operation                     | 5-8  |

| Reply/Reject Logic                 | 5-8  |

| Data Register and Parity Generator | `,   |

| Interrupt Logic                    | 5-10 |

| Interrupt Logic                    | 5-10 |

| Control Logic and Timing           |      |

| Generator                          | 5-10 |

| Control Logic                      | 5-10 |

| Timing Generator                   | 5-12 |

| Differential Transmitters/         |      |

| Receivers                          | 5-12 |

| MAINTENANCE                        |      |

| Tools and Special Equipment        | 6-1  |

| Maintenance                        | 6-1  |

| PARTS DATA                         |      |

| WIRE LIST                          |      |

# FIGURES

| 2-1 | Q-Register Format           | 2-1 | 3-2 | Location For Installation of     |     |

|-----|-----------------------------|-----|-----|----------------------------------|-----|

| 2-2 | Function Code Format        | 2-2 |     | Controller PW Assembly (A/Q Bus) | 3-5 |

| 2-3 | Status Code Format          | 2-2 | 4-1 | Line Printer Controller Block    |     |

| 2-4 | Data Transfer Format        | 2-2 |     | Diagram                          | 4-2 |

| 2-5 | Jumper Plug Selection       | 2-3 | 4-2 | A/Q Timing Read/Write            | 4-4 |

| 3-1 | Jumper Plug Location on PWB | 3-4 | 4-3 | Print Operation Timing           | 4-6 |

|     |                             |     | 4-4 | Data Transfer                    | 4-8 |

# TABLES

| 1-1 | Specifications             | 1-2 | 3-3 | Interrupt Pin Assignments         | 3-6 |

|-----|----------------------------|-----|-----|-----------------------------------|-----|

| 2-1 | Addressing Codes           | 2-1 | 4-1 | Read/Write Functions              | 4-2 |

| 2-2 | LP Controller Bit          |     | 4-2 | Director Functions                | 4-4 |

|     | Settings in Register A     | 2-8 | 8-1 | External Shielded Cable Wire List | 8-2 |

| 3-1 | Jumper Plug Selection      | 3-3 | 8-2 | Internal Cable Wire List          | 8-5 |

| 3-2 | Equipment Number Selection | 3-3 | 8-3 | PWB Pin List                      | 8-8 |

# GENERAL DESCRIPTION

### INTRODUCTION

This section contains the functional and operational description of the CONTROL DATA® FF524-A Line Printer Controller.

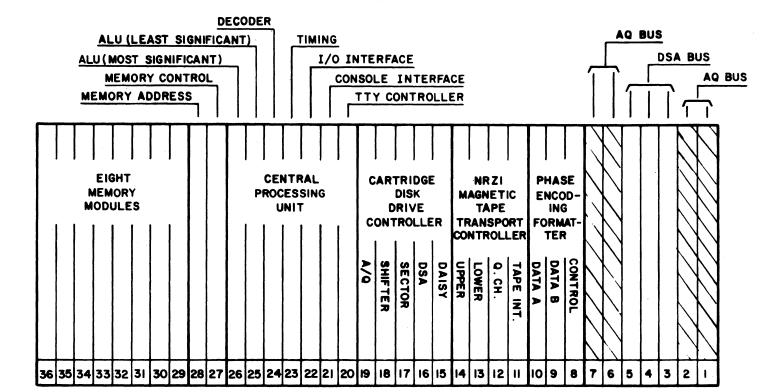

The line printer controller logic circuitry is mounted on a single 50-PAK board. The line printer controller interfaces with the A/Q channel of the AB107-A or AB108-A to control line printer operations. Refer to the 1742 Reference Manual for controller placement in CPU. Each controller will handle one of the CONTROL DATA® CL408-A/B or CL409-A/B Line Printers. It contains the logic that interprets AB107-A/AB108-A function codes, controls line printer operations, transfers data to the line printer, and provides line printer status information to the CPU. The line printer controller may be accommodated in any unused A/Q slot within the AB107-A/AB108-A enclosure or the BT148-A Expansion Enclosure. Table 1-1 supplies a list of specifications for the controller.

### INTERFACE CONNECTORS AND CABLES

The cables required for the operation of the controller and the line printer are listed in Section 7, Parts Data.

### DATA TRANSFER

To perform data transfer, bit Q00 of the Q register shall be zero (Q00 = 0) and an Output-from-A instruction executed. Bits A00 through A07 of the A register shall contain the character bits to be transmitted, with leading zeros. The first character of a line is identified as the control character and will not be printed. (See Page 2-8 for description)

The Data Transfer command is rejected if one of the following conditions occurs:

- 1. Printer is not Ready.

- 2. Printer is Busy.

- 3. Data Status is false.

- 4. Protect Violation.

Data Transfer command clears EOP and ERROR status.

1

| SPECIFICATIONS           | EXPLANATION                                        |

|--------------------------|----------------------------------------------------|

| PHYSICAL CHARACTERISTICS |                                                    |

| Dimensions               |                                                    |

| Width                    | 6-13/16 inches                                     |

| Length                   | 12-3/8 inches                                      |

| Depth                    | 3/8 inches                                         |

| ENVIRONMENT              |                                                    |

| Temperature              |                                                    |

| Shipping                 | -40° F to 158° F (-40° C to 70° C)                 |

| Storage                  | 14° F to 122° F (10° C to 50° C)                   |

| Operating                | 40°F to 120°F (5°C to 50°C)                        |

| Humidity                 |                                                    |

| Shipping                 | 0 to 100% RH non-condensing                        |

| Storage                  | 10% to 90% RH non-condensing                       |

| Operating                | 10% to 90% RH non-condensing                       |

| POWER                    |                                                    |

| Input Requirements       | 5 volts de                                         |

| Signal Level             |                                                    |

| Low State (0)            | 0.4 volts dc, or less                              |

| High State (1)           | 2.4 volts dc, or more                              |

| Ground                   | Logic ground is connected to computer logic ground |

Table 1-1. Specifications

# PROGRAMMING AND OPERATION

This section describes the programming for the FF524-A Line Printer Controller. Preparation for operation and operation are described in Section 3.

### PROGRAMMING

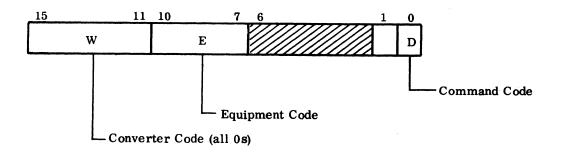

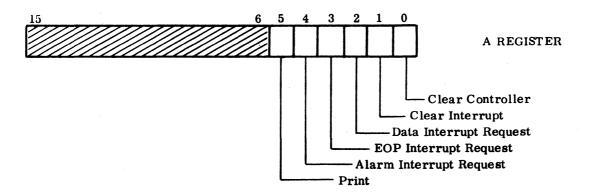

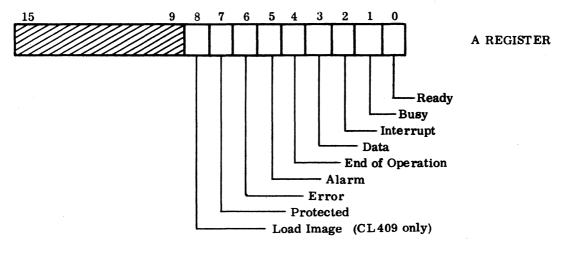

Table 2-1 and Figures 2-1 through 2-4 provide programming information. A description of the codes follows the figures.

| COMMAND CODE | INPUT-TO-A      | OUT PUT - FROM-A  |

|--------------|-----------------|-------------------|

| Q00 = 0      | lllegal         | Data transfer     |

| Q00 = 1      | Director Status | Director Function |

Table 2-1. Addressing Codes

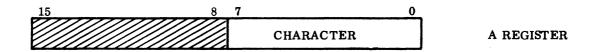

Figure 2-1. Q Register Format

Figure 2-3. Status Code Format

Figure 2-4. Data Transfer Format

## CODES

Equipment codes and Command codes are described in the following.

#### CONVERTER

The W portion of the Q register (Q11 through Q15) must be all zeros for all line printer operations.

### EQUIPMENT

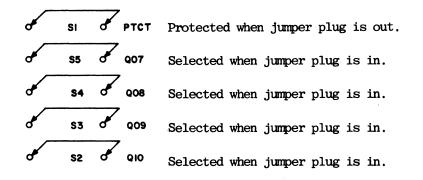

The E portion of the Q register (Q07 through Q10) defines the line printer equipment code. This code should match the setup of the four Equipment Select jumper plugs shown in Figure 2-5.

#### COMMAND

The Command code (bit 00 of the Q register) defines the operation to be performed by the line printer. It must be accompanied by an Equipment code and either a Read or a Write signal. Table 2-1 gives the Command code functions.

Figure 2-5. Jumper Plug Selection

#### DATA TRANSFER (Q00 = 0)

When bit Q00 is zero and an Output-from-A instruction is executed, the controller is directed to perform a data transfer. Data will be accepted unless one or more of the following reject conditions is present: the line printer is Not Ready, the line printer is Busy with a Print operation, data status is false, or a protect violation exists.

Bits 00 through 07 of the A register contain the character bits to be transmitted with leading zeros (A08 through A15 are zero). The first character of a line is identified as the control character and is not printed. (See Page 2-8 for description of control characters)

When six-bit characters are transmitted, bits 06, 07 of A should be zeros.

The Data Transfer command clears EOP and ERROR status.

#### DIRECTOR FUNCTIONS (Q00 = 1)

When Q00 is a 1 and it is accompanied by both an Equipment code and Output-from-A instruction, the controller is directed to perform a director function. Director functions are accepted if no protect violation occurs, with the following constraints: Print directive is accepted if controller is Ready, Not Busy, and Data Status is true (bit A03 = 1).

Director functions, except the Print directive, may be stacked; that is, two or more functions may be issued at the same time.

#### CLEAR PRINTER (A00 = 1)

This function clears the controller logic, clears EOP status, and generates the Buffer Clear signal to the line printer. It generates Clear Interrupt functions. It is subordinate to all other bits in this group except Print (A05).

#### CLEAR INTERRUPT (A01 = 1)

This function clears all interrupt requests and interrupt responses. It is subordinate to all interrupt requests.

#### DATA INTERRUPT REQUEST (A02 = 1)

This function sets the Data Interrupt Request flag. This in turn enables the generation of an interrupt when the Data status flag is true indicating that data transfer to the line printer is permitted. The interrupt request is cleared by Clear Printer or Clear Interrupt.

The interrupt response may be cleared by clearing the interrupt request as stated above, or by Data Transfer or Print functions. Before Data Transfer to the printer, Data Interrupt may be requested and the response will signal the computer that the printer is ready to receive another data transfer. Without reselecting or clearing this interrupt response, the data transfer can take place. During this data transfer, interrupt response will be removed until the printer is ready to receive another data transfer.

#### END-OF-OPERATION INTERRUPT REQUEST (EOP) (A03 = 1)

This function enables the generation of an interrupt on completion of an operation, when EOP occurs. The interrupt may be selected before or during the operation. An interrupt response will not occur for an operation which was ended before the selection was made. The interrupt request may be cleared by Clear Controller or Clear Interrupt.

The interrupt response may be cleared by clearing the request or by Data Transfer or Print functions.

#### A LARM INTERRUPT REQUEST (A04 = 1)

This function enables the generation of an interrupt when an alarm condition exists. An alarm condition that exists at the time this interrupt request is made will immediately provide a response. If the alarm condition does not exist at the time of the interrupt request, the interrupt response will be provided as soon as an alarm condition is detected. These conditions are listed in the Alarm section. The interrupt request may be cleared by Master Clear or by either A00 = 1 or A01 = 1 with A04 = 0.

The interrupt response may be cleared by clearing the request or by Data Transfer or Print functions.

#### PRINT FUNCTION (A05 = 1)

۴%;

This function directs the line printer to initiate a print operation. A print operation lasts between the acceptance of a Print function and completion of a line of print.

A register bits 06 through 15 in this group are not used.

#### DIRECTOR STATUS

The line printer always replies to a status request. It therefore replies when Q00 = 1 and it is accompanied by an equipment code and a Read signal. The status responses are described below.

#### READY (A00 1)

Indicates that a Ready condition exists. The Ready condition must be existing before the printer can operate, and the absence of any one of several requirements can prevent this.

#### BUSY (A01 = 1)

Indicates that the line printer is Busy. The line printer becomes Busy:

- 1. After the initiation of a print cycle and until the characters have been printed.

- 2. If the Clear Printer (A00 = 1) directive was issued directly after the control character has been issued.

#### INTERRUPT (A02 = 1)

This signal indicates that an interrupt occurred. The other status bits must be monitored to determine the cause of the interrupt: bits A03 through A05 define which interrupt occurred. This status is cleared by either the Clear Printer (A00 = 1) or Clear Interrupt (A01 = 1).

#### DATA (A03 = 1)

This signal indicates that the line printer is ready to receive a character. If Interrupt on Data has been selected, this status will also indicate that this interrupt has occurred. The status is cleared by Clear Printer (A00 = 1) and by either Data Transfer or Print directive.

#### END-OF-OPERATION (EOP) (A04 = 1)

This signal indicates that the line printer has completed an operation. If Interrupt on End-of-Operation has been selected, this status bit will also indicate that this interrupt has occurred. This status is true whenever the Line Ready signal goes high. The status is cleared by Clear Printer, Data Transfer, Print.

#### ALARM (A05 = 1)

This signal indicates that an alarm condition is present, that is, an error or printer malfunction occurred. The status is cleared by Clear Printer (A00 = 1), Data Transfer or Print directive provided that the cause of the alarm has been corrected.

#### ERROR (A06 = 1)

- a. For the CL408 Line Printer this signal indicates that data transfer parity error occurred. The parity error occurs when an incorrect character code is received by the line printer. The incorrect character code is printed as blank if it is a data character and ignored if a control character, i.e., it is performed as if Suppress Space was issued. The line printer stays Ready when this condition occurs. The status is cleared by Clear Printer (A00 = 1) or either Data Transfer or Print directive.

- b. For the CL409 Line Printer this signal indicates that any one or any combination of Parity Error, Synchronization Error or Compare Error (indicated on the Printer console) occurred. In case of Parity Error the Line Printer stays Ready. The condition is cleared by Clear Printer (A00 = 1) or either Data Transfer or Print directive.

In case of Synchronization Error or Compare Error the line printer becomes Busy. The condition is cleared by Clear Printer (A00 = 1) only.

#### **PROTECTED** (A07 = 1)

This bit indicates that the controller is in the protect state; that is, the protect jumper plug is absent. See Protection Logic, page 4-3. In this state, the controller accepts only instructions having a 1 on the Program Protect line. All other instructions except Director Status will be rejected. The Program Protect bit is ignored when the controller is not in the Protect state.

#### LOAD IMAGE (A08 = 1)

In the CL409 Line Printer this bit indicates that the next 288 characters will be transferred to the Line Printer Image Memory. If Parity Error occurs no further transmission takes place until Clear Printer (A00 = 1) is issued. Load Image status is not applicable to the CL408.

Bits A09 through A15 are not used.

#### CONTROL CHARACTERS

The first data character after a print operation is defined as the Control Character. It controls the paper vertical motion and will not be printed.

The printer operates in 'pre-print' mode, i.e. paper motion is performed before printing. The printer executes the Control Character immediately upon reception and does not set Busy Status. The Busy Status will be set after reception of a Print Directive.

NOTE: If a Control Character is issued, which performs a vertical paper motion and CLRP Directive is issued immediately thereafter, the Busy Status will be set until paper motion stops.

|      | Bi                                                       | ts in A                                                |                                                                                                                                                                                                                                           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|----------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A 05 | A04                                                      | A03                                                    | A02                                                                                                                                                                                                                                       | A01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| x    | x                                                        | x                                                      | x                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Suppress space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| x    | x                                                        | x                                                      | х                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Single space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| x    | x                                                        | x                                                      | x                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Double space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| x    | x                                                        | x                                                      | x                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Triple space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                          |                                                        |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Vertical Format Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| x    | x                                                        | 0                                                      | 0                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Channel 1 (TOF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| x    | x                                                        | 0                                                      | 0                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Channel 2 (B0F)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| x    | x                                                        | 0                                                      | 0                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Channel 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |                                                          |                                                        |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |                                                          |                                                        |                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| x    | x                                                        | 1                                                      | 0                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Channel 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| x    | x                                                        | 1                                                      | 1                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| x    | x                                                        | 1                                                      | 1                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Illegal as vertical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| x    | x                                                        | 1                                                      | 1                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| x    | x                                                        | 1                                                      | 1                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x | A05A04xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx | x     x     x       x     x     x       x     x     x       x     x     x       x     x     0       x     x     0       x     x     0       x     x     0       x     x     1       x     x     1       x     x     1       x     x     1 | A05       A04       A03       A02         x       x       x       x       x         x       x       x       x       x         x       x       x       x       x         x       x       x       x       x         x       x       x       x       x         x       x       0       0       0         x       x       0       0       0         x       x       1       0       0         x       x       1       1       1         x       x       1       1       1         x       x       1       1       1 | A05       A04       A03       A02       A01         x       x       x       x       0         x       x       x       x       0         x       x       x       x       0         x       x       x       x       1         x       x       x       x       1         x       x       0       0       0         x       x       0       0       0         x       x       0       0       1         x       x       1       0       1         x       x       1       0       1         x       x       1       1       0         x       x       1       1       1 | A05       A04       A03       A02       A01       A00         x       x       x       x       x       0       0         x       x       x       x       x       0       1         x       x       x       x       1       0         x       x       x       x       1       0         x       x       x       x       1       1         x       x       0       0       0       0         x       x       0       0       0       1         x       x       0       1       0       1         x       x       1       0       1       1         x       x       1       0       1       1         x       x       1       1       0       0         x       x       1       1       0       1       1 |

TABLE 2-2. LP control bit settings in Register A.

Notes: a. x - don't care

b. When an illegal Vertical Control is issued the character is decoded as if A05=0.

## INSTALLATION

#### UNPACKING

- 1. Carefully remove wrapping from the 50-PAK controller card. Check for physical damage to the card and record any damage on the packing list. Check that the part number agrees with the parts list.

- 2. Remove the wrapping from the cable and check for physical damage. Record any damage on the packing list. Check that the part number agrees with the packing list.

#### PHYSICAL LIMITATIONS

Care must be taken to prevent damage to the controller card. The card must not be flexed, bent, or dropped.

#### POWER REQUIREMENTS

The controller card requires +5 vdc derived from the power supply of the computer.

## CABLING AND CONNECTORS

An external interconnecting cable is available for use with the controller for connection between the computer and the line printer. The external cable (Part No. 89818500) is 25 feet long and shielded.

The internal cable (Part No. 89641800) used between the back of the computer and the connector pins on the back plane is 15.5 inches long.

The interrupt cable (Part No. 89724702) is 13.8 inches long.

The wire lists for pin assignments are in Section 8.

#### COOLING REQUIREMENTS

The controller card is cooled by the forced air system of the computer. No further cooling is required. Refer to the 1784 Computer Customer Engineering Manual (Publication No. 89633300) for further information concerning the cooling capabilities of the computer.

### ENVIRONMENTAL CONSIDERATIONS

The environmental considerations necessary for operation (or storage) of the controller are listed in the specifications (Table 1-1).

#### PREPARATION AND INSTALLATION

Before installing the controller card, perform the following:

- 1. Remove the air-flow block from the lower slide of the card slot to be used.

- 2. Inspect the enclosure, card slot, PW board slides, and connector pins for physical damage.

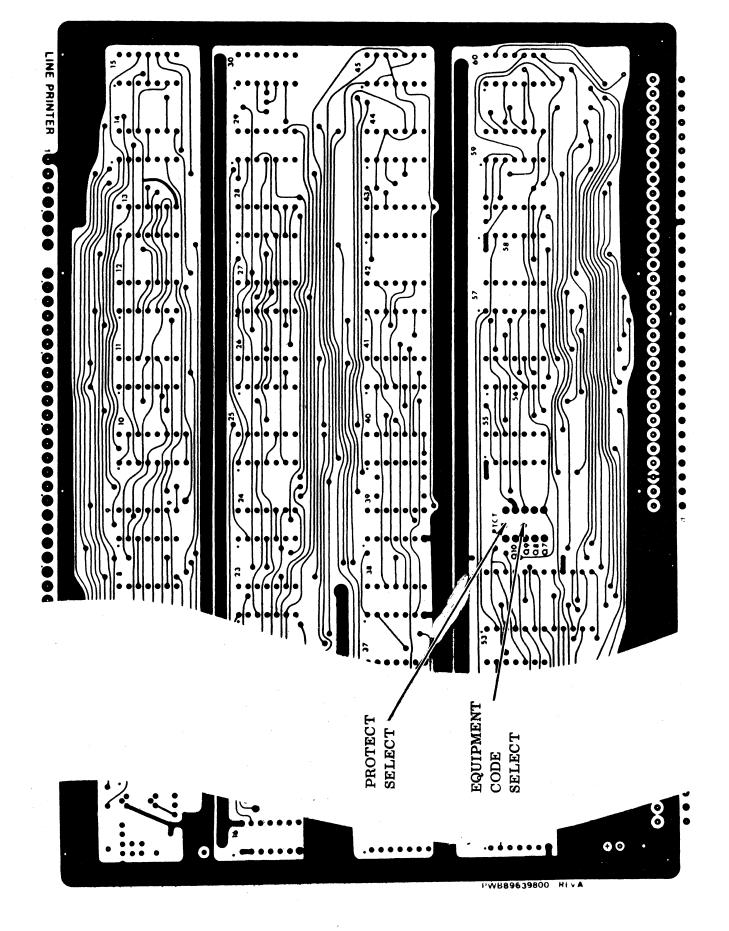

- 3. Place the Equipment Number and Protect jumpers in the proper positions on the card. Refer to Tables 3-1 and 3-2 and Figure 3-1.

#### CAUTION

Do not install or remove controller card or cables from computer or expansion enclosure with power on.

- 4. Carefully install the controller card in the assigned A/Q slot. The PWA must slide in smoothly. The slot must be selected according to the equipment configuration. Refer to Figure 3-2 and to the 1784 Computer CE Manual for card placement.

- 5. Place the interrupt cable in the position on the backplane as indicated in Table 3-3.

- 6. Install the internal cable between connector P2 of the position the controller PWA is placed in and the applicable output connector position of the CPU or expansion enclosure connector panel.

- 7. Install the external cable between the internal cable output connector and the line printer.

| SELECTION                                                                                                                 | LOCATION | PINS                                                                                                                                 | REMARKS                                      |

|---------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| PROTECT<br>(S1 on logic diagram)                                                                                          | U54      | 1 and 10<br>(Marked PTCT on PW Assy)                                                                                                 | Protected when<br>Jumper plug is out.        |

| EQUIPMENT CODE SELECT<br>(S5 on logic diagram)<br>(S4 on logic diagram)<br>(S3 on logic diagram)<br>(S2 on logic diagram) | U54      | 5 and 6<br>(Marked Q07 on PWB)<br>4 and 7<br>(Marked Q08 on PWB)<br>3 and 8<br>(Marked Q09 on PWB)<br>2 and 9<br>(Marked Q10 on PWB) | Selected<br>when<br>jumper<br>plug<br>is in. |

Table 3-1. Jumper Plug Selection

| LINKS                                                                                    | Q10<br>(S2) | Q09<br>(S3) | Q08<br>(S4) | Q07<br>(S5) |  |  |  |

|------------------------------------------------------------------------------------------|-------------|-------------|-------------|-------------|--|--|--|

| Hexadecimal Code 0                                                                       | 0           | 0           | 0           | 0 *         |  |  |  |

| 1                                                                                        | 0           | 0           | 0           | 1**         |  |  |  |

| 2                                                                                        | 0           | 0           | 1           | 0           |  |  |  |

| 3                                                                                        | 0           | 0           | 1           | 1           |  |  |  |

| 4                                                                                        | 0           | 1           | 0           | 0           |  |  |  |

| 5                                                                                        | 0           | 1           | 0           | 1           |  |  |  |

| 6                                                                                        | 0           | 1           | 1           | 0           |  |  |  |

| 7                                                                                        | 0           | 1           | 1           | 1           |  |  |  |

| 8                                                                                        | 1           | 0           | 0           | 0           |  |  |  |

| 9                                                                                        | 1           | 0           | 0           | 1           |  |  |  |

| Α                                                                                        | 1           | 0           | 1           | 0           |  |  |  |

| В                                                                                        | 1           | -0          | 1           | 1           |  |  |  |

| С                                                                                        | 1           | 1           | 0           | 0           |  |  |  |

| D                                                                                        | 1           | 1           | 0           | 1           |  |  |  |

| E                                                                                        | 1           | 1           | 1           | 0           |  |  |  |

| F                                                                                        | 1           | 1           | 1           | 1           |  |  |  |

| NOTE: * A binary 0 indicates jumper plug out.<br>** A binary 1 indicates jumper plug in. |             |             |             |             |  |  |  |

Table 3-2. Equipment Number Selection

Figure 3-1. Jumper Plug Location on PWA

Figure 3-2. Location for Installation of Controller PW Assembly (A/Q Bus)

| Table 0 0; meetinge the readenments              |          |                 |  |  |

|--------------------------------------------------|----------|-----------------|--|--|

| Line Printer Controller                          |          | e e la compañía |  |  |

| EOP Interrupt                                    |          | P1B24           |  |  |

| Common Interrupt                                 |          | P1B25           |  |  |

| Data Interrupt                                   |          | P1B26           |  |  |

| Alarm Interrupt                                  |          | P1B27           |  |  |

| Connections may be made to any of the following: |          |                 |  |  |

| <u>C PU</u>                                      | Position |                 |  |  |

| Line 1                                           | 25       | P1B10           |  |  |

| Line 2                                           | 25       | <b>P1A7</b>     |  |  |

| Line 3                                           | 25       | P1B7            |  |  |

| Line 4                                           | 25       | <b>P1A5</b>     |  |  |

| Line 5                                           | 25       | P1A6            |  |  |

| Line 6                                           | 25       | P1B6            |  |  |

| Line 7                                           | 25       | P1B5            |  |  |

| Line 8                                           | 26       | P1A10           |  |  |

| Line 9                                           | 26       | P1B10           |  |  |

| Line 10                                          | 26       | P1A7            |  |  |

| Line 11                                          | 26       | P1B7            |  |  |

| Line 12                                          | 26       | P1A5            |  |  |

| Line 13                                          | 26       | P1A6            |  |  |

| Line 14                                          | 26       | P1B6            |  |  |

| Line 15                                          | 26       | P1B5            |  |  |

### Table 3-3. Interrupt Pin Assignments

# CHECKOUT

- 1. Refer to Section 2 of this manual and the 1784 Computer Reference Manual for operation of the controller.

- 2. Determine that proper voltages are supplied to the controller card by measuring +5 vdc between test points 1 (ground) and 63 on the PWA.

- 3. Perform diagnostics check as described in the Systems Maintenance Monitor (SMM17) Manual, Publication Number 60182000.

.

# THEORY OF OPERATION

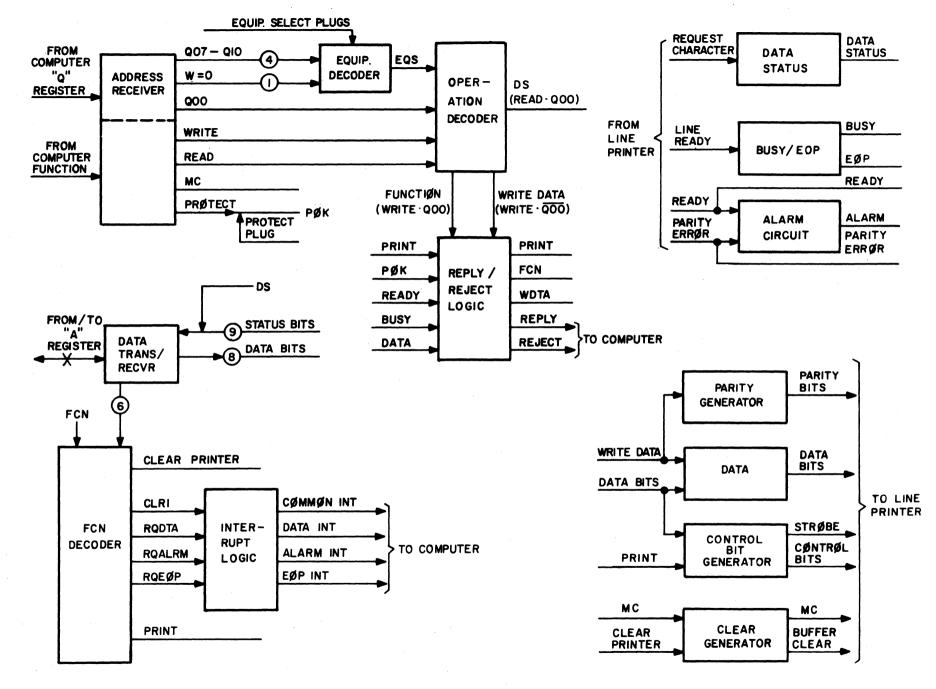

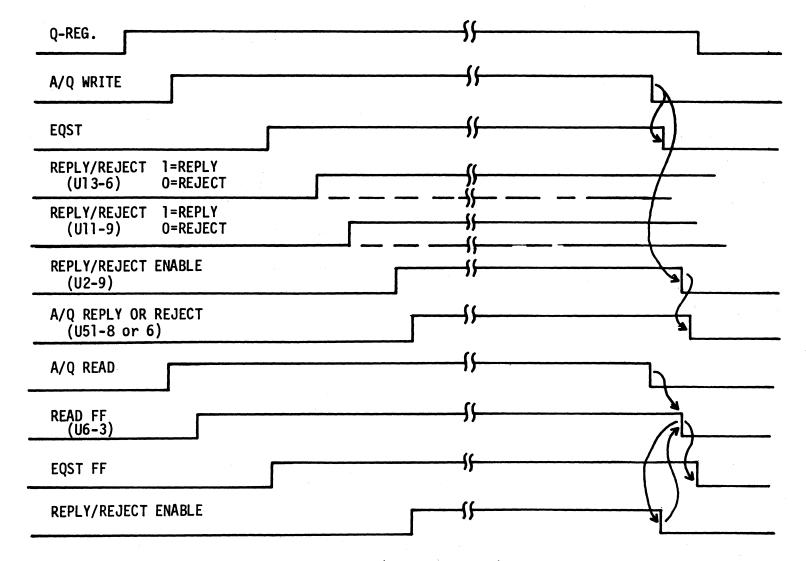

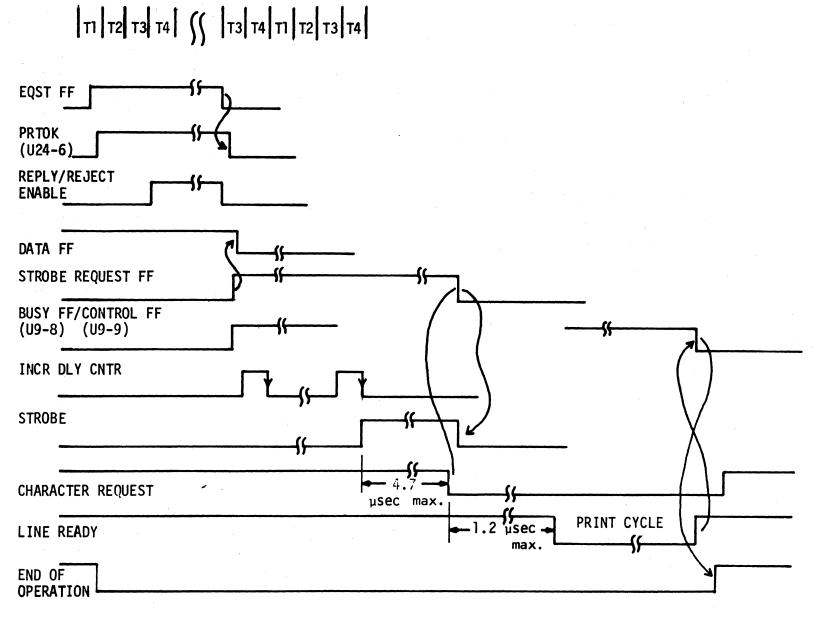

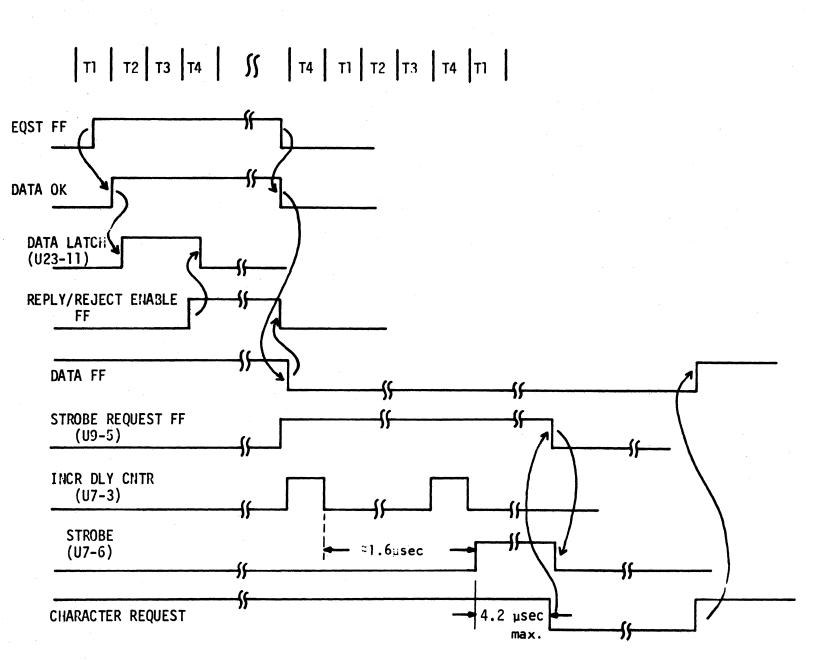

This section presents a general description of the equipment, using an overall block diagram (Figure 4-1) and timing diagrams (Figures 4-2 through 4-4). Descriptions are keyed to the detailed logic diagrams in Section 5 and afford a basis for understanding the detailed description of the specific circuits in that section.

#### NOTE

It is assumed that the reader is familiar with Control Data equipment and with the programming characteristics of the computer as described in the 1784 Computer System Reference Manual, Publication Number 89633400.

### GENERAL

The controller interfaces the computer through the A/Q channel.

In Write Data operation the data is transferred to the line printer from the eight least significant bits of the A register. The line printer incorporates a full line of buffered characters and the data is stored there until the controller issues a Print command.

The operation of the line printer can be divided into two phases: 1) when it receives data from the controller and stores it, and 2) the Print cycle, in which it prints directly from the buffer without intervention from the controller. The controller interfaces the line printer on a one-to-one basis.

When the line printer receives a character, it deactivates the Character Request signal.

The data from the controller's data register, together with the Parity bit, is strobed by the Strobe signal, from the controller to the line printer.

When the data has been sampled, the line printer activates the Character Request again (see Figure 4-4).