# CONTROL DATA® 1700 SYSTEM MAINTENANCE MONITOR

Volume 3 of 3

**REFERENCE MANUAL**

# **REVISION RECORD**

| REVISION                    | DESCRIPTION                                                                                       |  |  |  |  |  |  |

|-----------------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 01                          | Original Printing, preliminary edition.                                                           |  |  |  |  |  |  |

| (05-13-66)                  |                                                                                                   |  |  |  |  |  |  |

| 02                          | Publications Change Order 14307. Reprint with revision which obsoletes all previous editions.     |  |  |  |  |  |  |

| (08-08-66)                  | Tests were updated and the following new tests were added: 1711/1712 Teletype, 1729 Card          |  |  |  |  |  |  |

|                             | Reader, 1731 Magnetic Tape, 1706/1716 Buffered Data Channel and Coupling, Random Protect,         |  |  |  |  |  |  |

|                             | 1700 SMM Edit Routine, and Enter Program.                                                         |  |  |  |  |  |  |

| А                           | Manual released. Publication Change Order 16368. The following new tests are added: 0B (1718      |  |  |  |  |  |  |

| (05-01-67)                  | Satellite Coupler Test), 0C (1742 Line Printer Test), and 3D (Enter Program). Other tests were    |  |  |  |  |  |  |

|                             | extensively revised and updated. This edition obsoletes all previous editions.                    |  |  |  |  |  |  |

| В                           | Publication Change Order 17146. To revise existing tests and add new tests. Introduction: page 5  |  |  |  |  |  |  |

| (09-14-67)                  | revised. Description: pages 7, 12, 15, 18, 25, 26, 27, 30 and 35 revised. Pages 30-a and 30-b     |  |  |  |  |  |  |

|                             | added. Tests: pages 90-1, 90-2, 100-7, 100-8, 100-10, 101-2, 101-7, 202-1, 202-7, 205-2,          |  |  |  |  |  |  |

|                             | 206-6 thru 206-10, 207-3, 208-2 and 208-6 revised. Page 100-8a added. Tests sections: 102,        |  |  |  |  |  |  |

|                             | 201, 203, 212, 213, and 214 added. Sections 102 Rev A, 201 Rev A and 203 Rev A removed.           |  |  |  |  |  |  |

| С                           | Publications Change Order 18929. To add 1728 Card Reader/Punch test, No. D.                       |  |  |  |  |  |  |

| (02-28-68)                  |                                                                                                   |  |  |  |  |  |  |

| D                           | Publications Change Order 19818, to make miscellaneous publication corrections. Pages 37,         |  |  |  |  |  |  |

| (06-11-68)                  | 100-2, 100-18, 101-9, 102-7, 200-10, 201-6, 202-9, 203-7, 204-1, 204-12, 205-14, 206-9, 206-10    |  |  |  |  |  |  |

|                             | 207-4, 208-21, 210-4, 210-6, 211-13, and 215-23 revised. Pages 207-5 and 212-24 added.            |  |  |  |  |  |  |

| E                           | Manual Revised, Engineering Change Order 21307, publications change only. Information included    |  |  |  |  |  |  |

| (01-06-69)                  | through Edition 2.1. Pages 35, 90-1, 90-2, 90-6, 101-10, and 208-1 thru 208-21 revised; pages     |  |  |  |  |  |  |

|                             | 30-c through 30-f, 51 through 60, 103, 216, 217, 218, 219, 220, 221, 222 and red tab dividers     |  |  |  |  |  |  |

|                             | added. Manual divided into two volumes.                                                           |  |  |  |  |  |  |

| F                           | Manual revised, Engineering Change Order 21883. This manual is complete through Edition 2.1.      |  |  |  |  |  |  |

| (12-15-69)                  |                                                                                                   |  |  |  |  |  |  |

| G                           | Manual revised. New tests are added and editorial corrections made. This manual is complete       |  |  |  |  |  |  |

| (02-15-70)                  | through Edition 2.2.                                                                              |  |  |  |  |  |  |

| Н                           | Manuals revised. This publication is complete through Ed. 2.3. All previous editions are obsolete |  |  |  |  |  |  |

| (12-15-70)                  |                                                                                                   |  |  |  |  |  |  |

| J                           | Manuals revised. New tests are added and minor corrections are made. This publication is          |  |  |  |  |  |  |

| (02-05-73)                  | complete through Ed. 3.0.                                                                         |  |  |  |  |  |  |

| K                           | Manuals revised. Tests are added, deleted, and corrected.                                         |  |  |  |  |  |  |

| (09-20-73)                  |                                                                                                   |  |  |  |  |  |  |

| L                           | Manuals revised. Tests are added, deleted, and corrected. This publication is complete through    |  |  |  |  |  |  |

| (02-01-74)                  | Edition 3. 1.                                                                                     |  |  |  |  |  |  |

| М                           | Manuals revised. Tests are added and corrected. This publication is complete through Edition      |  |  |  |  |  |  |

| (12-10-74)                  | 3.1-1.                                                                                            |  |  |  |  |  |  |

| Publication No.<br>60182000 |                                                                                                   |  |  |  |  |  |  |

# REVISION LETTERS I, O, Q AND X ARE NOT USED

© 1966, 1967, 1968, 1969, 1973, 1974, 1975, 1977, 1978 by Control Data Corporation Printed in the United States of America Address comments concerning this manual to:

Control Data Corporation Publications and Graphics Division 4201 North Lexington Avenue St. Paul, Minnesota 55112

or use Comment Sheet in the back of this manual.

|                                       | REVISION RECORD (CONT'D)                                                                     |

|---------------------------------------|----------------------------------------------------------------------------------------------|

| REVISION                              | DESCRIPTION                                                                                  |

| N                                     | Manuals revised. Tests are added and corrected. This publication is complete through Edition |

| (10-1-75)                             | 3.1-2.                                                                                       |

| P                                     | Manuals revised. Tests are added, corrected, and deleted. This publication is complete       |

| (2-15-77)                             | through Edition 4.0.                                                                         |

| <u> </u>                              | Manual revised. Tests are corrected. This publication is complete through Edition 4.0-1.     |

|                                       |                                                                                              |

|                                       |                                                                                              |

|                                       |                                                                                              |

|                                       |                                                                                              |

|                                       |                                                                                              |

|                                       |                                                                                              |

| - <u></u> .                           |                                                                                              |

| <u></u>                               |                                                                                              |

| · · · · · · · · · · · · · · · · · · · |                                                                                              |

|                                       |                                                                                              |

| · .                                   |                                                                                              |

|                                       |                                                                                              |

| ·                                     |                                                                                              |

|                                       |                                                                                              |

| ·                                     |                                                                                              |

|                                       |                                                                                              |

| - <u></u>                             |                                                                                              |

|                                       |                                                                                              |

|                                       |                                                                                              |

|                                       |                                                                                              |

| ۰.                                    |                                                                                              |

| · · · · · · · · · · · · · · · · · · · |                                                                                              |

|                                       |                                                                                              |

|                                       |                                                                                              |

|                                       |                                                                                              |

|                                       |                                                                                              |

| <u> </u>                              |                                                                                              |

|                                       |                                                                                              |

|                                       |                                                                                              |

|                                       |                                                                                              |

|                                       |                                                                                              |

|                                       |                                                                                              |

|                                       |                                                                                              |

| · · · · · · · · · · · · · · · · · · · |                                                                                              |

|                                       |                                                                                              |

| Publication No.                       |                                                                                              |

| 60182000                              | ii-a/ii-b                                                                                    |

| PAGE        | REV                  | PAGE          | REV      | PAGE   | REV | PAGE   | REV | PAGE   | REV |

|-------------|----------------------|---------------|----------|--------|-----|--------|-----|--------|-----|

| Front Cover | -                    | 550-17        | J        | 552-29 | к   | 555-25 | L   | 602-10 | н   |

| Title Page  |                      | 551-1         | L        | 552-30 | ĸ   | 555-26 |     | 602-11 | H   |

| ii          | Ν                    | 551-2         | P        | 552-31 | ĸ   | 555-27 | L   | 602-12 | H   |

| ii-a/ii-b   | R                    | 551-3         | Ĵ        | 553-1  | P   | 555-28 | P   | 602-13 | H   |

| iii         | R                    | 551-4         | P        | 553-2  | P   | 555-29 | Ĺ   | 602-14 | H   |

| iv          | Р                    | 551-5         | Ĵ        | 553-3  | P   | 555-30 | Ĺ   | 602-15 | H   |

| iv-a/iv-b   | R                    | 551-6         | J        | 553-4  | ĸ   | 600-1  | J   | 602-16 | H   |

| v/vi        | P                    | 551-7         | J        | 553-5  | ĸ   | 600-2  | H   | 602-17 | H   |

| vii         | Р                    | 551-8         | Ĵ        | 553-6  | K   | 600-3  | H   | 602-18 | Ĥ   |

| viii        | R                    | 551-9         | J        | 553-7  | K   | 600-4  | H   | 602-19 | H   |

| ix          | R                    | 551-10        | J        | 554-1  | P   | 600-5  | H   | 602-20 | H   |

| x           | R                    | 551-11        | J        | 554-2  | К   | 600-6  | H   | 602-21 | Н   |

| xi/xii      | R                    | 551-12        | J        | 554-3  | P   | 600-7  | н   | 602-22 | Н   |

| 500-1       | M                    | 551-13        | J        | 554-4  | К   | 600-8  | н   | 602-23 | Н   |

| 500-2       | Р                    | 551-14        | J        | 554-5  | К   | 600-9  | н   | 603-1  | J   |

| 500-3       | H                    | 551-15        | J        | 554-6  | ĸ   | 600-10 | H   | 603-2  | Н   |

| 500-4       | Н                    | 551-16        | J        | 554-7  | K   | 600-11 | H   | 603-3  | Н   |

| 500-5       | н                    | 551-17        | J        | 554-8  | P   | 600-12 | L   | 603-4  | H   |

| 500-6       | Н                    | 551-18        | J        | 554-9  | K   | 600-13 | H   | 603-5  | H   |

| 500-7       | P                    | 551-19        | J        | 554-10 | K   | 600-14 | H   | 603-6  | H   |

| 500-8       | K                    | 551-20        | J        | 554-11 | K   | 600-15 | H   | 603-7  | H   |

| 500-9       | K                    | 551-21        | J        | 554-12 | K   | 600-16 | H   | 603-8  | H   |

| 500-10      | М                    | 551-22        | J        | 554-13 | K   | 600-17 | н   | 603-9  | н   |

| 500-11      | K                    | 551-23        | J        | 554-14 | K   | 600-18 | H   | 603-10 | H   |

| 500-12      | K                    | 551-24        | J        | 554-15 | K   | 600-19 | н   | 603-11 | H   |

| 500-13      | L                    | 551-25        | J        | 554-16 | K   | 600-20 | H   | 603-12 | H   |

| 500-14      | L                    | 551-26        | J        | 554-17 | К   | 600-21 | J   | 603-13 | Н   |

| 501-1       | L                    | 551-27        | J        | 554-18 | K   | 600-22 | J   | 603-14 | H   |

| 501-2       | $\mathbf{L}_{\perp}$ | 551-28        | Р        | 554-19 | K   | 600-23 | J   | 603-15 | P   |

| 501-3       | L                    | 551-29        | J        | 554-20 | K   | 600-24 | J   | 603-16 | н   |

| 501-4       | Н                    | 551-30        | J        | 554-21 | K   | 600-25 | J   | 603-17 | Н   |

| 501-5       | $\mathbf{L}$         | 552-1         | P        | 554-22 | K   | 600-26 | J   | 603-18 | н   |

| 501-6       | L                    | 552-2         | Μ        | 554-23 | K   | 601-1  | J   | 603-19 | ·H  |

| 501-7       | Μ                    | 552-3         | K        | 554-25 | K   | 601-2  | J   | 603-20 | Н   |

| 501-8       | H                    | 552-4         | К        | 554-26 | K   | 601-3  | н   | 603-21 | H   |

| 501-9       | H                    | 552- <b>5</b> | К        | 555-1  | P   | 601-4  | н   | 603-22 | Н   |

| 501-10      | L                    | 552-6         | К        | 555-2  | P   | 601-5  | н   | 603-23 | Н   |

| 501-11      | Н                    | 552-7         | К        | 555-3  | R   | 601-6  | н   | 603-24 | H   |

| 501-12      | н                    | 552-8         | К        | 555-4  | P   | 601-7  | н   | 603-25 | Н   |

| 501-13      | н                    | 552-9         | К        | 555-5  | M   | 601-8  | н   | 603-26 | Н   |

| 501-14      | L                    | 552-10        | К        | 555-6  | L   | 601-9  | н   | 603-27 | Н   |

| 501-15      | L                    | 552-11        | К        | 555-7  | L   | 601-10 | н   | 603-28 | н   |

| 501-16      | L                    | 552-12        | К        | 555-8  | P   | 601-11 | н   | 603-29 | Н   |

| 501-17      | L                    | 552-13        | К        | 555-9  | P   | 601-12 | H   | 603-30 | H   |

| 550-1       | Р                    | 552-14        | К        | 555-10 | P   | 601-13 | H   | 603-31 | Н   |

| 550-2       | Р                    | 552-15        | K        | 555-11 | L   | 601-14 | H   | 603-32 | H   |

| 550-3       | Р                    | 552-16        | K        | 555-12 | P   | 601-15 | Н   | 603-33 | H   |

| 550-4       | J                    | 552-17        | К        | 555-13 | Р   | 601-16 | H   | 603-34 | H   |

| 550-5       | Η                    | 552-18        | K        | 555-14 | Р   | 601-17 | н   | 603-35 | Н   |

| 550-6       | H                    | 552-19        | К        | 555-15 | L   | 601-18 | н   | 603-36 | Н   |

| 550-7       | Р                    | 552-20        | ĸ        | 555-16 | P   | 602-1  | J   | 603-37 | H   |

| 550-8       | Н                    | 552-21        | К        | 555-17 | L   | 602-2  | J   | 603-38 | H   |

| 550-9       | Р                    | 552-22        | К        | 555-18 | L   | 602-3  | н   | 603-39 | Р   |

| 550-10      | L                    | 552-23        | K        | 555-19 | Ĺ   | 602-4  | H   | 603-40 | н   |

| 550-11      | $\mathbf{L}$         | 552-24        | ĸ        | 555-20 | Ĺ   | 602-5  | H   | 603-41 | H   |

| 550-12      | Н                    | 552-25        | К        | 555-21 | Ē   | 602-6  | Ĥ   | 603-42 | H   |

| 550-13      | Н                    | 552-26        | K        | 555-22 | L   | 602-7  | H   | 603-43 | H   |

| 550-14      | Н                    | 552-27        | ĸ        | 555-23 | L   | 602-8  | H   | 604-1  | Ĵ   |

| 550-15      | Р                    | 552-28        | ĸ        | 555-24 | L   | 602-9  | H   | 604-2  | J   |

| 550-16      | $\mathbf{L}$         |               | <u> </u> |        |     |        |     |        | L   |

New features, as well as changes, deletions, and additions to information in this manual, are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

| PAGE             | REV          | PAGE             | REV                                                   | PAGE               | REV          | PAGE             | REV    | PAGE                     | REV    |

|------------------|--------------|------------------|-------------------------------------------------------|--------------------|--------------|------------------|--------|--------------------------|--------|

| 604-3            | J            | 612-8            | L                                                     | 613-10             | L            | 650-16           | Н      | 657-34                   | N      |

| 604-4            | J            | 612-9            | L                                                     | 614-1              | М            | 650-17           | H      | 657-35                   | Ν      |

| 604-5<br>604-6   | J            | 612-10<br>612-11 | $egin{array}{c} \mathbf{L} \\ \mathbf{L} \end{array}$ | 614-2              |              | 650-18           | M      | 657-36                   | N      |

| 604-6<br>604-7   | J<br>J       | 612-12           |                                                       | 614-3<br>614-4     | L<br>M       | 650-19<br>650-20 | H<br>H | 657-37<br>657-38         | N<br>P |

| 604-8            | J            | 612-13           |                                                       | 614-5              | M            | 650-21           | H H    | 657-39                   | P      |

| 604-9            | Ĵ            | 612-14           | L I                                                   | 614-6              | N            | 650-22           | Ĥ      | 657-40                   | P      |

| 604-10           | J            | 612-15           |                                                       | 614-7              | L            | 650-23           | н      | 657-41                   | Р      |

| 604-11           | J            | 612-16           | N                                                     | 614-8              | $\mathbf{L}$ | 650-24           | H      | 657-42                   | Ν      |

| 604-12           | J            | 612-17<br>612-18 | N                                                     | 614-9              | L            | 650-25           | H      | 657-43                   | N      |

| 604-13<br>604-14 | J<br>J       | 612-18           | N<br>N                                                | 614-10<br>614-11   |              | 650-26<br>650-27 | H<br>M | 657-44<br>657-4 <b>5</b> | N      |

| 604-15           | J            | 612-20           | N                                                     | 614-12             |              | 650-28           | M      | 657-46                   | N<br>N |

| 604-16           | J            | 612-21           | N                                                     | 614-13             | M            | 656-1            | N      | 657-47                   | N      |

| 604-17           | J            | 612-22           | Ν                                                     | 614-14             | M            | 656-2            | P      | 657-48                   | Ν      |

| 604-18           | J            | 612-23           | Ν                                                     | 615-1              | L            | 656-3            | Р      | 657-49                   | Ν      |

| 604-19           | J            | 612-24           | N                                                     | 615-2              | L            | 656-4            | Р      | 657-50                   | Ν      |

| 604-20<br>604-21 | J            | 612-25<br>612-26 | N                                                     | 615-3              |              | 656-5            | P<br>N | 657-51                   | N      |

| 604-21           | J<br>J       | 612-26           | N<br>N                                                | 615-4<br>615-5     | L<br>L       | 656-6<br>656-7   | N<br>N | 657-52<br>657-53         | N<br>N |

| 604-23           | J            | 612-28           | N                                                     | 615-6              |              | 656-8            | P      | 657-54                   | N      |

| 604-25           | J            | 612-29           | N                                                     | 615-7              | Ĺ            | 656-9            | P      | 657-55                   | N      |

| 604-26           | J            | 612-30           | N                                                     | 615-8              | L            | 656-10           | Р      | 657-56                   | N      |

| 604-27           | J            | 612-31           | Ν                                                     | 615-9              | L            | 656-11           | Ν      | 657-57                   | Ν      |

| 604-28           | J            | 612-32           | N                                                     | 615-10             | L            | 656-12           | N      | 657-58                   | Ν      |

| 605-1<br>605-2   | P<br>P       | 612-33<br>612-34 | N<br>N                                                | 615-11             |              | 656-13<br>656-14 | J<br>N | 657-59<br>657-60         | N      |

| 605-3            | P            | 612-35           | N                                                     | 616-1<br>616-2     | M<br>M       | 656-15           | P      | 657-61                   | N<br>N |

| 605-4            | P            | 612-36           | N                                                     | 616-3              | M            | 656-16           |        | 657-62                   | N      |

| 605-5            | P            | 612-37           | Ĺ                                                     | 616-4              |              | 656-17           | P      | 658-1                    | N      |

| 605-6            | Р            | 612-38           | Ν                                                     | 616-5              | L            | 656-18           | P      | 658-2                    | N      |

| 605-7            | Р            | 612-39           | Ν                                                     | 616-6              | М            | 656-19           | P      | 658-3                    | N      |

| 605-8            | P            | 612-40           | N                                                     | 616-7              | Μ            | 656-20           | P      | 658-4                    | Ν      |

| 605-9<br>605-10  | P<br>P       | 612-41<br>612-42 | N<br>N                                                | 616-8              | M            | 656-21<br>656-22 | P<br>P | 658-5                    | K      |

| 605-11           | г<br>Р       | 612-43           | N                                                     | 616-9<br>616-10    |              | 656-23           | P      | 658-6<br>658-7           | K<br>K |

| 605-12           | P            | 612-44           | N                                                     | 616-11             | L            | 656-24           | P      | 658-8                    | K      |

| 605-13           | L            | 612-45           | Ν                                                     | 616-12             | L            | 656-25           | P      | 658-9                    | ĸ      |

| 605-14           | L            | 612-46           | Ν                                                     | 616-13             | L            | 657-1            | N      | 658-10                   | K      |

| 605-15           | L            | 612-47           | L                                                     | 616-14             | $\mathbf{L}$ | 657-2            | N      | 658-11                   | К      |

| 605-16           | P<br>P       | 612-48<br>612-49 | L<br>L                                                | 616-15             | L<br>P       | 657-3            | N      | 658-12                   | K      |

| 605-17<br>605-18 | P<br>P       | 612-49           |                                                       | 617-1<br>617-2     | M            | 657-4<br>657-5   | N<br>N | 658-13<br>658-14         | K<br>K |

| 605-19           | P            | 612-51           | L                                                     | 617-3              |              | 657-6            | N      | 658-15                   | K      |

| 605-20           | P            | 612-52           | L L                                                   | 617-4              | м            | 657-7            | N      | 658-16                   | ĸ      |

| 605-21           | P            | 612-52.1         | M                                                     | 617-5              | М            | 657-8            | N      | 658-17                   | K      |

| 605-22           | P            | 612-53           | L                                                     | 617-6              | М            | 657-9            | N      | 658-18                   | K      |

| 605-23           | Р            | 612-54           |                                                       | 617-7              | М            | 657-10           | N      | 658-19                   | К      |

| 605-24<br>605-25 | P            | 612-55<br>612-56 | L<br>L                                                | 617-8              | N            | 657-11<br>657-12 | N      | 658-20<br>658-21         | K      |

| 610-1            | P<br>M       | 612-57           |                                                       | 650-1<br>650-2     | M<br>M       | 657-13           | N<br>N | 658-23                   | M<br>K |

| 610-2            |              | 612-58           | L                                                     | 650-3              | M            | 657-14           | N      | 658-24                   | K      |

| 610-3            | L            | 612-59           | L                                                     | 650-4              | M            | 657-15           | P      | 658-25                   | K      |

| 610-4            | Ĺ            | 612-60           | L                                                     | 650-4.1            | м            | 657-16           | Р      | 658-26                   | K      |

| 610-5            | L            | 612-61           |                                                       | 650-4.2            | M            | 657-17           | P      | 658-27                   | K      |

| 610-6            | $\mathbf{L}$ | 612-62           | L                                                     | 650-4.3            | M            | 657-18           | P      | 658-28                   | K      |

| 610-7            |              | 612-63<br>612-64 | L<br>L                                                | 650-4.4<br>650-4.5 | M            | 657-19<br>657-20 | P<br>P | 658-29<br>658-30         | K      |

| 610-8<br>610-9   |              | 612-65           | Ľ                                                     | 650-4.5            | M<br>M       | 657-21           | P<br>N | 658-30                   | K<br>K |

| 611-1            | M            | 612-66           | Ĺ                                                     | 650-6              | H            | 657-22           | N      | 658-32                   | K      |

| 611-2            | L            | 612-67           | L                                                     | 650-7              | H            | 657-23           | N      | 658-33                   | ĸ      |

| 611-3            | ī            | 612-68           | L                                                     | 650-8              | н            | 657-24           | Ν      | 658-34                   | K      |

| 611-4            | L            | 613-1            | М                                                     | 650-9              | Н            | 657-25           | N      | 658-35                   | K      |

| 611-5            | L            | 613-2            | L                                                     | 650-10             | M            | 657-26           | N      | 658-36                   | K      |

| 612-1            | P            | 613-3<br>613-4   | L<br>M                                                | 650-11             | M            | 657-27<br>657-28 | N<br>N | 658-37                   | K      |

| 612-2<br>612-3   |              | 613-4            | N                                                     | 650-12<br>650-12.1 | M<br>M       | 657-28           | N<br>N | 658-38<br>658-39         | K<br>K |

| 612-3            | L<br>M       | 613-6            |                                                       | 650-12.2           | M            | 657-30           | N      | 658-40                   | K      |

| 612-4            | M            | 613-7            | L L                                                   | 650-13             | M            | 657-31           | N      | 658-41                   | K      |

| 612-6            | M            | 613-8            | М                                                     | 650-14             | M            | 657-32           | N      | 658-42                   | ĸ      |

| 612-7            | N            | 613-9            | N                                                     | 650-15             | н            | 657-33           | N      | 658-43                   | K      |

60182000 P

• 1

ĝ

ß

iv

#### PREFACE

This manual is intended to serve as a reference aid for field and checkout personnel involved in the running of the CONTROL DATA<sup>®</sup> 1700 System Maintenance Monitor (SMM17).

This manual contains a detailed description of the operation and use of the monitor, instructions for the operator, restrictions, and necessary parameters. Detailed test descriptions are also included.

If information is required concerning the SMM17 QSE library, refer to SMM17 QSE Reference Manual, publication no. 60454710.

# CONTENTS

| VO  | LUME 1                                                                    |             |

|-----|---------------------------------------------------------------------------|-------------|

| SYS | STEM FLOW CHART                                                           | xi          |

| SM  | M17 DESCRIPTION                                                           |             |

|     |                                                                           |             |

| Ι.  | SMM17 DEFINITION                                                          | . 1         |

|     | A. General                                                                | 1           |

|     | B. Minimum System Configurations                                          | 1           |

|     | C. Standard System Configurations                                         | 4           |

| * . |                                                                           |             |

| II. | DESCRIPTION                                                               | 5           |

|     | A. System Loading and Initialization                                      | 5           |

|     | B. System/Operator Communications                                         | 12          |

|     | C. Monitor Error Codes                                                    | 20          |

|     | D. System Subroutines Available to Library Test                           | 20          |

| SUI | PPLEMENT A. Hand-Entered Bootstraps                                       | A-1         |

| SUF | PPLEMENT B. Quick Look Error Stops and Intermediate<br>Loader Error Stops | B-1         |

| SUF | PPLEMENT C. Monitor Error Codes                                           | C-1         |

| SUF | PPLEMENT D. SMM17 Programming Specifications                              | D <b>-1</b> |

| SUF | PPLEMENT E. Monitor Based Subroutines Programming Specification           | E <b>-1</b> |

| SUF | PPLEMENT F. SMM17 Library Format                                          | F-1         |

| OPI | ERATING PROCEDURES                                                        |             |

| I.  | LOAD THE BOOTSTRAP                                                        | 50-1        |

|     | A. Executing Quick Look Command Tests                                     | 50-1        |

| тт  |                                                                           | E0 9        |

| II. | SETTING THE SYSTEM PARAMETERS                                             | 50-2        |

|     | A. First Stop                                                             | 50-2        |

60182000 P

| B. Second Stop                         |                |               |                  | 50-3          |

|----------------------------------------|----------------|---------------|------------------|---------------|

| C. Third Stop                          |                |               |                  | 50-5          |

| D. Fourth Stop                         |                |               |                  | 50-5          |

| E. Fifth Stop                          |                |               |                  | 50 <b>-</b> 6 |

| III. SYSTEM INITIAL MESSAGE            |                |               |                  | 50-6          |

| A. Build Test List                     |                |               |                  | 50-7          |

| IV. TEST EXECUTION                     |                |               |                  | 5 <b>0-</b> 9 |

| A. Controlling Test Execution          |                |               |                  | <b>50-</b> 9  |

| ROUTINES                               | MNEMONIC       | NUMBER        | SUPPORT<br>CLASS | PAGE          |

| SERVICE ROUTINES                       |                |               |                  |               |

| Printer/Teletype Dump                  | $\mathbf{DMP}$ | 3B            | II               | 100-1         |

| Tape to Print Routine                  | LST            | 3C            | II               | 101-1         |

| 3000 Channel Simulator Assembler       | SAS            | 3D            | II               | 102-1         |

| SMM Edit Routine                       | $\mathbf{EDT}$ | $3\mathrm{E}$ | II               | 103-1         |

| 3000 Channel Simulator Program Update  | UD3            | 2D            | II               | 104-1         |

| 1700 Source/6000 TVC Update            | UD1            | 57            | II               | 105-1         |

| 1700 Source/6000 BUCAL Update          | UD2            | 58            | II               | 106-1         |

| 1700 MSMS Installation Program         | INS            | $\mathbf{FD}$ | II               | 107-1         |

| 1700 Disk Pack Call-Up Program         | DPC            | FC            | II               | 108-1         |

| Diagnostic Replace Program             | REP            | $\mathbf{FB}$ | II               | 109-1         |

| Punch-A-Deck Program                   | PAD            | <b>6</b> 9    | II               | 110-1         |

| Card Punch Verify Routine              | CPV            | F0            | II               | 111-1         |

| INTERNAL TESTS                         |                |               |                  |               |

| 1700 Command Test                      | COM            | 01            | II               | 200-1         |

| 1700 Memory Test                       | MEM            | 14            | II               | 201-1         |

| 1700 Protect Test                      | RPT            | 09            | II               | 202-1         |

| 1700 Quick Look Memory and Protect Tes | t QL2          | FE            | II               | 203-1         |

| 1774 System Controller Command Test    | CAR            | 1B            | II               | 204-1         |

| 1700 Memory Test                       | MY2            | 02            | II               | 205-1         |

| 1700 Memory Test                       | MY1            | 12            | II               | 206-1         |

| 1700 Command Test                      | CMD            | 1C            | II               | 207-1         |

| 1784 MOS Memory Test                   | MOS            | $1\mathrm{E}$ | II               | 208-1         |

|                                        |                |               |                  |               |

d'en

| ROUTINES                                                                | MNEMONIC             | NUMBER        | SUPPORT<br>CLASS | PAGE  |  |

|-------------------------------------------------------------------------|----------------------|---------------|------------------|-------|--|

| EXTERNAL TESTS                                                          |                      |               |                  |       |  |

| Paper Tape Equipment                                                    |                      |               |                  |       |  |

| 1723 Paper Tape Punch Test                                              | $\operatorname{PTP}$ | 03            | II               | 300-1 |  |

| 1721 Paper Tape Reader Test                                             | PTR                  | 04            | II               | 301-1 |  |

| 1720-1 Paper Tape Punch Test                                            | $\mathbf{PT1}$       | 92            | II               | 302-1 |  |

| 1720-1 Paper Tape Reader Test                                           | $\mathbf{PT2}$       | 93            | IĻ               | 303-1 |  |

| Printing Equipment                                                      |                      |               |                  |       |  |

| 1711/12/13 Teletypewriter Test                                          | $\mathbf{TTY}$       | 05            | II               | 350-1 |  |

| 1740/501,1742 Line Printer Test                                         | LP <b>1</b>          | 0C            | II               | 351-1 |  |

| FF524-A/1742-120/512 Printer Test                                       | LP5                  | 23            | II               | 352-1 |  |

| Card Equipment                                                          |                      |               |                  |       |  |

| 1728/430 Card Reader Punch Test                                         | CRP                  | <b>0</b> D    | II               | 401-1 |  |

| 1729-2 Card Reader Test                                                 | CR3                  | 13            | II               | 402-1 |  |

| 1726/405 Card Reader Test                                               | $\mathbf{CR2}$       | 17            | II               | 403-1 |  |

| 1725-1/FH302 Card Punch Test                                            | CPC                  | 88            | II               | 404-1 |  |

| Magnetic Tape Equipment                                                 |                      |               |                  |       |  |

| 1731/601,602,612 Magnetic Tape Test                                     | MT1                  | 07            | II               | 450-1 |  |

| 1731/601,602,612 Magnetic Tape Test                                     | MT2                  | 0E            | II               | 451-1 |  |

| 1732/608, Magnetic Tape Test                                            | MT3                  | 15            | II               | 452-1 |  |

| 1731/601,602,612-1732/608,609 Special<br>Magnetic Tape Test             | MTS                  | $1\mathrm{F}$ | II               | 453-1 |  |

| 1731, 1732/60X Magnetic Tape Test                                       | $\mathbf{MTX}$       | 4A            | II               | 454-1 |  |

| 1732-2/615-73/93 or 1732-3/616-72/93/95<br>Magnetic Tape Subsystem Test | PET                  | 4B            | II               | 455-1 |  |

| VOLUME 2                                                                |                      |               |                  |       |  |

| Data Channel                                                            |                      |               |                  |       |  |

| 1706 Data Channel Test                                                  | BD1                  | 0A            | II               | 500-1 |  |

| 1706/16 Data Channel Test                                               | BD2                  | <b>0</b> F    | II               | 501-1 |  |

| Rotating Mass Storage                                                   |                      |               |                  |       |  |

| 1738/853/854 Disk Drive Test                                            | DP1                  | 08            | II               | 550-1 |  |

| 1739 Cartridge Disk Drive Controller                                    | CDD                  | 78            | II               | 551-1 |  |

| BG504A/H Drum Controller Diagnostic                                     | DRM                  | 80            | II               | 552-1 |  |

| 1738 Disk Quick Look Test                                               | DP5                  | 84            | II               | 553-1 |  |

| 1733-1/1738/853,854 and QSE $4730$                                      | DP3                  | 27            | II               | 554-1 |  |

| 1733-2 Multiple Cartridge Disk Driver<br>Controller                     | MDC                  | <b>7</b> A    | II               | 555-1 |  |

|                                                                         |                      |               |                  |       |  |

| ROUTINES                                                     | MNEMONIC       | NUMBER        | SUPPORT<br>CLASS | PAGE  |

|--------------------------------------------------------------|----------------|---------------|------------------|-------|

| Displays                                                     |                |               |                  |       |

| 1745/6-1,210 Display Test                                    | DDC            | 40            | II               | 600-1 |

| 1745/6-2,211 Display Test                                    | $\mathrm{DDT}$ | 1D            | II               | 601-1 |

| 1700/8000 Data Transfer Buffer Display                       | DTB            | 10            | II               | 602-1 |

| 1744/274 Digigraphics Display Test                           | DIG            | $4\mathrm{F}$ | II               | 603-1 |

| 1744/274 Digigraphics Display System                         | DG4            | 6F            | II               | 604-1 |

| CYBERDATA Key Entry Station Test                             | KEY            | 60            | II               | 605-1 |

| General Purpose Graphics Terminal (GPGT                      | 7) N/A         | N/A           | N/A              | 610-1 |

| GPGT Troubleshooting Program                                 | GT0            | 70            | II               | 611-1 |

| GPGT Command Test                                            | GT1            | 71            | II               | 612-1 |

| GPGT Display Quality Test                                    | GT2            | 72            | II               | 613-1 |

| GPGT Light Pen and Keyboard Test                             | GT3            | 73            | II               | 614-1 |

| GPGT Communications Test                                     | GT4            | <b>74</b>     | II               | 615-1 |

| GPGT Communications Test (12 Bit Interfa                     | ce) GT5        | 75            | II               | 616-1 |

| GPGT Specification Verification Test                         | GT6            | 76            | II               | 617-1 |

| Optical/MICR Readers                                         |                |               |                  |       |

| 1735/915 Optical Character Reader                            | OCR            | 35            | II               | 650-1 |

| 1700/FF104/955 System Test                                   | RX1            | 30            | II               | 656-1 |

| 955-959/1700-1774-1784 Module Test                           | LDR/RX3        | 32/33         | II               | 657-1 |

| SC17/1700/FR101 MEM/COM/IFP Test                             | BC2            | 56            | II               | 658-1 |

| 1700/FR101/955 Transport Test                                | RX4            | 34            | II               | 660-1 |

| SC/1700/FR101/FR113 Interface Test                           | BC3            | 59            | III              | 661-1 |

| 929/1784 Diagnostic                                          | LR1            | 31            | II               | 662-1 |

| 234-14 Reader/Sorter                                         | $\mathbf{RST}$ | 61            | II               | 663-1 |

| VOLUME 3                                                     |                |               |                  |       |

| Communication Equipment                                      |                |               |                  |       |

| 1718 Satellite Coupler Test                                  | SC1            | <b>0</b> B    | II               | 700-1 |

| 1747/6000 Data Set Controller Test                           | DSC            | 11            | II               | 701-1 |

| 1747 Data Set Controller Test                                | DS1            | 20            | II               | 702-1 |

| 1749 Communications Terminal Test                            | CTC            | 43            | II               | 703-1 |

| 1748-2 Multiplexer Controller CSPL<br>Communications Adapter | MCC            | 48            | II               | 704-1 |

| DJ814A A/Q Communications Multiplexer<br>(NUMOD)             | AQM            | 36            | II               | 706-1 |

| 1743-2 Asynchronous Communications<br>Controller Test        | ACC            | 86            | II               | 707-1 |

1

| ROUTINES                                               | MNEMONIC       | NUMBER | SUPPORT<br>CLASS | PAGE  |

|--------------------------------------------------------|----------------|--------|------------------|-------|

| 1743-1 Synchronous Communications<br>Controller Test   | SCC            | 87     | II               | 708-1 |

| FJ505 Bisync Controller Test                           | BSC            | 89     | II               | 709-1 |

| Analog/Digital                                         |                |        |                  |       |

| Event Counter Subsystem                                | $\mathbf{CTR}$ | 81     | II               | 753-1 |

| Digital Input/Output Subsystem                         | DIO            | 83     | II               | 754-1 |

| IOM Mother Unit Diagnostic                             | IOM            | 90     | II               | 755-1 |

| 1500 Series Remote Peripheral Controller<br>Diagnostic | HOR            | 4C     | II               | 756-1 |

| Miscellaneous                                          |                |        |                  |       |

| 10126 Clock Test                                       | CLK            | 42     | II               | 850-1 |

| 10336-1 Real-Time Clock                                | RTC            | 91     | II               | 851-1 |

| 1700 Hardware Floating Point Unit Diagnostic           | c HFP          | 8A     | II               | 852-1 |

|                                                        |                |        |                  |       |

#### 1718 SATELLITE COUPLER TEST

# (SC1A0B Test No. 0B)

#### I. OPERATING INSTRUCTIONS

#### A. RESTRICTIONS

- 1. Test SC1 on the 3000 or 6000 side should be called first.

- 2. No other 1700 test may be run with this test. This test does not return control to the monitor.

- 3. Bit 5 in the SMM parameter word must be set.

# B. LOADING PROCEDURE

This program is called as test number 0B via SMM17. The 3000 or 6000 side is called as SC1 via the SMM3L or SMM6X, respectively. The 3000 or 6000 is the master and should be called first.

# C. PARAMETERS

#### 1. First stop

A = Test ID word (0B21)

Q = Test Stop/Jump parameter

Selective stops and jumps

- Bit 0 Parameter word (no typeout occurs)

- Bit 1 End of section (no typeouts)

- Bit 2 End of pass through test (typeout unless bit 8 is set)

- Bit 3 Error stop (typeout unless bit 8 set)

- Bit 4 Repeat conditions

Bits 5, 6, 7 - Not used

- Bit 8 No typeouts

- Bit 9 Return address corresponds to memory location rather than program listing

- Bit 11 Selects shift cable option (Set this bit when using a special data cable which is wired to shift the data cable bits left by 4 bits. When running with this option character mode is disabled.)

- 2. Second Stop

- A = Interrupt line

If bit 0 of the Stop/Jump parameter word is set, a Stop occurs with bit 6 in the A register set. This bit specifies interrupt line 6. If

新

the 1718 uses a different interrupt line, the operator must clear the A register, set the bit corresponding to the correct interrupt line, and run.

- Q = 6000 flag

- Bit 15 = 1 (6000 system)

Bit 15 = 0 (3000 system)

Sections can be selected only on the master side, the 3000 or 6000 Series Computer.

#### D. MESSAGES

#### 1. Normal Messages

a. SC1A0B, 1718 SATELLITE COUPLER TEST 1A = XXXX, FC = XX.

Start of test. Initial address is XXXX, frequency count is XX.

b. PROTECT STATUS SET

The Protect switch on the 1718 is set according to the status.

c. 0B24 XXXX 00YY ZZZZ

End of test. 0B is the test number. 2 is the number of stops, if any, and the number of pairs of words typed. 4 (bit 2) is the type of stop (End of Test stop) which occurs if bit 2 of the Stop/Jump parameter word is set.

XXXX is the Stop/Jump parameter.

00YY - YY is the pass number.

ZZZZ is the return address. This is relative to the initial address (program listing) of the test unless bit 9 of the Stop/Jump parameter is set, in which case ZZZZ is the memory location.

#### 2. Error Messages

a. Errors

All error typeouts are prefixed by 0BV8 XXXXX 0SYY ZZZZ. 0B is the test number.

V is the number of stops (if any), or the number of pairs of words to be typed.

8 (bit 3) is the type of stop (Error stop) which will occur if bit 3 of the Stop/Jump parameter word is set.

S is the section number.

YY is the error code.

ZZZZ is the return address.

If V = 2, there is no error typeout suffix.

b. Error Codes

01 - Insufficient core for test

02 - Equipment address in error. Start over.

03 - Interrupt line selection in error. Start over.

04 - Internal reject of status input

05 - Internal reject of select

- 06 Internal reject of AQ channel input or internal reject of direct input to BDC channel

- 07 Internal reject of AQ channel output or internal reject of direct output from BDC channel

08 - Not used

09 - Not used

0A - Unexpected status.

A = actual status, Q = expected status.

0B - Data error after read.

A = actual data, Q = expected data.

After a data error is found, no more data checking is performed for that input unless bit 4 (repeat conditions) of the Stop/Jump parameter is set.

0C - Alarm interrupt, division A channel parity error

A = Status upon interrupt

Q = Selected interrupts

Bit 2 of Q set - Data

Bit 3 of Q set - End of Operation

Bit 4 of Q set - Alarm

0D - Alarm interrupt, division A computer inactive

A and Q same as for error  $0\mathrm{C}$

0E - Interrupt status bit not set when interrupt occurred

A and Q same as for error 0C

0F - Non-selected interrupt occurred

A and Q same as for error 0C

10 - Flag interrupt did not occur when expected

A = current status

Q = current 1718 mask, 1700 side

11 - Not used

9

- 12 Non terminating buffer occurred

- 13 End of Operation status set before other computer

Write status is clear during Direct Read

- 14 Not used

- 15 Unexpected number of words read

- A = actual word count

- Q = expected word count

- 16 No End of Operation interrupt during Read

- 17 No End of Operation interrupt during Write.

- 3. Error Stops

Error stops occur if bit 3 of the Stop/Jump parameter is set. Error typeouts occur unless bit 8 of the Stop/Jump parameter is set. At error stops, the contents of the A and Q registers are the same as the typeout.

#### II. DESCRIPTION

#### A. GENERAL

- The test is divided into three sections, selectable on the 3000 or 6000 (master) side. These are Flag/Status section, Write/Read section, Mask/Interrupt section.

- 2. Each operational check is performed first from the 3000 or 6000 side to the 1700, then from the 1700 to the 3000 or 6000 side.

- 3. Each operational check is repeated 64 times.

#### B. DESCRIPTION OF TEST SECTIONS

1. Preliminary

Because flags 6 and 7 are used for communication, these flags are checked by each side prior to entering Section 1.

- 2. Section 1- Flag/Status Test

- a. Set all flags and check flags.

- b. Set individual flags and check.

- c. Set all but one flag and check.

- d. Clear individual flags and check.

- e. Clear all but one flag and check.

- f. Clear flags, check other computer Write/Read "1's", check for flags clear.

- g. Set flags, check other computer Read/Write "0's", check for all flags set.

- 3. Section 2, Write/Read Test

- a. Check other computer Write/Read.

- b. Check other computer Read/Write.

- c. Read and check data, Write.

- d. Repeat c for lengths of 4, 32, 256 words.

- e. Repeat c and d for each of seven patterns.

- f. Read random lengths of random pattern. Check data.

- g. Repeat f.

In Sections 1 and 2, reads and writes are not in Interrupt mode except for some of the random length reads. The buffered reads of random length are executed in Interrupt mode. Buffered and Direct mode for reads and writes are selected at random. Character and Word mode for reads and writes are selected at random. Reads and writes in section 3 are in Interrupt mode. Alarm and End of Operation interrupts are selected for reads and writes in Interrupt mode. Also, Data interrupt is selected for reads and writes in Interrupt mode, but not in Buffered mode.

- 4. Section 3, Mask/Interrupt Test

- a. Clear all flags, set all masks, expect no interrupts

- b. Set all flags, set individual masks, expect interrupts

- c. Set individual flags, set corresponding masks, expect interrupts.

- d. Set all but one flag, each flag. Set mask for flag not set. Expect no interrupt.

- e. Set individual flags. Set masks except flag set. Expect no interrupts.

- f. Read in Interrupt mode.

- g. Write in Interrupt mode.

#### III. PHYSICAL REQUIREMENTS

- A. SPACE REQUIRED About 2600<sub>10</sub> locations

- B. TEMPORARY STORAGE Current status of the 1718 is stored at memory location  $\text{SDD}_{16}$ .

#### C. PATTERNS

- 1. 000 (all "0's")

- 2. FFF (all "1's")

- 3. 000 FFF (all "0's", all "1's" alternate)

- 4. 555 AAA ("0", "1"; "1", "0")

- 5. F11 88F 47C 3E2 (3-bit end-around left shift)

- 6. F19 8CF 67C 3E3 (3-bit end-around left shift)

- 7. F11 0EE 88F 770 (complement, complement-shift) 47C B83 3E2 C1D

- Random (word N+1 = word n + addend, first word random 12-bit number, addend random 12-bit number, 12 bit end-around carry addition used)

- D. TIMING About 4 minutes for all three sections.

# E. EQUIPMENT CONFIGURATION

- 1. 17X4 Computer with 8K memory

- 2. 1705 Interrupt Data Channel

- 3. 1706 Buffer Data Channel (optional)

- 4. 1718 Satellite Coupler

- 5. 3000 or 6000 Series Computer with one data channel.

- 6. A device for loading program.

# DSC 1700 DATA SET CONTROLLER

# (DSCA11 Test No. 11)

#### I. OPERATIONAL PROCEDURE

#### A. RESTRICTIONS

- 1. Test must be run with 6X00/6675 Data Set Controller Test ( $6000 \rightarrow RT3$ ).

- 2. Operator must make section selections, and stop/jump options correspond to those of the 6X00 operator.

- 3. Test must be loaded first (it does not return control to SMM after an I/O operation).

- 4. This test MUST be started before the 6675 test is initiated.

# B. LOADING PROCEDURE

- 1. Loads under SMM17

- 2. Test mnemonic DSC

- 3. Test number 11

#### C. PARAMETERS

Parameter selection follows standard 1700 SMM format. Bit 11 of the stop/jump parameter word must be set for Input/Output from A mode; if not set, test runs in Buffer mode. The test parameter stops for section selection in A (preset to 000F) and interrupt mask in Q (preset to 0000). To set the interrupt mask parameter, the bit in Q matching the interrupt line should be set to "1" (i.e. bit 5 for interrupt line 5). For a normal run, the Stop at End of Section parameter bit should not be set.

# D. MESSAGES

1. Normal Messages

DSCA11, 1700 DATA SET CONTROLLER TEST IA = XXXX, FC = XX This message is typed at the beginning of the test. All other typeouts appear in standard SMM17 format.

Either an expected interrupt did not occur or an unexpected interrupt

# 2. Error Codes

- 01 Unidentified interrupt

- 02

did occur

A = actual status

**Q** = expected status

03

present

- A = actual status

- Q = expected status

04

Data compare error between data sent and data received. If more than 10<sub>16</sub> errors occur or the errors occur in section 5, then

Either an expected status is not present or an unexpected status is

A = number of errors

Q = pattern number

- 05 Cyclic code from the remote controller does not compare with the cyclic code generated.

- 06 Internal reject on an I/O attempt. (Repeats attempt following error display)

07 Interrupt status bit is set following a Clear Interrupt function

- 08 W of the equipment code is not 0, 02, 07, or 0C.

- 09 Sync Word Not Acknowledged status bit is in error. Following a select transmit, the status bit should be set, if not, the program records the error and proceeds to attempt the output. If the status bit is not down, the output is attempted  $20_{16}$  more times before the error is reported.

- 13 Insufficient memory for test

- 14 Status after an input operation does not compare with the expected status (see error code 3).

# 1748-2 MULTIPLEXER CONTROLLER, CSPL COMMUNICATIONS ADAPTER (MCCA48 Test No. 48)

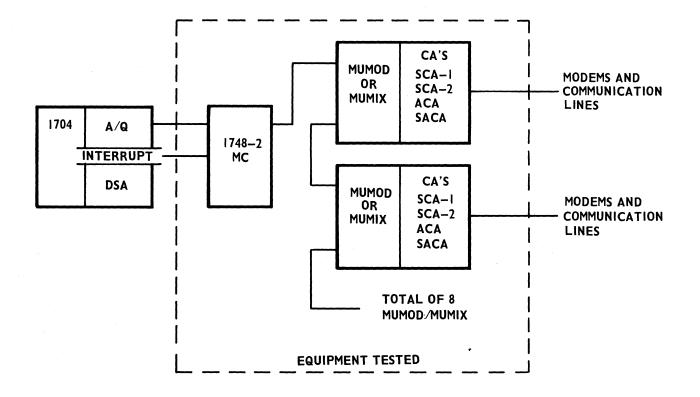

#### I. IDENTIFICATION

#### A. EQUIPMENT TESTED

1748-2 Multiplexer Controller (MC)

DJ808A Communications Multiplexer (MUMOD) - 364-1,2

DJ813A Communications Multiplexer (MUMIX) - 364-3

DJ144A Synchronous Communication Adapter (SCA-1) - 361-5

DJ145A Synchronous Communication Adapter (SCA-2) - 361-6

DJ122A Asynchronous Communication Adapter (ACA-1) - 361-4

DJ142A, DJ143A Communication Adapter (SACA) - 361-1

#### II. INTRODUCTION

The 1748-2 MC CSPL Diagnostic Program checks the function, status, and data handling capabilities of the multiplexer controller, communication multiplexers, and communication adapters (SCA-1, SCA-2, ACA, and SACA) through the use of individually selectable sections. Up to 512 single address communication adapters (CAs) or any combination of single and dual address CAs, not to exceed 512 addresses, may be tested at one time.

#### III. REQUIREMENTS

A. HARDWARE

1748-2 Multiplexer Controller (MC)

DJ808A Communication Multiplexer (MUMOD)

DJ813A Communication Multiplexer (MUMIX)

DJ144A, DJ145A Synchronous Communications

Adapter (SCA-1, SCA-2)

DJ122A Asynchronous Communication Adapter (ACA)

DJ142A, DJ143A Communication Adapter (SACA)

(See Figure 1)

Figure 1.

1000

ŝ

Citran State

#### B. SOFTWARE

The 1748-2 MC CSPL Diagnostic Program operates under the SMM17 Diagnostic Monitor as a type 7 test.

#### C. ACCESSORIES

No special accessories are required for test execution.

#### **IV. LIMITATIONS**

- A. Due to the limited computer hardware and time, the test is not capable of the following:

- 1. Testing the DJ146A (ACUCA).

- 2. DSA test.

- 3. Generating a Character Lost interrupt (bit 09), and parity (bit 08).

- 4. Transparent mode.

- 5. SACA Set and Clear Break test.

- B. The following equipment is the only CSPL hardware on which the test has been executed.

- 1. Three DJ808A's (MUMOD)

- 2. Sixteen DJ142's (SACA)

- 3. Four DJ144A's (SCA-1)

- 4. Four DJ145A's (SCA-2)

- 5. One DJ122A's (ACA)

All of the above equipments have been simultaneously tested by this diagnostic.

- C. When selecting pluggable options on the asynchronous communication adapter, the send clock rate and bit level must equal the receive clock rate and bit level.

- D. When testing synchronous communication adapters, a data set or equivalent must be connected to the CA. The following data sets and their equivalents are compatible.

- 1. Data Sets 201-A/B

- 2. Data Sets X203-A

- 3. Data Set 303

- E. The single address communication adapter (SACA) must be placed in the echo mode before testing.

- F. Run in 32K mode only when using 1714.

- G. Prestoring Parameters The parameters for the DJ808/813 can only be prestored in this test using edit Prestored Parameters feature. The parameter A6, Q6, however, cannot be effectively prestored.

The CA parameters may be prestored using Program Modification feature in edit for a maximum of 14 CA's.

# V. OPERATIONAL PROCEDURE

#### A. LOADING PROCEDURE

1. Load the SMM17 library.

- 2. The computer will halt with the Overflow light lit. Set the A register equal to the desired SMM parameter word configuration (for normal operation, set bits 4 and 5 and the appropriate loader designation bit). Set the Q register equal to the desired SMM Stop/Jump parameter configuration and place the STEP/RUN switch in the Run position.

- 3. When the computer stops, set the A register to the desired SMM ID word configuration with the upper eight bits equal to 48. Set the Q register bits 7 through 10 equal to the 1748-2 MC equipment number and set bit 0. Place the SELECTIVE SKIP switch in the Off position. Place the STEP/ RUN switch in the Run position.

- 4. The typewriter will type: MCCA48, 1748-2 MC CSPL DIAGNOSTIC - TEST. VRS. 3.1 IA = XXXX. FC = XXXX CP 03

- 5. The computer will halt with the Overflow light lit. The A register will contain the test ID word and the Q register will contain the Stop/Jump word. The Stop/Jump parameter word in the Q register may be changed at this time if desired. No change is required for normal operation of the program.

- 6. The following stops will be parameter stops necessary for test execution.

#### NOTE

If only function tests are to be run, it is necessary to enter parameters for at least one CA, even though there is no CA to test (in the multiplexer rack). Address 001 is sent to the 1748-2 MC along with a Set CA Address Register function. The 1748-2 is checked for Busy status. A Clear CA Address Register function is issued to the 1748-2 MC and status is checked for Not Busy. Any unexpected status, interrupt or reject will result in an error.

#### 34. Subtest 44 - Word Mode Interrupt

This 1748-2 MC function test checks operation of the Word Mode Interrupt. Start Scan and Start Word Mode Interrupt functions are issued to the 1748-2 MC. If periodic Word Mode Interrupts are not received from the 1748-2 MC, an error is reported. If the interrupts are received, Stop Scan and Stop Word Mode Interrupt functions are issued to the 1748-2 MC. No further Word Mode Interrupts should be received. Any reject, unexpected status or unexpected interrupt, will result in an error.

#### 35. Subtest 45 - End of Operation Interrupt

This 1748-2 MC function test verifies operation of the scanner and checks the End of Operation Interrupt. The scanner is started and the CA Address register is cleared. CA address 000 is issued and the 1748-2 MC is checked for Busy status and End of Operation Interrupt. If the interrupt is not received and/or the Busy status does not clear, an error is reported. If the End of Operation interrupt is received and the 1748-2 MC goes Not Busy, the CA address equal to the maximum scan setting is issued. The maximum scan setting is a parameter received during parameter entry which indicates the last or highest CA address to be generated by the 1748-2 MC and expansion network (MUMOD's and/or MUMIX's). Tf an End of Operation interrupt is not received and/or Busy status does not drop, an error is reported. Any reject, unexpected status or unexpected interrupt, will result in an error report.

36. Subtest 46 - Scan Failure Interrupt

This 1748-2 MC function test checks the Scan Failure this Unit Interrupt. Status is first checked for Not Scanning other Unit Set. The scanner is started and status is checked for bit 4 clear (Scan Failure this Unit). The scanner is stopped, a Scan Failure Interrupt this Unit is expected, error code 57 is reported if not received. Any unexpected interrupt, unexpected status, or reject will also result in an error.

#### 37. Subtest 47 - Busy Check

This 1748-2 MC function test verifies operation of the Busy status. The CA Address register is cleared, CA address 000 is issued, and the 1748-2 MC is checked for Busy status. If Busy the CA Address register is cleared and the 1748-2 MC is checked for Not Busy. CA address 000 is issued again and Busy is checked. The scanner is then started, CA address equal to the Maximum Scan setting plus one is issued to the 1748-2 MC and Busy is checked. If the 1748-2 MC remains Busy, the CA Address register is cleared and Not Busy status is checked. Any reject, unexpected status, unexpected interrupt, or any variation from the expected will result in an error.

#### 38. Subtest 48 - Program Protect Fault

This 1748-2 MC function test checks the Program Protect Fault Status bit. It is assumed that the 1748-2 MC and the console PROGRAM PROTECT switch is in the OFF or UNPROTECTED position. The test will issue three clear Interrupt and Status functions with the program protect bit clear and then three clear Interrupt and Status functions with the program protect bit set. With the PROGRAM PROTECT switch OFF, no Program Protect faults should be detected. This test may be selected by itself and run with the 1748-2 MC and the console PROGRAM PROTECT switch ON. In this situation three SMM 02 errors should be generated for the three unprotected Clear Interrupt and Status functions. Any unexpected status, unexpected interrupt, or reject will also result in an error.

#### NOTE

If SLS is set, a stop will be performed at the location Program Protect was detected. If SLS is left off, this stop will not occur and SMM will display the error.

#### 39. Subtest 49 - Single Scan, Dual Scan

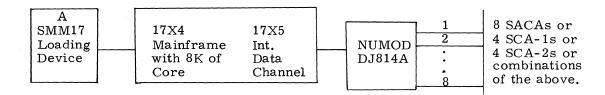

This 1748-2 MC function test verifies operation of the Single Scan and Dual Scan functions in a communications system operating in the single scan mode. Single Scan functions and Dual Scan functions are issued to the 1748-2 MC. It is assumed the DMU is not connected to the 1748, an external reject will then be expected on Dual Scan function. Any unexpected status, unexpected interrupt, or reject will also result in an error. 2. Core Requirements

The minimum amount of core required is 8K.

3. Peripheral Requirements

One standard SMM17 input device

1721/1722 Paper Tape Reader

1728/1729 Card Reader Controller

1726 Card Reader (405) Controller

1712/1713 Teletypewriter

1731/1732 Magnetic Tape Controller

1738 Disk Pack Controller

8000 Tape Drives

One NUMOD Communications Multiplexer

4. Maximum Configuration

All items referenced in the above paragraph, plus expansion of the CAs to the following limits:

Eight SACAs, or

Four SCA-1s, or SCA-2s, or

Combinations of SCA-1, SCA-2, and SACAs (SCA-1, ACA, and SCA-2 requires two addresses per CA, SACA requires one address per CA).

5. Equipment Configuration

**9**33

#### B. SOFTWARE

#### 1. Environment

The diagnostic program operates under control of the SMM17 Monitor in the teletypewriter non-interrupt mode. The monitor and the test require parameters which can either be supplied each time the test is initiated or the test can execute with a prestored set of parameters.

#### 2. External References

The diagnostic test makes reference to the monitor-based subroutines and tables. Linkages are through low core via equates. These equates are incorporated in the diagnostic test.

# IV. OPERATIONAL PROCEDURE

# A. LOADING PROCEDURE

The diagnostic is loaded using the standard SMM17 Monitor Test loading procedure.

#### **B. PARAMETERS**

Prestore parameter location for NUMOD Test

| CATOTS + 0   | First CA Parameter  | First Stop  | (A) | 0F3D         |

|--------------|---------------------|-------------|-----|--------------|

| CATOTS + 1   |                     |             | (Q) | 0F3E         |

| CATOTS + 2   |                     | Second Stop | (A) | <b>0F3F</b>  |

| CATOTS + 3   |                     |             | (Q) | 0F40         |

| CATOTS + 4   | Second CA Parameter | First Stop  | (A) | 0F41         |

| CATOTS $+ 5$ |                     |             | (Q) | <b>0F42</b>  |

| CATOTS + 6   |                     | Second Stop | (A) | <b>0F43</b>  |

| CATOTS + 7   |                     |             | (Q) | <b>0F44</b>  |

| CATOTS + 8   | Third CA Parameter  | First Stop  | (A) | <b>0F45</b>  |

| CATOTS + 9   |                     |             | (Q) | 0F46         |

| CATOTS + A   |                     | Second Stop | (A) | <b>0F47</b>  |

| CATOTS + B   |                     |             | (Q) | <b>0F</b> 48 |

| CATOTS + C   | Fourth CA Parameter | First Stop  | (A) | <b>0F49</b>  |

| CATOTS + D   |                     |             | (Q) | 0F4A         |

| CATOTS + E   |                     | Second Stop | (A) | 0F4B         |

| CATOTS + F   |                     |             | (Q) | 0F4C         |

|              |                     |             |     |              |

| CATOTS + $10$ | Fifth CA Parameter       | First Stop     | (A)         |    | 0F4D |

|---------------|--------------------------|----------------|-------------|----|------|

| CATOTS + 11   |                          |                | <b>(</b> Q) |    | 0F4E |

| CATOTS + $12$ |                          | Second Stop    | (A)         |    | 0F4F |

| CATOTS + 13   |                          |                | (Q)         |    | 0F50 |

| CATOTS + 14   | Sixth CA Parameter       | First Stop     | (A)         |    | 0F51 |

| CATOTS + $15$ |                          |                | <b>(</b> Q) |    | 0F52 |

| CATOTS + 16   |                          | Second Stop    | (A)         |    | 0F53 |

| CATOTS + 17   |                          |                | <b>(</b> Q) |    | 0F54 |

| CATOTS + 18   | Seventh CA Parameter     | First Stop     | (A)         |    | 0F55 |

| CATOTS + 19   |                          |                | (Q)         |    | 0F56 |

| CATOTS + 1A   |                          | Second Stop    | (A)         |    | 0F57 |

| CATOTS + 1B   |                          |                | (Q)         |    | 0F58 |

| CATOTS + 1C   | Eighth CA Parameter      | First Stop     | (A)         |    | 0F59 |

| CATOTS + $1D$ |                          |                | (Q)         |    | 0F5A |

| CATOTS + $1E$ |                          | Second Stop    | (A)         |    | 0F5B |

| CATOTS + 1F   |                          |                | (Q)         |    | 0F5C |

| ONOINT        | Interrupt line number    |                |             | *  | 0EF9 |

| CCANUM        | Number of CAs to test    | and NUMOD Test | <b>;</b>    | *  | 0EFA |

| CDELAY        | NUMOD Interrupts Cloc    | k Time         |             | ** | 0EFB |

| CEQBAD        | Illegal equipment number | er             |             | ** | 0EFC |

|               |                          |                |             |    |      |

#### 1. Prestored Parameters

The diagnostic is set to run with a prestored set of parameters. No parameter changes are required if the prestored list of parameters are valid for the CAs being tested.

The following is a list of the prestored parameters.

- a. NUMOD equipment E.

- b. Interrupt line number 3.

- c. Illegal equipment number 0.

- d. NUMOD subtest selection 0 through 5.

- e. NUMOD clock prestored as \$64 (1 millisecond).

\* 2. b. Second stop (A) (Q) respectively.

\*\*2.c. Third stop (A) (Q) respectively.

)

f. Three communications adapters are selected:

- 1) SCA-1 addresses 0 and 1

- 2) SACA address 2