### CONTROL DATA® 1700 SYSTEM MAINTENANCE MONITOR

$\bigcirc$

$\bigcirc$

$\bigcirc$

$\bigcirc$

$\bigcirc$

0 0 0

$\bigcirc$

$\bigcirc$

()

Volume 3 of 3

|                 | RECORD of REVISIONS                                                                                           |

|-----------------|---------------------------------------------------------------------------------------------------------------|

| REVISION        | NOTES                                                                                                         |

| 01              | Original Printing, preliminary edition.                                                                       |

| (5-13-66)       |                                                                                                               |

| 02              | Publications Change Order 14307. Reprint with revision which obsoletes all previous editions.                 |

| (8-8-66)        | Tests were updated and the following new tests were added: 1711/1712 Teletype, 1729 Card Reader,              |

|                 | 1731 Magnetic Tape, 1706/1716 Buffered Data Channel and Coupling, Random Protect, 1700 SMM                    |

|                 | Edit Routine, and Enter Program.                                                                              |

| А               | Manual released. Publication Change Order 16368. The following new tests are added: 0B (1718                  |

| (5-1-67)        | Satellite Coupler Test). 0C (1742 Line Printer Test), and 3D (Enter Program). Other tests were                |

|                 | extensively revised and updated. This edition obsoletes all previous editions.                                |

| В               | Publication Change Order 17146. To revise existing tests and add new tests. Introduction: page 5              |

| (9-14-67)       | revised. Description: pages 7, 12, 15, 18, 25, 26, 27, 30 and 35 revised. Pages 30-a and 30-b                 |

|                 | added. Tests: pages 90-1, 90-2, 100-7, 100-8, 100-10, 101-2, 101-7, 202-1, 202-7, 205-2, 206-6                |

|                 | thru 206-10, 207-3, 208-2 and 208-6 revised. Page 100-8a added. Tests sections: 102, 201, 203,                |

|                 | 212, 213 and 214 added. Sections 102 Rev A, 201 Rev A and 203 Rev A removed.                                  |

| C               | Publications Change Order 18929. To add 1728 Card Reader/Punch test, No. D.                                   |

| (2-28-68)       |                                                                                                               |

| D               | Publications Change Order 19818, to make miscellaneous publication corrections. Pages 37,                     |

| (6-11-68)       | 100-2, 100-18, 101-9, 102-7, 200-10, 201-6, 202-9, 203-7, 204-1, 204-12, 205-14, 206-9, 206-10                |

| (0 11 00)       | 207-4, 208-21, 210-4, 210-6, 211-13, and 215-23 revised. Pages 207-5 and 212-24 added.                        |

| E               | Manual Revised, Engineering Change Order 21307, publications change only. Information included                |

| (1-6-69)        | through Edition 2.1. Pages 35, 90-1, 90-2, 90-6, 101-10, and 208-1 thru 208-21 revised; pages                 |

| (1 0 00)        | 30-c through 30-f, 51 through 60, 103, 216, 217, 218, 219, 220, 221, 222 and red tab dividers                 |

| <u></u>         | added. Manual divided into two volumes.                                                                       |

| <br>F           | Manual revised, Engineering Change Order 21083. This manual is complete through Edition 2.1.                  |

| (12-15-69)      | Mandal Tovibod, Engineering ondige of der Broot, Tinb mandar ib competer an og andran Lift                    |

| G               | Manual revised. New tests are added and editorial corrections made. This manual is complete                   |

| (2-15-70)       | through Edition 2.2.                                                                                          |

| н               | Manuals revised. This publication is complete through Ed. 2. 3. All previous editions are obsolete.           |

| (12-15-70)      | Mandals revised. This publication is complete through Ed. 2. 0. An previous editions are observes.            |

| J               | Manuals revised. New tests are added and minor corrections are made. This publication is                      |

| (2-5-73)        | complete through Ed. 3. 0.                                                                                    |

| K               | Manuals revised. Tests are added, deleted, and corrected.                                                     |

| (9-20-73        | manuars revised. resis are audeu, dereted, and corrected,                                                     |

|                 | Manuals revised. Tests are added, deleted, and corrected. This publication is complete through                |

| <u> </u>        |                                                                                                               |

| (2-1-74)<br>M   | Edition 3, 1.<br>Manuals revised. Tests are added and corrected. This publication is complete through Edition |

| M (12-10-74)    |                                                                                                               |

| (12-10-74)<br>N | 3.1-1.<br>Manuals revised. Tests are added and corrected. This publication is complete through Edition        |

| (10-1-75)       | Manuals revised. Tests are added and corrected. This publication is complete through Edition 3.1-2.           |

Address comments concerning this manual to:

Control Data Corporation Publications and Graphics Division 4201 North Lexington Avenue St. Paul, Minnesota 55112

or use Comment Sheet in the back of this manual.

Pub.No. 60182000 © 1966, 1967, 1968, 1969, 1973, 1974, 1975 by Control Data Corporation Printed in United States of America

#### PREFACE

#### MANUAL STRUCTURE

This manual is intended to serve as a reference aid for field and checkout personnel involved in the running of the CONTROL DATA® 1700 System Maintenance Monitor (SMM17). It consists of two sections:

#### SMM17 DESCRIPTION

A detailed description of the operation and use of the monitor, instructions for the operator, restrictions and necessary parameters. An asterisk (\*) on the left of the page will highlight operator tasks. Supplements are included in the back of this section.

#### TESTS

Detailed test descriptions complete the three volume reference manual.

#### CONTENTS

| VOLUME 1                                                                    |                       |

|-----------------------------------------------------------------------------|-----------------------|

| SYSTEM FLOW CHART                                                           | xi                    |

| SMM17 DESCRIPTION                                                           |                       |

| I. SMM17 DEFINITION                                                         | 1                     |

| A. General                                                                  | 1                     |

| B. Minimum System Configurations                                            | 1                     |

| C. Standard System Configurations                                           | 4                     |

| II. DESCRIPTION                                                             | 5                     |

| A. System Loading and Initialization                                        | 5                     |

| B. System/Operator Communications                                           | 12                    |

| C. Monitor Error Codes                                                      | 18                    |

| D. System Subroutines Available to Library Test                             | 18                    |

| SUPPLEMENT A. Hand-Entered Bootstraps                                       | A <b>-</b> 1          |

| SUPPLEMENT B. Quick Look Error Stops and Intermediate<br>Loader Error Stops | B <b>-</b> 1          |

| SUPPLEMENT C. Monitor Error Codes                                           | C-1                   |

| SUPPLEMENT D. SMM17 Programming Specifications                              | D <b>-1</b>           |

| SUPPLEMENT E. Monitor Based Subroutines Programming Specification           | E-1                   |

| OPERATING PROCEDURES                                                        |                       |

| I. LOAD THE BOOTSTRAP                                                       | 50-1                  |

| A. Executing Quick Look Command Test                                        | 50-1                  |

|                                                                             | 50.0                  |

| II. LOADING THE MONITOR                                                     | 50-2                  |

| A. First Stop                                                               | 50-2                  |

| <ul><li>B. Second Stop</li><li>C. Third Stop</li></ul>                      | 50-3                  |

| III. SYSTEM INITIAL MESSAGE                                                 | 50-4<br>50 <b>-</b> 4 |

| A. Build Test List                                                          | 50-5                  |

|                                                                             | 200                   |

60182000 M

v

|   | SERVICE ROUTINES                      | MNEMONIC                         | NUMBER        | PAGE  |

|---|---------------------------------------|----------------------------------|---------------|-------|

|   | Printer/Teletype Dump                 | $\mathrm{DM}\mathrm{P}$          | <b>3</b> B    | 100-1 |

|   | Tape to Print Routine                 | LST                              | 3C            | 101-1 |

|   | 3000 Channel Simulator Assembler      | SAS                              | <b>3</b> D    | 102-1 |

|   | SMM Edit Routine                      | $\mathbf{E}\mathbf{D}\mathbf{T}$ | 3E            | 103-1 |

|   | 3000 Channel Simulator Program Update | UD3                              | 2D            | 104-1 |

|   | 1700 Source/6000 TVC Update           | UĐ1                              | 57            | 105-1 |

|   | 1700 Source/6000 BUCAL Update         | UD2                              | 58            | 106-1 |

|   | 1700 MSMS Installation Program        | INS                              | FD            | 107-1 |

|   | 1700 Disk Pack Call-Up Program        | DPC                              | $\mathbf{FC}$ | 108-1 |

|   | Diagnostic Replace Program            | REP                              | $\mathbf{FB}$ | 109-1 |

|   | Punch-A-Deck Program                  | PAD                              | 69            | 110-1 |

| - | INTERNAL TESTS                        |                                  |               |       |

|   | 1700 Command Test                     | COM                              | 1             | 200-1 |

|   | 1700 Memory Test                      | MEM                              | 14            | 201-1 |

|   | 1700 Protect Test                     | RPT                              | 09            | 202-1 |

|   | 1774 System Controller Command Test   | CAR                              | $1\mathrm{B}$ | 204-1 |

|   | 1700 Memory Test                      | MY2                              | 02            | 205-1 |

|   | 1700 Memory Test                      | MY1                              | 12            | 206-1 |

|   | 1700 Command Test                     | CMD                              | 1C            | 207-1 |

|   | EXTERNAL TESTS                        |                                  |               |       |

|   | Paper Tape Equipment                  |                                  |               |       |

|   | 1723 Paper Tape Punch Test            | PTP                              | 03            | 300-1 |

|   | 1721 Paper Tape Reader Test           | PTR                              | 04            | 301-1 |

|   | Printing Equipment                    |                                  |               |       |

|   | 1711/12/13 Teletypewriter Test        | TTY                              | 05            | 350-1 |

|   | 1740/501,1742 Line Printer Test       | LP1                              | 0C            | 351-1 |

|   | FF524-A/1742-120/512 Printer Test     | LP5                              | 23            | 352-1 |

|   | Card Equipment                        |                                  |               |       |

|   | 1729 Card Reader (Lo Speed Package)   | CR1                              | 06            | 400-1 |

|   | 1728/430 Card Reader Punch Test       | CRP                              | 0D            | 401-1 |

|   | 1729-2 Card Reader Test               | CR3                              | 13            | 402-1 |

|   | 1726/405 Card Reader Test             | CR2                              | 17            | 403-1 |

|   |                                       |                                  | -             |       |

$\widehat{\ }$

$\langle \cdot \rangle$

#### Magnetic Tape Equipment

| 1731/601,602,612 Magnetic Tape Test                         | MT1 | 07    | 450-1 |

|-------------------------------------------------------------|-----|-------|-------|

| 1731/601,602,612 Magnetic Tape Test                         | MT2 | 0E    | 451-1 |

| 1732/608,609-1732-2/658,659 Magnetic                        |     |       |       |

| Tape Test                                                   | MT3 | 15    | 452-1 |

| 1731/601,602,612-1732/608,609 Special<br>Magnetic Tape Test | MTS | 1F    | 453-1 |

| 1731,1732/60X Magnetic Tape Test                            | MTX | 4A    | 454-1 |

| 1732/608,609 or 1732-2/615-73/93                            |     |       |       |

| Magnetic Tape Subsystem Test                                | PET | 4B    | 455-1 |

| VOLUME 2                                                    |     |       |       |

| Data Channel                                                |     |       |       |

| 1706 Data Channel Test                                      | BD1 | 0A    | 500-1 |

| 1706/16 Data Channel Test                                   | BD2 | 0F    | 501-1 |

|                                                             |     |       |       |

| Rotating Mass Storage                                       |     |       |       |

| 1738/853/854 Disk Drive Test                                | DP1 | 08    | 550-1 |

| 1739 Cartridge Disk Drive Controller                        | CDD | 78    | 551-1 |

| BG504A/H Drum Controller Diagnostic                         | DRM | 80    | 552-1 |

| 1738 Disk Quick Look Test                                   | DP5 | 84    | 553-1 |

| 1733-1/1738/853,854 and QSE 4730                            | DP3 | 27    | 554-1 |

| 1733-2 Multiple Cartridge Disk Driver<br>Controller         | MDC | 7A    | 555-1 |

|                                                             |     | 1 4 4 | 000 1 |

| Displays                                                    |     |       |       |

| 1745/6-1,210 Display Test                                   | DDC | 40    | 600-1 |

| 1745/6-2,211 Display Test                                   | DDT | 1D    | 601-1 |

| 1700/8000 Data Transfer Buffer Display                      | DTB | 10    | 602-1 |

| 1744/274 Digigraphics Display Test                          | DIG | 4F    | 603-1 |

| 1744/274 Digigraphics Display System                        | DG4 | 6F    | 604-1 |

| Validata Key Entry Station Test                             | KEY | 60    | 605-1 |

| General Purpose Graphics Terminal (GPGT)                    | N/A | N/A   | 610-1 |

| GPGT Troubleshooting Program                                | GT0 | 70    | 611-1 |

| GPGT Command Test                                           | GT1 | 71    | 612-1 |

| GPGT Display Quality Test                                   | GT2 | 72    | 613-1 |

| GPGT Light Pen and Keyboard Test                            | GT3 | 73    | 614-1 |

| GPGT Communications Test                                    | GT4 | 74    | 615-1 |

| GPGT Communications Test (12 Bit Interface)                 | GT5 | 75    | 616-1 |

| GPGT Specification Verification Test                        | GT6 | 76    | 617-1 |

|                                                             |     |       |       |

$\bigcirc$

60182000 M

#### Optical Readers

|   | 1735/915 Optical Character Reader                            | OCR | 35 | 650-1          |

|---|--------------------------------------------------------------|-----|----|----------------|

|   | 935-2 Read Transport Test                                    | OC2 | 52 | 652-1          |

|   | FF406/935 Module Test                                        | OC3 | 53 | 653-1          |

|   | 935 System Test                                              | OC4 | 55 | 654-1          |

|   | FF406/1700 I/O Interface Test                                | BC1 | 54 | . 655-1        |

|   | 1700/FF104/955 System Test                                   | RX1 | 30 | 656 <b>-</b> 1 |

|   | 1700/955 Module Test                                         | RX3 | 33 | 657-1          |

|   | SC17/1700 FR101 MEM/COM/IFP Test                             | BC2 | 56 | 658-1          |

|   | 1700/FR101/955 Transport Test                                | RX4 | 34 | 660-1          |

|   | SC/1700/FR101/FR113 Interface Test                           | BC3 | 59 | 661-1          |

|   | VOLUME 3                                                     |     |    |                |

|   | Communication Equipment                                      |     |    |                |

|   | 1718 Satellite Coupler Test                                  | SC1 | 0B | 700-1          |

|   | 1747/6000 Data Set Controller Test                           | DSC | 11 | 701-1          |

|   | 1747 Data Set Controller Test                                | DS1 | 20 | 702-1          |

|   | 1749 Communications Terminal Test                            | CTC | 43 | 703-1          |

|   | 1748-2 Multiplexer Controller CSPL<br>Communications Adapter | MCC | 48 | 704-1          |

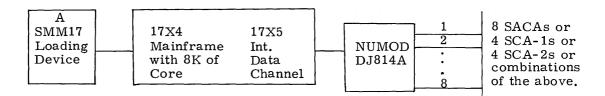

| 0 | DJ814A A/Q Communications Multiplexer<br>(NUMOD)             | AQM | 36 | 706-1          |

|   | Analog/Digital                                               |     |    |                |

|   | Event Counter Subsystem                                      | CTR | 81 | 753-1          |

|   | Digital Input/Output Subsystem                               | DIO | 83 | 754-1          |

|   | IOM Mother Unit Diagnostic                                   | IOM | 90 | 755-1          |

|   | 1500 Series Remote Peripheral Controller<br>Diagnostic       | HOR | 4C | 756-1          |

|   | Miscellaneous                                                |     |    |                |

|   | 10126 Clock Test                                             | CLK | 42 | 850-1          |

|   | QSE TESTS                                                    |     |    |                |

|   | 1700/6600 (QSE 3604/3308) Rover Multi-<br>plexer Test        | RMT | 16 | 900-1          |

|   | 1706 Buffered Data Channel Test<br>W/QSE 3247                | BD3 | 18 | 901-1          |

|   |                                                              |     |    |                |

| 1738/853,854 Dual Access Disk Test                                        | DAD            | 19             | 902-1 |

|---------------------------------------------------------------------------|----------------|----------------|-------|

| 1700/415 Card Punch - QSE 5986                                            | CP1<br>CP2     | 21<br>22       | 903-1 |

| 1738 Disk Pack Test - QSE 1811                                            | DP2            | 25             | 904-1 |

| 1706/1716 Channel Test - QSE 3311                                         | BD4            | 26             | 905-1 |

| 1738/853,854 Disk Pack Test - QSE 4777                                    | DP4            | 28             | 907-1 |

| 1706 Buffered Data Channel Test with<br>Non-Terminating Buffer - QSE 3694 | BD5            | 29             | 908-1 |

| DC215 Data Transfer/405 Card Reader                                       | CR4            | $2 \mathrm{F}$ | 909-1 |

| FFT Algorithm - QSE 3116, 6693                                            | $\mathbf{FFT}$ | 41             | 910-1 |

| 1700/200 Remoter User Terminal<br>Diagnostic - QSE 4557                   | СТИ            | 44             | 911-1 |

| 1700/1749/332/2-103s/Remote Teletype<br>Test - QSE 4557                   | СТТ            | 45             | 912-1 |

| High Speed Data Set Controller Test<br>QSE 8249                           | НСА            | 24             | 913-1 |

| FV219 Plotter Controller Test QSE 6340                                    | PLT            | 39             | 914-1 |

| Operand Bank Test - QSE 7812                                              | Q0B            | 3A             | 915-1 |

| 1745-1746/210 Display Station Test QSE 7698                               | DDD            | 46             | 916-1 |

| DC215 Data Transfer Buffer/415 Card<br>Punch Test (QSE)                   | CP4            | <b>2</b> E     | 917-1 |

| Ponya Parking Lot Data Acquisition<br>and Revenue Control System          | PNY            | 1A             | 918-1 |

| DC216A/3555/512 Printer Test                                              | LPX            | 5A             | 919-1 |

| House of Representatives Vote<br>Station Exerciser                        | VSD            | 4D             | 920-1 |

| QSE 14735 Buffered Data<br>Channel Test                                   | BDL            | 85             | 921-1 |

, ~~. S. 19 , --. . 2 - `` . •  $\sim$ 2 **~** ~ 2018) 21 .  $c \sim \infty$ 25 275 . \_ . . , ```` . • <

``

#### 1718 SATELLITE COUPLER TEST

(SC1A0B Test No. 0B)

#### I. OPERATING INSTRUCTIONS

#### A. RESTRICTIONS

$\bigcirc$

$\bigcirc$

$\bigcirc$

- 1. Test SC1 on the 3000 side should be called first.

- 2. No other 1700 test may be run with this test. This test does not return control to the monitor.

#### B. LOADING PROCEDURE

This program is called as test number 0B via SMM17. The 3000 side is called as SC1 via the SMM3L or SMM3U. The 3000 side is the master and should be called first.

#### C. PARAMETERS

- 1. First stop

- A = Test ID word (0B21)

- Q = Test Stop/Jump parameter Selective stops and jumps

- Bit 0 Parameter word (no typeout occurs)

- Bit 1 End of section (no typeouts)

- Bit 2 End of pass through test (typeout unless bit 8 is set)

- Bit 3 Error stop (typeout unless bit 8 set)

- Bit 4 Repeat conditions

- Bits 5, 6, 7 Not used

- Bit 8 No typeouts

- Bit 9 Return address corresponds to memory location rather than program listing

- Bit 11 Selects shift cable option (Set this bit when using a special data cable which is wired to shift the data cable bits left by 4 bits. When running with this option character mode is disabled.)

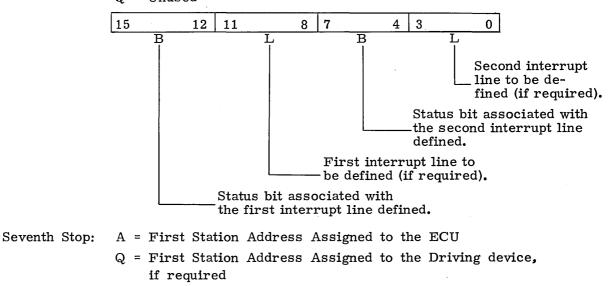

- 2. Second Stop

A = Interrupt line

If bit 0 of the Stop/Jump parameter word is set, a Stop occurs with bit 6 in the A register set. This bit specifies interrupt line 6. If the 1718 uses a different interrupt line, the operator must clear the A register, set the bit corresponding to the correct interrupt line, and run.

Q = 6000 flag

Bit 15 = 1 (6000 system)

Bit 15 = 0 (3000 system)

Sections can be selected only on the master side, the 3000 Series Computer.

D. MESSAGES

1. Normal Messages

- a. SC1A0B, 1718 SATELLITE COUPLER TEST 1A = XXXX, FC = XX. Start of test. Initial address is XXXX, frequency count is XX.

- b. PROTECT STATUS SET

The Protect switch on the 1718 is set according to the status.

c. 0B24 XXXX 00YY ZZZZ

End of test. 0B is the test number. 2 is the number of stops, if any, and the number of pairs of words typed. 4 (bit 2) is the type of stop (End of Test stop) which occurs if bit 2 of the Stop/Jump parameter word is set.

XXXX is the Stop/Jump parameter.

00YY - YY is the pass number.

ZZZZ is the return address. This is relative to the initial address (program listing) of the test unless bit 9 of the Stop/Jump parameter is set, in which case ZZZZ is the memory location.

#### 2. Error Messages

a. Errors

All error typeouts are prefixed by 0BV8 XXXXX 0SYY ZZZZ. 0B is the test number.

V is the number of stops (if any), or the number of pairs of words to be typed.

8 (bit 3) is the type of stop (Error stop) which will occur if bit 3 of the Stop/Jump parameter word is set.

S is the section number.

YY is the error code.

ZZZZ is the return address.

If V = 2, there is no error typeout suffix.

If V = 3, there is a suffix depending on the error code.

- 01 Insufficient core for test

- 02 Equipment address in error. Start over.

- 03 Interrupt line selection in error. Start over.

- 04 Internal reject of status input

- 05 Internal reject of select

- 06 Internal reject of AQ channel input or internal reject of direct input to BDC channel

- 07 Internal reject of AQ channel output or internal reject of direct output from BDC channel

- 08 Not used

- 09 Not used

- 0A Unexpected status.

A = actual status, Q = expected status.

0B - Data error after read.

A = actual data, Q = expected data.

After a data error is found, no more data checking is performed for that input unless bit 4 (repeat conditions) of the Stop/Jump parameter is set.

0C - Alarm interrupt, division A channel parity error

A = Status upon interrupt

Q = Selected interrupts

Bit 2 of Q set - Data

Bit 3 of Q set - End of Operation

Bit 4 of Q set - Alarm

0D - Alarm interrupt, division A computer inactive

A and Q same as for error 0C

0E - Interrupt status bit not set when interrupt occurred

A and Q same as for error 0C

0F - Non-selected interrupt occurred

A and Q same as for error 0C

10 - Flag interrupt did not occur when expected

A = current status

Q = current 1718 mask, 1700 side

11 - Not used

$\bigcirc$

- 12 Non terminating buffer occurred

- 13 End of Operation status set before other computer

Write status is clear during Direct Read

- 14 Not used

- 15 Unexpected number of words read

- A = actual word count

- Q = expected word count

- 16 No End of Operation interrupt during Read

- 17 No End of Operation interrupt during Write.

- 3. Error Stops

Error stops occur if bit 3 of the Stop/Jump parameter is set. Error typeouts occur unless bit 8 of the Stop/Jump parameter is set. At error stops, the contents of the A and Q registers are the same as the typeout.

#### II. DESCRIPTION

- A. GENERAL

- The test is divided into three sections, selectable on the 3000 (master) side. These are Flag/Status section, Write/Read section, Mask/Interrupt section.

- 2. Each operational check is performed first from the 3000 side to the 1700, then from the 1700 to the 3000 side.

- 3. Each operational check is repeated 64 times.

#### **B. DESCRIPTION OF TEST SECTIONS**

1. Preliminary

Because flags 6 and 7 are used for communication, these flags are checked by each side prior to entering Section 1.

- 2. Section 1- Flag/Status Test

- a. Set all flags and check flags.

- b. Set individual flags and check.

- c. Set all but one flag and check.

- d. Clear individual flags and check.

- e. Clear all but one flag and check.

$\bigcirc$

- f. Clear flags, check other computer Write/Read "1's", check for flags clear.

- g. Set flags, check other computer Read/Write "0's", check for all flags set.

- 3. Section 2, Write/Read Test

- a. Check other computer Write/Read.

- b. Check other computer Read/Write.

- c. Read and check data, Write.

- d. Repeat c for lengths of 4, 32, 256 words.

- e. Repeat c and d for each of seven patterns.

- f. Read random lengths of random pattern. Check data.

- g. Repeat f.

In Sections 1 and 2, reads and writes are not in Interrupt mode except for some of the random length reads. The buffered reads of random length are executed in Interrupt mode. Buffered and Direct mode for reads and writes are selected at random. Character and Word mode for reads and writes are selected at random. Reads and writes in section 3 are in Interrupt mode. Alarm and End of Operation interrupts are selected for reads and writes in Interrupt mode. Also, Data interrupt is selected for reads and writes in Interrupt mode, but not in Buffered mode.

- 4. Section 3, Mask/Interrupt Test

- a. Clear all flags, set all masks, expect no interrupts

- b. Set all flags, set individual masks, expect interrupts

- c. Set individual flags, set corresponding masks, expect interrupts.

- d. Set all but one flag, each flag. Set mask for flag not set. Expect no interrupt.

- e. Set individual flags. Set masks except flag set. Expect no interrupts.

- f. Read in Interrupt mode.

- g. Write in Interrupt mode.

#### III, PHYSICAL REQUIREMENTS

- A. SPACE REQUIRED About 2500, locations

- B. TEMPORARY STORAGE Current status of the 1718 is stored at memory location  $11_{16}$ .

60182000 H

- 1. 000 (all "0's")

- 2. FFF (all "1's")

- 3. 000 FFF (all "0's", all "1's" alternate)

- 4. 555 AAA ("0", "1"; "1", "0")

- 5. F11 88F 47C 3E2 (3-bit end-around left shift)

- 6. F19 8CF 67C 3E3 (3-bit end-around left shift)

- 7. F11 0EE 88F 770 (complement, complement-shift) 47C B83 3E2 C1D

- Random (word N+1 = word n + addend, first word random 12-bit number, addend random 12-bit number, 12 bit end-around carry addition used)

- D. TIMING About 4 minutes for all three sections.

#### E. EQUIPMENT CONFIGURATION

- 1. 1704 Computer with 4K memory

- 2. 1705 Interrupt Data Channel

- 3. 1706 Buffer Data Channel (optional)

- 4. 1718 Satellite Coupler

- 5. 3000 Series Computer with one data channel, or 1 0A Computer with a 3681 Data Channel Converter.

- 6. A device for loading program.

- f. Clear flags, check other computer Write/Read "1's", check for flags clear.

- g. Set flags, check other computer Read/Write "0's", check for all flags set.

- 3. Section 2, Write/Read Test

- a. Check other computer Write/Read.

- b. Check other computer Read/Write.

- c. Read and check data, Write.

- d. Repeat c for lengths of 4, 32, 256 words.

- e. Repeat c and d for each of seven patterns.

- f. Read random lengths of random pattern. Check data.

- g. Repeat f.

In Sections 1 and 2, reads and writes are not in Interrupt mode except for some of the random length reads. The buffered reads of random length are executed in Interrupt mode. Buffered and Direct mode for reads and writes are selected at random. Character and Word mode for reads and writes are selected at random. Reads and writes in section 3 are in Interrupt mode. Alarm and End of Operation interrupts are selected for reads and writes in Interrupt mode. Also, Data interrupt is selected for reads and writes in Interrupt mode, but not in Buffered mode.

- 4. Section 3, Mask/Interrupt Test

- a. Clear all flags, set all masks, expect no interrupts

- b. Set all flags, set individual masks, expect interrupts

- c. Set individual flags, set corresponding masks, expect interrupts.

- d. Set all but one flag, each flag. Set mask for flag not set. Expect no interrupt.

- e. Set individual flags. Set masks except flag set. Expect no interrupts.

- f. Read in Interrupt mode.

- g. Write in Interrupt mode.

#### III, PHYSICAL REQUIREMENTS

- A. SPACE REQUIRED About 2500<sub>10</sub> locations

- B. TEMPORARY STORAGE Current status of the 1718 is stored at memory location  $11_{16}$ .

60182000 H

- 1. 000 (all "0's")

- 2. FFF (all "1's")

- 3. 000 FFF (all "0's", all "1's" alternate)

- 4. 555 AAA ("0", "1"; "1", "0")

- 5. F11 88F 47C 3E2 (3-bit end-around left shift)

- 6. F19 8CF 67C 3E3 (3-bit end-around left shift)

- 7. F11 0EE 88F 770 (complement, complement-shift) 47C B83 3E2 C1D

- Random (word N+1 = word n + addend, first word random 12-bit number, addend random 12-bit number, 12 bit end-around carry addition used)

- D. TIMING About 4 minutes for all three sections.

#### E. EQUIPMENT CONFIGURATION

- 1. 1704 Computer with 4K memory

- 2. 1705 Interrupt Data Channel

- 3. 1706 Buffer Data Channel (optional)

- 4. 1718 Satellite Coupler

- 5. 3000 Series Computer with one data channel, or 1 0A Computer with a 3681 Data Channel Converter.

- 6. A device for loading program.

#### DSC 1700 DATA SET CONTROLLER

(DSCA11 Test No. 11)

#### I. OPERATIONAL PROCEDURE

#### A. RESTRICTIONS

0 0 0

0 0 0

- 1. Test must be run with 6X00/6675 Data Set Controller Test ( $6000 \rightarrow RT3$ ).

- 2. Operator must make section selections, and stop/jump options correspond to those of the 6X00 operator.

- 3. Test must be loaded first (it does not return control to SMM after an I/O operation).

- 4. This test MUST be started before the 6675 test is initiated.

#### B. LOADING PROCEDURE

- 1. Loads under SMM17

- 2. Test mnemonic DSC

- 3. Test number 11

#### C. PARAMETERS

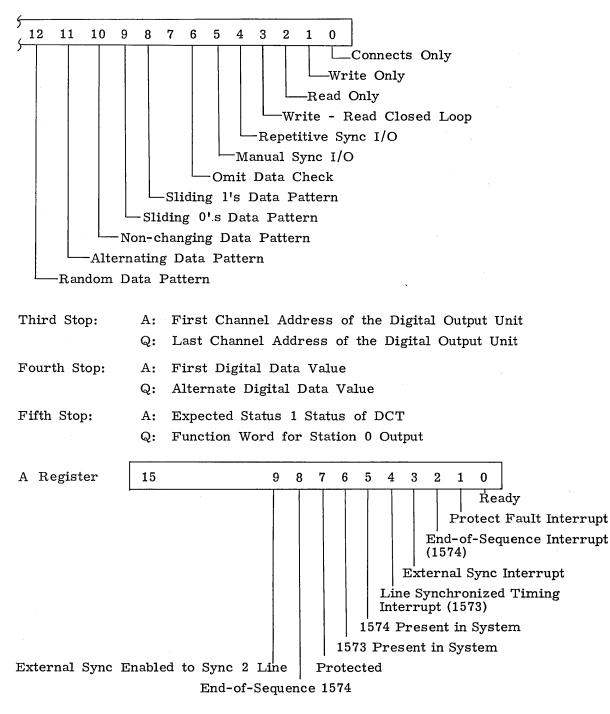

Parameter selection follows standard 1700 SMM format. Bit 11 of the stop/jump parameter word must be set for Input/Output from A mode; if not set, test runs in Buffer mode. The test parameter stops for section selection in A (preset to 000F) and interrupt mask in Q (preset to 0000). To set the interrupt mask parameter, the bit in Q matching the interrupt line should be set to "1" (i.e. bit 5 for interrupt line 5). For a normal run, the Stop at End of Section parameter bit should not be set.

#### D. MESSAGES

1. Normal Messages

DSCA11, 1700 DATA SET CONTROLLER TEST IA = XXXX, FC = XX

60182000 J

This message is typed at the beginning of the test. All other typeouts appear in standard SMM17 format.

#### 2. Error Codes

- 01 Unidentified interrupt

- 02 Either an expected interrupt did not occur or an unexpected interrupt did occur

- A = actual status

- Q = expected status

- 03 Either an expected status is not present or an unexpected status is present

- A = actual status

- Q = expected status

- 04 Data compare error between data sent and data received. If more than  $10_{16}$  errors occur or the errors occur in section 5, then

A = number of errors

Q = pattern number

- 05 Cyclic code from the remote controller does not compare with the cyclic code generated.

- 06 Internal reject on an I/O attempt. (Repeats attempt following error display)

- 07 Interrupt status bit is set following a Clear Interrupt function

- 08 W of the equipment code is not 0, 02, 07, or 0C.

- 09 Sync Word Not Acknowledged status bit is in error. Following a select transmit, the status bit should be set, if not, the program records the error and proceeds to attempt the output. If the status bit is not down, the output is attempted 20<sub>16</sub> more times before the error is reported.

- 13 Insufficient memory for test

- 14 Status after an input operation does not compare with the expected status (see error code 3).

#### II. DESCRIPTION

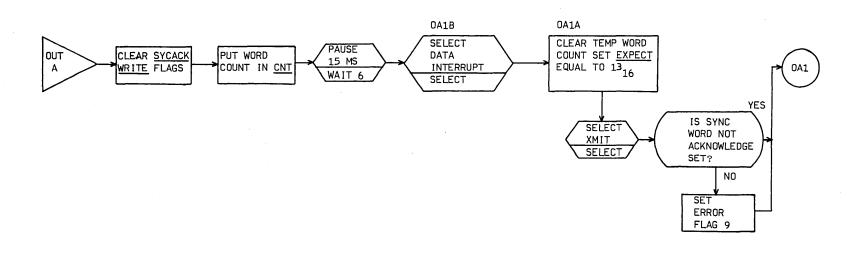

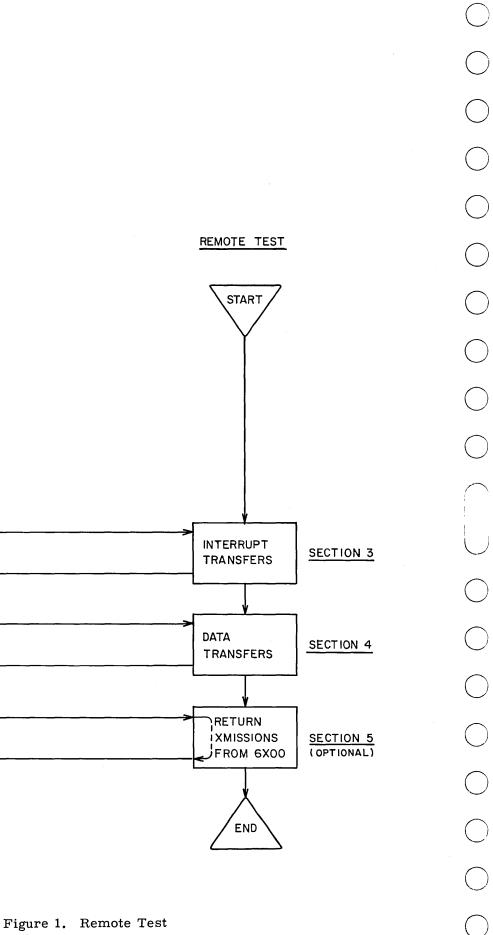

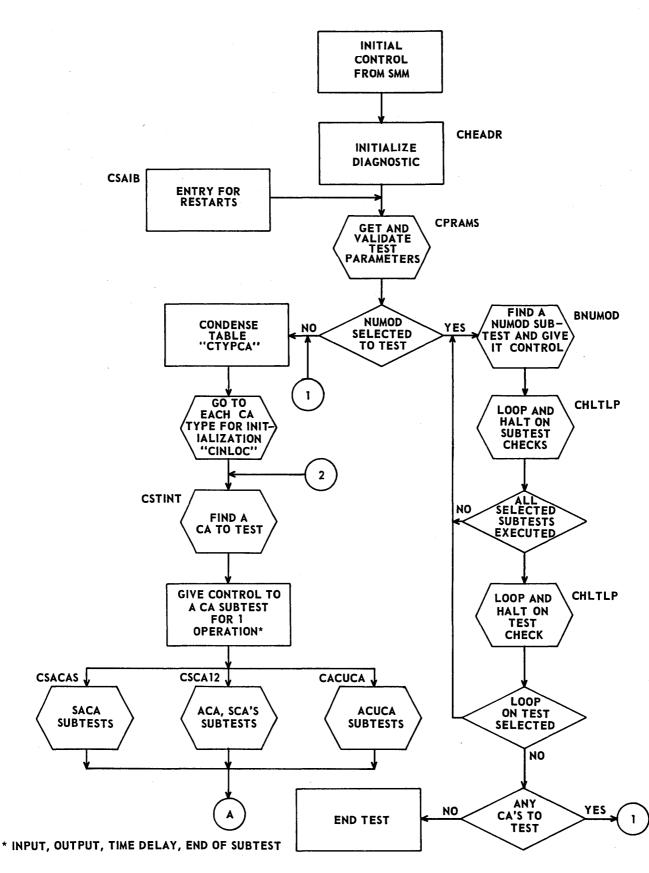

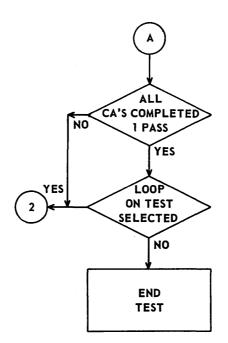

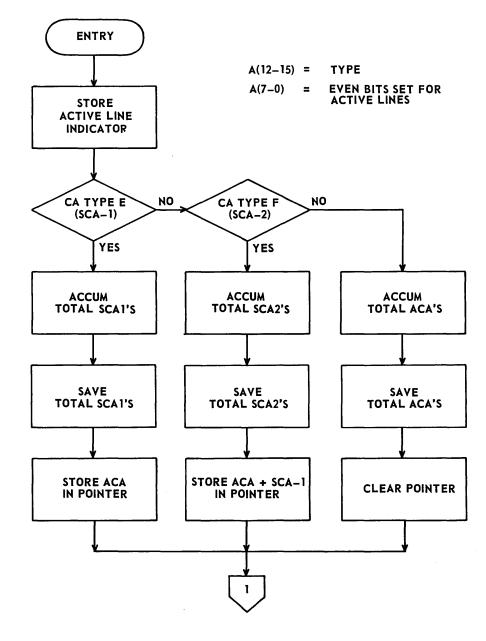

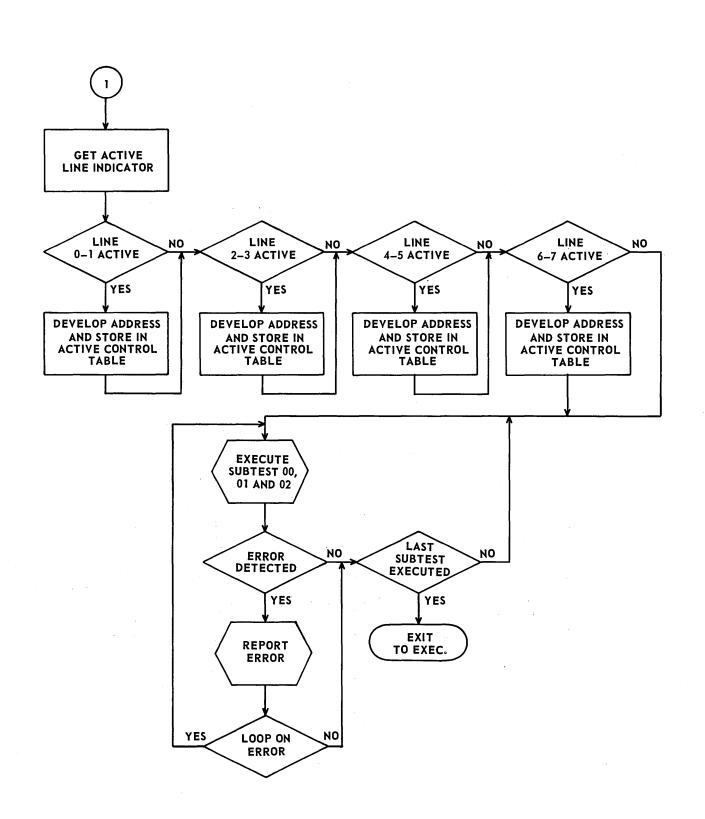

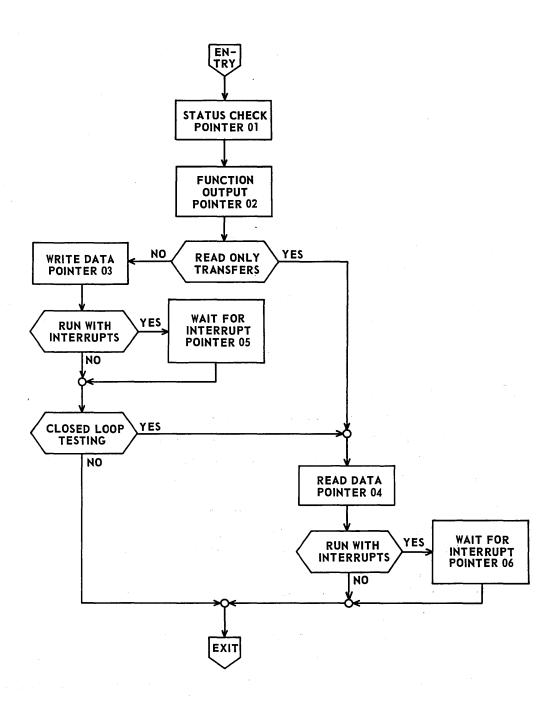

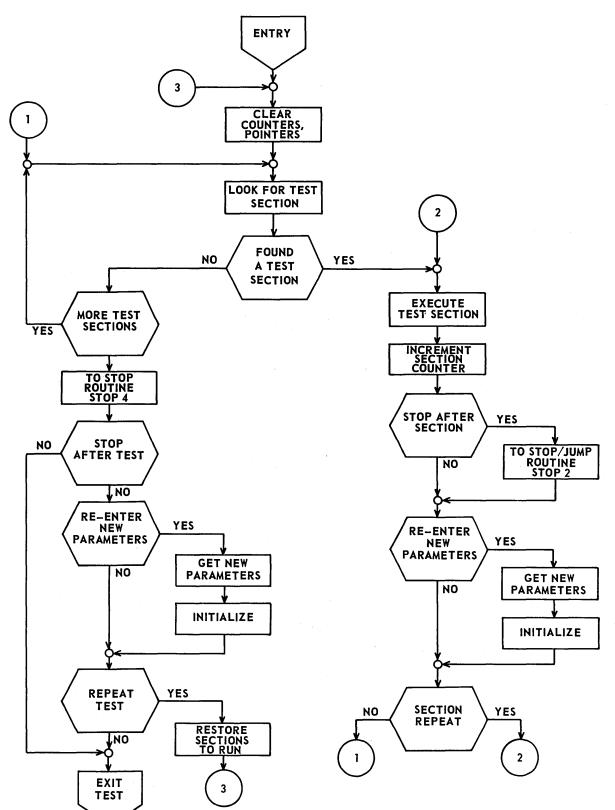

This test is written to interface with 6X00/6675 DATA SET CONTROLLER TEST (SCT) (See Appendix).

During initialization of the test, the program halts for a parameter entry. The lower four bits of the A register hold the section selections (bit 0 for section 3, bit 1 for section 4, etc.). The bit corresponding to the interrupt line number should be set in the Q register (bit 2 for interrupt line 2, etc.). By setting the JUMP switch, each section will stop for a parameter change at the operators option.

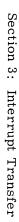

#### A. SECTION 3 - TRANSFER INTERRUPTS

Upon entering this section, the Interrupt Word interrupt is selected and the program loops until the interrupt is received from the 6X00. Upon receiving the interrupt, the section sends the Interrupt Word to the 6X00 and waits for a second interrupt. This exchange is repeated forty-nine more times. Due to the simplicity of this section the Repeat Condition option is not present.

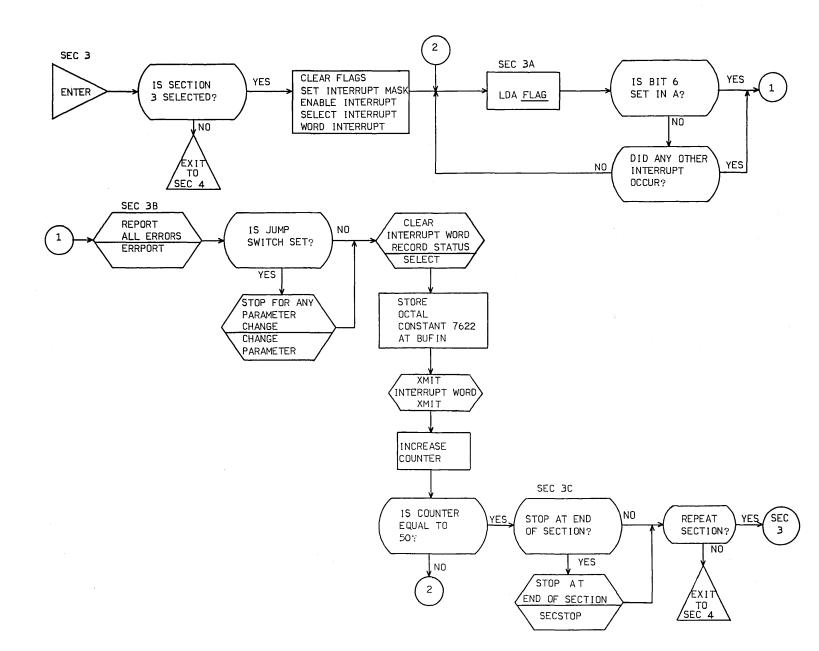

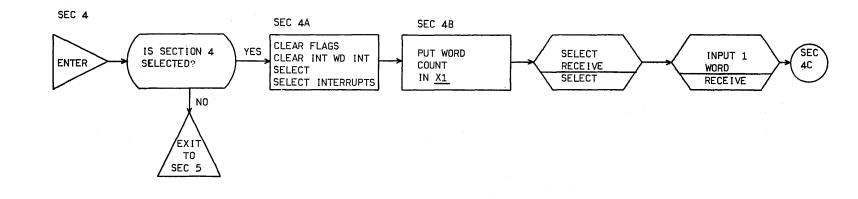

#### B. SECTION 4 - TRANSFER DATA

Upon entering this section, the test puts the controller in Receive mode and waits for the 6X00 test to send the first pattern. Upon receiving the pattern, the data is checked against a generated pattern and produces error code 4 if there is a data compare error. After checking the data, the section returns the data pattern or a one word transmission if the operator wishes to repeat the last pattern transfer and again sets the controller to receive mode. If the test receives a one word transmission from the 6X00, the last pattern is again transmitted to the 6X00. Beginning with pattern thirty-one, an extra word is added to the input to get the cyclic code. This code is checked against one generated by the test from the data pattern. If they do not compare, error 5 is given. Following the cyclic check the test continues with the data check and transmissions. After sending pattern 60, the 6X00 sends a "wasted" pattern and the section gains control to send random data patterns to the 6X00. The 6X00 returns the pattern and they are checked against the generated patterns. Following the check of pattern 74, a "wasted" pattern is sent to the 6X00 and the section is completed.

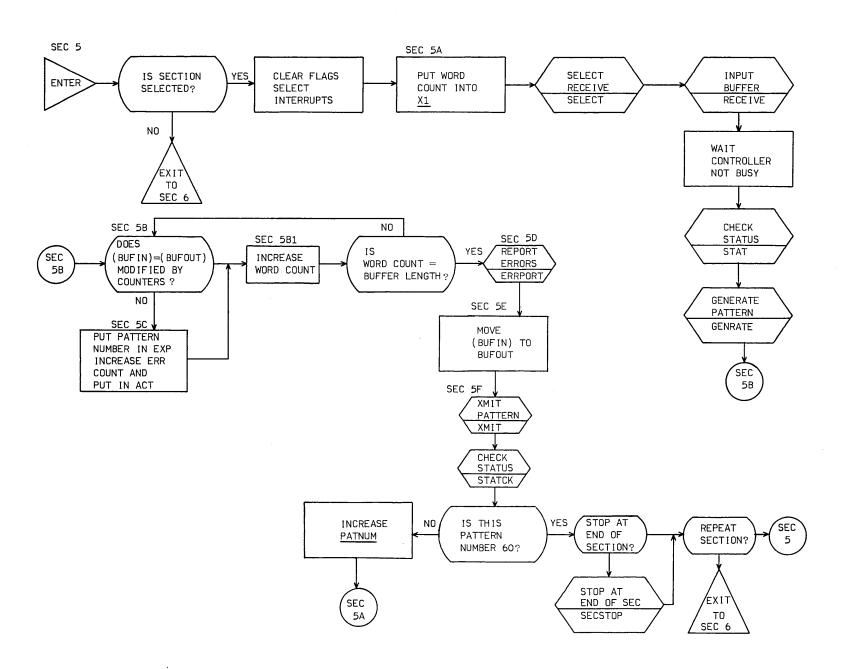

#### C. SECTION 5 - RETURN TRANSMISSION FOR 6X00

Upon entering the section, the controller is set to Receive mode and waits for a 6X00 transmission to the test. When the data is received it is checked against a generated pattern and the data that is received is returned to the 6X00. If a data error occurs, only the pattern number (See Appendix) and the number of errors will be reported.

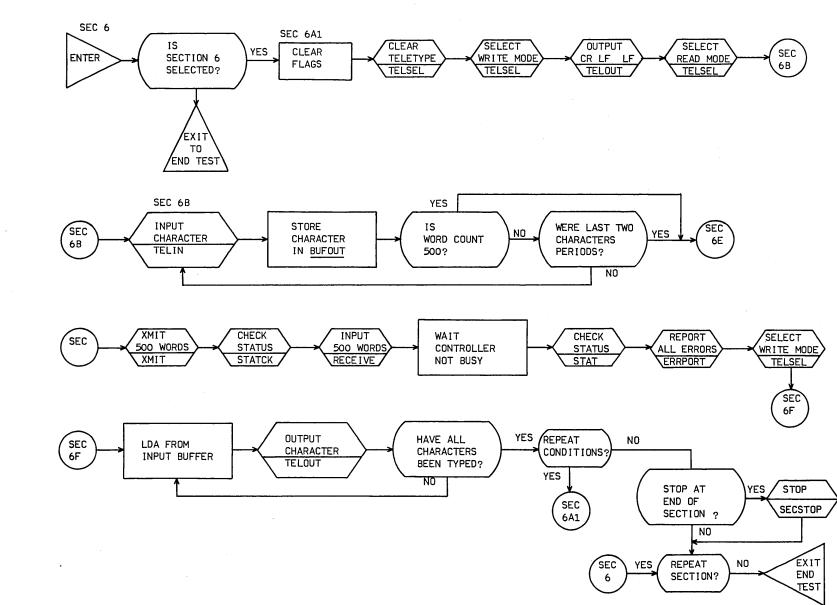

#### D. SECTION 6 - (OPTIONAL) 6X00 DATA TURN AROUND

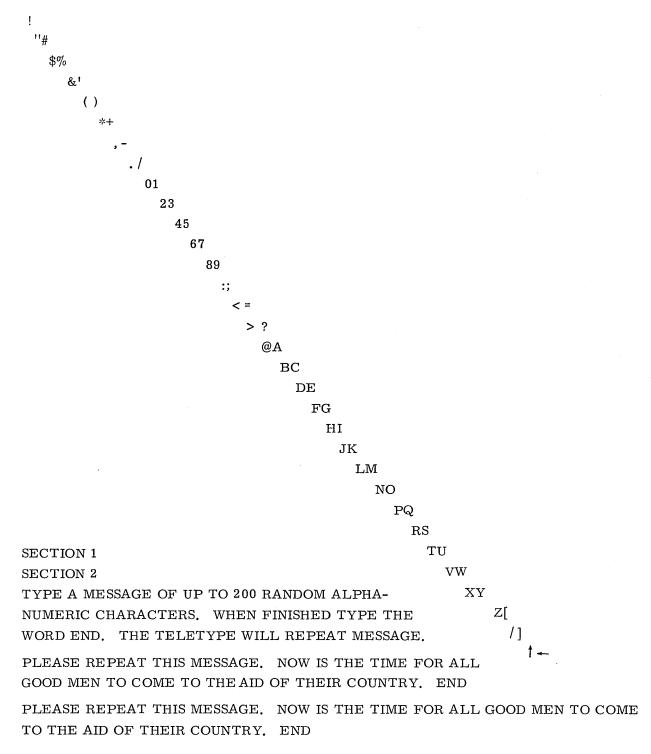

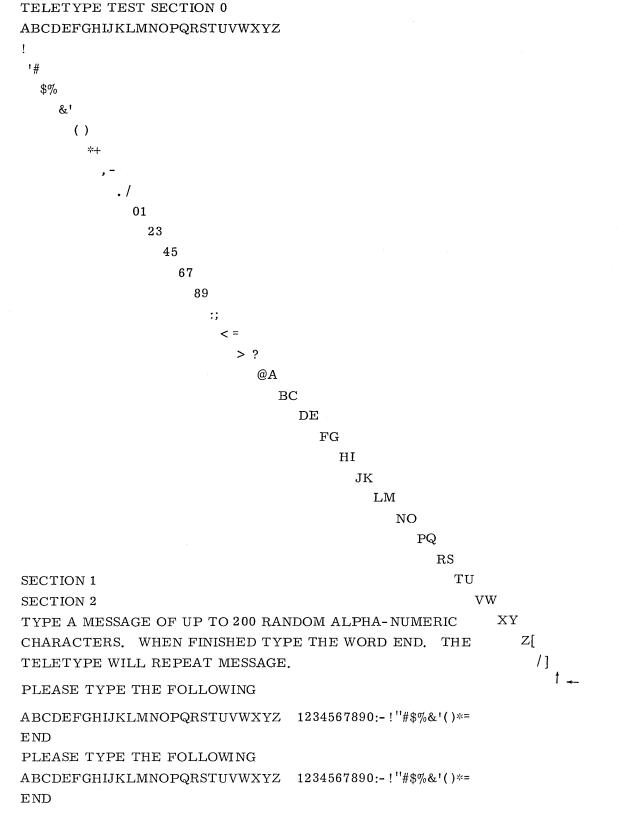

Upon entering this section, the test clears the teletype and a carriage return and two line feed character codes to notify the operator that the test is ready for input. The operator may type any message up to  $320_{10}$  characters. Two consecutive periods ends the input if less than  $320_{10}$  characters are to be transmitted. After two periods or when the count reaches  $320_{10}$ , the data list is send to the 6X00 and returned by the 6X00 to be typed on the teletype.

#### NOTE

For best results, the first two characters of an input should be a carriage return and a line feed.

To type in more than one pattern, the Repeat Conditions option must be selected or Repeat Section option.

E. END TEST

If the Stop At End Of Test option is selected, the test stops for a new parameter entry. A will hold the section selection and Q the interrupt line (this cannot be changed).

#### APPENDIX A

$\bigcirc$

$\bigcirc$

C

$\bigcap$

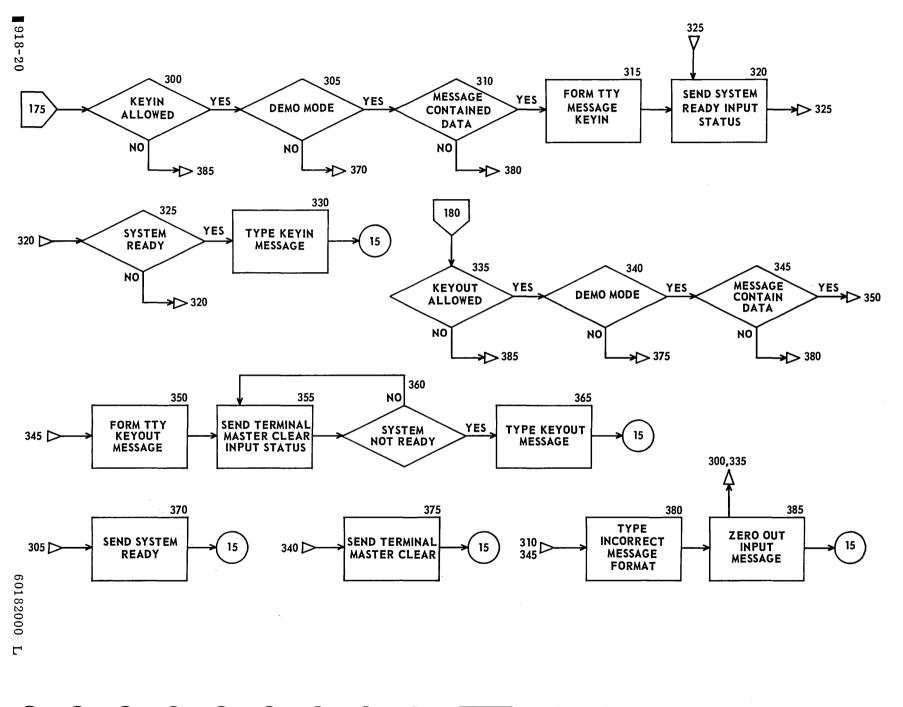

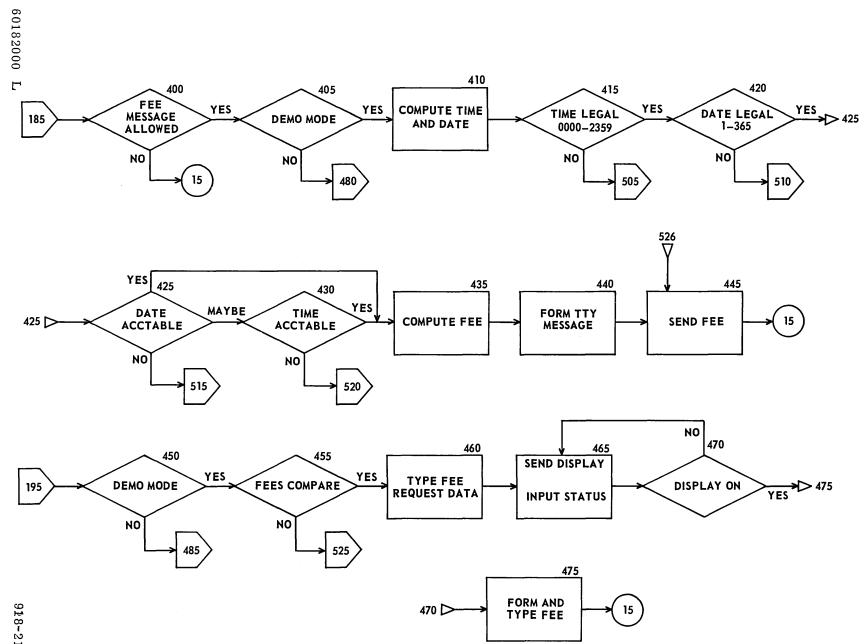

FLOW CHARTS

# C. $\bigcirc$ Ċ $\bigcirc$ $\bigcirc$ $\bigcirc$ $\bigcirc$ $\bigcirc$ $\bigcirc$

60182000 H

701-5

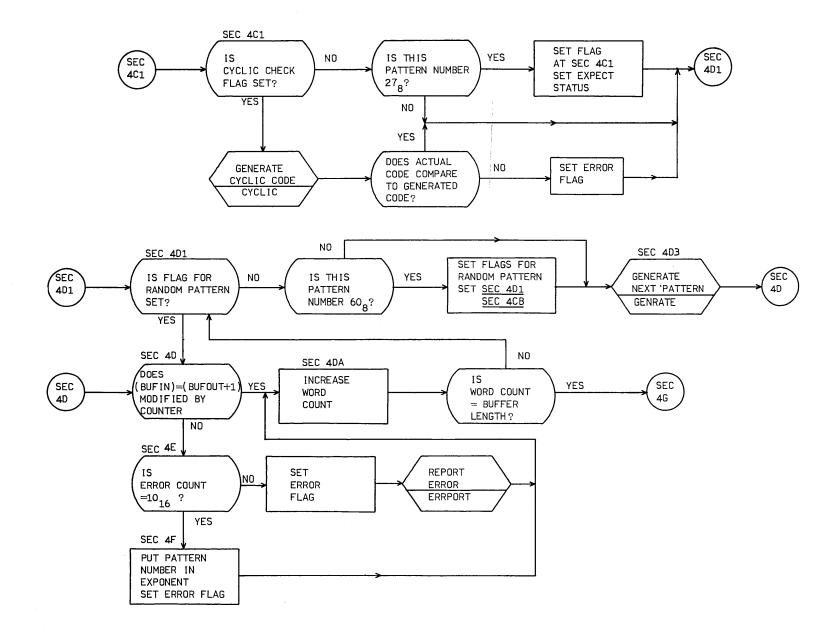

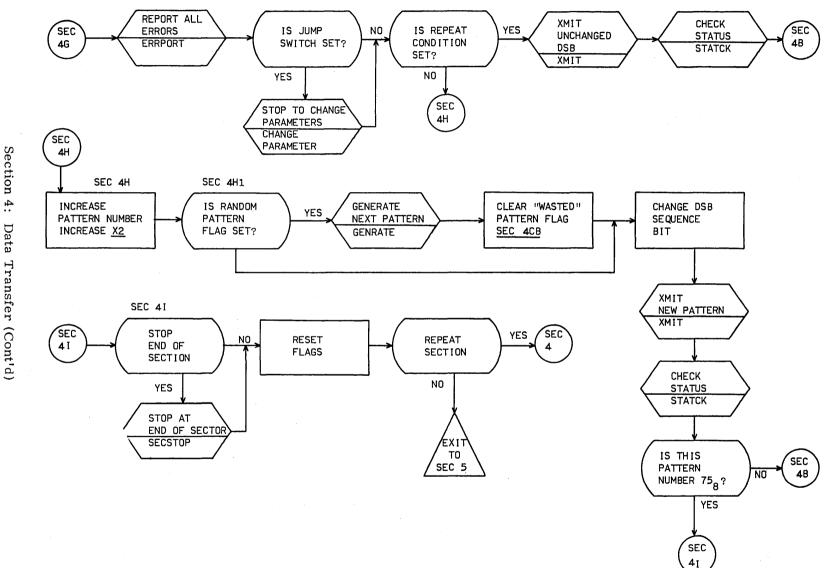

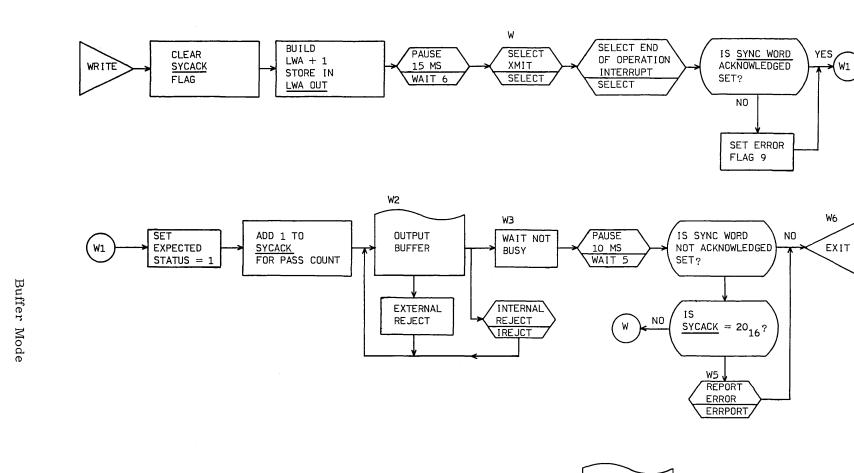

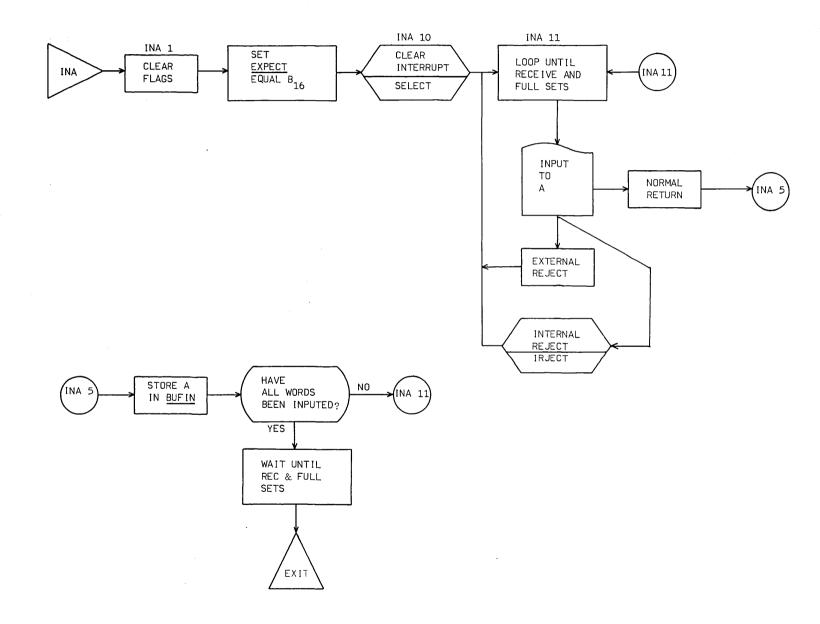

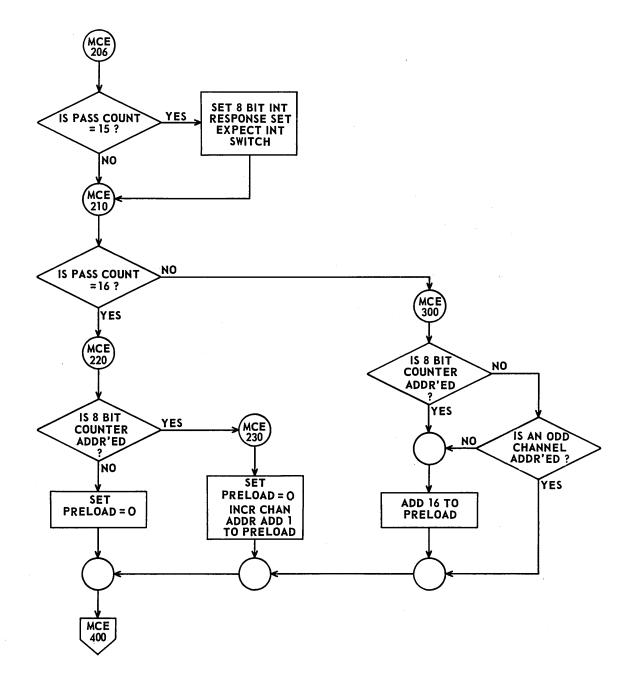

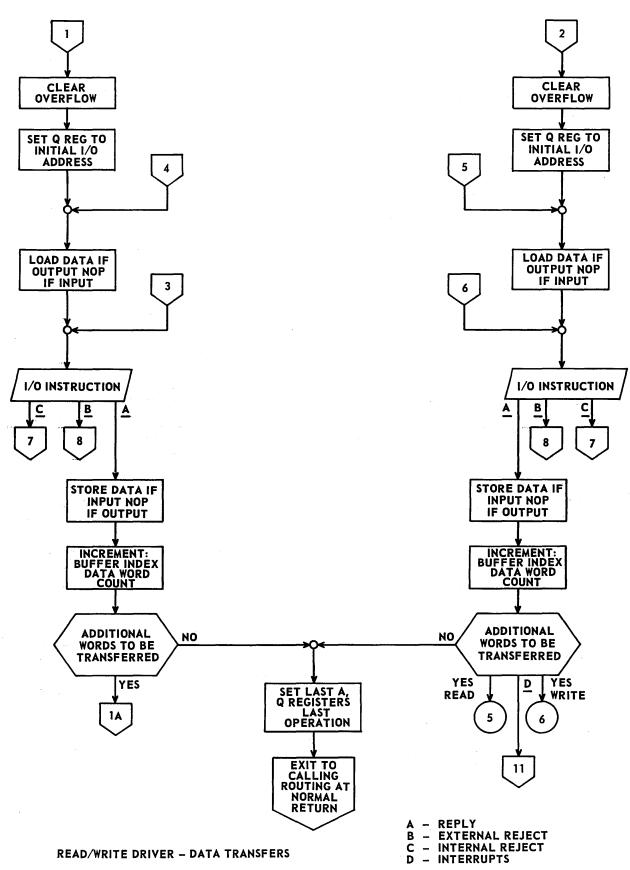

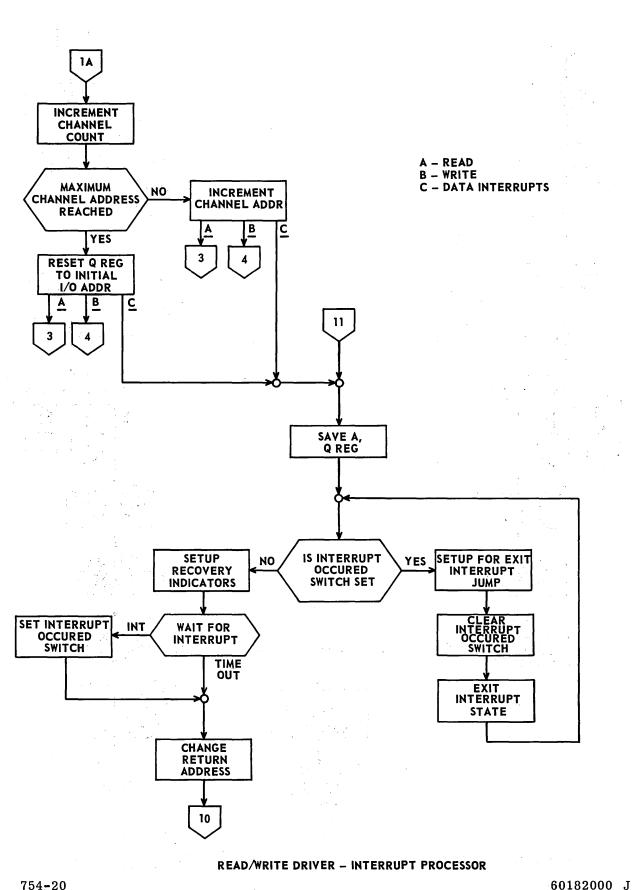

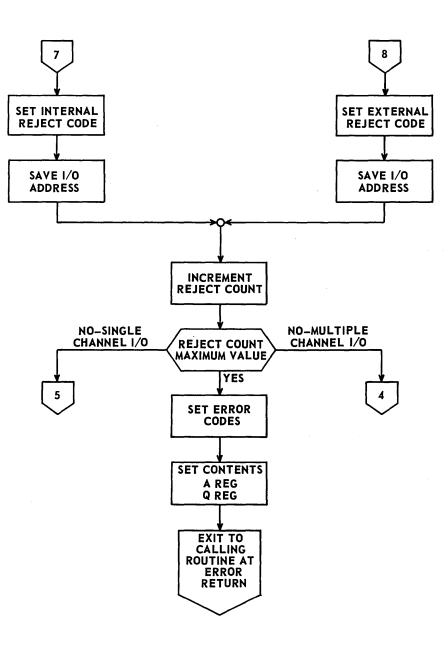

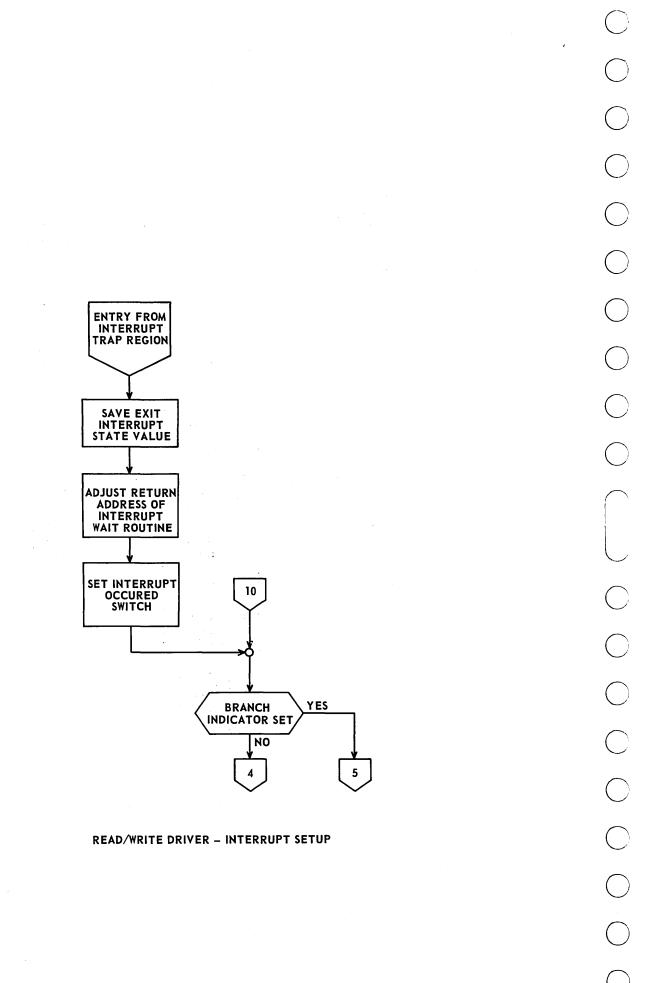

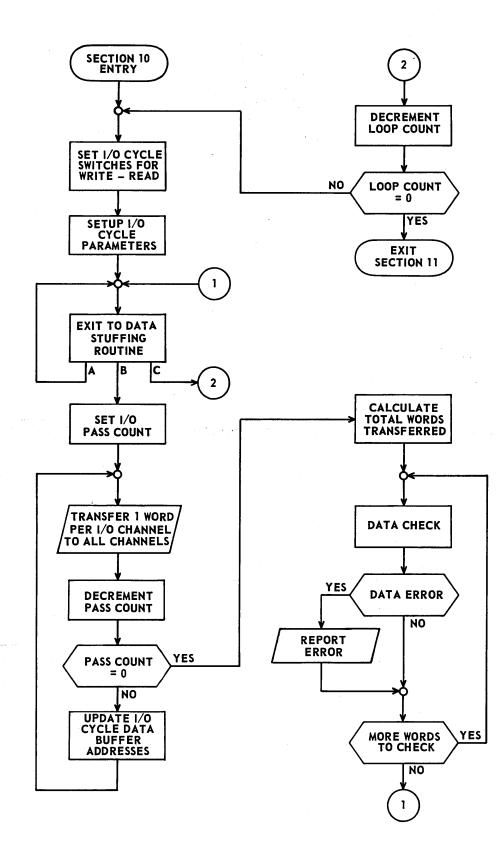

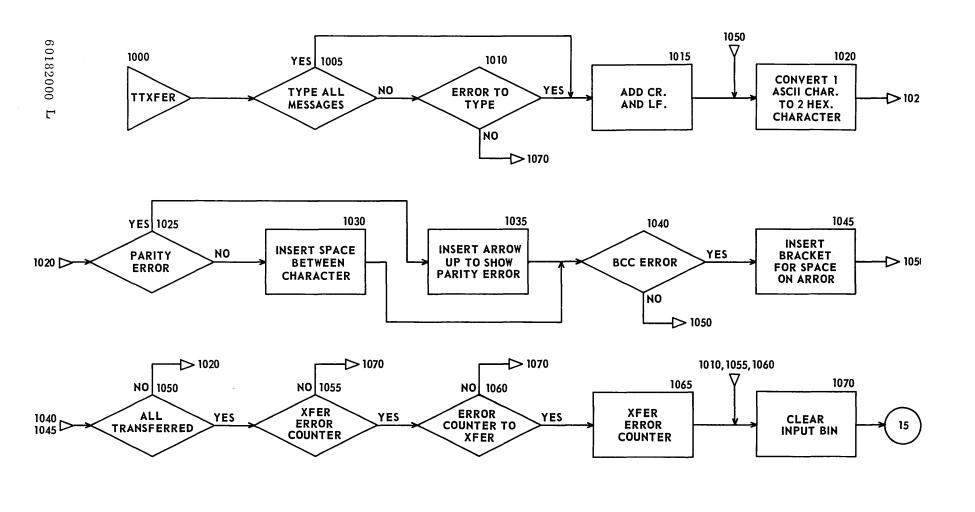

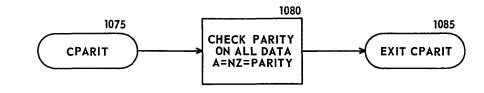

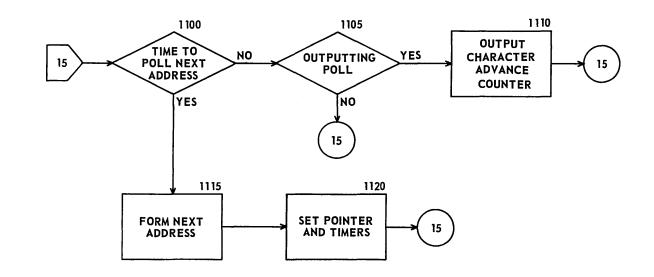

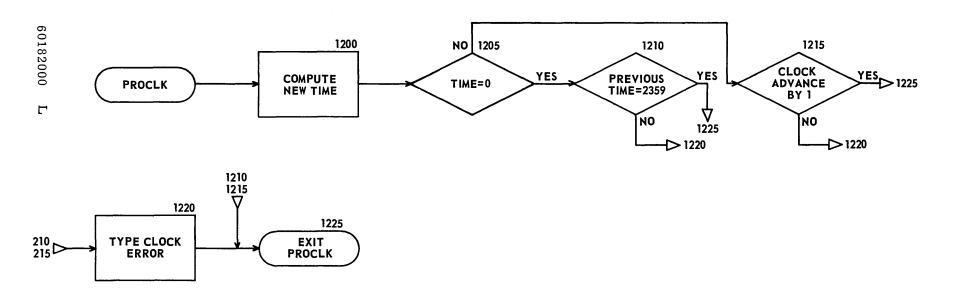

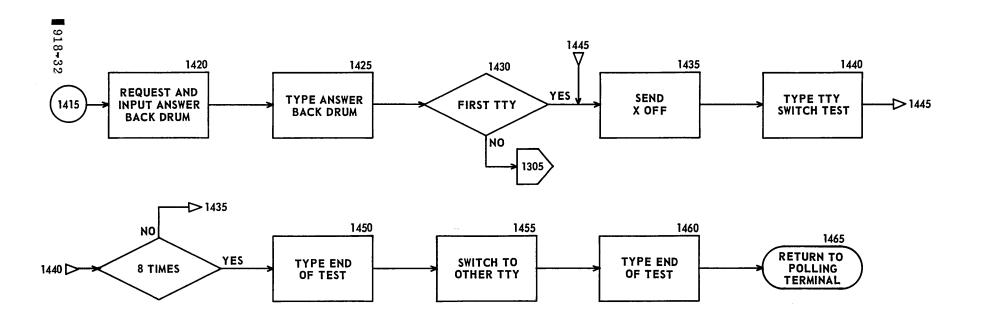

Section 4: Data Transfer

60182000 H

##

60182000 H

Section 4: Data Transfer (Cont'd)

.

7- TOZ

60182000 Η

60182000 H

P-107

60182000 H

1

60182000

Η

11-107

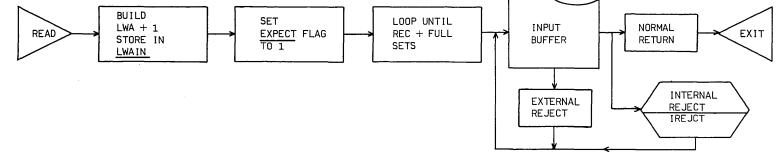

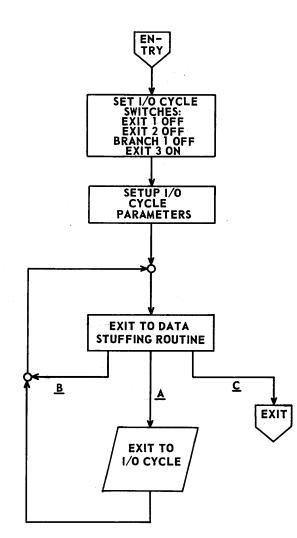

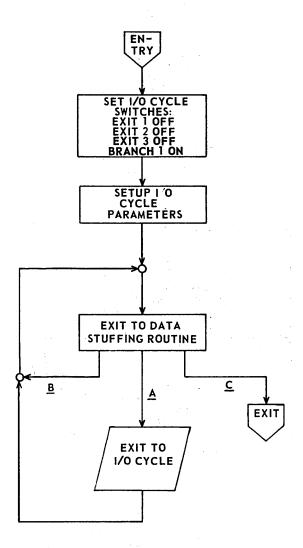

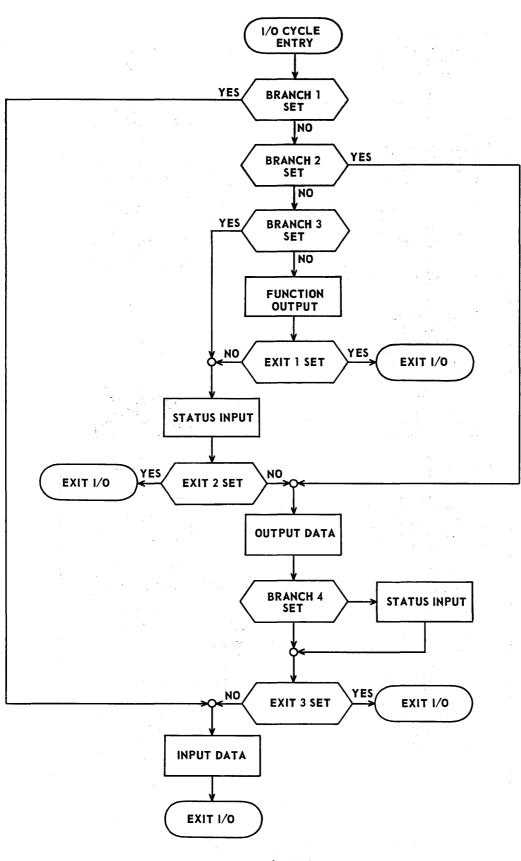

I/O From A Mode

60182000 H

60182000 H

ET-T02

.

#### APPENDIX B

#### SOFTWARE INTERFACING

between

A Remote Computer/Data Set Controller Test

and

The 6X00/6675 Data Set Controller Test (SCT)

#### SOFTWARE INTERFACING

#### between

#### A Remote Computer/Data Set Controller Test

and

#### The 6X00/6675 Data Set Controller Test (SCT)

- A. Establishing Communication With Central (6X00)

- 1. The remote test will be started before the central test.

- 2. After the remote test receives its parameters from its operator and completes its initialization, it should inform its operator that it is waiting for the first interrupt from central.

- 3. The central test will then be started and will complete its initial status checks and optional segments before sending the first interrupt to the remote test.

- 4. After the remote test receives this first interrupt, it should return an interrupt and communication will then be established.

- B. Interrupt Transfers (Section 3)

- 1. Forty-nine more interrupts will be exchanged, with the remote test being the last to send an interrupt.

- 2. If errors occur, they should be reported between the time the remote receives an interrupt and the time it returns the interrupt. The central test will be waiting for an interrupt while the remote test reports its error and communication between the two programs will not be lost. (The central test follows the same procedure for reporting its errors).

- C. Data Transfers (Section 4)

- 1. After sending the last interrupt of section 3, the remote test should place its controller in the Receive mode and wait for pattern number 1 to be transmitted from central.

- 2. After checking pattern number 1 for errors, the remote test should generate pattern 1 and transmit it to the 6X00 and place its controller in Receive mode and wait for pattern number 2.

- a. Just as errors were reported in Section 3, errors in Section 4 should be reported between the time the remote test receives a transmission and the time it returns a transmission.

- b. An exception to C.2. a. is the case when status bits indicate equipment failure (transmission line, data set, etc.). These errors should be reported when they occur and a jump to the test's parameter entry halt should be executed.

- 3. The exchange of patterns will continue until pattern number  $60_8$  is sent by the remote to the 6X00. Up until this time the 6X00 sent the first transmission of each exchange. After this point the remote will send the first transmission of each exchange. This change of control will allow the remote computer to control the contents of the random patterns (pattern numbers  $61_8 74_8$ ).

- a. After the remote sends pattern number  $60_8$  to the 6X00, the 6X00 will send a "wasted" transmission back to the remote to indicate that the remote now has control and should generate and send pattern number  $61_8$  to the 6X00.

- b. The remote program will have control until the  $6\times00$  transmits pattern number 74<sub>8</sub>. At this point the remote program should transmit a "wasted" transmission to the  $6\times00$  to return control to the  $6\times00$  for section 5.

- 4. Patterns Exchanged

- a. The remote program should contain Table 1. Patterns sent to the 6X00 should be generated from this table. (The 6X00 has the same table and generates its patterns from its own table).

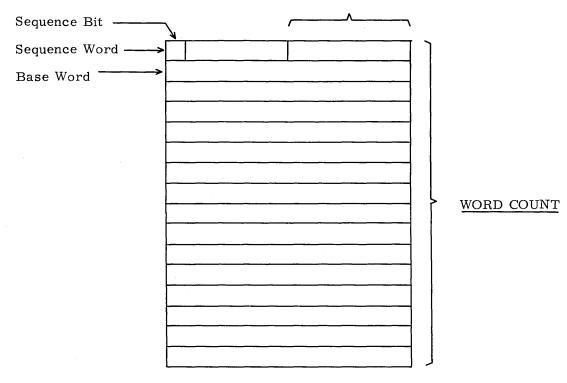

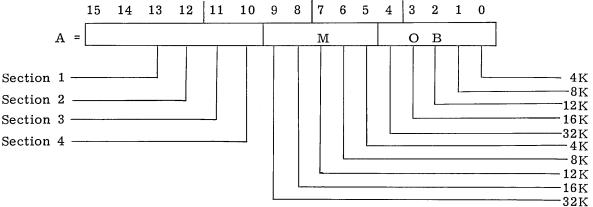

- b. Each three-word entry in the table is used to generate a pattern in the Data Transfer Format (see Figure 2). The Word Count as found in the table entry is the length of the entire transmission (including the sequence word). The Base Word as found in the table will always be the second word of the transmission.

- c. The rest of the pattern will be generated according to bits b, c, d, and e (see Table Entry, Figure 2).

(The pattern number is included in the Data Transfer Format for debugging purposes only. The remote test should not, upon receiving a transmission, use the pattern number received to generate data for comparison).

- d. When the remote has control during the exchange of patterns  $61_8$  to  $74_8$ , the remote determines what the base word will be. The 6X00 program will use the random algorithm to generate its comparison pattern.

- 5. Use of Sequence Bit

$\bigcirc$

- a. Every transmission in section 4 will contain a sequence bit as the first bit transmitted. This bit will allow either the 6X00 or the remote to have a pattern re-transmitted to itself.

- b. The terminology used in following paragraphs regarding the sequence bit technique is the same as that found in the Import/Export Manual (Pub. No. 38707300). All transmissions from the 6X00 to a remote are called Status Transfers. The sequence bit in these transmissions is called the Status Sequence bit or SSB. All transmissions from a remote to the 6X00 are called the Directive Sequence bit or DSB.

#### RANDOM ALGORITHM

The 6X00 Test and the remote test will use the same random algorithm to generate the random patterns  $(61_8 - 74_8)$ . The remote test will pack the base word, generate the pattern, and then transmit the base word and pattern in the Data Transfer Format (see Figure 2). The 6X00 will use the base word transmitted to generate its comparison pattern. The following algorithm is used by the 6X00 test and should be used in the remote test also:

- 1. Load previous word (or base word).

- 2. Add 7 (mode  $2^{12} 1$ ).

- 3. Left Shift 1 End-Around (mod  $2^{12}$  1).

- 4. Store.

6X00/6675 TEST

START

STATUS

CHECKS

OPTIONAL

SEGMENTS

INTERRUPT

TRANSFERS

TRANSFERS

MULTIPLEXED

TRANSFERS

END

DATA

DATA

SECTION I

SECTION 2

SECTION 3

SECTION 4.

SECTION 5

(OPTIONAL)

60182000 H

$\bigcirc$

| COLUMN 1 | COLUMN 2 | COLUMN 3 | COLUMN 4 | COLUMN 5 |

|----------|----------|----------|----------|----------|

| 0101     | 1501     | 3104     | 4502     | 6110     |

| 0002     | 0002     | 0010     | 0032     | 0004     |

| 0001     | 2525     | 2525     | 0001     | XXXX     |

| 0201     | 1601     | 3204     | 4602     | 6210     |

| 0002     | 0004     | 0100     | 0100     | 0006     |

| 7776     | 2525     | 2525     | 7776     | XXXX     |

| 0301     | 1701     | 3304     | 4702     | 6310     |

| 0004     | 0006     | 0500     | 0200     | 0010     |

| 0001     | 5252     | 2525     | 0001     | XXXX     |

| 0401     | 2001     | 3404     | 5002     | 6410     |

| 0004     | 0010     | 0500     | 0400     | 0032     |

| 7776     | 5252     | 0001     | 7776     | XXXX     |

| 0501     | 2101     | 3504     | 5102     | 6510     |

| 0006     | 0032     | 0500     | 0500     | 0100     |

| 7070     | 2525     | 1463     | 0001     | XXXX     |

| 0601     | 2201     | 3604     | 5202     | 6610     |

| 0010     | 0100     | 0500     | 0500     | 0300     |

| 0001     | 5252     | 7070     | 7776     | XXXX     |

| 0701     | 2301     | 3704     | 5302     | 6710     |

| 0010     | 0200     | 0500     | 0500     | 0500     |

| 7776     | 2525     | 7431     | 6314     | XXXX     |

| 1001     | 2401     | 4004     | 5402     | 7010     |

| 0032     | 0300     | 0500     | 0500     | 0500     |

| 0001     | 5252     | 7700     | 7431     | XXXX     |

| 1101     | 2501     | 4104     | 5502     | 7110     |

| 0032     | 0400     | 0500     | 0500     | 0500     |

| 7776     | 2525     | 0101     | 7700     | XXXX     |

| 1201     | 2601     | 4204     | 5602     | 7210     |

| 0100     | 0500     | 0500     | 0500     | 0500     |

| 0001     | 5252     | 6060     | 7070     | XXXX     |

| 1301     | 2701     | 4304     | 5702     | 7310     |

| 0100     | 0500     | 0500     | 0500     | 0500     |

| 7776     | 2525     | 5511     | 1234     | XXXX     |

| 1401     | 3001     | 4404     | 6002     | 7410     |

| 0500     | 0500     | 0500     | 0500     | 0500     |

| 7776     | 5252     | 3232     | 4321     | XXXX     |

# TABLE 1. PATTERNS SENT TO THE 6X00

()

$\bigcirc$

$\bigcap$

| $\bigcirc$ |

|------------|

|            |

| $\bigcirc$ |

|            |

|            |

| $\bigcirc$ |

|            |

|               | Γ | a                | а      | a | a | а | а | $\geq$ | < | b | с | d | е |

|---------------|---|------------------|--------|---|---|---|---|--------|---|---|---|---|---|

| (see Table 1) | 1 | $\triangleright$ | $\sim$ | < | f | f | f | f      | f | f | f | f | f |

|               | L | g                | g      | g | g | g | g | g      | g | g | g | g | g |

a = 6-bit pattern number

b = bit is set if random algorithm is to be used (see Random Algorithm)

c = bit is set if each word is to be the complement of the previous word

d = bit is set if each word is to be left-shifted one from previous word

e = bit is set if entire pattern is fixed (base word)

f = word count of entire transmission

g = base word

## DATA TRANSFER FORMAT

Pattern Number

- c. The 6X00 only changes the state of the SSB. The remote computer only changes the state of the DSB.

- d. The remote program will see the SSB change state on every transmission if the 6X00 does not want the remote to repeat a transmission. If, however, the SSB <u>does not</u> change its state (0 to 1 or 1 to 0), the remote should repeat its last transmission to the 6X00.

- e. The remote should change the state of the DSB on every transmission to the 6X00 unless the remote program wants the 6X00 to repeat its last transmission.

- f. The remote program should expect an SSB of zero on the first transmission it receives from the 6X00 and should therefore have a Ghost 1 bit in its status Sequence Bit Storage location.

- g. The 6X00 will also expect a DSB of zero on the first transmission from the remote program (unless, of course, the remote program wants the first transmission from the 6X00 repeated).

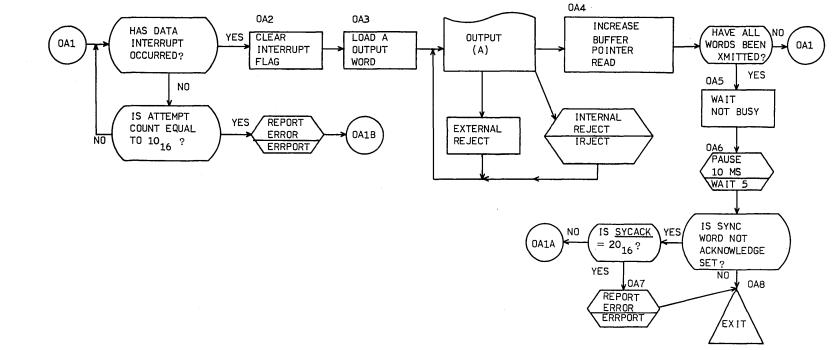

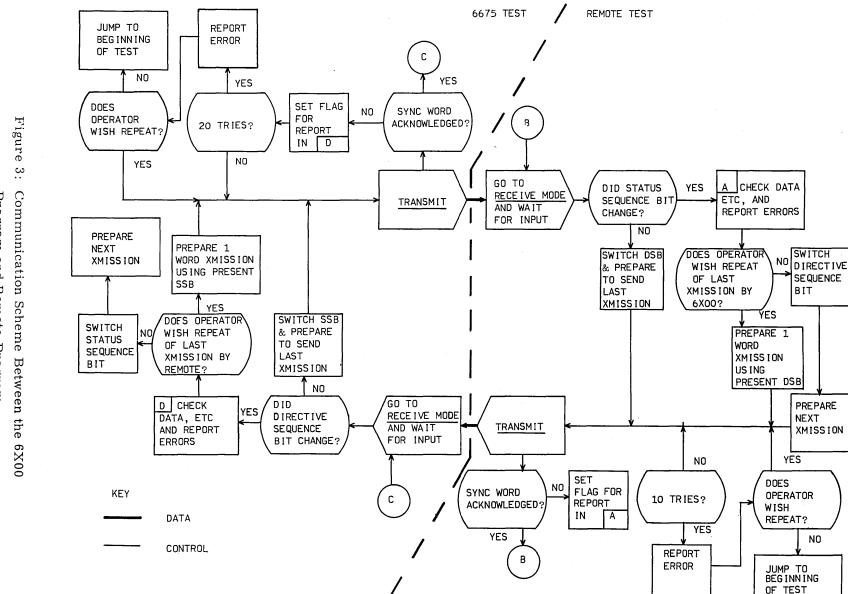

- h. Figure 3 is a flow chart which should help clarify the communication scheme between the 6X00 program and the remote program.

- D. RETURN TRANSMISSIONS FROM 6X00 (SECTION 5)

- 1. This section should not normally run in the test but should be selectable in the parameter entry at the beginning of the test.

- 2. The remote program should go to Receive Mode and expect a transmission of pattern number 1 from the 6X00.

- After the receive operation is complete, the remote program should delay for 100 milliseconds. This will allow the 6X00 program time to set up for a multiplexed receive operation.

- 4. When the delay runs out, the remote program should send the pattern <u>as it</u> was received from the 6X00, back to the 6X00 and go into Receive Mode for the next pattern.

- 5. This process will continue until all of the patterns  $(60_8)$  have been exchanged.

- 6. Equipment Failure errors and Sync Word Not Acknowledged errors should be reported as they occur.

- 7. If any data errors occur, the total number and the <u>pattern number</u> should be reported before returning the transmission to the 6X00.

Program and Remote Program

60182000 Ξ

207-55

## 1747 DATA SET CONTROLLER TEST

(DS1020 Test No. 20)

## I. GENERAL

0000000

$\bigcirc$

This specification is for a 1747 DSC (Data Set Controller) unit diagnostic test that is designed to operate under Control Data's 1700 Maintenance Monitor System. Sufficient information, necessary to the specific operation and interpretation of the diagnostic, is contained within this specification and the SMM17 Reference Manual. The installation and operation of the diagnostic is in accordance with the standard procedures as defined in the SMM17 Reference Manual.

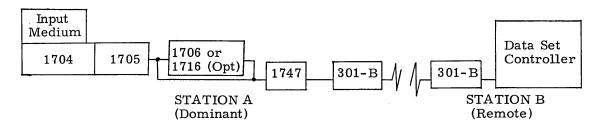

## II. EQUIPMENT

Equipment necessary to the complete operation of the test:

- A. One 1704 Computer

- B. One 1705 Interrupt Data Channel

- C. One 1712/13 Teletype\*

- D. The following input media:

- 1. 1731 Magnetic Tape Controller

- 2. 1712/13 Teletype\*

- 3. 6673

- 4. 6674

\*The teletype is not required if the test is executed with the prestored test selection parameter.

60182000 J

702-l

ALC:N

E. Two 1747 DSC's or one 1747 and one of the following DSC's:

- 1. 8529B

- 2. 3275C

- 3. 6673

- 4. 6674

F. An interconnecting wideband common-carrier facility with two 301-B Data Sets.

As optional equipment, the 1747 DSC may be interfaced with the 1706 or 1716 Data Channel. Capabilities are provided for exercising the 1706 or 1716 through the use of converter codes that are generated by the diagnostic.

#### III. SOFTWARE DEPENDENCIES

- A. The 1747 diagnostic is designed to operate under Control Data's 1700 Maintenance Monitor System (SMM17).

- B. Interface between the system and the diagnostic is through programs that are contained within SMM17.

- C. All tables required by the diagnostic are contained internally within SMM17 and the 1747 diagnostic program.

## IV. LIMITATIONS

- A. As required by the SMM17 test specifications, core residence for the test does not exceed 2500 decimal locations.

- B. Only one 1747 DSC is software tested per each execution of the diagnostic. The diagnostic makes no attempts to concurrently test more than one DSC at the dominant station, nor are any attempts made to diagnose troubles at the remote station. Faults at the remote station must be diagnosed by a diagnostic that is compatible with the remote station or by an attendant who is able to observe and/or scope the remote DSC while it is being exercised by the 1747 diagnostic.

- C. Although only one computer system is required to run the test (the 1700 at Station A; see Par. II), coordination is required between Station A and Station B. While the diagnostic is executed, the operator at Station A and Station B. While the diagnostic is executed, the operator at Station A must coordinate with Station B the positioning of test switches at the remote DSC.

- D. Message transmission and cyclic generation testing is limited to the use of oneword data buffers. This is a hardware restriction imposed by the remote DSC's capability of receiving and transmitting fixed-length records that consist of:

- a sync word one data word a cyclic word a space word

The dominant station is further limited because it cannot verify (self-check) its own transmissions by means of a hardware echoing technique. Reception at the dominant station is also limited because the remote DSC is capable of transmitting only nine distinct patterns:

One 4257<sub>8</sub> (Sync word) four data patterns four cyclic code words (generated from the four data patterns)

E. Test section 3 requires an extensive amount of manual intervention. If section 3 is selected, the 1747 DSC test should be run alone.

|    | The Course of the later is a set |                |              |           |                        |

|----|----------------------------------|----------------|--------------|-----------|------------------------|

| F. | Before the diagnosti             | c is executed, | DSC switches | should be | positioned as follows: |

| Local DSC Switches |                     | Position                               |

|--------------------|---------------------|----------------------------------------|

| 1.                 | POWER               | ON                                     |

| 2.                 | TRANSMIT TEST       | OFF                                    |

| 3.                 | RECEIVE TEST        | OFF                                    |

| 4.                 | PROTECT             | UNPROTECTED                            |

| Rea                | mote DSC Switches   | Position                               |

| 1.                 | POWER               | ON                                     |

| 2.                 | TRANSMIT TEST       | Any position except the INTERRUPT word |

| 3.                 | RECEIVE TEST        | Any position                           |

| 4.                 | PROTECT (if a 1747) | Any position                           |

| 5.                 | SYNC WORD LENGTH    | 12                                     |

| 6.                 | INTERRUPT WORD      | 7622                                   |

|                    | (if an 8529-B)      |                                        |

## V. OPERATING INSTRUCTIONS

## A. LOADING PROCEDURE

- 1. The test is loaded under the control of the 1700 System Maintenance Monitor (SMM17). Loading procedures are as explained in SMM17 for an external test under SMM17.

- 2. The calling sequence is as specified by SMM17 for an external test. The test number is 20.

#### B. PARAMETERS

- 1. If Bit 0 of the Stop/Jump word is not set, the test is run using prestored parameters. The prestored parameters assume the following:

- a. The 1747 is not connected to a 1706 or 1716. All I/O is through the AQ channel and test sections 3 through 8 are not executed.

- b. All 1747 interrupts are received on interrupt line number 2.

- c. The 1747 is designated as equipment number 2.

<u>Note:</u> If the prestored parameters do not fit a particular site's configuration, they may be changed by following the procedures in the SMM17 Edit Routine.

2. If Bit 0 of the Stop/Jump word is set, the program makes three stops for test parameter display and/or entry.

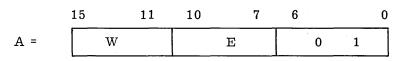

First Stop

Displays the identification word in a (2031) and the Stop/Jump word in Q. The overflow indicator is lit for this stop.

Second Stop

The W field (pre-stored value of 0) is used to identify a 1706 or 1716 data channel. This field is to be changed by the operator only if a 1706 or 1716 is interfaced with the 1747. Change W to equal:

00010 - for 1706/16 number 1 00111 - for 1706/16 number 2 01100 - for 1706/16 number 3 The E field (pre-stored value of 2) should contain a value that is equal to the equipment switch setting of the 1747 to be tested.

Bits 11 thru 0 (pre-stored to all 0's) may be used by the operator to enter a special test pattern. This pattern is used as transmission data by sections 4 and 8.

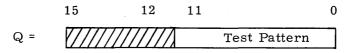

Third Stop

$\bigcirc$

$\bigcap$

Bits 8 thru 0 (pre-stored value = 0007; i.e., only test sections 0, 1, and 2 are preselected) are the section select bits. A set bit in the nth bit position selects test section n; if all bits are set, all the test sections are selected.

|     | 15                  | 0 |

|-----|---------------------|---|

| Q = | Interrupt Line Mask |   |

A single bit set in this mask designates the interrupt line for the 1747. Only one bit is set in this word. Bit position n designates interrupt line n. The pre-stored value in this word designates interrupt line 2.

## C. SELECTIVE SKIP AND STOP SETTINGS

- 1. The STOP switch must be set for running SMM17.

- 2. The SKIP switch, when set, causes the Stop/Jump word to be displayed in the Q register during the first stop in any series of stops.

#### D. CONSOLE PROTECT SWITCH SETTING

Set the console protect switch to UNPROTECTED.

#### E. MESSAGES

No typeouts occur if Bit 8 of the Stop/Jump parameter is set.

- 1. Typeouts or Alarms

- a. Normal Program Display

- 1) Test identification typeout at start of test

DS1020, 1747 DSC TEST IA = XXXX, FC = XX (XXXX = Starting address of the test)

(XX = Frequency count)

60182000 J

,

2) Request typeouts for operator intervention.

See the description of test section 3 in this document for a list of typical request typeouts.

3) End of test typeout

A Q A Q 2024 Stop/Jump Pass Number Return Address Word

b. Error Display

Errors are displayed according to the format prescribed by SMM17:

STOPS 1 and 2  $\,$

| А           | Q         | А              | Q       |

|-------------|-----------|----------------|---------|

| Information | Stop/Jump | Section Number | Return  |

| Word        | Parameter | and Error Code | Address |

| ADDITIONAL  | STOPS     |                |         |

| А           | Q         | . А            | Q       |

One or more additional stops are made to display information related to the specific error.

2. Error Codes

An error code is displayed in the lower two digits of the A register on the second stop of all error-display sequences. A description of the error codes used and the information displayed during the additional stops follows:

| 01 Tu comment de stansmer et                          | the way and and The way way will                              |

|-------------------------------------------------------|---------------------------------------------------------------|

| -                                                     | ter was entered.  The program will<br>er stop when restarted. |

| 02 External reject on inpu<br>Current test section is | -                                                             |

| A = 0000 or 1706 statu<br>Q = 1747 address code       | s if reject was caused by 1706                                |

| 03 Internal reject on inpu<br>Current test section is | •                                                             |

| A = 0000 or 1706 statu<br>Q = 1747 address code       | s if reject was caused by 1706                                |

| Error Code (Cont'd) | Meaning                                                                                                                                  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 04                  | Unexpected external reject on output function attempt                                                                                    |

|                     | <ul> <li>A = Rejected function code</li> <li>Q = 1747 address code</li> <li>A = 1747 status prior to output</li> <li>Q = 0000</li> </ul> |

| 05                  | Unexpected internal reject on output function attempt                                                                                    |

| · · · ·             | A = Rejected function code<br>Q = 1747 address code<br>A = 1747 status prior to output<br>Q = 0000                                       |

| 06                  | 1747 is in the test mode                                                                                                                 |

|                     | A = Status $Q = 0000$                                                                                                                    |

| 07                  | 1747 is not Ready<br>Control is returned to SMM until DSC is made Ready                                                                  |

|                     | A = Status $Q = 0000$                                                                                                                    |

| 08                  | Unexpected alarm interrupt<br>Current test section is aborted after display                                                              |

|                     | A = Status<br>Q = Insignificant value                                                                                                    |

| 09                  | Data interrupt expected but not received<br>Current test section is aborted after display                                                |

|                     | A = Status<br>Q = Insignificant                                                                                                          |

| <b>0.</b>           | EOP interrupt expected but not received<br>Current test section is aborted after display                                                 |

|                     | A = Status<br>Q = Insignificant value                                                                                                    |

|                     |                                                                                                                                          |

| Error Code (Cont'd) | Meaning                                                                                                                                                  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0B                  | Interrupt word interrupt expected but not received<br>Current test section is aborted after display                                                      |

|                     | A = Status<br>Q = Insignificant value                                                                                                                    |

| 0C                  | External reject expected but not received                                                                                                                |

|                     | A = Contents of A when output was attempted<br>Q = 1747 address code<br>A = 1747 status prior to output<br>Q = 1747 status after functioning             |

| 0D                  | Internal reject expected but not received                                                                                                                |

|                     | A = Contents of A when output was attempted<br>Q = 1747 address code<br>A = 1747 status prior to output<br>Q = 1747 status after functioning             |

| <b>0</b> E          | Cyclic error forced but no status                                                                                                                        |

|                     | A = Status<br>Q = Insignificant value                                                                                                                    |

| 0F                  | A = Status<br>Q = Insignificant value                                                                                                                    |

| 10                  | Unexpected cyclic error                                                                                                                                  |

|                     | A = Status<br>Q = Insignificant value                                                                                                                    |

| 11                  | Unexpected status                                                                                                                                        |

|                     | A = Actual status<br>Q = Expected status                                                                                                                 |

| 12                  | Unexpected status after function select                                                                                                                  |

|                     | <ul> <li>A = Actual status</li> <li>Q = Expected status</li> <li>A = Function code selected</li> <li>Q = 1747 status prior to function select</li> </ul> |

| rror Code (Cont'd) | Meaning                                                                                                                                                                                                                                                                                    |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13*                | External reject on attempt to input 1706 status<br>Current test section is aborted after display                                                                                                                                                                                           |

|                    | A = 0000<br>Q = Contents of Q when status input was attempted                                                                                                                                                                                                                              |

| 14*                | Internal reject on attempt to input 1706 status<br>Current test section is aborted after display                                                                                                                                                                                           |

|                    | <ul> <li>A = 0000</li> <li>Q = Contents of Q when status input was attempted. 1706<br/>status input is attempted only if a reject was received<br/>from a 1747 status input attempt and the W field of the<br/>address code indicates that the 1747 is connected to a<br/>1706.</li> </ul> |

| 15                 | External reject on clear interrupt attempt while in the interrupt state. This error is fatal to this test and may affect the operation of other tests by destroying their return links to SMM.                                                                                             |

|                    | <ul> <li>A = Rejected function code</li> <li>Q = 1747 address code</li> <li>A = 1747 status prior to output</li> <li>Q = 0000</li> </ul>                                                                                                                                                   |

| 16                 | Internal reject on clear interrupt attempt while in the<br>interrupt state. This error is fatal to this test and may<br>affect the operation of other tests by destroying their<br>return links to SMM.                                                                                    |

|                    | <ul> <li>A = Rejected function code</li> <li>Q = 1747 address code</li> <li>A = 1747 status prior to output</li> <li>Q = 0000</li> </ul>                                                                                                                                                   |

| 17                 | Interrupt occurred, but interrupt status bit not set                                                                                                                                                                                                                                       |

|                    | A = Status                                                                                                                                                                                                                                                                                 |

| Error Code (Cont'd) | Meaning                                                                                                                                    |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 18                  | Alarm interrupt expected, but not received. Current test section is aborted after display.                                                 |

|                     | A = Status<br>Q = Insignificant value                                                                                                      |

| 19                  | Unexpected data interrupt<br>Current test section is aborted after display                                                                 |

|                     | A = Status<br>Q = Insignificant value                                                                                                      |

| 1A                  | Unexpected end of operation interrupt.<br>Current test section is aborted after display.                                                   |

|                     | A = Status<br>Q = Insignificant value                                                                                                      |

| 1B                  | Unexpected interrupt word interrupt.<br>Current test section is aborted after display.                                                     |

|                     | A = Status<br>Q = Insignificant value                                                                                                      |

| 1C                  | Unexpected external reject on data output attempt.                                                                                         |

|                     | A = Status<br>Q = Rejected data word                                                                                                       |

| 1D                  | Unexpected internal reject on data output attempt.                                                                                         |

|                     | A = Status<br>Q = Rejected data word                                                                                                       |

| 1E                  | Unidentified interrupt. An interrupt occurred, but status<br>does not indicate the type. Current test section is aborted<br>after display. |

|                     | A = Status<br>Q = Insignificant value                                                                                                      |

| 1F                  | Data pattern from remote DSC incorrect                                                                                                     |

|                     | A = Data word received<br>Q = 0000                                                                                                         |

|       | Cont'd) <u>Meaning</u>                                                                                                                                                                                                                                                                                                              |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20    | Unexpected external reject on data input<br>A = Status                                                                                                                                                                                                                                                                              |

|       | Q = Insignificant value                                                                                                                                                                                                                                                                                                             |

| 21    | Unexpected internal reject on data input                                                                                                                                                                                                                                                                                            |

|       | A = Status<br>Q = Insignificant value                                                                                                                                                                                                                                                                                               |

| 22 ** | Manual interrupt received but will not clear                                                                                                                                                                                                                                                                                        |

| 23**  | Rejected on attempt to clear teletype interrupt                                                                                                                                                                                                                                                                                     |

| 24**  | Rejected on attempt to input teletype status                                                                                                                                                                                                                                                                                        |