CONTROL DATA

# CONTROL DATA® 1700 SYSTEM MAINTENANCE MONITOR (SMM17)

VOLUME 2 REFERENCE MANUAL

|            | RECORD of REVISIONS                                                                                |  |  |

|------------|----------------------------------------------------------------------------------------------------|--|--|

| REVISION   | NOTES                                                                                              |  |  |

| 01         | Original Printing, preliminary edition.                                                            |  |  |

| (5-13-66)  |                                                                                                    |  |  |

| 02         | Publications Change Order 14307. Reprint with revision which obsoletes all previous editions.      |  |  |

| (8-8-66)   | Tests were updated and the following new tests were added: 1711/1712 Teletype, 1729 Card Reader,   |  |  |

|            | 1731 Magnetic Tape, 1706/1716 Buffered Data Channel and Coupling, Random Protect, 1700 SMM         |  |  |

|            | Edit Routine, and Enter Program.                                                                   |  |  |

| A          | Manual released. Publication Change Order 16368. The following new tests are added: 0B (1718       |  |  |

| (5-1-67)   | Satellite Coupler Test), 0C (1742 Line Printer Test), and 3D (Enter Program). Other tests were     |  |  |

|            | extensively revised and updated. This edition obsoletes all previous editions.                     |  |  |

| В          | Publication Change Order 17146. To revise existing tests and add new tests. Introduction: page 5   |  |  |

| (9-14-67)  | revised. Description: pages 7, 12, 15, 18, 25, 26, 27, 30 and 35 revised. Pages 30-a and 30-b      |  |  |

|            | added. Tests: pages 90-1, 90-2, 100-7, 100-8, 100-10, 101-2, 101-7, 202-1, 202-7, 205-2, 206-6     |  |  |

|            | thru 206-10, 207-3, 208-2 and 208-6 revised. Page 100-8a added. Tests sections: 102, 201, 203,     |  |  |

|            | 212, 213 and 214 added. Sections 102 Rev A, 201 Rev A and 203 Rev A removed.                       |  |  |

| с          | Publications Change Order 18929. To add 1728 Card Reader/Punch test, No. D.                        |  |  |

| (2-28-68)  |                                                                                                    |  |  |

| D          | Publications Change Order 19818, to make miscellaneous publication corrections. Pages 37,          |  |  |

| (6-11-68)  | 100-2, 100-18, 101-9, 102-7, 200-10, 201-6, 202-9, 203-7, 204-1, 204-12, 205-14, 206-9, 206-10     |  |  |

|            | 207-4, 208-21, 210-4, 210-6, 211-13, and 215-23 revised. Pages 207-5 and 212-24 added.             |  |  |

| E          | Manual Revised, Engineering Change Order 21307, publications change only. Information included     |  |  |

| (1-6-69)   | through Edition 2.1. Pages 35, 90-1, 90-2, 90-6, 101-10, and 208-1 thru 208-21 revised; pages      |  |  |

|            | 30-c through 30-f, 51 through 60, 103, 216, 217, 218, 219, 220, 221, 222 and red tab dividers      |  |  |

|            | added. Manual divided into two volumes.                                                            |  |  |

| F          | Manual revised, Engineering Change Order 21883. This manual is complete through Edition 2.1.       |  |  |

| (12-15-69) |                                                                                                    |  |  |

| G          | Manual revised. New tests are added and editorial corrections made. This manual is complete        |  |  |

| (2-15-70)  | through Edition 2.2.                                                                               |  |  |

| Н          | Manuals revised. This publication is complete through Ed. 2. 3. All previous editions are obsolete |  |  |

| (12-15-70) |                                                                                                    |  |  |

| J          | Manuals revised. New tests are added and minor corrections are made. This publication is           |  |  |

| (2-5-73)   | complete through Ed. 3.0.                                                                          |  |  |

| K          | Manuals revised. Tests are added, deleted, and corrected,                                          |  |  |

| (9-20-73   |                                                                                                    |  |  |

| Ĺ          | Manuals revised. Tests are added, deleted, and corrected. This publication is complete through     |  |  |

| (2-1-74)   | Edition 3, 1,                                                                                      |  |  |

| <u> </u>   |                                                                                                    |  |  |

|            |                                                                                                    |  |  |

|            |                                                                                                    |  |  |

|            |                                                                                                    |  |  |

Address comments concerning this manual to:

Control Data Corporation Technical Publications Department 4201 North Lexington Ave. Arden Hills, Minnesota 55112

or use Comment Sheet in the back of this manual.

Pub. No.

60182000

©

1966, 1967, 1968, 1969, 1973, 1974

by Control Data Corporation

Printed in United States of America

#### PREFACE

#### MANUAL STRUCTURE

This manual is intended to serve as a reference aid for field and checkout personnel involved in the running of the CONTROL DATA® 1700 System Maintenance Monitor (SMM17). It consists of two sections:

#### SMM17 DESCRIPTION

A detailed description of the operation and use of the monitor, instructions for the operator, restrictions and necessary parameters. An asterisk (\*) on the left of the page will highlight operator tasks. Supplements are included in the back of this section.

#### TESTS

Detailed test descriptions complete the three volume reference manual.

iii

÷,

.

## CONTENTS

| VOI                  | LUM                                 | E 1                                  |   |   |    |

|----------------------|-------------------------------------|--------------------------------------|---|---|----|

| SYSTEM FLOW CHART xi |                                     |                                      |   |   |    |

| SMI                  | <b>M17</b>                          | DESCRIPTION                          |   |   |    |

| I.                   | SM                                  | M DEFINITION                         |   |   | 1  |

|                      |                                     |                                      |   |   |    |

| II.                  | LO                                  | ADER DEFINITION                      |   |   | 1  |

| III. LOADING SMM 1   |                                     |                                      |   |   |    |

|                      | Α.                                  | Quick Look Load                      |   |   | 1  |

|                      | в.                                  | Quick Look Stops for SMM Information |   |   | 2  |

|                      | c.                                  | Disabling System Interrupts          |   |   | 3  |

| TT7                  | 10                                  | ADING AND EXECUTING TESTS            |   |   | 9  |

| IV.                  |                                     |                                      |   |   | 3  |

|                      | Α.                                  | Test List Construction               |   |   | 3  |

|                      | в.                                  | Test List Execution                  |   |   | 4  |

| v.                   | SMI                                 | M/OPERATOR INTERFACE                 |   |   | 4  |

|                      | Α.                                  | Programmed Information Stops         |   |   | 4  |

|                      | в.                                  | Stop/Jump Parameter                  |   |   | 5  |

|                      | Ć.                                  | SMM Parameter                        |   |   | 7  |

|                      | D.                                  | System Messages                      |   |   | 9  |

| VI.                  | SYS                                 | TEM USAGE                            |   |   | 9  |

|                      | А.                                  | Test Restart                         |   |   | 9  |

|                      | в.                                  | TTY Input Package Selection          |   | , | 9  |

|                      | с.                                  | Worst-Case Setups                    |   |   | 11 |

|                      | D.                                  | Load and Execution Automation        |   |   | 12 |

| VII.                 | MO                                  | NITOR ERROR CODES                    |   |   | 12 |

|                      |                                     | NERAL OPERATING INSTRUCTIONS         | • |   | 14 |

| A TT1                | VIII.GENERAL OFERATING INSTRUCTIONS |                                      |   |   |    |

60182000 L

v

|   | IX. TELETYPE INPU    | JT PACKAGE           |                |                     | 20          |   |

|---|----------------------|----------------------|----------------|---------------------|-------------|---|

|   | Supplement A.        | Hand-Entered Bootstr | aps            |                     | A-1         |   |

|   | Supplement B.        | SMM17 Library Form   | nat            |                     | B-1         |   |

|   | Supplement C.        | Quick Look Command   | Test           |                     | C-1         |   |

|   | Supplement D.        | SMM17 Programming    | Specifications |                     | D-1         |   |

|   | Supplement E.        | Monitor Based Subrou | itines Program | nming Specification | E-1         |   |

|   | SERVICE ROUTINES     |                      | MNEMONIC       | NUMBER              | PAGE        |   |

|   | Printer/Teletype Dur | np,                  | $\mathbf{DMP}$ | 3B                  | 100-1       |   |

| - | Tape to Print Routin | ie .                 | LST            | 3C                  | 101-1       |   |

|   | 3000 Channel Simula  | tor Assembler        | SAS            | 3D                  | 102-1       |   |

| - | SMM Edit Routine     |                      | $\mathbf{EDT}$ | $3\mathrm{E}$       | 103-1       |   |

|   | 3000 Channel Simulat | or Program Update    | UD3            | 2D                  | 104-1       |   |

|   | 1700 Source/6000 TV  | C Update             | UD1            | 57                  | 105-1       |   |

|   | 1700 Source/6000 BU  | CAL Update           | UD2            | 58                  | 106-1       |   |

|   | INTERNAL TESTS       |                      |                |                     |             |   |

|   | 1700 Command Test    |                      | COM            | 1                   | 200-1       |   |

|   | 1700 Memory Test     |                      | MEM            | 14                  | 201-1       |   |

|   | 1700 Protect Test    |                      | RPT            | 09                  | 202-1       |   |

|   | 1774 System Control  | ler Command Test     | CAR            | 1B                  | 204-1       |   |

|   | 1700 Memory Test     |                      | MY1            | 02                  | 205-1       |   |

|   | 1700 Memory Test     |                      | MY2            | 12                  | 206-1       |   |

|   | EXTERNAL TESTS       | •                    |                |                     |             |   |

|   | Paper Tape Equ       | ipment               |                |                     |             |   |

|   | 1723 Paper Tape Pu   | nch Test             | PTP            | 03                  | 300-1       |   |

|   | 1721 Paper Tape Re   |                      | PTR            | 04                  | 301-1       |   |

|   | Printing Equipm      | ent                  |                |                     |             |   |

|   | 1711/12/13 Teletype  | writer Test          | TTY            | 05                  | 350-1       |   |

|   | 1740/501,1742 Line   |                      | LP1            | 0C                  | 351-1       |   |

|   | FF524-A/1742-120/5   | 12 Printer Test      | LP5            | 23                  | 352-1       |   |

|   | Card Equipment       |                      |                |                     | -<br>-<br>- |   |

|   | 1729 Card Reader (1  | Lo Speed Package)    | CR1            | 06                  | 400-1       |   |

|   | 1728/430 Card Read   |                      | CRP            | 0D                  | 401-1       |   |

|   | 1729-2 Card Reader   | Test                 | CR3            | 13                  | 402-1       |   |

|   | 1726/405 Card Read   | er Test              | CR2            | 17                  | 403-1       |   |

| ۲ | vi                   |                      |                |                     | 60182000    | L |

|   |                      |                      |                |                     |             |   |

.

# Magnetic Tape Equipment

| 1731/601,602,612 Magnetic Tape Test                         | MT1    | 07         | 450-1 |

|-------------------------------------------------------------|--------|------------|-------|

| 1731/601,602,612 Magnetic Tape Test                         | MT2    | 0E         | 451-1 |

| 1732/608, 609-1732-2/658, 659 Magnetic                      |        |            |       |

| Tape Test                                                   | MT3    | 15         | 452-1 |

| 1731/601,602,612-1732/608,609 Special<br>Magnetic Tape Test | MTS    | 1F         | 453-1 |

| highene Tupe Test                                           | WI 1 5 | 11         | 100 1 |

| VOLUME 2                                                    |        |            |       |

|                                                             |        |            |       |

| Data Channel                                                |        |            |       |

| 1706 Data Channel Test                                      | BD1    | 0A         | 500-1 |

| 1706/16 Data Channel Test                                   | BD2    | 0F         | 501-1 |

|                                                             |        |            |       |

| Rotating Mass Storage                                       |        |            |       |

| 1738/853/854 Disk Drive Test                                | DP1    | 08         | 550-1 |

| 1739 Cartridge Disk Drive Controller                        | CDD    | 78         | 551-1 |

| BG504A/H Drum Controller Diagnostic                         | DRM    | 80         | 552-1 |

| 1738 Disk Quick Look Test                                   | DP5    | 84         | 553-1 |

| 1733-1/1738/853,854 and QSE 4730                            | DP3    | 27         | 554-1 |

| 1733-2 Multiple Cartridge Disk Driver                       |        |            |       |

| Controller                                                  | MDC    | 7A         | 555-1 |

| Displays                                                    |        |            |       |

| 1745/6-1,210 Display Test                                   | DDC    | 40         | 600-1 |

| 1745/6-2,311 Display Test                                   | DDT    | 1D         | 601-1 |

| 1700/8000 Data Transfer Buffer Display                      | DTB    | 10         | 602-1 |

| 1744/274 Digigraphics Display Test                          | DIG    | <b>4</b> F | 603-1 |

| 1744/274 Digigraphics Display System                        | DG4    | 6F         | 604-1 |

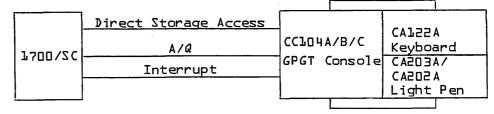

| General Purpose Graphics Terminal (GPGT)                    | N/A    | N/A        | 610-1 |

| GPGT Troubleshooting Program                                | GT0    | 70         | 611-1 |

| GPGT Command Test                                           | GT1    | 71         | 612-1 |

| GPGT Display Quality Test                                   | GT2    | 72         | 613-1 |

| GPGT Light Pen and Keyboard Test                            | GT3    | 73         | 614-1 |

| GPGT Communications Test                                    | GT4    | 74         | 615-1 |

| GPGT Communications Test (12 Bit Interface)                 | GT5    | 75         | 616-1 |

| GPGT Specification Verification Test                        | GT6    | 76         | 617-1 |

|                                                             |        |            |       |

### **Optical Readers**

|   | 1735/915 Optical Character Reader                            | OCR | 35 | 650-1 |

|---|--------------------------------------------------------------|-----|----|-------|

|   | 935-2 Read Transport Test                                    | OC2 | 52 | 652-1 |

|   | FF406/935 Module Test                                        | OC3 | 53 | 653-1 |

|   | 935 System Test                                              | OC4 | 55 | 654-1 |

|   | FF406/1700 I/O Interface Test                                | BC1 | 54 | 655-1 |

|   | 1700/FF104/955 System Test                                   | RX1 | 30 | 656-1 |

|   | 1700/955 Module Test                                         | RX3 | 33 | 657-1 |

|   | SC17/1700 FR101 MEM/COM/IFP Test                             | BC2 | 56 | 658-1 |

|   | 1700/FR101/955 Transport Test                                | RX4 | 34 | 660-1 |

|   | SC/1700/FR101/FR113 Interface Test                           | BC3 | 59 | 661-1 |

|   | VOLUME 3                                                     |     |    |       |

|   | Communication Equipment                                      |     |    |       |

|   | 1718 Satellite Coupler Test                                  | SC1 | 0B | 700-1 |

|   | 1747/6000 Data Set Controller Test                           | DSC | 11 | 701-1 |

|   | 1747 Data Set Controller Test                                | DS1 | 20 | 702-1 |

|   | 1749 Communications Terminal Test                            | CTC | 43 | 703-1 |

| 1 | 1748-2 Multiplexer Controller CSPL<br>Communications Adapter | MCC | 48 | 704-1 |

|   | DJ814A A/Q Communications Multiplexer<br>(NUMOD)             | AQM | 36 | 706-1 |

|   | Analog/Digital                                               |     |    |       |

|   | Event Counter Subsystem                                      | CTR | 81 | 753-1 |

|   | Digital Input/Output Subsystem                               | DIO | 83 | 754-1 |

|   | IOM Mother Unit Diagnostic                                   | IOM | 90 | 755-1 |

|   | 1500 Series Remote Peripheral Controller<br>Diagnostic       | HOR | 4C | 756-1 |

|   | Miscellaneous                                                |     |    |       |

|   | 10126 Clock Test                                             | CLK | 42 | 850-1 |

|   | QSE TESTS                                                    |     |    |       |

|   | 1700/6600 (QSE 3604/3308) Rover Multi-<br>plexer Test        | RMT | 16 | 900-1 |

|   | 1706 Buffered Data Channel Test<br>W/QSE 3247                | BD3 | 18 | 901-1 |

|   |                                                              |     |    |       |

| 1738/853,854 Dual Access Disk Test                                        | DAD            | 19       | 902-1          |

|---------------------------------------------------------------------------|----------------|----------|----------------|

| 1700/415 Card Punch - QSE 5986                                            | CP1<br>CP2     | 21<br>22 | 903-1          |

| 1738 Disk Pack Test - QSE 1811                                            | DP2            | 25       | 904-1          |

| 1706/1716 Channel Test - QSE 3311                                         | BD4            | 26       | 905-1          |

| 1738/853,854 Disk Pack Test - QSE 4777                                    | DP4            | 28       | 907-1          |

| 1706 Buffered Data Channel Test with<br>Non-Terminating Buffer - QSE 3694 | BD5            | 29       | 908-1          |

| DC215 Data Transfer/405 Card Reader                                       | CR4            | 2F       | 909-1          |

| FFT Algorithm - QSE 3116, 6693                                            | $\mathbf{FFT}$ | 41       | 910-1          |

| 1700/200 Remoter User Terminal<br>Diagnostic - QSE 4557                   | CTU            | 44       | 911-1          |

| 1700/1749/332/2-103s/Remote Teletype<br>Test - QSE 4557                   | CTT            | 45       | 912-1          |

| High Speed Data Set Controller Test<br>QSE 8249                           | HCA            | 24       | 913-1          |

| FV219 Plotter Controller Test QSE 6340                                    | PLT            | 39       | 914-1          |

| Operand Bank Test - QSE 7812                                              | Q0B            | 3A       | 915-1          |

| 1745-1746/210 Display Station Test QSE 7698                               | DDD            | 46       | 916 <b>-</b> 1 |

| DC215 Data Transfer Buffer/415 Card<br>Punch Test (QSE)                   | CP4            | 2E       | 917-1          |

| Ponya Parking Lot Data Acquisition<br>and Revenue Control System          | PNY            | 1A       | 918-1          |

| DC216A/3555/512 Printer Test<br>House of Representatives Vote             | LPX            | 5A       | 919-1          |

| Station Exerciser                                                         | VSD            | 4D       | 920-1          |

|                                                                           |                |          |                |

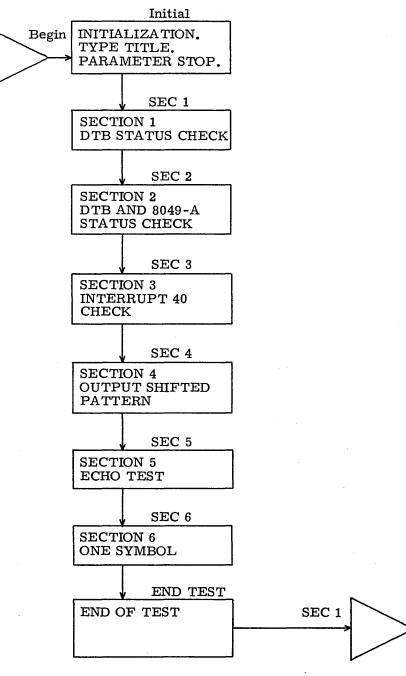

#### 1706 BUFFERED DATA CHANNEL TEST

(BD100A Test No. 0A)

#### OPERATIONAL PROCEDURE

A. RESTRICTIONS

Sections 3, 4, and 5 do not select density on the MT units. However, it is recommended that 200 BPI be selected to allow greater accuracy in testing the CWA register.

- B. LOADING PROCEDURE

- 1. The test operates under control of 1700 System Maintenance Monitor (SMM17).

- 2. The calling sequence is that specified by SMM17.

- 3. The test can be restarted after loading from Initial address.

- C. PARAMETERS

- If bit 0 of the Stop/Jump word is set, the program will have one monitor stop displaying \$A31 in the A register and the Stop/Jump word in the Q register. Two additional stops with the test parameters displayed in the A and Q registers are defined as follows:

| Stop 2 | A = $WE01$ , | where the W field is bits 15–11 and defines the BDC      |

|--------|--------------|----------------------------------------------------------|

|        |              | to be tested. Enter 2, 7, or C for the BDC numbers       |

|        |              | 1, 2, or 3 respectively. The E field is bits 10-7 and    |

|        |              | specifies the equipment number of the 1731/1732          |

|        |              | Magnetic Tape Controller.                                |

|        | ର = 000U.    | where U specifies the $601/608/609$ Tape Unit which will |

Q = 000U, where U specifies the 601/608/609 Tape Unit which will be used for I/O.

Stop 3 A = XXXX, the End of Operation interrupt line for the BDC. Only 1 bit is set in this word which must indicate the interrupt line. For example if the End of Operation interrupts are to be received on line 5, Bit 5 would be set.

- Q = XXXX, the sections of the BDC test to run. Bit 0 of Q will select Section 1 to be run, etc. There are five sections in all. If all five sections were to be run, Q would be set to 001F.

- Stop 4 A = XXXX, illegal equipment (enter into A an equipment address that is unused on your system. This equipment address is used to check internal rejects)

60182000 L

Q = XXXX, unused (prestored as 0001)

500-1

- 2. If bit 0 of the Stop/Jump word is not set, the test will be run using the prestored parameters. These parameters assume the following:

- a. BDC number 1 is to be tested and the tape controller is number 3.(WE01 = 1181)

- b. Tape unit 7 is the tape to use for I/O.

- c. The interrupts on End of Operation from the BDC are received on line 3.

- d. All five sections of the test will be run.

- 3. A typeout of selected parameters will occur after last stop.

- D. SELECTIVE SKIP AND STOP SETTINGS

- 1. STOP must be set for running of SMM17.

- 2. SKIP when the Stop/Jump word is displayed in Q.

#### E. MESSAGES

- 1. Typeouts or Alarms

- a. Normal Program Typeouts

- Test identification at start of test BD100A, 1706 BUFFERED DATA CHANNEL TEST IA = XXXX, FC = XX

- 2) End of test typeout

AQAQ0A24S/JPass No.Return Address

- b. Error Alarms

- 1) The following is typed out:

- a) Identification word

- b) Stop/Jump parameter

- c) Section/Error number

- d) Return address

- e) Information dependent upon specific error

- f) Information dependent upon specific error

- 2. Error Codes

An error code is displayed in the lower two digits of the A register on the second stop of all error stop sequences. A description of the error codes used and the data displayed in the A and Q registers of the third stop is listed as follows:

Error 01 - Incorrect equipment parameter was entered. Program will make another parameter stop if placed in Run.

A = the equipment parameter entered Q = 0000

Error 02 - External reject on input of BDC status. If the error condition is not repeated (Bit 4 of Stop/Jump word set) the test will be terminated.

A = the contents of Q when the input instruction was executed Q = 0000

- Error 03 Internal reject on input of BDC status. If the error condition is not repeated, the test is terminated.

- Error 04 Ready not set on BDC status. If the condition is not repeated, the test is terminated.

A = BDC status Q = 0000

Error 05 - External reject on input of BDC current address.

A = contents of Q when the input instruction was executed Q = 0000

Error 06 - Internal reject on input of BDC current address.

A = contents of Q when the input instruction was executed Q = 0000

Error 07 = External reject on Terminate Buffer.

A = contents of Q when the input instruction was executed Q = 0000

- Error 08 = Internal reject on Terminate Buffer.

- A = contents of Q when the input instruction was executed Q = 0000

- Error 09 = External reject on attempt to output a function to the BDC.

A = contents of Q when output was attempted

Q = contents of A when output was attempted

Error 0A - Internal reject on attempt to output a function to the BDC.

A = contents of Q when output was attempted Q = contents of A when output was attempted

Error 0B - External reject on direct output of a function to the 1731 Tape Controller.

A = contents of A when ouput was executed

Q = contents of Q when output was executed

Error 0C - Internal reject on direct output of a function to the 1731 Tape Controller.

A = contents of A when output was executed Q = contents of Q when output was executed

#### Error 0D - External reject on input of status 1 of the 1731 Tape Controller.

A = the contents of Q when the input was executed Q = 0000

Error 0E - Internal reject on input of status 1 of the 1731 Tape Controller. A = the contents of Q when the input was executed

Q = 0000

Error OF - External reject on input of status 2 of the 1731 Tape Controller.

A = the contents of Q when the input was executed Q = 0000

Error 10 - Internal reject on input of status 2 of the 1731 Tape Controller.

A = the contents of Q when the input was executed Q = 0000

Error 11 - No write ring in selected tape unit. If this error condition is not repeated, the test is terminated.

A = the selected tape unit

Q = status 2 of the selected tape unit

Error 12 - The selected tape unit is protected. If this error condition is not repeated, the test will be terminated.

A = the selected tape unit

Q = status 1 of the selected tape unit

Error 13 - External reject on attempt to initiate buffered output to tape.

A = the first word address minus 1 of the buffer area Q = contents of Q when the output instruction was executed

# Error 14 - Internal reject on attempt to initiate buffered output to tape. A = the first word address minus 1 of the buffer area Q = contents of Q when the output instruction was executed

Error 15 - External reject on the attempt to initiate a buffered input from tape.

A = the first word address minus 1 of the buffer area Q = the contents of Q when the output instruction was executed

Error 16 - Internal reject on the attempt to initiate a buffered input from tape.

A = the first word address minus one of the buffer area

- $\mathbf{Q}$  = the contents of  $\mathbf{Q}$  when the output instruction was executed

- Error 17 Busy bit (bit 1) of the BDC status was not set after initiating a buffered output.

- A = BDC status Q = 0000

- Error 18 Busy bit (bit 1) of the BDC status was not set after initiating a buffered input.

- A = BDC status Q = 0000

- Error 19 Reply bit (bit 9) of the BDC status was not set after initiating a buffered output.

- A = BDC status Q = 0000

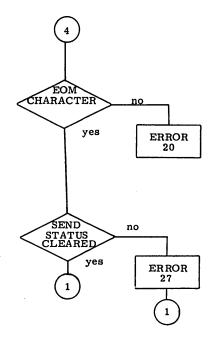

- Error 20 Reply bit (bit 9) of the BDC status was not set after initiating a buffered input.

- A = BDC statusQ = 0000

- Error 21 Reject bit (bit 8) of the BDC status was never set (over an arbitrary length of time) after initiating a buffered output.

- A = BDC status Q = 0000

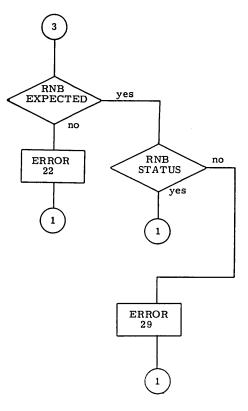

Error 22 - Reject bit (bit 8) of the BDC status was never set (over an arbitrary length of time) after initiating a buffered input.

A = BDC status Q = 0000

Error 23 - End of Operation bit (bit 4) of the BDC status is set at the same time as the Busy bit.

A = BDC status Q = 0000

Error 24 - End of Operation bit (bit 4) of the BDC status is not set after the Busy cleared at the end of a buffered output.

> A = BDC status Q = 0000

Error 25 - End of Operation bit (bit 4) of the BDC status is not set after the Busy cleared at the end of a buffered input.

A = BDC statusQ = 0000

Error 26 - No reject received from the BDC when attempting a direct output when the BDC was Busy.

A = BDC status Q = 0000

Error 27 - No interrupt received from the BDC on End of Operation (buffered output).

A = BDC status Q = 0000

Error 28 - Alarm bit set in tape status 1 after a buffered output was complete.

A = Tape status 1 Q = 0000

Error 29 - No interrupt received from the BDC on End of Operation (buffered input).

A = BDC status

Q = 0000

- Error 2A Interrupt bit (bit 2) of the BDC status was not set after an End of Operation interrupt occurred.

- A = BDC status when interrupted

- Q = 0000

Error 2B - Data error

- A = Data read

- Q = Expected value

- A = Failing address

- Q = 0000

- Error 2C Current address of the BDC was not equal to one greater than the FWA-1 after initiating a buffered output.

- A = Current address which was input

- Q = 0000

- Error 2D The current address which was input from the BDC was neither the same as or up to two greater than the previous current address input.

- A = Previous current address

- Q = Current address

- Error 2E End of Operation status bit (bit 4) was not set in the BDC status when an Interrupt on End of Operation occurred.

- A = BDC status

- Q = 0000

- Error 2F Buffer terminated at incorrect address.

- A3 = Actual address buffer terminated at

- Q3 = Expected last word address, at EOP

- Error 33 Incorrect status after initiating buffer to non-existent equipment (parameter A4) on this 17X6.

- A3 = Expected channel status after initiating a buffer

- Q3 = Actual channel status after initiating a buffer

- A4 = Expected address register status

- Q4 = Actual address register status

- A5 = Equipment address when error occurred

- Q5 = Iteration count (range = FFFC-0003)

- Error 34 Current word address was not one greater than FWA-1 after initiating a buffer to illegal equipment on BDC.

- A3 = Expected channel status

- Q3 = Actual channel status

- A4 = FWA-1 output to BDC to initiate buffer

- Q4 = CWA of BDC on terminate buffer command

- A5 = Same as error 33

- Q5

- Error 35 Internal reject on clear controlled direct through BDC

- A3 = BDC expected status

- Q3 = BDC actual status

- A4 = Equipment expected status

- Q4 = Equipment actual status

- A5 = Equipment address when error detected

- Q5 = Not available

- Error 36 External reject on clear controller

Same as error 35

Error 37 - Channel busy or not ready

A3 = 0 Q3 = BDC actual status A4 = 0 Q4 = 0 A5 = Same as error 33Q5

Error 38 - Unit/Equipment busy

A3 = 0 Q3 = BDC actual status A4 = 0 Q4 = Unit status A5 = Same as error 33 Q5 = Same as error 33 Error 39 - Buffer terminated before programmed LWA+1

- A3 = Not available

- Q3 = BDC status

A4 = Actual CWA status at EOP

Q4 = Expected CWA status at EOP

- A5 = Same as error 33

- Q5

Error 3A - Buffer did not terminate at last word ADDES+1

- A3 = Not available

- Q3 = BDC status

- A4 = Current word address when buffer was terminated

- Q4 = Expected LWA register

Error 3C - 17X6 not busy before CWA=LWA+1

- A3 = Expected BDC status

- Q3 = Actual BDC status

- A4 = CWA register status

- Q4 = LWA+1 sent to BDC

- A5 = Same as error 33

- Q5

Error 3D - 17X6 buffer hung before CWA=LWA+1 when doing buffered equipment status inputs or buffered clear controller outputs.

- A3 = Expected status of BDC

- Q3 = Actual status of BDC

- A4 = CWA register status of hung buffer

- Q4 = Expected LWA+1 of buffer

- A5 = Same as error 33

- Q5 = Same as error 33

- 3. Error Stops

Error stops will occur if bit 3 of the Stop/Jump word is set and an error occurs in the test.

#### **II. DESCRIPTION**

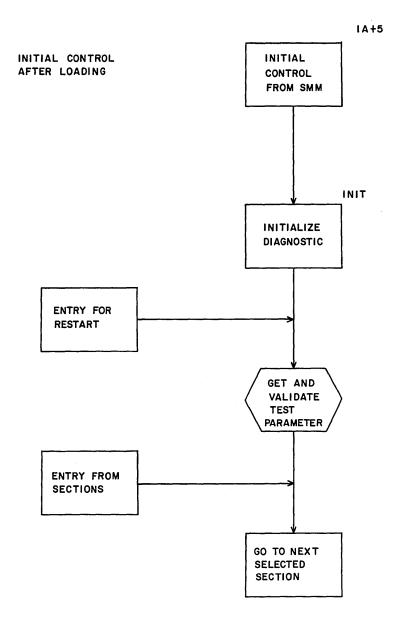

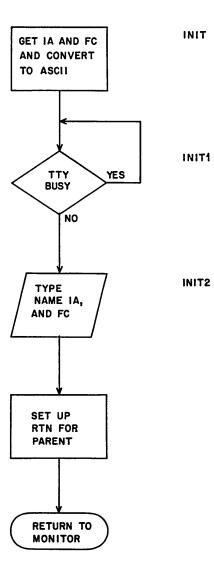

- A. INITIALIZATION (UNIT)

- 1. Convert bias value and frequency count to ASCII and store in typeout routine.

- 2. Type out test title, initial address, and frequency count.

- 3. Set up return address (IA+5).

- 4. Parameter entry stop.

- 5. Check for correct W field in equipment code. Error stop if incorrect.

- 7. Exit to SMM.

#### B. SECTION ONE (S1)

This section checks static conditions of BDC then proceeds to check the CWA register, LWA register, adder, buffer read capabilities, and buffer write capabilities.

- 1. Check status for ready.

- 2. Input current address; no Reject expected.

- 3. Execute terminate buffer and input current address to

- a. No Reject expected.

- 4. Check EOP interrupt select and clear.

- 5. Attempt buffer output to non-existent equipment on channel.

- a. Start with FWA-1=0. Expect BDC to hang with CWA one greater than FWA-1. Expect status to be busy.

- b. Do until FWA-1 = \$7FFF.

- c. Do a and b three times

- 6. Attempt buffer input from non-existent equipment on channel (same as 5).

- 7. Do direct FCN clear controller to selected Equipment Expect Reply.

- 8. Do 500<sub>10</sub> word buffer out of clear controller.

- a. Monitor CWA. Expect termination when CWA=LWA+1.

- b. Monitor BDC status. Expect busy until CWA=LWA+1.

- c. Do 100<sub>10</sub> times.

- 9. Do direct input status 1 of selected equipments. Save for use in next step. Expect reply.

- 10. Do  $500_{10}$  word buffer input of status 1 from selected device.

- a. Same as 8a and 8b.

- b. Compare data from step 9 and report errors.

- c. Do 100<sub>10</sub> times.

#### C. SECTION TWO (S2)

This section checks static conditions on the BDC, tape controller, and tape unit.

- 1. Connect selected tape unit.

- 2. Check for write enable. Error if not present.

- 3. Check for tape unit unprotected. Error if protected.

- 4. Rewind tape.

- 5. Exit section two.

#### D. SECTION THREE (S3)

This section does a 500-word buffered Write and Read.

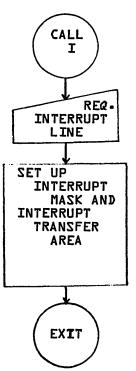

- 1. Request interrupt line from SMM.

- 2. Select tape unit and rewind it.

- 3. Select binary mode.

- 4. Initiate a 500-word buffered write.

- 5. Check BDC status for Busy. Repeat from item 2 if Not Busy.

- 6. Check BDC status for Reply. Should be set.

- 7. Check BDC status for Reject during output. Should be set.

- 8. Exit to SMM until buffer is complete.

- 9. Rewind tape.

- 10. Repeat from item 4 for a 500-word read.

- 11. Clear interrupt request in SMM.

- 12. Exit section three.

- E. SECTION FOUR (S4)

This section writes and reads ten 500-word records for each of fifteen patterns. End of Operation interrupt is checked after each record.

- 1. Request interrupt line from SMM.

- 2. Select tape.

- 3. Pick up current data pattern.

- 4. Select binary mode if pattern number is Odd. Select BCD mode if pattern number is Even.

- 5. Clear interrupt flag.

- 6. Select EOP interrupt on BDC.

- 7. Initiate 500-word buffered write.

- 8. Check for reject during buffered operation.

- 9. Exit to SMM until buffer is complete.

- 10. Check for EOP interrupt. Error if not present.

- 11. Check tape status for EOT, Parity, Lost Data, and Alarm.

- 12. Repeat from item 5 for 10 records.

- 13. Update data pattern.

- 14. Repeat from item 2 for 15 patterns.

- 15. Rewind tape.

- 16. Blank out storage data.

- 17. Repeat from item 5 using a Read instead of a Write. Data is checked for each record.

- 18. Exit section four.

#### F. SECTION FIVE (S5)

This section tests the current word address.

- 1. Request interrupt line from SMM.

- 2. Rewind tape, select binary mode.

- 3. Initiate buffered output. Word Count = 7FFE<sub>16</sub>-LOCSEX.

- 4. Input current address to A. Address should be one greater than the CWA.

- 5. Store current address.

- 6. Input current address to A. This address should be equal to or up to two greater than previous address. Error if not one of these two conditions.

- 7. If current address is one greater than previous address, repeat from item 4.

- 8. If current address equals previous address, check BDC status for EOP. Loop to item 4 if not set.

- 9. Check tape status for EOT, Parity, Lost Data, and Alarm. Error if any of these are set.

- 10. Clear interrupt request.

- 11. Exit section five.

#### III. PHYSICAL REQUIREMENTS

A. SPACE REQUIRED

Approximately 2000 locations.

B. INPUT AND OUTPUT TAPE MOUNTINGS

The 601/608/609 Tape Unit selected for I/O must have a write ring and must be ready.

C. TIMING - approximately 1 minute 15 seconds.

#### D. EQUIPMENT CONFIGURATION

- 1. 17X4 Computer

- 2. 17X5 Interrupt Data Channel

- 3. 1706 Buffer Data Channel

- 4. 1731/1732 Magnetic Tape Controller

- 5. 601/608/609 Magnetic Tape Unit

#### 1706/1716 CHANNEL TEST

(BD200F Test No. 0F)

#### I. OPERATIONAL PROCEDURE

A. RESTRICTIONS

None available

- B. LOADING PROCEDURE

- 1. The test operates under control of 1700 System Maintenance Monitor (SMM17).

- 2. The calling sequence is that specified by SMM17. The test number for the 1706/1716 test is F.

- 3. The test can be restarted after loading from initial address.

- C. PARAMETERS

- 1. If bit 0 of the Stop/Jump word is set, the program will allow for test parameter display and/or entry. The first stop made in the parameter sequence displays the identification word in A (0F31) and the Stop/Jump word in Q.

The second and third stops display the test parameters. The test parameters can be changed by the operator at the time when they are displayed. The contents of the A and Q registers on the second and third stops is defined below. (Parameter typeout will occur after last stop)

a. Stop 2

A = WE01, where the W field is bits 15-11 and identifies the 17X6\* equipment address. The allowable values for the 5-bit W field are:

00010 - for 17X6 number 1 00111 - for 17X6 number 2 01100 - for 17X6 number 3

The E field is bits 10-7 and identifies the 1731/1732 Magnetic Tape Controller Q = 000U, where U specifies the 601 or 602 Magnetic Tape Unit which will be used for I/O in sections 2, 3, and 4.

\*17X6 refers to either 1706 or 1716, whichever is being used or tested.

#### b. Stop 3

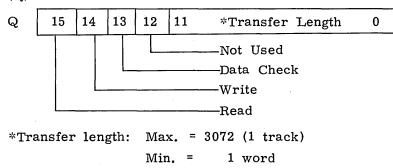

A = The End of Operation interrupt line for the 17X6. Only one bit is set in this word. The bit position must identify the interrupt line. For example, if the End of Operation interrupts from the 17X6 are to be received on line 5, only bit 5 of this word would be set. Q register contents are described below:

- Bit 15 = 1: A 1716 is connected to this computer.

- Bit 15 = 0: A 1706 is connected to this computer.

- Bit 14 = 1: This computer will initiate the first output if section 6 is selected to be run.

- Bit 14 = 0: The other computer will initiate the first data transfer if section 6 is selected to be run.

- Bit 5 = 1: Run test section 6. This section will use the 1716 to transfer data between two computers which are necessary to run this section. A common 1716 must be connected to both the computers. Bit 14 of this parameter must be set in one of the computers. Bit 14 of the other computer must be equal to zero. The decision to repeat Section 6 must be made in the computer which has bit 14 = 0.

- Bit 4 = 1: Run test Section 5. This section will use the 1716 to make block transfers of data within a computer's core storage.

- Bit 3 = 1: Run test Section 4. This section uses the 17X6 1731/1732 and a 601/608/609 to test direct output/ input of data.

- Bit 2 = 1: Run test Section 3. This section uses the 17X6, 1731/1732 and a 601/608/609 to test the current word address of the 17X6.

- Bit 1 = 1: Run test Section 2. This section will use the 17X6, 1731/1732 and a 601/608/609 to test buffered output/input.

- Bit 0 = 1: Run test Section 1. This section will check the ability of the 17X6 to accept all legal functions (reject should not be received). If a 1716 is connected, this section will also test the flags, masks, and interrupts when corresponding masks and flags are both set.

- 2. If bit 0 of the Stop/Jump word is not set, the test will be run using the set of prestored parameters. These parameters assume the following:

- a. 1706 number 1 and equipment number of the 1731/1732 Magnetic Tape Controller is 3.

- b. Tape unit 7 is ready and write-enabled.

- c. The End of Operation interrupts from the 17X6 will be received on line 4.

- d. Test Sections 1, 2, 3, and 4 will be run.

- 3. Selective Skip and Stop Settings

- a. STOP switch must be set for running SMM17.

- b. SKIP switch, when set, displays the Stop/Jump word in Q.

#### D. MESSAGES

- 1. Typeouts or Alarms

- a. Normal Program Typeouts

- Test identification at start of test BD200F, 1706/1716 DATA CHANNEL TEST IA = XXXX, FC = XX

- 2) End of test typeout

| A           | Q        | A           | Q              |

|-------------|----------|-------------|----------------|

| <b>0F24</b> | S/J word | Pass number | Return Address |

b. Error Typeouts

If an error occurs, the following information is typed out:

- 1) Identification word

- 2) Stop/Jump word

- 3) Test section/error number

- 4) Return address

- 5) Additional information related to the specific error

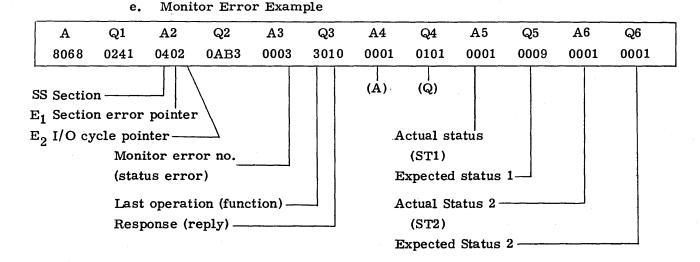

A sample error typeout is shown and described as follows:

| A    | Q    | A    | ଦ    | A    | Q    |

|------|------|------|------|------|------|

| 0F38 | 000F | 0107 | 0507 | 0201 | 1800 |

0F38 is the identification word where

F is the test number

3 is the number of stops in this error stop sequence

8 identifies the stop as an error stop (bit 3 set)

000F is the Stop/Jump word

0107 is the section number and error number (Section 1, error number 7)

0507 is the address in the program (list address) where the error occurred.

0201 was the status of the 17X6 prior to the attempt to terminate the buffer (see information under error number 7).

1800 was the contents of Q when the attempt to terminate the buffer was made (see information under error 7).

2. Error Codes

An error code is displayed in the lower two digits of the A register on the second stop of all error stop sequences. A description of the error codes used and the additional information displayed on each error is described below.

| Error | Description                                                                                                                                                                        |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 01    | Incorrect test parameter was entered. The program will make another parameter stop when restarted.                                                                                 |  |

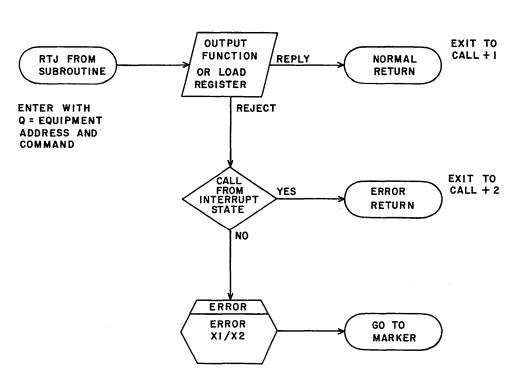

| 02/03 | External/internal reject on attempt to input 17X6 status. If<br>this error condition is not repeated (bit 4 of the Stop/Jump<br>word set), the test will make a final exit to SMM. |  |

|       | A = 0000<br>Q = Contents of Q when the input was attempted                                                                                                                         |  |

| 04    | Ready not set on 17X6 status. If the condition is not repeated the test will be terminated.                                                                                        |  |

|       | A = $17X6$ status                                                                                                                                                                  |  |

Q = Equipment address of the 17X6

| Error | Description                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------|

| 05/06 | External/internal reject on input of the 17X6 current address                                                               |

|       | A = 0000<br>Q = Contents of Q when input was attempted                                                                      |

| 07/08 | External/internal reject on Terminate Buffer operation on 17X6                                                              |

|       | A = 17X6 status prior to the Terminate Buffer operation<br>Q = Contents of Q when Terminate Buffer was attempted            |

| 09/0A | External/internal reject on attempt to output a function to the 17X6                                                        |

|       | A = Contents of A when output was attempted                                                                                 |

|       | Q = Contents of Q when output was attempted                                                                                 |

|       | A = Status of the 17X6 prior to the output<br>Q = 0000                                                                      |

| 0B/0C | External/internal reject on direct output of a function to the 1731/1732                                                    |

|       | A = Contents of A when the output was attempted (function)<br>Q = Contents of Q when output was attempted                   |

|       | A = Status 1 of the 1731/1732 prior to output<br>Q = Status of the 17X6 prior to the output                                 |

| 0D/0E | External/internal reject on input of status one of the 1731/1732                                                            |

|       | A = Status of the 17X6 prior to the input                                                                                   |

|       | Q = Contents of $Q$ when the input was attempted                                                                            |

| 0F/10 | External/internal reject on input of status two of the 1731/1732                                                            |

|       | A = Status of the 17X6 prior to the input<br>Q = Contents of Q when the input was attempted                                 |

| 11    | No write ring in selected tape unit                                                                                         |

|       | A = Status 2 of the tape unit                                                                                               |

|       | Q = WEOU, where W is the address of the 17X6, E is the equipment number of the $1731/1732$ and U is the selected tape unit. |

| 12    | Selected tape unit is protected                                                                                             |

|       | A = Status 1 of the tape unit<br>Q = WEOU                                                                                   |

,

| Error | Description                                                                                                                             |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 13/14 | External/internal reject on attempt to initiate a buffered output to the 601/608/609.                                                   |

|       | A = Contents of A when output was attempted (FWA-1)<br>Q = Contents of Q when output was attempted                                      |

|       | A = Status 1 of the tape unit prior to the output<br>Q = Status of the 17X6 prior to the output                                         |

| 15/16 | External/internal reject on attempt to initiate a buffered input from the 601/608/609.                                                  |

|       | A = Contents of A when the output was attempted (FWA-1)<br>Q = Contents of Q when the output was attempted                              |

|       | A = Status 1 of the tape unit prior to the output<br>Q = Status of the 17X6 prior to the output                                         |

| 17/18 | Busy bit of the 17X6 status did not set after initiating a buffered output/input                                                        |

|       | A = 17X6 status<br>Q = 0000                                                                                                             |

| 19/1A | The Device Reply bit (bit 9) of the 17X6 status was never set within a time period after initiating a buffered output/input.            |

|       | A = the last 17X6 status input<br>Q = 0000                                                                                              |

| 1B/1C | The Device Reject bit (bit 8) of the 17X6 status was never set within a time period after initiating a buffered output/input.           |

|       | A = The last 17X6 status input<br>Q = 0000                                                                                              |

| ID    | The End of Operation bit (bit 4) of the 17X6 status is set at the same time as Busy (bit 1) is set.                                     |

|       | A = 17X6 status<br>Q = 0000                                                                                                             |

| 1E/1F | The End of Operation bit (bit 4) of the 17X6 status is not set after the Busy dropped at the completion of a buffered output/<br>input. |

|       | A = 17X6 status<br>Q = 0000                                                                                                             |

|       |                                                                                                                                         |

Ì

|  | Error | Description                                                                                                                                                                                                                                                                                 |

|--|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | 20/21 | No reject received from the 17X6 on an attempt to execute a direct output/input to the 17X6 when the 17X6 was Busy.                                                                                                                                                                         |

|  |       | A = Status of the 17X6 prior to the output<br>Q = 0000                                                                                                                                                                                                                                      |

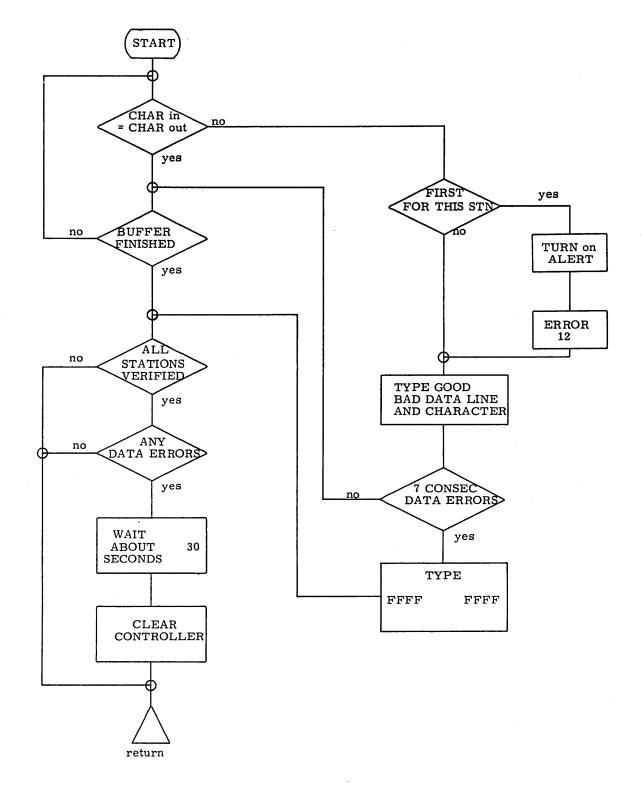

|  | 22/23 | No interrupt received from the 17X6 on end of operation after a buffer was completed.                                                                                                                                                                                                       |

|  |       | A = Status 1 of the tape after the buffer was completed $Q$ = Status of the 17X6 after the buffer was completed                                                                                                                                                                             |

|  | 24/25 | Alarm bit set in tape status 1 after a buffered output/input<br>was completed                                                                                                                                                                                                               |

|  |       | A = Status 1 of the tape after the buffer was completed $Q$ = Status of the 17X6 after the buffer was completed                                                                                                                                                                             |

|  | 26/27 | Interrupt bit (bit 2) of the 17X6 status was not set after an End<br>of Operation interrupt occurred when a buffer output/input was<br>completed.                                                                                                                                           |

|  |       | A = Status 1 of the tape unit after the buffer was completed $Q$ = Status of the 17X6 after the buffer was completed                                                                                                                                                                        |

|  | 28    | Data error occurred                                                                                                                                                                                                                                                                         |

|  |       | A = Data read<br>Q = Expected value                                                                                                                                                                                                                                                         |

|  |       | A = Word number within the block which is incorrect $Q = 0000$                                                                                                                                                                                                                              |

|  | 29    | Current address of the 17X6 was not equal to 0008 after initiating<br>a buffered output with first word address equal to 0007. (The<br>1731/1732 will accept the first data word and the 17X6 will<br>increment the current address prior to the program inputting<br>the current address.) |

|  |       | A = The current address which was input<br>Q = 0000                                                                                                                                                                                                                                         |

|  |       |                                                                                                                                                                                                                                                                                             |

I

| Error      | Description                                                                                                                                                        |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2A         | The current address input from the 17X6 was neither greater<br>nor the same as the previous current address input while a<br>buffered output was active.           |

|            | A = The previous current address<br>Q = The last current address input                                                                                             |

| 2B/2C      | The End of Operation status bit (bit 4) was not set in the 17X6 status when an Interrupt on End of Operation occurred after a buffered output/input was completed. |

| 2D         | Reserve bit (bit 3) in the 1716 status is still set after executing a Terminate Buffer.                                                                            |

|            | A = 1716 status<br>Q = 0000                                                                                                                                        |

| <b>2</b> E | Reserve bit (bit 3) in the 1716 status is still set after executing the function to clear it.                                                                      |

|            | A = Contents of A when the function was output<br>Q = Contents of Q on the output                                                                                  |

|            | A = 1716 status after the function<br>Q = 0000                                                                                                                     |

| 2F         | Flag bit not set in the 1716 status after executing function to set it.                                                                                            |

|            | A = Contents of A when function was output<br>Q = Contents of Q when function was output                                                                           |

|            | A = 1716 status after the function<br>Q = 0000                                                                                                                     |

| 30         | Flag bit set in the 1716 status after executing function to clear it.                                                                                              |

|            | A = Contents of A when function was output<br>Q = Contents of Q when function was output                                                                           |

|            | A = 1716 status prior to function<br>Q = 1716 status after executing function                                                                                      |

|            |                                                                                                                                                                    |

~

| Error | Description                                                                                                                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | No interrupt received from the 1716 after setting a Mask bit and then setting the corresponding flag bit.                                                                                                                                                                            |

|       | A = Contents of A to set mask<br>Q = Contents of Q used when setting the Mask and the Flag bits                                                                                                                                                                                      |

|       | A = Contents of A to set Flag bit<br>Q = Present status of the 1716                                                                                                                                                                                                                  |

| 32/33 | External/internal reject received from the 1716 when attempting to initiate a buffered transfer.                                                                                                                                                                                     |

|       | A = Contents of A when output was attempted<br>Q = Contents of Q when output was attempted                                                                                                                                                                                           |

|       | A = Status of the 1716 prior to attempting the buffered transfer $Q$ = Status of the 1716 after receiving the reject                                                                                                                                                                 |

| 34    | Flag status bits are not equal to the expected flags. The other<br>computer set a cretain configuration of flags and then stored a<br>word in this computer's core storage indicating the present<br>state of the flag bits. The flags did not correspond to the<br>indication word. |

|       | A = Status of the 1716<br>Q = Expected status of the 1716 (flag bits are in bits 10-14)                                                                                                                                                                                              |

| 35    | Data error in data the other computer sent this one. If the<br>error condition is to be repeated, set bit 4 in the Stop/Jump<br>word of the other computer when it types out error number 36.                                                                                        |

|       | A = Data received from other computer<br>Q = Data expected                                                                                                                                                                                                                           |

|       | A = Word number within data block<br>Q = 0000                                                                                                                                                                                                                                        |

| 36    | The other computer detected at least one data error in the data<br>this computer sent it. (The other computer has typed out<br>error number 35 (one or more times).                                                                                                                  |

|       | A = Number of errors found by other computer<br>Q = 0000                                                                                                                                                                                                                             |

|       |                                                                                                                                                                                                                                                                                      |

X

| Error | Description                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| 37    | Data error in data this computer sent the other computer and then read back to this one.                                            |

|       | A = Data word read back<br>Q = Data word originally sent to other computer                                                          |

|       | A = Word number within block<br>Q = 0000                                                                                            |

| 38    | Interrupt bit not set in the 1716 status after an interrupt occurred because the corresponding mask bit and flag bit were both set. |

|       | A = Status of the 1716 after the interrupt occurred $Q = 0000$                                                                      |

| 39/3A | Alarm bit set in status 1 of the 1731/1732 after a direct output/input                                                              |

|       | A = Status 1 of the $1731/1732$<br>Q = Status of the 1716                                                                           |

| 3B    | Interrupt not received after a data transfer was completed.                                                                         |

|       | A = Status of the 1716<br>Q = $0000$                                                                                                |

#### E. ERROR STOPS

Error stops will occur if bit 3 of the Stop/Jump word is set, the STOP switch is set, and an error occurs.

#### II. DESCRIPTION

#### A. METHOD

#### 1. Initialization

- a. Convert bias value and frequency count and store in typeout routine.

- b. Type out the test title, and frequency count.

- c. Store return address.

- d. Make parameter stop if bit 1 of Stop/Jump word is set.

- e. Set up for control to be given to distributor on return from SMM.

- f. Return control to SMM.

#### 2. Distributor

- a. Run Section 1 if selected.

- b. Stop at end of section if bit 1 of Stop/Jump word is set.

- c. Go to a if bit 5 of Stop/Jump word is set (repeat section).

- d. Run Section 2 if selected.

- e. Stop at end of section if bit 1 of Stop/Jump word is set.

- f. Go to d if bit 5 of Stop/Jump word is set.

- g. Run Section 3 if selected.

- h. Stop at end of section if bit 1 of Stop/Jump word is set.

- i. Go to g if bit 5 of Stop/Jump word is set.

- j. Run Section 4 if selected.

- k. Stop at end of section if bit 1 of Stop/Jump word is set.

- 1. Go to j if bit 5 of Stop/Jump word is set.

- m. Run Section 5 if selected.

- n. Stop at end of section if bit 1 of Stop/Jump word is set.

- o. Go to m if bit 5 of Stop/Jump word is set.

- p. Run Section 6 if selected.

- q. Add 1 to pass counter.

- r. Stop at end of test if bit 2 of Stop/Jump word is set.

- s. Go to b if bit 6 of Stop/Jump is set (repeat test).

- t. Check if new parameters are to be entered (bit 10 of Stop/Jump word set).

- u. Load bias and exit to SMM.

- v. Go to a if SMM returns control (test frequency was greater than 1).

- 3. Section 1

- a. Purpose: Check the static conditions of a 17X6. Checks for no rejects on all legal functions which will not initiate data transfer.

- b. Procedure:

- 1) Check for Ready set on 17X6.

- 2) Check for no reject received on input of current address.

- 3) Check for no reject received on Terminate Buffer.

- 4) Check for reserve clear if 1716.

- 5) Check for no reject received on Select and Clear interrupt functions.

- 6) If 1706 return to distributor.

- 7) Clear all masks and flags.

- 8) Test for interrupts after setting each mask and then the corresponding flag.

- 9) Return to distributor.

- 4. Section 2

- a. Purpose: To test the data transfer capabilities of the 17X6. Interrupt on End of Operation is also tested.

- b. Procedure:

- 1) Set reserve bit if 1716.

- 2) Check for selected tape unit write-enabled and non-protected.

- 3) Rewind.

- 4) Select 200 BPI.

- 5) If this is an odd record of the current data pattern, select binary; if even, select BCD.

- 6) Select interrupt from 17X6 on End of Operation

- 7) Initiate buffer output.

- 8) Check for Busy set in 17X6 status.

- 9) Check for device Reject set.

- 10) Check for a reject on output to 17X6 while 17X6 is Busy.

- 11) Check for device Reply set in 17X6 status.

- 12) Return control to SMM.

- 13) Check for End of Operation bit set after Busy clears.

- 14) Check if interrupt occurred on End of Operation.

- 15) Check if Interrupt and End of Operation bits were set in 17X6 status when interrupt occurred.

- 16) Check tape status.

- 17) If 20 records of current data pattern have not been written, go to 5).

- 18) If all data patterns have not been used, change patterns and go to 5).

- 19) Rewind.

- 20) If odd record, select binary; if even, select BCD.

- 21) Select Interrupt on End of Operation from 17X6.

- 22) Initiate buffer input.

- 23) Check for Busy set on 17X6.

- 24) Check for device Reject set in 17X6 status.

- 25) Check for a reject on output to 17X6 while it is Busy.

- 26) Check for device Reply set in 17X6 status.

- 27) Return control to SMM.

- 28) Check for End of Operation bit set when Busy clear.

- 29) Check if Interrupt on End of Operation occurred.

- 30) Check if Interrupt and End of Operation bits were set in 17X6 status when interrupt occurred.

- 31) Check tape status.

- 32) Check data.

- 33) If 20 records of current data pattern have not been read, go to 20).

- 34) If all data patterns have not been read, change patterns and go to 20).

- 35) Rewind.

- 36) Clear reserve if 1716.

- 37) Return to distributor.

- 5. Section 3

- a. Purpose: Check the ability of the 17X6 to increment the current address correctly.

- b. Procedure

- 1) Set reserve if 1716.

- 2) Rewind and select 200 BPI.

- 3) Initiate buffer output with FWA = 0007.

- 4) Input current address of 17X6 and check for 0008.

- 5) Input current address and check for equal or one greater than the previous one input.

- 6) If End of Operation is not set go to 5).

- 7) Clear reserve if 1716.

- 8) Return to distributor.

- 6. Section 4

- a. Purpose: Check the direct I/O of data to a 601/608/609 via the 17X6.

- b. Procedure:

- 1) Set Reserve bit if 1716.

- 2) Rewind and select 200 BPI.

- 3) If odd record of current data pattern, select binary; if even, select BCD.

- 4) Do direct output of 500 words.

- 5) Check for alarm up on tape unit.

- 6) If 20 records of current data pattern have not been written go to 3).

- 7) If all data patterns have not been used, change patterns and go to 3).

- 8) Rewind.

- 9) Initialize data pattern and record count.

- 10) If odd record, select binary; if even, select BCD.

- 11) Do direct input of 500 words.

- 12) Check for alarm up on tape unit.

- 13) Check the data.

- 14) If 20 records of current pattern have not been read, go to 10).

- 15) If all data patterns have not been used, change patterns and go to 10).

- 16) Rewind.

- 17) Return to distributor.

- 7. Section 5

- a. Purpose: Check the ability of a 1716 to transfer a block of data from an area of storage to a different area within the same computer.

- b. Procedure

- 1) Set reserve on 1716.

- 2) Set up output area.

- 3) Select Interrupt on End of Operation.

- 4) Initiate buffered transfer and exit to SMM until complete.

- 5) Check if interrupt occurred.

- 6) Check data.

- 7) Go back to 3) if the current data pattern has not been buffered 100 times.

- Change data patterns and go back to 2) if all patterns have not been used.

- 9) Clear reserve.

- 10) Return to distributor.

- 8. Section 6

- a. Purpose: Check the ability of a 1716 transfer data between two 17X4 Computers.

- b. Procedure: In the following sequence of steps, Computer A is initially defined as the computer in which bit 14 of Q equals 1 on the third parameter stop. The other computer is B. TMESS is an absolute location in "this" computer (location 0052). OMESS is the same absolute location in the "other" computer.

- 1) If computer B, go to 22).

- 2) Set reserve on 1716.

- 3) Wait for B to set OMESS to its FWA of data area.

- 4) Initiate buffered transfer to B.

- 5) Set flags equal to the lower five bits of code which identify the data pattern.

- 6) Transfer data code to OMESS.

- 7) Wait for OMESS to change values.

- 8) If negative, B found at least one data error.

- 9) Initiate buffered transfer from B to A.

- 10) Check data.

- 11) Go to 4) if current pattern has not been transferred 100 times.

- 12) Go to 14) if all data patterns have been transferred.

- 13) Change data patterns and go to 4).

- 14) If this computer was initially B, go to 18).

- 15) Clear reserve on 1716.

- 16) Store 0 at TMESS, -0 at OMESS.

- 17) Switch names of computers and go to 22).

- 18) Stop at end of section.

- 19) If section is to be repeated, go to 15).

- 20) Store 0 at TMESS, 0 at OMESS.

- 21) Clear reserve and return to distributor.

## Computer B

- 22) Clear reserve on 1716.

- 23) Set TMESS equal to FWA of buffer area.

- 24) Wait for TMESS to change values.

- 25) If TMESS is -0, go to 31).

- 26) If TMESS is 0, go to 32).

- 27) Check for flags equal to same configuration as lower 5 bits of TMESS.

- 28) Check data.

- 29) If data errors, store the complement of the number of errors at TMESS and go to 24).

- 30) Go to 32).

- 31) Store 0 at TMESS, change names, and go to 2).

- 32) Stop at end of section.

- 33) Return to distributor.

#### III. PHYSICAL REQUIREMENTS

- A. SPACE REQUIRED Approximately 2500<sub>10</sub> locations.

- B. INPUT AND OUTPUT TAPE MOUNTINGS If Section 2, 3, or 4 is selected to be run a 601/608/609 Tape Unit must be write-labeled and non-protected.

- C. TIMING 3 min. 15 sec.

- D. EQUIPMENT CONFIGURATION computer with 8K memory.

- 1. Section 1 17X4, 1705, 17X6

- 2. Section 2 17X4, 1705, 17X6, 1731/1732, 601/608/609

- 3. Section 3 17X4, 1705, 17X6, 1731/1732, 601/608/609

- 4. Section 4 17X4, 1705, 17X6, 1731/1732, 601/608/609

- 5. Section 5 17X4, 1705, 1716

- 6. Section 6 two 17X4's, two 1705's, one 1716

## 1738/853, 854 DISK PACK TEST

### (DP1008 Test No. 8) (CP=2F)

#### I. OPERATIONAL PROCEDURE

### A. RESTRICTIONS

- 1. Cautions to User

- a. The range of cylinders upon which data will be written may be limited during the parameter stop. However, the lower limit is ignored in Section 12 (data is written in cylinder 0 to be autoloaded).

- b. A large number of typeouts and/or stops may occur for error codes 14,

1B, and 1D unless bit 11 of the Stop/Jump parameter is set.

- c. There may be insufficient core for a long buffer operation if memory is only 8k and more than one test is loaded before the disk pack test is loaded. In this case neither section 6 nor 9 will be run unless the operator selects one or both of them. If the operator selects 6 or 9 in this case, short buffer operations are performed and each of these two sections may take an hour for an 853 disk drive unit.

- d. Section 7 (overlap seek) requires two disk packs. If an attempt is made to run this section with only one disk pack, the program will loop on an external reject of an output from A, and the director status will become Not Ready and Not on Cylinder.