# CDC®1700 TRANSFORM WITH MICRO MEMORY DE402-A

GENERAL DESCRIPTION OPERATION INSTALLATION AND CHECKOUT THEORY OF OPERATION DIAGRAMS MAINTENANCE EQUATION SUMMARY

HARDWARE MAINTENANCE MANUAL

|                             | <b>REVISION RECORD</b>       |  |  |  |  |  |  |

|-----------------------------|------------------------------|--|--|--|--|--|--|

| REVISION                    | DESCRIPTION                  |  |  |  |  |  |  |

| 01                          | Preliminary manual released. |  |  |  |  |  |  |

| (10/75)                     |                              |  |  |  |  |  |  |

| Α                           | Manual released.             |  |  |  |  |  |  |

| (6/77)                      |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             | *                            |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

| ·····                       |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             | N                            |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

|                             |                              |  |  |  |  |  |  |

| Publication No.<br>96728700 |                              |  |  |  |  |  |  |

### REVISION LETTERS I, O, Q AND X ARE NOT USED

© 1977 by Control Data Corporation Printed in the United States of America

ii

Address comments concerning this manual to: Control Data Corporation Publications and Graphics Division 4455 Eastgate Mall La Jolla, California 92037

or use Comment Sheet in the back of this manual.

## MANUAL TO EQUIPMENT LEVEL CORRELATION SHEET

This manual reflects the equipment configurations listed below.

EXPLANATION: Locate the equipment type and series number, as shown on the equipment FCO log, in the list below. Immediately to the right of the series number is an FCO number. If that number and all of the numbers underneath it match all of the numbers on the equipment FCO log, then this manual accurately reflects the equipment.

| EQUIPMENT TYPE                           | SERIES               | WITH FCOs           | COMMENTS |

|------------------------------------------|----------------------|---------------------|----------|

| AA109-A<br>Ab109-b<br>AA123-b<br>AA123-C | 02<br>08<br>03<br>04 | ECO 14239/<br>14241 | ·        |

|                                          |                      |                     |          |

|                                          |                      |                     |          |

|                                          |                      |                     |          |

|                                          |                      |                     |          |

|                                          |                      |                     |          |

|                                          |                      |                     |          |

iii/iv

.

## LIST OF EFFECTIVE PAGES

|                                              |        | ······ |     |       |     | ·    |     | <b>.</b> |     |

|----------------------------------------------|--------|--------|-----|-------|-----|------|-----|----------|-----|

| PAGE                                         | REV    | PAGE   | REV | PAGE  | REV | PAGE | REV | PAGE     | REV |

| Cover                                        |        |        |     |       |     |      |     |          |     |

| Fitle page<br>i<br>ii/iv<br>v/vi<br>vii/viii | <br>A  |        |     |       |     |      |     |          |     |

| ii/iv<br>//vi                                | A<br>A |        |     |       |     |      |     |          |     |

| vii/viii<br>x                                | A<br>A |        |     |       |     |      |     |          |     |

| -1<br>-1<br>-1                               | A<br>A |        |     |       | ·   |      |     |          |     |

| -1<br>-1                                     | A<br>A |        |     |       |     |      |     |          |     |

| l–1 thru 4–15<br>i–1 thru 5–8                | A<br>A |        |     |       |     |      |     |          |     |

| 5-1                                          | A      |        |     |       |     |      |     |          |     |

| A-1<br>Comment sheet                         | A<br>A |        |     |       |     |      |     |          |     |

| Cover                                        |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     | · · · |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        | -      |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        | -      |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

|                                              |        |        |     |       |     |      |     |          |     |

New features, as well as changes, deletions, and additions to information in this manual, are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

PREFACE

This manual is intended to be used in conjunction with the CONTROL DATA  $^{\textcircled{R}}$  Basic Micro-Programmable Processor Hardware Maintenance Manual to form a system manual. It contains the theory of operation, diagrams and maintenance information for the CONTROL DATA<sup>®</sup> DE402-A 1700 Transform with Read-Only Micro Memory. Information presented in this manual is intended for use by maintenance personnel in training and in the field.

The logic diagrams, parts data, and wire lists for this equipment are included in the field print package. Other documents that may be of use to the reader are listed below.

Refer to the Basic Micro-Programmable Processor Hardware Maintenance Manual for a listing of additional applicable documents and for a detailed description of the micro processor.

| Title                                                                           | Publication Number   |

|---------------------------------------------------------------------------------|----------------------|

| 1700 Transform with ROM Field Print Package                                     | 96751300             |

| Basic Micro-Programmable Processor Hardware<br>Maintenance Manual               | 39451400             |

| CYBER 18 Computer Systems Installation Manual                                   | 39451500             |

| CYBER 18 Processor with Core Memory (Macro<br>Level) Reference Manual           | 88973500             |

| CYBER 18-05/10 Computer Systems Hardware<br>Maintenance Manual, Volumes 1 and 2 | 96767500<br>96767600 |

| CYBER 18 Processor with MOS Memory (Macro<br>Level) Hardware Reference Manual   | 96768300             |

| CYBER 18 Processor (Micro Level) Reference<br>Manual                            | 88973400             |

## CONTENTS

| 1. GENERAL DESCRIPTION                                                 | 1-1                      |

|------------------------------------------------------------------------|--------------------------|

| Scope<br>Physical Description<br>Electrical Description<br>Environment | 1-1<br>1-1<br>1-1<br>1-1 |

| 2. OPERATION                                                           | 2-1                      |

| 3. INSTALLATION AND CHECKOUT                                           | 3-1                      |

| 4. THEORY OF OPERATION                                                 | 4-1                      |

| Instruction Transform (IXT) Register                                   | 4-2                      |

| IXT' Register                                                          | 4-2                      |

| MA Transform                                                           | 4-3                      |

| K/N Transform                                                          | 4-7                      |

| Bit Test Decoder                                                       | 4-7                      |

| MIR Encode                                                             | 4-7                      |

| Delta Translator                                                       | 4-8                      |

| Read-Only Micro Memory                                                 | 4-8                      |

| 1700 Emulator                                                          | 4-8                      |

| Miscellaneous Circuitry                                                | 4-9                      |

| Protect Violation Detecting Circuit                                    | 4-9                      |

| Interrupt Enable                                                       | 4-10                     |

| XTBLKT4 Signal Generation                                              | 4-11                     |

| BLKM100 Signal Generation                                              | 4-11                     |

А

4-1

4-2

4-3

4-4

4-5

5-1

5 - 2

**Equation Summary**

MA Transforms

K/N Transforms

Instruction LDA

1700 Transform Module Block Diagram

Step-by-Step Emulation of Macro

MA Transform Selection for 1700

**Storage Reference Instructions**

Micro-Code Subroutines to Emulate LDA Micro Instructions

1700 Transform with Read-Only Micro

Memory Functional Block Diagram

External Interface 4-13 DIAGRAMS 5. 5-1 1700 Transform Functional Block Diagram 5-1 Instruction Transform (IXT) Register 5-1 IXT' Register MA Transform 5-1 5-1 K/N Transforms 5-1 5-3 5-3 Bit Test Decoder MIR Encode Delta Translator 5-3 Read-Only Micro Memory 5-4 Upper/Lower Micro-Memory Data Select 5-5 **Miscellaneous** Circuitry 5-5 Protect Violation Detecting Circuit 5-5 Interrupt Enable 5-6 XTBLKT4 Signal Generator 5-6 BLKM100 Signal Generator 5-6 1700 Transform/Processor Interface Signals 5-6 Logic Diagrams 5-6 6. MAINTENANCE 6-1 **Preventive Maintenance** 6-1

Typical 1700 Macro Instruction Emulation

## **APPENDIX**

Calibration and Adjustment

Troubleshooting

### A-1

4-2

4-3

4-8

4-12

4-13

5-2

5-3

## FIGURES

| 5-3 | MA Transform Selection for 1700<br>Register Reference and Inter-Register |     |

|-----|--------------------------------------------------------------------------|-----|

|     | Reference Instructions                                                   | 5-3 |

| 5-4 | MIR Transform of 1700 Storage                                            |     |

|     | Reference Instructions                                                   | 5-4 |

| 5-5 | MIR Transforms of 1700 Register                                          |     |

|     | Reference Instructions                                                   | 5-4 |

| 5-6 | Simplified Read-Only Micro Memory                                        |     |

|     | Block Diagram                                                            | 5-5 |

| 5-7 | Interconnecting Diagram Between 1700                                     |     |

|     | Transform Module and Basic Processor                                     | 5-7 |

|     |                                                                          |     |

#### ix

4-11

6-1

6-1

## TABLES

| 4-1 | Transform Operations               | 4-1 | 4-5 | 1700 Inter-Register Transforms       |      |

|-----|------------------------------------|-----|-----|--------------------------------------|------|

| 4-2 | MA Transform Applications          | 4-4 |     | During GETMAK/XT Operation           | 4-6  |

| 4-3 | 1700 Storage Reference Transforms  |     | 4-6 | Emulation Test Conditions            | 4-9  |

|     | During GETMAK/XT Operation         | 4-4 | 4-7 | Delta Translations                   | 4-10 |

| 4-4 | 1700 Register Reference Transforms |     | 4-8 | Glossary of Terms (External Signals) | 4-14 |

|     | During GETMAK/XT Operation         | 4-5 | 5-1 | K/N Transform Position Selection     | 5-3  |

96728700 A

## SCOPE

This manual contains the functional and physical descriptions of the 1700 transform with read-only micro memory. The 1700 transform module, when used with the basic micro processor, allows the 1700 instruction repertoire to be emulated more efficiently. This manual completes the CYBER 18 Processor Hardware Maintenance Manual when combined with the Basic Micro-Programmable Processor Hardware Maintenance Manual.

### PHYSICAL DESCRIPTION

The 1700 transform module consists of one 11 by 14 inch printed circuit board, which plugs into slot R of the processor chassis.

## **ELECTRICAL DESCRIPTION**

The 1700 transform module requires +5 V dc, which is obtained from the main central processor unit (CPU) power supply. This module draws approximately 4 amperes (average power consumption is about 20 watts).

The logic level of the 1700 transform module is transistortransistor logic (TTL) level as follows:

| Logical zero (low): | 0.4 V dc or less  |

|---------------------|-------------------|

| Logical one (high): | +2.4 to 5.25 V de |

### ENVIRONMENTAL CONDITIONS

Refer to the Basic Micro-Programmable Processor Hardware Maintenance Manual for information on the environmental requirements of the 1700 transform.

Once installed, the 1700 transform module requires no operation or programming.

2-1

÷

Information for this section is contained in the CYBER 18 computer systems installation manual and in the systems level CYBER 18 computer systems hardware maintenance manual.

96728700 A

--

X

The 1700 transform with read-only micro memory is used to emulate the CDC<sup>®</sup> 1700 computer instruction repertoire when it is combined with the basic micro processor to form the 1700 enhanced processor. The emulation process utilizes both hardware and firmware for more efficient operation.

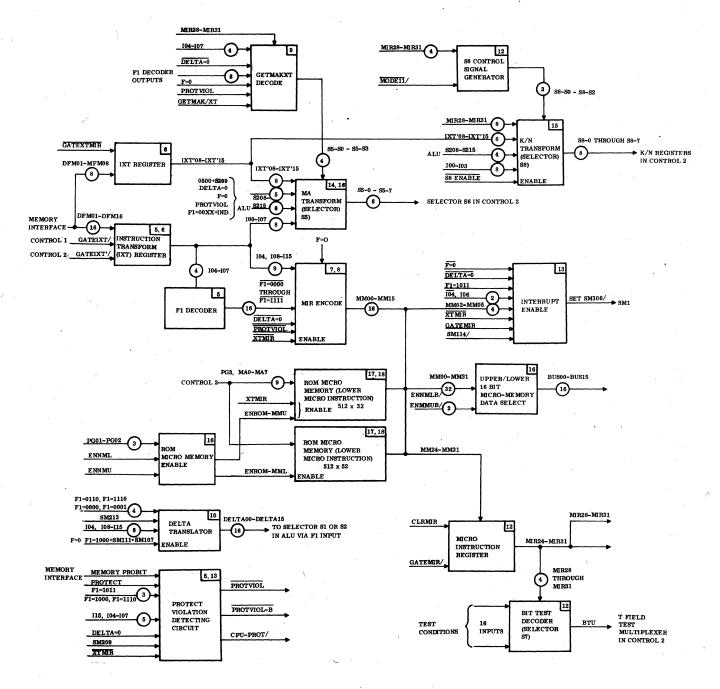

The firmware consists mainly of many micro-code subroutines that emulate 1700 macro instructions; therefore, it is also called the 1700 emulator. For each 1700 macro instruction, there exists a corresponding subroutine required to emulate it. To start the emulation, the macro instruction is read out from macro memory by a portion of the micro The macro instruction is then decoded by program. hardware; this hardware decoder is called the transform. The transform **provides the** micro program with the capability to select patterns of bits from the registers and the data transmission path of the processor to form the micromemory address. This micro-memory address selects the appropriate micro-code subroutine to emulate the macro instruction. More than one transform operation may be required to completely emulate a macro instruction. The transform also sets the parameters, generates the micro code needed for the arithmetic and logical operation (refer to MIR Encode) during the emulation process, and sets the contents of the N and K registers.

There are three types of transforms:

- MA transform

- K or N transform

- Combined MA and K transform

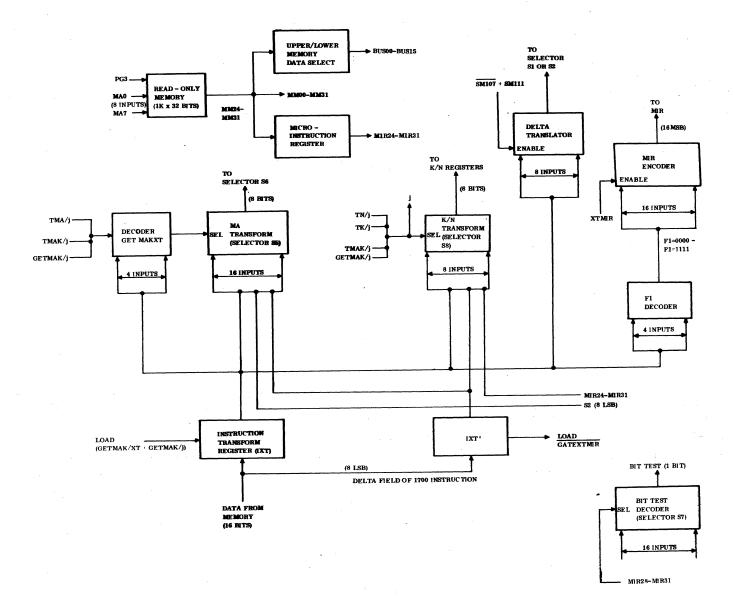

The transform commands are coded in the C field of the micro instruction as TMA/j, TN/j, GETMAK/j, and GETMAK/XT. The letter j is decoded from the lower four bits (MIR28 through MIR31) of the micro-instruction register for the MA transform and the lower three bits (MIR29 through MIR31) for the K and N transform. These bits specify the selector position of the MA transform and of the K and N transform. Table 4-1 lists the operations that result when the above transform commands are executed. Figure 4-1 is the block diagram of the 1700 transform module.

### TABLE 4-1. TRANSFORM OPERATIONS

| Mnemoni <b>cs</b>             | Operation                                                                                                                                                                                                                                                                                            |  |  |  |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TMA/j                         | Obtain mext micro-instruction pair from the address specified by MA transform (selector S5), setting j.                                                                                                                                                                                              |  |  |  |  |

| TK/j                          | Set K register to value specified by K transform (selector S8), setting j.                                                                                                                                                                                                                           |  |  |  |  |

| TN/j                          | Set N register to value specified by N transform (selector S8), setting j.                                                                                                                                                                                                                           |  |  |  |  |

| TMAK/j                        | An MA and K transform is executed based on the value of j.                                                                                                                                                                                                                                           |  |  |  |  |

| getmak/j <sup>†</sup>         | 1. Output data from macro memory is gated into the instruction transform (IXT) register.                                                                                                                                                                                                             |  |  |  |  |

| i.                            | 2. An MA and K transform is executed based on the value of j.                                                                                                                                                                                                                                        |  |  |  |  |

| GETMAK/ <b>XT<sup>†</sup></b> | 1. Output data from macro memory is gated into the IXT and IXT' registers.                                                                                                                                                                                                                           |  |  |  |  |

|                               | 2. One of eight MA transforms is executed based on the macro instruction loaded into the IXT register (selected from selector S5, positions 8 through 15). The K register is always transformed from S8, position 7.                                                                                 |  |  |  |  |

|                               | 3. The most significant 16 bits of the micro instruction register (MIR) are loaded with a micro command encoded from the macro instruction residing in the IXT register. This operation is referred to as MIR transform (XT/MIR). The least significant 16 bits of MIR are loaded from micro memory. |  |  |  |  |

Figure 4-1. 1700 Transform Module Block Diagram

# INSTRUCTION TRANSFORM

This is a 16-bit register that holds the macro instruction currently being emulated. It receives inputs directly from macro (main) memory. The IXT register outputs are sent to the MA Transform, K/N transform, delta translator, and via the F1 decoder to the MIR encoder to be transformed. Other IXT register outputs are also sent to the GETMAK/XT decoder to generate the proper select signals for the MA transform during a GETMAK/XT operation. This register is loaded by executing a macro memory read micro instruction followed by a micro instruction into GETMAK/J or GETMAK/XT in the C" (double prime) field. Otherwise the IXT register can be loaded by executing a micro instruction with C' (prime) equal to 011xxxx to generate a general purpose strobe at time T4.

### IXT' REGISTER

The IXT' register is an 8-bit register that holds the eight least significant bits (delta field) of the 1700 macro instruction. This register provides emulation of the 1700 enhanced instructions that have double word format. Inputs to the IXT' register are obtained directly from macro (main) memory. The macro memory data is gated into this register by application of GATEXTMIR, which is generated only during the GETMAK/XT command. IXT' register outputs are sent to the MA and K/N transforms to be transformed.

### MA TRANSFORM

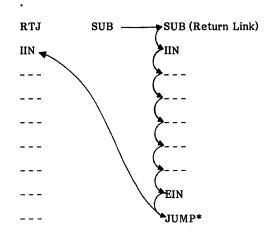

The MA transform (selector S5) is an 8-bit wide selector that is used to form micro-memory addresses. The MA transform provides selection of 16 different micro memory address (MA) transforms. These micro memory address transforms specify one of 256 64-bit emulation instructions contained within a micro memory page. The selection of each emulation instruction is determined by the j value of transform commands (TMA/j, TMAK/j, and GETMAK/j) or depends upon the macro instruction via transform hardware (MIR 28 through MIR 31, GETMAK/XT commands).

Figure 4-2 indicates 16 different instruction transforms. Transform selections (j value) 0 through 7 and 9 through C are applicable to emulation of enhanced 1700 instructions. Transform selections 8 through F are applicable to emula-

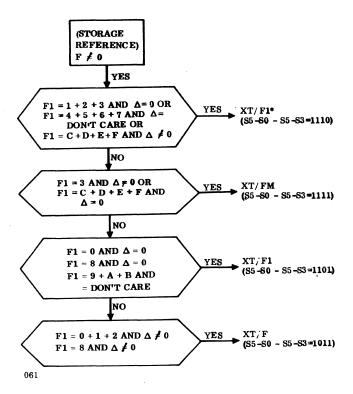

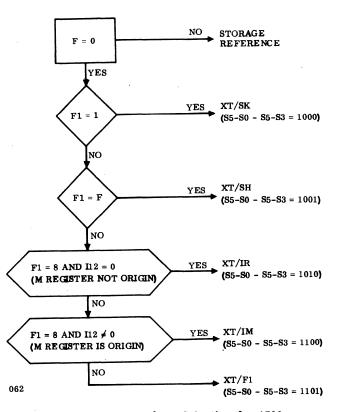

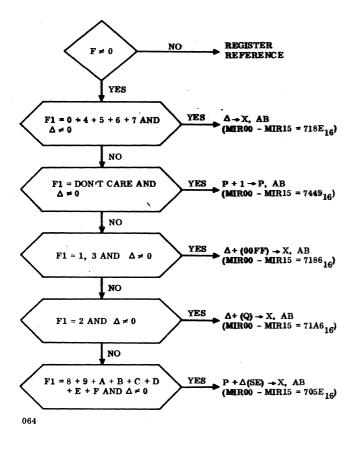

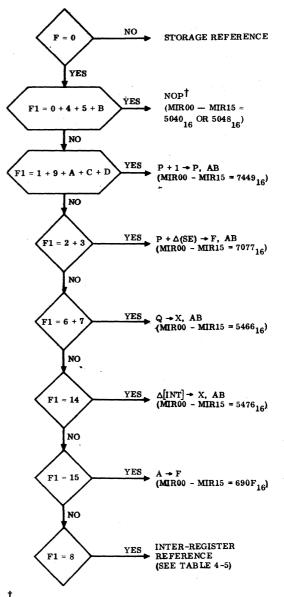

tion of the basic 1700 instruction set. The patterns of bits are derived from hardwired connections to +5 V and ground, IXT and IXT' registers, CPU selector S2, and special conditions (such as protect violation or indirect address mode) that are decoded from the macro instruction. Table 4-2 lists the 16 different MA transforms applied for different types of macro instructions and for different addressing modes. Whenever the GETMAK/XT command is executed, one of the eight MA transforms (8 through F) is selected, based on the macro instruction being emulated. Tables 4-3, 4-4, and 4-5 list the MA transforms for the basic 1700 instruction set storage reference ( $F \neq 0$ ), register reference, and inter-register reference instructions, respectively. The MA transforms for the enhanced instructions are selected by MA transform of instruction XT/F1 (j value D).

During GETMAK/XT operations, the MA transform select signals are derived from the TMA/j, TMAK/j, and GETMAK/j inputs to the GETMAK/XT decoder. During GETMAK/XT operations the MA transform select signals are derived from the MIR12 through MIR15 inputs obtained form the read only memory.

| INSTRUCTION            | j VALUE | TRANSFORM OUTPUT                                      | INSTRUCTION           | j VALUE |     | TRAN    | SFORM | I OUTPUT                     |                |

|------------------------|---------|-------------------------------------------------------|-----------------------|---------|-----|---------|-------|------------------------------|----------------|

|                        |         | 0 1 2 3 4 5 6 7                                       |                       |         | 0 1 | . 2     | 3     | 6                            | 7              |

| XT/INT                 | 0       | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | XT/SK                 | . 8     | 1   | 0       |       | IXT'<br>8 - 11)              | 0              |

| XT/IR2                 | 1       | 1 0 1 1 1 IXT'<br>(11 - 12) 0                         | XT/SH or<br>XT/DRP    | 9       | 1   | ) 1     | 1     | 0 IXT'<br>(08 - 10           | o)             |

| XT/F3A                 | 2       | 1 1 0 1 1 <b>IXT'</b><br>(13 - 15)                    | XT/IR or<br>XT/F3     | А       | 1   | 1       | 0     | IXT'<br>(12 - 15)            |                |

| XT/DEST                | 3       | 0 0 1 1 1 <b>IXT'</b> (13 - 15)                       | XT/F or<br>XT/F4      | В       | 1 0 | 0       |       | IXT'<br>00 - 03)             | 0              |

| XT/F3*                 | 4       | 1 1 1 1. <b>IXT'</b><br>(11 - 15)                     | XT/IM or<br>XT/SKIP 2 | с       | 1   | 1       | 1     | IXT'<br>(08 - 11)            |                |

|                        | 5       | 0 0 0 0 0 0 0 0                                       | XT/F1                 | D       | 0   | F=<br>0 | (     | IXT<br>(04 <del>-</del> .07) | Δ'=<br>0       |

| XT/F2                  | 6       | $1 	 0 	 1 	 0 	 IXT' 	 \Delta^{=} 	 0 	 0$           | XT/F1*                | F       | 1 0 | ) 1     | 0     |                              | IXT<br>5 - 07) |

| <b>X</b> T/ <b>S</b> 2 | 7       | S2, LOWER 8 BITS<br>(08 through 15)                   | XT/FM                 | F       | 1   | 0 1     | 1     | 1 0 c <sup>†</sup>           | Dţ             |

|                        | •       |                                                       |                       |         |     |         |       |                              |                |

<sup>†</sup>A = (IXT=0500) + S209

= IIN instruction or false attempt

B = (F1=00xx) + MULTILEVEL INDIRECT MODE

C = Protect violation

$\mathbf{D} = (\Delta' = \mathbf{0}) + \mathbf{B}$

060

| Instruction          | MIR28-MIR31 = j | Application                                                                      |  |  |  |  |

|----------------------|-----------------|----------------------------------------------------------------------------------|--|--|--|--|

| XT/INT               | 0               | Micro/macro interrupt                                                            |  |  |  |  |

| XT/IR2               | 1               | Inter-register type 2 instruction                                                |  |  |  |  |

| XT/F3A               | 2               | Field instruction                                                                |  |  |  |  |

| XT/DEST              | 3               | Register destination                                                             |  |  |  |  |

| XT/F3*               | 4               | Miscellaneous instruction                                                        |  |  |  |  |

|                      | 5               | Not used                                                                         |  |  |  |  |

| XT/F2                | 6               | F2 (address mode) for enhanced instruction                                       |  |  |  |  |

| XT/S2                | . 7             | Selector S2 (lower eight bits); normally used for the breakpoint panel           |  |  |  |  |

| XT/SK                | 8               | Skip instruction                                                                 |  |  |  |  |

| XT/SH or<br>XT/DRP   | 9               | Shift instruction, or decrement and repeat instruction                           |  |  |  |  |

| XT/IR or<br>XT/F3    | Α               | Inter-register instruction with M not the origin, or miscellaneous instruction   |  |  |  |  |

| XT/F or<br>XT/F4     | В               | F (OP CODE) field, or OP CODE for storage reference type 2 and field instruction |  |  |  |  |

| XT/IM or<br>XT/SKIP2 | С               | Inter-register with M origin, or skip isntruction type 2                         |  |  |  |  |

| XT/F1                | D               | F1 (address mode) field                                                          |  |  |  |  |

| XT/F1*               | Е               | Alternate F1 field                                                               |  |  |  |  |

| XT/FM                | F               | Miscellaneous F1 field                                                           |  |  |  |  |

## TABLE 4-2. MA TRANSFORM APPLICATIONS

## TABLE 4-3. 1700 STORAGE REFERENCE TRANSFORMS DURING GETMAK/XT OPERATION

| Mode                 | F1<br>(Binary) | Hexadecimal | Delta    | Instruction      | MIR Transform                                                    |

|----------------------|----------------|-------------|----------|------------------|------------------------------------------------------------------|

| Absolute<br>Constant | 0000           | 0 ~         | ≠0<br>=0 | XT/F<br>XT/F1    | $\Delta \rightarrow X, AB$<br>P + 1 $\rightarrow$ P, AB          |

| Absolute<br>Constant | 0001           | . 1         | ≠0<br>=0 | XT/F<br>XT/F1*   | $\Delta + (00FF) \rightarrow X, AB$<br>P + 1 $\rightarrow$ P, AB |

| Absolute<br>Constant | 0010           | 2           | ≠0<br>=0 | XT/F<br>XT/F1*   | $\Delta + (Q) \rightarrow X, AB$ $P + 1 \rightarrow P, AB$       |

| Absolute<br>Constant | 0011           | 3           | ≠0<br>=0 | XT/FM<br>XT/F1*  | $\Delta + (00FF) \rightarrow X, AB$<br>P + 1 $\rightarrow$ P, AB |

| Indirect<br>Storage  | 0100           | 4           | ≠0<br>=0 | XT/F1*<br>XT/F1* | $\Delta \rightarrow X, AB$<br>P + 1 $\rightarrow$ P, AB          |

| Mode                                   | F1<br>(Binary) | Hexadecimal | Delta    | Instruction      | MIR Transform                                                   |

|----------------------------------------|----------------|-------------|----------|------------------|-----------------------------------------------------------------|

| Indirect<br>Storage                    | 0101           | 5           | ≠0<br>=0 | XT/F1*<br>XT/F1* | $\Delta \rightarrow X, AB$<br>P + 1 $\rightarrow$ P, AB         |

| Indirect<br>Sto <b>ra</b> ge           | 0110           | 6           | ≠0<br>=0 | XT/F1*<br>XT/F1* | $\Delta \rightarrow X, AB$<br>P + 1 $\rightarrow$ P, AB         |

| Indirect<br>Storage                    | 0111           | 7           | ≠0<br>=0 | XT/F1*<br>XT/F1* | $\Delta \rightarrow X, AB$<br>P + 1 $\rightarrow$ P, AB         |

| Relative<br>16-bit relative            | 1000           | 8           | ≠0<br>=0 | XT/F<br>XT/F1    | $P + \Delta(SE) \rightarrow X, AB$<br>$P + 1 \rightarrow P, AB$ |

| Relative<br>16-bit relative            | 1001           | 9           | ≠0<br>=0 | XT/F1<br>XT/F1   | $P + \Delta(SE) \rightarrow X, AB$<br>$P + 1 \rightarrow P, AB$ |

| Relative<br>16-bit relative            | 1010           | A           | ≠0<br>=0 | XT/F1<br>XT/F1   | $P + \Delta(SE) \rightarrow X, AB$<br>$P + 1 \rightarrow P, AB$ |

| Relative<br>16-bit relative            | 1011           | В           | ≠0<br>=0 | XT/F1<br>XT/F1   | $P + \Delta(SE) \rightarrow X, AB$<br>$P + 1 \rightarrow P, AB$ |

| Relative indirect<br>Relative indirect | 1100           | С           | ≠0<br>=0 | XT/F1*<br>XT/FM  | $P + \Delta(SE) \rightarrow X, AB$<br>$P + 1 \rightarrow P, AB$ |

| Relative indirect<br>Relative indirect | 1101           | D           | ≠0<br>=0 | XT/F1*<br>XT/FM  | $P + \Delta(SE) \rightarrow X, AB$<br>$P + 1 \rightarrow P, AB$ |

| Relative indirect<br>Relative indirect | 1110           | Е           | ≠0<br>=0 | XT/F1*<br>XT/FM  | $P + \Delta(SE) \rightarrow X, AB$<br>$P + 1 \rightarrow P, AB$ |

| Relative indirect<br>Relative indirect | 1111           | F           | ≠0<br>=0 | XT/F1*<br>XT/FM  | $P + \Delta(SE) \rightarrow X, AB$<br>$P + 1 \rightarrow P, AB$ |

## TABLE 4-3. 1700 STORAGE REFERENCE TRANSFORMS DURING GETMAK/XT OPERATION (Contd)

### TABLE 4-4. 1700 REGISTER REFERENCE TRANSFORMS DURING GETMAK/XT OPERATION

| F1 (Binary) | Instruction | MIR Transform                       | Comment                                               |

|-------------|-------------|-------------------------------------|-------------------------------------------------------|

| 0000        | XT/F1       | NOP                                 | Selective stop (∆=0)<br>Instruction enhanced (∆≠0)    |

| 0001        | XT/SK       | P + 1 → P, AB                       | Skip                                                  |

| 0010        | XT/F1       | $P + \Delta(SE) \rightarrow F$ , AB | Input to A                                            |

| 0011        | XT/F1       | P + Δ(SE) → F, AB                   | Output from A                                         |

| 0100        | XT/F1       | NOP                                 | Enable interrupt (∆=0)<br>Instruction enhanced (∆≠0)  |

| 0101        | XT/F1       | NOP                                 | Inhibit interrupt (∆=0)<br>Instruction enhanced (∆≠0) |

| F1 (Binary) | Instruction | MIR Transform                                      | Comment                                                   |

|-------------|-------------|----------------------------------------------------|-----------------------------------------------------------|

| 0110        | XT/F1       | $\mathbf{Q} \rightarrow \mathbf{X}, \ \mathbf{AB}$ | Set program protect (∆=0)<br>Instruction enhanced (∆≠0)   |

| 0111        | XT/F1       | <b>Q →</b> X, AB                                   | Clear program protect (∆=0)<br>Instruction enhanced (∆≠0) |

| 1000        | t           | †                                                  | Inter-register                                            |

| 1001        | XT/F1       | $P + 1 \rightarrow P$ , AB                         | Increase A                                                |

| 1010        | XT/F1       | $P + 1 \rightarrow P$ , AB                         | Enter A                                                   |

| 1011        | XT/F1       | NOP                                                | Pass (∆=0)<br>Instruction enhanced (∆≠0)                  |

| 1100        | XT/F1       | $P + 1 \rightarrow P$ , AB                         | Enter Q                                                   |

| 1101        | XT/F1       | P + 1 → P, AB                                      | Increase Q                                                |

| 1110        | XT/F1       | $\Delta(INT) \rightarrow X, AB$                    | Exit interrupt                                            |

| 1111        | XT/SH       | A → F                                              | Shift                                                     |

TABLE 4-4. 1700 REGISTER REFERENCE TRANSFORMS DURING GETMAK/XT OPERATION (Contd)

## TABLE 4-5. 1700 INTER-REGISTER TRANSFORMS DURING GETMAK/XT OPERATION

|                      | Ins           | struction       |                 |                                                                   |            |          | Condi    | tion     |             |          |          |

|----------------------|---------------|-----------------|-----------------|-------------------------------------------------------------------|------------|----------|----------|----------|-------------|----------|----------|

|                      |               | XT/IR<br>XT/IM  |                 | M not origin register (I12 ≠ 0)<br>M is origin register (I12 = 0) |            |          |          |          |             |          |          |

|                      | MIR Transform |                 |                 |                                                                   | Conditions |          |          |          |             |          |          |

|                      |               | Fields)         |                 |                                                                   |            |          | Origin   |          | Destination |          |          |

| F<br>Bits 2-6        | A<br>Bits 7-9 | B<br>Bits 10-12 | D<br>Bits 13-15 | LP<br>I8                                                          | XR<br>I9   | A<br>I10 | Q<br>I11 | M<br>I12 | A<br>I13    | Q<br>114 | M<br>115 |

| ADDT<br>11001        | -             | -               | -               | 0                                                                 | 0          | Х        | X        | 0        | Х           | X        | X        |

| A B<br>01110         | -             | -               | -               | 1                                                                 | 0          | Х        | x        | 0        | X           | x        | x        |

| A + B<br>01001       | -             | -               |                 | 0                                                                 | 1          | Х        | x        | 0        | X           | x        | X        |

| (-A) + (-B)<br>00001 | -             | -               | -               | 1                                                                 | 1          | Х        | x        | 0        | x           | х        | x        |

| Instruction   |                   |                   | Condition                      |                                 |          |            |           |           |          |          |          |

|---------------|-------------------|-------------------|--------------------------------|---------------------------------|----------|------------|-----------|-----------|----------|----------|----------|

|               | XT/IR             |                   |                                | M not origin register (I12 ≠ 0) |          |            |           |           |          |          |          |

|               | Х                 | T/IM              |                                |                                 |          | M is c     | origin re | gister (I | 12 = 0)  |          |          |

|               | MIR Tr            | ansform           |                                |                                 |          |            | Condi     | tions     |          |          |          |

|               |                   | Fields)           |                                |                                 |          |            | Origin    |           | De       | stinatio | n        |

| F<br>Bits 2–6 | A<br>Bits 7-9     | B<br>Bits 10–12   | D<br>Bits 13-15                | LP<br>I8                        | XR<br>I9 | A<br>I10   | Q<br>I11  | M<br>I12  | A<br>I13 | Q<br>I14 | M<br>I15 |

| ADD+<br>11010 | P register<br>001 | Zeros<br>001      | P register <sup>†</sup><br>001 | х                               | x        | X          | x         | 1         | x        | х        | Х        |

| -             | Ones<br>110       | -                 | -                              | х                               | x        | 0          | x         | 0         | x        | Х        | х        |

| -             | A register<br>100 | -                 | -                              | Х                               | x        | 1          | x         | 0         | x        | Х        | х        |

| -             | -                 | Ones<br>110       | -                              | X                               | X        | X          | 0         | 0         | x        | Х        | х        |

| -             | -                 | Q register<br>100 | -                              | Х                               | x        | <b>X</b> . | 1         | 0         | x        | Х        | х        |

| -             | -                 | -                 | NOP<br>000                     | x                               | x        | x          | x         | 0         | 0        | 0        | 0        |

|               | -                 | -                 | A register <sup>†</sup><br>101 | х                               | x        | x          | x         | 0         | 1        | X        | x        |

| -             | -                 | -                 | Q register <sup>†</sup><br>011 | х                               | x        | x          | x         | 0         | 0        | 1        | x        |

| -             | -                 | -                 | F register<br>111              | х                               | x        | x          | x         | 0         | 0        | 0        | X        |

### TABLE 4-5. 1700 INTER-REGISTER TRANSFORMS DURING GETMAK/XT OPERATION (Contd)

## K/N TRANSFORM

The K/N transform (selector S8) is an 8-bit wide selector that chooses one of eight instruction transforms to be loaded into the CPU K and N registers. Figure 4-3 indicates the eight K/N transform assignments. Bit patterns for creation of the transform outputs are derived from direct ground connections, eight bits from CPU selector S2 (S208 through S215), IXT and IXT' registers, and eight bits from the CPU micro instruction register (MIR24 through MIR31). The K/N transform is enabled by receipt of an S8ENABLE/ (low). The S8ENABLE/ (high) disables the K/N transform during the clear K register, clear N register, and clear N and page register commands. These clear commands allow all zeros to be loaded into the respective (K or N) register.

## **BIT TEST DECODER**

The bit test decoder (selector S7) is a 1-bit wide selector that provides for up to 16 different conditions (external/internal) to be tested. These tests determine whether the upper or lower micro instruction shall be executed from the next micro-instruction pair. The test bit is selected by the least significant four bits of the micro-instruction register (MIR28 through MIR31). The bit test output is sent to the T-field test multiplexer in the control 2 module and is tested if the T field of the micro instruction contains a BTU command. Table 4-6 list the conditions to be tested by the 1700 emulator during the emulation process.

### MIR ENCODE

During GETMAK/XT command, the macro instruction is encoded from the F1 bits of the 1700 instruction. the F1 bit values select the various configuration of the upper 16 bits (MM00 through MM15) that are loaded into the CPU MIR register. These micro memory instructions control the arithmetic functions for read next instruction cycles and other required operations to provide efficient execution. The various types of MIR transforms, based on the macro instruction being emulated, are listed in tables 4-3, 4-4, and 4-5 for storage, register, and inter-register reference

| INSTRUCTION        | j VALUE | 1 | TRANSFORM OUTPUT                             |   |   |                  |                   |  |  |  |

|--------------------|---------|---|----------------------------------------------|---|---|------------------|-------------------|--|--|--|

| XT/S2              | 0       | 0 | 0 7<br><b>S2,</b> LOWEST 8 BITS<br>(08 - 15) |   |   |                  |                   |  |  |  |

| XT/SHCNT           | 1       | o | 0 0 0 IXT'<br>(11 - 15)                      |   |   |                  |                   |  |  |  |

| XT/FLDL <b>T</b> H | 2       | 0 | 0                                            | 0 | 0 | IXT<br>(04 - 07) |                   |  |  |  |

| XT/RA              | 3       | 0 | 0                                            | 0 | 0 | 0                | IXT'<br>(10 - 12) |  |  |  |

| XT/RA*             | 4       | 0 | 0                                            | 0 | 0 | 0                | IXT'<br>(08 - 10) |  |  |  |

| XT/RB              | 5       | 0 | 0                                            | 0 | 0 | 0                | IXT'<br>(13 - 15) |  |  |  |

| XT/MIR             | 6       |   | MIR, LOWEST 8 BITS<br>(24 - 31)              |   |   |                  |                   |  |  |  |

| XT/FLDSTR<br>063   | 7       | 0 | 0                                            | 0 | 0 |                  | XT<br>00 - 03)    |  |  |  |

Figure 4-3. K/N Transforms

instructions, respectively. Figure 5-4 shows the MIR transform selections for storage reference instructions, and figure 5-5 shows the MIR transform selections for register reference instructions. These figures illustrate the selection conditions and not the sequential steps that select the MIR transform.

## **DELTA TRANSLATOR**

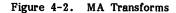

To emulate certain basic and enhanced 1700 instructions, the delta field of the macro instruction figure 4-4 must be modified:

This modification is necessary before the delta field can be processed for operations indicated by MIR, transforms. Table 4-7 lists the conditions and modified delta field. The delta translator translates the delta field according to the type of macro instructions being emulated as indicated in table 4-4. The delta translator is enabled by conditions of SM107, SM111, F field, and F1 field:

- SM107 is not set (decimal arithmetic correction logic is disabled).

- SM111 is not set (the CPU file F1 output to selectors S1 and S2 is disabled and delta translator output to selectors S1 and S2 is enabled).

- F = 0 and F1 = 1000 are low (the inter-register reference instruction is not selected).

When an inter-register reference instruction is emulated, the delta translator is disabled. This causes the delta  $(FFFF_{1R})$  to be sent to selector S1 and S2.

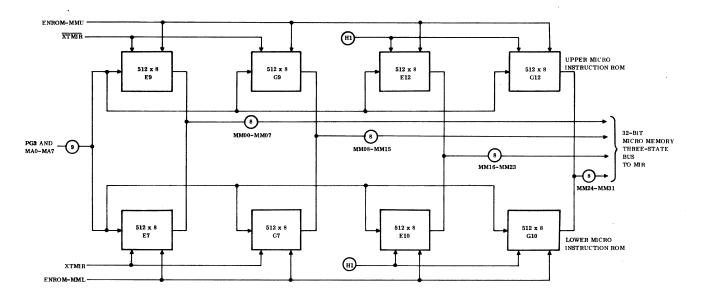

## **READ-ONLY MICRO MEMORY**

The micro memory of the 1700 transform module is a readonly memory that has been preprogrammed with the 1700 instruction emulator. This micro memory consists of 512 64-bit words (two pages). Each word consists of two micro instructions that are referred to as upper (32 bit) and lower (32 bit). Each word in the micro memory is addressed by the memory address bits (MA0 through MA7, PG3). The MA0 through MA7 specify one of 256 words (micro instruction pairs, 32-bit upper and 32-bit lower instruction within a page. The page (PG3) selects the page (page 0 or 1) in which the instruction resides. The output of the read-only memory is coupled to the upper/lower memory data select where the sequence of selection (upper or lower) is determined in accordance with the emulation required. The selected instruction is transferred via the CPU three-state bus to the X register.

### **1700 EMULATOR**

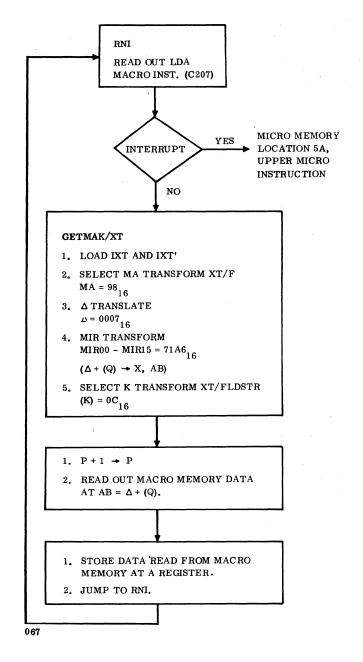

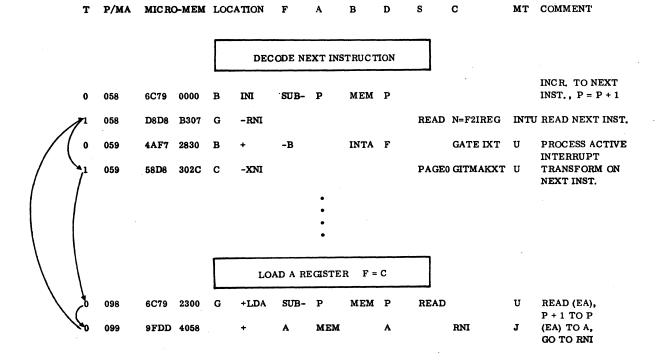

The 1700 emulator is the firmware program that emulates both the basic and enhanced 1700 computer instruction set. The emulator also contains firmware for handling I/O operations, macro and micro interrupts, auto-data transfer (ADT) operations, and panel simulation. The 1700 emulator consists of micro-memory subroutines that are preprogrammed in the read-only memory. These subroutines are completely contained in the two pages (0 and 1, 1024 32-bit micro instructions) micro-memory. The 1700 emulator consists of many micro-code subroutines. Each subroutine micro code performs a specific task, such as generating and controlling the operations required to emulate a macro instruction. For example, the micro-code subroutine titled the decode-next-instruction subroutine is executed at the beginning of every new macro-instruction emulation. This subroutine resides in micro location  $058_{16}$  and  $059_{16}$  and includes the following micro instructions.

|                           |                                                                                                                                    | Sele | ector S7 |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|----------|

| Test Bit                  | Operation                                                                                                                          | Pin  | Position |

| BTU00                     | Not assigned                                                                                                                       | 8    | 0        |

| 102                       | Execute upper micro instruction if IO2 is a 1.                                                                                     | 7    | 1        |

| 107                       | Execute upper micro instruction if I07 is a 1.                                                                                     | 6    | 2        |

| 106                       | Execute upper micro instruction if I06 is a 1.                                                                                     | 5    | 3        |

| IND00FF                   | Execute upper micro instruction if STORE 00FF (index 1) status is true.                                                            | 4    | 4        |

| SM105/<br>(PROTECT FAULT) | Execute lower micro instruction if storage protect fault is detected.                                                              | 3    | 5        |

| SELSTOP                   | Execute lower micro instruction if selective stop switch is set.                                                                   | 2    | 6        |

| SELSKIP/                  | Execute lower micro instruction if selective skip switch is set.                                                                   | 1    | 7        |

| SM108<br>(PARITY ERROR)   | Execute lower micro instruction if storage parity error is detected.                                                               | 23   | 8        |

| BTU00                     | Not assigned                                                                                                                       | 22   | 9        |

| DELTA'=0                  | Execute upper micro instruction if delta equals 0 (LXT8 through $IXT15 = 0$ )                                                      | 21   | 10       |

| EA=OPER                   | Execute lower micro instruction if the effective address equals the operand.                                                       | 20   | 11       |

| EVENPAR                   | Execute upper micro instruction if memory parity line is true (even parity).                                                       | 19   | 12       |

| 100                       | Execute upper micro instruction if I00 is a 1.                                                                                     | 18   | 13       |

| MULTIND                   | Execute upper micro instruction if multilevel indirect address mode is selected.                                                   | 17   | 14       |

| SM105+SM108               | Execute upper micro instruction if previous macro memory write cycle was aborted (caused either by parity error or protect fault). | 16   | 15       |

### TABLE 4-6. EMULATION TEST CONDITIONS

- Increment to next instruction (INI)

- Read the next instruction (RNI) and check for interrupt. Go to process micro/macro interrupt subroutine if an interrupt occurred

- Transform GETMAK/XT on the next instruction (XNI) if there is no interrupt

At the end of every macro-instruction emulation, a jump command is used to branch to specific locations in the

decode-next-instruction subroutine to start the emulation of the next macro instruction.

## MISCELLANEOUS CIRCUITRY

### **PROTECT VIOLATION DETECTING CIRCUIT**

To emulate the 1700 series computer protect function, a combination of hardware and firmware (1700 emulator) is

### TABLE 4-7. DELTA TRANSLATIONS

| Conditions                                                                           | Delta (Δ)                                                                                 |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| a. (F=0) (F1 = 0xxx)                                                                 |                                                                                           |

| b. Enhanced instructions: (F=0) (F1 = 4 + 5) (r = 0) <sup><math>\dagger</math></sup> | $\Delta = 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0$                                          |

| a. (F=0) (F1 = 1xxx)                                                                 |                                                                                           |

| b. (F=0) (F1= 2 + 3)                                                                 | $\Delta(SE) \text{ (with sign extend)} = C C C C C C C C IO8 IO9 I10 I11 I12 I13 I14 I15$ |

| c. Enhanced instructions: (F=0) (F1 = 4 + 5) (r = 0) <sup><math>\dagger</math></sup> | Constant = I08                                                                            |

| a. (F=0) (F1=1)                                                                      | $\Delta(SK)$ (for skip instruction) =                                                     |

| b. (F=0) (F1= 0 + 6)                                                                 | 0 0 0 0 0 0 0 0 0 0 0 0 112 113 114 115                                                   |

| a. (F=0) (F1=E)                                                                      | ∆(INT) (for interrupt instruction =<br>0 0 0 0 0 0 0 1 108 109 110 111 112 113 114 115    |

| a. (F=0) (F1=8)                                                                      | $\Delta(FFFF) = 1 1 1 1 1 1 1 1 1 1 1 1 1$                                                |

required. The 1700 computer incorporates a program protect function that inhibits access into protected programs by nonprotected programs. The function develops around a memory protect bit that is contained in each word of macro (main) memory. The protect violation conditions detected by the 1700 transform hardware are:

- An attempt to execute instructions that are not protected

- An attempt to execute a protected instruction following the execution of a nonprotected instruction

- An attempt to execute an unprotected miscellaneous instruction with the protect switch set

All other violations, such as an attempt by a nonprotected instruction to write into a protected storage location, are detected by the macro memory interface hardware and processor hardware.

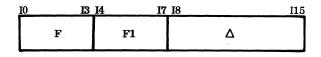

### INTERRUPT ENABLE

The 1700 computer systems require that the interrupt function be activated after on instruction has been executed following the enable interrupt instruction (EIN). A combination of hardware and firmware is required to prevent the interrupt function from being activated during the execution of the instruction following EIN if the instruction is either:

- A storage reference instruction with multilevel indirect address mode that requires more than one memory reference (more than one RNI cycle)

- An enhanced instruction with double-word format.

The implementation of the interrupt function is described below.

Status mode bit SM114 is first set by the 1700 emulator whenever the EIN is emulated to pre-enable the interrupt function. If the instruction following EIN is neither a storage reference instruction (F = 0) nor an enhanced instruction (except a type 2 skip instruction), the hardware enables the SETSM106 at the next RNI cycle which in turn sets SM106 to enable the CPU interrupt function. If the instruction following EIN is either a storage reference or enhanced instruction, SM106 is set after the 1700 emulator has executed a SUB- operation (increment P counter). The SUB- operation indicates the end of the macro instruction emulation. Once status mode bit SM106 is set, SM114 is cleared by the hardware.

1700 series computers also require that the inhibit interrupt instruction (IIN) tape precedence over enable interrupt

instructions (EIN). If the IIN instruction is executed after one instruction following an EIN (as in the following example) the macro interrupt function must be disabled.

#### Main Program

The 1700 emulator implements the above example as follows: whenever an interrupt is detected, the interrupt transform (XT/INT, MA transform 0) is performed. The XT/INT transform forms the micro memory address of BC<sub>16</sub> of BE<sub>16</sub> for the micro interrupt (S211 = 0) or macro interrupt (S211 = 1), respectively. If the interrupt is a macro interrupt, the emulator ignores the macro interrupt and rereads the macro instruction. (This has the same effect as disabling the macro interrupt function.) If the interrupt is a micro interrupt, the emulator processes the micro interrupt as normal.

If the macro interrupt being emulated is not an IIN instruction and there is no false interrupt, the XT/INT transform forms micro memory address  $BD_{16}$  or  $BF_{16}$  for the micro interrupt or macro interrupt, respectively. The interrupt is then processed accordingly by the micro or macro interrupt subroutine residing at the above address.

### **XTBLKT4 SIGNAL GENERATION**

During any operation except GETMAK/XT, the destination is decoded and strobed at time T4. However, during a GETMAK/XT transform operation, the previously read data is strobed into the destination register by the trailing edge of RESUME the read macro memory command. (Refer to the processor manuals for more details.) This allows the correct delta field to be used in emulation of the macro instruction.

### **BLKM100 SIGNAL GENERATION**

During macro step mode, the macro halt interrupt must be blocked while either a memory reference instruction or an enhanced instruction is emulated; this instruction is enabled only at the end of instruction execution. The following example with step- by-step operation of the emulator shows the need for the block mask bit 100 (BLKM100/) signal.

Assume that the machine is in step mode and is idling.

- 1. A macro GO command is executed (enter I: with function control register bit 12 clear).

- 2. The GO command sets SM215 (clear macro halt interrupt).

- 3. The RNI cycle is executed to read the instruction. Assume that the instruction is a memory reference instruction with multilevel indirect addressing mode. Check for interrupt. Since SM215 is set, there is no macro halt interrupt.

- 4. Perform the GETMAK/XT transform operation.

- 5. Hardware clears SM215 of either the breakpoint controller or the I/O-TTY mode whenever the CPU is in step mode and GETMAK/XT is executed. This sets the macro halt interrupt (enabled by mask bit M100).

- 6. The emulator executes a multilevel indirect address subroutine to look for the effective address. The interrupt is also checked.

- 7. Since the macro interrupt is set, the emulator branches to the interrupt subroutine and the instruction cannot be completed.

To avoid the problem in step 7, BLKM100/ must be generated to block the macro halt interrupt from being set to step 5. BLKM100/ is set low during a GETMAK/XT operation whenever a memory reference instruction or an enhanced instruction is decoded.

At the end of the above macro instruction emulation, the emulator executes a SUB- operation (increment the P counter), which sets the BLKM100/ signal high. BLKM100/ is also set high by the master clear.

# TYPICAL 1700 MACRO INSTRUCTION EMULATION

The following 1700 macro instruction, load A register, is selected to demonstrate the transform operation and the emulation of a macro instruction.

The above macro instruction loads the A register with the contents of the storage location specified by the effective address (EA). EA is  $\Delta + (Q)$ . Figure 4-4 shows the step-by-step emulation of this macro instruction in the form of a flow chart. Figure 4-5 lists the micro-code subroutines

required to emulate the instruction. First, the above instruction must be read out from macro memory using the read next instruction (RNI) cycle. Refer to the decodenext-instruction subroutine at location  $058_{16}$ . The interrupt is also checked. Assuming that there is no interrupt at this time, then the transform next instruction (XNI) cycle (the GETMAK/XT command) is executed. Execution of the GETMAK/XT command causes the following sequence of events.

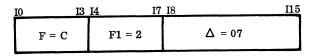

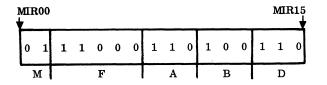

1. Data from memory is loaded into the IXT and IXT' registers. The IXT register now contains:

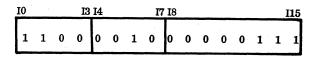

2. The output of the IXT register is decoded into j value select signals to select the MA transform. Refer to figure 5-2 for MA transform selection. For the macro instruction used in this example, the XT/F MA transform is selected since j value equals  $B_{16}$ . The output of the MA transform becomes:

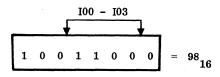

which is then applied to CPU selector S6 to designate the new micro-memory address (MA). The new micro-memory address,  $98_{16}$ , points to the load-A-register subroutine of the 1700 emulator.

- 3. If required, the outputs of the IXT and IXT' registers are also sent out to the delta translator circuit to be modified. In this example the output of the delta translator contains the following:

Refer to table 4-7 for more detail.

4. Simultaneously with the operations in step 2 and 3, the output of IXT is encoded to form the upper 16 bits (MM00 through MM15) of micro memory. Refer to figure 5-4.

During the GETMAK/XT operation, the read-only memory chips containing the upper 16 bits of micro memory data are disabled to allow the output of the MIR encoder to be loaded into MIR at time T5.

Figure 4-4. Step-by-Step Emulation of Macro Instruction LDA

Figure 4-5. Micro-Code Subroutines to Emulate LDA Micro Instructions

The upper 16 bits of MIR now contain:

- Where: F = 11000 indicates that this is an A+B operation

- A = 110 selects the output of file 1 as the A input to the ALU. Since status mode bit SM111 is clear, the output of the delta translator is used as the A input.

- B = 100 selects the Q register as the B input to the ALU.

- D = 110 transfers the results of the add operation to X and the macro memory address AB registers.

When executed, the above 16 bits form the effective address  $\Delta + (Q)$ .

5. K transform 7 (XT/FLDSTR) is always selected during the GETMAK/XT operation (that is, the K register is loaded with  $0C_{16}$ ). However, since SM113 is not set by the emulator, the contents of the K register is not used for emulation of this instruction.

After the GETMAK/XT transform operation is completed, the upper micro instruction of the load A register subroutine at location  $98_{16}$  is loaded into the MIR and executed. From this micro instruction, the P counter is incremented by 1 and data from macro memory at address  $\Delta + (Q)$ , determined by the content of the macro memory address register, AB, is read out. The upper micro instruction is executed next. From this micro instruction, the data read from macro memory is loaded into the A register and a jump is made to the RNI cycle. This completes the emulation of the load A register (LDA) macro instruction.

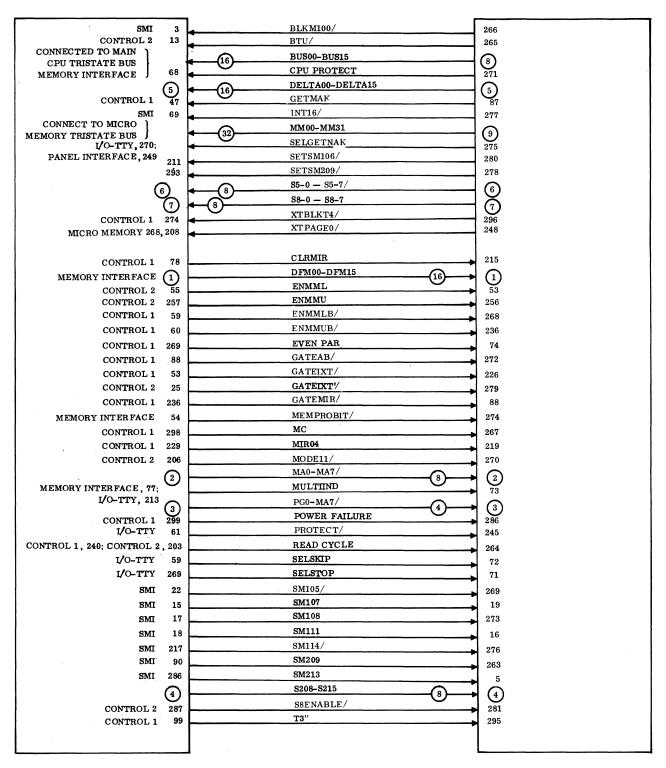

### EXTERNAL INTERFACE

Table 4-8 provides a glossary of terms for external interface signals. This glossary tabulates the mnemonics found on the logic diagrams the term that the mnemonic represents, and the application of the signal(s).

The field print package logic diagrams contain diagonal (1) and bar ( ) symbols to indicate active low conditions. The diagonal is used with external signals and the bar is used with internal signals.

## TABLE 4-8. GLOSSARY OF TERMS (EXTERNAL SIGNALS)

| Mnemonic                                 | Term                                 | Application                                                                                                         |  |  |

|------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|

| BLKM100                                  | Block mask interrupt bit 100         | Disables emulator branch to interrupt sub-<br>routine during macro halt                                             |  |  |

| BTU                                      | Bit test unit                        | One bit used to modify any CPU word                                                                                 |  |  |

| BUS00 - BUS15                            | Bus lines                            | Three-state bus lines of CPU                                                                                        |  |  |

| CARRYOUT 0 -<br>CARRYOUT 3               | Carry-out bits                       | Carry output from ALU of processor                                                                                  |  |  |

| CLRMIR                                   | Clear memory instruction register    | Clear signal to clear transform MIR                                                                                 |  |  |

| CPU PROT Central processing unit protect |                                      | Discrete signal that indicates that CPU is in<br>a protect status; only protected instructions<br>will be processed |  |  |

| DELTA00 -<br>DELTA15                     | Delta translator bits                | Delta translator output lines to selector 1 of CPU                                                                  |  |  |

| DFM01 - DFM16                            | Data from memory bits                | Macro memory word bits                                                                                              |  |  |

| ENMMLEnable micro-memory lowerENMMLBbits |                                      | Signal used to enable the output of lower<br>micro-memory bits MM00 - MM15                                          |  |  |

| ENMMUEnable micro-memory upperENMMUBbits |                                      | Signal used to enable the output of upper<br>micro-memory bits MM16 - MM31                                          |  |  |

| EVENPAR                                  | Even parity                          | Signal used to test for even or odd parity                                                                          |  |  |

| GATEAB                                   | CPU memory address register<br>clock | Clocks store 00FF to bit test if store statu is true                                                                |  |  |

| GATEIXT                                  | Gate instruction transform           | Gates macro memory bits into IXT register                                                                           |  |  |

| GATEIXT-                                 | Gate instruction transform prime     | Gates macro memory bits DFM01 - DFM08<br>into IXT' register                                                         |  |  |

| GATEMIR                                  | Gate micro instruction register      | Clocks the micro memory bit MM24 - MM31<br>into the micro instruction register of the<br>1700 transform             |  |  |

| GETMAK                                   | Gate transform of MA and K registers | Gates macro memory to IXT register and performs transform of MA and K registers                                     |  |  |

| ILLCHAR0 -<br>ILLCHAR3                   | Illegal character                    | Determines selection of delta translator outputs                                                                    |  |  |

| IND00FF                                  | Indicator of ALU equals 00FF         | Enables execution of upper micro instruction                                                                        |  |  |

| MA0 - MA7                                | Memory address bits                  | Selects one of 256 micro-memory instruction residing in either page 0 or 1                                          |  |  |

| MCDELAYED                                | Delayed master clear                 | Clears transform protect bit and clocks the block mask bit 100 signal                                               |  |  |

| MEMPROTBT                                | Memory protect bit                   | Enables the transform protect function                                                                              |  |  |

| MODE11                                   | Sequential address mode              | Determines selection of K/N transforms                                                                              |  |  |

| MM00 - MM31                              | Micro-memory bits                    | Micro-memory bits from read only memory that contain the emulation instruction                                      |  |  |

| Mnemonic    | Term                                       | Application                                                                 |

|-------------|--------------------------------------------|-----------------------------------------------------------------------------|

| PG0 - PG3   | Page bits                                  | Enables selection of upper or lower micro-<br>memory instruction            |

| POWERFAIL   | Power failure                              | Activates program interrupt to inhibit processing if a power failure occurs |

| PROTECT     | Protect switch input                       | Activates the program protect function                                      |

| READCYCLE   | Read cycle                                 | Enables the transform memory instruction register                           |

| RPINT16     | Program interrupt 16                       | Enables micro-interrupt control programs                                    |

| SELGETMAK   | Select GETMAK                              | Selects gate transform of MA and K registers                                |

| SELSKIP     | Select skip                                | Enables skip operation                                                      |

| SELSTOP     | Select stop                                | Activates stop condition                                                    |

| SETSM106    | Set status mode bit 106                    | Enables interrupt function                                                  |

| SETSM209    | Sets status mode bit 209                   | Sets protect fault detection function                                       |

| SM105       | Protect fault                              | Set if a protect violation occurred                                         |

| SM108       | Memory parity error                        | Set if a macro memory parity error exists                                   |

| SM111       | Enable F1                                  | Enables transform input to CPU selector S1 and S2 when low.                 |

| SM114       | Pre-enable interrupt function              | Enables interrupt function by permitting interrupt bit SM106 to be set.     |

| SM209       | Protect fault detection bit                | Enables protect fault detection                                             |

| SM213       | Delta translator select bit                | Enables delta translator selection conditions $0$ and $1.$                  |

| S208 - S215 | CPU selector 2 inputs                      | Enables breakpoint selections                                               |

| S5-0 - S5-7 | Transform selector S5 bits                 | Memory address register transform selection                                 |

| S8-0 - S8-7 | Transfer selector S8 bits                  | K and N register transform selection                                        |

| S8ENABLE    | K/N transform enable                       | Enables K/N transform selector S8                                           |

| Т3          | Time T3 from CPU                           | Clock pulse T3 to enable destination register selection by T4 pulse         |

| XTBLKT4     | Transfer block destination timing pulse T4 | Block selection of destination register at time T4                          |

| XTPAGE0     | Transform page 0                           | Enable additional read-only memory if included in system                    |

### TABLE 4-8. GLOSSARY OF TERMS (EXTERNAL SIGNALS) (Contd)

### 1700 TRANSFORM FUNCTIONAL BLOCK DIAGRAM

Each block of figure 5-1 contains one or more numbers in the upper right corner. These numbers correspond to the logic diagram sheet where the function is located. Input and output signals, including the control signals to each block, are also included. This block diagram supplements the logic diagrams.

### INSTRUCTION TRANSFORM (IXT) REGISTER

This register is a 16-bit register that holds the macro instruction currently being emulated. The register consists of D-type flip-flops A3, J2, C5, and B5. The macro instruction residing in the register is received from main memory via lines DFM01 through DFM16 (DFM01 is the least significant bit and DFM16 is the most significant bit). The outputs from the IXT register, I00 through I15 (I00 is the least significant bit and I15 is the most significant bit), are coupled to the MA transform (selector S5), K/N transform (selector S8), delta translator, and F1 and GETMAK/XT decoders. Data-from-memory (DFM) bits are transferred through the associated register elements when the gate instruction transform (GATEIXT/) and gate instruction transform prime (GATEIXT-1) are active (high). When both are active, the bit condition at input D is placed on the output lines by the leading edge (low to high transition) of the gate pulse (IXT + IXT').

## IXT' REGISTER