# CONTROL DATA<sup>®</sup> MICRO-PROGRAMMABLE COMPUTER FAMILY 1700 ENHANCED PROCESSOR WITH CORE MEMORY

HARDWARE REFERENCE MANUAL

|                                        | <b>REVISION RECORD</b>                                                                   |

|----------------------------------------|------------------------------------------------------------------------------------------|

| REVISION                               | DESCRIPTION                                                                              |

| 01                                     | Preliminary Release                                                                      |

| (10/74)                                |                                                                                          |

| Α                                      | Manual released. This manual obsoletes all previous editions.                            |

| (8/75)                                 |                                                                                          |

| В                                      | Manual revised; includes Engineering Change Order 14967 which corrects storage reference |

| (9/77)                                 | instructions. Page 4-16 is revised.                                                      |

|                                        |                                                                                          |

| •                                      | ·                                                                                        |

| -                                      |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

|                                        | 1                                                                                        |

| ······································ |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

|                                        |                                                                                          |

REVISION LETTERS I, O, Q AND X ARE NOT USED

© 1974, 1975, 1977 by Control Data Corporation Printed in the United States of America Address comments concerning this manual to: Control Data Corporation Publications and Graphics Division 4455 Eastgate Mall LaJolla, Calif. 92037 or use Comment Sheet in the back of this manual.

Publication No. 88973500

| PAGE             | REV | PAGE | REV | PAGE                                  | REV | PAGE | REV | PAGE | REV |

|------------------|-----|------|-----|---------------------------------------|-----|------|-----|------|-----|

|                  |     |      |     |                                       |     |      |     |      |     |

| Cover            |     |      |     |                                       |     |      |     |      | {   |

| Title Page       |     |      |     |                                       |     |      |     |      |     |

| Revision         |     |      |     |                                       |     |      |     |      |     |

| Record           | В   |      |     |                                       |     |      |     |      |     |

| iii/iv           | В   |      |     |                                       |     |      |     |      |     |

| v thru           | [ [ |      |     |                                       |     |      |     |      |     |

| viii             | A   |      |     |                                       |     |      |     |      |     |

| 1-1 thru         |     |      |     |                                       |     |      |     |      |     |

| 1-8              | A   |      |     |                                       |     |      |     |      |     |

| 2 <b>-1</b> thru | {   |      |     |                                       |     |      |     |      |     |

| 2-6              | A   |      |     |                                       |     |      |     |      |     |

| 3 <b>-1</b> thru |     |      |     |                                       |     |      |     |      |     |

| 3-7              | A   |      |     |                                       |     |      |     |      |     |

| 4-1 thru         |     |      |     |                                       |     |      |     |      |     |

| 4-15             | A   |      |     |                                       |     |      |     | 1    |     |

| 4-16             | В   |      |     |                                       |     |      |     |      |     |

| 4–17 thru        |     |      |     |                                       |     |      |     |      |     |

| 4-29             | A   |      |     |                                       |     |      |     |      |     |

| 5-1 thru         |     |      |     |                                       |     |      |     |      |     |

| 5-3              | A   |      |     |                                       |     |      |     |      |     |

| 6-1              | A   |      |     |                                       |     |      |     |      |     |

| 6-2              | A   |      |     |                                       |     |      |     |      |     |

| 7-1 thru         |     |      |     |                                       |     |      |     |      |     |

| 7-4              | A   |      |     |                                       |     |      |     |      |     |

| A-1 thru         |     |      |     |                                       |     |      |     |      |     |

| A-3              | A   |      |     |                                       |     |      |     |      |     |

| B <b>-1</b> thru |     |      |     |                                       |     |      |     |      |     |

| B-4              | A   |      |     |                                       |     |      |     |      |     |

| C-1 thru         |     |      |     |                                       |     |      |     |      |     |

| C-8              | Α   |      |     |                                       |     |      |     |      |     |

| Index-1 thru     |     |      |     |                                       |     |      |     |      |     |

| Index-6          | A   |      |     |                                       |     | 1    |     |      |     |

| Comment          |     |      |     |                                       |     |      |     |      |     |

| Sheet            | В   |      |     |                                       |     |      |     |      |     |

| Envelope         |     |      |     |                                       |     |      |     |      |     |

| Back Cover       |     |      |     | · · · · · · · · · · · · · · · · · · · |     |      |     |      |     |

|                  |     |      |     |                                       |     |      |     |      |     |

|                  |     |      |     |                                       |     |      |     |      |     |

|                  |     |      |     |                                       |     |      |     |      |     |

|                  |     |      |     |                                       |     |      |     |      |     |

|                  |     |      |     |                                       |     |      |     |      |     |

|                  |     |      |     |                                       |     |      |     |      |     |

|                  |     |      |     |                                       |     |      |     |      | 1   |

|                  |     |      |     |                                       |     |      |     |      |     |

|                  | 1   |      |     |                                       |     |      |     |      |     |

|                  |     |      |     |                                       |     |      |     |      |     |

|                  |     |      |     |                                       |     |      |     |      |     |

|                  |     |      |     |                                       |     |      |     |      |     |

|                  |     |      |     |                                       |     |      |     |      |     |

New features, as well as changes, deletions, and additions to information in this manual, are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

The micro-programmable (MP) computer emulates the 1700 family of computers. Readers of this document should be familiar with the CONTROL DATA<sup>®</sup> 1700 series computers and their associated hardware. The MP is upward-compatible and has an enhanced instruction capability.

Additional information on Control Data software applicable to the MP system will be found in the following publications:

v

| Description                                                | Publication No.  |

|------------------------------------------------------------|------------------|

| 1700 Computer System Codes                                 | 60163500         |

| 1700 MSOS Version 4 Reference Manual                       | 60361500         |

| 1700 MSOS 4 MS FORTRAN Version 3A/B                        | 60362000         |

| Micro Processor Reference Manual                           | 88973400         |

| CCP Support Software 1 MICRO Assembler<br>Reference Manual | <b>889</b> 88800 |

| CCP Support Software 1 MACRO Assembler<br>Reference Manual | <b>8898</b> 8900 |

1

~

## CONTENTS

| 1.   | SYSTEM DESCRIPTION                | 1-1 |

|------|-----------------------------------|-----|

| Intr | oduction                          | 1-1 |

| Fun  | ctional Characteristics           | 1-1 |

| Phy  | sical Characteristics             | 1-1 |

| Maj  | or System Component Description   | 1-5 |

|      | Micro Processor                   | 1-5 |

|      | Transform                         | 1-5 |

|      | Micro Memory                      | 1-5 |

|      | Macro Memory (Core) and Memory    |     |

|      | Interface                         | 1-5 |

|      | I/O-TTY Interface                 | 1-7 |

|      | External I/O Interface            | 1-7 |

| 2.   | FUNCTIONAL DESCRIPTION            | 2-1 |

| Gen  | eral Description                  | 2-1 |

| Mic  | ro Processor                      | 2-1 |

|      | Transforms and the Transform      |     |

|      | Module                            | 2-1 |

|      | Arithmetic/Logical Unit (ALU)     |     |

|      | and Data Transfer Organization    | 2-1 |

|      | Macro Memory                      | 2-4 |

|      | Macro Memory Configuration        | 2-5 |

|      | I/O-TTY Module                    | 2-5 |

|      | Maintenance Interface/            |     |

|      | Maintenance Panel                 | 2-6 |

| 3.   | OPERATING PROCEDURE               | 3-1 |

| Star | rtup                              | 3-1 |

|      | ulator or Macro-Program Deadstart | 3-1 |

| Shu  | tdown                             | 3-1 |

| Sys  | tem Failure                       | 3-1 |

| MS   | OS Autoload                       | 3-1 |

| Ope  | erator Interface for the MP       | 3-1 |

| Fun  | ction Control Register (FCR)      | 3-1 |

|      | o-Display                         | 3-4 |

|      | el Interface Control Commands     | 3-4 |

|      | el/Program Mode Commands          | 3-7 |

|      | Operations                        | 3-7 |

| 4.   | MP INSTRUCTION DESCRIPTION       | 4-1  |

|------|----------------------------------|------|

| Inst | ruction Format                   | 4-1  |

| Bas  | ic Instruction Set               | 4-1  |

|      | Storage Reference                | 4-1  |

|      | Register Reference               | 4-1  |

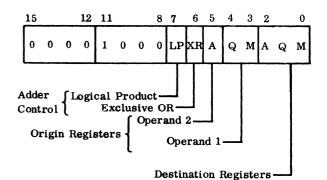

|      | Inter-Register                   | 4-3  |

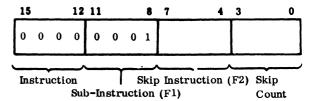

|      | Skip                             | 4-5  |

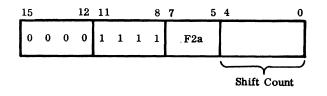

|      | Shift                            | 4-7  |

| Enh  | anced MP Instructions            | 4-9  |

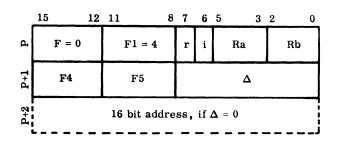

|      | Enhanced Storage Reference       | 4-9  |

|      | Field Reference                  | 4-17 |

|      | Enhanced Inter-Register          | 4-18 |

|      | Enhanced Skip                    | 4-19 |

|      | Decrement and Repeat             | 4-19 |

|      | Miscellaneous                    | 4-20 |

| Aut  | o Data Transfer                  | 4-24 |

| 5.   | INTERRUPT SYSTEM                 | 5-1  |

| Inte | errupt Trap Locations            | 5-1  |

| Ma   | sk Register                      | 5-1  |

|      | ority                            | 5-1  |

| Inte | rnal Interrupts                  | 5-2  |

| Оре  | ration                           | 5-2  |

| 6.   | PROGRAM PROTECT                  | 6-1  |

| Pro  | gram Protect Violations          | 6-1  |

| Stor | rage Parity Errors as Related to |      |

|      | Program Protection               | 6-1  |

| Set, | Clear Program Protect Bit        | 6-1  |

| Pro  | gramming Requirements            | 6-1  |

| Per  | ipheral Equipment Protection     | 6-2  |

| 7.   | I/O DEVICES                      | 7-1  |

| Par  | el/Program Device                | 7-1  |

|      | ll-Time Clock                    | 7-3  |

|      |                                  |      |

## **APPENDIXES**

| Glossary            | A-1 | С | Instruction Execution Times | C-1 |

|---------------------|-----|---|-----------------------------|-----|

| Instruction Summary | B-1 |   |                             |     |

A

в

## INDEX

## FIGURES

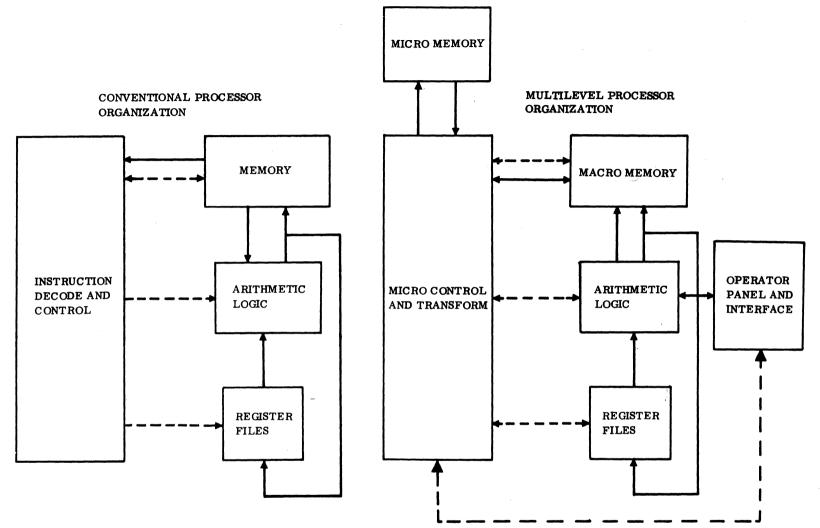

| 1-1 | Digital Processor Organizations | 1-4 | 2-2 | Detailed Block Diagram of  |      |

|-----|---------------------------------|-----|-----|----------------------------|------|

| 1-2 | MP Standard Chassis             | 1-5 |     | 1700 Enhanced Processor    | 2-2  |

| 1-3 | Typical MP Circuit Card         | 1-6 | 2-3 | Macro Memory Configuration | 2-5  |

| 1-4 | Typical MP Chassis Layout       | 1-7 | 2-4 | Major Signal Flow Paths of |      |

| 1-5 | MP Functional Block Diagram     | 1-8 |     | I/O-TTY Module             | 2-5  |

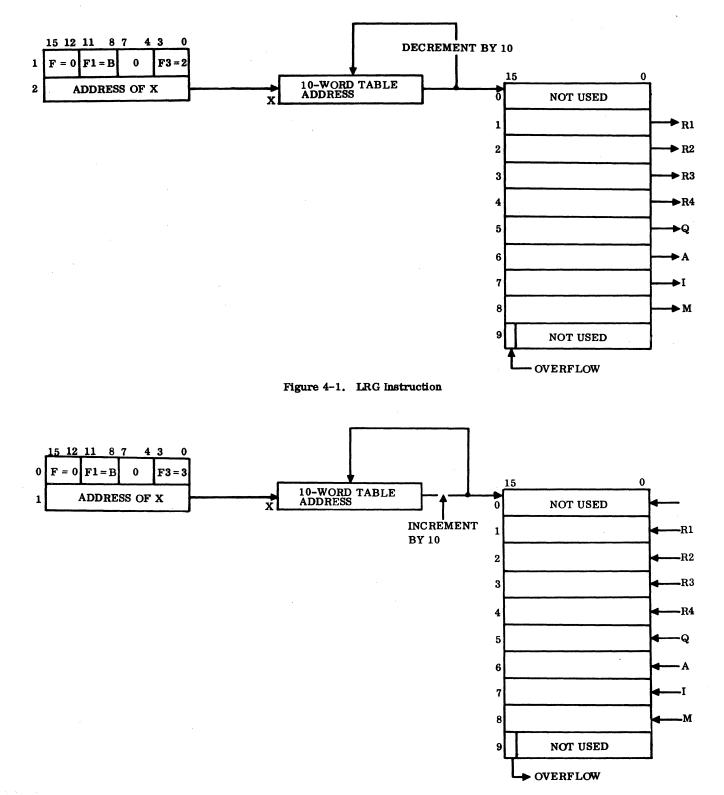

| 2-1 | MP Block Diagram                | 2-1 | 4-1 | LRG Instruction            | 4-23 |

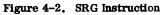

|     |                                 |     | 4-2 | SRG Instruction            | 4-23 |

## TABLES

| 1-1 | MP General Characteristics               | 1-2  | 4-9  | Enhanced Storage Reference          |      |

|-----|------------------------------------------|------|------|-------------------------------------|------|

| 2-1 | MP Mask Register/Interrupt Addresses     | 2-4  |      | Instructions                        | 4-14 |

| 3-1 | Function Control Register (FCR)          | 3-2  | 4-10 | Field Reference Instructions        | 4-18 |

| 3-2 | Display Code Definitions                 | 3-3  | 4-11 | Enhanced Skip Instructions          | 4-19 |

| 3-3 | MP/1700 Register Correspondence          | 3-5  | 4-12 | Miscellaneous Enhanced Instructions | 4-21 |

| 4-1 | Storage Reference Instruction Addressing | 4-2  | 4-13 | ADT Table for a Single A/Q Device   | 4-25 |

| 4-2 | Storage Reference Instructions           | 4-4  | 4-14 | ADT Table for Multiple A/Q Devices  | 4-27 |

| 4-3 | <b>Register Reference Instructions</b>   | 4-6  | 4-15 | ADT Table for the Clock             | 4-28 |

| 4-4 | Inter-Register Instructions              | 4-8  | 4-16 | ADT Table for Single or Multiple    |      |

| 4-5 | Inter-Register Instruction Truth Table   | 4-9  |      | M05 Devices                         | 4-29 |

| 4-6 | Skip Instructions                        | 4-10 | 5-1  | Interrupt State Definitions         | 5-1  |

| 4-7 | Shift Instructions                       | 4-10 | 7-1  | Standard MP Assignment of Equipment |      |

| 4-8 | Enhanced Storage Reference               |      |      | Codes, Macro/Micro Interrupt        |      |

|     | Instruction Addresses                    | 4-12 |      | Lines                               | 7-2  |

V.

## INTRODUCTION

The 1700 enhanced processor computer is a special configuration of the CONTROL DATA<sup>®</sup> MP family of parallel mode, stored program, digital processors. It is dedicated to perform as a CDC<sup>®</sup> 1700-compatible digital computer. The MP uses micro programming to perform 1700 language programs.

This manual describes the basic as well as the optional characteristics of the MP. It covers the hardware, general operating procedures, and the MP instruction repertoire.

The basic MP configuration consists of:

- Micro processor with 1700 transform

- Micro memory

- Macro memory

- I/O interface

- Power supply

Various standard options, such as a card reader and a line printer, are available for the MP. The user may also use the micro memory and I/O to perform nonstandard 1700 functions to achieve even greater flexibility with the MP processor.

A listing of the general characteristics of the MP is contained in table 1-1.

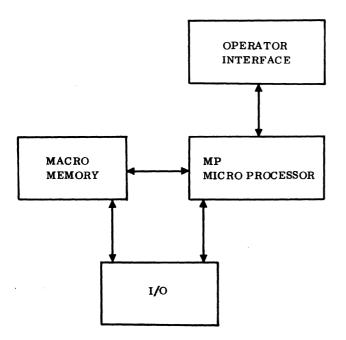

## FUNCTIONAL CHARACTERISTICS

The micro-programmable computer is a multilevel processor, which uses a semiconductor ROM and a special hardware function (transform) to emulate a CDC 1700 computer. The macro memory unit contains 1700 language programs (called macro instructions). The multilevel processor differs from the conventional processor, as shown in figure 1-1. The MP operation is controlled by a program (micro program) in the semiconductor memory (referred to as micro memory). The micro program reads 1700 macro instructions from macro memory and decodes them for execution in the micro processor. The semiconductor memory is several times faster than the macro memory. The transform aids in decoding and program execution. Therefore, the MP uses special micro-programming techniques to emulate an enhanced CDC 1700 system for lower cost, smaller size, and equal or better speed.

## **PHYSICAL CHARACTERISTICS**

The MP is modularly designed with standard TTL MSI components and commercial construction.

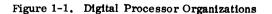

The standard chassis, shown in figure 1-2, is 18.5 inches high by 17.5 inches wide by 12 inches deep. The chassis includes cooling fans. The standard chassis back panel has the I/O wiring for the 1700 A/Q and 1700 A/Q-DMA. However, it may also contain specialized I/O for the user. Wiring details are included in the system wirelist provided for the unit. A front cover panel is provided on the chassis for maximum cooling.

Power requirements for the MP vary with the user's application. CDC provides power supplies of  $\pm 5$ ,  $\pm 12$ , and  $\pm 15$  volts with input power requirements of 115 vac, 50 or 60 Hz. Physical dimensions for a power supply chassis are 8.75 inches high by 17.5 inches wide by 16.0 inches deep. Cooling fans for logic and power supply chassis require 115 vac, 50 or 60 Hz.

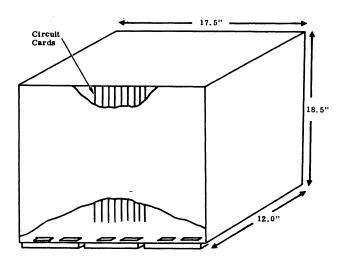

A typical MP circuit card, shown in figure 1-3, is 11 by 14 inches and has 204 input/output contacts.

The MP chassis has a pre-wired location for an optional panel interface card. The maintenance panel is a 16-inch by 4.5-inch printed circuit board, connected by a flexible cable to the panel interface card. The panel contains controls and LED indicators for manually controlling the MP at the micro level. The panel interface card also provides an interface to ASCII RS232-compatible consoles (full-duplex interface). The normal configuration for the 1700 enhanced processor uses the I/O-TTY module for manual operator interface.

1

| Ba                               | sic Configuration                                                                                                        |  |  |  |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Processor                        |                                                                                                                          |  |  |  |  |  |

| Туре                             | General-purpose, micro-programmable digital processor                                                                    |  |  |  |  |  |

| Organization                     | Register oriented or file oriented.                                                                                      |  |  |  |  |  |

| Word length                      | 16 bit                                                                                                                   |  |  |  |  |  |

| Micro-instruction word           | 32-bit format; two micro instructions per micro-memory<br>address                                                        |  |  |  |  |  |

| Micro-memory type                | Semiconductor read/write memory (RAM) and/or read only memory (ROM)                                                      |  |  |  |  |  |

| Micro-memory size                | 512 words in 64-bit increments (on transform); maximum of 4,096 additional words available.                              |  |  |  |  |  |

| Micro-memory access time         | 70 nanoseconds                                                                                                           |  |  |  |  |  |

| Arithmetic                       | Binary with dynamic selection of ones or twos complemen mode                                                             |  |  |  |  |  |

|                                  | Up to four parallel unrelated operations are possible in one micro instruction                                           |  |  |  |  |  |

| Macro-instruction execution time | Approximately the same as a 1700 computer with 900 $\mu$ sec<br>memory cycle time (for detailed timing, see Appendix C). |  |  |  |  |  |

| Macro Memory                     | •                                                                                                                        |  |  |  |  |  |

| Requirement                      | Variable, according to application                                                                                       |  |  |  |  |  |

| Туре                             | Core memory: available in 8K stacks, with a maximum of 32K; the main chassis has a 16-bit format.                        |  |  |  |  |  |

|                                  | Parity and protect bits are available in the standard stack                                                              |  |  |  |  |  |

| Core speed                       | Read: 600 nanoseconds cycle time <sup>†</sup><br>Write: 700 nanoseconds cycle time <sup>†</sup>                          |  |  |  |  |  |

| Direct memory access             | Four I/O ports are wired for DMA devices; one can be a CDC 1700 DSA (QSE feature).                                       |  |  |  |  |  |

| Input/Output (I/O)               |                                                                                                                          |  |  |  |  |  |

| Interfaces                       | Teletypewriter<br>Display terminal (RS232–C compatible)                                                                  |  |  |  |  |  |

#### TABLE 1-1. MP GENERAL CHARACTERISTICS

$^{\dagger}$  The shortest possible time between successive operations.

| Basic Con              | figuration (Continued)                                                                              |

|------------------------|-----------------------------------------------------------------------------------------------------|

| Mechanical             |                                                                                                     |

| Hardware               | Modular                                                                                             |

| Construction           | RETMA 19-inch, rack mountable                                                                       |

| Dimensions             | Logic Chassis:                                                                                      |

|                        | Height — 18.5 inches (47 cm)<br>Width — 17.5 inches (44.5 cm)<br>Depth — 16.0 inches (40.64 cm)     |

|                        | Power Supply Chassis:                                                                               |

|                        | Height — 8.75 inches (22.25 cm)<br>Width — 17.5 inches (44.5 cm)<br>Depth — 16.0 inches (40.64 cm)  |

| Weight                 | Logic Chassis: 40 pounds (approximately) (18 kg)<br>Power Supply: 50 pounds (approximately) (45 kg) |

| Input power            | 115 volts, 50/60 Hz                                                                                 |

| Miscellaneous Features |                                                                                                     |

|                        | Real-time clock<br>Auto-data transfer<br>Enhanced 1700 instruction repertoire                       |

| Sta                    | ndard Options                                                                                       |

| Input/Output (I/O)     |                                                                                                     |

| Interfaces             | Maintenance panel<br>CDC 1700 A/Q-DMA (TTL level)<br>RS232-C compatible console                     |

| Operator input device  | Teletypewriter ASR/KSR 33/35<br>CDC conversational display terminals<br>(RS232-C compatible)        |

## TABLE 1-1. MP GENERAL CHARACTERISTICS (Continued)

NOTES: 1. DOTTED LINES ARE CONTROL SIGNALS.

2. SOLID LINES ARE INSTRUCTIONS AND DATA FLOW.

14

Figure 1-2. MP Standard Chassis

The MP will operate in computer rooms, general offices, and industrial environments. It will operate at temperatures of 40° F to 120° F (4.5° C to 48.8° C), withstand a maximum temperature gradient of 0.2° F per minute or at a rate that precludes condensation, and a relative humidity of 10 to 90 percent. Non-operating environment extends the temperature range from -30° F to 150° F (-35° C to 65° C) and a maximum thermal gradient not to exceed 20° F per hour or at a rate that precludes condensation. Storage temperatures with proper packaging protection may range from -60° F to 160° F and relative humidity from 2 to 98 percent with temperature cycles of not more than 60° F per hour or at a rate that will preclude condensation. The user should note that these ranges cover only the micro processor; peripheral equipments may require more stringent environmental controls.

## MAJOR SYSTEM COMPONENT DESCRIPTION

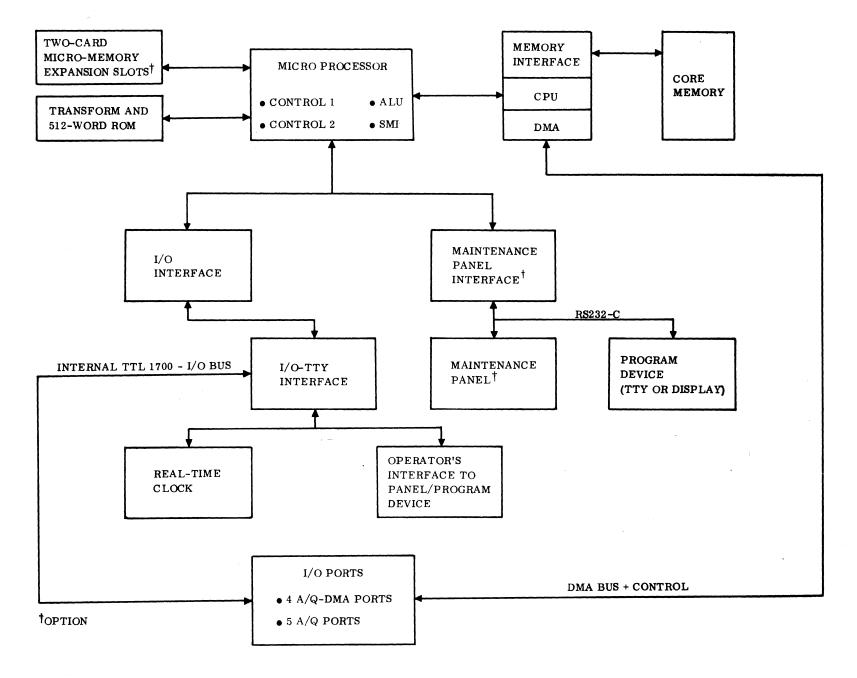

Figure 1-4 shows the chassis layout for the MP equipment; figure 1-5 is the functional block diagram.

#### MICRO PROCESSOR

The MP enhanced processor consists of an arithmetic card (ALU), a status mode interrupt card (SMI), control

cards 1 and 2, and a 1700 transform module. The micro-processor cards are interconnected through the basic backpanel wiring. Special user options will require additional wiring.

#### TRANSFORM

The transform hardware is packaged as a separate module and is specially designed for the MP application. The MP has a 512-word, 64-bit ROM micro memory on the transform module.

Functioning as the hardware portion of the macro-instruction decode process, the transform causes the micro program to form program branches, sets various parameters, and performs arithmetic or logical operations. It provides the micro program with the capability of selecting patterns of bits from the data transmission paths to form the micro-memory addresses that sequence the micro program.

#### MICRO MEMORY

The MP contains a 512-word micro memory on the 1700 transform board. It also has two card slots for additional micro-memory or special algorithms if required by the user. The slots are interconnected to the micro processor through the backpanel and are accessible only by the micro processor.

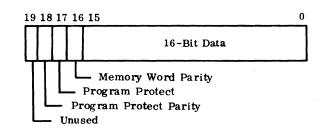

## MACRO MEMORY (CORE) AND MEMORY INTERFACE

The core macro memory consists of memory stacks and an interface card. The memory stacks are configured in 8K increments of 20 bits: 1 parity, 1 protect, 1 protect parity, 1 unused, and 16 data bits. The stacks are mounted on standard 11 x 14-inch circuit boards, with each stack requiring two card spaces in the chassis.

Data flow is in 16-bit word format, with a maximum of 32K possible in the basic chassis. A direct memory access (DMA) channel is included in the memory interface as well as the parity and program protect generation and checking. The DMA for the MP can provide access for four external DMA devices through a port to the macro memory.

## Figure 1-3. Typical MP Circuit Card

| 8K CORE MEMORY† | 8K CORE MEMORY † | 8K CORE MEMORY † | 8K CORE MEMORY | MEMORY INTERFACE | PANEL INTERFACE † | MICRO MEMORY † | MICRO MEMORY/ALGORITHM † | 1700 TRANSFORM | CONTROL 1 | CONTROL 2 | ALU | IWS | I/O-TTY | 1700 A/Q | 1700 А/Q-DMA |  |

|-----------------|------------------|------------------|----------------|------------------|-------------------|----------------|--------------------------|----------------|-----------|-----------|-----|-----|---------|----------|--------------|----------|--------------|----------|--------------|----------|--------------|--|

|-----------------|------------------|------------------|----------------|------------------|-------------------|----------------|--------------------------|----------------|-----------|-----------|-----|-----|---------|----------|--------------|----------|--------------|----------|--------------|----------|--------------|--|

Option<sup>†</sup>

Figure 1-4. Typical MP Chassis Layout

#### I/O-TTY INTERFACE

The standard operator interface to the MP is through the I/O-TTY module. It can interface with Teletype Corporation Model ASR/KSR 33/35 Teletype or the Control Data RS232-C compatible conversational display terminals. A TTL bus is available in the I/O-TTY module for interfacing the controller cards in the main chassis to the micro processor.

#### EXTERNAL I/O INTERFACE

}.

The main chassis for the MP includes nine slots for external I/O devices (in addition to the I/O capability of the I/O-TTY module). As shown in figure 1-4, four slots are prewired for 1700 A/Q-DMA Channels and five slots are prewired for 1700 A/Q channels. These may be used with standard CDC equipment or for special user applications.

Figure 1-5. MP Functional Block Diagram

## **GENERAL DESCRIPTION**

The micro-programmable computer will emulate a CDC 1700 computer system. It can perform all 1700 functions, utilizing an expanded instruction set with interfacing capabilities to 1700 Series peripherals. Figure 2-1 shows a block diagram of the MP system. The basic MP configuration includes the micro processor, macro memory, I/O interface, and the operator's interface. The flexible design of the system permits the user to incorporate his own equipment or to upgrade the MP with additional micro memory, I/O capability, or a special hardware algorithm module.

Figure 2-1. MP Block Diagram

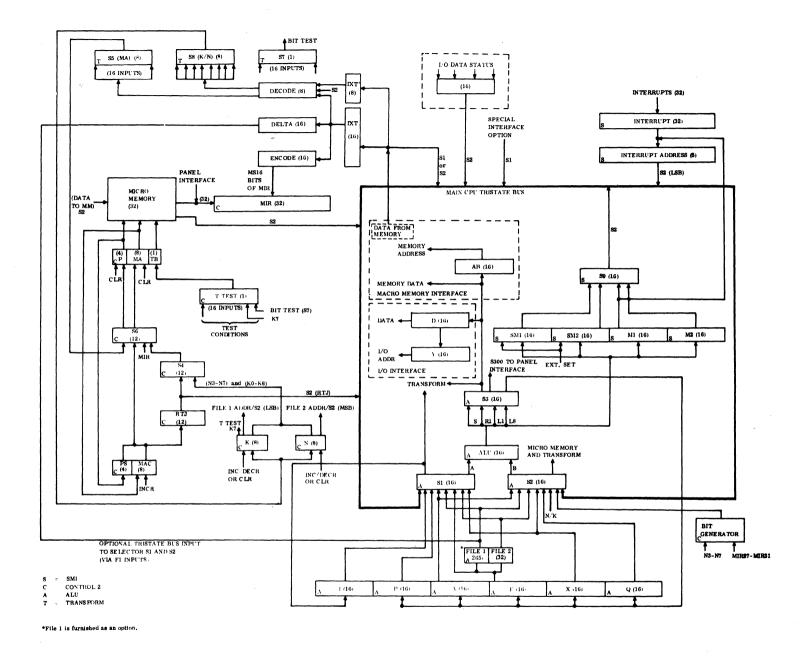

## MICRO PROCESSOR

The MP central processing unit (CPU) is a special configuration that consists of an ALU module, an SMI module, two control modules, and the standard MP transform module. Detailed organization of the MP is shown in figure 2-2. This diagram shows MP registers interconnected primarily by selectors. A selector is a multiplexer that transfers one of several inputs to an output. They are either one, eight, 12, 16, or 32 bits wide.

#### TRANSFORMS AND THE TRANSFORM MODULE

Transforms enable quick and efficient decoding of an emulated instruction. A transform can be designed to extract bits from a register or registers, shift the bits to the required position, and add a base address or constant bits. This result can then be transferred to the micro-memory address register (transform jump) or to the K or N register (transform register load). For example, when a 1700 instruction is read from macro memory, one micro-instruction transform jump transfers control to one of 108 micro-memory locations. Without the transform feature the above operation would require many micro instructions.

The transform hardware is packaged in a separate module and is implemented using three selectors. The transform module includes 1, 024 micro instructions (512 words) in ROM. The majority of these instructions are used to execute the 1700 emulator. The ROM also contains instructions for the panel interface simulation via the I/O-TTY board.

# ARITHMETIC/LOGICAL UNIT (ALU) AND DATA TRANSFER ORGANIZATION

The ALU provides the arithmetic and logical capabilities of the MP. This unit combines two input words of the system word length. These two inputs are combined according to the function code specified in the micro instruction. The result is immediately available at the output of the ALU for possible shifting via selector S3 and delivery to the destination register, memory interface, panel interface, and I/O. The unshifted output of the ALU is delivered to the SM and mask registers. The ALU output can be ignored on an operation. The results of the ALU operation regarding sign, zero, and magnitude (by means of carryout test) are available to the test bit logic for instruction sequencing.

The data transfer organization of the MP provides for storing data in one of six working registers and two

Figure 2-2. Detailed Block Diagram of 1700 Enhanced Processor

files, and for selecting data for processing through the ALU. ALU results are transferred back to one of the registers or out of the organization to control external equipment.

The primary data registers are I, P, A, F, X, and Q.

The following are brief descriptions of the primary registers. Table 3-3 contains a comparison of the MP registers with 1700 registers.

- I Register A word-length register whose only input and output is the selector S1. This register should not be confused with the 1700 I register (location 00FF<sub>16</sub>).

- P Register<sup>†</sup>— A word-length, general-purpose register that receives data from the ALU and provides output to S1. Normally it is used to hold the software instruction counter.

- A Register<sup>†</sup> A word-length, general-purpose register that receives data from the ALU and provides output to S1. The A register is mechanized as a shifting register, and can be shifted left or right without using the ALU. The A register may also be combined with the Q register to form a double-length shifting register that operates independently of the ALU.

- F Register A word-length, general-purpose register that receives data from the ALU and provides data to S1 or S2 as ALU input. This register is also used as the file entry register and contains information written into the files when they are used as the destination of an ALU operation.

- X Register A word-length, general-purpose register that receives data from the ALU and provides data to S1 or S2.

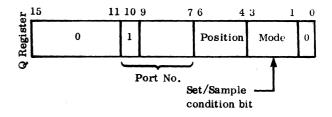

- Q Register<sup>†</sup> A word-length, general-purpose register that receives data from the ALU and provides output to S2. The Q register is mechanized as a shifting register. It may be shifted left or right in conjunction with the A register without using the ALU.

Other major portions of the standard MP are:

• File 2 — A 32-word scratchpad file that may be used as a general-purpose, word-sized register. It delivers its output to S1 and S2; data input is provided by the F register. File 2 is reserved for the emulator, except for registers R1, R2, R3, and R4, which are available to the 1700 programmer through enhanced instructions.

- Bit Generator (BG) The BG circuit generates one bit at any position in a word as input to the B side of the ALU. Control to drive the bit generator is derived from either the micro instruction (bits 27 to 31) or the lower five bits of the N register. Control is usually obtained from the micro instruction. A bit setting in an SM register determines the input that will drive the bit generator.

- Status/Mode Register (SM) The SM register allows the micro program to control the mode of operation and also allows the micro program to examine the status of certain internal and external conditions. The MP can access one of two SM registers, SM1 and SM2.

The SM register module contains 16 bits of SM1 and 16 bits of SM2. All 32 bits of an SM module can be set or reset by the micro program by transferring information to the SM register from the output of the ALU. Master clear will also clear SM1 and SM2.

• Interrupts and Mask Register — The interrupt system is implemented as a sampled data system at the micro-program level, instead of a true vectored interrupt system as used in conventional computers.

> The mask register enables the micro processor to disable/enable interrupts. The MP can access two mask registers, M1 or M2. For each mask bit there is a corresponding bit in the interrupt register.

M1 is available to the 1700 programmer through the DMI instruction, while M2 (referred to as M) is available through the basic inter-register instruction (see section 4).

Interrupts are identified by their corresponding mask bits, which are assigned to control the interrupt recognition. The bits in the mask registers are identified as follows:

- Mask Register 1 (M1): M100 through M115

- Mask Register 2 (M2): M200 through M215

<sup>&</sup>lt;sup>•†</sup>Available to the 1700 programmer.

Interrupt addresses are generated by the interrupt address encoder, according to the assignments given in table 2-1.

|       | ADDRESSES                                                                                                           |

|-------|---------------------------------------------------------------------------------------------------------------------|

| Mask  | Interrupt Address                                                                                                   |

| Bit   | Mask Register 1                                                                                                     |

| M 100 | 15 Lowest Priority (M1)                                                                                             |

| M101  | 14                                                                                                                  |

| M 102 | 13                                                                                                                  |

| M 103 | 12                                                                                                                  |

| M104  | 11                                                                                                                  |

| M105  | 10                                                                                                                  |

| M106  | 09 _                                                                                                                |

| M 107 | 08                                                                                                                  |

| M 108 | 07                                                                                                                  |

| M 109 | 06                                                                                                                  |

| M110  | 05                                                                                                                  |

| M111  | .04                                                                                                                 |

| M112  | 03                                                                                                                  |

| M 113 | 02                                                                                                                  |

| M114  | 01                                                                                                                  |

| M115  | 00 Highest Priority (M1)                                                                                            |

|       | Interrupt Address                                                                                                   |

|       | Mask Register 2                                                                                                     |

|       |                                                                                                                     |

| M200  | 31 Lowest Priority (M2)                                                                                             |

| M201  | 30                                                                                                                  |

| M202  | 29                                                                                                                  |

| M203  | 28                                                                                                                  |

| M204  | 27                                                                                                                  |

| M205  | 26                                                                                                                  |

| M206  | 25                                                                                                                  |

| M207  | 24                                                                                                                  |

| M208  | 23                                                                                                                  |

| M209  | 22                                                                                                                  |

| M210  | 21                                                                                                                  |

| M211  | 20                                                                                                                  |

| M212  | 19                                                                                                                  |

| M213  | 18                                                                                                                  |

| M214  | 17                                                                                                                  |

| M215  | 16 Highest Priority (M2)                                                                                            |

|       | The interrupt address generated is the same as its priority level; i.e., the highest priority interrupt generates a |

0 interrupt address and the lowest priority interrupt generates a 31

interrupt address.

| TABLE 2-1. | MP MASK REGISTER/INTERRUPT |

|------------|----------------------------|

|            | ADDRESSES                  |

The interrupt priorities correspond to the interrupt address generated; that is, interrupt address 00 is associated with the highest priority interrupt line and interrupt address 31 is associated with the lowest priority interrupt line. For example, an interrupt associated with M112 would have priority over an interrupt associated with M111, and an interrupt address of 3 would be developed by the interrupt address encoder.

- K Register An eight-bit counter that can be cleared, incremented, or decremented. It is used to address file 1 in addition to any program usage as a counter.

- N Register An eight-bit counter that may be cleared, incremented, or decremented. It is used to address file 2, control shifts, control the scale operations, and may be used as an iteration counter that controls micro-instruction execution.

- N/K Register The N and K registers may be combined to provide operand addresses outside the current operating micro page.

- File 1 An optional file of 256 general-purpose, word-sized registers that are addressed by the contents of the K register. The output of the addressed file is delivered to S1 and S2 and thus to the A and B side of the ALU on demand. This file 1 input to selectors S1 and S2 is a submultiplexed input to the ALU. Thus, depending on the state of status mode bit (SM111), either file 1 or transform data can be selected as either an A or B input to the ALU.

#### MACRO MEMORY

Macro memory for the MP consists of 8K core memory stacks and an interface card. The interface card provides the control and interfacing required for MP/memory function and peripheral (DMA) equipment/memory functions. The 8K memory stacks are in 20-bit format:

The parity and program protect bits are generated and tested in the interface card. One interface card will handle up to four stacks (32K) in the main MP chassis.

Minimum memory cycle time is 600 ns, which is defined as the shortest possible time between successive read operations in macro memory. Minimum macro memory cycle time is 700 ns for write operations.

#### MACRO MEMORY CONFIGURATION

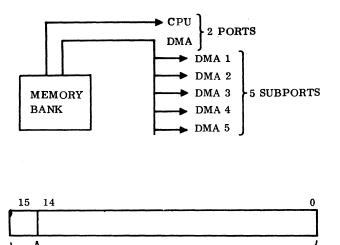

The macro memory configuration is shown in figure 2-3.

The core memory configuration (for 8K to 32K) is a onebank, two-port memory. One bank signifies that only one reference may take place at one time. Two ports provide two independent data and control paths to the memory; either port may request memory independent of any operation underway on the other port. The ports are CPU and DMA (direct memory access).

#### I/O-TTY MODULE

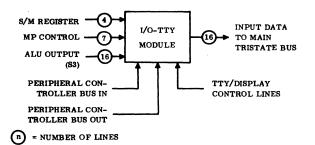

Figure 2-4 illustrates major signal flow paths to and from the I/O-TTY module.

This module includes the following components:

- Real-Time Clock In conjunction with the micro code it appears as a 1700 peripheral to the macro-level programmer.

- I/O Teletypewriter/Display Control This controller is an integral part of the module. It interfaces to Teletype Corporation ASR/KSR 33/35 teletypes and to the Control Data RS232-C compatible conversational display terminals.

- Internal Peripheral Controller Bus Provides all I/O data lines, interrupts, and control signals necessary to generate, in conjunction with the micro code, an internal CDC 1700 A/Q (input/output) bus. This TTL-level bus is intended to interface with controllers located in the basic MP chassis.

- Panel Interface Simulation A logic section that is required when a panel/program device is used for operator input in the panel mode.

The MP is interfaced to the I/O module as follows:

- ALU Output All output data and address information is provided from the output of the ALU via S3.

- SM Register All commands to peripheral controllers are generated by micro code manipulation of the MP status mode register.

- MP Control Timing and control information for controlling internal I/O module data gating is provided from the MP control signals.

- Interrupts Interrupts from peripheral controllers (within the basic chassis) are wired directly from the peripheral controller module to the MP.

- Input Data and Peripheral Response Signals All of these are provided to the MP on the main CPU tristate bus.

- Real-Time Clock An integral part of the I/O module, the real-time clock appears as a 1700 peripheral to the macro-level software. Two functions are available to the macro-level program: Enable Limit Interrupt and Disable Limit Interrupt. Two status bits are also available to the macro-level program: Limit Interrupt and Lost Count.

The user may use his own design for I/O interfacing to facilitate use of special hardware.

# MAINTENANCE INTERFACE/MAINTENANCE

The maintenance panel interface is an optional circuit module available for manual interface to the micro processor. The panel interface provides interfaces for a maintenance panel or for an RS232-C compatible console that has full-duplex serial ASCII characteristics. A card slot is prewired for the panel interface card control, and data lines tie directly into the control cards and to the ALU. This section discusses the operating procedure for the micro-programmable computer in general terms. Since each user will have a different equipment application and setup, it is recommended that the user evaluate and develop his own operating procedure. The following sections present a general outline for startup and shutdown actions. Included is a description of the normal operator's interface to the MP.

## STARTUP

The following startup sequence is a suggested outline:

- 1. Power-On Switch. Turn the MP power-on switch to the ON position.

- 2. Peripheral Power On Sequence. Turn on all peripherals and auxiliary power units.

# EMULATOR OR MACRO-PROGRAM DEADSTART

- 1. Master clear the machine.

- 2. Place the emulator or macro-program deadstart deck in the reader.

- 3. Press ESCAPE on the panel/program device.

- 4. Depress the deadstart switch.

## SHUTDOWN

De-energize all peripherals. Position the power-on switch to the OFF position.

### SYSTEM FAILURE

After a system failure, follow the startup procedure and deadstart/autoload for restart.

## **MSOS AUTOLOAD**

- 1. Master clear

- 2. Depress the autoload button for the mass storage controller

- 3. Press ESCAPE on the panel/program device

- 4. Type K31002800:

- 5. Type I@

- After the initial MSOS messages, press ESCAPE on the panel/program device

- 7. Set the program protect by typing J28@

- 8. Input data/time on the panel/program device and continue

## **OPERATOR INTERFACE FOR THE MP**

The normal MP configuration will include a CRT display unit as the panel/program device. The panel/ program device is connected to the MP through the I/O-TTY card. It will function as a panel interface or a program (input/output) device.

### FUNCTION CONTROL REGISTER (FCR)

The function control register (table 3-1) is the basic means of communication between the MP and the panel / program device in the panel interface mode. The eight hexadecimal digits (32 bits) of the FCR can be grouped as follows (0 is highest order):

| Display:        | Digits 0 and 1 |

|-----------------|----------------|

| Machine Modes:  | Digits 2 to 5  |

| Machine Status: | Digits 6, 7    |

The display digits determine which individual registers of two groups of registers (identified in table 3-2) can be displayed and/or modified. Digits 2 to 5 of the FCR are used to set such conditions as selective top/on/off, tep/run mode, etc.

|                            | Bit                   | Digit | Bit Definition                                                                                                                                           |               |

|----------------------------|-----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| (LSB) 31<br>30<br>29<br>28 | 1F<br>1E<br>1D<br>1C  | 7     | Overflow<br>Not Protected Instruction<br>Protect Fault<br>Parity Error                                                                                   | ţ             |

| 27<br>26<br>25<br>24       | 1B<br>1A<br>19<br>18  | 6     | Interrupt System Active<br>Auto-Restart Enabled<br>Micro Running<br>Macro Running                                                                        | Status Only - |

| 23<br>22<br>21<br>20       | 17<br>16<br>15<br>14  | 5     | Not used<br>Not used<br>Enable Auto Display<br>Enable Console Echo                                                                                       |               |

| 19<br>18<br>17<br>16       | 13<br>12<br>11<br>10  | 4     | Enable Micro Memory Write<br>Multilevel Indirect Addressing Mode<br>Not used<br>Suppress Console Transmit                                                |               |

| 15<br>14<br>13<br>12       | 0F<br>0E<br>0D<br>.0C | 3     | 00Breakpoint Off01Instruction Reference BP10Storage Operand BP11All References BPBPInterrupt (BP Stop if Clear)Micro BP, Step, Go, Stop (Macro if Clear) | -             |

| 11<br>10<br>09<br>08       | 0B<br>0A<br>09<br>08  | 2     | Step<br>Selective Stop<br>Selective Skip<br>Protect Switch                                                                                               |               |

| 07<br>06<br>05<br>04       | 07<br>06<br>05<br>04  | 1     | DISPLAY 1                                                                                                                                                |               |

| 03<br>02<br>01<br>(MSB) 00 | 03<br>02<br>01<br>00  | 0     | DISPLAY 0                                                                                                                                                |               |

#### TABLE 3-1. FUNCTION CONTROL REGISTER (FCR)

|   | Code    | Display 1              | Display 0                                                                                                   |

|---|---------|------------------------|-------------------------------------------------------------------------------------------------------------|

| 0 | 0 0 0 0 | FCR                    | F2 (Addressed by N)                                                                                         |

| 1 | 0001    | pt                     | N (MSBs) <sup>††</sup>                                                                                      |

| 2 | 0 0 1 0 | I                      | K (LSBs) <sup>††</sup>                                                                                      |

| 3 | 0011    |                        | x                                                                                                           |

| 4 | 0 1 0 0 | A                      | Q                                                                                                           |

| 5 | 0 1 0 1 | MIR                    | F                                                                                                           |

| 6 | 0 1 1 0 | BP/P-MA (Display Only) | $\mathbf{F1} \left\{ \begin{array}{l} \text{Addressed by K} \\ \text{Enabled by SM111} \end{array} \right.$ |

| 7 | 0 1 1 1 | P-MA (Display Only)    | MEM                                                                                                         |

| 8 | 1 0 0 0 | SM1                    |                                                                                                             |

| 9 | 1 0 0 1 | M1                     | RTJ                                                                                                         |

| A | 1 0 1 0 | SM2                    |                                                                                                             |

| в | 1011    | M2                     |                                                                                                             |

| с | 1 1 0 0 |                        | ММ                                                                                                          |

| D | 1 1 0 1 | A*                     |                                                                                                             |

| E | 1 1 1 0 | X*                     |                                                                                                             |

| F | 1 1 1 1 | Q*                     |                                                                                                             |

|   |         |                        |                                                                                                             |

|   |         |                        |                                                                                                             |

|   |         |                        |                                                                                                             |

|   |         |                        |                                                                                                             |

|   |         |                        |                                                                                                             |

#### TABLE 3-2. DISPLAY CODE DEFINITIONS

1

<sup>†</sup> Used to address macro memory. Automatically incremented after each memory reference.

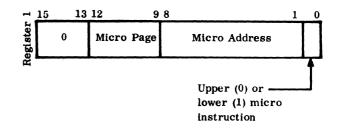

<sup>††</sup>The combined contents of these two registers are used to address micro memory. The K register is automatically incremented after each memory reference. The N register does not automatically increment. The two least significant digits (6, 7) of the FCR are set by the MP and indicate the machine status, such as overflow on/off, macro storage parity error, protect fault, etc.

#### NOTES

- Bits 14<sub>16</sub> and 15<sub>16</sub> of the FCR (Enable Console Echo and Enable Auto Display) are mutually exclusive; that is, the operator may select one or theother, but not both simultaneously.

- Digit 3 of the FCR (bits 0C<sub>16</sub> to 0F<sub>16</sub>), Breakpoint, is applicable only if the user has the optional maintenance panel and panel interface card.

- Unassigned display codes (table 3-2) should be assumed to be undefined.

- Selecting BP or P/MA (table 3-2) will result in both BP and P-MA being displayed. BP is the leftmost 16 bits and P-MA is the rightmost 16 bits. BP can be modified only if BP is selected; P-MA cannot be modified in either case.

- 5. Selecting N or K (table 3-2) will result in both N and K being displayed. N is the left eight bits and K is the right eight bits. However, when N is selected only the N register can be modified; when K is selected only the K register can be modified.

### AUTO-DISPLAY

When auto-display is enabled, the register selected by the control code and display code will be output to the operator's interface and continuously updated (assuming the operator's interface contains a display and not a teletypewriter). With auto-display enabled, depressing a terminator (:, G or @) with no characters preceding it will cause a go signal.

# PANEL INTERFACE CONTROL COMMANDS

The control commands used in the panel interface mode include: H, I, J, K, L, @, :, G, and ?. Control commands H through L identify the type of data or operation entered or returned. The at symbol (@), the colon (:), and G all perform an entry termination function. The @ will also cause the operator's interface to go from the panel interface mode to program (A/Q) mode. The question mark, ?, generates a master clear.

A normal entry consists of one control character H through L; two, four, or eight hexadecimal digits 0 through F; and a terminating entry (: or G), in that order.

A normal response consists of the control character identifying the data that follows and four or eight hexadecimal digits. If a transmission or operator error occurs on the entry, an asterisk (\*) precedes the control character and the function control register is unconditionally displayed with the last legal control character. All entries except the ? cause a response, unless bit  $10_{16}$  (Suppress Console Transmit) of the FCR is set. The following are examples of the control functions. The colon (:) is used as the terminating entry.

- Master Clear A master clear can be generated in several ways:

- A power on master clear

- The MC button on the maintenance panel

- A signal from a peripheral controller

- A question mark from a panel device (programmers console)

#### NOTE

Baud rate compatibility between the panel device and the machine must exist for ? master clear.

Stop/Go Control — The following entry will cause a go:

#### I: (Initiate)

3-4

This is a micro go if bit 12 of the FCR is set. It is both a micro and macro go if bit 12 of the FCR is clear.

The I control function may also be used to set a bit in the FCR.

The following entry will cause a stop:

H: (Halt)

This is a micro stop if bit 12 of the FCR is set. It is a macro stop if bit 12 of the FCR is Clear.

The response to a start or stop entry is a display of the FCR.

The H control function may also be used to clear a specific bit in the FCR. The entry

H14:

would clear bit  $14_{16}$  in the FCR and the response would be a display of the updated FCR.

NOTE

The clear and set capabilities of the H and I control functions are not available in the panel simulation mode.

J Control Function — The J control function is used to replace the contents of the function control register in a digit mode. While it may be used to change the value of any FCR digit, it is generally used to change digits 0 and 1. The value of Display 0 and Display 1 specifies which MP parameter is displayed on display requests, or entered on enter requests (refer to table 3-3). J functions always consist of J followed by two hexadecimal digits and a terminator (:, G, or @). The first hexadecimal digit specifies the FCR digit 0 through 5 and the second hexadecimal digit specifies the value the digit is to assume, 0 through F.

The function code

J14:

| МР                                                               | 1700                                        |

|------------------------------------------------------------------|---------------------------------------------|

| р                                                                | Р                                           |

| А                                                                | Α                                           |

| Q                                                                | Q                                           |

| x                                                                | (P) (i.e., next instruction) (display only) |

| I                                                                | I (see notes 1 and 2) (display only)        |

| F2(1)                                                            | R1                                          |

| F2(2)                                                            | R2                                          |

| F2(3)                                                            | R3                                          |

| F2(4)                                                            | R4                                          |

| F2(5)                                                            | Q (display only)                            |

| F2(6)                                                            | A (display only)                            |

| F2(7)                                                            | I (see notes 1 and 2)                       |

| M2                                                               | М                                           |

| NOTE: To change I:<br>1. Change location 00FF<br>2. Change F2(7) | 3                                           |

#### TABLE 3-3. MP/1700 REGISTER CORRESPONDENCE

would set FCR digit 1 to 4 (select the A register), and the response would be a display of the updated FCR.

The J code is also used to alternately display the upper and lower 16 bits of a 32-bit register on the 16-bit maintenance panel display.

In the panel simulation mode, J: will result in the display of the entire FCR register. There is no upper/lower mode.

K Control Function — The K control function is used to display or enter data into the parameter specified by Display 1. The K function uses two formats. The first format is a request to display the parameter specified by Display 1:

K:

The second format is an enter data request. The data is entered into the parameter specified by Display 1. It consists of K followed by four or eight hexadecimal digits, followed by a terminator (:, G, or @). The hexadecimal digits are the data to be entered. For example:

- To display the P register, type:

- J11: Set Display 1 to P register (FCR Digit  $1 = 1_{16}$ ).

- K: Display parameter selected in Display 1.

- To enter 14FE into the breakpoint register, type:

- J16: Set Display 1 to BP register (FCR Digit  $1 = 6_{16}$ ).

- K14FE: Enter data into parameter selected in Display 1.

- L Control Function The L function is operationally the same as the K function, except that it is associated with Display 0.

#### NOTE

When macro memory is displayed or entered, the register selected in Display 1 is the macro memory address. The Display 1 selection must be the P or A register. This register is incremented by 1 after the display. In the panel simulation mode, the Display 1 selection must be the P register. When micro memory is displayed or entered, the K register is the eight least significant bits of the address, and the N register provides the remaining bits. The K register is incremented by 1 after the display.

Breakpoint (BP) — There are two types of breakpoint: micro and macro. If bit 12 of the FCR is set, micro breakpoint is selected. If bit 12 is clear, macro breakpoint is selected. In the panel simulation mode there is no micro or macro breakpoint capability.

Bits 14 and 15 of the FCR are used to select three types of macro BP:

| Bit 14 | Bit 15 |                          |

|--------|--------|--------------------------|

| 0      | 0      | Breakpoint not selected  |

| 0      | 1      | Instruction reference BP |

| 1      | 0      | Store operand BP         |

| 1      | 1      | All references BP        |

A macro breakpoint occurs if the breakpoint register is equal to the macro memory address and the select conditions are met. For example:

- J16: Set display 1 to breakpoint register.

- K0050: Set breakpoint register to 0050<sub>16</sub>.

- J31: Set macro mode and breakpoint on instruction reference.

A stop will occur after the instruction at macro location  $50_{16}$  is executed.

If bit 13 of the FCR is set, an interrupt occurs when the breakpoint conditions are met rather than a stop.

For a micro breakpoint, P/MA is compared to the lower 12 bits of the breakpoint register. In addition, the upper/lower selection (32-bit select) is compared to bit 13 of the breakpoint register. If all bits are equal and the combination of FCR bits 14 and 15 is not zero, then a micro stop occurs. If FCR bit 14 is set, then a comparison of FCR bit 13 and the upper/lower selector is not required.

• Auto Display — When auto display is enabled, the register selected by the control and display codes will be output to the operator's interface and continuously updated as long as the interface is a display terminal and not a teletypewriter. Depressing a terminator (:, G, or @) with no characters preceding it will cause a go signal, which is useful for stepping through a micro or macro program.

#### NOTE

Auto-display mode and echo mode should never be selected simultaneously. In other words, FCR bits 20 and 21 should be mutually exclusive.

## PANEL/PROGRAM MODE COMMANDS

Commands for use in the program mode are escape (ESC) and manual interrupt. The ESC command will cause the panel/program device to go from program mode to panel interface mode. It sets the reserve status line, which will indicate to the software that the panel/ program device is busy if the macro program would attempt to reference it.

The manual interrupt is generated by a control G (BELL) command. It is used instead of a console manual interrupt button.

The command for use in panel mode is the @ symbol. It will generate a release reserve as it causes the panel/program device to enter into the program mode from the panel mode. Selecting the @ during program mode will be accepted as a normal ASCII character with no special function.

## I/O OPERATIONS

With the exceptions specified in the program mode commands, the program mode is to be used as standard operator data interface to the MP for I/O.

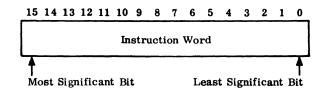

## INSTRUCTION FORMAT

The MP computer instruction word shown in the following example consists of 16 bits, numbered right to left as 0 to 15, with the leftmost bit, 15, being the most significant and the rightmost bit, 0, being the least significant.

Hexadecimal (base 16) notation is used in this computer.

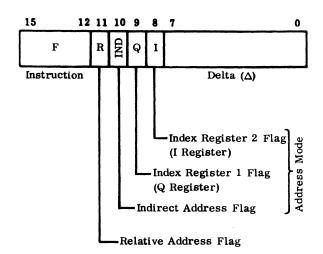

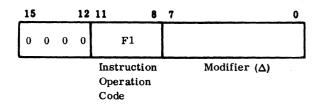

The MP computer is composed of a basic and an enhanced instruction set. The basic set is 1700-compatible and is divided into storage reference, register reference, inter-register, skip, and shift instructions. The enhanced instruction set is divided into the enhanced storage reference, field reference, enhanced interregister, enhanced skip, decrement and repeat, and miscellaneous instructions.

## **BASIC INSTRUCTION SET**

#### STORAGE REFERENCE

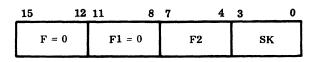

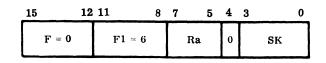

The storage reference instructions shown in the following illustration contain three fields: instruction, address mode, and delta. The instruction field contains the operation code.

The address mode field contains flags for indexing, indirect addressing, and relative addressing. The delta field is a signed eight-bit address modifier in which the most significant bit is the sign bit. Storage reference instructions have the following format:

Five types of addresses and/or address methods are created by these instructions:

- Instruction Address The address of the instruction being executed; also called P

- Indirect Address A storage address that contains an address rather than an operand

- Base Address The operand address after all indirect addressing but before modification by the index registers. The base address is the effective address when no indexing is specified.

- Effective Address The final address of the operand. At certain times the effective address equals the operand for read-operand type instructions (refer to table 4-1).

- Indexing The computer has two index registers. Index register 1 is the Q register; index register 2 is storage location 00FF (I register). The base address may be modified by either or both of the index registers. If the index 1 flag is set, the contents of the Q register are added to the base address.

## TABLE 4-1. STORAGE REFERENCE INSTRUCTION ADDRESSING

| Mode                                   | Binary<br>11 10 9 8 | Hex.   | ∆<br>Delta | Effective Address             | Address of<br>Next Instruction |

|----------------------------------------|---------------------|--------|------------|-------------------------------|--------------------------------|

|                                        |                     |        | ·          |                               |                                |

| 8-Bit Absolute                         | 0000                | 0      | <b>≠</b> 0 | Δ                             | P+1                            |

|                                        | 0001                | 1      |            | $\Delta$ +(00FF)              |                                |

|                                        | 0010                | 2      |            | Δ+(Q)                         |                                |

|                                        | 0011                | 3      |            | Δ+(Q)+(00FF)                  |                                |

| 8-Bit Absolute Indirect <b>†</b>       | 0100                | 4      |            | (Δ)                           |                                |

|                                        | 0101                | 5      |            | (Δ)+(00FF)                    |                                |

|                                        | 0110                | 6      |            | (Δ)+(Q)                       |                                |

|                                        | 0111                | 7      |            | $(\Delta)+(Q)+(00  {\rm FF})$ |                                |

| 8-Bit Relative                         | 1000                |        |            | DIA                           |                                |

| 8-Bit Relative                         | 1000                | 8      |            | $P+\Delta$                    |                                |

|                                        | 1001                | 9      |            | $P+\Delta+(00FF)$             | ,                              |

|                                        | 1010                | A      |            | P+Δ+(Q)                       |                                |

|                                        | 1011                | В      |            | P+∆+(Q)+(00FF)                |                                |

| 8-Bit Relative Indirect <sup>††</sup>  | 1100                | с      |            | (P+Δ)                         |                                |

|                                        | 1101                | D      |            | (P+A)+(00FF)                  |                                |

|                                        | 1110                | E      |            | (P+Δ)+(Q)                     | · ·                            |

|                                        | 1111                | F      |            | (P+Δ)+(Q)+(00FF)              |                                |

| Absolute Constant                      | 0000                | 0      | =0         | P+1                           | D.0                            |

|                                        | 0000                | 0      | -0         | (P+1)+(00FF) <sup>†</sup>     | P+2                            |

|                                        |                     |        |            | $(P+1)+(Q)^{\dagger}$         |                                |

|                                        | 0010<br>0011        | 2<br>3 |            | $(P+1)+(Q)+(00FF)^{\dagger}$  |                                |

|                                        | 0011                | ა      |            | (1+1)+(4)+(0011).             |                                |

| 16-Bit Storage <sup>††</sup>           | 0100                | 4      |            | (P+1)                         |                                |

|                                        | 0101                | 5      |            | (P+1)+(00FF)                  |                                |

|                                        | 0110                | 6      |            | (P+1)+(Q)                     |                                |

|                                        | 0111                | 7      |            | (P+1)+(Q)+(00FF)              |                                |

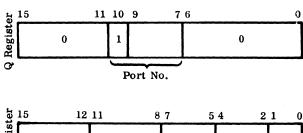

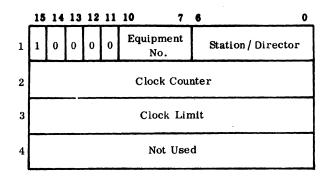

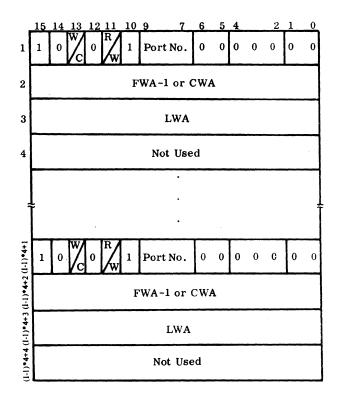

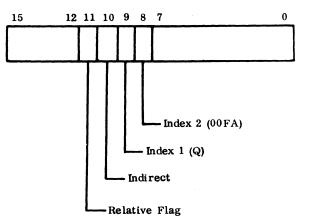

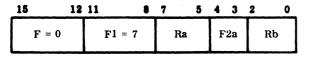

| 16-Bit Relative                        | 1000                | 8      |            | P+1+(P+1)                     |                                |