# CYBER 18-20 Input/Output

**Version W**

SUPPLEMENTARY REFERENCE MANUAL

# CYBER 18-20 Input/Output

Pub. No. 76361225 A

Copyright © 1978, 1979, 1983 by Control Data Corporation.

All rights reserved. No part of this material may be reproduced by any means without permission in writing from the publisher.

Printed in the United States of America.

2/83

# **Table of Contents**

Block 1 INTERRUPT SYSTEM

> Interrupt Characteristics, 1-1 Interrupt System Functional Areas, 1-4 Interrupt System, 1-12 Interrupt Processing (Text), 1-14 Interrupt Processing (Exercise), 1-18 SMI Register Descriptions, 1-19 SMI Data Flow (Text), 1-23 SMI Data Flow (Exercise), 1-26 Interrupt Condition Processing, 1-27 Logic Diagram, 1-30

Block 2 I/O SYSTEM

> I/O Functional Description, 2-1 I/O Schemes, 2-3 I/O System, 2-8 I/O Signal Flow, 2-9

Block 3 TTY/CDT CONTROLLER

> CDT Functional Description, 3-1 Control Signals, 3-4 Data Flow, 3-12 Controller, 3-28

APPENDIX A. TEST ITEM DIAGRAMS, A-1

# Block 1

**Interrupt System**

## **Interrupt Characteristics**

The interrupt system allows the computer to sense or test for certain conditions in the computer or external equipment. If these conditions are present, the computer changes or interrupts the normal flow of processing and temporarily goes to a subroutine (program) that will take care of the condition that caused the interrupt. After this subroutine is completed, the computer will return to normal processing at the point at which it was interrupted.

The interrupt system in the computer can be compared to many everyday occurences, for example, a student reading a text book. The student's normal flow of processing is reading and interpreting the text material. If a cup of coffee spills, an interrupt occurs. To process the interrupt, the student cleans up the spill—a temporary subroutine. After the spill is cleaned up, the student goes back to the normal processing, i.e., returns to the point in the text where the interruption occured.

The conditions that may cause an interrupt can be divided into two major categories, internal and external. Internal interrupts usually indicate some fault condition in the computer proper, such as a power failure or a portion of data that was lost or altered. External interrupts are sensed when some external equipment is requesting the use of the computer. It may be a printer that is ready to print the result of some computation or it may be a card reader wanting to input information to the computer. In any case, the computer, after setting up the means to return to its present processing point, honors the request and either inputs from or outputs to the external device depending on the type of request.

Figure 1-1 shows in a simplified form what happens when an interrupt occurs. The computer is executing some program as shown in the main program block. Just after executing some instruction at address 3002, some fault occurs, causing the computer to sense an interrupt request, as shown by step 1. The computer jumps at step 2 to store the current address of the main program so that it knows where to return when it is finished with the interrupt routine. After storing the current main program address, the computer goes at step 3 to the location of the interrupt subroutine. When the interrupt subroutine is completed and the appropriate action has been taken, the computer jumps at step 4 to the address where the main program address is stored. At step 5 the computer jumps back to the main program and executes the first unexecuted instruction in the main program.

After executing each main program instruction, a test is made for the conditions which could cause an interrupt. If one of these conditions exists, and the conditions for interrupting are present, execution of the main program halts. The contents of the P Register (the address of the next instruction to have been executed) are stored in a predetermined address, and an interrupt routine is initiated. This routine takes the

an interrupt state is entered, the mask for that state is placed in the mask register. There may be up to sixteen levels of priority, and it is possible to change priority during execution of a program.

The computer can distinguish between up to sixteen macrointerrupts (one internal and fifteen external). Each of these interrupts has its respective address to which control is transferred when the interrupt is recognized.

When the computer is processing a particular interrupt, it will be defined as being in that interrupt state (state 00 through 15). Thus, the interrupts and their respective bits in the interrupt mask register are numbered 00 through 15. An interrupt in bit 7 will put the computer in interrupt state 7, etc.

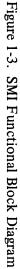

It is important to remember that since the CYBER 18 emulates the 1700 computer system, some inconsistencies in the labeling of bit positions occur. The 1700 programming terminology refers to the most significant bit as bit 15 and the least significant bit as bit 0. The CYBER 18 hardware diagrams are labeled with the most significant bit as bit 0 and the least significant bit as bit 15. When the text refers to the circuit diagrams, the CYBER 18 terminology is used.

Before the computer can recognize any interrupt, the mask bit for that interrupt must be set and the interrupt system must be activated. The mask register is set by an interregister instruction and the system is activated by an enable interrupt instruction (EIN).

When an interrupt is recognized, the computer automatically stores the return address (address of next instruction to be executed in main program) in the storage location reserved for that interrupt state. The interrupt system is de-activated and control is transferred to a subroutine (program) that stores all registers, including the mask register, in addresses reserved for this interrupt state and loads the mask register with the mask to be used in this state. The 1's in the mask indicate the interrupts that have a higher priority than the interrupt being processed. The mask should not have a 1 in the position of the interrupt being processed, as this would cause the return link to be lost. The interrupt system is then activated and the interrupt is processed.

The computer exits from an interrupt state when the program inhibits further interrupts and restores the registers which were stored from the main program. After loading the registers, the program executes the exit interrupt instruction with delta equal to the lower eight bits of the base address of the interrupt state. This instruction reads the storage location where the return address is stored, the interrupt system is again activated, and control is transferred to the return address. The main program then continues until it is completed or another interrupt occurs.

### **Interrupt System Functional Areas**

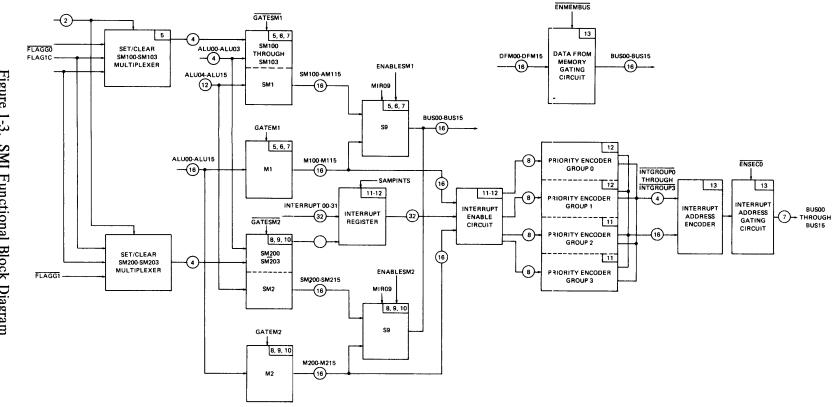

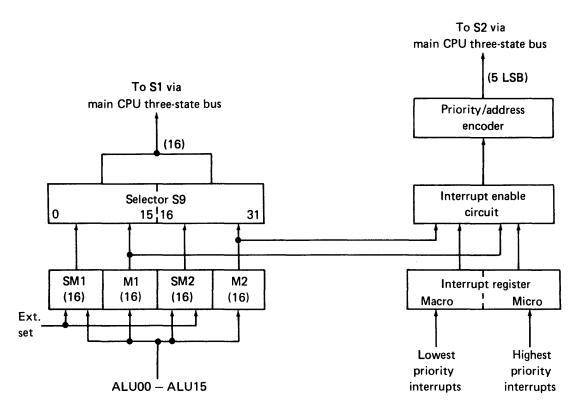

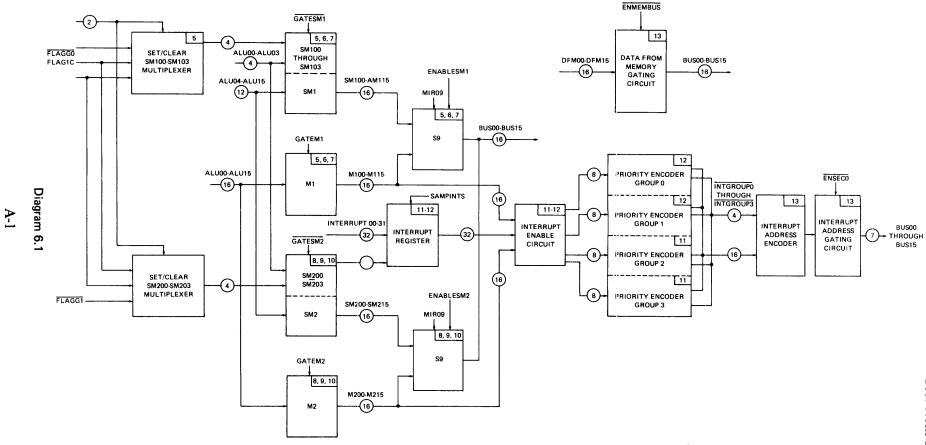

Figure 1-3 shows a functional block diagram of the SMI module. The areas which are involved with interrupts are described below. Follow the block diagram as each area is being described.

#### **Mask Registers**

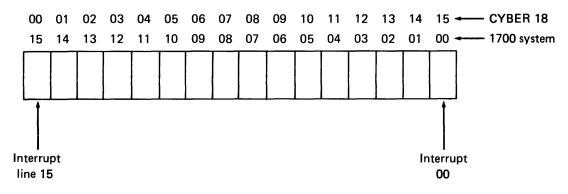

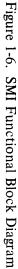

Note that there are two mask registers, M1 and M2, fed by the ALU circuit. The M1 register is used to enable the microinterrupts and the M2 register is used to enable the macrointerrupts. During this block we will be concerned with the macrointerrupts, so the M2 register will be used (see figure 1-2).

Figure 1-2. M2 Mask Register

The main purpose of the mask register is to enable and disable the desired interrupt lines. Each bit in the mask register corresponds to an interrupt line. Interrupt 00 corresponds to bit 15 in the mask register, and so on. The interrupt priorities designating the lower numbered interrupts have the higher priorities. So interrupt 00 has the highest priority while interrupt 15 has the lowest priority. The internal interrupt is interrupt 00 while all other interrupts are designated external. When a particular interrupt line is to be enabled, the corresponding bit in the mask register must be set. This is accomplished by using an interregister instruction. A zero in any bit position of the mask register indicates that particular interrupt line is disabled and no interrupt may occur on that line.

#### Interrupt System

#### **Interrupt Register**

The interrupt register is fed by the different interrupt lines and will hold the active interrupt signals to be serviced by the processor. Note that there are thirty-two lines coming into this register, sixteen for microinterrupts and sixteen for macro-interrupts. The macrointerrupt lines, numbered 16 through 31, are the ones with which we will be concerned. Line 16 corresponds to interrupt state 00, line 17 to interrupt state 01, etc.

#### **Interrupt Enable Circuit**

The interrupt enable circuit is fed by the interrupt register and by the mask registers. When an interrupt occurs and is placed in the interrupt register, the enable circuit checks to see if the mask bit for that particular interrupt is set. If the mask bit is not set, the interrupt will not be recognized and no action will be taken. If the mask bit is set for a particular interrupt that occurs, the interrupt enable circuit passes this on to the priority encoder circuits.

#### **Priority Encoder Circuits**

The priority encoder circuits are divided into four groups of eight interrupt lines. These are referred to as INTGROUP0, INTGROUP1, INTGROUP2, and INTGROUP3. For the macrointerrupts, INTGROUP2 and INTGROUP3 are used. First, the active interrupt signals are priority encoded, each within its own group, by the enabled priority encoder. These encoders are enabled by grounding input pins of the desired interrupt group. Next, the priority among the interrupt groups is encoded by placing a voltage on the input pins of the group encoders. The interrupts are encoded in such a way that interrupt 00 has the highest priority and interrupt 31 has the lowest. In the macrointerrupts, interrupt 16 has the highest priority. Once this is active it indicates to the processor that a power failure, a protect fault, or a parity error condition has been detected. Since the processor is being used as a 1700 emulator, the sixteen lower priority interrupt program interrupts are utilized to generate the standard sixteen 1700 macrointerrupts (one internal and fifteen external).

#### **Interrupt Address Encoder and Gating Circuit**

After the priority has been determined, the information is sent to the interrupt address encoder. This generates the address of the interrupt that has the highest priority and is active. The address tells the processor which interrupt lines caused the interrupt. This address is gated to the processor by the interrupt address gating circuit via the tri-state bus. The computer then initiates the appropriate program to take care of the interrupt. In addition to the areas described above, the interrupt system contains other parts which are just as important. These are:

- The macroinstructions which control the interrupt system

- The interrupt trap region

- The common interrupt handler

- The interrupt processor

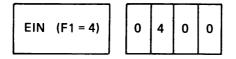

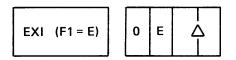

The instructions which control the interrupt system are enable interrupt (EIN), inhibit interrupt (IIN), and exit interrupt (EXI).

#### Enable Interrupt

The enable interrupt (EIN) instruction causes the 1700 interrupt system to become enabled. Until the interrupt system is enabled no interrupts can occur. Once the interrupt system has been enabled, the computer will be interrupted when one of the selected interrupt conditions occurs.

If the PROTECT bit switch is set, the EIN instruction can be executed only if it is stored in a protected location (that is, a location having its protect bit set). An attempt to execute an unprotected EIN instruction (with the PROTECT bit switch set) is considered illegal. The computer will clear "F" and execute an SLS instruction instead. With the PROTECT bit switch clear, all instructions are treated as unprotected; thus the EIN instruction would be executed regardless of its protect status.

The computer is so designed that one instruction will be executed after an EIN instruction before the computer can be interrupted. This feature was included to help simplify interrupt routines. At this point you only need to know that the earliest an interrupt can occur is during RNI sequence of the second instruction following the EIN instruction which enables the interrupt system. Interrupt System

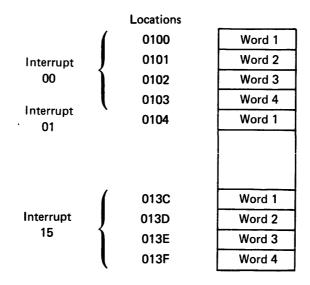

#### **Inhibit Interrupt**

The inhibit interrupt instruction causes the 1700 interrupt system to become disabled. Once disabled, the interrupt system is unable to detect any interruptible conditions.

The IIN instruction requires protection (that is, with the PROTECT bit switch set, the location of the IIN instruction must be protected). An attempt to execute an unprotected IIN instruction (with the PROTECT bit switch set) is illegal. Under such a condition, the computer will clear "F" and execute an SLS instruction instead. With the PROTECT bit switch clear, all instructions are treated as being protected. The interrupt system will not be inhibited until the RNI of the second instruction following the IIN instruction.

#### **Exit Interrupt**

<u>Note</u>: Delta  $\triangle$  field specifies the jump address.

The exit interrupt (EXI) instruction will always be the last instruction of an interrupt subroutine and provides for automatic return to the operation which was interrupted. When a computer interrupt occurs, the operation being performed is temporarily set aside and a routine to process the interrupt is performed. At the time of the interrupt, the computer stores into memory the address to which it must return after completing the interrupt routine.

To be executed, the EXI instruction must be protected; that is, either the PROTECT bit switch is clear or the location of the EXI instruction is protected. When executed, the computer forms the address  $\triangle + 100$ , which is the location of the return address for that interrupt level. The return address is read from memory and placed into X. From the X register the address is placed into the P register. Then the computer reads the instruction specified by the P register and executes the instruction.

As an example, let's assume that the computer is executing an instruction contained in memory location 1000. An interrupt occurs. This causes the contents of the P register (1001) to be stored in the appropriate area. After the execution of the interrupt subroutine the EXI instruction is executed. The EXI instruction forces the 1001 to be placed back into the P register. The computer then continues working at the point in the program where it was when the interrupt occurred.

If the EXI instruction is not protected, an attempt to execute it is illegal, resulting in a protect fault, the clearing of "F," and the execution of an SLS instruction in place of the EXI instruction.

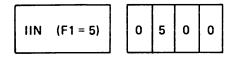

#### **Interrupt Trap Region**

The interrupt trap region is a special area in memory reserved for use by the interrupts. Each of the sixteen possible interrupts has reserved for its use four consecutive memory locations. The interrupt trap region consists of memory locations 0100 through 013F. The breakdown of the interrupt trap region is shown in figure 1-4.

Figure 1-4. Breakdown of Interrupt Trap Region

Interrupt System

The four locations are referred to as word 1 through word 4. The first four memory locations are reserved for macrointerrupt 00, the second four locations for interrupt 1 and so forth.

Word 1 is where the contents of the P register are stored. For example, if interrupt 1 becomes active, the contents of the P register are stored in word 1 of interrupt 1, location 0104. Word 2 is the return jump of the common interrupt handler. Word 3 is the interrupt priority which is loaded into the mask register. Every time an interrupt is received the mask register is loaded with a new priority scheme. This data comes from word 3 of the interrupt which becomes active. Word 4 is the address of the interrupt processor.

#### **Common Interrupt Handler**

It is the job of the common interrupt handler to store the contents of the A, Q and M registers after an interrupt has occurred. This causes the computer to remember the results it had before the interrupt occurred. In addition to storing the register contents, the interrupt handler places the new interrupt priority in the mask register. When the interrupt handler completes its task, it turns control over to the interrupt processor.

For each interrupt that occurs the contents of the registers must be stored and new mask priorities set up. The same program is used for all interrupts (hence the name "common" interrupt handler).

#### **Interrupt Processor**

The interrupt processor is the program which processes or takes action on the particular interrupt which has occurred. There are sixteen possible interrupts and therefore sixteen different interrupt processors. The last instruction of each interrupt processor is the exit interrupt (EXI) instruction. The EXI instruction causes a jump back to word 1 of the interrupt where the contents of the P register is obtained and used to cause the computer to continue what it was doing before the interrupt occurred.

#### Summary

Mask register M2 is used for macrointerrupts. Interrupt line 16 corresponds to macrointerrupt 00. Each bit in the mask register corresponds to one of the sixteen possible interrupts. Interrupt 00 is the highest priority interrupt and coincides with bit 15 of the mask register. An interrupt may only be processed if its corresponding bit in the mask register is set. The interrupt register holds the active interrupts until the interrupt can be processed. There are thirty-two interrupt lines of which interrupts 16 through 31 are used for macrointerrupts.

The interrupt enable circuit compares the contents of the interrupt and mask registers. If the interrupt occurs and the specific bit in the mask register is set, the interrupt is processed.

The priority encoder circuits determine which interrupt has the highest priority and allows it to be processed. Then the interrupt address encoder generates the address of the interrupt and tells the computer which interrupt is active. The instructions EIN, IIN, and EXI are used to control the interrupt system. EIN turns on the interrupt system, IIN turns off the interrupt system, and EXI is a jump instruction which returns control of the computer back to the program that was being executed before the interrupt occurred.

The interrupt trap region is a part of memory reserved for use by the interrupts. It consists of locations 0100 through 013F and each interrupt uses four consecutive locations, beginning with interrupt 0 at location 0100.

The common interrupt handler is a program which stores the contents of the A, Q and M registers and places the new interrupt priorities in the mask register. The same interrupt handler is used by all sixteen macrointerrupts.

There are sixteen different interrupt processors, one for each interrupt. The interrupt processor takes care of the particular interrupt which becomes active.

# **Interrupt System**

DIRECTIONS: For the following questions, fill in the blanks.

- 1. The two major categories of conditions that may cause an interrupt are \_\_\_\_\_\_ and \_\_\_\_\_\_.

- 2. The interrupt system is enabled by the \_\_\_\_\_\_ instruction.

- 3. An interrupt occurring on line 4 will put the computer in interrupt state \_\_\_\_\_\_.

- 4. When an interrupt becomes active, this information is stored in the \_\_\_\_\_\_ register.

- 5. The computer is notified of which interrupt occurred by the \_\_\_\_\_\_ address.

DIRECTIONS: Mark the statements T for true or F for false.

- \_\_\_\_\_ 6. An EIN instruction is not necessary if the mask register is set with the appropriate bit.

- 7. When an interrupt occurs, the return address is stored in a location determined by the address where the interrupt occurred.

- 8. The interrupt register and the mask register allow an interrupt to be recognized.

- 9. The computer can recognize 16 external interrupts.

- \_\_\_\_\_ 10. An interrupt on line 16 indicates that an internal interrupt has occurred.

#### ANSWERS

1. Internal and external 2. Mask, EIN 3. 4 4. Interrupt 5. Interrupt 6. F 7. F 8. T 9. F 10. T

### **Interrupt Processing (Text)**

The following information shows and describes the events that occur in the processing of an interrupt. First, the enable for the system is the mask register, and information is entered into this register by an interregister command. In this example, suppose that 0008 is entered into the M register. This indicates that interrupt line 3 is to be enabled, as bit 12 of M corresponds to interrupt state 3. Specific locations are set aside in memory to store the return address of each interrupt level. For example, interrupt level 01 would have its return address stored in location 0104, interrupt level 02 at location 0108, etc. See table 1-1 for the location of all interrupt levels. These locations are called interrupt trap regions or areas. In addition to the mask register being set, an EIN instruction (enable interrupt) must be executed in order for the processor to recognize the interrupt. The machine language code for this instruction is 0400.

PROGRAM EXAMPLE: M = 0008

Main Program

| 3000 | 0400 (EIN) |                       |

|------|------------|-----------------------|

| 3001 | XXXX       |                       |

| 3002 | XXXX       |                       |

| 3003 | xxxx       | "Interrupt on line 3" |

| 3004 | xxxx       |                       |

#### Interrupt Trap Region (For state 3)

| 010C | 0000                           |

|------|--------------------------------|

| 010D | RTJ                            |

| 010E | Priority Level                 |

| 010F | Address of interrupt processor |

| Interrupt<br>State<br>10 | Delta<br>Used in<br>Exit State<br>16 | Location of<br>Return<br>Address<br>16 | Location of<br>First Instruction<br>After Interrupt<br>Occurs<br>16 |

|--------------------------|--------------------------------------|----------------------------------------|---------------------------------------------------------------------|

| 00                       | 00                                   | 0100                                   | 0101                                                                |

| 01                       | 04                                   | 0104                                   | 0105                                                                |

| 02                       | 08                                   | 0108                                   | 0109                                                                |

| 03                       | 0C                                   | 010C                                   | 010D                                                                |

| 04                       | 10                                   | 0110                                   | 0111                                                                |

| 05                       | 14                                   | 0114                                   | 0115                                                                |

| 06                       | 18                                   | 0118                                   | 0119                                                                |

| 07                       | 1C                                   | 011C                                   | 011D                                                                |

| 08                       | 20                                   | 0120                                   | 0121                                                                |

| 09                       | 24                                   | 0124                                   | 0125                                                                |

| 10                       | 28                                   | 0128                                   | 0129                                                                |

| 11                       | 2C                                   | 012C                                   | 012D                                                                |

| 12                       | 30                                   | 0130                                   | 0131                                                                |

| 13                       | 34                                   | 0134                                   | 0135                                                                |

| 14                       | 38                                   | 0138                                   | 0139                                                                |

| 15                       | 3C                                   | 013C                                   | 013D                                                                |

TABLE 1-1Interrupt State Definitions

#### Interrupt System

Since bit 12 of M corresponds to interrupt level 3, the interrupt is recognized and the main program halts. The address of the next instruction to have been executed (3004) is stored in memory location 010C, and the next instruction is read at location 010D. This is normally a return jump to a common interrupt handler (a program common to all interrupts).

#### Common Interrupt Handler

| 5000 | Address of next instruction in trap region 010F stored here. |

|------|--------------------------------------------------------------|

| 5001 | STA                                                          |

| 5002 | STQ                                                          |

| 5003 | XXXX                                                         |

| 5004 | XXXX                                                         |

| 5005 | XXXX                                                         |

| 5006 | JMP                                                          |

The interrupt handler program stores the contents of the A, Q, and X registers, and the mask register is replaced by the contents of trap region word 3 (location 010E). The last instruction in the interrupt handler is an indirect jump to the interrupt processor. Its effective address is the contents of location 5000 (location 010F).

#### Interrupt Subprogram For State 3 Interrupt

| 6000 | XXXX |

|------|------|

| 6001 | XXXX |

| 6002 | XXXX |

| 6003 | XXXX |

| 6004 | OEOC |

The exit interrupt instruction (OEOC) will always be the last instruction of an interrupt subroutine and this provides for a return to the operation which was interrupted. Note that all return address locations have the same upper two hexadecimal digits, 01. The EXI instruction will identify the lower two digits of the return address location with delta. In this example, delta is 0C, which contains the address of the next instruction in the main program. After the EXI instruction is executed, control is returned to the main program beginning at location 3004. However, before this occurs, the state 3 subprogram restores all the registers with what they contained when the interrupt occurred.

A brief summary of the processing of an interrupt is given in the following steps:

- 1. Set mask register

- 2. EIN instruction

- 3. Interrupt occurs

- 4. Store address of next instruction in trap region.

- 5. Jump to common interrupt handler which stores register, etc.

- 6. Place new interrupt priority in mask register.

- 7. Obtain address of interrupt subprogram and transfer control there

- 8. Execute subroutine to accomplish the necessary action for the particular interrupt

- 9. Restore all necessary registers

- 10. Exit the interrupt state and return to the main program.

# **Interrupt Processing (Exercise)**

**DIRECTIONS**: Place a T or F in the space provided by each of the following True/False questions.

| <br>1. | If the instruction OE1C is used to exit the interrupt state, interrupt state 03 was active.                   |

|--------|---------------------------------------------------------------------------------------------------------------|

| <br>2. | The instructions in the interrupt trap region store the needed register.                                      |

| <br>3. | If an interrupt state 07 becomes active, the return address is stored in location 011C.                       |

| <br>4. | If the M register contains 0090 and the EIN instruction is executed, interrupt lines 7 and 4 will be enabled. |

| <br>5. | The return address for a particular interrupt is stored by the common interrupt handler.                      |

| <br>6. | Sixty-four locations are set aside in the trap region to handle the sixteen interrupts.                       |

#### ANSWERS

#### 1. F 2. F 3. T 4. T 5. $\hat{F}$ 6. T

# **SMI Register Descriptions**

In this activity you will learn the functions of the status mode interrupt (SMI) module.

The SMI module consists of the following functional areas:

- Status mode registers, SM1 and SM2

- Mask registers, M1 and M2

- Interrupt Register

- Interrupt System

- Selector S9

Some areas of the SMI are not used in the interrupt process but are included here for completeness.

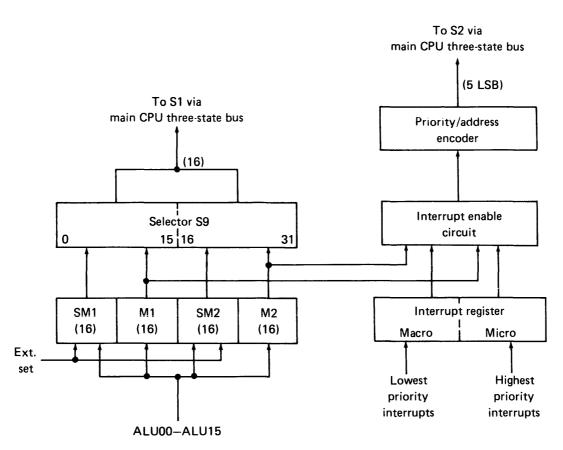

As you read about each area, refer to the SMI block diagram in figure 1-5 to see the relationships between areas.

#### **Status Mode Register**

Two status/mode (SM) registers referred to as SM1 and SM2, allow the microprogram to control the mode of operation and to examine the status of certain internal and external conditions. Each register has sixteen bits for a total of thirty-two status mode bits. All SM bits can be set or cleared by transferring information from the output of the ALU. MASTER CLEAR clears both SM1 and SM2.

#### **Mask Register**

The main purpose of the mask register is to enable and disable the desired interrupt lines. To enable an interrupt line, its corresponding mask bit must be set to 1. Mask register M1 controls interrupt lines 00 through 15 (microinterrupts) and M2 controls interrupt lines 16 through 31 (macrointerrupts).

The mask bits can be set and cleared only be transferring information from the ALU outputs. MASTER CLEAR does not clear the mask bits.

#### **Interrupt Register**

The thirty-two bit interrupt register stores the conditions of the interrupt lines. The output of this register is compared with the outputs of the mask register to control the

The numbers in parentheses indicate the width of the registers.

Figure 1-5. SMI Module Block Diagram

interrupt recognition. The interrupt system is implemented as a sampled data system at the microprogram level. The INTU microinstruction samples the interrupt system to determine if the corresponding mask register bit of any interrupt present is set to 1. The interrupt signals must be in a steady state because of this interrupt sampling method. The typical interrupt line assignments are shown in table 1-2. Keep in mind that you will be primarily concerned with lines 16 through 31, the macrointerrupt lines.

#### **Interrupt System**

Once the interrupts are recognized, the interrupt address encoder selects the highest priority interrupt and generates its corresponding address. The interrupt address is the same as its priority level; i.e., the highest priority for macrointerrupts is 16,

| Mask<br>Bit | Interrupt<br>Line<br>Number | Slot/Pin | Prewired to<br>I/O Slot/Pin | Functions                                                             |

|-------------|-----------------------------|----------|-----------------------------|-----------------------------------------------------------------------|

| M115        | 00                          | L227     |                             | Open                                                                  |

| M114        | 01                          | L27      | K242                        | ADT interrupt for TTY/display controller                              |

| M113        | 02                          | L32      |                             | Open                                                                  |

| M112        | 03                          | L232     |                             | Open                                                                  |

| M111        | 04                          | L28      | J250                        | ADT interrupt for line printer con-<br>troller                        |

| M110        | 05                          | L31      | G250                        | ADT interrupt for communications line adapter                         |

| M109        | 06                          | L231     |                             | Open                                                                  |

| M108        | 07                          | L228     | E250                        | ADT interrupt for tape cassette interface                             |

| M107        | 08                          | L30      | K86                         | Real-time clock microinterrupt                                        |

| M106        | 09                          | L230     |                             | Open                                                                  |

| M105        | 10                          | L229     |                             | Open                                                                  |

| M104        | 11                          | L29      | J50                         | ADT interrupt for card reader con-<br>troller                         |

| M103        | 12                          | L33      | K85                         | Panel simulation (keyboard input)                                     |

| M102        | 13                          | L226     | K272                        | Panel simulation (display output)                                     |

| M101        | 14                          | L233     | U99                         | Panel request to CPU (used during emulation)                          |

| M100        | 15                          | L234     | L288                        | Macrostop signal (SM215); suspends emulation                          |

| M215        | 16                          | L69      | R277                        | Internal interrupt for power failure, parity error, and protect fault |

| M214        | 17                          | L269     | K58                         | Program interrupt for TTY/display . controller                        |

| M213        | 18                          | L270     |                             | Open                                                                  |

| M212        | 19                          | L70      | H249                        | Program interrupt for disk adapter<br>(SMD operation)                 |

TABLE 1-2Typical Interrupt Line Assignments

| Mask<br>Bit | Interrupt<br>Line<br>Number | Slot/Pin | Prewired to<br>I/O Slot/Pin | Functions                                              |

|-------------|-----------------------------|----------|-----------------------------|--------------------------------------------------------|

| M211        | 20                          | L272     | J249                        | Program interrupt for line printer controller          |

| M210        | 21                          | L272     | G249                        | Program interrupt for communica-<br>tions line adapter |

| M209        | 22                          | L271     |                             | Open                                                   |

| M208        | 23                          | L71      | E249                        | Program interrupt for tape cassette interface          |

| M207        | 24                          | L73      | K285                        | Program interrupt for real-time clock                  |

| M206        | 25                          | L274     | Open                        |                                                        |

| M205        | 26                          | L74      |                             | Open                                                   |

| M204        | 27                          | L273     | J49                         | Program interrupt for card reader controller           |

| M203        | 28                          | L277     |                             | Open                                                   |

| M202        | 29                          | L276     |                             | Open                                                   |

| M201        | 30                          | L77      |                             | Open                                                   |

| M200        | 31                          | L275     |                             | Macrobreakpoint (SM104) interrupt                      |

TABLE 1-2 (continued)

corresponding to mask bit M215. The interrupt address generated would be 16. The output of the interrupt address encoder is the complement of the interrupt address. This output sends the address of the interrupt to the computer S2 register.

### **Selector S9**

The last area in the SMI to be covered is selector S9. It is a sixteen-bit-wide selector that selects one of four sources (SM1, SM2, M1, or M2) to be sent to the ALU. During an interrupt, this is used to transfer the mask register to storage in order to save the information for use when the main program is resumed.

# **SMI Data Flow (Text)**

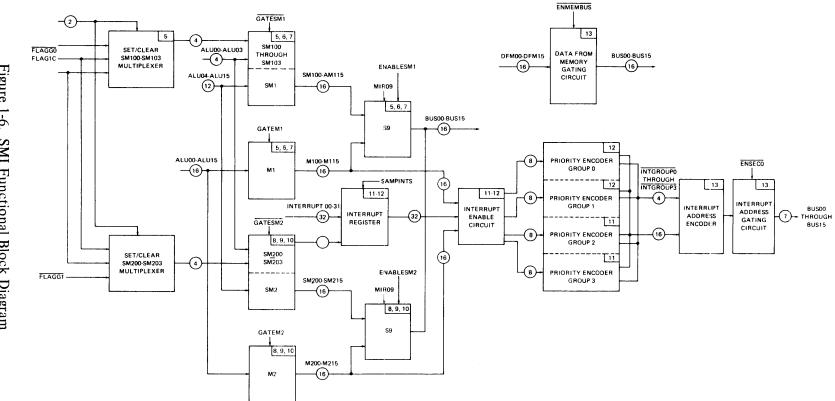

During this activity you will follow the data flow path through the SMI module using the block diagram in figure 1-6. The data flow descriptions will be for the interrupts that may take place in the SMI.

#### **Interrupt Enable**

First, in order to enable the interrupt system, the EIN instruction must have been executed and the appropriate bit or bits must be set in the mask register M2. Setting the mask register is accomplished by transferring the bits from the ALU section to the mask register. Once the mask is set, the output of M2 is available to the input of the interrupt enable circuit.

#### **Interrupt Generation**

When an interrupt or interrupts occur, the interrupt register is clear in accordance with the interrupt line, or lines, that are active. The output of this register is placed on the input lines of the interrupt enable circuit which checks to see if a mask bit is set for the interrupt line that is active. If the active interrupt line and the bit in the mask register match, the interrupt is passed on to the priority encoder section.

#### **Interrupt Priority**

If more than one interrupt is active, the priority encoder section determines which interrupt has the highest priority and passes it on to the interrupt address encoder. The encoder generates the address of the interrupt, this allows the computer to recognize the origin of the interrupt. This address is gated to the processor by the interrupt address gating circuit through the tri-state bus.

#### **Interrupt Process**

When the computer is halted by the interrupt, the return address is stored in the trap region and the M2 mask register is stored so the information can later be recalled. After the interrupt has been processed, M2 will be loaded with the original contents (contents when interrupt occurred) by way of the ALU lines. When all registers have been restored, the main program will continue within the CPU.

### Summary

The interrupt process consists of the following four basic steps.

- Enable interrupt

- Generate interrupt

- Determine priority and generate interrupt address

- Interrupt process

# **SMI Data Flow (Exercise)**

DIRECTIONS: Answer the following questions by filling in the blanks.

- 1. The M2 register is set by information that is transferred from the \_\_\_\_\_\_ circuits.

- 2. When an interrupt occurs, it causes the \_\_\_\_\_\_ to be clear.

- 3. An interrupt is checked to see if the corresponding bit in the mask register is set in the \_\_\_\_\_\_ circuit.

- 5. The computer recognizes which interrupt has occurred by receiving the output of the \_\_\_\_\_\_.

DIRECTIONS: Answer the following True/False questions by placing a T or F in the space provided.

- 6. If M2 register is not available, M1 may be used to enable certain macrointerrupts.

- \_\_\_\_\_ 7. The interrupt address encoder specifies which interrupt has occurred.

- 8. Selector S9 provides a path from the mask register to the interrupt enable circuit.

#### ANSWERS

1. ALU 2. Interrupt register 3. Interrupt enable 4. Selector S9

5. Interrupt address encoder 6. F 7. T 8. F

# **Interrupt Condition Processing**

During this activity, you will follow the steps that are involved in the processing of an interrupt. You will need the logic prints for the SMI module, as you will be tracing the signal flow for the interrupt. In the example that is used, only one interrupt is active, but keep in mind that all interrupts are processed in a similar manner.

#### Set Mask Register

The first step involved in the interrupt process is setting the appropriate bits in the mask register. Suppose, for example, that it is desired to check interrupt line 22 (macrointerrupt 06). An interregister instruction is used to place 0040 in the M2 register. This places a "1" in bit position 6, which enables the interrupt. Refer to sheet 9 of the logic prints. The flip-flop that will set in the M2 register is in position K2. It is set by the pin 4 input when the GATEM2 signal occurs. The set output of this flip-flop is M209.

Next, refer to sheet 11 of the logic prints. Note that M209 is one of the inputs to a NAND gate at location H2. The other input to this gate is from output pin 14 of the flip-flop at H7. When an interrupt occurs, interrupt line 22 becomes active and the flip-flop at H7 clears when the SAMPINTS signal is received. The interrupt signal can now be checked against the corresponding mask bit by the NAND gate at H2.

#### **Interrupt Priority**

From the NAND gate, the signal is sent to the priority interrupt level encoder, J3, which determines the priority if more than one interrupt happens to be active. In this case the output of the encoder indicates a group 2 interrupt on line 22.

#### **Interrupt Address**

From the priority level encoder, the signals are placed on the inputs of the interrupt address encoder located on sheet 13 of the logic prints. These circuits are composed of the encoder in E1, the MUX chip at H1 and the MUX chip at G1.

The INTGROUP 2/signal into the encoder causes a signal output which sets the active interrupt present flip-flop when the SAMPINTS signal is active. This informs the

#### Interrupt System

computer that an interrupt has become active. Other outputs from the encoder form a portion of the interrupt address. The interrupt address is sent to the computer on BUS11 through BUS15 to inform the processor which interrupt line caused the interrupt. Note that the two MUX chips form the remainder of the address sent to the computer.

The interrupt address for the example used (22) is sent to the computer as 0 1 0 0  $1_2$  on Bus11 through Bus15. Refer to Table 1-3, Basic Processor Interrupt Addresses, and note that this is the inversion of the actual interrupt address,  $16_{16}$ . The signals which enable the address to be sent to the processor on Bus11-Bus15 are ENSEC0/ and ENSEC1/.

#### **Summary**

Briefly, the steps involved in processing an interrupt are as follows:

- 1. Set mask register.

- 2. Interrupt occurs clearing the interrupt register.

- 3. Output of interrupt register is compared with mask bit.

- 4. Priority encoder determines level of priority for interrupt.

- 5. Information is sent to interrupt address encoder.

- 6. Address of interrupt is generated and enabled to computer via BUS11-BUS15.

| Mask<br>Bit                                                  | Actual<br>Interrupt<br>Address<br>16         | Interrupt Line<br>Number |                                              |                 | Output of<br>Interrupt<br>Address<br>Encoder<br>BUS11-BUS15                                                                                                                                         |

|--------------------------------------------------------------|----------------------------------------------|--------------------------|----------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M200<br>M201<br>M202<br>M203<br>M204<br>M205<br>M206<br>M207 | 1F<br>1E<br>1D<br>1C<br>1B<br>1A<br>19<br>18 | Group 3                  | 31<br>30<br>29<br>28<br>27<br>26<br>25<br>24 | Lowest Priority | $\begin{array}{c} 0 \ 0 \ 0 \ 0 \ 0 \\ 0 \ 0 \ 0 \ 0 \ 1 \\ 0 \ 0 \ 0 \ 1 \ 0 \\ 0 \ 0 \ 0 \ 1 \ 1 \\ 0 \ 0 \ 1 \ 0 \ 0 \\ 0 \ 0 \ 1 \ 0 \ 1 \\ 0 \ 0 \ 1 \ 1 \ 0 \\ 0 \ 0 \ 1 \ 1 \ 1 \end{array}$ |

| M208<br>M209<br>M210<br>M211<br>M212<br>M213<br>M214<br>M215 | 17<br>16<br>15<br>14<br>13<br>12<br>11<br>10 | Group 2                  | 23<br>22<br>21<br>20<br>19<br>18<br>17<br>16 |                 | $\begin{array}{c} 0 \ 1 \ 0 \ 0 \ 0 \\ 0 \ 1 \ 0 \ 0 \ 1 \\ 0 \ 1 \ 0 \ 1 \\ 0 \ 1 \ 0 \ 1 \\ 0 \ 1 \ 0 \ 1 \\ 0 \ 1 \ 1 \\ 0 \ 1 \ 1 \ 0 \\ 0 \ 1 \ 1 \ 1 \\ 0 \ 1 \ 1 \ 1 \\ \end{array}$         |

| M100<br>M101<br>M102<br>M103<br>M104<br>M105<br>M106<br>M107 | 0F<br>0E<br>0D<br>0C<br>0B<br>0A<br>09<br>08 | Group 1                  | 15<br>14<br>13<br>12<br>11<br>10<br>09<br>08 |                 | $1 0 0 0 0 \\ 1 0 0 0 1 \\ 1 0 0 1 0 \\ 1 0 0 1 1 \\ 1 0 1 0 0 \\ 1 0 1 0 1 \\ 1 0 1 0 1 \\ 1 0 1 1 0 \\ 1 0 1 1 1 $                                                                                |

| M108<br>M109<br>M110                                         | 07<br>06<br>05                               | Group 0                  | 07<br>06<br>05                               |                 | 1 1 0 0 0<br>1 1 0 0 1<br>1 1 0 1 0                                                                                                                                                                 |

TABLE 1-3Basic Processor Interrupt Addresses

# Logic Diagram

DIRECTIONS: Answer the following questions about the SMI circuit operation. Refer to the SMI logic diagrams for any information you require.

- 1. In order to place information into the mask 2 register, an enable signal must be provided. This enable signal is \_\_\_\_\_.

- a. ALU 15

- b. GATEM2

- c. GATEM1

- d. SM215

# \_\_\_\_\_ 2. Refer to sheet 11 of the logic prints. The purpose of the SAMPINTS signal is to \_\_\_\_\_.

- a. Clear the flip-flops in the interrupt register

- b. Load interrupt conditions into the interrupt register

- c. Indicate that an interrupt has occurred by going low.

- d. Inform the computer that an interrupt has occurred

- 3. If the mask 2 register contains 0009 and an internal interrupt occurs, the flip-flop in the interrupt register that will be clear is \_\_\_\_\_\_.

- a. H6, cleared by pin 12

- b. H5, cleared by pin 13

- c. H6, cleared by pin 13

- d. No flip-flop is set for this interrupt

4. Refer to sheet 11 of the logic prints. If interrupt state 04 becomes active, the circuit that checks to determine if the mask bit is set for this interrupt is \_\_\_\_\_\_.

- a. NAND circuit at H4, pin 9 input

- b. Priority interrupt level encoder J3, pin 13 input.

- c. Flip-flop at H7, pin 5 input

- d. NAND circuit at H2, pin 1 input

- 5. If the M2 register contains 0080 and an interrupt occurs for state 07, this interrupt is\_\_\_\_\_\_.

- a. Recognized by pin 8 of H2 going low

- b. Not recognized because mask bit is not set

- c. Recognized by pin 3 of J1 going low

- d. Recognized by the setting of flip-flop at H5, pin 13 input

Logic Diagram

ANSWERS

1. b 2. b 3. a 4. d 5. a

Block 2

I/O System

## **I/O Functional Description**

Input/output is an important functional part of any computer. On the CYBER 18-20 processor, the I/O logic is located on the I/O-TTY controller board. What is on this board, when it is used, and how it is used are all introduced in this reading.

#### What Is on the Board

A number of different functions are found on the I/O-TTY. One is, of course, the I/O logic; another is the controller for a teletypewriter or conversational display terminal.

Also located on the I/O-TTY board are circuits that involve panel simulation functions and status or interrupt selection functions. The panel simulation functions are used if the breakpoint controller board is not installed in the processor. The status or interrupt functions provide status data to the CPU and macrointerrupts to the SMI logic.

#### When I/O Is Used

Information is transferred through the I/O section in four cases:

- When data is sent from the CPU to a peripheral

- When data is sent from a peripheral to the CPU

- When special functions are being selected in a peripheral

- When the status (condition) of a peripheral is being checked

In addition to the information, the address of the peripheral device being used must be sent through the I/O section. The address is used to gate the information to or from a specific peripheral device.

### How I/O Is Used

The information transferred through the I/O section either originates in or goes to the A register. The address of the peripheral device originates in the Q register. (Both the A and Q registers are in the arithmetic logic unit.) When information leaves the A register and goes to the I/O section, it is referred to as a "write, output, or set operation." Information going to the A register from the I/O section is referred to as a "read, input, or sample operation."

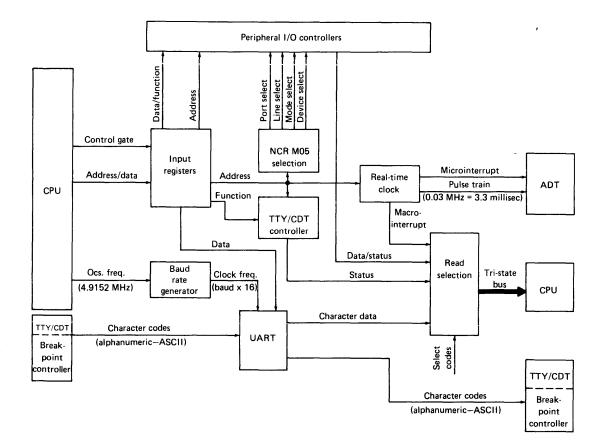

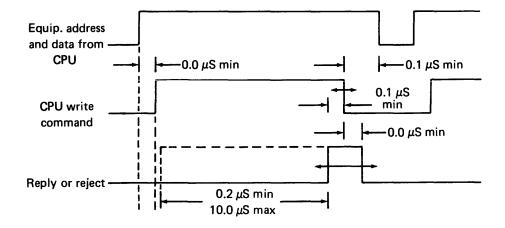

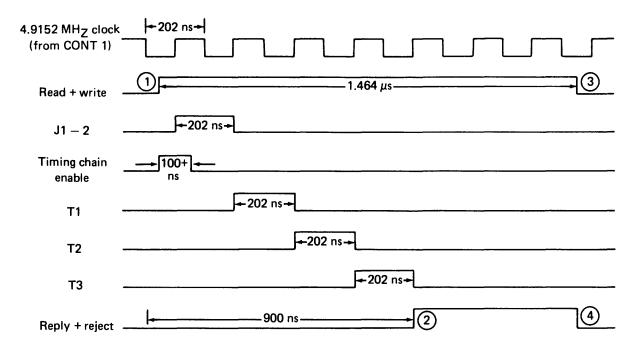

#### I/O System

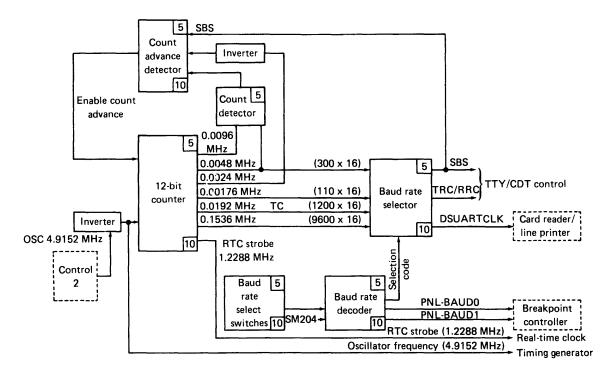

To perform a read or write operation, the computer must decode the read or write instruction. Once the instruction is decoded, control signals are sent to the I/O section from control 1 and SMI sections. Timing for the I/O operations are controlled by a 4.9152 MHz clock signal from control 2, a baud rate generator, and a three-phase timing generator. The baud rate and timing generator are both located on the I/O-TTY controller board.

The I/O operations are of two types: internal and external. When an external operation is specified by the address, the data is processed by the addressed peripheral controller. When an internal operation is selected, the data is processed on the I/O-TTY controller board. The internal operations are the real time clock (RTC) and the communications interface. The real time clock is used in the automatic data transfer (ADT) routine. The communications interface involves the transfer of data between the CPU and the TTY or CDT.

#### **Summary**

The I/O function is found on the I/O-TTY controller board. It is used in transferring data between one CPU and associated peripherals and in selecting special functions in checking the status of those peripherals. I/O operations are either read or write operations, and occur internally or externally.

## I/O Schemes

In the CYBER 18-20, three data transfer schemes are possible: the 1700 computer A/Q scheme, the M05 set/sample scheme, and the automatic data transfer (ADT) scheme. Each of these schemes will be explained in this text.

The CYBER 18-20 can be made to emulate the Control Data 1700 computer, which uses an I/O system in which the A and Q registers directly interface with the I/O channel. When this emulation occurs, the I/O system is referred to as an "A/Q scheme" and the I/O channel is called the "A/Q channel." The A/Q channel scheme is used with the following peripherals: line printers, card readers, disks, and display consoles.

Because the CYBER 18-20 processor is a result of the efforts of two companies, Control Data Corporation (CDC) and National Cash Register (NCR), the I/O section of the CYBER 18-20 contains both the Control Data and the NCR I/O schemes. While the A/Q scheme is a Control Data scheme, the M05 set/sample scheme is the NCR I/O scheme. The M05 set/sample scheme is used with the magnetic tape peripheral.

The 1700 A/Q scheme and the M05 set/sample scheme transfer only one word of information at a time. When blocks of information are to be transferred, the ADT method of data transfer is used. Using the ADT scheme results in faster data I/O.

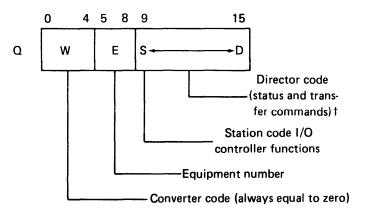

### A/Q Scheme

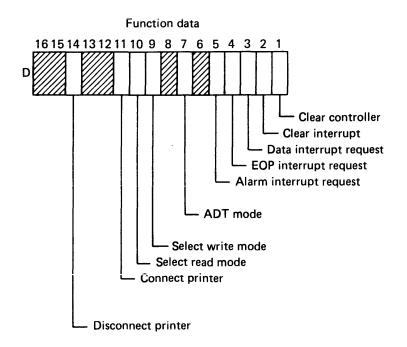

The A/Q scheme of input/output is initiated when the microprocessor executes the instructions INP or OUT. Prior to the execution of either instruction, the address of the intended peripheral must have been loaded into the Q register. The A register contains data, status, or functions, depending upon the value of the director bits in the Q register. During I/O operations, the A and Q registers have a specific format. The format of the Q register is shown in figure 2-1.

When the director code is a logic 0, the A register is assumed to contain data. This data goes to the peripheral (OUT) or from the peripheral to the A register (INP), depending upon the instruction being executed. When the director code is nonzero, the A register is assumed to contain either a function to be selected in the peripheral (OUT) or the present status of that peripheral (INP), depending again upon the instruction (INP or OUT) executed. Table 2-1 illustrates the use of the A register, depending on the director bit and the instruction executed.

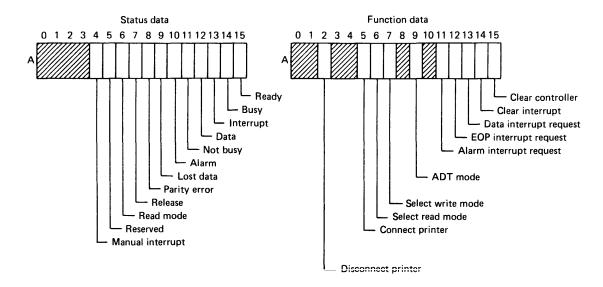

Figure 2-2 shows examples of the A register data when it contains peripheral status or peripheral functions to be selected. Its use varies with each equipment type.

†The S and D fields have no bound, but may not overlap.

Figure 2-1. Q Register Format I/O Operations

# TABLE 2-1Use of the A Register

| Director Bit | Instruction    |                   |  |

|--------------|----------------|-------------------|--|

|              | INP            | OUT               |  |

| 0            | Read<br>Data   | Write<br>Data     |  |

| 1            | Read<br>Status | Write<br>Function |  |

Figure 2-2. A Register Format Peripheral Status or Function

To output data to a peripheral, the address (equipment number) is placed in the Q register and the director bit is set. The write select bit (bit 7) in the A register must be set and the OUT instruction executed. This process sets up the peripheral to receive data from the CPU. Next, the director bit is cleared and the output data is placed in the A register. When the next OUT instruction is executed, the data in the A register is sent to the peripheral.

The procedure for receiving data at the CPU is similar to the output procedure. First of all, bit 6 of the A register is set. This selects a read operation. The function is sent to the peripheral when the OUT instruction is executed. Then, the input (INP) instruction is executed. This causes the data to be gated from the peripheral to the CPU. The operational status of a peripheral may be sensed by having the address in the Q register, having the director bit set, and executing an input instruction. The status of the peripheral is then sent to the CPU. I/O System

#### M05 Set/Sample Scheme

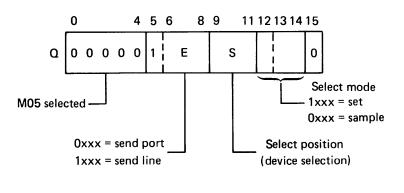

The M05 set/sample I/O scheme is used to transfer data to and from the magnetic tape peripheral devices. The set/sample I/O scheme is initiated by the SIO instruction. The Q register is used to hold the address of the peripheral device and the data is transferred to or from the A register. The format of the Q register is shown in figure 2-3.

Bits 0 through 11 are used to determine if the M05 set/sample has been selected. Bits 0 through 4 must be clear. Bit 5 must be set. Bits 6 through 8 (the E field) may be  $1_8-7_8$ . The S field may be  $0_8-7_8$ , and bit 12 (the set/sample bit) may be 1 (set) or 0 (sample). When the above conditions are met, the M05 set/sample scheme has been selected. When bit 12 is set, data is sent to the peripherals; when bit 12 is clear, data is sent by the peripheral to the CPU. The status of the peripherals may be checked or the functions selected when bit 12 is clear or set, respectively. The send lines (bits 6 through 8) are used to select the peripheral controller while the "select position" selects a peripheral on the controller.

#### Automatic Data Transfer (ADT)

The ADT type of data transfer can be used when blocks (groups of words) are to be transferred to or from a peripheral device. This type of data transfer is faster than the A/Q scheme, but slower than a DMA transfer. The peripheral and the peripheral controller must be capable of handling the ADT transfers. To initiate an ADT transfer, the DMI instruction must be executed. This specifies both the direction of transfer (read or write) and the addresses (in memory) of the first and last word of the block of data to be transferred. The address of the peripheral must be in the Q register, and bit 9 of the A register must be set. Next, an I/O instruction (INP, OUT, SIO) must be executed.

The complete block of data is not transferred at once but one word at a time. Whenever a word is to be transferred, a microinterrupt is generated. When the interrupt has the highest priority, it is executed by the microsubroutine. While the ADT operation is in progress, the emulator can be busy executing other macroinstructions. At the end of the ADT operation, a macrointerrupt is generated, at which time another ADT operation can be specified or the ADT interrupts can be disabled.

#### **Summary**

Table 2-2 summarizes the three types of I/O schemes used with the CYBER 18-20 processor.

| Names                             | How Used                                                       | Initiated by |

|-----------------------------------|----------------------------------------------------------------|--------------|

| 1700 computer A/Q<br>scheme       | With line printers, card<br>readers, disks, display<br>console | INP or OUT   |

| M05 set/sample<br>scheme          | With magnetic tapes                                            | SIO          |

| Automatic data<br>transfer scheme | When blocks of informa-<br>tion are transferred                | DMI          |

# TABLE 2-2Summary of I/O Schemes

## I/O System

DIRECTIONS: Answer the following questions, or complete the following statements.

\_\_\_\_

- 1. List the three I/O schemes used in the CYBER 18-20 microprocessor.\_\_\_\_\_

- 2. The I/O section is located on the \_\_\_\_\_ board.

\_\_\_\_

- 3. In addition to the I/O section, what are two other controls on the board referenced in question 2 above?

- 4. The M05 set/sample scheme is initiated by the \_\_\_\_\_\_ instruction.

- 5. Name the peripheral that uses the set/sample I/O scheme. \_\_\_\_\_.

- 6. What is the main purpose of the ADT type of I/O operation?\_\_\_\_\_

- 7. List two advantages of the ADT scheme.

#### ANSWERS

1. A/Q scheme, ADT scheme, M05 set/sample scheme 2. I/O-TTY controller 3. TTY controller, real time clock 4. SIO 5. Magnetic tape 6. To transfer blocks of data 7. It is faster than the A/Q scheme, and macroinstructions can be executed while the ADT is in operation.

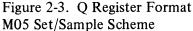

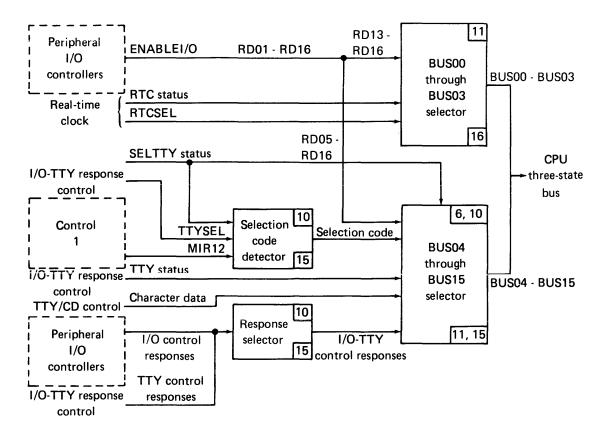

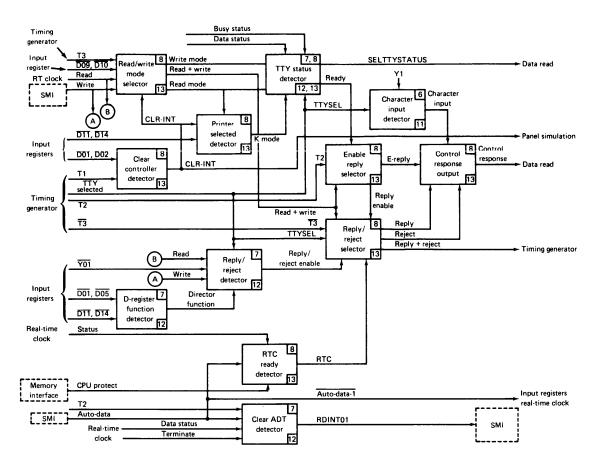

## I/O Signal Flow

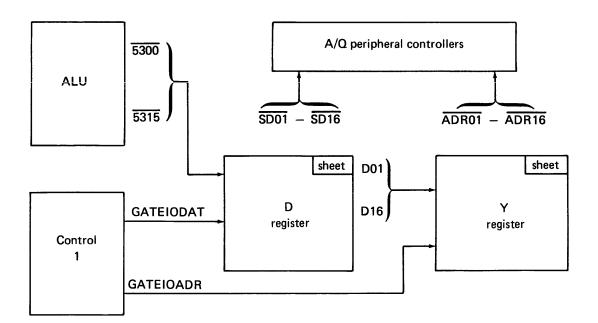

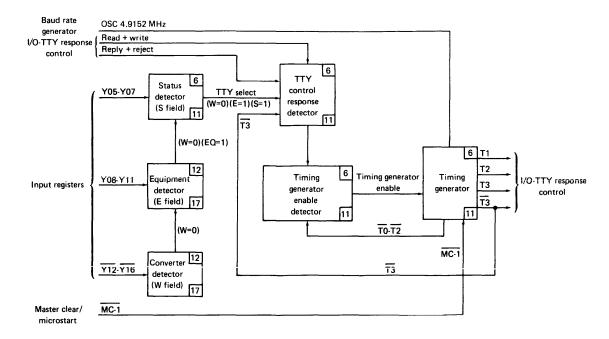

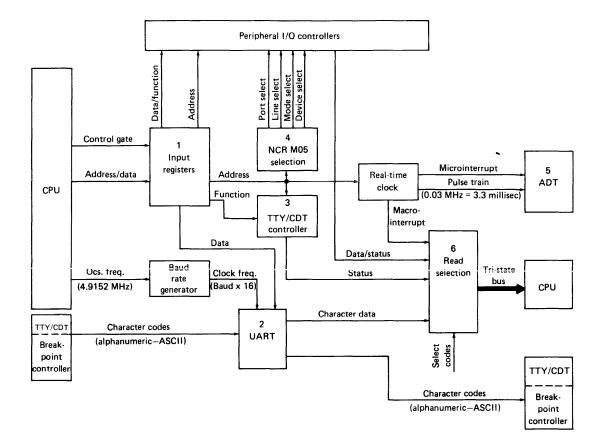

The functions of the I/O-TTY board can be broken into two parts: internal and external. The part used depends upon the address in the Q register. When the address specifies any peripheral except for the TTY or CDT, the external function will be selected. On the other hand, when the address specifies an internal operation, the real time clock (RTC) or the TTY/CDT controller will be selected. Figure 2-4 is a functional block diagram of the I/O-TTY controller board.

Figure 2-4. I/O-TTY Controller Functional Block Diagram

The input registers, NCR M05 selection circuits, and read selection circuits make up the external functional circuits. When an internal function is selected, all blocks are considered. The RTC internal function will use the input registers, real time clock, ADT, and read selection circuits. When the TTY or CDT has been selected, all blocks except the real time clock, ADT, and NCR M05 selection circuits are used.

## I/O Addressing

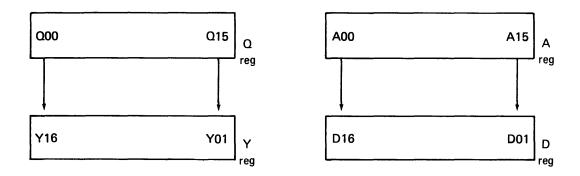

When any output operation is specified, the input registers on the I/O-TTY controller board are loaded with the peripheral address from the Q register and data or function from the A register. The registers on the I/O-TTY board are the Y and D registers. The Y register is used to hold the peripheral address while the D register holds the data or function. When the output instruction is decoded, the control 1 section generates two signals that gate the information into the Y and D registers. The Y and D registers are just extensions of the Q and A registers. The only differences between the Y and D and the Q and A registers are the way their bits are numbered. The Q and A registers have the most significant bit as Q00 and A00, while the Y and D registers have the most significant bits as Y16 and D16. This is shown in figure 2-5.

Figure 2-5. Differences Between Y, D, Q, and A Registers

Refer to the logic prints for the I/O-TTY controller. The D register consists of flipflops A10, C10, F9, and F10, on sheet 9, and flip-flops F9, on sheet 17. The data inputs to the D register are the signals S301/ through S315/, which are coming from the CPU. (Remember that the slash (/) represents a low active signal.) The Y register consists of flip-flops A9, C9, and G10, on sheet 9, and flip-flops F8, on sheet 17. The data inputs to the Y register are the complemented outputs from the D register.

- After an output instruction is decoded by the CPU, the peripheral address from the Q register appears on the signal lines \$\overline{3300}\$ through \$\overline{3315}\$. The signal GATEIOADR, on sheet 9, comes from the control 1 section. When an I/O instruction is decoded, this signal goes low.

- 2. When the signal GATEIOADR goes low, the output of gate D3, on sheet 9, goes high and clocks the peripheral address into the D register.

- a. The complemented outputs of the D register feed the Y register, so now the peripheral address is present at the data inputs to the Y register.

- b. When the signal GATEIOADR goes high, the output of gate B3, on sheet 9, goes high and gates the peripheral address into the Y register.

- 3. Next, the contents of the A register, data or function, appear on the signal lines  $\overline{S300}$  through  $\overline{S315}$ . The signal  $\overline{GATEIODAT}$ , from control 1, goes low.

- 4. When the signal GATEIODAT goes low, the output of gate D3, on sheet 9, will go high and gate the data or function into the D register.

Now the Y and D registers have been loaded with the contents of the Q and A registers, respectively. The destination of the function or data within the D register depends upon the address in the Y register. This address may specify a peripheral on the A/Q channel, the M05 set/sample I/O system, the RTC, or the TTY/CDT on the communications channel.

When the address in the Y register specifies a peripheral on the A/Q channel, then the address goes to the peripheral from the complemented outputs of the Y register—the signals  $\overline{\text{ADR01}}$  through  $\overline{\text{ADR16}}$  on sheets 9 and 17 of the I/O-TTY controller logic sheets—and the data or function goes to the peripheral from the true outputs of the D register, signals  $\overline{\text{SD01}}$  through  $\overline{\text{SD16}}$  on sheets 9 and 12 of the I/O-TTY controller logic prints. Bit 1 of the Y register is the director bit. When Y1 is set, the D register contains a peripheral function; when it is clear, the D register contains data. Figure 2-6 is a block diagram of the I/O system A/Q scheme.

Figure 2-6. Block Diagram of A/Q Scheme

#### I/O System

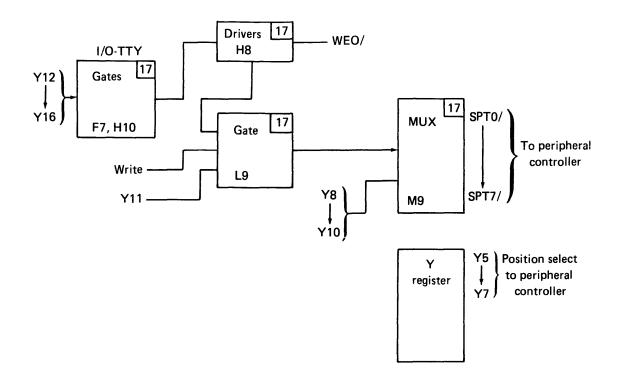

The address in the Y register can reference the M05 set/sample I/O scheme. Along with specific bits in the Y register, the signals AUTO-DATA and WRITE from the SMI module enable the selection of the M05 set/sample scheme. Y register bits 5 through 16 determine if the M05 I/O scheme has been selected. The decoding of bits Y8 through Y16 occurs on the I/O-TTY board, on sheet 17.

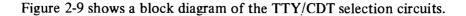

- 1. The W field (Y12 through Y16) must be equal to zero. The complemented outputs of the four flip-flops F8, on sheet 17, are ANDed together in gate F7, on sheet 17. These flip-flops contain bits Y13 through Y16.

- a. The output of gate F7 is ANDed with bit Y12 in gate H10. The output of gate H10 goes low when the W field (bits Y12 through Y16) is equal to zero.

- b. The output of gate H10 goes through two inverters, H8, and makes the signal WE0 go low when the W field is equal to zero.

- 2. The output of the first inverter, H8, partially enables gate L9. The other inputs to gate L9 are the signals WRITE and Y11. The signal WRITE is generated on the SMI board in the CPU and is a logic 1 during an output operation. Y11 (bit 11 of the Y register) must be a logic 1 when selecting the M05 I/O scheme.

- 3. When the inputs to gate L9 are high, its output goes low and enables multiplexer M9.

- a. The outputs of the multiplexers M9 are the port select signals  $\overline{SPT0}$  through  $\overline{SPT7}$ . The output is selected by the select inputs of the multiplexers, which are connected to the signals Y8 and Y9.

- b. The select inputs of multiplexer M9 enable the D data input to be applied to one output. The D input (pin 15) of the top mux M9 is low active, while the D input (pin 1) of the bottom mux M9 is high active. The D inputs of both multiplexer is the signal Y10. The port select lines are enabled by any combination of bits Y8 through Y10 (the E field).

- 4. The peripheral is completely selected by specifying the position select (the S field). The S field (bits Y5 through Y7) are decoded on the peripheral controller specified by the port select lines SPT0 through SPT7, which were decoded above.

Figure 2-7 is a diagram of the M05 scheme selection circuit.

Figure 2-7. MO5 Scheme Selection Circuit

The MO5 scheme may be selected during automatic data transfer (ADT) when the Y register bits Y8 through Y11 specify the M05 scheme and the SMI module sends the signal AUTO-DATA to the I/O-TTY controller board.

- 1. The signal AUTO-DATA enters the I/O-TTY board on sheet 17. It passes through inverter M4 and is applied to gates H10 and L10.

- a. The signal AUTO-DATA is inverted twice as it passes through gates H10 and H8, on sheet 17, before being applied to gate L9.

- b. The signal Y11, on sheet 17, must be high to enable gate L10 and partially enable gate L9. Gate L9 is completely enabled when the signal WRITE is high.

- c. The low outputs of the gates L9 and L10 enable multiplexers M9 and M10. The selection of the port and select lines is made by signals Y8 through Y10.

#### I/O System

When an external device has been addressed by the A/Q or M05 schemes and an output instruction (OUT or SIO) is executed, data or functions are sent from the D register to the peripheral controller. When a function is sent to the controller, the controller sets up logic conditions that cause the peripheral to act in a specified manner. As an example, the function might cause a write or read operation to be set up in the magnetic tape peripheral and controller.

The address in the Y register can specify internal operations as well as external operations. The two internal operations are the real time clock (RTC) and the communications interface (TTY or CDT).

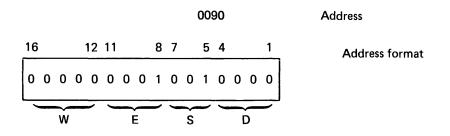

The address required to select the TTY/CDT is 0090 or 0091. Address 0091 causes functions to be selected or status to be sensed, while 0090 causes a data transfer. The TTY is selected by using the twelve most significant bits of the Y register. With 009 as the bit configuration required to select the TTY/CDT, the decoding of the Y register, using the Y register format, gives (W = 0), (E = 1), and (S = 1). This is illustrated in figure 2-8.

Figure 2-8. Decoding the Y Register

To select the TTY/CDT, bits Y5 and Y8 must be set, while all other bits are clear.

The decoding of the address in the Y register begins on sheet 17 of the I/OTTY board logic prints.

- 1. Bits Y16 through Y13 are ANDed together in gate F7. The output of gate F7 and bit Y12 are ANDed in gate H10. The output of gate H10 will be low when bits Y12 through Y16 are clear, when W = 0.

- 2. The output of gate H10 goes through inverter H8 and goes to gate J8. The output of gate J8 will be high when W = 0 and bit Y8 are both true.

3. The output of gate J8 goes to gate L8 with a logic 1. Pins 2, 5, and 4 of gate L8 are high when bits Y11, Y9, and Y10, respectively, are low. The output of gate L8, the signal (W = 0) (EQ = 1) will be high when Y16 through Y9 are low and Y8 is high, that is, when W equals zero and E equals 1.

<u>Note</u>: The decoding of W = 0 and E = 1 is done for both internal functions: selecting the RTC or the TTY/CDT.

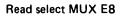

4. The signal (W = 0) (EQ = 1) goes to sheet 11 of the I/O-TTY board, where it goes to gate F7. The other inputs to gate F7 are signal Y5 and the outputs from inverter C8. The output of gate F7, the signal TTYSEL, will be high when signals (W = 0) (EQ = 1) and Y5 are true and the signals Y6 and Y7 are false.

Figure 2-9. Block Diagram of TTY/CDT Selection Circuits

Once the address in the Y register has selected the TTY/CDT, functions may be selected, status may be sensed or data may be transferred, depending upon the Y register bit Y1.

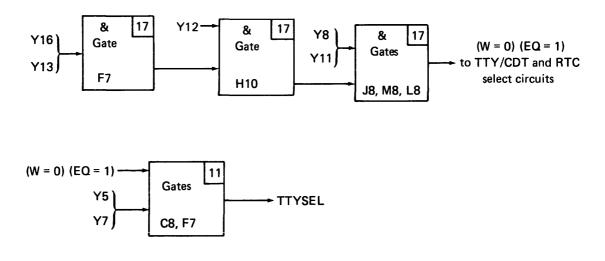

When the RTC is to be selected, the signal (W = 0) (EQ = 1), which was decoded above on sheet 17, goes to sheet 16. This signal goes to gate C4 along with signals Y5, Y6 and Y7. When all four signals are true, the output of gate C4 goes high and enables the RTC. To select the RTC, the address must be 00F0 or 00F1; the part of the address that selects the RTC is 00F. Once the peripheral has been correctly addressed, desired operations may be selected by the contents of the D register, bit Y1 of the Y register, and commands from the CPU. During output operations to external peripherals, the contents of the D and Y registers are decoded in the addressed peripheral controller. During an output to internal functions, the contents of the Y and D registers are decoded on the I/O-TTY controller board. During all input (read) operations, the decoding of the Y and D registers and CPU commands are done in the peripheral controllers and the I/O-TTY board. Read operations are used to send data or status to the CPU by way of the read selection circuit on the I/O-TTY controller (refer to figure 2-4). The information sent to the CPU on a read operation can be data or status from an external peripheral device, status from the RTC, or data or status from the TTY/CDT. The determination of which information gets sent to the CPU comes from decoding CPU command signals and bits of the Y register. When the address specifies an external peripheral, then the data or status enters the I/O-TTY controller on signal lines RD01/ through RD16/. When the TTY is addressed, then the input to the read select circuits is TTY data or status, and when the RTC is addressed, then RTC status is sent to the CPU. The outputs of the read select circuit feed the tri-state bus (BUS00 through BUS16, which carries the information to the CPU from the I/O-TTY controller.

- 1. The read select circuit consists of six multiplexers and their associated gates. They are on the I/O-TTY controller board and are multiplexers E9, on sheet 11, F6, G5, C7, and A7 on sheet 15, and E8, on sheet 16.

- 2. a. The signal ENABLEIO enters the I/O-TTY board on sheet 15, where it goes through the two E10 inverters and becomes the enable input to multiplexers F6 and G5.

- b. The signal MIR12 enters the I/O-TTY board on sheet 15, where it goes through gate L6. Together, the signals ENABLE10, from gate E10, and MIR12, from gate L6, go through AND gate B2 and generate the signal ENABLE10.

- c. The signal ENABLEIO, the output of gate B2, is the enable input to multiplexers C7 and A7, on sheet 15, E8, on sheet 16, and E9, on sheet 11.

- 3. The select inputs to the read select multiplexers are controlled by bits Y1, Y5 through Y16 of the Y register, and the signal MIR12.

- a. When an external peripheral is addressed, the select inputs to the multiplexers are zero. This selects the signals RD01/ through RD16/ to be applied to the read multiplexers. The signals RD01/ through RD16/ are the signals that carry the external information to the read multiplexers.

- b. On sheet 16, the signals RD13/ through RD16/ go through gates D8 before going to MUX E8. On sheet 11, the signals RD09/ through RD12/ go through gates D9 before going to MUX E9. On sheet 15, the signals RD01/ through RD08/ go through gates C8, B7, B8, and A8 before going to multiplexers C7, A7, F6 and G5.

- c. When an external peripheral is selected, the status from the peripherals is applied to multiplexers F6 and G5, on sheet 15, via input pins 3 and 13. The status inputs enter the I/O-TTY board and go into MUX G6 on sheet 15 before going to the read selector multiplexers F6 and G5.

- 4. When the RTC is addressed, MUX E8, on sheet 16, is used to apply the RTC status to the tri-state bus.

- 5. When the TTY/CDT has been addressed, the TTY-CDT status is applied to multiplexers E9, pins 3, 6, 10 and 13, on sheet 11, and F6, G5, A7, and C7, pins 5 and 11, on sheet 15; or the TTY/CDT data is applied to multiplexers F6, G5, A7, and C7, pins 6 and 10, on sheet 15. The TTY/CDT data-signals RR1 through RR8-go through gates B7, C8, and A8 before reaching the multiplexers.

The tables in figure 2-10 show the selection of read data to be applied to the read select multiplexers.

Figure 2-11 shows a block diagram of the read select circuits.

Read select MUX E9

| Selector | Output                     |

|----------|----------------------------|

| 0        | External data<br>RD09-RD12 |

| 1        | TTY status                 |

| Selector | Output                     |

|----------|----------------------------|

| 0        | External data<br>RD13-RD16 |

| 1        | RTC status                 |

#### Read select multiplexers F6, G5, A7, C7

| Selector |    |                            |

|----------|----|----------------------------|

| SO       | S1 | Output                     |

| 0        | 0  | External data RD03-RD08    |

| 0        | 1  | TTY/CDT status             |

| 1        | 0  | TTY/CDT data RR01-RR08     |

| 1        | 1  | External control responses |

Figure 2-10. Selection of Read Data

Figure 2-11. Block Diagram of Read Select Circuits

Block 3

**TTY/CDT Controller**

## **CDT Functional Description**

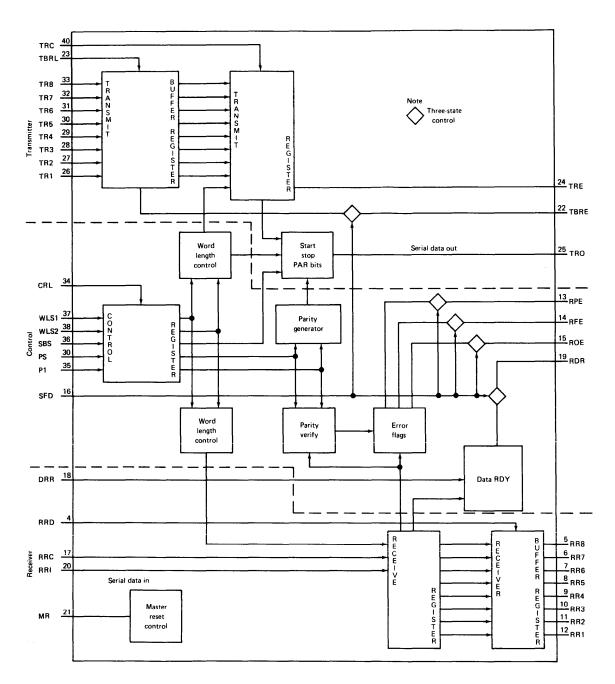

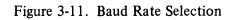

This text describes the functional parts of the TTY/CDT controller. Included are signal level conversion, serial/parallel conversion, mode selection, and control and timing. A block diagram of these functions is shown in figure 3-1.

#### **Signal Level Conversion**

The I/O-TTY controller board contains the TTY/CDT controller. This controller provides a communications link between the CPU and the teletypewriter (TTY), console display terminal (CD or CDT), or the breakpoint controller.

Because the TTY, CDT, and breakpoint controller each have different interface signals, the I/O-TTY controller must provide conversion to the different signals.

- Information to or from the TTY is in the form of a 20-milliamp current loop. The TTY/CDT controller uses transistor-to-transistor (TTL) logic levels of 0 to 5 volts. Therefore, the controller contains a 20 milliamp-to-TTL converter and a TTL-to-20 milliamp converter.

- Information entering or leaving the CDT uses the RS232-C logic levels (+3 to +12 equals high, and -3 to -12 equals low). The TTY/CDT controller contains converters which convert between RS232 format ant TTL logic levels.

- Information to or from the breakpoint controller is already in the TTL format, so no conversions are required.

#### Serial/Parallel Conversion

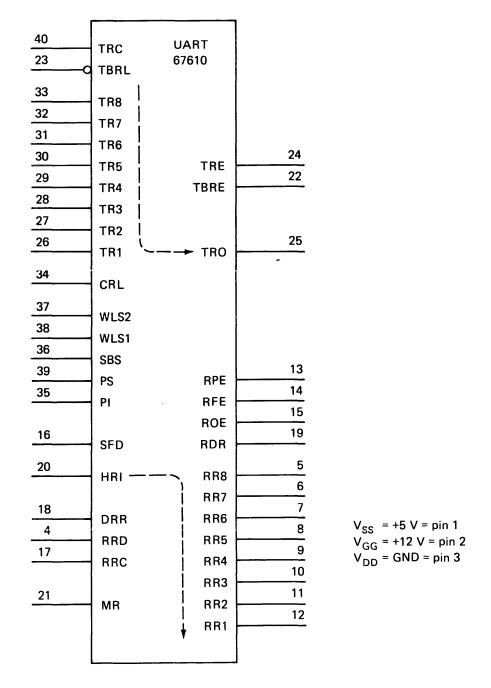

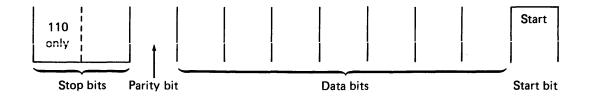

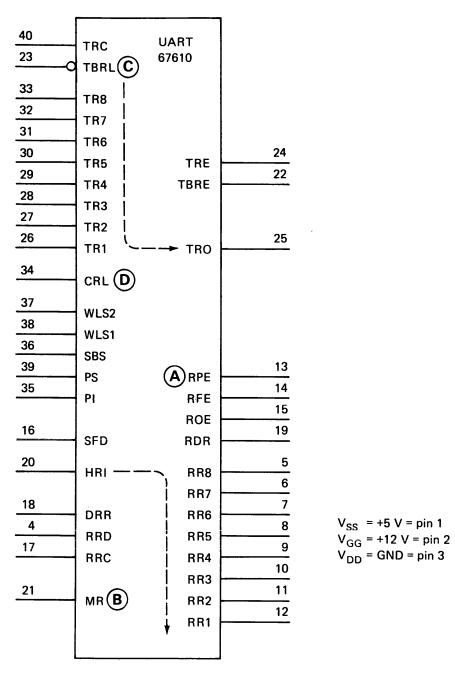

Because of differences in data transfers between the CPU and the TTY/CDT, a serialto-parallel and a parallel-to-serial converter is required on the TTY/CDT controller board. The TTY and the CDT use the ASCII code.

Data transfers between the TTY/CDT and the controller are in serial format. The data word may be seven or eight bits (with parity). The format includes one start bit, seven or eight data bits and one or two stop bits (two when the baud rate is 110). Data transfers between the CPU and the controller, on the other hand, are in a seven- or eight-bit parallel format. It is the job of the unversal asynchronous receiver/transmitter (UART), therefore, to convert the data from serial to parallel format and from parallel to serial format.

### **Mode Selection**

The TTY/CDT controller also provides the character echo response and circuits that allow the TTY/CDT to be shared by the TTY/CDT controller and the breakpoint controller. The TTY/CDT controller uses the TTY/CDT when the program mode is selected and the breakpoint controller uses the TTY/CDT when the panel mode is selected. This sharing is accomplished through special characters-ESC and BEL-used as commands and not as legal characters.

### **Control and Timing**