# **CONTROL DATA® 1700** COMPUTER SYSTEM

1704-A/B, 1705-A, 1708-A (Including Standard Options 10040-10043), AA101-A/B, AA1A1-A, AA1A3-A

DIAGRAMS & CIRCUIT DESCRIPTION CARD PLACEMENT

CUSTOMER ENGINEERING MANUAL

|            | RECORD of REVISIONS                                                                                                                                                                                  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REVISION   | NOTES                                                                                                                                                                                                |

| 01         | This edition obsoletes all previous editions.                                                                                                                                                        |

| (10-22-65) |                                                                                                                                                                                                      |

| 02         | This revision includes prerelease revisions through No. 5. All pages in Part 1 and page 117 in                                                                                                       |

| (1-21-66)  | Part 2 were changed.                                                                                                                                                                                 |

| A.         | Publications Change Order 14476 (manual released). Complete revision to circuit description                                                                                                          |

| (8-19-66)  | command timing charts deleted. This manual is correct through the following Product                                                                                                                  |

|            | Designation levels: 1703-A02, 1704-A12, 1705-A02, 1708-A01, 1709-A01, Standard Options                                                                                                               |

|            | 10040-A01, 10041-A01, 10042-A01, and 10043-A01. This edition obsoletes all previous editions.                                                                                                        |

| В          | Change Order 14535, no Product Designation change. Page 143 revised.                                                                                                                                 |

| (12-23-66) |                                                                                                                                                                                                      |

| С          | Field Change Order 14750, new Product Designation 1704-A13. Page 145 revised.                                                                                                                        |

| (12-23-66) |                                                                                                                                                                                                      |

| D          | Field Change Order 14392, new Product Designation 1704-A14. Pages 15, 17, and 19 revised.                                                                                                            |

| (12-23-66) |                                                                                                                                                                                                      |

| E          | Publications Change Order 15272, no Product Designation change. Pages 7, 9, 11, 17, 23, 27,                                                                                                          |

| (12-23-66) | 29, 31, 35, 39, 47, 49, 51, 69, 73, 75, 77, 81, 83, 85, 87, 89, 91, 93, 95, 97, 99, 101, 102,                                                                                                        |

|            | 103, 105, 107 and 135 revised.                                                                                                                                                                       |

|            | Field Change Order 14912, (MDR 15) new Product Designation 1704-A15. No change to this                                                                                                               |

|            | manual.                                                                                                                                                                                              |

|            | Field Change Order 15192, new Product Designation 1704-A16, (MDR 16) no change to this manual.                                                                                                       |

| F          | Field Change Order 15688, new Product Designation 1704-A17, (MDR 17). Pages 18, 19, 101,                                                                                                             |

| (3-16-67)  | 141 and 155 revised.                                                                                                                                                                                 |

| G          | Change Order 15843, no Product Designation change. Page 7 revised.                                                                                                                                   |

| (3-16-67)  |                                                                                                                                                                                                      |

| Н          | Publications Change Order 16028, no Product Designation change. Pages 75, 78.4, 80, 81, 108,                                                                                                         |

| (3-16-67)  | 131, and 133 revised.                                                                                                                                                                                |

| (7-28-67)  | Field Change Order 16043, new Product Designation 1704-A18 (MDR 18). No change to this                                                                                                               |

|            | manual.                                                                                                                                                                                              |

| J          | Change Order 16088, no Product Designation change. Page 149 revised.                                                                                                                                 |

| (7-28-67)  |                                                                                                                                                                                                      |

| К          | Field Change Order 16267, new Product Designation 1704-A19 (MDR 19). Page 153 revised.                                                                                                               |

| (7-28-67)  | Field Change Order 16344, new Product Designation 1704-A20 (MDR 20). No change to this manual                                                                                                        |

| L          | Field Change Order 16482, new Product Designation 1704-A21 (MDR 21). Pages 103 and 105                                                                                                               |

| (7-28-67)  | Field Change Order 1642, new Product Designation 1704-A21 (MDR 21). Pages 103 and 103         revised.         Field Change Order 16531, new Product Designation 1704-A22 (MDR 22). Pages 75 and 153 |

| М          | Field Change Order 16531, new Product Designation 1704-A22 (MDR 22). Pages 75 and 153                                                                                                                |

| (7-28-67)  | revised.                                                                                                                                                                                             |

| (7-28-67)  | Field Change Order 16615, new Product Designation 1704-A23. No change to this manual.                                                                                                                |

| N          | Field Change Order 16529, no Product Designation Change. Page 149 revised.                                                                                                                           |

| (7-28-67)  | Field Change Order 16615, new Product Designation 1704-A23. No change to this manual.<br>Field Change Order 16529, no Product Designation Change. Page 149 revised.                                  |

Address comments concerning this manual to:

1

l

Control Data Corporation Technical Publications Department 4201 North Lexington Avenue St. Paul, Minnesota 55112

or use Comment Sheet in the back of this manual.

Pub No. 60152700  $\odot$  1965, 1966, 1967, 1968, 1969, 1970, 1971, 1972 by Control Data Corporation

Printed in United States of America

# RECORD of REVISIONS (CONT'D)

| REVISION  | NOTES                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------|

| Р         | Publications Change Order 17060, no Product Designation change. Pages 3, 7, 15, 17, 19, 21, 23, 29,           |

| (7-28-67) | 47, 49, 51, 55, 56. 0, 80, 81, 119, 153 and 155 revised.                                                      |

| R         | Field Change Order 16817 (MDR 23, new Product Desitnation 1704-A24. Pages vi, 3, 13, 19, 20. 1,               |

| (9-1-67)  | 20. 2, 23, 39, 41, 69, 99, 105, 107, 127, 129, 131, 133, 135, 137, 139, 141, 143, 145 and 147 revised.        |

| S         | Field Change Order 17320 (MDR 24), new Product Designation 1704-A25. Pages 31, 35, 43, 53,                    |

| (10-6-67) | 57, 71, 77, 107 and 145 revised.                                                                              |

| (3-7-68)  | Field Change Order 17750, new Product Designation 1704-A26. No change to this manual.                         |

| Т         | Field Change Order 18378, new Product Designation 1704-A27. Pages 81, 103, 145 and 147                        |

| (3-7-68)  | revised.                                                                                                      |

| U         | Publications Change Order 19012, no Product Designation change. Pages 3, 67, 133 and 141                      |

| (3-8-68)  | revised.                                                                                                      |

| v         | Field Change Order 19097, new Product Designation 1704-A28. Page 135 revised.                                 |

| (8-6-68)  |                                                                                                               |

| W         | Engineering/Publications Change Order 19375, no Product Designation change. Pages 81, 103,                    |

| (8-6-68)  | 105, 145 and 147 revised.                                                                                     |

| Y         | Engineering Change Order 20253. Pages 19, 21, 35, 43, 51, 59, 61, 63, 65, 73, 81, 121 and 123                 |

| (8-6-68)  | revised.                                                                                                      |

| (12-4-68) | Manual revised; includes Field Change Order 19317, equipment level 1704-A29. No change to                     |

|           | this manual.                                                                                                  |

| Z         | Manual revised; includes Field Change Order 20893, equipment level 1704-A30.                                  |

| (12-4-68) | Pages 135 and 139 revised. Added pages 145, 147 and 149.                                                      |

| AA        | Manual revised; includes Engineering Change Order 21046. Publication Change only. Cover and                   |

| (12-4-68) | Title Page revised. Pages vi, 4, 12, 17, 19, 22, 24, 31, 35, 39, 48, 57, 59, 61, 63, 65, 69, 75, 80, 99, 103, |

| <u> </u>  | 105, 117, 125, 127, 133, 151 and 153 revised. Page 106 was added. Added 1704-B information                    |

|           | at equipment level B01.                                                                                       |

| (4-10-69) | Field Change Order 20971, equipment level 1704-A30. No change to this manual.                                 |

| AB        | Manual revised; includes Engineering Change Order 21570, publication change only. Pages 139,                  |

| (4-10-69) | 141 and 149 revised. Added page 148.                                                                          |

| AC        | Manual revised, includes Field Change Order 21048, equipment level 1704-A01 through A31,                      |

| (5-8-70)  | 1704-B01 through B02. Pages 31 and 35 revised.                                                                |

| AD        | Manual revised, includes Engineering Change Order 22284. Page 141 revised.                                    |

| (5-8-70)  |                                                                                                               |

| AE        | Manual revised, includes Engineering Change Order 22477. Pages 135 and 145 revised.                           |

| (5-8-70)  |                                                                                                               |

| AF        | Field Change Order 22196. No change to this manual.                                                           |

| (5-8-70)  |                                                                                                               |

| AG        | Manual revised, includes Engineering Change Order 24078. Page 147 revised.                                    |

| (5-8-70)  |                                                                                                               |

| AH        | Manual revised, includes Engineering Change Order 24271. Pages 155 through 172 added.                         |

| (5-8-70)  |                                                                                                               |

| AJ        | Manual revised, includes Engineering Change Order 24238. Page 147 revised.                                    |

| (5-8-70)  |                                                                                                               |

| AK        | Manual revised, includes Engineering Change Order 25071. Page 153 revised.                                    |

| (5-8-70)  |                                                                                                               |

|           | Manual revised, includes Field Change Order 25377, equipment level 1704-A01/B01 through                       |

| (9-15-70) | A32/B03. Pages 11,57 and 69 changed.                                                                          |

| AM        | Manual revised, includes Engineering Change Order 26170, publication change only. Pages 7                     |

| (9-15-70) |                                                                                                               |

| (9-19-(0) | and 49 revised, pages A-1 through A-28 added.                                                                 |

|           | 1                                                                                                             |

Pub. No. 60152700

|                                         | RECORD of REVISIONS (CONT'D)                                                                    |  |  |  |  |  |  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| REVISION                                | NOTES                                                                                           |  |  |  |  |  |  |

| AN                                      | Engineering Change Order 26078; no change to this manual.                                       |  |  |  |  |  |  |

| (6-3-71)                                |                                                                                                 |  |  |  |  |  |  |

| AP                                      | Manual revised; includes Engineering Change Order 27989, publication change only. Pages 7, 11,  |  |  |  |  |  |  |

| (6-3-71)                                | 25, 26, 49, and Comment Sheet revised.                                                          |  |  |  |  |  |  |

| AR                                      | Manual revised; includes Field Change Order 28032. Pages 133, 135, and 145 are revised.         |  |  |  |  |  |  |

| (7-26-72)                               |                                                                                                 |  |  |  |  |  |  |

| AS                                      | Manual revised; includes Field Change Order 31812. Pages 137 and 147 are revised.               |  |  |  |  |  |  |

| (7-26-72)                               |                                                                                                 |  |  |  |  |  |  |

| AT                                      | Manual revised; includes Engineering Change Order 32216, publications change only. Pages iv, 3, |  |  |  |  |  |  |

| (7-26-72)                               | 7, 8.1, 9, 11, 13, 15, 16, 18, 21, 23, 27, 30, 31, 39, 40.1, 44.1, 44.2, 49, 57, 58.0, 59, 61,  |  |  |  |  |  |  |

|                                         | 63, 65, 69, 70, 73, 75, 78.4, 102, 104, 105, 107, 113, 135, 137, 145, 151, 153, 160, Cover, and |  |  |  |  |  |  |

|                                         | Title Page are revised. Correlation Sheet is added.                                             |  |  |  |  |  |  |

| AU                                      | Manual revised; includes Field Change Order 31772. Pages 29, 41, 59, 73, 75, 77, 81, 103,       |  |  |  |  |  |  |

| (9-28-72)                               | 105, 107, and 153 are revised.                                                                  |  |  |  |  |  |  |

| AV                                      | Manual revised; includes Field Change Order 32640. Pages 135 and 145 are revised. Pages iii,    |  |  |  |  |  |  |

| (12-5-72)                               | vi, 22, 31, 43, 44. 1, 44. 2, 48, 52, 72. 0, 72-1, 75 and 80 contain editorial corrections.     |  |  |  |  |  |  |

|                                         | Appendix B is added.                                                                            |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

| · • · · · · · · · · · · · · · · · · · · |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

| · · · · · · · · · · · · · · · · · · ·   |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

| 10.0.0.0.0.0.0.0.0.0.0.0.0.0.0.0.0.0.0. |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

| <b></b>                                 |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

| <u></u>                                 |                                                                                                 |  |  |  |  |  |  |

|                                         |                                                                                                 |  |  |  |  |  |  |

# MANUAL TO EQUIPMENT LEVEL CORRELATION SHEET

•

| SHEET         | _OF        |                  |           | EQUIPM  | ENTS    |                 |                 |

|---------------|------------|------------------|-----------|---------|---------|-----------------|-----------------|

| MANUAL<br>REV | FCO OR ECO | AA1A1 <b>-</b> A | AA1A3-A   | AA101-A | AA101-B | 1704 <b>-</b> A | 1704 <b>-</b> B |

| AR            | FCO28032   | A05              | A03       | A07     | B06     | A35             | B06             |

| AS            | FCO31812   | A06              | A04       | A08     | B07     | A36             | B07             |

| AT            | ECO32216   | A06              | A04       | A08     | B07     | A36             | B07             |

| AU            | FCO31772   | A07              | A04       | A09     | B08     | A37             | B08             |

| AV            | FCO32640   | A08              | A05       | A10     | B09     | A38             | B09             |

|               |            |                  |           |         |         | •               |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  | · · · · · |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  | · .       |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

|               |            |                  |           |         |         |                 |                 |

# MANUAL TO EQUIPMENT LEVEL CORRELATION SHEET (CONT.)

| SHEETOF       |            |        |        | EQUIPMI | ENTS |  |

|---------------|------------|--------|--------|---------|------|--|

| MANUAL<br>REV | FCO OR ECO | 1705-A | 1708-A |         |      |  |

| AR            | FCO28032   | A02    | A02    |         |      |  |

| AS            | FCO31812   | A02    | A02    |         |      |  |

| AT            | ECO32216   | A06    | A02    |         |      |  |

| AU            | FCO31772   | A06    | A02    |         |      |  |

| AV            | FCO32640   | A06    | A02    |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            | ł      |        | х.      |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

|               |            |        |        |         |      |  |

.

60152700

### PREFACE

The 1700 Customer Engineering Manual provides logic diagrams and circuit descriptions of the CONTROL DATA<sup>®</sup> 1700 Computer System. This manual contains information on all units contained in the main computer cabinet with the exception of the Basic Peripheral Equipment, which is in Pub. No. 60164200.

The circuit descriptions and diagrams are arranged to give a general continuity of logic flow. Thus, the Clock and Timing controls are given first, followed by the Register groupings, Adder/Shifter, etc. A special reference is made to the Command Timing sequences. These sequences give the detailed timing of each instruction. Thus, the Command Timing sequences logically interconnect various diagrams on a timed sequence basis. Refer to the 1700 Computer System Command Timing Charts, Pub. No. 60194500.

The logic diagram symbol description and the block diagram description precede the detailed circuit descriptions. The Logic Diagram Symbol section lists each of the standard logic symbols used on the diagrams and a brief description of their meaning and use.

## CONTENTS

| Part 1. Diagrams                                                        |    |

|-------------------------------------------------------------------------|----|

| Main Computer                                                           |    |

| Block Diagram                                                           | 1  |

| Clock - Normal Speed                                                    | 3  |

| Clock - Slow and Fast                                                   | 5  |

| Timing Chain                                                            | 7  |

| Sequence Controls                                                       | 9  |

| Cycle Control                                                           | 11 |

| Addressing Controls                                                     | 13 |

| Manual Controls (Sheet 1)<br>(Register Selection and Clear<br>Controls) | 15 |

| Manual Controls (Sheet 2)<br>(Switch and Indicator Drivers)             | 17 |

| Manual Controls (Sheet 3)<br>(Test Mode and Run/Step)                   | 19 |

| Manual Controls (Sheet 4)<br>(Typical Register Display)                 | 21 |

| F Register                                                              | 23 |

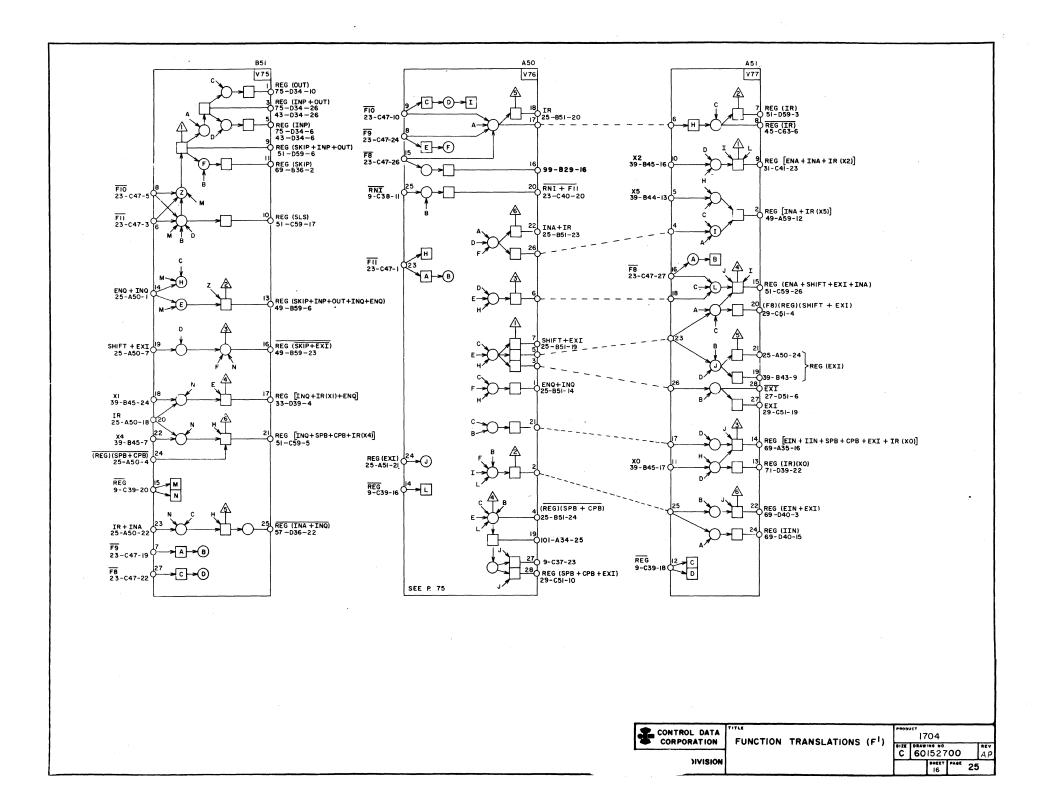

| Function Translations (Sheet 1)                                         | 25 |

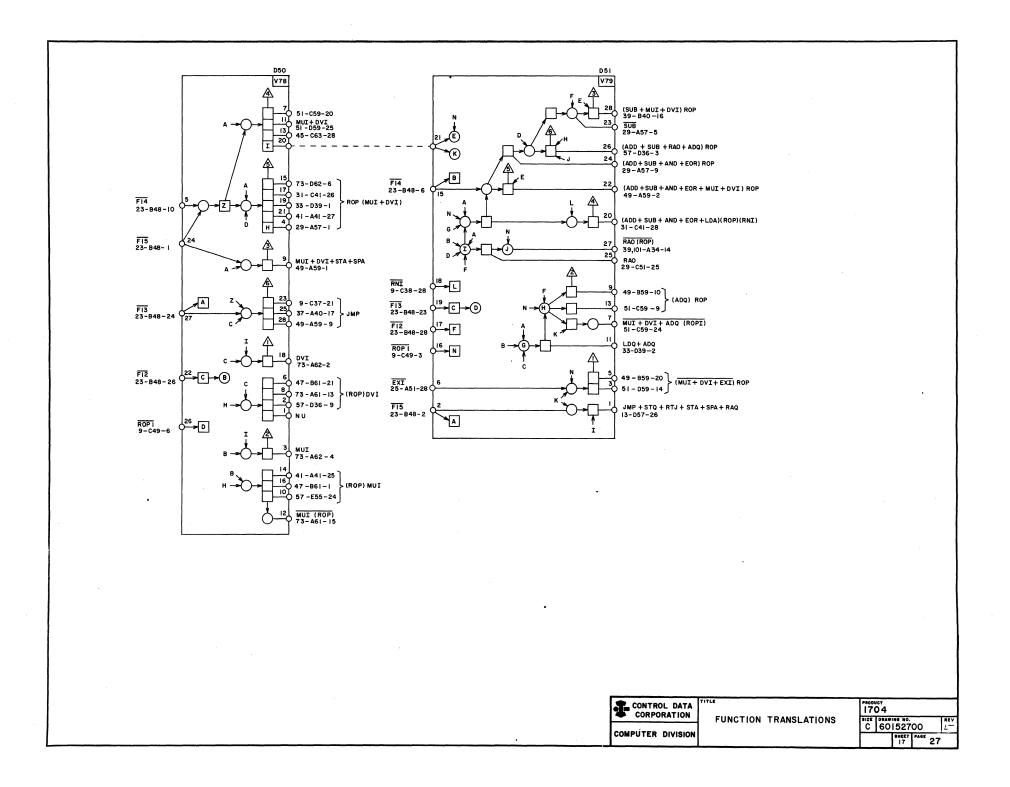

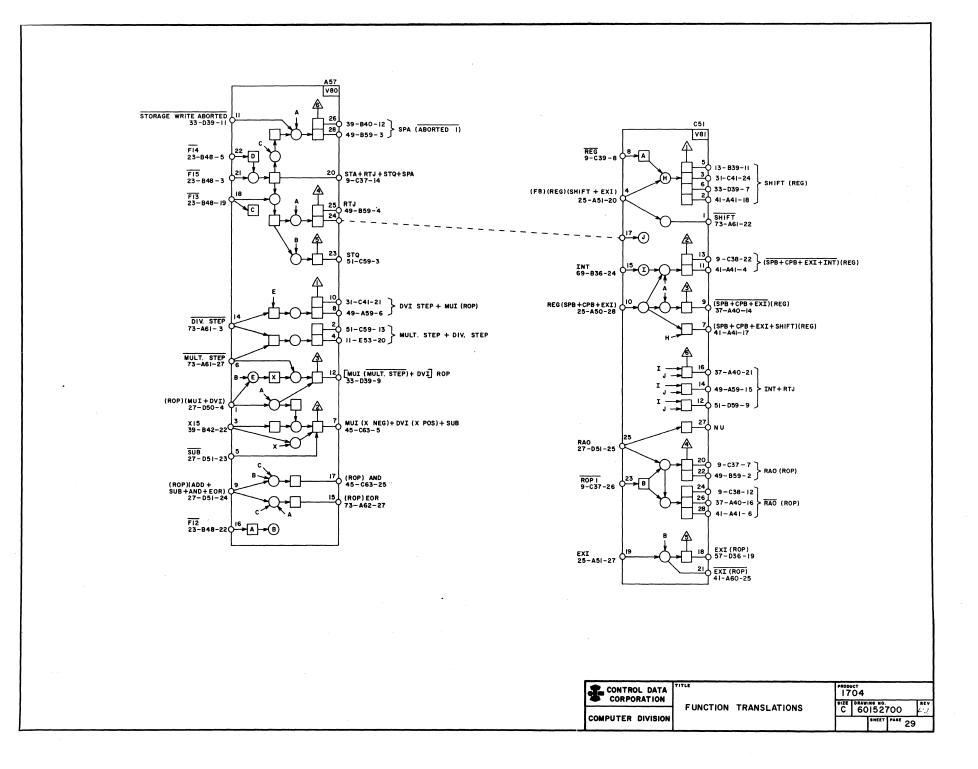

| Function Translations (Sheet 2)                                         | 27 |

| Function Translations (Sheet 3)                                         | 29 |

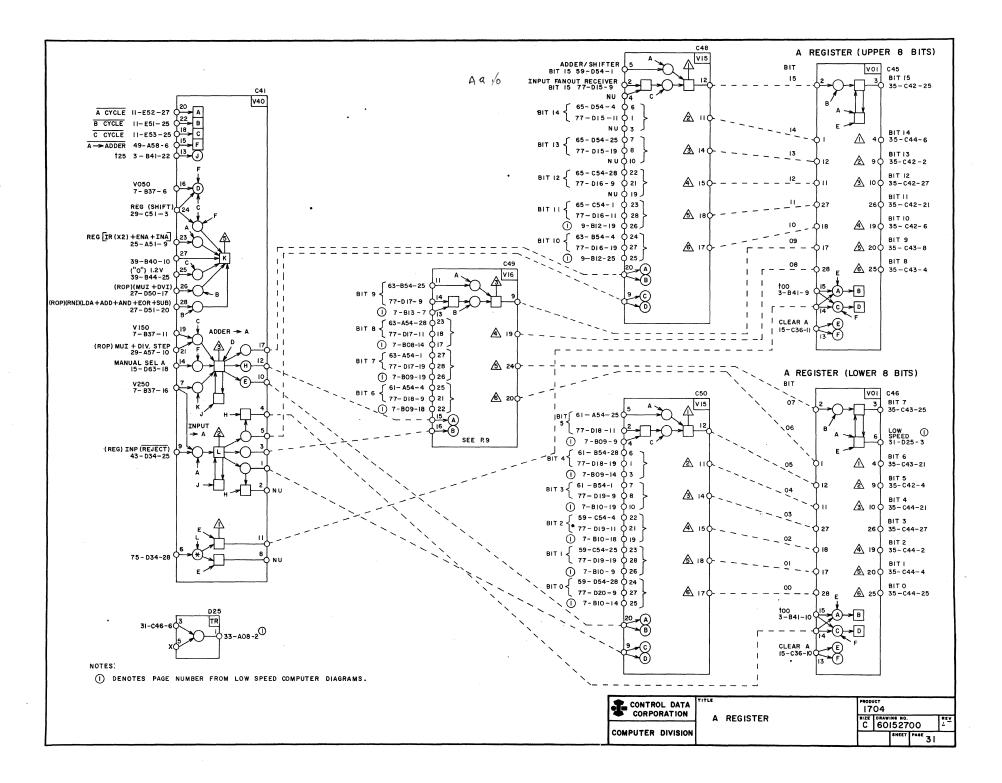

| A Register                                                              | 31 |

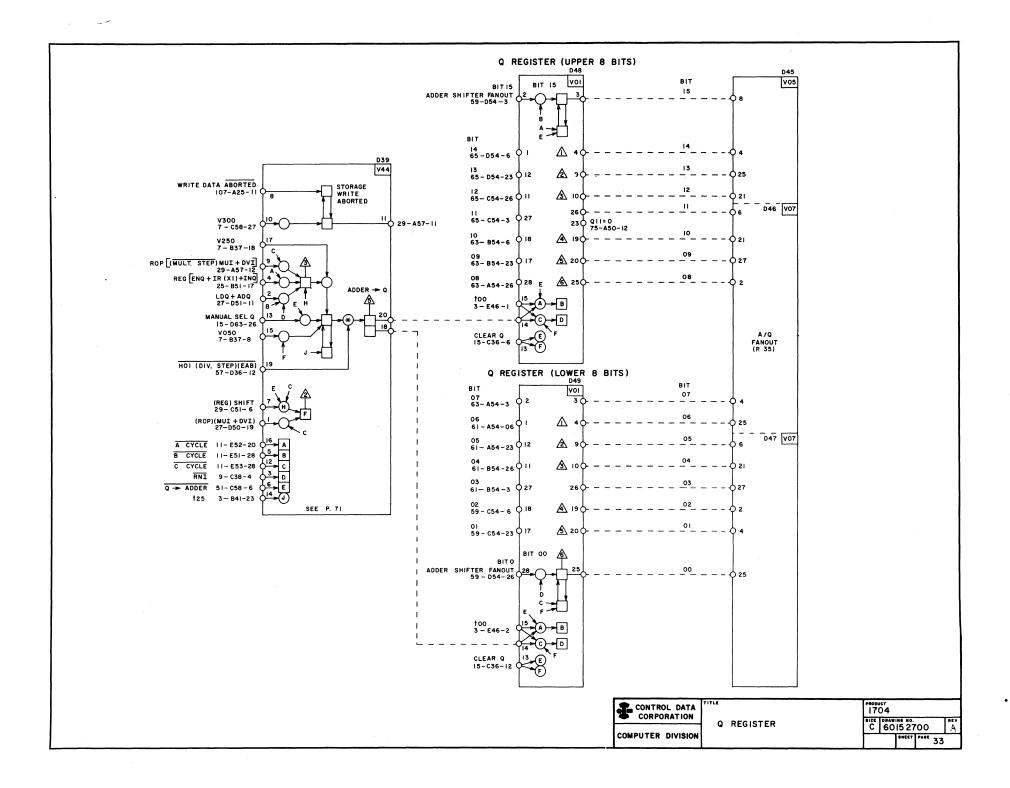

| Q Register                                                              | 33 |

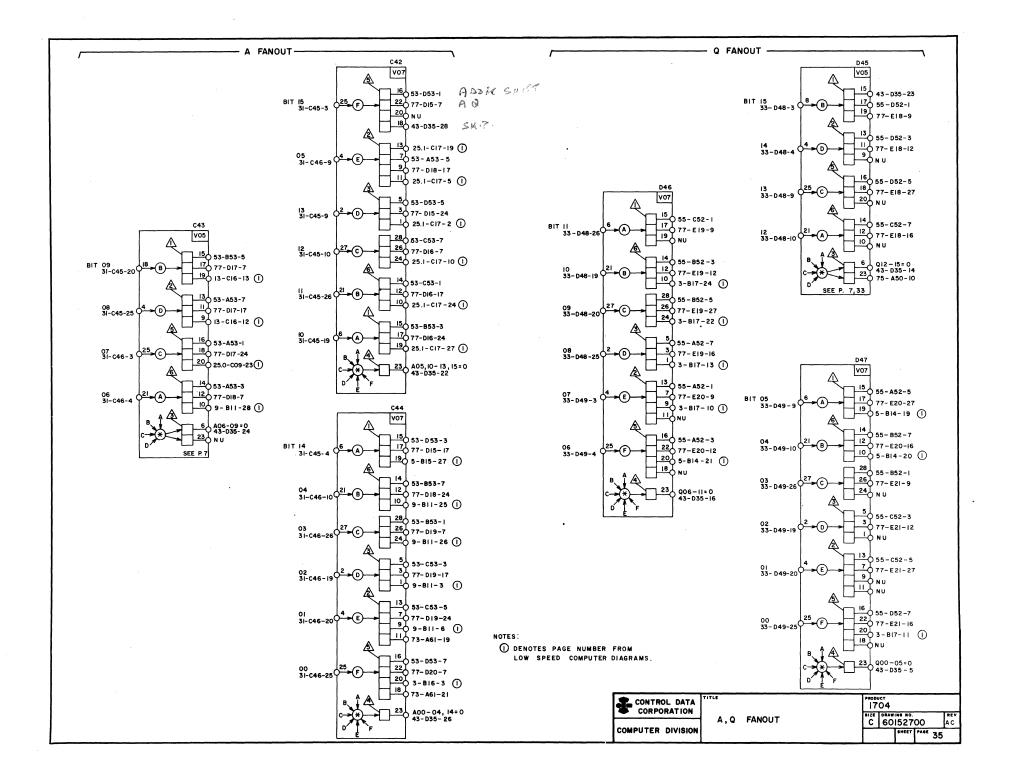

| A, Q Fan-Out                                                            | 35 |

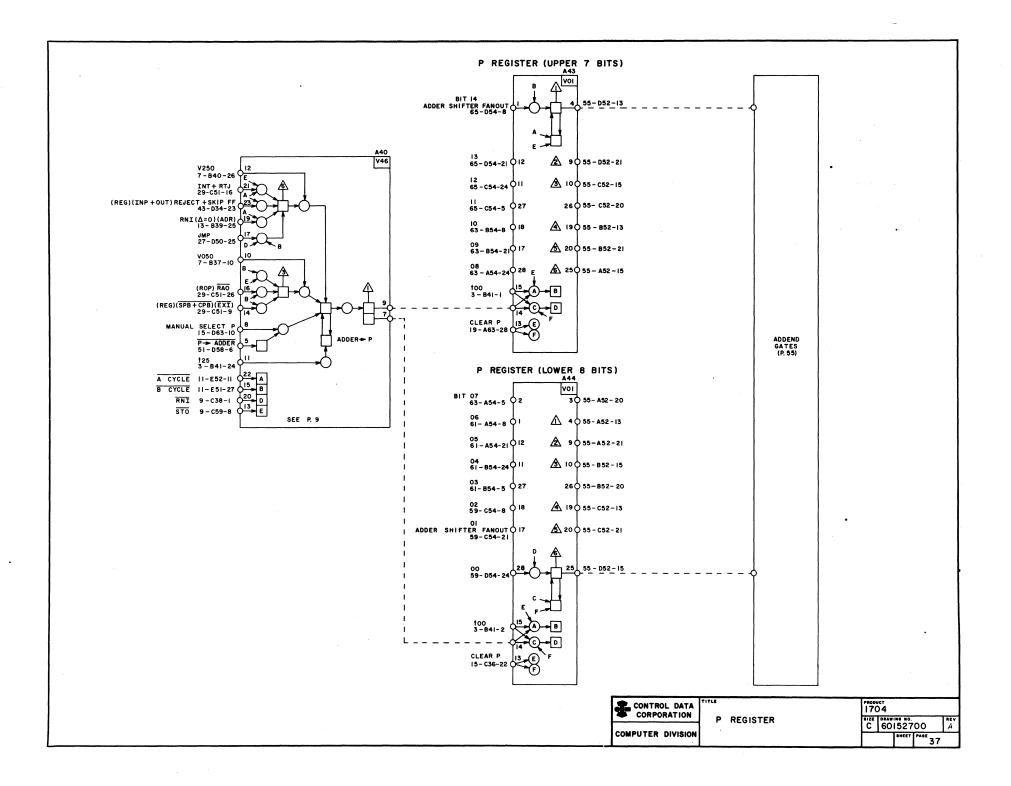

| P Register                                                              | 37 |

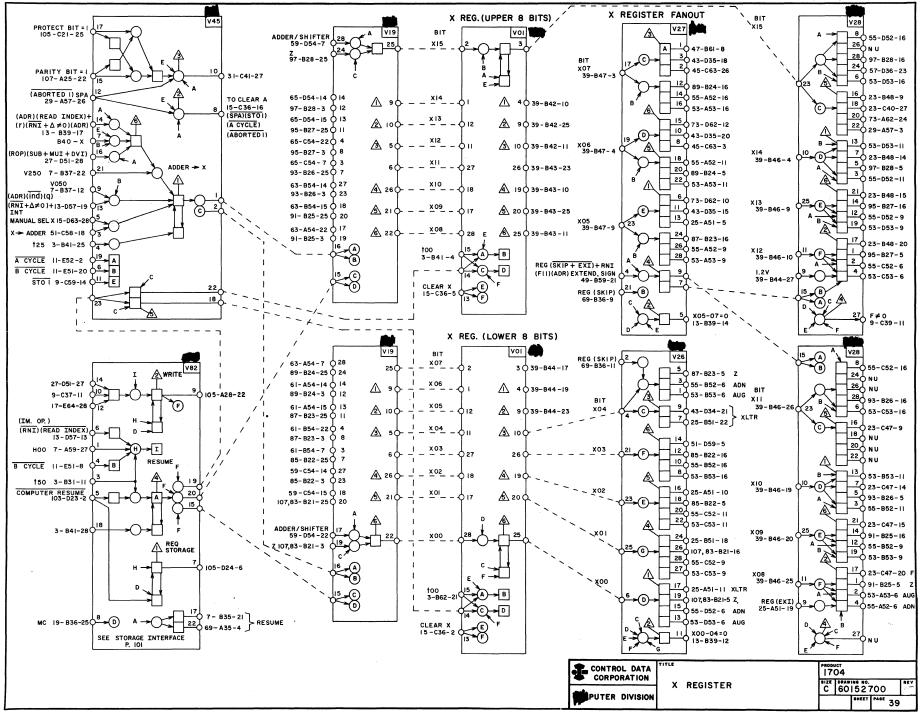

| X Register                                                              | 39 |

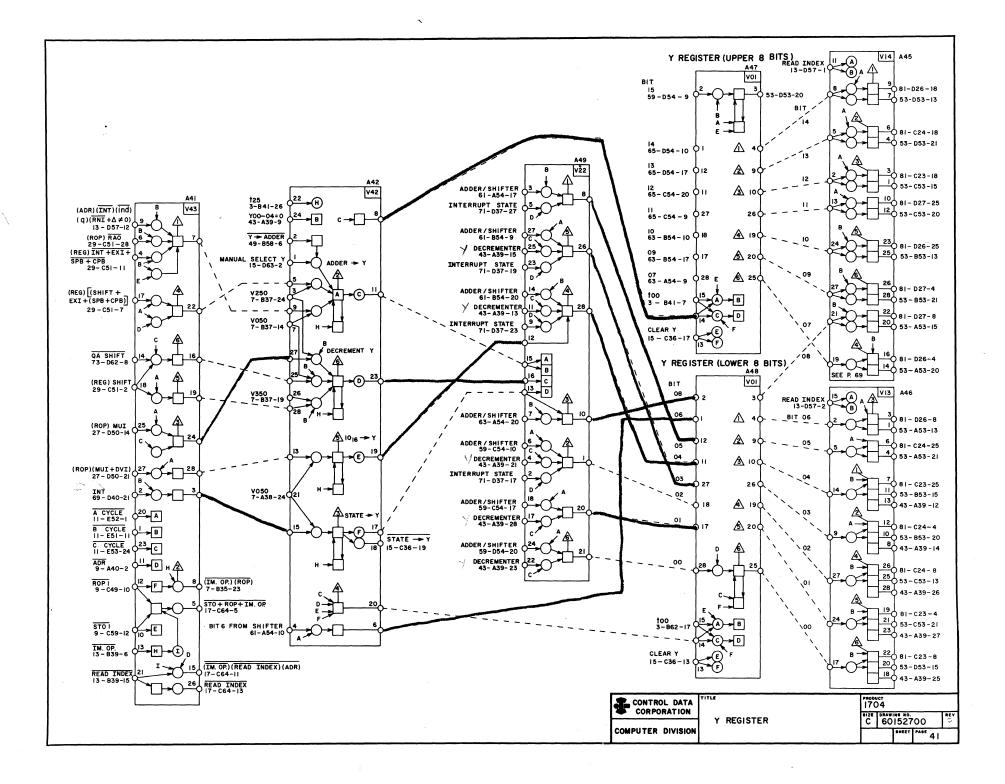

| Y Register                                                              | 41 |

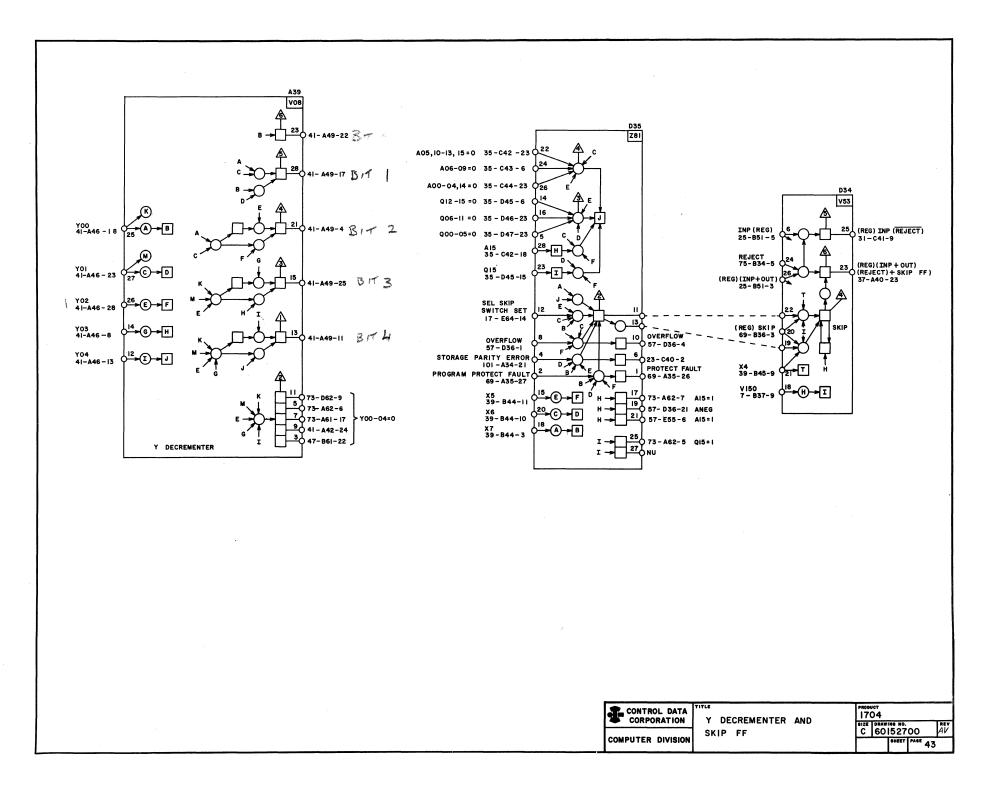

| Y Decrementer and Skip FF                                               | 43 |

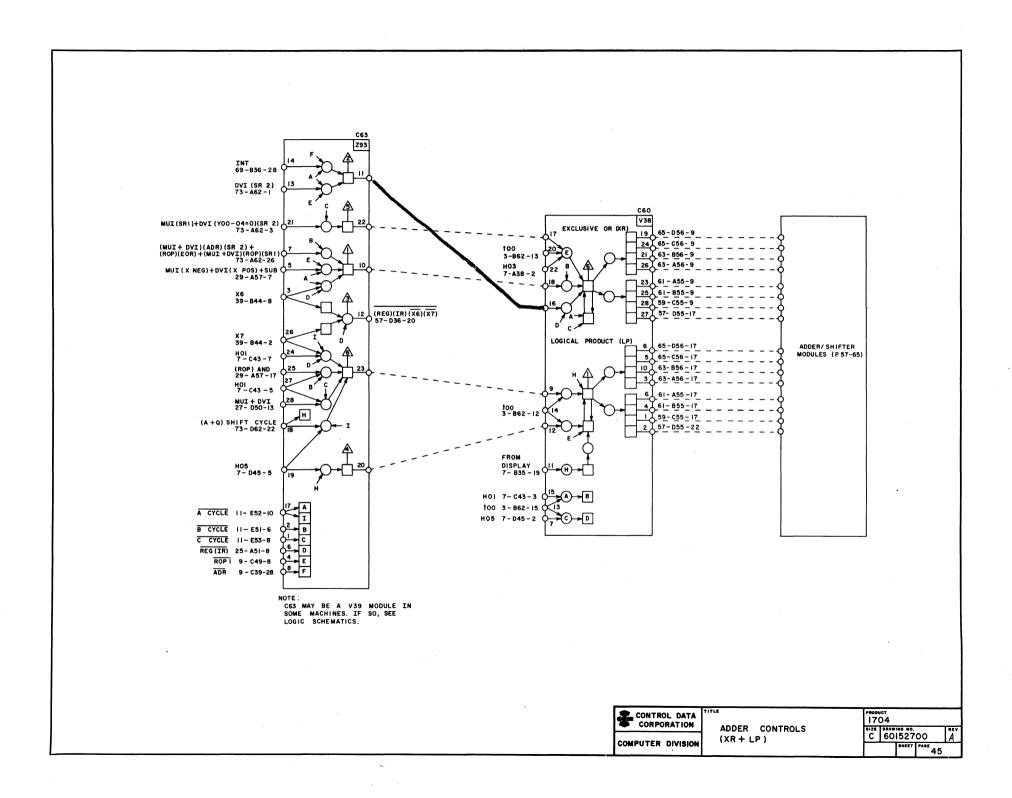

| Adder Controls (XR and LP)                                              | 45 |

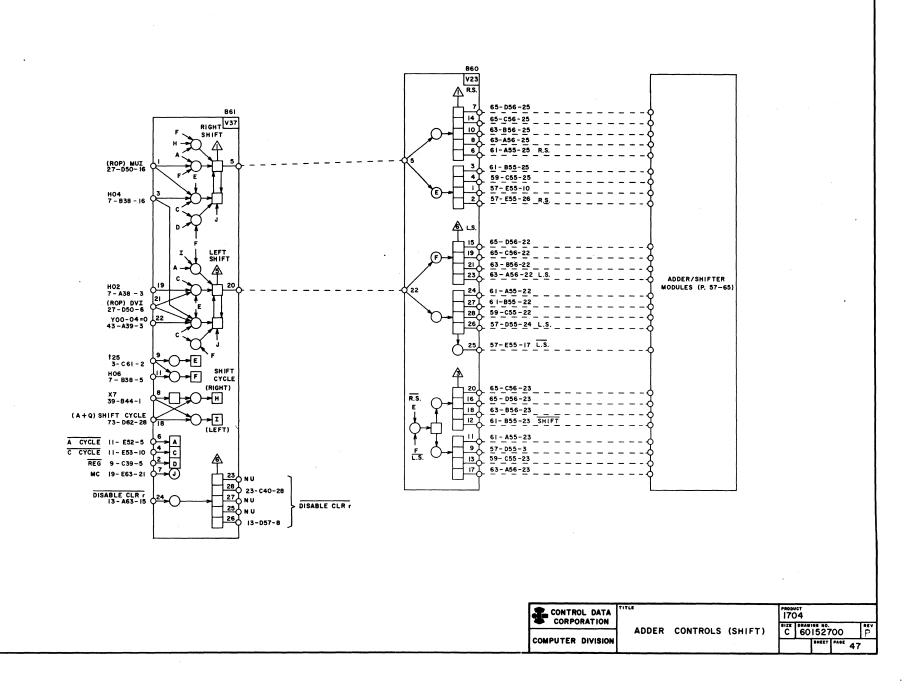

| Adder Controls (Shift)                                                  | 47 |

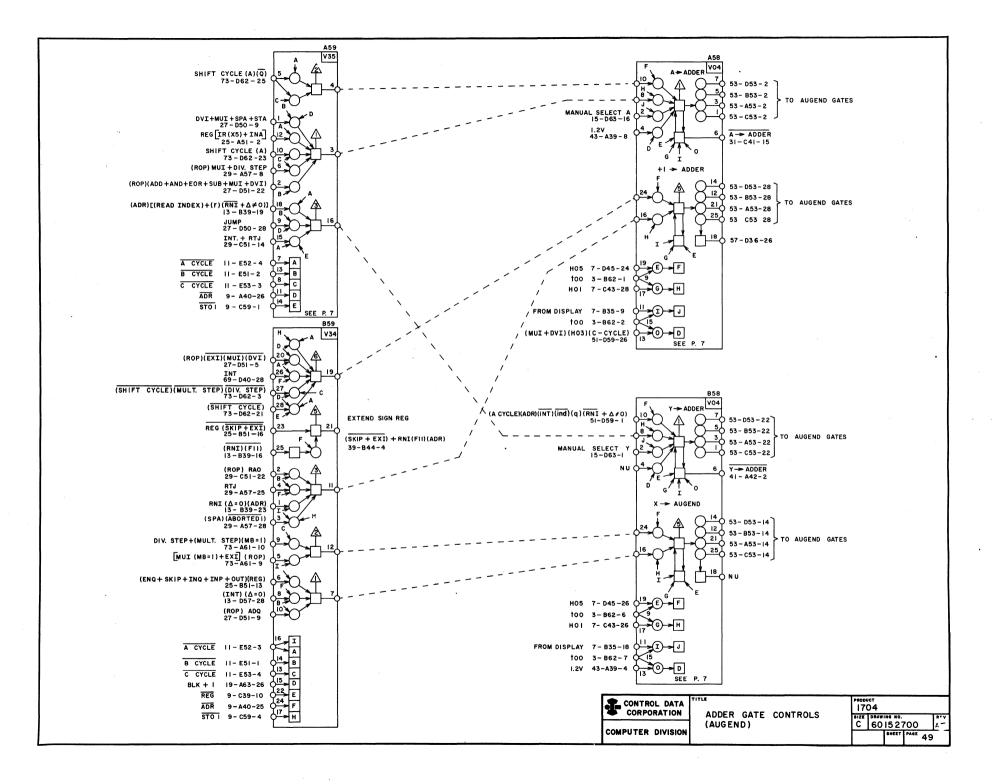

| Adder Gate Controls (Augend)                                            | 49 |

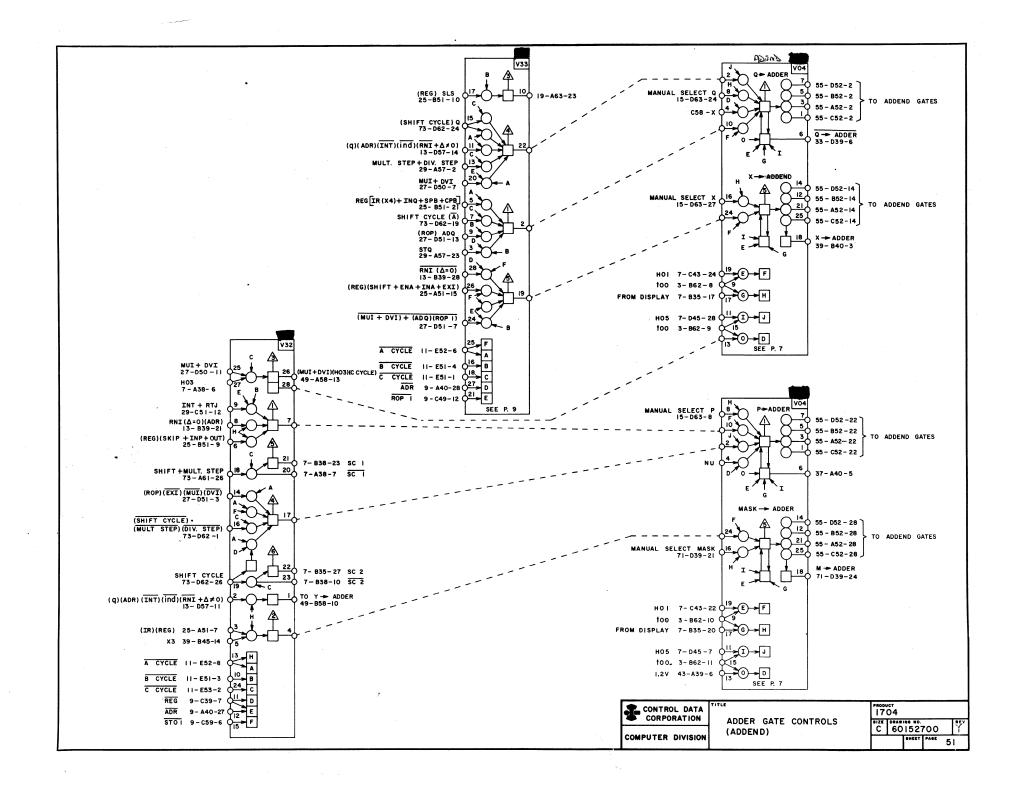

| Adder Gate Controls (Addend)                                            | 51 |

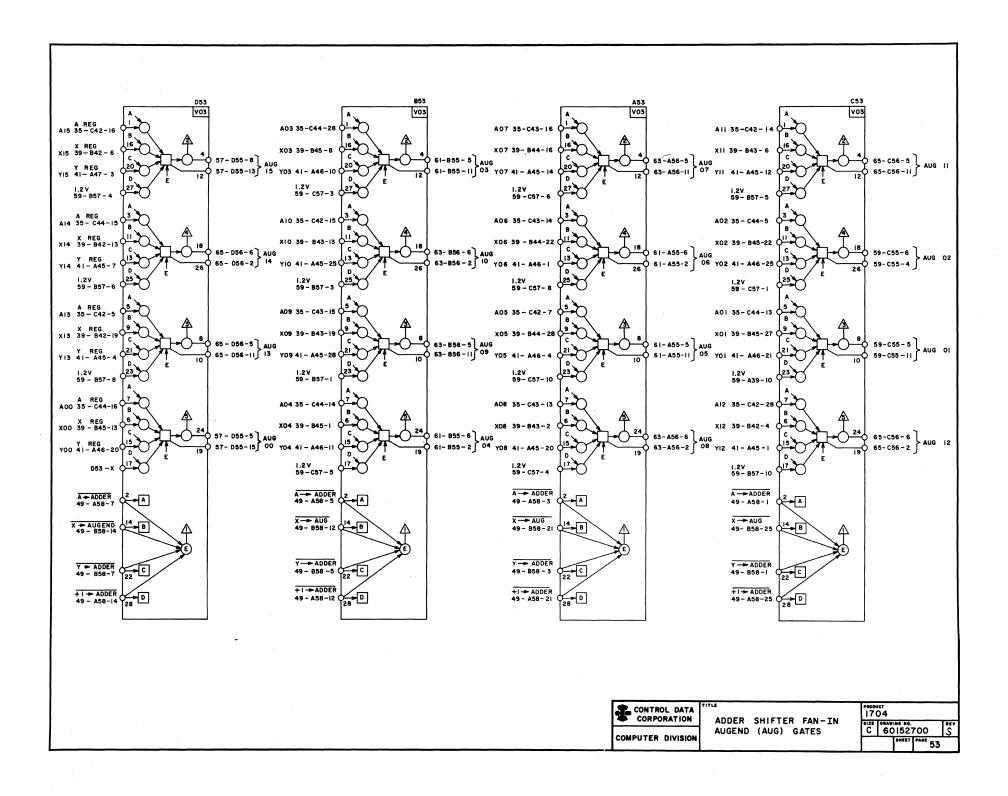

| Adder/Shifter Fan-In<br>Augend Gates                                    | 53 |

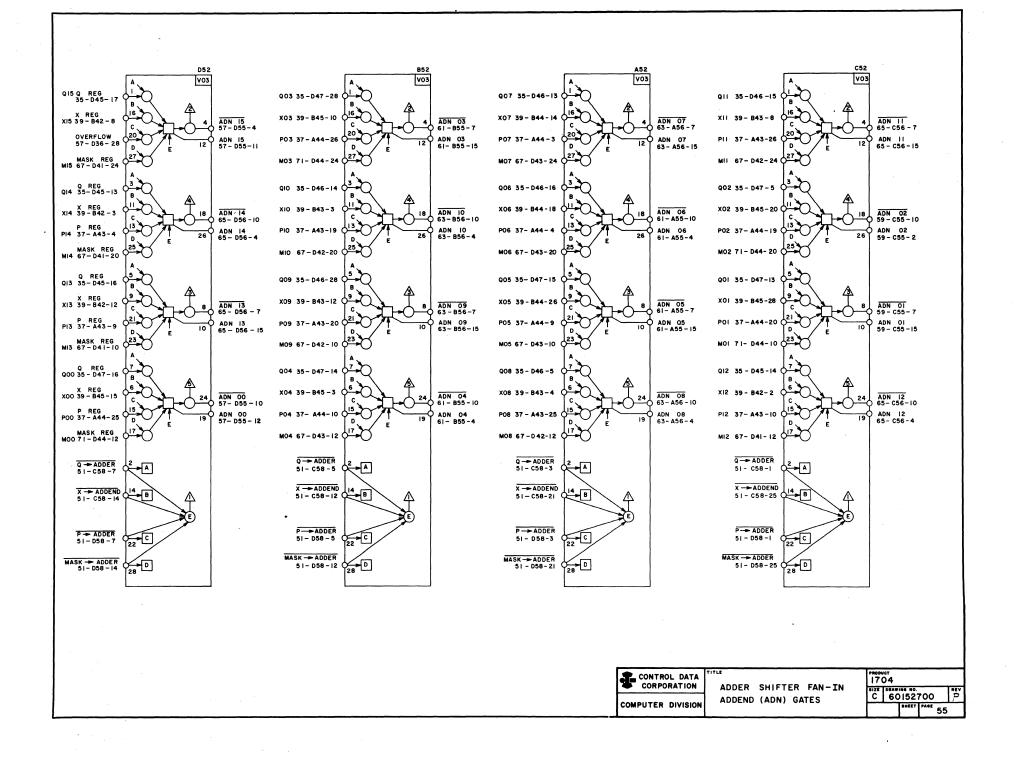

| Adder/Shifter Fan-In<br>Adder Gates                                     | 55 |

| NTS                                                      |    |

|----------------------------------------------------------|----|

| Group 0 of Adder 5                                       | 7  |

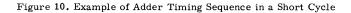

| Adder/Shifter Groups 0 and 1 5                           | 9  |

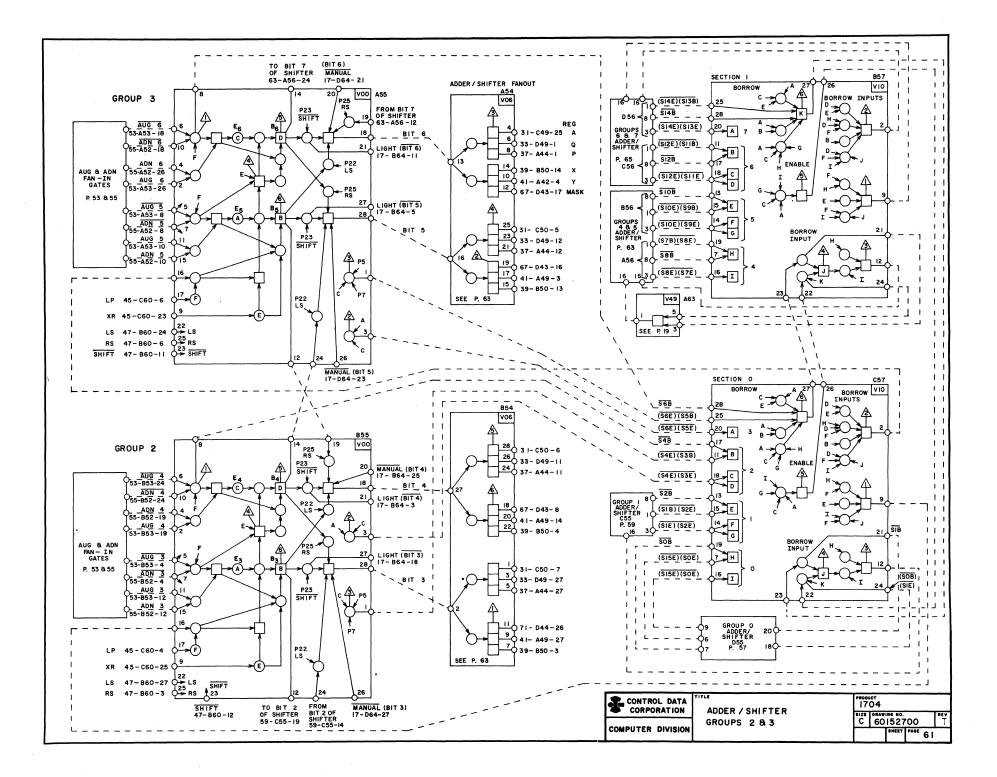

| Adder/Shifter Groups 2 and 3 6                           | 1  |

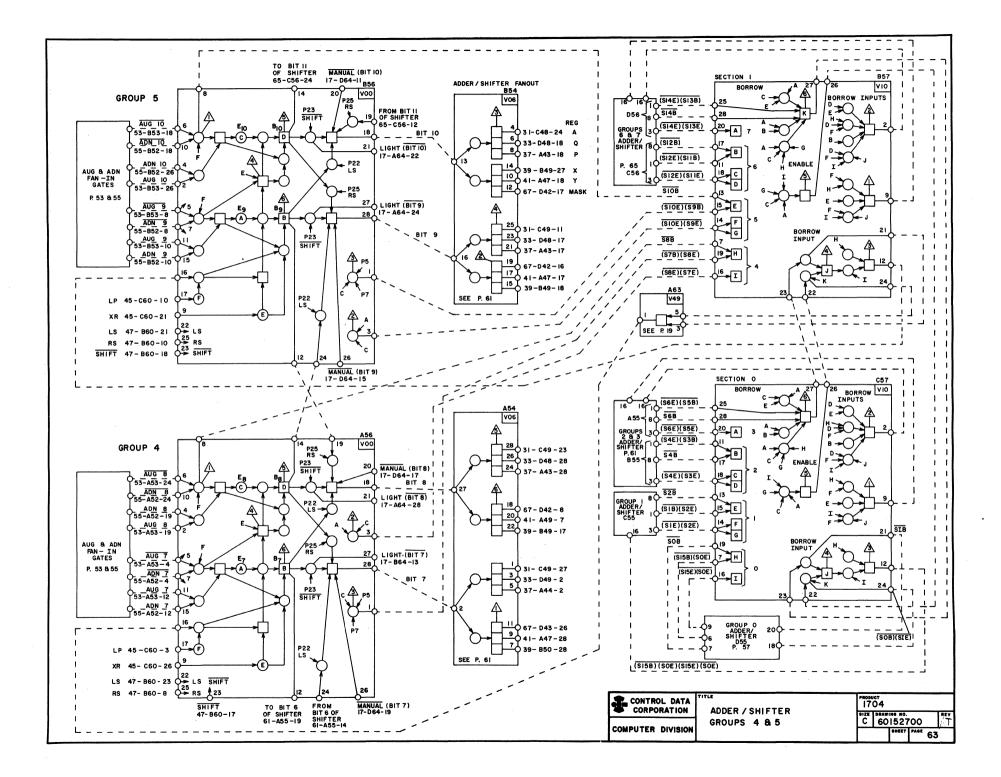

| Adder/Shifter Groups 4 and 5 6                           | 3  |

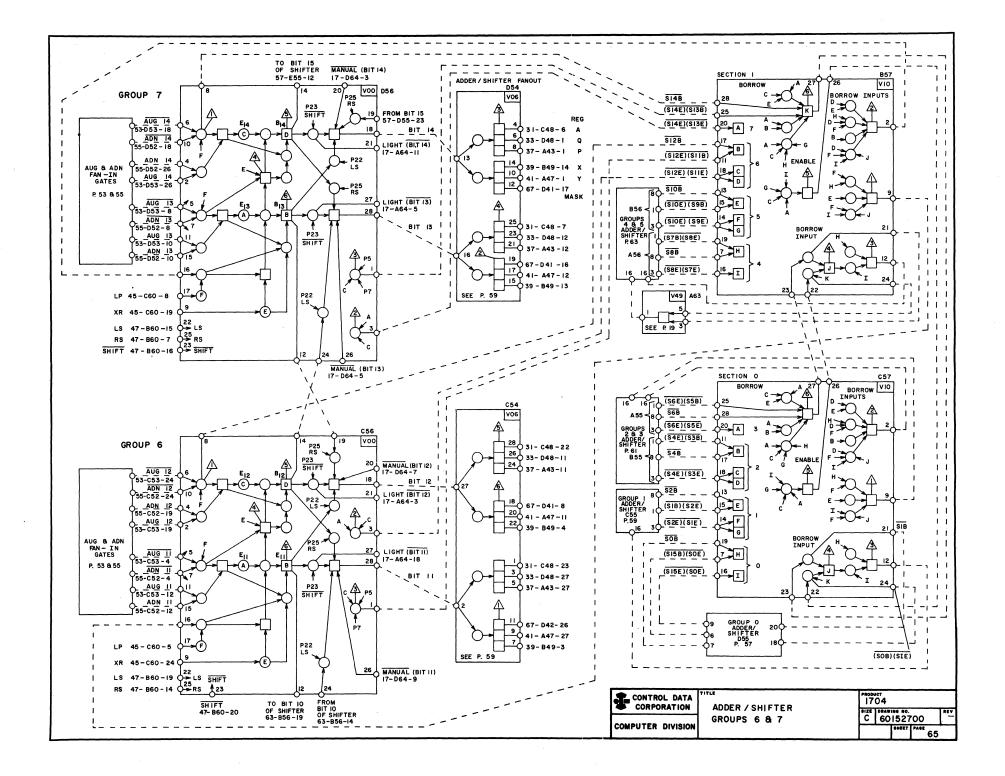

| Adder/Shifter Groups 6 and 7 6                           | 5  |

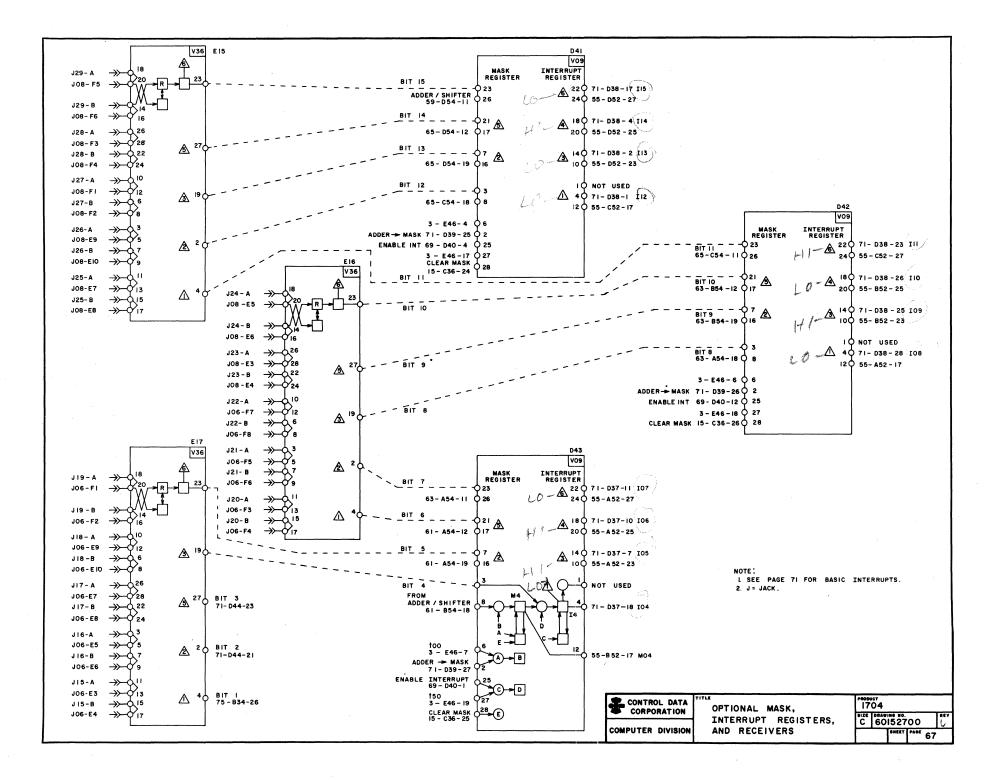

| Optional Mask and Interrupt<br>Registers and Receivers 6 | 7  |

| Program Protect and Interrupt 6                          | 9  |

| Mask Register and Interrupt<br>Priority 7                | 1  |

| Shift , MUI, and DVI Controls 7                          | 3  |

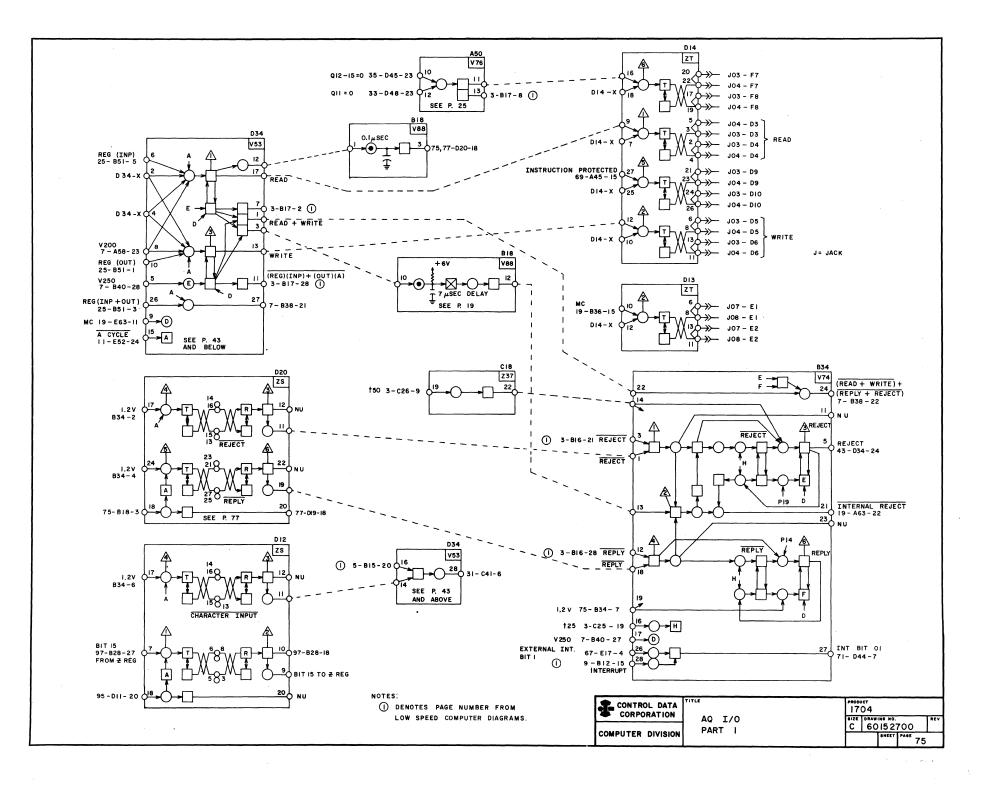

| AQ I/O (Part 1) 7                                        | 5  |

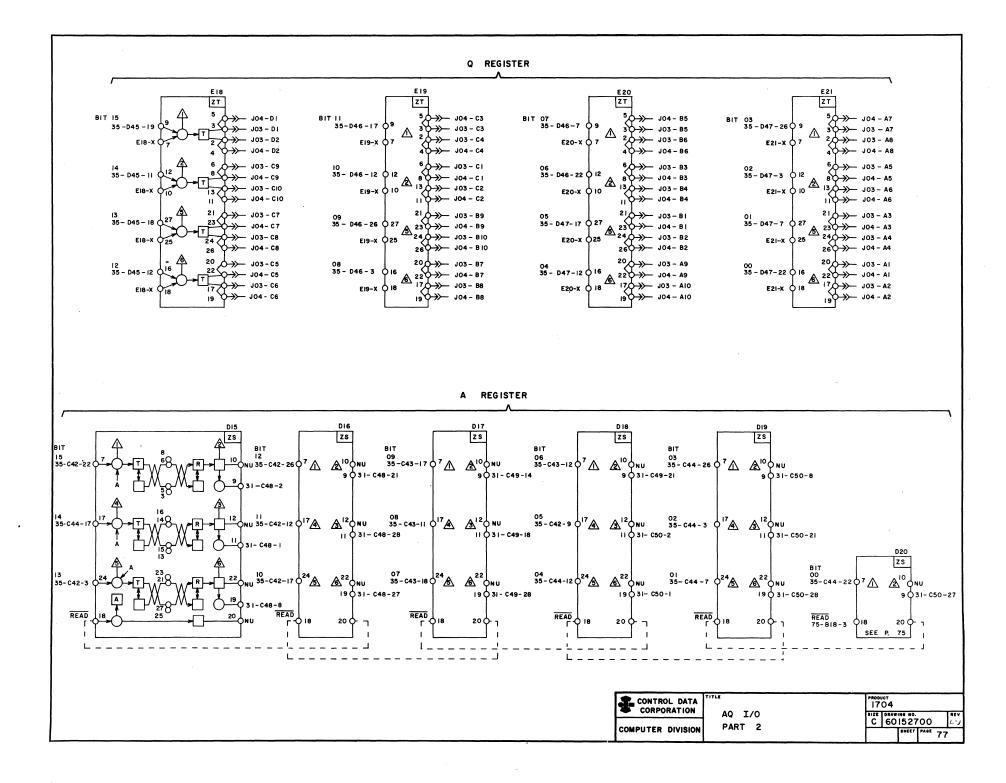

| AQ I/O (Part 2) 7                                        | 7  |

| Storage                                                  |    |

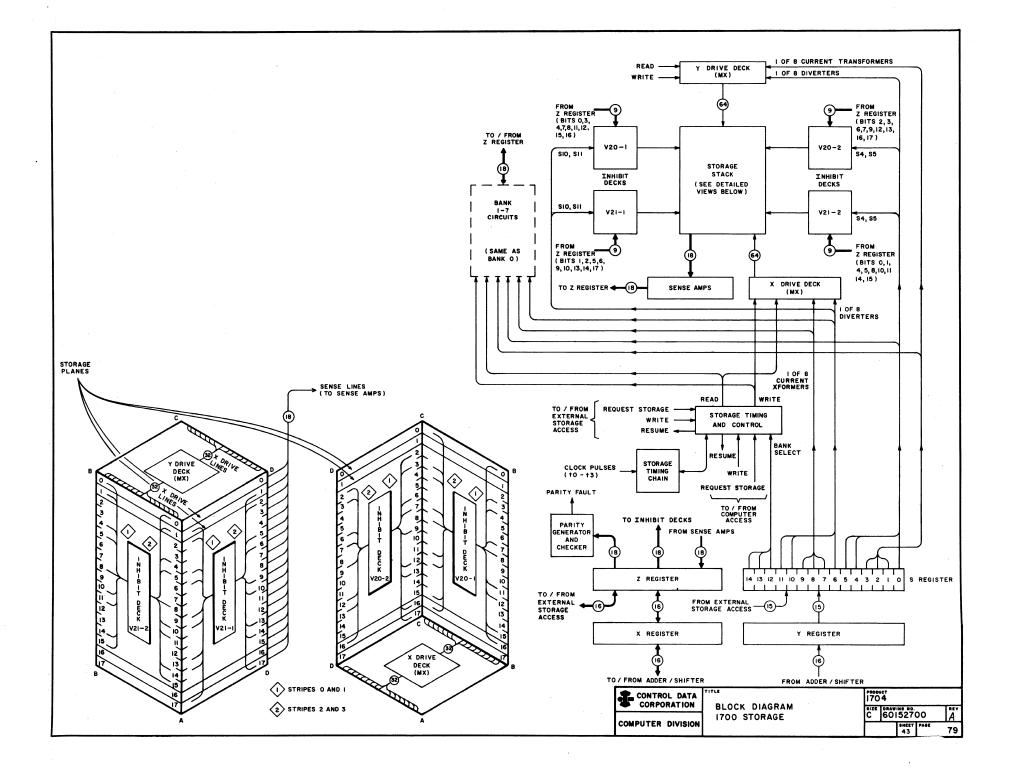

| Block Diagram 1700 Storage 7                             | 9  |

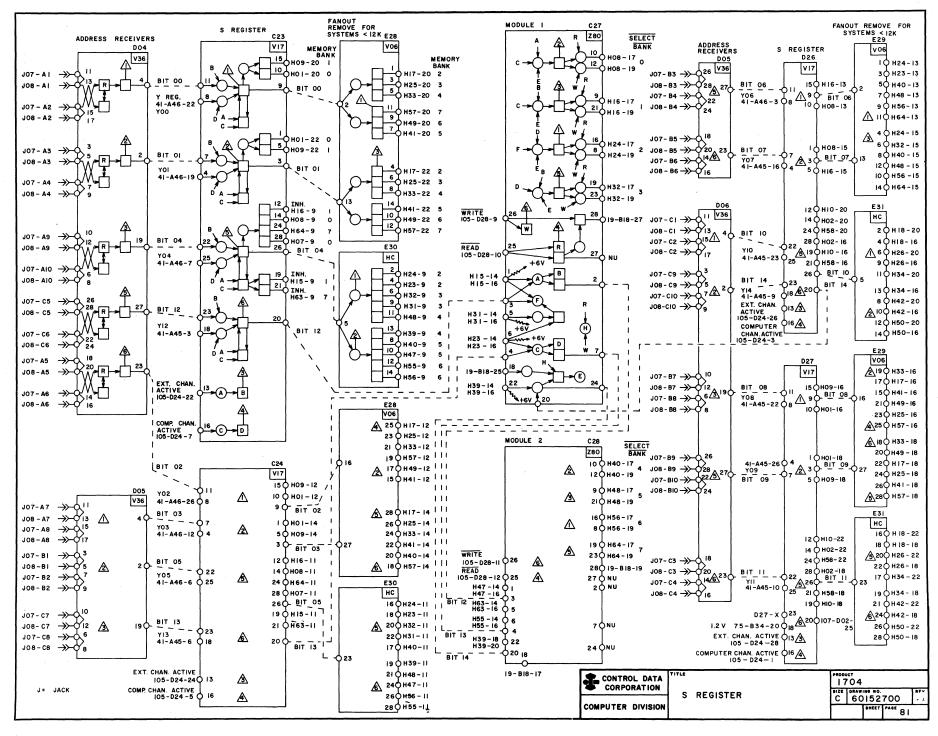

| S Register 8                                             | 1  |

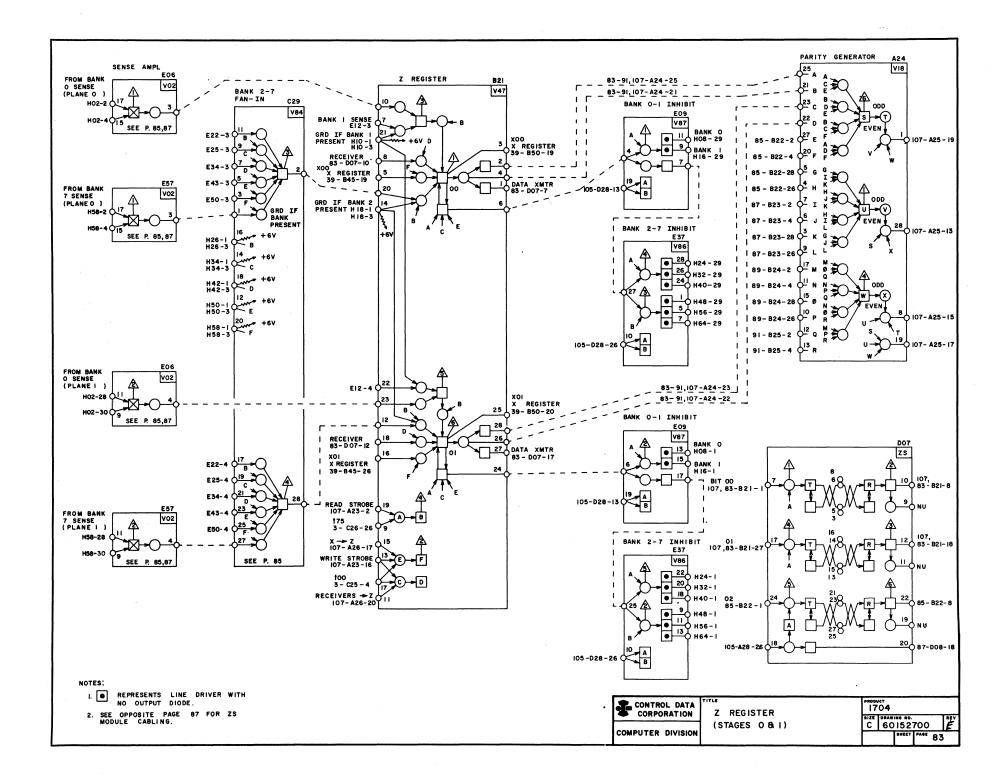

| Z Register (Stages 0 and 1) 8                            | 3  |

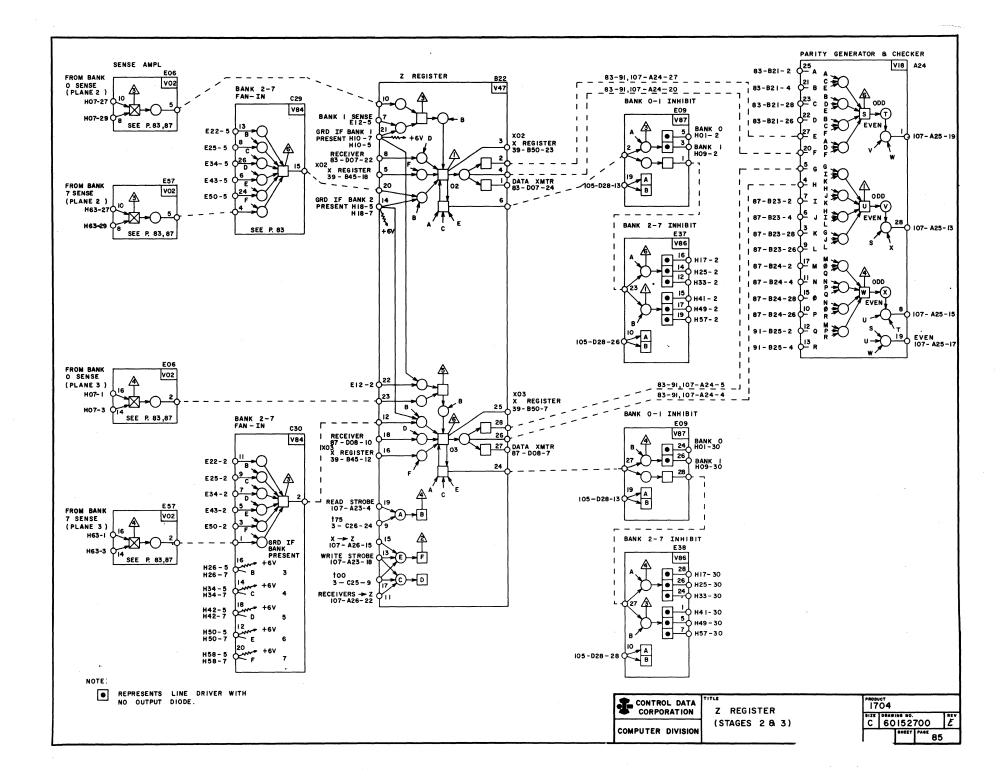

| Z Register (Stages 2 and 3) 8                            | 5  |

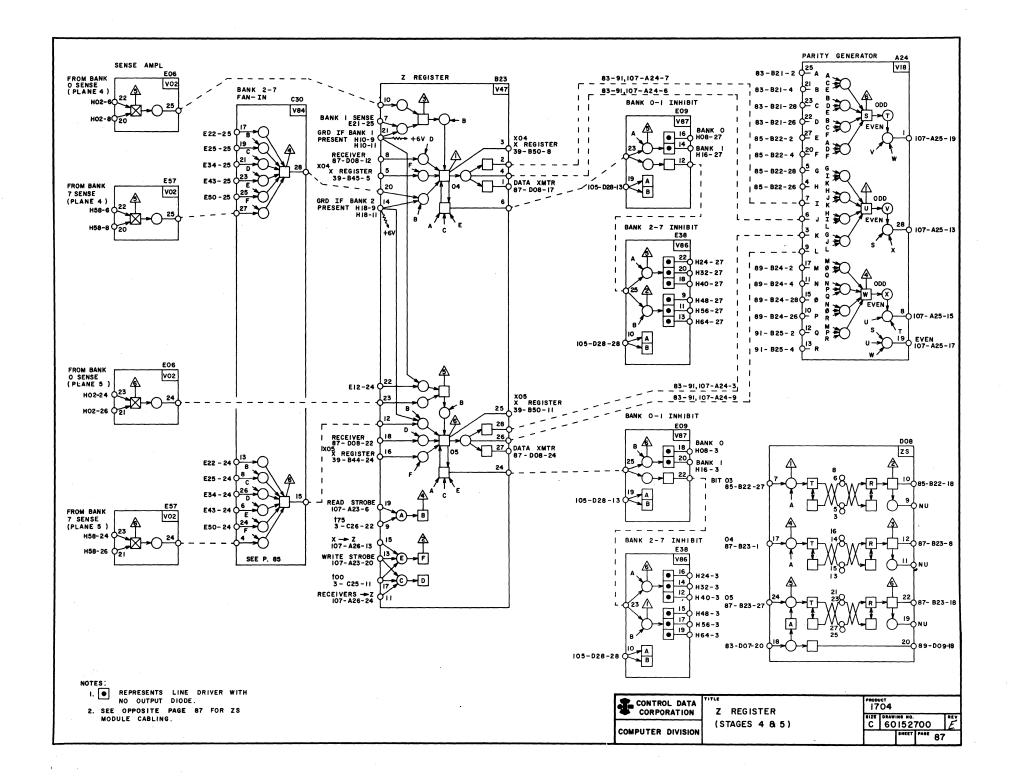

| Z Register (Stages 4 and 5) 8                            | 7  |

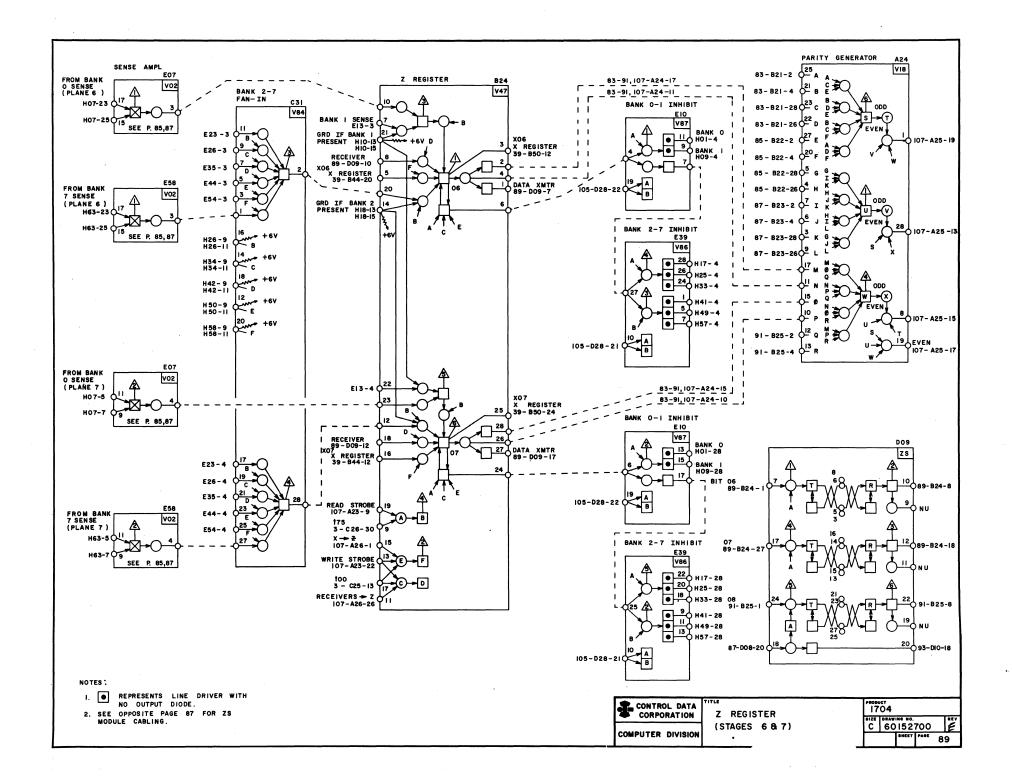

| Z Register (Stages 6 and 7) 8                            | 9  |

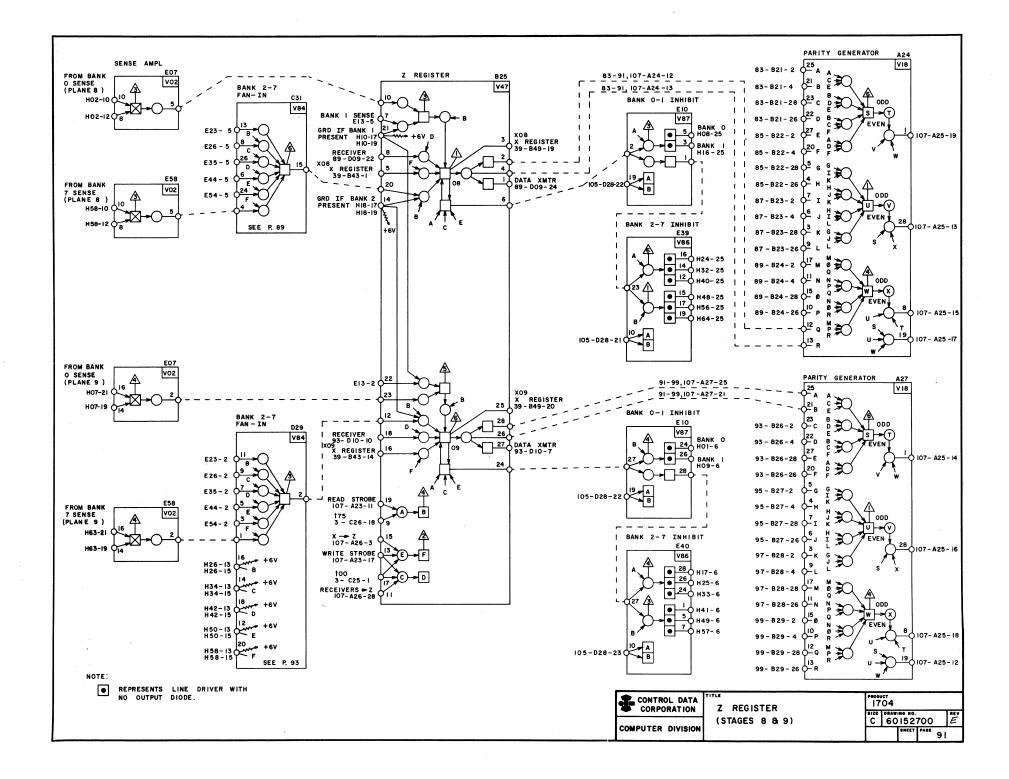

| Z Register (Stages 8 and 9) 9                            | 1  |

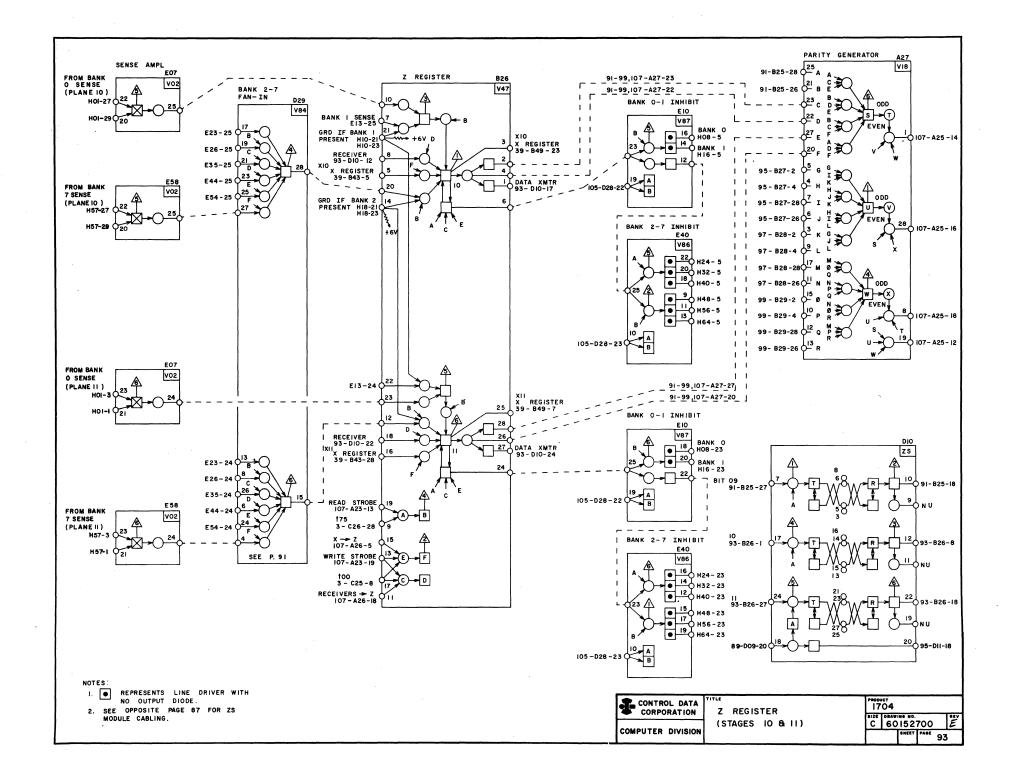

| Z Register (Stages 10 and 11) 9                          | 3  |

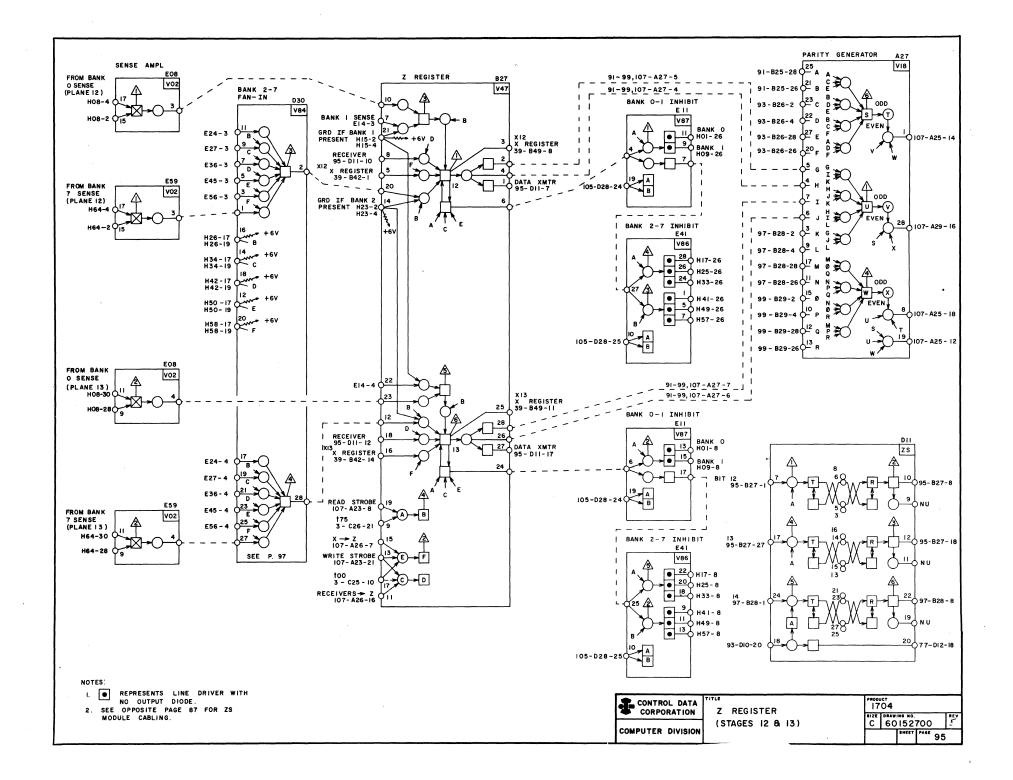

| Z Register (Stages 12 and 13) 9                          | 5  |

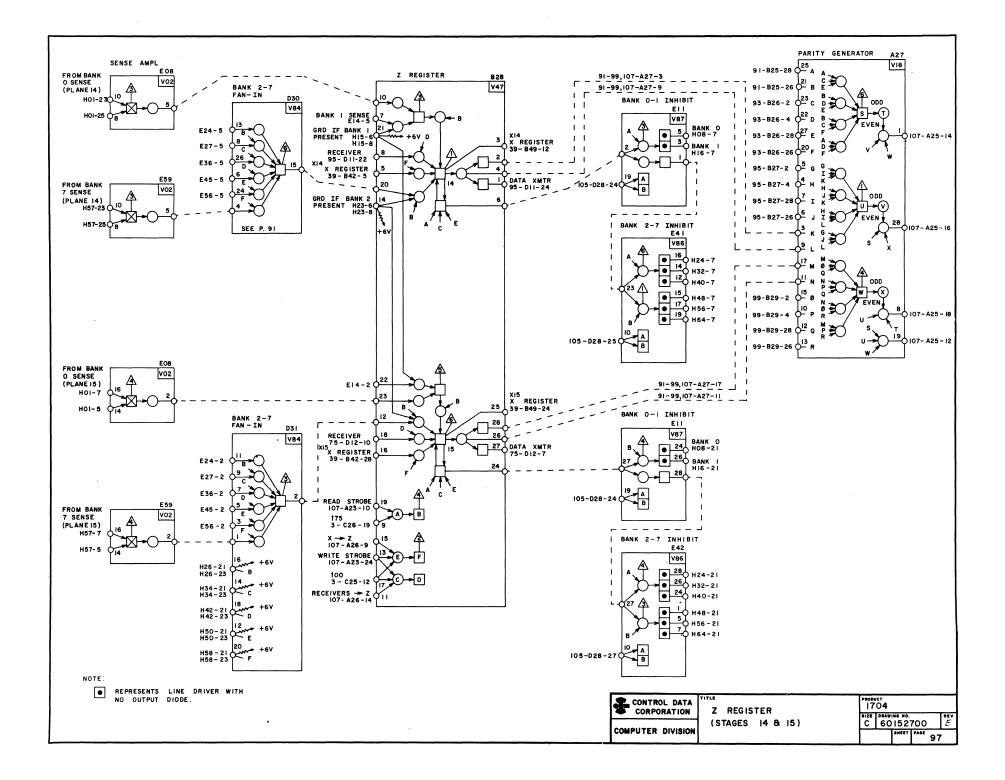

| Z Register (Stages 14 and 15) 9                          | 7  |

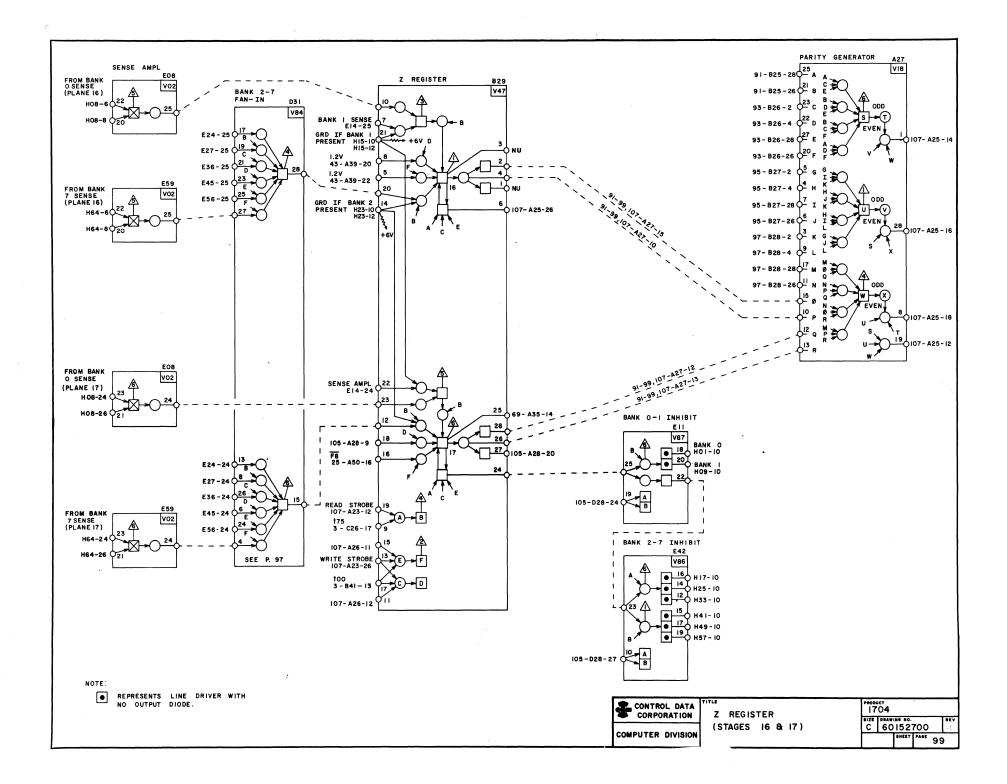

| Z Register (Stages 16 and 17) 9                          | 9  |

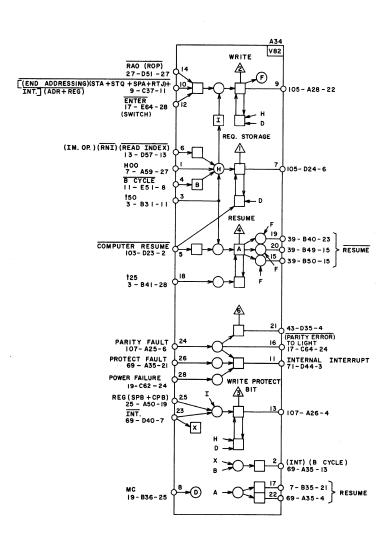

| Storage Interface 1                                      | 01 |

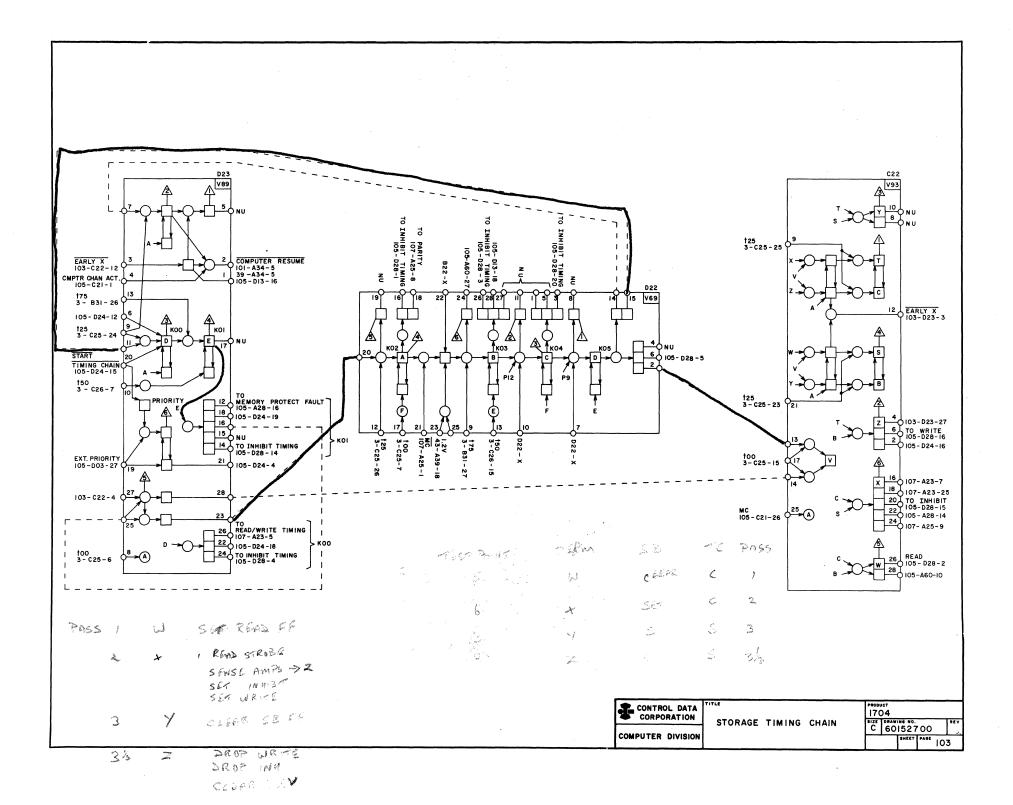

| Storage Timing Chain 1                                   | 03 |

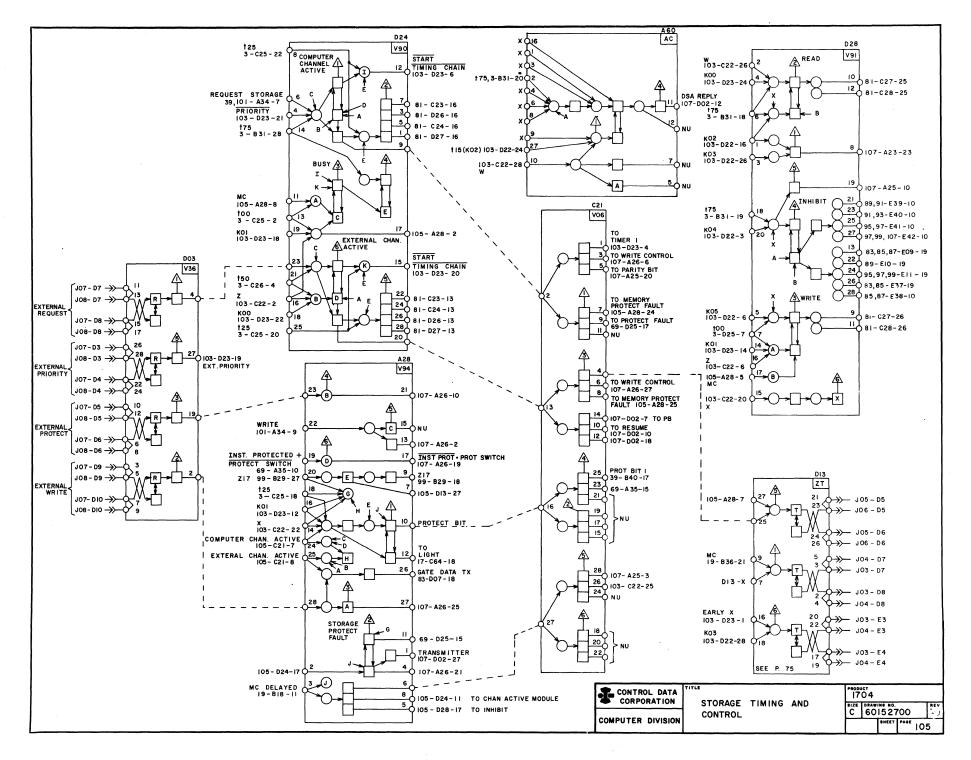

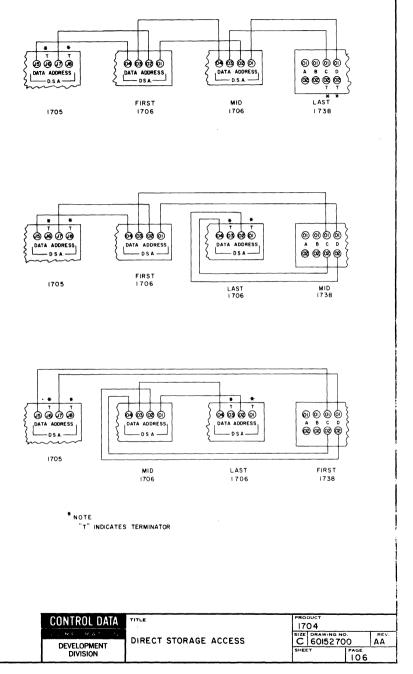

| Storage Timing and Control<br>(Sheet 1) 1                | 05 |

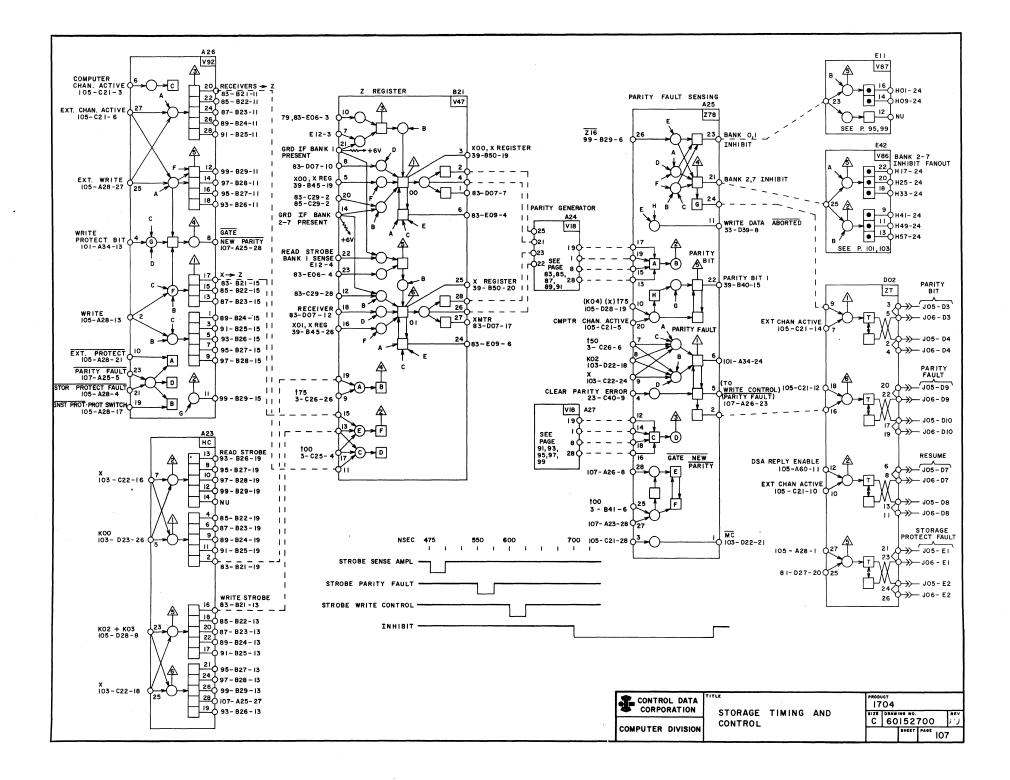

| Storage Timing and Control<br>(Sheet 2) 1                | 07 |

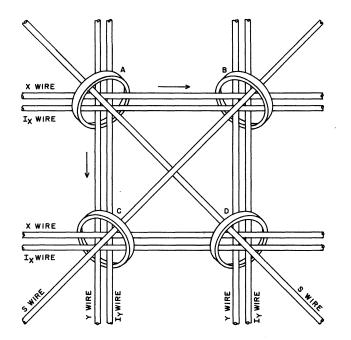

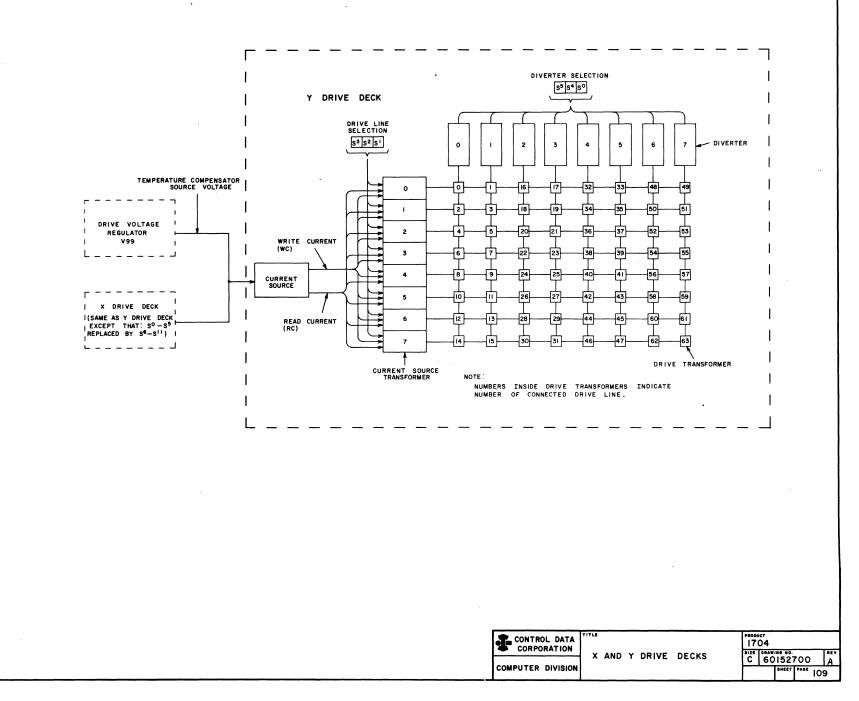

| X and Y Drive Decks 1                                    | 09 |

| Inhibit Drive Decks 1                                    | 11 |

| Transfers                                                |    |

| Addressing Modes 1                                       | 13 |

| Addressing Modes 1                                       | 15 |

## CONTENTS (Cont'd)

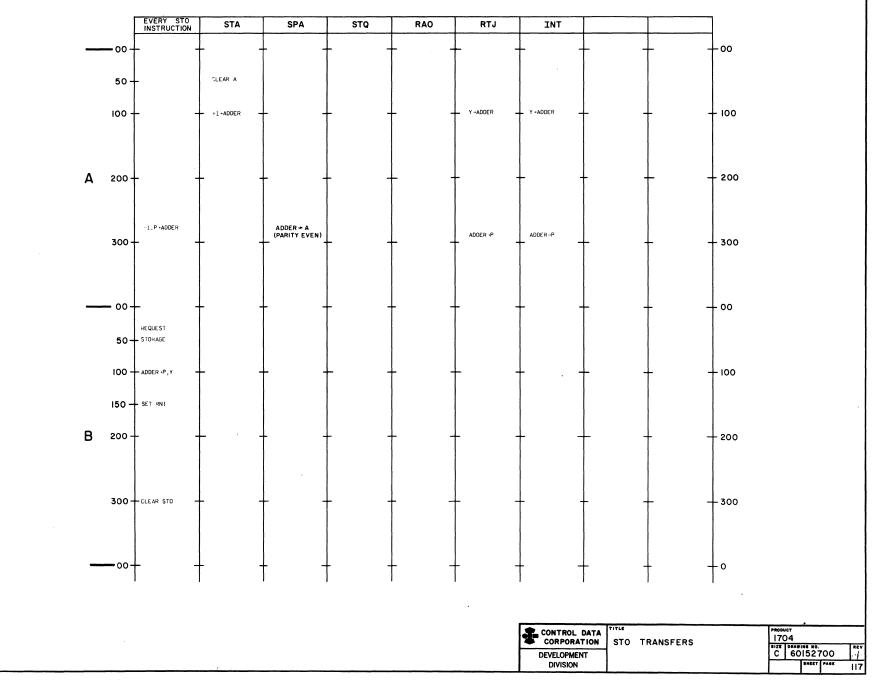

| STO Transfers                                     | 117 |

|---------------------------------------------------|-----|

| REG Transfers                                     | 119 |

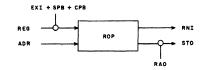

| <b>ROP Transfers</b>                              | 121 |

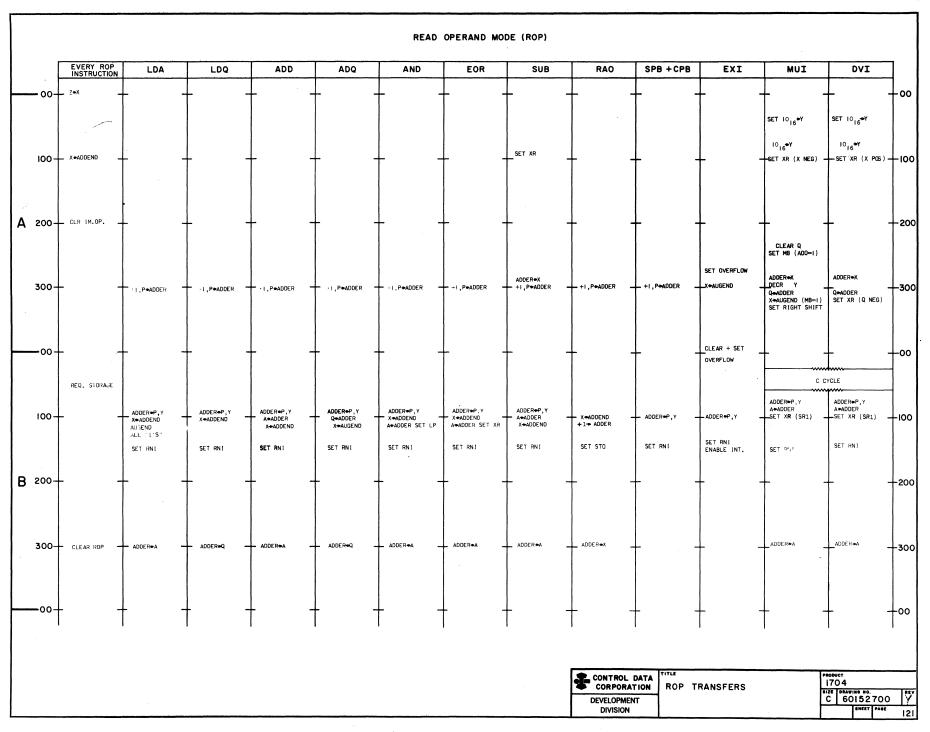

| B Cycle Transfers                                 | 123 |

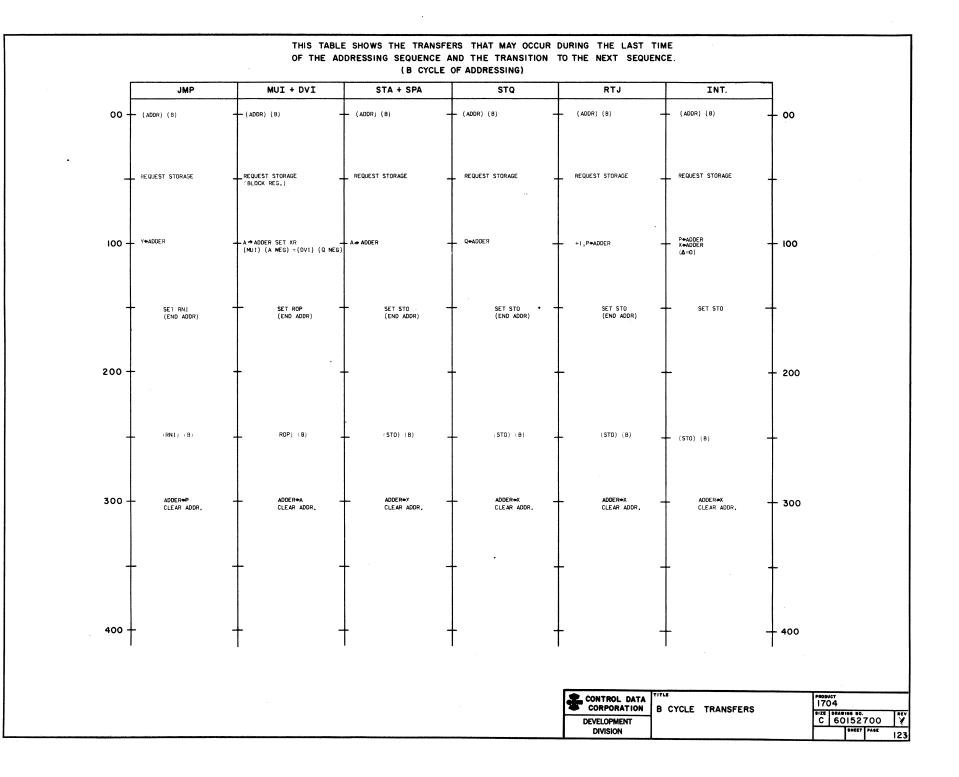

| C Cycle Transfers°                                | 125 |

| Power and Cabling                                 |     |

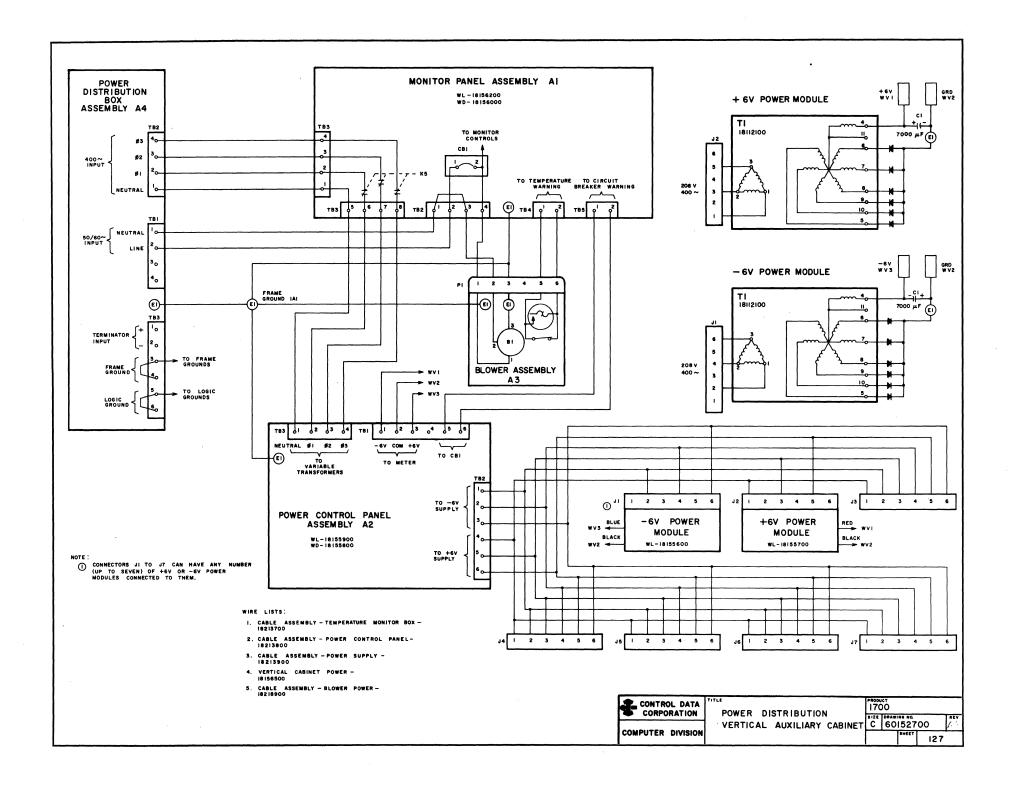

| Power Distribution, Vertical<br>Auxiliary Cabinet | 127 |

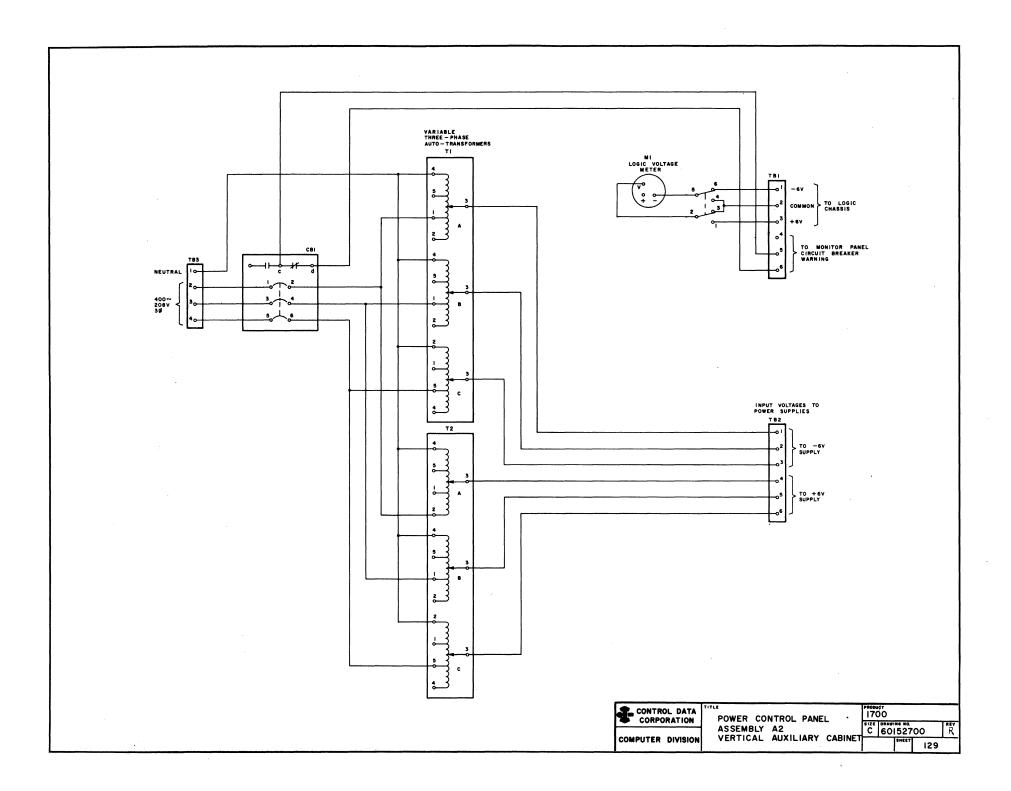

| Power Control Panel                               | 129 |

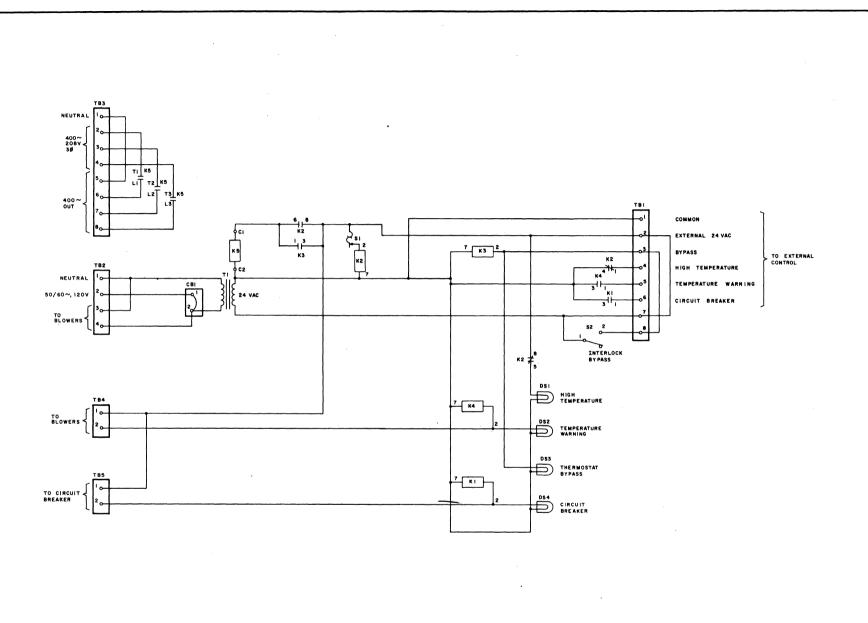

| Monitor Panel                                     | 131 |

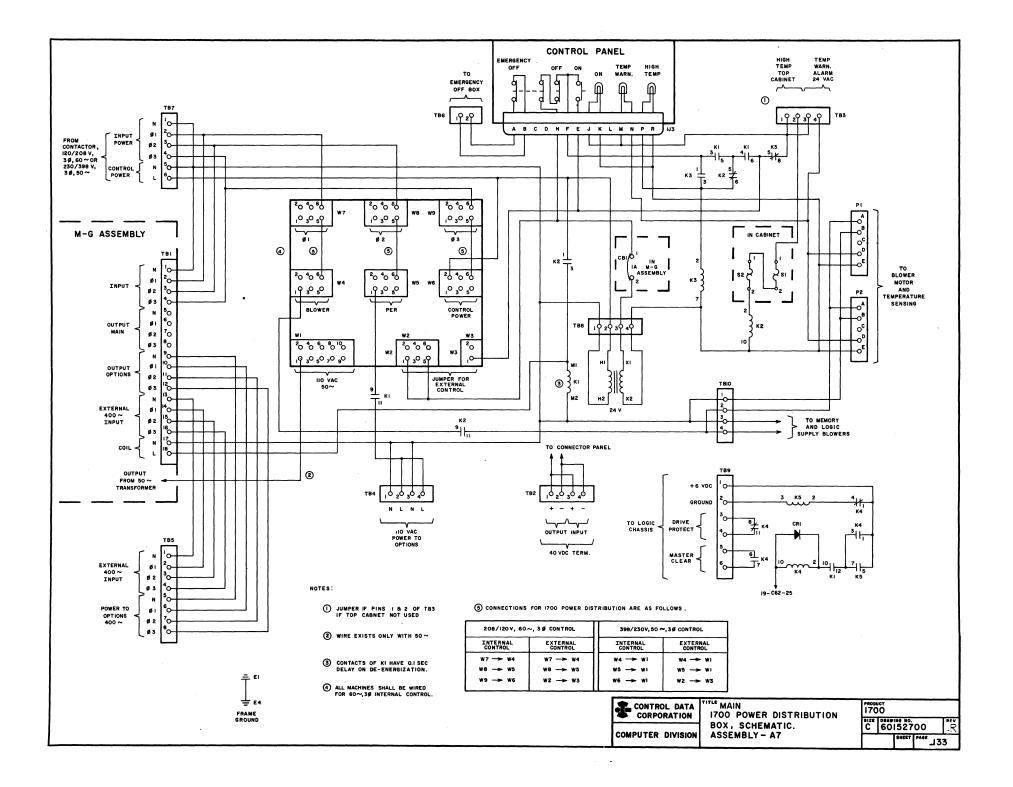

| Power Distribution Box<br>Schematic               | 133 |

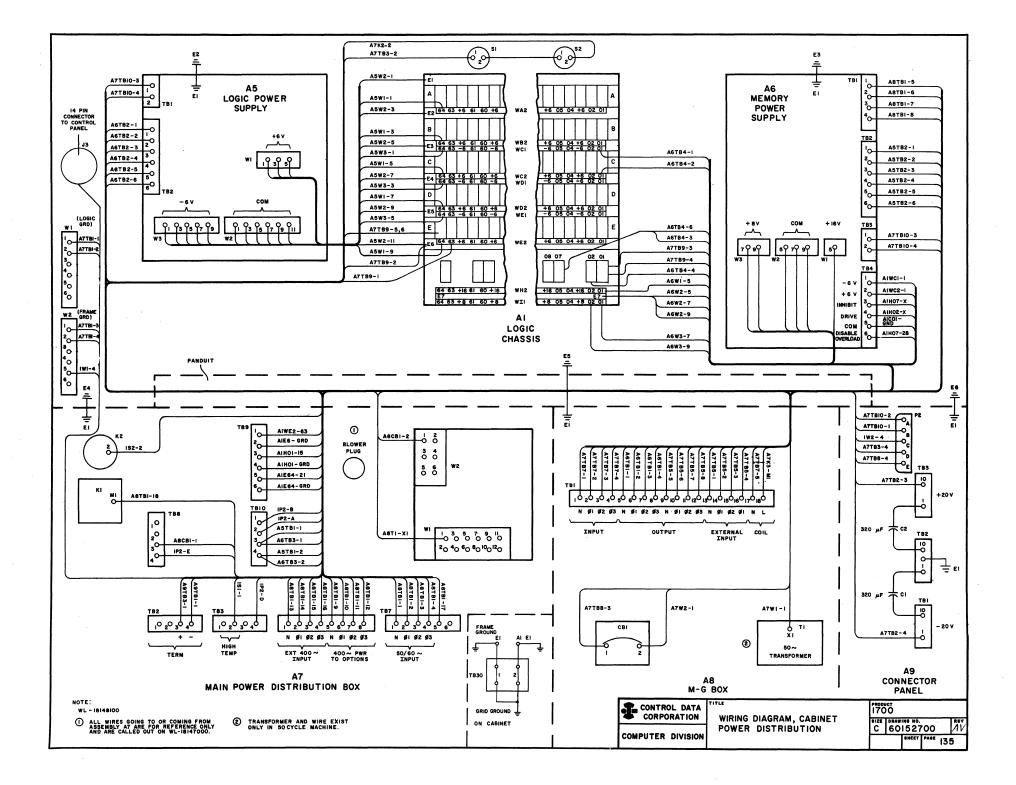

| Wiring Diagram                                    | 135 |

|                                                   |     |

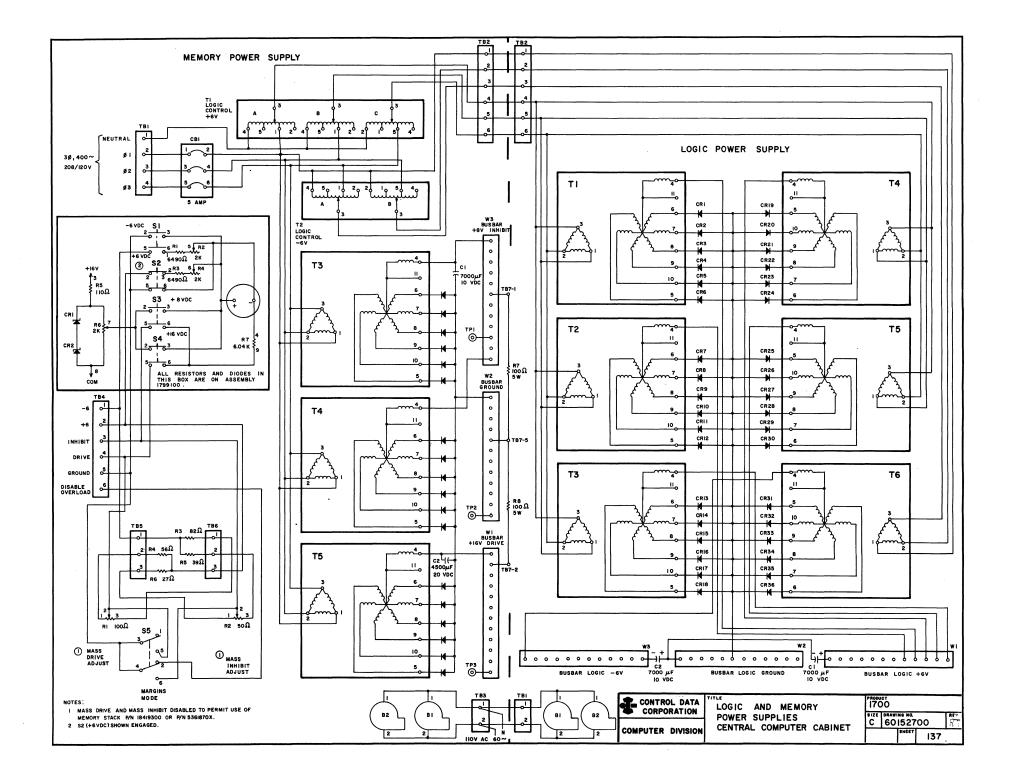

| Logic and Memory Power                 |     |

|----------------------------------------|-----|

| Supplies                               | 137 |

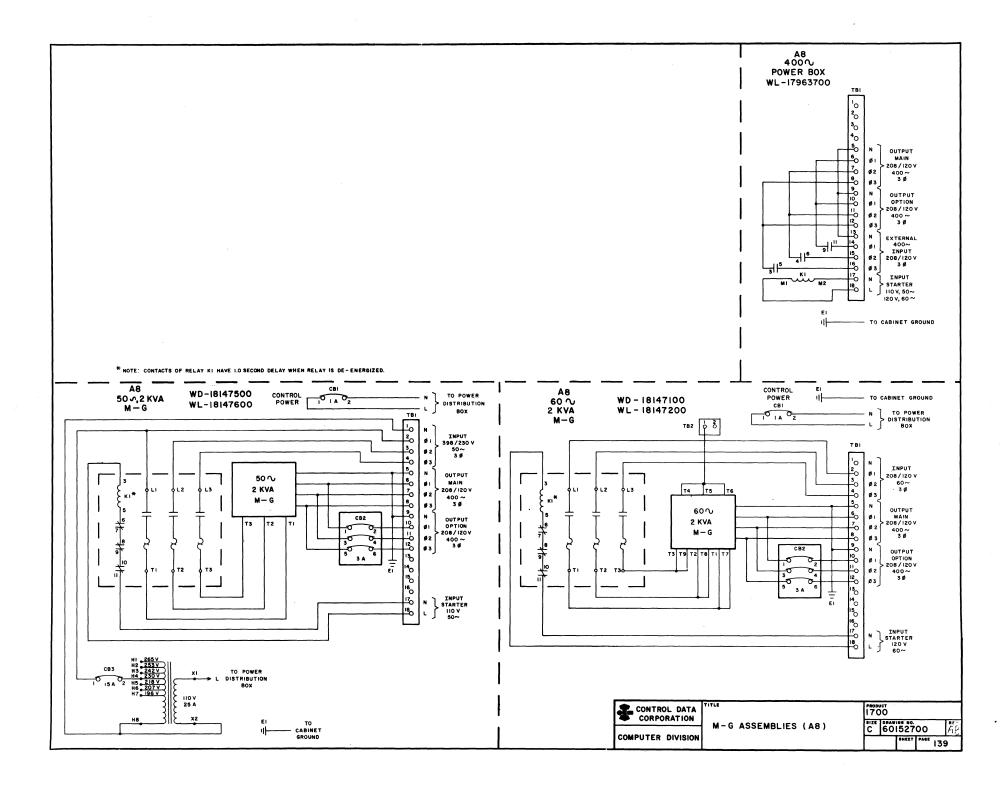

| M-G Assemblies                         | 139 |

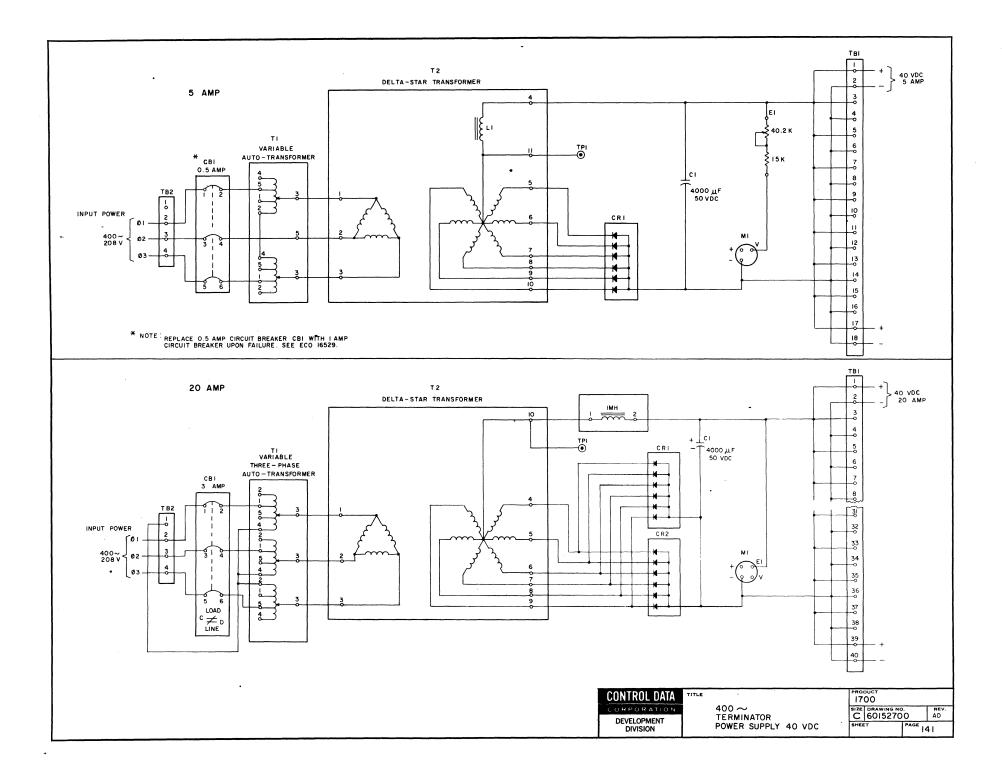

| 400 Cycle Terminator Power<br>Supply   | 141 |

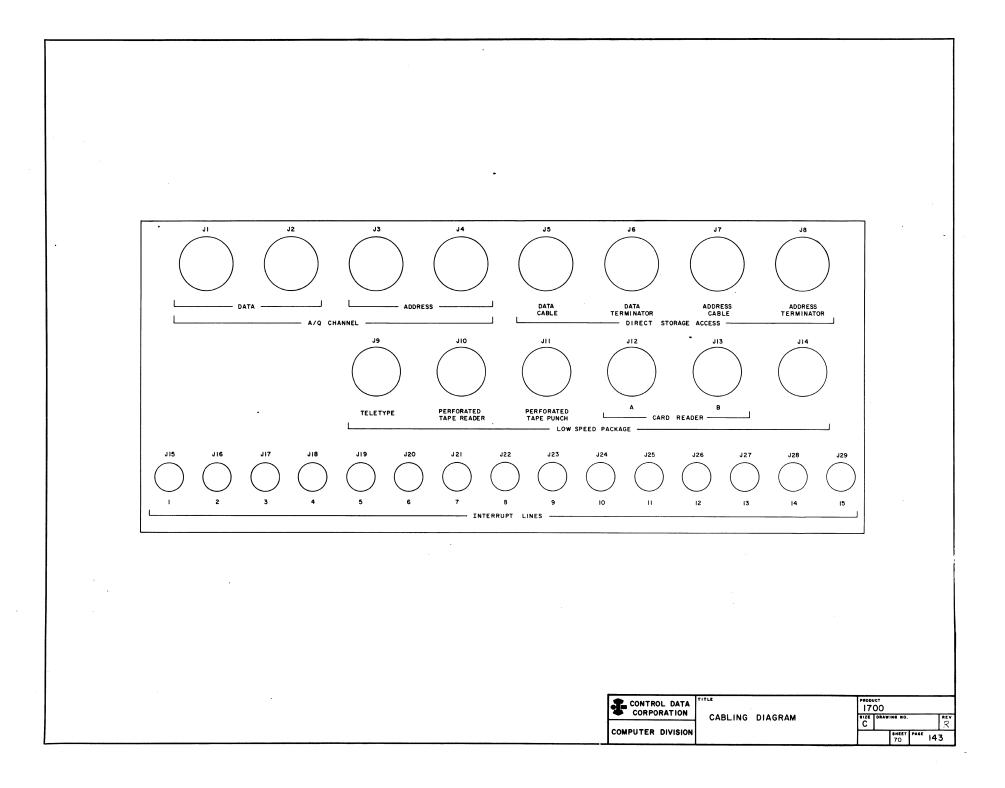

| Cabling Diagram                        | 143 |

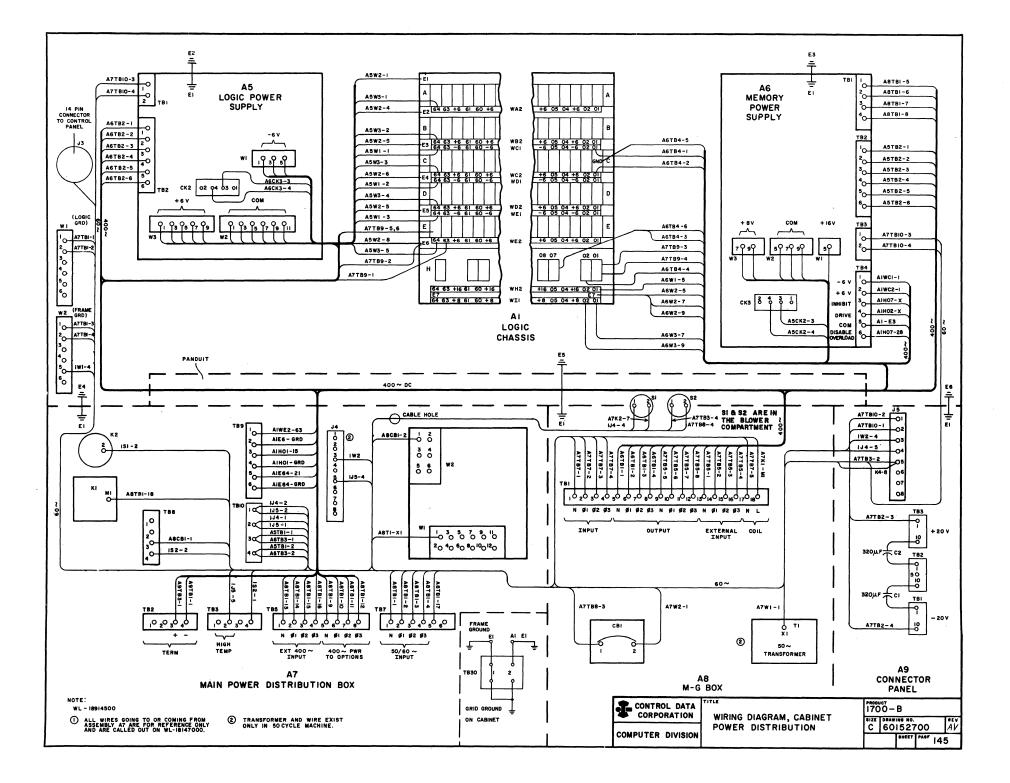

| 1704-B Cabinet Power Distribution      | 145 |

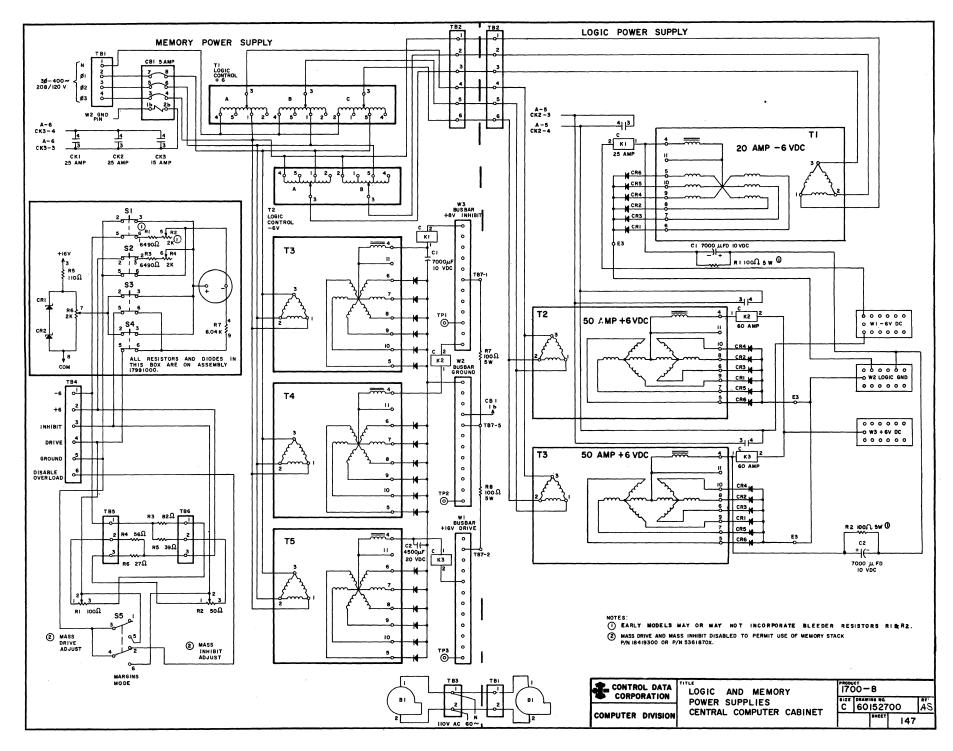

| Power Supplies                         | 147 |

| Power Distribution Box<br>Schematic    | 149 |

| Part 2. Card Placement                 |     |

| Maintenance                            | 155 |

| Appendix A                             |     |

| Instruction Flow Charts                |     |

| Appendix B                             |     |

| Tech Tips and Installation<br>Checkout |     |

vi

## MAIN COMPUTER

#### LOGIC DIAGRAM SYMBOLS

Two signals, a logical "0" and a logical "1", are the possible input or output conditions of a circuit. By convention, "1" is considered "up" and "0" is considered "down" on a timing chart, for example. Detailed descriptions of logic symbols and their associated electronic representations are contained in the Printed Circuits Manual, Vols. 3 and 4.

#### STANDARD LOGIC SYMBOLS

The 1700 Computer logic is mainly composed of the CONTROL DATA 6000 Series printed circuit modules. Standard logic diagram symbols for this type of printed circuit modules are inverters, test points, flip-flops, and twisted pair line drivers.

#### INVERTERS

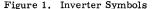

An inverter is a logic element which provides an output that is an inversion of its input. When an inverter receives more than one input, "01s" take precedence over "1's" and drive the output of the inverter to "1". Because all of the several inputs have to be "1" to drive the output of the inverter to a "0", the inverter may be considered an inverting AND (or NAND) gate when more than one input is present. Logic diagrams show the basic inverter as an arrow into either a circle or a square (see Figure 1). Both symbols represent the same electronic circuit and have the same logical interpretation. In a logic sequence of inverters, circle and square symbols are usually alternated as an aid in tracing signals, e.g., a "1" output from a square symbol implies a "1" output from subsequent squares in the logic chain if each symbol in the chain has only one input.

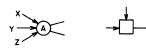

Acceptable conventions for showing multiple inputs and outputs are given in Figure 2. Note that the output of inverter A is "0" only if inputs X, Y, and Z are all "1". The multiple outputs are identical.

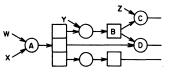

Figure 3 shows an example of an inverter network. Because multiple outputs are identical, Figure 4 shows only one arrow in cases where an inverter (A) serves as the single input to several succeeding inverters. In more complex inverter networks, multiple arrows are used (B to C and D because B is not the only input to C or D).

DENOTES SPECIAL TEXT REFERENCE

Figure 2. Multiple Inputs/Outputs

Figure 3. Inverter Networks

#### TEST POINTS

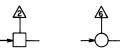

A test point performs no logic function. Logic diagrams show the test point as a triangle (see Figure 4). Test points are numbered from 1 to 6.

Figure 4. Test Point Symbols

#### FLIP-FLOPS (FF)

The flip-flop is composed of two inverters and functions as a storage device with two stable states designated as set and clear (see Figure 5). The flip-flop is set when the set output (B) is a "1" and clear when it is a "0". Note that the input (A) must be "0" to set the flip-flop, and (C) must be "0" to clear it.

Figure 5. Flip-Flop Symbol

#### WIRE TAB DESIGNATIONS

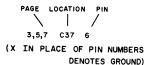

Wire tab designations written next to a pin indicate where in the drawings the pin is connected. 3, 5, 7 - C37 - 6 indicates a connection with pin 6 of module C37, found on pages 3, 5, and 7. See Figure 5.1.

Figure 5.1. Wire Tab Designations

#### TWISTED PAIR DRIVERS

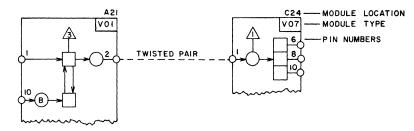

A Line Driver circuit transmits logic signals from one module to another. Modules are connected by twisted-pair lines. The standard square or circle represents the twisted-pair driver. However, the output of the square or circle connects to a pin of the module. The pin is then wired to a pin on another module (see Figure 6). The ground wire of the pair is wired to the connector ground bus of each module. The pins are represented by small circles and are numbered from 1 to 28. (Pins 29 and 30 are ground and +6 volts, respectively, and generally are not shown in logic diagrams.) The module location is shown above the card, and the module type is denoted in the upper right-hand corner.

#### RECEIVER/TRANSMITTER CIRCUITS

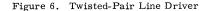

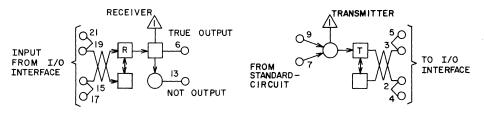

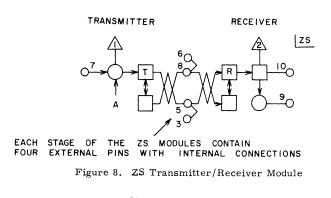

The Receiver and Transmitter circuits detect and transmit signals from and to I/O interface respectively. The Receiver and Transmitter circuits are modifications of the standard 3000 Series circuits of the same name. These circuits are contained on a printed circuit module along with the standard inverter circuits.

Figures 7 and 8 shows that Receiver and Transmitter circuits are represented by the square symbol with an "R" or "T" respectively. The two inputs to the receiver are each connected to two pins on the module.

In Figure 7, a "1" input to R is inverted, causing a "1" output from pin 6 and a "0" output from pin 13. Thus, with a "1" input, the Receiver circuit produces both True and Not outputs.

The Transmitter circuit receives a "1" input signal from a standard inverter or FF and transmits a "1" output signal to the I/O interface. In Figure 7, a "1" input to pins 7 and 9 causes a "1" output from T and thus to the I/O line.

Figure 7. Receiver / Transmitter Circuit Examples

#### SPECIAL CIRCUITS

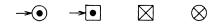

In addition to the standard symbols, the diagrams also use symbols representing special nonstandard circuits. The symbols for these circuits along with a brief description are given below.

Special variations of the standard building block are indicated by the symbols shown on Figure 9. The symbol and schematic for the corresponding special circuit are shown on the applicable logic diagram and also on the module schematic in the Printed Circuits Manual.

Figure 9. Special Circuits

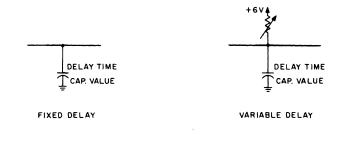

#### CAPACITIVE DELAY CIRCUITS

Capacitive Delay circuits delay input "1" signals a prescribed time before issuing an output "1" signal. The 1700 uses both fixed and variable delay circuits. Figure 10 shows examples of both types. The delay time of the circuit and capacitor value are listed beside the capacitor symbol. The variable potentiometer enables adjustment of the delay time of the circuit within certain limits.

iv Rev. AT

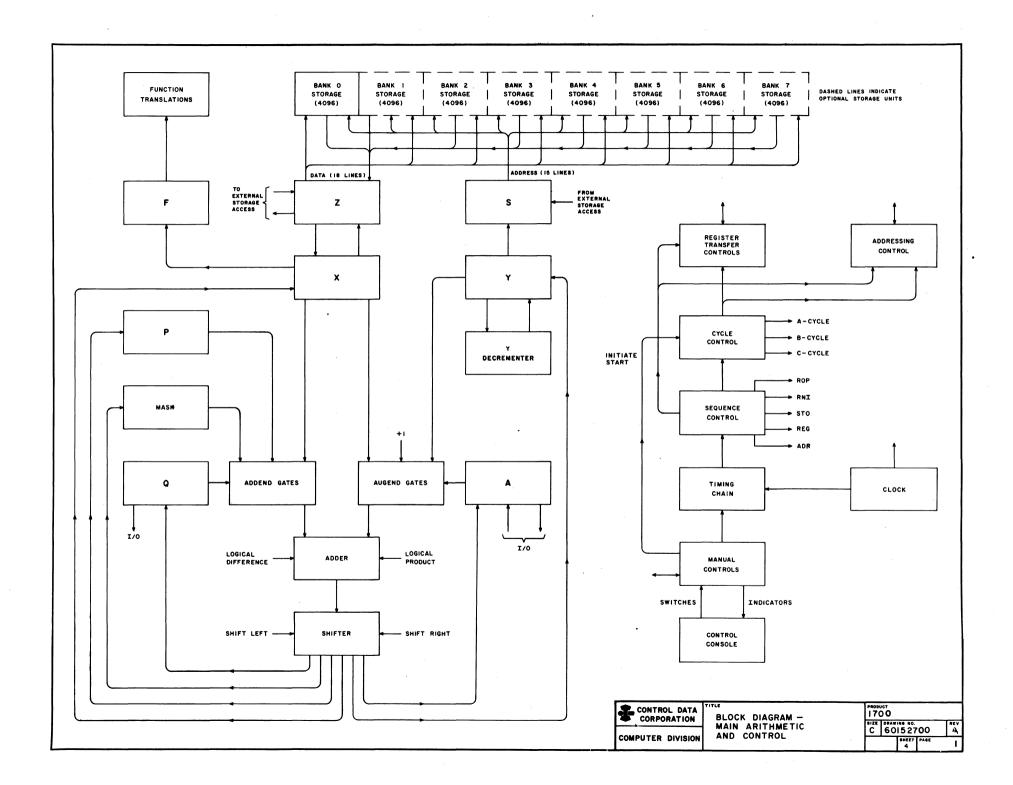

#### BLOCK DIAGRAM

The block diagram shows the main circuits in the 1704 Arithmetic and Control portion of the CONTROL DATA 1700 small industrial computer. The I/O and memory interfaces are indicated.

As shown, the 1704 consists mainly of registers, the adder/shifter network, and control circuits. In general, the registers contain quantities for some period of time. When the quantities require an Arithmetic, Logical, or Transfer operation, they are transmitted through the adder/shifter network. The adder/shifter combines the quantities with one another in a Logical or Arithmetic operation, operates on them independently as in a shift, or simply serves as a path for the contents of one register to transfer to another register. Thus, the adder/shifter serves as the main path for all Arithmetic, Logical, or Inter-Register Transfer operations.

#### MAIN REGISTERS

The function of the main registers shown on the block diagram is briefly described in the following paragraphs.

#### Z REGISTER

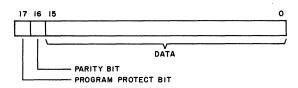

The 18-bit Z register temporarily stores all data words being read from or written into storage. Bits 16 and 17 are not part of the data but are the program protect and parity bits respectively. Control operates on these bits independently from the data bits.

In a Read Memory operation, the 16 data bits transfer to the X register. In a Write operation, the data bits to be written are transferred from X to Z register.

#### X REGISTER

The 16-bit X register holds the data bits transferring to or from the Z register. This register holds one of the parameters in most Arithmetic operations. When the X register contains an instruction, the high-order 8 bits transfer to the F register for translation.

#### F REGISTER

The 8-bit F register contains the instruction code and/or addressing mode bits. The translation of these bits direct the execution of the instructions.

#### Y REGISTER

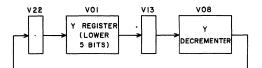

The 16-bit Address register contains the storage address for transfer to the S register during a storage reference. The Y register in conjunction with the Y Decrementer also functions as a counter during the multiply and shift instructions. The Y register temporarily stores the incomplete addresses during address modification and the final effective address when modification is complete.

#### S REGISTER

The 15-bit Storage Address register contains the effective storage address transferred from the Y register or from the external storage access. All address selection for internal storage access is controlled by the contents of the Y register.

#### P REGISTER

The 15-bit P register contains the program address of the instruction currently being executed. In the later stages of instruction execution, except in certain Jump and Skip instructions, the P register is advanced by adding +1 in the adder/shifter network for referencing the next instruction.

#### A REGISTER

The 16-bit A register functions as the principal register in most Arithmetic and Logical operations.

#### Q REGISTER

The 16-bit Q register serves as the auxiliary register in most Arithmetic and Logical operations.

#### MASK REGISTER

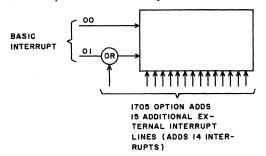

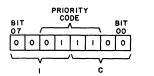

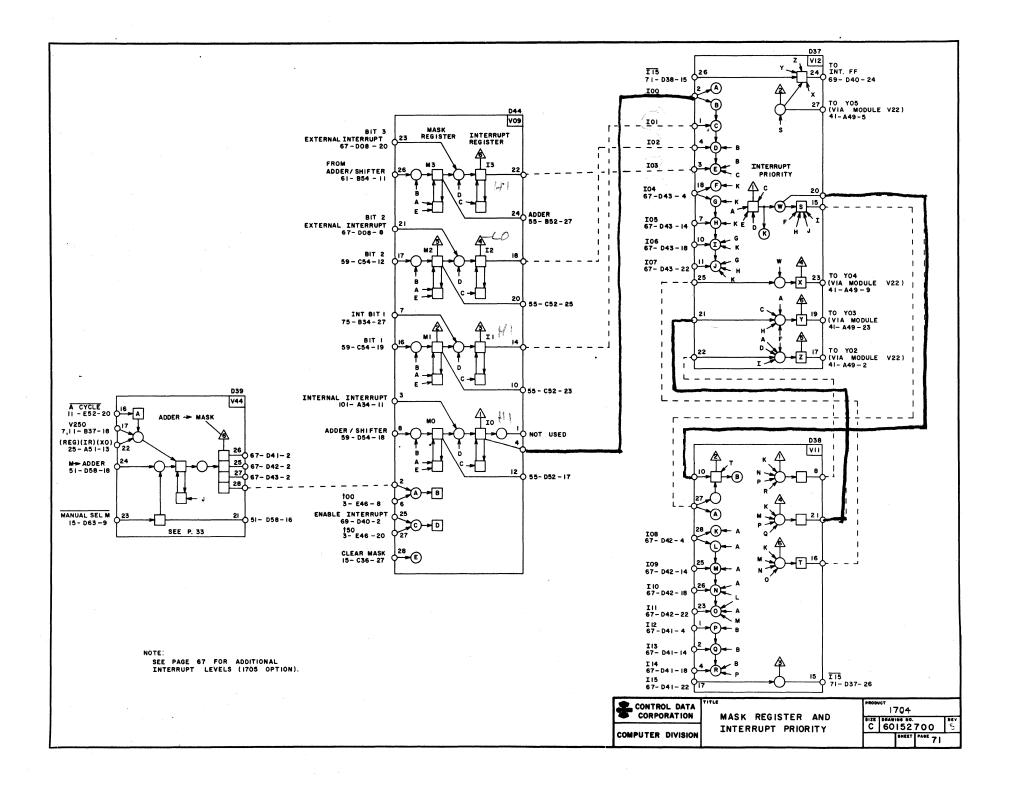

The 16-bit Mask register contains the interrupt mask bits. Each bit in the Mask register corresponds to a particular interrupt line. In order for a particular type of interrupt to be recognized when it occurs, the corresponding bit in the Mask register must be a "1".

#### ADDEND/AUGEND GATES

The addend/augend gates serve as the input gate control for the adder/shifter. In most Arithmetic, Logical, or Register Transfer operations, one input is selected by the addend gates and one by the augend gates. Thus, four inputs are applied to addend and augend gates respectively.

#### ADDER/SHIFTER

The adder/shifter performs all Arithmetic and Logical operations on the register contents. The adder/shifter also serves as the transfer path for all Inter-Register Transfer operations.

#### MAIN CONTROL

The main control circuits are shown on the right side of the block diagram.

#### MANUAL CONTROLS

The manual controls consist of the start, stop, manual set, and indicator control circuits. Thus, the manual controls initiate all start, stop, and manual selection operations in the computer.

#### CLOCK

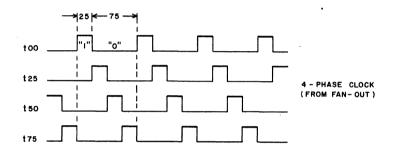

The clock circuit produces 4-phase, 25-nsec clock pulses which form the timing base for all control operations in the computer.

#### TIMING CHAIN

With an input from the clock and manual controls, the timing chain produces a series of eight controlled 25-nsec timing pulses at 50-nsec intervals.

#### SEQUENCE CONTROL

The sequence control circuit controls the mode of operation for the execution of a given instruction. There are five general modes of operation:

- 1) Read Next Instruction (RNI)

- 2) Address Mode (ADR)

- 3) Read Operand (ROP)

- 4) Store Operand (STO)

- 5) Register Transfer Mode (REG)

The execution of an instruction may pass through two or more modes of operation. All instructions begin in the RNI mode and then enter one or more of the other modes in sequence.

#### CYCLE CONTROL

Three main timing cycles control instruction operation: the A cycle, B cycle, and C cycle. The A cycle begins with an initial start or resume from storage. The A cycle enables such operations as addressing, initial register transfers, etc.

The B cycle is initiated immediately after the A cycle except in multiply, divide, and shift operations. The B cycle initiates storage operations.

The  ${\rm C}$  cycle begins after the A cycle and performs multiply, divide, or shift cycle iterations.

#### REGISTER TRANSFER CONTROLS

This circuit controls the transfer of registers in the computer based on the cycle, sequence mode, and instruction being executed.

#### ADDRESSING CONTROL

This circuit controls the modification of the address in storage reference instruction. The addressing control circuit receives inputs from cycle control, sequence control, and the address control bits in the instruction.

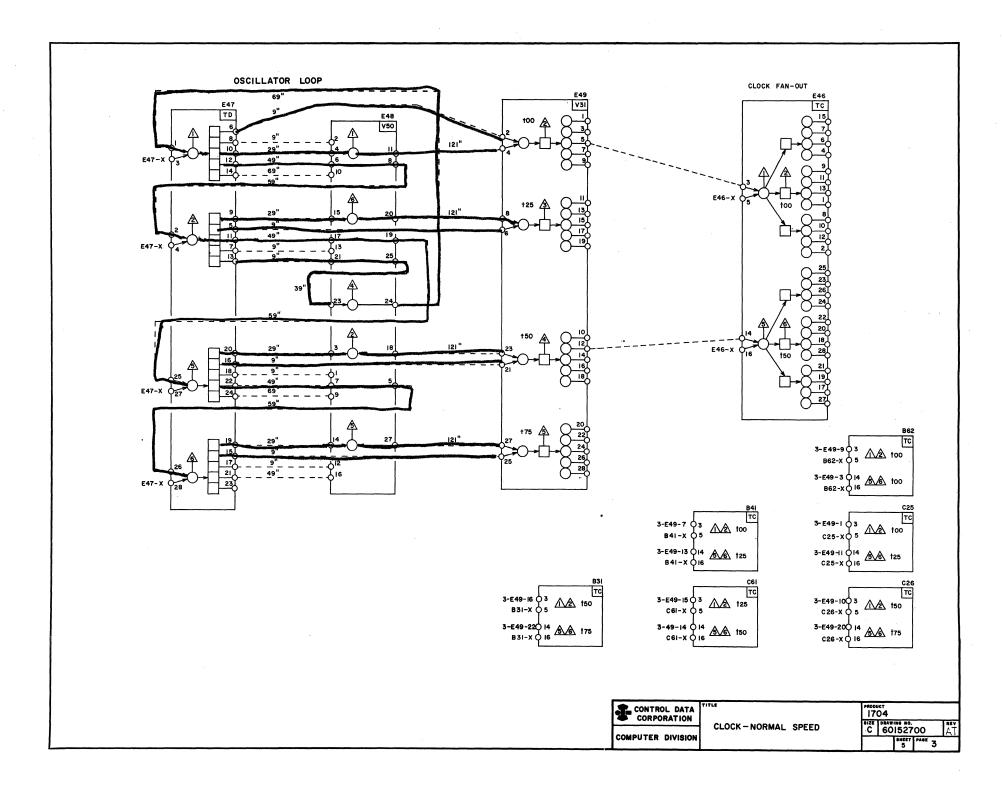

#### MASTER CLOCK - NORMAL SPEED

Timing in the 1700 is controlled by a 4-phase master clock. Four 25-nsec pulses are issued each minor cycle to control movement of data and instructions.

The master clock oscillator consists of a TD module and a V50 module. To form the 25-nsec pulses, a pulse from the TD is ANDed with a similar pulse which has

been delayed and inverted by the V50. The result is a series of pulses (primary clock) which are fanned out through V31 and TC modules to be used as timing control.

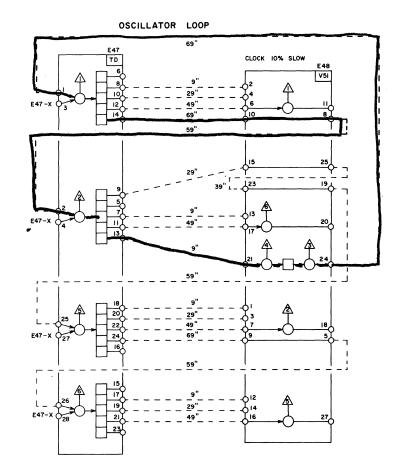

#### MASTER CLOCK - SLOW AND FAST

The master 'clock pulse rate may be increased or decreased by substitution of a V51 or V52 in place of a V50 module. The V51 module has a longer oscillator loop than the normal V50 module.

.

.

The V52 module has a shorter oscillator loop which increases the clock speed by shortening the wires between the TD and V52 module.

The V51 and V52 modules are for maintenance only and can not be used for normal computer operation.

. .

| CONTROL DATA      | CLOCK-SLOW AND FAST |     | PRODUCT<br>1704 |           |     |       |   |    |

|-------------------|---------------------|-----|-----------------|-----------|-----|-------|---|----|

|                   |                     | AND | ND FAST         | aizi<br>C | 601 | 52700 | ٦ | RE |

| COMPUTER DIVISION |                     |     |                 |           | 1   | PHEET | ~ |    |

•

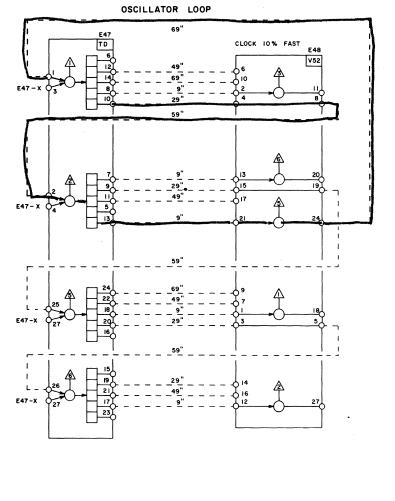

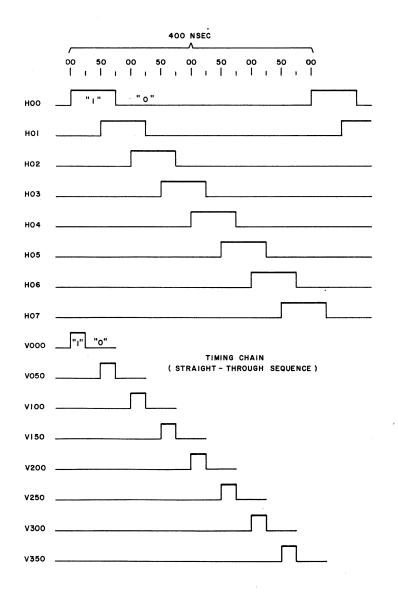

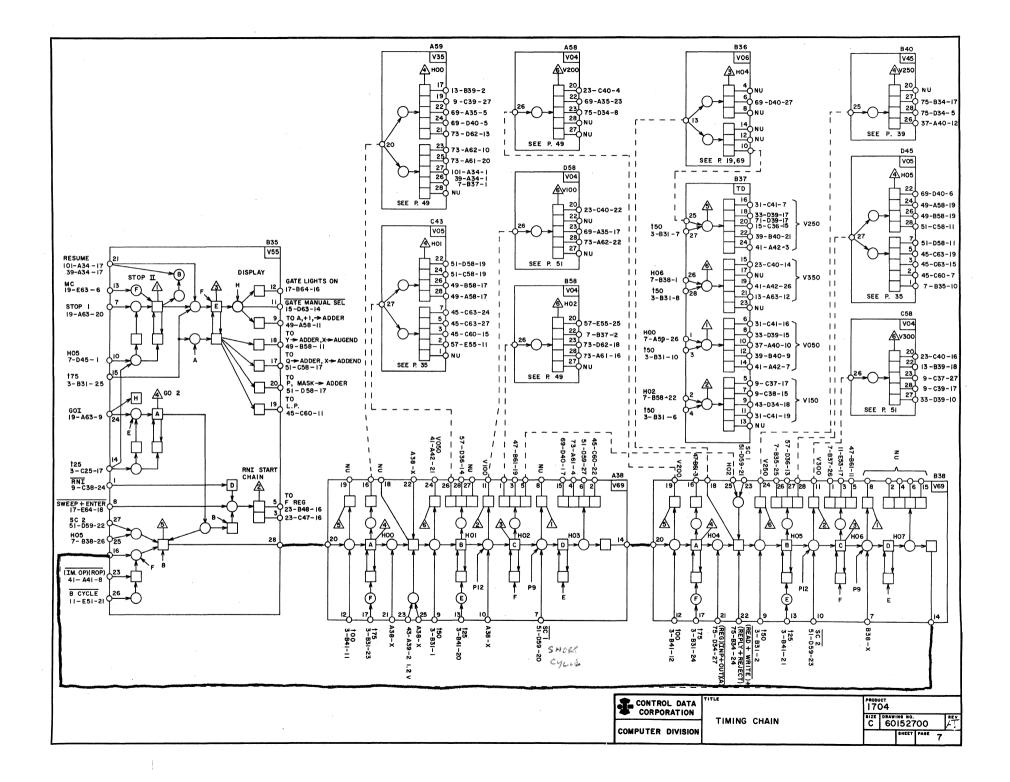

#### TIMING CHAIN AND CONTROL

The timing chain for the 1700 Computer consists of two V69 modules. Each module contains four FFs connected together, forming a chain of eight FFs (H00-H07). Each FF is gated by a clock pulse. As a "1" passes down the chain, each FF is set for 75 nsec. The FFs alternately set at t00 and t50 and clear at t25 and t75, thus overlapping each other by 25 nsec. Normally, the total cycle time for one pass of the timing chain is 400 nsec. The exception is explained below under Short Cycle 1.

The timing chain enables the V000-V350 25-nsec pulses. The V pulses occur at t00 and t50, simultaneous to the setting of the timing chain FFs.

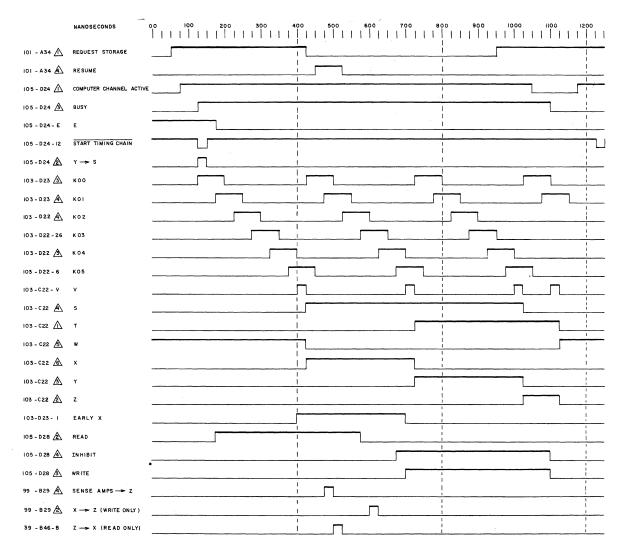

T pulses, V pulses, and H--FFs control computer timing, with the exception of storage control. Storage control uses a separate timing chain consisting of K--FFs.

Shown on the top of page 7 are a number of fan-outs for the timing chain. The fanouts are shown as partial modules, because they are included on modules of un-. related logic.

#### SHORT CYCLE 1

During Multiply and Shift instructions, time 250 occurs 100 nsec early. This sequence occurs only during the C cycle when the Short Cycle 1 (SC1) signal is present. FF H02 sets at time 100, but an SC1 signal blocks the setting of H03 at time 150. Instead, the H02 enable leaves module V69 through pin 5 and enters the second V69 module at pin 25. The SC1 signal at pin 23 enables the setting of H05 at time 250. FFs H03 and H04 are not set during the SC1 condition.

#### START TIMING CHAIN

Initially, the timing chain starts by enabling the RUN/STEP or TEST MODE switches. The Run/Step or Test Mode switch sets the Go 1 FF on module V49, p. 19. The Go 2 FF (module V55) sets and starts the timing chain if the Go 1 signal is present and the Display FF set. The Go 2 FF sets at time 25 and the timing chain starts 75 nsec later at time 00.

#### RESTART TIMING CHAIN

There are three main gates for restarting the timing chain without using the manual switches. These are the conditions for restarting the computer during program control.

1) Stop 2 FF clear and Storage Resume signal present

or

- 2) H07  $(\overline{MC})$   $\overline{B \text{ cycle}}$  + (IM.OP.) (ROP)

- 3) H05 and SC 2

- Go 2 FF set

The first condition restarts the timing chain after a storage reference. The second condition restarts the timing chain at the end of the B cycle if no storage reference is initiated or at the end of the A and C cycles. The third condition occurs during the C cycle of a Shift instruction. The SC 2 signal blocks H06 and H07 and restarts the timing chain early.

#### SET F REGISTER

4)

Output pins 3 and 5 of module V55 enable the setting of the F register under the following conditions:

- 1) Sweep + Enter (RNI) (Go 2)

- 2) Sweep + Enter (RNI) (Resume) (Stop 2)

The Run/Step or Test Mode switches enable the first condition and the storage resume enables the second condition.

### TIMING CHAIN AND CONTROL (Continued)

.

6.2 Rev. A

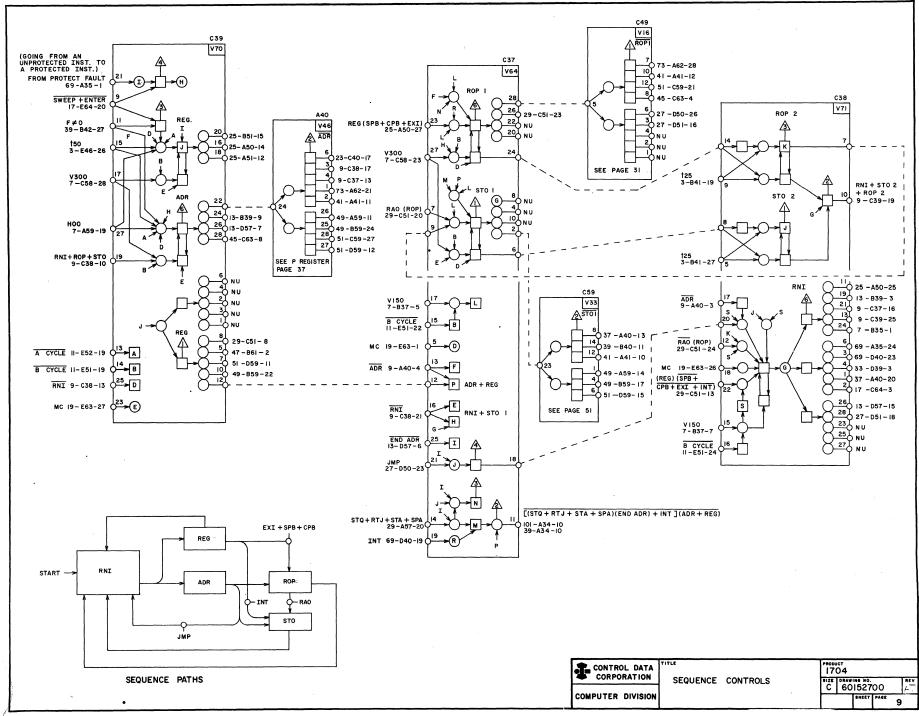

#### SEQUENCE CONTROLS

There are five modes of operation in the 1700 which enable a general series of commands for groups of instructions.

| 1) | RNI | = | <b>Read Next Instruction</b> |

|----|-----|---|------------------------------|

| 2) | ADR | = | Addressing                   |

| 3) | REG | = | Register Transfer            |

| 4) | ROP | = | Read Operand from Storage    |

| 5) | STO | = | Store Operand in Storage     |

#### RNI

The command timing for all instructions starts in the RNI mode. During RNI, the instruction code transfers from the Z register to the X register and from the X register to the F register. While in the F register, the instruction code is translated to determine whether it is addressable. If it is addressable, the ADR mode is initiated. If it is not addressable, the REG mode is initiated. A block diagram on the lower portion of the diagram shows the possible sequence paths.

The RNI Control FF is located on module V71 and has five main setting gates. If any one of the gates is satisfied, the RNI mode is enabled.

- 1) Master Clear before starting a program.

- 2) (B150)(STO2) after storing an operand

- 3) (B150) (ROP 2) [RAO (ROP)] after reading an operand (except Replace Add One instruction)

- 4) (B150) (ADR) [(JMP) (End ADR)] after addressing (Jump instruction only)

- 5) (B150) [(REG) (SPB + CPB + EXI + INT)] after REG mode (except Set/Clear Program Protect, Exit Interrupt, and interrupt during REG)

The RNI Control FF clears at time 150 of the B cycle (B150) if none of the setting gates are satisfied.

#### ADR

Instructions which are read from or written into storage use the ADR mode. The only exceptions are Set/Clear Program Protect, Exit Interrupt, and Interrupt During REG mode in which the address is already determined. During the ADR mode, storage is always requested.

The ADR Control FF is located on module V70 and has one main setting gate which enables the ADR mode.

(RNI) (A050) (F  $\neq$  0) [(Protect Fault) (Sweep + Enter)] - after reading next instruction, if F  $\neq$  0, not addressing a protected instruction from an unprotected instruction and Sweep or Enter switch not enabled.

Storage is referenced when the Sweep switch is on but not during an ADR mode.

The ADR Control FF clears at time V300, providing the RNI, ROP, or STO Control FF is set. The setting of the two control FFs overlap but the mode remains ADR until the ADR FF clears.

#### REG

Instructions which do not reference storage for reading or writing operands are considered as being in the Register Transfer mode (REG). During REG, computer control enables control FFs, enables register transfers, updates the address for the next instruction, and requests storage. The exceptions are Set/Clear Program Protect, and Exit Interrupt, where the REG mode is followed by an ROP mode. During the REG mode of these instructions the address is modified and storage requested. The address for the next instruction is updated during the ROP mode. If the computer is in REG mode when an interrupt occurs, the STO FF sets and enables STO mode.

The REG control FF is located on module V70 and has one main setting gate which enables the REG mode.

(Protect Fault) + [(RNI)(A050)([Sweep + Enter] + F = 0)]

A Protect Fault signal enables the REG mode and treats the instruction as a nonprotected "Pass" with REG mode updating the address of the next instruction. The Sweep or Enter signal enables the REG mode during RNI, and the next address is updated without using ADR mode. If the upper 4 bits of the instruction equal zero (F = 0) the REG FF sets during the RNI mode.

The REG Control FF clears at time B300 whenever the set input is not satisfied.

#### ROP

The ROP mode applies to instructions which read operands from storage and the EXI, SPB, and CPB instructions.

The ROP Control FF (ROP 1) is located on module V64 and has two main setting gates. The ROP 2.FF on module V71 provides a delay which prevents the RNI FF from setting at the same time (B150) as ROP or STO. The setting gates for ROP I are as follows:

- (B150) (ADR) [(End ADR + STQ + RTJ + STA + SPA) (End ADR) (JMP + End ADR)] - not a Store instruction, end of addressing, and not a Jump instruction. The End ADR condition is not considered in the setting of the FF.

- 2) (B150) (INT) [REG (SPB + CPB + EXI)] an interrupt during REG mode enables STO.

The ROP 1 FF clears at time B300 if the RNI or STO 1 FF is set. The normal sequence path is from ROP to RNI, as a Replace Add One instruction is necessary to set STO.

STO

The STO mode applies to instructions which write operands into storage and interrupts occurring during the ADR or REG modes.

The STO Control FF (STO 1) is located on module V64 and has two main setting gates. The STO 2 FF on module V71 provides a delay which prevents the RNI FF from setting at the same time (B150) as ROP or STO. The setting gates for STO 1 are as follows:

- 1) (B150) (ADR + REG) [(End ADR) (STQ + RTJ + STA + SPA) + INT] interrupt enables STO 1 from ADR or REG mode, other instructions come from ADR mode only.

- (B150) (ROP 2 (RAO) Replace Add One instruction came from ROP mode. It reads from and then writes into storage.

The STO 1FF clears at time B300 if the RNI FF is set. The computer always initiates an RNI mode after writing into storage.

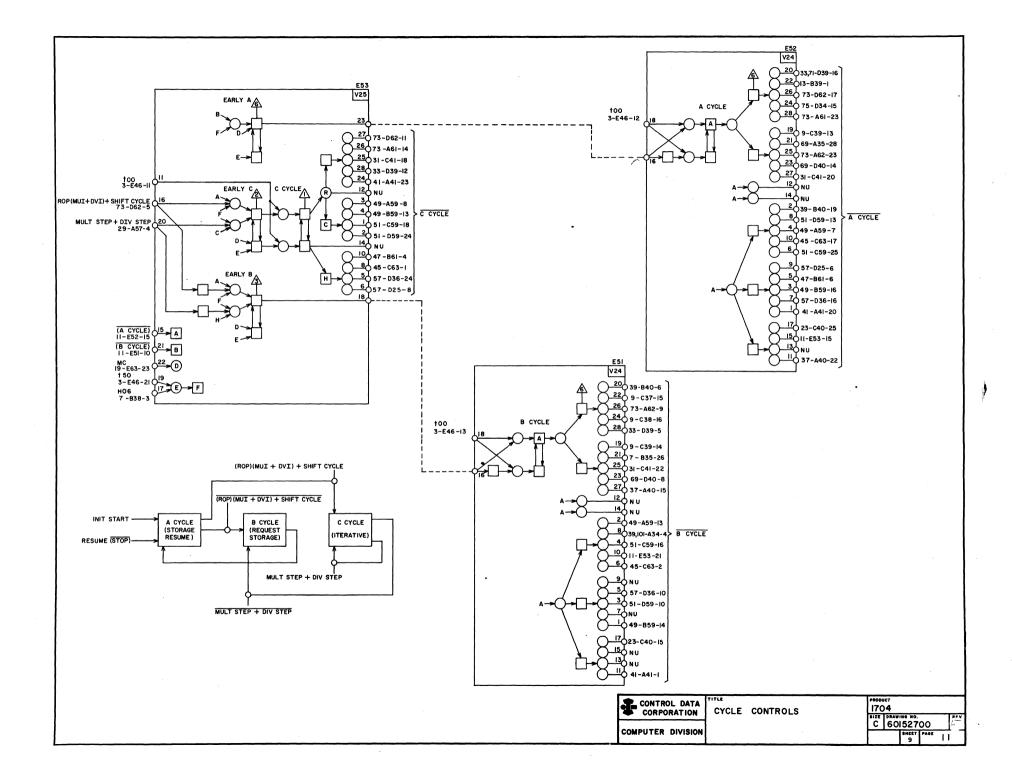

#### CYCLE CONTROL

One pass down the timing chain is considered a cycle. The 1700 Computer has three unique cycles.

- 1) A cycle (storage resume)

- 2) B cycle (storage request)

- 3) C cycle (iterative)

The normal cycle sequence is resume, request, resume, request, etc. or  $A \to B \to A \to B$ , etc.

The Multiply, Divide, and Shift instructions use a C cycle in addition to the A and B cycles. The C cycle is iterative because the computer stays in the C cycle until shifting for that particular instruction is complete. The C cycle occurs between the resume and the next request.

$$A \rightarrow C \rightarrow B$$

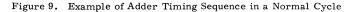

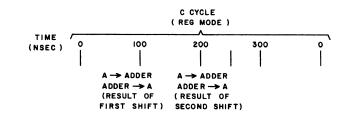

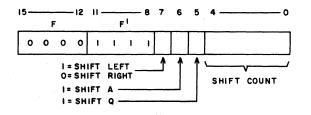

A and B cycles are always 400 nsec long. C cycles are either 200, 300 (short cycle) or 400 nsec long. Shift C cycles are 200 nsec long and multiply C cycles are 300 nsec long until the last C cycle (Y00-04 = 0), which is 400 nsec long. All C cycles for divide are 400 nsec long.

Cycle control, sequence control, and timing chain times are combined to enable specific conditions in command timing. For example, an instruction may have two or more B cycles and time 100s. The sequence mode combined with B100 enables a unique condition such as ADR (B100), ROP (B100), or RNI (B100).

The three modules below contain two Control FFs and the fan-out for each cycle. The Early Cycle FFs set at time 350 and clear at the following 350 time. The Normal Cycle FFs set at time 00 and clear at the following time 00 providing the corresponding Early Cycle FF is set.

A Master Clear pulse starts the computer in the A cycle. At time A350 the Early B or Early C Cycle FF sets, depending upon the condition (ROP) (MUI + DVI) + Shift Cycle. At the same time the Early A FF clears. The A Cycle FF clears and the B or C Cycle FF sets 50 nsec later. B cycles are followed by A cycles either upon a storage resume or ( $\overline{\text{ROP}}$ ) (IM. OP) condition. C cycles are followed by B cycles or another C cycle. The Multiply Step + Divide Step condition reinitiates the C cycle. The C Cycle FF does not need a reinitiation pulse for Shift instructions. During the shift cycle the Early C Cycle FF does not clear because the H06 pulse is not available. Short Cycle 2 (SC 2 blocks the setting of H06 and H07 during a shift cycle (see Timing Chain, page 7). The (H05) (SC 2 pulse (page 7 module V55) restarts the timing chain after each shift, and the computer remains in the C cycle. On the last iteration of shift, the  $\overline{\text{SC 2}}$  pulse enables H06, and the Early C Cycle FF clears.

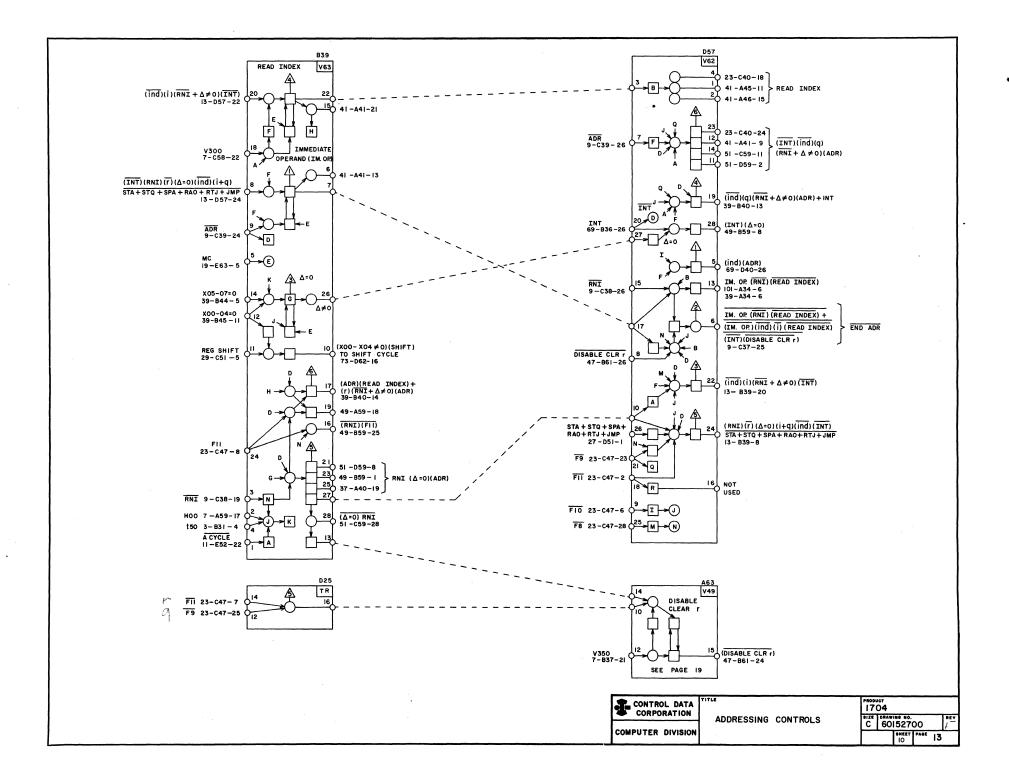

#### ADDRESSING CONTROLS

The outputs of the four modules below are addressing conditions used in command timing. These addressing translations enable commands used in assembling the effective address. Module V63 contains three addressing control FFs.

#### READ INDEX

The setting of the Read Index FF indicates that the present storage reference is for the Index register (address 00FF). The Read Index FF sets at time A300 when the following condition is present:

ind (i)  $(\overline{RNI} + \Delta \neq 0)$   $(\overline{INT})$

This condition does not mean that the Indirect and Relative signals are unused in forming the effective address. It means that these conditions are not available when indexing. Indexing is the last operation in forming the effective address. The output of the Read Index FF is used in forming other addressing conditions. When the set condition is disabled, the Read Index FF clears at time A300.

#### IMMEDIATE OPERAND (IM. OP.)

The IM.OP. FF sets at time A300 when the indicated condition is present. The IM.OP. signal means that the effective address is the operand for ReadOperand instructions. The three addressing modes which use IM.OP. are marked by an 6 at the bottom of the chart on page 115. The IM.OP. FF clears at the first A300 time after addressing is complete.

#### Δ = 0

The  $\Delta = 0$  FF sets at time A050 of the RNI mode when  $\Delta = 0$ . This FF enables the P + 1 portion of the effective address and is combined with other translations to form addressing conditions. This FF stays set until the next A050 time of RNI.

ø

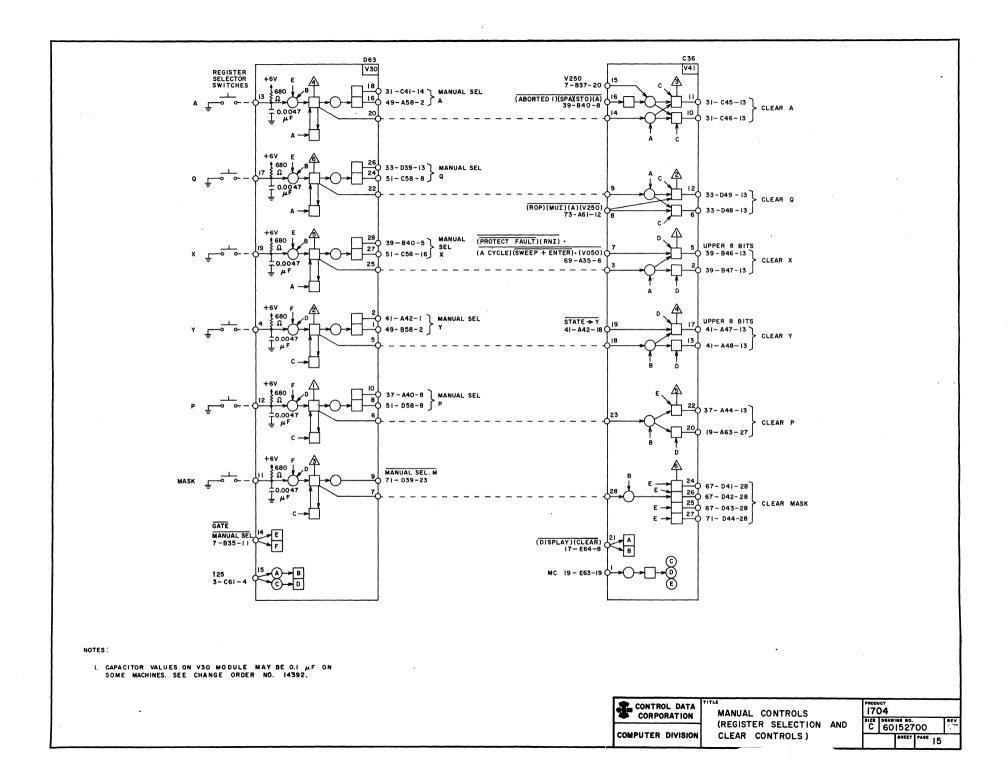

#### MANUAL CONTROLS (REGISTER SELECTION AND CLEAR CONTROLS)

A six-position Register Selector switch and associated logic selects one of the X, A, Q, P, y, and Mask registers for manual display and entry.

The condition (Register Selector switch set) (Display) (T25) sets a FF in the V30 module that corresponds to the Register Selector switch position. (Since only one position of the Register Selector switch can be engaged at one time, two or more registers are not available simultaneously.)

The output from the set FF goes to the V41 module enabling an inverter if the condition (Display) (Clear) exists. Then the selected register is cleared. The following table shows the other conditions which cause a register to clear. CONDITION

#### CLEARS

SPA (STO)(A cycle)(V250) ROP (A cycle)(V250)(MUI) (Protect Fault)(RNI)(A cycle)(Sweep+ ENTER)(V050) Interrupt STATE → Y

entire Q register upper 8 bits of X register

upper 8 bits of Y register

entire A register

If the Master Clear switch is set, all six registers clear simultaneously.

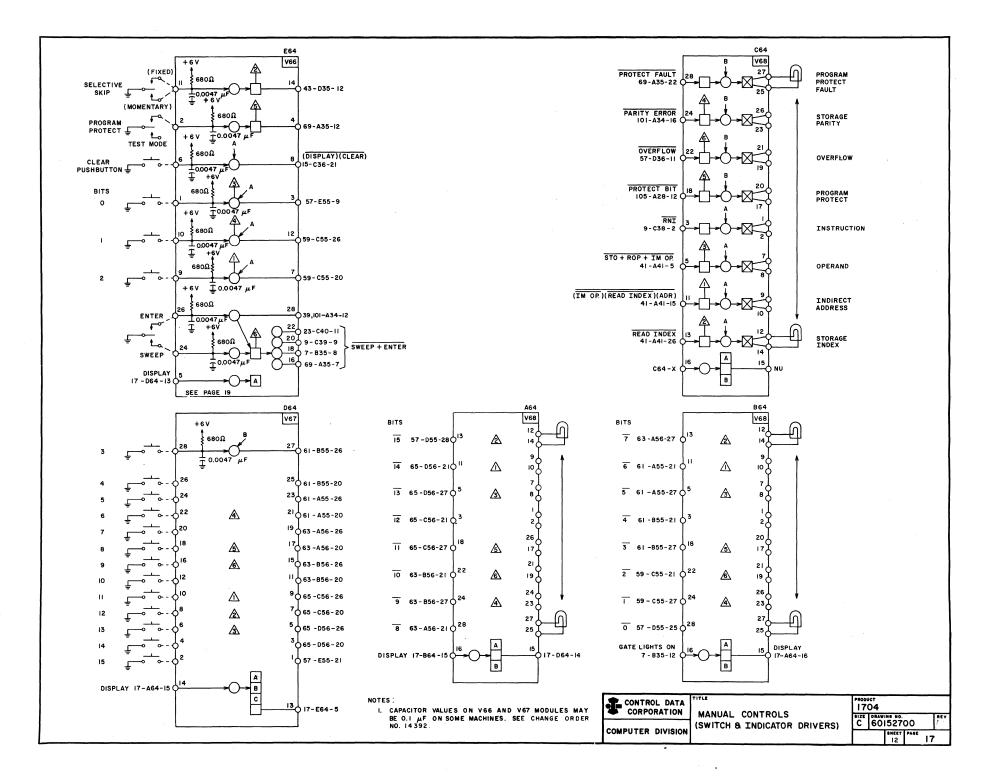

#### MANUAL CONTROLS (SWITCH AND INDICATOR DRIVERS)

The Selective Skip, Program Protect, and Enter/Sweep switches connect to the V66 module. The Selective Skip switch is a 3-position lever switch that is OFF in the center position; ON in the up and down position. The up position is fixed and the down position is momentary. The Selective Skip switch in the ON position conditions the Selective Skip instruction shown on page 43. Placing the Program Protect switch in the up position, conditions the Program Protect logic shown on page 69.

The Enter/Sweep switch is a 3-position lever switch which is fixed in all positions with the center position OFF. In the ENTER position, each step operation of the Run/Step switch stores the contents of the X register at the location specified by the P register and advances the P register by one. In the SWEEP position, each step operation of the Run/Step switch transfers the contents of the storage location whose address is in the P register into the X register and advances the P register by one, with the exception of the first step operation following a MC or Clear P function.

- Program Protect Fault This indicator will be lit when a violation of the program protect system has been detected.

- 2. Storage Parity This indicator will light anytime a parity error has been detected in data read from storage.

- 3. Overflow This indicator will light when arithmetic overflow has occurred.

- 4. Program Protect This indicator lights when the program protect bit of the last word read from storage is set.

- 5. Instruction The instruction indicator will be illuminated anytime RNI is set.

- Operand The operand indicator will be turned on when the following translation exists: STO+ROP+IM OP

- Indirect Address This indicator will be on when the following translation exists:

(Im Op) (Read Index) (ADR).

- Storage Index The index indicator will light anytime OOFF is referenced.

The 16 pushbuttons connected to the V66 and V67 modules control manual entry into a selected register. A set pushbutton ANDed with the Display condition sends a "0" to the Adder/Shifter. This puts a "1" into the corresponding bit position of the selected register. The indicators on the two V68 modules (locations A64 and B64) display the contents of the selected register (Display condition present). An enabled indicator represents "1" in that location.

When set, the Clear pushbutton attached to the V66 module clears the contents of the selected register. When a bit is manually set, it remains in that state until the Clear pushbutton is enabled.

A V68 module (location C64) controls the eight indicators (excluding TEMP) located on the left side of the 1700 console. Note that a "0" input enables the corresponding indicator.

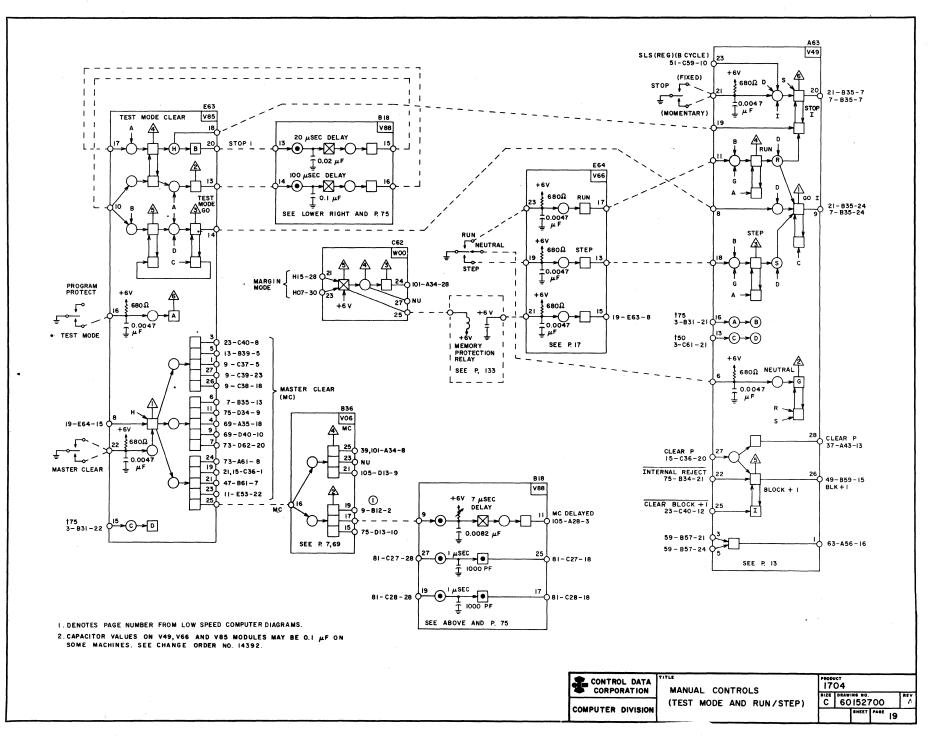

## MANUAL CONTROLS (TEST MODE AND RUN/STEP)

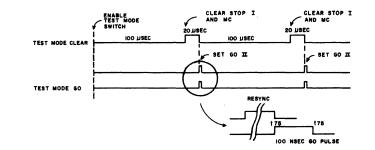

The Test Mode switch connects to module V85. Modules V85 and V88 contain the Test Mode logic. The computer executes the following sequence of events when the Test Mode switch is placed in the down position:

- 1) 100 usec delay before Test Mode is operational.

- 20 usec Master Clear. This clears the P register and all other operational registers.

- 3) 100 usec program run starting from P = 0000.

- 4) Return to step 2 and repeat.

The accompanying timing chart shows the setting and clearing of the three Test Mode FFs. The Test Mode Go FF enables a 100 usec Go pulse to the Go1 FF on module V49. The Go1 FF sets the Go2 FF 75 nsec later. The Go2 pulse starts the timing chain which runs for 100 usec or until a Program Stop is enabled. At the end of 100 usec the Test Mode Clear FF enables the Master Clear and the timing chain stops.

## MASTER CLEAR (MC)

The Master Clear switch connects to module V85. A Master Clear is executed when the switch is momentarily placed in the up or down position. The Master Clear disables the timing chain, clears all registers, and clears most Control FFs. Modules V85 and V06 contain Master Clear fan-outs.

Module V88 contains a delayed Master Clear for storage control. This allows the completion of the present storage reference and prevents unnecessary fault conditions from occurring.

## LOGIC VOLTAGE SENSOR

Module W00 is used to determine power failures by sensing the +6-volt logic bus. When the voltage drops below a preset value, the special circuit de-energizes relay K4 and protects memory. Another output of module W00 is used to generate interrupt 00 on power failure. Approximately 8 milliseconds of program execution time is available between relay coil de-energization and contact closure.

The logic voltage sensor can be disabled for voltage margin checking by turning the MARGIN MODE switch on (this switch is located on the memory power supply).

• • • •

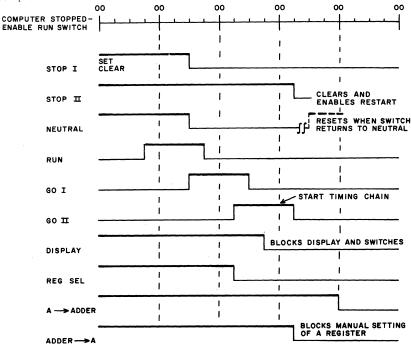

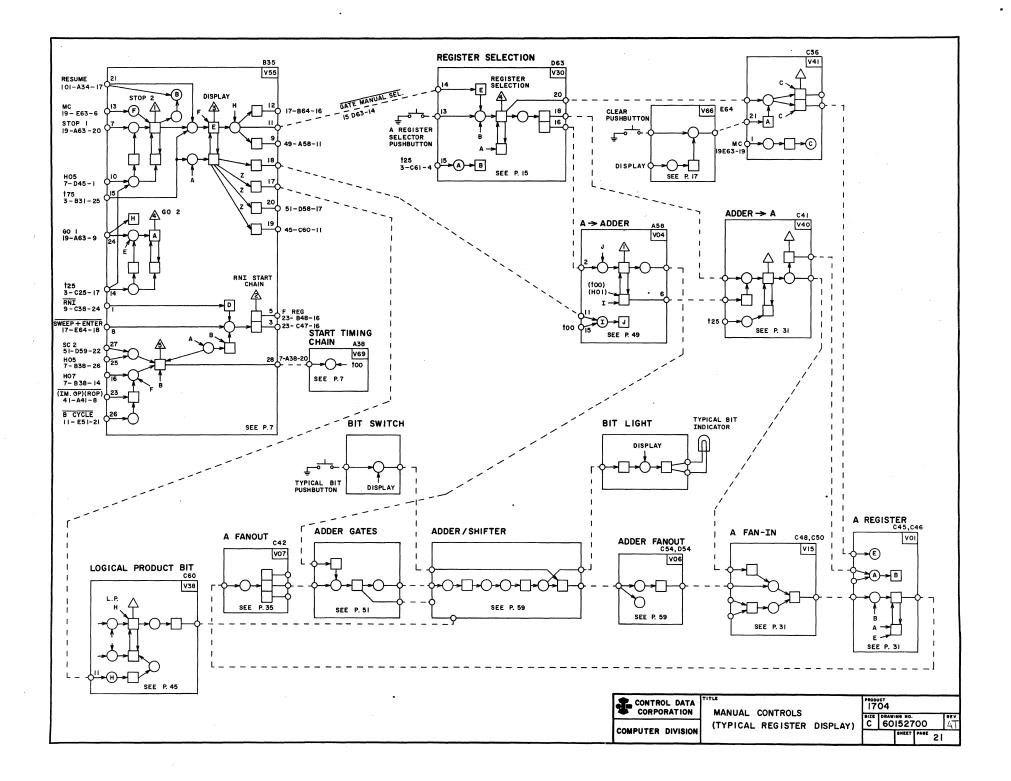

## TYPICAL REGISTER DISPLAY

The diagram below shows a typical register display sequence using the A register. For a starting reference, assume the following conditions:

- 1) Power on

- 2) A register selector button pressed

- 3) Timing chain stopped

- 4) Display FF set (enabling pushbuttons and display)

When the Run/Step switch is momentarily placed in the up position (RUN), the timing chain starts and the switches and display are disabled. The following timing chart shows the setting and clearing of Control FFs for starting the computer.

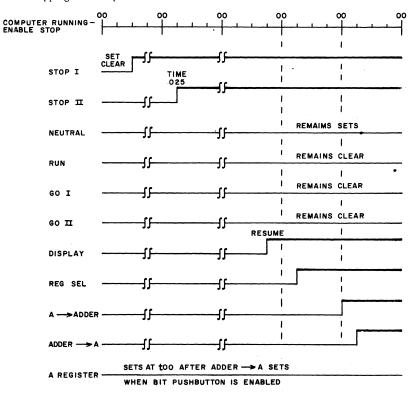

The timing chain is disabled and the display enabled when the Stop FFs set. The timing chain can not be restarted until the Run/Step switch is activated. The

individual bits of the A registers are manually set by the bit pushbuttons while the Display FF is set. Pressing a bit pushbutton enables the Adder/Shifter to set the corresponding bit in the A register and light the corresponding bit indicator. The raw clock pulses enable the setting of the A register, although the timing chain is stopped. The following timing chart shows the setting of Control FFs for stopping the computer.

Pressing the Clear pushbutton clears the A register if the Display FF is set. Other registers may be selected while the Display FF is set by pressing the corresponding register selector switch. For example, if the X register is selected, the Adder/Shifter samples the X register and the corresponding bit indicators light.

## TYPICAL REGISTER DISPLAY (Cont'd)

The computer is stopped momentarily by placing the Run/Step switch in the down position. If the switch is repeatedly placed in the down position, the computer steps through the program, stopping after each storage reference. The significance of the storage reference just made is indicated by the instruction sequence indicators.

This diagram shows a typical register display sequence (A register). The register selector switch must be set for the A register. With the Run-Step switch (page 19)

in the center position, the Neutral FF is set. When the switch is placed in the STEP position, the timing chain stops at the end of the current storage reference and the display is enabled. During the step sequence, the Go 2 FF remains cleared and the Stop 2 FF sets, thus disabling the timing chain at the end of the B cycle. The Display FF sets when Stop 2 is set and a Resume and 75 time are present. Each step pulse sets Go 1, Go 2, and moves the timing chain one storage reference. The chain is stopped by the 125 pulse clearing Go 2 before the next storage reference.

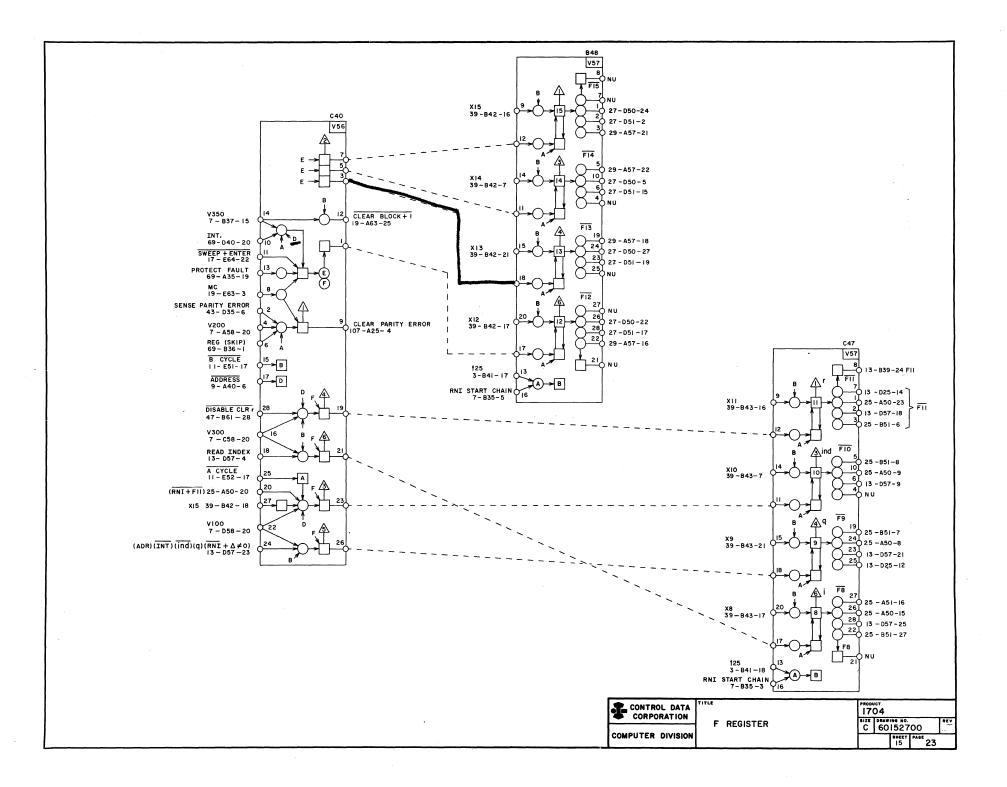

The 8-stage F register is divided into two 4-stage groups contained on two V57 modules. The low-order four stages (F8-F11) contain the  $f^1$  instruction designator bits. The high-order four stages (F12-F15) contain the f instruction designator bits. The stages of the F register are numbered 8-15 to coincide with the instruction bit positions that they contain. The outputs of the F register translate into the various function codes.

In storage reference instructions, the low-order stages of the F register contain the relative  $(\mathbf{r})$ , indirect (ind), Q register index (q), and storage index (i) designators as shown on the diagram. In this type of instruction, the designators control the addressing mode of instruction execution.

#### $X \rightarrow F$ CONTROL

At t25 time of each RNI sequence, inverter A forces a "0" input to B on the V57 modules. The outputs of A and B transfer the high-order eight bits in X to F. Thus, the f and  $f^1$  designator portions of the instruction are transferred at this time.

#### F REGISTER CLEAR CONTROL

The diagram shows the conditions under which both the f and  $f^1$  positions are cleared. The enabling of one of these conditions, e.g., Protect Fault, produces "0" outputs from inverters E and F on the V56 module. The resulting "1" outputs from the output inverters on this module clear the F register.

During the ADR mode of storage reference instructions, the r, ind, q, and i designators in the  $f^1$  portion are cleared individually. The following table

lists the conditions for clearing each of the designators.

| Designator | Conditions                                                                                         | Time |

|------------|----------------------------------------------------------------------------------------------------|------|

| r (F11)    | (ADR) (B cycle) (Disable Clr r)                                                                    | V300 |

| ind (F10)  | (ADR) $(A cycle)$ $(X15)$ $(RNI)$ $(F11)$                                                          | V100 |

| q (F9)     | (ADR) ( $\overline{INT}$ ) ( $\overline{ind}$ ) (q) ( $\overline{RNI} + \Delta \neq 0$ ) (B cycle) | V100 |

| i (F8)     | (Read Index) (B cycle)                                                                             | V300 |

Timing pulse V300 clears the r designator during the B cycle of the ADR mode if condition (Disable Clr r) is present. At this time, all relative addressing is complete. If r was not initially set, the operation becomes irrelevant.

The above table shows that the clearing of ind during the A cycle of ADR following the reading of the indirect address  $(\overline{RNI})$  (F11) depends on the state of bit 15 contained in the X register. If this bit is a "1" indicating that the address corresponds to another indirect address, V100 does not clear ind. If this bit is a "0", indirect addressing is complete and ind is cleared.

The V100 pulse clears q during the ADR mode on a  $\overline{\text{INT}}$  condition. If indirect or relative or both Addressing modes were initially specified, these operations are completed first. The condition for clearing q specifies that q must be initially set.

The V300 pulse clears i during the B cycle on a Read Index operation. The condition for clearing i need not specify the ADR mode since a Read Index can occur only during this mode. The adding of the i index always takes place last if any other addressing mode designators were initially set.

# FUNCTION TRANSLATORS

The Function Translators translate the contents of the F register to obtain the current instruction. The 1700 repertoire of instructions may be grouped into Storage Reference instructions (F portion) and Register Reference instructions ( $F^1$  portion). In the table of instructions on page 26, the Storage Reference instructions are in column one (beginning with JMP) and the Register Reference instructions are in column three (beginning with SLS).

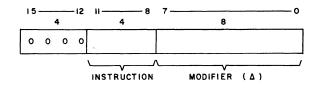

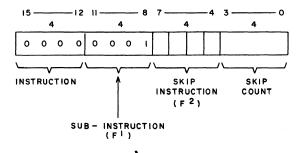

Register Reference instructions are identified when the upper 4 bits (15-12) of the instruction are all "0's". The format of Register Reference is diagrammed below:

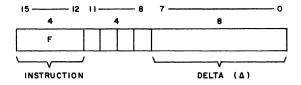

Storage Reference instructions have their instruction code in bits 15-12, and bits 11-08 become the address mode. Storage Reference . instruction format is diagrammed below:

The static logic of the Function Translator translates the 16-bit input to the selected instruction. The logic searches through the input until it recognizes a unique instruction. The Function Translator dispenses the signals that enable the selected instruction and its associated logic.

# FUNCTION TRANSLATIONS