**Technical Reference Manual**

# Wide SCSI Host Adapters for PCI and EISA Systems

## **Revision History**

| Revision | Change Activity | t.e. | Date    |

|----------|-----------------|------|---------|

| A        | Release         |      | 12/9/94 |

# Copyright

© Copyright 1994 BusLogic Inc. All rights reserved.

BusLogic Inc. makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. BusLogic is not liable for any errors contained herein or incidental or consequential damages in connection with furnishing, performance or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without prior written consent of BusLogic Inc.

## Trademarks

Company and product names are trademarks or registered trademarks of their respective companies.

# **Table of Contents**

Preface

Part 1 Adapter Operation

Part 2

PCI Host Adapters

Part 3

EISA Host Adapters

Index

# Preface

The BusLogic Wide SCSI Host Adapter Technical Reference Manual is intended for system software programmers desiring to develop device driver software for Bus-Logic's family of SCSI adapter products.

This manual covers adapter architecture, hardware and software operation and includes electrical signaling information for each bus architecture.

Products covered in this document include:

- BT-956C PCI Wide SCSI Host Adapter (20 MBytes/sec synchronous data transfer rate)

- BT-956CD Differential PCI Wide SCSI Host Adapter

- BT-757C EISA Wide SCSI Host Adapter (20 MBytes/sec synchronous data transfer rate)

- BT-757CD Differential EISA Wide SCSI Host Adapter

# Contents

This manual is organized in the following manner:

#### **Part 1: Adapter Operation**

- Section 1 contains an overview to BusLogic's MultiMaster<sup>™</sup> technology.

- Section 2 details adapter hardware components and operation.

- Section 3 discusses software operation between the host adapter and the host system.

- Section 4 describes the adapter's SCSI electrical interface.

- Section 5 describes the adapter's floppy controller interface.

- Section 6 details adapter internal diagnostics.

- Appendix A is a list of industry acronyms.

#### **Part 2: PCI Host Adapters**

- Section 1 includes descriptions and specifications for the BT-956X host adapters.

- Section 2 describes the electrical interface for PCI host adapters.

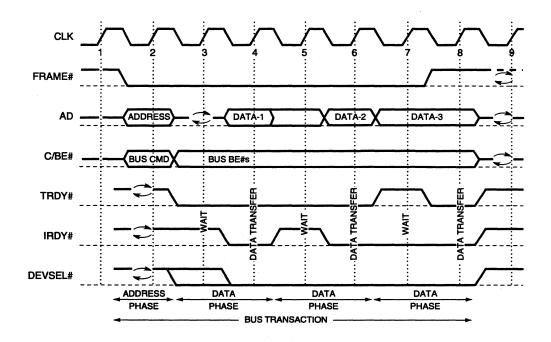

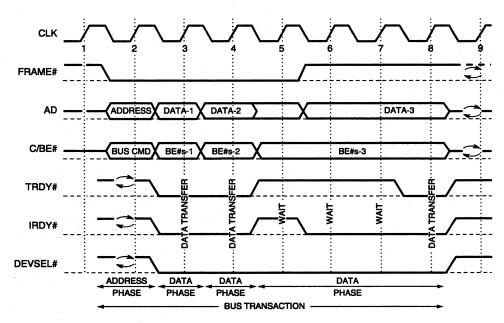

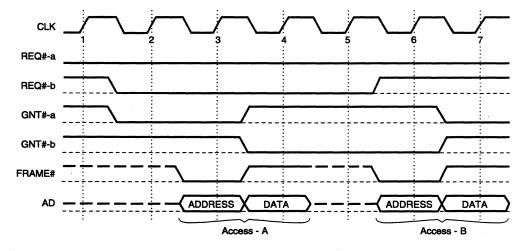

- Section 3 contains the PCI bus timing diagrams.

- Section 4 details the configuration for non-conforming PCI motherboards.

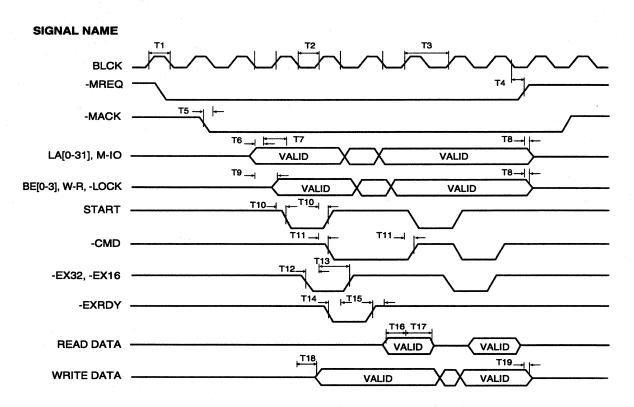

#### **Part 3: EISA Host Adapters**

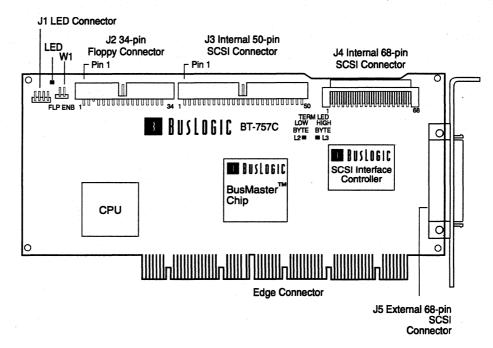

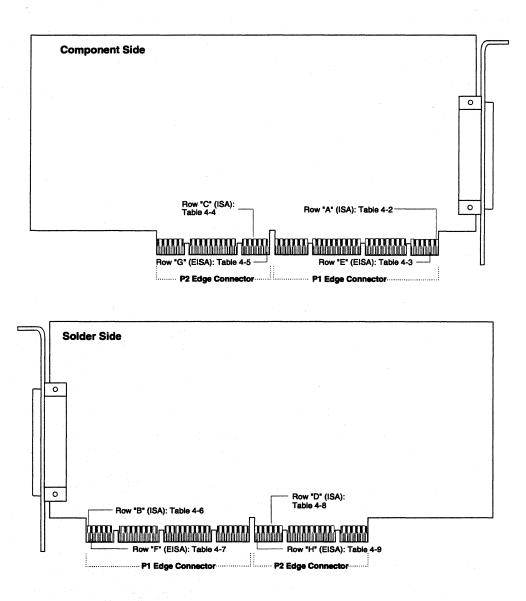

- Section 1 includes descriptions and specifications for the BT-757X host adapters.

- Section 2 describes the electrical interface for EISA host adapters.

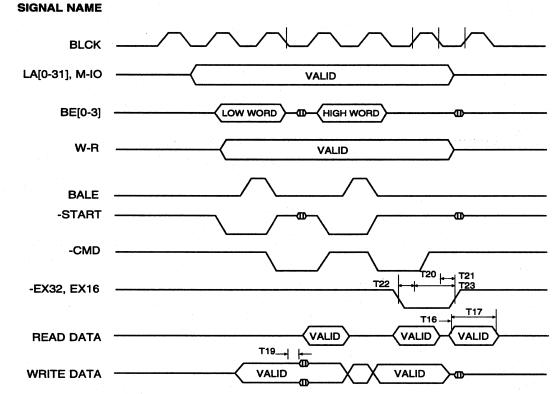

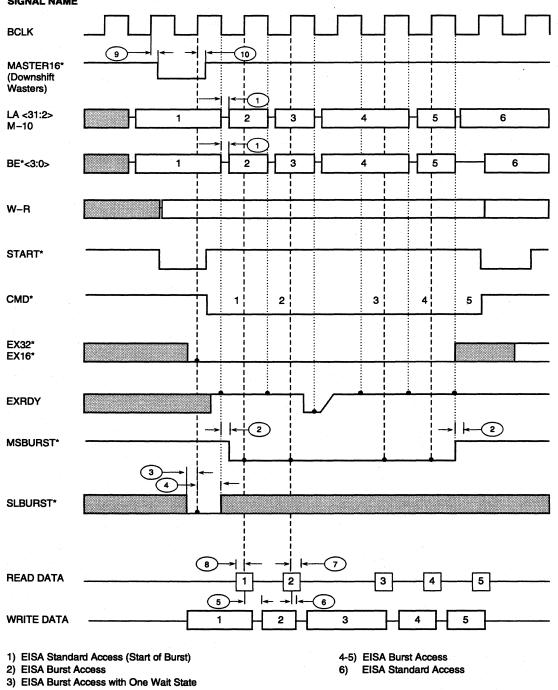

- Section 3 contains the EISA bus master timing diagrams.

# **Related Documentation**

Refer to the user's guide provided with your BusLogic host adapter for details on host adapter installation and configuration.

# **Notational Conventions**

The following conventions are used throughout this manual:

| Convention | Description                                  |  |

|------------|----------------------------------------------|--|

| UPPERCASE  | Used to indicate the names of keys.          |  |

| -          | A hyphen indicates an active low signal.     |  |

| +          | A plus sign indicates an active high signal. |  |

# PART I Adapter Operation

# Part 1: Contents

## Section 1•1: BusLogic MultiMastering Technology

| Introduction           | 1-1 |

|------------------------|-----|

| Bus Mastering DMA      | 1-1 |

| Description            |     |

| Configuration          |     |

| Bus Master Transfers   |     |

| MultiMaster Advantages |     |

## Section 1-2: Hardware Description

| Adapter Architecture                                     | 1-7          |

|----------------------------------------------------------|--------------|

| Bus Master DMA Controller                                | 1-8          |

| Advanced SCSI Controller                                 |              |

| Microprocessor Unit (MPU)                                |              |

| Local BIOS ROM                                           |              |

| Floppy Disk Controller                                   | 1 <b>-</b> 9 |

| Host DMA Data Transfer Control                           | 1-9          |

| EISA                                                     | 1-9          |

| PCI                                                      |              |

| Hardware Registers                                       | 1-10         |

| Control Register (Write Only) I/O Base Address + 0       | 1-10         |

| Status Register (Read Only) I/O Base Address + 0         | 1-11         |

| Command/Parameter Register (Write Only) I/O Base Address | + 1 1-13     |

| Data In Register (Read Only) I/O Base Address + 1        | 1-13         |

| Interrupt Register (Read Only) I/O Base Address + 2      | 1-14         |

| Reset Operations                                         | 1-16         |

| Host-Initiated Reset Operations                          | 1-17         |

| SCSI Bus Reset Operations                                | 1-17         |

|                                                          |              |

## Section 1-3: Software Interface

| Bus Master Direct Memory Access (DMA)     | 1-20 |

|-------------------------------------------|------|

| Interrupt Processing                      | 1-20 |

| Host Adapter Commands                     | 1-21 |

| Addressing Mode                           | 1-30 |

| 24-Bit Mode Mailbox Commands              | 1-30 |

| 24-Bit Mode Mailbox Initialization        | 1-31 |

| 24-Bit Mode Outgoing Mailbox Structure    | 1-32 |

| 24-Bit Mode Incoming Mailbox Structure    | 1-33 |

| Host Adapter as Initiator on the SCSI Bus | 1-33 |

| 24-Bit Mode CCB Structure                 | 1-36 |

| 32-Bit Mode Mailbox Structure             | 1-40 |

| 32-Bit Mode CCB Structure                 | 1-41 |

| 32-Bit Mode CCB Description               | 1-42 |

| Wide SCSI Mode CCB Description            |      |

| Scatter-Gather Operations                 |      |

| Scatter-Gather Operation for 32-Bit Mode  |      |

| 32- Bit Mode Command Queueing             |      |

| <b>0</b>                                  |      |

| Implementation Requirements        |  |

|------------------------------------|--|

| Project Relationship               |  |

| BIOS Command Interface             |  |

| BIOS Commands and Input Parameters |  |

| BIOS Command Completion Status     |  |

| BIOS Disk Commands                 |  |

## Section 1-4: SCSI Electrical Interface

| SCSI Signal Interface for the 50-Pin Connector  | 1-62 |

|-------------------------------------------------|------|

| SCSI Signal Interface for the 68-Pin Connectors |      |

| SCSI Signal Definitions                         |      |

| <b>0</b>                                        |      |

## Section 1•5: Floppy Drive Pin Assignments

## Section 1•6: Internal Diagnostics

## Section 1•A: List of Acronyms

# **List of Figures**

## Section 1•1: BusLogic MultiMastering Technology

## Section 1-2: Hardware Description

| Figure 1-2. System Architecture                | 1-7  |

|------------------------------------------------|------|

| Figure 1-3. Host Adapter Architecture          | 1-8  |

| Figure 1-4. Control Register (Write)           | 1-10 |

| Figure 1-5. Status Register (Read)             | 1-11 |

| Figure 1-6. Command/Parameter Register (Write) | 1-13 |

| Figure 1-7. Data In Register (Read)            |      |

| Figure 1-8. Interrupt Register (Read Only)     |      |

### Section 1-3: Software Interface

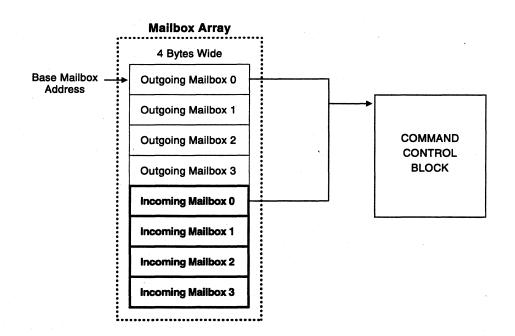

| Figure 1-9. Mailbox Array                                    | 1-32 |

|--------------------------------------------------------------|------|

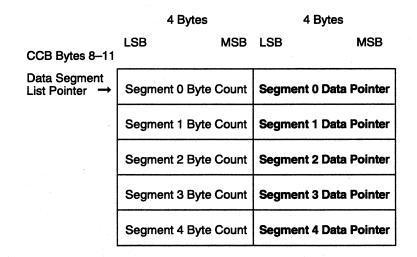

| Figure 1-10. Scatter-Gather Data Segment List-CCB Bytes 7-9  |      |

| Figure 1-11. Scatter-Gather Data Segment List-CCB Bytes 8-11 | 1-48 |

## Section 1•4: SCSI Electrical Interface

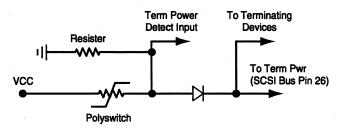

| Figure 1-12. | Terminator Power Schematic | . 1-60 |

|--------------|----------------------------|--------|

|              |                            |        |

# **List of Tables**

## Section 1•2: Hardware Description

| Table 1-1. Host Ada | pter Hardware Register | s1-10 |

|---------------------|------------------------|-------|

|                     |                        |       |

## Section 1•3: Software Interface

| Table 1-2. Host Adapter Commands                  |  |

|---------------------------------------------------|--|

| Table 1-3. 24-Bit Mode CCB Structure              |  |

| Table 1-4. 24-Bit Mode CCB Field Definitions      |  |

| Table 1-5. 32-Bit Mode CCB Structure              |  |

| Table 1-6. 32-Bit Mode CCB Field Definitions      |  |

| Table 1-7. Wide SCSI Mode CCB Field Definitions   |  |

| Table 1-8. Valid Host Adapter BIOS Disk Functions |  |

| Table 1-9. Valid BIOS Disk Functions              |  |

### Section 1-4: SCSI Electrical Interface

| Table 1-10. Termination Options                                       | 1-61 |

|-----------------------------------------------------------------------|------|

| Table 1-11. Single-Ended SCSI Interface Signal Pin Assignments        | 1-62 |

| Table 1-12. 50-Pin Differential SCSI Interface Signal Pin Assignments | 1-63 |

| Table 1-13. Single-Ended 68-Pin SCSI Interface Signal Pin Assignments | 1-64 |

| Table 1-14. 68-Pin Differential SCSI Interface Signal Pin Assignments | 1-65 |

| Table 1-15. SCSI Interface Signal Descriptions                        | 1-66 |

## Section 1•5: Floppy Drive Pin Assignments

| Table 1-16. Floppy | <sup>v</sup> Disk Controller Pin | Assignments |  |

|--------------------|----------------------------------|-------------|--|

|                    |                                  |             |  |

# **BusLogic MultiMastering Technology**

# Introduction

Bus mastering data transfers are commonly used by intelligent I/O controllers to increase system performance by off-loading the low level control tasks to a dedicated micro-controller. BusLogic has created a unique technology for implementing a diverse family of high performance bus mastering SCSI host adapters while maintaining a high degree of compatibility among them. This technology is called MultiMaster<sup>™</sup> and is implemented in a single ASIC. The MultiMaster technology is utilized on all BusLogic bus mastering adapters allowing them to share common device drivers, firmware and BIOS. The following describes the key features, capabilities and benefits of BusLogic MultiMaster technology.

# **Bus Mastering DMA**

Bus mastering DMA is a form of information transfer between two devices. The advantages of bus mastering in a PC environment are that it requires less host CPU time and offers high performance data transfers. An intelligent bus master device will use a micro-controller or micro-processor to perform complex I/O operations that would otherwise require interaction from the host system CPU. BusLogic intelligent SCSI controllers utilize a 16-bit micro-controller to off-load control of information transfers, thus freeing the system CPU for other tasks and increasing overall system performance as well as I/O performance.

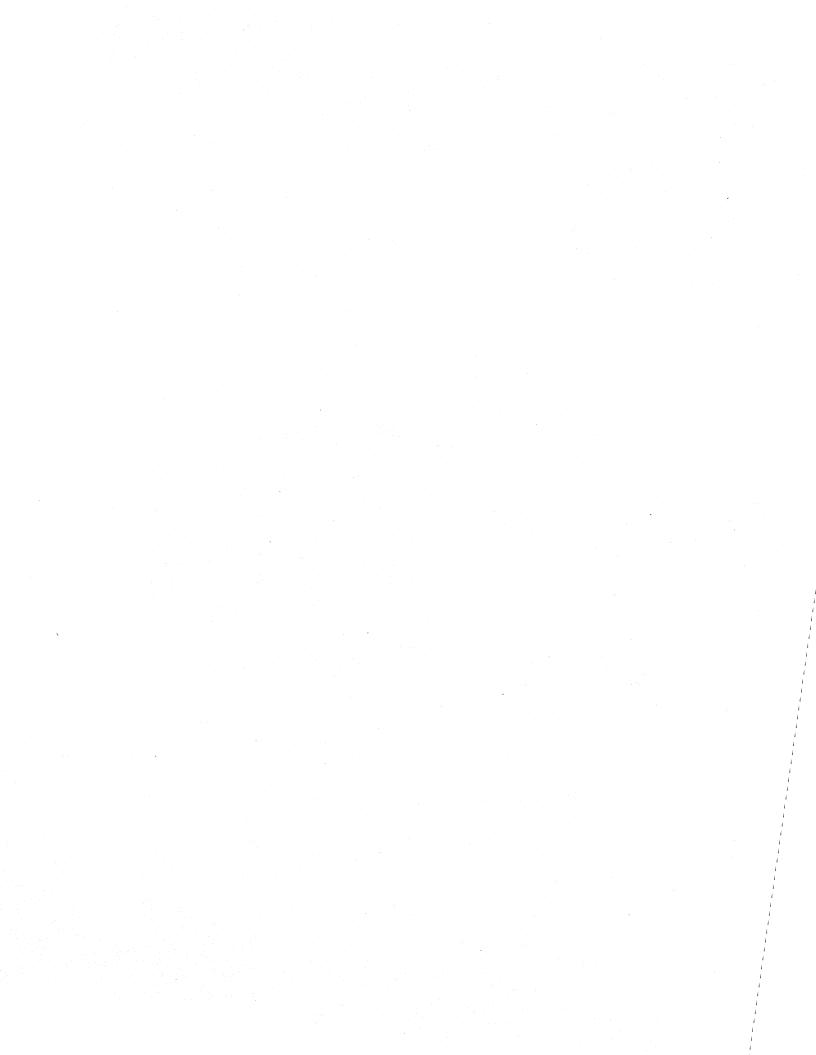

BusLogic's MultiMaster technology allows the use of a single ASIC as the interface to all of our bus mastering adapters. The MultiMaster ASIC contains all the logic required to fully automate a bus master transfer on five different system buses, ISA, EISA (EMB), VL-Bus, PCI and MCA. This technology enables a common high performance microprocessor-based architecture to be applied to many system platforms. It allows the use of a single device driver per operating system to support all BusLogic bus mastering SCSI controllers.

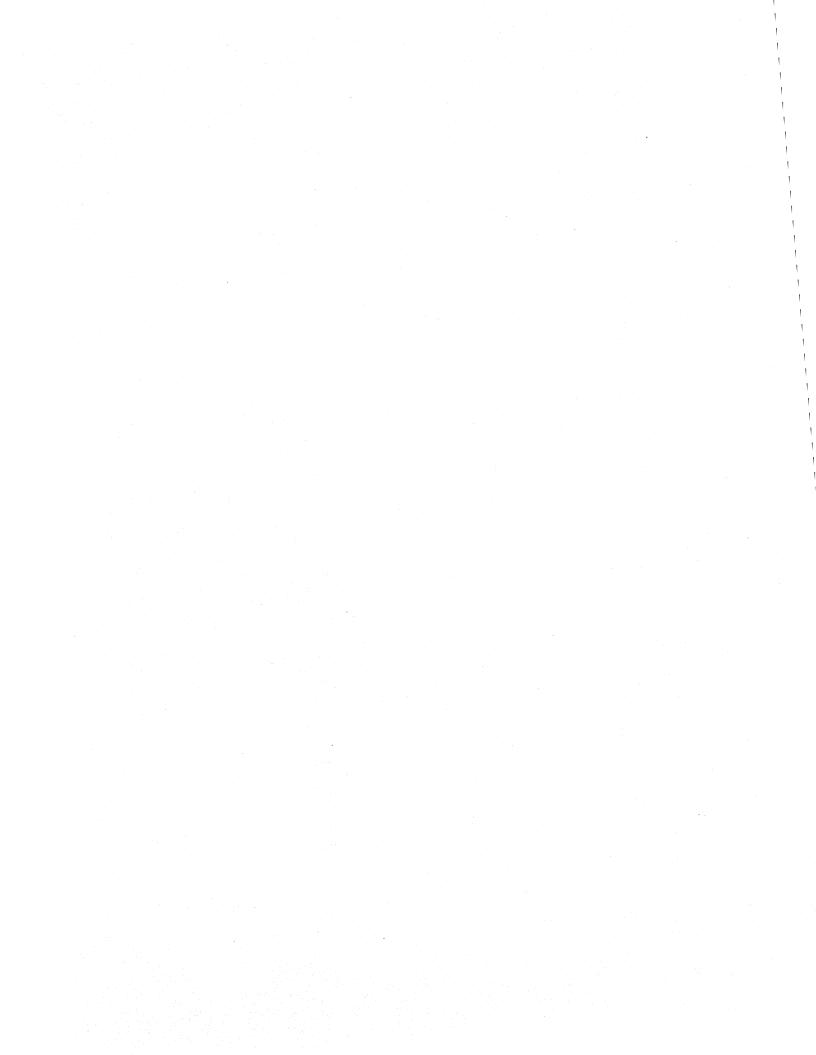

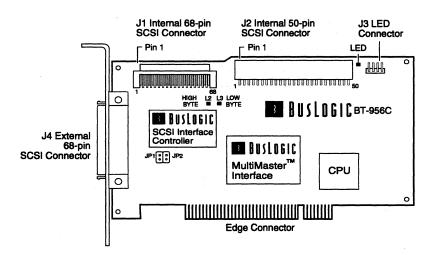

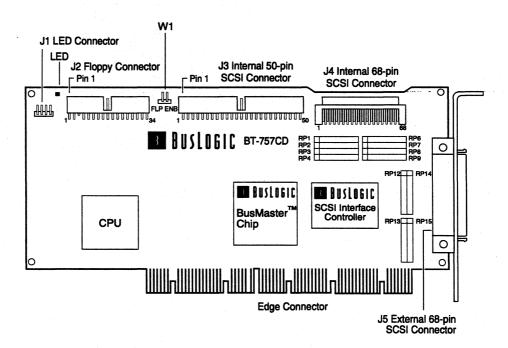

Figure 1-1. Typical MultiMaster SCSI Adapter

MultiMaster provides a complete register and interrupt interface between the host system and the host adapter microcontroller. SCSI command overhead is reduced by reading and updating mailboxes in host memory without intervention by the host adapter microcontroller. Data transfers between the SCSI controller and host system memory are under complete control of the MultiMaster ASIC, from system bus arbitration to the completion of data transfer.

#### Configuration

The MultiMaster ASIC is configured to interface with a particular system bus by hard wiring three mode select pins. Each host adapter has these pins tied to logic levels representing the host bus the adapter interfaces with. The ASIC contains the bus interface protocols required for each supported system bus. By embedding all the bus specific protocols in the MultiMaster ASIC the microcontroller and firmware design issues become independent of the target host platform.

Registers within the MultiMaster ASIC are configured at power-up to determine host adapter operating parameters.

In an MCA system the MultiMaster ASIC monitors the CDSETUP and address signals to allow the configuration registers to be read and written by the host system. CDSETUP is unique for each slot on the MCA bus allowing MCA adapter cards to use the same set of I/O addresses for configuration registers and avoid bus contention problems. During power-on initialization the host system BIOS reads an adapter ID from the MultiMaster configuration registers. The ID field is used to look up a set of operating parameters previously stored in the system CMOS memory. If no match is found for the ID field the system will invoke a configuration program allowing the operating parameters for this adapter card to be defined and stored for future power on initializations.

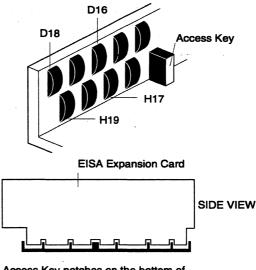

EISA compatible adapter cards use I/O addresses 0zC80h - 0zC84h for configuration purposes. The EISA motherboard generates I/O cycles to these addresses on a per slot basis by only activating the AENz (z represents slot number) signal for the desired slot. This allows each EISA compatible add-in card to decode the same register address range for configuration purposes. Software running on the system sees each card's I/O register at unique addresses.

PCI is very different from MCA or EISA during power-on initialization. The PCI system BIOS will scan the system bus and assign I/O port address, BIOS memory address and interrupt level dynamically each time the system is powered up. This fully automatic initialization is also supported by the BusLogic MultiMaster ASIC.

In an environment such as the ISA and VL-Bus, boot time configuration is not performed by the host system. In these environments the host adapter microcontroller will configure the MultiMaster based on information read from switches or stored in EEPROM (BusLogic Model C boards only).

The MultiMaster ASIC maintains a high level of isolation between the host environment and adapter firmware, allowing a common architecture to be applied to all BusLogic bus mastering SCSI host adapters.

#### **Bus Master Transfers**

There are three basic phases of a bus master transfer: arbitration, where the bus master requests and gains access to the system bus; data transfer, in which the bus master has control of the bus and is actively transferring data across the bus. Data transfer is followed by bus release once all available data has been transferred or bus release is being forced to allow another device access or a system memory refresh cycle. Although signals and timing vary from one bus type to another, our MultiMaster technology fully automates the data transfer process.

#### Arbitration

Once a DMA transfer has been programmed into the MultiMaster by the local microprocessor, the resulting bus master transfer is completely automated by the MultiMaster ASIC. Bus arbitration is initiated by asserting the DMA request or bus request signal appropriate to the particular environment the MultiMaster is residing in. The host system then responds with an acknowledge signal granting access to the system bus. The MultiMaster then asserts a host bus signal to indicate it will be acting as a bus master. The host adapter is now the active bus master and has complete control over the system bus. In an ISA system the MultiMaster arbitrates for the system bus by asserting the DMA request line and waiting for a DMA acknowledge.

#### Data Transfer

Data transfer begins after the host system has granted the host adapter access to the system bus. The MASTER signal is then asserted by the MultiMaster to inform the host system it is acting as a bus master device. The host adapter is now the active bus master and controls the system address, memory read and memory write signals to perform the current data transfer. This continues until one of three things happens: (1) the data transfer is complete, (2) the host adapter is unable to continue transferring due to an empty or full FIFO buffer or (3) the host system requires the bus to be released.

#### **Bus Release**

During the bus release phase the MultiMaster will relinquish control of the system bus through the appropriate protocol for the currently supported host bus. For example in an ISA system the MASTER signal is released and the address and data lines are tri-stated. DMA request is then released and the host system de-asserts the DMA acknowledge signal.

#### Preempt

The MultiMaster will release the host system bus when preempted. Most advanced system bus architectures have provisions for preemption of the current bus master. This allows other bus masters to share the system bus. This also is required to allow the host system to perform system memory refresh cycles. The ISA bus does not have a provision for preemption of a bus master. When configured for ISA bus operation the MultiMaster utilizes two timers to control the bus on and bus off times to control the amount of time the MultiMaster can remain as bus master of the system. The bus off time controls the amount of time the MultiMaster must release the system bus before arbitrating to become bus master again. This allows the system to periodically perform refresh cycles to the system memory and allows access to the system bus by other bus masters.

#### MultiMaster Advantages

MultiMaster technology offers several key advantages: performance, reliability and efficient product design cycles.

#### Performance

MultiMaster enhances the performance of BusLogic bus mastering SCSI products in several ways. The MultiMaster ASIC automatically retrieves mailbox entries and associated commands from the host system memory in a single operation. This greatly reduces the command overhead associated with maintaining the mailbox interface. Scatter/gather operations are streamlined under control of the MultiMaster. The microcontroller is able to pre-initialize the next segment of a scatter/ gather transfer while the current segment is being transferred. This maintains the continuous flow of data during scatter/gather operations.

All BusLogic SCSI bus mastering host adapters utilize the same mailbox structure interface. This mailbox interface allows the host system to perform multitasking I/O operations with minimum overhead. Mailboxes are located in system memory. The mailbox structure allows up to 255 independent I/O commands to be processed by the SCSI adapter simultaneously. The MultiMaster will automatically scan the mailboxes for a valid entry. Once a valid entry is found the MultiMaster will automatically read the mailbox and store the associated CCB (Command Control Block) in the host adapter local RAM and clears the mailbox semaphore. The advanced features of BusLogic MultiMaster ASIC coupled with a 16-bit microcontroller resident on all BusLogic bus mastering SCSI adapters provides high performance and reliability.

BusLogic bus mastering host adapters are able to perform an entire I/O operation without intervention from the host CPU. By automating the data transfer between the system memory and utilizing a dedicated microcontroller to handle the high level control of the operation, BusLogic host adapters deliver superior performance over PIO types of interface cards.

All of these features combine to deliver the user the best possible I/O performance. The MultiMaster ASIC allows this high performance architecture to be implemented on five different host system buses without any significant design changes.

#### **Common OS Drivers/BIOS/Firmware**

The MultiMaster ASIC separates the SCSI, interface microcontroller, and firmware from the system bus allowing one design to be applied to all system platforms.

MultiMaster's common system interface allows a single device driver per operating system to support BusLogic's host adapters. Only one device driver needs to be tested, qualified and embedded into the operating system kernel to support all the BusLogic bus mastering adapters. All BusLogic bus mastering SCSI adapters are also supported by common BIOS source code.

MultiMaster provides the isolation from the host system required for a common architecture to be applied to many system platforms. This common architecture allows the use of common firmware across the entire bus mastering host adapter product line.

1-6 Part 1: Adapter Operation

# **Hardware Description**

BusLogic host adapters are based on a BusLogic-designed, MultiMaster ASIC technology, offering high-performance interconnection between the bus architecture and Small Computer System Interface (SCSI) peripheral devices. A BusLogic-designed bus master controller ASIC, an advanced SCSI controller chip and a 16-bit microprocessor chip provide higher speed, lower power consumption, fewer parts and higher reliability.

The 50-pin internal and 68-pin internal and external connectors are included on the board for flexibility in attaching SCSI devices to the system.

This section describes the adapter's functional hardware operation. It covers the hardware control registers that are mapped into the system's I/O address space. It also describes command use, data flow and hardware management.

# Adapter Architecture

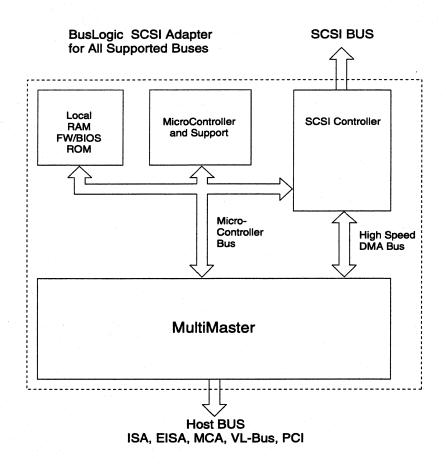

The host adapter plugs into a host system and supports the attachment of internal SCSI drives or the connection to external SCSI peripheral devices in add-on enclosures. The system architecture is illustrated in Figure 1-2.

Figure 1-2. System Architecture

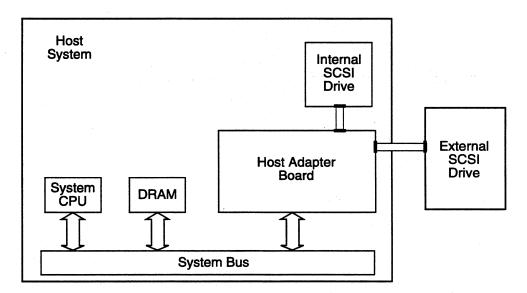

Figure 1-3 is a functional block diagram of the BusLogic adapter. The paragraphs that follow describe the numbered components in the figure.

#### Notes:

1. Not all models have a floppy connector.

2. Depending on the model, hardware configuration may be done via a switch or jumpers.

#### Figure 1-3. Host Adapter Architecture

#### **Bus Master DMA Controller**

All host bus interface logic is provided on the board by a BusLogic designed bus master ASIC ①. This chip provides bus master capabilities which greatly reduce the involvement of the host system's CPU in I/O control and data transfer activities. Under control of this chip, 32-bit bus master transfers at up to 132 MBytes/sec to and from the main system memory are possible with the use of its internal 128-byte FIFO. A true multitasking mailbox structure supports up to 255 tasks. This performance and improved bus utilization significantly enhances multitasking and multi-user applications.

#### Advanced SCSI Controller

On-board control of the interface to SCSI peripheral devices is provided by another ASIC, the BusLogic SCSI controller chip **9**. Up to 20 MBytes/sec synchronous and 14 MBytes/sec asynchronous 16-bit SCSI data transfers are supported by the SCSI interface controller. This low-power, high-performance CMOS component completely conforms to the ANSI standard, X3.131-1986 for the Small Computer System Interface. The chip reduces protocol overhead by performing common SCSI algorithms or sequences in response to a single host system command.

#### Microprocessor Unit (MPU)

An on-board, 16-bit Intel-based 8018X microprocessor unit (MPU) **③** coordinates all activity on the host adapter under the direction of the board's local ROM. Consequently, the on-board MPU orchestrates such activities as the initialization, command decoding, interrupt generation and the control of the data flow among the board's components.

#### Local BIOS ROM

The host adapter can be used in place of or in conjunction with a standard hard disk controller. The host adapter's on-board local BIOS **①** provides a compatible method of attaching a SCSI hard drive to a system just as any other type of hard disk is connected. The host adapter's BIOS intercepts each host software interrupt that requests a disk I/O service and manages these interrupts according to the address of the requested drive. If the designated drive is a disk assigned to the system's internal disk controller, the host adapter's BIOS passes the command on to that disk controller. If the designated disk is one of the SCSI disks attached to the host adapter, the host adapter's BIOS responds to the request and instructs the host adapter to execute the command.

#### Floppy Disk Controller

On models with a floppy controller, a floppy disk controller chip **6** provides support for any combination of up to two 3.5" and 5.25" floppy disk drives with 250 KBits/sec, 300 KBits/sec, 500 KBits/sec, and 1 MBits/sec data transfer rates. This floppy controller circuitry is completely independent from the SCSI logic and is accessed by the system BIOS floppy diskette routines.

# Host DMA Data Transfer Control

#### **EISA**

A typical EISA system provides up to six EISA bus master (-MREQx) slots. Each EISA slot is also ISA compatible and provides hardware pins to connect to the ISA DMA channel. Because EISA bus master transfers are faster and more efficient than ISA DMA transfers the EISA host adapter assumes the role of a 32-bit EISA bus master for all host data transfers.

#### PCI

The DMA control logic manages bus arbitration and data transfer coordination. The BT-956X operates as a PCI bus master during data transfers. The BT-956X arbitrates for PCI bus access and, once granted, it takes over control of the bus. It generates the PCI bus address and command strobes. The BT-956X supports both odd and even starting addresses, commonly known as aligned and unaligned transfers. If presented with an even transfer count beginning at an odd memory starting address, the BT-956X will first transfer a single byte (data bits D24-D31). The remaining data is then transferred as double words (32 bits) until the last byte, which is transferred as a single byte (data bits D0-D7). While odd byte transfers are fully supported, it is recommended that when possible, PCI host buffers be double-word aligned to gain better data transfer performance.

# **Hardware Registers**

The host adapter's I/O interface consists of three hardware registers that are used by the host to issue start commands to the host adapter, to gain status information about the adapter's operation, and to manage interrupts generated by the host adapter. These registers are located in the I/O address space at three consecutive addresses. The beginning or base address is determined by the I/O base address switch settings described in the host adapter user's guide. Table 1-1 provides a summary of these 8-bit wide registers.

| Address              | Туре | Description                |  |

|----------------------|------|----------------------------|--|

| I/O Base Address + 0 | W    | Control Register           |  |

| I/O Base Address + 0 | R    | Status Register            |  |

| I/O Base Address + 1 | W    | Command/Parameter Register |  |

| I/O Base Address + 1 | R    | R Data In Register         |  |

| I/O Base Address + 2 | R    | Interrupt Register         |  |

#### **Table 1-1. Host Adapter Hardware Registers**

#### Control Register (Write Only) I/O Base Address + 0

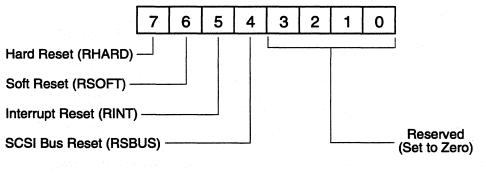

#### Figure 1-4. Control Register (Write)

The host system's CPU uses this register to specify programmable options within the host adapter (e.g., soft reset, hard reset, SCSI bus reset). For example, the host system's CPU can stop all host adapter activity immediately by setting this register's Bit 6, the Soft Reset bit (RSOFT). This is a write-only register.

Bits 0-3-These bits are reserved and must be set to zero.

**Bit 4 Reset SCSI Bus (RSBUS)**—When this bit is set to a one, the Reset signal on the SCSI bus is maintained true for at least 25 microseconds. This Reset condition immediately clears all SCSI devices from the bus. The assertion of the SCSI Reset condition supersedes all other activity on the SCSI bus. See the heading "Reset Operations" later in this section for additional details on the Reset operation.

**Bit 5 Reset Interrupt (RINT)**—The system's CPU sets this bit to acknowledge a host adapter interrupt. When this bit is set to one by the CPU, the host adapter's hardware-generated interrupt is reset and the Interrupt Register is cleared. Note that all bits in the Interrupt Register are cleared by setting this bit.

**Bit 6 Soft Reset (RSOFT)**—When this bit is set to one, it causes all host adapter activity to stop immediately. All mailboxes, command control blocks, and any pending commands are discarded by the host adapter. Previous mailbox pointers must be cleared by host processes. The primary difference between a hard and soft reset is that this bit does not effect a SCSI Bus Reset condition. Once the soft reset activity has been completed by the host adapter, the host adapter must be reinitialized for any future operation. This state is indicated by the setting of the Host Adapter Ready bit (HARDY) and the Initialization Required bit (INREQ) in the Status Register.

**Bit 7 Hard Reset (RHARD)**–The setting of this bit causes the host adapter to enter an initial condition power-on state. Any command in process is stopped and pending commands are abandoned. The host adapter will execute its internal diagnostic function and report any errors. During reset, the Diagnostic Active bit (DACT) is set. Once the hard reset activity has been completed by the host adapter, the host adapter must be reinitialized for any future operation. This state is indicated by the setting of the Host Adapter Ready bit (HARDY) and the Initialization Required bit (INREQ) in the Status Register.

Specific operation bits in the Control Register are automatically reset by the host adapter when the specific operation is completed. The host-controlling software is not required to reset the operational control bit for a specific function.

#### Status Register (Read Only) I/O Base Address + 0

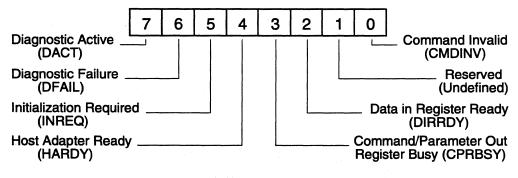

Figure 1-5. Status Register (Read)

The host adapter uses this register to report the status of its condition to the system's CPU. For example, the host adapter sets this register's Data In Register Ready bit (DIRRDY) when it has written data to its Data In Register. By setting this bit, the host adapter notifies the host system's CPU that there is fresh data in the Data In Register that should be read. As soon as the host system's CPU reads the Data In Register, the host adapter immediately resets the Data In Register Ready bit (DIRRDY). The host adapter resets this bit to zero to ensure that the host system's CPU does not reread the same data in the Data In Register. When the host adapter writes fresh data to its Data In Register, it will then set the Data In Register Ready bit (DIRRDY) to one again.

The host system's CPU can also read this register to check for error conditions. For example, the host adapter sets this register's Command Invalid bit (CMDINV) when it detects an invalid command or parameter byte in its Command/Parameter Register. Consequently, the host system's CPU can check the Command Invalid bit (CMDINV) to see if such an error condition currently exists. This is a read-only register.

**Bit 0 Command Invalid (CMDINV)**-The host adapter sets this bit immediately upon detection of an invalid command or parameter byte in the Command/Parameter Register. When the host is sending a single or multibyte command, the host adapter terminates the data transfer sequence by setting the Command Complete bit (CMDC) in the Interrupt Register and by generating a hardware interrupt. The host adapter terminates all commands (valid or invalid) by this method. Invalid commands are indicated by the setting of this bit. The condition of this bit is only meaningful while the Command Complete bit (CMDC) is true.

Bit 1 This bit is reserved and is set to zero.

**Bit 2 Data In Register Ready (DIRRDY)**—This status bit is used to synchronize the transfer of status information from the host adapter to the host system. The host adapter sets this bit to one when it has placed a byte of data in the Data In Register. This condition notifies the host that it may read and process the data. When the host reads the data byte in the Data In Register, this bit is reset to zero by the host adapter. This sequence is repeated for multibyte data transfers.

**Bit 3 Command/Parameter Register Busy (CPRBSY)**-This status bit is used to synchronize the transfer of command and associated parameter bytes from the system host to the host adapter. When this bit is reset to zero the host may place a command or parameter byte in the Command/Parameter Register. When the host writes a byte to the Command/Parameter Register, the host adapter will set this bit to a one indicating a Busy condition. The host adapter will reset this bit when it has read and processed the command/parameter byte. This sequence is repeated for multibyte data transfers.

**Bit 4 Host Adapter Ready (HARDY)**-This bit indicates the ready or not ready internal command state of the host adapter. When this bit is set, the host adapter is ready for a new host adapter command. In general the host system's processor may only issue host adapter commands while this bit is set.

**Note:** The multitasking design of the host adapter's firmware permits the following commands to be issued regardless of the busy or not-busy state of the host adapter.

- Start SCSI (02) command

- Enable Outgoing Mailbox Ready Interrupt (05) command...

See Section 1-3, "Software Interface," for details on these commands

**Bit 5 Initialization Required (INREQ)**—When this bit is set to one, it indicates that the mailbox structures must be initialized. This bit is typically set immediately after the completion of self-diagnostic tests following a reset. This bit is not set if diagnostics fail (the Diagnostic Failure bit (DFAIL) is set). The host system must now issue an Initialize Mailbox command (01) to inform the host adapter of the base memory address of the mailbox structure area. The host adapter will reset this bit after successful completion of the Initialize Mailbox command.

**Bit 6 Diagnostic Failure (DFAIL)**–When this bit is set, it indicates that the host adapter's internal self diagnostic has detected an error. This bit may be reset only by a hard reset initiated either by hardware or by the host software. See Section 1-6, "Internal Diagnostics," for more details.

**Bit 7 Diagnostic Active (DACT)**–This bit is set when the host adapter begins its self-testing activity immediately after a power-on reset or a programmed hard reset (Control Register, Bit 7 is set). This bit is reset upon the successful completion of the self-test activity. If the diagnostics fail, this bit may not be reset indicating

that the self-test programs could not be completed. In the case of most failures, the Diagnostic Failure bit (DFAIL) will also be set. See Section 1-6, "Internal Diagnostics," for more details.

#### Command/Parameter Register (Write Only) I/O Base Address + 1

**Command/Parameter Register**

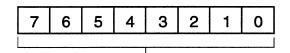

Figure 1-6. Command/Parameter Register (Write)

The Command/Parameter Register serves as the input port through which the host system software may issue commands and associated parameter bytes to the host adapter. The commands issued to the host adapter by this method provide initialization and establish control specifications for subsequent operations. SCSI-bus related commands are issued through a mailbox command structure (See Section 1-3, "Software Interface."). The host is responsible for issuing the correct number of command and parameter bytes for each operation. Otherwise, incorrect operation may occur along with the cessation of command acceptance by the host adapter. This condition is indicated by the setting of the Command Invalid bit (CMDINV) in the Status Register.

The coordination of command and parameter data byte transfers between the host adapter and the host system is governed by the Host Adapter Ready bit (HARDY), the Command/Parameter Register Busy bit (CPRBSY), and the Data In Register Ready bit (DIRRDY). All host adapter commands, with the exception of Enable OMBR Interrupt (05) and Start SCSI (02), require the Host Adapter Ready bit (HARDY) to be set. Parameter data bytes are written to the Command/Parameter Register. The host must first test the Command/Parameter Register Busy bit (CPRBSY) for a not set condition to determine if the host adapter is ready to accept a command parameter data byte. When the host writes a command or parameter byte to the Command/Parameter Register, the host adapter sets the Command/ Parameter Register Busy bit (CPRBSY) to a one. When the local MPU has read the byte, the host adapter will reset the Command/Parameter Register Busy bit (CPRBSY) to indicate that the host can write another byte.

When all the bytes for a particular command have been transferred, and the command has been completed, the host adapter will set the Command Complete bit (CMDC) in the Interrupt Register. If an error is detected in the command, the Command Invalid bit (CMDINV) will be set in the Status Register.

#### Data In Register (Read Only) I/O Base Address + 1

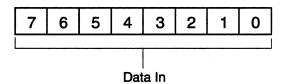

Figure 1-7. Data In Register (Read)

The host adapter uses this register to return information bytes to the host system. For commands that return information bytes to the host, the Data In Register Ready bit (DIRRDY) is used to synchronize data byte transfers. The host adapter sets the Data In Register Ready bit (DIRRDY) to a one when a data byte is available to be read by the host system. The Data In Register Ready bit (DIRRDY) is automatically reset to zero by the host adapter when the host system reads the data byte from the host adapter's Data In Register. For multiple data byte transfers, the host should wait for the Data In Register Ready bit (DIRRDY) to return to the set state before reading additional data. When the last byte of an information block (single or multiple byte) has been transferred, the host adapter will set the Command Complete bit (CMDC) in the Interrupt Register. This is a read-only register.

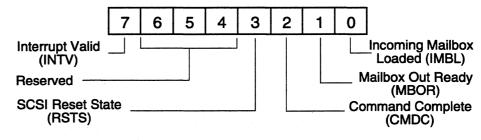

#### Interrupt Register (Read Only) I/O Base Address + 2

Figure 1-8. Interrupt Register (Read Only)

The host adapter uses this read-only register to tell the host system the reason why it generated a hardware interrupt signal. The following are the four conditions under which the host adapter can generate a hardware interrupt to the host system:

- 1. Incoming Mailbox Loaded interrupt (IMBL): the host adapter has made an entry in an incoming mailbox.

- 2. Mailbox Out Ready interrupt (MBOR): an outgoing mailbox location(s) is ready for the host system to use.

- Command Complete interrupt (CMDC): the host adapter has completed a command.

- 4. SCSI Reset State interrupt (RSTS): the host adapter has detected a SCSI Bus Reset condition.

When the host adapter generates a hardware interrupt signal for one of the preceding four reasons, the host adapter sets bits in this register to provide the host system with more information about the interrupt. The host adapter completes the following actions:

- 1. It sets Bit 7, the Interrupt Valid bit (INTV), to indicate that the interrupt is valid.

- 2. It also sets one of the other unreserved bits to indicate why it generated a hardware interrupt signal to the host system. These bits (Bits 0-3) are collectively referred to as interrupt cause bits. This group of bits include the Incoming Mailbox Loaded bit (IMBL), the Mailbox Out Ready bit (MBOR), the Command Complete bit (CMDC), and the SCSI Reset State bit (RSTS).

In response to this interrupt request by the host adapter, the host system should execute the following sequence to service the interrupt:

- 1. Read the Interrupt Register. The host should maintain this value internally for further interrupt processing.

- 2. Clear the Interrupt Register. This is accomplished by setting the host adapter's Control Register's Reset Interrupt bit (RINT).

- 3. Determine the interrupt cause (from the saved Interrupt Register value in the preceding Step 1) and then execute the appropriate interrupt service routine.

**Note:** A hard reset, a soft reset, or initial board power-on condition will cause the Interrupt Register to be cleared, i.e., no interrupts pending.

The host adapter sets the priority of certain interrupt conditions. This topic will be discussed before describing the individual bits of the Interrupt Register. Refer to the following heading "Interrupt Timing and Synchronization."

Interrupt Timing and Synchronization. The host adapter sets the priority of certain interrupt conditions. The posting of a mailbox-related interrupt is withheld if a SCSI Reset State interrupt (RSTS) or a Command Complete interrupt (CMDC) is pending service from the host. Once the SCSI Reset State interrupt (RSTS) or the Command Complete interrupt (CMDC) is cleared, the host adapter will post the mailbox interrupt(s). Likewise, a SCSI Reset State interrupt (RSTS) or a Command Complete interrupt (CMDC) will only be presented if the Interrupt Register has been cleared, and the Data In Ready bit (DIRRDY) shows no additional data is pending.

Because all outbound host mailboxes are typically controlled by host-resident software, it is not necessary to enable the Outgoing Mailbox Ready interrupt (OMBR) unless all mailboxes are being utilized. This technique also lessens the possibility of missed interrupt notification for an Incoming Mailbox Loaded (IMBL) condition. If all outgoing mailboxes are in use, then the host could enable the Outgoing Mailboxes Ready interrupt (OMBR) to gain notification of a Mailbox Ready condition. See the Enable Outgoing Mailbox Ready command description in Section 1-3, "Software Interface," for instructions on how to enable the Outgoing Mailboxes interrupts (OMBR).

**Bit 0 Incoming Mailbox Loaded (IMBL)**—When this bit is set, it indicates that the host adapter has made an entry in an incoming mailbox location. This bit is qualified by the Interrupt Valid bit (INTV) also being set and by the generation of a bus interrupt signal. The host should service this interrupt as soon as possible to allow additional host adapter interrupts to be posted. The multitasking firmware of the host adapter continues to process outstanding SCSI commands after the posting of an Incoming Mailbox Loaded interrupt (IMBL). If additional outstanding commands are completed before the servicing of a previous Incoming Mailbox Loaded interrupt (IMBL), the status of completed commands will be placed in an available incoming mailbox location. The host should therefore scan all mailboxes to determine if additional data has been provided. The host adapter will use Incoming Mailbox locations in a round-robin order permitting the host to scan in the same manner. When a vacant mailbox is found the host may discontinue its scan.

**Bit 1 Outgoing Mailbox Ready (OMBR)**–When this bit is set to a one, it indicates that one or more of the outgoing mailbox locations is available for use by the host. This bit is qualified by the Interrupt Valid bit (INTV) also being set and by the generation of a bus interrupt signal. The Outgoing Mailboxes Ready interrupt (OMBR) is generated only when Outgoing Mailbox interrupts (OMBR) have been enabled and an outgoing mailbox entry is cleared by the host adapter. An Outgoing Mailbox Ready interrupt (OMBR) is suppressed if a SCSI Reset State (RSTS) or a Com-

mand Complete (CMDC) interrupt is pending service. When these previous interrupts are cleared by the host, the pending Outgoing Mailboxes Ready interrupt (OMBR) will be issued by the host adapter.

Application Note: It is recommended that the Outgoing Mailbox Ready interrupt (OMBR) not be enabled unless all outgoing mailbox locations are in use. For most applications, the host adapter will process command requests faster than a host will issue them. If the situation does occur where all outgoing mailbox locations are busy, the host may issue the Enable Outgoing Mailbox Ready Interrupt command without waiting for the status of the Host Adapter Ready bit (HARDY).

**Bit 2 Command Complete (CMDC)**–This bit is set to a one when the Command/ Parameter Register is ready to accept a command. Any previous command will have been completed, either normally or abnormally. If a previous command completed with an error condition or was aborted for any reason, this bit will still be set along with the Command Invalid bit (CMDINV) in the Status Register. Normally completed commands are indicated by the setting of this bit without any accompanying error condition status bits. This bit is qualified by the Interrupt Valid bit (INTV) also being set and by the generation of a bus interrupt signal. A Command Complete interrupt (CMDC) is suppressed if an Interrupt Valid bit (INTV) is set (indicating an interrupt is pending service) or if the Data In Register Ready bit (DIRRDY) is set. When these previous interrupts are cleared by the host, the temporarily withheld Command Complete interrupt (CMDC) will be issued by the host adapter.

**Bit 3 SCSI Reset State (RSTS)**—When this bit is set, it indicates that a SCSI Bus Reset condition has been detected by the host adapter. This bit is qualified by the Interrupt Valid bit (INTV) also being set and by the generation of a bus hardware interrupt signal. In cooperation with host system driver software, the host adapter can implement the SCSI specification soft reset option. host adapter queued operations will resume once the SCSI bus has returned to the operational state. If a currently running command was aborted due to the SCSI Bus Reset condition, the host adapter may have to restart the command.

The host may convert the SCSI bus soft reset to a SCSI bus hard reset by setting the Soft Reset bit (RSOFT) in the host adapter's Control Register. In this case, all queued commands are abandoned and the host adapter must be reinitialized. See the heading "Reset Operations" later in this section for details on the reset conditions.

Bit 4 Reserved-Value read is zero.

Bit 5 Reserved-Value read is zero.

Bit 6 Reserved-Value read is zero.

**Bit 7 Interrupt Valid (INTV)**–When this bit is set, it indicates that a valid interrupt has been generated by the host adapter. This bit reflects the state of the host adapter generated interrupt signal on the bus. The specific reason for the interrupt condition is determined by Bits 0-3 of this register.

# **Reset Operations**

Host adapter reset conditions are initiated from two different vantage points: the host system and the SCSI bus. A description of each follows.

#### **Host-Initiated Reset Operations**

The host system may reset the host adapter to an initial power-on condition through two different operations, one system and the other software.

**System Reset**-The host adapter is fully reset and initialized to a power-on initial condition when the Reset signal is true on the host system bus. The Reset signal is asserted to a true condition by the host (1) during power on, (2) host detected low-power conditions, or (3) a user-invoked reset switch reset. The Reset signal is applied universally to all installed host adapters in the system bus. A host adapter system reset causes a power-on initialization process which also results in a reset of all the devices on the SCSI bus.

**Software Reset**—The host adapter may be fully reset to an initial state by a software command, just the same as if a system reset had been received by setting the Hard Reset bit (RHARD). When RHARD is set to true, a Reset condition occurs immediately. However, this Reset condition will only affect *one* host adapter, unlike the system reset (described above) which resets *all* host adapters installed in the system bus. An RHARD reset may issue a subsequent reset to the SCSI device depending on the AutoSCSI utility configuration setting for the Enable SCSI Bus Reset option (see the manual for your host adapter for more information).

Either type of host-initiated reset will cause the following conditions on the host adapter.

- The control registers of all intelligent logic modules on the host adapter will be initialized to a known state.

- All pending operations are aborted and all data structures are initialized to a no operation pending state.

- The host adapter executes all internal diagnostic functions. While the diagnostic functions are in process, the host adapter will indicate this condition by setting the Diagnostic Active bit (DACT) to true in the Status Register.

- During a system reset, the host adapter places a SCSI Bus Reset condition on the SCSI bus. This may also occur during a software reset (using the RHARD bit), but depends on the AutoSCSI utility configuration setting for the Enable SCSI Bus Reset option. This will reset all peripheral devices, whether a target or initiator.

- After completion of a system reset, the host adapter indicates that it is now in an initial condition by asserting the Initialization Required bit (INREQ) in the host adapter's Status Register. This condition requires that all mailbox, command control blocks, and host adapter operation parameters be established before operations may begin.

*Note:* The host may initiate a soft reset by setting the RSOFT bit. This reset reinitializes the specific host adapter, but there is no subsequent SCSI bus reset.

#### **SCSI Bus Reset Operations**

The SCSI Bus Reset condition is used to clear all SCSI devices immediately from the SCSI bus. When the SCSI bus Reset signal is asserted, the SCSI Bus Reset condition takes precedence over all other bus phases. A SCSI Bus Reset condition may be forced by any device on the bus, whether a target or initiator. Whenever a SCSI Reset condition occurs, a Bus Free phase always follows the Reset condition. The five ways in which a SCSI bus reset may be either asserted or sensed by the host adapter are as follows:

- R1 The SCSI Bus Reset condition is always asserted when the host adapter is reset by the host system (host system **system** reset only). This is described earlier in this section under the heading "Host-Initiated Reset Operation."

- R2 The SCSI Bus Reset condition may be asserted when the host adapter is **soft** reset by the host system when RHARD is set to true (depending on the AutoSCSI utility configuration setting for the **Enable SCSI Bus Reset** option). This is also described under the heading "Host-Initiated Reset Operations."

- R3 The SCSI Bus Reset condition is asserted if the Reset SCSI Bus bit (RSBUS) is set by the host system control software.

- R4 The host adapter may initiate a SCSI Bus Reset condition in reaction to a detected bus phase error. The host adapter constantly monitors the SCSI bus for invalid conditions. If an invalid phase is detected, the host adapter will perform a normal SCSI Bus Reset operation which includes the assertion of the SCSI bus Reset signal.

- R5 The host adapter will detect and respond to a SCSI Bus Reset condition that is asserted by another device on the bus. Other SCSI devices may normally assert the Reset signal during either initialization or certain error recovery states. The device driver requires an acknowledgment from the host adapter that a SCSI Reset operation has taken place, so the SCSI Reset State bit is set in the interrupt register.

While the SCSI specification defines two methods by which the SCSI bus may be reset, either by the hard reset option or the soft reset option, *BusLogic host adapters* only support the hard reset option.

The SCSI bus hard reset option restores ALL SCSI devices, target or initiator, to the initial power-on condition. All system activity is lost, and all devices must be completely reinitialized before normal operations may be restored. SCSI devices that implement the hard reset option perform the following operations:

- Clear all uncompleted commands.

- Release all SCSI device reservations.

- Return any SCSI device operating modes to their default condition.

Here is how the host adapter implements a SCSI hard reset:

- When the host adapter detects a SCSI reset, it issues an interrupt indicating a SCSI reset has occurred to the host system.

- The host adapter sets both the SCSI Reset State bit (RSTS) and the Interrupt Valid bit (INTV) in the host adapter's Interrupt Register.

- All host adapter command control blocks (CCBs) are abandoned and the host adapter readies itself to accept new initialization commands.

- BusLogic recommends that after the device driver receives the RSTS, it issue a RHARD or an RSOFT to ensure that the host adapter is re-initialized.

- All the mailbox and command control blocks must be reinitialized.

# **Software Interface**

For the host adapter to operate properly, the host system must issue the correct command and associated parameters to the host adapter. The host adapter has its own set of executable instructions that the host system can issue to the host adapter. This command set can be subdivided into the following three groups:

- 1. Host adapter commands

- 2. Mailbox commands

- 3. BIOS commands

The host system uses the host adapter commands to initialize and to establish control specifications for subsequent operations of the host adapter. The host system uses the host adapter's Command/Parameter Register as an input port through which it issues any host adapter commands and associated parameter bytes to the host adapter. For more details on each of these host adapter commands refer to the heading "Host Adapter Commands" later in this section.

The second category of commands, mailbox commands, is issued to the host adapter when multithreaded operations are required. Mailboxes are reserved storage areas which reside at a fixed contiguous memory location in the host system's main memory. The mailboxes coordinate communications between the host system and the host adapter when the host adapter is operating in multithreaded mode. This software interface enables the host adapter to execute multiple commands concurrently for multiple targets with minimal intervention from the host system. For more details on these mailbox commands refer to the heading "Mailbox Commands" later in this section.

The third category of commands, BIOS commands, is issued to the host adapter when single-threaded operations are required. In this case the BIOS commands work with the host adapter's on-board BIOS. These commands in unison with the on-board BIOS function in a manner fully compatible with DOS and the standard BIOS interface as defined in the host system's technical reference manual. For more details on each of these BIOS commands refer to the heading "BIOS Command Interface" later in this section.

Before these commands are discussed in detail, a brief look at how the host adapter acts as bus master to transfer data on the memory bus and how it requests interrupt service from the host is presented.

# **Bus Master Direct Memory Access (DMA)**

The DMA control logic manages bus arbitration and data transfer coordination. The host adapter operates as a bus master during data transfers. The host adapter arbitrates for bus access and once granted, it takes over control of the bus. It generates the bus address and command strobes. The host adapter supports both odd and even starting addresses, commonly known respectively as aligned and unaligned transfers. If presented with an even transfer count beginning at odd memory starting address, the host adapter will first transfer a single byte (data bits D24-D31). The remaining data is then transferred as double words (32 bits) until the last byte which is transferred as a single byte (data bits D0-D7). While odd byte data transfers are fully supported, it is recommended that when possible host buffers be double-word aligned to gain better data transfer performance.

# Interrupt Processing

Several interrupt channels are available to the host adapter. The channel to be used by each host adapter board is specified by configuration settings as described in the host adapter user's guide.

The host system contains a programmable interrupt controller which receives all interrupts and directs the host's CPU to a corresponding vector location which in turn contains a memory address for the software Interrupt Service routine which performs the necessary actions required by each interrupt. It also contains a Mask Register whose bits may be set to mask or cleared to permit corresponding interrupt channels to be acknowledged.

In order to respond correctly to host adapter interrupts during normal operation, the host interrupt controller must be programmed appropriately. The software driver will have to program the host's Interrupt Mask Register and interrupt vector before attempting to use interrupts from the host adapter. The interrupt vector locations and Interrupt Mask Register's bits which need to be cleared to permit acknowledgment of each interrupt channel are listed as follows:

| Hardware Interrupt Line |       | Vector Location<br>in Memory (Hex) | Interrupt Mask Register<br>Hex Address A1 |  |

|-------------------------|-------|------------------------------------|-------------------------------------------|--|

|                         | IRQ9  | 1C4-1C7                            | Bit 1                                     |  |

|                         | IRQ10 | 1C8-1CB                            | Bit 2                                     |  |

| Default                 | IRQ11 | 1CC-1CF                            | Bit 3                                     |  |

|                         | IRQ12 | 1D0-1D3                            | Bit 4                                     |  |

|                         | IRQ14 | 1D8-1DB                            | Bit 6                                     |  |

|                         | IRQ15 | 1DC-1DF                            | Bit 7                                     |  |

If the host adapter is configured for Interrupt Channel 11, for example, the system's interrupt controller must be initialized by **clearing** Bit 3 in its Interrupt Mask Register. The address of the interrupt service routine for Channel 11 will be contained in the four bytes of memory beginning at memory address 1CCH.

The remainder of this section describes the structure and operation of the three categories of commands that the host can issue to the host adapter.

# **Host Adapter Commands**

Host adapter command codes and associated parameter bytes are supplied to the host adapter's Control Register under the coordination of certain bits in the host adapter's Status Register. Table 1-2 provides a summary of these commands.

| Operation Code Hex Value | Host Adapter Command                         |

|--------------------------|----------------------------------------------|

| 00                       | Test CMDC interrupt                          |

| 01                       | Initialize Mailbox                           |

| 02                       | Start Mailbox command                        |

| 03                       | Start BIOS command                           |

| 04                       | Inquire Board ID                             |

| 05                       | Enable OMBR interrupt                        |

| 06                       | Set SCSI Selection Time-Out                  |

| 07                       | Set Time On Bus                              |

| 08                       | Set Time Off Bus                             |

| 09                       | Set Bus Transfer Rate                        |

| 0A                       | Inquire Installed Devices                    |

| OB                       | Inquire Configuration                        |

| 0D                       | Inquire Set-up Information                   |

| 1A                       | Write Adapter Local RAM                      |

| 1B                       | Read Adapter Local RAM                       |

| 10                       | Write Bus Master Chip FIFO                   |

| 1D                       | Read Bus Master Chip FIFO                    |

| 1F                       | Echo Data Byte                               |

| 20                       | Host Adapter Diagnostic                      |

| 21                       | Set Adapter Options                          |

| 23                       | Inquire Installed Devices for Target ID 8-15 |

| 81                       | 32-Bit Mode Initialize Mailbox               |

| 8D                       | Inquire Extended Set-up Information          |

| 96                       | Enable Wide Mode CCB                         |

|                          |                                              |

Table 1-2. Host Adapter Commands

The host system can write a command to the Command/Parameter Register only after checking to see that the Host Adapter Ready bit (HARDY) is set to one, except that the Start Mailbox command and the Enable OMBR Interrupt command may be written at any time. After writing a command, the host may write a predetermined number of parameter bytes to the Command/Parameter Register after checking that the Command/Parameter Register Busy bit (CPRBSY) is zero, indicating that the Command/Parameter Register is not busy and can accept another parameter byte.

In response to some commands, the host adapter may transfer a predetermined number of parameter bytes back to the host. The host adapter places each byte into the Data In Register and then sets the Data In Register Ready bit (DIRRDY) to indicate to the host that the byte is ready to be read by the host. After the host has read the input data byte, the host adapter resets the Data In Register Ready bit (DIRRDY).

The following table lists each host adapter command code along with the associated number of parameter bytes coming into or being sent out from the host adapter and a brief description of the function performed.

| Operation Code | Command             | Parameter Byte Count | Direction |

|----------------|---------------------|----------------------|-----------|

| 00             | TEST CMDC INTERRUPT | None                 | None      |

**Description.** The host adapter's only response to this command is to set the Command Complete bit (CMDC) in the Interrupt Register. When this bit is set, the host can verify proper functioning of this bit.

| <b>Operation Code</b> | Command            | Parameter Byte Count | Direction |

|-----------------------|--------------------|----------------------|-----------|

| 01                    | INITIALIZE MAILBOX | 4                    | Out       |

**Description.** This command specifies the number of mailboxes used by the host adapter, and the base memory location of the mailbox array to be used when executing mailbox commands. Four parameter bytes follow the command byte to provide the following information:

#### Byte Description

0 Number of mailboxes needed - must be greater than zero.

1 - 3 Base mailbox address - specifies the location of the first byte of the mailbox array. Byte 1 is the most significant byte (MSB).

Each mailbox location in memory will occupy four outgoing mailbox bytes and four incoming mailbox bytes. The Command Invalid bit (CMDINV) will be set with the Command Complete bit (CM-DC) if the number of mailboxes is specified as zero. At command completion, the Command Complete bit (CMDC) is set to one and the Initialization Required bit (INREQ) is reset to zero to acknowledge that initialization is unnecessary. See the heading "Mailbox Commands" later in this section for more information on the mailbox structure.

| Operation Code | Command               | Parameter Byte Count | Direction |

|----------------|-----------------------|----------------------|-----------|

| 02             | START MAILBOX COMMAND | None                 | None      |

**Description.** This command is normally issued every time the host makes an outgoing mailbox entry. Upon receipt of this command, the host adapter begins scanning for active outgoing mailbox entries and continues scanning until all outgoing mailbox entries have been serviced. This can be accomplished by either beginning the requested operations or queuing the commands and executing them later. To avoid unnecessary interrupt servicing by the host, the Command Complete bit (CMDC) is *not* set after receipt of this command. If this command is received before the Initialize Mailbox command, however, the host adapter will then set both the Command Invalid bit (CMDINV) and the Command Complete bit (CMDC) in the Status Register.

| <b>Operation Code</b> | Command            | Parameter Byte Count | Direction |

|-----------------------|--------------------|----------------------|-----------|

| 03                    | START BIOS COMMAND | None                 | None      |

**Description.** This command is used exclusively by the host adapter's BIOS to communicate with the host adapter's firmware. This command is *not* used by application programs.

| Operation Code | Command          | Parameter Byte Count | Direction |

|----------------|------------------|----------------------|-----------|

| 04             | INQUIRE BOARD ID | 4                    | in 🦿      |

Description. Upon receipt of this command, the host adapter sends four bytes of data to the host which contain identification and revision information about itself. Refer to these byte contents:

| Byte                                                        | Description                                                                                                        |                                                                                                     |  |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|

| 0                                                           | BusLogic Board Type - value allows software support for PC/AT, PCI and Micro<br>Channel BusLogic host adapters.    |                                                                                                     |  |

|                                                             | Hex Value                                                                                                          | Meaning                                                                                             |  |

|                                                             | 41                                                                                                                 | Board is a BT-54X, BT-74X, BT-44X, or BT-946C<br>with 64-head BIOS                                  |  |

|                                                             | 42                                                                                                                 | Board is a BT-640A with 64-head BIOS                                                                |  |

|                                                             | Other                                                                                                              | Reserved                                                                                            |  |

| 1 Custom Features - indicates what custom features adapter. |                                                                                                                    | res - indicates what custom features may be supported by the host                                   |  |

|                                                             | Hex Value                                                                                                          | Meaning                                                                                             |  |

|                                                             | 41                                                                                                                 | Standard host adapter                                                                               |  |

|                                                             | Other                                                                                                              | Reserved                                                                                            |  |

| 2                                                           | Firmware Revision Level - a byte designating the revision level of the host adapt-<br>er firmware. ASCII "0" - "9" |                                                                                                     |  |

| 3                                                           | Firmware Vers                                                                                                      | sion - a byte designating the revision level of the installed firmware                              |  |

|                                                             |                                                                                                                    | bytes of data have been transferred, the Command Complete bit indicating normal command completion. |  |

|                                                             |                                                                                                                    |                                                                                                     |  |

| <b>Operation Code</b> | Command               | Parameter Byte Count | Direction |

|-----------------------|-----------------------|----------------------|-----------|

| 05                    | ENABLE OMBR INTERRUPT | 1                    | Out       |

Description. This command specifies whether the Outgoing Mailbox Ready bit (OMBR) should be set when an outgoing mailbox entry is cleared by the host adapter. The single parameter byte from the host instructs the host adapter as follows:

| Hex Value | Meaning                                                           |

|-----------|-------------------------------------------------------------------|

| 00        | The Outgoing Mailbox Ready Interrupt bit (OMBR) is not to be set. |

| 01        | The Outgoing Mailbox Ready Interrupt bit (OMBR) is to be set once |

|           | the outgoing mailbox has been cleared by the host adapter.        |

To avoid unnecessary interrupt servicing by the host, the Command Complete bit (CMDC) is not set after receipt of this command. If the parameter byte contains a value other than 00H or 01H, however, the Command Invalid bit (CMDINV) is set, as well as the Command Complete bit (CM-DC), to indicate receipt of an invalid command.

| Operation Code | Command                     | Parameter Byte Count | Direction |

|----------------|-----------------------------|----------------------|-----------|

| 06             | SET SCSI SELECTION TIME-OUT | 4                    | Out       |

Description. This command specifies the wait time used to determine whether or not a SCSI selection was successful. If the SCSI Busy signal is not returned within the specified time-out period, the selection will be terminated and the appropriate error message recorded in the returned CCB. The contents of the four parameter bytes received with this command are as follows:

| Byte | Description                                                                                                                                |                                                                                |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|

| 0    | Enable/Disable SCSI Selection Time-Out - specifies whether or not the SCSI Se-<br>lection time-out is used. Refer to the following values. |                                                                                |  |

|      | Hex Value                                                                                                                                  | Meaning                                                                        |  |

|      | 00                                                                                                                                         | No time-out is performed.                                                      |  |

|      | 01                                                                                                                                         | The time specified in Bytes 02 and 03 is used as the SCSI time-<br>out period. |  |

Reserved - must be set to zero.

1

2 - 3 Time-Out Value - specifies the SCSI selection time-out period in milliseconds. The default value is 250 milliseconds. Byte 2 is the most significant byte.

After command completion, the Command Complete bit (CMDC) is set indicating normal command completion. The Command Invalid bit (CMDINV) is set only if data Byte 0 is invalid (neither 00H nor 01H) or data Byte 1 is not zero which indicates an invalid command.

| <b>Operation Code</b> | Command                 | Parameter Byte Count | Direction |

|-----------------------|-------------------------|----------------------|-----------|

| 07                    | SET PREEMPT TIME ON BUS | 1                    | Out       |

**Description.** This command specifies the time the host adapter is allowed on the bus after being preempted. One parameter byte is sent to the host adapter indicating the length of time in microseconds. This time can be from 2 to 15 microseconds. The default value is 7 microseconds. After command completion, the Command Complete bit (CMDC) is set indicating normal command completion. If the data byte value is greater than 15, the Command Invalid bit (CMDINV) is set indicating that an invalid command was received.

When the host adapter requires a host data transfer, it asserts the Master (x) Request signal and waits for the host arbitration logic to respond with the Master (x) Acknowledge signal. Once it obtains ownership of the bus it then transfers data across the bus directly into or out of main system memory. The host adapter releases the bus when the transfer is completed within Preempt Time On Bus after a preempt condition (deassertion of the Master (x) Acknowledge signal).

| <b>Operation Code</b> | Command          | Parameter Byte Count | Direction |

|-----------------------|------------------|----------------------|-----------|

| 08                    | SET TIME OFF BUS | 1                    | Out       |

**Description.** This command specifies the time the host adapter will spend off the bus. One parameter byte is sent to the host adapter indicating the length of time in microseconds. This command is treated as a no operation command. It is supported for software compatibility to ISA software.

| <b>Operation Code</b> | Command               | Parameter Byte Count | Direction |

|-----------------------|-----------------------|----------------------|-----------|

| 09                    | SET BUS TRANSFER RATE | 1                    | Out       |

**Description.** This command is treated as a no operation command. It is supported for software compatibility to ISA software.

| <b>Operation Code</b> | Command                   | Parameter Byte Count | Direction |

|-----------------------|---------------------------|----------------------|-----------|

| 0A                    | INQUIRE INSTALLED DEVICES | 8                    | In        |

|                       | ID 0-7                    |                      |           |

**Description.** The host adapter will check if nay devices are attached at Target ID 0-7 on the SCSI bus. Each byte is associated with a Target ID; each bit is associated with a LUN.For example, if set to byte 0: bit 0, it indicates Target 0: LUN 0 is installed. If set to byte 7: bit 7, it indicates that Target ID 7: LUN 7 is installed.

The byte associated with the host adapter will always be zero. Once all information has been transferred, the Command Complete bit (CMDC) is set to indicate normal command completion.

| Operation Code | Command               | Parameter Byte Count | Direction |

|----------------|-----------------------|----------------------|-----------|