.

# INDEX

# Page No.

# INTRODUCTION AND OPERATION - SECTION I

| Communication Options .  |  |   |  |   |  | . 18 |

|--------------------------|--|---|--|---|--|------|

| Communication Procedures |  |   |  |   |  |      |

| Functional Description   |  | • |  | • |  | . 1  |

| General Description      |  |   |  |   |  | . 1  |

| Glossary of Terms        |  |   |  |   |  |      |

| Operation                |  |   |  |   |  | . 3  |

| Physical Characteristics |  |   |  |   |  | . 1  |

| System Interface         |  |   |  | • |  | . 19 |

|                          |  |   |  |   |  |      |

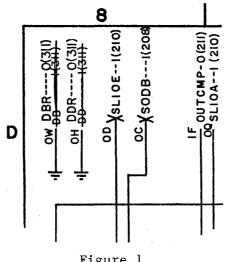

# FUNCTIONAL DETAIL - SECTION II

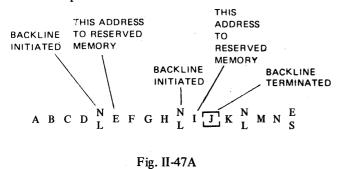

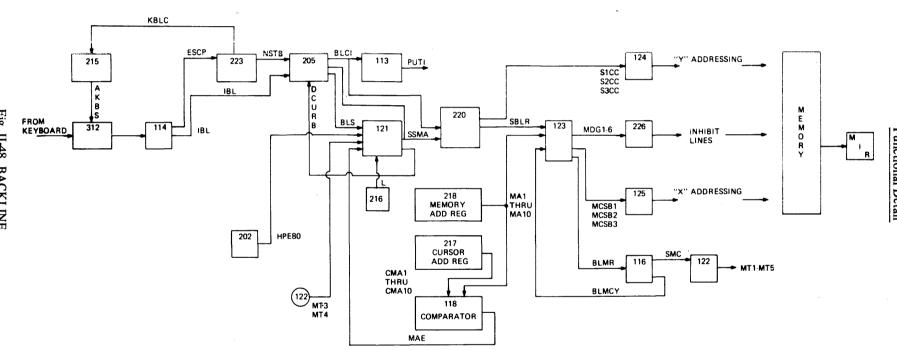

| Backline                                         | 50 |

|--------------------------------------------------|----|

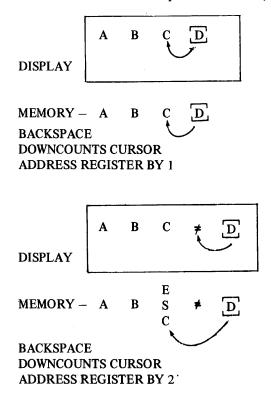

| Backspace                                        | 53 |

| Basic Machine Timing                             | 3  |

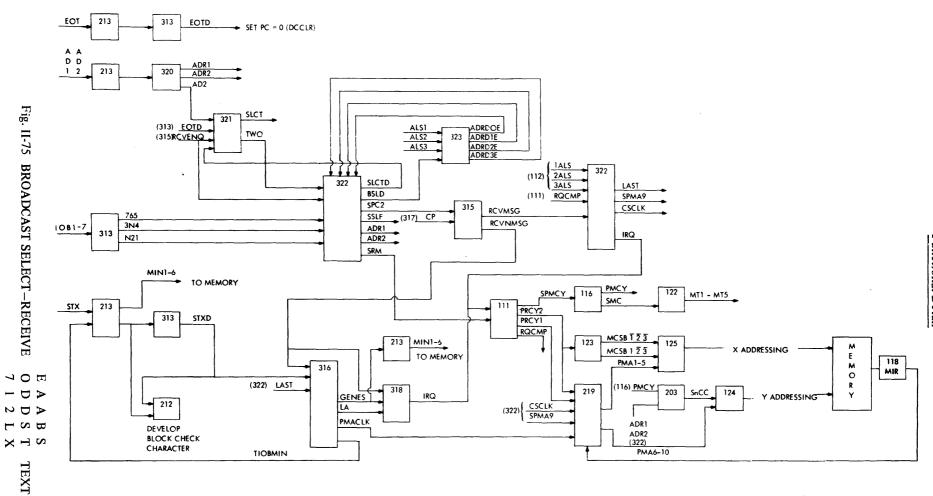

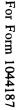

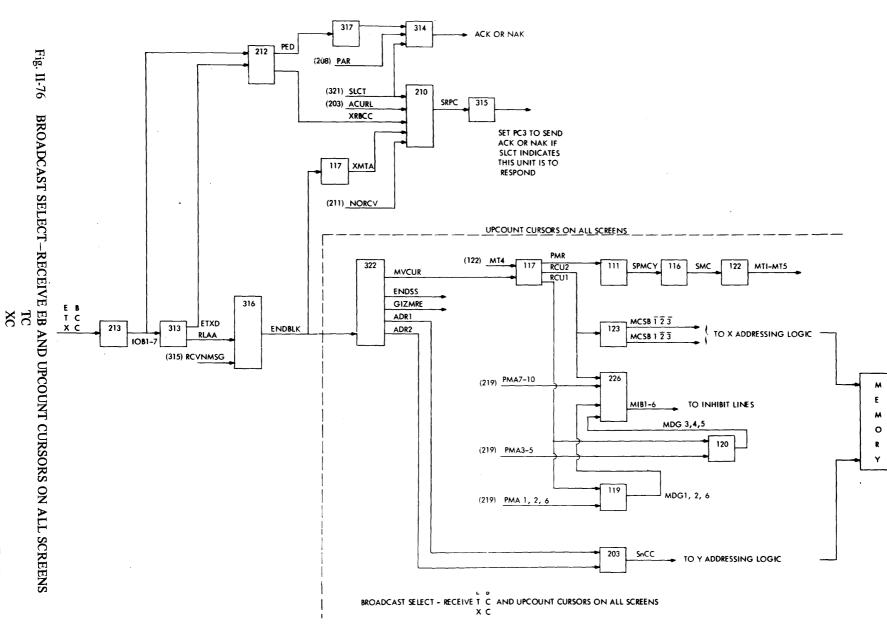

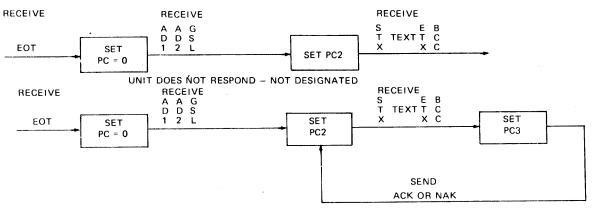

| Broadcast Select                                 | 84 |

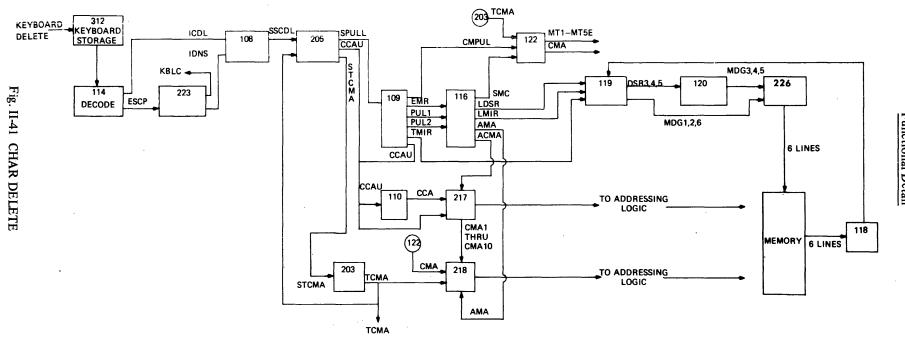

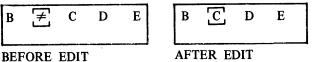

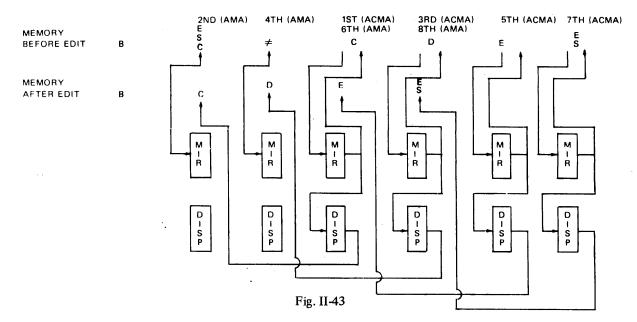

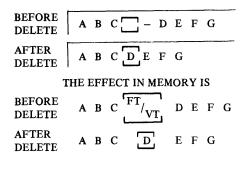

| Character Delete (One Memory Position Character) | 45 |

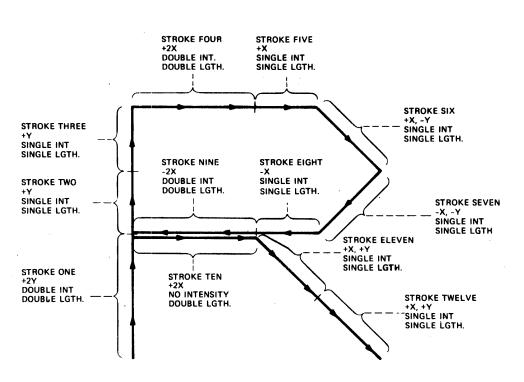

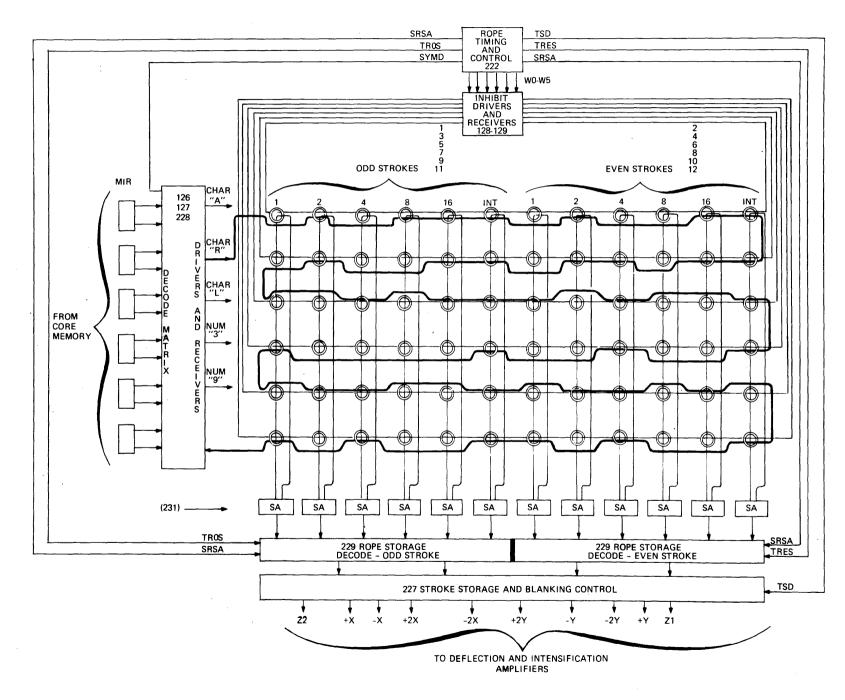

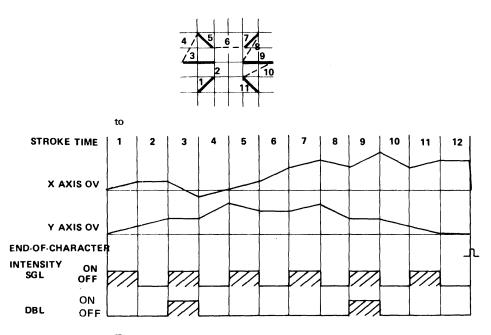

| Character Generation                             | 9  |

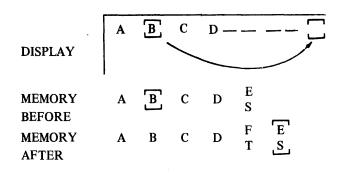

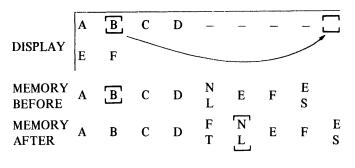

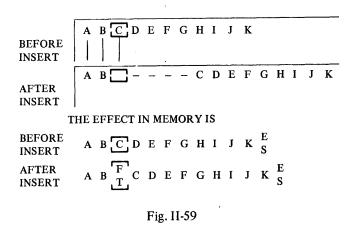

| Character Insert                                 | 50 |

| Clear                                            | 54 |

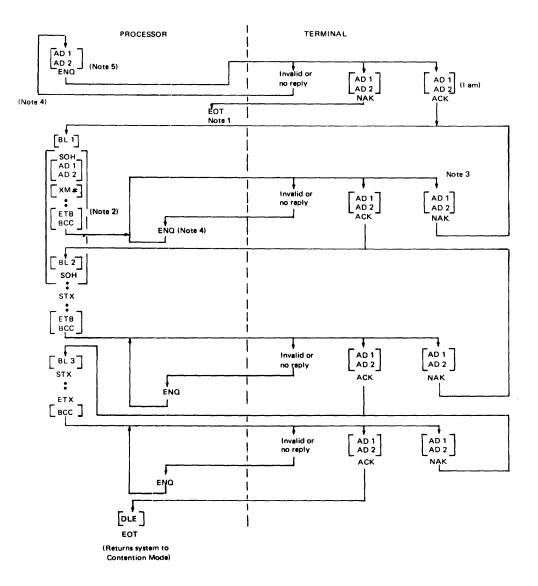

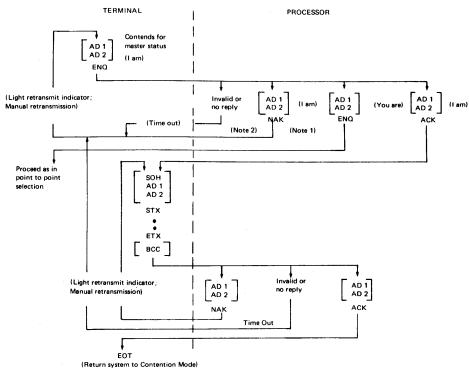

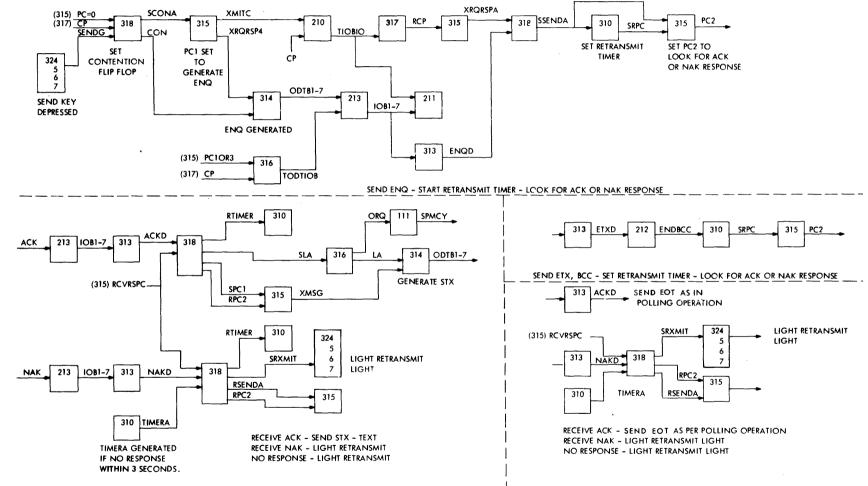

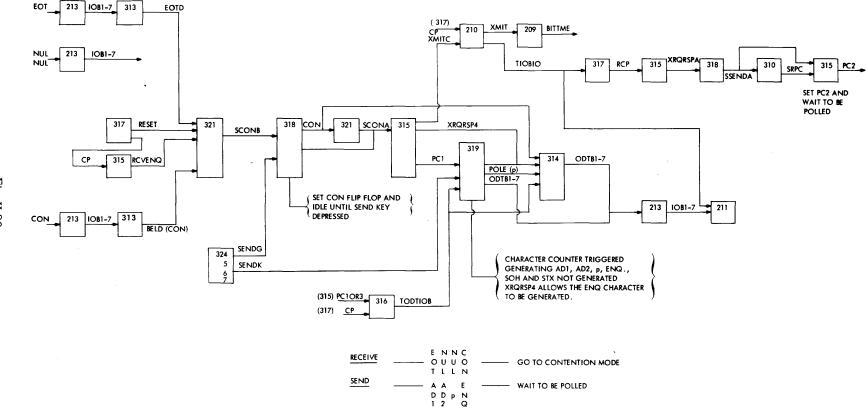

| Contention Mode                                  | 93 |

| Control Storage Register                         | 17 |

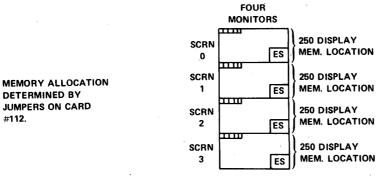

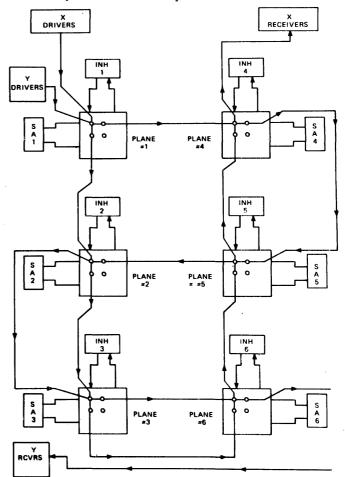

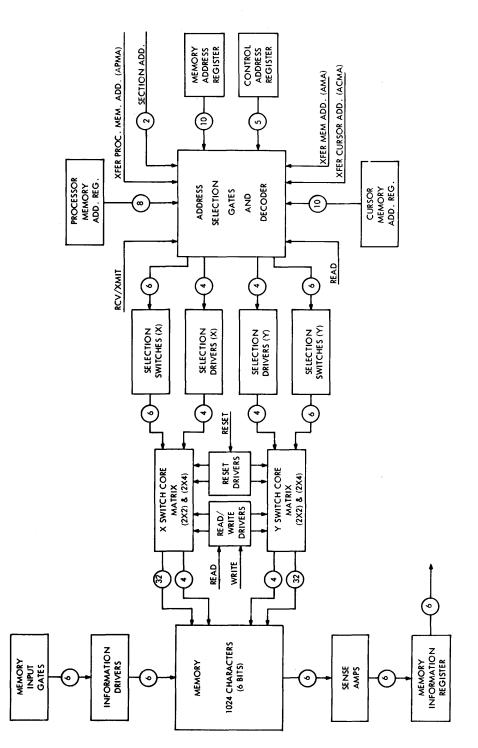

| Core Memory Addressing                           | 6  |

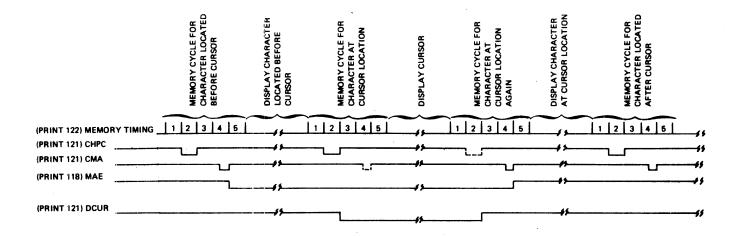

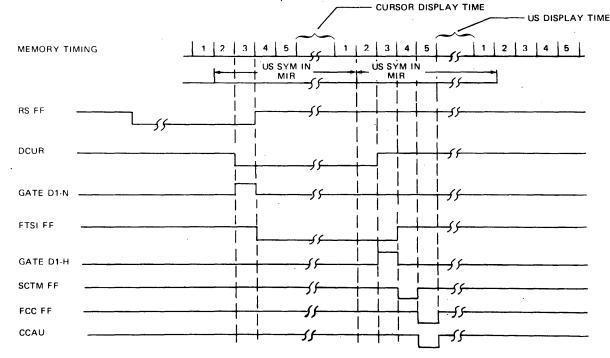

| Cursor Display                                   | 15 |

| Display Sequence & Rope Timing                   | 12 |

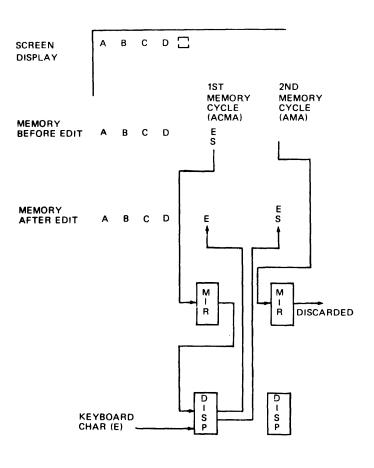

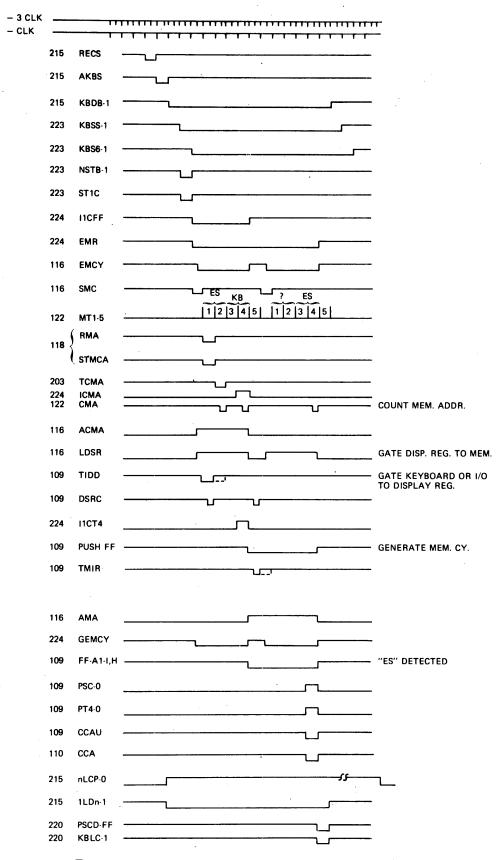

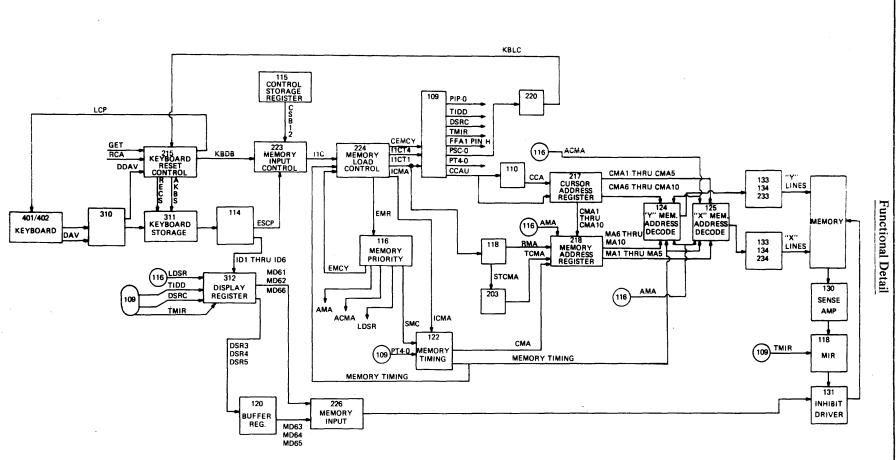

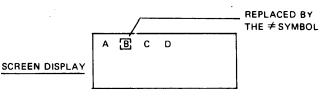

| Edit & Processor Memory Sequences                | 25 |

| Edit Sequence (One Position)                     | 25 |

| Edit Sequence (Two Position)                     | 27 |

|                                                  | 63 |

| Fast Select                                      | 84 |

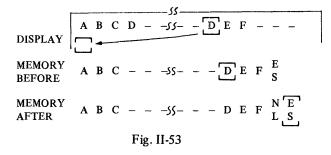

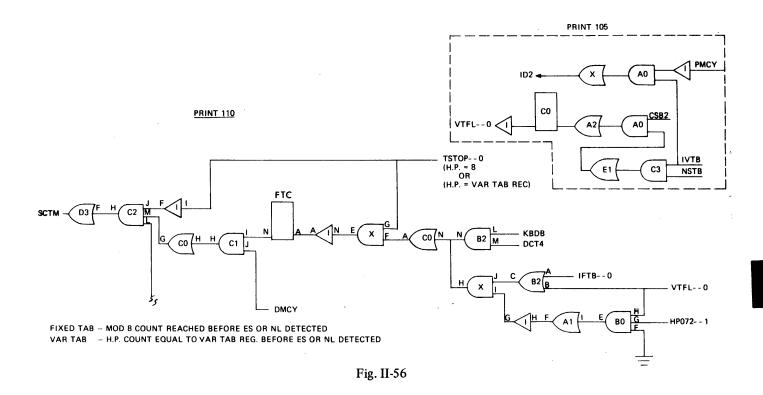

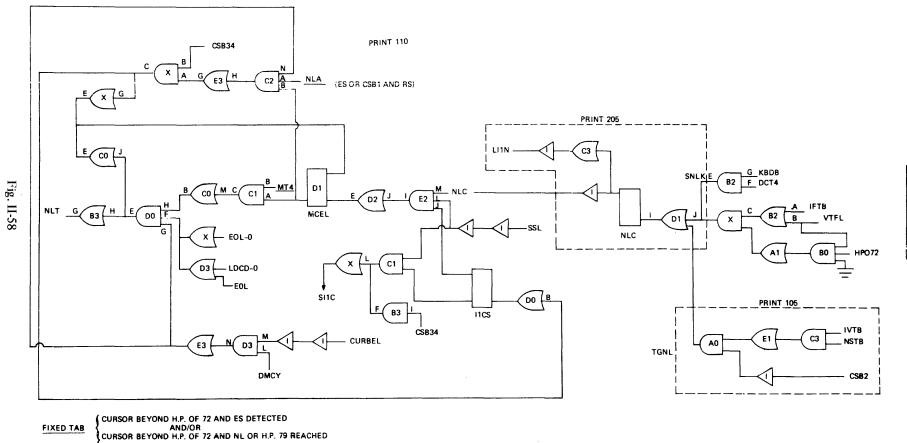

| Fixed Tab                                        | 55 |

| Flyback (Retrace)                                | 16 |

|                                                  | 63 |

|                                                  | 63 |

| Forward Space – Shift                            | 63 |

| -                                                | 80 |

| General Description of B9353 System              | 1  |

|                                                  | 88 |

| -                                                | 53 |

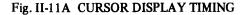

| Keyboard                                         | 17 |

| •                                                | 48 |

| Line Insert                                      | 50 |

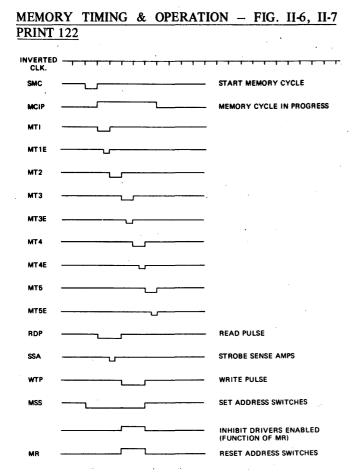

| Memory Timing & Operation                        | 9  |

|                                                  | 61 |

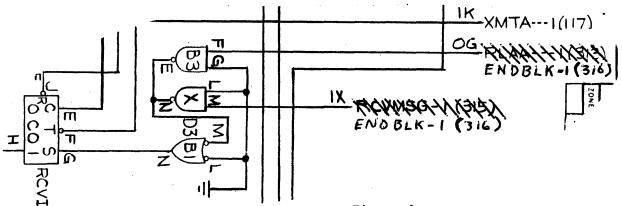

| Point to Point Receive                           | 92 |

| Point to Point Transmit                          | 93 |

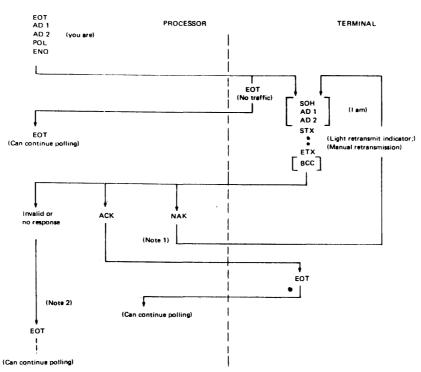

| Polling                                          | 75 |

| Power on Clear                                   | 54 |

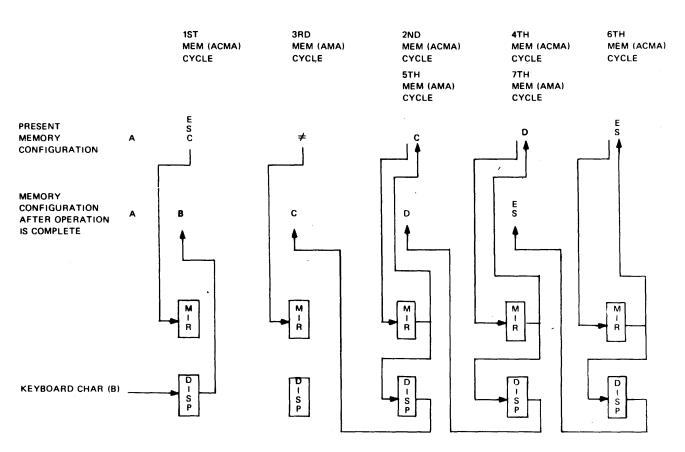

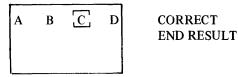

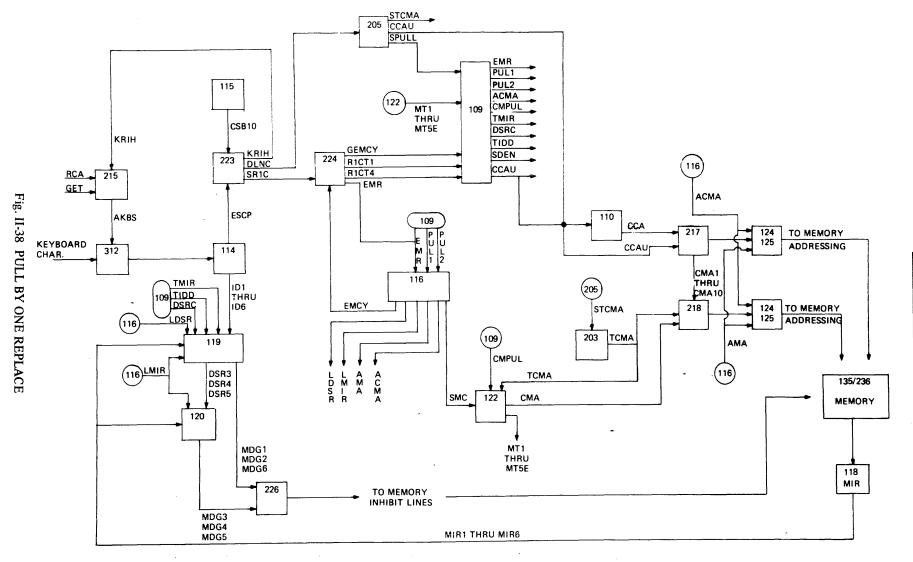

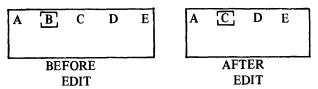

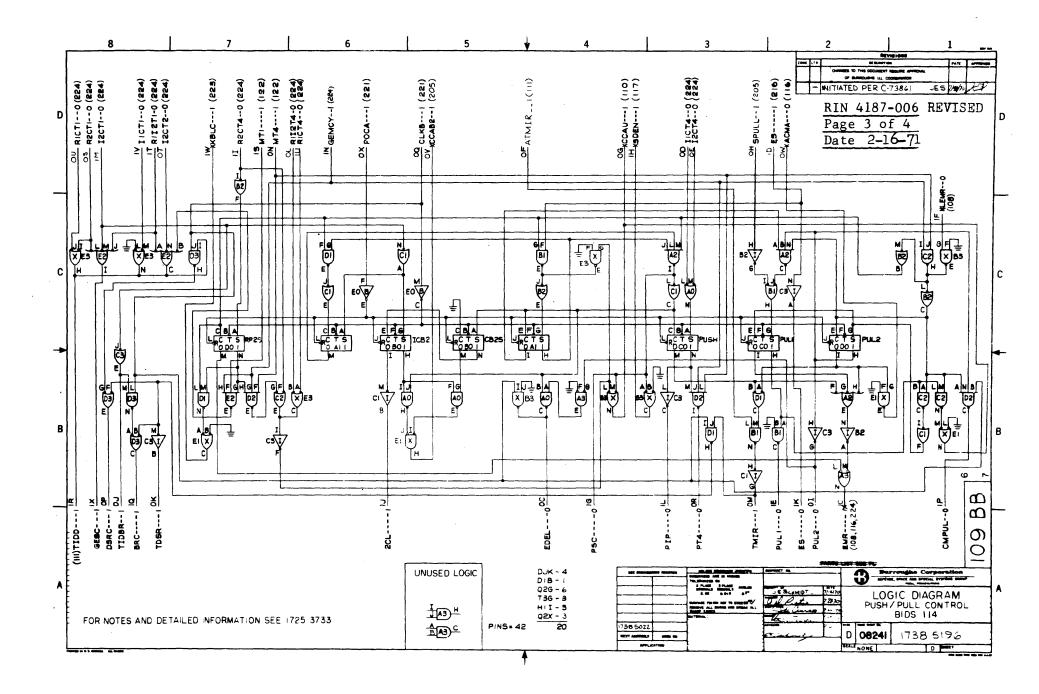

| Pull by One Replace                              | 38 |

| Pull by 2 Replace Character Delete (2 Memory     |    |

|                                                  | 47 |

| Purch has Quee Deallance - Current Queer ES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |      |     | . 28        | 0  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------|----|

| Push by One Replace – Cursor Over ES · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |      |     |             | 2  |

| Push by One Replace –(One Memory Position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |      |     |             | 1  |

| Replaced by a Two Memory Position Cha<br>Push by Two Replace – Cursor Over ES.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |      |     |             |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |      |     |             |    |

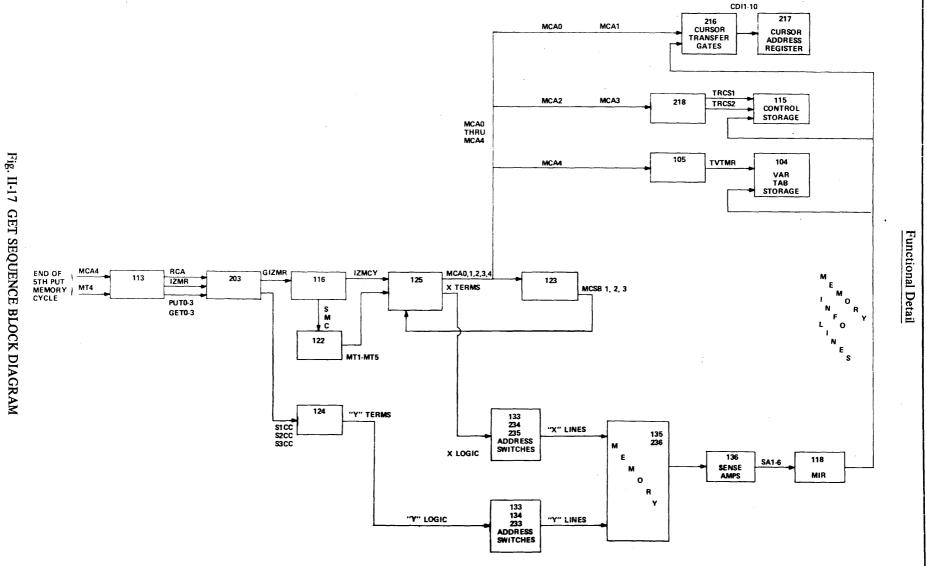

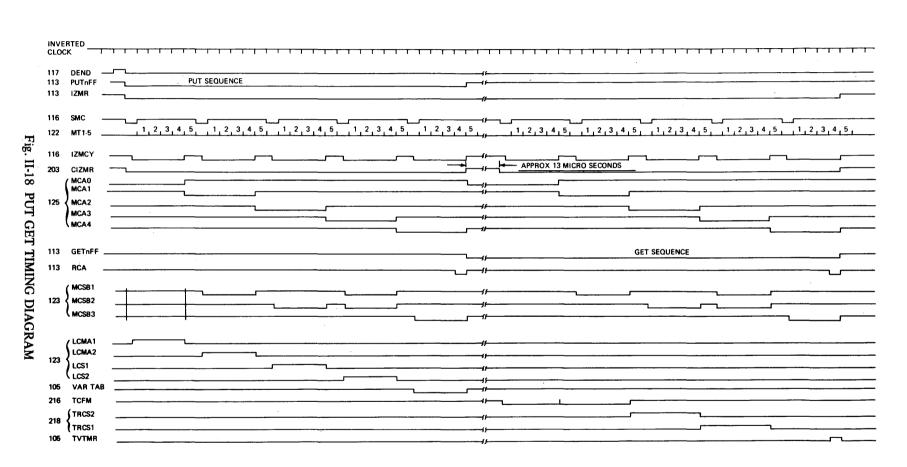

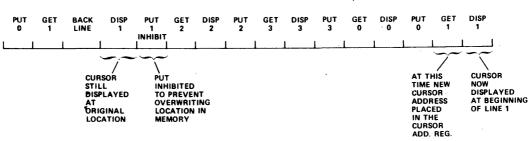

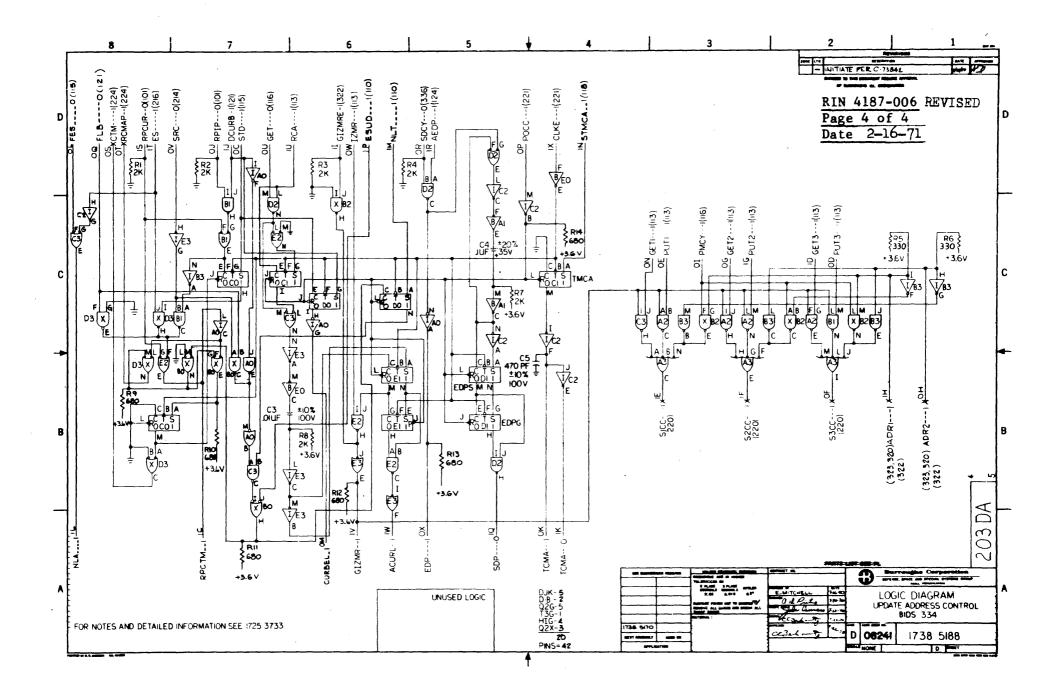

| Put and Get                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | •••  | •   | · 24        | -  |

| Reposition Cursor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |      |     |             | -  |

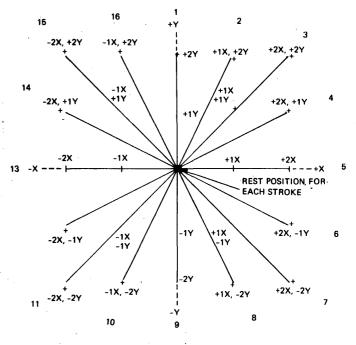

| Rope Character Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |      |     |             | -  |

| F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | • •  |     |             | -  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | • •  |     |             |    |

| Selective Send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •   | •••  |     |             |    |

| So que num server                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | •••  | •   |             |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | • •  | •   |             |    |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . • | • •  | •   |             |    |

| Tab Delete         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         ·         · <th< td=""><td></td><td>• •</td><td>·</td><td></td><td></td></th<> |     | • •  | ·   |             |    |

| Tab Insert · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | • •  | •   |             |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | • •  | •   | . 58        | 3  |

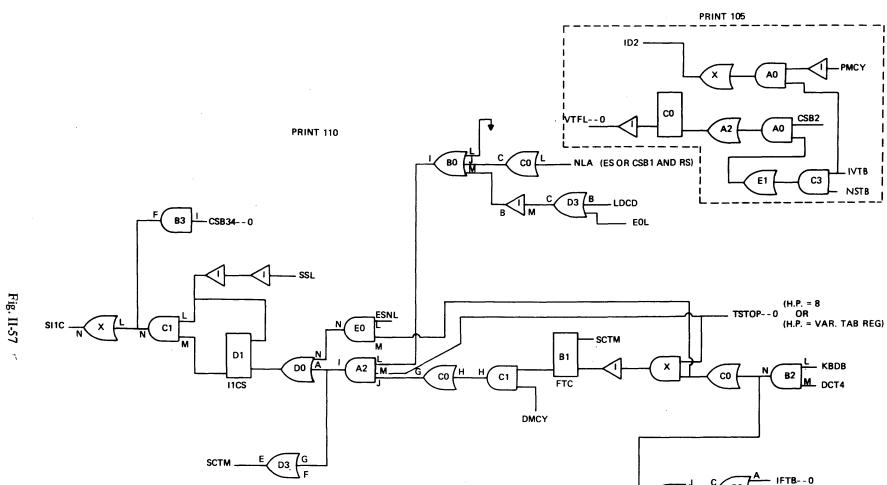

| Variable Tab Operation • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |      | •   | . 57        | 1  |

| VTAB Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |      | •   | . 57        | 1  |

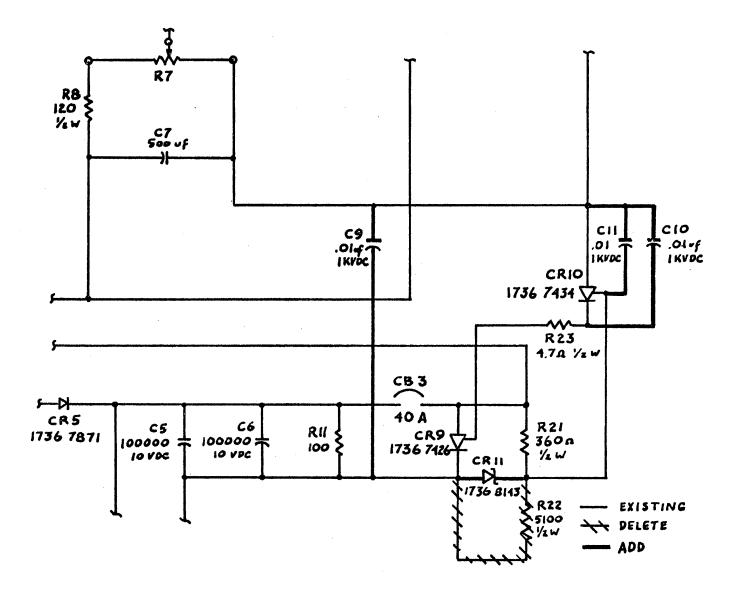

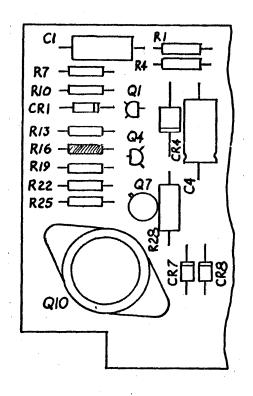

| CIRCUIT DETAIL - SECTION III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |      |     |             |    |

| CIRCUIT DETAIL - SECTION III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |      |     |             |    |

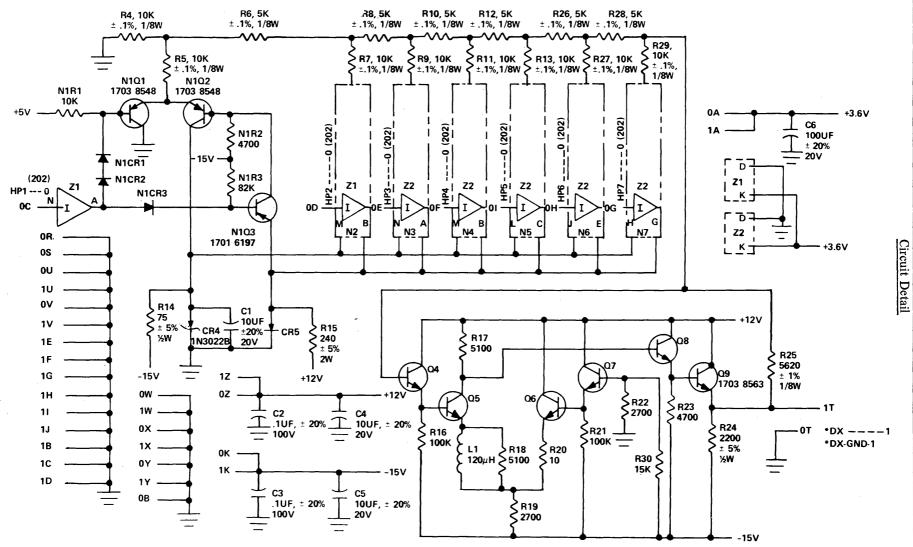

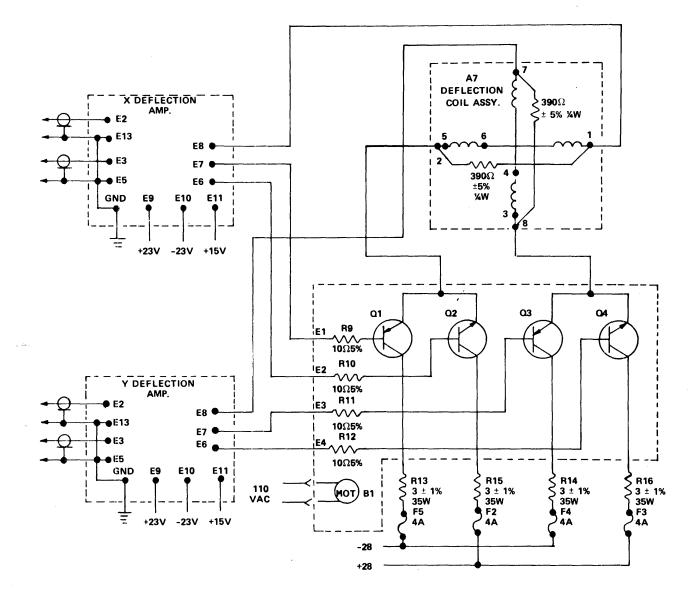

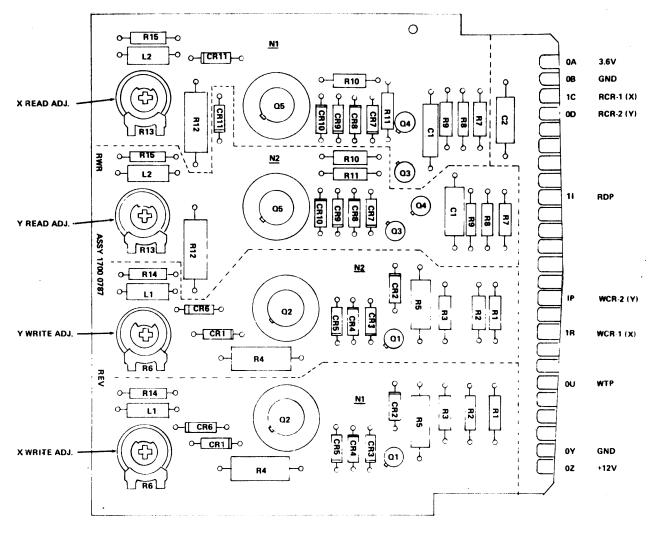

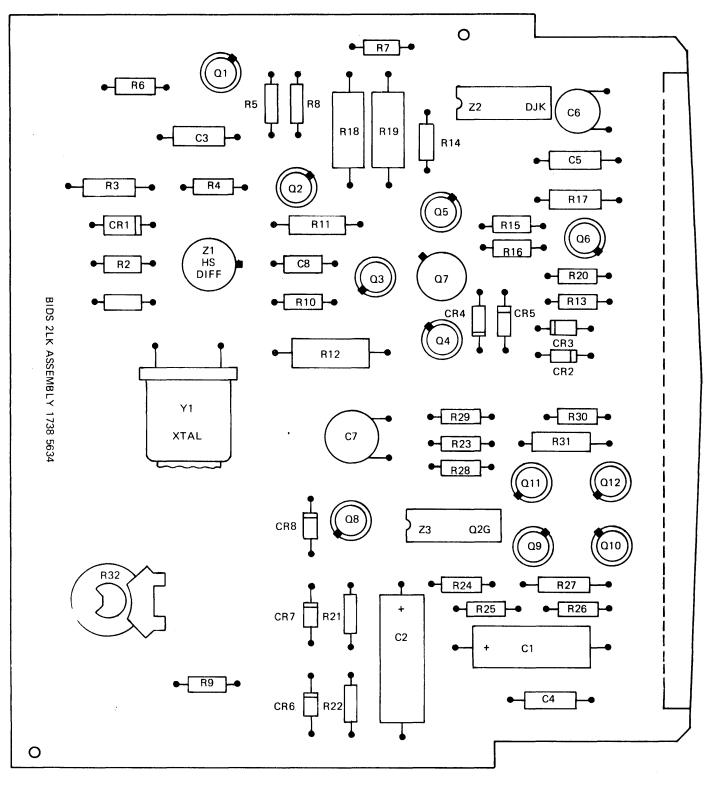

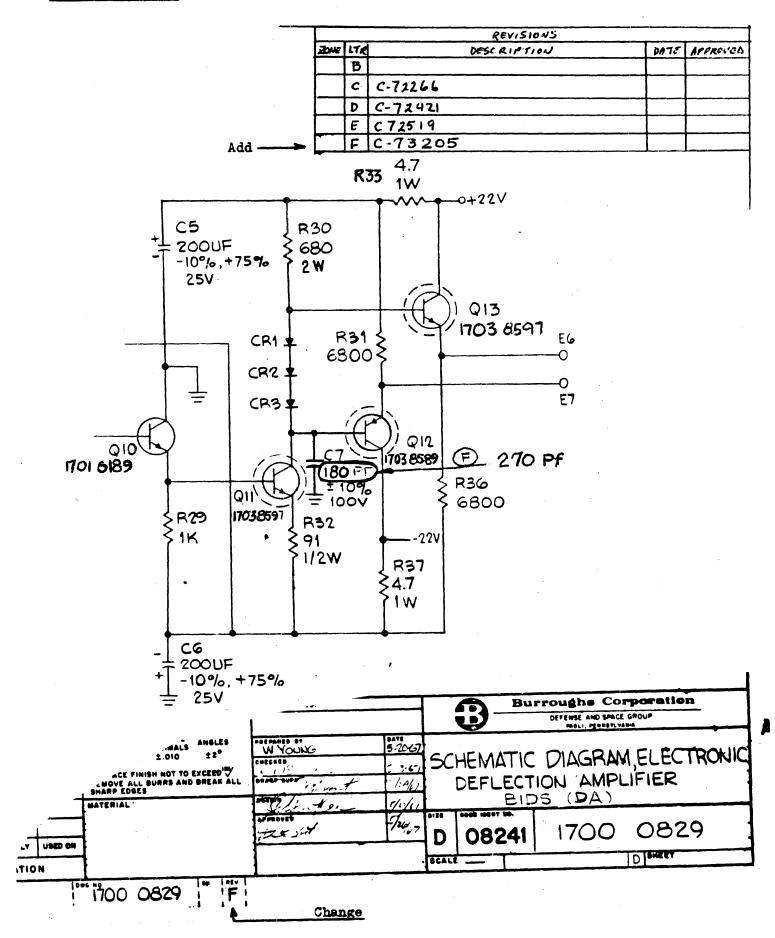

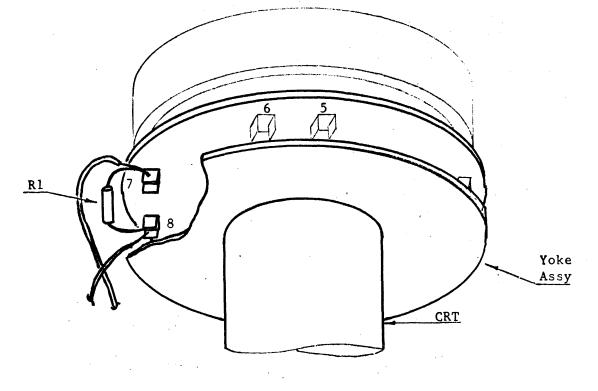

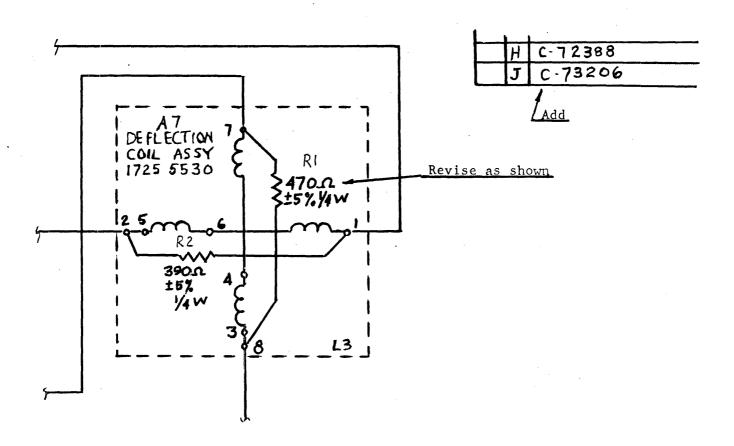

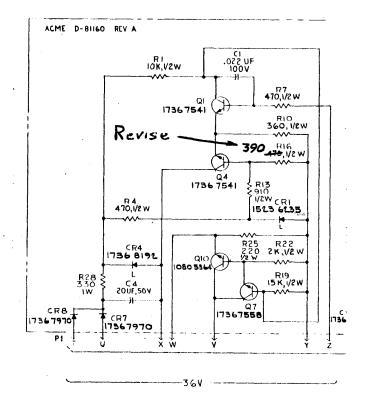

| Deflection Amerilifian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |      |     | . 23        | ł  |

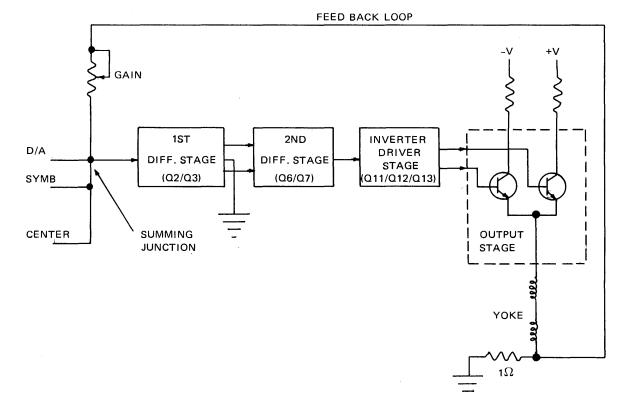

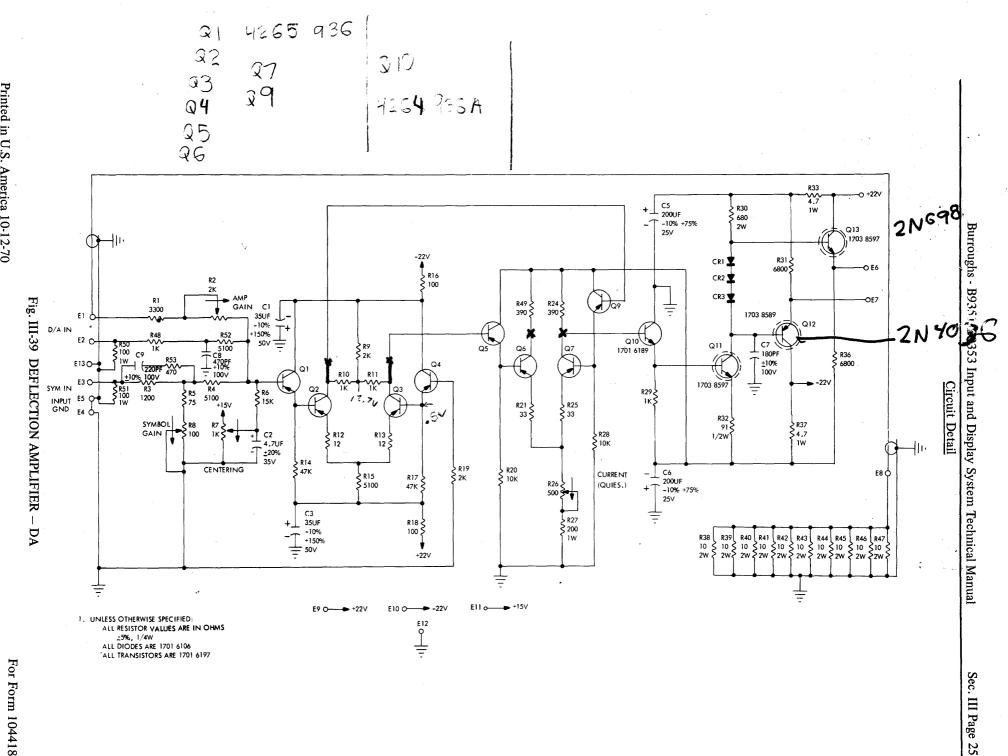

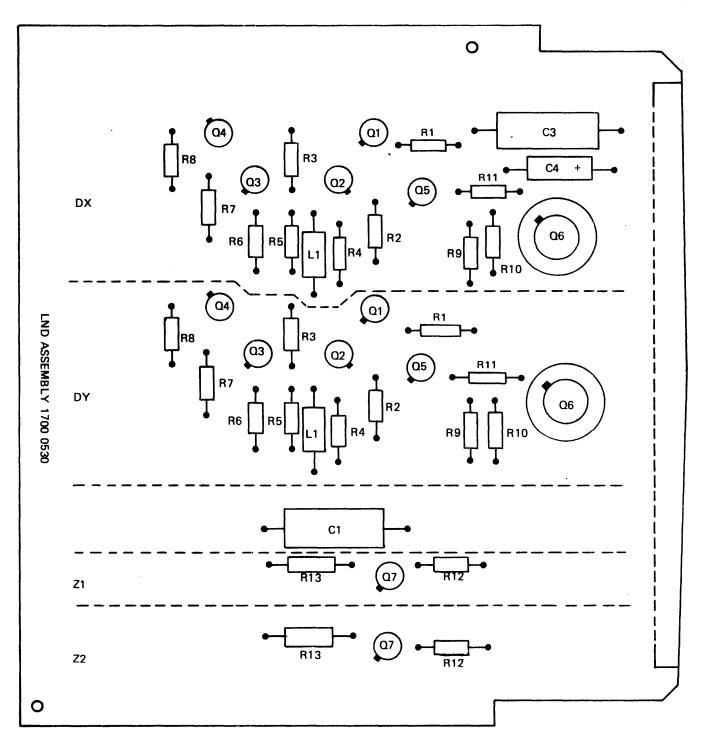

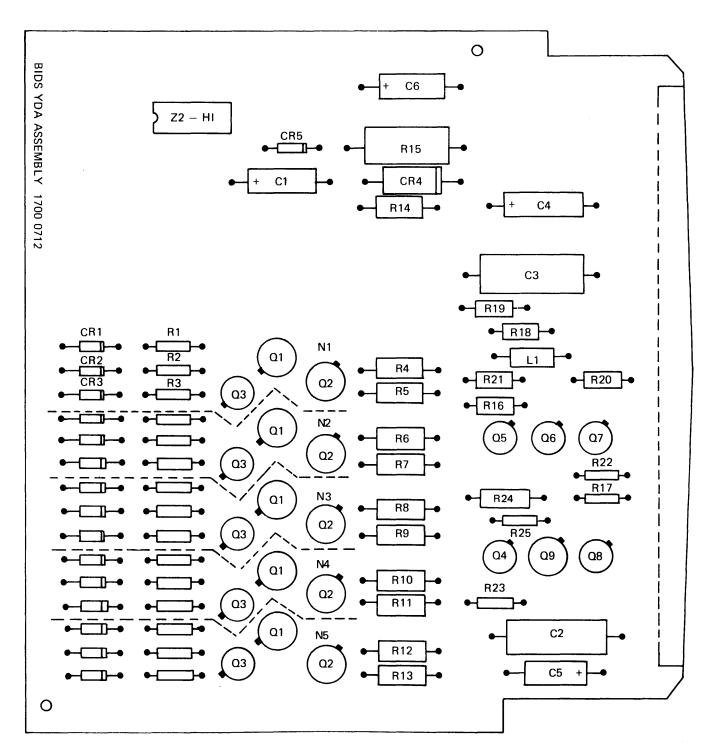

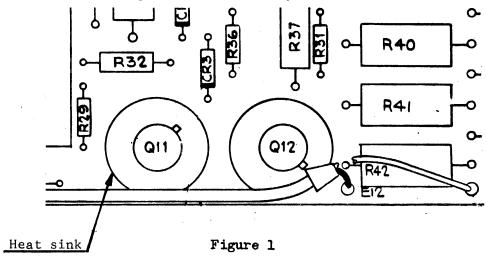

| Deflection Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •   | •••  | •   | . 20        |    |

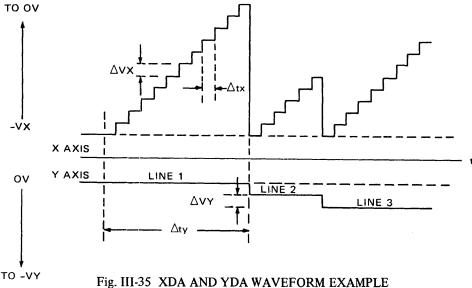

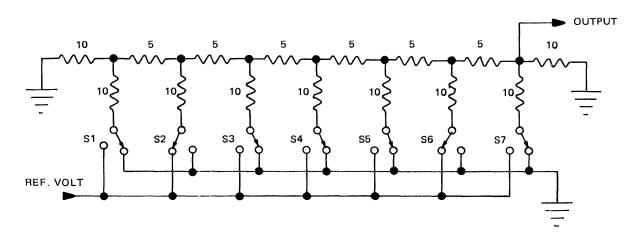

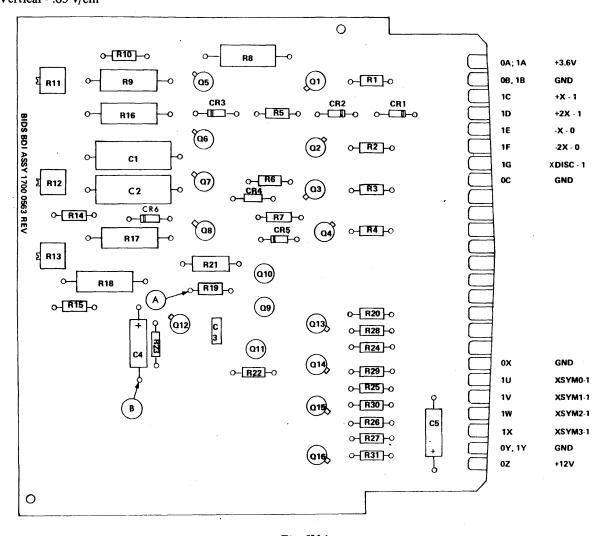

| Digital-to-Analog Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | • •  | •   | . 20        |    |

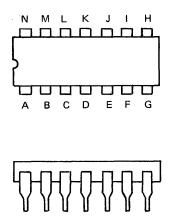

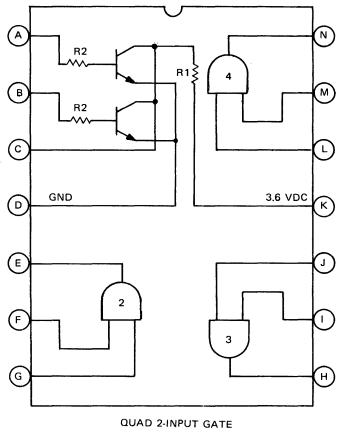

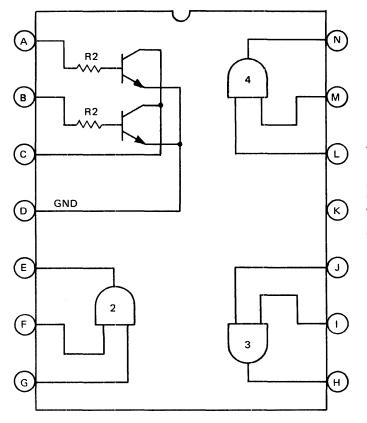

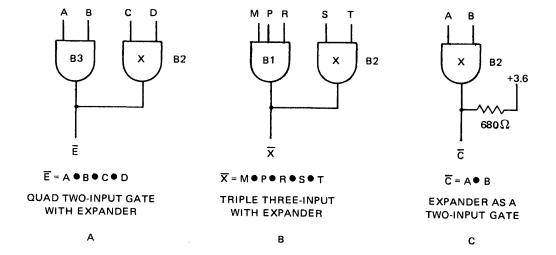

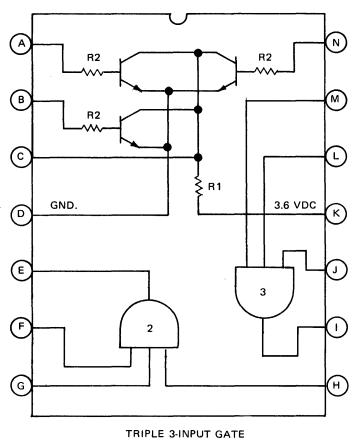

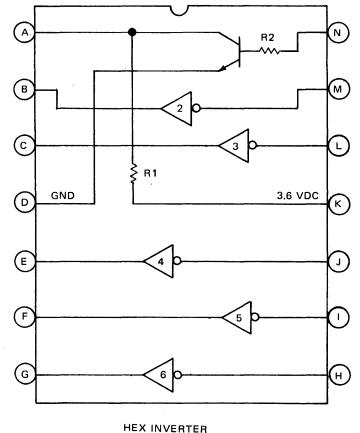

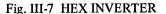

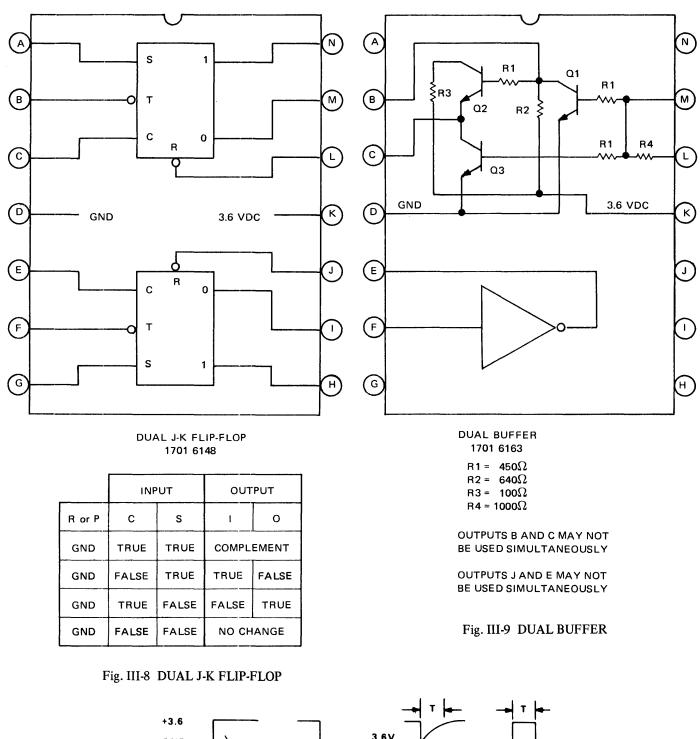

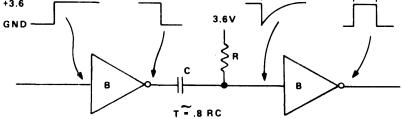

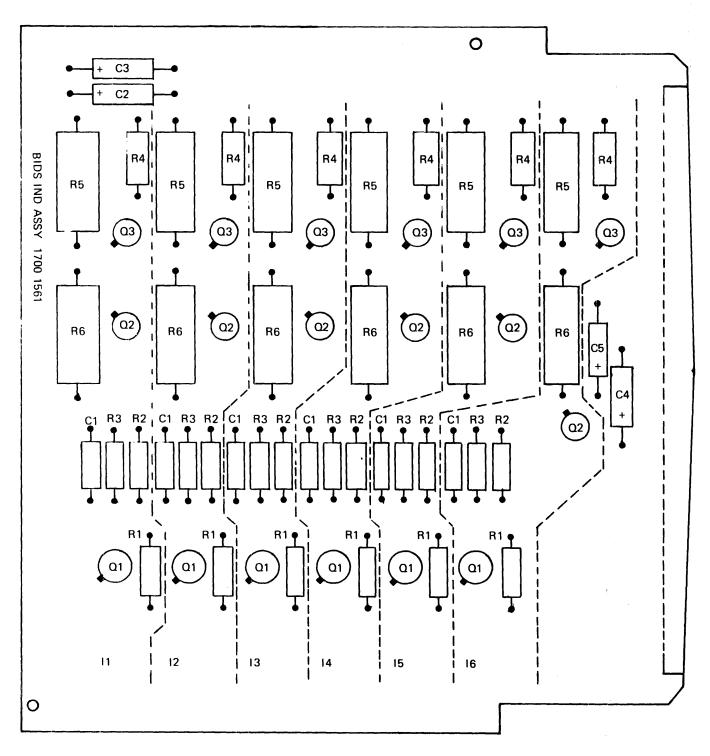

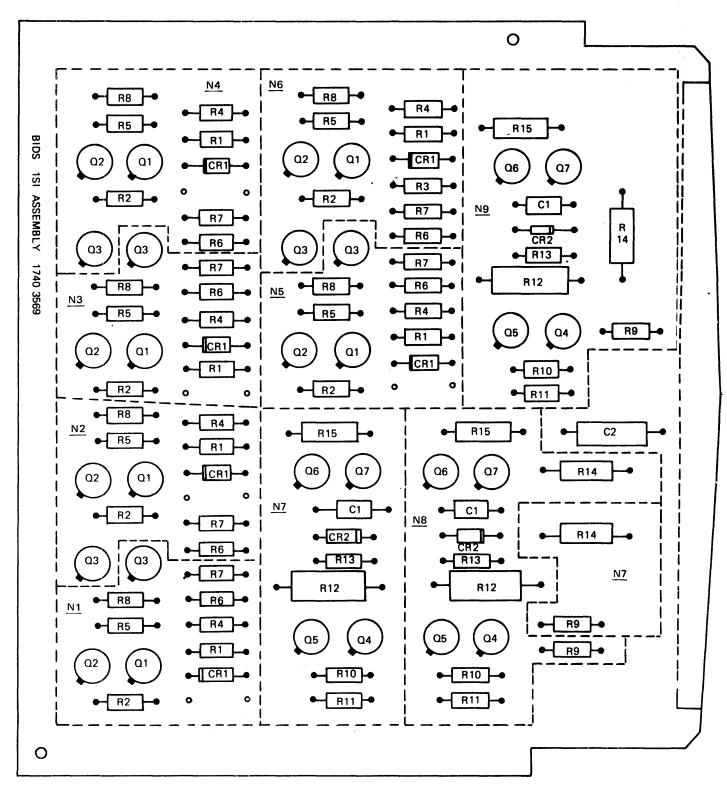

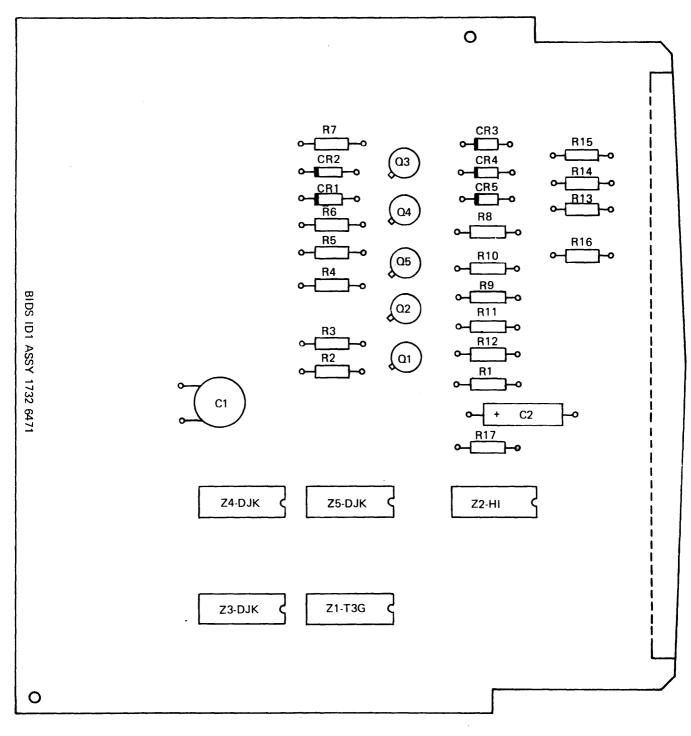

| Logical Elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | •••  |     | . 1         |    |

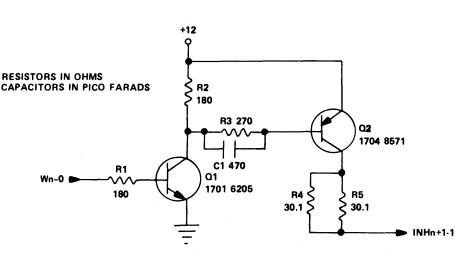

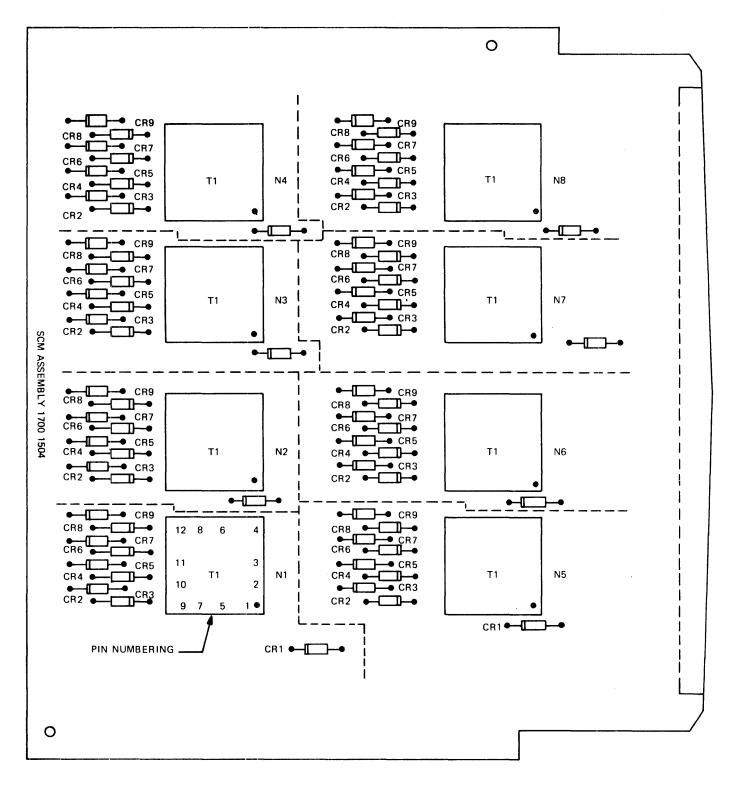

| Memory Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | • •  | •   | . 14        |    |

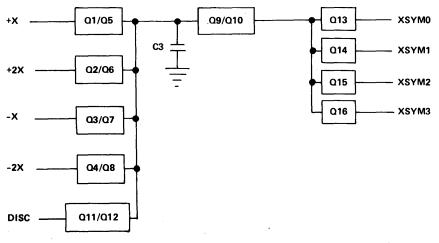

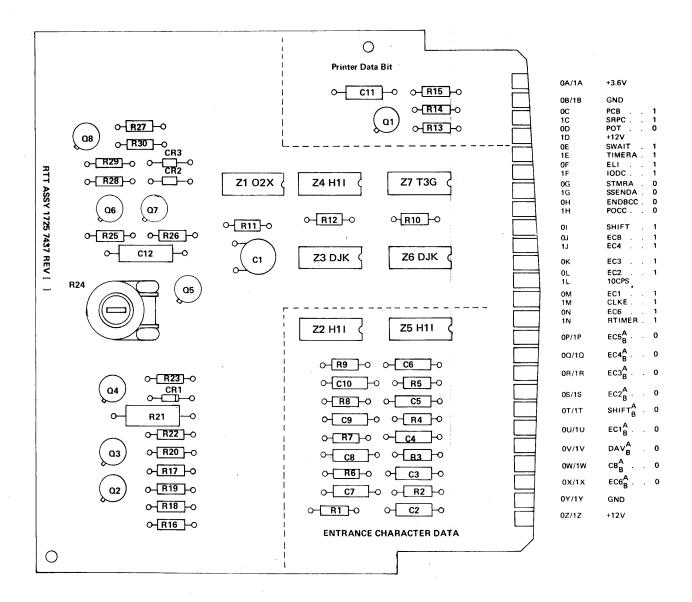

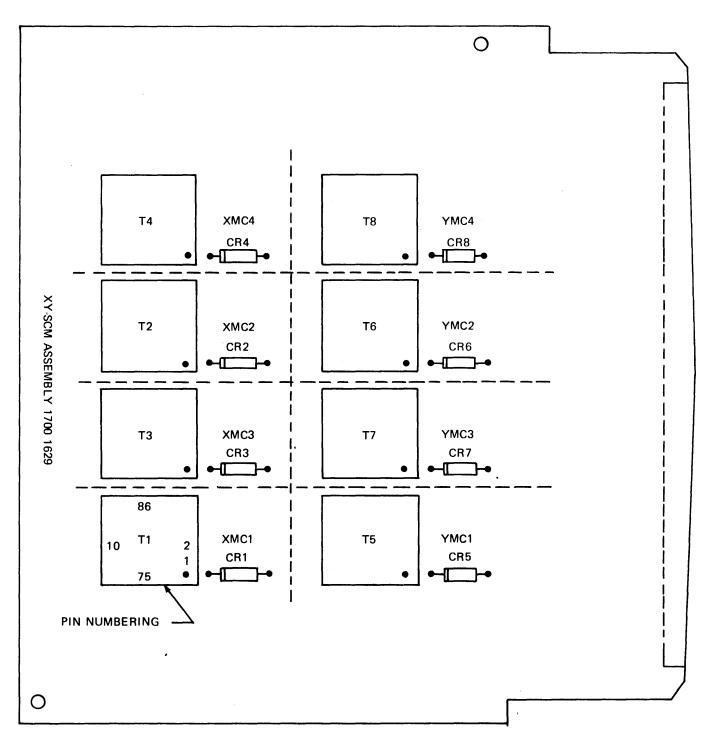

| Symbol Generator Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | • •  | •   | . 14        |    |

| ADJUSTMENTS – SECTION IV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |      |     |             |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |      |     |             |    |

| Control Unit Adjustments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |      |     | . 1         |    |

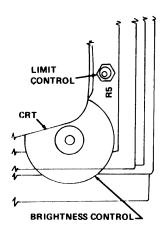

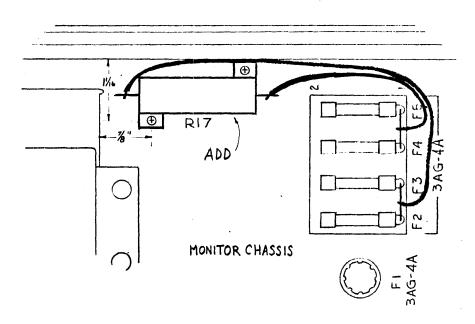

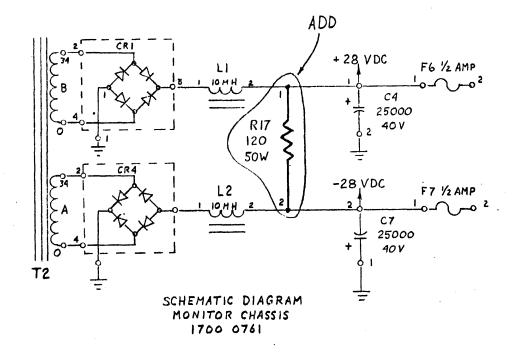

| Monitor Adjustments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |      |     | . 6         |    |

| MAINTENANCE PROCEDURES – SECTIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ΝV  | Z    |     |             |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |      |     | 22          | ,  |

| Fault Isolation Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |      |     | . 23        | 5  |

| INSTALLATION PROCEDURES – SECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ON  | I VI |     |             |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |      |     |             |    |

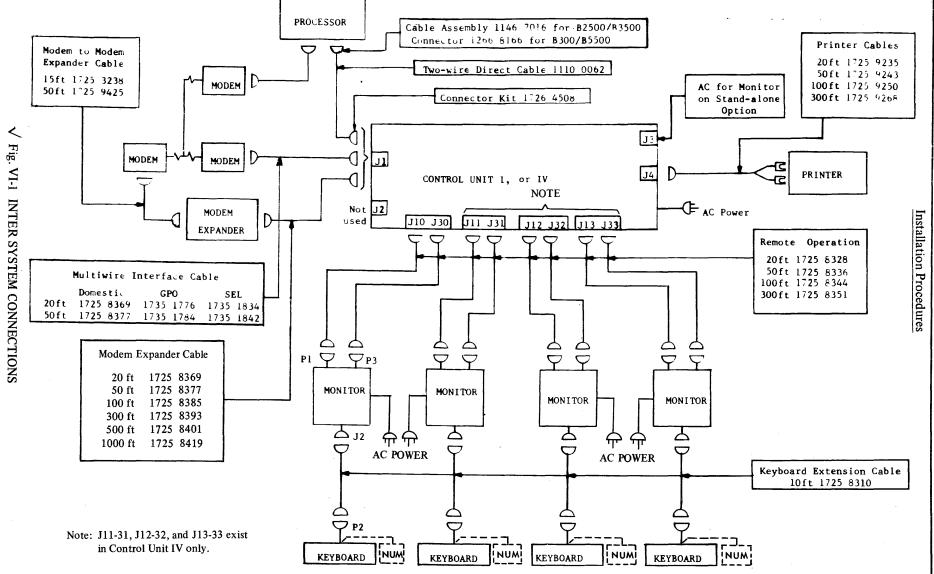

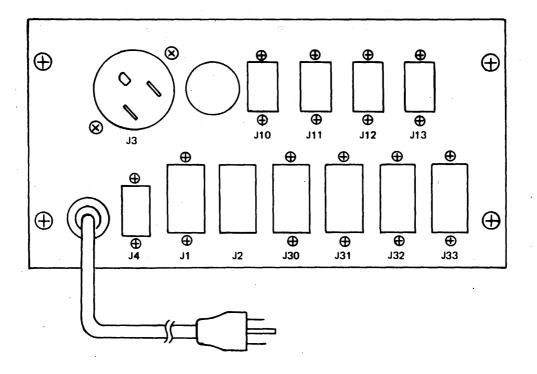

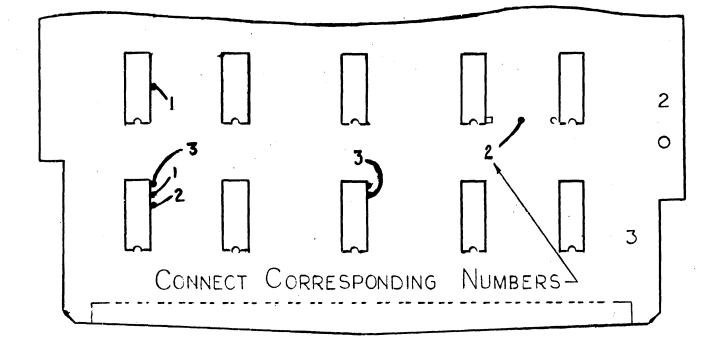

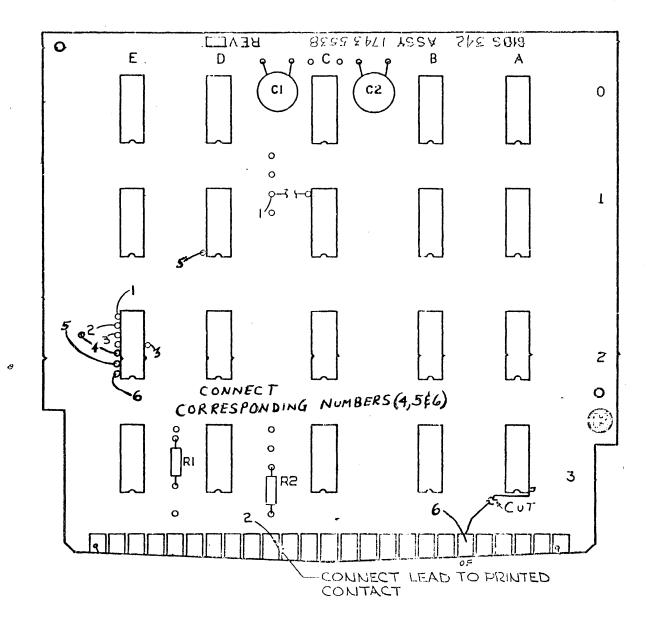

| Interunit Cabling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |      | • • | •           | 1  |

| Special Wiring and Cabling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | •    | • • | • •         | 5  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |      |     |             |    |

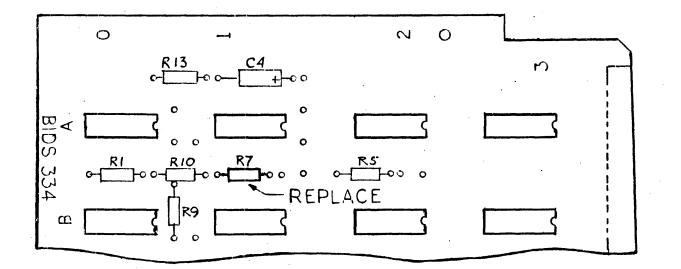

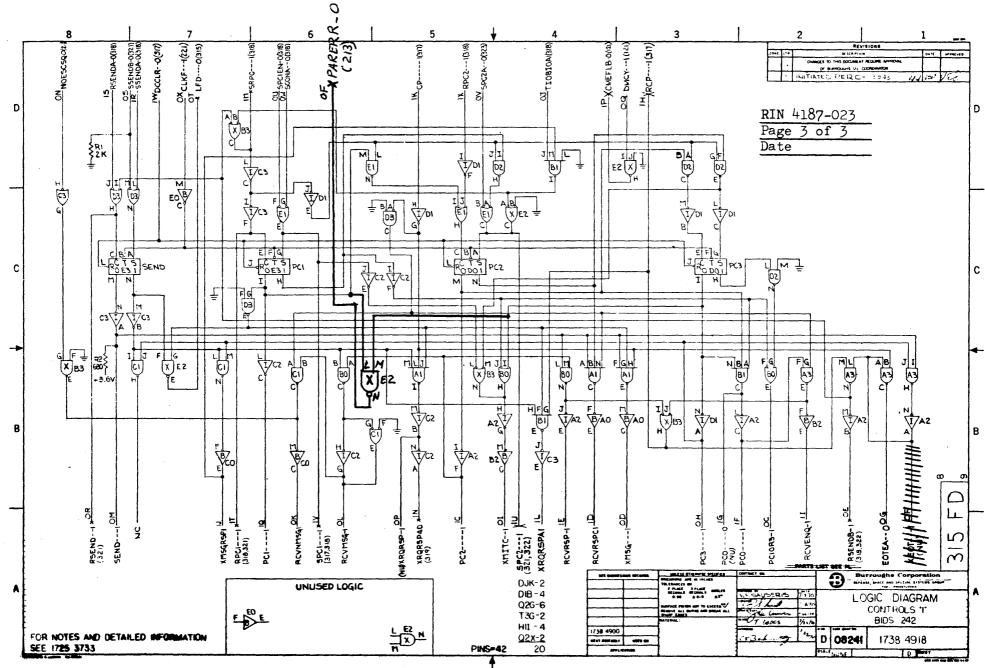

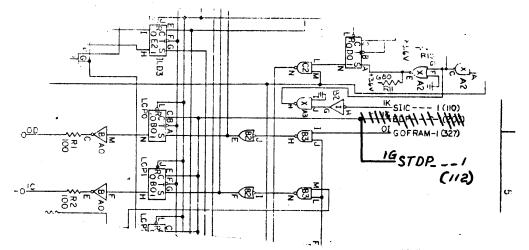

| RELIABILITY IMPROVEMENT NOTICES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | SEC  | TIC | <u>)N V</u> | II |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |      |     |             |    |

| Index – RIN/EI-EWI-ECN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |      |     | •           |    |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |      |     |             |    |

| RIN File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •   | •    |     |             |    |

| Unit Travel Log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |      |     |             |    |

| <b>OPTIONAL FEATURES – SECTION VIII</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |      |     |             |    |

| OPTIONAL FEATURES - SECTION VIII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |      |     |             |    |

| AIC Elin/Elong                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |      |     | . 3         | į  |

| AIC Flip/Flops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •   | •    | ••• | . 1         |    |

| Functional DescriptionFunctional Detail••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••••• <t< td=""><td>•</td><td>•</td><td>•••</td><td>. 1</td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •   | •    | ••• | . 1         |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •   | •    | ••• | . 1         |    |

| General · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •   | •    | ••• | . 1         |    |

| Glossary of Signal Names                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •   | •    | • • | . 3         | ,  |

Printed in U.S. America Revised 7-30-73

i

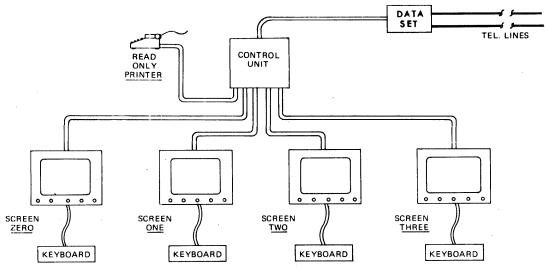

# GENERAL DESCRIPTION

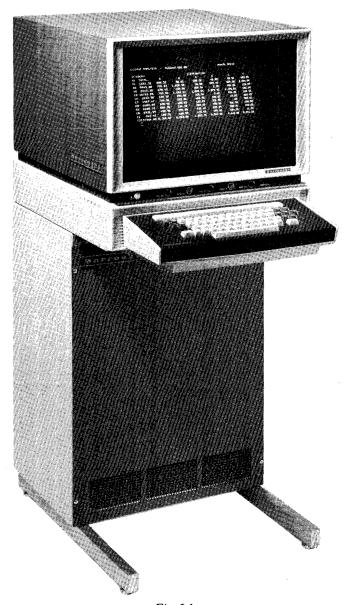

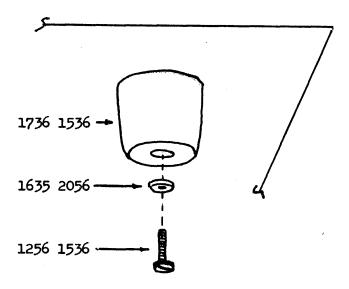

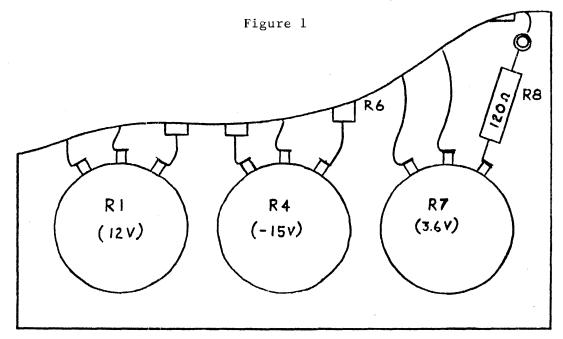

# Fig. I-1

The Burroughs Input and Display Set incorporates a keyboard for data entry and a cathode ray tube (CRT) with a character generator for data display. The display has a repertoire of 66 alphanumeric and special symbols, plus space and non-destructive cursor. The content of the internal storage is sampled, converted to stroke code, and displayed 50 to 60 times per second to produce a display presentation with 2000 character positions arranged as 25 lines of 80 characters each. The memory may be partitioned and the associated logic time-shared by up to four separate, functionally independant CRT displays, each with

an independent keyboard. Figure I-1 illustrates a single monitor in the "Free Standing" configuration.

The data content of the internal storage is generated or altered by a keyboard or incoming message or both. All or part of the content of storage may be transmitted as an outgoing message upon initiation by a keyboard. A multiwire direct system interface is standard. This interface is also compatible with several Bell System data sets utilizing either 2-wire or 4-wire private lines, or DATA-phone<sup>®</sup> for communications circuit or with a 2-wire direct circuit.

DATA-phone service is a data communication transmission service supplied by the Bell System. This service utilizes the switched telephone network and includes the use of the following features of this network: DDD(Direct Distance Dialing) WATS (Wide Area Telephone Service)

PBX (Private Branch Exchange)

Automatic alternate routing.

# PHYSICAL CHARACTERISTICS

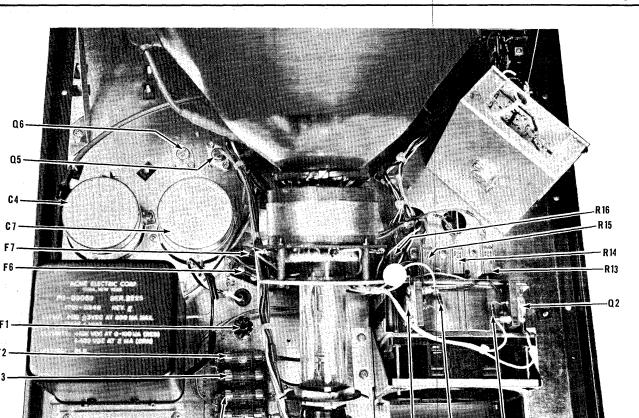

# MONITOR UNIT

The monitor unit houses the 17-inch CRT, all CRT power, CRT driving circuits and CRT controls and status indicators. The brightness control, the only CRT control accessible to the operator, is located on the lower right side. An AC power switch is located on the left front of the monitor.

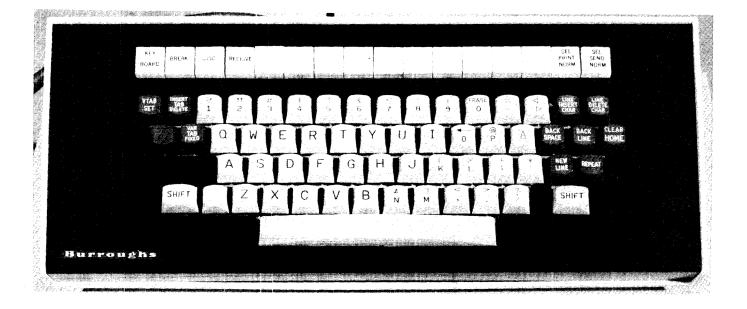

#### **KEYBOARD UNIT**

The keyboard is designed to comply with the touch and geometry common to conventional office typewriters. The keyboard is electrically interlocked so that no more than one key is operative at a time. The keyboard unit also includes control keys above the keyboard proper. The slope top case is designed to be either mounted with the control unit and monitor unit for the free-standing composite assembly or as a separate assembly. An option can be provided to permit remote keyboard operation up to 10 feet from the monitor.

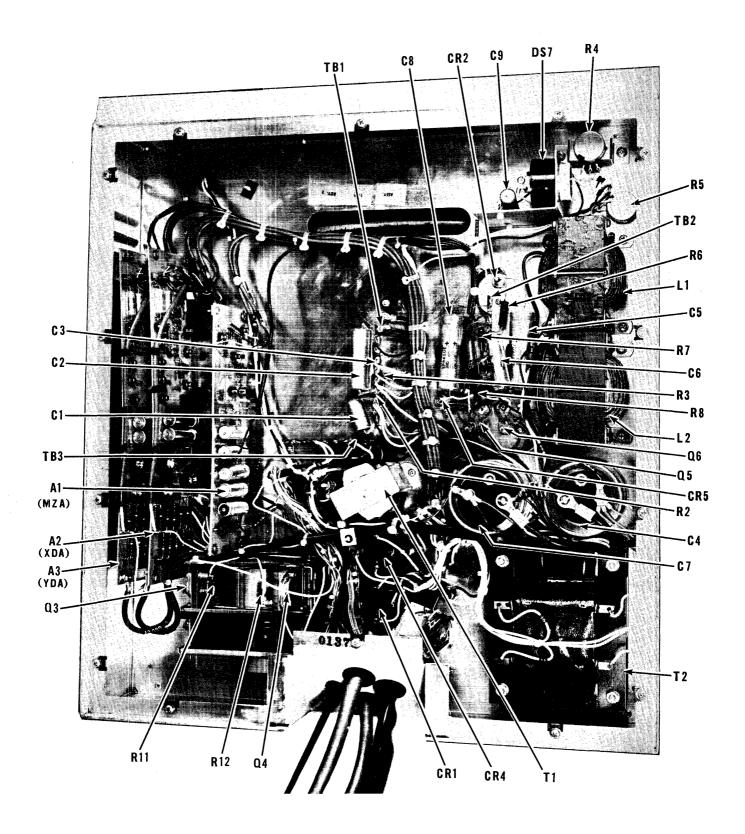

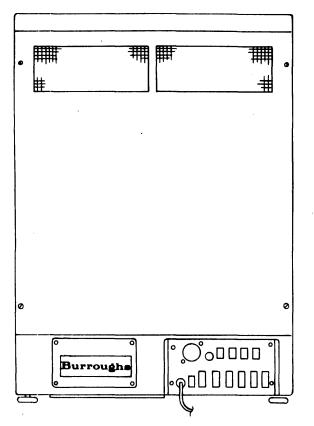

#### CONTROL UNIT

The control unit houses the logic circuits, memory and power supplies. The logic circuits are separated into replaceable circuit cards. An AC power switch is located on the top of the control unit. The unit is intended to rest on the floor.

#### FUNCTIONAL DESCRIPTION

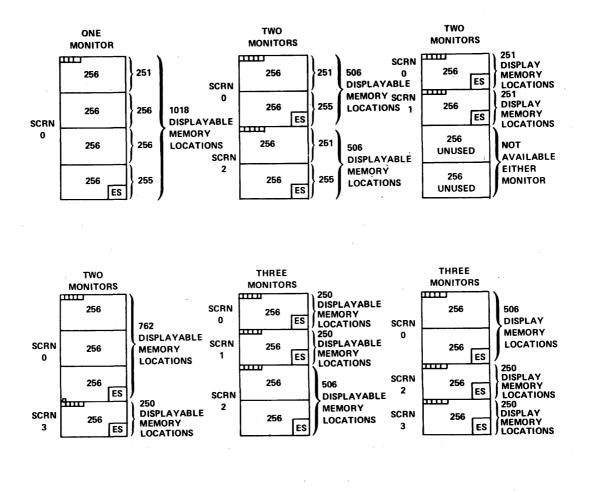

This system contains a magnetic core memory with 1024 six-bit bytes. The entire memory may be associated with a single monitor (CRT) and keyboard or the memory may be divided into four equal sections with each section

<sup>&</sup>lt;sup>®</sup> DATA-phone is registered service mark of AT&T Co.

4

# TABLE I-1 PHYSICAL CHARACTERISTICS

| Power:       | (Control Unit) | 105 to 130 volt                              | s AC, 60 Hz, 40                                        | 00 watts                                 |                                        |

|--------------|----------------|----------------------------------------------|--------------------------------------------------------|------------------------------------------|----------------------------------------|

|              | (Monitor)      | 105 to 130 volt                              | s AC, 60 Hz, 30                                        | 00 watts                                 |                                        |

| Weight:      |                | Monitor Unit                                 | – 100 pounds                                           |                                          |                                        |

|              |                | Keyboard Unit                                | - 5.5 pounds                                           |                                          |                                        |

|              |                | Control Unit                                 | – 140 pounds (                                         | including powe                           | r supplies)                            |

| Dimensions:  |                |                                              | Height<br>(inches)                                     | Width<br>(inches)                        | Depth<br>(inches)                      |

|              |                | Monitor                                      | 18                                                     | 19.2                                     | 22                                     |

|              |                | Keyboard                                     | 3.5                                                    | 17.5                                     | 6.6                                    |

|              |                | Control                                      | 27                                                     | 19.2                                     | 14.5                                   |

| Cooling:     |                | Quiet, low-spee                              | d fans in Monit                                        | or and Control                           | Unit                                   |

| Temperature: |                | +59 to +100 <sup>0</sup> F                   | F (15 to 37.7 <sup>0</sup> C                           | C)                                       |                                        |

| Cabling:     |                | Standard                                     |                                                        | Optional                                 |                                        |

|              |                | Keyboard to M<br>4.5 ft., conn<br>in middle. |                                                        | Keyboard to<br>10 ft. ext                |                                        |

|              |                | Monitor to Con<br>4 ft. assy. pa             |                                                        |                                          | Control<br>)0, 300 ft.<br>s (in pairs) |

|              |                |                                              | lem<br>cables are option<br>00, and 300 ft.            |                                          | be ordered.                            |

|              |                |                                              | lem Expander<br>to interface cab<br>00 ft. cables avai |                                          | are also                               |

|              |                | Control to Syst<br>Two wire di               | em Direct Conr<br>rect connect op                      |                                          |                                        |

|              |                |                                              |                                                        | Control to P<br>20, 50, 10<br>cables ava | 00, 300 ft.                            |

NOTE: For additional cabling information, see Section VI Installation Procedures.

or group of sections associated with a separate monitor and keyboard. Each section or group of sections associated with a particular keyboard is loaded by that keyboard or by an incoming message addressed to the associated monitor. The content of each section or group of sections of the memory is displayed on the associated monitor at a flicker-free refresh rate. All or part of the display content of a section or group of sections of the memory is transmitted as an outgoing message upon command from the associated keyboard.

#### MEMORY

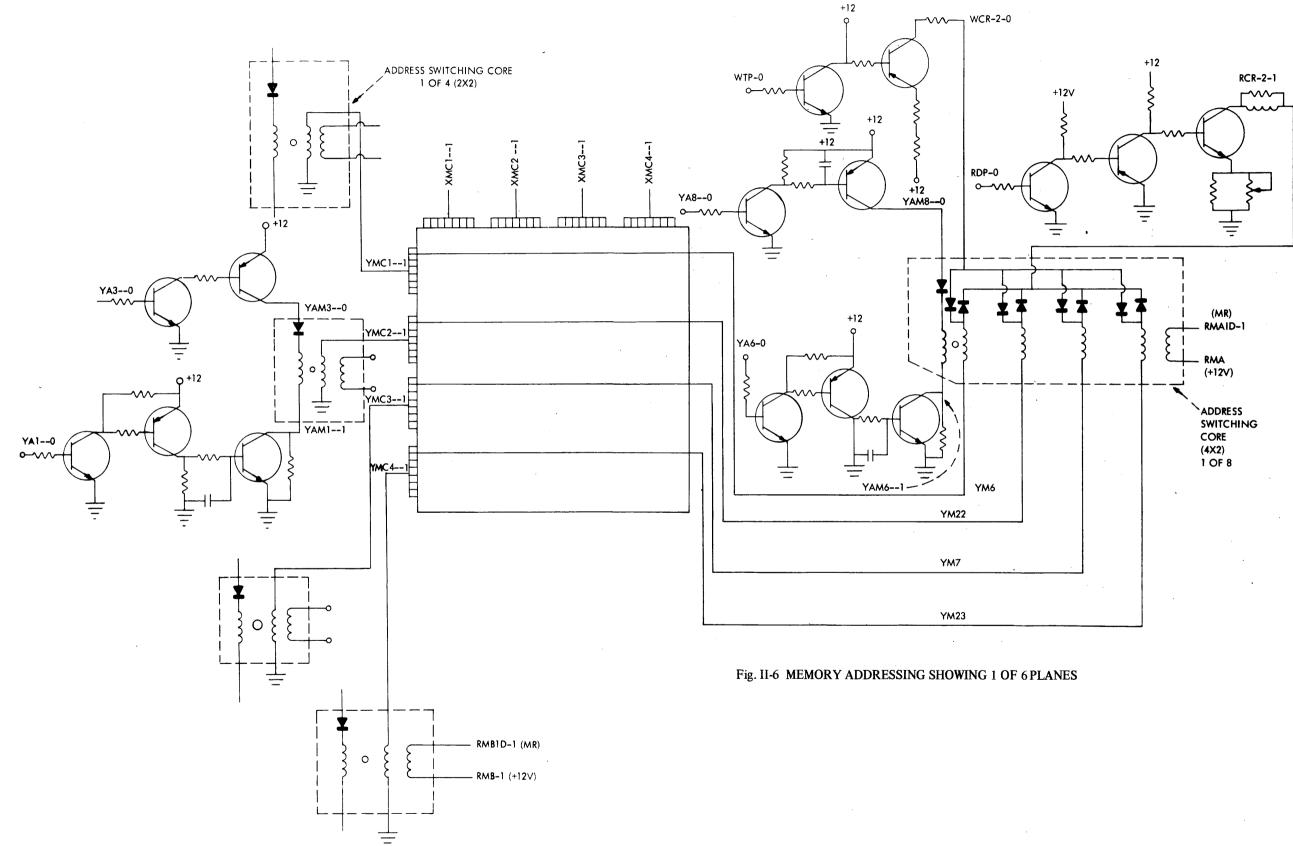

For each monitor-keyboard connected to the Input Display System, six memory bytes are reserved for internal functions and the remainder of the memory assigned to the screen is available for display data. The number of bytes available for display data on a monitor is dependent upon the number of sections of memory assigned to the monitor as follows:

| Number of<br>Sections of Memory<br>Assigned to Monitor | Total Number of<br>Memory Bytes<br>Assigned to Monitor | Number of Display<br>Data Memory Bytes<br>Assigned to Monitor |

|--------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------|

| 1                                                      | 256                                                    | 250                                                           |

| 2                                                      | 512                                                    | 506                                                           |

| 3                                                      | 768                                                    | 762                                                           |

| 4                                                      | 1024                                                   | 1018                                                          |

The display data consists of both graphics and format effectors.

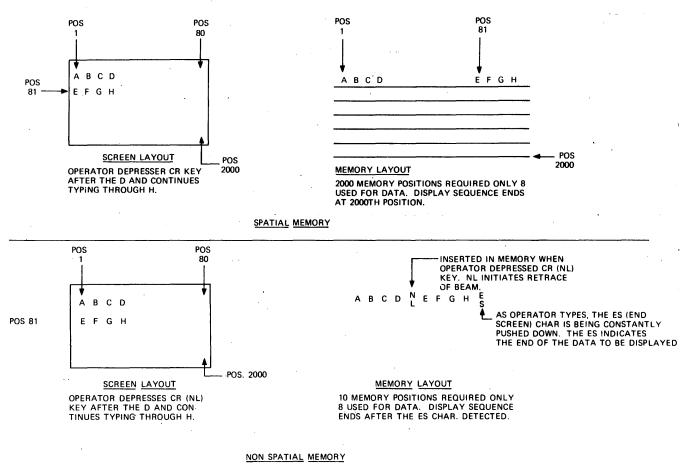

The first display data memory byte corresponds to the upper left screen position. If this character is a graphic, the next memory byte corresponds to the next screen position on the line. Each graphic character in memory assigns the next memory byte to the next screen position across each line and automatically from the end of one line to the beginning of the next line. A format effector in memory assigns the next memory byte to a screen position dependent upon the format effector. For example, the format effector character NL (new line) assigns the next memory byte to the first position of the next line; therefore, the screen positions after the NL screen position do not have an associated byte in memory. These screen positions are referred to as unassigned positions. Two memory bytes are and  $\leftarrow$ . One memory byte is required for each screen for the end-of-screen position. This byte is one of the six mentioned above.

## DISPLAY FORMAT

The memory data content is displayed on a 17-inch CRT. Table I-2 lists the CRT display characteristics. The tube is masked to correspond to the horizontal and vertical extremities of the 80-character by 25-line format, which

yields a 12-inch horizontal by 9-inch vertical, rectangular display presentation.

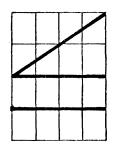

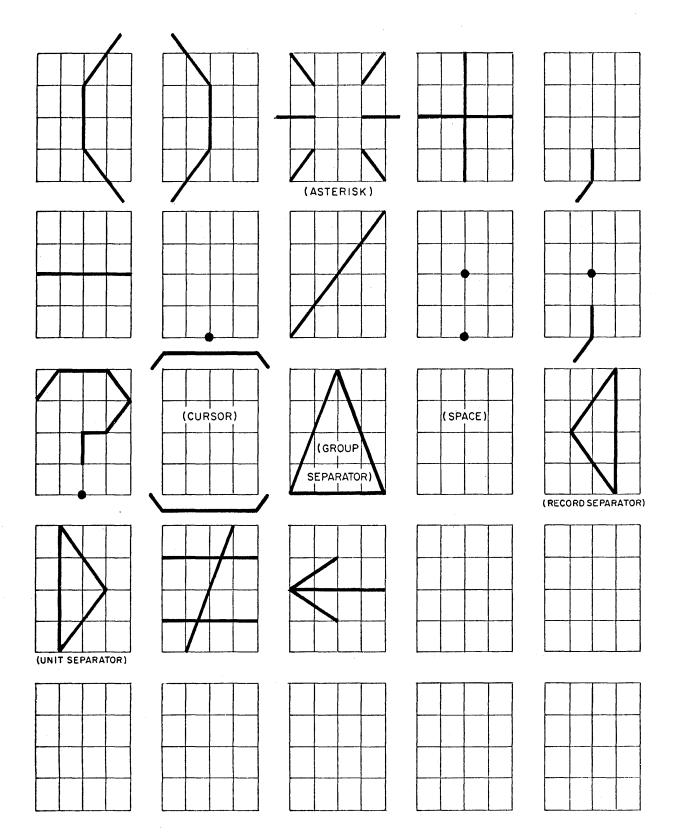

Corresponding to each of the graphic codes stored in memory, the appropriate graphic character is generated by using up to 12 straight-line strokes to form the character. A cursor presentation is also provided. It appears at the character position where the next keyboard or Input/Output operation is to take place. The character is formed on the screen as a set of horizontal brackets,  $\Box$ , that surround the character position, such that the character to be edited remains viewable. Chart I-1 shows the font of the Input Display graphic character set.

## CHARACTER SET AND CODE

Burroughs Input Display System uses a modified limited subset of the USASCII, USASCII X3.4. Figures I-2 and I-3 designate the characters to each seven-bit character code for receive and transmit respectively.

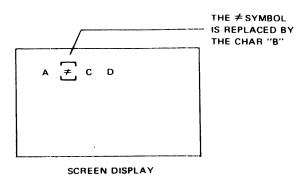

With the exception of five character substitutions, namely the characters  $\geq \leq x$ ,  $\neq$  and + in lieu of the characters !, ', /,  $\wedge$  and -, respectively, the figures agree with the proposed USASCII. These figures differ only in the inclusion of certain characters.

#### **Undesignated** Codes

Received character codes undesignated in Figure I-2 are undefined in the Input Display System. The character codes undesignated in Figure I-3 are not generated by the Input Display System.

#### **OPERATION**

Operation may be considered to consist of four phases: Composition, Send, Wait, and Receive. The modes are independent for each keyboard.

#### COMPOSITION PHASE

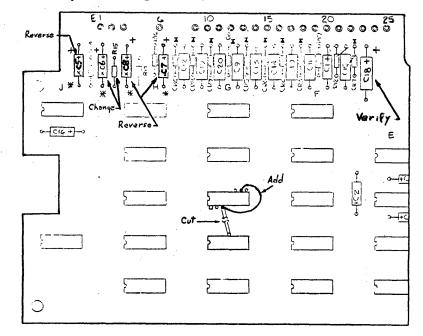

In the composition phase, the operator may compose a message by using the keyboard shown diagrammatically in Figure I-4. The operator has complete freedom to edit and compose information anywhere on the screen (except with forms mode option).

The composition phase is ended by pressing the SEND or PRINT keys, either of which evoke the Send phase.

During composition phase, the KEYBOARD LOCK indicator is OFF. Depressing the KEYBOARD key reverts the terminal to the composition phase. The keyboard consists of graphic, cursor movement, and control keys. Certain of the keys work in conjunction with the SHIFT key.