Burroughs believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

Correspondence regarding this document should be addressed directly to Burroughs Corporation, P.O. Box 4040, El Monte, California 91734, Attn: Publications Department, TIO-West.

# LIST OF EFFECTIVE PAGES

# Page

#### Issue

| Title          |   |   |   |   |   |   |   |   |   |   | Original |

|----------------|---|---|---|---|---|---|---|---|---|---|----------|

| ii             |   |   |   |   |   |   |   | • |   |   | Original |

| iii            |   |   |   |   |   |   |   |   |   |   | Original |

| iv             |   |   |   |   |   |   |   |   |   |   | Blank    |

| v thru ix      |   |   |   |   |   |   |   |   |   |   | Original |

| х              |   |   |   |   |   |   |   |   |   |   | Blank    |

| 1-1 thru 1-30  |   |   |   |   |   |   |   |   |   |   | Original |

| 2-1 thru 2-15  |   |   |   |   |   |   |   |   |   |   | Original |

| 2-16           |   |   |   |   |   |   |   |   |   |   | Blank    |

| 3-1 thru 3-116 |   |   |   |   |   |   |   |   |   |   | Original |

| 4-1 thru 4-9.  |   |   |   |   |   |   |   |   |   |   | Original |

| 4-10           |   |   |   |   |   |   |   |   |   |   | Blank    |

| 5-1 thru 5-15  |   |   |   |   |   |   |   |   |   |   | Original |

| 5-16           |   |   |   |   |   |   |   |   |   |   | Blank    |

| 6-1 thru 6-29  |   |   |   |   |   |   |   |   |   |   | Original |

| 6-30           |   |   |   |   |   |   |   |   |   |   | Blank    |

| A-1 thru A-5   |   |   |   |   |   |   |   |   |   |   | Original |

| A-6            |   |   |   |   |   |   |   |   |   |   | Blank    |

| B-1 thru B-3   |   |   |   |   |   |   |   |   |   |   | Original |

| B-4            |   |   |   |   |   |   |   |   |   |   | Blank    |

| C-1 thru C-7   |   |   |   |   |   |   |   |   |   |   | Original |

| С-8            |   |   |   |   |   |   |   |   | • |   | Blank    |

| D-1 thru D-2   |   |   |   |   |   |   |   |   |   |   | Original |

| E-1            |   |   |   |   |   |   |   |   |   |   | Original |

| E-2            |   |   |   |   |   |   |   |   |   |   | Blank    |

| F-1            |   |   |   |   |   |   |   |   |   |   | Original |

| F-2            |   |   |   |   |   |   |   |   |   |   | Blank    |

| • • • •        | • | • | • | • | • | • | • | • | • | • |          |

# TABLE OF CONTENTS

# Section

| 1 | FUNCTION AND OPERATION                                                                                                                 |   |

|---|----------------------------------------------------------------------------------------------------------------------------------------|---|

|   | General Description                                                                                                                    | 1 |

|   | Basic Capabilities                                                                                                                     | 2 |

|   | Operation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$ -4                                                                 | 4 |

|   | Main Features                                                                                                                          | 4 |

|   | Configuration Control                                                                                                                  | 4 |

|   | Escape (ESC) Functions                                                                                                                 | 4 |

|   | Data Comm Pointer         1         1         1         1                                                                              |   |

|   | Display Capacity (Working Data Field)                                                                                                  | - |

|   | Status Line Display                                                                                                                    | - |

|   | Negative Video (Non-Forms)                                                                                                             |   |

|   |                                                                                                                                        |   |

|   |                                                                                                                                        | - |

|   |                                                                                                                                        | - |

|   |                                                                                                                                        | - |

|   | Bright Video (SUB) $\dots \dots \dots$ | - |

|   | Reverse Video (SO)         1-7                                                                                                         |   |

|   | Blink Video (CAN)                                                                                                                      |   |

|   | Secure Video (EM)                                                                                                                      |   |

|   | Cursor Display                                                                                                                         |   |

|   | Cursor Positioning                                                                                                                     |   |

|   | Edit Functions                                                                                                                         | 7 |

|   | Character Insert by Line or Page                                                                                                       | 7 |

|   | Character Delete by Line or Page                                                                                                       | 8 |

|   | Line Insert Deletes                                                                                                                    | 8 |

|   | Line Movement Up/Down                                                                                                                  | 8 |

|   | Clear to End of Line or Page                                                                                                           | 8 |

|   | Lower Case Enable or Disable                                                                                                           |   |

|   | Search Mode (Item Correction)                                                                                                          |   |

|   | Page Roll Up or Down                                                                                                                   |   |

|   | Display Scroll Up/Down                                                                                                                 |   |

|   |                                                                                                                                        |   |

|   |                                                                                                                                        |   |

|   |                                                                                                                                        | - |

|   | Right Justify Field                                                                                                                    |   |

|   | Field Overflow Inhibit                                                                                                                 |   |

|   | Transmission of Control Messages                                                                                                       |   |

|   | Data Transmission Variable                                                                                                             |   |

|   | I/O Interfaces                                                                                                                         |   |

|   | Asynchronous Data Communication                                                                                                        |   |

|   | Synchronous Data Communication                                                                                                         |   |

|   | Software Controllable Escape (ESC) Functions                                                                                           |   |

|   | Remote Controller Initiated Configuration Changes                                                                                      |   |

|   | Local Input                                                                                                                            | 6 |

|   | Keyboard Subsystem                                                                                                                     | 6 |

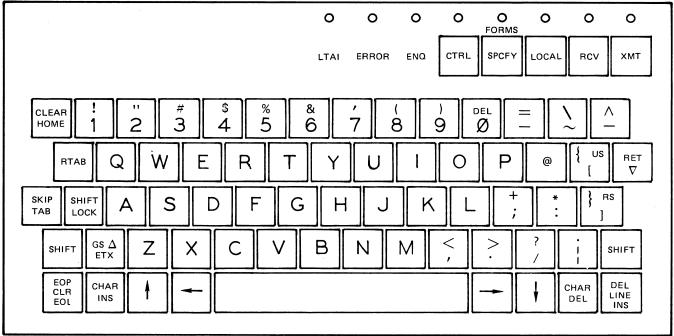

|   | Keyboard                                                                                                                               | 6 |

|   | Keyboard Configurations                                                                                                                | 7 |

|   | U.S. Typewriter Keyboards                                                                                                              | 8 |

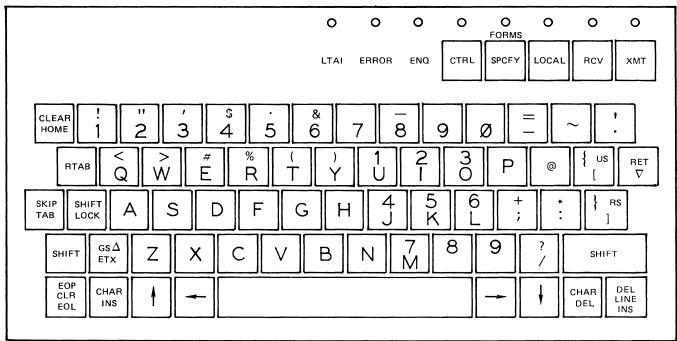

|   | Data Preparation Keyboards                                                                                                             |   |

|   | Local Output                                                                                                                           | - |

|   | Display Subsystem                                                                                                                      |   |

|   |                                                                                                                                        |   |

### TABLE OF CONTENTS (Cont)

| Section | Pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ge         |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|         | Screens 1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.1        |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -          |

|         | Operator Controls and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

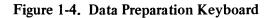

|         | Keyboard Security Locks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

|         | Operator Cleaning Procedures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

|         | Character Sets and Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29         |

| 2       | INSTALLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

|         | Site Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-1        |

|         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-1        |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-1        |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-1        |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-2        |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-2        |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-2        |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2<br>2-2   |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2<br>2-2   |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -3         |

|         | for the second sec | -4         |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-5        |

|         | $\mathbf{I}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-6        |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-6        |

|         | CTRL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-7        |

|         | CTRL R H H1 H2 H3 H4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-7        |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -7         |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -8         |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -8         |

| ,<br>N  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -8         |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -9         |

|         | Sample Terminal Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

|         | Preprogrammed Error Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15         |

| 3       | DOCUMENTATION AND COMPONENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

|         | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -1         |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -2         |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |