# Burroughs B 700 SYSTEMS

B 720 Systems

**REFERENCE MANUAL**

# Burroughs B 700 SYSTEMS

# **B 720 Systems**

**REFERENCE MANUAL**

**Burroughs Corporation**

Detroit, Michigan 48232

#### COPYRIGHT © 1975 BURROUGHS CORPORATION

#### AA615386

Burroughs believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

Correspondence regarding this document should be forwarded using the Remarks Form at the back of the manual, or may be addressed directly to Systems Documentation, Technical Information Organization, Burroughs Corporation, 200 West Lancaster Ave., Wayne, Pa. 19087.

# TABLE OF CONTENTS

| Section | Title                                                     | Page         | Section   | Title                                                    | Page       |

|---------|-----------------------------------------------------------|--------------|-----------|----------------------------------------------------------|------------|

|         | INTRODUCTION                                              | v            |           | D. D. mint or                                            | 0.5        |

| 1       | SYSTEM DESCRIPTION                                        | 1-1          |           | B Register<br>Memory Information Register (MIR)          | 3-5<br>3-5 |

|         | General                                                   | 1-1          |           | Adder                                                    | 3-5        |

|         | System Equipment Configuration and                        | 1-1          |           | Barrel Switch (BSW)                                      | 3-5        |

|         | Characteristics<br>Peripheral Device Subsystems           | 1-2          |           | Memory Control Unit                                      | 3-5        |

|         | Console Subsystem                                         | 1-2          |           | Microprogram Count Register                              | 3-5        |

|         | Magnetic Disk Subsystem                                   | 1-6          |           | (MPCR)                                                   |            |

|         | Magnetic Tape Subsystem                                   | 1-6          |           | Alternate Microprogram Count                             | 3-5        |

|         | Punched-Card Reader Subsystems                            | 1-6          |           | Register (AMPCR)                                         | 0.5        |

|         | Punched Paper Tape/Edge-Punched                           | 1-9          |           | Incrementer<br>Microprogram Address Controls             | 3-5<br>3-5 |

|         | Card (PPT/EPC) Subsystems                                 |              |           | (MPAD)                                                   | 9-9        |

|         | Punched-Card Reader/Punch/                                | 1-9          |           | Memory Address Register (MAR)                            | 3-5        |

|         | Recorder Subsystems                                       | 1.0          |           | Base Register 1 (BR1)                                    | 3-5        |

|         | Line Printer Subsystems                                   | 1-9          |           | Base Register 2 (BR2)                                    | 3-5        |

|         | Reader Sorter Subsystem<br>Data Communications Subsystems | 1-9<br>1-10  |           | Output Selection Gates (OS)                              | 3-6        |

|         | Communications Processor Subsystems                       | 1-10         |           | Counter (CTR)                                            | 3-6        |

|         | Single-Line Data Communications                           | 1-11         |           | Literal Register (LIT)                                   | 3-6        |

| ·       | Subsystem                                                 |              |           | MAR/CTR Input Selection Gates                            | 3-6        |

| 2       | PROGRAMMING SYSTEM                                        | 2-1          |           | Control Register                                         | 3-6        |

| 2       | DESCRIPTION                                               | 2-1          |           | Control Unit                                             | 3-6        |

|         | General Concetps                                          | 2-1          |           | Shift Amount Register                                    | 3-6<br>3-6 |

|         | High-Level Languages                                      | 2-1          |           | Condition Register and Select<br>SIGN-SAVE Flip-Flop     | 3-0<br>3-6 |

|         | Interpreters                                              | 2-1          |           | Clock Generator and Clock Driver                         | 3-0<br>3-6 |

|         | Delayed Binding                                           | <b>2-</b> 1  |           | External Operation Controls (EO)                         | 3-6        |

|         | Breakout                                                  | 2-1          |           | Error Detection                                          | 3-7        |

|         | Programming System Structure                              | 2-2          |           | I/O Control Section                                      | 3-7        |

|         | System Software                                           | 2-2          |           | Device Addressing                                        | 3-8        |

|         | Initialization Programs                                   | 2-2          |           | Interrupt Handling                                       | 3-8        |

|         | Interpreters                                              | 2-2          |           | Memory Loading                                           | 3-9        |

|         | Interpreter Firmware<br>Utility Programs                  | 2-2<br>2-3   |           | Direct Memory Access                                     | 3-9        |

|         | General Sort Program                                      | 2-3<br>2-3   | 4         | DATA COMMUNICATIONS                                      | 4-1        |

|         | COBOL Compiler                                            | 2-3<br>2-3   |           | SUBSYSTEMS                                               |            |

|         | RPG Compiler                                              | 2-3          |           | General                                                  | 4-1        |

|         | NDL Compiler                                              | 2-4          |           | Programmable Communications                              | 4-1        |

|         | Virtual Machine Description                               | 2-4          |           | Processor                                                |            |

|         | Concepts and Structure                                    | 2-4          |           | Subsystem Interface                                      | 4-1        |

|         | Memory Organization                                       | 2-4          |           | Functional Operation<br>Firmware/Software Considerations | 4-2<br>4-3 |

|         | Interpreter Memory                                        | 2-4          |           | Interface Communications                                 | 4-3<br>4-4 |

|         | User Memory                                               | 2-4          |           | Operational Indicators                                   | 4-5        |

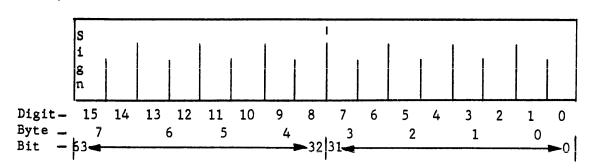

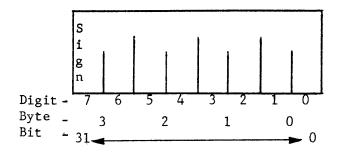

|         | Word Organization<br>Instruction Format                   | 2-6<br>2-8   |           | File Inquiry Subsystem (Single-Line                      | 4-5        |

|         | Virtual Machine Registers                                 | 2-0<br>2-11  |           | Data Communications)                                     | -          |

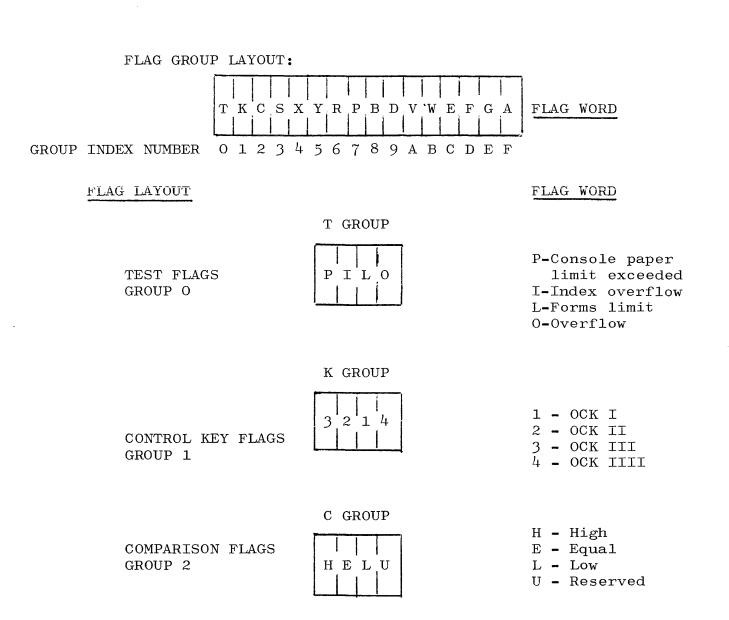

|         | Virtual Machine Condition Flags                           | 2-11<br>2-11 |           | System Equipment and Software                            | 4-6        |

|         | A Group (Accumulator Flags)                               | 2-11         |           | Requirements                                             |            |

|         | C Group (Comparison Flags)                                | 2-12         |           | Firmware Requirements                                    | 4-6        |

|         | T Group (Test Flags)                                      | 2-12         |           | Inquiry Interrupt Controller                             | 4-6        |

|         | K Group (Operator Control Keys)                           | 2-12         |           | Inquiry Controller/Handler                               | 4-6        |

|         | G Group (I/O Error Recovery)                              | 2-12         | 5         | Inquiry System Programming<br>READER SORTER SUBSYSTEM    | 4-7<br>5-1 |

| 3       | SYSTEM PROCESSOR                                          | 3-1          | 5         | General                                                  | 5-1        |

| -       | DESCRIPTION                                               |              |           | Reader Sorter Subsystem Operation                        | 5-1        |

|         | General                                                   | 3-1          |           | Reader Sorter Characteristics                            | 5-3        |

|         | Memory Section                                            | 3-2          | A         |                                                          |            |

|         | Firmware Store Section                                    | 3-2          | Apdx<br>A | ABBREVIATIONS, ACRONYMS,<br>AND TERMS                    | A-1        |

|         | Data/Program (User) Memory                                | 3-3          |           |                                                          |            |

|         | Section                                                   |              | Apdx      | INSTRUCTION LIST                                         | B-1        |

|         | Shared Memory Controls                                    | 3-3          | В         |                                                          |            |

|         | S-Level Memory Operation                                  | 3-3          | Apdx      | VIRTUAL MACHINE REGISTERS                                | C-1        |

|         | Memory Standby Mode<br>Processor Section                  | 3-3          | C         |                                                          | -          |

|         | Logic Unit                                                | 3-3<br>3-3   | Apdx      | FLAG LIST                                                | D-1        |

|         | A Registers (A1, A2 and A3)                               | о-о<br>3-3   | D         |                                                          | 1-1        |

|         |                                                           | 0-0          | -         |                                                          |            |

----

# LIST OF ILLUSTRATIONS

| Figure | Title                                                     | Page |

|--------|-----------------------------------------------------------|------|

| 1-1    | Typical B 720 Computer System                             | 1-1  |

| 1-2    | B 720 System Interface Configuration                      | 1-2  |

| 1-3    | B 720 Peripheral Subsystem<br>Configurator                | 1-7  |

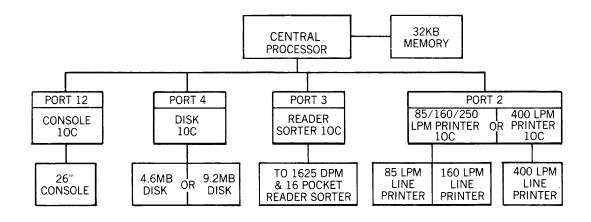

| 1-4    | Data Communications Subsystem<br>Configurator             | 1-10 |

| 2-1    | Typical Memory Allocation                                 | 2-5  |

| 2-2    | Typical Program/Data Memory<br>(CPM/DPM) Allocation       | 2-6  |

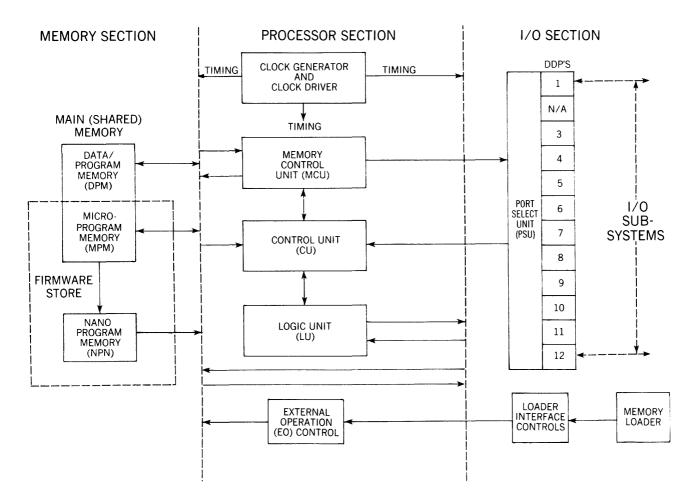

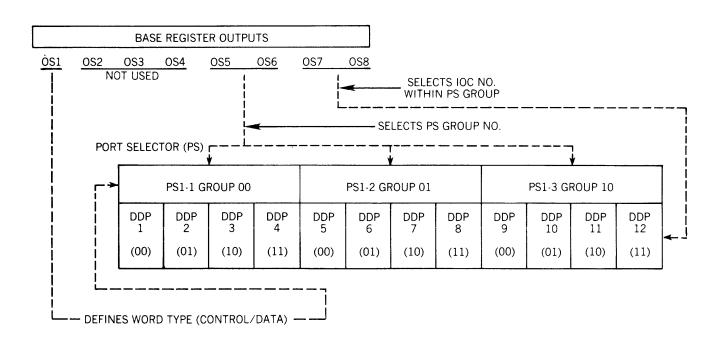

| 3-1    | B 720 Central Processing Unit                             | 3-1  |

| 3-2    | CPU General Functional Block<br>Diagram                   | 3-2  |

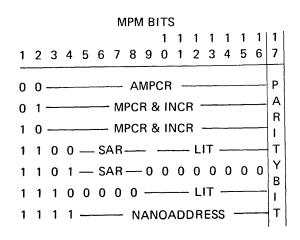

| 3-3    | Microprogram and Nanoprogram<br>Codes                     | 3-4  |

| 3-4    | I/O Device Addressing                                     | 3-8  |

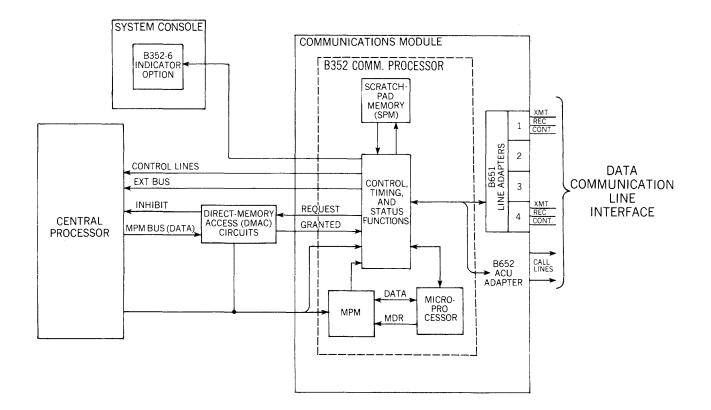

| 4-1    | Multiline Data Communications<br>Subsystem Interface      | 4-1  |

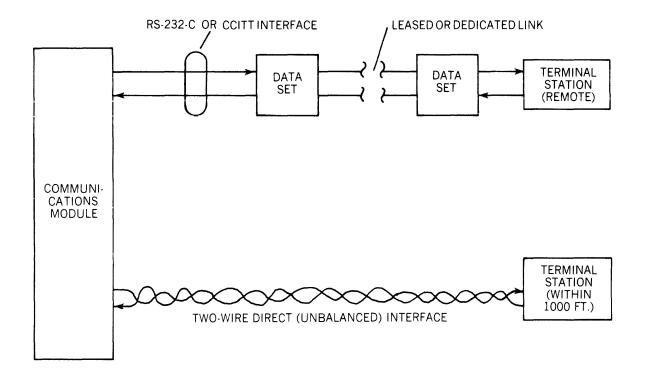

| 4-2    | Terminal Station Interface<br>Configurations              | 4-2  |

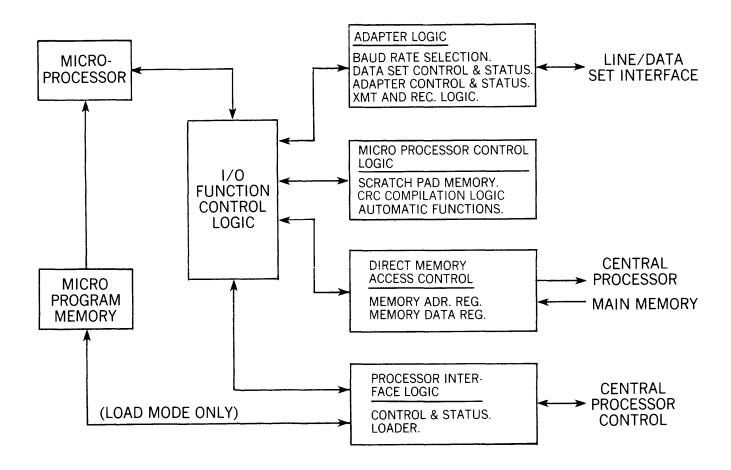

| 4-3    | Communications Processor Functional<br>Block Diagram      | 4-3  |

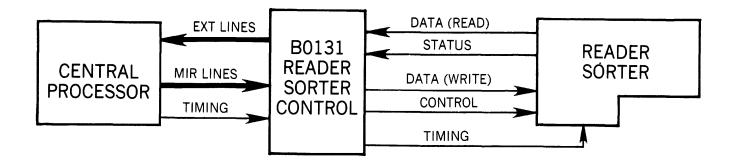

| 5-1    | Basic System Configuration for<br>Reader Sorter Operation | 5-1  |

| 5-2    | Reader Sorter Subsystem Interface                         | 5-2  |

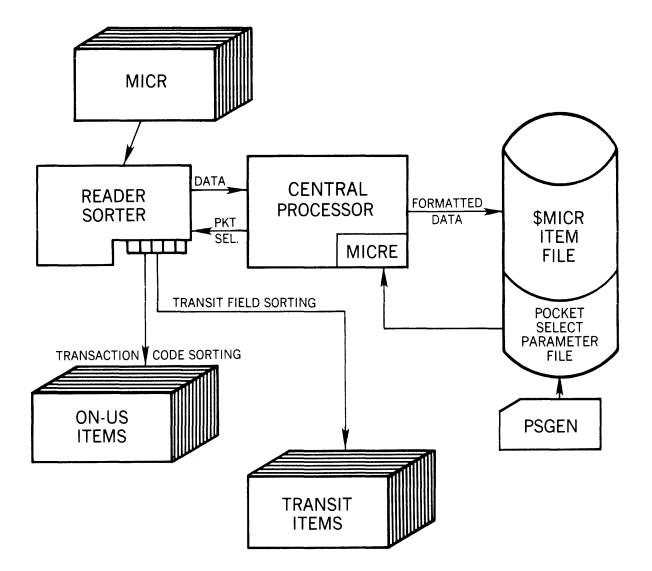

| 5-3    | MICR Entry System                                         | 5-2  |

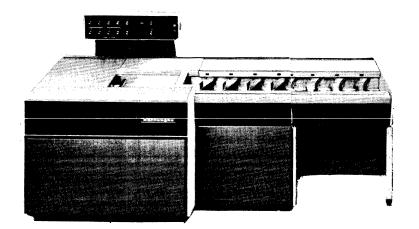

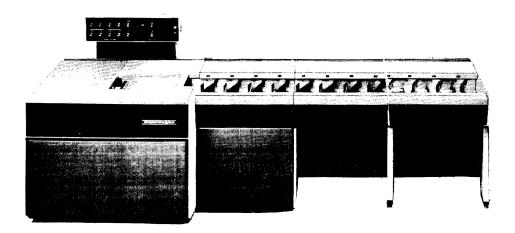

| 5-4    | A9135 Reader Sorter                                       | 5-3  |

# LIST OF TABLES

| Table | Title                                            | Page |

|-------|--------------------------------------------------|------|

| 1-1   | B 720 Equipment Characteristics and Capabilities | 1-3  |

| 1-2   | B 720 I/O Controls                               | 1-8  |

| 3-1   | Error Descriptor Codes                           | 3-7  |

## INTRODUCTION

The Burroughs B 720-Series Computer System is a smallscale, but powerful, system which incorporates the latest state-ofthe art data processing techniques, such as dynamic interpreter, interpretive structure, and programmable data communications processor.

This manual provides reference data concerning the major functional, operational, and programming characteristics and capabilities of the B 720 System. The intent of the presentation is to provide system-level product information to sales personnel, prospective customers, and users of the system, while also providing sufficient systems and programming reference data to aid programmers in understanding and applying the capabilities of the System.

Section 1, Equipment System Description, introduces the B 720 System and its physical/functional configuration. Basic operational characteristics and capabilities are presented for each major equipment unit and subsystem.

Section 2, Programming System Description, describes the B 720 programming system structure and the function/application of each major programming element. Application data, such as memory allocation and word/data structure, are provided for reference purposes.

Section 3, System Processor Description, provides a general functional and operational description of the B 720 Central Processing Unit.

Section 4, Data Communications Subsystems, provides a general functional and operational description of the two types of data communications subsystems: the programmable communications processor subsystem, and the single-line subsystem (file inquiry application).

Section 5, Reader Sorter Subsystem, provides a general functional and operational description of the B 720 application of the reader sorter capability in processing encoded documents.

Appendices are provided for quick reference to such items as terms and abbreviations, instruction codes, registers, and flags.

## SECTION 1

## SYSTEM DESCRIPTION

#### GENERAL

The Burroughs B 720 Computer System represents a significant expansion, in terms of capabilities and flexibility, to the B 700-Series of small-scale, powerful computer systems. In addition to retaining most of the existing B 720 System capabilities, the B 720 provides the following major enhancements and capabilities:

• Main memory capacity of up to 96K, 8-bit bytes (expansible from 16KB to 96KB in 8KB increments).

• Expanded I/O device or subsystem handling (up to 11 I/O ports; modular I/O expansion capability).

• Programmable data communications subsystem (communications processor) with enhanced communications capabilities.

• Direct-memory access for disk and data communications subsystems.

• Integral photoelectric memory loader.

• Direct entry system console with electronic keyboard.

• MICR/OCR (character recognition) subsystem capability.

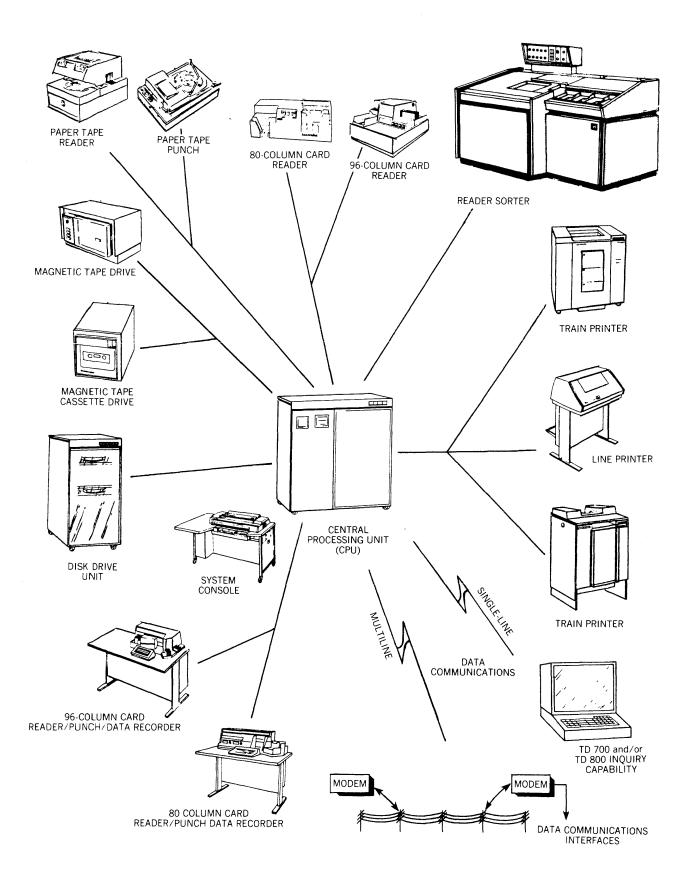

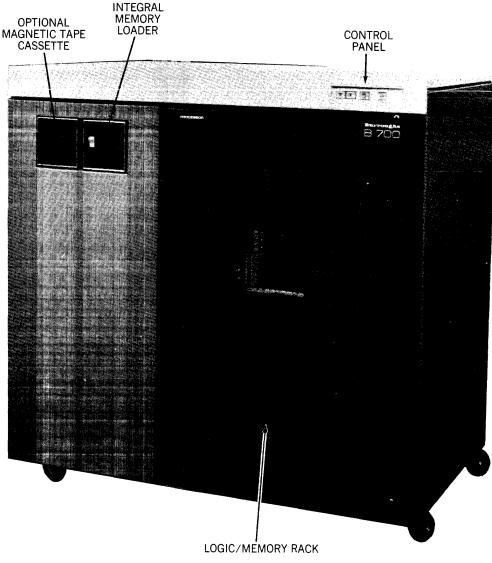

Figure 1-1 illustrates a typical console-based system.

# SYSTEM EQUIPMENT CONFIGURATION AND CHARACTERISTICS

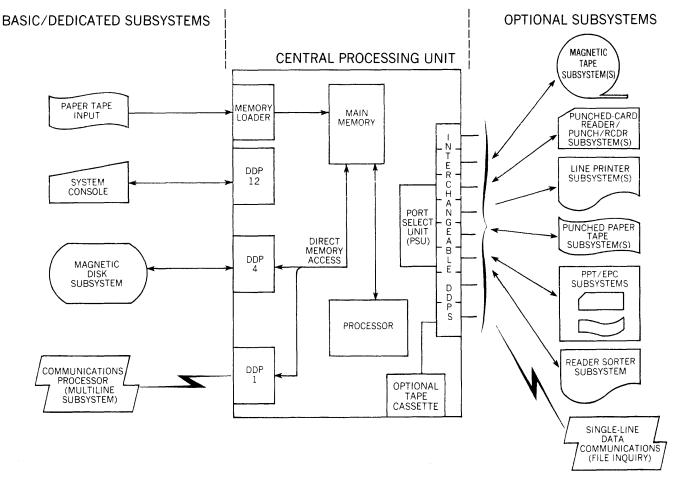

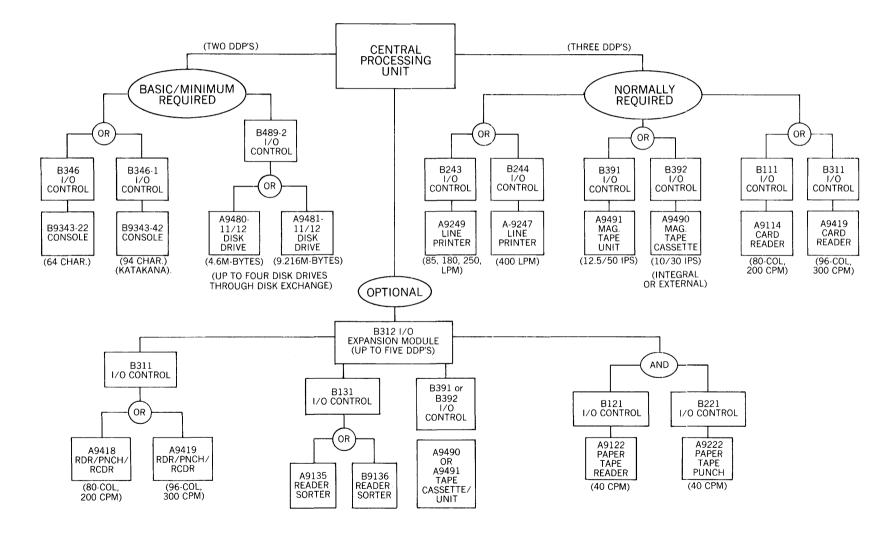

The B 720 is a modular system in terms of functional equipment units or subsystems and can be configured within the minimum and maximum restrictions to fulfill a customer's requirements. Figure 1-2 is a functional interface representation of the general system configuration. Table 1-1 lists the general characteristics and capabilities of the Central Processor and each type of peripheral device that can be used in the system. The basic (or minimum requirement System consists of the following:

a. B 720 Central Processing Unit (CPU) with minimum main-memory capacity of 32K-bytes, photoelectric (paper tape) memory loader, and power supply group.

b. B 9343-22 Console (26 inch form-feed, 64 characters) or B 9343-42 Console (26 inch form-feed, 94 characters).

c. B 346 (64-character) or B 346-1 (94-character) Console Control.

Figure 1-1. Typical B 720 Computer System

d. B 9480-11/12 (single/dual drive, 100 TPI) or B 9481-11/12 (single/dual drive, 200 TPI) Disk Cartridge Drive.

e. B 489-2 Cartridge Disk Drive Control.

The main-memory capacity can be expanded to 96 K-bytes in 8 K-byte increments (total of 12 B 31-2 memory modules). Up to 11 I/O control ports (Device Dependent Ports, DDP's) are available in the processor to accommodate basic and optional peripheral devices or interfaces. An additional port is reserved for communications processor expansion.

Three of the processor IOC ports (DDP1, DDP4, and DDP12) are dedicated to the data communications subsystem and basic system controls. Three additional controls may be installed in interchangeable ports in the basic system. Up to five additional controls may be installed by use of the optional I/O expansion module, which provides five interchangeable ports. Table 1-2 lists the applicability of the basic system I/O controls (IOC's) and those I/O controls available to interface the various optional peripheral devices.

#### PERIPHERAL DEVICE SUBSYSTEMS

As shown in figures 1-2 and 1-3 (peripheral device subsystem configurator), the minimum system configuration incorporates two dedicated peripheral device subsystems: the B 9343-22 or B 9343-42 Console interfaced through the B 346 or B 346-1 Console I/O Control, and the A 9480-11/12 or A 9481-11/12 Disk Cartridge Drive Unit interfaced through the B 489-2 Cartridge Disk Drive I/O Control. The integral processor memory loader device is interfaced directly with the processor main memory and does not require a dedicated port.

In addition to the basic or required peripheral subsystems, the following optional peripheral device subsystems are available for use with the system through their respective I/O controls and the processor interchangeable ports:

a. Punched card reader subsystems (80-column and/or 96-column).

b. Punched Paper Tape Reader/Punch Subsystem.

c. Punched Paper Tape (PPT)/Edge-Punched Card (EPC) subsystems.

Figure 1-2. B 720 System Interface Configuration

| Equipment<br>B 720 Central | Characteristics and Capabilities<br>Main (semiconductor memory of up to 96K 8-bit bytes (48K-words).                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Processing Unit<br>(CPU)   | Memory expansion from 32K-bytes (min.) to 96K-bytes (max.) in 8K-byte increments.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                            | Operating rate of 1 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|                            | I/O interface of up to 11 I/O ports (DDP'S); five interchangeable ports are<br>provided in basic processor.<br>Up to eight interchangeable (common) I/O ports (three in basic processor,<br>five in I/O expansion module)                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                            | Integral photoelectric memory loader; optional integral magnetic tape cassette.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| B 9343-22 or B 9343-       | Electronic Keyboard.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 42 Console                 | 64 characters (B 9343-22) or 94 characters (Katakana, B 9343-42).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                            | 26-in. forms transport (handler).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                            | Optional 64-character sets.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| A 9480-11 or A 9480-       | Single (A 9480-11) or dual (A 9480-12) drive capability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 12 Disk Cartridge<br>Drive | Replaceable disk cartridges with:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                            | <ul> <li>14-in. diameter coated disk.</li> <li>200 tracks (plus 3 spares) per surface.</li> <li>100 tracks per inch (TPI) recording.</li> <li>32 segments per track (180 bytes per segment).</li> <li>1,152M-bytes per surface; total of 2.304M-bytes per disk.</li> <li>4.6M-byte total recording capacity (two disks).</li> <li>Data access time of 14 msec. (min) to 125 msec. (max).</li> <li>1.55M-bits per sec. data transfer rate.</li> <li>1500 ±20 rpm disk rotation speed.</li> <li>60 msec. average seek time.</li> <li>20 msec. average latency.</li> </ul> |  |  |  |  |  |  |

| A 9481-11 or A 9481-       | Single (A 9481-11) or dual (A 9481-12) drive capability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 12 Disk Cartridge<br>Drive | Replaceable disk cartridges with:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                            | <ul><li>14-in. diameter coated disk.</li><li>400 tracks (plus 6 spares) per surface.</li><li>200 tracks per inch (TPI) recording.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                            | 32 segments per track (180 bytes/segment)<br>2.304M-bytes per surface; total of 4.608M-bytes per disk).<br>9.216M-byte total recording capacity (two disks).<br>Data access of 14 msec. (min.) to 125 msec. (max).<br>1.55M-bits per sec data transfer rate.<br>1500 $\pm 20$ rpm disk rotation speed.<br>60 msec. average seek time.<br>20 msec. average latency.                                                                                                                                                                                                      |  |  |  |  |  |  |

### Table 1-1. B 720 Equipment Characteristics and Capabilities

| Table 1-1. B 720 Equipment Characteristics and Capabilities (Cont) |                                                                                                |  |  |  |  |  |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Equipment                                                          | Characteristics and Capabilities                                                               |  |  |  |  |  |

| A 9247-2/3 or A 9247-<br>12/13 Line Printer                        | 400 or 750 line-per-minute printing rate.                                                      |  |  |  |  |  |

| 12/15 Line 1 miter                                                 | 120 print position (132 print-position option).                                                |  |  |  |  |  |

|                                                                    | Standard 48-character set (optional character sets available).                                 |  |  |  |  |  |

|                                                                    | 20-IPS paper slew rate.                                                                        |  |  |  |  |  |

|                                                                    | Two-channel or 12-channel (optional) format control tape.                                      |  |  |  |  |  |

|                                                                    | Self-aligning forms.                                                                           |  |  |  |  |  |

| A 9249-2/3 Line<br>Printer                                         | 85, 160, or 250 line-per-minute printing rate.<br>132 print positions; 10 characters per inch. |  |  |  |  |  |

|                                                                    | Standard 48-character set (64 or 94 character set optional).                                   |  |  |  |  |  |

|                                                                    | Two-channel or 12-channel (optional) format control tape.                                      |  |  |  |  |  |

|                                                                    | Self-contained 132-character buffer.                                                           |  |  |  |  |  |

| A 9114-1 Card Reader                                               | 80-column card media.                                                                          |  |  |  |  |  |

|                                                                    | 200-card per minute reading rate.                                                              |  |  |  |  |  |

|                                                                    | 350-card input hopper capacity.                                                                |  |  |  |  |  |

|                                                                    | 350-card output stacker capacity.                                                              |  |  |  |  |  |

|                                                                    | Table-top mounting.                                                                            |  |  |  |  |  |

| A 9119-1 Card Reader                                               | 96-column card media.                                                                          |  |  |  |  |  |

|                                                                    | 300-card per minute reading rate.                                                              |  |  |  |  |  |

|                                                                    | 600-card input hopper capacity.                                                                |  |  |  |  |  |

|                                                                    | 600-card output stacker capacity.                                                              |  |  |  |  |  |

|                                                                    | Table-top mounting.                                                                            |  |  |  |  |  |

| A 9490-21 or A 9490-                                               | Optional integral (A 9490-21) or external (A 9490-25) installation.                            |  |  |  |  |  |

| 25 Magnetic Tape<br>Cassette Drive Unit                            | Dual-gap read-write head.                                                                      |  |  |  |  |  |

|                                                                    | Spindle-controlled, 10 or 30 IPS reel drive.                                                   |  |  |  |  |  |

|                                                                    | Photoelectrically controlled tape speed.                                                       |  |  |  |  |  |

|                                                                    | Dual-track recording (one data track; one clock track).                                        |  |  |  |  |  |

|                                                                    | Data is NRZI encoded at 800 BPI.                                                               |  |  |  |  |  |

|                                                                    | 100 characters per inch (bit serial).                                                          |  |  |  |  |  |

|                                                                    | 280-ft. cassette recording capacity.                                                           |  |  |  |  |  |

|                                                                    | 10-IPS nominal read/write speed.                                                               |  |  |  |  |  |

|                                                                    | 30-IPS nominal fast forward or rewind speed.                                                   |  |  |  |  |  |

| A 9491-2 Magnetic                                                  | Table-top mounting.                                                                            |  |  |  |  |  |

| Tape Unit                                                          | Nine-track tape.                                                                               |  |  |  |  |  |

|                                                                    | Dual-gap read-write heads.                                                                     |  |  |  |  |  |

|                                                                    | 12.5 IPS read/write speed.                                                                     |  |  |  |  |  |

|                                                                    | 50-IPS rewind speed.                                                                           |  |  |  |  |  |

|                                                                    | Data is NRZI encoded at 800 BPI.                                                               |  |  |  |  |  |

|                                                                    | 600-foot tape reel capacity.                                                                   |  |  |  |  |  |

|                                                                    | 10,000 characters per second transfer rate.                                                    |  |  |  |  |  |

#### Table 1-1. B 720 Equipment Characteristics and Capabilities (Cont)

#### Table 1-1. B 720 Equipment Characteristics and Capabilities (Cont)

| Equipment                                      | Characteristics and Capabilities                                                                |

|------------------------------------------------|-------------------------------------------------------------------------------------------------|

| A 9418-2 Card<br>Reader/Punch/Data<br>Recorder | 80-column card media.<br>200-card per minute reading rate.                                      |

| Recorder                                       | 45-card per minute card punching and printing rates.<br>600-card primary input hopper capacity. |

|                                                | 400-card secondary input hopper capacity.                                                       |

|                                                | Two 400-card capacity output stackers.                                                          |

| A 9419-2/6 Card                                | 96-column card media.                                                                           |

| Reader/Punch/Data<br>Recorder                  | 300-card per minute reading rate.                                                               |

| Recorder                                       | 60-card per minute card punching rate.                                                          |

|                                                | 60-card per minute card printing rate.                                                          |

|                                                | 600-card primary input hopper capacity.                                                         |

|                                                | 400-card secondary input hopper capacity.                                                       |

|                                                | Two 400-card capacity output stackers.                                                          |

| A 9222-1 Paper Tape<br>Punch                   | Punches tape, or edge-punches cards.                                                            |

| r unen                                         | Reads 5, 6, 7, or 8 channel coded tape or cards at 40 code-per-second rate.                     |

|                                                | Photoelectric sensing.                                                                          |

|                                                | Handles reeled, strip, or fanfold $11/16$ in. or 1-in. tape.                                    |

|                                                | Handles individual, fanfold, or Mylar-reinforced edge-punched cards.                            |

|                                                | Supply and rewind mechanism for roll tape.                                                      |

| A 9122-1 Paper Tape                            | Punched paper tape or edge-punched card media.                                                  |

| Reader                                         | Punches 5, 6, 7, or 8 channel codes at 40 code-per-second rate.                                 |

|                                                | Tape-supply holder with 8-inch roll capacity.                                                   |

|                                                | Power-driven takeup reel.                                                                       |

|                                                | Handles card widths from 3 to 5 inches.                                                         |

|                                                | 250-card supply stacker.                                                                        |

| A 9135 or B 9136                               | Magnetic-ink or optical character recognition capabilities (MICR/OCR).                          |

| Reader Sorter                                  | Up to 16 document pockets in 4-pocket increments.                                               |

|                                                | Handles 900 documents per minute.                                                               |

|                                                | Mis-sort and double-document detection.                                                         |

|                                                | 17.5-inch input hopper capacity.                                                                |

|                                                | 3.5-inch capacity stackers.                                                                     |

|                                                |                                                                                                 |

d. Line Printer Subsystems.

e. Reader Sorter (Character Recognition) Subsystem.

g. Magnetic-tape unit/cassette subsystems.

A mixture of devices, or multiples of types, may be used in the system; however each separate device interface requires a separate corresponding device I/ O control. (Refer to Table 1-2.)

Although the interchangeable ports can be allocated to any device subsystem, certain ports are normally allocated to certain devices because of I/O service priority classifications. Also, certain devices (such as the Reader-Sorter are restricted to installation in an I/ O expansion port).

In typical operational applications, a device subsystem is used and controlled individually (such as magnetic tape or reader-sorter), or configured with other related device subsystems to form low-speed, medium-speed, and/or high-speed subsystems. For example, a low-speed subsystem might consist of the following peripheral devices with associated I/O controls:

a. A 9114-1 Card Reader (80-column card media, 200 CPM rate).

b. A 9249-1 Line Printer (90 LPM rate).

c. A 9122-1 Paper Tape Reader (40 code-per-second rate).

d. A 9222-1 Paper Tape Punch (40 code-per-second rate).

A medium-speed subsystem might consist of the A 9418-2 and A 9419-2 Card Reader/Punch/Data Recorder devices and their controls. These devices are 80-column/200 CPM and 96-column/300 CPM card devices, respectively.

A high-speed subsystem might consist of the A 9247-2/12 Line Printer (400 LPM rate) and the A 9119-1 Card Reader (96-column card media, 300 CPM rate) and their associated controls.

The following paragraphs provide general descriptions of each type of peripheral subsystem.

#### CONSOLE SUBSYSTEM

The basic or minimum system includes a B 9343-22 (64-character) or B 9343-42 (Katakana 94-character) console which serves as the system operating console and a direct-entry peripheral. The selected console is interfaced with the processor through the B 346 console I/O control (64-character) or the B 346-1 Console I/O Control (94-character) though dedicated port 12 (highest service priority).

Each type of console has an electronic keyboard, a 26-inch front-feed forms transport (handler), and a set of program-select keys. Optional 64-character sets are available in addition to the standard 64-character set supplied with the B 9343-22 console.

Only one console subsystem is used in the system.

#### MAGNETIC DISK SUBSYSTEM

The basic or minimum system includes an A 9480-11/12 or A 9481-11/12 Disk Cartridge drive unit interfaced with the processor through a B 489-2 Cartridge Disk Drive Control. Each model is capable of handling one or two disk cartridges (single drive is 11; dual drive is 12). A total magnetic disk storage capacity of 9,216,000 bytes is obtained when the B 9481-12 unit is used. The B 720 may use a maximum of four disk units and a total of eight drives (spindles) through a multiplexer.

Only one disk control, dedicated to processor port 4, can be installed in the system.

#### MAGNETIC TAPE SUBSYSTEM

Magnetic tape storage capabilities can be added to the system in a number of optional forms, involving the use of the A 9490-21 or A 9490-25 Magnetic Tape Cassette Unit and/or the A 9491-2 Magnetic Tape Unit. The A 9490-21 is available for installation as an integral part of the processor cabinet, while the A 9490-25 is the external desk-top version. Either or both can be used; however each requires a B 392-1 (internal) and B 392 Magnetic Tape I/O control in a selected interchangeable port (DDP).

The A 9490-21/25 has a dual-gap read-write head, dual-track (one data, one clock) recording capability, and cassette drive speeds of 10 IPS (forward) and 30 IPS (rewind).

The B 9491-2 Magnetic Tape Unit is an external reel-type, table-top mounted device that provides a nine-track recording capability, 12.5-IPS forward speed, and 50-IPS rewind speed. This unit is interfaced through a B 391 Magnetic Tape I/O control installed in an interchangeable port. A 10,000 characterper-second data transfer rate is possible with the A 9491-2 unit.

#### PUNCHED-CARD READER SUBSYSTEMS

Either or both 80-column and 96-column punchedcard reader subsystems are available for use in the system. The A 9114-1 Card Reader is an 80-column device with a 200 card-per-minute rate and a 350-card hopper/stacker capacity. This table-top device is interfaced through a B 111 Card Reader Control in an interchangeable DDP and is normally used in lowspeed subsystem applications.

The A 9119-1 Card Reader provides the 96-column and handling capability and has a 300 card-per-minute rate and 600-card hopper and stacker. This tabletop device is interfaced through a B 311 Card Reader Control in an interchangeable DDP and is normally used in high-speed subsystem applications.

Figure 1-3. Peripheral Device Subsystem Configurator

#### Table 1-2. B 720 I/O Controls

| I/O Control                                  | Peripheral Interface                                                                                   | Notes                                                                                                                                                |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| B 346 Console Control                        | B 9343-22 Console                                                                                      | Required for 64-character electronic keyboard; dedicated to port 12 of processor.                                                                    |

| B 346-1 Console Control                      | B 9343-42 Console                                                                                      | Required for 94-character<br>(Katakana) electronic keyboard;<br>dedicated to port 12 of processor.                                                   |

| B 489-2 Cartridge Disk Drive                 | B 9480-11/12 or B 9481-11/12<br>Disk Cartridge Drive                                                   | Dedicated to processor port 4.                                                                                                                       |

| B 351-1 Single-Line Control<br>(SLC)         | Single-Line data<br>communications interface<br>(direct or through data set/<br>modem)                 | Occupies two interchangeable processor ports (DDP's).                                                                                                |

| B 352 Communications<br>Processor            | Communications Processor<br>interface (direct of through<br>data sets/modems).                         | Dedicated to processor port 1;<br>must be installed in modular I/O<br>expansion rack. (Refer to<br>description of Data<br>Communications Subsystem.) |

| B 111 Card Reader Control                    | A 9114-1 Card Reader                                                                                   | For 80-column card media;<br>installed in interchangeable<br>processor port (DDP).                                                                   |

| B 243 Line Printer Control                   | A 9249 Line Printers (1, 2, 3)                                                                         | Installed in interchangeable processor port (DDP).                                                                                                   |

| B 244 and B 244-X Line Printer<br>Control    | A 9247 Line Printers (2, 3,<br>12, 13)                                                                 | Installed in interchangeable<br>processor port (DDP). Optional<br>EBCDIC and KATAKANA code<br>sets.)                                                 |

| B 391 Magnetic Tape Unit                     | A 9491-2 Magnetic Tape Unit                                                                            | Installed in interchangeable processor port (DDP).                                                                                                   |

| B 392 Magnetic Tape Cassette<br>Control      | A 9490-25 Magnetic Tape<br>Cassette Unit                                                               | Used for external tape unit<br>installation; installed in<br>interchangeable processor port<br>(DDP).                                                |

| B 392-1 Magnetic Tape Cassette<br>Control    | A 9490-21 Magnetic Tape<br>Cassette Unit                                                               | Used for processor cabinet<br>(integral) installation of tape unit;<br>installed in interchangeable<br>processor port (DDP).                         |

| B 131 Reader Sorter Control                  | A 9135 or B 9136<br>Reader Sorter                                                                      | Installed B 312 I/O expansion<br>module; restricted from installation<br>in basic system interchangeable<br>DDP's.                                   |

| B 121-1 Paper Tape Reader<br>Control         | A 9122-1 Paper Tape Reader                                                                             | Installed in interchangeable processor port (DDP).                                                                                                   |

| B 221 Paper Tape Punch<br>Control            | A 9222-1 Paper Tape Punch                                                                              | Installed in interchangeable processor port (DDP).                                                                                                   |

| B 311 Card Reader/Punch/<br>Recorder Control | A 9418 RDR/PNCH/RCDR<br>(80-col), A 9419 RDR/PNCH/<br>RCDR (96 col), or A 9119<br>Card Reader (96 col) | Handles 80 or 90 column card<br>formats; installed in<br>interchangeable processor port<br>(DDP)                                                     |

1

#### PUNCHED PAPER TAPE/EDGE-PUNCHED CARD (PPT/EPC) SUBSYSTEMS

Punched paper tape and edge-punched card reading and punching capabilities are provided by the A 9122-1 Paper Tape Reader and A 9222-1 Paper Tape Punch, respectively. These units are small, compact, desk-top or free-standing units that read and punch, respectively, 5, 6, 7, or 8 channel coded tapes or cards at a 40 code-per-second rate.

The A 9122-1 is interfaced with the processor by the B 121-1 Paper Tape Reader I/O Control, while the A 9122-1 is interfaced by the B 221 Paper Tape Punch I/O Control. Each type of control can be installed in an interchangeable processor DDP. Either, both, or multiples of these subsystems can be used in lowspeed subsystem applications.

The A 9122-1 Paper Tape Reader has a photoelectric sensing mechanism and can handle reeled, strip, or fanfold punched paper tape. The A 9122-1 also handles individual, fanfold, or Mylar reinformed edgepunched cards. Supply and rewind mechanisms are provided for roll tape.

The A 9222-1 Paper Tape Punch has a tape-supply holder with an 8-inch roll capacity, a power-driven tapeup reel, and a 250-card supply stacker. Card widths from 3 to 5 inches can be handled.

#### PUNCHED-CARD READER PUNCH RECORDER SUBSYSTEMS

Combination punched-card reading, punching, and recording capabilities in medium-speed subsystem applications are provided by the A 9418-2 and A 9419-2/6 Card Reader/Punch/Data Recorder Units. The A 9418-2 handles standard 80-column cards and is interfaced with the processor through the B 311 Reader/Punch/Recorder I/O control. The A 9418-2 can read punched cards at a 200 card-per-minute rate and/or punch and print cards at a 45 card-per-minute rate. A 600-card primary input hopper, a 400-card secondary input hopper, and two 400-card output stackers are provided on the A 9418-2.

The A 9419-2/6 (2/6 pocket) Card Reader/Punch/ Data Recorder handles 96-column cards and also is interfaced with the processor by the B 311 I/O control. The A 9419 has a reading rate of 300 cards-per-minute and punching/printing rates of 60 cards per minute. A 600-card primary input hopper, a 400-card secondary input hopper, and two 400-card output stackers are provided on the A 9419.

#### LINE PRINTER SUBSYSTEMS

Output printing capabilities of various speeds and formats are provided by the A 9247 and A 9249 Line Printers available for use on B 720 Systems. The A 9247 Line Printer is interfaced through a B 244 Line Printer Control, while the A 9249 Line Printer is interfaced through a B 243 Line Printer Control. Both types of controls are installed in interchangeable I/O ports.

Normally, one line printer subsystem is used in the B 721 System. The A 9249 Line Printer is used in lowspeed subsystem applications; however, if it is the only line printer used in the system, it is configured as a high-speed device. The A 9247 is normally used in high-speed subsystem applications with the A 9119 Card Reader.

The A 9247-2/3 and A 9247-12/13 Line Printers have 400 and 750 line-per-minute printing rates, respectively, and provide 120 print positions. (A 132 print-position option is available.) The A 9247 is provided with a standard 48-character set, but optional character sets are available. A standard two-channel (or optional 12-channel) format control tape is provided. The B 244 I/O control interfaces those printers using ASCII code. B 244-1 through B 244-6 controls provide interfaces with EBCDIC and KATAKANAvariations.

The A 9249 Line Printer has 85, 160, and 250 lineper-minute rates and 132 character positions. A standard 48-character set is provided; optional 64 and 96 character sets are available. A standard two-channel (or optional 12-channel) format control tape is provided. The A 9249 has a self-contained 132-character buffer.

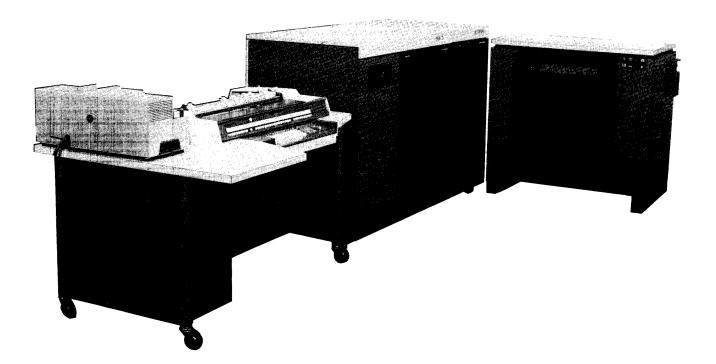

#### **READER SORTER SUBSYSTEM**

The Reader Sorter subsystem is a character-recognition subsystem designed for sorting and processing magnetic ink or optically encoded documents (MICR or OCR). This subsystem consists of the A 9135 or B 9136 Reader-Sorter interfaced through the B 131 Reader-Sorter Control.

The B 131 Reader-Sorter Control must be installed in an interchangeable port provided by the B 312 I/ O Expansion Module. That is, an I/O Expansion Module, with the required cabling and cooling options, must be included in the CPU when installing a reader-sorter subsystem.

The Reader-Sorter has both magnetic ink and optical character-recognition capabilities and can handle 900 documents per minute. Up to 16 document sorting pockets may be installed on the Reader-Sorter (in four-pocket increments). Mis-sort and doubledocument detection capabilities are provided, along with a 17.5-inch capacity input hopper and 3.5-inch capacity stackers. Only one Reader-Sorter Subsystem may be used on the system. A complete system includes a readersorter subsystem, processor and console, disk, and line printers. Section 5 provides a general description of the Reader-Sorter Subsystem. Refer to the B 700 Reader-Sorter Subsystem Reference Manual, form 1082500, for a complete description of the system.

#### DATA COMMUNICATIONS SUBSYSTEMS

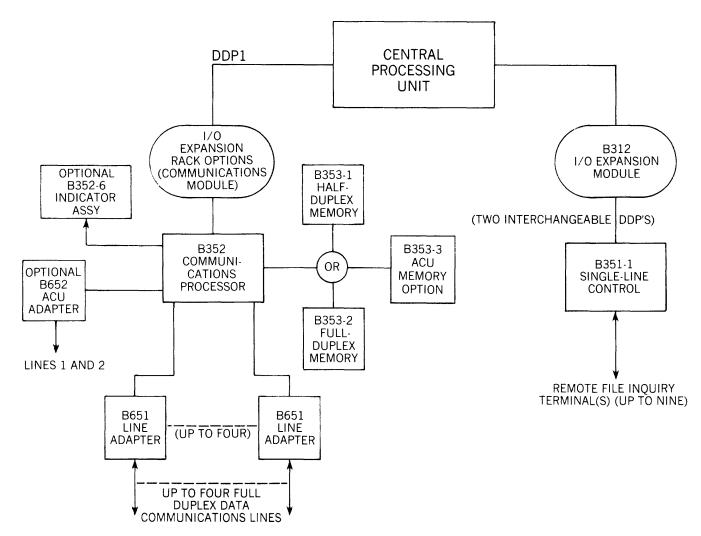

There are two types of data communications subsystems systems available for B 720 Systems: a programmable communications processor subsystem, and a single-line data communications subsystem. Figure 1-4 is a data communications subsystem configurator.

#### COMMUNICATIONS PROCESSOR SUBSYSTEM

An optional programmable communications processor is available for servicing up to four communications lines in the half-duplex or full-duplex modes. This subsystem is allocated an entire I/O module in the CPU I/O expansion rack and consists of basic (required) and optional elements. Only one communications processor may be used in the system, and it is dedicated to I/O port 1 (DDP1).

The major programmable controlling and processing element in the subsystem is the B 352 Communications Processor. The B 352 consists of an I/O expansion rack module wired and configured to accept the following required or optional items:

a. Up to four B 651 Line Adapters (one for each communications line to be serviced).

Figure 1-4. Data Communications Subsystem Configurator

b. The B 353-1 four-line half-duplex option, or the B 353-2 four-line full-duplex option. (Installation of one selected option is required for operation; a B 353-3 memory option is available for use with the ACU option.

c. One data set interface cable for each line adapter-to-data set interface, or a direct-connect kit for each interface to be directly connected to a terminal (TDI interface).

d. A B 652 ACU (Automatic Calling Unit) option, which provides the capability of automatic dialing on two of the four communication lines.

e. The optional B 352-6 Data Communications Console Indicator Assembly, which provides transmit and receive monitoring indicators for each communications line serviced.

The B 352, together with the mentioned options and cabling, comprise the communications module. The B 352, unlike the other I/O controls, is programmable and executes program instructions to control the flow of data between the system processor and data communications channels. This capability, which normally is implemented by execution of a firmware program in the system processor, frees the system processor to accomplish more useful data processing functions. The system processor only monitors the operational status of the B 352 in this application.

The subsystem can handle synchronous or asynchronous data transmissions and can accommodate two basic types of interfaces: data set/modem (RS- 232-C or CCITT) and two-wire direct (unbalanced). Combinations of interfaces (up to four) may be used; a B 651 Line Adapter is required for each interface.

All standard data sets/modems may be interfaced by a B 651 Line Adapter.

A complete functional description of the data communications subsystem is provided in Section 4.

# SINGLE-LINE DATA COMMUNICATIONS SUBSYSTEM

The optional single-line data communications capability on B 720 Systems is provided for a special and restricted application of data communications: file inquiry operation. The file inquiry capability, which is implemented through the use of a B 351-1 Single-Line Control (SLC), permits an operator at a remote inquiry station to make disk data file inquires under user programmatic control.

The remote terminals, interfaced by the B 351-1 SLC in this application are TD 700, TD 800, and TD 801 Terminal Display Units. Only one B 351-1 SLC, which occupies two interchangeable I/O ports in the B 312 I/O expansion module, may be used in the system. Up to nine terminals may be interfaced by the SLC (mixture of types if desired).

The terminals are interfaced with the system processor over a private (direct-connect), asynchronous, 9600-baud communications lines by the B 351-1 SLC. A complete functional description of file inquiry operation is provided in Section 4.

# SECTION 2 PROGRAMMING SYSTEM DESCRIPTION

#### **GENERAL CONCEPTS**

The B 720 programming system incorporates the latest data processing concepts, such as soft (interpretive) structure and dynamic interpreter configurator. The B 720 Central Processing Unit (CPU) is referred to as the "host machine." Interpreter and system programs are loaded into the host machine to form a "virtual machine." Therefore, there can be many variations of virtual machines, using one host machine, if a variety of interpreters are available. An interpreter may be oriented toward general purpose applications and thus can be used with a variety of programs. However, some interpreters may be highly oriented to a particular program application.

#### **HIGH-LEVEL LANGUAGES**

The B 720 can be described as a system that executes programs under control of "microinstructions." It is impractical for applications programmers to write microprograms; therefore, various higherlevel languages have been developed for customer use on the system. It is not the intent of this reference manual to describe these higher-level languages, but to describe the relationship that exists between the microprogram and the higher-level languages.

S (Secondary)-language instructions are intermediate instructions which are equivalent to the machine language of a conventional system. For each S-instruction there exists a string of microinstructions which interpretively executes the function specified by that S-instruction. It must be remembered that the S-instruction does not directly cause the hardware to perform a function.

S-instructions may completely specify a compiler level language. Burroughs Corporation has defined the S-instructions and has written the interpreters and compiler programs for the COBOL, RPG, and NDL languages. These compiler programs generate the S-language instructions to perform the various operations specified by the higher-level language.

#### INTERPRETERS

In addition to the S-language program (compiler user program), another program referred to as an interpreter is utilized. An interpreter system has been developed which satisfies each of the higher level Slanguages, as well as utility programs. It is the function of the interpreter to fetch the S-language instructions from main memory and to interpret or execute the instructions. The S-instructions are decoded, and a series of microinstructions are executed to cause the hardware to perform the function specified by the Slanguage instruction. When the execution of a series of microinstructions (representing an S-instruction) is completed, the interpreter fetches the next S-language instruction and the operation continues in this manner. The series of microinstructions used for each S-language instruction may be stored in main memory or called from disk.

The S-language programs and the interpreter system are located and loaded from disk under control of the system loader. On completion of the load, the system loader then passes control to the S-language program.

#### DYNAMIC INTERPRETER CONFIGURATOR

The dynamic interpreter configurator is based on the noncommitment of resources until the actual need for these resources arises. The proper utilization of resources enables the user to get the maximum system throughput per dollar investment.

System configuration occurs at program load (from disk) time. The system loader is provided with information about the required subsystem device controllers, subsystem buffers, number of SPM words, and the actual interpreter structure needed by the S-level program being loaded. The system loader then constructs the required interpreter and allocates the remaining memory for the required buffers, SPM, and user program.

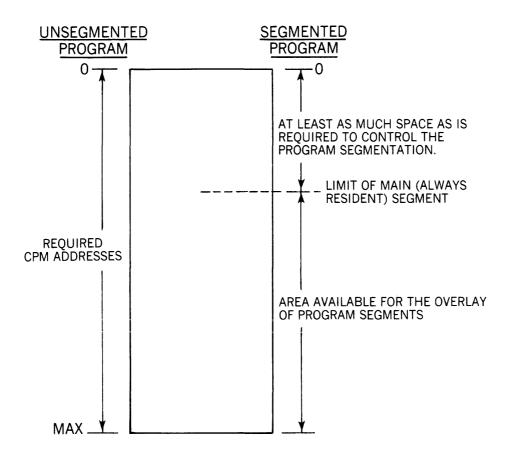

User (S-level space is within the area specified by the program base and limit registers and is divided into two portions: overlayable and nonoverlayable (or resident) sections. Compiler generated code is completely independent of absolute memory locations and consequently is not restricted to particular areas of memory.

Proper control of input/output resources and a flexible system architecture are other features which provide for proper utilization of resources on the system.

#### BREAKOUT

At any time during execution, an S-level program may be interrupted to enable the loading and execution of a different program. The interruption is called "breakout", and the program along with the virtual machine registers are saved on the disk. After the desired program is executed, execution of the interrupted program may be resumed at the point where breakout occurred. Only one level of breakout may occur; that is, only one program can be saved.

#### PROGRAMMING SYSTEM STRUCTURE

The elements of the complete programming system are categorized into the following groups:

a. System Software, which consists of the operating system programs essential to the primary startup and operation of the system.

b. Program product development aids (such as NDL), which facilitate the generation of application programs by a user.

c. Application programs, which are designed for specific user functions (such as character recognition and sorting, production control, and item processing).

#### SYSTEM SOFTWARE

System software, or operating system programs, consists of initialization programs, interpreters, and system software functional utility programs. The B 700 System Software Operation Guide, form 1082492, contains descriptions of the application and operation of these system software elements.

#### INITIALIZATION PROGRAMS

Initialization programs, consisting of cold start and warm start programs, provide the means to bring the system up to normal operating status. Cold start programs consist of the following:

a. The Disk Primer/Cold Start (DPCS) program, which prepares a new system disk cartridge, copies a backup cartridge, and loads the system loader from disk to main memory.

b. Bootstrap loaders which provide the minimum control required to load the Disk Primer/Cold Start program from four types of input media to main memory.

When the system loader program is loaded by DPCS, it is used to define the I/O environment and load the interpreter from disk to main memory. At the conclusion of this process, the system attains the normal operating status. DPCS consists of the following four routines used in the cold-start process:

a. INIT, which initializes a disk cartridge to the interpreter format by providing a variable number of protected spaces on disk for system software, plus four protected directory segments.

b. LOAD, which loads the interpreter from input media to the protected area on disk and thus creates a system disk.

c. COPY, which copies a system disk to a backup disk. Only those tracks occupied by the system software load are copied.

d. BOOT, which reads the system loader program from system disk to main memory.

#### SYSTEM LOADER PROGRAM

The System Loader program is used to define the system configuration. The definition process occurs in the following sequence:

a. The peripheral device and system configuration is defined.

b. Translation algorithms and associated tables are defined for those devices that require them.

c. Total memory size is defined.

The System Loader is read from the system disk under control of the BOOT routine in DPCS, or from the warm start program during a warm start or restart. For a warm start or restart, the System Loader is already resident on the system disk. In all cases, the program is stored at the same reserved starting location on disk and is read into main memory, starting at location 0000, and is given control.

#### WARM START PROGRAM (WSTRT)

The Warm Start program, identified as WSTRT, provides the minimum controls necessary to transfer the system loader program from disk to main memory. The WSTRT program is contained on punched paper tape and is loaded to memory by means of the integral memory loader.

#### **INTERPRETERS**

Interpreters are microprograms that comprise the actual machine instructions to which the equipment responds. B 720 system interpreters are designed to emulate the operation of other computer systems at the user level. Interpreters for COBOL, RPG, and NDL have been developed for use on B 720 systems.

Intrinsic segments of the interpreter firmware are provided to initialize and copy a user disk cartridge (INITD), print the contents of machine memory and registers (SYSDUMP), and trace and list each step of a COBOL or RPG program (TRACE).

#### INTERPRETER FIRMWARE.

The interpreter firmware is comprised of the following segments and routines which form the minimum interpreter necessary to load program memory and bring the system up to operating status:

a. Common interpreter segments (ACOMMON), which comprise the interpreter segments common to all software elements of the systems. ACOMMON is always resident in memory.

b. BCOMMON, which contains the elements necessary to perform the operation as specified by the user COBOL or RPG program. BCOMMON is transferred to main memory at the time that a program which requires it is loaded from disk to memory for execution.

c. CCOMMON, which contains the elements necessary to support the B 700 onboard COBOL Compiler and onboard NDL Compiler. CCOMMON is transferred to main memory only when required.

d. Interpreter overlays (OVERLAY), which are retained on disk until required during program execution. A part of main memory is reserved, such that only the single overlay actually in use is occupying it. The dynamic maintenance of the overlays in main memory is an automatic function of the system firmware. e. Intrinsic segments, which are brought into memory only if actually required by the program to be executed, or if desired by the system operator to be executed. Memory not filled with relative segments is made available to the S-level program. Relative segments include those portions of the interpreter required for data communication controllers, System Dump, and Trace.

f. Fatal Error Routine (FATAL), which is used by the operating system to alert the operator to the existence of a condition that impairs proper functioning of the system. Error conditions handled by FATAL include certain hardware errors, address limit errors, and I/O errors.

#### UTILITY PROGRAMS

The B 720 System is provided with a library of functional utility programs that perform various utility operations, such as loading files from card devices to disk, or dumping program/data disk files to magnetic tape. These programs are loaded and executed like any other program. Application of a particular utility program on a system depends on the peripheral device configuration of the system. The available library of utility programs is as follows:

| Designation | Name                                      |  |  |  |  |  |

|-------------|-------------------------------------------|--|--|--|--|--|

| CDGEN       | Check Digit Table Generator               |  |  |  |  |  |

| CDLST       | Card List                                 |  |  |  |  |  |

| CRDLD       | Load Object Program From Cards<br>to Disk |  |  |  |  |  |

| DDLST       | Disk Directory List                       |  |  |  |  |  |

| DFLST       | Disk File List                            |  |  |  |  |  |

| DMPPG       | Disk File Dump and Purge                  |  |  |  |  |  |

| DSKTP       | Dump Disk Files to Tape                   |  |  |  |  |  |

| INTTP       | Create Cold Start Tape From 80-           |  |  |  |  |  |

|             | Column Cards                              |  |  |  |  |  |

| ODP80       | Punch Object Program, Disk to 80-         |  |  |  |  |  |

|             | Column, R/P/P                             |  |  |  |  |  |

| ODP96       | Punch Object Program, Disk to 96-         |  |  |  |  |  |

|             | Column, R/P/P                             |  |  |  |  |  |

| O8096       | 80-Column to 96-Column Object             |  |  |  |  |  |

|             | Program Conversion                        |  |  |  |  |  |

| PTCPY       | Paper Tape Copy With Verify And           |  |  |  |  |  |

| ao 4 att    | Fancy Punch                               |  |  |  |  |  |

| SQASH       | Disk Space Reallocation                   |  |  |  |  |  |

| TPCPY       | Copy Tape To Tape And Verify              |  |  |  |  |  |

| TPDSK       | Dump Tape File To Disk                    |  |  |  |  |  |

| TPLST       | Tape List                                 |  |  |  |  |  |

The B 700 System Operating Guide, form 1082492, provides descriptions and operating instructions for each utility program.

#### GENERAL SORT PROGRAM

Also provided with the system software is the General Sort Program (SORT), which performs all or part of the operations necessary to provide and control a sorted tag file associated with a particular master file and/or sort the master file itself. SORT has the following five selectable modes of operation:

a. Tag sort mode, which creates a tag file from the master file and sorts the file according to specified keys.

b. Record sort mode, which sorts the master file according to specified keys and purges any deleted master records.

c. Full sort mode, which performs combined functions of tag and record sorts.

d. Basic sort mode, which takes an existing unsorted tag file and sorts it according to specified keys.

e. Update sort mode, which sorts and merges an existing overflow tag file with an existing sorted tag file to create a new updated tag file. A new (empty) overflow file is opened.

Refer to the B 700 System Software Operation Guide, form 1082492, for a complete description and operating instructions.

#### COBOL COMPILER

The B 720 may implement the B 700 series onboard COBOL Compiler, which consists of an input program (B7CBL) that collects COBOL statements from various media and uses six separate processing phases to produce the compiled program. If any syntax errors are detected during input operations, certain phases of the processing sequence are bypassed. The detected errors are displayed to allow the user to perform error correction without requiring code generation.

The B 700-series COBOL Compiler allows the user the capability of compiling from 80-column cards, 96column cards, disk files, tape files, or system console input. Source patches may be included from 80- or 96-column cards, or from the system console. The user may optionally save the resultant source file on disk, cassette, tape, 80-column cards, or 96-column cards.

Output listings are available on the wide-line printer or the console. The resulting object program is placed on disk. Refer to the B 700 COBOL Reference Manual, form 1064391, for a complete description of B 700 COBOL.

#### RPG COMPILER

The B 700 RPG (Report Program Generator) Compiler is available onboard to the users of B 720 Systems. The compiler consists of a front-end program (B7RPG), which collects RPG source from various media, and six separate programs which are phases of the RPG Compiler. As each portion of the compiler completes its program, it automatically calls the next phase. However, if there are any syntax errors, several phases will be eliminated, allowing the user to see the source errors without the expense of code generation. The time of a compile varies and depends on the number and type of RPG source submitted. The B 700 RPG Compiler provides the user with the capability of compiling from 80-column cards, 96-column cards, disk files, tape files or console input. If either tape or disk is used as input, a merge feature is available from 80- or 96-column cards, or the console. When a merge function is used, the user optionally may save the resultant source file on disk or tape. A disk source file is always created for each compile (reserved name (\$\$\$)).

Refer to the B 700 System RPG Reference Manual, form 1073897, for a complete description of B 700 RPG.

#### NDL COMPILER

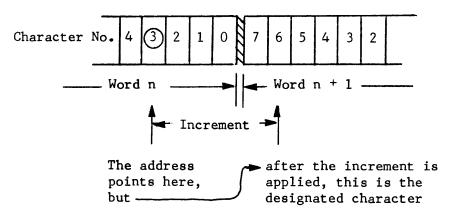

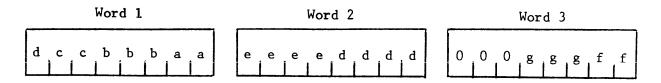

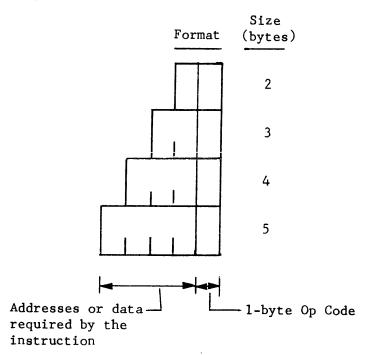

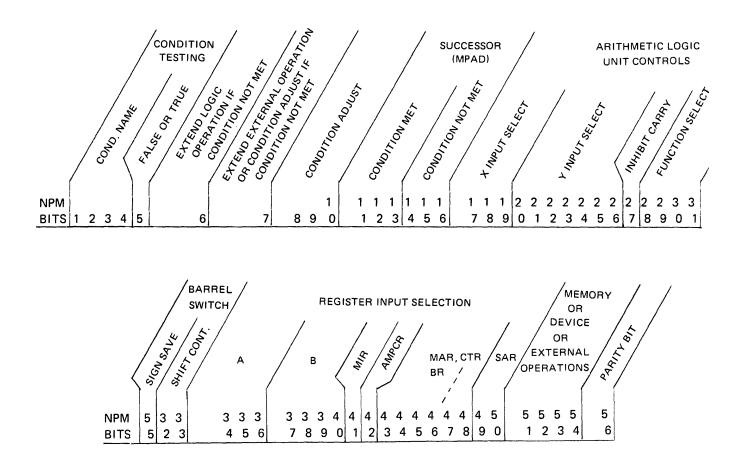

The B 720 Network Definition Language Compiler (B7NDL) consists of an input phase that collects NDL statements from various media, and uses several processing phases to produce a compiled program and firmware tables. If any syntax errors are detected during input, certain phases of the processing sequence are bypassed and the errors are displayed. Thus, the user is permitted to perform error correction before code generation and table building are attempted.