# B 0346/B 0346-1 CONSOLE I/O CONTROL

(B 700 SYSTEMS)

INTRODUCTION AND OPERATION

FUNCTIONAL DETAIL

CIRCUIT DETAIL

ADJUSTMENTS

MAINTENANCE PROCEDURES

INSTALLATION PROCEDURES

RELIABILITY IMPROVEMENT NOTICES

> OPTIONAL FEATURES

# Burroughs

FIELD ENGINEERING

# TECHNICAL MANUAL

COPYRIGHT © 1975 BURROUGHS CORPORATION Detroit, Michigan 48232

# INDEX

# Page No.

#### INTRODUCTION AND OPERATION - SECTION I

| Console Interface     |    |     |    |  |  | • |   | 5 |

|-----------------------|----|-----|----|--|--|---|---|---|

| Console to IOC        |    |     |    |  |  |   |   | 6 |

| IOC to Console        |    |     |    |  |  |   |   | 6 |

| Glossary of Terms and | Si | gna | ls |  |  |   |   | 7 |

| Introduction          |    |     |    |  |  |   | • | 1 |

| Processor Interface . |    |     |    |  |  | • |   | 1 |

| IOC-to-Processor      |    |     |    |  |  | • |   | 1 |

| Processor-to-IOC      |    |     |    |  |  |   |   | 1 |

| Word Formats.         |    |     |    |  |  |   |   | 1 |

|                       |    |     |    |  |  |   |   |   |

# FUNCTIONAL DETAIL - SECTION II

| • | • | •                   | •                     | •                 | •             | • | • | • | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---|---|---------------------|-----------------------|-------------------|---------------|---|---|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • |   |                     |                       |                   |               | • |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| n |   |                     |                       | •                 | •             | • | • |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| n |   |                     |                       | •                 | •             | • |   |   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |   |                     |                       | •                 | •             | • |   | • |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| • |   |                     |                       | •                 | •             | • |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |   |                     |                       |                   | •             | • |   |   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |   |                     |                       | •                 | •             | • |   | • | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |   |                     | •                     | •                 | •             | • | • | • | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |   | •                   |                       | •                 |               |   | • | • | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |   | •                   |                       | •                 |               |   | • | • | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | • | •                   |                       | •                 |               |   | • | • | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | n | <br>n .<br><br><br> | <br>n<br><br><br><br> | <br>n<br><br><br> | <br>n<br><br> |   |   |   | .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    . | .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    . |

# CIRCUIT DETAIL - SECTION III

| Differential Comparator       |      |     |    |    |    |   |   |   |   | 1 |

|-------------------------------|------|-----|----|----|----|---|---|---|---|---|

| Introduction                  |      |     |    |    |    |   |   | : |   | 1 |

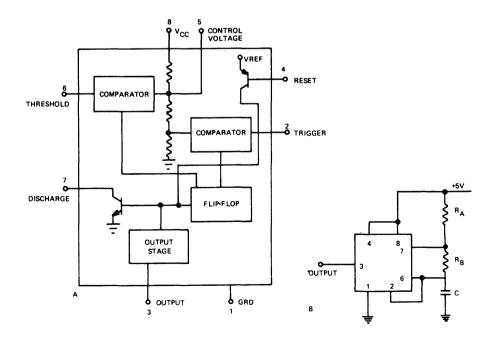

| Linear Timer (1409 1039) .    |      |     |    |    |    |   |   |   |   | 1 |

| Quad D-Type Flip-flop (1449 1 | 27   | 8)  |    |    |    |   |   |   |   | 1 |

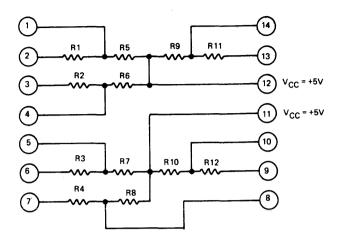

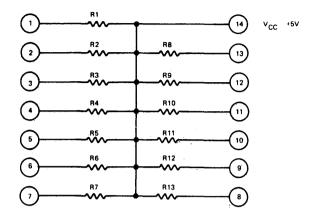

| Resistor Module (1447 5396)   |      |     |    |    |    |   |   |   |   | 1 |

| Resistor Module (1448 2319)   | •    | •   | •  | •  | •  | • | • | • | • | 1 |

| MAINTENANCE PROCEDURE         | ES - | – S | EC | TI | ON | V |   |   |   |   |

| Installation Package . |      |      |     |     |     |     |     |    |     |   |   | 1 |

|------------------------|------|------|-----|-----|-----|-----|-----|----|-----|---|---|---|

| Installation Procedure |      |      |     |     |     |     |     |    |     |   |   | 1 |

| Maintenance Philosoph  | ıy   |      |     |     |     |     |     | •, |     |   |   | 1 |

| Maintenance Aid        | s a  | nd   | Eq  | uir | ome | ent |     |    |     |   |   | 1 |

| Maintenance Test Rou   | tine | es ( | (M) | [R  | 's) | •   |     | •  | •   |   | • | 1 |

| INSTALLATION PRO       | CE   | DL   | R   | ES  | - : | SEC | CTI | 0  | I V | Ι |   |   |

| Installation Package . |      |      |     |     |     |     |     |    |     |   |   | 1 |

| Installation Procedure |      |      |     |     |     |     |     |    |     |   |   |   |

Burroughs believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

#### Page No.

# Introduction and Operation

#### INTRODUCTION

This Technical Manual covers the B0264 and B0264-1 Console I/O Controls (IOC's). The B0264 Console IOC services the B9343-XX Consoles with the 64-print character set; the B0264-1 Console IOC services the B9343-XX Consoles with the 94-print character set. Each IOC consists of 12 cards installed in dedicated ports (DDP's) of the B705/711-1 and B721 Processors. The logic cards are the same for all types, except that CC6E and CC7E cards are used in the B0264-10C, and CC6EK and CC7EK cards are used in the B0264-1.

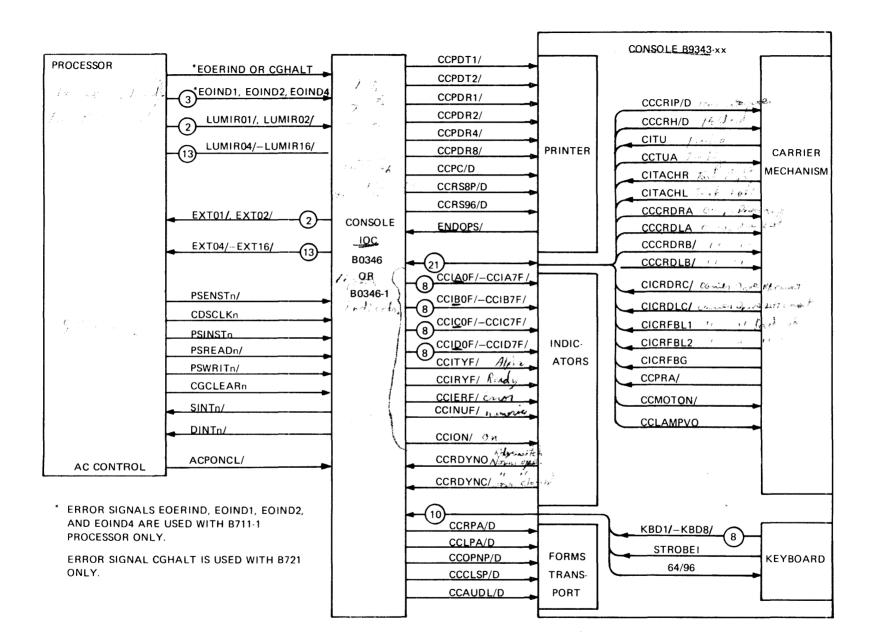

The B0264/B0264-1 Console I/O Control (IOC or DDP), hereinafter called the IOC, provides the interface between the B9343 Console equipped with an electronic keyboard and a B700 Central Processing Unit (processor). (See Figure I-1.) The IOC controls the transfer of information and commands between the processor and the console.

The IOC acts upon control words sent by the processor, performs specified operations, and upon completion of an operation, generates a status word containing the status and error information. The port select unit (PSU) of the processor controls the synchronization of the IOC interface with the processor.

#### PROCESSOR INTERFACE

Interface communications between the processor and the IOC are accomplished by word transfers over input and output data lines, and by various control lines as described below:

#### PROCESSOR-TO-IOC

- a. <u>Error Indicators (B711-1 only-EOIND1, EOIND2,</u> <u>EOIND4, EOERIND) (B721 only-CGHALT).</u> When high, cause appropriate indicator to light.

- b. <u>Input Data Lines (LUMIRn/)</u>. When low, indicate a logical true at the appropriate bits.

- c. <u>Output Data Lines (EXTn/)</u>. When low, indicate a logical true at the appropriate bits.

- d. <u>Enable Status Line (PSENSTn/)</u>. When low, initiates the status word from IOC to the processor.

- e. <u>Clock Line (CDSCLKn). Provides system clock pulses</u> from the processor.

- f. <u>Instruction Line (PSINSTn)</u>. When high, indicates that the data on the MIR lines is a control word.

- g. <u>Read Line (PSREADn/)</u>. When low, initiates a onecharacter data transfer from the IOC to the processor.

- h. Write Line (PSWRITn/). When low, initiates a onecharacter data transfer from the processor to the IOC.

- i. <u>Clear Line (CGCLEARn</u>). When high, clears all control flip-flops in the IOC.

- j. Power On Clear (ACPONCL/). Resets motor-on and motor up-to-speed flip-flops.

#### IOC-TO-PROCESSOR

- a. <u>Status Interrupt (SINTn/)</u>. When low, indicates to the processor that the IOC has a status word for the processor.

- b. Data Interrupt (DINTn/). When low, indicates to the processor that the IOC is ready for another data transfer operation.

#### WORD FORMATS

The initiation of an information transfer between the processor and the IOC is the same for all devices, the distinction being in the device address contained in the base register (BR1 or BR2) of the processor output select gates. The port select unit decodes three bit groups from the processor to completely define the operation that is to take place. Nanobits 51 through 54 establish whether an operation is to be a device read or a device write. The four least significant bits of BR1 or BR2 contain the specific device address; the most significant bit of BR1/BR2, in conjunction with the type of operation, distinguishes between control, data, and status words. The word formats are illustrated in Figure I-2.

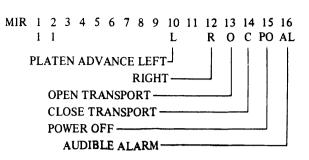

# Control Word

Operation of the console is controlled by the transfer of a control word from the processor to the IOC. The control word consists of an operation field which specifies the function to be performed by the IOC as follows:

| MIR Bits  | Function                                                                                                                                                         |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 thru 11 | Not used.                                                                                                                                                        |

| 12        | Enable Carrier Data Interrupt: a ONE in<br>this bit enables data interrupts to the<br>processor when the console is ready to<br>accept carrier positioning data. |

| 13        | Enable Forms Data Interrupt: a ONE in<br>this bit enables data interrupts to the<br>processor when the console is ready to<br>accept forms control data.         |

| 14        | Enable Printer Data Interrupt: a ONE in<br>this bit enables data interrupts to proces-<br>sor when console is ready to request print<br>data.                    |

| 15        | Enable Keyboard Data Interrupt: a ONE<br>in this bit enables data interrupts to<br>processor when console is ready to trans-<br>mit keyboard data.               |

16 Not used.

Burroughs - B0346/B0346-1 Console Control Technical Manual Introduction and Operation Fig. I-2 CONSOLE IOC WORD FORMATS

|                           |                                 |                 |                |                          | 1                        |                                   |                                   |                            |             | Å         |                |            |                                 |                                      |                                      |                                      |                  |

|---------------------------|---------------------------------|-----------------|----------------|--------------------------|--------------------------|-----------------------------------|-----------------------------------|----------------------------|-------------|-----------|----------------|------------|---------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|------------------|

|                           | MSB                             |                 |                |                          |                          |                                   |                                   |                            |             | 1         |                |            |                                 |                                      | PRTR                                 | Kin                                  | LSB              |

| MIR                       | 1                               | 2               | 3              | 4                        | 5                        | 6                                 | 7                                 | 8                          | (           | 9         | 10             | 11         | 12                              | 13                                   | 14                                   | 15                                   | 16               |

| CONTROL<br>WORD           | -                               | -               | _              | _                        | -                        | _                                 | -                                 | _                          |             | -         | ~              | -          | ENABLE<br>CARR<br>DATA<br>INTER | ENABLE<br>FORMS<br>DATA<br>INTERRUPT | ENABLE<br>FORMS<br>DATA<br>INTERRUPT | ENABLE<br>FORMS<br>DATA<br>INTEBRUPT | -                |

| KEYBOARD<br>DATA<br>WORD  | 4                               | <u>†  </u>      | v −<br>Gegener |                          | -                        |                                   | -                                 |                            |             | DATA<br>7 | DATA<br>6      | DATA<br>5  | DATA<br>4                       | DATA<br>3                            | DATA<br>2                            | DATA<br>1                            | DATA<br>0        |

| CARRIER<br>DATA<br>WORD   | <b>0</b><br>P <sup>ic</sup> are | 0               | -              | -                        | -                        | -                                 |                                   | CARRI<br>DIRECT            |             | DATA<br>7 | DATA<br>6      | DATA<br>5  | DATA<br>4                       | DATA<br>3                            | DATA<br>2                            | DATA<br>1                            | DATA<br>0        |

| PRINT<br>DATA<br>WORD     | <b>.</b><br>7                   | 1<br>5 [        | -              | -                        | ESCAPE<br>RIGHT          | ESCAPE<br>LEFT                    | RED<br>RIBBON                     | PRI                        | NT          | -         | DATA<br>6      | DATA<br>5* | <b>ΔΑ</b> ΥΑ<br>4               | DATA<br>3                            | DATA<br>2                            | DATA<br>1                            | DATA<br>0        |

| INDICATOR<br>DATA<br>WORD | 1                               | 0               | _              | IND<br>BANK<br>ADDR<br>A | IND<br>BANK<br>ADDR<br>B | INDICATOR<br>BANK<br>ADDRESS<br>C | INDICATOR<br>BANK<br>ADDRESS<br>D | INDICA<br>BAN<br>ADDR<br>S | K<br>ESS    | DATA<br>7 | DATA<br>6      | DATA<br>5  | DATA<br>4                       | DATA<br>3                            | DATA<br>2                            | DATA<br>1                            | <b>DATA</b><br>0 |

| FORMS<br>DATA<br>WORD     | 1                               | 1               | _              | -                        | -                        | _                                 | _                                 | -                          | 200 Million | _         | LEFT<br>PLAT   | -          | RIGHT<br>PLATEN                 | OPEN<br>PLATEN                       | CLOSE<br>PLATEN                      | POWER<br>OFF                         | ALARM            |

| STATUS<br>WORD            | DATA<br>REQUEST                 | END OF<br>PAPER | -              | DEVICE<br>ADDR<br>4      | DEVICE<br>ADDR<br>3      | DEVICE<br>ADDR<br>2               | DEVICE<br>ADDR<br>1               | DEVI<br>ADD<br>0           | R           |           | FORMS<br>READY |            | KYBD<br>READY                   | READY<br>PB                          | INTRPT<br>NOT<br>HONORED             | OVER<br>SPEED                        | STALL            |

NOTE: DEVICE ADDRESS BITS OF STATUS WORD ARE INSERTED AT PSU • USED FOR 94-CHARACTER SET; NOT APPLICABLE TO 64-CHARACTER SET.

#### Introduction and Operation

#### Keyboard Data Word

Keyboard data transfer between the IOC and the processor is in 8 bit parallel form, where bit 16 is the least-significant bit of the low-order digit and bit 12 is the least-significant bit of the high-order digit. The functions are as follows:

| EXT Bits   | Function                                                                         |

|------------|----------------------------------------------------------------------------------|

| 1 thru 8   | Not used.                                                                        |

| 9 thru 12  | Data: High-order digit portion of 8-bit byte of data from keyboard to processor. |

| 13 thru 16 | Data: Low-order digit portion of 8-bit byte of data from keyboard to processor.  |

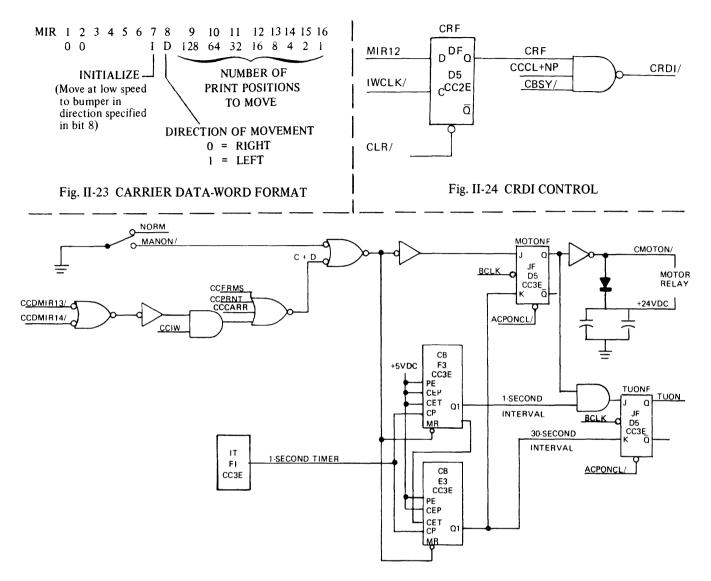

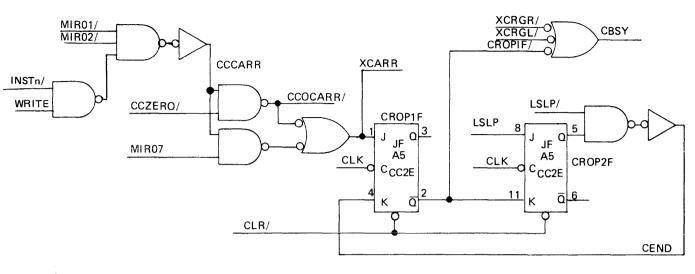

#### Carrier Data Word

Carrier data transfer between the processor and the IOC determines the horizontal direction of movement of the print ball and the number of horizontal positions which the print ball is to be moved. The assigned bit positions are as follows:

| MIR Bits        | Function                                                                                                                                                       |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 and 2         | Control Select: Defines console function.<br>Code 00 selects carrier control.                                                                                  |

| 3 thru 6        | Not used.                                                                                                                                                      |

| 7               | Initialize: a ONE in this bit position<br>causes a routine to be performed which<br>moves the carrier to the extreme left or<br>right, as determined by bit 8. |

| 8               | Carrier Direction: Defines horizontal direction of printer ball. A ONE specifies movement to left and a ZERO specifies movement to right.                      |

| 9 thru 16       | Data: Defines number of horizontal posi-<br>tions which the printer ball is to be<br>moved from its present position.                                          |

| Print Data Word |                                                                                                                                                                |

Print Data Word

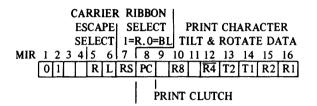

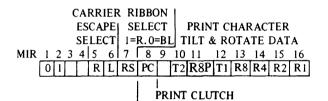

Print data transfer between the processor and the IOC defines the carrier escape, selects red or black ribbon, and the tilt and rotate position of the print ball. The functions are as follows:

| MIR Bits | Function                                                                                                                                          |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 and 2  | Control Select: Defines console function.<br>Code 01 selects system printer.                                                                      |

| 3 and 4  | Not used.                                                                                                                                         |

| 5 and 6  | Escape: Determines that carrier position-<br>ing is to be left (01), right (10), or no<br>escape (00). The printer escapes first,<br>then prints. |

7

8

Each ribbon: A ONE in this bit shifts the ribbon mechanism to red ribbon, otherwise black ribbon is used.

Print: a ONE in this bit causes the character defined by bits 9 through 16 to be printed following escapement specified in bits 5 and 6. Otherwise escapement takes place but no printing occurs. Since there is no space position on the 64-character print ball, a space is printed by suppression of print bit plus appropriate escape bit; bit 7 is zero and data bits equal zero to avoid ribbon or print ball movement at this time.

9 Not used.

10 thru 16 Data: Defines tilt and rotate positions of print ball. For the 64-character set the code conversion is as follows:

| <u>Bit</u> | Print Ball                   |

|------------|------------------------------|

| 10         | Rotate 8                     |

| 12         | Rotate 4 NOT (negated value) |

| 13         | Tilt 2                       |

| 14         | Tilt 1                       |

| 15         | Rotate 2                     |

| 16         | Rotate 1                     |

|            |                              |

For the 96-character set the code conversion is as follows:

| <u>Bit</u> | Print Ball            |

|------------|-----------------------|

| 10         | Tilt 2                |

| 11         | Rotate code expansion |

| 12         | Tilt 1                |

| 13         | Rotate 8              |

| 14         | Rotate 4              |

| 15         | Rotate 2              |

| 16         | Rotate 1              |

|            |                       |

- ---

\_

# Introduction and Operation

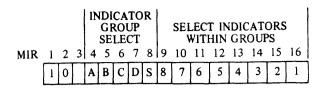

Indicator Data Word

Indicator data transfer between the processor and the IOC specifies the indicator bank and the particular indicator to be lit. The bit assignments are as follows:

| Function                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control Select: Defines console function.<br>Code 10 selects indicator control.                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Not used.                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Indicator bank address A.                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Indicator bank address B.                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Indicator bank address C.                                                                                                                                                                                                                                                                                                                                                         | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Indicator bank address D.                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Indicator bank address S.                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Data: Specifies the direct code to a particular bank of indicators on the con-<br>sole panel. An indicator is lit on receipt<br>of a data word with a ONE in the<br>appropriate data bit position. This indica-<br>tor remains lit until receipt of a new data<br>word for the same bank and a ZERO in<br>the data bit position, or unless it is<br>extinguished by system clear. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                   | Control Select: Defines console function.<br>Code 10 selects indicator control.<br>Not used.<br>Indicator bank address A.<br>Indicator bank address B.<br>Indicator bank address C.<br>Indicator bank address D.<br>Indicator bank address S.<br>Data: Specifies the direct code to a<br>particular bank of indicators on the con-<br>sole panel. An indicator is lit on receipt<br>of a data word with a ONE in the<br>appropriate data bit position. This indica-<br>tor remains lit until receipt of a new data<br>word for the same bank and a ZERO in<br>the data bit position, or unless it is |

#### Forms Data Word

Forms data transfer between the processor and the IOC controls platen operation, system power, and console audible alarm. The functions are as follows:

| MIR Bits | Function                                                                         |             |

|----------|----------------------------------------------------------------------------------|-------------|

| 1 and 2  | Control Select: Defines console function.<br>Code 11 selects forms control.      |             |

| 3 thru 9 | Not used.                                                                        |             |

| 10       | Left Platen: A ONE in this bit causes the left platen to be advanced one line.   |             |

| 11       | Not used.                                                                        |             |

| 12       | Right Platen: A ONE in this bit causes the right platen to be advanced one line. |             |

| 13       | Open Platen: A ONE in this bit causes the forms control chute to open.           |             |

| 14       | Close Platen: A ONE in this bit causes the forms control chute to close.         | (           |

| 15       | Power Off: A ONE in this bit turns off system power.                             | 2           |

| 16       | Alarm: A ONE in this bit activates the audible alarm.                            | t<br>a<br>r |

Status Word

Status word transfer between the IOC and the processor notifies the processor that a failure or particular

functional condition has occurred. It consists of a device address (inserted at the port select unit) and a device status field. The functions are as follows:

| EXT Bits         | Function                                                                                                                                                                                       |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                | Data Request: IOC is ready to receive or<br>send a data character. This status condi-<br>tion follows the data interrupt to the<br>processor.                                                  |  |

| 2                | End of Paper: Paper on either or both platens has been exhausted.                                                                                                                              |  |

| 3                | Not used.                                                                                                                                                                                      |  |

| 4 thru 8         | Device Address: Device address bits are inserted at the port select unit.                                                                                                                      |  |

| 9                | Carrier Ready: Carrier buffer is ready for<br>next data word; a ONE whenever carrier<br>data interrupt is true.                                                                                |  |

| 10               | Forms Ready: Forms buffer is ready for<br>next data word; a ONE whenever forms<br>data interrupt is true.                                                                                      |  |

| 11               | Printer Ready: Print buffer is ready for<br>next data word; a ONE whenever printer<br>data interrupt is true.                                                                                  |  |

| 12               | Keyboard Ready: Keyboard character is<br>available for transfer to processor; a ONE<br>whenever keyboard data interrupt is true.                                                               |  |

| 13               | Ready: Ready pushbutton has been pressed and console is ready for operation.                                                                                                                   |  |

| 14               | Interrupt Not Honored: Processor did not<br>service data interrupt. A ONE bit when a<br>key is pressed and keyboard data has not<br>been shifted from the first stage of the<br>output buffer. |  |

| 15               | Overspeed: Carrier is moving too fast. A<br>ONE in this bit after carrier data word is<br>received and an overspeed condition is<br>detected.                                                  |  |

| 16               | Stall: Carrier is moving too slow. A ONE<br>in this bit after carrier data word is<br>received and a stall condition is detected.                                                              |  |

| ONSOLE INTERFACE |                                                                                                                                                                                                |  |

#### CONSOLE INTERFACE

The console is comprised of five functional sections: the printer, indicators, forms transport, carrier mechanism, and the keyboard sections. Each section is controlled by a respective part of the IOC.

Print data from the IOC provides the mechanical positioning of the print head. The carrier position operation is interleaved with the print function. The firmware of the

processor maintains records of print ball locations and vertical positioning of the forms.

The indicators are divided into five banks: A, B, C, D, and S, plus a power-on indicator. The power-on indicator is lit when power is on at the processor; the remaining indicators are controlled by processor firmware.

The keyboard is used for data entry and for program control. The console interface is illustrated in Figure I-1; the signals are described under the following headings:

#### IOC TO CONSOLE

- a. <u>Print Decode Tilt (CCPDT1/, CCPDT2/)</u>. Two lines which determine the proper tilt position of the print head.

- b. <u>Print Decode Rotate (CCPDR1/, CCPDR2/,</u> <u>CCPDR4/, CCPDR8/</u>). Four lines which determine the proper rotate position of the print head.

- c. <u>Print Clutch Driver (CCPC/D)</u>. Activates hammer fire solenoid and causes print ball to impact paper.

- d. <u>Ribbon Shift or Rotate-8P (CCRS8P/D)</u>. For 64--character printers, a low causes ribbon solenoid to shift to red ribbon. For 96-character printers, provides for expansion of the rotate code for the print head.

- e. <u>Ribbon Shift, 96-Character Printers (CCRS96/D)</u>. For 96-character printers, a low causes ribbon solenoid to shift to red ribbon.

- f. <u>Indicator Group A (CCIAOF/ to CCIA7F/)</u>. A low on any line in this group causes the corresponding indicator to light.

- g. <u>Indicator Group B (CCIB0F/ to CCIB7F/)</u>. A low on any line in this group causes the corresponding indicator to light.

- h. <u>Indicator Group C (CCIC0F/ to CCIC7F/)</u>. A low on any line in this group causes the corresponding indicator to light.

- i. <u>Indicator Group D (CCID0F/ to CCID7F/)</u>. A low on any line in this group causes the corresponding indicator of the left-most group of eight indicators to light.

- j. Indicator Group S (CCITYF/, CCIRYF/, CCIERF/, CCINUF/). A low on any line in this group causes the ALPHA, READY, ERROR, or NUMERIC indicator to light.

- k. <u>Audible Alarm (CCAUDL/D)</u>. When low, activates the audible alarm solenoid and causes the alarm to sound.

- 1. <u>Power On (CCION/)</u>. Always low (ground).

- m. <u>Right Platen Advance (CCRPA/)</u>. When low, activates right platen solenoid and causes left platen to advance.

- n. <u>Left Platen Advance (CCLPA/)</u>. When low, activates left platen solenoid and causes the left platen to advance.

- o. <u>Open Platen (CCOPNP/D</u>). When low, activates open platen solenoid and causes the forms control chute to open.

- p. <u>Close Platen (CCCLSP/D)</u>. When low, activates close platen solenoid and causes the forms control chute to close.

- q. <u>Carrier Interposer (CCCRIP/D)</u>. When low, activates carrier interposer solenoid and causes the carrier detent latches to be driven away from the shaft-locking device.

- r. <u>Carrier Hold (CCCRH/D).</u> When low, activates carrier hold solenoids and causes the carrier detent locking latches to be held away from the detent gears.

- s. <u>Timer Unit Input (CCTUA)</u>. Signal console to test timer unit (TU).

- t. <u>Carrier Drive Controls (CCCRDRA, CCCRDLA,</u> <u>CCCRDRB/, CCCRDLB/)</u>. Amplifier and bias signals providing drive controls to the carrier motor.

- u. <u>Motor-On Signal (CCMOTON/)</u>. When low, causes the decoder motor to be turned on.

- v. <u>Carrier Position Read-Out Lamp Voltage</u> (CCLAMPVO). Supplies a current-limited voltage to carrier position read out lamp source.

- w. <u>64/96 Character Mode (64/96)</u>. Allows 64- or <u>96-character mode to be selected</u>.

#### CONSOLE TO IOC

- a. End of Paper (ENDOPS/). When low during forms function, enables end of paper bit in status word to IOC.

- b. <u>Ready Switch, Normally-Open Contacts</u> (CCRDYNO). When ready switch is pressed, CCRDYNO is 0 volts.

- c. <u>Ready Switch, Normally-closed contacts</u> (CCRDYNC/). When ready switch is pressed, CCRDYNC/ is +5 volts.

- d. <u>Timer Unit (CITU).</u> Core readout from rotating shaft of decoder motor, synchronizes mechanical timing in all functions.

- e. <u>Tachometer Right (CITACHR)</u>. When high, tachometer right output is monitored.

- f. <u>Tachometer Left (CITACHL)</u>. When high, tachometer left output is monitored.

- g. <u>Carrier Drive Controls (CICRDRC/, CICRDLC/,</u> <u>CICRFBL1, CICRFBL2, CRFBG</u>). Signals sent from carrier control to carrier drive circuits for generation of control signals to the carrier motor.

- h. <u>Carrier Position Readout (CCCPR/A)</u>. Signal from Carrier photocell used to count position of carrier.

Signal

CCEQ1

CCFRMS

CCIAnF/

CCIBnF/

CCICnF/

Forms

Group A indicator n

Group B indicator n

Group C indicator n

Meaning

Equal to 1 (output from carrier buffer)

#### Introduction and Operation

- Keyboard Data (KBD1/ to KBD8/). When low, i. indicates a binary ONE bit at appropriate bit position.

- j. Keyboard Strobe (STROBEI). Indicates to IOC that keyboard data lines contain a character.

#### GLOSSARY OF TERMS AND SIGNALS

|                                                                                        |                                                                      | ,                  |                                                                 |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------|-----------------------------------------------------------------|

| The following is a list of the mnemonics and names of signals used in the console IOC: |                                                                      | CCIDnF             | Group D indicator n                                             |

|                                                                                        |                                                                      | CCIERF/            | Error indicator                                                 |

|                                                                                        |                                                                      |                    | One Mask, (disables EQ1 for 10 milli-                           |

| Signal                                                                                 | Meaning                                                              |                    | seconds, and sets LSLPF for a carrier movement of one position) |

| ACPONCL/                                                                               | Power-on clear                                                       | CCINITF            | Initialize flip-flop                                            |

| CCAUDAL/                                                                               | Audible alarm                                                        | CCINTU/            | Interposer and TUF                                              |

| CCAUDAL/D                                                                              | Audible alarm signal driver                                          | CCION/             | On indicator                                                    |

| CCCARR                                                                                 | Carrier, indicates presence of a carrier data word on MIR lines.     | CCIRYF/            | Indicator ready                                                 |

| CCCLR/                                                                                 | Clear                                                                | CCITYF/            | Indicator alpha                                                 |

| CCCLSP/                                                                                | Close platen                                                         | CCINUF/            | Indicator numeric                                               |

| CCCL+NP                                                                                | Clear or not print                                                   | CCIW               | Instruction write                                               |

| CCCOUNT/                                                                               | Count signal used to count down the                                  | CCKBF              | Keyboard enable flip-flop                                       |

|                                                                                        | carrier position data as the carrier moves                           | CCKINH/            | Keyboard interrupt not honored                                  |

| CCCPR                                                                                  | Carrier position readout                                             | CCKDI              | Keyboard data interrupt                                         |

| CCCRDI/                                                                                | Carrier data interrupt                                               | CCKSTA/            | Keyboard status                                                 |

| CCCRDLA                                                                                | Carrier drive left amplifier                                         | CCLAMPVO           | Carrier position lamp voltage                                   |

| CCCRDLB/                                                                               | Carrier drive left bias                                              | CCLPA/             | Left platen advance                                             |

| CCCRDRA                                                                                | Carrier drive right amplifier                                        | CCLPA/D            | Left platen advance driver                                      |

| CCCRDRB/                                                                               | Carrier drive right bias                                             | CCLSP/             | Close forms control chute                                       |

| CCCRGL/                                                                                | Carrier go left                                                      | CCLSP/D            | Close forms control chute solenoid driver                       |

| CCCRGR/                                                                                | Carrier go right                                                     | CCLTEQ6            | Less than or equal to 6, output from                            |

| CCCRHS/                                                                                | Carrier high speed                                                   |                    | carrier buffer                                                  |

| CCCRH/                                                                                 | Carrier hold                                                         | CCMCTU/            | Mechanical timing signal                                        |

| CCCRH/D                                                                                | Carrier hold solenoid driver                                         | CCMOTON            | Motor on                                                        |

| CCCRLT/                                                                                | Carrier left time                                                    | CCNOOPT/           | No option                                                       |

| CCCR4A/                                                                                | Carrier 4 amperes                                                    | CCOCARR            | Operate carrier (signal true when a carrier                     |

| CCCS                                                                                   | Core Strobe                                                          |                    | data word is not equal to zero)                                 |

| CCDINT                                                                                 | Data interrupt                                                       | CCOPNP/            | Open platen                                                     |

| CCDMIRn                                                                                | Memory information register bit n rede-<br>veloped through inverter. | CCOPNP/D<br>CCPCLR | Open platen driver<br>CCCL+NP                                   |

| CCDREAD/                                                                               | Data read                                                            | CCPC/              | Print clutch                                                    |

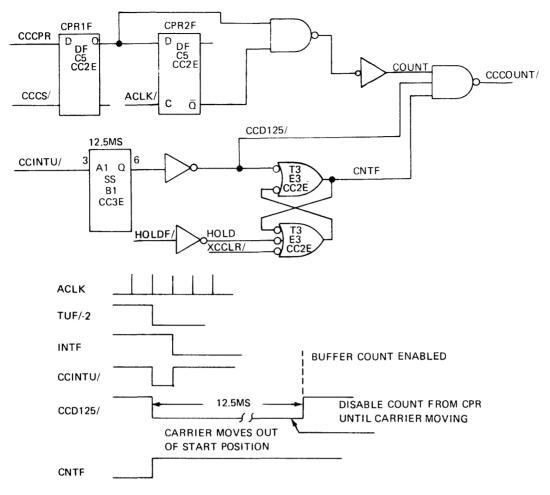

| CCD125/                                                                                | Delay 125 (used to disable CCCOUNT signal for 12.5 milliseconds)     | CCPC/D             | Print clutch driver                                             |

|                                                                                        |                                                                      | CCPDRn/            | Print rotate n driver                                           |

| CCEKDI/                                                                                | Enable keyboard data interrupt                                       | CCPDTn/            | Print tilt n driver                                             |

| CCENSTA                                                                                | Enable status                                                        | CCPRA/             | Carrier position readout                                        |

|                                                                                        |                                                                      |                    |                                                                 |

# Introduction and Operation

| Signal      | Meaning                                         | Signal       | Meaning                             |

|-------------|-------------------------------------------------|--------------|-------------------------------------|

| CCPRF       | Printer flip-flop                               | CICRDRC/     | Carrier drive right current         |

| CCPRI       | Printer interposer                              | CICRFBG      | Carrier feedback ground.            |

| CCPRNT      | Print (decoded from MIR data)                   | CICRFBL1     | Carrier feedback level one          |

| CCPRRN/     | Printer rotate n                                | CICRFBL2     | Carrier feedback level two          |

| CCPRTn/     | Printer Tilt n                                  | CITACHBK     | Tachometer feedback                 |

| CCPWRO/     | Programmatic power off                          | CITACHL      | Tachometer left                     |

| CCRDY       | Ready pushbutton                                | CITACHR      | Tachometer right                    |

| CCRDYNC/    | Ready switch normally-closed                    | CLEAR        | Clear                               |

| CCRDYNO     | Ready switch normally-open                      | CROP1F       | Carrier operation #1 flip-flop      |

| CCRENST/    | Enable status                                   | DINTn/       | Data interrupt                      |

| CCRIP/      | Carrier interposer, signal used to drive the    | ENDOPS/      | End of paper signal                 |

|             | interposer solenoid                             | EOERIND      | B711-1 only, error indicator signal |

| CCRIP/D     | Carrier interposer driver                       | EOIND1, 2, 4 | B711-1 only, hard error indicators  |

| CROP1F      | Carrier operation #1 flip-flop                  | EXTn         | External bus bit n                  |

| CCRPA/      | Right platen advance                            | FMPR         | Forms or print data                 |

| CCRPA/D     | Right platen advance driver                     | F+PDATA      | Forms or print data                 |

| CCRS96/     | 96-character ribbon shift                       | HOLD         | Hold                                |

| CCRS96/D    | 96-character ribbon shift driver                | IND1, 2, 4   | Memory parity indicator             |

| CCRS+8P/    | Ribbon shift for 64 character printer or        | KBDn/        | Keyboard data n                     |

|             | expansion of rotate code to 96 char-<br>acters. | PRTU         | Printer timer unit                  |

| CCRS8P/D    | CCRS+8P/ driver                                 | PSENSTn/     | Enable status                       |

| CCTU        | Timer unit signal                               | PSINSTn      | Port select instruction             |

| CCTUA       | Input signal to decoder transducer              | PSREADn/     | Port select read                    |

| CCTUF-1     | Timer unit flip-flop                            | PSWRITn/     | Port select write                   |

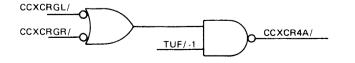

| CCXCRGL/    | Escape carrier, go left                         | SCLK         | Clock signal                        |

| CCXCRGR/    | Escape carrier, go right                        | SINTn        | Status interrupt                    |

| CCXCR4A/    | Escape carrier 4 amperes                        | STALF        | Stall flip-flop                     |

| CCZERO/     | Signal indicates that the data on the MIR       | STROBEI      | Keyboard strobe                     |

|             | lines is not equal to zero                      | TU           | Timer unit                          |

| CDSCLKC,D,n | Clock signals.                                  | TUF          | Timer unit flip-flop                |

| CGCLEARn    | System clear                                    |              |                                     |

| CGHALT      | Error indicator signal (B721 only)              | 64/96        | 64- or 96-character mode            |

| CICRDLC/    | Carrier drive left current                      |              |                                     |

#### **GENERAL OPERATION**

As shown in Figure I-1, there are five major functional sections in the console; the logic in the IOC is divided into corresponding sections. Because of its complexity, the console IOC is located in a dedicated DDP area of the processor (B711-1 port 8 and B721 port 12).

The five logic sections of the IOC are as follows:

- a. Keyboard Control.

- b. Indicator Control.

- c. Printer Control.

- d. Carrier Mechanism Control.

- e. Forms Transport Control.

Communications between the processor and the IOC is accomplished by means of control words, data words, and status words. The formats of the various words are shown in Figure I-2.

To enable any of the console mechanisms, the processor must send a control word with the appropriate bit set (MIR12, 13, 14, or 15). This enables the logic associated with a particular mechanism to generate a data interrupt when the logic is ready to send or receive a data word. The only exception is the indicator control logic, which neither requires a control word nor generates an interrupt. A data word may be addressed to the indicators at any time and will be acted upon.

The status word is send to the processor when a device-read to the console is executed with the instruction bit (most-significant bit in the active base register) set, or when the processor executes an Address and Status Request (ASR) and the console IOC is the highest priority IOC generating a status interrupt.

The four status-word bits associated with a data interrupt are EXT9, 10, 11 and 12. EXT13, 14, 15 and 16 are the bits associated with a status interrupt.

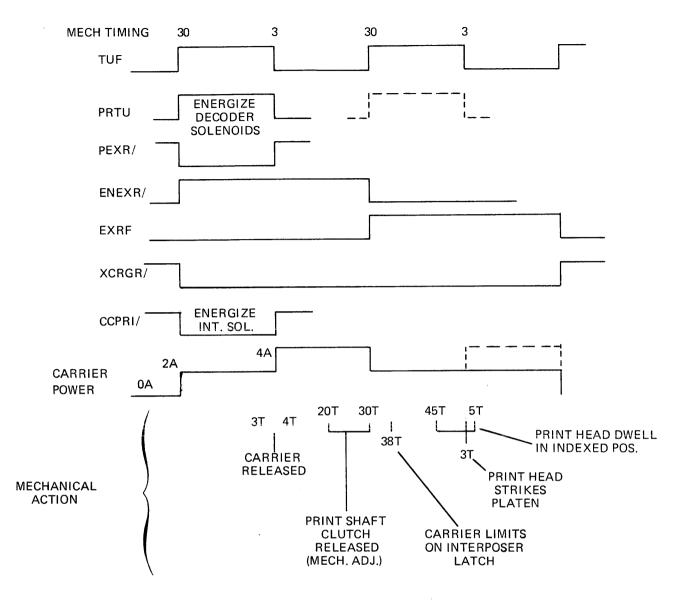

#### **BASIC TIMING**

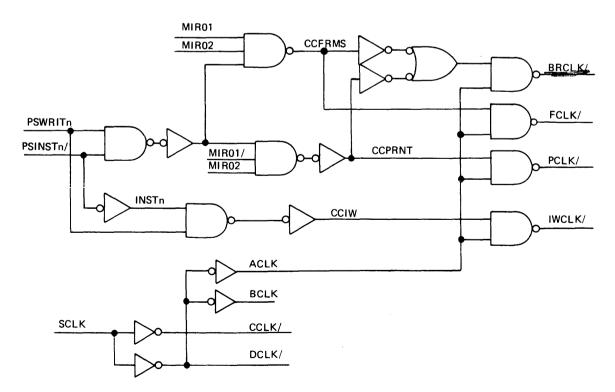

The processor provides the IOC with clock pulses (CDSCLKn) at a rate of 1 MHz. This clock signal is redeveloped, distributed, and used for various operations between the IOC and processor.

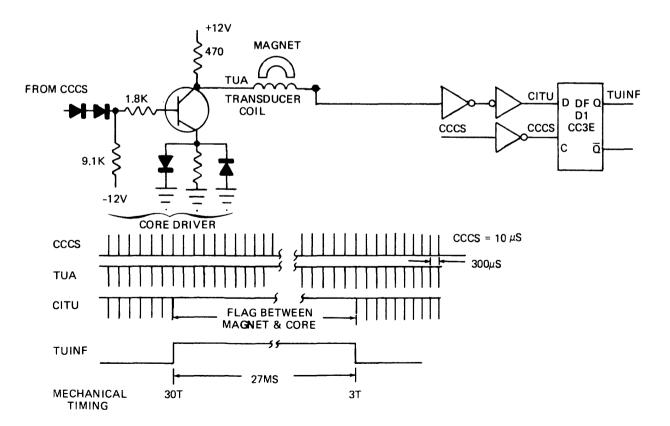

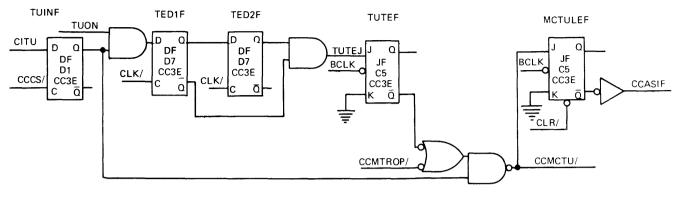

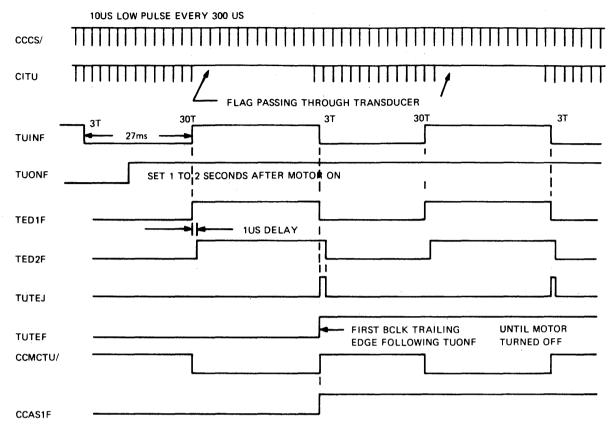

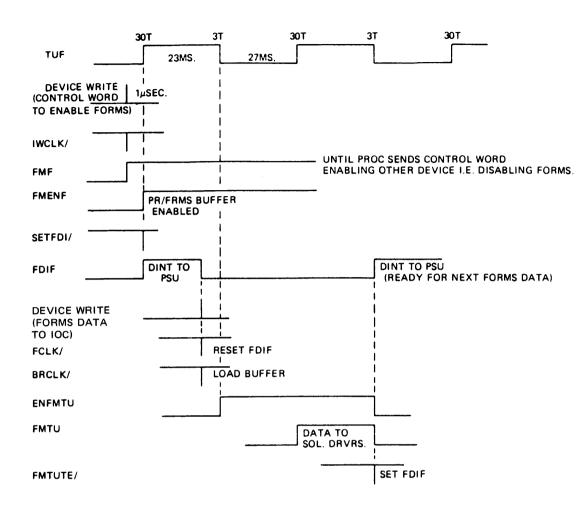

To synchronize logic functions of the IOC with mechanical sections of the console, a timer unit signal (CITU) is generated by a transducer core readout from a rotating shaft in the console. A timing pulse TUA is generated once every 300 microseconds.

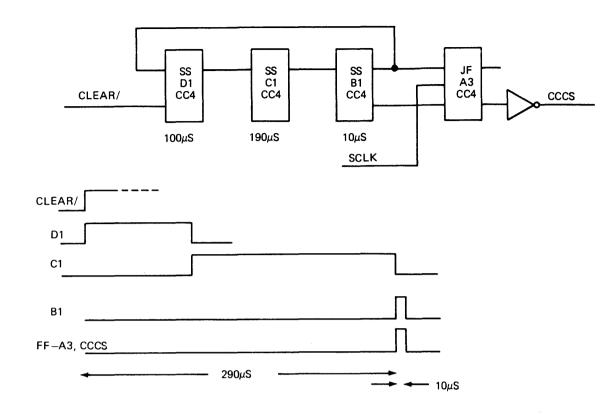

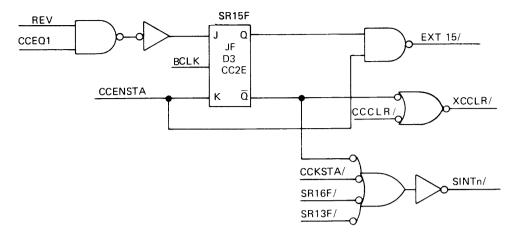

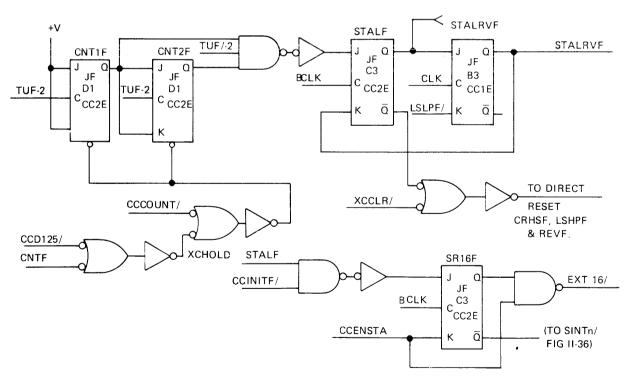

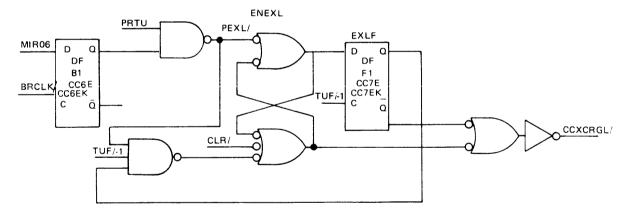

To strobe the transducer operation, signal CCCS is generated by three single-shot devices and a JK flip-flop (Figure II-1). This circuit produces a 10-microsecond pulse every 300 microseconds which is routed to the transducer core driver circuit. If the flag on the rotating shaft is not between the transducer and its associated magnet, then the field of the magnet saturates the transducer core so that it exhibits a low inductive impedance. Thus, when CCCS is applied to the circuit, the output of the transducer goes low. If a flag is present, it provides a shunt path for the magnetic field, the transducer core exhibits a high inductive impedance and, when CCCS is applied to the circuit, the output of the transducer remains high (Figure II-2). With CITU high, the timer unit input flip-flop (TUINF) remains in the set condition.

#### **KEYBOARD CONTROL**

To enable data to be read from the console keyboard, the processor must send a control word with MIR15 bit set, to the console to enable the keyboard strobe circuit. However, when the system is initially turned on, or if the halt and clear pushbutton is used, the keyboard strobe circuit is automatically enabled.

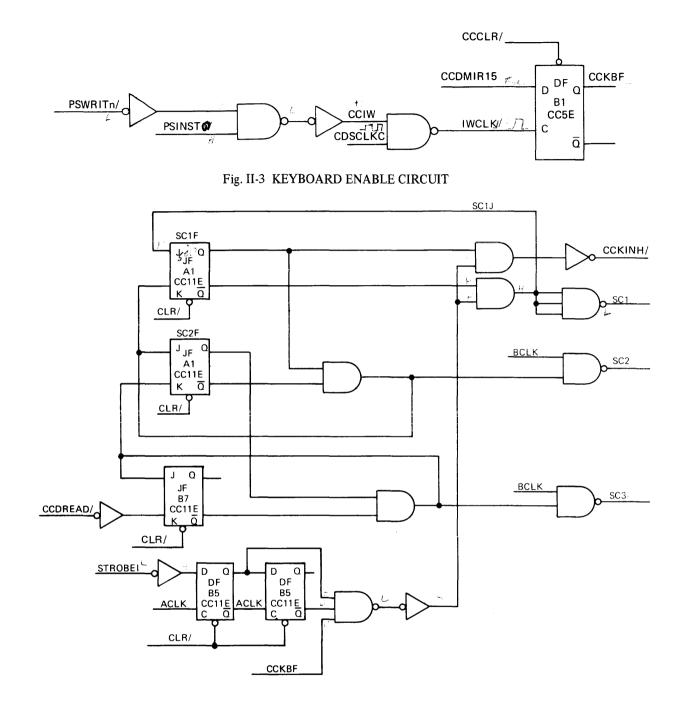

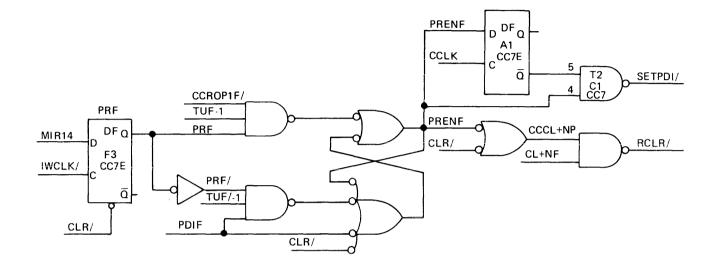

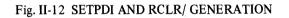

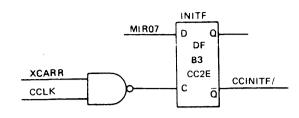

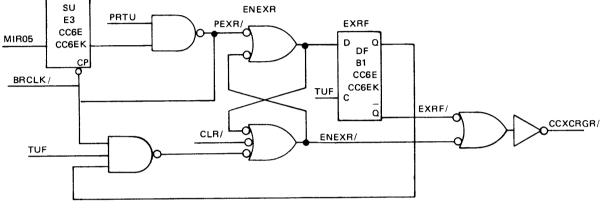

The keyboard control circuit is shown in Figure II-3. The receipt of a write signal (PSWRITn/ is low) and an instruction signal (PSINSTn is high) from the processor produces signal CCIW. CCIW is gated with the system clock to generate IWCLK/. With CCDMIR15 high, keyboard enable flip-flop KBF is set. Whenever the clear signal (CCCLR/) is present, the keyboard enable flip-flop is direct-set.

#### KEYBOARD BUFFER

A three-character first-in, first-out buffer is dedicated to keyboard operation. When any key is pressed, the keyboard ready status bit is set and a data interrupt signal is sent to the processor if the keyboard is enabled.

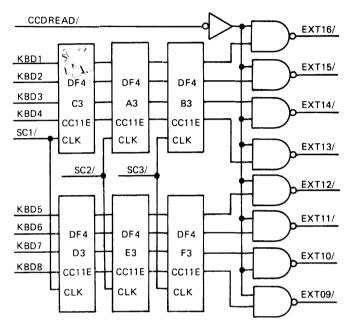

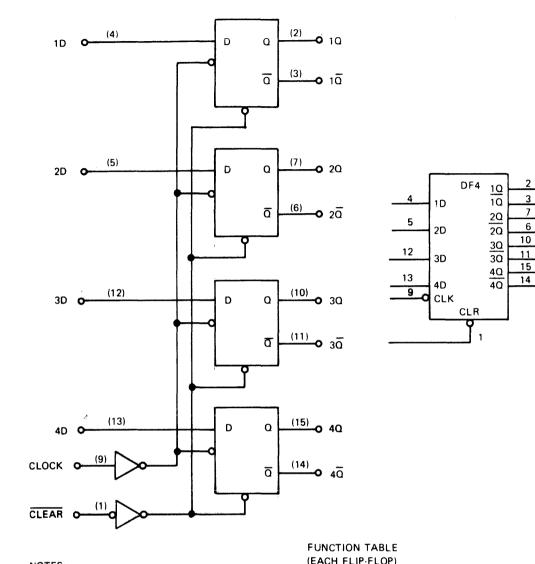

The shift clock pulses SC1/, SC2/, and SC3/ are used to clock keyboard data through the three stages of the keyboard buffer (Figure II-4). The keyboard buffer is comprised of six quad D-type flip-flop IC's (Figure II-5).

Initially, SC1F and SC2F flip-flops are reset by the system clear signal. When a key is pressed, the keyboard data (KBD1 through KBD8) is applied to the first stage of the buffer. Pressing a key also generates the keyboard strobe signal STROBEI. Signal STROBEI is gated with CCKBF. The resulting signal is inverted and gated with the  $\overline{Q}$  side of flip-flop SC1F which produces SC1J. Signal SC1J is inverted to produce clock pulse SC1/ and is also fed back to set flip-flop SC1F. Input data from the first stage of the buffer is transferred to its output and to the input of the second stage on the positive edge of signal SC1/.

The output of the Q-side of flip-flop SC1F is gated with the  $\overline{Q}$  side of flip-flop SC2F to set flip-flop SC2F, reset flip-flop SC1F, and generate an SC2/ pulse. On the positive edge of SC2/ the input data at the second stage is transferred to the input of the third stage.

The presence of signal CCDREAD/ (a read signal is present without an instruction signal) with flip-flop SC2F set, produces clock pulse SC3/. On the positive edge of pulse SC3/ the input data on the third stage of the keyboard buffer is applied to the MIR lines to the processor.

Fig. II-4 KEYBOARD BUFFER SHIFT CLOCK AND INTERRUPT NOT HONORED

# INTERRUPT NOT HONORED

The interrupt-not-honored status is generated when a key is pressed before a keyboard character has been shifted from the first stage of the keyboard buffer. This condition results in a lost keyboard character. When the processor is notified of this condition, it enters an error routine to notify the operator that the condition must be corrected.

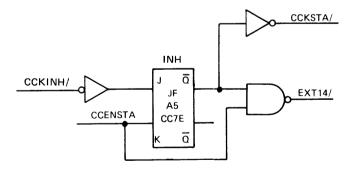

The shift clock pulse SC1/ is generated by the Q output of flip-flop SC1F and the keyboard strobe

(STROBEI). Signal SC1 sets the SC1F flip-flop (Figure II-4), whose output generates SC2/ and also causes SC1F to be reset. If a STROBEI pulse is received before SC1F is reset, the interrupt-not-honored (CCKINH/) signal is generated, indicating that a character is still present in the first buffer stage. Signal CCKINH/ sets the INH flip-flop (Figure II-6), which sends a status interrupt to the processor (CCKSTA) and sets the interrupt-not-honored bit (EXT14/) in the status word.

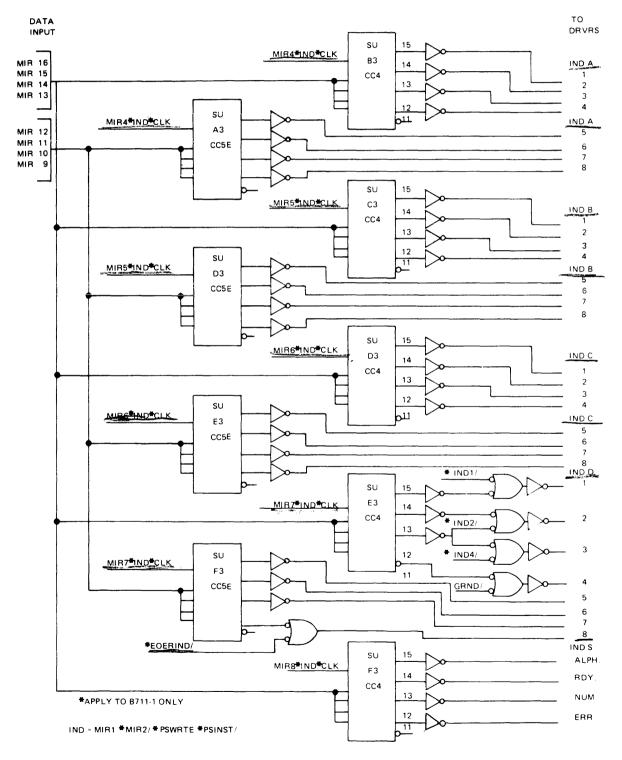

#### INDICATOR CONTROL

The indicators provide a visual indication to the console operator of machine and program status and of required keyboard entries. The indicators are lit by the generation of an indicator data word by the processor firmware; data interrupts are not involved in this implementation.

Fig. II-5 KEYBOARD BUFFER OUTPUT

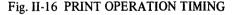

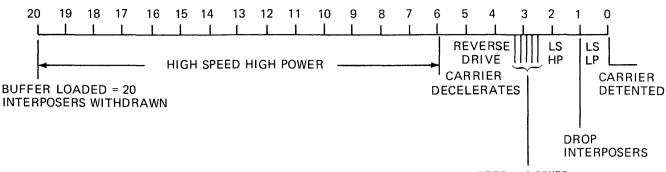

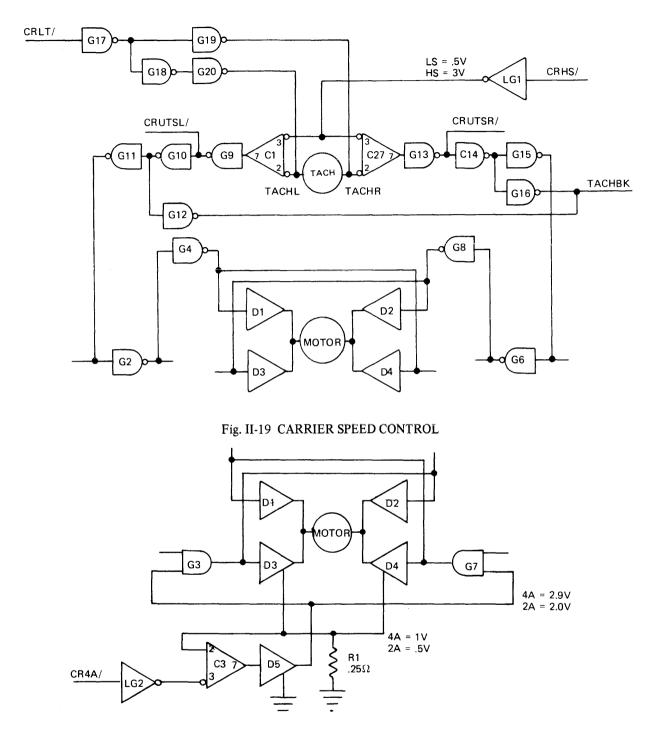

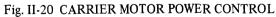

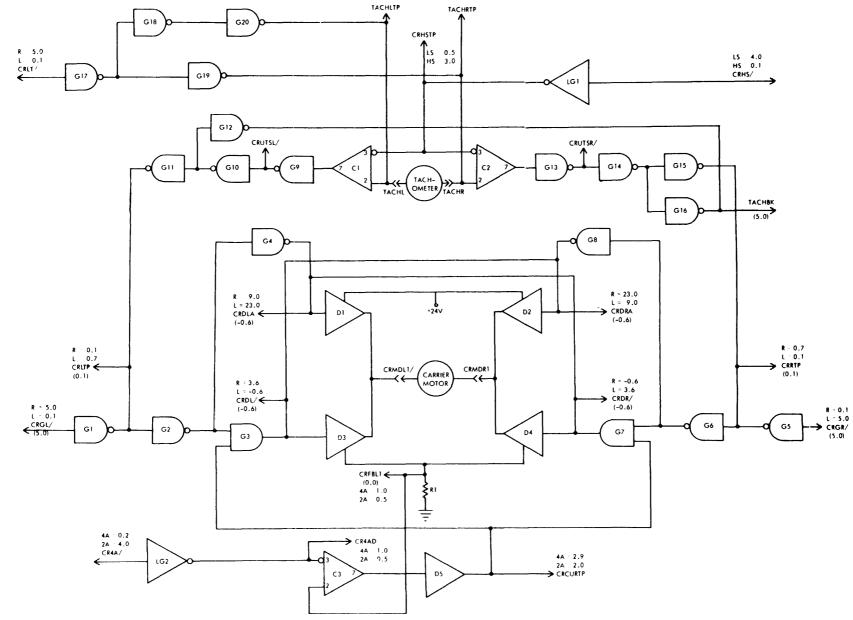

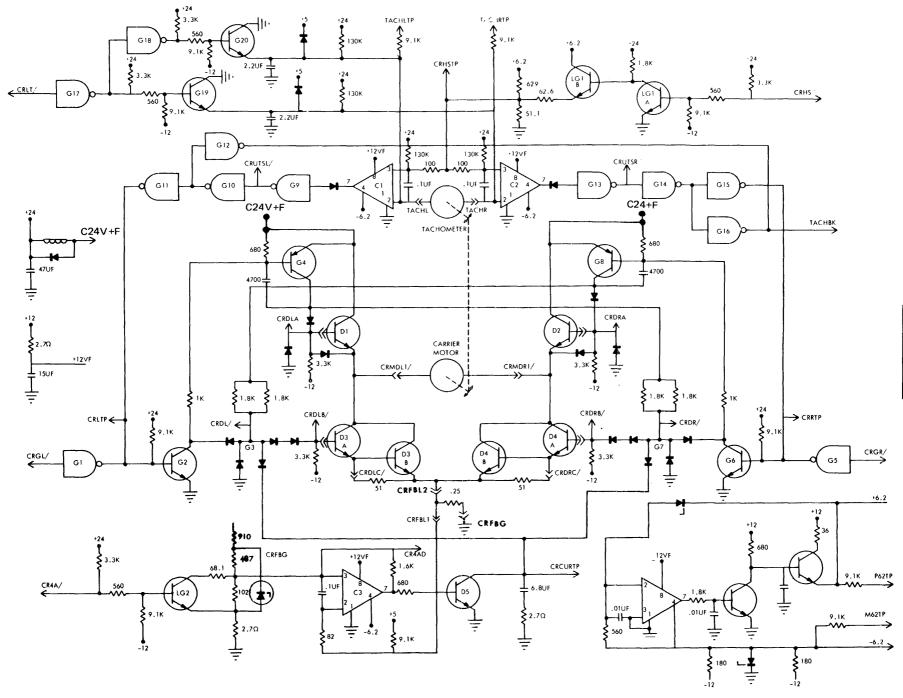

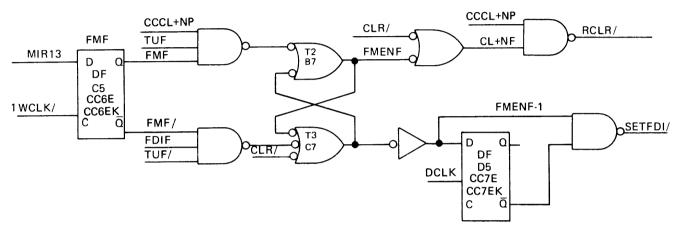

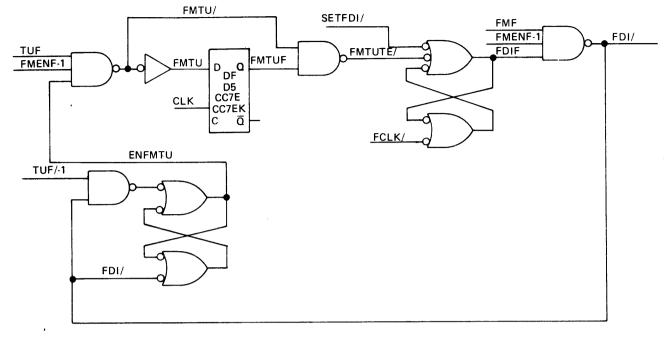

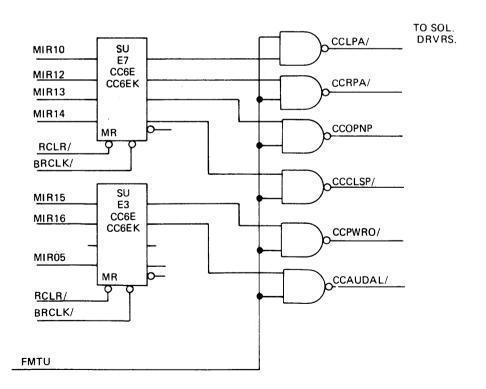

Fig. II-6 INTERRUPT NOT HONORED